第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本開示の実施形態は、広くは集積回路分野に関し、特にヘテロ構造電界効果トランジスタとその製造方法に関する。

【背景技術】

【0002】

ヘテロ構造電界効果トランジスタは、一般に、異なるバンドギャップを有する2つの半導体材料間に形成されたヘテロ接合を含む。高移動度電荷キャリアは、例えば、広いバンドギャップ層(例えばn−型ドナー供給層)と狭いバンドギャップ層とのヘテロ接合を用いて形成され得る。ゲート端子への印加電圧によって制御される電流は、一般にこれらの層の界面の非常に狭いチャンネルに閉じ込められて、ソース端子とドレイン端子間を流れる。

【発明の概要】

【発明が解決しようとする課題】

【0003】

ヘテロ構造電界効果トランジスタは、極超短波(UHF)からミリ波周波数に亘って適切な電力性能を呈し得るが、電流デバイスでは、電流崩壊、ゲートリークおよび高温信頼性に対する課題が生じ得る。例えば、高電力無線周波数(RF)スイッチ用途を含む種々の用途において、電流HEMTに関して、高絶縁破壊電圧、低リークおよび高い信頼性を有するデバイスが望ましい。

【図面の簡単な説明】

【0004】

添付図面と以下の詳細な説明によって、実施形態は容易に理解されるであろう。説明を容易にするために、同じ構成要素には同じ符号を付す。実施形態は例示として示されるものであり、添付図面の形状を制限するものではない。

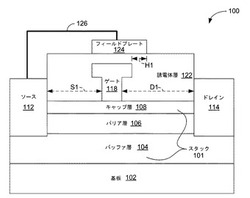

【図1】種々の実施形態に係る集積回路(IC)デバイスの概略横断面図である。

【図2】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面である。

【図3】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面図である。

【図4】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面図である。

【図5】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面図である。

【図6】種々の実施形態に係る集積回路デバイスの製造方法を示すフロー図である。

【図7】種々の実施形態に係るICデバイスを備えるシステムの概略図である。

【発明を実施するための形態】

【0005】

本開示の実施形態は、例えば高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの構成形態やその製造方法およびシステムを提供するものである。以下の詳細な説明では、本明細書の一部を成す添付図面を参照する。図面中、同じ符号は同じ部品を示し、また、本開示の主題が実施された実施形態は、例示として示されるものである。他の実施形態を用いることも可能であり、また、構造や論理的な変更が本開示の範囲を逸脱することなく可能であることは理解されるべきである。従って、以下の詳細な説明は制限的な意味合いで捉えられるものではなく、実施形態の範囲は、添付の請求項およびその均等物によって画定されるものである。

【0006】

本開示の目的のために、「AおよびまたはB」は、(A)、(B)または(AおよびB)を意味する。本開示の目的のために、「A、BおよびまたはC」は、(A)、(B)、(C)、(AおよびB)、(AおよびC)、(BおよびC)または(A、BおよびC)を意味する。

【0007】

以下の説明では、「ある実施形態では」または「実施形態では」が使用されるが、これらはそれぞれ、1つまたは複数の同じであっても異なっていてもよい実施形態を指す。また、本開示の実施形態に関して使用される「備える」、「含む」、「有する」などは同意語である。また、「連結された」は、直接接続、間接接続あるいは間接的な伝達を指す。

【0008】

「連結された」とその派生語も本明細書で使用されるが、この「連結された」は、以下の1つまたは複数を指す。すなわち、2つ以上の要素が直接物理的または電気的に接触しているか、あるいは、2つ以上の要素が互いに間接的に接触し、さらには互いに協働もしくは相互作用しているか、あるいは、互いに連結しているとされる要素間に、1つまたは複数の他の要素が連結されている、ことを意味する。

【0009】

種々の実施形態において、「第2の層上で形成された第1の層」は、前記第2の層の上部に前記第1の層が形成されており、該第1の層の少なくとも一部が、該第2の層の少なくとも一部と直接接触(例えば、物理的およびまたは電気的な直接接触など)しているか、あるいは間接接触(例えば、第1の層と第2の層間に、1つまたは複数の他の層を有しているなど)していることを意味する。

【0010】

図1は、種々の実施形態に係る集積回路(IC)デバイス100の概略横断面図である。ICデバイス100は、例えばHEMTデバイスであってもよい。

【0011】

ICデバイス100は、基板102上で形成されてもよい。基板102は、一般に、その上にスタックされた層(あるいは単に「スタック101」)が堆積される支持材を含む。ある実施形態では、基板102は、シリコン(Si)、炭化ケイ素(SiC)、酸化アルミニウム(Al2O3)すなわち「サファイア」、窒化ガリウム(GaN)およびまたは窒化アルミニウム(AlN)を含む。他の実施形態では、基板102に対して、第II〜VI族および第III〜V族の好適な半導体材料系を含む他の材料が用いられる。ある実施形態では、基板102は、その上にバッファ層104の材料がエピタキシャル成長できる任意の材料またはその材料の組み合わせで構成されていてもよい。

【0012】

基板102上に形成されたスタック101は、1つまたは複数のヘテロ接合/ヘテロ構造を形成する異なる材料から成るエピタキシャル堆積層を含んでいてもよい。スタック101の層はその場(in−situ)形成されてもよい。すなわち、スタック101は、基板102を取り出さずにその構成層を形成する(例えばエピタキシャル成長させる)製造装置(例えばチャンバ)内で、基板102上に形成されてもよい。

【0013】

一実施形態では、ICデバイス100のスタック101は、基板102上に形成されたバッファ層104を含む。バッファ層104は、ICデバイス100の基板102と他の構成要素(例えばバリア層106)間の結晶構造転移を提供し、その結果、この2つの間のバッファ層または絶縁層として働く。例えば、バッファ層104によって、基板102と他の格子不整合材料(例えばバリア層106)間の応力緩和がなされてもよい。バッファ層104は、基板102とエピタキシャルに連結されていてもよい。他の実施形態では、基板102とバッファ層104間に核形成層(図示せず)が介在してもよい。

【0014】

一部の実施形態では、バッファ層104は、例えば窒化ガリウム(GaN)などの窒化物を含んでいてもよい。バッファ層104の厚みは、その下の基板102の表面に実質的に垂直な方向において、1〜2μmであってもよい。他の実施形態では、バッファ層104は、他の好適な材料およびまたは厚みを有していてもよい。一部の実施形態では、バッファ層104は非ドープであってもよい。

【0015】

スタック101は、バッファ層104上に形成されたバリア層106をさらに含んでいてもよい。バリア層106とバッファ層104間に、ヘテロ接合が形成されていてもよい。バリア層106のバンドギャップエネルギーは、バッファ層104のそれより大きくてもよい。バリア層106は、可動電荷キャリアを供給するより広いバンドギャップ層であってもよく、バッファ層104は、可動電荷キャリアの経路を提供するより狭いバンドギャップ層であってもよい。作動中(例えば、ゲート端子(以後、ゲート118)に電圧印加時)は、二次元電子ガス(2DEG)がバッファ層104とバリア層106との界面に形成され、これによって、ソース端子(以後、ソース112)とドレイン端子(以後、ドレイン114)間に電流(例えば、前記可動電荷キャリア)が流れてもよい。一部の実施形態では、バリア層106は、バッファ層104にエピタキシャルに連結されてもよい。

【0016】

バリア層106は、広範な好適な材料系の内の任意のもので形成されてもよい。バリア層106は、例えば、インジウム(In)およびまたはガリウム(Ga)と共に、アルミニウム(Al)および窒素(N)を含んでいてもよい。一実施形態では、バリア層106は、窒化ガリウムアルミニウム(AlxGa1−xN)(xは、アルミニウムとガリウムとの相対量を表わす0〜1の値)であってもよい。一部の実施形態では、xは0.15〜0.3であるが、他の実施形態では、他の値も取り得る。

【0017】

バリア層106がAlGaNである実施形態では、バリア層106の厚みは、その下のバッファ層104の表面に実質的に垂直な方向において、160〜300Åであってもよい。他の実施形態では、バリア層106は、他の好適な材料およびまたは厚みを有していてもよい。

【0018】

別の実施形態では、バリア層106は、窒化アルミニウムインジウム(InyAl1−yN)(yは、インジウムとアルミニウムとの相対量を表す0〜1の値)であってもよい。バリア層106の組成は、バッファ層104のそれを補完するものであってもよい。一部の実施形態では、例えば、バリア層106中のインジウム組成は、yが0.17のものであってもよい。このインジウム濃度によって、バッファ層がGaNの場合のバッファ層104の格子構造と整合する格子構造がバリア層106に与えられる。こうした整合によって応力が低減でき得、ICデバイス100の作動中の信頼性が向上する。一方、インジウム濃度が17%から変化すると、格子構造不整合が増加し得、この変化によっても、特定の実施形態に対して望ましい動作特性が得られる。インジウム濃度を例えば13%までに減少させると、例えば、より多くの電荷チャージ(電流)を誘起し得るが、ICデバイス100の応力も増加し得る。反対に、インジウム濃度を例えば21%まで上げると、例えば、電荷は少なくなるが、ICデバイス100の全体の応力も低減させ得る。一部の実施形態では、yは0.13〜0.21であるが、他の実施形態では、他の値も取り得る。バリア層106がInAlNである実施形態では、バリア層とバッファ層間に、厚みが約5〜20ÅのAlNから成る他の層(図示せず)を堆積してもよい。

【0019】

バリア層106がInAlNである実施形態では、バリア層106の厚みは、その下のバッファ層104の表面に実質的に直角な方向において、30〜150Åであってもよい。他の実施形態では、バリア層106は、他の好適な材料およびまたは厚みを有していてもよい。例えば、AlまたはInの代わりに、他の第III族材料が含まれ得る。一部の実施形態では、バリア層106は非ドープであってもよい。

【0020】

スタック101は、バリア層106上に形成されたキャップ層108をさらに含んでいてもよい。キャップ層108は、バリア層106にエピタキシャルに連結されていてもよい。キャップ層108によって、ICデバイス100に対して高抵抗保護層およびまたはゲート絶縁体/誘電体が提供され得る。例えば、ICデバイス100は、キャップ層108がゲート118の絶縁体として機能する金属−絶縁半導体(MIS)電界効果トランジスタであってもよい。キャップ層108を含むMIS構造によって、例えば交流(AC)−直流(DC)変換器やDC−DC変換器、DC−AC変換器などの電力調整用途を含む電力スイッチング用途用の効率的なスイッチングデバイスが提供され得る。ゲート118は、キャップ層108を通してバリア層106に容量連結されていてもよい。

【0021】

キャップ層108は、広範な好適な材料系の内の任意のもので構成されてもよい。種々の実施形態では、キャップ層108は、インジウム(In)と組み合わされた窒素(N)、アルミニウム(Al)およびまたはガリウム(Ga)を含んでいてもよい。ある実施形態では、キャップ層108は、窒化アルミニウム(AlN)または窒化ガリウム(GaN)であってもよい。他の実施形態では、キャップ層108に対して、その他の好適な材料を使用してもよい。

【0022】

一部の実施形態では、キャップ層108を比較的低温(例えば500℃〜600℃)で成長させてもよい。例えば、比較的高温(例えば1000℃〜1100℃)で成長させたAlNまたはGaNからは、より単結晶型の格子構造を有する材料が得られ、これによって、付随的なトラップ形成により表面保護に対してより反応する圧電性を有する材料が得られる。比較的高温で形成したキャップ層108がICデバイス100に使用されると、こうした材料特性のために、電流崩壊およびゲートリークが増え得る。キャップ層108をより低温で形成することによって、より多結晶の格子構造を有する材料が得られ、このために、トラップ形成が低減でき、ICデバイス100の電流崩壊とゲートリークが軽減できる。一部の実施形態では、キャップ層108は多結晶材料を含む。種々の実施形態では、比較的低温で形成されたキャップ層108のバンドギャップエネルギーは5〜6電子ボルト(eV)である。キャップ層108のバンドギャップエネルギーは、バリア層106のそれより大きくてもよい。

【0023】

キャップ層108は、例えば、信号の無線送信用のマイクロ波からミリ波に亘る電力増幅スイッチングデバイス(例えばRF用途)などの、高電力、高効率および低ゲートリーク用途用に設計された厚みを有していてもよい。種々の実施形態では、キャップ層108の厚みは50Å未満である。キャップ層108の厚みが約50〜100Åより大きい場合は、効率的な電力増幅運転としては厚すぎる可能性がある。

【0024】

本明細書に記載のキャップ層108によって、ICデバイス100では、このようなキャップ層108を含まないICデバイスに対して、リークおよびまたは電流崩壊が低減し、絶縁破壊電圧、順電圧、アイドル電流のドリフトおよび信頼性が向上する。ここに記載のキャップ層108によってさらに、ICデバイス100の直線性の向上(例えば、広いトランスコンダクタンス、ゲート−ソース間容量の変動の減少)とひずみの減少が得られ、これによって、信号の振幅/相の再現性(例えば振幅変調(AM)からAMへの変換およびAMから位相変調(PM)への変換など)が向上し得る。

【0025】

ICデバイス100は、キャップ層108上に形成されたゲート118をさらに含む。ゲート118は、ICデバイス100の接続端子の役目をする。ゲート118は、キャップ層108に直接連結されていてもよい。

【0026】

図示のように、ゲート118は、キャップ層108に直接に連結されたトランク部すなわち底部と、該トランク部から、ゲート118の下のキャップ層108の表面に実質的に平行な逆方向に離れるように延在する頂部と、を有していてもよい。ゲート118のトランク部および蓋部のこうした構造をT−形ゲートと呼んでもよい。一部の実施形態では、ゲート118は、絶縁破壊電圧を向上させ得る、およびまたはゲート118とドレイン114間の電界を低減させ得るフィールドプレートであってもよい。ゲート118のトランク部の厚みは、その下のキャップ層108の表面に実質的に平行な方向において、約300〜約1400Åであってもよい。

【0027】

ゲート118は一般に、金属などの導電性材料で構成される。一部の実施形態では、ゲート118は、ニッケル(Ni)、プラチナ(Pt)、イリジウム(Ir)、モリブデン(Mo)、金(Au)およびまたはアルミニウム(Al)であってもよい。ある実施形態では、キャップ層108とゲートコンタクトさせるために、Ni、Pt、IrまたはMoを含む材料がゲート118のトランク部に配置され、また、ゲート118の導電性と低抵抗を確実にするために、Auを含む材料がゲート118の頂部に配置されている。種々の実施形態では、ゲート118は、高電子移動度トランジスタ(HEMT)デバイスの一部である。

【0028】

ICデバイス100は、キャップ層108上に形成されたソース112とドレイン114を含み得る。図示のように、ソース112とドレイン114はそれぞれ、キャップ層108およびバリア層106を通ってバッファ層104内に延在していてもよい。種々の実施形態では、ソース112とドレイン114はオーミックコンタクトしている。ソース112とドレイン114は、標準の成長コンタクトより比較的低接触抵抗であり得る再成長コンタクトであってもよい。一部の実施形態では、ソース112とドレイン114の接触抵抗は約0.01Ω・mmである。

【0029】

ソース112とドレイン114はそれぞれ、金属などの導電性材料で構成されていてもよい。ある実施形態では、ソース112とドレイン114はそれぞれ、チタン(Ti)、アルミニウム(Al)、モリブデン(Mo)、金(Au)およびまたはシリコン(Si)を含む。他の実施形態では、他の材料が使用できる。

【0030】

ある実施形態では、ドレイン114とゲート118間の距離D1は、ソース112とゲート118間の距離S1より大きい。一部の実施形態では、距離D1は、ドレイン114とゲート118間の最短距離であってもよく、距離S1は、ソース112とゲート118間の最短距離であってもよい。距離S1を距離D1より短くすることによって、ドレイン114に対してゲート118の絶縁破壊電圧を向上させ得、およびまたはソース112の抵抗を低減させ得る。

【0031】

一部の実施形態では、キャップ層108上に誘電体層122を形成してもよい。誘電体層122は、例えば窒化ケイ素(SiN)を含んでいてもよい。他の実施形態では、誘電体層122に対して、他の材料が使用できる。一部の実施形態では、キャップ層108に連結された誘電体層122の少なくとも一部は、スタック101を形成するその場プロセス中に、エピタキシャル堆積によって形成される。誘電体層122は、ゲート118を実質的に封入してもよい。誘電体層122は、ICデバイス100の保護層の役目をする。

【0032】

ICデバイス100は、絶縁破壊電圧の向上およびまたはゲート118とドレイン114間の電界低減のために、誘電体層122上で形成されたフィールドプレート124を含んでいてもよい。フィールドプレート124は、導電性材料126を用いて、ソース112に電気的に連結されていてもよい。導電性材料126は、例えば、誘電体層122上に電極あるいは線状構造として堆積された金(Au)などの金属を含んでいてもよい。他の実施形態では、導電性材料126に対して、他の好適な材料を用いてもよい。

【0033】

フィールドプレート124は一般に、金属などの導電性材料で構成され、ゲート118に関連して説明した材料を含んでいてもよい。フィールドプレート124は、誘電体層122を通してゲート118に容量連結されていてもよい。一部の実施形態では、フィールドプレート124とゲート118間の最短距離は1000〜2000Åである。図示のように、フィールドプレート124のオーバーハング領域を設けるために、該プレートの一部がゲート118の真上に配置され、別の部分はその真上に形成されないように、ゲート118の上部にフィールドプレート124を形成してもよい。一部の実施形態では、フィールドプレート124の該オーバーハング領域は、ゲート118の頂部端部より距離H1だけ延在している。一部の実施形態では、距離H1は0.2〜1μmであってもよいが、他の実施形態では、他の数値であってもよい。

【0034】

図2は、種々の実施形態に係る別の集積回路(IC)デバイス200の概略横断面である。図2では、ゲート218のトランク部がキャップ層108内に距離Rだけ延在している点を除いて、ICデバイス200は、図1のICデバイス100に関連して説明した実施形態に実質的に適合していてもよい。例えば、形成したキャップ層108から材料を除去するための異方性エッチングなどのエッチングプロセスにより、キャップ層108に凹部を設け、その凹部にゲート218を形成してもよい。他の実施形態では、ゲート218がキャップ層108内に延在するようにゲート218を形成する他の方法が用いられる。キャップ層108内に延在するゲート218を設けることによって、ICデバイス200の絶縁破壊電圧を向上でき、およびまたは電流崩壊を低減し得る。一部の実施形態では、Rは10〜30Åの距離を表わすが、他の実施形態では、他の値であってもよい。

【0035】

図3は、種々の実施形態に係る別の集積回路(IC)デバイス300の概略横断面図である。図示のように、図3では、キャップ層108がバリア層106上に形成された第1の部分308と、前記第1の部分上に形成された第2の部分309と、を含む点を除いて、図1のICデバイス100に関連して説明した実施形態に実質的に適合していてもよい。

【0036】

第1の部分308は、例えば、本明細書に記載の高温プロセスによって形成された(例えば、1000℃〜1100℃の比較的高温で成長させた)GaNまたはAlNのいずれかの層であってもよい。一部の実施形態では、第1の部分308は、実質的なあるいは完全な単結晶材料を含んでいてもよい。第1の部分308の厚みは20〜30Åであってもよい。他の実施形態では、他の材料または厚みが用いられてもよい。

【0037】

第2の部分309は、例えば、本明細書に記載の低温プロセスによって形成された(例えば、500℃〜600℃の比較的低温で成長させた)GaNまたはAlNいずれかの層であってもよい。第2の部分309は、ゲート118に対して、リークを防止し転位やその他の欠陥を低減する界面あるいはバッファ層の役目をする。一部の実施形態では、第2の部分309は、実質的なあるいは完全な多結晶材料を含む。第2の部分309の厚みは20〜30Åであってもよい。他の実施形態では、他の材料または厚みが用いられてもよい。一部の実施形態では、第1の部分308および第2の部分309は、スタック101の一部としてエピタキシャルに堆積されてもよい。

【0038】

図4は、種々の実施形態に係る別の集積回路(IC)デバイス400の概略横断面図である。図示のように、図4では、ICデバイス400がキャップ層108上に形成されたその場誘電体409を含む点を除いて、図1のICデバイス100に関連して説明した実施形態に実質的に適合していてもよい。

【0039】

その場誘電体409は、例えば、スタック101の一部としてキャップ層108の上に形成された窒化ケイ素(SiN)あるいは他の好適な誘電体材料などの誘電体層であってもよい。一部の実施形態では、その場誘電体409の厚みは50〜200Åであってもよい。他の実施形態では、その場誘電体409に対して、他の厚みおよびまたは材料が用いられてもよい。

【0040】

一部の実施形態では、その場誘電体409は、キャップ層108上にエピタキシャルに堆積され、基板102を取り出さずにスタック101の構成層を形成する(例えばエピタキシャル成長させる)製造装置(例えばチャンバ)内で形成されてもよい。図示のように、開口を形成するためのエッチングプロセスなどの任意の好適なプロセスにより、その場誘電体409に凹部を設け、そのキャップ層108上にゲート118を形成してもよい。誘電体層122は、その場誘電体409の形成に用いられたその場プロセスに付帯的なプロセスにおけるゲート118の形成後に堆積されてもよい。その場誘電体409によって、汚染が低減され得、およびまたはICデバイス400のトラップ密度を低減させる界面が提供され得る。

【0041】

図5は、種々の実施形態に係る別の集積回路(IC)デバイス500の概略横断面図である。ICデバイス500は、基板102上に形成されたドープ層504を含む。ドープ層504は、例えば、図1のICデバイス100に関連して、基板102に対して説明した材料を含む種々の材料を含むことができる。種々の実施形態では、ドープ層504は、n−型シリコン(Si)などの不純物ドープされる。ドープ層504の厚みは500〜1500Åであってもよい。他の実施形態では、ドープ層504に対して、他の好適なドーパント、材料およびまたは厚みが用いられる。図5のICデバイス500のその他の特長は、図1のICデバイス100に関連して上記した実施形態に適合していてもよい。

【0042】

ICデバイス100、200、300、400およびまたは500に関連して説明した実施形態は、種々の実施形態において好適に組み合わせられてもよい。例えば、図4のその場誘電体409は、図3の第1の部分308と第2の部分309とを有するキャップ層108上に形成されてもよく、およびまたは図2のゲート218は、図3または4のキャップ層108内に延在して形成されてもよい。

【0043】

図6は、種々の実施形態に係る集積回路デバイス(例えば、図1、2、3あるいは4それぞれのICデバイス100、200、300あるいは400)の製造方法600を示すフロー図である。方法600は、602において、基板(例えば図1の基板102)上にバッファ層(例えば図1のバッファ層104)を形成するステップと、604において、前記バッファ層上にバリア層(例えば図1のバリア層106)を形成するステップと、606において、前記バリア層上にキャップ層(例えば図1、2、3、あるいは4のキャップ層108)を形成するステップと、を備える。種々の実施形態では、これらの層間に介在させるために他の層を形成してもよい。

【0044】

種々の実施形態では、前記バッファ層、バリア層およびキャップ層はそれぞれ、分子線エピタキシャル法(MBE)、原子層エピタキシャル法(ALE)、化学ビームエピタキシャル法(CBE)およびまたは有機金属気相成長法(MOCVD)によってエピタキシャルに堆積される。前記バッファ層、バリア層および(または)キャップ層は、図1〜4に関連して上記した実施形態に準じて形成されてもよい。前記バッファ層、バリア層およびキャップ層は、本明細書に記載のその場プロセスを用いて形成された層のスタック(例えば図1のスタック101)の一部であってもよい。他の実施形態では、他の好適な堆積法が用いられる。スタックの層に対する材料およびまたは厚みは、図1、2、3および4それぞれのICデバイス100、200、300および400に関連して上記した実施形態と適合していてもよい。

【0045】

方法600は、608において、ソース(例えば図1のソース112)とドレイン(例えば図1のドレイン114)を形成するステップをさらに備えてもよい。種々の実施形態において、前記ソースとドレインは前記キャップ層上に形成されてもよい。ある実施形態では、例えば蒸発プロセスを用いて前記ソースとドレインが形成される領域内のキャップ層上に、1つまたは複数の金属などの材料が堆積される。前記ソースとドレインを形成するための材料は、以下の順序で堆積された金属を含んでいてもよい。チタン(Ti)→アルミニウム(Al)→モリブデン(Mo)→チタン(Ti)→金(Au)。前記堆積材料を加熱(例えば、高速熱アニールプロセスを用い約850℃で約30秒間)し、この材料を貫通させ、前記キャップ層、バリア層およびまたはバッファ層の下位の材料と溶融させてもよい。一部の実施形態では、前記ソースとドレインはそれぞれ、キャップ層を通ってバッファ層内に延在している。前記ソースとドレインの厚みは1000〜2000Åであり得る。他の実施形態では、ソースとドレインに対して、他の厚みが用いられる。

【0046】

ソースとドレインを再成長プロセスで形成し、低減された接触抵抗または低減されたオン抵抗を有するオーミックコンタクトを得てもよい。前記再成長プロセスでは、ソースとドレインが形成される領域では、キャップ層、バリア層およびまたはバッファ層の材料は選択的に除去される(例えば、エッチングされる)。これらの層が選択的に除去された領域に、高濃度ドープ材料(例えばn++材料)が堆積される。ソースとドレインの高濃度ドープ材料は、バッファ層104またはバリア層106に使用した材料と同様の材料であってもよい。例えば、バッファ層がGaNを含むシステムでは、前記選択的に除去した領域に、シリコン(Si)で高濃度にドープされたGaN系材料を厚みが400〜700Åになるまでエピタキシャルに堆積してもよい。前記高濃度ドープ材料は、分子線エピタキシャル法(MBE)、原子層エピタキシャル法(ALE)、化学ビームエピタキシャル法(CBE)、有機金属気相成長法(MOCVD)またはこれらの好適な組み合わせによってエピタキシャルに堆積できる。他の実施形態では、前記高濃度ドープ材料に対して、他の材料、厚みあるいは堆積法が用いられる。前記高濃度ドープ材料上に、例えば、チタン(Ti)およびまたは金(Au)を含む1つまたは複数の金属を、例えばリフトオフプロセスを用いて1000Å〜1500Åの厚みで形成/堆積できる。他の実施形態では、前記1つまたは複数の金属に対して、他の材料、厚みおよびまたは方法が用いられる。

【0047】

一部の実施形態では、ソースとドレインに高濃度ドープ材料を提供するために、不純物(例えばシリコン)を導入する注入法を用いた注入プロセスによって、ソースとドレインを形成してもよい。注入後、ソースとドレインを高温(例えば1100〜1200℃)でアニールする。前記再成長プロセスでは、前記注入後アニールに伴う高温を好適に避け得る。

【0048】

方法600は、610において、ゲート(例えば図1のゲート構造118)を形成するステップをさらに備えてもよい。前記キャップ層上に導電性材料を堆積することによって、該キャップ層上にゲートを形成してもよい。例えば、蒸発、原子層堆積(ALD)およびまたは化学蒸着法(CVD)を含む任意の好適な堆積プロセスによって、ゲート材料を堆積できる。前記ゲートがT−形ゲートである実施形態では、金属堆積/エッチングプロセスまたはリフトオフフプロセスを用いて、このT−ゲートのトランク部または頂部を形成してもよい。

【0049】

方法600は、612において、前記ゲート上に誘電体層(例えば図1の誘電体層122)を形成するステップをさらに備える。任意の好適な堆積法を用いて、誘電体材料を前記ゲート上およびまたはキャップ層上に堆積することにより、前記誘電体層を形成してもよい。

【0050】

方法600は、614において、前記誘電体層上にフィールドプレート(例えば図1のフィールドプレート124)を形成するステップをさらに備える。任意の好適な堆積法を用いて、導電性材料を前記誘電体層上に堆積することにより、前記フィールドプレートを形成してもよい。リソグラフィおよびまたはエッチングプロセスなどのパターニングプロセスを用いて、前記堆積した導電性材料部分を選択的に除去して前記フィールドプレートを形成できる。他の実施形態では、他の好適な方法を用いてもよい。方法600に関連して記載したものと同様な方法を行って、図5のICデバイス500を製造してもよい。

【0051】

特許請求される主題の理解に最も有用な方法で、種々の操作を複数の別個の操作として記載したが、これらの操作は必然的に順序依存であることを示唆するようには記載の順序を解釈すべきではない。これらの操作は、特に提示の順番に行われなくてもよい。記載の実施形態と異なる順番で、記載された操作を行ってもよい。追加の実施形態では、種々の追加の操作を行ってもよく、およびまたは記載の操作を省略してもよい。

【0052】

本明細書に記載のICデバイス(例えばICデバイス100、200、300、400または500)の実施形態およびこうしたICデバイス100を含む装置を、他の種々の装置およびシステムに組み込んでもよい。例となるシステム700のブロック図を図7に示す。図示のように、システム700は、電力増幅器(PA)モジュール702を備えており、このモジュール702は、一部の実施形態では、無線周波数(RF)PAモジュールであってもよい。図示のように、システム700は、電力増幅器モジュール702に連結されたトランシーバ704を備えていてもよい。電力増幅器モジュール702は、本明細書に記載のICデバイス(例えばICデバイス100、200、300、400または500)を備えていてもよい。

【0053】

電力増幅器モジュール702は、トランシーバ704からRF入力信号(RFin)を受信してもよい。電力増幅器モジュール702は、RF入力信号(RFin)を増幅してRF出力信号(RFout)を出力してもよい。図7でそれぞれTx−RFinおよびTx−RFoutで示されるRF入力信号(RFin)およびRF出力信号(RFout)は共に、送信チェーンの一部であってもよい。

【0054】

増幅されたRF出力信号(RFout)は、アンテナスイッチモジュール(ASM)706に与えられてもよく、このモジュールによって、アンテナ構造708経由で、RF出力信号(RFout)の無線(OTA)送信が実現される。また、ASM706は、アンテナ構造708経由でRF信号を受信し、その受信RF信号(Rx)を受信チェーンに沿ってトランシーバ704につなぐ。

【0055】

種々の実施形態では、アンテナ構造708は、例えば、ダイポールアンテナ、モノポールアンテナ、パッチアンテナ、ループアンテナ、マイクロストリップアンテナ、あるいはRF信号のOTA送信/受信に好適な任意の他の形式のアンテナを含む指向性アンテナおよびまたは全方向性アンテナの1つまたは複数を含んでいてもよい。

【0056】

システム700は、電力増幅を含む任意のシステムであってもよい。前記ICデバイス(例えばICデバイス100、200、300、400または500)は、例えば交流(AC)−直流(DC)変換器やDC−DC変換器、DC−AC変換器などの電力調整用途を含む電力スイッチング用途用の効率的なスイッチングデバイスを提供してもよい。種々の実施形態では、システム700は、高無線周波数電力と周波数における電力増幅には特に有用であり得る。例えば、システム700は、陸上および衛星通信、レーダーシステムおよび恐らく種々の産業および医学用途における利用のいずれか1つまたは複数に対して好適であり得る。より具体的には、種々の実施形態において、システム700は、レーダー装置、衛星通信装置、携帯電話、携帯電話基地局、ラジオ放送あるいはテレビ増幅器システムから選択された1つであり得る。

【0057】

説明の目的で実施形態を例示し記載したが、同じ目的を実現するように意図された、広範な代替となるおよびまたは均等な実施形態あるいは実施によって、本開示の範囲を逸脱することなくこれらの実施形態を置換できる。本出願は、本明細書で検討した実施形態に対するいかなる適応や変形もカバーするように意図される。従って、本明細書に記載の実施形態は、請求項とその均等物によってのみ限定されることが明白に意図される。

【技術分野】

【0001】

本開示の実施形態は、広くは集積回路分野に関し、特にヘテロ構造電界効果トランジスタとその製造方法に関する。

【背景技術】

【0002】

ヘテロ構造電界効果トランジスタは、一般に、異なるバンドギャップを有する2つの半導体材料間に形成されたヘテロ接合を含む。高移動度電荷キャリアは、例えば、広いバンドギャップ層(例えばn−型ドナー供給層)と狭いバンドギャップ層とのヘテロ接合を用いて形成され得る。ゲート端子への印加電圧によって制御される電流は、一般にこれらの層の界面の非常に狭いチャンネルに閉じ込められて、ソース端子とドレイン端子間を流れる。

【発明の概要】

【発明が解決しようとする課題】

【0003】

ヘテロ構造電界効果トランジスタは、極超短波(UHF)からミリ波周波数に亘って適切な電力性能を呈し得るが、電流デバイスでは、電流崩壊、ゲートリークおよび高温信頼性に対する課題が生じ得る。例えば、高電力無線周波数(RF)スイッチ用途を含む種々の用途において、電流HEMTに関して、高絶縁破壊電圧、低リークおよび高い信頼性を有するデバイスが望ましい。

【図面の簡単な説明】

【0004】

添付図面と以下の詳細な説明によって、実施形態は容易に理解されるであろう。説明を容易にするために、同じ構成要素には同じ符号を付す。実施形態は例示として示されるものであり、添付図面の形状を制限するものではない。

【図1】種々の実施形態に係る集積回路(IC)デバイスの概略横断面図である。

【図2】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面である。

【図3】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面図である。

【図4】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面図である。

【図5】種々の実施形態に係る別の集積回路(IC)デバイスの概略横断面図である。

【図6】種々の実施形態に係る集積回路デバイスの製造方法を示すフロー図である。

【図7】種々の実施形態に係るICデバイスを備えるシステムの概略図である。

【発明を実施するための形態】

【0005】

本開示の実施形態は、例えば高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの構成形態やその製造方法およびシステムを提供するものである。以下の詳細な説明では、本明細書の一部を成す添付図面を参照する。図面中、同じ符号は同じ部品を示し、また、本開示の主題が実施された実施形態は、例示として示されるものである。他の実施形態を用いることも可能であり、また、構造や論理的な変更が本開示の範囲を逸脱することなく可能であることは理解されるべきである。従って、以下の詳細な説明は制限的な意味合いで捉えられるものではなく、実施形態の範囲は、添付の請求項およびその均等物によって画定されるものである。

【0006】

本開示の目的のために、「AおよびまたはB」は、(A)、(B)または(AおよびB)を意味する。本開示の目的のために、「A、BおよびまたはC」は、(A)、(B)、(C)、(AおよびB)、(AおよびC)、(BおよびC)または(A、BおよびC)を意味する。

【0007】

以下の説明では、「ある実施形態では」または「実施形態では」が使用されるが、これらはそれぞれ、1つまたは複数の同じであっても異なっていてもよい実施形態を指す。また、本開示の実施形態に関して使用される「備える」、「含む」、「有する」などは同意語である。また、「連結された」は、直接接続、間接接続あるいは間接的な伝達を指す。

【0008】

「連結された」とその派生語も本明細書で使用されるが、この「連結された」は、以下の1つまたは複数を指す。すなわち、2つ以上の要素が直接物理的または電気的に接触しているか、あるいは、2つ以上の要素が互いに間接的に接触し、さらには互いに協働もしくは相互作用しているか、あるいは、互いに連結しているとされる要素間に、1つまたは複数の他の要素が連結されている、ことを意味する。

【0009】

種々の実施形態において、「第2の層上で形成された第1の層」は、前記第2の層の上部に前記第1の層が形成されており、該第1の層の少なくとも一部が、該第2の層の少なくとも一部と直接接触(例えば、物理的およびまたは電気的な直接接触など)しているか、あるいは間接接触(例えば、第1の層と第2の層間に、1つまたは複数の他の層を有しているなど)していることを意味する。

【0010】

図1は、種々の実施形態に係る集積回路(IC)デバイス100の概略横断面図である。ICデバイス100は、例えばHEMTデバイスであってもよい。

【0011】

ICデバイス100は、基板102上で形成されてもよい。基板102は、一般に、その上にスタックされた層(あるいは単に「スタック101」)が堆積される支持材を含む。ある実施形態では、基板102は、シリコン(Si)、炭化ケイ素(SiC)、酸化アルミニウム(Al2O3)すなわち「サファイア」、窒化ガリウム(GaN)およびまたは窒化アルミニウム(AlN)を含む。他の実施形態では、基板102に対して、第II〜VI族および第III〜V族の好適な半導体材料系を含む他の材料が用いられる。ある実施形態では、基板102は、その上にバッファ層104の材料がエピタキシャル成長できる任意の材料またはその材料の組み合わせで構成されていてもよい。

【0012】

基板102上に形成されたスタック101は、1つまたは複数のヘテロ接合/ヘテロ構造を形成する異なる材料から成るエピタキシャル堆積層を含んでいてもよい。スタック101の層はその場(in−situ)形成されてもよい。すなわち、スタック101は、基板102を取り出さずにその構成層を形成する(例えばエピタキシャル成長させる)製造装置(例えばチャンバ)内で、基板102上に形成されてもよい。

【0013】

一実施形態では、ICデバイス100のスタック101は、基板102上に形成されたバッファ層104を含む。バッファ層104は、ICデバイス100の基板102と他の構成要素(例えばバリア層106)間の結晶構造転移を提供し、その結果、この2つの間のバッファ層または絶縁層として働く。例えば、バッファ層104によって、基板102と他の格子不整合材料(例えばバリア層106)間の応力緩和がなされてもよい。バッファ層104は、基板102とエピタキシャルに連結されていてもよい。他の実施形態では、基板102とバッファ層104間に核形成層(図示せず)が介在してもよい。

【0014】

一部の実施形態では、バッファ層104は、例えば窒化ガリウム(GaN)などの窒化物を含んでいてもよい。バッファ層104の厚みは、その下の基板102の表面に実質的に垂直な方向において、1〜2μmであってもよい。他の実施形態では、バッファ層104は、他の好適な材料およびまたは厚みを有していてもよい。一部の実施形態では、バッファ層104は非ドープであってもよい。

【0015】

スタック101は、バッファ層104上に形成されたバリア層106をさらに含んでいてもよい。バリア層106とバッファ層104間に、ヘテロ接合が形成されていてもよい。バリア層106のバンドギャップエネルギーは、バッファ層104のそれより大きくてもよい。バリア層106は、可動電荷キャリアを供給するより広いバンドギャップ層であってもよく、バッファ層104は、可動電荷キャリアの経路を提供するより狭いバンドギャップ層であってもよい。作動中(例えば、ゲート端子(以後、ゲート118)に電圧印加時)は、二次元電子ガス(2DEG)がバッファ層104とバリア層106との界面に形成され、これによって、ソース端子(以後、ソース112)とドレイン端子(以後、ドレイン114)間に電流(例えば、前記可動電荷キャリア)が流れてもよい。一部の実施形態では、バリア層106は、バッファ層104にエピタキシャルに連結されてもよい。

【0016】

バリア層106は、広範な好適な材料系の内の任意のもので形成されてもよい。バリア層106は、例えば、インジウム(In)およびまたはガリウム(Ga)と共に、アルミニウム(Al)および窒素(N)を含んでいてもよい。一実施形態では、バリア層106は、窒化ガリウムアルミニウム(AlxGa1−xN)(xは、アルミニウムとガリウムとの相対量を表わす0〜1の値)であってもよい。一部の実施形態では、xは0.15〜0.3であるが、他の実施形態では、他の値も取り得る。

【0017】

バリア層106がAlGaNである実施形態では、バリア層106の厚みは、その下のバッファ層104の表面に実質的に垂直な方向において、160〜300Åであってもよい。他の実施形態では、バリア層106は、他の好適な材料およびまたは厚みを有していてもよい。

【0018】

別の実施形態では、バリア層106は、窒化アルミニウムインジウム(InyAl1−yN)(yは、インジウムとアルミニウムとの相対量を表す0〜1の値)であってもよい。バリア層106の組成は、バッファ層104のそれを補完するものであってもよい。一部の実施形態では、例えば、バリア層106中のインジウム組成は、yが0.17のものであってもよい。このインジウム濃度によって、バッファ層がGaNの場合のバッファ層104の格子構造と整合する格子構造がバリア層106に与えられる。こうした整合によって応力が低減でき得、ICデバイス100の作動中の信頼性が向上する。一方、インジウム濃度が17%から変化すると、格子構造不整合が増加し得、この変化によっても、特定の実施形態に対して望ましい動作特性が得られる。インジウム濃度を例えば13%までに減少させると、例えば、より多くの電荷チャージ(電流)を誘起し得るが、ICデバイス100の応力も増加し得る。反対に、インジウム濃度を例えば21%まで上げると、例えば、電荷は少なくなるが、ICデバイス100の全体の応力も低減させ得る。一部の実施形態では、yは0.13〜0.21であるが、他の実施形態では、他の値も取り得る。バリア層106がInAlNである実施形態では、バリア層とバッファ層間に、厚みが約5〜20ÅのAlNから成る他の層(図示せず)を堆積してもよい。

【0019】

バリア層106がInAlNである実施形態では、バリア層106の厚みは、その下のバッファ層104の表面に実質的に直角な方向において、30〜150Åであってもよい。他の実施形態では、バリア層106は、他の好適な材料およびまたは厚みを有していてもよい。例えば、AlまたはInの代わりに、他の第III族材料が含まれ得る。一部の実施形態では、バリア層106は非ドープであってもよい。

【0020】

スタック101は、バリア層106上に形成されたキャップ層108をさらに含んでいてもよい。キャップ層108は、バリア層106にエピタキシャルに連結されていてもよい。キャップ層108によって、ICデバイス100に対して高抵抗保護層およびまたはゲート絶縁体/誘電体が提供され得る。例えば、ICデバイス100は、キャップ層108がゲート118の絶縁体として機能する金属−絶縁半導体(MIS)電界効果トランジスタであってもよい。キャップ層108を含むMIS構造によって、例えば交流(AC)−直流(DC)変換器やDC−DC変換器、DC−AC変換器などの電力調整用途を含む電力スイッチング用途用の効率的なスイッチングデバイスが提供され得る。ゲート118は、キャップ層108を通してバリア層106に容量連結されていてもよい。

【0021】

キャップ層108は、広範な好適な材料系の内の任意のもので構成されてもよい。種々の実施形態では、キャップ層108は、インジウム(In)と組み合わされた窒素(N)、アルミニウム(Al)およびまたはガリウム(Ga)を含んでいてもよい。ある実施形態では、キャップ層108は、窒化アルミニウム(AlN)または窒化ガリウム(GaN)であってもよい。他の実施形態では、キャップ層108に対して、その他の好適な材料を使用してもよい。

【0022】

一部の実施形態では、キャップ層108を比較的低温(例えば500℃〜600℃)で成長させてもよい。例えば、比較的高温(例えば1000℃〜1100℃)で成長させたAlNまたはGaNからは、より単結晶型の格子構造を有する材料が得られ、これによって、付随的なトラップ形成により表面保護に対してより反応する圧電性を有する材料が得られる。比較的高温で形成したキャップ層108がICデバイス100に使用されると、こうした材料特性のために、電流崩壊およびゲートリークが増え得る。キャップ層108をより低温で形成することによって、より多結晶の格子構造を有する材料が得られ、このために、トラップ形成が低減でき、ICデバイス100の電流崩壊とゲートリークが軽減できる。一部の実施形態では、キャップ層108は多結晶材料を含む。種々の実施形態では、比較的低温で形成されたキャップ層108のバンドギャップエネルギーは5〜6電子ボルト(eV)である。キャップ層108のバンドギャップエネルギーは、バリア層106のそれより大きくてもよい。

【0023】

キャップ層108は、例えば、信号の無線送信用のマイクロ波からミリ波に亘る電力増幅スイッチングデバイス(例えばRF用途)などの、高電力、高効率および低ゲートリーク用途用に設計された厚みを有していてもよい。種々の実施形態では、キャップ層108の厚みは50Å未満である。キャップ層108の厚みが約50〜100Åより大きい場合は、効率的な電力増幅運転としては厚すぎる可能性がある。

【0024】

本明細書に記載のキャップ層108によって、ICデバイス100では、このようなキャップ層108を含まないICデバイスに対して、リークおよびまたは電流崩壊が低減し、絶縁破壊電圧、順電圧、アイドル電流のドリフトおよび信頼性が向上する。ここに記載のキャップ層108によってさらに、ICデバイス100の直線性の向上(例えば、広いトランスコンダクタンス、ゲート−ソース間容量の変動の減少)とひずみの減少が得られ、これによって、信号の振幅/相の再現性(例えば振幅変調(AM)からAMへの変換およびAMから位相変調(PM)への変換など)が向上し得る。

【0025】

ICデバイス100は、キャップ層108上に形成されたゲート118をさらに含む。ゲート118は、ICデバイス100の接続端子の役目をする。ゲート118は、キャップ層108に直接連結されていてもよい。

【0026】

図示のように、ゲート118は、キャップ層108に直接に連結されたトランク部すなわち底部と、該トランク部から、ゲート118の下のキャップ層108の表面に実質的に平行な逆方向に離れるように延在する頂部と、を有していてもよい。ゲート118のトランク部および蓋部のこうした構造をT−形ゲートと呼んでもよい。一部の実施形態では、ゲート118は、絶縁破壊電圧を向上させ得る、およびまたはゲート118とドレイン114間の電界を低減させ得るフィールドプレートであってもよい。ゲート118のトランク部の厚みは、その下のキャップ層108の表面に実質的に平行な方向において、約300〜約1400Åであってもよい。

【0027】

ゲート118は一般に、金属などの導電性材料で構成される。一部の実施形態では、ゲート118は、ニッケル(Ni)、プラチナ(Pt)、イリジウム(Ir)、モリブデン(Mo)、金(Au)およびまたはアルミニウム(Al)であってもよい。ある実施形態では、キャップ層108とゲートコンタクトさせるために、Ni、Pt、IrまたはMoを含む材料がゲート118のトランク部に配置され、また、ゲート118の導電性と低抵抗を確実にするために、Auを含む材料がゲート118の頂部に配置されている。種々の実施形態では、ゲート118は、高電子移動度トランジスタ(HEMT)デバイスの一部である。

【0028】

ICデバイス100は、キャップ層108上に形成されたソース112とドレイン114を含み得る。図示のように、ソース112とドレイン114はそれぞれ、キャップ層108およびバリア層106を通ってバッファ層104内に延在していてもよい。種々の実施形態では、ソース112とドレイン114はオーミックコンタクトしている。ソース112とドレイン114は、標準の成長コンタクトより比較的低接触抵抗であり得る再成長コンタクトであってもよい。一部の実施形態では、ソース112とドレイン114の接触抵抗は約0.01Ω・mmである。

【0029】

ソース112とドレイン114はそれぞれ、金属などの導電性材料で構成されていてもよい。ある実施形態では、ソース112とドレイン114はそれぞれ、チタン(Ti)、アルミニウム(Al)、モリブデン(Mo)、金(Au)およびまたはシリコン(Si)を含む。他の実施形態では、他の材料が使用できる。

【0030】

ある実施形態では、ドレイン114とゲート118間の距離D1は、ソース112とゲート118間の距離S1より大きい。一部の実施形態では、距離D1は、ドレイン114とゲート118間の最短距離であってもよく、距離S1は、ソース112とゲート118間の最短距離であってもよい。距離S1を距離D1より短くすることによって、ドレイン114に対してゲート118の絶縁破壊電圧を向上させ得、およびまたはソース112の抵抗を低減させ得る。

【0031】

一部の実施形態では、キャップ層108上に誘電体層122を形成してもよい。誘電体層122は、例えば窒化ケイ素(SiN)を含んでいてもよい。他の実施形態では、誘電体層122に対して、他の材料が使用できる。一部の実施形態では、キャップ層108に連結された誘電体層122の少なくとも一部は、スタック101を形成するその場プロセス中に、エピタキシャル堆積によって形成される。誘電体層122は、ゲート118を実質的に封入してもよい。誘電体層122は、ICデバイス100の保護層の役目をする。

【0032】

ICデバイス100は、絶縁破壊電圧の向上およびまたはゲート118とドレイン114間の電界低減のために、誘電体層122上で形成されたフィールドプレート124を含んでいてもよい。フィールドプレート124は、導電性材料126を用いて、ソース112に電気的に連結されていてもよい。導電性材料126は、例えば、誘電体層122上に電極あるいは線状構造として堆積された金(Au)などの金属を含んでいてもよい。他の実施形態では、導電性材料126に対して、他の好適な材料を用いてもよい。

【0033】

フィールドプレート124は一般に、金属などの導電性材料で構成され、ゲート118に関連して説明した材料を含んでいてもよい。フィールドプレート124は、誘電体層122を通してゲート118に容量連結されていてもよい。一部の実施形態では、フィールドプレート124とゲート118間の最短距離は1000〜2000Åである。図示のように、フィールドプレート124のオーバーハング領域を設けるために、該プレートの一部がゲート118の真上に配置され、別の部分はその真上に形成されないように、ゲート118の上部にフィールドプレート124を形成してもよい。一部の実施形態では、フィールドプレート124の該オーバーハング領域は、ゲート118の頂部端部より距離H1だけ延在している。一部の実施形態では、距離H1は0.2〜1μmであってもよいが、他の実施形態では、他の数値であってもよい。

【0034】

図2は、種々の実施形態に係る別の集積回路(IC)デバイス200の概略横断面である。図2では、ゲート218のトランク部がキャップ層108内に距離Rだけ延在している点を除いて、ICデバイス200は、図1のICデバイス100に関連して説明した実施形態に実質的に適合していてもよい。例えば、形成したキャップ層108から材料を除去するための異方性エッチングなどのエッチングプロセスにより、キャップ層108に凹部を設け、その凹部にゲート218を形成してもよい。他の実施形態では、ゲート218がキャップ層108内に延在するようにゲート218を形成する他の方法が用いられる。キャップ層108内に延在するゲート218を設けることによって、ICデバイス200の絶縁破壊電圧を向上でき、およびまたは電流崩壊を低減し得る。一部の実施形態では、Rは10〜30Åの距離を表わすが、他の実施形態では、他の値であってもよい。

【0035】

図3は、種々の実施形態に係る別の集積回路(IC)デバイス300の概略横断面図である。図示のように、図3では、キャップ層108がバリア層106上に形成された第1の部分308と、前記第1の部分上に形成された第2の部分309と、を含む点を除いて、図1のICデバイス100に関連して説明した実施形態に実質的に適合していてもよい。

【0036】

第1の部分308は、例えば、本明細書に記載の高温プロセスによって形成された(例えば、1000℃〜1100℃の比較的高温で成長させた)GaNまたはAlNのいずれかの層であってもよい。一部の実施形態では、第1の部分308は、実質的なあるいは完全な単結晶材料を含んでいてもよい。第1の部分308の厚みは20〜30Åであってもよい。他の実施形態では、他の材料または厚みが用いられてもよい。

【0037】

第2の部分309は、例えば、本明細書に記載の低温プロセスによって形成された(例えば、500℃〜600℃の比較的低温で成長させた)GaNまたはAlNいずれかの層であってもよい。第2の部分309は、ゲート118に対して、リークを防止し転位やその他の欠陥を低減する界面あるいはバッファ層の役目をする。一部の実施形態では、第2の部分309は、実質的なあるいは完全な多結晶材料を含む。第2の部分309の厚みは20〜30Åであってもよい。他の実施形態では、他の材料または厚みが用いられてもよい。一部の実施形態では、第1の部分308および第2の部分309は、スタック101の一部としてエピタキシャルに堆積されてもよい。

【0038】

図4は、種々の実施形態に係る別の集積回路(IC)デバイス400の概略横断面図である。図示のように、図4では、ICデバイス400がキャップ層108上に形成されたその場誘電体409を含む点を除いて、図1のICデバイス100に関連して説明した実施形態に実質的に適合していてもよい。

【0039】

その場誘電体409は、例えば、スタック101の一部としてキャップ層108の上に形成された窒化ケイ素(SiN)あるいは他の好適な誘電体材料などの誘電体層であってもよい。一部の実施形態では、その場誘電体409の厚みは50〜200Åであってもよい。他の実施形態では、その場誘電体409に対して、他の厚みおよびまたは材料が用いられてもよい。

【0040】

一部の実施形態では、その場誘電体409は、キャップ層108上にエピタキシャルに堆積され、基板102を取り出さずにスタック101の構成層を形成する(例えばエピタキシャル成長させる)製造装置(例えばチャンバ)内で形成されてもよい。図示のように、開口を形成するためのエッチングプロセスなどの任意の好適なプロセスにより、その場誘電体409に凹部を設け、そのキャップ層108上にゲート118を形成してもよい。誘電体層122は、その場誘電体409の形成に用いられたその場プロセスに付帯的なプロセスにおけるゲート118の形成後に堆積されてもよい。その場誘電体409によって、汚染が低減され得、およびまたはICデバイス400のトラップ密度を低減させる界面が提供され得る。

【0041】

図5は、種々の実施形態に係る別の集積回路(IC)デバイス500の概略横断面図である。ICデバイス500は、基板102上に形成されたドープ層504を含む。ドープ層504は、例えば、図1のICデバイス100に関連して、基板102に対して説明した材料を含む種々の材料を含むことができる。種々の実施形態では、ドープ層504は、n−型シリコン(Si)などの不純物ドープされる。ドープ層504の厚みは500〜1500Åであってもよい。他の実施形態では、ドープ層504に対して、他の好適なドーパント、材料およびまたは厚みが用いられる。図5のICデバイス500のその他の特長は、図1のICデバイス100に関連して上記した実施形態に適合していてもよい。

【0042】

ICデバイス100、200、300、400およびまたは500に関連して説明した実施形態は、種々の実施形態において好適に組み合わせられてもよい。例えば、図4のその場誘電体409は、図3の第1の部分308と第2の部分309とを有するキャップ層108上に形成されてもよく、およびまたは図2のゲート218は、図3または4のキャップ層108内に延在して形成されてもよい。

【0043】

図6は、種々の実施形態に係る集積回路デバイス(例えば、図1、2、3あるいは4それぞれのICデバイス100、200、300あるいは400)の製造方法600を示すフロー図である。方法600は、602において、基板(例えば図1の基板102)上にバッファ層(例えば図1のバッファ層104)を形成するステップと、604において、前記バッファ層上にバリア層(例えば図1のバリア層106)を形成するステップと、606において、前記バリア層上にキャップ層(例えば図1、2、3、あるいは4のキャップ層108)を形成するステップと、を備える。種々の実施形態では、これらの層間に介在させるために他の層を形成してもよい。

【0044】

種々の実施形態では、前記バッファ層、バリア層およびキャップ層はそれぞれ、分子線エピタキシャル法(MBE)、原子層エピタキシャル法(ALE)、化学ビームエピタキシャル法(CBE)およびまたは有機金属気相成長法(MOCVD)によってエピタキシャルに堆積される。前記バッファ層、バリア層および(または)キャップ層は、図1〜4に関連して上記した実施形態に準じて形成されてもよい。前記バッファ層、バリア層およびキャップ層は、本明細書に記載のその場プロセスを用いて形成された層のスタック(例えば図1のスタック101)の一部であってもよい。他の実施形態では、他の好適な堆積法が用いられる。スタックの層に対する材料およびまたは厚みは、図1、2、3および4それぞれのICデバイス100、200、300および400に関連して上記した実施形態と適合していてもよい。

【0045】

方法600は、608において、ソース(例えば図1のソース112)とドレイン(例えば図1のドレイン114)を形成するステップをさらに備えてもよい。種々の実施形態において、前記ソースとドレインは前記キャップ層上に形成されてもよい。ある実施形態では、例えば蒸発プロセスを用いて前記ソースとドレインが形成される領域内のキャップ層上に、1つまたは複数の金属などの材料が堆積される。前記ソースとドレインを形成するための材料は、以下の順序で堆積された金属を含んでいてもよい。チタン(Ti)→アルミニウム(Al)→モリブデン(Mo)→チタン(Ti)→金(Au)。前記堆積材料を加熱(例えば、高速熱アニールプロセスを用い約850℃で約30秒間)し、この材料を貫通させ、前記キャップ層、バリア層およびまたはバッファ層の下位の材料と溶融させてもよい。一部の実施形態では、前記ソースとドレインはそれぞれ、キャップ層を通ってバッファ層内に延在している。前記ソースとドレインの厚みは1000〜2000Åであり得る。他の実施形態では、ソースとドレインに対して、他の厚みが用いられる。

【0046】

ソースとドレインを再成長プロセスで形成し、低減された接触抵抗または低減されたオン抵抗を有するオーミックコンタクトを得てもよい。前記再成長プロセスでは、ソースとドレインが形成される領域では、キャップ層、バリア層およびまたはバッファ層の材料は選択的に除去される(例えば、エッチングされる)。これらの層が選択的に除去された領域に、高濃度ドープ材料(例えばn++材料)が堆積される。ソースとドレインの高濃度ドープ材料は、バッファ層104またはバリア層106に使用した材料と同様の材料であってもよい。例えば、バッファ層がGaNを含むシステムでは、前記選択的に除去した領域に、シリコン(Si)で高濃度にドープされたGaN系材料を厚みが400〜700Åになるまでエピタキシャルに堆積してもよい。前記高濃度ドープ材料は、分子線エピタキシャル法(MBE)、原子層エピタキシャル法(ALE)、化学ビームエピタキシャル法(CBE)、有機金属気相成長法(MOCVD)またはこれらの好適な組み合わせによってエピタキシャルに堆積できる。他の実施形態では、前記高濃度ドープ材料に対して、他の材料、厚みあるいは堆積法が用いられる。前記高濃度ドープ材料上に、例えば、チタン(Ti)およびまたは金(Au)を含む1つまたは複数の金属を、例えばリフトオフプロセスを用いて1000Å〜1500Åの厚みで形成/堆積できる。他の実施形態では、前記1つまたは複数の金属に対して、他の材料、厚みおよびまたは方法が用いられる。

【0047】

一部の実施形態では、ソースとドレインに高濃度ドープ材料を提供するために、不純物(例えばシリコン)を導入する注入法を用いた注入プロセスによって、ソースとドレインを形成してもよい。注入後、ソースとドレインを高温(例えば1100〜1200℃)でアニールする。前記再成長プロセスでは、前記注入後アニールに伴う高温を好適に避け得る。

【0048】

方法600は、610において、ゲート(例えば図1のゲート構造118)を形成するステップをさらに備えてもよい。前記キャップ層上に導電性材料を堆積することによって、該キャップ層上にゲートを形成してもよい。例えば、蒸発、原子層堆積(ALD)およびまたは化学蒸着法(CVD)を含む任意の好適な堆積プロセスによって、ゲート材料を堆積できる。前記ゲートがT−形ゲートである実施形態では、金属堆積/エッチングプロセスまたはリフトオフフプロセスを用いて、このT−ゲートのトランク部または頂部を形成してもよい。

【0049】

方法600は、612において、前記ゲート上に誘電体層(例えば図1の誘電体層122)を形成するステップをさらに備える。任意の好適な堆積法を用いて、誘電体材料を前記ゲート上およびまたはキャップ層上に堆積することにより、前記誘電体層を形成してもよい。

【0050】

方法600は、614において、前記誘電体層上にフィールドプレート(例えば図1のフィールドプレート124)を形成するステップをさらに備える。任意の好適な堆積法を用いて、導電性材料を前記誘電体層上に堆積することにより、前記フィールドプレートを形成してもよい。リソグラフィおよびまたはエッチングプロセスなどのパターニングプロセスを用いて、前記堆積した導電性材料部分を選択的に除去して前記フィールドプレートを形成できる。他の実施形態では、他の好適な方法を用いてもよい。方法600に関連して記載したものと同様な方法を行って、図5のICデバイス500を製造してもよい。

【0051】

特許請求される主題の理解に最も有用な方法で、種々の操作を複数の別個の操作として記載したが、これらの操作は必然的に順序依存であることを示唆するようには記載の順序を解釈すべきではない。これらの操作は、特に提示の順番に行われなくてもよい。記載の実施形態と異なる順番で、記載された操作を行ってもよい。追加の実施形態では、種々の追加の操作を行ってもよく、およびまたは記載の操作を省略してもよい。

【0052】

本明細書に記載のICデバイス(例えばICデバイス100、200、300、400または500)の実施形態およびこうしたICデバイス100を含む装置を、他の種々の装置およびシステムに組み込んでもよい。例となるシステム700のブロック図を図7に示す。図示のように、システム700は、電力増幅器(PA)モジュール702を備えており、このモジュール702は、一部の実施形態では、無線周波数(RF)PAモジュールであってもよい。図示のように、システム700は、電力増幅器モジュール702に連結されたトランシーバ704を備えていてもよい。電力増幅器モジュール702は、本明細書に記載のICデバイス(例えばICデバイス100、200、300、400または500)を備えていてもよい。

【0053】

電力増幅器モジュール702は、トランシーバ704からRF入力信号(RFin)を受信してもよい。電力増幅器モジュール702は、RF入力信号(RFin)を増幅してRF出力信号(RFout)を出力してもよい。図7でそれぞれTx−RFinおよびTx−RFoutで示されるRF入力信号(RFin)およびRF出力信号(RFout)は共に、送信チェーンの一部であってもよい。

【0054】

増幅されたRF出力信号(RFout)は、アンテナスイッチモジュール(ASM)706に与えられてもよく、このモジュールによって、アンテナ構造708経由で、RF出力信号(RFout)の無線(OTA)送信が実現される。また、ASM706は、アンテナ構造708経由でRF信号を受信し、その受信RF信号(Rx)を受信チェーンに沿ってトランシーバ704につなぐ。

【0055】

種々の実施形態では、アンテナ構造708は、例えば、ダイポールアンテナ、モノポールアンテナ、パッチアンテナ、ループアンテナ、マイクロストリップアンテナ、あるいはRF信号のOTA送信/受信に好適な任意の他の形式のアンテナを含む指向性アンテナおよびまたは全方向性アンテナの1つまたは複数を含んでいてもよい。

【0056】

システム700は、電力増幅を含む任意のシステムであってもよい。前記ICデバイス(例えばICデバイス100、200、300、400または500)は、例えば交流(AC)−直流(DC)変換器やDC−DC変換器、DC−AC変換器などの電力調整用途を含む電力スイッチング用途用の効率的なスイッチングデバイスを提供してもよい。種々の実施形態では、システム700は、高無線周波数電力と周波数における電力増幅には特に有用であり得る。例えば、システム700は、陸上および衛星通信、レーダーシステムおよび恐らく種々の産業および医学用途における利用のいずれか1つまたは複数に対して好適であり得る。より具体的には、種々の実施形態において、システム700は、レーダー装置、衛星通信装置、携帯電話、携帯電話基地局、ラジオ放送あるいはテレビ増幅器システムから選択された1つであり得る。

【0057】

説明の目的で実施形態を例示し記載したが、同じ目的を実現するように意図された、広範な代替となるおよびまたは均等な実施形態あるいは実施によって、本開示の範囲を逸脱することなくこれらの実施形態を置換できる。本出願は、本明細書で検討した実施形態に対するいかなる適応や変形もカバーするように意図される。従って、本明細書に記載の実施形態は、請求項とその均等物によってのみ限定されることが明白に意図される。

【特許請求の範囲】

【請求項1】

基板上に形成されたバッファ層と、

前記バッファ層上に形成され、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むバリア層と、

前記バリア層上に形成され、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むキャップ層と、

前記キャップ層上に形成され、前記キャップ層に直接に連結されているゲートと、

を備えることを特徴とする装置。

【請求項2】

前記キャップ層は、多結晶窒化ガリウム(GaN)または多結晶窒化アルミニウム(AlN)であり、その厚みは50Å以下であることを特徴とする請求項1に記載の装置。

【請求項3】

前記キャップ層は、5電子ボルト(eV)超の第1のバンドギャップエネルギーを有し、

前記バリア層は、前記第1のバンドギャップエネルギー未満の第2のバンドギャップエネルギーを有し、

前記バッファ層は、前記第2のバンドギャップエネルギー未満の第3のバンドギャップエネルギーを有していることを特徴とする請求項1に記載の装置。

【請求項4】

前記バリア層は、前記バッファ層にエピタキシャルに連結され、

前記キャップ層は、前記バリア層にエピタキシャルに連結されていることを特徴とする請求項1に記載の装置。

【請求項5】

前記バッファ層は窒化ガリウム(GaN)を含み、

その厚みは1〜2μmであることを特徴とする請求項1に記載の装置。

【請求項6】

前記バリア層は、窒化ガリウムアルミニウム(AlxGa1−xN)(xは、アルミニウムとガリウムとの相対量を表わす0.15〜0.3の値)を含むことを特徴とする請求項5に記載の装置。

【請求項7】

前記バリア層は、窒化アルミニウムインジウム(InyAl1−yN)(yは、インジウムとアルミニウムとの相対量を表す0.13〜0.21の値)をことを特徴とする請求項5に記載の装置。

【請求項8】

前記ゲートは、前記キャップ層内に数なくとも5Å延在していることを特徴とする請求項1に記載の装置。

【請求項9】

前記キャップ層は、実質的に単結晶材料を有し前記バリア層上に形成されてそれに直接連結された第1の部分を含み、

前記キャップ層は、実質的に多結晶材料を有し前記第1の部分上に形成されてそれに直接連結された第2の部分を含むことを特徴とする請求項1に記載の装置。

【請求項10】

前記キャップ層にエピタキシャルに連結された誘電体層をさらに備えることを特徴とする請求項1に記載の装置。

【請求項11】

前記ゲートはT−形のフィールドプレートゲートであり、

前記ゲートは、ニッケル(Ni)、プラチナ(Pt)、イリジウム(Ir)、モリブデン(Mo)あるいは金(Au)を含むことを特徴とする請求項1に記載の装置。

【請求項12】

前記キャップ層に連結されたソースと、

前記キャップ層に連結されたドレインと、をさらに備えた装置であって、前記ソースおよび前記ドレインはそれぞれ、前記キャップ層およびバリア層を通って前記バッファ層内に延在し、前記ソースはオーミックコンタクトであり、前記ドレインはオーミックコンタクであり、前記ドレインと前記ゲート間の最短距離は、前記ソースと前記ゲート間の最短距離より大きいことを特徴とする請求項1に記載の装置。

【請求項13】

シリコン(Si)、炭化ケイ素(SiC)、サファイア(Al2O3)、窒化ガリウム(GaN)または窒化アルミニウム(AlN)を含む前記基板と、

前記キャップ層上に形成され、実質的に前記ゲートを封入する誘電体層と、

ゲート上部の前記誘電体層上に形成され、前記ソースに電気的に連結されたフィールドプレートと、をさらに備えることを特徴とする請求項12に記載の装置。

【請求項14】

前記キャップ層は、キャップ層を通って前記バリア層に容量連結されたゲート誘電体であり、

前記ゲートは、電力増幅器用途用の高電子移動度トランジスタ(HEMT)スイッチングデバイスの一部であることを特徴とする請求項1に記載の装置。

【請求項15】

基板上にバッファ層を形成するステップと、

アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むバリア層を前記バッファ層上に形成するステップと、

窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むキャップ層を前記バリア層上に形成するステップと、

前記キャップ層に直接連結されたゲートを前記キャップ層上に形成するステップと、

を備えることを特徴とする方法。

【請求項16】

前記バッファ層、バリア層およびキャップ層はそれぞれ、分子線エピタキシャル法(MBE)、原子層エピタキシャル法(ALE)、化学ビームエピタキシャル法(CBE)または有機金属気相成長法(MOCVD)によってエピタキシャルに堆積されることを特徴とする請求項15に記載の方法。

【請求項17】

前記キャップ層は、500℃〜600℃の温度で、窒化ガリウム(GaN)または窒化アルミニウム(AlN)をエピタキシャルに堆積させて形成され、

前記キャップ層は、厚みが50Å以下で形成されることを特徴とする請求項15に記載の方法。

【請求項18】

前記キャップ層は、5電子ボルト(eV)超の第1のバンドギャップエネルギーを有し、

前記バリア層は、前記第1のバンドギャップエネルギー未満の第2のバンドギャップエネルギーを有し、

前記バッファ層は、前記第2のバンドギャップエネルギー未満の第3のバンドギャップエネルギーを有していることを特徴とする請求項15に記載の方法。

【請求項19】

前記バリア層は、前記バッファ層上にエピタキシャルに堆積されることによって形成され、

前記キャップ層は、前記バリア層上にエピタキシャルに堆積されることによって形成されることを特徴とする請求項15に記載の方法。

【請求項20】

ソースおよびドレインを前記キャップ層上に形成するステップと、

誘電体層を形成して前記ゲートを実質的に封入するステップと、

前記ゲートの上部に配置されるフィールドプレートを前記誘電体層上に形成するステップと、

をさらに備えることを特徴とする請求項15に記載の方法。

【請求項1】

基板上に形成されたバッファ層と、

前記バッファ層上に形成され、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むバリア層と、

前記バリア層上に形成され、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むキャップ層と、

前記キャップ層上に形成され、前記キャップ層に直接に連結されているゲートと、

を備えることを特徴とする装置。

【請求項2】

前記キャップ層は、多結晶窒化ガリウム(GaN)または多結晶窒化アルミニウム(AlN)であり、その厚みは50Å以下であることを特徴とする請求項1に記載の装置。

【請求項3】

前記キャップ層は、5電子ボルト(eV)超の第1のバンドギャップエネルギーを有し、

前記バリア層は、前記第1のバンドギャップエネルギー未満の第2のバンドギャップエネルギーを有し、

前記バッファ層は、前記第2のバンドギャップエネルギー未満の第3のバンドギャップエネルギーを有していることを特徴とする請求項1に記載の装置。

【請求項4】

前記バリア層は、前記バッファ層にエピタキシャルに連結され、

前記キャップ層は、前記バリア層にエピタキシャルに連結されていることを特徴とする請求項1に記載の装置。

【請求項5】

前記バッファ層は窒化ガリウム(GaN)を含み、

その厚みは1〜2μmであることを特徴とする請求項1に記載の装置。

【請求項6】

前記バリア層は、窒化ガリウムアルミニウム(AlxGa1−xN)(xは、アルミニウムとガリウムとの相対量を表わす0.15〜0.3の値)を含むことを特徴とする請求項5に記載の装置。

【請求項7】

前記バリア層は、窒化アルミニウムインジウム(InyAl1−yN)(yは、インジウムとアルミニウムとの相対量を表す0.13〜0.21の値)をことを特徴とする請求項5に記載の装置。

【請求項8】

前記ゲートは、前記キャップ層内に数なくとも5Å延在していることを特徴とする請求項1に記載の装置。

【請求項9】

前記キャップ層は、実質的に単結晶材料を有し前記バリア層上に形成されてそれに直接連結された第1の部分を含み、

前記キャップ層は、実質的に多結晶材料を有し前記第1の部分上に形成されてそれに直接連結された第2の部分を含むことを特徴とする請求項1に記載の装置。

【請求項10】

前記キャップ層にエピタキシャルに連結された誘電体層をさらに備えることを特徴とする請求項1に記載の装置。

【請求項11】

前記ゲートはT−形のフィールドプレートゲートであり、

前記ゲートは、ニッケル(Ni)、プラチナ(Pt)、イリジウム(Ir)、モリブデン(Mo)あるいは金(Au)を含むことを特徴とする請求項1に記載の装置。

【請求項12】

前記キャップ層に連結されたソースと、

前記キャップ層に連結されたドレインと、をさらに備えた装置であって、前記ソースおよび前記ドレインはそれぞれ、前記キャップ層およびバリア層を通って前記バッファ層内に延在し、前記ソースはオーミックコンタクトであり、前記ドレインはオーミックコンタクであり、前記ドレインと前記ゲート間の最短距離は、前記ソースと前記ゲート間の最短距離より大きいことを特徴とする請求項1に記載の装置。

【請求項13】

シリコン(Si)、炭化ケイ素(SiC)、サファイア(Al2O3)、窒化ガリウム(GaN)または窒化アルミニウム(AlN)を含む前記基板と、

前記キャップ層上に形成され、実質的に前記ゲートを封入する誘電体層と、

ゲート上部の前記誘電体層上に形成され、前記ソースに電気的に連結されたフィールドプレートと、をさらに備えることを特徴とする請求項12に記載の装置。

【請求項14】

前記キャップ層は、キャップ層を通って前記バリア層に容量連結されたゲート誘電体であり、

前記ゲートは、電力増幅器用途用の高電子移動度トランジスタ(HEMT)スイッチングデバイスの一部であることを特徴とする請求項1に記載の装置。

【請求項15】

基板上にバッファ層を形成するステップと、

アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むバリア層を前記バッファ層上に形成するステップと、

窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含むキャップ層を前記バリア層上に形成するステップと、

前記キャップ層に直接連結されたゲートを前記キャップ層上に形成するステップと、

を備えることを特徴とする方法。

【請求項16】

前記バッファ層、バリア層およびキャップ層はそれぞれ、分子線エピタキシャル法(MBE)、原子層エピタキシャル法(ALE)、化学ビームエピタキシャル法(CBE)または有機金属気相成長法(MOCVD)によってエピタキシャルに堆積されることを特徴とする請求項15に記載の方法。

【請求項17】

前記キャップ層は、500℃〜600℃の温度で、窒化ガリウム(GaN)または窒化アルミニウム(AlN)をエピタキシャルに堆積させて形成され、

前記キャップ層は、厚みが50Å以下で形成されることを特徴とする請求項15に記載の方法。

【請求項18】

前記キャップ層は、5電子ボルト(eV)超の第1のバンドギャップエネルギーを有し、

前記バリア層は、前記第1のバンドギャップエネルギー未満の第2のバンドギャップエネルギーを有し、

前記バッファ層は、前記第2のバンドギャップエネルギー未満の第3のバンドギャップエネルギーを有していることを特徴とする請求項15に記載の方法。

【請求項19】

前記バリア層は、前記バッファ層上にエピタキシャルに堆積されることによって形成され、

前記キャップ層は、前記バリア層上にエピタキシャルに堆積されることによって形成されることを特徴とする請求項15に記載の方法。

【請求項20】

ソースおよびドレインを前記キャップ層上に形成するステップと、

誘電体層を形成して前記ゲートを実質的に封入するステップと、

前記ゲートの上部に配置されるフィールドプレートを前記誘電体層上に形成するステップと、

をさらに備えることを特徴とする請求項15に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−89970(P2013−89970A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−230753(P2012−230753)

【出願日】平成24年10月18日(2012.10.18)

【出願人】(599034594)トライクイント・セミコンダクター・インコーポレイテッド (17)

【氏名又は名称原語表記】TriQuint Semiconductor,Inc.

【住所又は居所原語表記】2300 NE Brookwood Parkway,Hillsboro,Oregon 94124,U.S.A.

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2012−230753(P2012−230753)

【出願日】平成24年10月18日(2012.10.18)

【出願人】(599034594)トライクイント・セミコンダクター・インコーポレイテッド (17)

【氏名又は名称原語表記】TriQuint Semiconductor,Inc.

【住所又は居所原語表記】2300 NE Brookwood Parkway,Hillsboro,Oregon 94124,U.S.A.

【Fターム(参考)】

[ Back to top ]