等価回路パラメータ生成装置、並びに生成方法

【課題】測定によって得られた周波数特性を集中定数素子からなる等価回路に高精度に近似合成することができ、しかも、当該回路全体としての受動性が保証される等価回路パラメータ生成方法を提供する。

【解決手段】本発明に係る第1の等価回路パラメータ生成方法は、留数kを含んだ形式に近似された測定対象物の周波数特性と、留数kからなる等価回路パラメータを有する等価回路とを準備し(ステップS1〜S3)、最小自乗近似を用いて周波数特性の留数kを算出することにより、測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、最小自乗近似を行う前に、等価回路パラメータが負とならないような留数kに関する第1の拘束条件を決定し(ステップS4)、当該第1の拘束条件下で最小自乗近似を行う(ステップS5)。

【解決手段】本発明に係る第1の等価回路パラメータ生成方法は、留数kを含んだ形式に近似された測定対象物の周波数特性と、留数kからなる等価回路パラメータを有する等価回路とを準備し(ステップS1〜S3)、最小自乗近似を用いて周波数特性の留数kを算出することにより、測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、最小自乗近似を行う前に、等価回路パラメータが負とならないような留数kに関する第1の拘束条件を決定し(ステップS4)、当該第1の拘束条件下で最小自乗近似を行う(ステップS5)。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、測定によって得られた周波数特性を、集中定数素子からなる等価回路に近似合成するための等価回路パラメータ生成装置、並びに生成方法に関する。

【背景技術】

【0002】

近年、パワーエレクトロニクスの分野では、システムの高周波化に伴ってEMIが大きな問題となっている。EMIは、他の電子機器に誤動作等の悪影響を及ぼすおそれがあることから、適切な対策を施すことが求められている。また、コンピュータシミュレーションによってEMI対策を検討する場合には、等価回路を構成する個々の素子の素子値(以下、「等価回路パラメータ」)をどのようにして生成し、集中定数素子からなる等価回路に近似(モデリング)するかが問題となる。

同様に、LSIの分野においても、動作周波数の上昇に伴って、素子間配線による信号伝播遅延、素子間配線同士の干渉等の問題が顕在化してきている。これらのメカニズムを解析し、適切な対策を施すためにも、素子間配線のモデリングは非常に重要である。

【0003】

従来の等価回路パラメータ生成方法としては、最小自乗近似を利用した方法が知られている。この従来の生成方法では、まず、モデリングしたい測定対象物のN点の周波数特性X(s)をインピーダンスメータ等の測定器で測定する。得られた周波数特性は、分数多項式で表現された測定周波数特性X^(s)で近似することができる。なお、表記“X^”は、Xの上にハット記号“^”が付されていることを意味する。

【数1】

ここで、m及びnは、モデリングしたい周波数特性の複雑さに応じて任意に決定することができる次数である。また、i=1、2・・・N、si=j2πfi(ただし、fi:サンプル周波数、j=√(−1))である。

(1)式を展開して、部分分数で表現すると次式となる。

【数2】

ここで、Nc及びNsは、必要とされるモデリング精度等に応じて、任意に決定することができる個数である。

【0004】

(2)式に含まれる(2+Ns+2Nc)個の留数kは、次式によって最小自乗近似することにより、算出される。

【数3】

ここで、行列Acは留数ベクトルkの係数行列であり、そのi行成分は、

【数4】

である。

また、(3)式において、測定周波数特性値ベクトルxc及び留数ベクトルkは、

【数5】

である。

ここで、(5)式の“N”は、測定サンプル数である。また、X(sN)は測定によって得られたN番目のサンプル周波数における測定周波数特性値である。

【0005】

続いて、回路合成が行われる。モデリングしたい周波数特性がインピーダンスの場合、(3)〜(6)式によって得られた(2+Ns+2Nc)個の留数は、図1及び次式で表される等価回路(Fosterの第1回路)に合成される。

【数6】

ここで、図1に示す等価回路の等価回路パラメータは、次式によって表される。

【数7】

なお、R0とL∞は省略することもできる。

【0006】

一方、モデリングしたい周波数特性がアドミタンスの場合、(3)〜(6)式によって得られた(2+Ns+2Nc)個の留数は、図2及び次式で表される等価回路(Fosterの第2回路)に合成される。

【数8】

ここで、図2に示す等価回路の等価回路パラメータは、次式によって表される。

【数9】

なお、G0とC∞は省略することもできる。

【0007】

ところが、上記した従来の等価回路パラメータ生成方法では、最終的に得られる等価回路パラメータ((8)〜(10)式、(12)〜(14)式参照)が負の値を示す場合があった。

本来、Fosterの第1回路(図1参照)及び第2回路(図2参照)は受動性を有する集中定数素子からなり、回路全体としても受動性を示すべきものある。しかしながら、回路の一部に負の素子値を有する集中定数素子が含まれると、当該回路は局所的に受動性を有していないことになり、回路全体としても受動性を有さない可能性がある。

したがって、従来の等価回路パラメータ生成方法で得られた等価回路の周波数特性は、現実の測定対象物と大きくかけ離れた周波数特性となる場合があった。また、当該回路を用いたシミュレーションは不安定になる場合があり、信頼性が問題となっていた。

【0008】

上記問題の解決を試みた等価回路パラメータ生成方法として、非特許文献1に係る方法がある。

この方法では、最小自乗近似によって得られた等価回路パラメータのうち、負となった素子の素子値を強制的に“0”にすることにより、等価回路の受動性を確保している。しかしながら、この方法によって得られた等価回路は、勝手に値が変更された集中定数素子が含まれることになるので、周波数特性のモデリングの精度が問題となっていた。

【非特許文献1】J. Morsey and A.C. Cangellaris,“PRIME: passive realization of interconnect models from measured data”, IEEE Electrical Performance of Electronic Packaging, 2001, pp.47-50

【発明の開示】

【発明が解決しようとする課題】

【0009】

そこで、本発明は、測定によって得られた周波数特性を集中定数素子からなる等価回路に高精度に近似合成することができ、しかも、当該等価回路全体としての受動性が保証される等価回路パラメータ生成装置、並びに生成方法を提供することを課題とする。

【課題を解決するための手段】

【0010】

本発明者等は、上記課題を解決するために鋭意検討を重ねた結果、最小自乗近似を行う前に、(1)各等価回路パラメータが負となることを禁止し、局所的に見ても全体として見ても等価回路の受動性が確保されるような拘束条件、または(2)個々の等価回路パラメータが負となることは許容しつつ、等価回路全体としての受動性が確保されるような拘束条件を決定し、その条件下で最小自乗近似を行うことを見出し、本発明を完成させた。

【0011】

すなわち、本発明に係る第1の等価回路パラメータ生成方法は、留数kを含んだ形式に近似された測定対象物の周波数特性と、前記留数kからなる等価回路パラメータを有する等価回路とを準備し、最小自乗近似を用いて前記周波数特性の留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、前記最小自乗近似を行う前に、前記等価回路パラメータが負とならないような留数kに関する第1の拘束条件を決定し、当該第1の拘束条件下で前記最小自乗近似を行って留数kを算出することを特徴とする。

【0012】

また、本発明に係る第1の等価回路パラメータ生成装置は、測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、前記測定対象物の周波数特性を測定するとともに、測定された前記周波数特性を前記留数kを含んだ形式に近似する測定部と、適宜必要な情報の入力を受け付ける入力部と、前記入力部から入力された等価回路選択データに基づいて選択された前記等価回路の前記等価回路パラメータが負とならないような前記留数kに関する第1の拘束条件を決定する拘束条件決定部と、前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記第1の拘束条件を受け取り、前記第1の拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路パラメータを生成する演算部と、を備えたことを特徴とする。

【0013】

また、本発明に係る第2の等価回路パラメータ生成方法は、測定対象物を所定の周波数範囲で測定し、N個の測定周波数特性値X(si)(ただし、i=1、2…N)からなる周波数特性を得て、当該周波数特性を留数kを含んだ形式に近似するとともに、前記留数kからなる等価回路パラメータを有する等価回路を準備し、(数10)式から(数12)式を用いた最小自乗近似を行って前記留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、

【数10】

【数11】

【数12】

(ただし、Ac:留数ベクトルkの係数行列、Aic:係数行列Acのi行成分、i=1、2・・・N、si=j2πfi(ただし、fi:サンプル周波数、j=√(−1))、Nc:任意個数、Ns:任意個数)

前記最小自乗近似を行う前に、(数13)式で表される、前記所定の周波数範囲内についての第2の拘束条件を決定し、

【数13】

(ただし、Ar:係数行列Acの実数部)

前記第2の拘束条件下で前記最小自乗近似を行い、留数kを算出することを特徴とする。

【0014】

上記第2の等価回路パラメータ生成方法は、好ましくは、前記所定の周波数範囲外の任意の周波数についての第3の拘束条件を決定し、前記第2及び第3の拘束条件の下で前記最小自乗近似を行い、留数kを算出することを特徴とする。

【0015】

また、本発明に係る第2の等価回路パラメータ生成装置は、上記第2の等価回路パラメータ生成方法を用いて決定される前記第2の拘束条件、または前記第2及び第3の拘束条件からなる拘束条件を用いて、測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、前記測定対象物の周波数特性を測定するとともに、測定された周波数特性を前記留数kを含んだ形式に近似する測定部と、前記留数kに関する前記拘束条件を決定する拘束条件決定部と、前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記拘束条件を受け取り、前記拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路の前記等価回路パラメータを生成する演算部と、を備えたことを特徴とする。

【発明の効果】

【0016】

本発明に係る等価回路パラメータ生成装置、及び生成方法によれば、測定によって得られた周波数特性を集中定数素子からなる等価回路に近似合成するにあたり、事前に、(1)各等価回路パラメータが負となることを禁止し、局所的に見ても全体として見ても等価回路の受動性が確保されるような第1の拘束条件、または(2)個々の等価回路パラメータが負となることは許容しつつ、等価回路全体としての受動性が確保されるような第2の拘束条件を算出しておき、いずれかの条件下で最小自乗近似を行うことによって、少なくとも回路全体としての受動性を確保しつつ、高精度に当該周波数特性を再現する等価回路を得ることができる。

【発明を実施するための最良の形態】

【0017】

[第1の等価回路パラメータ生成方法]

以下、添付図面を参照して、本発明に係る第1の等価回路パラメータ生成方法について説明する。本方法では、各等価回路パラメータが負となることを禁止することにより、局所的に見ても全体として見ても等価回路の受動性が確保されるような拘束条件が決定される。

【0018】

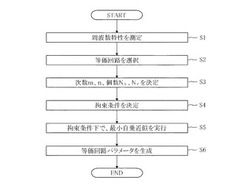

具体的には、本生成方法において、等価回路パラメータは図3に示すようなフローで生成される。すなわち、本生成方法では、はじめに、モデリングしたい測定対象物の周波数特性をインピーダンスメータ等の測定器で測定し(図3のステップS1)、使用する等価回路を選択し(ステップS2)、当該周波数特性に応じて次数m、n、及び個数Nc、Nsを決定する(ステップS3)。等価回路は、例えば、一般的な等価回路であるFosterの第1回路(図1参照)、及びFosterの第2回路(図2参照)等から選択される。なお、等価回路の選択(ステップS2)は、ステップS1の前、またはステップS3とS4の間に行ってもよい。

【0019】

続いて、本生成方法では、最小自乗近似を実行する前に、各素子の素子値が負とならないような拘束条件を決定する(ステップS4)。そして、その拘束条件下で、(3)式による最小自乗近似を行う(ステップS5)。なお、ステップS5は、公知の数値解析ソフトウェアを用いることで容易に行うことができる。

【0020】

例えば、モデリングしたい測定対象物の周波数特性がインピーダンスの場合、ステップS3において、図1に示すFosterの第1回路が等価回路として選択される。

この等価回路において、R0、L∞が負とならない条件は、(8)式より、

【数14】

また、(9)式より、Cls、Glsが負とならない条件は、

【数15】

さらに、(10)式より、Clc、Glc、Llc、Rlcが負とならない条件は、

【数16】

となる。

【0021】

(15)〜(17)式の条件を行列・ベクトル形式で表現すると、

【数17】

となる。ここで、行列Dは、

【数18】

である。

ステップS4で決定された(18)式の条件(以下、「第1の拘束条件」)下でステップS5の最小自乗近似を行うことで、すべての素子値が負とならないことが保証された留数ベクトルkを算出することができる。なお、(19)式の行列Dを、以下、「第1の拘束条件行列」と称する。

【0022】

最後に、本生成方法では、ステップS5で算出された留数を(15)〜(17)式に代入し、選択した等価回路における各集中定数素子の素子値である等価回路パラメータを生成する(ステップS6)。

【0023】

以上のように、本発明に係る第1の等価回路パラメータ生成方法によれば、事前に決定された第1の拘束条件下で最小自乗近似を行うことにより、負の素子値を含まない等価回路パラメータを生成することができる。

また、第1の拘束条件によれば、すべての素子値が負とならないように調整されるとともに、この調整に伴って、他の素子値が最小自乗近似の過程で調整されるので、等価回路全体としての周波数特性の精度が悪化するのを防ぐことができる。

さらに、本発明に係る第1の等価回路パラメータ生成方法で得られる等価回路は、負となっていた幾つかの素子値が“0”になるので、当該等価回路を用いたシミュレーションを簡略化及び高速化することができる。

【0024】

続いて、本発明に係る第1の等価回路パラメータ生成方法によってモデリングされた等価回路の周波数特性と、従来から行われている他の方法によってモデリングされた等価回路の周波数特性とを比較した実験結果について説明する。

【0025】

(比較実験1−1:乾式進相コンデンサ、Fosterの第2回路)

本比較実験では、50μFの乾式進相コンデンサを2個直列に接続したものを測定対象物とし、その周波数特性をインピーダンスメータで測定した。また、本比較実験では、等価回路としてFosterの第2回路を選択し、次数m=2、n=3の下で個数Ns=1、Nc=1とし、最小自乗近似を行った。

なお、前記の通り、次数m、n、及び個数Ns、Ncは任意に決定することができる。基本的に、個数NsとNcを大きくするとモデリングの精度が上がるが、最小自乗近似の計算に時間を要することとなる。また、個数Ns及びNcによるモデリング精度の向上には限界があり、一定以上にしてもほとんどモデリング精度は向上しない。

【0026】

(12)〜(14)式より第1の拘束条件を決定し、その条件下で最小自乗近似を行うと、最終的に、以下に示す等価回路パラメータが得られた。

【数19】

上記等価回路パラメータから明らかなように、本発明に係る第1の等価回路パラメータ生成方法では第1の拘束条件下で最小自乗近似を行うため、負の値を有する集中定数素子が存在しない。

【0027】

第1の拘束条件を使用することなく、単に最小自乗近似を行った場合(以下、「従来方法」)に得られた等価回路パラメータは、以下の通りである。

【数20】

この方法では、素子G0、C∞、G1cが負の素子値となり、少なくとも等価回路の局所的な受動性が損なわれてしまっている。また、従来方法では、等価回路全体としての受動性を確保するような調整が一切行われていない。したがって、この等価回路パラメータを用いた等価回路は、全体として見ても受動性が保証されていない。

【0028】

さらに、比較のために、従来方法において得られた等価回路パラメータのうち、負となった素子値を無理やり“0”とし、他の素子値について何ら調整を行わない場合(以下、「比較方法」)についても実験を行った。比較方法で得られた等価回路パラメータは、以下の通りである。

【数21】

【0029】

図4に、測定によって得られた乾式進相コンデンサの周波数特性、及び上記3つの方法によって得られた等価回路の周波数特性を示す。

図4(A)に示すアドミタンス特性については、いずれの方法に係る周波数特性も乾式進相コンデンサの周波数特性(測定値)をよく再現している。また、図4(B)に示す位相特性については、100Hz、1〜10MHz付近の帯域において、比較方法に係るグラフは誤差が比較的大きい。これは、負となった素子値を、無理やり“0”にし、他の素子値を調整しなかったためだと思われる。

なお、従来方法に係るグラフは、アドミタンス及び位相の両特性において乾式進相コンデンサの周波数特性(測定値)をよく再現しているが、前記の通り、従来方法に係る等価回路は全体として受動性が保証されていない。したがって、この等価回路は、乾式進相コンデンサの周波数特性とかけ離れた特性を示すおそれがある。

【0030】

(比較実験1−2:トロイダルコア、Fosterの第1回路)

本比較実験では、500μHのトロイダルコアを測定対象物とし、その周波数特性をインピーダンスメータで測定した。また、本比較実験では、等価回路としてFosterの第1回路を選択し、次数m=5、n=6の下で個数Ns=0、Nc=3とし、最小自乗近似を行った。

【0031】

(8)〜(10)式より第1の拘束条件を決定し、その条件下で最小自乗近似を行うと、最終的に、以下に示す等価回路パラメータが得られた。

【数22】

上記等価回路パラメータから明らかなように、本発明に係る第1の等価回路パラメータ生成方法では、第1の拘束条件下で最小自乗近似を行うため、負の値を有する集中定数素子が存在しない。

【0032】

従来方法によって得られた等価回路パラメータは次の通りである。

【数23】

この方法では、素子C1s、G1s、R1cが負の素子値となり、少なくとも等価回路の局所的な受動性が損なわれてしまっている。

【0033】

また、比較方法によって得られた等価回路パラメータは次の通りである。

【数24】

【0034】

図5に、測定によって得られたトロイダルコアの周波数特性、及び上記3つの方法によって得られた等価回路の周波数特性を示す。

図5(A)に示すインピーダンス特性については、従来方法及び本発明に係る第1の生成方法で得られた周波数特性は、いずれもトロイダルコアの周波数特性(測定値)をよく再現している。一方、比較方法に係るグラフは、10kHz以下の帯域で他の方法に比べて誤差が大きくなっている。さらに、比較方法で得られた周波数特性は、全周波数帯域において、トロイダルコアの位相特性(測定値)を全く再現できていない(図5(B)参照)。

なお、比較実験1と同様に、従来方法で得られた周波数特性は、インピーダンス及び位相の両特性においてトロイダルコアの周波数特性(測定値)をよく再現しているが、前記の通り、従来方法に係る等価回路は全体として受動性が保証されていない。したがって、この等価回路は、トロイダルコアの周波数特性とかけ離れた特性を示すおそれがある。

【0035】

以上をまとめると、本発明に係る第1の等価回路パラメータ生成方法では、測定によって得られた測定対象物の周波数特性を集中定数素子からなる等価回路に近似合成するにあたり、事前に、各素子の値が負とならないような第1の拘束条件を算出しておき、その条件下で最小自乗近似を行う。これにより、受動性を損なうことなく、高精度に測定対象物の周波数特性を再現することができる。

【0036】

[第2の等価回路パラメータ生成方法]

続いて、添付図面を参照して、本発明に係る第2の等価回路パラメータ生成方法について説明する。本生成方法では、等価回路全体としての受動性が確保されるような拘束条件が決定される。その一方で、本生成方法では、個々の等価回路パラメータが負となることは禁止されないので、等価回路が局所的に受動性を失うことは許容される。

つまり、第2の等価回路パラメータ生成方法では、第1の等価回路パラメータ生成方法よりも緩和された拘束条件下で最小自乗近似を行う。これにより、第1の等価回路パラメータ生成方法で得られる等価パラメータよりも、さらにモデリング精度の高い等価回路パラメータが得られることが期待できる。

【0037】

具体的には、本生成方法において、等価回路パラメータは図3に示すようなフローで生成される。すなわち、本生成方法では、上記した第1の等価回路パラメータ生成方法と同様にして、ステップS1からステップS3を行う。

【0038】

続いて、本生成方法では、最小自乗近似を実行する前に、個々の等価回路パラメータが負となることは許容しつつ、等価回路全体としての受動性が確保されるような拘束条件を決定する(ステップS4)。そして、その拘束条件下で、(3)式による最小自乗近似を行う(ステップS5)。なお、ステップS5は、公知の数値解析ソフトウェアを用いることで容易に行うことができる。

【0039】

等価回路が全体として受動性を有するためには、その等価回路の抵抗成分が正であることが必要である。したがって、第2の等価回路パラメータ生成方法における拘束条件(以下、「第2の拘束条件」)は、

【数25】

となる。ここで、係数行列Arは係数行列Ac((4)式参照)の実数部であり、

【数26】

で表される。

ステップS4で決定された(20)式の条件下でステップS5の最小自乗近似を行うことで、等価回路が全体として受動性を有することが保証された留数ベクトルkを算出することができる。

【0040】

最後に、第2の等価回路パラメータ生成方法では、ステップS5で算出された留数を(8)〜(10)式、または(12)〜(14)式に代入し、選択した等価回路における各集中定数素子の素子値である等価回路パラメータを生成する(ステップS6)。

【0041】

以上のように、本発明に係る第2の等価回路パラメータ生成方法によれば、事前に決定された第2の拘束条件下で最小自乗近似を行うことにより、等価回路全体としての受動性が確保された等価回路パラメータを生成することができる。

また、第2の拘束条件は、局所的に受動性が失われることを禁止するものではないので、個々の等価回路パラメータの自由度が高い。したがって、第2の等価回路パラメータ生成方法によれば、第1の拘束条件を使用して得た等価回路よりも、さらにモデリング精度の高い等価回路を得ることができる。

【0042】

続いて、本発明に係る第1及び第2の等価回路パラメータ生成方法によってモデリングされた等価回路の周波数特性と、従来から行われている他の方法によってモデリングされた等価回路の周波数特性とを比較した実験結果について説明する。

【0043】

(比較実験2:積層セラミックコンデンサ、Fosterの第2回路)

本比較実験では、220nFの積層セラミックコンデンサを測定対象物とし、その周波数特性をインピーダンスメータで測定した。また、本比較実験では、等価回路としてG0とC∞を省略したFosterの第2回路を選択し、次数m=8、n=9の下で個数Ns=1、Nc=4とし、最小自乗近似を行った。

【0044】

(20)式に示す第2の拘束条件下で最小自乗近似を行い、算出された留数kを(13)及び(14)式に代入すると、最終的に、以下に示す等価回路パラメータが得られた。

【数27】

上記等価回路パラメータから明らかなように、本発明に係る第2の等価回路パラメータ生成方法では、局所的に受動性が損なわれることは禁止されないので、幾つかの集中定数素子が負の値を示している。

【0045】

本発明に係る第1の等価回路パラメータ生成方法によって得られた等価回路パラメータは次の通りである。

【数28】

この方法では、局所的に見ても全体として見ても等価回路の受動性が確保されるような第1の拘束条件下で最小自乗近似を行うので、負の値を示す集中定数素子は存在しない。

【0046】

従来方法によって得られた等価回路パラメータは次の通りである。

【数29】

この方法では、G1CとG4Cが負の素子値となり、少なくとも等価回路の局所的な受動性が損なわれてしまっている。また、この方法では、等価回路全体としての受動性を確保するような調整が一切行われていないので、等価回路全体としても受動性が保証されていない。

【0047】

また、比較方法によって得られた等価回路パラメータは次の通りである。

【数30】

【0048】

図6に、測定によって得られた積層セラミックコンデンサの周波数特性、及び上記4つの方法によって得られた等価回路の周波数特性を示す。

図6(A)に示すアドミタンス特性については、いずれの方法で得られた周波数特性も積層セラミックコンデンサの周波数特性(測定値)をよく再現している。また、図6(B)に示す位相特性については、各方法で得られた周波数特性は、特に30〜60MHz付近の帯域において誤差を有しているものの、各方法で得られた周波数特性同士にはほとんど差異がないように見える。

【0049】

しかしながら、図6(B)に示す位相特性の低周波領域を拡大した図7によれば、特に5MHz以下の帯域において、各方法に係る等価回路の周波数特性はかなり異なっていることが分かる。

まず、単に最小自乗近似を行っただけの従来方法に係る周波数特性は、500kHz以下の帯域において位相が90°を超えている。これは、従来方法によって得られた等価回路が、全体として受動性を有していないことを示している。次に、比較方法に係る周波数特性は、積層セラミックコンデンサの周波数特性(測定値)に対する誤差が非常に大きい。これは、負となった素子値を無理やり“0”にし、これに伴う他の素子値の調整を行わなかったためだと思われる。

【0050】

本発明に係る第1の等価回路パラメータ生成方法に係るグラフは、積層セラミックコンデンサの周波数特性(測定値)をよく再現している。また、本発明に係る第2の等価回路パラメータ生成方法に係るグラフは、第1の生成方法よりもさらに誤差が少なく、積層セラミックコンデンサの周波数特性(測定値)を高精度に再現している。これは、局所的に受動性が損なわれることを許容することにより、個々の等価回路パラメータの自由度が高くなったためだと思われる。

【0051】

なお、第2の拘束条件に別の拘束条件(以下、「第3の拘束条件」)を追加して、2以上の拘束条件の下で最小自乗近似を行ってもよい。以下、その方法について説明する。

【0052】

上記第2の等価回路パラメータ生成方法では、測定対象物の周波数特性に基づいて拘束条件を決定し、その拘束条件の下で最小自乗近似を行っている。上記してきたように、この方法によれば、測定を行った周波数領域における等価回路の受動性が保証される。一方、第2の等価回路パラメータ生成方法では、測定を行っていない周波数領域については何ら拘束がかけられていないので、等価回路の受動性は保証されない。

【0053】

図9に、一例として、比較実験2で使用した積層セラミックコンデンサの周波数特性を300kHz〜3GHzの範囲で測定し、その周波数特性を第2の等価回路パラメータ生成方法で近似して得た位相特性を示す。このグラフから明らかなように、測定範囲外である100kHz以下(厳密には、300kHz以下)の領域において、位相は90°を超えている。これは、当該周波数領域において、等価回路が受動性を有していないことを意味している。同様に、位相が−90°を下回る場合は、その周波数において等価回路が受動性を有していないことを意味する。

第3の拘束条件によれば、このような測定範囲外の周波数領域における受動性をも保証することができる。

【0054】

具体的には、第3の拘束条件を用いた方法において、等価回路パラメータは図8に示すようなフローで生成される。すなわち、本方法では、第2の等価回路パラメータ生成方法で等価回路パラメータが生成された後に(ステップS1〜S6)、当該等価回路パラメータを用いた等価回路の検証が行われる(ステップS7)。検証は、測定範囲外における等価回路の位相の絶対値が90°を超えているか否かによって行われる。位相の絶対値が90°を超えていない場合は(ステップS7の“No”)、測定範囲外においても受動性は保証されているので、当該フローはそのまま終了する。

【0055】

一方、位相の絶対値が90°を超えている場合は(ステップS7の“Yes”)、拘束をかける周波数が選択される。図9に示すように、周波数が低くなるにつれて位相が90°を超えて大きくなっていくような場合には、拘束をかける周波数として0Hzが選択される。そして、その周波数における周波数特性の実数成分が正((20)(21)式参照)であるという第3の拘束条件が追加される(ステップS8)。その後、第2及び第3の拘束条件の下で再度最小自乗近似が行われ、等価回路パラメータが生成される(ステップS5、S6)。結局、図9に示す一例では、測定範囲外である0Hzにおける周波数特性の実数成分について第3の拘束条件が追加され、第2及び第3の拘束条件の下で最小自乗近似が行われる。

なお、拘束をかける周波数の選択方法は上記したものに限定されず、例えば、実際に計算を行って得られた等価回路の周波数特性の中で、位相の絶対値が最も大きい周波数(図9に示す一例では、30Hz)で拘束をかけるようにしてもよい。

【0056】

続いて、第2及び第3の拘束条件の下で得られた等価回路の検証が行われ(ステップS7)、位相の絶対値が90°を超えている場合は新たな拘束条件が追加される(ステップS8)。以下、位相の絶対値が90°を超えなくなるまで、ステップS5からステップS8が繰り返し実行される。

【0057】

この方法を用いて、比較実験2と同一の測定対象物(積層セラミックコンデンサ)、条件(次数m=8、n=9、個数Ns=1、Nc=4)で最小自乗近似を行うと、最終的に、以下に示す等価回路パラメータが得られた。

【数31】

【0058】

図10に、測定によって得られた積層セラミックコンデンサの周波数特性(300kHz〜)、第2の等価回路パラメータ生成方法、及び第2の拘束条件と第3の拘束条件とを併用した方法によって得られた等価回路の周波数特性(30Hz〜)を示す。

前記の通り、第2の等価回路パラメータ生成方法に係る周波数特性は、測定範囲外である300kHz以下の領域において位相が90°を超え、受動性が大きく損なわれている。これに対して、第3の拘束条件を追加した方法に係る周波数特性は、当該領域においても位相が90°を超えることはない。

つまり、第3の拘束条件を追加した方法によれば、測定範囲外の周波数領域における受動性をも保証することができる。

【0059】

[等価回路パラメータ生成装置]

また、本発明は、上記各等価回路パラメータ生成方法を用いた等価回路パラメータ生成装置として実現することもできる。

【0060】

図11は、本発明に係る第1の等価回路パラメータ生成方法を用いた等価回路パラメータ生成装置の一構成例を示すブロック図である。等価回路パラメータ生成装置1に備えられた入力部4及び出力部7は、例えば、キーボード、液晶ディスプレイである。当該装置で等価回路パラメータを生成するユーザは、出力部7を参照して、入力部4を介して必要な指示を当該装置に与える。

【0061】

入力部4に測定開始の指示が入力されると、測定部3は、測定対象物10に微小な電流または電圧を出力し、測定対象物10の周波数特性を測定する(図3のステップS1に相当)。測定部3による測定は、プローブ2を介して行われる。測定によって得られたデータは、演算部5に送られ、メモリ等の記憶装置(図示せず)に格納される。

【0062】

続いて、使用可能な等価回路が選択肢として出力部7に表示され、そのうちの一つが入力部4を介して選択される(ステップS2に相当)。そして、入力部4を介して、最小自乗近似に用いる次数m、n、及び個数Ns、Ncが入力される(ステップS3に相当)。入力された次数、個数、及び等価回路の選択情報も、また、メモリ等の記憶装置に格納される。

【0063】

続いて、演算部5に含まれる拘束条件生成部6は、記憶装置に格納された情報を参照して、第1の拘束条件行列Dを生成する(ステップS4に相当、(19)式参照)。そして、演算部5は、第1の拘束条件行列D、記憶装置に格納された測定対象物10の周波数特性データ、次数m、n、及び個数Ns、Ncを用いて、(3)式による最小自乗近似を実行する(ステップS5に相当)。さらに、演算部5は、最小自乗近似によって得た留数に基づいて、選択した等価回路における各集中定数素子の等価回路パラメータを生成する(ステップS6に相当)。

第2の等価回路パラメータ生成方法を用いる場合は、第1の拘束条件行列Dの代わりに(20)式で表される第2の拘束条件を生成し、その条件下で(3)式による最小自乗近似を実行する(ステップS5に相当)。

【0064】

生成された等価回路パラメータは、出力部7に表示される。また、等価回路パラメータ生成装置1は、必要に応じて、生成された等価回路パラメータを電子データ(例えば、CSV形式)に変換して出力することもできる。

【0065】

以上、本発明の好ましい実施形態について説明したが、本発明は上記構成に限定されるものではない。

例えば、使用する等価回路はFosterの第1及び第2回路に限定されず、他の等価回路を使用することができる。

また、第1に等価回路パラメータ生成方法における拘束条件行列は(19)式に示したものに限定されず、例えば、各行を定数倍しても同一の作用効果を得ることができる。

【図面の簡単な説明】

【0066】

【図1】等価回路として用いられるFosterの第1回路図である。

【図2】等価回路として用いられるFosterの第2回路図である。

【図3】本発明に係る等価回路パラメータ生成方法のフローチャートである。

【図4】本発明に係る第1の等価回路パラメータ生成方法、従来方法、及び比較方法で、乾式進相コンデンサの周波数特性を近似したグラフであって、(A)はアドミタンス特性、(B)は位相特性のグラフである。

【図5】本発明に係る第1の等価回路パラメータ生成方法、従来方法、及び比較方法で、トロイダルコアの周波数特性を近似したグラフであって、(A)はインピーダンス特性、(B)は位相特性のグラフである。

【図6】本発明に係る第1及び第2の等価回路パラメータ生成方法、従来方法、及び比較方法で、積層セラミックコンデンサの周波数特性を近似したグラフであって、(A)はアドミタンス特性、(B)は位相特性のグラフである。

【図7】図6(B)に示す位相特性の低周波領域を拡大したグラフである。

【図8】第3の拘束条件を追加して最小自乗近似を行う等価回路パラメータ生成方法のフローチャートである。

【図9】本発明に係る第2の等価回路パラメータ生成方法、及び第3の拘束条件を追加して最小自乗近似を行う等価回路パラメータ生成方法で、積層セラミックコンデンサの周波数特性(位相特性)を近似したグラフである。

【図10】図9に示す位相特性の低周波領域を拡大したグラフである。

【図11】本発明に係る等価回路パラメータ生成装置の一構成例を示すブロック図である。

【符号の説明】

【0067】

1 等価回路パラメータ生成装置

2 プローブ

3 測定部

4 入力部

5 演算部

6 拘束条件生成部

7 出力部

10 測定対象物

【技術分野】

【0001】

本発明は、測定によって得られた周波数特性を、集中定数素子からなる等価回路に近似合成するための等価回路パラメータ生成装置、並びに生成方法に関する。

【背景技術】

【0002】

近年、パワーエレクトロニクスの分野では、システムの高周波化に伴ってEMIが大きな問題となっている。EMIは、他の電子機器に誤動作等の悪影響を及ぼすおそれがあることから、適切な対策を施すことが求められている。また、コンピュータシミュレーションによってEMI対策を検討する場合には、等価回路を構成する個々の素子の素子値(以下、「等価回路パラメータ」)をどのようにして生成し、集中定数素子からなる等価回路に近似(モデリング)するかが問題となる。

同様に、LSIの分野においても、動作周波数の上昇に伴って、素子間配線による信号伝播遅延、素子間配線同士の干渉等の問題が顕在化してきている。これらのメカニズムを解析し、適切な対策を施すためにも、素子間配線のモデリングは非常に重要である。

【0003】

従来の等価回路パラメータ生成方法としては、最小自乗近似を利用した方法が知られている。この従来の生成方法では、まず、モデリングしたい測定対象物のN点の周波数特性X(s)をインピーダンスメータ等の測定器で測定する。得られた周波数特性は、分数多項式で表現された測定周波数特性X^(s)で近似することができる。なお、表記“X^”は、Xの上にハット記号“^”が付されていることを意味する。

【数1】

ここで、m及びnは、モデリングしたい周波数特性の複雑さに応じて任意に決定することができる次数である。また、i=1、2・・・N、si=j2πfi(ただし、fi:サンプル周波数、j=√(−1))である。

(1)式を展開して、部分分数で表現すると次式となる。

【数2】

ここで、Nc及びNsは、必要とされるモデリング精度等に応じて、任意に決定することができる個数である。

【0004】

(2)式に含まれる(2+Ns+2Nc)個の留数kは、次式によって最小自乗近似することにより、算出される。

【数3】

ここで、行列Acは留数ベクトルkの係数行列であり、そのi行成分は、

【数4】

である。

また、(3)式において、測定周波数特性値ベクトルxc及び留数ベクトルkは、

【数5】

である。

ここで、(5)式の“N”は、測定サンプル数である。また、X(sN)は測定によって得られたN番目のサンプル周波数における測定周波数特性値である。

【0005】

続いて、回路合成が行われる。モデリングしたい周波数特性がインピーダンスの場合、(3)〜(6)式によって得られた(2+Ns+2Nc)個の留数は、図1及び次式で表される等価回路(Fosterの第1回路)に合成される。

【数6】

ここで、図1に示す等価回路の等価回路パラメータは、次式によって表される。

【数7】

なお、R0とL∞は省略することもできる。

【0006】

一方、モデリングしたい周波数特性がアドミタンスの場合、(3)〜(6)式によって得られた(2+Ns+2Nc)個の留数は、図2及び次式で表される等価回路(Fosterの第2回路)に合成される。

【数8】

ここで、図2に示す等価回路の等価回路パラメータは、次式によって表される。

【数9】

なお、G0とC∞は省略することもできる。

【0007】

ところが、上記した従来の等価回路パラメータ生成方法では、最終的に得られる等価回路パラメータ((8)〜(10)式、(12)〜(14)式参照)が負の値を示す場合があった。

本来、Fosterの第1回路(図1参照)及び第2回路(図2参照)は受動性を有する集中定数素子からなり、回路全体としても受動性を示すべきものある。しかしながら、回路の一部に負の素子値を有する集中定数素子が含まれると、当該回路は局所的に受動性を有していないことになり、回路全体としても受動性を有さない可能性がある。

したがって、従来の等価回路パラメータ生成方法で得られた等価回路の周波数特性は、現実の測定対象物と大きくかけ離れた周波数特性となる場合があった。また、当該回路を用いたシミュレーションは不安定になる場合があり、信頼性が問題となっていた。

【0008】

上記問題の解決を試みた等価回路パラメータ生成方法として、非特許文献1に係る方法がある。

この方法では、最小自乗近似によって得られた等価回路パラメータのうち、負となった素子の素子値を強制的に“0”にすることにより、等価回路の受動性を確保している。しかしながら、この方法によって得られた等価回路は、勝手に値が変更された集中定数素子が含まれることになるので、周波数特性のモデリングの精度が問題となっていた。

【非特許文献1】J. Morsey and A.C. Cangellaris,“PRIME: passive realization of interconnect models from measured data”, IEEE Electrical Performance of Electronic Packaging, 2001, pp.47-50

【発明の開示】

【発明が解決しようとする課題】

【0009】

そこで、本発明は、測定によって得られた周波数特性を集中定数素子からなる等価回路に高精度に近似合成することができ、しかも、当該等価回路全体としての受動性が保証される等価回路パラメータ生成装置、並びに生成方法を提供することを課題とする。

【課題を解決するための手段】

【0010】

本発明者等は、上記課題を解決するために鋭意検討を重ねた結果、最小自乗近似を行う前に、(1)各等価回路パラメータが負となることを禁止し、局所的に見ても全体として見ても等価回路の受動性が確保されるような拘束条件、または(2)個々の等価回路パラメータが負となることは許容しつつ、等価回路全体としての受動性が確保されるような拘束条件を決定し、その条件下で最小自乗近似を行うことを見出し、本発明を完成させた。

【0011】

すなわち、本発明に係る第1の等価回路パラメータ生成方法は、留数kを含んだ形式に近似された測定対象物の周波数特性と、前記留数kからなる等価回路パラメータを有する等価回路とを準備し、最小自乗近似を用いて前記周波数特性の留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、前記最小自乗近似を行う前に、前記等価回路パラメータが負とならないような留数kに関する第1の拘束条件を決定し、当該第1の拘束条件下で前記最小自乗近似を行って留数kを算出することを特徴とする。

【0012】

また、本発明に係る第1の等価回路パラメータ生成装置は、測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、前記測定対象物の周波数特性を測定するとともに、測定された前記周波数特性を前記留数kを含んだ形式に近似する測定部と、適宜必要な情報の入力を受け付ける入力部と、前記入力部から入力された等価回路選択データに基づいて選択された前記等価回路の前記等価回路パラメータが負とならないような前記留数kに関する第1の拘束条件を決定する拘束条件決定部と、前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記第1の拘束条件を受け取り、前記第1の拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路パラメータを生成する演算部と、を備えたことを特徴とする。

【0013】

また、本発明に係る第2の等価回路パラメータ生成方法は、測定対象物を所定の周波数範囲で測定し、N個の測定周波数特性値X(si)(ただし、i=1、2…N)からなる周波数特性を得て、当該周波数特性を留数kを含んだ形式に近似するとともに、前記留数kからなる等価回路パラメータを有する等価回路を準備し、(数10)式から(数12)式を用いた最小自乗近似を行って前記留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、

【数10】

【数11】

【数12】

(ただし、Ac:留数ベクトルkの係数行列、Aic:係数行列Acのi行成分、i=1、2・・・N、si=j2πfi(ただし、fi:サンプル周波数、j=√(−1))、Nc:任意個数、Ns:任意個数)

前記最小自乗近似を行う前に、(数13)式で表される、前記所定の周波数範囲内についての第2の拘束条件を決定し、

【数13】

(ただし、Ar:係数行列Acの実数部)

前記第2の拘束条件下で前記最小自乗近似を行い、留数kを算出することを特徴とする。

【0014】

上記第2の等価回路パラメータ生成方法は、好ましくは、前記所定の周波数範囲外の任意の周波数についての第3の拘束条件を決定し、前記第2及び第3の拘束条件の下で前記最小自乗近似を行い、留数kを算出することを特徴とする。

【0015】

また、本発明に係る第2の等価回路パラメータ生成装置は、上記第2の等価回路パラメータ生成方法を用いて決定される前記第2の拘束条件、または前記第2及び第3の拘束条件からなる拘束条件を用いて、測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、前記測定対象物の周波数特性を測定するとともに、測定された周波数特性を前記留数kを含んだ形式に近似する測定部と、前記留数kに関する前記拘束条件を決定する拘束条件決定部と、前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記拘束条件を受け取り、前記拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路の前記等価回路パラメータを生成する演算部と、を備えたことを特徴とする。

【発明の効果】

【0016】

本発明に係る等価回路パラメータ生成装置、及び生成方法によれば、測定によって得られた周波数特性を集中定数素子からなる等価回路に近似合成するにあたり、事前に、(1)各等価回路パラメータが負となることを禁止し、局所的に見ても全体として見ても等価回路の受動性が確保されるような第1の拘束条件、または(2)個々の等価回路パラメータが負となることは許容しつつ、等価回路全体としての受動性が確保されるような第2の拘束条件を算出しておき、いずれかの条件下で最小自乗近似を行うことによって、少なくとも回路全体としての受動性を確保しつつ、高精度に当該周波数特性を再現する等価回路を得ることができる。

【発明を実施するための最良の形態】

【0017】

[第1の等価回路パラメータ生成方法]

以下、添付図面を参照して、本発明に係る第1の等価回路パラメータ生成方法について説明する。本方法では、各等価回路パラメータが負となることを禁止することにより、局所的に見ても全体として見ても等価回路の受動性が確保されるような拘束条件が決定される。

【0018】

具体的には、本生成方法において、等価回路パラメータは図3に示すようなフローで生成される。すなわち、本生成方法では、はじめに、モデリングしたい測定対象物の周波数特性をインピーダンスメータ等の測定器で測定し(図3のステップS1)、使用する等価回路を選択し(ステップS2)、当該周波数特性に応じて次数m、n、及び個数Nc、Nsを決定する(ステップS3)。等価回路は、例えば、一般的な等価回路であるFosterの第1回路(図1参照)、及びFosterの第2回路(図2参照)等から選択される。なお、等価回路の選択(ステップS2)は、ステップS1の前、またはステップS3とS4の間に行ってもよい。

【0019】

続いて、本生成方法では、最小自乗近似を実行する前に、各素子の素子値が負とならないような拘束条件を決定する(ステップS4)。そして、その拘束条件下で、(3)式による最小自乗近似を行う(ステップS5)。なお、ステップS5は、公知の数値解析ソフトウェアを用いることで容易に行うことができる。

【0020】

例えば、モデリングしたい測定対象物の周波数特性がインピーダンスの場合、ステップS3において、図1に示すFosterの第1回路が等価回路として選択される。

この等価回路において、R0、L∞が負とならない条件は、(8)式より、

【数14】

また、(9)式より、Cls、Glsが負とならない条件は、

【数15】

さらに、(10)式より、Clc、Glc、Llc、Rlcが負とならない条件は、

【数16】

となる。

【0021】

(15)〜(17)式の条件を行列・ベクトル形式で表現すると、

【数17】

となる。ここで、行列Dは、

【数18】

である。

ステップS4で決定された(18)式の条件(以下、「第1の拘束条件」)下でステップS5の最小自乗近似を行うことで、すべての素子値が負とならないことが保証された留数ベクトルkを算出することができる。なお、(19)式の行列Dを、以下、「第1の拘束条件行列」と称する。

【0022】

最後に、本生成方法では、ステップS5で算出された留数を(15)〜(17)式に代入し、選択した等価回路における各集中定数素子の素子値である等価回路パラメータを生成する(ステップS6)。

【0023】

以上のように、本発明に係る第1の等価回路パラメータ生成方法によれば、事前に決定された第1の拘束条件下で最小自乗近似を行うことにより、負の素子値を含まない等価回路パラメータを生成することができる。

また、第1の拘束条件によれば、すべての素子値が負とならないように調整されるとともに、この調整に伴って、他の素子値が最小自乗近似の過程で調整されるので、等価回路全体としての周波数特性の精度が悪化するのを防ぐことができる。

さらに、本発明に係る第1の等価回路パラメータ生成方法で得られる等価回路は、負となっていた幾つかの素子値が“0”になるので、当該等価回路を用いたシミュレーションを簡略化及び高速化することができる。

【0024】

続いて、本発明に係る第1の等価回路パラメータ生成方法によってモデリングされた等価回路の周波数特性と、従来から行われている他の方法によってモデリングされた等価回路の周波数特性とを比較した実験結果について説明する。

【0025】

(比較実験1−1:乾式進相コンデンサ、Fosterの第2回路)

本比較実験では、50μFの乾式進相コンデンサを2個直列に接続したものを測定対象物とし、その周波数特性をインピーダンスメータで測定した。また、本比較実験では、等価回路としてFosterの第2回路を選択し、次数m=2、n=3の下で個数Ns=1、Nc=1とし、最小自乗近似を行った。

なお、前記の通り、次数m、n、及び個数Ns、Ncは任意に決定することができる。基本的に、個数NsとNcを大きくするとモデリングの精度が上がるが、最小自乗近似の計算に時間を要することとなる。また、個数Ns及びNcによるモデリング精度の向上には限界があり、一定以上にしてもほとんどモデリング精度は向上しない。

【0026】

(12)〜(14)式より第1の拘束条件を決定し、その条件下で最小自乗近似を行うと、最終的に、以下に示す等価回路パラメータが得られた。

【数19】

上記等価回路パラメータから明らかなように、本発明に係る第1の等価回路パラメータ生成方法では第1の拘束条件下で最小自乗近似を行うため、負の値を有する集中定数素子が存在しない。

【0027】

第1の拘束条件を使用することなく、単に最小自乗近似を行った場合(以下、「従来方法」)に得られた等価回路パラメータは、以下の通りである。

【数20】

この方法では、素子G0、C∞、G1cが負の素子値となり、少なくとも等価回路の局所的な受動性が損なわれてしまっている。また、従来方法では、等価回路全体としての受動性を確保するような調整が一切行われていない。したがって、この等価回路パラメータを用いた等価回路は、全体として見ても受動性が保証されていない。

【0028】

さらに、比較のために、従来方法において得られた等価回路パラメータのうち、負となった素子値を無理やり“0”とし、他の素子値について何ら調整を行わない場合(以下、「比較方法」)についても実験を行った。比較方法で得られた等価回路パラメータは、以下の通りである。

【数21】

【0029】

図4に、測定によって得られた乾式進相コンデンサの周波数特性、及び上記3つの方法によって得られた等価回路の周波数特性を示す。

図4(A)に示すアドミタンス特性については、いずれの方法に係る周波数特性も乾式進相コンデンサの周波数特性(測定値)をよく再現している。また、図4(B)に示す位相特性については、100Hz、1〜10MHz付近の帯域において、比較方法に係るグラフは誤差が比較的大きい。これは、負となった素子値を、無理やり“0”にし、他の素子値を調整しなかったためだと思われる。

なお、従来方法に係るグラフは、アドミタンス及び位相の両特性において乾式進相コンデンサの周波数特性(測定値)をよく再現しているが、前記の通り、従来方法に係る等価回路は全体として受動性が保証されていない。したがって、この等価回路は、乾式進相コンデンサの周波数特性とかけ離れた特性を示すおそれがある。

【0030】

(比較実験1−2:トロイダルコア、Fosterの第1回路)

本比較実験では、500μHのトロイダルコアを測定対象物とし、その周波数特性をインピーダンスメータで測定した。また、本比較実験では、等価回路としてFosterの第1回路を選択し、次数m=5、n=6の下で個数Ns=0、Nc=3とし、最小自乗近似を行った。

【0031】

(8)〜(10)式より第1の拘束条件を決定し、その条件下で最小自乗近似を行うと、最終的に、以下に示す等価回路パラメータが得られた。

【数22】

上記等価回路パラメータから明らかなように、本発明に係る第1の等価回路パラメータ生成方法では、第1の拘束条件下で最小自乗近似を行うため、負の値を有する集中定数素子が存在しない。

【0032】

従来方法によって得られた等価回路パラメータは次の通りである。

【数23】

この方法では、素子C1s、G1s、R1cが負の素子値となり、少なくとも等価回路の局所的な受動性が損なわれてしまっている。

【0033】

また、比較方法によって得られた等価回路パラメータは次の通りである。

【数24】

【0034】

図5に、測定によって得られたトロイダルコアの周波数特性、及び上記3つの方法によって得られた等価回路の周波数特性を示す。

図5(A)に示すインピーダンス特性については、従来方法及び本発明に係る第1の生成方法で得られた周波数特性は、いずれもトロイダルコアの周波数特性(測定値)をよく再現している。一方、比較方法に係るグラフは、10kHz以下の帯域で他の方法に比べて誤差が大きくなっている。さらに、比較方法で得られた周波数特性は、全周波数帯域において、トロイダルコアの位相特性(測定値)を全く再現できていない(図5(B)参照)。

なお、比較実験1と同様に、従来方法で得られた周波数特性は、インピーダンス及び位相の両特性においてトロイダルコアの周波数特性(測定値)をよく再現しているが、前記の通り、従来方法に係る等価回路は全体として受動性が保証されていない。したがって、この等価回路は、トロイダルコアの周波数特性とかけ離れた特性を示すおそれがある。

【0035】

以上をまとめると、本発明に係る第1の等価回路パラメータ生成方法では、測定によって得られた測定対象物の周波数特性を集中定数素子からなる等価回路に近似合成するにあたり、事前に、各素子の値が負とならないような第1の拘束条件を算出しておき、その条件下で最小自乗近似を行う。これにより、受動性を損なうことなく、高精度に測定対象物の周波数特性を再現することができる。

【0036】

[第2の等価回路パラメータ生成方法]

続いて、添付図面を参照して、本発明に係る第2の等価回路パラメータ生成方法について説明する。本生成方法では、等価回路全体としての受動性が確保されるような拘束条件が決定される。その一方で、本生成方法では、個々の等価回路パラメータが負となることは禁止されないので、等価回路が局所的に受動性を失うことは許容される。

つまり、第2の等価回路パラメータ生成方法では、第1の等価回路パラメータ生成方法よりも緩和された拘束条件下で最小自乗近似を行う。これにより、第1の等価回路パラメータ生成方法で得られる等価パラメータよりも、さらにモデリング精度の高い等価回路パラメータが得られることが期待できる。

【0037】

具体的には、本生成方法において、等価回路パラメータは図3に示すようなフローで生成される。すなわち、本生成方法では、上記した第1の等価回路パラメータ生成方法と同様にして、ステップS1からステップS3を行う。

【0038】

続いて、本生成方法では、最小自乗近似を実行する前に、個々の等価回路パラメータが負となることは許容しつつ、等価回路全体としての受動性が確保されるような拘束条件を決定する(ステップS4)。そして、その拘束条件下で、(3)式による最小自乗近似を行う(ステップS5)。なお、ステップS5は、公知の数値解析ソフトウェアを用いることで容易に行うことができる。

【0039】

等価回路が全体として受動性を有するためには、その等価回路の抵抗成分が正であることが必要である。したがって、第2の等価回路パラメータ生成方法における拘束条件(以下、「第2の拘束条件」)は、

【数25】

となる。ここで、係数行列Arは係数行列Ac((4)式参照)の実数部であり、

【数26】

で表される。

ステップS4で決定された(20)式の条件下でステップS5の最小自乗近似を行うことで、等価回路が全体として受動性を有することが保証された留数ベクトルkを算出することができる。

【0040】

最後に、第2の等価回路パラメータ生成方法では、ステップS5で算出された留数を(8)〜(10)式、または(12)〜(14)式に代入し、選択した等価回路における各集中定数素子の素子値である等価回路パラメータを生成する(ステップS6)。

【0041】

以上のように、本発明に係る第2の等価回路パラメータ生成方法によれば、事前に決定された第2の拘束条件下で最小自乗近似を行うことにより、等価回路全体としての受動性が確保された等価回路パラメータを生成することができる。

また、第2の拘束条件は、局所的に受動性が失われることを禁止するものではないので、個々の等価回路パラメータの自由度が高い。したがって、第2の等価回路パラメータ生成方法によれば、第1の拘束条件を使用して得た等価回路よりも、さらにモデリング精度の高い等価回路を得ることができる。

【0042】

続いて、本発明に係る第1及び第2の等価回路パラメータ生成方法によってモデリングされた等価回路の周波数特性と、従来から行われている他の方法によってモデリングされた等価回路の周波数特性とを比較した実験結果について説明する。

【0043】

(比較実験2:積層セラミックコンデンサ、Fosterの第2回路)

本比較実験では、220nFの積層セラミックコンデンサを測定対象物とし、その周波数特性をインピーダンスメータで測定した。また、本比較実験では、等価回路としてG0とC∞を省略したFosterの第2回路を選択し、次数m=8、n=9の下で個数Ns=1、Nc=4とし、最小自乗近似を行った。

【0044】

(20)式に示す第2の拘束条件下で最小自乗近似を行い、算出された留数kを(13)及び(14)式に代入すると、最終的に、以下に示す等価回路パラメータが得られた。

【数27】

上記等価回路パラメータから明らかなように、本発明に係る第2の等価回路パラメータ生成方法では、局所的に受動性が損なわれることは禁止されないので、幾つかの集中定数素子が負の値を示している。

【0045】

本発明に係る第1の等価回路パラメータ生成方法によって得られた等価回路パラメータは次の通りである。

【数28】

この方法では、局所的に見ても全体として見ても等価回路の受動性が確保されるような第1の拘束条件下で最小自乗近似を行うので、負の値を示す集中定数素子は存在しない。

【0046】

従来方法によって得られた等価回路パラメータは次の通りである。

【数29】

この方法では、G1CとG4Cが負の素子値となり、少なくとも等価回路の局所的な受動性が損なわれてしまっている。また、この方法では、等価回路全体としての受動性を確保するような調整が一切行われていないので、等価回路全体としても受動性が保証されていない。

【0047】

また、比較方法によって得られた等価回路パラメータは次の通りである。

【数30】

【0048】

図6に、測定によって得られた積層セラミックコンデンサの周波数特性、及び上記4つの方法によって得られた等価回路の周波数特性を示す。

図6(A)に示すアドミタンス特性については、いずれの方法で得られた周波数特性も積層セラミックコンデンサの周波数特性(測定値)をよく再現している。また、図6(B)に示す位相特性については、各方法で得られた周波数特性は、特に30〜60MHz付近の帯域において誤差を有しているものの、各方法で得られた周波数特性同士にはほとんど差異がないように見える。

【0049】

しかしながら、図6(B)に示す位相特性の低周波領域を拡大した図7によれば、特に5MHz以下の帯域において、各方法に係る等価回路の周波数特性はかなり異なっていることが分かる。

まず、単に最小自乗近似を行っただけの従来方法に係る周波数特性は、500kHz以下の帯域において位相が90°を超えている。これは、従来方法によって得られた等価回路が、全体として受動性を有していないことを示している。次に、比較方法に係る周波数特性は、積層セラミックコンデンサの周波数特性(測定値)に対する誤差が非常に大きい。これは、負となった素子値を無理やり“0”にし、これに伴う他の素子値の調整を行わなかったためだと思われる。

【0050】

本発明に係る第1の等価回路パラメータ生成方法に係るグラフは、積層セラミックコンデンサの周波数特性(測定値)をよく再現している。また、本発明に係る第2の等価回路パラメータ生成方法に係るグラフは、第1の生成方法よりもさらに誤差が少なく、積層セラミックコンデンサの周波数特性(測定値)を高精度に再現している。これは、局所的に受動性が損なわれることを許容することにより、個々の等価回路パラメータの自由度が高くなったためだと思われる。

【0051】

なお、第2の拘束条件に別の拘束条件(以下、「第3の拘束条件」)を追加して、2以上の拘束条件の下で最小自乗近似を行ってもよい。以下、その方法について説明する。

【0052】

上記第2の等価回路パラメータ生成方法では、測定対象物の周波数特性に基づいて拘束条件を決定し、その拘束条件の下で最小自乗近似を行っている。上記してきたように、この方法によれば、測定を行った周波数領域における等価回路の受動性が保証される。一方、第2の等価回路パラメータ生成方法では、測定を行っていない周波数領域については何ら拘束がかけられていないので、等価回路の受動性は保証されない。

【0053】

図9に、一例として、比較実験2で使用した積層セラミックコンデンサの周波数特性を300kHz〜3GHzの範囲で測定し、その周波数特性を第2の等価回路パラメータ生成方法で近似して得た位相特性を示す。このグラフから明らかなように、測定範囲外である100kHz以下(厳密には、300kHz以下)の領域において、位相は90°を超えている。これは、当該周波数領域において、等価回路が受動性を有していないことを意味している。同様に、位相が−90°を下回る場合は、その周波数において等価回路が受動性を有していないことを意味する。

第3の拘束条件によれば、このような測定範囲外の周波数領域における受動性をも保証することができる。

【0054】

具体的には、第3の拘束条件を用いた方法において、等価回路パラメータは図8に示すようなフローで生成される。すなわち、本方法では、第2の等価回路パラメータ生成方法で等価回路パラメータが生成された後に(ステップS1〜S6)、当該等価回路パラメータを用いた等価回路の検証が行われる(ステップS7)。検証は、測定範囲外における等価回路の位相の絶対値が90°を超えているか否かによって行われる。位相の絶対値が90°を超えていない場合は(ステップS7の“No”)、測定範囲外においても受動性は保証されているので、当該フローはそのまま終了する。

【0055】

一方、位相の絶対値が90°を超えている場合は(ステップS7の“Yes”)、拘束をかける周波数が選択される。図9に示すように、周波数が低くなるにつれて位相が90°を超えて大きくなっていくような場合には、拘束をかける周波数として0Hzが選択される。そして、その周波数における周波数特性の実数成分が正((20)(21)式参照)であるという第3の拘束条件が追加される(ステップS8)。その後、第2及び第3の拘束条件の下で再度最小自乗近似が行われ、等価回路パラメータが生成される(ステップS5、S6)。結局、図9に示す一例では、測定範囲外である0Hzにおける周波数特性の実数成分について第3の拘束条件が追加され、第2及び第3の拘束条件の下で最小自乗近似が行われる。

なお、拘束をかける周波数の選択方法は上記したものに限定されず、例えば、実際に計算を行って得られた等価回路の周波数特性の中で、位相の絶対値が最も大きい周波数(図9に示す一例では、30Hz)で拘束をかけるようにしてもよい。

【0056】

続いて、第2及び第3の拘束条件の下で得られた等価回路の検証が行われ(ステップS7)、位相の絶対値が90°を超えている場合は新たな拘束条件が追加される(ステップS8)。以下、位相の絶対値が90°を超えなくなるまで、ステップS5からステップS8が繰り返し実行される。

【0057】

この方法を用いて、比較実験2と同一の測定対象物(積層セラミックコンデンサ)、条件(次数m=8、n=9、個数Ns=1、Nc=4)で最小自乗近似を行うと、最終的に、以下に示す等価回路パラメータが得られた。

【数31】

【0058】

図10に、測定によって得られた積層セラミックコンデンサの周波数特性(300kHz〜)、第2の等価回路パラメータ生成方法、及び第2の拘束条件と第3の拘束条件とを併用した方法によって得られた等価回路の周波数特性(30Hz〜)を示す。

前記の通り、第2の等価回路パラメータ生成方法に係る周波数特性は、測定範囲外である300kHz以下の領域において位相が90°を超え、受動性が大きく損なわれている。これに対して、第3の拘束条件を追加した方法に係る周波数特性は、当該領域においても位相が90°を超えることはない。

つまり、第3の拘束条件を追加した方法によれば、測定範囲外の周波数領域における受動性をも保証することができる。

【0059】

[等価回路パラメータ生成装置]

また、本発明は、上記各等価回路パラメータ生成方法を用いた等価回路パラメータ生成装置として実現することもできる。

【0060】

図11は、本発明に係る第1の等価回路パラメータ生成方法を用いた等価回路パラメータ生成装置の一構成例を示すブロック図である。等価回路パラメータ生成装置1に備えられた入力部4及び出力部7は、例えば、キーボード、液晶ディスプレイである。当該装置で等価回路パラメータを生成するユーザは、出力部7を参照して、入力部4を介して必要な指示を当該装置に与える。

【0061】

入力部4に測定開始の指示が入力されると、測定部3は、測定対象物10に微小な電流または電圧を出力し、測定対象物10の周波数特性を測定する(図3のステップS1に相当)。測定部3による測定は、プローブ2を介して行われる。測定によって得られたデータは、演算部5に送られ、メモリ等の記憶装置(図示せず)に格納される。

【0062】

続いて、使用可能な等価回路が選択肢として出力部7に表示され、そのうちの一つが入力部4を介して選択される(ステップS2に相当)。そして、入力部4を介して、最小自乗近似に用いる次数m、n、及び個数Ns、Ncが入力される(ステップS3に相当)。入力された次数、個数、及び等価回路の選択情報も、また、メモリ等の記憶装置に格納される。

【0063】

続いて、演算部5に含まれる拘束条件生成部6は、記憶装置に格納された情報を参照して、第1の拘束条件行列Dを生成する(ステップS4に相当、(19)式参照)。そして、演算部5は、第1の拘束条件行列D、記憶装置に格納された測定対象物10の周波数特性データ、次数m、n、及び個数Ns、Ncを用いて、(3)式による最小自乗近似を実行する(ステップS5に相当)。さらに、演算部5は、最小自乗近似によって得た留数に基づいて、選択した等価回路における各集中定数素子の等価回路パラメータを生成する(ステップS6に相当)。

第2の等価回路パラメータ生成方法を用いる場合は、第1の拘束条件行列Dの代わりに(20)式で表される第2の拘束条件を生成し、その条件下で(3)式による最小自乗近似を実行する(ステップS5に相当)。

【0064】

生成された等価回路パラメータは、出力部7に表示される。また、等価回路パラメータ生成装置1は、必要に応じて、生成された等価回路パラメータを電子データ(例えば、CSV形式)に変換して出力することもできる。

【0065】

以上、本発明の好ましい実施形態について説明したが、本発明は上記構成に限定されるものではない。

例えば、使用する等価回路はFosterの第1及び第2回路に限定されず、他の等価回路を使用することができる。

また、第1に等価回路パラメータ生成方法における拘束条件行列は(19)式に示したものに限定されず、例えば、各行を定数倍しても同一の作用効果を得ることができる。

【図面の簡単な説明】

【0066】

【図1】等価回路として用いられるFosterの第1回路図である。

【図2】等価回路として用いられるFosterの第2回路図である。

【図3】本発明に係る等価回路パラメータ生成方法のフローチャートである。

【図4】本発明に係る第1の等価回路パラメータ生成方法、従来方法、及び比較方法で、乾式進相コンデンサの周波数特性を近似したグラフであって、(A)はアドミタンス特性、(B)は位相特性のグラフである。

【図5】本発明に係る第1の等価回路パラメータ生成方法、従来方法、及び比較方法で、トロイダルコアの周波数特性を近似したグラフであって、(A)はインピーダンス特性、(B)は位相特性のグラフである。

【図6】本発明に係る第1及び第2の等価回路パラメータ生成方法、従来方法、及び比較方法で、積層セラミックコンデンサの周波数特性を近似したグラフであって、(A)はアドミタンス特性、(B)は位相特性のグラフである。

【図7】図6(B)に示す位相特性の低周波領域を拡大したグラフである。

【図8】第3の拘束条件を追加して最小自乗近似を行う等価回路パラメータ生成方法のフローチャートである。

【図9】本発明に係る第2の等価回路パラメータ生成方法、及び第3の拘束条件を追加して最小自乗近似を行う等価回路パラメータ生成方法で、積層セラミックコンデンサの周波数特性(位相特性)を近似したグラフである。

【図10】図9に示す位相特性の低周波領域を拡大したグラフである。

【図11】本発明に係る等価回路パラメータ生成装置の一構成例を示すブロック図である。

【符号の説明】

【0067】

1 等価回路パラメータ生成装置

2 プローブ

3 測定部

4 入力部

5 演算部

6 拘束条件生成部

7 出力部

10 測定対象物

【特許請求の範囲】

【請求項1】

留数kを含んだ形式に近似された測定対象物の周波数特性と、前記留数kからなる等価回路パラメータを有する等価回路とを準備し、最小自乗近似を用いて前記周波数特性の留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、

前記最小自乗近似を行う前に、

前記等価回路パラメータが負とならないような留数kに関する第1の拘束条件を決定し、当該第1の拘束条件下で前記最小自乗近似を行って留数kを算出することを特徴とする生成方法。

【請求項2】

測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、

前記測定対象物の周波数特性を測定するとともに、測定された前記周波数特性を前記留数kを含んだ形式に近似する測定部と、

適宜必要な情報の入力を受け付ける入力部と、

前記入力部から入力された等価回路選択データに基づいて選択された前記等価回路の前記等価回路パラメータが負とならないような前記留数kに関する第1の拘束条件を決定する拘束条件決定部と、

前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記第1の拘束条件を受け取り、前記第1の拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路パラメータを生成する演算部と、

を備えたことを特徴とする等価回路パラメータ生成装置。

【請求項3】

測定対象物を所定の周波数範囲内で測定し、N個の測定周波数特性値X(si)(ただし、i=1、2…N)からなる周波数特性を得て、当該周波数特性を留数kを含んだ形式に近似するとともに、前記留数kからなる等価回路パラメータを有する等価回路を準備し、(数1)式から(数3)式を用いた最小自乗近似を行って前記留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、

【数1】

【数2】

【数3】

(ただし、Ac:留数ベクトルkの係数行列、Aic:係数行列Acのi行成分、i=1、2・・・N、si=j2πfi(ただし、fi:サンプル周波数、j=√(−1))、Nc:任意個数、Ns:任意個数)

前記最小自乗近似を行う前に、(数4)式で表される、前記所定の周波数範囲内についての第2の拘束条件を決定し、

【数4】

(ただし、Ar:係数行列Acの実数部)

前記第2の拘束条件下で前記最小自乗近似を行い、留数kを算出することを特徴とする生成方法。

【請求項4】

前記所定の周波数範囲外の任意の周波数についての第3の拘束条件を決定し、前記第2及び第3の拘束条件の下で前記最小自乗近似を行い、留数kを算出することを特徴とする請求項3に記載の生成方法。

【請求項5】

請求項3または4に記載の方法を用いて決定される前記第2の拘束条件、または前記第2及び第3の拘束条件からなる拘束条件を用いて、測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、

前記測定対象物の周波数特性を測定するとともに、測定された周波数特性を前記留数kを含んだ形式に近似する測定部と、

前記留数kに関する前記拘束条件を決定する拘束条件決定部と、

前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記拘束条件を受け取り、前記拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路の前記等価回路パラメータを生成する演算部と、

を備えたことを特徴とする等価回路パラメータ生成装置。

【請求項1】

留数kを含んだ形式に近似された測定対象物の周波数特性と、前記留数kからなる等価回路パラメータを有する等価回路とを準備し、最小自乗近似を用いて前記周波数特性の留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、

前記最小自乗近似を行う前に、

前記等価回路パラメータが負とならないような留数kに関する第1の拘束条件を決定し、当該第1の拘束条件下で前記最小自乗近似を行って留数kを算出することを特徴とする生成方法。

【請求項2】

測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、

前記測定対象物の周波数特性を測定するとともに、測定された前記周波数特性を前記留数kを含んだ形式に近似する測定部と、

適宜必要な情報の入力を受け付ける入力部と、

前記入力部から入力された等価回路選択データに基づいて選択された前記等価回路の前記等価回路パラメータが負とならないような前記留数kに関する第1の拘束条件を決定する拘束条件決定部と、

前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記第1の拘束条件を受け取り、前記第1の拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路パラメータを生成する演算部と、

を備えたことを特徴とする等価回路パラメータ生成装置。

【請求項3】

測定対象物を所定の周波数範囲内で測定し、N個の測定周波数特性値X(si)(ただし、i=1、2…N)からなる周波数特性を得て、当該周波数特性を留数kを含んだ形式に近似するとともに、前記留数kからなる等価回路パラメータを有する等価回路を準備し、(数1)式から(数3)式を用いた最小自乗近似を行って前記留数kを算出することにより、前記測定対象物の周波数特性に近似した周波数特性を有する等価回路の前記等価回路パラメータを生成する方法であって、

【数1】

【数2】

【数3】

(ただし、Ac:留数ベクトルkの係数行列、Aic:係数行列Acのi行成分、i=1、2・・・N、si=j2πfi(ただし、fi:サンプル周波数、j=√(−1))、Nc:任意個数、Ns:任意個数)

前記最小自乗近似を行う前に、(数4)式で表される、前記所定の周波数範囲内についての第2の拘束条件を決定し、

【数4】

(ただし、Ar:係数行列Acの実数部)

前記第2の拘束条件下で前記最小自乗近似を行い、留数kを算出することを特徴とする生成方法。

【請求項4】

前記所定の周波数範囲外の任意の周波数についての第3の拘束条件を決定し、前記第2及び第3の拘束条件の下で前記最小自乗近似を行い、留数kを算出することを特徴とする請求項3に記載の生成方法。

【請求項5】

請求項3または4に記載の方法を用いて決定される前記第2の拘束条件、または前記第2及び第3の拘束条件からなる拘束条件を用いて、測定対象物の周波数特性を、留数kからなる等価回路パラメータを有する等価回路で近似するための等価回路パラメータ生成装置であって、

前記測定対象物の周波数特性を測定するとともに、測定された周波数特性を前記留数kを含んだ形式に近似する測定部と、

前記留数kに関する前記拘束条件を決定する拘束条件決定部と、

前記測定部から前記留数kを含む前記周波数特性に関するデータを受け取るとともに、前記拘束条件決定部から前記拘束条件を受け取り、前記拘束条件下で前記周波数特性の最小自乗近似を行って前記留数kを算出し、算出された前記留数kに基づいて前記等価回路の前記等価回路パラメータを生成する演算部と、

を備えたことを特徴とする等価回路パラメータ生成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2009−134683(P2009−134683A)

【公開日】平成21年6月18日(2009.6.18)

【国際特許分類】

【出願番号】特願2008−49169(P2008−49169)

【出願日】平成20年2月29日(2008.2.29)

【出願人】(503027931)学校法人同志社 (346)

【Fターム(参考)】

【公開日】平成21年6月18日(2009.6.18)

【国際特許分類】

【出願日】平成20年2月29日(2008.2.29)

【出願人】(503027931)学校法人同志社 (346)

【Fターム(参考)】

[ Back to top ]