粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、n型FETおよびp型FETの双方を含むCMOSデバイス構造等の半導体デバイス構造に関する。

【背景技術】

【0002】

例えばCMOSデバイス技術のような将来の半導体にとって、移動度の向上は重要である。従来のプロセス技術からの性能改善は、達成することが極めて困難になっている。Siチャネルに応力を印加するための方法には、チャネルの下部から応力を印加するSiGeを用いること、様々な側面から応力を印加する異なる浅いトレンチ分離(STI:shallow trench isolation)材料の選択、および、側面から長手方向の応力を印加するSiNエッチ・ストップ層が含まれる。歪みSiキャップ層(stained Si cap layer)を用いたSiGeバッファ層または注入−アニール−バッファ手法の欠点は、周知である。その欠点には、歩留まりに大きな影響を与える転位、および、As拡散の向上を制御することが極めて困難であることが含まれる。更に、このプロセスは、非常に複雑でコストが高い。STI手法は、それよりもコストが低いが、ゲートに対して自己整合(self-aligned)せず、RXサイズに関して敏感である。窒化物エッチ・ストップ層を用いて応力を生成するというコストの低い手法は、ある程度の利点があるが、その利点は比較的瑣末なものと考えられている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

本発明は、チャネル移動度の向上を利用してデバイスの性能を改善する。本発明は、適正に調整したポリシリコン・ゲート・スタックの応力特性を用いることによって、チャネルの上部から移動度を改善する。本発明より以前には、これらの応力特性を制御することは極めて困難であった。しかしながら、本発明が含む方法および構造は、細粒ポリシリコンを用いて応力特性を制御する。本発明は、p型FETに圧縮応力を印加し、n型FETチャネルに引張り応力を印加する方法および構造を提供する。他の実施形態は、n型FETチャネルに圧縮応力が印加されることを防ぎつつ、p型FETチャネルに圧縮応力を印加することを含む。本発明の別の実施形態は、p型FETチャネルに引張り応力が印加されることを防ぎつつ、n型FETチャネルに引張り応力を印加することを含む。

【0004】

本発明の方法は、ゲート電極スタックにおいて細粒ポリシリコン膜を配置(例えば蒸着)し、この膜はアニーリングの結果として伸張性が高くなる。伸張性膜の応力は、ポリシリコン膜の上に配置した堆積SiN膜を低温でアニーリングすることによって、抑えることができる。

【課題を解決するための手段】

【0005】

本発明の主な目的は、半導体デバイスにおいてチャネル移動度を向上させることである。

【0006】

本発明によれば、半導体デバイス構造を製造する方法は、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、を含む。また、本発明は、半導体デバイス構造も提供する。

【0007】

本発明の更に別の目的は、以下の詳細な記載を、添付図面と関連付けて考慮することによって、よりいっそう容易に明らかになろう。

【発明を実施するための最良の形態】

【0008】

ここで図面、特に図1を参照すると、半導体基板1が設けられている。半導体基板は、バルクSi基板、SOI基板、または応力を印加した(歪み)Si基板である。あるいは、基板は、2つ以上の表面方位を含むハイブリッド基板である。あるいは、基板は、Geまたは、III−V族元素またはII−VI族元素のいずれかの組み合わせ等、Si以外の半導体材料を含む。

【0009】

初期基板洗浄手順(従来のもの)を行った後、分離方法を実行する。半導体製造において周知のように、分離方法を用いて、選択したデバイスを電気的に相互に絶縁する。分離方法は、標準的な、または変更を加えた浅いトレンチ分離(STI)方法とすることができる。図1にSTI2を示す。あるいは、分離は、半導体デバイスを製造する当技術分野において周知のように、LOCOSプロセスまたはメサ分離方式を用いて達成する。半導体デバイスを製造するための様々な公知または従来のプロセスについては、VLSI Technology, 2nd Edition、S. M. Sze(McGraw HillPublishing Co.、1988年)を参照のこと。

【0010】

分離2を形成した後、従来のゲート酸化物前洗浄プロセスを実行する。高性能論理回路製造プロセスの場合と同様に、様々な従来のゲート酸化物プロセスを用いて、異なるゲート酸化物厚を有するデバイスを製造することができる。例えば、従来の熱酸化プロセスを用いて、ゲート酸化物3を形成する。酸化物3は、N2O、NO、O2、またはそれらのいずれかの組み合わせを用いて形成する。従来のプラズマ・プロセスを用いて、酸化物を窒化させることができる。あるいは、ゲート酸化物を形成するには、ベース酸化物を用い、その後に、酸化アルミニウム、または酸化ハフニウム等の高k誘電体、または別の高kゲート誘電体を堆積すれば良い。ゲート誘電体材料3は、約(±10%)0.6nmから約7nmの範囲内で、ほぼ(±10%)均一な厚さを有する。

【0011】

次に、ウエハ構造1、2、3の全体を覆うように、膜4を堆積する。膜4は、可処分(除去可能)または半可処分のゲート電極材料として用いる。好適な実施形態では、膜4は、約80nmから約150nmの範囲内でほぼ均一な厚さまたは高さ(T)を有するポリシリコン(ポリSi)材料を含む。低圧気相化学付着(LPCVD:low pressure chemical vapor deposition)または急速熱化学気相付着(RPCVD:rapid thermal chemical vapor deposition)等の堆積技法を用いて、除去可能ゲート電極材料4を堆積する。図1に、結果として得られる構造を示す。ポリSi層4は、好ましくは、約1nmから約40nmの範囲の標準的な粒径を有する。

【0012】

次に、従来のリソグラフィ・プロセスを用いて、除去可能ゲート電極材料4の上に、フォトレジスト画像をパターニングする。図には示さないが、フォトレジスト画像を用いて、従来のドライ・エッチング・プロセスを利用することによって、除去可能ゲート電極材料4内に所望の構造体を転写する。ドライ・エッチング・プロセスは、ゲート酸化物材料3に対して選択的に除去可能ゲート電極材料4をエッチングすることができるいくつかの化学成分を含む。図2に示す構造は、n型FETゲート・スタック3、5のための完全にパターニングした除去可能ゲート電極5、および、p型FETゲート・スタック3、6のための除去可能ゲート電極6を示す。

【0013】

次いで、図には示さないが、高性能論理回路製造プロセスにおいて一般的に行われるように、従来のゲート再酸化プロセスを用いる。再酸化は、熱酸化プロセスを用いて約1nmから約7nmのほぼ均一な厚さを達成することで形成する。再酸化プロセスの後に、従来のフォトリソグラフィ・プロセスを用いて、p型FET領域を覆うように、ブロック・マスクをパターニングする。ブロック(例えばレジスト)マスク(図には示さない)を用いて、適切なn型FET領域を注入している間にp型FET領域が注入されるのを阻止または防ぐ。n型FET拡張部7およびハロ(図示せず)は、それぞれ低エネルギAsおよびBの注入を用いて注入される。次いで、ドライまたはウエット・エッチングを用いて、レジスト・マスクを除去する。n型FET領域を覆うように、別のブロック・マスク(図示せず)をパターニングする。p型FET拡張部8およびハロ(図示せず)を、それぞれ低エネルギBF2またはBの注入およびAsの注入を用いて注入する。図2に、n型FETおよびp型FETのための拡張注入プロファイル7、8を示す。

【0014】

拡張部およびハロを注入した後、ウエハ構造全体を覆うように、誘電体ライナ層9を形成する(図3)。ライナ層9として用いる誘電膜は、好ましくは、CVDもしくはRTCVDまたは他のいずれかの適切な堆積技法によって堆積されるSiNである。ライナ層9の目的は、次のプロセスのためのCMPストップ層を設けることである。更に、SiNライナ9は、プロセス・フローの後の時点でエッチングして、ソース−ドレイン・スペーサを形成する。図3に、結果として得られる構造を示す。

【0015】

プロセス・フローの次のステップは、酸化物膜10を堆積することである。酸化物膜10を堆積し、化学機械研磨(CMP:chemical mechanical polishing)を用いて平坦化する。膜10は、例えば、高密度プラズマ(HDP:high density plasma)プロセスを用いて堆積する。除去可能ゲート電極5の上のライナ9の上部は、ドライ・エッチング・プロセスを用いて除去する。このプロセスは、窒化シリコンをエッチングすることができるが、酸化物またはポリSiの相当量をエッチングしない。図4に、ライナ層9の上部を除去した後の、平坦化した酸化物膜10およびSiNライナ9構造を示す。

【0016】

本発明の重要な態様は、本発明のプロセス・フローのこの時点で、ゲート・リセス・プロセスを用いて、ゲート電極5、6から、完全にまたは部分的に、ポリSiを除去することである。図5に、ポリSiを部分的に除去する好適な実施形態を示す。いずれかの適切なドライまたはウエット・エッチング・プロセスを用いて、ポリSiにくぼみを形成する(recessed)。最初のポリSiの部分12および部分13は、残ったままであり、約1nmから約20nmの範囲内でほぼ均一な厚さを有する。図5に、n型FETゲート電極のリセス部分12およびp型FETゲート電極のリセス部分13を示す。別の実施形態(図示せず)では、ポリSiを完全に除去する。この実施形態を用いる場合、従来のゲート酸化物前洗浄プロセスを行い、その後に従来のゲート酸化プロセスを実行する。

【0017】

本発明の別の重要な態様は、ゲート・リセス・プロセスの後に、ウエハ全体を覆うように、細粒ポリSiを堆積することである。細粒ポリシリコンは、Shimizu, S等のProceedings ofthe 1997 Symposium on VLSI Technology(京都(日本)、1997年6月10〜12日)、および、Silicon Processing for The VLSI Era, Vol 1 Process Technology、S. Wolf(1999年)から公知である。好ましくは、粒構造は、約1nmから約50nmの範囲内である。より好ましい粒径は、約5nmから30nmの範囲の実質的に等しい大きさである。ポリSiは、RTCVDまたはLPCVDによって堆積する。次に、例えばCMPまたはドライ・エッチングを用いて、酸化物層10の上から、ポリSiを平坦化し、くぼませる。CMPおよびドライ・エッチング・プロセスは、双方とも、SiO2層10に対して選択的にポリSiを除去することができる。図6に、CMPおよびドライ・エッチングの後の、n型FETのための本発明のゲート電極構造17、12、および、p型FETのための本発明のゲート電極構造13、18を示す。

【0018】

本発明の方法のこの時点で、n型FET領域を覆うように、図7に示すハード・マスク15をパターニングする。マスク15は、SiNを含む誘電膜および従来のフォトリソグラフィ手順を用いてパターニングする。約350℃から約700℃の範囲の温度で、プラズマ・エンハンス化学気相付着等の低温堆積プロセスを用いて、ハード・マスク15を堆積する。好ましくは、550度以下の温度で、ハード・マスク15を形成する材料を堆積して、ポリSi粒の再成長を防ぐ。次に、構造全体を、約500℃から約600℃の温度を用いて約1時間アニーリングする。あるいは、約700℃から約1000度で約1秒から約7秒間の熱アニーリングを実行しても良い。別の実施形態では、構造12、14は、プロセスのもっと後の時点でアニーリングを行う。n型FETゲート電極部17では、細粒ポリSiは、好ましくは約5nmから約30nmの範囲で小さいままである。なぜなら、SiNキャップ層15が存在するからである。しかしながら、p型FETゲート電極部18の粒は、約30nmを超える粒径まで著しく成長する。

【0019】

本発明者等は、本発明のプロセス(例えば図7に関して)が、従来のプロセス技術からの大きな転換を示すと考える。細粒ポリSiが標準的な熱量を受ける場合、ポリSi粒の成長によって引張り応力が著しく増大する。引張り応力は、チャネル領域において圧縮応力を生成し、これが電子移動度を劣化させ、n型FETの性能を制限する。図10のシミュレーションを参照のこと。本発明者等は、粒の成長およびその結果としての引張り応力の顕著な増大は、n型FET領域を覆うように配置したSiNハード・マスク15を用いたアニーリングによってほぼ完全に排除されると考える。細粒ポリSiをくぼみ内に堆積し、n型FETをSiNハード・マスクを用いてアニーリングすることによって、各デバイスごとに別個に粒構造を最適化することができる。このステップは、n型FETデバイス性能を著しく向上させる結果となると思われる。

【0020】

本発明のプロセスの次のステップは、酸化物膜10の水平部分全体から、または水平部分全体から(図8に示すように、部分17上を除いて)、Siハード・マスク15を除去することである。ポリSiは前述のようにくぼませているので、図8に示すように、ハード・マスク15の部分19は、くぼみ孔内に残ったままである(配置されている)。構造19の目的は、標準的な最新の半導体製造プロセス技術において一般的に行われる、この後の従来の熱サイクルの間に、粒の成長を防ぐことである。SiNをエッチングした後、SiNおよびポリSi材料に対して選択的にSiO2膜を除去することができる適切なドライまたはウエット・エッチング・プロセスを用いて、酸化物膜10を除去する。次に、方向性ドライ・エッチング・プロセスをライナ層9に行って、図8に示すように、スペーサ20、25を形成する。本発明に必須ではないが、p型FETのスペーサ20およびn型FETのスペーサ25は、図示のように異なる高さを有する場合がある。n型FETおよびp型FET拡張領域7、8を形成するのに用いたものと同様のブロック・マスクおよび注入プロセスを用いて、図8に示すように、n型FETソース−ドレイン領域21およびp型FETソース−ドレイン領域22を形成する。次に、急速熱アニーリングを用いて、接合を活性化する。n型FETにはSiN層19が存在し続けるので、n型FETゲートにおける粒の成長は抑えられ、これによって、ゲート電極スタック3、12、17の張力、およびこのスタックの下のチャネル領域における以降の圧縮は、最小限に抑えられる。

【0021】

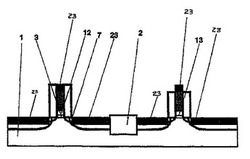

次に、ウエットまたはドライ・エッチング・プロセスを用いて、ゲート電極スタックの上の残り部分19を除去する。次に、シリサイド前洗浄プロセスを実行し、その後に従来のシリサイド・プロセスを行う。図9およびシリサイド23を参照のこと。標準的な後半の(back-end-of-line)処理を行う。この処理には、前金属誘電体堆積および平坦化、コンタクト・エッチング、コンタクト・ライナ形成およびコンタクト形成が含まれる。その後に、金属配線および最終チップ形成を行う。これらは全て図示しない。

【0022】

シミュレーションの結果によって、キャップのないポリSiにおける引張り応力のレベルは、約600℃の温度で約1時間アニーリングを行った結果、約600MPaから約1200MPa増大するが、キャップを有するポリSiでは、引張り応力の増大は約10MPaのみであることが示される。我々のシミュレーション結果は、ゲート材料における応力の約33%から約50%(ゲート応力に対して逆の符号を有する)は、チャネル領域内に移すことができることを示す。このため、キャップなしのゲート・スタックは、−200MPaから−300MPaを印加するが、キャップありのゲート・スタックは、チャネル領域にほとんどまたは全く応力が移らない。図10のグラフに、応力曲線の1つのシミュレーションを示す。

【0023】

現時点で本発明の好適な実施形態と考えられるものを図示し説明したが、本発明の精神および範囲から逸脱することなく、様々な変更および変形を実施可能であることは、当業者には明らかであろう。本発明の精神および範囲は、特許請求の範囲によってのみ限定されるものとする。

【図面の簡単な説明】

【0024】

【図1】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図2】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図3】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図4】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図5】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図6】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図7】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図8】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図9】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図10】本発明の好適な構造のゲートおよびチャネルにおける応力曲線のシミュレーションを示す図である。

【技術分野】

【0001】

本発明は、n型FETおよびp型FETの双方を含むCMOSデバイス構造等の半導体デバイス構造に関する。

【背景技術】

【0002】

例えばCMOSデバイス技術のような将来の半導体にとって、移動度の向上は重要である。従来のプロセス技術からの性能改善は、達成することが極めて困難になっている。Siチャネルに応力を印加するための方法には、チャネルの下部から応力を印加するSiGeを用いること、様々な側面から応力を印加する異なる浅いトレンチ分離(STI:shallow trench isolation)材料の選択、および、側面から長手方向の応力を印加するSiNエッチ・ストップ層が含まれる。歪みSiキャップ層(stained Si cap layer)を用いたSiGeバッファ層または注入−アニール−バッファ手法の欠点は、周知である。その欠点には、歩留まりに大きな影響を与える転位、および、As拡散の向上を制御することが極めて困難であることが含まれる。更に、このプロセスは、非常に複雑でコストが高い。STI手法は、それよりもコストが低いが、ゲートに対して自己整合(self-aligned)せず、RXサイズに関して敏感である。窒化物エッチ・ストップ層を用いて応力を生成するというコストの低い手法は、ある程度の利点があるが、その利点は比較的瑣末なものと考えられている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

本発明は、チャネル移動度の向上を利用してデバイスの性能を改善する。本発明は、適正に調整したポリシリコン・ゲート・スタックの応力特性を用いることによって、チャネルの上部から移動度を改善する。本発明より以前には、これらの応力特性を制御することは極めて困難であった。しかしながら、本発明が含む方法および構造は、細粒ポリシリコンを用いて応力特性を制御する。本発明は、p型FETに圧縮応力を印加し、n型FETチャネルに引張り応力を印加する方法および構造を提供する。他の実施形態は、n型FETチャネルに圧縮応力が印加されることを防ぎつつ、p型FETチャネルに圧縮応力を印加することを含む。本発明の別の実施形態は、p型FETチャネルに引張り応力が印加されることを防ぎつつ、n型FETチャネルに引張り応力を印加することを含む。

【0004】

本発明の方法は、ゲート電極スタックにおいて細粒ポリシリコン膜を配置(例えば蒸着)し、この膜はアニーリングの結果として伸張性が高くなる。伸張性膜の応力は、ポリシリコン膜の上に配置した堆積SiN膜を低温でアニーリングすることによって、抑えることができる。

【課題を解決するための手段】

【0005】

本発明の主な目的は、半導体デバイスにおいてチャネル移動度を向上させることである。

【0006】

本発明によれば、半導体デバイス構造を製造する方法は、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、を含む。また、本発明は、半導体デバイス構造も提供する。

【0007】

本発明の更に別の目的は、以下の詳細な記載を、添付図面と関連付けて考慮することによって、よりいっそう容易に明らかになろう。

【発明を実施するための最良の形態】

【0008】

ここで図面、特に図1を参照すると、半導体基板1が設けられている。半導体基板は、バルクSi基板、SOI基板、または応力を印加した(歪み)Si基板である。あるいは、基板は、2つ以上の表面方位を含むハイブリッド基板である。あるいは、基板は、Geまたは、III−V族元素またはII−VI族元素のいずれかの組み合わせ等、Si以外の半導体材料を含む。

【0009】

初期基板洗浄手順(従来のもの)を行った後、分離方法を実行する。半導体製造において周知のように、分離方法を用いて、選択したデバイスを電気的に相互に絶縁する。分離方法は、標準的な、または変更を加えた浅いトレンチ分離(STI)方法とすることができる。図1にSTI2を示す。あるいは、分離は、半導体デバイスを製造する当技術分野において周知のように、LOCOSプロセスまたはメサ分離方式を用いて達成する。半導体デバイスを製造するための様々な公知または従来のプロセスについては、VLSI Technology, 2nd Edition、S. M. Sze(McGraw HillPublishing Co.、1988年)を参照のこと。

【0010】

分離2を形成した後、従来のゲート酸化物前洗浄プロセスを実行する。高性能論理回路製造プロセスの場合と同様に、様々な従来のゲート酸化物プロセスを用いて、異なるゲート酸化物厚を有するデバイスを製造することができる。例えば、従来の熱酸化プロセスを用いて、ゲート酸化物3を形成する。酸化物3は、N2O、NO、O2、またはそれらのいずれかの組み合わせを用いて形成する。従来のプラズマ・プロセスを用いて、酸化物を窒化させることができる。あるいは、ゲート酸化物を形成するには、ベース酸化物を用い、その後に、酸化アルミニウム、または酸化ハフニウム等の高k誘電体、または別の高kゲート誘電体を堆積すれば良い。ゲート誘電体材料3は、約(±10%)0.6nmから約7nmの範囲内で、ほぼ(±10%)均一な厚さを有する。

【0011】

次に、ウエハ構造1、2、3の全体を覆うように、膜4を堆積する。膜4は、可処分(除去可能)または半可処分のゲート電極材料として用いる。好適な実施形態では、膜4は、約80nmから約150nmの範囲内でほぼ均一な厚さまたは高さ(T)を有するポリシリコン(ポリSi)材料を含む。低圧気相化学付着(LPCVD:low pressure chemical vapor deposition)または急速熱化学気相付着(RPCVD:rapid thermal chemical vapor deposition)等の堆積技法を用いて、除去可能ゲート電極材料4を堆積する。図1に、結果として得られる構造を示す。ポリSi層4は、好ましくは、約1nmから約40nmの範囲の標準的な粒径を有する。

【0012】

次に、従来のリソグラフィ・プロセスを用いて、除去可能ゲート電極材料4の上に、フォトレジスト画像をパターニングする。図には示さないが、フォトレジスト画像を用いて、従来のドライ・エッチング・プロセスを利用することによって、除去可能ゲート電極材料4内に所望の構造体を転写する。ドライ・エッチング・プロセスは、ゲート酸化物材料3に対して選択的に除去可能ゲート電極材料4をエッチングすることができるいくつかの化学成分を含む。図2に示す構造は、n型FETゲート・スタック3、5のための完全にパターニングした除去可能ゲート電極5、および、p型FETゲート・スタック3、6のための除去可能ゲート電極6を示す。

【0013】

次いで、図には示さないが、高性能論理回路製造プロセスにおいて一般的に行われるように、従来のゲート再酸化プロセスを用いる。再酸化は、熱酸化プロセスを用いて約1nmから約7nmのほぼ均一な厚さを達成することで形成する。再酸化プロセスの後に、従来のフォトリソグラフィ・プロセスを用いて、p型FET領域を覆うように、ブロック・マスクをパターニングする。ブロック(例えばレジスト)マスク(図には示さない)を用いて、適切なn型FET領域を注入している間にp型FET領域が注入されるのを阻止または防ぐ。n型FET拡張部7およびハロ(図示せず)は、それぞれ低エネルギAsおよびBの注入を用いて注入される。次いで、ドライまたはウエット・エッチングを用いて、レジスト・マスクを除去する。n型FET領域を覆うように、別のブロック・マスク(図示せず)をパターニングする。p型FET拡張部8およびハロ(図示せず)を、それぞれ低エネルギBF2またはBの注入およびAsの注入を用いて注入する。図2に、n型FETおよびp型FETのための拡張注入プロファイル7、8を示す。

【0014】

拡張部およびハロを注入した後、ウエハ構造全体を覆うように、誘電体ライナ層9を形成する(図3)。ライナ層9として用いる誘電膜は、好ましくは、CVDもしくはRTCVDまたは他のいずれかの適切な堆積技法によって堆積されるSiNである。ライナ層9の目的は、次のプロセスのためのCMPストップ層を設けることである。更に、SiNライナ9は、プロセス・フローの後の時点でエッチングして、ソース−ドレイン・スペーサを形成する。図3に、結果として得られる構造を示す。

【0015】

プロセス・フローの次のステップは、酸化物膜10を堆積することである。酸化物膜10を堆積し、化学機械研磨(CMP:chemical mechanical polishing)を用いて平坦化する。膜10は、例えば、高密度プラズマ(HDP:high density plasma)プロセスを用いて堆積する。除去可能ゲート電極5の上のライナ9の上部は、ドライ・エッチング・プロセスを用いて除去する。このプロセスは、窒化シリコンをエッチングすることができるが、酸化物またはポリSiの相当量をエッチングしない。図4に、ライナ層9の上部を除去した後の、平坦化した酸化物膜10およびSiNライナ9構造を示す。

【0016】

本発明の重要な態様は、本発明のプロセス・フローのこの時点で、ゲート・リセス・プロセスを用いて、ゲート電極5、6から、完全にまたは部分的に、ポリSiを除去することである。図5に、ポリSiを部分的に除去する好適な実施形態を示す。いずれかの適切なドライまたはウエット・エッチング・プロセスを用いて、ポリSiにくぼみを形成する(recessed)。最初のポリSiの部分12および部分13は、残ったままであり、約1nmから約20nmの範囲内でほぼ均一な厚さを有する。図5に、n型FETゲート電極のリセス部分12およびp型FETゲート電極のリセス部分13を示す。別の実施形態(図示せず)では、ポリSiを完全に除去する。この実施形態を用いる場合、従来のゲート酸化物前洗浄プロセスを行い、その後に従来のゲート酸化プロセスを実行する。

【0017】

本発明の別の重要な態様は、ゲート・リセス・プロセスの後に、ウエハ全体を覆うように、細粒ポリSiを堆積することである。細粒ポリシリコンは、Shimizu, S等のProceedings ofthe 1997 Symposium on VLSI Technology(京都(日本)、1997年6月10〜12日)、および、Silicon Processing for The VLSI Era, Vol 1 Process Technology、S. Wolf(1999年)から公知である。好ましくは、粒構造は、約1nmから約50nmの範囲内である。より好ましい粒径は、約5nmから30nmの範囲の実質的に等しい大きさである。ポリSiは、RTCVDまたはLPCVDによって堆積する。次に、例えばCMPまたはドライ・エッチングを用いて、酸化物層10の上から、ポリSiを平坦化し、くぼませる。CMPおよびドライ・エッチング・プロセスは、双方とも、SiO2層10に対して選択的にポリSiを除去することができる。図6に、CMPおよびドライ・エッチングの後の、n型FETのための本発明のゲート電極構造17、12、および、p型FETのための本発明のゲート電極構造13、18を示す。

【0018】

本発明の方法のこの時点で、n型FET領域を覆うように、図7に示すハード・マスク15をパターニングする。マスク15は、SiNを含む誘電膜および従来のフォトリソグラフィ手順を用いてパターニングする。約350℃から約700℃の範囲の温度で、プラズマ・エンハンス化学気相付着等の低温堆積プロセスを用いて、ハード・マスク15を堆積する。好ましくは、550度以下の温度で、ハード・マスク15を形成する材料を堆積して、ポリSi粒の再成長を防ぐ。次に、構造全体を、約500℃から約600℃の温度を用いて約1時間アニーリングする。あるいは、約700℃から約1000度で約1秒から約7秒間の熱アニーリングを実行しても良い。別の実施形態では、構造12、14は、プロセスのもっと後の時点でアニーリングを行う。n型FETゲート電極部17では、細粒ポリSiは、好ましくは約5nmから約30nmの範囲で小さいままである。なぜなら、SiNキャップ層15が存在するからである。しかしながら、p型FETゲート電極部18の粒は、約30nmを超える粒径まで著しく成長する。

【0019】

本発明者等は、本発明のプロセス(例えば図7に関して)が、従来のプロセス技術からの大きな転換を示すと考える。細粒ポリSiが標準的な熱量を受ける場合、ポリSi粒の成長によって引張り応力が著しく増大する。引張り応力は、チャネル領域において圧縮応力を生成し、これが電子移動度を劣化させ、n型FETの性能を制限する。図10のシミュレーションを参照のこと。本発明者等は、粒の成長およびその結果としての引張り応力の顕著な増大は、n型FET領域を覆うように配置したSiNハード・マスク15を用いたアニーリングによってほぼ完全に排除されると考える。細粒ポリSiをくぼみ内に堆積し、n型FETをSiNハード・マスクを用いてアニーリングすることによって、各デバイスごとに別個に粒構造を最適化することができる。このステップは、n型FETデバイス性能を著しく向上させる結果となると思われる。

【0020】

本発明のプロセスの次のステップは、酸化物膜10の水平部分全体から、または水平部分全体から(図8に示すように、部分17上を除いて)、Siハード・マスク15を除去することである。ポリSiは前述のようにくぼませているので、図8に示すように、ハード・マスク15の部分19は、くぼみ孔内に残ったままである(配置されている)。構造19の目的は、標準的な最新の半導体製造プロセス技術において一般的に行われる、この後の従来の熱サイクルの間に、粒の成長を防ぐことである。SiNをエッチングした後、SiNおよびポリSi材料に対して選択的にSiO2膜を除去することができる適切なドライまたはウエット・エッチング・プロセスを用いて、酸化物膜10を除去する。次に、方向性ドライ・エッチング・プロセスをライナ層9に行って、図8に示すように、スペーサ20、25を形成する。本発明に必須ではないが、p型FETのスペーサ20およびn型FETのスペーサ25は、図示のように異なる高さを有する場合がある。n型FETおよびp型FET拡張領域7、8を形成するのに用いたものと同様のブロック・マスクおよび注入プロセスを用いて、図8に示すように、n型FETソース−ドレイン領域21およびp型FETソース−ドレイン領域22を形成する。次に、急速熱アニーリングを用いて、接合を活性化する。n型FETにはSiN層19が存在し続けるので、n型FETゲートにおける粒の成長は抑えられ、これによって、ゲート電極スタック3、12、17の張力、およびこのスタックの下のチャネル領域における以降の圧縮は、最小限に抑えられる。

【0021】

次に、ウエットまたはドライ・エッチング・プロセスを用いて、ゲート電極スタックの上の残り部分19を除去する。次に、シリサイド前洗浄プロセスを実行し、その後に従来のシリサイド・プロセスを行う。図9およびシリサイド23を参照のこと。標準的な後半の(back-end-of-line)処理を行う。この処理には、前金属誘電体堆積および平坦化、コンタクト・エッチング、コンタクト・ライナ形成およびコンタクト形成が含まれる。その後に、金属配線および最終チップ形成を行う。これらは全て図示しない。

【0022】

シミュレーションの結果によって、キャップのないポリSiにおける引張り応力のレベルは、約600℃の温度で約1時間アニーリングを行った結果、約600MPaから約1200MPa増大するが、キャップを有するポリSiでは、引張り応力の増大は約10MPaのみであることが示される。我々のシミュレーション結果は、ゲート材料における応力の約33%から約50%(ゲート応力に対して逆の符号を有する)は、チャネル領域内に移すことができることを示す。このため、キャップなしのゲート・スタックは、−200MPaから−300MPaを印加するが、キャップありのゲート・スタックは、チャネル領域にほとんどまたは全く応力が移らない。図10のグラフに、応力曲線の1つのシミュレーションを示す。

【0023】

現時点で本発明の好適な実施形態と考えられるものを図示し説明したが、本発明の精神および範囲から逸脱することなく、様々な変更および変形を実施可能であることは、当業者には明らかであろう。本発明の精神および範囲は、特許請求の範囲によってのみ限定されるものとする。

【図面の簡単な説明】

【0024】

【図1】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図2】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図3】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図4】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図5】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図6】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図7】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図8】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図9】本発明の好適な実施形態によるプロセス・ステップの側面概略図である。

【図10】本発明の好適な構造のゲートおよびチャネルにおける応力曲線のシミュレーションを示す図である。

【特許請求の範囲】

【請求項1】

半導体デバイス構造を製造する方法であって、

基板を設けるステップと、

前記基板上に電極を設けるステップと、

前記電極内に開口を有するくぼみを形成するステップと、

前記くぼみ内に細粒半導体材料を配置するステップと、

前記開口を覆って前記くぼみ内に前記細粒半導体材料を閉じこめるステップと、

上述のステップの結果として得られる構造をアニーリングするステップと、

を含む、方法。

【請求項2】

前記アニーリングするステップが、約500℃から約600℃の範囲のほぼ一定の温度で約1時間、前記結果として得られる構造をアニーリングすることを含む、請求項1に記載の方法。

【請求項3】

前記細粒半導体材料が、約1nmから約30nmの範囲の平均粒径を有するポリシリコン材料である、請求項1に記載の方法。

【請求項4】

前記覆うステップが前記開口全体をマスクすることを含む、請求項1に記載の方法。

【請求項5】

半導体デバイス構造であって、

第1のゲート・スタックを有する第1の半導体デバイスと、

第2のゲート・スタックを有する第2の半導体デバイスと、

を含み、前記第1のゲート・スタックが、約30nm未満の平均粒径を有する第1の半導体材料を含み、前記第2のゲート・スタックが、約30nmより大きい平均粒径を有する第2の半導体材料を含む、半導体デバイス構造。

【請求項6】

前記第1の半導体材料が粒状ポリシリコンである、請求項5に記載の構造。

【請求項7】

前記第1の半導体デバイスがn型FETであり、前記第2の半導体デバイスがp型FETである、請求項5に記載の構造。

【請求項8】

前記第1のゲート・スタックの下に配置された第1のチャネルと、前記第2のゲート・スタックの下に配置された第2のチャネルと、を更に含み、前記第2のゲート・スタックが、約−200MPaから約−600MPaの範囲の圧縮応力を前記第2のチャネルに印加し、前記第1のゲート・スタックが、約−10MPaから約−100MPaの範囲の圧縮応力を前記第1のチャネルに印加する、請求項5に記載の構造。

【請求項9】

前記第1の半導体デバイスと前記第2の半導体デバイスとの間に配置された分離領域を更に含む、請求項5に記載の構造。

【請求項10】

前記第2の半導体材料が粒状ポリシリコンである、請求項5に記載の構造。

【請求項11】

第3の半導体材料および第4の半導体材料を更に含み、前記第1の半導体材料が前記第3の半導体材料上に配置され、前記第2の半導体材料が前記第4の半導体材料上に配置されている、請求項5に記載の構造。

【請求項12】

前記第3の半導体材料が細粒ポリシリコンであり、前記第4の半導体材料が細粒ポリシリコンである、請求項11に記載の構造。

【請求項13】

半導体デバイス構造を製造する方法であって、

基板を設けるステップと、

前記基板上にn型FETおよびp型FETを設けるステップと、

前記n型FETおよび前記p型FETからのゲート電極の一部を細粒ポリシリコンによって置換するステップと、

前記n型FETの前記細粒ポリシリコンを覆い、次いで前記n型FETおよび前記p型FETを加熱して、前記n型FET内の前記粒の平均直径が前記p型FET内の前記粒の平均直径未満になるようにする、ステップと、

を含む、方法。

【請求項14】

前記加熱するステップが、約500℃から約600℃の範囲内の温度で約1時間、前記n型FETおよび前記p型FETを加熱することを含む、請求項13に記載の方法。

【請求項15】

前記細粒ポリシリコンが約5nmから約30nmの範囲の平均粒径を有する、請求項13に記載の方法。

【請求項16】

前記置換するステップが、前記ゲート電極の前記一部を除去してくぼみを形成し、次いで前記n型FETおよび前記p型FETのくぼみ内に前記細粒ポリシリコンを配置することを含む、請求項13に記載の方法。

【請求項17】

前記置換するステップが、前記ゲート電極の全部分を除去してくぼみを形成し、次いで前記くぼみ内に前記細粒ポリシリコンを堆積することを含む、請求項13に記載の方法。

【請求項18】

前記覆うステップが、前記n型FETの前記細粒ポリシリコンの上にマスクを配置することを含み、前記マスクが実質的にSiNから成る、請求項13に記載の方法。

【請求項19】

前記n型FETおよび前記p型FETのためのスペーサを形成するステップを更に含み、前記スペーサが異なる高さを有する、請求項13に記載の方法。

【請求項20】

前記n型FETおよび前記p型FETのためにスペーサを設けるステップを更に含み、前記p型FETのための前記スペーサの高さが、前記n型FETのための前記スペーサの高さ未満である、請求項13に記載の方法。

【請求項1】

半導体デバイス構造を製造する方法であって、

基板を設けるステップと、

前記基板上に電極を設けるステップと、

前記電極内に開口を有するくぼみを形成するステップと、

前記くぼみ内に細粒半導体材料を配置するステップと、

前記開口を覆って前記くぼみ内に前記細粒半導体材料を閉じこめるステップと、

上述のステップの結果として得られる構造をアニーリングするステップと、

を含む、方法。

【請求項2】

前記アニーリングするステップが、約500℃から約600℃の範囲のほぼ一定の温度で約1時間、前記結果として得られる構造をアニーリングすることを含む、請求項1に記載の方法。

【請求項3】

前記細粒半導体材料が、約1nmから約30nmの範囲の平均粒径を有するポリシリコン材料である、請求項1に記載の方法。

【請求項4】

前記覆うステップが前記開口全体をマスクすることを含む、請求項1に記載の方法。

【請求項5】

半導体デバイス構造であって、

第1のゲート・スタックを有する第1の半導体デバイスと、

第2のゲート・スタックを有する第2の半導体デバイスと、

を含み、前記第1のゲート・スタックが、約30nm未満の平均粒径を有する第1の半導体材料を含み、前記第2のゲート・スタックが、約30nmより大きい平均粒径を有する第2の半導体材料を含む、半導体デバイス構造。

【請求項6】

前記第1の半導体材料が粒状ポリシリコンである、請求項5に記載の構造。

【請求項7】

前記第1の半導体デバイスがn型FETであり、前記第2の半導体デバイスがp型FETである、請求項5に記載の構造。

【請求項8】

前記第1のゲート・スタックの下に配置された第1のチャネルと、前記第2のゲート・スタックの下に配置された第2のチャネルと、を更に含み、前記第2のゲート・スタックが、約−200MPaから約−600MPaの範囲の圧縮応力を前記第2のチャネルに印加し、前記第1のゲート・スタックが、約−10MPaから約−100MPaの範囲の圧縮応力を前記第1のチャネルに印加する、請求項5に記載の構造。

【請求項9】

前記第1の半導体デバイスと前記第2の半導体デバイスとの間に配置された分離領域を更に含む、請求項5に記載の構造。

【請求項10】

前記第2の半導体材料が粒状ポリシリコンである、請求項5に記載の構造。

【請求項11】

第3の半導体材料および第4の半導体材料を更に含み、前記第1の半導体材料が前記第3の半導体材料上に配置され、前記第2の半導体材料が前記第4の半導体材料上に配置されている、請求項5に記載の構造。

【請求項12】

前記第3の半導体材料が細粒ポリシリコンであり、前記第4の半導体材料が細粒ポリシリコンである、請求項11に記載の構造。

【請求項13】

半導体デバイス構造を製造する方法であって、

基板を設けるステップと、

前記基板上にn型FETおよびp型FETを設けるステップと、

前記n型FETおよび前記p型FETからのゲート電極の一部を細粒ポリシリコンによって置換するステップと、

前記n型FETの前記細粒ポリシリコンを覆い、次いで前記n型FETおよび前記p型FETを加熱して、前記n型FET内の前記粒の平均直径が前記p型FET内の前記粒の平均直径未満になるようにする、ステップと、

を含む、方法。

【請求項14】

前記加熱するステップが、約500℃から約600℃の範囲内の温度で約1時間、前記n型FETおよび前記p型FETを加熱することを含む、請求項13に記載の方法。

【請求項15】

前記細粒ポリシリコンが約5nmから約30nmの範囲の平均粒径を有する、請求項13に記載の方法。

【請求項16】

前記置換するステップが、前記ゲート電極の前記一部を除去してくぼみを形成し、次いで前記n型FETおよび前記p型FETのくぼみ内に前記細粒ポリシリコンを配置することを含む、請求項13に記載の方法。

【請求項17】

前記置換するステップが、前記ゲート電極の全部分を除去してくぼみを形成し、次いで前記くぼみ内に前記細粒ポリシリコンを堆積することを含む、請求項13に記載の方法。

【請求項18】

前記覆うステップが、前記n型FETの前記細粒ポリシリコンの上にマスクを配置することを含み、前記マスクが実質的にSiNから成る、請求項13に記載の方法。

【請求項19】

前記n型FETおよび前記p型FETのためのスペーサを形成するステップを更に含み、前記スペーサが異なる高さを有する、請求項13に記載の方法。

【請求項20】

前記n型FETおよび前記p型FETのためにスペーサを設けるステップを更に含み、前記p型FETのための前記スペーサの高さが、前記n型FETのための前記スペーサの高さ未満である、請求項13に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公表番号】特表2007−511909(P2007−511909A)

【公表日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願番号】特願2006−539779(P2006−539779)

【出願日】平成16年11月9日(2004.11.9)

【国際出願番号】PCT/US2004/037434

【国際公開番号】WO2005/050701

【国際公開日】平成17年6月2日(2005.6.2)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MASCHINES CORPORATION

【Fターム(参考)】

【公表日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願日】平成16年11月9日(2004.11.9)

【国際出願番号】PCT/US2004/037434

【国際公開番号】WO2005/050701

【国際公開日】平成17年6月2日(2005.6.2)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MASCHINES CORPORATION

【Fターム(参考)】

[ Back to top ]