素子付き基板、赤外線センサー、および貫通電極形成方法

【課題】マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサーおよび貫通電極形成方法を提供する。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は貫通電極を備えた素子付き基板、赤外線センサーおよび貫通電極形成方法に関する。

【背景技術】

【0002】

3次元実装パッケージでは、複数のチップ(素子付き基板)を垂直に積み重ね、1つのパッケージとすることで占有面積を小さくできる。このため、シリコンウェハーやダイといったチップを垂直に貫くビアホールを利用した貫通電極によってウェハーやダイ同士の垂直方向の電気的接続を行なうことが行なわれている。

【0003】

このような貫通電極を備えたチップは、半導体基板と半導体基板に形成された貫通電極とを含んで構成されている。このようなチップにおいて、半導体基板は、半導体基板上に形成された回路に対して一定の電位となっており、回路と導通している貫通電極とは電位差があるため、貫通電極と半導体基板との間でリーク電流が発生する場合がある。そのため、特許文献1では、リーク電流を防止するために、貫通電極や貫通電極に接続された電極と、基板との間には、樹脂絶縁層が形成されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−177237号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、樹脂絶縁層を用いて微細で高アスペクトの貫通電極を形成する場合には、十分な厚さの樹脂絶縁層を形成することができず、絶縁機能が低下する課題があった。

【0006】

本発明は、上記の課題に着目してなされたもので、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサー、および貫通電極形成方法を提供することを目的としている。

【課題を解決するための手段】

【0007】

本発明は、以下のような適用例を採用することにより、上記目的の少なくとも一部を達成することができる。

【0008】

[適用例1]一方の面と他方の面とに開口するビアホールが形成されたベース基板と、前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、前記配線層に電気的に接続された素子回路と、を有し、前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする素子付き基板。

【0009】

このような構成を採用することで、ベース基板の一方の面からビアホール内の面に掛けて熱酸化による緻密で均一な肉厚の絶縁膜を形成することができ、リーク電流が発生しやすいベース基板の一方の面とビアホール内の面とが形成する角部(ビアコーナー部分)での絶縁特性が良好な素子付き基板を得ることが出来る。

【0010】

[適用例2]適用例1において、前記第1絶縁層に接続されており、前記ベース基板の他方の面に設けられた第2絶縁層を有することを特徴とする素子付き基板。

この構成により、ベース基板の他方の面とビアホール内の面とが形成する角部での絶縁特性も良好にできる。

【0011】

[適用例3]適用例1又は2において、前記導電体は前記ベース基板の他方の面に突出する突起部を含むことを特徴とする素子付き基板。

この構成により、素子付き基板を垂直に積層することが容易となり、3次元積層パッケージの製造が容易になる。

【0012】

[適用例4]ベース基板の一方の面からビアホールを形成するビアホール形成工程と、前記ベース基板の一方の面と前記ビアホール内の面とに熱酸化により熱酸化絶縁層を形成する熱酸化工程と、前記熱酸化工程後に、前記ベース基板の一方の面に導電部を有する素子回路を形成する素子回路形成工程と、前記素子回路形成工程後に、前記ビアホールに導電体を埋め込み形成する導電体形成工程と、を含むことを特徴とする貫通電極形成方法。

上記構成により、マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を形成することができる。

【0013】

[適用例5]適用例4において、前記熱酸化工程と前記素子回路形成工程との間に、前記ビアホール内に仮埋め込み材を埋め込む工程を含み、前記素子回路形成工程と前記導電体形成工程との間に、前記仮埋め込み材を除去する工程を含むことを特徴とする貫通電極形成方法。

【0014】

上記構成により、予めビアホールを形成していても、ビアホール空洞部の残留気体が素子形成工程で膨張することによってベース基板に対する素子回路の密着力が低下することを有効に防止できる。

【0015】

[適用例6]適用例4又は5において、前記素子回路形成工程と前記導電体形成工程との間に、前記ベース基板の他方の面を研削し、前記ベース基板の他方の面に前記熱酸化絶縁層と連続する第2絶縁層を設ける工程を含むことを特徴とする貫通電極形成方法。

このような構成では、ベース基板の他方の面とビアホール内の面とが形成する角部でのリーク電流発生を効果的に抑制することができる。

【0016】

[適用例7]適用例6において、前記導電体形成工程後に、前記ベース基板の他方の面に前記導電体に接続された端子を形成する工程を含むことを特徴とする貫通電極形成方法。

このような構成では、ベース基板の他方の面において外部接続することができる。

【0017】

[適用例8]適用例7において、前記ベース基板の他方の面を研削する前に、支持部材を前記ベース基板の一方の面に貼り付けることを特徴とする貫通電極形成方法。

これにより、薄板化したベース基板への加工性を確保することができる。

【0018】

[適用例9]適用例8において、前記ベース基板の一方の面に貼り付けられた前記支持部材を前記端子形成後に除去することを特徴とする貫通電極形成方法。

これにより、次工程への支持基板の持込がなくなる。

【0019】

[適用例10]適用例4において、前記ビアホール形成工程では、前記ベース基板を貫通したビアホールを形成することを特徴とする貫通電極形成方法。

このような構成では、予めビアホールを形成しても空洞部に気体が残留することがないので、仮の埋め込み材を用いることが不要となり、工程の短縮化につながる。

【0020】

[適用例11]適用例4乃至10のいずれかにおいて、前記導電体形成工程では、めっきにより前記導電体を形成することを特徴とする貫通電極形成方法。

これにより、微細でアスペクトが高いビアホール内に導電体を埋め込むことが容易に行え、高額なCVDなどの装置を使用しなくてよい。

【0021】

[適用例12]一方の面と他方の面とに開口するビアホールが形成されたベース基板と、前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、前記配線層に電気的に接続された赤外線検出素子と、を有し、前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする赤外線センサー。

【0022】

このような構成を採用することで、ベース基板の一方の面からビアホール内の面に掛けて熱酸化による緻密で均一な肉厚の絶縁膜を形成することができ、リーク電流が発生しやすいベース基板の一方の面とビアホール内の面とが形成する角部(ビアコーナー部分)での絶縁特性が良好な素子付き基板を得ることが出来る。そして、微細で高アスペクトの貫通電極を形成することができるため、高密度に赤外線検出素子を設けることができる。

【発明の効果】

【0023】

本発明の構成によれば、貫通電極を構成するビアホールおよび絶縁層の形成と、導電体からなる埋め込み電極の形成とを、素子回路形成前後で分断する工程で作製するようにしたので、微細、高アスペクト、多ビアの貫通電極構造を持つ素子回路付き基板構造体の作製が容易になる。具体的には、微細、高アスペクト対応の素子回路形成前での貫通電極の絶縁特性がよい熱酸化絶縁膜の形成、マイグレーションの問題を生じることなく、素子回路形成後でのめっきによる導電体の埋め込みが可能となり、容易な装置や工法を用いることが可能となる。

【図面の簡単な説明】

【0024】

【図1】本発明に係る素子付き基板を模式的に示した要部断面図である。

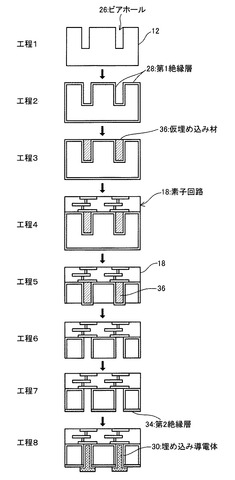

【図2】本発明に係る素子付き基板の貫通電極形成方法の基本工程を示すフローチャートである。

【図3】第1実施形態に係る素子付き基板の貫通電極形成方法の工程を示すフローチャートである。

【図4】第2実施形態に係る素子付き基板の貫通電極形成方法の工程を示すフローチャートである。

【図5】本発明に係る赤外線センサーの1セル分の赤外線検出素子の断面図である。

【図6】図6(A)、図6(B)は赤外線検出素子を二次元配置した赤外線センサーの構成例を示す図である。

【発明を実施するための形態】

【0025】

以下に、本発明に係る素子付き基板、赤外線センサーおよび貫通電極形成方法の具体的実施形態につき、図面を参照しながら詳細に説明する。

なお、下記の実施形態は一例であり、本発明の主旨を逸脱しない範囲で各種変形構成を取り得る。

【0026】

<素子付き基板の構成>

図1は実施形態に係る素子付き基板10の断面図である。この図に示されているように、この素子付き基板10には、ベース基板12を厚さ方向に貫通させることによって形成された貫通電極14が設けられている。この貫通電極14の一端側であるベース基板12の表面側には、配線層16を介し前記貫通電極14と接続される素子回路18が設けられている。一方、貫通電極14の他端側はベース基板12の裏面から突出され、ここに外部電極端子20が形成されて突起電極21を形成している。これにより、当該素子付き基板10を他のチップ上に垂直に積み重ね、占有面積の少ない1つのパッケージを作製することができる。

【0027】

より具体的には、次のように構成されている。まず、ベース基板12として本実施形態では、Si半導体基板が用いられている。貫通電極14はSiベース基板12の裏面から素子回路18の形成面であるベース基板12の表面に形成された配線層16に至っており、当該配線層16と、Siベース基板12の裏面に形成された外部電極端子20とを電気的に接続している。また、前記配線層16の上には互いに絶縁膜22によって隔てられた素子回路18が形成されている。配線層16はその間に位置する配線間絶縁膜22に形成されたビア配線24により素子回路18に電気的接続されている。なお、配線層16は複数の金属層が積層されたものであってもよい。

【0028】

貫通電極14はSiベース基板12に形成されたビアホール(ベース基板貫通孔)26の内壁をSiO2などの無機材料の第1絶縁層28が覆っている。この第1絶縁層28は、1000℃前後の温度環境で、熱酸化により形成されたもので、前記Siベース基板12と素子回路18(具体的には配線層16)の間に介在され、連続してビアホール26内壁面に至っている。熱酸化による絶縁膜形成であるため、前記Siベース基板12の素子回路18形成面と、ビアホール26内壁面とに対し、緻密で厚みが均等となるように一体に形成されている。この第1絶縁層28の厚みはビアホール26の直径の約5〜10%とされ、ビアホール直径が約20μmとすれば、約1〜2μmの肉厚となるように成膜されている。これにより、ビアホール26の配線層16側のコーナー部分が緻密で厚肉の第1絶縁層28で覆われるため、絶縁破壊が生じやすいコーナー部分での絶縁特性が向上し、リーク電流の抑制効果が高いものとなっている。

【0029】

さらに、ビアホール26の開口に臨まれている素子回路18の配線層16と、第1絶縁層28の内壁には、その内周に形成される埋め込み導電体30のSi基板への拡散を防止するバリア層および密着層として、TiWなどの金属膜(以下バリア層32という)が形成されている。

【0030】

バリア層32の内壁にはCu、Ni、Auなどの導電体30が埋め込み形成されている。埋め込み導電体30はバリア層で囲まれた孔空間内に完全に充填されていてもよい。または孔空間の内壁に沿って膜状に覆うものであってもよい。その場合、導体膜の内側の孔部には補強のために樹脂などの第三絶縁物を埋め込むのが望ましい。

【0031】

また、Siベース基板12の素子回路18形成面と反対側の裏面上には、裏面側ビアコーナー部を絶縁するために、樹脂またはSiO2、SiNなどの無機材料などからなる第2絶縁層34が、第1絶縁層28と連続するように形成されている。さらに、第2絶縁層34の外表面部には、前記埋め込み導電体30が前記ベース基板12の裏面側に突出しており、この突出部と接続される外部電極端子20が形成され、突起電極21とされている。

【0032】

これにより、裏面側ビアコーナー部は、表面側ビアコーナー部と同様に、第1絶縁層28と第2絶縁層34によって確実に覆われ、絶縁破壊が生じやすいコーナー部分での絶縁特性が向上し、リーク電流の抑制効果が高いものとなっている。

【0033】

なお、この実施形態では、図1に示すように、貫通電極14がストレート貫通電極とした例をあげているが、ビアホール26をテーパ形状にしたテーパ形状の貫通電極としてもよい。

【0034】

<素子付き基板の製造プロセス>

上述のような素子付き基板10を作製するための基本的プロセスを図2に示している。すなわち、素子回路18の形成前に、Siベース基板12にビアホール26を形成し(工程1)、次いで、Siベース基板12を熱酸化することによって絶縁膜(第1絶縁層28)まで形成しておく(工程2)。このときには、ビアホール26内には埋め込み導電体30を設けない。その後、ビアホール26の開口側に素子回路18を形成するが(工程4)、ビアホール26が空洞のまま素子回路18を積層形成すると密閉された空洞に雰囲気ガスが充満して、Siベース基板12に対する素子回路18の密着力が低下する可能性があるので、予めビアホール26内に仮の埋め込み材36を充填しておく(工程3)。素子回路18の形成後、当該素子回路18の形成面と反対側のSiベース基板12の裏面側を研削して薄型化し(工程5)、ビアホール26の中の仮埋め込み材36を除去してベース裏面側を開口させる(工程6)。次いで、Siベース基板12の裏面に絶縁膜(第2絶縁層34)を形成する(工程7)。最後に、先行して作製したビアホール26に導電材料(導電体30)を埋め込むようにしている(工程8)。すなわち、素子回路18の形成前に、ビアホール26と第1絶縁層28まで形成しておき、素子回路18を形成してからビアホール26の内部に導電体30を埋め込み形成するようにしているものである。

【0035】

このように、素子回路18の形成前に熱酸化によりビアホール26内に絶縁膜(第1絶縁層28)を形成することにより、従来技術では実現が難しい非常に緻密で絶縁性の高い膜が均一に形成できる。また素子回路18の形成後であれば、マイグレーションの問題を生じることなく、埋め込み導電体30として、めっきによりCuなどの導電材料を埋め込むことが可能となる。導電体30の埋め込み処理は、素子回路18の形成面と反対側のベース基板12の裏面を薄型化し、裏面より埋め込みを行えばよい。いずれの工程も、CVDのような高価な装置を用いず、安価な機器により成し遂げることが可能となる。このように絶縁膜(第1絶縁層28)の形成と導電体30の埋め込みを別工程で行うことにより、微細でアスペクトの高い貫通電極の形成ができる。

【0036】

<赤外線センサーの構成>

図5は、本発明の赤外線センサーを構成する赤外線検出素子を示す断面図である。赤外線センサー300は、赤外線検出素子220を含むセンサーセルが複数配列されて構成される。なお、赤外線センサー300の詳細な構成については後述する。

【0037】

図5に示すように、赤外線センサー300は、赤外線検出素子220と、赤外線検出素子220を搭載したSiベース基板12と、を有している。Siベース基板12には、ビアホール26が形成されており、ベース基板12の一方の面とビアホール26内の面とには、熱酸化により第1絶縁層28が形成されている。また、Siベース基板12の他方の面には第2絶縁層34が設けられている。そして、ビアホール内に設けられた導電体により、貫通電極14が構成されている。

【0038】

赤外線検出素子220は、熱酸化層を含む第1絶縁層28を介してSiベース基板の一方の面に搭載されており、キャパシター230を含んでいる。キャパシター230は、焦電体232と、焦電体232の下面に接続される第1電極(下部電極)234と、焦電体232の上面に接続される第2電極(上部電極)236とを含んでおり、温度に基づいて分極量が変化する。

【0039】

キャパシター230の表面には層間絶縁膜260が設けられている。層間絶縁膜260には、第1電極234に通ずる第1コンタクトホール252と、第2電極236に通ずる第2コンタクトホール254とが形成されている。

【0040】

層間絶縁膜260の表面には、第1、第2電極配線層222、224が設けられており、第1電極配線層222は第1コンタクトホール252を通じて第1電極に接続されている。同様に、第2電極配線層224は第2コンタクトホール254を通じて第2電極に接続されている。

【0041】

第1、第2電極配線層222、224の一方には貫通電極14が接続されている。この貫通電極14は、Siベース基板12の他方の面において、後述する行選択回路(行ドライバー)か、または列線を介して検出器からのデータを読み出す読み出し回路に接続される。

【0042】

図6は、本発明の赤外線センサーの構成例を示す図である。図6(A)に示すように。この赤外線センサー300は、センサーアレイ310と、行選択回路(行ドライバー)320と、読み出し回路330を含む。またA/D変換部340、制御回路350を含むことができる。このセンサーを用いることで、例えばナイトビジョン機器などに用いられる赤外線カメラなどを実現できる。

【0043】

センサーアレイ310には、二軸方向に複数のセンサーセルが配列(配置)される。また複数の行線(ワード線、走査線)と複数の列線(データ線)が設けられる。なお行線及び列線の一方の本数が1本であってもよい。例えば行線が1本である場合には、図6(A)において行線に沿った方向(横方向)に複数のセンサーセルが配列される。一方、列線が1本である場合には、列線に沿った方向(縦方向)に複数のセンサーセルが配列される。

【0044】

図6(B)に示すように、センサーアレイ310の各センサーセルは、各行線と各列線の交差位置に対応する場所に配置(形成)される。例えば図6(B)のセンサーセルは、行線WL1と列線DL1の交差位置に対応する場所に配置されている。他のセンサーセルも同様である。行選択回路320は、1又は複数の行線に接続される。そして各行線の選択動作を行う。例えば図6(B)のようなQVGA(320×240画素)のセンサーアレイ310(焦点面アレイ)を例にとれば、行線WL0、WL1、WL2・・・・WL239を順次選択(走査)する動作を行う。即ちこれらの行線を選択する信号(ワード選択信号)をセンサーアレイ310に出力する。

【0045】

読み出し回路330は、1又は複数の列線に接続される。そして各列線の読み出し動作を行う。QVGAのセンサーアレイ310を例にとれば、列線DL0、DL1、DL2・・・・DL319からの検出信号(検出電流、検出電荷)を読み出す動作を行う。

【0046】

A/D変換部340は、読み出し回路330において取得された検出電圧(測定電圧、到達電圧)をデジタルデータにA/D変換する処理を行う。そしてA/D変換後のデジタルデータDOUTを出力する。具体的には、A/D変換部340には、複数の列線の各列線に対応して各A/D変換器が設けられる。そして、各A/D変換器は、対応する列線において読み出し回路330により取得された検出電圧のA/D変換処理を行う。なお、複数の列線に対応して1つのA/D変換器を設け、この1つのA/D変換器を用いて、複数の列線の検出電圧を時分割にA/D変換してもよい。

【0047】

制御回路350(タイミング生成回路)は、各種の制御信号を生成して、行選択回路320、読み出し回路330、A/D変換部340に出力する。例えば充電や放電(リセット)の制御信号を生成して出力する。或いは、各回路のタイミングを制御する信号を生成して出力する。

【0048】

本発明の赤外線センサーによれば、熱酸化によりSiベース基板12の一方の面とビアホール26内の面とに絶縁層(第1絶縁層28)を形成することにより、非常に緻密で絶縁性の高い膜を均一に形成することができる。また、微細で高アスペクトの貫通電極を形成することができるため、高密度に赤外線検出素子を設けることができる。従って、高精彩の赤外線カメラなどを実現できる。

【0049】

[実施例1]

図3に、本発明に係る素子付き基板の貫通電極形成方法の実施例1のプロセスを示す。

<第1工程:ベース基板の準備>

ベース基板12としては、この実施例ではSi半導体基板を用いている。

【0050】

<第2工程:ビアホール形成(Siエッチング)>

Siベース基板12の表面側から裏面側に向けてエッチングし、Siベース基板12の任意の場所まで至るビアホール26を形成する。方法としてはRIE、ICPなどのドライエッチングによる方法、レーザーにより形成する方法がある。

【0051】

ドライエッチングを例に取れば、エッチング、デポジションを交互に繰り返しながら掘り進めるボッシュプロセスを用いることができる。その場合のガスとしては、エッチングにはSF6、O2、デポジションにはC4F8、O2を用いる。方法としてはレジストなどで孔を開けたい部分を除き被覆保護し、ドライエッチ処理後、レジスト等の被覆膜を除去する。

【0052】

本実施例では微細、高アスペクト、多ビア用に、ビアホール26をφ10μm〜20μmとしストレート形状にした。ビアホールの深さを70〜100μmとし、アスペクトが5〜7確保した。ビアホール26の配列はアレイ状(マトリックス)でもよいし、ペリフェラル配列でもよい。ピッチは15〜30μmで形成した。エリアアレイの場合は7万ビア〜33万ビア/chip形成した。

【0053】

<第3工程:ビアホール内・基板表面の絶縁>

ビアホール26の側壁、Siベース基板12の表面全体を第1絶縁層28で被覆する。CVD法によるSiO2、SiNなどの無機膜を形成することができるが、素子回路18の形成前の利点を生かし、加工が容易で装置が安価な熱酸化によるSiO2膜の形成を行った。1000℃以上で数時間加熱することにより、0.5μm〜3μm程度の膜厚とした。熱酸化膜はCVD法による膜に比べ非常に緻密なため、絶縁特性も非常に高い。

【0054】

<第4工程:埋め込み材(犠牲層)の仮埋め込み>

側壁が絶縁されたビアホール26内に仮の埋め込み材36を埋め込む。ビアホール26内が空洞のままであると、素子回路形成工程での熱プロセスで空洞内の空気が膨張しベース基板12に対する素子回路18の密着性が低下する可能性がある。埋め込む材料は熱による拡散が少なく、絶縁膜との相性がよいものを選定する。今回はポリシリコンを用いた。ポリシリコンはビア内への埋め込み性が良い。

【0055】

<第5工程:素子回路形成>

ビアホール26を形成したSiベース基板12の表面側に素子回路18を形成する。素子は集積回路でもよく、センサー回路でも良い。今回は赤外線検出素子を形成しており、赤外線検出素子は焦電体と、焦電体の上面に接続される上部電極と、焦電体の下面に接続される下部電極とを含んでいる。この赤外線検出素子の製造工程には700℃以上の加熱が必要になる。もし、ビアファースト工法で素子形成前にビアホール内に埋め込み導電体30を埋め込んでいる場合、導電材料は700℃以上の熱により拡散しづらく、なおかつ赤外線検出素子を汚染しないものが必要となる。また一般的にはタングステンなどの高融点材料が使用されるが、第2工程でのSiビアホール形状にはCVDで埋め込むのは非常に難しい。仮に可能でも専用の装置が必要であり、コストアップは避けられない。

【0056】

<第6工程:支持基板の貼付>

Siベース基板12の素子回路18の形成面に接着剤などを介してガラスサポートウェハー38を貼り付ける。このガラスサポートウェハー38は薄く加工されるSiベース基板12を補強することにより、その後の薄型加工以降の工程流動における割れの防止、流動性を確保するものである。ガラスは後の工程で加熱を伴う可能性があるため、Siベース基板12と線膨張係数が近いものが望ましい。例えば、耐熱ガラス、石英ガラスなどを用いることができる。

【0057】

<第7工程:ウェハーの薄型化>

素子回路18の形成面と逆面となるSiベース基板12の裏面をバックグラインドにより、たとえば50〜100μm厚程度まで薄肉化する。バックグラインドした面についてはたとえば、ドライエッチング、スピンエッチング、ポリッシュなどの方法により、バックグラインドで形成されたSiの破砕層を取り除いてもよい。今回はビアの表面がわずかに出るまで薄型を行った。

【0058】

<第8工程:埋め込み材(犠牲層)除去>

第4工程でビアホール26に充填した仮埋め込み材36を、素子回路18の形成面の逆の面(Siベース基板12の裏面)側から突出したビアホール内の埋め込み材料を除去する。化学的または物理的に取り除いても良い。犠牲層を除去することによりビアホール26の底部には素子回路18の導電部である配線層16が露出する。

【0059】

<第9工程:第2絶縁層の形成>

素子回路18の形成面と逆の面(Siベース基板12の裏面)の薄型化された面に第2絶縁層34を設ける。この第2絶縁層34としては、CVD法によるSiO2、SiNなどの無機膜を形成することで構成してもよく、樹脂材料でもよい。樹脂材料による成膜はスピンコーティング法、スプレイコーティング法、印刷法などにより行う。膜厚は孔側壁で0.3〜3μm、ウェハー裏面上においては3μm以上形成する。ウェハー裏面上の膜厚は5μm以上が寄生容量低減の観点で望ましい。今回はCVD法によりSiO2を設けた。この第2絶縁層34の形成後、ビアホール底の素子回路18との導電部(配線層16)にも絶縁膜が形成されている可能性があるため、レジストで薄型化された面を保護し、ドライエッチングにより除去する。装置は酸化膜エッチャーを使用し、そのプロセスガスとしては、C2F6、CF4、CHF3を用いる。なお、第9工程は第8工程より先に行ってもよい。

【0060】

<第10工程:バリア層(密着層)、シード層の形成>

ビアホール26の開口に臨まれている素子回路18の配線層16と、第1絶縁層28の内壁に、その内周に形成される埋め込み導電体30のSi基板への拡散を防止するバリア層32を形成する。バリア層としてはTi、TiW、TiNなどを使うことができる。またその後、次のめっき工程のためのシード層を形成する。シード層材料はたとえばCuを用いることができる。これらの工程はスパッタ、CVDで形成することができる。膜厚はたとえば、TiW;10〜100nm、Cu;10〜300nmである。

【0061】

なお、素子回路18の導電部(配線層16)に形成された自然酸化膜を除去する目的で、バリア膜形成前に逆スパッタを行ってもよい。逆スパッタの処理量はたとえばSiO2換算で300nmエッチング相当である。

【0062】

<第11工程:シリコン貫通電極、再配置配線、裏面端子の形成>

ビアホール26への埋め込み導電体30の充填時に、ベース基板12の裏面側にめっき用のレジストを形成する。そのレジストは貫通電極部、または貫通電極部と裏面に形成する再配置配線・外部素子と接続するための端子部が開口されている。貫通孔内にめっき充填を行い、引き続きベース基板裏面の外部電極端子20のめっきを行う。

【0063】

なお、ビアホール26の穴埋めと裏面の端子形成、再配置配線の形成を一連のめっき工程で形成する例を示したが、それらは別々の工程で形成してもよい。今回は貫通電極部上部に外部電極端子20を形成する。外部電極端子20の厚みはたとえば6μm厚とすればよい。この実施例ではCuを用いているが、最表面はSnAgなどの低融点金属やAuなどの貴金属を積層してもよい。

【0064】

<第12工程:バリア層(密着層)、シード層のエッチング>

ビアホール26内へのめっき充填と、ベース基板裏面の外部電極端子20のめっき終了後、余剰のめっきレジストを剥離し、端子をマスクにして下地金属(例;TiW,Cu)をエッチングで除去する。

【0065】

<第13工程:ガラスサポート剥離>

最後にSi基板を支持しているガラスサポートウェハー38を剥離する。

以上のプロセスを用い作製した微細、高アスペクト、多ビアの貫通電極構造を持つ構造体を温度サイクル試験による信頼性テストを行った結果、素子回路導電部と貫通電極間や絶縁膜部分での剥離等による不良は認められなかった。

【0066】

[実施例2]

図4に、本発明に係る素子付き基板の貫通電極形成方法の実施例2のプロセスを示す。

基本は実施例1と同じだが、一部プロセスが異なる。すなわち、実施例1の第2工程のビアホール形成のためのSiエッチングの後(工程2−1)、裏面側からもSiエッチングを行い、Siベース基板12を厚さ方向に貫通する貫通孔を作製する(工程2−2)。その後は概ね同じ工程を経る。貫通孔を設けておくので、素子回路形成工程での温度によるビアホール内の空気によりSiベース基板12に対する素子回路の密着力が低下するのを防止することが可能である。したがって、仮埋め込み材36をビアホール26に充填する工程(実施例1の工程4)、および仮埋め込み材36の除去工程(実施例1の工程8)を省略することができる。なお、この図4の工程図にはウェハーの薄型化につき、Siベース基板12の裏面側において、基板エッチング工程(工程7−1)と第1絶縁層28の平滑化(工程7−2)を別途に記載している。その他の工程については、第1実施例と同一の工程には、一の工程番号((1)〜(13))を付している。

【0067】

以上のプロセスを用い作製した微細、高アスペクト、多ビアの貫通電極構造を持つ構造体を温度サイクル試験による信頼性テストを行った結果、素子回路導電部と貫通電極間や絶縁膜部分での剥離等による不良は認められなかった。

【産業上の利用可能性】

【0068】

本発明は、赤外線カメラ、水晶振動子パッケージなどの製造技術に利用可能である。

【符号の説明】

【0069】

10………素子付き基板、12………ベース基板、14………貫通電極、16………配線層、18………素子回路、20………外部電極端子、21………突起電極、22………絶縁膜、24………ビア配線、26………ビアホール(ベース基板貫通孔)、28………第1絶縁層、30………埋め込み導電体、32………バリア層、34………第2絶縁層、36………仮埋め込み材、38………ガラスサポートウェハー。

【技術分野】

【0001】

本発明は貫通電極を備えた素子付き基板、赤外線センサーおよび貫通電極形成方法に関する。

【背景技術】

【0002】

3次元実装パッケージでは、複数のチップ(素子付き基板)を垂直に積み重ね、1つのパッケージとすることで占有面積を小さくできる。このため、シリコンウェハーやダイといったチップを垂直に貫くビアホールを利用した貫通電極によってウェハーやダイ同士の垂直方向の電気的接続を行なうことが行なわれている。

【0003】

このような貫通電極を備えたチップは、半導体基板と半導体基板に形成された貫通電極とを含んで構成されている。このようなチップにおいて、半導体基板は、半導体基板上に形成された回路に対して一定の電位となっており、回路と導通している貫通電極とは電位差があるため、貫通電極と半導体基板との間でリーク電流が発生する場合がある。そのため、特許文献1では、リーク電流を防止するために、貫通電極や貫通電極に接続された電極と、基板との間には、樹脂絶縁層が形成されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−177237号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、樹脂絶縁層を用いて微細で高アスペクトの貫通電極を形成する場合には、十分な厚さの樹脂絶縁層を形成することができず、絶縁機能が低下する課題があった。

【0006】

本発明は、上記の課題に着目してなされたもので、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサー、および貫通電極形成方法を提供することを目的としている。

【課題を解決するための手段】

【0007】

本発明は、以下のような適用例を採用することにより、上記目的の少なくとも一部を達成することができる。

【0008】

[適用例1]一方の面と他方の面とに開口するビアホールが形成されたベース基板と、前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、前記配線層に電気的に接続された素子回路と、を有し、前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする素子付き基板。

【0009】

このような構成を採用することで、ベース基板の一方の面からビアホール内の面に掛けて熱酸化による緻密で均一な肉厚の絶縁膜を形成することができ、リーク電流が発生しやすいベース基板の一方の面とビアホール内の面とが形成する角部(ビアコーナー部分)での絶縁特性が良好な素子付き基板を得ることが出来る。

【0010】

[適用例2]適用例1において、前記第1絶縁層に接続されており、前記ベース基板の他方の面に設けられた第2絶縁層を有することを特徴とする素子付き基板。

この構成により、ベース基板の他方の面とビアホール内の面とが形成する角部での絶縁特性も良好にできる。

【0011】

[適用例3]適用例1又は2において、前記導電体は前記ベース基板の他方の面に突出する突起部を含むことを特徴とする素子付き基板。

この構成により、素子付き基板を垂直に積層することが容易となり、3次元積層パッケージの製造が容易になる。

【0012】

[適用例4]ベース基板の一方の面からビアホールを形成するビアホール形成工程と、前記ベース基板の一方の面と前記ビアホール内の面とに熱酸化により熱酸化絶縁層を形成する熱酸化工程と、前記熱酸化工程後に、前記ベース基板の一方の面に導電部を有する素子回路を形成する素子回路形成工程と、前記素子回路形成工程後に、前記ビアホールに導電体を埋め込み形成する導電体形成工程と、を含むことを特徴とする貫通電極形成方法。

上記構成により、マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を形成することができる。

【0013】

[適用例5]適用例4において、前記熱酸化工程と前記素子回路形成工程との間に、前記ビアホール内に仮埋め込み材を埋め込む工程を含み、前記素子回路形成工程と前記導電体形成工程との間に、前記仮埋め込み材を除去する工程を含むことを特徴とする貫通電極形成方法。

【0014】

上記構成により、予めビアホールを形成していても、ビアホール空洞部の残留気体が素子形成工程で膨張することによってベース基板に対する素子回路の密着力が低下することを有効に防止できる。

【0015】

[適用例6]適用例4又は5において、前記素子回路形成工程と前記導電体形成工程との間に、前記ベース基板の他方の面を研削し、前記ベース基板の他方の面に前記熱酸化絶縁層と連続する第2絶縁層を設ける工程を含むことを特徴とする貫通電極形成方法。

このような構成では、ベース基板の他方の面とビアホール内の面とが形成する角部でのリーク電流発生を効果的に抑制することができる。

【0016】

[適用例7]適用例6において、前記導電体形成工程後に、前記ベース基板の他方の面に前記導電体に接続された端子を形成する工程を含むことを特徴とする貫通電極形成方法。

このような構成では、ベース基板の他方の面において外部接続することができる。

【0017】

[適用例8]適用例7において、前記ベース基板の他方の面を研削する前に、支持部材を前記ベース基板の一方の面に貼り付けることを特徴とする貫通電極形成方法。

これにより、薄板化したベース基板への加工性を確保することができる。

【0018】

[適用例9]適用例8において、前記ベース基板の一方の面に貼り付けられた前記支持部材を前記端子形成後に除去することを特徴とする貫通電極形成方法。

これにより、次工程への支持基板の持込がなくなる。

【0019】

[適用例10]適用例4において、前記ビアホール形成工程では、前記ベース基板を貫通したビアホールを形成することを特徴とする貫通電極形成方法。

このような構成では、予めビアホールを形成しても空洞部に気体が残留することがないので、仮の埋め込み材を用いることが不要となり、工程の短縮化につながる。

【0020】

[適用例11]適用例4乃至10のいずれかにおいて、前記導電体形成工程では、めっきにより前記導電体を形成することを特徴とする貫通電極形成方法。

これにより、微細でアスペクトが高いビアホール内に導電体を埋め込むことが容易に行え、高額なCVDなどの装置を使用しなくてよい。

【0021】

[適用例12]一方の面と他方の面とに開口するビアホールが形成されたベース基板と、前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、前記配線層に電気的に接続された赤外線検出素子と、を有し、前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする赤外線センサー。

【0022】

このような構成を採用することで、ベース基板の一方の面からビアホール内の面に掛けて熱酸化による緻密で均一な肉厚の絶縁膜を形成することができ、リーク電流が発生しやすいベース基板の一方の面とビアホール内の面とが形成する角部(ビアコーナー部分)での絶縁特性が良好な素子付き基板を得ることが出来る。そして、微細で高アスペクトの貫通電極を形成することができるため、高密度に赤外線検出素子を設けることができる。

【発明の効果】

【0023】

本発明の構成によれば、貫通電極を構成するビアホールおよび絶縁層の形成と、導電体からなる埋め込み電極の形成とを、素子回路形成前後で分断する工程で作製するようにしたので、微細、高アスペクト、多ビアの貫通電極構造を持つ素子回路付き基板構造体の作製が容易になる。具体的には、微細、高アスペクト対応の素子回路形成前での貫通電極の絶縁特性がよい熱酸化絶縁膜の形成、マイグレーションの問題を生じることなく、素子回路形成後でのめっきによる導電体の埋め込みが可能となり、容易な装置や工法を用いることが可能となる。

【図面の簡単な説明】

【0024】

【図1】本発明に係る素子付き基板を模式的に示した要部断面図である。

【図2】本発明に係る素子付き基板の貫通電極形成方法の基本工程を示すフローチャートである。

【図3】第1実施形態に係る素子付き基板の貫通電極形成方法の工程を示すフローチャートである。

【図4】第2実施形態に係る素子付き基板の貫通電極形成方法の工程を示すフローチャートである。

【図5】本発明に係る赤外線センサーの1セル分の赤外線検出素子の断面図である。

【図6】図6(A)、図6(B)は赤外線検出素子を二次元配置した赤外線センサーの構成例を示す図である。

【発明を実施するための形態】

【0025】

以下に、本発明に係る素子付き基板、赤外線センサーおよび貫通電極形成方法の具体的実施形態につき、図面を参照しながら詳細に説明する。

なお、下記の実施形態は一例であり、本発明の主旨を逸脱しない範囲で各種変形構成を取り得る。

【0026】

<素子付き基板の構成>

図1は実施形態に係る素子付き基板10の断面図である。この図に示されているように、この素子付き基板10には、ベース基板12を厚さ方向に貫通させることによって形成された貫通電極14が設けられている。この貫通電極14の一端側であるベース基板12の表面側には、配線層16を介し前記貫通電極14と接続される素子回路18が設けられている。一方、貫通電極14の他端側はベース基板12の裏面から突出され、ここに外部電極端子20が形成されて突起電極21を形成している。これにより、当該素子付き基板10を他のチップ上に垂直に積み重ね、占有面積の少ない1つのパッケージを作製することができる。

【0027】

より具体的には、次のように構成されている。まず、ベース基板12として本実施形態では、Si半導体基板が用いられている。貫通電極14はSiベース基板12の裏面から素子回路18の形成面であるベース基板12の表面に形成された配線層16に至っており、当該配線層16と、Siベース基板12の裏面に形成された外部電極端子20とを電気的に接続している。また、前記配線層16の上には互いに絶縁膜22によって隔てられた素子回路18が形成されている。配線層16はその間に位置する配線間絶縁膜22に形成されたビア配線24により素子回路18に電気的接続されている。なお、配線層16は複数の金属層が積層されたものであってもよい。

【0028】

貫通電極14はSiベース基板12に形成されたビアホール(ベース基板貫通孔)26の内壁をSiO2などの無機材料の第1絶縁層28が覆っている。この第1絶縁層28は、1000℃前後の温度環境で、熱酸化により形成されたもので、前記Siベース基板12と素子回路18(具体的には配線層16)の間に介在され、連続してビアホール26内壁面に至っている。熱酸化による絶縁膜形成であるため、前記Siベース基板12の素子回路18形成面と、ビアホール26内壁面とに対し、緻密で厚みが均等となるように一体に形成されている。この第1絶縁層28の厚みはビアホール26の直径の約5〜10%とされ、ビアホール直径が約20μmとすれば、約1〜2μmの肉厚となるように成膜されている。これにより、ビアホール26の配線層16側のコーナー部分が緻密で厚肉の第1絶縁層28で覆われるため、絶縁破壊が生じやすいコーナー部分での絶縁特性が向上し、リーク電流の抑制効果が高いものとなっている。

【0029】

さらに、ビアホール26の開口に臨まれている素子回路18の配線層16と、第1絶縁層28の内壁には、その内周に形成される埋め込み導電体30のSi基板への拡散を防止するバリア層および密着層として、TiWなどの金属膜(以下バリア層32という)が形成されている。

【0030】

バリア層32の内壁にはCu、Ni、Auなどの導電体30が埋め込み形成されている。埋め込み導電体30はバリア層で囲まれた孔空間内に完全に充填されていてもよい。または孔空間の内壁に沿って膜状に覆うものであってもよい。その場合、導体膜の内側の孔部には補強のために樹脂などの第三絶縁物を埋め込むのが望ましい。

【0031】

また、Siベース基板12の素子回路18形成面と反対側の裏面上には、裏面側ビアコーナー部を絶縁するために、樹脂またはSiO2、SiNなどの無機材料などからなる第2絶縁層34が、第1絶縁層28と連続するように形成されている。さらに、第2絶縁層34の外表面部には、前記埋め込み導電体30が前記ベース基板12の裏面側に突出しており、この突出部と接続される外部電極端子20が形成され、突起電極21とされている。

【0032】

これにより、裏面側ビアコーナー部は、表面側ビアコーナー部と同様に、第1絶縁層28と第2絶縁層34によって確実に覆われ、絶縁破壊が生じやすいコーナー部分での絶縁特性が向上し、リーク電流の抑制効果が高いものとなっている。

【0033】

なお、この実施形態では、図1に示すように、貫通電極14がストレート貫通電極とした例をあげているが、ビアホール26をテーパ形状にしたテーパ形状の貫通電極としてもよい。

【0034】

<素子付き基板の製造プロセス>

上述のような素子付き基板10を作製するための基本的プロセスを図2に示している。すなわち、素子回路18の形成前に、Siベース基板12にビアホール26を形成し(工程1)、次いで、Siベース基板12を熱酸化することによって絶縁膜(第1絶縁層28)まで形成しておく(工程2)。このときには、ビアホール26内には埋め込み導電体30を設けない。その後、ビアホール26の開口側に素子回路18を形成するが(工程4)、ビアホール26が空洞のまま素子回路18を積層形成すると密閉された空洞に雰囲気ガスが充満して、Siベース基板12に対する素子回路18の密着力が低下する可能性があるので、予めビアホール26内に仮の埋め込み材36を充填しておく(工程3)。素子回路18の形成後、当該素子回路18の形成面と反対側のSiベース基板12の裏面側を研削して薄型化し(工程5)、ビアホール26の中の仮埋め込み材36を除去してベース裏面側を開口させる(工程6)。次いで、Siベース基板12の裏面に絶縁膜(第2絶縁層34)を形成する(工程7)。最後に、先行して作製したビアホール26に導電材料(導電体30)を埋め込むようにしている(工程8)。すなわち、素子回路18の形成前に、ビアホール26と第1絶縁層28まで形成しておき、素子回路18を形成してからビアホール26の内部に導電体30を埋め込み形成するようにしているものである。

【0035】

このように、素子回路18の形成前に熱酸化によりビアホール26内に絶縁膜(第1絶縁層28)を形成することにより、従来技術では実現が難しい非常に緻密で絶縁性の高い膜が均一に形成できる。また素子回路18の形成後であれば、マイグレーションの問題を生じることなく、埋め込み導電体30として、めっきによりCuなどの導電材料を埋め込むことが可能となる。導電体30の埋め込み処理は、素子回路18の形成面と反対側のベース基板12の裏面を薄型化し、裏面より埋め込みを行えばよい。いずれの工程も、CVDのような高価な装置を用いず、安価な機器により成し遂げることが可能となる。このように絶縁膜(第1絶縁層28)の形成と導電体30の埋め込みを別工程で行うことにより、微細でアスペクトの高い貫通電極の形成ができる。

【0036】

<赤外線センサーの構成>

図5は、本発明の赤外線センサーを構成する赤外線検出素子を示す断面図である。赤外線センサー300は、赤外線検出素子220を含むセンサーセルが複数配列されて構成される。なお、赤外線センサー300の詳細な構成については後述する。

【0037】

図5に示すように、赤外線センサー300は、赤外線検出素子220と、赤外線検出素子220を搭載したSiベース基板12と、を有している。Siベース基板12には、ビアホール26が形成されており、ベース基板12の一方の面とビアホール26内の面とには、熱酸化により第1絶縁層28が形成されている。また、Siベース基板12の他方の面には第2絶縁層34が設けられている。そして、ビアホール内に設けられた導電体により、貫通電極14が構成されている。

【0038】

赤外線検出素子220は、熱酸化層を含む第1絶縁層28を介してSiベース基板の一方の面に搭載されており、キャパシター230を含んでいる。キャパシター230は、焦電体232と、焦電体232の下面に接続される第1電極(下部電極)234と、焦電体232の上面に接続される第2電極(上部電極)236とを含んでおり、温度に基づいて分極量が変化する。

【0039】

キャパシター230の表面には層間絶縁膜260が設けられている。層間絶縁膜260には、第1電極234に通ずる第1コンタクトホール252と、第2電極236に通ずる第2コンタクトホール254とが形成されている。

【0040】

層間絶縁膜260の表面には、第1、第2電極配線層222、224が設けられており、第1電極配線層222は第1コンタクトホール252を通じて第1電極に接続されている。同様に、第2電極配線層224は第2コンタクトホール254を通じて第2電極に接続されている。

【0041】

第1、第2電極配線層222、224の一方には貫通電極14が接続されている。この貫通電極14は、Siベース基板12の他方の面において、後述する行選択回路(行ドライバー)か、または列線を介して検出器からのデータを読み出す読み出し回路に接続される。

【0042】

図6は、本発明の赤外線センサーの構成例を示す図である。図6(A)に示すように。この赤外線センサー300は、センサーアレイ310と、行選択回路(行ドライバー)320と、読み出し回路330を含む。またA/D変換部340、制御回路350を含むことができる。このセンサーを用いることで、例えばナイトビジョン機器などに用いられる赤外線カメラなどを実現できる。

【0043】

センサーアレイ310には、二軸方向に複数のセンサーセルが配列(配置)される。また複数の行線(ワード線、走査線)と複数の列線(データ線)が設けられる。なお行線及び列線の一方の本数が1本であってもよい。例えば行線が1本である場合には、図6(A)において行線に沿った方向(横方向)に複数のセンサーセルが配列される。一方、列線が1本である場合には、列線に沿った方向(縦方向)に複数のセンサーセルが配列される。

【0044】

図6(B)に示すように、センサーアレイ310の各センサーセルは、各行線と各列線の交差位置に対応する場所に配置(形成)される。例えば図6(B)のセンサーセルは、行線WL1と列線DL1の交差位置に対応する場所に配置されている。他のセンサーセルも同様である。行選択回路320は、1又は複数の行線に接続される。そして各行線の選択動作を行う。例えば図6(B)のようなQVGA(320×240画素)のセンサーアレイ310(焦点面アレイ)を例にとれば、行線WL0、WL1、WL2・・・・WL239を順次選択(走査)する動作を行う。即ちこれらの行線を選択する信号(ワード選択信号)をセンサーアレイ310に出力する。

【0045】

読み出し回路330は、1又は複数の列線に接続される。そして各列線の読み出し動作を行う。QVGAのセンサーアレイ310を例にとれば、列線DL0、DL1、DL2・・・・DL319からの検出信号(検出電流、検出電荷)を読み出す動作を行う。

【0046】

A/D変換部340は、読み出し回路330において取得された検出電圧(測定電圧、到達電圧)をデジタルデータにA/D変換する処理を行う。そしてA/D変換後のデジタルデータDOUTを出力する。具体的には、A/D変換部340には、複数の列線の各列線に対応して各A/D変換器が設けられる。そして、各A/D変換器は、対応する列線において読み出し回路330により取得された検出電圧のA/D変換処理を行う。なお、複数の列線に対応して1つのA/D変換器を設け、この1つのA/D変換器を用いて、複数の列線の検出電圧を時分割にA/D変換してもよい。

【0047】

制御回路350(タイミング生成回路)は、各種の制御信号を生成して、行選択回路320、読み出し回路330、A/D変換部340に出力する。例えば充電や放電(リセット)の制御信号を生成して出力する。或いは、各回路のタイミングを制御する信号を生成して出力する。

【0048】

本発明の赤外線センサーによれば、熱酸化によりSiベース基板12の一方の面とビアホール26内の面とに絶縁層(第1絶縁層28)を形成することにより、非常に緻密で絶縁性の高い膜を均一に形成することができる。また、微細で高アスペクトの貫通電極を形成することができるため、高密度に赤外線検出素子を設けることができる。従って、高精彩の赤外線カメラなどを実現できる。

【0049】

[実施例1]

図3に、本発明に係る素子付き基板の貫通電極形成方法の実施例1のプロセスを示す。

<第1工程:ベース基板の準備>

ベース基板12としては、この実施例ではSi半導体基板を用いている。

【0050】

<第2工程:ビアホール形成(Siエッチング)>

Siベース基板12の表面側から裏面側に向けてエッチングし、Siベース基板12の任意の場所まで至るビアホール26を形成する。方法としてはRIE、ICPなどのドライエッチングによる方法、レーザーにより形成する方法がある。

【0051】

ドライエッチングを例に取れば、エッチング、デポジションを交互に繰り返しながら掘り進めるボッシュプロセスを用いることができる。その場合のガスとしては、エッチングにはSF6、O2、デポジションにはC4F8、O2を用いる。方法としてはレジストなどで孔を開けたい部分を除き被覆保護し、ドライエッチ処理後、レジスト等の被覆膜を除去する。

【0052】

本実施例では微細、高アスペクト、多ビア用に、ビアホール26をφ10μm〜20μmとしストレート形状にした。ビアホールの深さを70〜100μmとし、アスペクトが5〜7確保した。ビアホール26の配列はアレイ状(マトリックス)でもよいし、ペリフェラル配列でもよい。ピッチは15〜30μmで形成した。エリアアレイの場合は7万ビア〜33万ビア/chip形成した。

【0053】

<第3工程:ビアホール内・基板表面の絶縁>

ビアホール26の側壁、Siベース基板12の表面全体を第1絶縁層28で被覆する。CVD法によるSiO2、SiNなどの無機膜を形成することができるが、素子回路18の形成前の利点を生かし、加工が容易で装置が安価な熱酸化によるSiO2膜の形成を行った。1000℃以上で数時間加熱することにより、0.5μm〜3μm程度の膜厚とした。熱酸化膜はCVD法による膜に比べ非常に緻密なため、絶縁特性も非常に高い。

【0054】

<第4工程:埋め込み材(犠牲層)の仮埋め込み>

側壁が絶縁されたビアホール26内に仮の埋め込み材36を埋め込む。ビアホール26内が空洞のままであると、素子回路形成工程での熱プロセスで空洞内の空気が膨張しベース基板12に対する素子回路18の密着性が低下する可能性がある。埋め込む材料は熱による拡散が少なく、絶縁膜との相性がよいものを選定する。今回はポリシリコンを用いた。ポリシリコンはビア内への埋め込み性が良い。

【0055】

<第5工程:素子回路形成>

ビアホール26を形成したSiベース基板12の表面側に素子回路18を形成する。素子は集積回路でもよく、センサー回路でも良い。今回は赤外線検出素子を形成しており、赤外線検出素子は焦電体と、焦電体の上面に接続される上部電極と、焦電体の下面に接続される下部電極とを含んでいる。この赤外線検出素子の製造工程には700℃以上の加熱が必要になる。もし、ビアファースト工法で素子形成前にビアホール内に埋め込み導電体30を埋め込んでいる場合、導電材料は700℃以上の熱により拡散しづらく、なおかつ赤外線検出素子を汚染しないものが必要となる。また一般的にはタングステンなどの高融点材料が使用されるが、第2工程でのSiビアホール形状にはCVDで埋め込むのは非常に難しい。仮に可能でも専用の装置が必要であり、コストアップは避けられない。

【0056】

<第6工程:支持基板の貼付>

Siベース基板12の素子回路18の形成面に接着剤などを介してガラスサポートウェハー38を貼り付ける。このガラスサポートウェハー38は薄く加工されるSiベース基板12を補強することにより、その後の薄型加工以降の工程流動における割れの防止、流動性を確保するものである。ガラスは後の工程で加熱を伴う可能性があるため、Siベース基板12と線膨張係数が近いものが望ましい。例えば、耐熱ガラス、石英ガラスなどを用いることができる。

【0057】

<第7工程:ウェハーの薄型化>

素子回路18の形成面と逆面となるSiベース基板12の裏面をバックグラインドにより、たとえば50〜100μm厚程度まで薄肉化する。バックグラインドした面についてはたとえば、ドライエッチング、スピンエッチング、ポリッシュなどの方法により、バックグラインドで形成されたSiの破砕層を取り除いてもよい。今回はビアの表面がわずかに出るまで薄型を行った。

【0058】

<第8工程:埋め込み材(犠牲層)除去>

第4工程でビアホール26に充填した仮埋め込み材36を、素子回路18の形成面の逆の面(Siベース基板12の裏面)側から突出したビアホール内の埋め込み材料を除去する。化学的または物理的に取り除いても良い。犠牲層を除去することによりビアホール26の底部には素子回路18の導電部である配線層16が露出する。

【0059】

<第9工程:第2絶縁層の形成>

素子回路18の形成面と逆の面(Siベース基板12の裏面)の薄型化された面に第2絶縁層34を設ける。この第2絶縁層34としては、CVD法によるSiO2、SiNなどの無機膜を形成することで構成してもよく、樹脂材料でもよい。樹脂材料による成膜はスピンコーティング法、スプレイコーティング法、印刷法などにより行う。膜厚は孔側壁で0.3〜3μm、ウェハー裏面上においては3μm以上形成する。ウェハー裏面上の膜厚は5μm以上が寄生容量低減の観点で望ましい。今回はCVD法によりSiO2を設けた。この第2絶縁層34の形成後、ビアホール底の素子回路18との導電部(配線層16)にも絶縁膜が形成されている可能性があるため、レジストで薄型化された面を保護し、ドライエッチングにより除去する。装置は酸化膜エッチャーを使用し、そのプロセスガスとしては、C2F6、CF4、CHF3を用いる。なお、第9工程は第8工程より先に行ってもよい。

【0060】

<第10工程:バリア層(密着層)、シード層の形成>

ビアホール26の開口に臨まれている素子回路18の配線層16と、第1絶縁層28の内壁に、その内周に形成される埋め込み導電体30のSi基板への拡散を防止するバリア層32を形成する。バリア層としてはTi、TiW、TiNなどを使うことができる。またその後、次のめっき工程のためのシード層を形成する。シード層材料はたとえばCuを用いることができる。これらの工程はスパッタ、CVDで形成することができる。膜厚はたとえば、TiW;10〜100nm、Cu;10〜300nmである。

【0061】

なお、素子回路18の導電部(配線層16)に形成された自然酸化膜を除去する目的で、バリア膜形成前に逆スパッタを行ってもよい。逆スパッタの処理量はたとえばSiO2換算で300nmエッチング相当である。

【0062】

<第11工程:シリコン貫通電極、再配置配線、裏面端子の形成>

ビアホール26への埋め込み導電体30の充填時に、ベース基板12の裏面側にめっき用のレジストを形成する。そのレジストは貫通電極部、または貫通電極部と裏面に形成する再配置配線・外部素子と接続するための端子部が開口されている。貫通孔内にめっき充填を行い、引き続きベース基板裏面の外部電極端子20のめっきを行う。

【0063】

なお、ビアホール26の穴埋めと裏面の端子形成、再配置配線の形成を一連のめっき工程で形成する例を示したが、それらは別々の工程で形成してもよい。今回は貫通電極部上部に外部電極端子20を形成する。外部電極端子20の厚みはたとえば6μm厚とすればよい。この実施例ではCuを用いているが、最表面はSnAgなどの低融点金属やAuなどの貴金属を積層してもよい。

【0064】

<第12工程:バリア層(密着層)、シード層のエッチング>

ビアホール26内へのめっき充填と、ベース基板裏面の外部電極端子20のめっき終了後、余剰のめっきレジストを剥離し、端子をマスクにして下地金属(例;TiW,Cu)をエッチングで除去する。

【0065】

<第13工程:ガラスサポート剥離>

最後にSi基板を支持しているガラスサポートウェハー38を剥離する。

以上のプロセスを用い作製した微細、高アスペクト、多ビアの貫通電極構造を持つ構造体を温度サイクル試験による信頼性テストを行った結果、素子回路導電部と貫通電極間や絶縁膜部分での剥離等による不良は認められなかった。

【0066】

[実施例2]

図4に、本発明に係る素子付き基板の貫通電極形成方法の実施例2のプロセスを示す。

基本は実施例1と同じだが、一部プロセスが異なる。すなわち、実施例1の第2工程のビアホール形成のためのSiエッチングの後(工程2−1)、裏面側からもSiエッチングを行い、Siベース基板12を厚さ方向に貫通する貫通孔を作製する(工程2−2)。その後は概ね同じ工程を経る。貫通孔を設けておくので、素子回路形成工程での温度によるビアホール内の空気によりSiベース基板12に対する素子回路の密着力が低下するのを防止することが可能である。したがって、仮埋め込み材36をビアホール26に充填する工程(実施例1の工程4)、および仮埋め込み材36の除去工程(実施例1の工程8)を省略することができる。なお、この図4の工程図にはウェハーの薄型化につき、Siベース基板12の裏面側において、基板エッチング工程(工程7−1)と第1絶縁層28の平滑化(工程7−2)を別途に記載している。その他の工程については、第1実施例と同一の工程には、一の工程番号((1)〜(13))を付している。

【0067】

以上のプロセスを用い作製した微細、高アスペクト、多ビアの貫通電極構造を持つ構造体を温度サイクル試験による信頼性テストを行った結果、素子回路導電部と貫通電極間や絶縁膜部分での剥離等による不良は認められなかった。

【産業上の利用可能性】

【0068】

本発明は、赤外線カメラ、水晶振動子パッケージなどの製造技術に利用可能である。

【符号の説明】

【0069】

10………素子付き基板、12………ベース基板、14………貫通電極、16………配線層、18………素子回路、20………外部電極端子、21………突起電極、22………絶縁膜、24………ビア配線、26………ビアホール(ベース基板貫通孔)、28………第1絶縁層、30………埋め込み導電体、32………バリア層、34………第2絶縁層、36………仮埋め込み材、38………ガラスサポートウェハー。

【特許請求の範囲】

【請求項1】

一方の面と他方の面とに開口するビアホールが形成されたベース基板と、

前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、

前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、

前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、

前記配線層に電気的に接続された素子回路と、

を有し、

前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする素子付き基板。

【請求項2】

請求項1において、

前記第1絶縁層に接続されており、前記ベース基板の他方の面に設けられた第2絶縁層を有することを特徴とする素子付き基板。

【請求項3】

請求項1又は2において、

前記導電体は前記ベース基板の他方の面に突出する突起部を含むことを特徴とする素子付き基板。

【請求項4】

ベース基板の一方の面からビアホールを形成するビアホール形成工程と、

前記ベース基板の一方の面と前記ビアホール内の面とに熱酸化により熱酸化絶縁層を形成する熱酸化工程と、

前記熱酸化工程後に、前記ベース基板の一方の面に導電部を有する素子回路を形成する素子回路形成工程と、

前記素子回路形成工程後に、前記ビアホールに導電体を埋め込み形成する導電体形成工程と、

を含むことを特徴とする貫通電極形成方法。

【請求項5】

請求項4において、

前記熱酸化工程と前記素子回路形成工程との間に、前記ビアホール内に仮埋め込み材を埋め込む工程を含み、

前記素子回路形成工程と前記導電体形成工程との間に、前記仮埋め込み材を除去する工程を含むことを特徴とする貫通電極形成方法。

【請求項6】

請求項4又は5において、

前記素子回路形成工程と前記導電体形成工程との間に、前記ベース基板の他方の面を研削し、前記ベース基板の他方の面に前記熱酸化絶縁層と連続する第2絶縁層を設ける工程を含むことを特徴とする貫通電極形成方法。

【請求項7】

請求項6において、

前記導電体形成工程後に、前記ベース基板の他方の面に前記導電体に接続された端子を形成する工程を含むことを特徴とする貫通電極形成方法。

【請求項8】

請求項7において、

前記ベース基板の他方の面を研削する前に、支持部材を前記ベース基板の一方の面に貼り付けることを特徴とする貫通電極形成方法。

【請求項9】

請求項8において、

前記ベース基板の一方の面に貼り付けられた前記支持部材を前記端子形成後に除去することを特徴とする貫通電極形成方法。

【請求項10】

請求項4において、

前記ビアホール形成工程では、前記ベース基板を貫通したビアホールを形成することを特徴とする貫通電極形成方法。

【請求項11】

請求項4乃至10のいずれか一項において、

前記導電体形成工程では、めっきにより前記導電体を形成することを特徴とする貫通電極形成方法。

【請求項12】

一方の面と他方の面とに開口するビアホールが形成されたベース基板と、

前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、

前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、

前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、

前記配線層に電気的に接続された赤外線検出素子と、

を有し、

前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする赤外線センサー。

【請求項1】

一方の面と他方の面とに開口するビアホールが形成されたベース基板と、

前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、

前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、

前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、

前記配線層に電気的に接続された素子回路と、

を有し、

前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする素子付き基板。

【請求項2】

請求項1において、

前記第1絶縁層に接続されており、前記ベース基板の他方の面に設けられた第2絶縁層を有することを特徴とする素子付き基板。

【請求項3】

請求項1又は2において、

前記導電体は前記ベース基板の他方の面に突出する突起部を含むことを特徴とする素子付き基板。

【請求項4】

ベース基板の一方の面からビアホールを形成するビアホール形成工程と、

前記ベース基板の一方の面と前記ビアホール内の面とに熱酸化により熱酸化絶縁層を形成する熱酸化工程と、

前記熱酸化工程後に、前記ベース基板の一方の面に導電部を有する素子回路を形成する素子回路形成工程と、

前記素子回路形成工程後に、前記ビアホールに導電体を埋め込み形成する導電体形成工程と、

を含むことを特徴とする貫通電極形成方法。

【請求項5】

請求項4において、

前記熱酸化工程と前記素子回路形成工程との間に、前記ビアホール内に仮埋め込み材を埋め込む工程を含み、

前記素子回路形成工程と前記導電体形成工程との間に、前記仮埋め込み材を除去する工程を含むことを特徴とする貫通電極形成方法。

【請求項6】

請求項4又は5において、

前記素子回路形成工程と前記導電体形成工程との間に、前記ベース基板の他方の面を研削し、前記ベース基板の他方の面に前記熱酸化絶縁層と連続する第2絶縁層を設ける工程を含むことを特徴とする貫通電極形成方法。

【請求項7】

請求項6において、

前記導電体形成工程後に、前記ベース基板の他方の面に前記導電体に接続された端子を形成する工程を含むことを特徴とする貫通電極形成方法。

【請求項8】

請求項7において、

前記ベース基板の他方の面を研削する前に、支持部材を前記ベース基板の一方の面に貼り付けることを特徴とする貫通電極形成方法。

【請求項9】

請求項8において、

前記ベース基板の一方の面に貼り付けられた前記支持部材を前記端子形成後に除去することを特徴とする貫通電極形成方法。

【請求項10】

請求項4において、

前記ビアホール形成工程では、前記ベース基板を貫通したビアホールを形成することを特徴とする貫通電極形成方法。

【請求項11】

請求項4乃至10のいずれか一項において、

前記導電体形成工程では、めっきにより前記導電体を形成することを特徴とする貫通電極形成方法。

【請求項12】

一方の面と他方の面とに開口するビアホールが形成されたベース基板と、

前記ベース基板の一方の面と前記ビアホール内の面とに形成された熱酸化層を含む第1絶縁層と、

前記第1絶縁層で囲まれており、前記ビアホール内に設けられた導電体と、

前記導電体に接続されており、前記第1絶縁層を介して前記ベース基板の一方の面に設けられた配線層と、

前記配線層に電気的に接続された赤外線検出素子と、

を有し、

前記ベース基板の一方の面における前記第1絶縁層の厚みと前記ビアホール内の面における前記第1絶縁層の厚みとが同じであることを特徴とする赤外線センサー。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−195514(P2012−195514A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−59798(P2011−59798)

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]