組み込み知能コントローラ、制御システム、制御プログラム、記録媒体、及び制御方法

【課題】インテリジェント・ロバスト制御を実現する組み込み知能コントローラを提供する。

【解決手段】

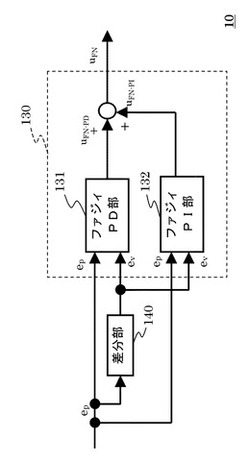

制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラ1のICS部10を用いる。ICS部10は、ファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるFB−FN部130(ファジィ・ニューラルネットワークによる非線形偏差補償器)を備える。FB−FN部130は、制御対象の非線形動特性のPD(比例、微分)補償を行うファジィPD部131と、制御対象の非線形動特性のPI(比例、積分)補償を行うファジィPI部132とを並列に備える。

【解決手段】

制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラ1のICS部10を用いる。ICS部10は、ファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるFB−FN部130(ファジィ・ニューラルネットワークによる非線形偏差補償器)を備える。FB−FN部130は、制御対象の非線形動特性のPD(比例、微分)補償を行うファジィPD部131と、制御対象の非線形動特性のPI(比例、積分)補償を行うファジィPI部132とを並列に備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、組み込み知能コントローラ、制御システム、制御プログラム、記録媒体、及び制御方法に係り、特にインテリジェント・ロバスト制御を行う組み込み知能コントローラ、制御システム、制御プログラム、記録媒体、及び制御方法に関する。

【背景技術】

【0002】

近年、宇宙探査機の『はやぶさ』や医療現場などの様々な作業環境でロボットマニピュレータが使用されている。また、ロボットの自動化・自律化も進められており、高精度な制御が求められている。しかし、このような制御を実現するには大きな問題点がある。それは、ロボットマニピュレータの動特性が位置・姿勢による慣性負荷や速度による遠心力、重力負荷などの非線形性を持つこと、それに加え環境条件や外的要因による外乱によって変動をきたすことなどである。

従来から、一般的な制御方法としてPID制御が知られている。PID制御は、P(Proportional、比例)動作、I(Integral、積分)、D(Differential、Derivative、微分)動作を用いたフィードバック制御である。すなわち、PID制御は、目標値−制御量である制御の偏差に対して、比例演算、積分演算、及び微分演算を行い、操作量を算出して制御する。

PID制御は、古典制御だが扱いやすさと正確性の良さから広く使われている。しかし、PID制御のような古典制御では外乱や非線形要素への対応が困難であった。

【0003】

そこで、従来から、一般にマニピュレータに関するシステム設計は、制御対象が多自由度系でも1自由度系と見なし近似式を用いて制御系を設計し、関節軸ごとに独立した制御系を構築する手法が多くの製品に採用されている。

しかし、一般的には、マニピュレータは、剛性が低く、重力や遠心力を受ける非線形な多入力多出力系である。また、従来手法では、PID制御における位相補償制御、最適サーボ系、外乱オブザーバを用いた制御あるいはH∞制御等を用いて精度、振動抑制、ロバスト性などを実現しているが、十分な制御性能が得られなかった。

【0004】

ここで、従来のPID調節装置として、特許文献1を参照すると、制御対象からの制御量PVnと目標値SVnから補償演算を行って得られる実効目標値SVn0との偏差が零となるようにPIまたはPID(P:比例,I:積分,D:微分)調節演算を行い、得られる調節演算信号を操作信号MVnとして前記制御対象に印加する調節装置において、制御量の目標値から実効目標値を得るために、比例ゲイン2自由度化係数α(α:0〜1間の定数)及び積分時間2自由度化係数β(β:1〜10間の定数)を用いた補償演算手段を設け、目標値から操作信号間の伝達関数Csv(s)がKp{α+[1/(TI・s)]・[(1+TI・s)/(1+βTI・s)]}とする2自由度PID調節装置、但し、Kp:比例ゲイン、TI:積分時間、s:ラプラス演算子であるものが記載されている(以下、従来技術1とする。)。

従来技術1によれば、PID制御の2自由度化のための積分動作の2自由度化を非常にシンプルな形とし、かつ、比例ゲインの2自由度化係数αと積分時間の2自由度化係数βの相互干渉を除去できる補償演算手段を設けたことにより、(1)積分動作の2自由度化が非常に簡単になり、かつ、分かり易い形に実現できる。(2)積分動作の2自由度化において比例ゲイン2自由度化係数αの関与を排除でき、調整が簡単になる。(3)さらに、積分動作の2自由度化係数βの関与を分母のみとし、シンプルで2自由度化係数βの調整時に直感的に把握可能となる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平07−072901号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来、遠心力・重力・クーロン摩擦などの外乱が顕著な場合には、入出力信号から状態変数を推定するオブザーバ(観測器)を用いてロバスト(堅牢)制御を行っていたものの、満足できるものではなかった。

このような従来のロバスト制御では、定常特性に関するパラメータであるゲインが固定であったため、突発的外乱の影響に対応できず、不具合発生が問題となっていたためであった。これは、従来技術1でも同等であった。

このため、実用的なインテリジェント(知能化)・ロバスト制御装置が強く望まれていた。

【0007】

本発明は、このような状況に鑑みてなされたものであり、上述の課題を解消することを課題とする。

【課題を解決するための手段】

【0008】

本発明の組み込み知能コントローラは、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラにおいて、ファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるフィードバック手段を備え、該フィードバック手段は、前記制御対象の非線形動特性のPD(比例、微分)補償を行うファジィPD手段と、前記制御対象の非線形動特性のPI(比例、積分)補償を行うファジィPI手段とを並列に備えることを特徴とする。

本発明の組み込み知能コントローラは、前記フィードバック手段は、ファジィ分割された空間において位置誤差に応じた可変フィードバックゲインを設定することを特徴とする。

本発明の組み込み知能コントローラは、制御系を2自由度制御構成とし、前記制御対象の変位、速度、及び加速度のパラメータをニューラルネットワークにより学習させ、前記制御対象の特性の逆特性を取得するフィードフォワード手段を備えることを特徴とする。

本発明の組み込み知能コントローラは、前記フィードフォワード手段又は前記フィードバック手段は、所定のサンプリング時間で実時間処理を行うことを特徴とする。

本発明の組み込み知能コントローラは、前記フィードフォワード手段又は前記フィードバック手段は、ソフトウェアPWM制御を行うことを特徴とする。

本発明の制御システムは、前記組み込み知能コントローラを含むことを特徴とする。

本発明の制御プログラムは、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラの制御プログラムにおいて、コンピュータをファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるフィードバック手段

として機能させるための制御プログラムであることを特徴とする。

本発明の記録媒体は、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラの制御プログラムの記録媒体において、コンピュータをファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるフィードバック手段として機能させるためのプログラムを記録したコンピュータ読み取り可能な記録媒体であることを特徴とする。

本発明の制御方法は、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する制御方法において、フィードバック手段により、ファジィ・ニューラルネットワークにより非線形誤差を減少させることを特徴とする。

【発明の効果】

【0009】

本発明によれば、ファジィ・ニューラルネットワークを用いることで、実用的な非線形動作特性をもつインテリジェント・ロバスト制御を実現する組み込み知能コントローラを提供することができる。

【図面の簡単な説明】

【0010】

【図1A】本発明の実施の形態に係る制御システムXの一例の外観図である。

【図1B】本発明の実施の形態に係る知能コントローラ部1のICS部10の外観図である。

【図2】本発明の実施の形態に係る制御システムXの制御構成を示すブロック図である。

【図3】本発明の実施の形態に係るICS部10の制御構成を示すブロック図である。

【図4】本発明の実施の形態に係る開発/学習処理に用いるICS部10の制御構成例を示すブロック図である。

【図5】本発明の実施の形態に係る開発/学習処理のフローチャートである。

【図6】本発明の実施の形態に係るモデル作成処理のフローチャートである。

【図7】本発明の実施の形態に係るFF−NN逆ダイナミックス処理に用いるICS部10の制御構成例を示すブロック図である。

【図8】本発明の実施の形態に係るFF−NN逆ダイナミックス処理のフローチャートである。

【図9A】本発明の実施の形態に係るFF−NN部120のニューラルネットワークの構成例を示す概念図である。

【図9B】本発明の実施の形態に係るFF−NN部120のニューラルネットワークのブロックを示す概念図である。

【図10】本発明の実施の形態に係るFB−FN学習処理に用いるICS部10の制御構成例を示すブロック図である。

【図11】本発明の実施の形態に係るFB−FN学習処理のフローチャートである。

【図12A】本発明の実施の形態に係るファジィ・ニューラルネットワークの構造を示す概念図である。

【図12B】本発明の実施の形態に係るファジィPD部131とファジィPI部132の全体構成を示す概念図である。

【図13】本発明の実施の形態に係るファジィPD部131とファジィPI部132の学習過程を示すブロック図である。

【図14】本発明の実施の形態に係る調整されたメンバーシップ関数の例を示す概念図である。

【図15】本発明の実施の形態に係るファジィPD部131及びファジィPI部132のファジィルールの設定方法を示す概念図である。

【図16A】本発明の実施の形態に係るFB−FN部130のファジィ・ニューラルネットワークゲインの計算方法を示す概念図である。

【図16B】本発明の実施の形態に係るFB−FN部130のゲインマトリックスを示す概念図である。

【図16C】本発明の実施の形態に係るFB−FN部130のファジィ・ニューラルネットワークによるゲインスケジューリングの概念を示すブロック図である。

【図16D】本発明の実施の形態に係るファジィPD部131のファジィPDゲインマトリックスを示す画面例である。

【図16E】本発明の実施の形態に係るファジィPD部131のファジィPD制御面を示す画面例である。

【図17】本発明の実施の形態に係るFB−FN部130のロバスト安定性について説明するための概念図である。

【図18】本発明の実施の形態に係るソフトウェアサーボ制御処理のPWM制御の概念図である。

【図19A】本発明の実施の形態の実施例に係る従来のPID制御のモデル図である。

【図19B】本発明の実施の形態の実施例に係るNN−PID制御のみの場合のモデル図である。

【図19C】本発明の実施の形態の実施例に係るファジィ・ニューラルネットワーク制御のモデル図である。

【図20A】本発明の実施の形態の実施例に係るPWM部150のモデル図である。

【図20B】本発明の実施の形態の実施例に係るPWM部150のSEIHUKIRIKAEブロックのモデル図である。

【図20C】本発明の実施の形態の実施例に係るPWM部150のSEIHUKIRIKAEブロックのPWM18−20ブロックのモデル図である。

【図20D】本発明の実施の形態の実施例に係る出力部170のモデル図である。

【図20E】本発明の実施の形態の実施例に係る入力部180のモデル図である。

【図20F】本発明の実施の形態の実施例に係るカウンタ部160のモデル図である。

【図20G】本発明の実施の形態の実施例に係るカウンタ部160のCOUNTERブロックのモデル図である。

【図20H】本発明の実施の形態の実施例に係るカウンタ部160のCOUNTERブロックのTriggered Subsystemのモデル図である。

【図21A】本発明の実施の形態に係る従来のPID制御のモデルを用いて制御の実験結果を示すグラフである。

【図21B】本発明の実施の形態の実施例に係るファジィ・ニューラルネットワーク制御の実験結果を示すグラフである。

【発明を実施するための形態】

【0011】

<実施の形態>

〔本発明の実施の形態に係る制御システムXの構成〕

まず、図1A〜図2を参照して、本発明の実施の形態に係る制御システムXの制御構成について説明する。

図1Aは、制御システムXを開発する際に用いる構成の一例の外観図である。本実施形態の制御システムXは、知能コントローラ部1が、テーブル移動装置である制御対象2と、図示しない制御装置3とに接続されている。

知能コントローラ部1は、インテリジェント・ロバスト制御に用いるICS部10(Intelligent Control System Module、組み込み知能コントローラ)を備えている制御部位である。図1Aの例では、知能コントローラ部1として、組み込みモジュールを接続できる開発用の組み込み型コンビュータを用いる例を示す。

また、制御対象2は、外乱の影響を受け、ロバスト制御が必要になる具体的な制御対象部位である。図1Aの例では、開発とシミュレーションに用いるテーブル移動装置を用いた例を示す。このテーブル移動装置は、モータドライバーやカウンタ等であるモータ駆動ドライバ20を備えている。モータ駆動ドライバ20は、駆動用のモータ230により、テーブル210を移動させ、その制御の応答を入力する。

図1Bは、ICS部10の外観図である。ICS部10は、組み込みコンピュータを用いたインテリジェント・ロバスト型組み込み知能コントローラであり、後述する学習後に、実際の制御対象の機器に装着してインテリジェント・ロバスト制御を行う。

【0012】

図2は、制御システムXの具体的な構成を示す制御ブロック図である。

制御システムXは、一例として、知能コントローラ部1と、制御対象2と、制御装置3とを含んでいる。

【0013】

知能コントローラ部1は、製品の製造時には、ロボット、自動車、自転車、航空機、ヒートポンプ等の制御が必要な各種機器そのものに、ICS部10を組み込んで用いる。ここでは、開発時の構成例として、例えば、システム開発ツールであり、主に実際の製品に搭載する前の開発段階で使用する組み込み型コンビュータを用いる例について説明する。この開発用の組み込み型コンビュータとしては、たとえば、エー・アンド・デイ社製のAD7011−EVAを用いることができる。また、知能コントローラ部1は、高速な制御手段を用いて、例えば、所定のサンプリング時間、例えば1ミリ秒〜数十ミリ秒程度にて、リアルタイム(実時間)処理を行うことができる。

制御対象2は、製品の製造時には、ロボット、自動車、自転車、航空機、ヒートポンプ等のモータやアクチュエータやヒータのように電磁的に駆動を調節する素子と、この素子の出力の状態を取得するセンサ等を含む。本実施形態では、一般的な外乱の起こる駆動系のシミュレーションを行う場合の構成として、駆動装置であるDC(直流)モータ駆動のテーブル移動装置を用いた構成の例について説明する。

制御装置3は、一般的なPC/AT互換機やMAC規格機のようなPC(Personal Computer)等を用いることができる。制御装置3は、Windows(登録商標)やLinux(登録商標)等のOS(Operating System)を用いて、制御用のソフトウェアをインストールして実行することができる。以下では、制御装置3のPCに、制御用ソフトウェアとしてMathWorks社製のMATLAB(登録商標)/Simlink(登録商標)をインストールしてファジィ/ニューラルネットを構築した例について説明するが、これに限られない。また、以下では、制御装置3において、エイ・アンド・デイ社のVCDesigner(商標)とModelDef(商標)ソフトウェアを用いてモデル定義とモデル実行画面の作成を行う例についても説明するが、これに限られず、各種のソフトウェアを用いて実現することができる。

【0014】

〈知能コントローラ部1の構成〉

より具体的に説明すると、知能コントローラ部1は、例えば、ICS部10、制御部11、補助記憶部14、主記憶部15、論理回路部16、I/F部17、及びコネクタ18と19を含んで構成される。

ICS部10は、EEPROM(Electrically Erasable Programmable Read−Only Memory)やNOR/NANDフラッシュメモリやSRAM(Static Random Access Memory)等を内蔵したiCS(intelligent Control System)モジュールである。ICS部10は、制御装置3で作成された制御部11のC言語等のプログラム(実行コード)であるバイナリファイル、各種モデルやパラメータに関する定義ファイルやデータ、FPGA(Field Programmable Gate Array)の論理回路データ、知能コントローラ部1のファームウェアやBIOS(Basic Input/Output System)等を記憶している記憶媒体(記録媒体)も備える。後述する開発/学習処理では、このプログラムやデータが制御部11により読み出されて実行される。また、ICS部10は、図1Aの外観図のように、それ自体が制御演算手段を備えたシングルボードコンピュータとして構成されていてもよい。

制御部11は、RISC(Reduced Instruction Set Computer、縮小命令セットコンピュータ)方式やCISC方式等の高速演算処理が可能なCPU(Central Processing Unit、中央処理装置、中央演算装置)、MPU(Micro Processing Unit)、DSP(Digital Signal Processor)、ASIC(Application Specific Processor、特定用途向けプロセッサー)等である演算・制御能力を備えた制御手段である。

補助記憶部14は、主にOS用の記憶媒体(記録媒体)として、SSD(Solid State Drive)やコンパクトフラッシュ(登録商標)ディスクやSDメモリカードやmicroSDメモリカード等のフラッシュメモリディスク、HDD(Hard Disk Drive)、磁気テープ媒体、光ディスク媒体等を備えた補助記憶手段である。補助記憶部14に記憶されたOSとしては、カーネルに組み込んで使用するリアルタイムモジュールであるXenomai拡張を用いたLinux(登録商標)や、ITRON等のリアルタイム処理が可能なOSを用いることが好適である。

主記憶部15は、主に制御/演算用の記憶媒体(記録媒体)として、SDRAM(Synchronous Dynamic Random Access Memory)やDDR(Double−Data−Rate)、DDR2、DDR3、LPDDR3、WideIO、XDR(extreme data rate)等の主記憶用に使われる高速な記憶手段を含んで構成される主記憶手段である。主記憶部15は、ICS部10の各プログラムやデータ、制御対象2から取得したセンサのデータ等を記憶する。

論理回路部16は、CPLD(Complex Programmable Logic Device)やFPGA等の論理回路及び各種アナログ回路等である。論理回路部16は、制御対象2とのインターフェイスの回路やA/D(analog−to−digital)コンバータやD/A(digital−to−analog)コンバータ等も含んで構成される。

I/F部17は、USB(Universal Serial Bus)、無線USB、シリアル、パラレル、LAN(Local Area Network)等のインターフェイスである。I/F部17は、主に制御装置3からプログラムやバイナリファイルやデータ等を転送し、制御結果等のデータを制御装置3に転送するために用いる。

コネクタ18は、主に制御装置3に接続するためのコネクタ等である。コネクタ18は、例えば、制御装置3と、LANクロスケーブルで接続できる。また、コネクタ18には、タッチパネルディスプレイ等の表示部/入力部やスピーカやマイクロフォン等を別途接続してもよい。

コネクタ19は、主に制御対象2に接続するためのコネクタであり、別途駆動用のアンプやセンサ等と接続してもよい。

【0015】

〈制御対象2の構成〉

また、制御対象2は、モータ駆動ドライバ20と、テーブル部21とを含んでいる。

モータ駆動ドライバ20は、一般的なDCモータを駆動するためのドライバIC(Integrated Circuit)を用いることができる。このドライバICは、知能コントローラ部1からの制御信号によりテーブル部21のモータ230を駆動する。また、モータ駆動ドライバ20は、エンコーダ220からの出力を取得して、知能コントローラ部1に送信する。

テーブル部21は、DCモータによって駆動する移動テーブルの例である。テーブル部21は、移動テーブル(ステージ)であるテーブル210と、テーブル210を駆動するDCモータ等のモータ230と、テーブル210の位置等を検知するエンコーダ220とを含んで構成される。

【0016】

(ICS部10の構成)

次に、図3を参照して、ICS部10の詳細な制御構成について説明する。

ICS部10は、主にPID部110、FF−NN部120(フィードフォワード手段)、FB−FN部130(フィードバック手段)、差分部140、PWM部150、カウンタ部160、出力部170、入力部180、制御信号発生部190、外乱シミュレート部195を含んで構成される。ICS部10は、これらの構成部位を組み合わせて、各処理における各種演算を行う。

【0017】

PID部110は、古典的なPID制御を行うためのモデルのプログラムとデータを含む部位である。

このPID部110は、フィードバック制御におけるPD(比例、微分)補償を行うためのPD補償器部111を備えている。PD補償器部111は、制御対象2の特性を把握するために用いる。

【0018】

FF−NN部120は、FF−NN(Feedforward neural network)補償器のモデルのプログラムとデータを含む部位である。FF−NN部120は、制御対象の位相遅れを改善するために、ニューラルネットワークによりサーボ系逆ダイナミックス特性を学習して用いる。

この学習について、FF−NN部120は、オフラインでPD補償器部111のPD制御系の逆ダイナミックス特性をBP(Backpropagation、誤差逆伝播)法により学習する。

FF−NN部120としては、例えば、例えば、図9Aで示すような、3層、3入力、4中間ユニット、1出力のニューラルネットワークを用いることができる。ここで、入力層(Input Layer)には、変位r、速度s(dr/dt)、加速度s2(d2r/dt2)をそれぞれ入力する。また、FF−NN部120のニューラルネットワークの出力値は操作量UNNである。

このFF−NN部120の学習方法の詳細については後述する。

【0019】

FB−FN部130は、FB−FN(Fuzzy neural network Based Feedforword Nonlinear error、ファジィ・ニューラルネットワークによる非線形偏差補償)補償器のモデルのプログラムとデータを含む部位である。

FB−FN部130は、制御対象2の非線形動特性の補償のために、ファジィ・ニューラルネットワークベースにより、目標信号r(t)と出力信号y(t)との偏差信号e(t)=r(t)−y(t)の二乗が最小となるようにオフラインで学習する。これらの学習後に、制御システムXを始めとする機器に組み込んで制御に使用することができる。このFB−FN部130は、ゲインスケジューリングにより出力の補償を行う。

【0020】

また、FB−FN部130は、ファジィPD部131(ファジィPD手段)とファジィPI部132(ファジィPI手段)を主に備えている。

ファジィPD部131は、ファジィ・ニューラルネットワークを用いて、PD補償を行う部位である。また、ファジィPI部132は、ファジィPI部131と同様のファジィ・ニューラルネットワークを用いて、PI(比例、積分)補償を行う部位である。

ファジィPD部131及びファジィPI部132は、それぞれ、例えば、図12Aで示すような、2入力4層1出力のファジィ・ニューラルネットワークを用いることができる。ファジィPD部131及びファジィPI部132とも、入力層には、それぞれ、位置誤差となる変位誤差信号epと、速度誤差となる変位時間微分の速度誤差信号evを入力信号として入力する。この上で、ファジィPD部131は、PID部110のPD補償の操作量UPDの2乗を評価関数として、BP法で結合加重を修正する。また、ファジィPI部132は、PID部110のPI補償の操作量UPIの2乗を評価関数として、BP法で結合加重を修正する。ファジィPD部131は、それぞれの入力の総和を操作量UFN-PDとして出力する。また、ファジィPI部132は、操作量UFN-PIを出力する。

このファジィPD部131及びファジィPI部132のファジィ・ニューラルネットワークの学習方法の詳細については後述する。

【0021】

差分部140は、従来の古典PD補償器であるPD補償器部111の操作信号(指令信号)の変位r、速度s(dr/dt)、加速度s2(d2r/dt2)を算出するプログラムとデータを含む部位である。差分部140は、速度sを算出する速度算出部141と、加速度s2を算出する加速度算出部142を含んでいる。また、差分部140は、変位誤差信号epと、速度誤差信号evを算出することもできる。

PWM部150は、DCモータ駆動用のソフトウェアPWM(Pulse Width Modulation、パルス幅変調)モジュールのプログラムとデータを含む部位である。このPWM部150の出力信号により、モータ駆動ドライバ20に接続されたモータ230をPWM制御することができる。

カウンタ部160は、エンコーダのカウンタのためのモジュールのプログラムとデータを含む部位である。このカウンタ部160により算出された値を用いて、差分部140が変位r、速度s、加速度s2、変位誤差信号epと、速度誤差信号evを求めることができる。

出力部170は、PWM部150からの出力をモータ駆動ドライバ20に伝えるための切り換え等を行う部位である。

入力部180は、モータ駆動ドライバ20を介して入力したエンコーダ220の信号等である制御対象2からの信号を入力し、カウンタ部160に送信する部位である。

制御信号発生部190は、図示しない外部機器からの指示信号を取得し、制御対象2を制御するための制御信号を出力するモジュールのプログラムとデータを含む部位である。制御信号発生部190は、制御のシミュレーション用に、例えばサイン波等の信号を出力することもできる。

外乱シミュレート部195は、外乱となる摩擦やガタ等による信号をシミュレートするための信号発生器等の部位である。外乱シミュレート部195は、所定出力のランダム信号等を出力可能である。

【0022】

〔制御システムXのICS部10の開発/学習処理〕

次に、図4と図5を参照して、制御システムXにおいて、ICS部10を学習させ、制御対象2の制御に最適化するための開発/学習処理について説明する。

図4は、この制御処理における主な構成部位と信号の流れを示すブロック図である。

本発明の実施の形態に係る制御システムXは、従来の制御システムの問題の解決のため、ファジィ・ニューラルネットワーク(FNN)ベースの制御を行う。ここで、ファジィとは複雑なシステムをヒトのように「暖昧」にとらえることができif−then型のファジィルールにより言語的に記述できるという特徴を持つ。一方、ニューラルネットワークの特徴は学習により入出力の関係を同定できることである。

本発明の実施の形態に係る制御処理においては、制御装置3により、主に、図4のICS部10のFF−NN部120、FB−FN部130、及び差分部140のモデルを作成して開発を行う。この上で、各部位のプログラム等を知能コントローラ部1の制御部100が実行して、制御対象2のフィードバック制御のための学習をさせ、実際の制御システムを構成する。この制御システムは、例えば、ソフトウェアサーボのPWM制御により制御対象2を駆動することができる。

【0023】

より具体的には、本発明の実施の形態に係るファジィ・ニューラルネットワークを用いたロバスト・ゲインスケジューリング制御系は、ニューラルネットワークによりサーボ系逆ダイナミックス特性を学習しているフィードフォワード補償を行うFF−NN部120、及びファジィ・ニューラルネットワークによるゲインスケジューリングを行うFB−FN部130の2つの補償要素から構成される。この制御系は、目標値応答特性と閉ループ特性が独立設計できる2自由度制御系とし、目標入力に対する追従および、外乱の影響の除去を実現することができる。モデル化誤差及び断続する外乱等による定常偏差の減少、メカトロ位置改善のために、FF−NN部120ではオフラインで従来の固定PD制御系の逆ダイナミックス特性を学習する。つぎに、非線形動特性の補償のために、FB−FN部130は、目標信号r(t)と出力信号y(t)との偏差信号e(t)=r(t)−y(t)の二乗が最小となるようにオフラインやオンラインで学習する。これらの学習後に提案する制御システムが構成される。

以下で、図5のフローチャートを参照して、この開発/学習処理の詳細について説明する。

【0024】

(ステップS101)

まず、制御装置3により、ICS部10の各部に対応するモデルをMATLAB/Simulink、Model Def、VCDesigner等のソフトウェアを用いて作成する。

制御装置3は、この作成したモデルをコンパイル等してプログラムのバイナリファイルに変換し、ICS部10に転送する。このバイナリファイルは、実際にバイナリファイルを実行する定義ファイルや各種データと共にICS部10の補助記憶手段に記憶される。

ICS部10に記憶されたプログラム等は、知能コントローラ部1の制御部11が単独で実行して、下記の学習処理等を行うことができる。

【0025】

(ステップS102)

次に、ICS部10の制御部11は、FF−NN部120を用いて、FF−NN逆ダイナミックス処理を行う。

この処理においては、制御対象2の非線形特性に対する逆ダイナミックスを獲得し、システム特性を線形化するための学習を行う。

ここで、制御対象の位相遅れを改善するために、FF−NN部120は、オフラインでPD補償器部111(図3)のPD制御系の逆ダイナミックス特性をBP法により学習する。

FF−NN部120による制御では、位相の遅れに対しての改善が期待できる。

【0026】

(ステップS103)

次に、ICS部10の制御部11は、FB−FN部130を用いてFB−FN学習処理を行う。

ここで、上述のFF−NN部120の制御だけでは、制御対象2のモータ230の軌道等の目標になる信号(目標軌道信号)に対し、非線形誤差が発生する。これは入力補償としてNNが制御対象の非線形特性の一部のみの補償に限定されるためである。

このため、本ステップにおいて、FB−FN部130を用いた非線形動特性の補償のための学習を行う。

FB−FN部130は、上述したように、差分部140から取得した目標信号r(t)と出力信号y(t)との偏差信号e(t)=r(t)−y(t)の二乗が最小となるように学習する。この学習は、制御中であるオンライン状態又は制御後のデータを用いたオフライン状態で実行可能である。

これらの学習後に制御システムXが構成される。

【0027】

このように、FF−NN部120とFB−FN部130とを用いて学習することで、制御における追従性の向上及び誤差低減を達成することができる。

よって、様々な制御系に対応する汎化能力をもたせることができ、知能化制御を実現することができる。

【0028】

(ステップS104)

また、ICS部10の制御部11は、PWM部150を用いて、ソフトウェアサーボ制御処理を行うことができる。

具体的には、上述の各学習時、及び学習後に構成された制御システムXにおいて、ICS部10の制御部11は、ソフトウェアサーボの処理を行い、実際の制御対象2を制御することが可能である。

以上により、開発/学習処理を終了する。

【0029】

〈モデル作成処理の詳細〉

ここで、図6のフローチャートを参照して、モデルの作成と知能コントローラ部1のICS部10への転送をするモデル作成処理の詳細について説明する。

【0030】

(ステップS111)

まず、制御装置3は、ユーザの指示を検知し、モデル作成処理を行う。具体的には、MATLAB/Simulinkソフトウェアにより制御システムブロック図を作成する。

より具体的に説明すると、MATLAB/Simulinkは、制御系設計支援ソフトウェアである。ここで、MATLABは、MATrix LABoratoryを略したものであり、行列・ベクトル演算に基づく数値解析ソフトウェアである。MATLABは、インタプリタ(対話)形式の高級フログラミング言語であり、BASIC言語に類似したMATLAB言語で記載された「Mファイル」が用いられる。MATLABは、制御ツールボックス、通信ツールボックスを始めとして、豊富なツールボックスを備えておりユーザが解析に利用できる。また、ブロック線図入力により制御系のシミュレータを構築できるSimulinkが準備されている。MATLAB/Simulinkにより設計されたコントローラを組み込みCPUにより実装するためのRealTime Workshopも製品化されているため、本実施形態で好適に利用できる。

Simulinkはアナログ計算機の機能をデジタル環境で実行させるソフトウェアであり、微分方程式の解析に便利なツールである。

【0031】

また、知能制御用ソフトウェアとして、Neural Network Toolbox、Fuzzy Logic Toolboxを適宜MATLAB/SIMULINKと合わせて用いることができる。

Neural Network Toolboxは、非線形システムに対し、パターン認識や同定、制御等で利用できるようなニューラルネットワークシステムの設計やシミュレーションに必要なMファイル群である。Neural Network Toolboxは、初期化、伝達関数、教師付ネットワーク/学習ルール、パーセプトロン、バックプロパゲーション(BP)、Levenberg−Marquardtバックプロパゲーション、Radial basisネットワーク、リカレントネットワーク(Elman,Hopfield)等に対応している。

Fuzzy Logic Toolboxは、ファジィ推論システムの作成、編集ができるプログラムである。Fuzzy Logic Toolboxは、ファジィ推論システムをグラフイカルツールまたはコマンド関数を使って簡単に作ることができる。SIMULINKを併用すれば、ブロック線図シミュレーション環境の中でファジィシステムをテストすることができる。また、Fuzzy Logic Toolboxは、Real−Time Workshopを使用できる環境ならば、SIMULINKの環境からリアルタイムまたはノンリアルタイムコードのいずれかを生成できる。

【0032】

作成されたモデルは、例えば、後述する実施例で示す図19A〜図20Cのようなものとなる。

【0033】

(ステップS112)

次に、制御装置3は、ユーザの指示を検知し、Cコード作成/コンパイル処理を行う。

この処理においては、MATLABのReal−Time Workshopによって作成したモデルから、例えばC言語で記載されたCコードやオブジェクトコードや実行コードを自動生成させる。

【0034】

(ステップS113)

次に、制御装置3は、ユーザの指示を検知し、モデル定義/ビルド処理を行う。

ここでは、ModelDefというソフトを使用し、モデルのパラメータや信号の定義を行う。

このモデル定義を行うことで、MATLAB/Simulinkで作成したモデル上のパラメータや信号を実行時に使用可能にする定義ファイルを作成することができる。

【0035】

(ステップS114)

次に、制御装置3は、ユーザの指示を検知し、VC(Virtual Console)画面作成処理を行う。

この処理においては、VCDesignerソフトウェアを用いて画面作成を行う。具体的には、制御装置3のPCの表示装置と、知能コントローラ部1の表示部に表示されるユーザインタフェイスとなる「VC画面」を作成できる。

また、VCDesignerでは、作成したモデルを実行するVC画面の設計ができる。

これにより、作成したモデルを実行するときに、ユーザが扱いやすいような画面の設計を行うことができる。

【0036】

(ステップS115)

次に、制御装置3は、ユーザの指示を検知し、実行コード転送処理を行う。

具体的に説明すると、制御装置3は、VCDesignerにより、プログラムを実行できる。ユーザは、制御装置3のエミュレータ等で実行テストを行った後で、実行コードのバイナリファイルや定義ファイルや各種データ等(以下、プログラム等という。)を転送する。

なお、制御装置3は、VCDesigner起勤時に制御装置3と知能コントローラ部1とが接続状態になっていれば、生成された実行コード等を自動的に転送することもできる。

【0037】

(ステップS116)

次に、知能コントローラ部1は、実行コード取得/実行処理を行う。

ここでは、知能コントローラ部1の制御部11が、上述の制御装置3から取得したプログラム等をICS部10の補助記憶手段に記憶する。

この実行コードを取得後に、実行コード等を知能コントローラ部1側単体で実行が可能となる。

【0038】

作成したプログラム等を実行するときも、VCDesignerを用いることができる。

具体的には、ユーザは、制御装置3と知能コントローラ部1が接続状態で、画面作成が終わったら、VCDesignerの実行ボタンを押下する。この実行ボタンを押下により、設計した画面が制御装置3と知能コントローラ部1の表示部上に描画され、実行可能となる。

なお、この実行においては、ステップ実行や、制御対象2からのデータの取得等を行うこともできる。知能コントローラ部1は、逐次、制御装置3に取得したデータ等を送信することもできる。また、所定時間後に、取得したデータを送信することもできる。

【0039】

(ステップS117)

次に、制御装置3は、制御結果取得分析処理を行う。

具体的には、制御装置3は、取得したデータやモデルの状態等を、MATLAB/Simulink、VCDesigner、又は解析用のソフトウェアで確認することができる。これにより、モデルの動作を確認し、下記で説明する学習処理を行うことが可能になる。

なお、VCDesignerを用いて実行している際には、ユーザは、知能コントローラ部1の画面のボタンでは指示ができず、制御装置3のユーザインタフェイスの画面で指示を行う。制御装置3で実行テストを行ったあとで、知能コントローラ部1単体で実行が可能となる。

以上により、モデル作成処理を終了する。

【0040】

〈FF−NN逆ダイナミックス処理の詳細〉

次に、図7〜図9Bを参照して、FF−NN逆ダイナミックス処理の詳細について説明する。この処理では、古典的なPD制御の結果の信号を用いて、フィードフォワードによる、FF−NN部120の学習を行う。

図7は、このFF−NN逆ダイナミックス処理に用いるICS部10の各部と制御対象との関係を示すブロック図である。このように、制御対象の動特性を改善するため、ニューラルネットワークであるFF−NN部120を用いる。FF−NN部120のニューラルネットワークは、サーボ系である制御対象2の逆ダイナミックスをオンライン又はオフラインで学習し、それをフィードフォワード補償器として利用する。

以下で、図8のフローチャートを基に、このFF−NN逆ダイナミックス処理の詳細をステップ毎に説明する。

【0041】

(ステップS201)

まず、知能コントローラ部1の制御部11は、ICS部10のPD補償器部111等を用いて、FF−NN用意処理を行う。

ここでは、図7のブロック図に示したように、従来の古典PD補償器であるPD補償器部111により、制御対象2の特性を把握する試験を行い、指令信号の変位(y)、速度(dy/dx)、加速度(d2y/dt2)の各信号を取得する。この取得においては、差分部140の速度算出部141により速度を、加速度算出部142により加速度を算出する。また、この試験は、摩擦、ガタ等の非線形特性が、この動作により含まれることが重要点である。

また、このPD制御の際のPDゲインは制御対象2が移動可能な小さい値とする。

なお、速度、加速度信号は、変位信号収得後、オフラインにて差分部140が数値演算処理により算出してもよい。

【0042】

(ステップS202)

次に、制御部11は、FF−NN部120を用いてFF−NN学習処理を行う。

ここで、まず、位置と速度フィードバック則を適用したプラントの動特性は非線形特性を2次系として近似し線形化すると、以下の式(1)にて表現できる。

【0043】

【数1】

【0044】

ここで、u(t)は入力、y(t)は位置、kp,kvは、それぞれ、位置と速度のフィードバックゲインである。ただしkvについては、サーボモータの逆起電力定数keが含まれているものとする。サーボ系の逆ダイナミックスは、r(t)を目標軌道とすると、上述の式(1)をy(t)=r(t)として逆に解くことにより、以下の式(2)となる。

【0045】

【数2】

【0046】

つまり、変位r(k)、速度dr/dt(k)、加速度d2r/dt2(k)からu(t)の関係をFF−NN部120のニューラルネットワークに学習させる。したがって、ネットワークへの入力I(k)を[3*1]の列ベクトルとし、下記の式で表せる:

I(k)=[r(k),kp/kv・dr/dt(k),J/kp・d2r/dt2(k)]T

各ユニットの入出力関係は線形関数f(x)=xを用いる。また、ネットワークの出力はプラントの入力の推定値φkとなる。

中間層の出力をψi(k)とすると、ニューラルネットワークの出力は、次の式(3)のように表せる。

【0047】

【数3】

【0048】

ただし、nは中間層のユニット数、mは入力層のユニット数である。

ニューラルネットワークの学習は、評価関数として、以下の式(4)を定義し、バックプロパゲーション(BP)法により行う。

【0049】

【数4】

【0050】

すなわち、式(4)は、FF−NN部120のニューラルネットワークから計算されるプラント入力の推定値から、制御対象2であるプラントからの信号の入力を引いて2乗して1/2で割ることで求める。

【0051】

〔FF−NN部120のニューラルネットワークの構成例〕

次に、図9Aを参照して、FF−NN補償器であるFF−NN部120のニューラルネットワークの構成例について説明する。FF−NN部120では、3層3入力4中間ユニット1出力のニューラルネットワークを用いた。

入力信号は変位r、速度dr/dt、加速度d2r/dt2の信号である。これにより、プラントの動特性を2次系として近似し、線形化する。

具体的には、FF−NN部120入力として、NN学習処理で収得した変位、速度、加速度のデータを入力することができる。データは所定量、例えば1秒間に100程度とする。この場合、サンプリング周波数は10msecである。

【0052】

FF−NN部120のニューラルネットワークの学習に必要なソフトウェアとしては、以下に示すMATLAB用のニューラルネットワーク生成コマンドの例を入力して用いることができる。

【0053】

P=[変位;

速度;

加速度];

T=[教師信号];

net=newff([-5 5 ; -5 5 ;-5 5],[3 1],{'tansig','purelin'},'trainlm');

y=sim(net,P);

plot(P,T,P,y,'o');

net.trainParam.show=10;

net.trainParam.epochs=20000;

net.trainParam.goal=(0.0037^2);

net=train(net,P,T);

y=sim(net,P);

plot(P,T,P,y,'o');

gensim(net,-1);

return

【0054】

ここで、P=変位、速度、加速度、T=教師信号である。

ただし、教師信号は操作信号yとし、特性把握に必要な時間(3周期程度)とする。

【0055】

図9Bを参照して説明すると、MATLABによりニューラルネットワークの学習が終了すると、ニューラルネットワーク(NN)のブロックが生成される。

このNNのブロックを制御ブロックとして、FF−NN部120に用いる。

以上により、FF−NN逆ダイナミックス処理を終了する。

【0056】

〈FB−FN学習処理の詳細〉

次に、図10〜図17を参照して、FB−FN学習処理の詳細について説明する。

図10は、FB−FN学習処理に対応するICS部10の各部の関係を示すブロック図である。

具体的には、FB−FN部130は、ファジィ・ニューラルネットワークにより、ファジィPDとファジィPIの制御を行う。

ファジィ・ニューラルネットワークは、ニューロの学習能力とファジィの推論能力とを相補的に組み合わせて、それぞれの長所を生かし短所を補うよう融合したものである。

本実施形態のFB−FN部130は、非線形摩擦により変化および速度の制御誤差が生じた場合、制御ゲインを適応調整するファジィ・ニューラルネットワークによる非線形偏差補償特性により、制御誤差を減少させる特徴がある。

ここで、制御対象2の実際のモデルには、製品ごとに慣性モーメント等の値がバラツキ、2次モデルで表現できない非線形要素が存在する。すなわち、制御対象2の制御においては、目標軌道信号に対して制御対象の非線形摩擦誤差が発生する。

そこで、モデル化誤差、摩擦、未知な外乱等により生じる偏差信号を適応的に減少させる作用が働くように、ファジィPIDコントローラであるFB−FN部130によりフィードバック補償を行う。このため、FB−FN補償器であるFB−FN部130を、取得したデータを用いて学習させ、非線形誤差信号を減少させる。

このようにFB−FN部130を学習させることで、軌道誤差やモデル誤差による偏差を、ファジィPIDによるフィードバックによって押さえられる。これにより、知能化とロバスト性を兼ね備える、インテリジェント・ロバスト制御システム(IRCS)を実現できる。

以下で、図11のフローチャートを参照して、このFB−FN学習処理の各ステップの詳細について説明する。

【0057】

(ステップS301)

まず、知能コントローラ部1の制御部11は、ICS部10のFB−FN部130のファジィ・ニューラルネットワーク設定処理を行う。

ここで、図12A〜図12Dを参照して、ファジィPD部131とファジィPI部132に共通に使われる、本発明の実施の形態に係るファジィ・ニューラルネットワーク(FNN)の構成について説明する。

ファジィ・ニューラルネットワークは、BP法による学習を可能としながら、階層型ニューラルネットワークの結合を工夫してファジィ推論ルールとの対応関係を持たせ、ニューラルネットワークの獲得した入出力関係に関するパターンの知識をファジィルールというシンボルの知識として把握することができる。また、ファジィ推論システムにおける問題点であるファジィルールの同定、メンバーシップ関数の調整の困難さを、ニューラルネットワークの学習機能により改善できる。

【0058】

まず、Fuzzy Logic Toolboxによるファジィ・ニューラルネットワークの作成方法について説明する。

まずは、Fuzzy Logic Toolboxのメニューを呼び出す。メニューには:

1) メンバーシップ関数エディタ

2) FISエディタ

3) ルールエディタ

4) ルールビューワ

5) サーフェスビューワ

が存在する。

ここで、本実施形態におけるファジィ・ニューラルネットワークを用いたファジィ推論システムにおいては、まずはFISエディタを選択してモデルを作成する。

その際に、

a) tipperと入力するとウィンドウが表示される。

b) メンバーシップ関数エディタを使用し、メンバーシップ関数の名前、位置、型を設定する。

・Range [0 10]

また、ガウス曲線を設定する。

Gauss2mf

2つのガウス曲線の組み合わせによるメンバーシップ関数の作成を行う。

たとえば、以下の式(5)を用いることができる。

【0059】

【数5】

【0060】

このようにして、本実施形態に係るファジィ推論システムが作成できる。

【0061】

〔ファジィ・ニューラルネットワークの構造、構成例〕

図12Aは、本発明の実施の形態に係るファジィ・ニューラルネットワークの構造を示す。

この図12Aの例では、(A)層の入力層は、変位誤差信号epと変位時間微分の速度誤差信号evを入力信号としており、この入力信号を次層のユニットに分配している。

次に、(B)層の中間層では、メンバーシップ関数を内部関数に持ちガウス関数を用いる。各ユニットの出力はメンバーシップ関数の値であり、前件部と呼ぶ。

(C)層はファジィルールで推論する後件部であり、(B)層で入力空間を9分割し、分割された空間の適合度をファジィルールの前件部適合度の式により計算し、(C)層の全ユニットで得られる前件部適合度の総和で規格した値μiを出力する。

(D)層は入力の総和を出力する線形ユニットである。

以上により、ファジィルール的構造を持つニューラルネットが構成でき、これをファジィ・ニューラルネットワークと称する。このファジィ・ニューラルネットワークはBP法による学習を可能としながら、階層型ニューラルネットワークの結合を工夫して、ファジィ推論ルールとの対応関係を持たせることができる。

【0062】

図12Bは、本発明の実施の形態に係るファジィPD部131とファジィPI部132の全体構成を示す概念図である。

このように、ファジィPD部131とファジィPI部132とをパラレルに組み合わせることにより、全体としてファジィPIDを実現することができる。

【0063】

(ステップS302)

次に、制御部11は、ICS部10のFB−FN部130のFNN学習処理を行う。

図13は、FB−FN部130のファジィPD部131とファジィPI部132の学習過程を表わすブロック図である。

ファジィ・ニューラルネットワークの学習は、上述のPD補償器部111によるPD制御の特性把握試験のデータを基にして、変位誤差、速度誤差を入力とする。この上で、PIDの操作量を求めて、これを教師信号として、BP法と最小二乗法を組み合わせた方法でファジィPD部131とファジィPI部132の学習を行う。

FB−FN部130のニューラルネットワークでは、フィードバックゲインの学習を位置誤差の2乗:

Ep =1/2ep2

が最小となるように行う。また、kij≧0(j=I,p,v)の条件を常に満たすように、kij=Wijとする。

より具体的に説明すると、学習に利用する入力データは、サーボ系がスムーズに動作するようにゲイン調整した線形PD制御および線形PI制御の位置誤差epとその変化分であるevとし、教師データは線形PD制御及び線形PI制御の出力信号Uとする。また、大きな誤差(ステップ)の学習については、方形波のステップ信号を入力データとし、教師データは上記同様の線形PD制御および線形PI制御の出力信号Uとする。

【0064】

ここで、図13を参照して、ファジィPD部131のファジィPD学習について説明する。

ファジィPD部131のファジィPD学習は、モデル化誤差、非線形摩擦を補償するための学習の根拠となる。すなわち、制御対象2の実際のモデルには、慣性モーメント等のバラツキ、2次モデルで表現できない非線形要素が存在するため、これを学習する。

これらのモデル化誤差、非線形摩擦の誤差を表わすと、以下の式になる:

e = Td + fd(y)

ここで、Tdは、未知の外乱としてモデル化誤差を含める。

fd(y)はsgn(y’){(Fs−Fc)exp(−|y’|/e)+Fc}とする。

ファジィPD学習は、上述の式で示されるモデル化誤差及び非線形摩擦誤差の偏差出力信号をフィードバックPD出力信号として獲得した教師信号により逆ダイナミックスとして学習する。

学習方法は非線形誤差学習方式としてuPDの2乗であるE(uPD)=l/2uPD2を評価関数とし、BP法で結合荷重を修正する。

【0065】

ここで、図13を更に参照して、ファジィPI部132のファジィPI学習について説明する。

ファジィPI部132のファジィPI学習は、クーロン摩擦、未知外乱による定常偏差の学習の根拠となる。つまり、制御対象2では、クーロン摩擦により定常偏差が生じる。これは、加速度が0のときの位置偏差である。また、未知外乱による定常偏差も発生する。

これらの誤差を表わすと、以下の式になる:

e = eFC + eTd

ここで、eFCはクーロン摩擦により発生する定常偏差eTdは未知外乱により発生する定常偏差である。ファジィPI学習は、上記の式で示されるクーロン摩擦および未知外乱による定常偏差を、フィードバックPI出力信号として獲得した教師信号により逆ダイナミックスとして学習する。

非線形誤差学習の方式としては、式としてuPIの2乗であるE(uPI)=1/2uPI 2を評価関数として、BP法で結合荷重を修正する。

【0066】

(ステップS303)

次に、制御部11は、ICS部10のFB−FN部130のメンバーシップ関数設定処理を行う。

図14を参照して、このメンバーシップ関数設定処理の説明をする。

上述したように、ファジィPD部131、ファジィPI部132における、ファジィ・ニューラルネットワークの前件部には、メンバーシップ関数を用いる。本実施の形態においては、このメンバーシップ関数に、ここではガウス関数を使用する。

上述のFNN学習処理による学習結果、メンバーシップ関数の形が決定されることにより、パラメータが自動調整される。

図14及び図12Aの下部は、この調整されたメンバーシップ関数の例である。

【0067】

(ステップS304)

次に、制御部11は、ICS部10のFB−FN部130に対して、ファジィルール設定処理を行う。

図15は、ファジィPD部131及びファジィPI部132のファジィルールの設定方法を示す概念図である。

本発明の実施の形態に係るファジィ・ニューラルネットワークでは、制御ゲインを適応調整するため、誤差入力量に対応して出力を調整するファジィルールを設定する。

つまり、FB−FN部130のゲインをマトリックス状に配置するために、ファジィPD部131、ファジィPI部132における後件部に以下に示すファジィルールを設定する。

【0068】

より詳細に説明すると、図12Bにおける出力UFNは、プラントの直接的な入力である。ファジィ部では、入力空間を9分割し、分割された空間の適合度を以下の式で与える。

μi=Ai1(ep)Ai2(ev)

ここで、i=1,2,…,9, i1,i2=1,2,3

また、Aijはメンバーシップ関数でファジィ変数を表す。

また、Ai1,Ai2はそれぞれPositive big、Small、Negative bigに対する適合度を表す。

ただし、適合度は、下記の式(6)のように正規化しておく。

【0069】

【数6】

【0070】

そして、制御ゲインを適応調整するため、誤差入力量に対応して出力を調整するファジィルールを設定する。

ここで、図12Cのように、ファジィ分割として9を設定し、ファジィルールは以下のように設定する。

i番目のファジィルールは:

Ri: IF ep is Ai1 and ev is Ai2 THEN y=fi(ep,ev)

ここで、i=1,2, ... ,9, i1,i2=1,2,3

である。

また、uFN-PD出力は、下記の式(7)として求める。

【0071】

【数7】

【0072】

ここで、各uFNの加算出力であるuFN-PID出力は、下記の式(8)で求める。

【0073】

【数8】

【0074】

また、ファジィ推論は、下記の式(9)で求める。

【0075】

【数9】

【0076】

ここで、fは、uFN-PIDとuFNが等しいとすると、下記の式(10)となる。

【0077】

【数10】

【0078】

ただし、kij≧0(j=I,p,v)は、後述するフィードバックゲインである。

ここで、式(10)の制御方法においては、誤差応答によりファジィPDとファジィPIを切り換える動作を行う。この際、外乱やパラメータ変動による制御系の影響に対し、応答を速やかに目標値に近づけるため、図15内の表で示すように、外乱やパラメータ変動による制御系の影響に対し、応答を速やかに目標値に近づけるために図15に示すように、変位誤差信号epと速度誤差信号evがいずれもSmallのときはPID制御、epがSmallでなくevの絶対値|ev|がbigのときは、ダンピングを小さくし速い応答を得るためにP制御、その他はPD制御とすることが好適である。

各フィードバックは、後段のニューラルネットワークで事前に学習することにより、制御則を構成する。各フィードバックゲインは後段のニューラルネットワークで事前に学習する。このような構成により制御則を構成する。つまり、誤差に適応した制御則を構成することができる。

図16Aは、このフィードバックであるファジィ・ニューラルネットワークゲインの計算方法を示す。

【0079】

また、図16Bに、FB−FN部130のゲインマトリックスを示す。

フィードバックゲインkijはファジィ分割された誤差空間ごとに学習するので、誤差量に依存するダイナミック補償器としての役割を果たす。このように、制御ゲインを適応調整するため、誤差入力量に対応して出力を調整する、上述のi番目のファジィルールを設定する。

すなわち、ファジィ推論の効果として、誤差が少ないときは低いゲインとなる。ただし、ゲインの最適調整は、ニューラルネットワークの学習により行われる。つまり、モデル化誤差、摩擦、未知な外乱等により位置と速度の誤差が生じると大きなゲインとなり、誤差の減少が期待できる。また、後述する図16BのC7の部分のように大きな誤差に対しては、フィードバックの効果が期待できる。このような構成により、外乱やパラメータ変動にロバストとなることが期待できる。

【0080】

図16Cは、ファジィ・ニューラルネットワークによるゲインスケジューリングのブロック図を示す。

このゲインスケジューリングにより決定されたCi=μi(kipep+kiv+kiI∫fepdt)式により、図16BのC1〜C9の各ゲインが算出される。

【0081】

図16Dは、ファジィPD部131のファジィPDゲインマトリックスを示す。これはファジィPDについて入力のCpとCvが9個のウィンドウに分割された入力空間で図16Aに示す通り計算がされたゲインである。入力誤差に対して制御ゲインが適応調整される。

図16Eは、ファジィPD部131のファジィPD制御面を示す。これはファジィPDについてCpとCvの入力に対する制御出力がどのように変化するかを表わしている。図16Eの制御面によれば、ステップ状の大きな外乱に対してロバスト性及びロバスト安定性を有することがわかる。

【0082】

〔ロバスト安定性の根拠〕

ここで、図17を参照して、本発明の実施の形態に係るFB−FN部130のロバスト安定性の根拠について説明する。

FB−FN部130は、パラメータ変動が微小ではなく、ある有限な範囲で生じるとし、その変動範囲で制御性能を保証する制御系を設計する必要がある。そこで、パラメータの変動範囲をカバーする多数の基準点を仮定しこの点におけるパラメータ感度を小さくすることが好適である。また、各基準点での感度を小さくする割合はメンバーシップ関数を用いることにより、システムの要求に応じて設定できる。

また、ファジィ・ニューラルネットコントローラの誤差のロバスト性を確保するには、パラメータがある基準点まわりで微小変動することを前提とし、その変動に対するパラメータ感度を最小化する必要がある。図17に、そのメンバーシップ関数と、ファジィPIの制御面を示す。

ここで、図17の古典PIの制御面に示す通り、eかe・(eの上点)の移行方向に順じた、あるいは逆らった方向にeかe・が摂動すると、duの変化が増大する。

これに対して、図17のファジィPIの制御面においては、制御誤差であるeかe・の変化量が小さいときはファジィPIには、さほど影響しない。すなわち、ファジィPIの制御面はe−e・が、ほぼ平行であり、摂動すると、eとe・が2つ以上のルールが作動する過渡的な領域に入っていくだけで、制御出力には影響しない。つまり、定常偏差を減少させる機能が働いていることがわかる。

これにより、ファジィPIDコントローラのロバスト性の根拠が説明できる。

【0083】

(ステップS304)

次に、制御部11は、ICS部10のFB−FN部130に対して、ファジィ推論処理を行う。

このファジィ推論処理においては、上述したシングルトン出力のメンバーシップ関数を使用して、ダイナミックスな非線形システムの種々の操作条件に適用する複数の線形コントローラを内挿的に組み込むことができる。

本実施の形態に係るこのファジィ推論処理においては、入力空間をスムーズに内挿して線形ゲインを求め、効果的なゲインスケジューラとし、非線形システムをモデル化できる。

つまり、ファジィ推論システムを使い、入出力データからBP法等のアルゴリズムを使ってチューニングする。ここでは、推論システムのパラメータを同定するためのハイブリッドな学習アルゴリズムを使う。非線形パラメータに対し、上述したように、最小二乗法とバックプロバゲーション勾配降下法(BP法)を適用する。

以上により、FB−FN学習処理を終了する。

【0084】

〔ファジィPD部131の例〕

以下で、作成して学習させたファジィPD部131であるFUZZY_PDのMファイルの例を示す:

[Input1]

Name='input1'

Range=[-0.2868 0.2804]

NumMFs=3

MF1='in1mf1':'gauss2mf',[0.0478592834462299 -0.371325 0.0319561439415608 -0.217974284608918]

MF2='in1mf2':'gauss2mf',[0.0608664733050278 -0.0978076222858487 0.0555142362386605 0.0852892043051262]

MF3='in1mf3':'gauss2mf',[0.0138714984932358 0.20884527353354 0.0478592834462299 0.361225]

[Input2]

Name='input2'

Range=[-1.0472 1.0472]

NumMFs=3

MF1='in2mf1':'gauss2mf',[0.177881957852323 -1.36136 0.178084149908005 -0.73222056738112]

MF2='in2mf2':'gauss2mf',[0.150801124394399 -0.302584545101134 0.1487581237134 0.303271696091688]

MF3='in2mf3':'gauss2mf',[0.178465822406237 0.732532304938343 0.177881957852323 1.36136]

[Output1]

Name='output'

Range=[-9.121 8.9183]

NumMFs=9

MF1='out1mf1':'linear',[29.9502149922501 0.502141541225866 -0.0114363187815991]

MF2='out1mf2':'linear',[0.699802412554496 2.88172200515163 -3.69267448235734]

MF3='out1mf3':'linear',[2.42419964633644e-009 1.94710601114873e-009 -4.46135969104574e-008]

MF4='out1mf4':'linear',[29.8646225385097 0.522490654609605 0.00109243397029133]

MF5='out1mf5':'linear',[29.9872760919535 0.502942439065712 -0.000137735051368041]

MF6='out1mf6':'linear',[29.9929707105531 0.500833500934634 0.000342857488096674]

MF7='out1mf7':'linear',[1.73151335707348e-014 7.40165806871063e-014 9.36256379708729e-014]

MF8='out1mf8':'linear',[0.60924632277904 2.59412276828522 3.30948675859052]

MF9='out1mf9':'linear',[29.9947186987529 0.494510357242337 0.00687566067744605]

[Rules]

1 1, 1 (1) : 1

1 2, 2 (1) : 1

1 3, 3 (1) : 1

2 1, 4 (1) : 1

2 2, 5 (1) : 1

2 3, 6 (1) : 1

3 1, 7 (1) : 1

3 2, 8 (1) : 1

3 3, 9 (1) : 1

【0085】

〔ファジィPI部132のファイル例〕

以下で、作成して学習させたファジィPI部132であるFUZZY_PIのMファイルの例についても示す:

[System]

Name='FNN_PI'

Type='sugeno'

Version=2.0

NumInputs=2

NumOutputs=1

NumRules=9

AndMethod='prod'

OrMethod='probor'

ImpMethod='prod'

AggMethod='sum'

DefuzzMethod='wtaver'

[Input1]

Name='input1'

Range=[-0.2275 0.2108]

NumMFs=3

MF1='in1mf1':'gauss2mf',[0.0372257745066239 -0.293245 0.0620222208404797 -0.145616701160321]

MF2='in1mf2':'gauss2mf',[0.0509989814349655 -0.0938664146504105 0.061773470568765 0.0711977845073082]

MF3='in1mf3':'gauss2mf',[0.0451928100610181 0.122287868166051 0.0372257745066239 0.276545]

[Input2]

Name='input2'

Range=[-1.0472 1.0472]

NumMFs=3

MF1='in2mf1':'gauss2mf',[0.177881957852323 -1.36136 0.194858188187073 -0.725976617084914]

MF2='in2mf2':'gauss2mf',[0.184472713520267 -0.318507248879403 0.182769544067602 0.316484420470913]

MF3='in2mf3':'gauss2mf',[0.189973693378099 0.727208320141822 0.177881957852323 1.36136]

[Output1]

Name='output'

Range=[-7.2538 6.6378]

NumMFs=9

MF1='out1mf1':'linear',[43.4662552481124 15.4046594018716 18.8528571837822]

MF2='out1mf2':'linear',[-72.3728068591604 -8.21719705183032 -35.8241392764794]

MF3='out1mf3':'linear',[-0.746178588917306 -0.0969956028725818 -409.511443589854]

MF4='out1mf4':'linear',[43.6763652955075 4.47961924229057 -1.2979557058011]

MF5='out1mf5':'linear',[-188.845013085459 16.3752420684739 2.26580569880905]

MF6='out1mf6':'linear',[52.6504877364809 13.6637475028015 -2.81582668956971]

MF7='out1mf7':'linear',[1.36664656988905 -101.944112740175 561.037900146712]

MF8='out1mf8':'linear',[-37.7754372896572 -2.37931907009803 20.5924135196645]

MF9='out1mf9':'linear',[77.3693139104994 7.01860325733576 -18.4498686710174]

[Rules]

1 1, 1 (1) : 1

1 2, 2 (1) : 1

1 3, 3 (1) : 1

2 1, 4 (1) : 1

2 2, 5 (1) : 1

2 3, 6 (1) : 1

3 1, 7 (1) : 1

3 2, 8 (1) : 1

3 3, 9 (1) : 1

【0086】

〈ソフトウェアサーボ制御処理の詳細〉

次に、図18を参照して、本発明の実施の形態に係るソフトウェアサーボ制御処理について説明する。

本発明の実施の形態に係るソフトウェアサーボ制御処理においては、DCモータ駆動用PWM(パルス幅変調)モジュールと位置検出用エンコーダのアップダウンカウンタモジュールを、ソフトウェアで作成して実現する。これにより、ハードウェア部品の省力化と、ハードウェアによる動作時間遅れやノイズの対策ができる。

PWM部150のPWMモジュールについて、設計によりソフトウェア化を行っている。すなわち、本実施形態においては、MATLAB/Simulinkによりロジック回路を作成し、PWMモジュールを実現させている。すなわち、図18のように、制御部11が信号の振幅を変更して出力することで、モータ230の駆動ができる。このPWMモジュールの例を、後述する実施例の図20A〜図20Cに示す。

また、COUNTER(カウンタ)モジュールについても、設計によりソフトウェア化を行っている。すなわち、本実施形態においては、MATLAB/Simulinkによりロジック回路を作成し、COUNTERモジュールを実現させている。このCOUNTERモジュールの例を、後述する実施例の図20F〜図20Hに示す。

このように、知能コントローラの演算処理の高速化により、インテリジェント・ロバスト制御を実現することができる。

【0087】

以上のように構成することで、以下のような効果を得ることができる。

まず、従来、産業界で問題となっている現代制御理論(Model Based Control)による電子制御の不具合が多発していた。これは、制御ゲインが固定ゲインであることに起因するものであった。

本発明の実施の形態に係る制御システムXは、次世代のファジィ・ニューラルネットワークベースト制御によるインテリジェント・ロバスト組み込み知能コントローラであるICS部10を用いることで、この問題を唯一解決することができる。

ICS部10には、目標軌道誤差の変化に適応的にゲインを可変調整するファジィ・ニューラルベースト制御の新規インテリジェント・ロバストゲイン補償器であるFB−FN部130が組み込まれている。これにより、システムパラメータ変動、突発的な外乱および目標変化に対して、十分な目標軌道追従制御性能が得られる。

【0088】

また、本発明の実施の形態に係る制御システムXの制御方法は、従来のPID制御方法を多変数系に拡張させることができる。

すなわち、本実施形態の制御方法は、非線形の運動方程式を直接使用して、FF−NN部120のニューラルネットワークにより線形化を行い、FB−FN部130のファジィ・ニューラルネットワークにより外乱抑制および非干渉化を行う。

本実施形態の制御方法は、時間によってパラメータが変化する非線形系がいつも臨界減衰となるように、時間によってゲインが適応的に変化する制御則を考案し、多変数系における各軸の相互干渉を非干渉化させる。このことにより、インテリジェント制御による多変数系制御を行い、マニピュレータの完全追従制御を実現することができる。

【0089】

また、本実施形態に係る制御システムXは、ファジィの推論能力とニューラルネットワークの学習能力を組み合わせることで、制御ゲインを可変調整し、未知の要素に対して適応させることができる。

実際に、下記の実施例にて構築したファジィ・ニューラルネットワーク制御システムを従来のPID制御、FF−NN制御のみのシステムと比較する実験を行ったところ、ファジィ・ニューラルネットワーク制御の有効性は高かった。

【0090】

また、従来、マニピュレータに関するシステム設計は、制御対象が多自由度系でも1自由度系と見なし近似式を用いて制御系を設計し、関節軸ごとに独立した制御系を構築する手法が多くの製品に採用されていた。

本実施形態に係る制御システムXは、この多自由度系設計化の未解決な課題を、インテリジェント制御により解決することができる。

すなわち、本実施形態に係る制御システムXは、ロバストで自動的なゲイン調整が可能な制御系を構築するために、ファジィ分割された空間において位置誤差に応じた可変フィードバックゲインが設定される制御系を、多自由度系化の設計に用いることができる。

【0091】

また、本実施形態に係る制御システムXは、ファジィ・ニューラルネットワークの学習によるゲインの自動設定ができ、インテリジェント制御によるロバスト性を実現することができる。

これにより、マニピュレータおよび多変数系メカニカルシステムに対する実用的なインテリジェント・ロバスト制御システムを実現し、ロボット、自動車、電動自転車、船舶、航空機、宇宙機、ロケット、温度制御、電動制御等、目標値を設定して制御する従来の制御が用いられていたあらゆる制御対象機器について、応用可能である。

また、本実施形態に係る制御システムXは、モデル化誤差、摩擦、未知の外乱等により変位および速度の制御誤差が生じた場合、制御ゲインを適応調整するファジィ・ニューラルネットワークによる非線形偏差補償が可能になる。

すなわち、ファジィ・ニューラルネットワークによるインテリジェント・ロバスト制御手法が確立し、多変数系メカニカルシステムに対する実用的なインテリジェント制御システムを実現することができる。

【0092】

また、本実施形態に係る制御システムXは、組み込み型コンビュータを知能コントローラ部1として用いて、通常のPC等による制御装置3によるRTW(Real−Time Workshop)を用いたモデルベースでのシステム開発により、短期間でのシステム開発を行うことが可能である。

さらに、MATLAB/Simulinkのようなソフトウェアを用いることで、シミュレーションも簡単に行えるため、システム開発のコストダウンや時間削減に大きな効果が得られる。

【0093】

また、本実施形態に係る制御システムXは、目標軌道誤差の変化に適応的にゲインを可変調整する新しい方式のインテリジェント・ロバストゲイン補償器(ファジィ・ニューラルベースド制御)が組み込まれており、システムパラメータ変動、外乱および目標変化に対して、十分な目標軌道追従制御性能が得られる。具体的には、ロバストで自動的なゲイン調整が可能な制御系を構築するために、ファジィ分割された空間において位置誤差に応じた可変フィードバックゲインが設定される制御系を構成している。

また、本実施形態に係る制御システムXは、制御系を2自由度制御構成とし、フィードフォワード部をニューラルネットワークにより構成し、変位、速度、加速度のパラメータによりプラントの特性を学習させ、プラント特性の逆特性を取得しシステムを線形化している。

また、フィードバック部は、ファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であり、完全追従性能を実現させている。

これらの制御系は、リアルタイム(実時間)処理で、例えばサンプリング時間が1ミリ秒で実行されていることを特徴とする。

【実施例】

【0094】

ここで、図19A〜図21Bを参照して、実際に上述のICS部10の構成と各処理を用いて、インテリジェント・ロバスト制御を行った実施例について説明する。

本実施例においては、組み込み型コンピュータであるICS部10を含む知能コントローラ部1によって制御対象2の位置制御を行う。制御対象2としては、DCモータによって駆動する移動テーブルを用いた。

ICS部10のOSには、Linux(登録商標)+Xenomai(商標)を用いており、リアルタイムでの制御が可能である。パソコンである制御装置3は、知能コントローラ部1とLANクロスケーブルにより直接接続して、イーサネット(登録商標)で通信を行った。

知能コントローラ部1は、知能コントローラ部1のD/Aコンバータから制御信号を送出する。この制御信号は、モータ駆動ドライパ20を介して、モータ230へと出力される。モータ230が回転すると、エンコーダ220からパルス波が出力される。このパルス波は、知能コントローラ部1のA/Dコンパータによって、知能コントローラ部1が取得する。このパルス波を1/8に分周させてあり、このパルス波をカウントすることによりモータ230の位置情報をフィードバックすることができる。

【0095】

また、本実施例では、モータ駆動ドライバ20として、東芝セミコンダクター社製のTA7281Pを用いた。また、モータ230として、ツカサ電工社製のTG−47C−SMを用いた。TG−47C−SMは、定格電圧12[V]、定格回転数4400[rpm]、定格電流160[mA]、無負荷回転数5250[rpm]、無負荷電流60[mA]である。

また、エンコーダ220として、TG−47C−SMに付属のロータリエンコーダを用いた。当該ロータリエンコーダは、1回転につき8パルス出力する。

【0096】

(実験方法)

本実施例では、MATLAB/Simulinkによりファジィ・ニューラルネットワークの制御システムXのためのモデルを構築した。また、比較のため、従来のPID制御、NN−PIDのみの制御システムのモデルも同様に構築した。

これらの制御システムのモデルを図19A〜図19Cに示す。また、この各制御システムの各部位のモデル図を、図20A〜図20Hに示す。

【0097】

より具体的には、図19Aは、従来のPID制御のモデル図である。このモデルのPIDパラメータについては、比例ゲインP=12、積分ゲインI=0、微分ゲインD=0、としてモータ駆動ドライバ20の制御を行った。

また、図19Bは、NN−PID制御のみの場合のモデル図である。FF−NN部120のニューラルネットワークの学習にはPID制御のデータを基にして行い、指令信号の変位、速度、加速度を入力とし、PIDの操作量を教師信号としてBP法で学習を行った。これによって得られたニューラルネットワークをPIDの操作量にフィードフォワードさせている。PIDパラメータはPID制御と同様である。

また、図19Cは、本実施例に係るファジィ・ニューラルネットワーク制御のモデル図である。FNNの学習には、図19AのPID制御のデータを基にして行い、変位誤差、速度誤差を入力とし、PIDの操作量を教師信号としてBP法と最小二乗法を組み合わせた方法で学習を行った。この際に、図19BのNN−PID制御のパラメータ等も、ファジィ・ニューラルネットワークの制御システムに用いた。

【0098】

制御対象2は、1つのDCモータ230によって動く移動テーブルとし、構築した制御システムにより位置制御を行う。指令信号は振幅5、周期30[s]のsin波とし、サンプリングタイムは1[msec]でモータの制御を行った。

また、比較のための動作テストとして外乱あり、外乱なしの状態で3つの制御システムを実行し性能比較を行った。外乱はモデル上で再現し、実行してから10秒後に+5の値を操作量に加えるようにした。

【0099】

(実験結果)

図21Aと図21Bを参照して、実験結果について説明する。

図21Aは、従来のPID制御のモデル(比較例)を用いて制御を行った結果である。従来のPID制御では、外乱がない場合には、1自由度の位置制御でも時間遅れがあり若干の誤差が見られた。さらに、従来のPID制御では、外乱が発生すると定常情差として誤差が現れ、外乱の信号に合わせて出力が上にずれていた。なお、図示しない図19BのNN−PIDのみの制御は、フィードフォワード補償により時間遅れを多少解消できていた。しかし、NN−PIDのみの場合、外乱がない場合にはそれほど制御信号とはズレないものの、外乱がある場合には従来のPID制御と同様な結果であり、ロバスト性がなく不十分であった。

図21Bは、本実施例に係るファジィ・ニューラルネットワーク制御を用いた結果である。ファジィ・ニューラルネットワーク制御では、制御対象の非線形要素に対応できると考えられる。すなわち、ファジィ・ニューラルネットワーク制御では外乱あり、外乱なしの両方で指令信号に追従できていたことから、制御ゲインを適応的に調整していると考えられる。このことから、ファジィ・ニューラルネットワーク制御はロバスト性のある制御方法であり、外乱や制御機器の非線形要素に対して有効であった。

【0100】

なお、上記実施の形態の構成及び反応及び動作は例であって、本発明の趣旨を逸脱しない範囲で適宜変更して実行することができることは言うまでもない。

【産業上の利用可能性】

【0101】

本発明は、インテリジェント・ロバスト制御を行う制御手段を提供することで、様々な装置の制御に使用でき、産業上利用可能である。

【符号の説明】

【0102】

1 知能コントローラ部

2 制御対象

3 制御装置

10 ICS部

11 制御部

14 補助記憶部

15 主記憶部

16 論理回路部

17 I/F部

18、19 コネクタ

20 モータ駆動ドライバ

21 テーブル部

110 PID部

111 PD補償器部

120 FF−NN部

130 FB−FN部

131 ファジィPD部

132 ファジィPI部

140 差分部

141 速度算出部

142 加速度算出部

150 PWM部

160 カウンタ部

170 出力部

180 入力部

190 制御信号発生部

195 外乱シミュレート部

210 テーブル

220 エンコーダ

230 モータ

X 制御システム

【技術分野】

【0001】

本発明は、組み込み知能コントローラ、制御システム、制御プログラム、記録媒体、及び制御方法に係り、特にインテリジェント・ロバスト制御を行う組み込み知能コントローラ、制御システム、制御プログラム、記録媒体、及び制御方法に関する。

【背景技術】

【0002】

近年、宇宙探査機の『はやぶさ』や医療現場などの様々な作業環境でロボットマニピュレータが使用されている。また、ロボットの自動化・自律化も進められており、高精度な制御が求められている。しかし、このような制御を実現するには大きな問題点がある。それは、ロボットマニピュレータの動特性が位置・姿勢による慣性負荷や速度による遠心力、重力負荷などの非線形性を持つこと、それに加え環境条件や外的要因による外乱によって変動をきたすことなどである。

従来から、一般的な制御方法としてPID制御が知られている。PID制御は、P(Proportional、比例)動作、I(Integral、積分)、D(Differential、Derivative、微分)動作を用いたフィードバック制御である。すなわち、PID制御は、目標値−制御量である制御の偏差に対して、比例演算、積分演算、及び微分演算を行い、操作量を算出して制御する。

PID制御は、古典制御だが扱いやすさと正確性の良さから広く使われている。しかし、PID制御のような古典制御では外乱や非線形要素への対応が困難であった。

【0003】

そこで、従来から、一般にマニピュレータに関するシステム設計は、制御対象が多自由度系でも1自由度系と見なし近似式を用いて制御系を設計し、関節軸ごとに独立した制御系を構築する手法が多くの製品に採用されている。

しかし、一般的には、マニピュレータは、剛性が低く、重力や遠心力を受ける非線形な多入力多出力系である。また、従来手法では、PID制御における位相補償制御、最適サーボ系、外乱オブザーバを用いた制御あるいはH∞制御等を用いて精度、振動抑制、ロバスト性などを実現しているが、十分な制御性能が得られなかった。

【0004】

ここで、従来のPID調節装置として、特許文献1を参照すると、制御対象からの制御量PVnと目標値SVnから補償演算を行って得られる実効目標値SVn0との偏差が零となるようにPIまたはPID(P:比例,I:積分,D:微分)調節演算を行い、得られる調節演算信号を操作信号MVnとして前記制御対象に印加する調節装置において、制御量の目標値から実効目標値を得るために、比例ゲイン2自由度化係数α(α:0〜1間の定数)及び積分時間2自由度化係数β(β:1〜10間の定数)を用いた補償演算手段を設け、目標値から操作信号間の伝達関数Csv(s)がKp{α+[1/(TI・s)]・[(1+TI・s)/(1+βTI・s)]}とする2自由度PID調節装置、但し、Kp:比例ゲイン、TI:積分時間、s:ラプラス演算子であるものが記載されている(以下、従来技術1とする。)。

従来技術1によれば、PID制御の2自由度化のための積分動作の2自由度化を非常にシンプルな形とし、かつ、比例ゲインの2自由度化係数αと積分時間の2自由度化係数βの相互干渉を除去できる補償演算手段を設けたことにより、(1)積分動作の2自由度化が非常に簡単になり、かつ、分かり易い形に実現できる。(2)積分動作の2自由度化において比例ゲイン2自由度化係数αの関与を排除でき、調整が簡単になる。(3)さらに、積分動作の2自由度化係数βの関与を分母のみとし、シンプルで2自由度化係数βの調整時に直感的に把握可能となる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平07−072901号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来、遠心力・重力・クーロン摩擦などの外乱が顕著な場合には、入出力信号から状態変数を推定するオブザーバ(観測器)を用いてロバスト(堅牢)制御を行っていたものの、満足できるものではなかった。

このような従来のロバスト制御では、定常特性に関するパラメータであるゲインが固定であったため、突発的外乱の影響に対応できず、不具合発生が問題となっていたためであった。これは、従来技術1でも同等であった。

このため、実用的なインテリジェント(知能化)・ロバスト制御装置が強く望まれていた。

【0007】

本発明は、このような状況に鑑みてなされたものであり、上述の課題を解消することを課題とする。

【課題を解決するための手段】

【0008】

本発明の組み込み知能コントローラは、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラにおいて、ファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるフィードバック手段を備え、該フィードバック手段は、前記制御対象の非線形動特性のPD(比例、微分)補償を行うファジィPD手段と、前記制御対象の非線形動特性のPI(比例、積分)補償を行うファジィPI手段とを並列に備えることを特徴とする。

本発明の組み込み知能コントローラは、前記フィードバック手段は、ファジィ分割された空間において位置誤差に応じた可変フィードバックゲインを設定することを特徴とする。

本発明の組み込み知能コントローラは、制御系を2自由度制御構成とし、前記制御対象の変位、速度、及び加速度のパラメータをニューラルネットワークにより学習させ、前記制御対象の特性の逆特性を取得するフィードフォワード手段を備えることを特徴とする。

本発明の組み込み知能コントローラは、前記フィードフォワード手段又は前記フィードバック手段は、所定のサンプリング時間で実時間処理を行うことを特徴とする。

本発明の組み込み知能コントローラは、前記フィードフォワード手段又は前記フィードバック手段は、ソフトウェアPWM制御を行うことを特徴とする。

本発明の制御システムは、前記組み込み知能コントローラを含むことを特徴とする。

本発明の制御プログラムは、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラの制御プログラムにおいて、コンピュータをファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるフィードバック手段

として機能させるための制御プログラムであることを特徴とする。

本発明の記録媒体は、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラの制御プログラムの記録媒体において、コンピュータをファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるフィードバック手段として機能させるためのプログラムを記録したコンピュータ読み取り可能な記録媒体であることを特徴とする。

本発明の制御方法は、制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する制御方法において、フィードバック手段により、ファジィ・ニューラルネットワークにより非線形誤差を減少させることを特徴とする。

【発明の効果】

【0009】

本発明によれば、ファジィ・ニューラルネットワークを用いることで、実用的な非線形動作特性をもつインテリジェント・ロバスト制御を実現する組み込み知能コントローラを提供することができる。

【図面の簡単な説明】

【0010】

【図1A】本発明の実施の形態に係る制御システムXの一例の外観図である。

【図1B】本発明の実施の形態に係る知能コントローラ部1のICS部10の外観図である。

【図2】本発明の実施の形態に係る制御システムXの制御構成を示すブロック図である。

【図3】本発明の実施の形態に係るICS部10の制御構成を示すブロック図である。

【図4】本発明の実施の形態に係る開発/学習処理に用いるICS部10の制御構成例を示すブロック図である。

【図5】本発明の実施の形態に係る開発/学習処理のフローチャートである。

【図6】本発明の実施の形態に係るモデル作成処理のフローチャートである。

【図7】本発明の実施の形態に係るFF−NN逆ダイナミックス処理に用いるICS部10の制御構成例を示すブロック図である。

【図8】本発明の実施の形態に係るFF−NN逆ダイナミックス処理のフローチャートである。

【図9A】本発明の実施の形態に係るFF−NN部120のニューラルネットワークの構成例を示す概念図である。

【図9B】本発明の実施の形態に係るFF−NN部120のニューラルネットワークのブロックを示す概念図である。

【図10】本発明の実施の形態に係るFB−FN学習処理に用いるICS部10の制御構成例を示すブロック図である。

【図11】本発明の実施の形態に係るFB−FN学習処理のフローチャートである。

【図12A】本発明の実施の形態に係るファジィ・ニューラルネットワークの構造を示す概念図である。

【図12B】本発明の実施の形態に係るファジィPD部131とファジィPI部132の全体構成を示す概念図である。

【図13】本発明の実施の形態に係るファジィPD部131とファジィPI部132の学習過程を示すブロック図である。

【図14】本発明の実施の形態に係る調整されたメンバーシップ関数の例を示す概念図である。

【図15】本発明の実施の形態に係るファジィPD部131及びファジィPI部132のファジィルールの設定方法を示す概念図である。

【図16A】本発明の実施の形態に係るFB−FN部130のファジィ・ニューラルネットワークゲインの計算方法を示す概念図である。

【図16B】本発明の実施の形態に係るFB−FN部130のゲインマトリックスを示す概念図である。

【図16C】本発明の実施の形態に係るFB−FN部130のファジィ・ニューラルネットワークによるゲインスケジューリングの概念を示すブロック図である。

【図16D】本発明の実施の形態に係るファジィPD部131のファジィPDゲインマトリックスを示す画面例である。

【図16E】本発明の実施の形態に係るファジィPD部131のファジィPD制御面を示す画面例である。

【図17】本発明の実施の形態に係るFB−FN部130のロバスト安定性について説明するための概念図である。

【図18】本発明の実施の形態に係るソフトウェアサーボ制御処理のPWM制御の概念図である。

【図19A】本発明の実施の形態の実施例に係る従来のPID制御のモデル図である。

【図19B】本発明の実施の形態の実施例に係るNN−PID制御のみの場合のモデル図である。

【図19C】本発明の実施の形態の実施例に係るファジィ・ニューラルネットワーク制御のモデル図である。

【図20A】本発明の実施の形態の実施例に係るPWM部150のモデル図である。

【図20B】本発明の実施の形態の実施例に係るPWM部150のSEIHUKIRIKAEブロックのモデル図である。

【図20C】本発明の実施の形態の実施例に係るPWM部150のSEIHUKIRIKAEブロックのPWM18−20ブロックのモデル図である。

【図20D】本発明の実施の形態の実施例に係る出力部170のモデル図である。

【図20E】本発明の実施の形態の実施例に係る入力部180のモデル図である。

【図20F】本発明の実施の形態の実施例に係るカウンタ部160のモデル図である。

【図20G】本発明の実施の形態の実施例に係るカウンタ部160のCOUNTERブロックのモデル図である。

【図20H】本発明の実施の形態の実施例に係るカウンタ部160のCOUNTERブロックのTriggered Subsystemのモデル図である。

【図21A】本発明の実施の形態に係る従来のPID制御のモデルを用いて制御の実験結果を示すグラフである。

【図21B】本発明の実施の形態の実施例に係るファジィ・ニューラルネットワーク制御の実験結果を示すグラフである。

【発明を実施するための形態】

【0011】

<実施の形態>

〔本発明の実施の形態に係る制御システムXの構成〕

まず、図1A〜図2を参照して、本発明の実施の形態に係る制御システムXの制御構成について説明する。

図1Aは、制御システムXを開発する際に用いる構成の一例の外観図である。本実施形態の制御システムXは、知能コントローラ部1が、テーブル移動装置である制御対象2と、図示しない制御装置3とに接続されている。

知能コントローラ部1は、インテリジェント・ロバスト制御に用いるICS部10(Intelligent Control System Module、組み込み知能コントローラ)を備えている制御部位である。図1Aの例では、知能コントローラ部1として、組み込みモジュールを接続できる開発用の組み込み型コンビュータを用いる例を示す。

また、制御対象2は、外乱の影響を受け、ロバスト制御が必要になる具体的な制御対象部位である。図1Aの例では、開発とシミュレーションに用いるテーブル移動装置を用いた例を示す。このテーブル移動装置は、モータドライバーやカウンタ等であるモータ駆動ドライバ20を備えている。モータ駆動ドライバ20は、駆動用のモータ230により、テーブル210を移動させ、その制御の応答を入力する。

図1Bは、ICS部10の外観図である。ICS部10は、組み込みコンピュータを用いたインテリジェント・ロバスト型組み込み知能コントローラであり、後述する学習後に、実際の制御対象の機器に装着してインテリジェント・ロバスト制御を行う。

【0012】

図2は、制御システムXの具体的な構成を示す制御ブロック図である。

制御システムXは、一例として、知能コントローラ部1と、制御対象2と、制御装置3とを含んでいる。

【0013】

知能コントローラ部1は、製品の製造時には、ロボット、自動車、自転車、航空機、ヒートポンプ等の制御が必要な各種機器そのものに、ICS部10を組み込んで用いる。ここでは、開発時の構成例として、例えば、システム開発ツールであり、主に実際の製品に搭載する前の開発段階で使用する組み込み型コンビュータを用いる例について説明する。この開発用の組み込み型コンビュータとしては、たとえば、エー・アンド・デイ社製のAD7011−EVAを用いることができる。また、知能コントローラ部1は、高速な制御手段を用いて、例えば、所定のサンプリング時間、例えば1ミリ秒〜数十ミリ秒程度にて、リアルタイム(実時間)処理を行うことができる。

制御対象2は、製品の製造時には、ロボット、自動車、自転車、航空機、ヒートポンプ等のモータやアクチュエータやヒータのように電磁的に駆動を調節する素子と、この素子の出力の状態を取得するセンサ等を含む。本実施形態では、一般的な外乱の起こる駆動系のシミュレーションを行う場合の構成として、駆動装置であるDC(直流)モータ駆動のテーブル移動装置を用いた構成の例について説明する。

制御装置3は、一般的なPC/AT互換機やMAC規格機のようなPC(Personal Computer)等を用いることができる。制御装置3は、Windows(登録商標)やLinux(登録商標)等のOS(Operating System)を用いて、制御用のソフトウェアをインストールして実行することができる。以下では、制御装置3のPCに、制御用ソフトウェアとしてMathWorks社製のMATLAB(登録商標)/Simlink(登録商標)をインストールしてファジィ/ニューラルネットを構築した例について説明するが、これに限られない。また、以下では、制御装置3において、エイ・アンド・デイ社のVCDesigner(商標)とModelDef(商標)ソフトウェアを用いてモデル定義とモデル実行画面の作成を行う例についても説明するが、これに限られず、各種のソフトウェアを用いて実現することができる。

【0014】

〈知能コントローラ部1の構成〉

より具体的に説明すると、知能コントローラ部1は、例えば、ICS部10、制御部11、補助記憶部14、主記憶部15、論理回路部16、I/F部17、及びコネクタ18と19を含んで構成される。

ICS部10は、EEPROM(Electrically Erasable Programmable Read−Only Memory)やNOR/NANDフラッシュメモリやSRAM(Static Random Access Memory)等を内蔵したiCS(intelligent Control System)モジュールである。ICS部10は、制御装置3で作成された制御部11のC言語等のプログラム(実行コード)であるバイナリファイル、各種モデルやパラメータに関する定義ファイルやデータ、FPGA(Field Programmable Gate Array)の論理回路データ、知能コントローラ部1のファームウェアやBIOS(Basic Input/Output System)等を記憶している記憶媒体(記録媒体)も備える。後述する開発/学習処理では、このプログラムやデータが制御部11により読み出されて実行される。また、ICS部10は、図1Aの外観図のように、それ自体が制御演算手段を備えたシングルボードコンピュータとして構成されていてもよい。

制御部11は、RISC(Reduced Instruction Set Computer、縮小命令セットコンピュータ)方式やCISC方式等の高速演算処理が可能なCPU(Central Processing Unit、中央処理装置、中央演算装置)、MPU(Micro Processing Unit)、DSP(Digital Signal Processor)、ASIC(Application Specific Processor、特定用途向けプロセッサー)等である演算・制御能力を備えた制御手段である。

補助記憶部14は、主にOS用の記憶媒体(記録媒体)として、SSD(Solid State Drive)やコンパクトフラッシュ(登録商標)ディスクやSDメモリカードやmicroSDメモリカード等のフラッシュメモリディスク、HDD(Hard Disk Drive)、磁気テープ媒体、光ディスク媒体等を備えた補助記憶手段である。補助記憶部14に記憶されたOSとしては、カーネルに組み込んで使用するリアルタイムモジュールであるXenomai拡張を用いたLinux(登録商標)や、ITRON等のリアルタイム処理が可能なOSを用いることが好適である。

主記憶部15は、主に制御/演算用の記憶媒体(記録媒体)として、SDRAM(Synchronous Dynamic Random Access Memory)やDDR(Double−Data−Rate)、DDR2、DDR3、LPDDR3、WideIO、XDR(extreme data rate)等の主記憶用に使われる高速な記憶手段を含んで構成される主記憶手段である。主記憶部15は、ICS部10の各プログラムやデータ、制御対象2から取得したセンサのデータ等を記憶する。

論理回路部16は、CPLD(Complex Programmable Logic Device)やFPGA等の論理回路及び各種アナログ回路等である。論理回路部16は、制御対象2とのインターフェイスの回路やA/D(analog−to−digital)コンバータやD/A(digital−to−analog)コンバータ等も含んで構成される。

I/F部17は、USB(Universal Serial Bus)、無線USB、シリアル、パラレル、LAN(Local Area Network)等のインターフェイスである。I/F部17は、主に制御装置3からプログラムやバイナリファイルやデータ等を転送し、制御結果等のデータを制御装置3に転送するために用いる。

コネクタ18は、主に制御装置3に接続するためのコネクタ等である。コネクタ18は、例えば、制御装置3と、LANクロスケーブルで接続できる。また、コネクタ18には、タッチパネルディスプレイ等の表示部/入力部やスピーカやマイクロフォン等を別途接続してもよい。

コネクタ19は、主に制御対象2に接続するためのコネクタであり、別途駆動用のアンプやセンサ等と接続してもよい。

【0015】

〈制御対象2の構成〉

また、制御対象2は、モータ駆動ドライバ20と、テーブル部21とを含んでいる。

モータ駆動ドライバ20は、一般的なDCモータを駆動するためのドライバIC(Integrated Circuit)を用いることができる。このドライバICは、知能コントローラ部1からの制御信号によりテーブル部21のモータ230を駆動する。また、モータ駆動ドライバ20は、エンコーダ220からの出力を取得して、知能コントローラ部1に送信する。

テーブル部21は、DCモータによって駆動する移動テーブルの例である。テーブル部21は、移動テーブル(ステージ)であるテーブル210と、テーブル210を駆動するDCモータ等のモータ230と、テーブル210の位置等を検知するエンコーダ220とを含んで構成される。

【0016】

(ICS部10の構成)

次に、図3を参照して、ICS部10の詳細な制御構成について説明する。

ICS部10は、主にPID部110、FF−NN部120(フィードフォワード手段)、FB−FN部130(フィードバック手段)、差分部140、PWM部150、カウンタ部160、出力部170、入力部180、制御信号発生部190、外乱シミュレート部195を含んで構成される。ICS部10は、これらの構成部位を組み合わせて、各処理における各種演算を行う。

【0017】

PID部110は、古典的なPID制御を行うためのモデルのプログラムとデータを含む部位である。

このPID部110は、フィードバック制御におけるPD(比例、微分)補償を行うためのPD補償器部111を備えている。PD補償器部111は、制御対象2の特性を把握するために用いる。

【0018】

FF−NN部120は、FF−NN(Feedforward neural network)補償器のモデルのプログラムとデータを含む部位である。FF−NN部120は、制御対象の位相遅れを改善するために、ニューラルネットワークによりサーボ系逆ダイナミックス特性を学習して用いる。

この学習について、FF−NN部120は、オフラインでPD補償器部111のPD制御系の逆ダイナミックス特性をBP(Backpropagation、誤差逆伝播)法により学習する。

FF−NN部120としては、例えば、例えば、図9Aで示すような、3層、3入力、4中間ユニット、1出力のニューラルネットワークを用いることができる。ここで、入力層(Input Layer)には、変位r、速度s(dr/dt)、加速度s2(d2r/dt2)をそれぞれ入力する。また、FF−NN部120のニューラルネットワークの出力値は操作量UNNである。

このFF−NN部120の学習方法の詳細については後述する。

【0019】

FB−FN部130は、FB−FN(Fuzzy neural network Based Feedforword Nonlinear error、ファジィ・ニューラルネットワークによる非線形偏差補償)補償器のモデルのプログラムとデータを含む部位である。

FB−FN部130は、制御対象2の非線形動特性の補償のために、ファジィ・ニューラルネットワークベースにより、目標信号r(t)と出力信号y(t)との偏差信号e(t)=r(t)−y(t)の二乗が最小となるようにオフラインで学習する。これらの学習後に、制御システムXを始めとする機器に組み込んで制御に使用することができる。このFB−FN部130は、ゲインスケジューリングにより出力の補償を行う。

【0020】

また、FB−FN部130は、ファジィPD部131(ファジィPD手段)とファジィPI部132(ファジィPI手段)を主に備えている。

ファジィPD部131は、ファジィ・ニューラルネットワークを用いて、PD補償を行う部位である。また、ファジィPI部132は、ファジィPI部131と同様のファジィ・ニューラルネットワークを用いて、PI(比例、積分)補償を行う部位である。

ファジィPD部131及びファジィPI部132は、それぞれ、例えば、図12Aで示すような、2入力4層1出力のファジィ・ニューラルネットワークを用いることができる。ファジィPD部131及びファジィPI部132とも、入力層には、それぞれ、位置誤差となる変位誤差信号epと、速度誤差となる変位時間微分の速度誤差信号evを入力信号として入力する。この上で、ファジィPD部131は、PID部110のPD補償の操作量UPDの2乗を評価関数として、BP法で結合加重を修正する。また、ファジィPI部132は、PID部110のPI補償の操作量UPIの2乗を評価関数として、BP法で結合加重を修正する。ファジィPD部131は、それぞれの入力の総和を操作量UFN-PDとして出力する。また、ファジィPI部132は、操作量UFN-PIを出力する。

このファジィPD部131及びファジィPI部132のファジィ・ニューラルネットワークの学習方法の詳細については後述する。

【0021】

差分部140は、従来の古典PD補償器であるPD補償器部111の操作信号(指令信号)の変位r、速度s(dr/dt)、加速度s2(d2r/dt2)を算出するプログラムとデータを含む部位である。差分部140は、速度sを算出する速度算出部141と、加速度s2を算出する加速度算出部142を含んでいる。また、差分部140は、変位誤差信号epと、速度誤差信号evを算出することもできる。

PWM部150は、DCモータ駆動用のソフトウェアPWM(Pulse Width Modulation、パルス幅変調)モジュールのプログラムとデータを含む部位である。このPWM部150の出力信号により、モータ駆動ドライバ20に接続されたモータ230をPWM制御することができる。

カウンタ部160は、エンコーダのカウンタのためのモジュールのプログラムとデータを含む部位である。このカウンタ部160により算出された値を用いて、差分部140が変位r、速度s、加速度s2、変位誤差信号epと、速度誤差信号evを求めることができる。

出力部170は、PWM部150からの出力をモータ駆動ドライバ20に伝えるための切り換え等を行う部位である。

入力部180は、モータ駆動ドライバ20を介して入力したエンコーダ220の信号等である制御対象2からの信号を入力し、カウンタ部160に送信する部位である。

制御信号発生部190は、図示しない外部機器からの指示信号を取得し、制御対象2を制御するための制御信号を出力するモジュールのプログラムとデータを含む部位である。制御信号発生部190は、制御のシミュレーション用に、例えばサイン波等の信号を出力することもできる。

外乱シミュレート部195は、外乱となる摩擦やガタ等による信号をシミュレートするための信号発生器等の部位である。外乱シミュレート部195は、所定出力のランダム信号等を出力可能である。

【0022】

〔制御システムXのICS部10の開発/学習処理〕

次に、図4と図5を参照して、制御システムXにおいて、ICS部10を学習させ、制御対象2の制御に最適化するための開発/学習処理について説明する。

図4は、この制御処理における主な構成部位と信号の流れを示すブロック図である。

本発明の実施の形態に係る制御システムXは、従来の制御システムの問題の解決のため、ファジィ・ニューラルネットワーク(FNN)ベースの制御を行う。ここで、ファジィとは複雑なシステムをヒトのように「暖昧」にとらえることができif−then型のファジィルールにより言語的に記述できるという特徴を持つ。一方、ニューラルネットワークの特徴は学習により入出力の関係を同定できることである。

本発明の実施の形態に係る制御処理においては、制御装置3により、主に、図4のICS部10のFF−NN部120、FB−FN部130、及び差分部140のモデルを作成して開発を行う。この上で、各部位のプログラム等を知能コントローラ部1の制御部100が実行して、制御対象2のフィードバック制御のための学習をさせ、実際の制御システムを構成する。この制御システムは、例えば、ソフトウェアサーボのPWM制御により制御対象2を駆動することができる。

【0023】

より具体的には、本発明の実施の形態に係るファジィ・ニューラルネットワークを用いたロバスト・ゲインスケジューリング制御系は、ニューラルネットワークによりサーボ系逆ダイナミックス特性を学習しているフィードフォワード補償を行うFF−NN部120、及びファジィ・ニューラルネットワークによるゲインスケジューリングを行うFB−FN部130の2つの補償要素から構成される。この制御系は、目標値応答特性と閉ループ特性が独立設計できる2自由度制御系とし、目標入力に対する追従および、外乱の影響の除去を実現することができる。モデル化誤差及び断続する外乱等による定常偏差の減少、メカトロ位置改善のために、FF−NN部120ではオフラインで従来の固定PD制御系の逆ダイナミックス特性を学習する。つぎに、非線形動特性の補償のために、FB−FN部130は、目標信号r(t)と出力信号y(t)との偏差信号e(t)=r(t)−y(t)の二乗が最小となるようにオフラインやオンラインで学習する。これらの学習後に提案する制御システムが構成される。

以下で、図5のフローチャートを参照して、この開発/学習処理の詳細について説明する。

【0024】

(ステップS101)

まず、制御装置3により、ICS部10の各部に対応するモデルをMATLAB/Simulink、Model Def、VCDesigner等のソフトウェアを用いて作成する。

制御装置3は、この作成したモデルをコンパイル等してプログラムのバイナリファイルに変換し、ICS部10に転送する。このバイナリファイルは、実際にバイナリファイルを実行する定義ファイルや各種データと共にICS部10の補助記憶手段に記憶される。

ICS部10に記憶されたプログラム等は、知能コントローラ部1の制御部11が単独で実行して、下記の学習処理等を行うことができる。

【0025】

(ステップS102)

次に、ICS部10の制御部11は、FF−NN部120を用いて、FF−NN逆ダイナミックス処理を行う。

この処理においては、制御対象2の非線形特性に対する逆ダイナミックスを獲得し、システム特性を線形化するための学習を行う。

ここで、制御対象の位相遅れを改善するために、FF−NN部120は、オフラインでPD補償器部111(図3)のPD制御系の逆ダイナミックス特性をBP法により学習する。

FF−NN部120による制御では、位相の遅れに対しての改善が期待できる。

【0026】

(ステップS103)

次に、ICS部10の制御部11は、FB−FN部130を用いてFB−FN学習処理を行う。

ここで、上述のFF−NN部120の制御だけでは、制御対象2のモータ230の軌道等の目標になる信号(目標軌道信号)に対し、非線形誤差が発生する。これは入力補償としてNNが制御対象の非線形特性の一部のみの補償に限定されるためである。

このため、本ステップにおいて、FB−FN部130を用いた非線形動特性の補償のための学習を行う。

FB−FN部130は、上述したように、差分部140から取得した目標信号r(t)と出力信号y(t)との偏差信号e(t)=r(t)−y(t)の二乗が最小となるように学習する。この学習は、制御中であるオンライン状態又は制御後のデータを用いたオフライン状態で実行可能である。

これらの学習後に制御システムXが構成される。

【0027】

このように、FF−NN部120とFB−FN部130とを用いて学習することで、制御における追従性の向上及び誤差低減を達成することができる。

よって、様々な制御系に対応する汎化能力をもたせることができ、知能化制御を実現することができる。

【0028】

(ステップS104)

また、ICS部10の制御部11は、PWM部150を用いて、ソフトウェアサーボ制御処理を行うことができる。

具体的には、上述の各学習時、及び学習後に構成された制御システムXにおいて、ICS部10の制御部11は、ソフトウェアサーボの処理を行い、実際の制御対象2を制御することが可能である。

以上により、開発/学習処理を終了する。

【0029】

〈モデル作成処理の詳細〉

ここで、図6のフローチャートを参照して、モデルの作成と知能コントローラ部1のICS部10への転送をするモデル作成処理の詳細について説明する。

【0030】

(ステップS111)

まず、制御装置3は、ユーザの指示を検知し、モデル作成処理を行う。具体的には、MATLAB/Simulinkソフトウェアにより制御システムブロック図を作成する。

より具体的に説明すると、MATLAB/Simulinkは、制御系設計支援ソフトウェアである。ここで、MATLABは、MATrix LABoratoryを略したものであり、行列・ベクトル演算に基づく数値解析ソフトウェアである。MATLABは、インタプリタ(対話)形式の高級フログラミング言語であり、BASIC言語に類似したMATLAB言語で記載された「Mファイル」が用いられる。MATLABは、制御ツールボックス、通信ツールボックスを始めとして、豊富なツールボックスを備えておりユーザが解析に利用できる。また、ブロック線図入力により制御系のシミュレータを構築できるSimulinkが準備されている。MATLAB/Simulinkにより設計されたコントローラを組み込みCPUにより実装するためのRealTime Workshopも製品化されているため、本実施形態で好適に利用できる。

Simulinkはアナログ計算機の機能をデジタル環境で実行させるソフトウェアであり、微分方程式の解析に便利なツールである。

【0031】

また、知能制御用ソフトウェアとして、Neural Network Toolbox、Fuzzy Logic Toolboxを適宜MATLAB/SIMULINKと合わせて用いることができる。

Neural Network Toolboxは、非線形システムに対し、パターン認識や同定、制御等で利用できるようなニューラルネットワークシステムの設計やシミュレーションに必要なMファイル群である。Neural Network Toolboxは、初期化、伝達関数、教師付ネットワーク/学習ルール、パーセプトロン、バックプロパゲーション(BP)、Levenberg−Marquardtバックプロパゲーション、Radial basisネットワーク、リカレントネットワーク(Elman,Hopfield)等に対応している。

Fuzzy Logic Toolboxは、ファジィ推論システムの作成、編集ができるプログラムである。Fuzzy Logic Toolboxは、ファジィ推論システムをグラフイカルツールまたはコマンド関数を使って簡単に作ることができる。SIMULINKを併用すれば、ブロック線図シミュレーション環境の中でファジィシステムをテストすることができる。また、Fuzzy Logic Toolboxは、Real−Time Workshopを使用できる環境ならば、SIMULINKの環境からリアルタイムまたはノンリアルタイムコードのいずれかを生成できる。

【0032】

作成されたモデルは、例えば、後述する実施例で示す図19A〜図20Cのようなものとなる。

【0033】

(ステップS112)

次に、制御装置3は、ユーザの指示を検知し、Cコード作成/コンパイル処理を行う。

この処理においては、MATLABのReal−Time Workshopによって作成したモデルから、例えばC言語で記載されたCコードやオブジェクトコードや実行コードを自動生成させる。

【0034】

(ステップS113)

次に、制御装置3は、ユーザの指示を検知し、モデル定義/ビルド処理を行う。

ここでは、ModelDefというソフトを使用し、モデルのパラメータや信号の定義を行う。

このモデル定義を行うことで、MATLAB/Simulinkで作成したモデル上のパラメータや信号を実行時に使用可能にする定義ファイルを作成することができる。

【0035】

(ステップS114)

次に、制御装置3は、ユーザの指示を検知し、VC(Virtual Console)画面作成処理を行う。

この処理においては、VCDesignerソフトウェアを用いて画面作成を行う。具体的には、制御装置3のPCの表示装置と、知能コントローラ部1の表示部に表示されるユーザインタフェイスとなる「VC画面」を作成できる。

また、VCDesignerでは、作成したモデルを実行するVC画面の設計ができる。

これにより、作成したモデルを実行するときに、ユーザが扱いやすいような画面の設計を行うことができる。

【0036】

(ステップS115)

次に、制御装置3は、ユーザの指示を検知し、実行コード転送処理を行う。

具体的に説明すると、制御装置3は、VCDesignerにより、プログラムを実行できる。ユーザは、制御装置3のエミュレータ等で実行テストを行った後で、実行コードのバイナリファイルや定義ファイルや各種データ等(以下、プログラム等という。)を転送する。

なお、制御装置3は、VCDesigner起勤時に制御装置3と知能コントローラ部1とが接続状態になっていれば、生成された実行コード等を自動的に転送することもできる。

【0037】

(ステップS116)

次に、知能コントローラ部1は、実行コード取得/実行処理を行う。

ここでは、知能コントローラ部1の制御部11が、上述の制御装置3から取得したプログラム等をICS部10の補助記憶手段に記憶する。

この実行コードを取得後に、実行コード等を知能コントローラ部1側単体で実行が可能となる。

【0038】

作成したプログラム等を実行するときも、VCDesignerを用いることができる。

具体的には、ユーザは、制御装置3と知能コントローラ部1が接続状態で、画面作成が終わったら、VCDesignerの実行ボタンを押下する。この実行ボタンを押下により、設計した画面が制御装置3と知能コントローラ部1の表示部上に描画され、実行可能となる。

なお、この実行においては、ステップ実行や、制御対象2からのデータの取得等を行うこともできる。知能コントローラ部1は、逐次、制御装置3に取得したデータ等を送信することもできる。また、所定時間後に、取得したデータを送信することもできる。

【0039】

(ステップS117)

次に、制御装置3は、制御結果取得分析処理を行う。

具体的には、制御装置3は、取得したデータやモデルの状態等を、MATLAB/Simulink、VCDesigner、又は解析用のソフトウェアで確認することができる。これにより、モデルの動作を確認し、下記で説明する学習処理を行うことが可能になる。

なお、VCDesignerを用いて実行している際には、ユーザは、知能コントローラ部1の画面のボタンでは指示ができず、制御装置3のユーザインタフェイスの画面で指示を行う。制御装置3で実行テストを行ったあとで、知能コントローラ部1単体で実行が可能となる。

以上により、モデル作成処理を終了する。

【0040】

〈FF−NN逆ダイナミックス処理の詳細〉

次に、図7〜図9Bを参照して、FF−NN逆ダイナミックス処理の詳細について説明する。この処理では、古典的なPD制御の結果の信号を用いて、フィードフォワードによる、FF−NN部120の学習を行う。

図7は、このFF−NN逆ダイナミックス処理に用いるICS部10の各部と制御対象との関係を示すブロック図である。このように、制御対象の動特性を改善するため、ニューラルネットワークであるFF−NN部120を用いる。FF−NN部120のニューラルネットワークは、サーボ系である制御対象2の逆ダイナミックスをオンライン又はオフラインで学習し、それをフィードフォワード補償器として利用する。

以下で、図8のフローチャートを基に、このFF−NN逆ダイナミックス処理の詳細をステップ毎に説明する。

【0041】

(ステップS201)

まず、知能コントローラ部1の制御部11は、ICS部10のPD補償器部111等を用いて、FF−NN用意処理を行う。

ここでは、図7のブロック図に示したように、従来の古典PD補償器であるPD補償器部111により、制御対象2の特性を把握する試験を行い、指令信号の変位(y)、速度(dy/dx)、加速度(d2y/dt2)の各信号を取得する。この取得においては、差分部140の速度算出部141により速度を、加速度算出部142により加速度を算出する。また、この試験は、摩擦、ガタ等の非線形特性が、この動作により含まれることが重要点である。

また、このPD制御の際のPDゲインは制御対象2が移動可能な小さい値とする。

なお、速度、加速度信号は、変位信号収得後、オフラインにて差分部140が数値演算処理により算出してもよい。

【0042】

(ステップS202)

次に、制御部11は、FF−NN部120を用いてFF−NN学習処理を行う。

ここで、まず、位置と速度フィードバック則を適用したプラントの動特性は非線形特性を2次系として近似し線形化すると、以下の式(1)にて表現できる。

【0043】

【数1】

【0044】

ここで、u(t)は入力、y(t)は位置、kp,kvは、それぞれ、位置と速度のフィードバックゲインである。ただしkvについては、サーボモータの逆起電力定数keが含まれているものとする。サーボ系の逆ダイナミックスは、r(t)を目標軌道とすると、上述の式(1)をy(t)=r(t)として逆に解くことにより、以下の式(2)となる。

【0045】

【数2】

【0046】

つまり、変位r(k)、速度dr/dt(k)、加速度d2r/dt2(k)からu(t)の関係をFF−NN部120のニューラルネットワークに学習させる。したがって、ネットワークへの入力I(k)を[3*1]の列ベクトルとし、下記の式で表せる:

I(k)=[r(k),kp/kv・dr/dt(k),J/kp・d2r/dt2(k)]T

各ユニットの入出力関係は線形関数f(x)=xを用いる。また、ネットワークの出力はプラントの入力の推定値φkとなる。

中間層の出力をψi(k)とすると、ニューラルネットワークの出力は、次の式(3)のように表せる。

【0047】

【数3】

【0048】

ただし、nは中間層のユニット数、mは入力層のユニット数である。

ニューラルネットワークの学習は、評価関数として、以下の式(4)を定義し、バックプロパゲーション(BP)法により行う。

【0049】

【数4】

【0050】

すなわち、式(4)は、FF−NN部120のニューラルネットワークから計算されるプラント入力の推定値から、制御対象2であるプラントからの信号の入力を引いて2乗して1/2で割ることで求める。

【0051】

〔FF−NN部120のニューラルネットワークの構成例〕

次に、図9Aを参照して、FF−NN補償器であるFF−NN部120のニューラルネットワークの構成例について説明する。FF−NN部120では、3層3入力4中間ユニット1出力のニューラルネットワークを用いた。

入力信号は変位r、速度dr/dt、加速度d2r/dt2の信号である。これにより、プラントの動特性を2次系として近似し、線形化する。

具体的には、FF−NN部120入力として、NN学習処理で収得した変位、速度、加速度のデータを入力することができる。データは所定量、例えば1秒間に100程度とする。この場合、サンプリング周波数は10msecである。

【0052】

FF−NN部120のニューラルネットワークの学習に必要なソフトウェアとしては、以下に示すMATLAB用のニューラルネットワーク生成コマンドの例を入力して用いることができる。

【0053】

P=[変位;

速度;

加速度];

T=[教師信号];

net=newff([-5 5 ; -5 5 ;-5 5],[3 1],{'tansig','purelin'},'trainlm');

y=sim(net,P);

plot(P,T,P,y,'o');

net.trainParam.show=10;

net.trainParam.epochs=20000;

net.trainParam.goal=(0.0037^2);

net=train(net,P,T);

y=sim(net,P);

plot(P,T,P,y,'o');

gensim(net,-1);

return

【0054】

ここで、P=変位、速度、加速度、T=教師信号である。

ただし、教師信号は操作信号yとし、特性把握に必要な時間(3周期程度)とする。

【0055】

図9Bを参照して説明すると、MATLABによりニューラルネットワークの学習が終了すると、ニューラルネットワーク(NN)のブロックが生成される。

このNNのブロックを制御ブロックとして、FF−NN部120に用いる。

以上により、FF−NN逆ダイナミックス処理を終了する。

【0056】

〈FB−FN学習処理の詳細〉

次に、図10〜図17を参照して、FB−FN学習処理の詳細について説明する。

図10は、FB−FN学習処理に対応するICS部10の各部の関係を示すブロック図である。

具体的には、FB−FN部130は、ファジィ・ニューラルネットワークにより、ファジィPDとファジィPIの制御を行う。

ファジィ・ニューラルネットワークは、ニューロの学習能力とファジィの推論能力とを相補的に組み合わせて、それぞれの長所を生かし短所を補うよう融合したものである。

本実施形態のFB−FN部130は、非線形摩擦により変化および速度の制御誤差が生じた場合、制御ゲインを適応調整するファジィ・ニューラルネットワークによる非線形偏差補償特性により、制御誤差を減少させる特徴がある。

ここで、制御対象2の実際のモデルには、製品ごとに慣性モーメント等の値がバラツキ、2次モデルで表現できない非線形要素が存在する。すなわち、制御対象2の制御においては、目標軌道信号に対して制御対象の非線形摩擦誤差が発生する。

そこで、モデル化誤差、摩擦、未知な外乱等により生じる偏差信号を適応的に減少させる作用が働くように、ファジィPIDコントローラであるFB−FN部130によりフィードバック補償を行う。このため、FB−FN補償器であるFB−FN部130を、取得したデータを用いて学習させ、非線形誤差信号を減少させる。

このようにFB−FN部130を学習させることで、軌道誤差やモデル誤差による偏差を、ファジィPIDによるフィードバックによって押さえられる。これにより、知能化とロバスト性を兼ね備える、インテリジェント・ロバスト制御システム(IRCS)を実現できる。

以下で、図11のフローチャートを参照して、このFB−FN学習処理の各ステップの詳細について説明する。

【0057】

(ステップS301)

まず、知能コントローラ部1の制御部11は、ICS部10のFB−FN部130のファジィ・ニューラルネットワーク設定処理を行う。

ここで、図12A〜図12Dを参照して、ファジィPD部131とファジィPI部132に共通に使われる、本発明の実施の形態に係るファジィ・ニューラルネットワーク(FNN)の構成について説明する。

ファジィ・ニューラルネットワークは、BP法による学習を可能としながら、階層型ニューラルネットワークの結合を工夫してファジィ推論ルールとの対応関係を持たせ、ニューラルネットワークの獲得した入出力関係に関するパターンの知識をファジィルールというシンボルの知識として把握することができる。また、ファジィ推論システムにおける問題点であるファジィルールの同定、メンバーシップ関数の調整の困難さを、ニューラルネットワークの学習機能により改善できる。

【0058】

まず、Fuzzy Logic Toolboxによるファジィ・ニューラルネットワークの作成方法について説明する。

まずは、Fuzzy Logic Toolboxのメニューを呼び出す。メニューには:

1) メンバーシップ関数エディタ

2) FISエディタ

3) ルールエディタ

4) ルールビューワ

5) サーフェスビューワ

が存在する。

ここで、本実施形態におけるファジィ・ニューラルネットワークを用いたファジィ推論システムにおいては、まずはFISエディタを選択してモデルを作成する。

その際に、

a) tipperと入力するとウィンドウが表示される。

b) メンバーシップ関数エディタを使用し、メンバーシップ関数の名前、位置、型を設定する。

・Range [0 10]

また、ガウス曲線を設定する。

Gauss2mf

2つのガウス曲線の組み合わせによるメンバーシップ関数の作成を行う。

たとえば、以下の式(5)を用いることができる。

【0059】

【数5】

【0060】

このようにして、本実施形態に係るファジィ推論システムが作成できる。

【0061】

〔ファジィ・ニューラルネットワークの構造、構成例〕

図12Aは、本発明の実施の形態に係るファジィ・ニューラルネットワークの構造を示す。

この図12Aの例では、(A)層の入力層は、変位誤差信号epと変位時間微分の速度誤差信号evを入力信号としており、この入力信号を次層のユニットに分配している。

次に、(B)層の中間層では、メンバーシップ関数を内部関数に持ちガウス関数を用いる。各ユニットの出力はメンバーシップ関数の値であり、前件部と呼ぶ。

(C)層はファジィルールで推論する後件部であり、(B)層で入力空間を9分割し、分割された空間の適合度をファジィルールの前件部適合度の式により計算し、(C)層の全ユニットで得られる前件部適合度の総和で規格した値μiを出力する。

(D)層は入力の総和を出力する線形ユニットである。

以上により、ファジィルール的構造を持つニューラルネットが構成でき、これをファジィ・ニューラルネットワークと称する。このファジィ・ニューラルネットワークはBP法による学習を可能としながら、階層型ニューラルネットワークの結合を工夫して、ファジィ推論ルールとの対応関係を持たせることができる。

【0062】

図12Bは、本発明の実施の形態に係るファジィPD部131とファジィPI部132の全体構成を示す概念図である。

このように、ファジィPD部131とファジィPI部132とをパラレルに組み合わせることにより、全体としてファジィPIDを実現することができる。

【0063】

(ステップS302)

次に、制御部11は、ICS部10のFB−FN部130のFNN学習処理を行う。

図13は、FB−FN部130のファジィPD部131とファジィPI部132の学習過程を表わすブロック図である。

ファジィ・ニューラルネットワークの学習は、上述のPD補償器部111によるPD制御の特性把握試験のデータを基にして、変位誤差、速度誤差を入力とする。この上で、PIDの操作量を求めて、これを教師信号として、BP法と最小二乗法を組み合わせた方法でファジィPD部131とファジィPI部132の学習を行う。

FB−FN部130のニューラルネットワークでは、フィードバックゲインの学習を位置誤差の2乗:

Ep =1/2ep2

が最小となるように行う。また、kij≧0(j=I,p,v)の条件を常に満たすように、kij=Wijとする。

より具体的に説明すると、学習に利用する入力データは、サーボ系がスムーズに動作するようにゲイン調整した線形PD制御および線形PI制御の位置誤差epとその変化分であるevとし、教師データは線形PD制御及び線形PI制御の出力信号Uとする。また、大きな誤差(ステップ)の学習については、方形波のステップ信号を入力データとし、教師データは上記同様の線形PD制御および線形PI制御の出力信号Uとする。

【0064】

ここで、図13を参照して、ファジィPD部131のファジィPD学習について説明する。

ファジィPD部131のファジィPD学習は、モデル化誤差、非線形摩擦を補償するための学習の根拠となる。すなわち、制御対象2の実際のモデルには、慣性モーメント等のバラツキ、2次モデルで表現できない非線形要素が存在するため、これを学習する。

これらのモデル化誤差、非線形摩擦の誤差を表わすと、以下の式になる:

e = Td + fd(y)

ここで、Tdは、未知の外乱としてモデル化誤差を含める。

fd(y)はsgn(y’){(Fs−Fc)exp(−|y’|/e)+Fc}とする。

ファジィPD学習は、上述の式で示されるモデル化誤差及び非線形摩擦誤差の偏差出力信号をフィードバックPD出力信号として獲得した教師信号により逆ダイナミックスとして学習する。

学習方法は非線形誤差学習方式としてuPDの2乗であるE(uPD)=l/2uPD2を評価関数とし、BP法で結合荷重を修正する。

【0065】

ここで、図13を更に参照して、ファジィPI部132のファジィPI学習について説明する。

ファジィPI部132のファジィPI学習は、クーロン摩擦、未知外乱による定常偏差の学習の根拠となる。つまり、制御対象2では、クーロン摩擦により定常偏差が生じる。これは、加速度が0のときの位置偏差である。また、未知外乱による定常偏差も発生する。

これらの誤差を表わすと、以下の式になる:

e = eFC + eTd

ここで、eFCはクーロン摩擦により発生する定常偏差eTdは未知外乱により発生する定常偏差である。ファジィPI学習は、上記の式で示されるクーロン摩擦および未知外乱による定常偏差を、フィードバックPI出力信号として獲得した教師信号により逆ダイナミックスとして学習する。

非線形誤差学習の方式としては、式としてuPIの2乗であるE(uPI)=1/2uPI 2を評価関数として、BP法で結合荷重を修正する。

【0066】

(ステップS303)

次に、制御部11は、ICS部10のFB−FN部130のメンバーシップ関数設定処理を行う。

図14を参照して、このメンバーシップ関数設定処理の説明をする。

上述したように、ファジィPD部131、ファジィPI部132における、ファジィ・ニューラルネットワークの前件部には、メンバーシップ関数を用いる。本実施の形態においては、このメンバーシップ関数に、ここではガウス関数を使用する。

上述のFNN学習処理による学習結果、メンバーシップ関数の形が決定されることにより、パラメータが自動調整される。

図14及び図12Aの下部は、この調整されたメンバーシップ関数の例である。

【0067】

(ステップS304)

次に、制御部11は、ICS部10のFB−FN部130に対して、ファジィルール設定処理を行う。

図15は、ファジィPD部131及びファジィPI部132のファジィルールの設定方法を示す概念図である。

本発明の実施の形態に係るファジィ・ニューラルネットワークでは、制御ゲインを適応調整するため、誤差入力量に対応して出力を調整するファジィルールを設定する。

つまり、FB−FN部130のゲインをマトリックス状に配置するために、ファジィPD部131、ファジィPI部132における後件部に以下に示すファジィルールを設定する。

【0068】

より詳細に説明すると、図12Bにおける出力UFNは、プラントの直接的な入力である。ファジィ部では、入力空間を9分割し、分割された空間の適合度を以下の式で与える。

μi=Ai1(ep)Ai2(ev)

ここで、i=1,2,…,9, i1,i2=1,2,3

また、Aijはメンバーシップ関数でファジィ変数を表す。

また、Ai1,Ai2はそれぞれPositive big、Small、Negative bigに対する適合度を表す。

ただし、適合度は、下記の式(6)のように正規化しておく。

【0069】

【数6】

【0070】

そして、制御ゲインを適応調整するため、誤差入力量に対応して出力を調整するファジィルールを設定する。

ここで、図12Cのように、ファジィ分割として9を設定し、ファジィルールは以下のように設定する。

i番目のファジィルールは:

Ri: IF ep is Ai1 and ev is Ai2 THEN y=fi(ep,ev)

ここで、i=1,2, ... ,9, i1,i2=1,2,3

である。

また、uFN-PD出力は、下記の式(7)として求める。

【0071】

【数7】

【0072】

ここで、各uFNの加算出力であるuFN-PID出力は、下記の式(8)で求める。

【0073】

【数8】

【0074】

また、ファジィ推論は、下記の式(9)で求める。

【0075】

【数9】

【0076】

ここで、fは、uFN-PIDとuFNが等しいとすると、下記の式(10)となる。

【0077】

【数10】

【0078】

ただし、kij≧0(j=I,p,v)は、後述するフィードバックゲインである。

ここで、式(10)の制御方法においては、誤差応答によりファジィPDとファジィPIを切り換える動作を行う。この際、外乱やパラメータ変動による制御系の影響に対し、応答を速やかに目標値に近づけるため、図15内の表で示すように、外乱やパラメータ変動による制御系の影響に対し、応答を速やかに目標値に近づけるために図15に示すように、変位誤差信号epと速度誤差信号evがいずれもSmallのときはPID制御、epがSmallでなくevの絶対値|ev|がbigのときは、ダンピングを小さくし速い応答を得るためにP制御、その他はPD制御とすることが好適である。

各フィードバックは、後段のニューラルネットワークで事前に学習することにより、制御則を構成する。各フィードバックゲインは後段のニューラルネットワークで事前に学習する。このような構成により制御則を構成する。つまり、誤差に適応した制御則を構成することができる。

図16Aは、このフィードバックであるファジィ・ニューラルネットワークゲインの計算方法を示す。

【0079】

また、図16Bに、FB−FN部130のゲインマトリックスを示す。

フィードバックゲインkijはファジィ分割された誤差空間ごとに学習するので、誤差量に依存するダイナミック補償器としての役割を果たす。このように、制御ゲインを適応調整するため、誤差入力量に対応して出力を調整する、上述のi番目のファジィルールを設定する。

すなわち、ファジィ推論の効果として、誤差が少ないときは低いゲインとなる。ただし、ゲインの最適調整は、ニューラルネットワークの学習により行われる。つまり、モデル化誤差、摩擦、未知な外乱等により位置と速度の誤差が生じると大きなゲインとなり、誤差の減少が期待できる。また、後述する図16BのC7の部分のように大きな誤差に対しては、フィードバックの効果が期待できる。このような構成により、外乱やパラメータ変動にロバストとなることが期待できる。

【0080】

図16Cは、ファジィ・ニューラルネットワークによるゲインスケジューリングのブロック図を示す。

このゲインスケジューリングにより決定されたCi=μi(kipep+kiv+kiI∫fepdt)式により、図16BのC1〜C9の各ゲインが算出される。

【0081】

図16Dは、ファジィPD部131のファジィPDゲインマトリックスを示す。これはファジィPDについて入力のCpとCvが9個のウィンドウに分割された入力空間で図16Aに示す通り計算がされたゲインである。入力誤差に対して制御ゲインが適応調整される。

図16Eは、ファジィPD部131のファジィPD制御面を示す。これはファジィPDについてCpとCvの入力に対する制御出力がどのように変化するかを表わしている。図16Eの制御面によれば、ステップ状の大きな外乱に対してロバスト性及びロバスト安定性を有することがわかる。

【0082】

〔ロバスト安定性の根拠〕

ここで、図17を参照して、本発明の実施の形態に係るFB−FN部130のロバスト安定性の根拠について説明する。

FB−FN部130は、パラメータ変動が微小ではなく、ある有限な範囲で生じるとし、その変動範囲で制御性能を保証する制御系を設計する必要がある。そこで、パラメータの変動範囲をカバーする多数の基準点を仮定しこの点におけるパラメータ感度を小さくすることが好適である。また、各基準点での感度を小さくする割合はメンバーシップ関数を用いることにより、システムの要求に応じて設定できる。

また、ファジィ・ニューラルネットコントローラの誤差のロバスト性を確保するには、パラメータがある基準点まわりで微小変動することを前提とし、その変動に対するパラメータ感度を最小化する必要がある。図17に、そのメンバーシップ関数と、ファジィPIの制御面を示す。

ここで、図17の古典PIの制御面に示す通り、eかe・(eの上点)の移行方向に順じた、あるいは逆らった方向にeかe・が摂動すると、duの変化が増大する。

これに対して、図17のファジィPIの制御面においては、制御誤差であるeかe・の変化量が小さいときはファジィPIには、さほど影響しない。すなわち、ファジィPIの制御面はe−e・が、ほぼ平行であり、摂動すると、eとe・が2つ以上のルールが作動する過渡的な領域に入っていくだけで、制御出力には影響しない。つまり、定常偏差を減少させる機能が働いていることがわかる。

これにより、ファジィPIDコントローラのロバスト性の根拠が説明できる。

【0083】

(ステップS304)

次に、制御部11は、ICS部10のFB−FN部130に対して、ファジィ推論処理を行う。

このファジィ推論処理においては、上述したシングルトン出力のメンバーシップ関数を使用して、ダイナミックスな非線形システムの種々の操作条件に適用する複数の線形コントローラを内挿的に組み込むことができる。

本実施の形態に係るこのファジィ推論処理においては、入力空間をスムーズに内挿して線形ゲインを求め、効果的なゲインスケジューラとし、非線形システムをモデル化できる。

つまり、ファジィ推論システムを使い、入出力データからBP法等のアルゴリズムを使ってチューニングする。ここでは、推論システムのパラメータを同定するためのハイブリッドな学習アルゴリズムを使う。非線形パラメータに対し、上述したように、最小二乗法とバックプロバゲーション勾配降下法(BP法)を適用する。

以上により、FB−FN学習処理を終了する。

【0084】

〔ファジィPD部131の例〕

以下で、作成して学習させたファジィPD部131であるFUZZY_PDのMファイルの例を示す:

[Input1]

Name='input1'

Range=[-0.2868 0.2804]

NumMFs=3

MF1='in1mf1':'gauss2mf',[0.0478592834462299 -0.371325 0.0319561439415608 -0.217974284608918]

MF2='in1mf2':'gauss2mf',[0.0608664733050278 -0.0978076222858487 0.0555142362386605 0.0852892043051262]

MF3='in1mf3':'gauss2mf',[0.0138714984932358 0.20884527353354 0.0478592834462299 0.361225]

[Input2]

Name='input2'

Range=[-1.0472 1.0472]

NumMFs=3

MF1='in2mf1':'gauss2mf',[0.177881957852323 -1.36136 0.178084149908005 -0.73222056738112]

MF2='in2mf2':'gauss2mf',[0.150801124394399 -0.302584545101134 0.1487581237134 0.303271696091688]

MF3='in2mf3':'gauss2mf',[0.178465822406237 0.732532304938343 0.177881957852323 1.36136]

[Output1]

Name='output'

Range=[-9.121 8.9183]

NumMFs=9

MF1='out1mf1':'linear',[29.9502149922501 0.502141541225866 -0.0114363187815991]

MF2='out1mf2':'linear',[0.699802412554496 2.88172200515163 -3.69267448235734]

MF3='out1mf3':'linear',[2.42419964633644e-009 1.94710601114873e-009 -4.46135969104574e-008]

MF4='out1mf4':'linear',[29.8646225385097 0.522490654609605 0.00109243397029133]

MF5='out1mf5':'linear',[29.9872760919535 0.502942439065712 -0.000137735051368041]

MF6='out1mf6':'linear',[29.9929707105531 0.500833500934634 0.000342857488096674]

MF7='out1mf7':'linear',[1.73151335707348e-014 7.40165806871063e-014 9.36256379708729e-014]

MF8='out1mf8':'linear',[0.60924632277904 2.59412276828522 3.30948675859052]

MF9='out1mf9':'linear',[29.9947186987529 0.494510357242337 0.00687566067744605]

[Rules]

1 1, 1 (1) : 1

1 2, 2 (1) : 1

1 3, 3 (1) : 1

2 1, 4 (1) : 1

2 2, 5 (1) : 1

2 3, 6 (1) : 1

3 1, 7 (1) : 1

3 2, 8 (1) : 1

3 3, 9 (1) : 1

【0085】

〔ファジィPI部132のファイル例〕

以下で、作成して学習させたファジィPI部132であるFUZZY_PIのMファイルの例についても示す:

[System]

Name='FNN_PI'

Type='sugeno'

Version=2.0

NumInputs=2

NumOutputs=1

NumRules=9

AndMethod='prod'

OrMethod='probor'

ImpMethod='prod'

AggMethod='sum'

DefuzzMethod='wtaver'

[Input1]

Name='input1'

Range=[-0.2275 0.2108]

NumMFs=3

MF1='in1mf1':'gauss2mf',[0.0372257745066239 -0.293245 0.0620222208404797 -0.145616701160321]

MF2='in1mf2':'gauss2mf',[0.0509989814349655 -0.0938664146504105 0.061773470568765 0.0711977845073082]

MF3='in1mf3':'gauss2mf',[0.0451928100610181 0.122287868166051 0.0372257745066239 0.276545]

[Input2]

Name='input2'

Range=[-1.0472 1.0472]

NumMFs=3

MF1='in2mf1':'gauss2mf',[0.177881957852323 -1.36136 0.194858188187073 -0.725976617084914]

MF2='in2mf2':'gauss2mf',[0.184472713520267 -0.318507248879403 0.182769544067602 0.316484420470913]

MF3='in2mf3':'gauss2mf',[0.189973693378099 0.727208320141822 0.177881957852323 1.36136]

[Output1]

Name='output'

Range=[-7.2538 6.6378]

NumMFs=9

MF1='out1mf1':'linear',[43.4662552481124 15.4046594018716 18.8528571837822]

MF2='out1mf2':'linear',[-72.3728068591604 -8.21719705183032 -35.8241392764794]

MF3='out1mf3':'linear',[-0.746178588917306 -0.0969956028725818 -409.511443589854]

MF4='out1mf4':'linear',[43.6763652955075 4.47961924229057 -1.2979557058011]

MF5='out1mf5':'linear',[-188.845013085459 16.3752420684739 2.26580569880905]

MF6='out1mf6':'linear',[52.6504877364809 13.6637475028015 -2.81582668956971]

MF7='out1mf7':'linear',[1.36664656988905 -101.944112740175 561.037900146712]

MF8='out1mf8':'linear',[-37.7754372896572 -2.37931907009803 20.5924135196645]

MF9='out1mf9':'linear',[77.3693139104994 7.01860325733576 -18.4498686710174]

[Rules]

1 1, 1 (1) : 1

1 2, 2 (1) : 1

1 3, 3 (1) : 1

2 1, 4 (1) : 1

2 2, 5 (1) : 1

2 3, 6 (1) : 1

3 1, 7 (1) : 1

3 2, 8 (1) : 1

3 3, 9 (1) : 1

【0086】

〈ソフトウェアサーボ制御処理の詳細〉

次に、図18を参照して、本発明の実施の形態に係るソフトウェアサーボ制御処理について説明する。

本発明の実施の形態に係るソフトウェアサーボ制御処理においては、DCモータ駆動用PWM(パルス幅変調)モジュールと位置検出用エンコーダのアップダウンカウンタモジュールを、ソフトウェアで作成して実現する。これにより、ハードウェア部品の省力化と、ハードウェアによる動作時間遅れやノイズの対策ができる。

PWM部150のPWMモジュールについて、設計によりソフトウェア化を行っている。すなわち、本実施形態においては、MATLAB/Simulinkによりロジック回路を作成し、PWMモジュールを実現させている。すなわち、図18のように、制御部11が信号の振幅を変更して出力することで、モータ230の駆動ができる。このPWMモジュールの例を、後述する実施例の図20A〜図20Cに示す。

また、COUNTER(カウンタ)モジュールについても、設計によりソフトウェア化を行っている。すなわち、本実施形態においては、MATLAB/Simulinkによりロジック回路を作成し、COUNTERモジュールを実現させている。このCOUNTERモジュールの例を、後述する実施例の図20F〜図20Hに示す。

このように、知能コントローラの演算処理の高速化により、インテリジェント・ロバスト制御を実現することができる。

【0087】

以上のように構成することで、以下のような効果を得ることができる。

まず、従来、産業界で問題となっている現代制御理論(Model Based Control)による電子制御の不具合が多発していた。これは、制御ゲインが固定ゲインであることに起因するものであった。

本発明の実施の形態に係る制御システムXは、次世代のファジィ・ニューラルネットワークベースト制御によるインテリジェント・ロバスト組み込み知能コントローラであるICS部10を用いることで、この問題を唯一解決することができる。

ICS部10には、目標軌道誤差の変化に適応的にゲインを可変調整するファジィ・ニューラルベースト制御の新規インテリジェント・ロバストゲイン補償器であるFB−FN部130が組み込まれている。これにより、システムパラメータ変動、突発的な外乱および目標変化に対して、十分な目標軌道追従制御性能が得られる。

【0088】

また、本発明の実施の形態に係る制御システムXの制御方法は、従来のPID制御方法を多変数系に拡張させることができる。

すなわち、本実施形態の制御方法は、非線形の運動方程式を直接使用して、FF−NN部120のニューラルネットワークにより線形化を行い、FB−FN部130のファジィ・ニューラルネットワークにより外乱抑制および非干渉化を行う。

本実施形態の制御方法は、時間によってパラメータが変化する非線形系がいつも臨界減衰となるように、時間によってゲインが適応的に変化する制御則を考案し、多変数系における各軸の相互干渉を非干渉化させる。このことにより、インテリジェント制御による多変数系制御を行い、マニピュレータの完全追従制御を実現することができる。

【0089】

また、本実施形態に係る制御システムXは、ファジィの推論能力とニューラルネットワークの学習能力を組み合わせることで、制御ゲインを可変調整し、未知の要素に対して適応させることができる。

実際に、下記の実施例にて構築したファジィ・ニューラルネットワーク制御システムを従来のPID制御、FF−NN制御のみのシステムと比較する実験を行ったところ、ファジィ・ニューラルネットワーク制御の有効性は高かった。

【0090】

また、従来、マニピュレータに関するシステム設計は、制御対象が多自由度系でも1自由度系と見なし近似式を用いて制御系を設計し、関節軸ごとに独立した制御系を構築する手法が多くの製品に採用されていた。

本実施形態に係る制御システムXは、この多自由度系設計化の未解決な課題を、インテリジェント制御により解決することができる。

すなわち、本実施形態に係る制御システムXは、ロバストで自動的なゲイン調整が可能な制御系を構築するために、ファジィ分割された空間において位置誤差に応じた可変フィードバックゲインが設定される制御系を、多自由度系化の設計に用いることができる。

【0091】

また、本実施形態に係る制御システムXは、ファジィ・ニューラルネットワークの学習によるゲインの自動設定ができ、インテリジェント制御によるロバスト性を実現することができる。

これにより、マニピュレータおよび多変数系メカニカルシステムに対する実用的なインテリジェント・ロバスト制御システムを実現し、ロボット、自動車、電動自転車、船舶、航空機、宇宙機、ロケット、温度制御、電動制御等、目標値を設定して制御する従来の制御が用いられていたあらゆる制御対象機器について、応用可能である。

また、本実施形態に係る制御システムXは、モデル化誤差、摩擦、未知の外乱等により変位および速度の制御誤差が生じた場合、制御ゲインを適応調整するファジィ・ニューラルネットワークによる非線形偏差補償が可能になる。

すなわち、ファジィ・ニューラルネットワークによるインテリジェント・ロバスト制御手法が確立し、多変数系メカニカルシステムに対する実用的なインテリジェント制御システムを実現することができる。

【0092】

また、本実施形態に係る制御システムXは、組み込み型コンビュータを知能コントローラ部1として用いて、通常のPC等による制御装置3によるRTW(Real−Time Workshop)を用いたモデルベースでのシステム開発により、短期間でのシステム開発を行うことが可能である。

さらに、MATLAB/Simulinkのようなソフトウェアを用いることで、シミュレーションも簡単に行えるため、システム開発のコストダウンや時間削減に大きな効果が得られる。

【0093】

また、本実施形態に係る制御システムXは、目標軌道誤差の変化に適応的にゲインを可変調整する新しい方式のインテリジェント・ロバストゲイン補償器(ファジィ・ニューラルベースド制御)が組み込まれており、システムパラメータ変動、外乱および目標変化に対して、十分な目標軌道追従制御性能が得られる。具体的には、ロバストで自動的なゲイン調整が可能な制御系を構築するために、ファジィ分割された空間において位置誤差に応じた可変フィードバックゲインが設定される制御系を構成している。

また、本実施形態に係る制御システムXは、制御系を2自由度制御構成とし、フィードフォワード部をニューラルネットワークにより構成し、変位、速度、加速度のパラメータによりプラントの特性を学習させ、プラント特性の逆特性を取得しシステムを線形化している。

また、フィードバック部は、ファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であり、完全追従性能を実現させている。

これらの制御系は、リアルタイム(実時間)処理で、例えばサンプリング時間が1ミリ秒で実行されていることを特徴とする。

【実施例】

【0094】

ここで、図19A〜図21Bを参照して、実際に上述のICS部10の構成と各処理を用いて、インテリジェント・ロバスト制御を行った実施例について説明する。

本実施例においては、組み込み型コンピュータであるICS部10を含む知能コントローラ部1によって制御対象2の位置制御を行う。制御対象2としては、DCモータによって駆動する移動テーブルを用いた。

ICS部10のOSには、Linux(登録商標)+Xenomai(商標)を用いており、リアルタイムでの制御が可能である。パソコンである制御装置3は、知能コントローラ部1とLANクロスケーブルにより直接接続して、イーサネット(登録商標)で通信を行った。

知能コントローラ部1は、知能コントローラ部1のD/Aコンバータから制御信号を送出する。この制御信号は、モータ駆動ドライパ20を介して、モータ230へと出力される。モータ230が回転すると、エンコーダ220からパルス波が出力される。このパルス波は、知能コントローラ部1のA/Dコンパータによって、知能コントローラ部1が取得する。このパルス波を1/8に分周させてあり、このパルス波をカウントすることによりモータ230の位置情報をフィードバックすることができる。

【0095】

また、本実施例では、モータ駆動ドライバ20として、東芝セミコンダクター社製のTA7281Pを用いた。また、モータ230として、ツカサ電工社製のTG−47C−SMを用いた。TG−47C−SMは、定格電圧12[V]、定格回転数4400[rpm]、定格電流160[mA]、無負荷回転数5250[rpm]、無負荷電流60[mA]である。

また、エンコーダ220として、TG−47C−SMに付属のロータリエンコーダを用いた。当該ロータリエンコーダは、1回転につき8パルス出力する。

【0096】

(実験方法)

本実施例では、MATLAB/Simulinkによりファジィ・ニューラルネットワークの制御システムXのためのモデルを構築した。また、比較のため、従来のPID制御、NN−PIDのみの制御システムのモデルも同様に構築した。

これらの制御システムのモデルを図19A〜図19Cに示す。また、この各制御システムの各部位のモデル図を、図20A〜図20Hに示す。

【0097】

より具体的には、図19Aは、従来のPID制御のモデル図である。このモデルのPIDパラメータについては、比例ゲインP=12、積分ゲインI=0、微分ゲインD=0、としてモータ駆動ドライバ20の制御を行った。

また、図19Bは、NN−PID制御のみの場合のモデル図である。FF−NN部120のニューラルネットワークの学習にはPID制御のデータを基にして行い、指令信号の変位、速度、加速度を入力とし、PIDの操作量を教師信号としてBP法で学習を行った。これによって得られたニューラルネットワークをPIDの操作量にフィードフォワードさせている。PIDパラメータはPID制御と同様である。

また、図19Cは、本実施例に係るファジィ・ニューラルネットワーク制御のモデル図である。FNNの学習には、図19AのPID制御のデータを基にして行い、変位誤差、速度誤差を入力とし、PIDの操作量を教師信号としてBP法と最小二乗法を組み合わせた方法で学習を行った。この際に、図19BのNN−PID制御のパラメータ等も、ファジィ・ニューラルネットワークの制御システムに用いた。

【0098】

制御対象2は、1つのDCモータ230によって動く移動テーブルとし、構築した制御システムにより位置制御を行う。指令信号は振幅5、周期30[s]のsin波とし、サンプリングタイムは1[msec]でモータの制御を行った。

また、比較のための動作テストとして外乱あり、外乱なしの状態で3つの制御システムを実行し性能比較を行った。外乱はモデル上で再現し、実行してから10秒後に+5の値を操作量に加えるようにした。

【0099】

(実験結果)

図21Aと図21Bを参照して、実験結果について説明する。

図21Aは、従来のPID制御のモデル(比較例)を用いて制御を行った結果である。従来のPID制御では、外乱がない場合には、1自由度の位置制御でも時間遅れがあり若干の誤差が見られた。さらに、従来のPID制御では、外乱が発生すると定常情差として誤差が現れ、外乱の信号に合わせて出力が上にずれていた。なお、図示しない図19BのNN−PIDのみの制御は、フィードフォワード補償により時間遅れを多少解消できていた。しかし、NN−PIDのみの場合、外乱がない場合にはそれほど制御信号とはズレないものの、外乱がある場合には従来のPID制御と同様な結果であり、ロバスト性がなく不十分であった。

図21Bは、本実施例に係るファジィ・ニューラルネットワーク制御を用いた結果である。ファジィ・ニューラルネットワーク制御では、制御対象の非線形要素に対応できると考えられる。すなわち、ファジィ・ニューラルネットワーク制御では外乱あり、外乱なしの両方で指令信号に追従できていたことから、制御ゲインを適応的に調整していると考えられる。このことから、ファジィ・ニューラルネットワーク制御はロバスト性のある制御方法であり、外乱や制御機器の非線形要素に対して有効であった。

【0100】

なお、上記実施の形態の構成及び反応及び動作は例であって、本発明の趣旨を逸脱しない範囲で適宜変更して実行することができることは言うまでもない。

【産業上の利用可能性】

【0101】

本発明は、インテリジェント・ロバスト制御を行う制御手段を提供することで、様々な装置の制御に使用でき、産業上利用可能である。

【符号の説明】

【0102】

1 知能コントローラ部

2 制御対象

3 制御装置

10 ICS部

11 制御部

14 補助記憶部

15 主記憶部

16 論理回路部

17 I/F部

18、19 コネクタ

20 モータ駆動ドライバ

21 テーブル部

110 PID部

111 PD補償器部

120 FF−NN部

130 FB−FN部

131 ファジィPD部

132 ファジィPI部

140 差分部

141 速度算出部

142 加速度算出部

150 PWM部

160 カウンタ部

170 出力部

180 入力部

190 制御信号発生部

195 外乱シミュレート部

210 テーブル

220 エンコーダ

230 モータ

X 制御システム

【特許請求の範囲】

【請求項1】

制御対象の目標軌道誤差の変化に適応的にゲインを可変調整する組み込み知能コントローラにおいて、

ファジィ・ニューラルネットワークにより非線形誤差を減少させる補償器であるフィードバック手段を備え、

該フィードバック手段は、

前記制御対象の非線形動特性のPD(比例、微分)補償を行うファジィPD手段と、

前記制御対象の非線形動特性のPI(比例、積分)補償を行うファジィPI手段とを並列に備える

ことを特徴とする組み込み知能コントローラ。

【請求項2】

前記フィードバック手段は、

ファジィ分割された空間において位置誤差に応じた可変フィードバックゲインを設定する

ことを特徴とする請求項1に記載の組み込み知能コントローラ。

【請求項3】

制御系を2自由度制御構成とし、

前記制御対象の変位、速度、及び加速度のパラメータをニューラルネットワークにより学習させ、前記制御対象の特性の逆特性を取得するフィードフォワード手段を備える

ことを特徴とする請求項1又は2に記載の組み込み知能コントローラ。

【請求項4】