絶縁ゲート型サイリスタ

【目的】優れたオン特性を維持しながら、ターンオフ能力の向上を図った絶縁ゲート型サイリスタを提供することを目的とする。

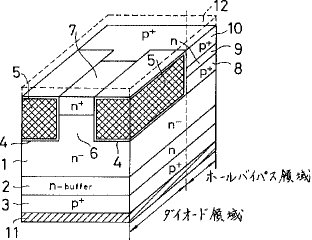

【構成】n- 型ベース層1の一方の面に少なくとも一対の溝4が形成され、この溝4内に絶縁ゲート電極5が埋込まれ、溝4に挟まれた領域の表面部にn+ 型カソード層7が形成され、n- 型ベース層1の他方の面にはn型バッファ層2を介してp+ 型アノード層3が形成されて、絶縁ゲート型サイリスタが構成されている。絶縁ゲート電極5の端部側面に接して、p+ 型ソース層8,n型チャネル層9およびp+ 型ドレイン層10がn- 型ベース層1に連続して形成されて、ターンオフ時にホールを排出するための縦型MOSトランジスタが構成されている。

【構成】n- 型ベース層1の一方の面に少なくとも一対の溝4が形成され、この溝4内に絶縁ゲート電極5が埋込まれ、溝4に挟まれた領域の表面部にn+ 型カソード層7が形成され、n- 型ベース層1の他方の面にはn型バッファ層2を介してp+ 型アノード層3が形成されて、絶縁ゲート型サイリスタが構成されている。絶縁ゲート電極5の端部側面に接して、p+ 型ソース層8,n型チャネル層9およびp+ 型ドレイン層10がn- 型ベース層1に連続して形成されて、ターンオフ時にホールを排出するための縦型MOSトランジスタが構成されている。

【発明の詳細な説明】[発明の目的]

【0001】

【産業上の利用分野】本発明は、小さいゲート電力で大きい主電流を制御することができる絶縁ゲート型サイリスタに関する。

【0002】

【従来の技術】ゲート電力低減のために絶縁ゲート構造を採用した各種サイリスタが提案されている。

【0003】図139は、その様な絶縁ゲート型サイリスタの一種である。このサイリスタは、p型アノード層,n型ベース層、p型ベース層およびn型エミッタ層のpnpn4層構造を持つ。p型ベース層内にはn型エミッタ層に隣接してn型ソース層が形成され、これをエミッタとする寄生サイリスタがラッチアップするのを防止するためにこれとオーバーラップして高濃度p型層が形成されている。n型エミッタ層とn型ソース層の間のp型ベース層上にゲート絶縁膜を介してゲート電極が形成されている。カソード電極は、n型エミッタ層ではなく、n型ソース層と高濃度p型層に同時にコンタクトして配設されている。p型エミッタ層にはアノード電極が形成されている。

【0004】この絶縁ゲート型サイリスタは、ゲート電極に印加する電圧によってn型ソース層とn型エミッタ層の間のチャネルをオン,オフすることにより、ターンオン,ターンオフ制御がなされる。

【0005】この絶縁ゲート型サイリスタでは、p型ベース層が高濃度p型層を介してカソード電極と常にコンタクトしているため、所謂カソードショートとなり、電子の注入効率が低く、サイリスタのオン電圧が高いという問題があった。

【0006】また、この絶縁ゲート型サイリスタでは、p型エミッタ層,n型ベース層,p型ベース層およびn型ソース層からなるpnpn構造が寄生サイリスタとなり、またn型エミッタ層,p型ベース層およびn型ソース層からなるnpn構造が寄生バイポーラトランジスタとなる。これらの寄生素子が動作するとゲートによる制御が不能になるため、ターンオフ能力が著しく低いという問題があった。

【0007】図140および図141は、埋込み絶縁ゲート構造を用いた絶縁ゲートサイリスタの例である(H.R.Chang,IEDM,1989)。これらは、いゆわる静電誘導サイリスタ(SIサイリスタ)の一種である。

【0008】図140(a) のものは、高抵抗のn型ベース層の一方の面にn型バッファ層を介してp型アノード層(ドレイン層)が形成されている。n型ベース層の他方の面には所定間隔をもって一対の溝が形成されて、ここに絶縁ゲートが埋込み形成されている。溝の間がチャネル領域であって、その表面部にn型カソード層(ソース層)が形成されている。溝の外側には、ホール排出のための高濃度p型層が形成されている。カソード電極はn型エミッタ層および溝の外側の高濃度p型層に同時にコンタクトして設けられている。p型アノード層にはアノード電極が設けられている。

【0009】この素子は、ゲート電極にバイアスを印加しなければオンしているノーマリオン型である。ターンオフするには、ゲート電極にカソード電極に対して負の電圧を印加する。これにより、溝の間のn型ベース層領域が空乏化し、n型カソード層からの電子注入が止まる。n型ベース層内に蓄積しているホールは、p型ウェルを介してカソード電極に排出される。このホール排出部分は、pnpトランジスタになっている。

【0010】図140(b) は、図140(a) と各部の導電型を逆にしただけである。

【0011】図141の素子は、図140(b) の素子を3次元的に展開した構造である。すなわち、オン状態で電流通路となるダイオード領域は、ストライプ状のアノード領域とゲート領域が交互に配列された状態として、これらダイオード領域のストライプ端部にキャリア(図の場合電子)排出用のトランジスタ領域が形成されている。

【0012】これらの埋込み絶縁ゲートを持つSIサイリスタでは、ターンオフ時のキャリア排出用バイポーラトランジスタ領域がダイオード領域に並列に寄生トランジスタとして設けられている。SIサイリスタがオン状態ではこのバイポーラトランジスタもオンであって、そのベースにはキャリア蓄積が生じる。このため、ターンオフ時のキャリア排出に時間がかかる。また、ターンオフ時に絶縁ゲートにより制御されるのは、電子,ホールのうち一方の注入のみであり、これもキャリア排出に時間がかかる原因となっている。したがって、ターンオフ能力が低い。

【0013】また上述した従来のSIサイリスタは、ノーマリオン型であるため、何等かの原因でゲートバイアスが印加できなくなると、ターンオフできずにオン状態のままになるため、フェールセーフの観点からも問題であった。

【0014】

【発明が解決しようとする課題】以上のように従来の絶縁ゲート型サイリスタは、一般にターンオフ能力が低く、特に優れたオン特性を維持しながら高速のターンオフを行なわせることが難しい、という問題があった。

【0015】本発明は、第1に、優れたオン特性を維持しながら、高速のターンオフを行うことのできる絶縁ゲート型サイリスタを提供することを目的とする。

【0016】本発明は、第2に、寄生バイポーラトランジスタや寄生サイリスタ動作を抑制して、ターンオフ能力の向上を図った絶縁ゲート型サイリスタを提供することを目的とする。

【0017】本発明は、第3に、ゲートバイアスが零ではオフ状態に保たれるノーマリオフ型とした絶縁ゲート型サイリスタを提供することを目的とする。

【0018】本発明は、第4に、素子の有効導通面積を確保しながら、ターンオフ能力の向上を図った絶縁ゲート型サイリスタを提供することを目的とする。

【0019】

【課題を解決するための手段】本発明に係る絶縁ゲート型サイリスタは、ターンオフ時のキャリア排出部に絶縁ゲート型トランジスタ構造を導入したことを特徴とする。

【0020】

【作用】本発明によれば、キャリア排出部に絶縁ゲート型トランジスタ構造を導入することによって、優れたオン特性を維持しながら、高速でターンオフできる絶縁ゲート型サイリスタが得られる。また、寄生バイポーラトランジスタや寄生サイリスタ動作を抑制し、高いターンオフ能力を実現することができる。

【0021】

【実施例】以下、図面を参照しながら本発明の実施例を説明する。なお以下の各実施例では原則として、通常種々の繰り返しパターンで一つの基板上にレイアウトされるサイリスタの単位セル部分のみ構造を示す。

【0022】図1は、本発明の一実施例に係る絶縁ゲート型サイリスタである。高抵抗のn- 型ベース層1の一方の面に所定間隔をもってストライプ状に一対の溝4が形成されている。溝4には、内壁にゲート絶縁膜が形成されてゲート電極材料が平坦に埋め込まれた絶縁ゲート電極5が設けられている。溝4に挟まれた領域のn- 型ベース層1の表面には、n+ 型カソード層(ソース層)7が形成されている。n- 型ベース層1の他方の面には、n型バッファ層2を介してp+ 型アノード層(ドレイン層)3が形成されている。これにより、カソード層7下の溝4で挟まれた領域がチャネル領域6となるSIサイリスタが構成されている。

【0023】絶縁ゲート電極5とカソード層7が形成された領域がダイオード領域であって、その端部,すなわちストライプ状のゲート電極5の端部に接する領域が、ターンオフ時にn- 型ベース層1内のホールをカソード側に排出するホールバイパス領域である。絶縁ゲート電極5の側面部に接する状態で縦方向に、p+ 型ソース層8,n型チャネル層9およびp+型ドレイン層10が形成されて、絶縁ゲート電極5をSIサイリスタ部と共有するホール排出用の縦型のpチャネルMOSトランジスタが構成されている。

【0024】素子裏面のp+ 型アノード層3にはアノード電極11が形成され、素子表面には、仮想的に破線で示したが、n+ 型カソード層7およびp+ 型ドレイン層10に同時にコンタクトするカソード電極12が形成される。

【0025】この絶縁ゲート型サイリスタの動作を説明する。絶縁ゲート電極5にカソードに対して正の電圧を印加すると、チャネル領域6には空乏層が形成されないので、n+ 型カソード層7から電子が注入されてターンオンする。

【0026】絶縁ゲート電極5にカソードに対して負の電圧を印加すると、チャネル領域6に空乏層が拡がり、n+ 型カソード層7からの電子注入が抑制される。このとき同時に、ゲート電極5の端部に形成された縦型pチャネルMOSトランジスタがオンとなり、n- 型ベース層1内に蓄積しているホールがこのMOSトランジスタを通してカソード電極に排出される。これにより、サイリスタはターンオフする。

【0027】この実施例によれば、従来のようなサイリスタと同時にオンする寄生バイポーラトランジスタがない。すなわちホール排出領域にはホールの蓄積は少なく、ターンオフ時のn- 型ベース層1のホール排出が縦型MOSトランジスタによって速やかに行われる。これによりターンオフ時間の短縮が図られる。

【0028】図2は、図1の実施例の各部の導電型を逆にした実施例である。高抵抗のp- 型ベース層21の一方の面にストライプ状に一対の溝24が形成され、溝24には絶縁ゲート電極25が埋込み形成されている。溝24に挟まれた領域のp- 型ベース層21の表面に、p+ 型アノード層27が形成されている。p- 型ベース層21の他方の面にはp型バッファ層22を介してn+ 型カソード層23が形成されている。アノード層27下の溝24で挟まれた領域がチャネル領域26となる。

【0029】絶縁ゲート電極25とアノード層27が形成された領域がダイオード領域であって、その端部に接する領域が、ターンオフ時にp- 型ベース層21内の電子をアノード側に排出する電子バイパス領域である。すなわち絶縁ゲート電極25の側面部に接する状態で縦方向に、n+ 型ソース層28,p型チャネル層29およびn+ 型ドレイン層30が形成されて、絶縁ゲート電極25をSIサイリスタ部と共有する、電子排出用の縦型のnチャネルMOSトランジスタが構成されている。

【0030】素子裏面のn+ 型カソード層23にはカソード電極12が形成されている。素子表面には、p+ 型アノード層27およびn+ 型ドレイン層30に同時にコンタクトするアノード電極11が形成される。

【0031】この実施例によっても、先の実施例と同様に短いターンオフ時間が得られる。

【0032】図3は、カソード側とアノード側に共に埋込み絶縁ゲート電極を設けた実施例の絶縁ゲートサイリスタである。n- 型ベース層1のカソード側には、図1の実施例と同様の構造で第1の埋込み絶縁ゲート電極5およびn+ 型カソード層7が形成される。n- 型ベース層1の他方の面にはp- 型チャネル層32を介してp+ 型アノード層3が形成されている。そしてこのアノード側にも、n- 型ベース層1に達する溝35がカソード側と同様にストライプ状をなして形成され、この溝35に第2の絶縁ゲート電極36が埋込み形成されている。

【0033】この様に構成されたダイオード領域の端部には、n- 型ベース層1のカソード側にp+ 型層33、アノード側にn+ 型層34が形成されて、逆並列ダイオードが構成されている。

【0034】サイリスタのp+ 型アノード層3および逆並列ダイオードのカソード層であるn+ 型層34に同時にコンタクトするアノード電極11が形成され、サイリスタのn+ 型カソード層7および逆並列ダイオードのアノード層であるp+ 型層33に同時にコンタクトするカソード電極(図示せず)が形成されている。

【0035】この素子をターンオンするには、第1のゲート電極5にカソード電極に対して正の電圧を印加する。第2のゲート電極36は零バイアスのままでよい。これにより、n+ 型カソード層7から電子注入がなされて、ターンオンする。

【0036】ターンオフ時は、第1のゲート電極5にカソードに対して負の電圧を印加し、同時に第2のゲート電極36にアノードに対して正の電圧を印加する。これにより、n+ 型カソード層7からの電子注入が抑制されると同時に、アノード側ではp- 型チャネル層33の電位が上昇して空乏化し、p+ 型アノード層3からのホール注入が抑制される。また、n- 型ベース層1内の蓄積キャリアは、ホールがp+ 型層33を介してカソード電極へ、電子がn+ 型層34を介してアノード電極11へそれぞれ排出される。

【0037】こうしてこの実施例によれば、ターンオフ時には、カソード側,アノード側で共にキャリア注入が抑えられ、さらに逆並列ダイオードによって蓄積キャリアの排出がなされるため、高速のターンオフができる。

【0038】図4は、図3の実施例のキャリア排出を行う逆並列ダイオードの部分を、縦型MOSトランジスタ構造とした実施例である。カソード側には、図1の実施例と同様に、第1の絶縁ゲート電極5の端部に接してp+ 型ソース層8,n型チャネル層9およびp+ 型ドレイン層10が形成されて縦型のpチャネルMOSトランジスタが構成されている。アノード側には、第2の絶縁ゲート電極36の端部にに接してn+ 型ソース層37,p型チャネル層38およびn+ 型ドレイン層39が形成されて、縦型のnチャネルMOSトランジスタが構成されている。

【0039】この実施例の素子は、ターンオフ時、第1の絶縁ゲート電極5に負の電圧を印加することによってカソード側のpチャネルMOSトランジスタがオンし、第2の絶縁ゲート電極36に正の電圧を印加することによってアノード側のnチャネルMOSトランジスタがオンする。これらの縦型MOSトランジスタによって、n- 型ベース層のキャリア排出が行われる。サイリスタがオン状態では、これらの縦型MOSトランジスタはオフに保たれる。

【0040】したがってこの実施例によれば、優れたオン特性を維持しながら、高速のターンオフが可能になる。

【0041】図5は、カソード側からの溝4をp+ 型アノード層3に達するまで深く形成した実施例である。キャリア排出領域は、n- 型ベース層1の表面にp+ 型層10が形成されて、pnpトランジスタが構成されている。このキャリア排出領域の構造は、従来の図141のそれと同様である。

【0042】この実施例の素子は、ターンオン時、絶縁ゲート電極5に正の電圧を印加すると、溝4の側壁にn+ 型カソード層7からn型バッファ層2にまで達する電子蓄積層が形成され、n+ 型カソード層7がこの蓄積層を介してn型バッファ層2につながるため、速やかに定常オン状態にまで素子電圧が降下する。ターンオフ時は、絶縁ゲート電極5に負の電圧を印加すると、溝4の側壁にp型チャネルが形成される。n- 型ベース層1内のホールはこのp型チャネル層を介し、p+ 型層10を介してカソード電極に排出される。

【0043】従ってこの実施例の素子は、ターンオン,ターンオフともに高速になる。

【0044】図6は、図5の実施例の素子の各部の導電型を逆にした実施例である。詳細な説明は省略するが、この実施例の素子でも高速のターンオン,ターンオフが可能である。

【0045】図7は、図5の実施例の素子を変形した実施例である。この実施例では、溝4がウェハのカソード側表面からアノード側表面にまで貫通する状態で形成されて、この中に絶縁ゲート電極5が埋込み形成されている。

【0046】この実施例の素子は、製造する際に溝4が基板を貫通して設けられるので、ゲート絶縁膜の形成時、溝4内に酸素が十分に供給されて、均一な膜厚のゲート絶縁膜が得られる。埋込みゲート電極5をCVD法による多結晶シリコンで形成する場合にも同様に、原料ガスが溝4内に十分に供給されるので、均一に電極埋込みが行われる。

【0047】以上の図1から図7の実施例において、溝間のチャネル領域となる部分が低いバイアス状態で完全空乏化する素子を得るためには、その幅と不純物濃度を最適設計する必要がある。具体的に例えば、チャネル領域の不純物濃度を5×1013/cm3 とする。このとき、ゲート電極側から伸びる空乏層の飽和値は5μm 以上となるから、溝を反応性イオンエッチングによって間隔5μm 以下の狭い状態で加工すれば、しきい値の浅い素子が容易に得られる。

【0048】図8は、溝間隔を更に微小値に設定した実施例の素子である。図8(a) に示すように、半導体基板中央部に高抵抗のn- 型ベース層1が設けられている。基板の一方の面にはn- 型ベース層1に達する深さの第1の溝4が、例えば1μm 以下の微小間隔をもって形成されて、この中に第1の絶縁ゲート電極5が埋込み形成されている。基板の他方の面にも同様に微少間隔の第2の溝35がn- 型ベース層1に達する深さに形成されて、ここに第2の絶縁ゲート電極36が埋込み形成されている。

【0049】第1の溝4の間にはn- 型ベース層1に接するn型チャネル層42が形成され、その表面部にn+ 型カソード層7が形成されている。第2の溝35の間にも、n- 型ベース層1に接するn型チャネル層43が形成され、その表面部にp+ 型アノード層3が形成されている。アノード層3にはアノード電極11が形成され、カソード層7にはカソード電極12が形成されている。

【0050】この素子をオン電圧の小さい十分なオン状態にするには、図8(b) に示すように、第1の絶縁ゲート電極5にカソードに対して正の電圧を印加し、第2のゲート電極36にアノードに対して負の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42は高濃度の電子蓄積層42aとなり、ここまで実質的なカソード層となる。第2の絶縁ゲート電極36に挟まれた領域のn型チャネル層43は逆にp型反転層43aとなり、低濃度のアノード層3は高濃度のホール蓄積層となって、これら全体が実質的なアノード層となる。この結果、カソード・アノード間距離が実質的に小さいものとなり、順バイアス時のカソードからの電子注入,アノードからホール注入の効率が大きく向上し、低いオン電圧が得られる。

【0051】この素子をオフにするには、図8(c) に示すように、第1の絶縁ゲート電極5にカソードに対して負の電圧を印加し、第2のゲート電極36にアノードに対して正の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42はp型反転層42bとなり、第2の絶縁ゲート電極36に挟まれた領域のn型チャネル層43は逆に高濃度の電子蓄積層43bとなる。これにより、カソード・アノード間はpnpn構造となって、カソードからの電子注入、アノードからのホール注入が止り、素子はターンオフする。

【0052】この実施例によれば、ターンオン時のキャリア注入効率の向上およびターンオフ時のキャリア注入の抑制が効果的に行われる。なおこの実施例において、ターンオフ時のn- 型ベース層1内のキャリア排出のための構造として、先の各実施例で用いたものを利用することができる。

【0053】図9は、図8の実施例を変形した実施例である。この実施例では、図8のアノード側のn型チャネル層43に代ってp型チャネル層44を用いている。

【0054】この素子をオン状態にするには、図8の実施例と同様、図9(b) に示すように、第1の絶縁ゲート電極5にカソードに対して正の電圧を印加し、第2のゲート電極36にアノードに対して負の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42は高濃度の電子蓄積層42aとなり、第2の絶縁ゲート電極36に挟まれた領域のp型チャネル層44は高濃度のホール蓄積層44aとなる。従って先の実施例と同様に、順バイアス時のカソードからの電子注入,アノードからホール注入の効率が大きく向上し、低いオン電圧が得られる。

【0055】この素子をオフにするには、図9(c) に示すように、第1の絶縁ゲート電極5にカソードに対して負の電圧を印加し、第2のゲート電極36にアノードに対して正の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42はp型反転層42bとなり、第2の絶縁ゲート電極36に挟まれた領域のp型チャネル層44はn型反転層44bとなる。これにより、カソード・アノード間はpnpn構造となって、カソードからの電子注入、アノードからのホール注入が止り、素子はターンオフする。

【0056】なお以上において、図1の実施例に対して図2の実施例を示したように、他の実施例についても各部の導電型を逆にして構成することができる。またオン時のエミッタ注入効率を高くするために、エミッタ接合部にヘテロ接合を用いることも有用である。

【0057】次に、埋込み絶縁ゲート構造であって、溝間隔が大きいものであってもノーマリオフ型となる絶縁ゲート型のSIサイリスタの実施例を説明する。

【0058】図10は、その様な実施例のSIサイリスタの断面図である。高抵抗のn- 型ベース層1の一方の面にp型ベース層45が形成され、このp型ベース層45の表面にn+ 型カソード層(ソース層)7が形成されている。n- 型ベース層1の裏面にはp+ 型アノード層(ドレイン層)3が形成されている。カソード側には、n- 型ベース層1に達する深さの溝4が少なくとも一対形成され、この溝4に絶縁ゲート電極5が埋込み形成されている。

【0059】n+ 型カソード層7にはカソード電極12が形成され、p+ 型アノード層3にはアノード電極11が形成されている。またp型ベース層45には直接接続されたゲート電極46が設けられている。

【0060】この実施例の素子は、pnpn構造を有するから、ゲートバイアス零のときはオフであり、ノーマリオフ型となる。絶縁ゲート電極5にカソードに対して正の電圧を印加すると、p型ベース層45の溝4側壁部にn型チャネルが形成されて、n+ 型カソード層7からの電子がn- 型ベース層1に注入される。注入された電子がp+ 型アノード層に達すると、p+ 型アノード層3からはホールが注入され、サイリスタはターンオンする。

【0061】絶縁ゲート電極5をカソードに対して負または零とすることにより、カソード層7からの電子注入が止まり、素子はターンオフする。このとき、n- 型ベース層1内に蓄積されたホールはこのn- 型ベース層1に直接接続されたゲート電極46を介して外部に排出され、高速のターンオフができる。

【0062】なお、ゲート電極46は独立に端子として取り出してもよいし、カソード電極と短絡してもよいが、ツェナーダイオードかまたは、ターンオフ時に導通するように制御されるMOSトランジスタを設けておくことが好ましい。

【0063】この実施例によれば、ノーマリオフ型であって、高速のターンオン,ターンオフができるSIサイリスタが得られる。またオフ時には、n-型ベース層1とp型ベース層45のpn接合部でn- 型ベース層側に空乏層が伸びることによって、高耐圧特性が保証される。

【0064】p+ 型アノード層3の部分を、図に示すようにn+ 型層とすれば、サイリスタではなく、絶縁ゲート型のSIトランジスタとなる。このことは、図11以下の実施例でも同様である。

【0065】図11は、図10の実施例を変形して、溝4をアノード層3に達する深さに形成した実施例である。この実施例では、ターンオン時、n- 型ベース層1の溝4の側壁部に沿って電子蓄積層が形成されるため、速やかにカソード・アノード間が導通する。したがってより高速のターンオンができる。

【0066】また、ターンオフ時、絶縁ゲート電極5にカソードに対して負の電圧を印加すれば、n- ベース層1の溝4側壁部にはp型反転層が形成される。そしてn- 型ベース層1内の蓄積ホールはこのp型反転層を介し、p型ベース層45を介して外部に速やかに排出される。従って、ターンオフ動作も高速に行われる。

【0067】図12〜図15はやはり図10の実施例を変形した実施例であり、p型ベース層45とn+ 型カソード層7の間に低濃度のn-型チャネル層47が設けられている。溝4は、図12ではn- 型チャネル層47の途中まで、図13ではp型ベース層45の途中まで、図1414ではn- 型ベース層1の途中まで、図15ではアノード層3に達する深さまで形成されている。これら図12R>2〜図15の実施例でも、絶縁ゲート電極5にカソードに対して負の電圧を印加して、n- 型チャネル層47の電位を下げてカソード層7からの電子注入を抑制することにより、ターンオフすることができる。

【0068】なお図12の実施例では、絶縁ゲート電極5によってp型ベース層45の電位は制御されないから、ターンオン時にはp型ベース層45に接続されたゲート電極46にカソードに対して正の電圧を印加する。

【0069】図14の実施例では、ターンオン時、絶縁ゲート電極5に印加する正電圧によってp型ベース層45の溝4側壁にn型チャネルが形成されて、高速ターンオンができる。

【0070】図15の実施例では、図11の実施例と同様に、溝4の側壁に形成される蓄積層または反転層によって、高速のターンオン,ターンオフが可能である。

【0071】図16(a) は、図10の実施例について、p型ベース層45からのゲート電極46の取り出し方の具体的構造を示している。図に示すように、ストライプ状にパターン形成されるカソード層7の長手方向端部にp型ベース層45が露出しており、ここにゲート電極46が形成されている。

【0072】図16(b) は、この実施例の素子構造を等価回路で示したものである。ただしこの等価回路は、基本素子がpnpn構造を持つSIサイリスタではなく、npn構造のSIトランジスタの場合である。トランジスタTのドレイン・ソース間にEタイプMOSトランジスタQ1 が接続され、ドレインに直列にDタイプMOSトランジスタQ2 が接続された形になる。EタイプMOSトランジスタQ1 は、p型ベース層45をチャネル領域とするトランジスタであり、DタイプMOSトランジスタQ2 は、絶縁ゲート電極5がn- 型ベース層1中に埋め込まれた部分のn- 型ベース層1をチャネル領域とするトランジスタである。

【0073】図17(a) は、図14の実施例について、p型ベース層45からのゲート電極46の取り出し方の具体的構造を示している。図16と同様に、ストライプ状にパターン形成されるカソード層7およびn- 型チャネル層47の長手方向端部にp型ベース層45が露出しており、ここにゲート電極46が形成されている。

【0074】図17(b) は、この実施例の素子構造を、基本素子がSIトランジスタの場合について等価回路で示したものである。トランジスタTのドレイン・ソース間にEタイプMOSトランジスタQ1 が接続され、ドレインおよびソースにそれぞれ直列にDタイプMOSトランジスタQ2 およびQ3 が接続された形になる。EタイプMOSトランジスタQ1 は、p型ベース層45をチャネル領域とするトランジスタであり、ドレイン側のDタイプMOSトランジスタQ2 は、絶縁ゲート電極5がn- 型ベース層1中に埋め込まれた部分のn- 型ベース層1をチャネル領域とするトランジスタであり、ソース側のDタイプMOSトランジスタQ3 は、n- 型チャネル層47をチャネル領域とするトランジスタである。

【0075】図18(a) (b) は、図10および図16の実施例を変形して、ターンオフ時のホール排出用の縦型MOSトランジスタを導入した実施例である。図18(a) に示すように、ストライプ状の絶縁ゲート電極5の端部に、図1の実施例と同様にして、p型ソース層8、n型チャネル層9およびp型ドレイン層10が形成されて、ゲート電極5を共有する縦型のpチャネルMOSトランジスタが構成されている。

【0076】縦型MOSトランジスタのドレイン電極41は、実際にはカソード電極12と一体に連続的に形成される。カソード層7の端部には、図16或いは図17の実施例と同様にp型ベース層45が露出していて、ここにもゲート電極46が形成されている。ただし、このゲート電極46は必ずしも必要ではない。このゲート電極46を設けなければ、カソード側はドレイン電極41を兼ねてカソード電極12を全面に形成してた単層電極構造とすることができる。

【0077】この様な単層電極構造は、大電力用素子として、圧接電極構造を採用する場合に有利である。

【0078】図18(b) は、基本素子がやはりSIトランジスタである場合についての等価回路を示している。トランジスタTに並列に接続されるMOSトランジスタQ1、ドレインに直列接続されるMOSトランジスタQ2は、先の実施例と同様である。この実施例で導入されたホール排出用の縦型MOSトランジスタは、Q4 として、p型ベース層とソース間に挿入された形になる。

【0079】図19(a) (b) は、図14および図17の実施例を変形して、図18と同様に、ターンオフ時のホール排出用の縦型MOSトランジスタを導入した実施例である。等価回路は、図17(b) に対して、MOSトランジスタQ4 が付加された形になっている。

【0080】図20は、図18の実施例を変形した実施例である。この実施例では、素子のメイン・チャネルとp型ベース層45の露出部、およびターンオフ時のホール排出用縦型MOSトランジスタのチャネル領域を一列に並べて、埋込み絶縁ゲート電極5を、メイン・チャネルを制御するゲート電極(G1 )51 とホール排出用縦型MOSトランジスタのチャネルを制御するゲート電極(G2 )52 とに分離して別々に形成した実施例である。

【0081】この実施例の素子でのターンオフ時の二つのゲートG1 ,G2 の駆動例を図20(b) に示した。図に示すように先ず、ゲートG1 に負の電圧を印加してホール排出用MOSトランジスタを導通状態とし、これに遅れてゲートG2 に負の電圧を印加してメイン・チャネルでの電子注入を止める。

【0082】この実施例のようなゲート駆動によって、ターンオフ時のメイン・チャネルでの電子注入の抑制が効率的になり、高いターンオフ能力が得られる。

【0083】図21は、図19の実施例の素子について同様に、埋込み絶縁ゲート電極5を、メイン・チャネルを制御するゲート電極51 とホール排出用縦型MOSトランジスタのチャネルを制御するゲート電極52 とに分離して別々に形成した実施例である。図21(b) は、図2020(b) と同様のゲート駆動法を示している。

【0084】この実施例によっても、高いターンオフ能力が得られる。

【0085】図22は、図13の実施例の素子において、溝4の間隔を十分に小さく、例えば1μm 以下に設定した実施例である。図22(a) に示すように、n+ 型カソード層7とp型ベース層45の間にはn型ウェル層51(図13のn- 型チャネル層47に相当する)が設けられている。

【0086】この実施例の素子をターンオンするには、図22(b) に示すように、絶縁ゲート電極5にカソードに対して正の電圧を印加する。このとき、n型ウェル層51は全体が高濃度n+ の電子蓄積層51aとなり、実質的にカソード層がp型ベース層45に接する状態となる。この結果カソードの電子注入効率が向上する。

【0087】この実施例の素子をターンオフするには、図22(c) に示すように、絶縁ゲート電極5にカソードに対して負の電圧を印加する。この時、n型ウェル層51は全体が高濃度p+ の反転層51cとなる。これにより、カソードからの電子注入が効果的に抑制される。

【0088】図23は、図22の実施例の溝4をn- 型ベース層1に達する深さまで掘り下げた実施例である。図22の実施例と同様に、ターンオン時は図23(b) に示すようにゲート電極に正の電圧を与え、ターンオフ時は図23(c) に示すようにゲート電極5に負の電圧を与える。この実施例では、ターンオン時、p型ベース層45の側壁にn型チャネルが形成されるために、より高速のターンオン動作が可能になる。

【0089】なお図23の実施例に於いて、溝4の深さは、n- 型ベース層1内に食い込まないように、p型ベース層45とn- 型ベース層1の接合部ぎりぎりの位置までとすることが特性上好ましい。それ以上深くすると、溝4に挟まれた領域でn- 型ベース層1の電位が制御されて、サイリスタ特性が悪化する可能性があるからである。

【0090】図24は、図22の実施例のn型ウェル51の部分をp型ウェル52に置き換えた実施例である。この場合、ターンオン時にはゲート電極5に負の電圧を印加して、図24(b) に示すようにp型ウェル52をn型反転層52aとする。ターンオフ時はゲート電極5に正の電圧を印加して、図24(c) に示すようにp型ウェル52の部分をp型の電子蓄積層52cとする。

【0091】図25は、図23の実施例のn型ウェル51の部分をp型ウェル52に置き換えた実施例である。この場合、ターンオン時にはゲート電極5に負の電圧を印加して、図25(b) に示すようにp型ウェル52をn型反転層52aとする。ターンオフ時はゲート電極5に正の電圧を印加して、図25(c) に示すようにp型ウェル52の部分をp型の電子蓄積層52cとする。

【0092】なおこれら図22〜図25の実施例においても、先の実施例と同様に、n- 型ベース層1内のホール排出用の縦型MOSトランジスタを組み込むことは有効である。

【0093】図26(a) (b) は、図14の実施例のサイリスタ構造の場合の断面図と等価回路図を示している。図26(b) に示すように、サイリスタTh のnpnトランジスタ部分に対して並列にEタイプMOSトランジスタQ1 が入り、カソード側に直列にDタイプMOSトランジスタQ3 が入る。トランジスタQ1 は、p型ベース層45をチャネルとするnチャネルMOSトランジスタであり、Q3 はn- 型チャネル層47をチャネルとするnチャネルMOSトランジスタである。

【0094】図27(a) (b) は、図26(a) (b) の実施例に対して、n- 型ベース層1内のホール排出のための高濃度p+ 型層33を設けた実施例の断面構造と等価回路である。ストライプ状にパターン形成されるn+ 型カソード層7の端部に、p型ベース層45に繋がる深さのp+ 型層33が形成されている。図ではカソード電極を省略しているが、カソード電極はn+ 型カソード層7と同時にp+ 型層33にもコンタクトするように全面に配設される。

【0095】p型ベース層45の横方向抵抗Rが、図27R>7(b) に示すように、サイリスタのp型ベース層をカソードに短絡する抵抗Rとなる。

【0096】図28(a) 〜(c) は、アノード側に埋込み絶縁ゲート電極36を有する絶縁ゲートサイリスタにおいて、p+ 型エミッタ層3とn- 型ベース層1の間に低濃度のp- 型チャネル層54が設けられた実施例である。図28(a) では、絶縁ゲート電極36の埋込み溝35がp+ 型エミッタ層3からp- 型チャネル層54の途中まで達する深さに形成されている。図28(b) では、埋込み溝35がn- 型ベース層1に達する深さに形成され、図28(c) では埋込み溝35がp型ベース層45に達する深さに形成されている。

【0097】これらの実施例によっても、ゲートバイアスは逆になるが、先の図12〜図14の実施例で説明したと同様の原理で高速のターンオン,ターンオフが可能である。

【0098】図29(a) (b) は、図28(b) の実施例について、具体的にp型ベース層からのゲート電極46の取出しの構造と等価回路を示している。ゲート電極46の取り出し構造は、先の図16,図17等の実施例と同様である。等価回路は、図29(b) に示すように、サイリスタTh のアノード側に直列にDタイプのpチャネルMOSトランジスタQ5 が接続された形になる。

【0099】図30は、カソード側に埋込み絶縁ゲート電極5を設けると共に、アノード側にも同様に埋込み絶縁ゲート電極36を設けた別の実施例の絶縁ゲートサイリスタである。p型ベース層45には直接ゲート電極46が接続されている。p+ 型エミッタ層3とn- 型ベース層1の間にはp- 型チャネル層54が設けられている。

【0100】図31は、図30の構造を僅かに変形した実施例で、n+ 型エミッタ層7とp型ベース層45の間にn- 型チャネル層47が形成されている。

【0101】これら図30,図31の実施例においても、ターンオフ時、カソード側からの電子注入とアノード側からのホール注入が抑制でき、高速のターンオフ動作が可能である。

【0102】図32(a) (b) は、図31の素子構造のp型ベース層45からのゲート電極取り出し構造と等価回路を示す。ストライプ状に形成されるn+ 型エミッタ層7の端部に、n- 型ベース層1に達する深さにp+ 型層33が形成され、ここに図示しないゲート電極が接続される。図では、アノード側にも、n- 型ベース層1をアノード電極11に短絡するn+ 型層34が、やはりストライプ状に形成されるp+ 型エミッタ層3の端部に形成されている。

【0103】図33は、図26の実施例の素子構造を基本として、カソード側にエミッタ短絡用のpチャネルMOSトランジスタを組み込んだ実施例である。p型ベース層45上に、n- 型チャネル層47が形成され、さらにn型ウェル層56(n型エミッタ層)が形成されている。このn型ウェル層56表面からn- 型ベース層1に達する深さに溝4が形成されて、ここに絶縁ゲート電極5が埋込み形成されている。n型ウェル層56の溝4の側壁部にp+ 型ドレイン層57が形成され、カソード電極12はn型ウェル層56と同時にこのp+ 型ドレイン層57に接続されている。

【0104】この実施例の素子では、ターンオフ時、絶縁ゲート電極5にカソード電極に対して負の電圧を印加すると、溝4の側壁からn- 型チャネル層47にのびる空乏層によってn型ウェル層45からの電子注入が抑制される。同時に、n型ウェル層56およびn- 型チャネル層47の側壁に形成されるp型チャネルを介してn- 型ベース層1内のホールがカソード電極12に排出される。これにより、高速のターンオフ動作ができる。

【0105】図34は、図33の実施例に加えて、カソード側にもエミッタ短絡用のnチャネルMOSトランジスタを同様の構造をもって組み込んだ実施例である。すなわちn- 型ベース層1のアノード側に、所定厚みのp型ウェル層58(p型エミッタ層)が形成され、これを貫通する形で溝35とこれに埋め込まれた絶縁ゲート電極36が形成される。そしてp型ウェルの溝35の側壁部にn+ 型ドレイン層59が形成される。アノード電極14は、p型ウェル層58と同時にこのn+ 型ドレイン層59に接続される。

【0106】この実施例の素子のターンオフ駆動は、好ましくは次のように行う。まずアノード側のゲート電極36にアノード電極14に対して正の電圧を印加する。これにより、p型ウェル層58の溝35側壁に形成されるn型チャネルを介してn-型ベース層1がアノード電極14に短絡されたアノード短絡状態となり、アノード側からのホール注入が抑制される。その後カソード側のゲート電極5にカソード電極12に対して負の電圧を印加する。これにより、カソード側の電子注入を抑制すると同時に、ホールをカソード電極13に排出する。

【0107】この様なゲート駆動を行うことによって、効率的なターンオフができる。

【0108】図35は、図33の実施例の構造を3次元的に展開した実施例の絶縁ゲートサイリスタである。ストライプ状に埋込み形成される絶縁ゲート電極5に沿って、p型ドレイン層57が複数個に分割されて配置される。図33の素子断面では、絶縁ゲート電極5に挟まれた領域内にn型ウェル層56とp+型ドレイン層57が同時に形成されているのにたいして、この実施例では、図33と同じ素子断面について見ると、在る箇所ではp型ドレイン層57のみ、他の箇所ではn型ウェル層56のみが見える状態になっている。

【0109】図36は、同様に図34の実施例の素子を3次元的に展開した実施例の絶縁ゲートサイリスタである。カソード側のp+ 型ドレイン層57と同様に、アノード側のn+ 型ドレイン層59が、ストライプ状の埋込み絶縁ゲート電極36に沿って複数個に分割配置されている。

【0110】これら図35および図36の実施例では、埋込みゲート電極の間の領域の幅いっぱいをMOSトランジスタのドレイン領域として利用することができる。したがって、図33および図34の実施例と比較すると、溝4および35の間隔を狭くすることが容易である。溝4および35の間隔を狭くすれば、それだけターンオフ時の絶縁ゲート電極側からの空乏化によるキャリア注入の抑制効果が大きくなり、ターンオフ能力の向上が可能になる。

【0111】図37(a) (b) は、図27の実施例の素子構造に更に、カソード側に縦型のnチャネルMOSトランジスタを組み込んだ実施例の素子構造と等価回路である。p型ベース層45上にn- 型チャネル層47,n型ウェル層56が形成され、更にこの上にp型ウェル層61,n+型ソース層62が形成されている。n+ 型ソース層62の表面からn- 型ベース層1に達する深さに溝4が形成されて、絶縁ゲート電極5が埋込み形成されている。これにより、p型ウェル61の溝側壁をチャネル領域とするnチャネルMOSトランジスタQ6 が、図37R>7(b) に示すように、サイリスタのカソードに直列に入った状態になる。またストライプ状のカソード領域の端部には、n- 型ベース層1に達する深いp+ 型層10が拡散形成されている。

【0112】この実施例の素子をターンオンするには、絶縁ゲート電極5にカソード電極に対して正の電圧を印加する。この時、p型ウェル層61とp型ベース層45の溝側壁にn型チャネルが形成され、n+ 型ソース層62から電子がn- 型ベース層1に注入される。この電子注入に対応してp+ 型エミッタ層3からホール注入がなされて、高速にターンオンする。

【0113】ターンオフの際には絶縁ゲート電極5にカソード電極に対して負の電圧を印加する。これによりn型チャネルは消滅してn+ 型ソース層62からの電子注入は止まり、同時にn- 型チャネル層47に広がる空乏層によって電子注入が抑制される。n- 型ベース層1に蓄積していたホールは、p+ 型層10を介してカソード電極に排出される。以上により、素子はターンオフする。

【0114】この実施例によれば、カソード側の電子注入がカソード側に直列に入ったMOSトランジスタの導通状態と、その下のn- 型チャネル層への空乏層の広がりによって効果的に制御されるので、高いターンオフ能力が得られる。

【0115】図38(a) (b) は、図37の素子を変形した実施例の素子断面構造と等価回路である。この実施例では、ストライプ状の埋込みゲート電極5に沿って、n+ 型ソース層62が複数個に分割されて配置されている。したがってカソード側にはp型ウェル層61も露出しており、カソード電極(図では省略している)がn+ 型ソース層62と同時にp型ウェル層61にもコンタクトしている。図37の実施例で設けられているホール排出用のp+ 型層10はこの実施例では設けられていない。

【0116】したがってこの実施例の素子は、図38(b) に示すように、カソード側に直列にnチャネルMOSトランジスタQ6 が入ると同時に、p型ベース層とカソードの間に、p型ウェル層61の抵抗を介してn型ウェル層56およびn- 型チャネル層46をチャネルとするpチャネルMOSトランジスタQ4 が入った形になっている。

【0117】この実施例の素子では、pチャネルMOSトランジスタQ4 がターンオフ時のn- 型ベース層1のホール排出用として機能する。この実施例によると、先の実施例と異なり、n- 型ベース層1のホールが直接カソードに抜ける経路がないので、サイリスタのオン特性を損なうことなく、高いターンオフ能力を実現することができる。

【0118】図39(a) (b) は、さらに図37或いは図38の実施例の素子を変形した実施例の素子構造と等価回路である。この実施例では、埋込み絶縁ゲート電極5を長手方向に複数個に分割して配置し、その長手方向端部に挟まれた領域に、図1の実施例と同様の構造でpチャネルMOSトランジスタを形成している。

【0119】この実施例によっても、オン特性を損なうことなく、優れたターンオフ能力を持つ絶縁ゲート型サイリスタが得られる。またホール排出用のpチャネルMOSトランジスタは、サイリスタ本体の拡散層とは別個の拡散層を利用して形成しているので、その拡散層の不純物濃度をサイリスタ本体とは独立に設定することができ、所望のしきい値等特性の最適化が容易である。

【0120】図40(a) (b) は、図37の素子構造を基本として、これと図32の構造とを組み合わせた実施例の素子構造と等価回路である。アノード側にもp- 型チャネル層54が形成され、埋込み絶縁ゲート電極36が形成されている。ストライプ状ゲート電極36の端部には、アノード側,カソード側にそれぞれ、エミッタ短絡用のp+ 型層33,n+ 型層34が形成されている。

【0121】この実施例の素子も、ターンオフ時、カソード側の電子注入とアノード側のホール注入がそれぞれ、縦型のMOSトランジスタQ6 ,Q5により抑制され、高いターンオフ能力が得られる。

【0122】図41(a) (b) は、カソード側の構造を図3838と同様とし、アノード側の構造を図40と同様とした実施例の素子構造と等価回路である。

【0123】この実施例によっても、ターンオフ時、カソード側の電子注入とアノード側のホール注入がMOSトランジスタQ6 ,Q5 により抑制されて高いターンオフ能力が得られる。しかも、n- 型ベース層のホールが直接カソード電極に抜ける経路はないので、サイリスタのオン特性を損なうことはない。

【0124】図42(a) (b) は、図39と図40の構造を組み合わせた実施例の素子構造と等価回路である。

【0125】この実施例によっても、ターンオフ時、カソード側の電子注入とアノード側のホール注入がMOSトランジスタQ6 ,Q5 により抑制されて高いターンオフ能力が得られる。n- 型ベース層のホールが直接カソード電極に抜ける経路はないので、サイリスタのオン特性を損なうことはない。ホール排出用のpチャネルMOSトランジスタは、サイリスタ本体の拡散層とは別個の拡散層を利用しているので、その拡散層の不純物濃度の最適化が容易である。

【0126】以上の図1から図42までの実施例において、絶縁ゲート電極が埋め込まれる溝の間隔とその領域の不純物濃度は、溝側壁からの空乏層の伸び方を考慮して最適設定される。絶縁ゲート電極により形成される空乏層幅は、絶縁ゲート電極に印加するバイアスが小さい間は反転層の少数キャリアが無視できるのでバイアスに比例して大きくなる。バイアスが大きくなって反転層のキャリアが多くなると、空乏層幅は飽和して一定値になる。この空乏層幅の飽和値は、チャネル層の不純物濃度が低いほど大きいが、例えば、不純物濃度が5×1013/cm3 以下では5μm 以上伸びる。従って反応性イオンエッチングを利用して微細間隔のゲート埋込み用溝を形成すれば、溝間を比較的低いゲートバイアスで完全空乏化して、カソード或いはアノードからのキャリア注入を止めるという制御を容易に行うことができる。

【0127】次に、カソード・エミッタに直列にMOSトランジスタを挿入した構造のEST(Emitter Switched Thyristor)と呼ばれる絶縁ゲート型サイリスタの実施例を説明する。

【0128】図43は、その基本実施例の素子構造であり、従来の図139で示す構造を改良したものである。高抵抗のn型ベース層1の一方にn型バッファ層2を介してp型エミッタ層3が形成されている。n型ベース層1の他方の面にはp型ベース層45が形成され、このp型ベース層45の表面にn型エミッタ層7が形成されている。ストライプ状のn型エミッタ層7の一辺に対向してホール排出用の高濃度p+ 型層71がストライプ状に形成され、このp+ 型層71のn型エミッタ層7側の辺に重なるようにn型ソース層72が形成されている。n型エミッタ層7とn型ソース層72により挟まれた領域のp型ベース層45上にゲート絶縁膜73を介してゲート電極74が形成されている。カソード電極12はn型ソース層72とp+ 型層71に同時にコンタクトして形成され、p型エミッタ層3にはアノード電極11が形成されている。

【0129】ここで、n型ソース層72は、図に示すように、ストライプ状のp+ 型層71に対してその長手方向に複数個に分割されて短冊状をなして、p+ 型層71の端部に配列形成されている。この点で従来の構造と異なる。

【0130】なお図では省略されているが、ゲート電極74と別に素子のターンオン用のゲート電極が必要である。そのためには例えば、p型ベース層45のp型ウェル層71に対向する端部とは反対側(図の左側)のn型エミッタ層7とn型ベース層1で挟まれた領域にゲート絶縁膜を介してゲート電極が設けられる。このことは、以下に示す実施例でも同様である。

【0131】この実施例の絶縁ゲート型サイリスタのターンオン時は、図示しないターンオン用ゲート電極を用いてn型カソード層7からn型ベース層1に電子を注入する。このときゲート電極74には、カソード電極に対して正の電圧を印加する。これによりn型エミッタ層7はn型反転チャネルを介し、n型ソース層72とを介してカソード電極12に接続される。

【0132】ターンオフ時は、ゲート電極74に零または負の電圧を印加する。これにより、n型チャネル層が消失して、n型エミッタ層7はn型ソース層72と切り離されてフローティングとなり、カソードからの電子注入が止まり、素子は高速にターンオフする。

【0133】ターンオフ時、n型ソース層72,p型ベース層45,n型ベース層1およびp型エミッタ層3からなる寄生サイリスタは、n型ベース層1のホールをカソード電極に排出する際の障害になる。n型ソース層72が、もし、p型ウェル層71の辺に沿って連続的に形成されていると、n型エミッタ層7がn型ソース層72から切り離された後にもn型ソース層72からの電子注入が止まらず、ターンオフ能力は著しく小さいものとなる。これに対してこの実施例では、n型ソース層72が複数個に分割されて配置されているから、n型ソース層72からの電子注入量は抑えられ、寄生サイリスタ効果が低減されて高いターンオフ能力が得られる。

【0134】図44〜図47は、図43の実施例の素子構造を基本として、より効果的に寄生バイポーラトランジスタ効果の影響低減を図った実施例である。

【0135】図44(a) では、p型ウェル層71の底部により高濃度のp+ 型層75が設けられている。これにより、p型ベース層45の横方向抵抗が低減されて、寄生サイリスタ効果が抑制される。図44(b) では、n型ベース層1のp型ベース層45との接合部近傍に低キャリアライフタイム層76が設けられている。これにより、n型ベース層1内の過剰ホールの寿命が短くなり、寄生サイリスタ効果が抑制されてターンオフ能力が向上する。

【0136】図45(a) では、アノード側に、n型ベース層1の一部を表面に露出させてアノード電極11に短絡するエミッタ短絡部77が設けられている。これにより、ターンオフ時、アノード側からのホール注入が抑制されるから、やはりターンオフ能力が改善される。

【0137】図45(b) では更に、p型エミッタ層3が選択的に拡散形成されてこの中にn型ソース層78が形成され、p型エミッタ層3のn型ベース層1とn型ソース層78に挟まれた領域にはゲート絶縁膜79を介してゲート電極80が形成されている。この実施例では、ターンオフ時、ゲート電極80にアノードに対して正の電圧を印加することによって、アノード側のエミッタ短絡構造が形成され、高速にターンオフができる。オン状態ではゲート電極80を零バイアスまたは負バイアスとすることにより、エミッタ短絡構造が形成されないから、サイリスタのオン特性を損なうことがない。

【0138】図46(a) は、図45(a) と図44(a) の構造を組み合わせた実施例である。図46(b) は、図45R>5(a) と図44(b) の構造を組み合わせた実施例である。図47(a) は、図45(b) と図44(b) の構造を組み合わせた実施例である。図47(b) は、図45(a) と図44(a) および(b) の構造を組み合わせた実施例である。

【0139】図48は、図47(a) の実施例の素子構造において、カソード側のゲート電極74(G1 )とアノード側のゲート電極80(G2)の駆動信号波形例を示している。オン状態では、カソード側のゲート電極74に正電圧VG1を与えて、n型エミッタ層をチャネルを介し、n型ソース層72を介してカソード電極12に接続した状態とし、アノード側のゲート電極80は零バイアスとしてp型エミッタ層3からの十分なホール注入を維持する。

【0140】ターンオフ時は、まずアノード側のゲート電極80に正電圧VG2を印加してエミッタ短絡状態としてp型エミッタ層3からのホール注入を抑制しておく。その後、カソード側のゲート電極74のバイアス電圧VG1を零に落とすことにより、n型エミッタ層7をカソード電極12から切り離し、n型ベース層1のホールをカソード電極12に排出させる。

【0141】以上のようなタイミングで二つのゲート駆動を行うことによって、高いターンオフ能力が得られる。

【0142】図49は、別の実施例の絶縁ゲート型サイリスタである。この実施例では、p型ベース層45とp型ウェル層71の対向する辺の間に、n型ベース層1が露出した状態としている。更に、p型ベース層45とp型ウェル層71の相対向する辺にそれぞれ、浅い低濃度のp型ウェル層81,82が形成されている。n型エミッタ層7のp型ウェル81側端部には高濃度のn+ 型層83が形成されている。そして、n型エミッタ層7とn型ソース層72により挟まれた領域のp型ウェル層81,82およびこれらp型ウェル層81,82に挟まれた領域に露出しているn型ベース層1を覆うようにゲート絶縁膜73を介してゲート電極74が形成されている。n型ソース層72はこの実施例では、図43の実施例と異なり、ストライプ状のp型ウェル71内では分割されずストライプ状をなして形成されている。

【0143】この実施例の素子でも、オン状態ではゲート電極74にカソードに対して正の電圧が印加される。このとき、p型ウェル層81,82の表面のn型反転チャネルとn型ベース層1を介して、n型エミッタ層7とn型ソース層72が短絡された状態となる。ターンオフ時はゲート電極74に零または負電圧が印加される。これにより、n型エミッタ層7はn型ソース層72から切り離される。

【0144】この実施例の素子では、ターンオン時にn型チャネルが形成されるp型ウェル層81,82がp型ベース層45およびp型ウェル層71とは別に形成されて、所望のしきい値に設定される。従ってp型ウェル層71のn型ソース層72下の部分を十分高濃度として横方向抵抗を小さくし、寄生サイリスタ効果を抑制して、ターンオフ時のホール排出を高速に行うことができる。

【0145】図50は、図49の実施例において、n型ソース層72を図43の実施例と同様に複数個に分割して配置した実施例の部分図である。この実施例によれば、より高いターンオフ能力が得られる。

【0146】図51〜図59は、図49或いは図50の実施例の素子構造に対して、さらにターンオフ能力の改善手段を講じた実施例である。図51の実施例では、図4444(a) と同様に、p型ウェル71の底部に高濃度のp+型層75が設けられている。図52の実施例では、図4444(b) と同様にn型ベース層1のp型ベース層45との接合部近傍に低キャリアライフタイム層76が形成されている。図53の実施例では、アノード側に図45(a)と同様のエミッタ短絡部77が設けられている。図5454の実施例では、図45(b) 同様にアノード側にMOSトランジスタによるエミッタ短絡構造が設けられている。図55の実施例は、図52と図53の実施例の構造を組み合わせたもの、図56の実施例は、図51と図54R>4の実施例の構造を組み合わせたもの、図57の実施例は、図51と図53の実施例の構造を組み合わせたもの、図58の実施例は、図51,図52および図54の実施例の構造を組み合わせたものである。図59は、図5454の構造に対して、p型ベース層45とn型ベース層1の接合部に低キャリアライフタイム層76を設けたものである。

【0147】これらの実施例の絶縁ゲート型サイリスタにおいても、優れたターンオフ能力が得られる。

【0148】図60は、別の実施例の絶縁ゲート型サイリスタである。この実施例では、p型ベース層45とこれに隣接するp型ウェル層71の間に、これらより浅く低濃度のp型チャネル層84が形成されている。p型ベース層45内のn型エミッタ層7のチャネル領域側端部には高濃度のn+ 型層83が形成されている。p型ウェル層71内のn型ソース層72は、チャネル側端部が一部p型チャネル層84の領域に入り込んだ状態で、複数個に分割されることなくストライプ状をなして形成されている。

【0149】この実施例においても、p型チャネル層84をp型ベース層45およびp型ウェル層71とは別に形成することで、n型エミッタ層7の短絡用MOSトランジスタのしきい値を最適設計することができる。そしてp型ベース層45およびp型ウェル層71を十分高濃度とすることよって、高いターンオフ能力を得ることができる。

【0150】図61は、図60の構造を変形した実施例の部分構造図であり、n型ソース層72が複数個に分割されて配列形成されている。図62は同様に図60の構造を変形した実施例の部分構造図であり、p型チャネル層84の一部をn型ベース層1を露出させている。これらの実施例によっても、図60の実施例と同様の効果が得られる。

【0151】図63は、図60の構造を基本として図44R>4(a) と同様に高濃度p+ 型層75を設けた実施例、図64は図60の構造を基本として図44(b) と同様に低キャリアライフタイム層76を設けた実施例、図65は図60の構造を基本として図45(a) と同様にアノード側のエミッタ短絡部77を設けた実施例、図66は図60R>0の構造を基本としてアノード側にも絶縁ゲートを設けた実施例である。更に図67は、図60の構造を基本としてこれに図44(a) および図45(a) の構造を組み合わせた実施例、図68は図60の構造を基本としてこれに図44(b) および図45(b) の構造を組み合わせた実施例である。

【0152】これらの実施例によって、更にターンオフ能力の向上を図った絶縁ゲート型サイリスタが得られる。

【0153】図69は、更に別の実施例の絶縁ゲート型サイリスタである。ここまでの実施例では、n型エミッタ層4のn型ソース層72とは反対側のp型ベース層45の端部にターンオン用絶縁ゲート(図では省略している)が設けられるものとした。この実施例においては、n型ソース層72を挟んでn型エミッタ層と反対側にターンオン用およびホールバイパス用のMOSトランジスタが構成されている。

【0154】すなわちp型ベース層45の端部に浅いp型ウェル層91が形成され、このp型ウェル層91内にp型ベース層45内のn型ソース層72と連続するn型ウェル層92が形成されている。このn型ウェル層92の表面にはp型ソース層93が形成されている。カソード電極12はn型ソース層72と同時にp型ソース層93にコンタクトして形成されている。またp型ソース層93とn型ベース層1の間のp型ウェル層91およびn型ウェル層92の表面を覆うようにゲート絶縁膜94を介してゲート電極95が形成されている。

【0155】なおゲート絶縁膜94およびゲート電極95は、n型ソース層72とn型エミッタ層7間をオン,オフするためのゲート絶縁膜73およびゲート電極74と一体的に形成されていても良い。

【0156】この実施例の素子は、ターンオン時、ゲート電極74および95にカソードに対して正電圧を印加する。これにより、ゲート電極95下のp型ウェル層91の表面反転層を介してn型ウェル層92からn型ベース層1に電子が注入される。同時にゲート電極74下のp型ベース層45表面の反転層を介してn型ソース層72とn型エミッタ層7が短絡され、n型エミッタ層7がカソード電極12に接続される。

【0157】ターンオフ時は、ゲート電極74および95に負電圧を印加する。これにより、n型エミッタ層7とn型ソース層72間が切り離される。また、p型ソース層93とp型ウェル層91間がn型ウェル層92の表面反転層を介して短絡される。このpチャネルMOSトランジスタの動作により、p型ベース層45はp型ウェル層91を介し、p型ソース層93を介してカソード電極12に接続され、ホール排出がなされる。

【0158】この実施例では、オン状態ではホール排出のバイパスがなく、従って優れたオン特性を維持することができる。またn型ソース層72の下は厚いp型ベース層45となっているので、寄生サイリスタ効果の影響は少ない。

【0159】図70は、図69の構造を変形した実施例である。この実施例では、p型ベース層45につながるp型ウェル層91が幅広く形成され、n型ソース層72,n型ウェル層92およびp型ソース層93はすべてこのp型ウェル層91の領域内にが形成されている。幅広く形成されるp型ウェル層75の横方向抵抗を小さくするために、その底部に高濃度p+ 型層75が形成されている。それ以外は、図60の実施例と同様である。

【0160】この実施例の素子動作は図69のそれと同じである。n型ソース層72の下が浅いp型ウェル層91になっているが、その底部にp+ 型層75が設けられているため、寄生サイリスタ効果は抑制される。

【0161】図71は、図70の構造を僅かに変形した実施例である。この実施例では、n型ソース層72の一部にp型ウェル層91を露出させて、カソード電極12を直接p型ウェル層91にコンタクトさせたカソード短絡構造としている。

【0162】この実施例によれば、ターンオフ時のカソード電極へのホール排出がより効果的に行われ、高速のターンオフ動作が可能になる。

【0163】図72は、図70の実施例の構造に対して、アノード側にエミッタ短絡部77を形成した実施例、更に図73は、図70の実施例に対してアノード側に選択的にエミッタ短絡構造を得るためのMOSトランジスタを形成した実施例である。これらの実施例によっても、高速のターンオフ動作が可能になる。

【0164】図74は、図69の実施例の構造を3次元的に展開した実施例である。図75は同様に図70の実施例の構造を3次元的に展開した実施例である。図76は同様に図71の実施例の構造を3次元的に展開した実施例である。図77は同様に図70の実施例の構造を3次元的に展開した実施例である。図78は同様に図73の実施例の構造を3次元的に展開した実施例である。図7979は図78の構造を基本として、p型エミッタ層3を取り囲むように絶縁ゲートトランジスタ構造を設けた実施例である。

【0165】次にカソード側の構造を従来の図139と同じとして、アノード側にカソード側と同様のMOSトランジスタを導入した実施例を、図80〜図87に示す。

【0166】図80の実施例では、アノード側にはp型エミッタ層3が選択的に形成され、これから所定距離離れてn+ 型層100が形成されている。n+ 型層100のp型エミッタ層3側の端部にはp型ソース層101が形成されている。p型ソース層101とp型エミッタ層3の間のn型バッファ層2表面にはゲート絶縁膜102を介してゲート電極103が形成されている。すなわちpチャネルMOSトランジスタが構成されている。アノード電極11は、n+ 型層100とp型ソース層101に同時にコンタクトして形成され、p型エミッタ層3には直接コンタクトしていない。

【0167】この実施例の素子では、ターンオン時、カソード側のゲート電極74にカソードに対して正の電圧が印加され、アノード側のゲート電極103にアノードに対して負の電圧が印加される。これにより、それぞれゲート電極下に形成されるチャネルを介して、n型エミッタ層7はn型ソース層72に、またp型エミッタ層3はp型ソース層101に短絡される。図示しないターンオン用ゲートによりp型ベース層にベース電流が供給されると、素子はターンオンする。

【0168】ターンオフ時は、カソード側のゲート電極74にカソードに対して零または負の電圧が印加され、アノード側のゲート電極103にアノードに対して零または正の電圧が印加される。これにより、n型エミッタ層7はn型ソース層72から切離され、n型エミッタ層7からの電子注入は止まる。また、p型エミッタ層3はp型ソース層101から切離され、p型エミッタ層3からのホール注入は止まる。

【0169】以上のようにしてこの実施例によれば、カソード側,アノード側共にMOSゲートでキャリア注入を制御することによって、高速のターンオフができる。なおこの実施例の素子はターンオフに際して、先に図48R>8で説明したようにアノード側のMOSトランジスタをオフにし、その後カソード側のMOSトランジスタをオフにする、というゲート制御を行うこともできる。これにより、より高いターンオフ能力が得られる。

【0170】図81は、アノード側のMOSトランジスタをnチャネルとした実施例である。p型エミッタ層3に連続するp型ウェル層104が形成され、p型エミッタ層とp型ウェル層104に跨がるようにn型ソース層106が形成され、これから所定距離離れてp型ウェル層104にn型ドレイン層105が形成されている。これらn型ソース層106とn型ドレイン層105の間のp型ウェル層104上にゲート絶縁膜102を介してゲート電極103が形成されて、nチャネルMOSトランジスタが構成されている。n型ソース層106とp型エミッタ層3の間は不純物を高濃度にドープした多結晶シリコン膜或いは金属膜による短絡電極107で短絡されている。

【0171】この実施例では、ターンオン時、カソード側のゲート電極74にカソードに対して正の電圧が印加され、アノード側のゲート電極103にはアノードに対して正の電圧が印加される。これにより、カソード側ではn型エミッタ層7はn型ソース層72と接続されて、電子注入が行われる。アノード側ではn型ドレイン層105とn型ソース層106がつながり、短絡電極107によってp型エミッタ層3はアノード電極11と短絡されて、p型エミッタ層3からのホール注入がなされる。

【0172】ターンオフ時は、カソード側のゲート電極74にカソードに対して零または負の電圧が印加され、アノード側のゲート電極103にアノードに対して零または負の電圧が印加される。これにより、n型エミッタ層7はn型ソース層72から切離され、n型エミッタ層7からの電子注入は止まる。また、p型エミッタ層3はn型ドレイン層105およびアノード電極11から切離され、p型エミッタ層3からのホール注入は止まる。

【0173】この実施例によっても、高いターンオフ能力が得られる。図80の実施例では、ターンオフ時、アノード側ではp型エミッタ層3からのホール注入が止まった後にもp型ソース層101からのホール注入が暫く続くが、この実施例ではゲート制御によってホール注入が完全に止まる。したがって優れたターンオフ能力が得られる。

【0174】図82は、図80の実施例に対して、図44R>4(a) と同様にp型ウェル層71の底部に高濃度p+ 型層75を設けた実施例である。図83は、図80の実施例に対して、アノード側のn型ウェル層100の底部に高濃度n+ 型層108を設けた実施例である。図84は、図82と図83を組み合わせた実施例である。

【0175】図85は、図80の実施例に対して、図44R>4(b) と同様にn型ベース層1のp型ベース層45との接合部近傍に低キャリアライフタイム層76を設けた実施例である。図86は、図80の実施例に対して、n型ベース層1のn型バッファ層2寄りのn+ 型層100下に低キャリアライフタイム層109を設けた実施例である。図87は、図80の実施例に対して、サイリスタの主電流経路のn型ベース層1中央部に低キャリアライフタイム層109を設けた実施例である。

【0176】これら図82〜図87の実施例によって、さらに高いターンオフ能力が得られる。

【0177】次に、再度埋込みゲート構造の絶縁ゲート型サイリスタの実施例を、幾つか説明する。

【0178】図88はその様な実施例の絶縁ゲート型サイリスタである。これは、先に説明した図37の構造と基本的に同じであり、埋込み絶縁ゲート電極5の間のn型エミッタ層7上にp型ウェル層61およびn+ 型ソース層62が形成されている。またn型ベース層1のp型エミッタ層3側にはn型バッファ層2が設けられている。上面全面に形成されるカソード電極は省略されている。

【0179】この実施例の素子は、ターンオン時、ゲート電極5にカソードに対して正の電圧が印加される。これにより、p型ウェル層61およびp型ベース層45の溝4側壁に形成されるn型チャネルを介してn+ 型ソース層62はn型エミッタ層7と短絡され、n型エミッタ層7はn型ベース層1と短絡される。これにより、n型ベース層1に電子注入が成される。ターンオフ時は、ゲート電極5にカソードに対して零または負の電圧が印加される。これにより、n型エミッタ層7はn+ 型ソース層62およびn型ベース層1から切り離され、電子注入が止まる。またn型ベース層1中のホールは、ゲート電極端部に設けられたp+ 型層10を介してカソード電極に排出される。

【0180】図89は、図88の構造を改良して、アノード側にエミッタ短絡部77を設けた実施例である。図9090は、同様に図88の構造を改良して、ダブルゲート構造とした実施例である。すなわちアノード側のp型エミッタ層3は選択的に形成され、このp型エミッタ層3内にn+ 型ソース層78が形成され、n+ 型ソース層78とn型バッファ層2により挟まれた領域にゲート絶縁膜79を介してゲート電極80が形成されている。図91R>1は、図88の構造に対して、図1と同様にストライプ状ゲート電極の端部に、p型層8,n型層9,p+ 型層10が縦方向に形成されてn型層9をチャネルとするホールバイパス用の縦型pチャネルMOSトランジスタを構成した実施例である。図92は、図91の構造に対して、図89と同様にアノード側にエミッタ短絡部77を設けた実施例である。図93は、図91の構造に対して、図90と同様にアノード側にMOSトランジスタを構成した実施例である。

【0181】これらの図88〜図93の実施例によっても、高いターンオフ能力を持つ絶縁ゲート型サイリスタが得られる。

【0182】図94は、図91と同様の構造を埋込みゲートではなく平面的に実現した実施例である。p型ベース層45の表面にn+ 型エミッタ層7が形成され、またp型ベース層45の端部にn+ 型エミッタ層7と隣接してn+ 型ソース層72が形成されている。n+ 型ソース層72下のp型ベース層45は十分に厚い。さらにp型ベース層45の外にp型ベース層45に隣接してp+ 型ドレイン層10が形成されている。n型エミッタ層7とn型ソース層72の間にp型ベース層45表面および、n+ 型ソース層71とp+ 型ドレイン層10に挟まれた領域のp型ベース層45およびn型ベース層1の表面には、ゲート絶縁膜73を介してゲート電極74が形成されている。カソード電極12はn+ 型エミッタ層72にコンタクトすると同時に、p+ 型ドレイン層10にもコンタクトするようにパターン形成されている。

【0183】この実施例の素子は、ターンオン時、ゲート電極74にカソードに対して正の電圧が印加される。これにより、n+ 型ソース層72とn+ 型エミッタ層7の間がn型チャネルにより短絡される。また、p型ベース層45の端部にn型チャネルが形成されて、n+ 型ソース層72からn型ベース層1に電子が注入される。ターンオフ時は、ゲート電極74にカソードに対して負の電圧が印加される。これにより、n+ 型エミッタ層7はn+ 型ソース層72から切り離される。また、p型ベース層とp+ 型ドレイン層10の間がn型ベース層1の表面に形成される反転チャネルを介して接続されて、カソード電極12にホール排出がなされる。

【0184】この実施例によれば、pチャネルMOSトランジスタ部分は素子がオン状態ではオフしているから、ホールバイパスはなく、したがってオン特性が損なわれることはない。また、n+ 型ソース層72下のp型ベース層45は十分厚いから、寄生トランジスタ効果の影響は少なく、ターンオフ時はp型ベース層45の小さい横方向抵抗を介し、p型反転チャネルを介してホール排出がなされるので高いターンオフ能力が得られる。

【0185】図95、図94の構造におけるn+ 型ソース層72下の部分を浅いp型ウェル層91とした実施例である。p型ウェル層91の底部には高濃度p+ 型層75が形成されている。

【0186】この実施例においては、p型ウェル層91をp型ベース層45とは別に形成することによって、MOSトランジスタのしきい値を最適設定することができ、しかも、高濃度p+ 型層75を設けることによって寄生サイリスタ効果を抑制して高いターンオフ能力を確保することができる。

【0187】図96は、図95の構造に対してアノード側にエミッタ短絡部77を形成した実施例である。図97R>7は同様に図95の構造に対して、アノード側にもエミッタ短絡構造を選択的に形成するためのMOSトランジスタを構成した実施例である。図98は更に、図95の構造に対して、カソード側にエミッタ短絡部96を設けた実施例である。

【0188】これら図96〜図98の実施例によっても、高いターンオフ能力の絶縁ゲート型サイリスタが得られる。

【0189】図99は、図88の構造を埋込みゲート構造ではなく、平面ゲート構造によって実現した実施例である。n型ベース層1に選択的にp型ベース層45が形成され、このp型ベース層45内に選択的にn型エミッタ層7が形成され、更にこのn型エミッタ層7内に選択的にp型ウェル層61が形成され、このp型ウェル層61内に選択的にn+ 型ソース層62が形成されている。n+ 型ソース層62とp型ウェル層61に同時にコンタクトするようにカソード電極12が形成されている。n+ 型ソース層62とn型ベース層1により挟まれた領域のp型ウェル層61,n型エミッタ層7およびp型ベース層45の表面に連続してゲート絶縁膜73を介してゲート電極74が形成されている。

【0190】この実施例の素子は、ターンオン時、ゲート電極74にカソードに対して正の電圧が印加される。これにより、n+ 型ソース層62とn型エミッタ層7の間がn型チャネルにより短絡され、またn型エミッタ層7とn型ベース層1の間がn型チャネルにより短絡される。これにより、n+型ソース層62からn型ベース層1に電子が注入される。ターンオフ時は、ゲート電極74にカソードに対して負の電圧が印加される。これにより、n型エミッタ層62はn+ 型ソース層62およびn型ベース層1から切り離され、電子注入が止まる。また、p型ベース層とp型ウェル層61の間がn型エミッタ層7の表面に形成されるp型チャネルを介して短絡されて、n型ベース層1のホールはp型ベース層45からp型チャネルを介し、p型ウェル層61を介してカソード電極12に排出される。

【0191】この実施例によっても、オン状態でのホールバイパスはなく、またターンオフ時はカソード・エミッタからの電子注入が抑制されると同時にホールバイパスがなされる。したがってオン特性を損なうことなく、高速のターンオフができる。

【0192】図100は、図99の構造を改良した実施例である。この実施例では、n型ベース層1にp型ベース層45およびn型エミッタ層7を拡散形成した後、その表面にn- 型エピタキシャル層111を形成している。そしてこのエピタキシャル層111にp型ウェル層61、およびp型ベース層45と繋がるp型ウェル層113を同時に形成し、またこれらp型ウェル層61と113の間にn型ウェル層112ウェル層を形成している。

【0193】図99の実施例では、n型ベース草1にp型ベース層45,n型エミッタ層7,p型ウェル層61およびn+ 型ソース層62と順次不純物拡散によって形成すると、不純物濃度が順次高くなるために、各部のMOSトランジスタのしきい値の最適化が難しい。この実施例で、n型エミッタ層7まで形成した後にエピタキシャル成長を行って、p型ウェル層61,113およびn型ウェル層112を形成するため、各MOSトランジスタのしきい値の最適設計が容易である。

【0194】図101は、図99の構造を基本として、アノード側にエミッタ短絡部77を形成した実施例である。図102は同様に図99の構造を基本として、アノード側に選択的にエミッタ短絡構造を形成するためのMOSトランジスタを導入した実施例である。これらの実施例によっても、同様の効果が得られる。

【0195】図103は、図43の実施例を改良した実施例の絶縁ゲート型サイリスタである。図43の実施例では、n+ 型ソース層72が複数個に完全に分離されて配置されたのに対して、この実施例では複数個のn+型ソース層72が完全には分離されず、n型エミッタ層7側で連続するようにパターン形成している。

【0196】図43の実施例では、n+ 型ソース層72を分割配置することによって前述のように寄生サイリスタ効果が低減されるが、反面、n+ 型ソース層72とn型エミッタ層7間に形成されるMOSトランジスタの実効ゲート幅(すなわちn+ 型ソース層72のn型エミッタ層7に対向する辺のトータルの長さ)が小さくなるために、オン電圧の上昇をきたす。この実施例によれば、n+ 型ソース層72がn型エミッタ層7に対向する辺ではつながっているから、実効ゲート幅を小さくすることなく、しかもカソード短絡率を十分大きく確保して寄生サイリスタ効果を低減することができる。

【0197】図104は本発明の別の実施例の素子構造を示す平面図であり、図105は図104のA−A′断面図である。p型エミッタ層3に接してn型ベース層1が形成され、このn型ベース層1内にp型ベース層45およびn型エミッタ層7が順次拡散形成されて、pnpnサイリスタ構造が構成されている。n型エミッタ層7に隣接してn型ソース層72が形成され、n型エミッタ層7とn型ソース層72に挟まれるp型ベース層45の表面部分にゲート絶縁膜73を介して第1のゲート電極74(G1 )が形成されて、CH1 をチャネル領域とするnチャネルMOSFETが構成されている。

【0198】この構造では、図139に示した従来構造ではあった高濃度p型層71は形成されていない。これに代って、この実施例の構造では、n型ソース層72のn型エミッタ層7と反対側の端部にp型ソース層93が形成されている。このp型ソース層93とp型ベース層45により挟まれた領域表面にゲート絶縁膜を介して第2のゲート電極95(G2 )が形成されている。

【0199】従って、ゲートG1 ,G2 共に正の電圧を印加すると、チャネル領域CH1 が導通し、チャネル領域CH2 が非導通となって、エミッタ短絡部はなくなる。これにより、電子はn型エミッタ層7から高い注入効率でサイリスタ構造に注入される。一方、ゲートG1 ,G2 共に負電圧とすると、チャネル領域CH2 が導通,チャネル領域CH1 が非導通となり、n型エミッタ層7からの電子注入は止まり、正孔はチャネル領域CH2 を通ってカソード電極13へ排出されるので、素子はターンオフする。

【0200】以上のようにこの実施例では、サイリスタがオンしている間はカソード短絡とならないので高い注入効率で電子がサイリスタ構造へ注入される。

【0201】図106は、図104の実施例の改良型の素子構造を示す平面図であり、図107は図106のA−A′断面図である。この実施例では、ゲート電極74の端部直下に高濃度n型ソース層72が形成されている。したがって、ソース層抵抗を低減できると共に、チャネル長を高精度で制御することができる。また、p型ベース層45、n型エミッタ層7の端部にp型ウェル91、n型ソース層72および第3のゲート電極80が設けられている。この様にn型エミッタ層72の端部にターンオン用MOSFETを形成すると、この部分からターンオンが開始するため、n型ウェル層92をn型エミッタとする寄生サイリスタがラッチアップしにくくなるという利点が得られる。

【0202】図108は同じく図104の実施例の改良型の素子構造を示す平面図であり、図109はそのA−A′断面図である。この実施例では、n型ソース層72とp型ソース層93が周期的に入り組んで形成されている。この実施例によれば、コンタクトホール105が小さいものであって、これらの層との十分低抵抗のコンタクトが可能となる。したがって素子領域のデッドスペースを低減することができる。

【0203】図111は、他の実施例の素子構造を示す平面図であり、図112は図111のA−A′断面図である。この実施例では、n型ソース層72のn型エミッタ層7と隣接した側の端部にp型ソース層93が形成されている。この実施例によれば、ターンオフ時、サイリスタ領域に近い部分から効率的に正孔を排出することができるので、高いターンオフ能力が得られる。

【0204】図113は、図111の実施例の改良型の素子構造を示す平面図であり、図114はそのA−A′断面図である。この実施例では、図111の実施例にターンオン用の絶縁ゲートが付加されている。したがって高速のターンオンが可能である。

【0205】図115は、同じく図111の実施例の改良型の素子構造を示す平面図であり、図116,図117R>7はそれぞれ、図115のA−A′,B−B′断面図である。この実施例では、n型ソース層72とp型ソース層93が周期的に入り組んで形成されている。この実施例によれば、ソース層抵抗が低減され、したがって小さいオン電圧を得ることができる。

【0206】図118は、本発明の他の実施例の素子構造を示す平面図であり、図119はそのA−A′断面図である。この実施例では、n型エミッタ層7の端部にp型ソース層93が形成されている。したがって、ゲートGに正電圧を印加すると、チャネル領域CH1 が導通し、チャネル領域CH2 が非導通となって、エミッタ短絡部はなくなる。これにより、電子はn型エミッタ層7から高い注入効率でサイリスタ部へ注入される。一方、ゲートGに負の電圧を印加すると、チャネル領域CH2 が導通,チャネル領域CH1 が非導通となって、n型エミッタ層7の電子注入は止まり、正孔がチャネル領域CH2 を通ってカソード電極12へ排出されるので、素子はターンオフする。

【0207】この実施例の素子構造であれば、サイリスタがオンしている間はカソード短絡にならないので、高い注入効率で電子がサイリスタ構造に注入される。p型層71は、n型ソース層72をエミッタとする寄生サイリスタのラッチアップ防止のために設けられている。

【0208】図120は、図118の実施例の改良型の素子構造を示す平面図であり、図121はそのA−A′断面図である。この実施例は、図118の実施例にターンオン用の絶縁ゲートを付加したもので、これにより高速ターンオンが可能になる。

【0209】図122は同じく図118の実施例の改良型の素子構造を示す平面図であり、図123はそのA−A′断面図、図124は同じくB−B′断面図である。この実施例では高濃度n型ソース層72が形成されている。これにより、ソース層抵抗が低減され、小さいオン電圧を得ることができる。

【0210】図125は、同じく図118の実施例の改良型の素子構造を示す平面図であり、図126はそのA−A′断面図である。この実施例では、高濃度p型ソース層93がn型エミッタ層7の全面にわたって形成されている。この実施例によれば、主に電流が流れるサイリスタ領域上を熱伝導率の高い金属電極が覆うことになる。これにより、素子内部で発生した熱が素子外部に効率よく排出されるので、結果的に素子の動作周波数を高めることができる。

【0211】図127は、本発明の他の実施例の素子構造を示す平面図であり、図128は図127のA−A′断面図、図129は同じくB−B′断面図、図130は同じくC−C′断面図である。この実施例は、ゲート電極95,80を互いに直交させて一体化し、n型エミッタ層7およびn型ソース層72を矩形状に形成している。図128のA−A′断面図を見ると、従来例と同じ素子構造になっているが、p型ベース層45がカソード電極12と接触していないので高い電子注入効率が得られる。またターンオンの際にはn型エミッタ層7からチャネル領域CH3を通ってn型ベース層1に電子が注入されるので、高速でターンオンができる。一方、図129R>9,図130のB−B′断面,C−C′断面を見ると、n型エミッタ層7或いはn型ソース層72の端部にp型ソース層93が形成されている。したがって、ゲートG2 をバイアスすると、チャネル領域CH2 を通って素子に蓄積されていた正孔がカソード電極12に排出されるから、素子は速やかにターンオフする。

【0212】この実施例では、p型ソース層93がn型ソース層72と離れて形成されるので、隣接して形成された場合よりもソース層抵抗を小さくすることができ、素子のオン電圧を小さくすることができる。またn型エミッタ層の幅と長さを変えることにより、チャネル領域CH1 ,CH2 の長さを独立に設定することができるので、オン電圧やターンオフ能力を、必要に応じて最適設計することが容易である。

【0213】この実施例では、3種類のゲート電極を一体化したが、駆動方法やプロセス上の利点を考慮してそれぞれを分離した構造としてもよい。またp型ソース層93をn型エミッタ層とn型ソース層72の両方の端部に形成したが、いずれか一方のみとしてもよい。

【0214】また以上の実施例において、p型ソース層93をゲート電極95から離れた位置に形成すれば、このp型ソース層93は絶縁ゲート型トランジスタのソース層としてではなく、ツェナーダイオードのアノードとして働く。この場合でも、カソード短絡部分は生じないので、高い注入効率で電子を注入することができる。

【0215】図131は、本発明の他の実施例の素子構造を示す平面図であり、図132は図131のA−A′断面図、図133は同じくB−B′断面図、図134は同じくC−C′断面図である。p型エミッタ層3に接してn型ベース層1が形成され、このn型ベース層1内にp型ベース層45およびn型エミッタ層7が順次拡散形成されて、pnpnサイリスタ構造が構成されている。p型エミッタ層3にはアノード電極1が形成され、n型エミッタ層7にはカソード電極11が形成されている。n型エミッタ層7は複数個の矩形状領域に分割配置されており、カソード電極12はこれらの各n型エミッタ層7に低抵抗接触している。

【0216】図132,図133に示すように、矩形状に形成された各n型エミッタ層7の長辺および一方の短辺に沿って、第3のゲート電極80が櫛歯状に形成されている。この第3のゲート電極80の端部に自己整合的にn型ウェル92およびp型ソース層93が形成されて、ターンオフ用MOSFETのチャネル領域CH2 が形成されている。図131に示すように、p型ソース層93は梯子状にパターン形成されている。図133はn型エミッタ層7がカソード電極12とコンタクトしている部分の断面に対応し、図134はp型ソース層93がカソード電極12とコンタクトしている部分の断面に対応している。なお説明を簡単にするため、図132では梯子状パターンのp型ソース層93の一部を省略して示している。

【0217】この様な形状のp型ソース層93を用いれば、n型エミッタ層7のコンタクトホールをぎりぎりまで縮めても、確実にカソード電極12をp型ソース層93にコンタクトさせることができるため、素子寸法を小さくすることができる。その結果、キャリア排出経路の抵抗が低減されるので、高いピークターンオフ電流を得ることができる。

【0218】矩形状に形成された各n型エミッタ層7の他方の短辺に沿っては、図131,図132に示すように、ストライプ状の第1のゲート電極74および第2のゲート電極95が形成されている。すなわち、n型ソース層72とn型ベース層1に挟まれた領域のp型ベース層45表面をチャネル領域CH1 として、この上にゲート絶縁膜73を介して第1のゲート電極74が形成されて、ターンオン用MOSFETが構成されている。またp型ソース層93とn型ソース層72に挟まれた領域のn型ウェル層92およびp型ベース層45の表面をそれぞれチャネル領域CH2 ,CH3 として、この上にゲート絶縁膜74を介して第2のゲート電極95が形成され、ターンオフ用MOSFETと本発明に特有の接続用MOSFETが構成されている。この実施例では、n型ソース層72はn型ウェル層92と同時に拡散形成される。これにより、プロセスの簡単化が図られている。

【0219】この実施例の素子の動作は次の通りである。ターンオン動作は、第1のゲート電極74および第2のゲート電極95に、正の電圧を印加することにより行われる。このとき、チャネル領域CH1 およびCH3 が導通して、n型ウェル層92からチャネル領域CH3 ,n型ソース層72,チャネル領域CH1 を通ってn型ベース層1に電子が注入され、それに見合った正孔がp型エミッタ層3から注入されて、素子はターンオンする。

【0220】ターンオフ動作は、第2のゲート電極96および第3のゲート電極80に負の電圧を印加することにより行われる。これにより、チャネル領域CH2 が導通して、正孔がp型ベース層45からチャネル領域CH2 およびp型ソース層93を通ってカソード電極12へと排出される。このときn型エミッタ層7の電位がp型ベース層45と同電位になるため、n型エミッタ層7からの電子注入は止まり、このサイリスタはターンオフする。

【0221】この実施例の素子構造では、ターンオン用MOSFETのチャネル領域CH1とターンオフ用MOSFETのチャネル領域CH2 が分離されるのでターンオフの際のキャリア排出経路の拡散層抵抗が低くなる。したがって反対側のチャネル領域CH2 と同等のターンオフ能力が得られる。またターンオン用MOSFETのn型ソース層72は、ターンオフ時にはチャネル領域CH3 が非導通となって他の層から分離されるので、n型ソース層72をエミッタとする寄生サイリスタがラッチアップしてターンオフ特性の劣化を引き起こすこともない。ターンオフの際のゲート駆動法として、まず第3のゲート電極80に負の電圧を印加し、これから一定時間遅れて第1のゲート電極74および第2のゲート電極95に負の電圧を印加するという方法を採用することもできる。この方法によれば、n型ベース層1内の過剰キャリアを排出した後にターンオフ動作を行うことになるので、ターンオフ損失を低減することができる。またこの実施例のように全てのゲート電極が分離されていると、それぞれのチャネル領域のしきい値電圧の大小関係がどのようになっていても、確実に動作させることができる。

【0222】図135は、図131の実施例の改良型の素子構造を示す平面図である。図のA−A′,B−B′,C−C′断面構造はそれぞれ、図132,図133R>3,図134と同じである。この実施例では、図131の実施例の第1のゲート電極74と第2のゲート電極95が一体形成されている。第1のゲート電極と第2のゲート電極とは、第3のゲート電極80の枝部分に対向する部分で接続されている。

【0223】この実施例によれば、矩形状のn型エミッタ層7の一方の短辺に形成されたトリガ部分のオン・オフ動作を一つのゲート電極で制御することができる、という利点が得られる。またこの実施例の構成では、チャネル領域CH1のしきい値電圧はチャネル領域CH2 のそれより低くなるので、ターンオンの際にはチャネル領域CH1 ,CH2 の順に導通し、ターンオフの際はCH2 ,CH1 の順に非導通となる。

【0224】図136は、同じく図131の実施例の改良型の素子構造を示す平面図である。図のA−A′,B−B′,C−C′断面構造はそれぞれ、図132,図13333,図134と同じである。この実施例では、図131R>1の実施例の第2のゲート電極95と第3のゲート電極80が一体形成されている。

【0225】この実施例によれば、矩形状のn型エミッタ層7の周囲に形成されたターンオフ用MOSFETを一つのゲート電極で制御できるという利点が得られる。この実施例の構成では、ターンオフの際はゲート電極に正の電圧を印加して、電子をチャネル領域CH3 およびCH1 を通してn型ベース層1に注入することが必要である。またゲート電極に負の電圧を印加するだけでn型ソース層13がn型ウェル層5から切り離され、正孔がチャネル領域CH2を通って排出されるので、ターンオフ動作に入ることができる。

【0226】図137は、同じく図131の実施例の改良型の素子構造を示す平面図である。図のA−A′,B−B′,C−C′断面構造はそれぞれ、図132,図13333,図134と同じである。この実施例では、図131R>1の実施例のゲート電極74,95,80を一体化して一つのゲート電極として形成している。

【0227】この実施例では、一つのゲート電極のみでターンオン,ターンオフ制御ができるという利点が得られる。この実施例の構成では、各チャネル領域のしきい値電圧の大きさが、CH3 >CH2 >CH1 となる。したがって、ゲート電極にチャネル領域CH3 のしきい値電圧以上の電圧を印加することにより、素子はターンオンし、チャネル領域CH2 のしきい値電圧以下の電圧を印加することにより、素子はターンオフすることになる。ターンオンの際はまず、ターンオフ用MOSFETのチャネル領域CH2 が非導通となり、次いでターンオン用MOSFETのチャネル領域CH1 、接続用MOSFETのチャネル領域CH3 の順に導通する。ターンオフの際は、最初に接続用MOSFETのチャネル領域CH3 が非導通となり、次いでターンオン用MOSFETのチャネル領域CH1 が非導通となり、その後ターンオフ用MOSFETのチャネル領域CH2 が導通状態になる。

【0228】図138は、同じく図131の実施例の改良型の素子構造を示す断面図である。の断面図は、図13131,図135,図136,図137で示した平面図のA−A′断面に対応しており、図132で示した断面構造とすることもできる。この実施例では、ターンオン用MOSFETのウェル層としてp型ベース層45とは別にp型ウェル層91が形成されている。

【0229】この実施例によれば、p型ウェル層91の濃度がp型ベース層45の濃度とは別に最適設定されるから、所望のしきい値電圧を得ることができる。この実施例において、p型ベース層45の端の位置をどこに選ぶかは、素子特性を決定する重要な要因になる。p型ベース層45の端は、少なくともn型エミッタ層7よりはn型ソース層72側に設定しなければ、p型ベース層45の端にアノード電流が集中することになる。またp型ベース層45の端を第2のゲート電極95よりn型ソース層72側に設定すれば、正孔の排出経路の拡散層抵抗が低くなり、高いターンオフ能力を得ることができる。

【0230】本発明は、上記実施例に限られるものではなく、その趣旨を逸脱しない範囲でさらに種々変形して実施することができる。

【0231】

【発明の効果】以上説明したように本発明によれば、優れたオン特性を維持しながら、ターンオフ能力の向上を図った絶縁ゲート型サイリスタを提供することができる。

【図面の簡単な説明】

【図1】埋込みゲート構造を用いた実施例に係る絶縁ゲート型サイリスタを示す図。

【図2】図1の各部の導電型を逆にした実施例の絶縁ゲート型サイリスタを示す図。

【図3】両面に埋込みゲート構造を設けた実施例に係る絶縁ゲート型サイリスタを示す図。

【図4】図3を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図5】図1の構造を変形して埋込み溝を深くした実施例の絶縁ゲート型サイリスタを示す図。

【図6】埋込み溝をさらに深くした実施例の絶縁ゲート型サイリスタを示す図。

【図7】埋込み溝が基板を貫通する状態とした実施例の絶縁ゲート型サイリスタを示す図。

【図8】微細チャネルの埋込みゲート型ダイオードの実施例を示す図。

【図9】同じく微細チャネルの埋込みゲート型ダイオードの実施例を示す図。

【図10】別の実施例の埋込みゲート構造の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図11】図10を変形した実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図12】図10を変形した実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図13】図12を変形した実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図14】図13の埋込み溝をより深くした実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図15】埋込み溝をさらに深くした実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図16】図10の構造を3次元的に展開した実施例の絶縁ゲート型サイリスタおよびトランジスタと、トランジスタの場合の等価回路を示す図。

【図17】図12の構造を3次元的に展開した実施例の絶縁ゲート型サイリスタおよびトランジスタと、トランジスタの場合の等価回路を示す図。

【図18】図16の実施例のホールバイパス部を縦型MOSトランジスタにした実施例の絶縁ゲート型サイリスタおよびトランジスタと、トランジスタの場合の等価回路を示す図。

【図19】図17の実施例のホールバイパス部を縦型MOSトランジスタにした実施例の絶縁ゲート型サイリスタおよびトランジスタと、トランジスタの場合の等価回路を示す図。

【図20】図18の構造のpチャネルMOSトランジスタを溝間に組込んで3次元的に展開した実施例の絶縁ゲート型サイリスタおよびトランジスタと、ゲート駆動波形を示す図。

【図21】図19の構造のpチャネルMOSトランジスタを溝間に組込んで3次元的に展開した実施例の絶縁ゲート型サイリスタおよびトランジスタと、ゲート駆動波形を示す図。

【図22】微細チャネルとした実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図23】図22の溝深さを変更した実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図24】図22の一部導電型を変更した実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図25】図24の溝深さを変更した実施例の絶縁ゲート型サイリスタおよびトランジスタを示す図。

【図26】図17の実施例のサイリスタの場合の断面構造と等価回路図。

【図27】同じく図17の実施例のサイリスタの場合の3次元構造と等価回路図。

【図28】アノード側に埋込みゲート構造を用いた実施例の絶縁ゲート型サイリスタを示す図。

【図29】図28(b) の実施例の3次元的構造と等価回路図。

【図30】図10の構造にアノード側にも埋込みゲート構造を導入した実施例の絶縁ゲート型サイリスタを示す図。

【図31】図30を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図32】図31の実施例のサイリスタの3次元構造と等価回路を示す図。

【図33】溝の間にカソード・エミッタと共にホールバイパス用のpチャネルMOSトランジスタを形成した実施例の絶縁ゲート型サイリスタを示す図。

【図34】図33の構造をアノード側にも適用した実施例の絶縁ゲート型サイリスタを示す図。

【図35】図33の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図36】図34の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図37】縦型のpチャネルMOSトランジスタとnチャネルMOSトランジスタを溝間に形成した実施例の絶縁ゲート型サイリスタの構造と等価回路図。

【図38】図37を変形した実施例の絶縁ゲート型サイリスタの構造と等価回路図。

【図39】図32の構造に縦型のpチャネルMOSトランジスタを導入した実施例の絶縁ゲート型サイリスタと等価回路図。

【図40】図37を変形したアノード側にも埋込み絶縁ゲートを導入した実施例の絶縁ゲート型サイリスタと等価回路図。

【図41】図40の実施例を変形した実施例の絶縁ゲート型サイリスタと等価回路図。

【図42】図41の実施例のカソード側に縦型のpチャネルMOSトランジスタを導入した実施例の絶縁ゲート型サイリスタと等価回路図。

【図43】平面ゲート構造を用いた実施例の絶縁ゲート型サイリスタを示す図。

【図44】図43の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図45】同じく図43の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図46】同じく図43の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図47】同じく図43の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図48】図47(a) の実施例のゲート駆動波形の例を示す図。

【図49】図43の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図50】図49の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図51】図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図52】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図53】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図54】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図55】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図56】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図57】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図58】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図59】同じく図49および図50の改良型の絶縁ゲート型サイリスタを示す図。

【図60】図43の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図61】図60の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図62】同じく図60の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図63】図60および図61の改良型の絶縁ゲート型サイリスタを示す図。

【図64】同じく図60および図61の改良型の絶縁ゲート型サイリスタを示す図。

【図65】同じく図60および図61の改良型の絶縁ゲート型サイリスタを示す図。

【図66】同じく図60および図61の改良型の絶縁ゲート型サイリスタを示す図。

【図67】同じく図60および図61の改良型の絶縁ゲート型サイリスタを示す図。

【図68】同じく図60および図61の改良型の絶縁ゲート型サイリスタを示す図。

【図69】別の実施例の絶縁ゲート型サイリスタを示す図。

【図70】図69の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図71】同じく図69の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図72】同じく図69の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図73】同じく図69の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図74】図69の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図75】図74の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図76】同じく図74の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図77】同じく図74の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図78】同じく図74の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図79】同じく図74の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図80】アノード側にカソード側と同様のスイッチング用MOSトランジスタを平面構造で導入した実施例の絶縁ゲート型サイリスタを示す図。

【図81】図80の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図82】同じく図80の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図83】同じく図80の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図84】同じく図80の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図85】同じく図80の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図86】同じく図80の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図87】同じく図80の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図88】埋込み絶縁ゲート構造の実施例の絶縁ゲート型サイリスタを示す図。

【図89】図88の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図90】同じく図88の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図91】同じく図88の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図92】同じく図88の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図93】同じく図88の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図94】平面構造のMOSトランジスタを用いた他の実施例の絶縁ゲート型サイリスタを示す図。

【図95】図94の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図96】同じく図94の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図97】同じく図94の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図98】同じく図94の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図99】平面構造のMOSトランジスタを用いた他の実施例の絶縁ゲート型サイリスタを示す図。

【図100】図99の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図101】同じく図99の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図102】同じく図99の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図103】図43の実施例を変形した実施例の絶縁ゲート型サイリスタを示す図。

【図104】本発明の他の実施例の絶縁ゲート型サイリスタを示す平面図。

【図105】図104のA−A′断面図。

【図106】図104の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図107】図106のA−A′断面図。

【図108】図104の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図109】図108のA−A′断面図。

【図110】図108のB−B′断面図。

【図111】本発明の他の実施例の絶縁ゲート型サイリスタを示す平面図。

【図112】図111のA−A′断面図。

【図113】図111の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図114】図113のA−A′断面図。

【図115】図111の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図116】図115のA−A′断面図。

【図117】図115のB−B′断面図。

【図118】本発明の他の実施例の絶縁ゲート型サイリスタを示す平面図。

【図119】図118のA−A′断面図。

【図120】図118の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図121】図120のA−A′断面図。

【図122】図118の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図123】図122のA−A′断面図。

【図124】図122のB−B′断面図。

【図125】図118の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図126】図125のA−A′断面図。

【図127】本発明の他の実施例の絶縁ゲート型サイリスタを示す平面図。

【図128】図127のA−A′断面図。

【図129】図127のB−B′断面図。

【図130】図127のC−C′断面図。

【図131】本発明の他の実施例の絶縁ゲート型サイリスタを示す平面図。

【図132】図131のA−A′断面図。

【図133】図131のB−B′断面図。

【図134】図131のC−C′断面図。

【図135】図131の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図136】同じく図131の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図137】同じく図131の実施例の改良型の絶縁ゲート型サイリスタを示す図。

【図138】同じく図131の実施例の改良型の絶縁ゲート型サイリスタのA−A′断面図。

【図139】従来の絶縁ゲート型サイリスタを示す図。

【図140】従来の他の絶縁ゲートサイリスタを示す図。

【図141】従来の他の絶縁ゲート型サイリスタを示す図。

【符号の説明】

1…n型ベース層、

2…n型バッファ層、

3…p型エミッタ層、

4…溝、

5…絶縁ゲート電極、

6…チャネル領域、

7…n型エミッタ層、

8…p型ソース層、

9…n型チャネル層、

10…n型ドレイン層、

11…アノード電極、

12…カソード電極、

35…溝、

36…絶縁ゲート電極、

41…カソード電極、

41b…ドレイン電極、

45…p型ベース層、

46…ゲート電極、

47…n型チャネル層、

54…n型チャネル層、

56…n型ウェル層(エミッタ層)、

57…p型ウェル層、

58…p型ウェル層(エミッタ層)

59…n型ウェル層、

61…p型ウェル層、

62…n型ソース層、

71…p+ 型層、

72…n型ソース層、

73…ゲート絶縁膜、

74…ゲート電極、

78…n型ソース層、

79…ゲート絶縁膜、

80…ゲート電極、

81,82…p型ウェル層、

83…n+ 型層、

84…p型ウェル層、

91…p型ウェル層、

92…n型ウェル層、

93…p型ソース層、

94…ゲート絶縁膜、

95…ゲート電極、

100…n+ 型層、

101…p型ソース層、

102…ゲート絶縁膜、

103…ゲート電極、

104…層間絶縁膜、

105…コンタクトホール。

【0001】

【産業上の利用分野】本発明は、小さいゲート電力で大きい主電流を制御することができる絶縁ゲート型サイリスタに関する。

【0002】

【従来の技術】ゲート電力低減のために絶縁ゲート構造を採用した各種サイリスタが提案されている。

【0003】図139は、その様な絶縁ゲート型サイリスタの一種である。このサイリスタは、p型アノード層,n型ベース層、p型ベース層およびn型エミッタ層のpnpn4層構造を持つ。p型ベース層内にはn型エミッタ層に隣接してn型ソース層が形成され、これをエミッタとする寄生サイリスタがラッチアップするのを防止するためにこれとオーバーラップして高濃度p型層が形成されている。n型エミッタ層とn型ソース層の間のp型ベース層上にゲート絶縁膜を介してゲート電極が形成されている。カソード電極は、n型エミッタ層ではなく、n型ソース層と高濃度p型層に同時にコンタクトして配設されている。p型エミッタ層にはアノード電極が形成されている。

【0004】この絶縁ゲート型サイリスタは、ゲート電極に印加する電圧によってn型ソース層とn型エミッタ層の間のチャネルをオン,オフすることにより、ターンオン,ターンオフ制御がなされる。

【0005】この絶縁ゲート型サイリスタでは、p型ベース層が高濃度p型層を介してカソード電極と常にコンタクトしているため、所謂カソードショートとなり、電子の注入効率が低く、サイリスタのオン電圧が高いという問題があった。

【0006】また、この絶縁ゲート型サイリスタでは、p型エミッタ層,n型ベース層,p型ベース層およびn型ソース層からなるpnpn構造が寄生サイリスタとなり、またn型エミッタ層,p型ベース層およびn型ソース層からなるnpn構造が寄生バイポーラトランジスタとなる。これらの寄生素子が動作するとゲートによる制御が不能になるため、ターンオフ能力が著しく低いという問題があった。

【0007】図140および図141は、埋込み絶縁ゲート構造を用いた絶縁ゲートサイリスタの例である(H.R.Chang,IEDM,1989)。これらは、いゆわる静電誘導サイリスタ(SIサイリスタ)の一種である。

【0008】図140(a) のものは、高抵抗のn型ベース層の一方の面にn型バッファ層を介してp型アノード層(ドレイン層)が形成されている。n型ベース層の他方の面には所定間隔をもって一対の溝が形成されて、ここに絶縁ゲートが埋込み形成されている。溝の間がチャネル領域であって、その表面部にn型カソード層(ソース層)が形成されている。溝の外側には、ホール排出のための高濃度p型層が形成されている。カソード電極はn型エミッタ層および溝の外側の高濃度p型層に同時にコンタクトして設けられている。p型アノード層にはアノード電極が設けられている。

【0009】この素子は、ゲート電極にバイアスを印加しなければオンしているノーマリオン型である。ターンオフするには、ゲート電極にカソード電極に対して負の電圧を印加する。これにより、溝の間のn型ベース層領域が空乏化し、n型カソード層からの電子注入が止まる。n型ベース層内に蓄積しているホールは、p型ウェルを介してカソード電極に排出される。このホール排出部分は、pnpトランジスタになっている。

【0010】図140(b) は、図140(a) と各部の導電型を逆にしただけである。

【0011】図141の素子は、図140(b) の素子を3次元的に展開した構造である。すなわち、オン状態で電流通路となるダイオード領域は、ストライプ状のアノード領域とゲート領域が交互に配列された状態として、これらダイオード領域のストライプ端部にキャリア(図の場合電子)排出用のトランジスタ領域が形成されている。

【0012】これらの埋込み絶縁ゲートを持つSIサイリスタでは、ターンオフ時のキャリア排出用バイポーラトランジスタ領域がダイオード領域に並列に寄生トランジスタとして設けられている。SIサイリスタがオン状態ではこのバイポーラトランジスタもオンであって、そのベースにはキャリア蓄積が生じる。このため、ターンオフ時のキャリア排出に時間がかかる。また、ターンオフ時に絶縁ゲートにより制御されるのは、電子,ホールのうち一方の注入のみであり、これもキャリア排出に時間がかかる原因となっている。したがって、ターンオフ能力が低い。

【0013】また上述した従来のSIサイリスタは、ノーマリオン型であるため、何等かの原因でゲートバイアスが印加できなくなると、ターンオフできずにオン状態のままになるため、フェールセーフの観点からも問題であった。

【0014】

【発明が解決しようとする課題】以上のように従来の絶縁ゲート型サイリスタは、一般にターンオフ能力が低く、特に優れたオン特性を維持しながら高速のターンオフを行なわせることが難しい、という問題があった。

【0015】本発明は、第1に、優れたオン特性を維持しながら、高速のターンオフを行うことのできる絶縁ゲート型サイリスタを提供することを目的とする。

【0016】本発明は、第2に、寄生バイポーラトランジスタや寄生サイリスタ動作を抑制して、ターンオフ能力の向上を図った絶縁ゲート型サイリスタを提供することを目的とする。

【0017】本発明は、第3に、ゲートバイアスが零ではオフ状態に保たれるノーマリオフ型とした絶縁ゲート型サイリスタを提供することを目的とする。

【0018】本発明は、第4に、素子の有効導通面積を確保しながら、ターンオフ能力の向上を図った絶縁ゲート型サイリスタを提供することを目的とする。

【0019】

【課題を解決するための手段】本発明に係る絶縁ゲート型サイリスタは、ターンオフ時のキャリア排出部に絶縁ゲート型トランジスタ構造を導入したことを特徴とする。

【0020】

【作用】本発明によれば、キャリア排出部に絶縁ゲート型トランジスタ構造を導入することによって、優れたオン特性を維持しながら、高速でターンオフできる絶縁ゲート型サイリスタが得られる。また、寄生バイポーラトランジスタや寄生サイリスタ動作を抑制し、高いターンオフ能力を実現することができる。

【0021】

【実施例】以下、図面を参照しながら本発明の実施例を説明する。なお以下の各実施例では原則として、通常種々の繰り返しパターンで一つの基板上にレイアウトされるサイリスタの単位セル部分のみ構造を示す。

【0022】図1は、本発明の一実施例に係る絶縁ゲート型サイリスタである。高抵抗のn- 型ベース層1の一方の面に所定間隔をもってストライプ状に一対の溝4が形成されている。溝4には、内壁にゲート絶縁膜が形成されてゲート電極材料が平坦に埋め込まれた絶縁ゲート電極5が設けられている。溝4に挟まれた領域のn- 型ベース層1の表面には、n+ 型カソード層(ソース層)7が形成されている。n- 型ベース層1の他方の面には、n型バッファ層2を介してp+ 型アノード層(ドレイン層)3が形成されている。これにより、カソード層7下の溝4で挟まれた領域がチャネル領域6となるSIサイリスタが構成されている。

【0023】絶縁ゲート電極5とカソード層7が形成された領域がダイオード領域であって、その端部,すなわちストライプ状のゲート電極5の端部に接する領域が、ターンオフ時にn- 型ベース層1内のホールをカソード側に排出するホールバイパス領域である。絶縁ゲート電極5の側面部に接する状態で縦方向に、p+ 型ソース層8,n型チャネル層9およびp+型ドレイン層10が形成されて、絶縁ゲート電極5をSIサイリスタ部と共有するホール排出用の縦型のpチャネルMOSトランジスタが構成されている。

【0024】素子裏面のp+ 型アノード層3にはアノード電極11が形成され、素子表面には、仮想的に破線で示したが、n+ 型カソード層7およびp+ 型ドレイン層10に同時にコンタクトするカソード電極12が形成される。

【0025】この絶縁ゲート型サイリスタの動作を説明する。絶縁ゲート電極5にカソードに対して正の電圧を印加すると、チャネル領域6には空乏層が形成されないので、n+ 型カソード層7から電子が注入されてターンオンする。

【0026】絶縁ゲート電極5にカソードに対して負の電圧を印加すると、チャネル領域6に空乏層が拡がり、n+ 型カソード層7からの電子注入が抑制される。このとき同時に、ゲート電極5の端部に形成された縦型pチャネルMOSトランジスタがオンとなり、n- 型ベース層1内に蓄積しているホールがこのMOSトランジスタを通してカソード電極に排出される。これにより、サイリスタはターンオフする。

【0027】この実施例によれば、従来のようなサイリスタと同時にオンする寄生バイポーラトランジスタがない。すなわちホール排出領域にはホールの蓄積は少なく、ターンオフ時のn- 型ベース層1のホール排出が縦型MOSトランジスタによって速やかに行われる。これによりターンオフ時間の短縮が図られる。

【0028】図2は、図1の実施例の各部の導電型を逆にした実施例である。高抵抗のp- 型ベース層21の一方の面にストライプ状に一対の溝24が形成され、溝24には絶縁ゲート電極25が埋込み形成されている。溝24に挟まれた領域のp- 型ベース層21の表面に、p+ 型アノード層27が形成されている。p- 型ベース層21の他方の面にはp型バッファ層22を介してn+ 型カソード層23が形成されている。アノード層27下の溝24で挟まれた領域がチャネル領域26となる。

【0029】絶縁ゲート電極25とアノード層27が形成された領域がダイオード領域であって、その端部に接する領域が、ターンオフ時にp- 型ベース層21内の電子をアノード側に排出する電子バイパス領域である。すなわち絶縁ゲート電極25の側面部に接する状態で縦方向に、n+ 型ソース層28,p型チャネル層29およびn+ 型ドレイン層30が形成されて、絶縁ゲート電極25をSIサイリスタ部と共有する、電子排出用の縦型のnチャネルMOSトランジスタが構成されている。

【0030】素子裏面のn+ 型カソード層23にはカソード電極12が形成されている。素子表面には、p+ 型アノード層27およびn+ 型ドレイン層30に同時にコンタクトするアノード電極11が形成される。

【0031】この実施例によっても、先の実施例と同様に短いターンオフ時間が得られる。

【0032】図3は、カソード側とアノード側に共に埋込み絶縁ゲート電極を設けた実施例の絶縁ゲートサイリスタである。n- 型ベース層1のカソード側には、図1の実施例と同様の構造で第1の埋込み絶縁ゲート電極5およびn+ 型カソード層7が形成される。n- 型ベース層1の他方の面にはp- 型チャネル層32を介してp+ 型アノード層3が形成されている。そしてこのアノード側にも、n- 型ベース層1に達する溝35がカソード側と同様にストライプ状をなして形成され、この溝35に第2の絶縁ゲート電極36が埋込み形成されている。

【0033】この様に構成されたダイオード領域の端部には、n- 型ベース層1のカソード側にp+ 型層33、アノード側にn+ 型層34が形成されて、逆並列ダイオードが構成されている。

【0034】サイリスタのp+ 型アノード層3および逆並列ダイオードのカソード層であるn+ 型層34に同時にコンタクトするアノード電極11が形成され、サイリスタのn+ 型カソード層7および逆並列ダイオードのアノード層であるp+ 型層33に同時にコンタクトするカソード電極(図示せず)が形成されている。

【0035】この素子をターンオンするには、第1のゲート電極5にカソード電極に対して正の電圧を印加する。第2のゲート電極36は零バイアスのままでよい。これにより、n+ 型カソード層7から電子注入がなされて、ターンオンする。

【0036】ターンオフ時は、第1のゲート電極5にカソードに対して負の電圧を印加し、同時に第2のゲート電極36にアノードに対して正の電圧を印加する。これにより、n+ 型カソード層7からの電子注入が抑制されると同時に、アノード側ではp- 型チャネル層33の電位が上昇して空乏化し、p+ 型アノード層3からのホール注入が抑制される。また、n- 型ベース層1内の蓄積キャリアは、ホールがp+ 型層33を介してカソード電極へ、電子がn+ 型層34を介してアノード電極11へそれぞれ排出される。

【0037】こうしてこの実施例によれば、ターンオフ時には、カソード側,アノード側で共にキャリア注入が抑えられ、さらに逆並列ダイオードによって蓄積キャリアの排出がなされるため、高速のターンオフができる。

【0038】図4は、図3の実施例のキャリア排出を行う逆並列ダイオードの部分を、縦型MOSトランジスタ構造とした実施例である。カソード側には、図1の実施例と同様に、第1の絶縁ゲート電極5の端部に接してp+ 型ソース層8,n型チャネル層9およびp+ 型ドレイン層10が形成されて縦型のpチャネルMOSトランジスタが構成されている。アノード側には、第2の絶縁ゲート電極36の端部にに接してn+ 型ソース層37,p型チャネル層38およびn+ 型ドレイン層39が形成されて、縦型のnチャネルMOSトランジスタが構成されている。

【0039】この実施例の素子は、ターンオフ時、第1の絶縁ゲート電極5に負の電圧を印加することによってカソード側のpチャネルMOSトランジスタがオンし、第2の絶縁ゲート電極36に正の電圧を印加することによってアノード側のnチャネルMOSトランジスタがオンする。これらの縦型MOSトランジスタによって、n- 型ベース層のキャリア排出が行われる。サイリスタがオン状態では、これらの縦型MOSトランジスタはオフに保たれる。

【0040】したがってこの実施例によれば、優れたオン特性を維持しながら、高速のターンオフが可能になる。

【0041】図5は、カソード側からの溝4をp+ 型アノード層3に達するまで深く形成した実施例である。キャリア排出領域は、n- 型ベース層1の表面にp+ 型層10が形成されて、pnpトランジスタが構成されている。このキャリア排出領域の構造は、従来の図141のそれと同様である。

【0042】この実施例の素子は、ターンオン時、絶縁ゲート電極5に正の電圧を印加すると、溝4の側壁にn+ 型カソード層7からn型バッファ層2にまで達する電子蓄積層が形成され、n+ 型カソード層7がこの蓄積層を介してn型バッファ層2につながるため、速やかに定常オン状態にまで素子電圧が降下する。ターンオフ時は、絶縁ゲート電極5に負の電圧を印加すると、溝4の側壁にp型チャネルが形成される。n- 型ベース層1内のホールはこのp型チャネル層を介し、p+ 型層10を介してカソード電極に排出される。

【0043】従ってこの実施例の素子は、ターンオン,ターンオフともに高速になる。

【0044】図6は、図5の実施例の素子の各部の導電型を逆にした実施例である。詳細な説明は省略するが、この実施例の素子でも高速のターンオン,ターンオフが可能である。

【0045】図7は、図5の実施例の素子を変形した実施例である。この実施例では、溝4がウェハのカソード側表面からアノード側表面にまで貫通する状態で形成されて、この中に絶縁ゲート電極5が埋込み形成されている。

【0046】この実施例の素子は、製造する際に溝4が基板を貫通して設けられるので、ゲート絶縁膜の形成時、溝4内に酸素が十分に供給されて、均一な膜厚のゲート絶縁膜が得られる。埋込みゲート電極5をCVD法による多結晶シリコンで形成する場合にも同様に、原料ガスが溝4内に十分に供給されるので、均一に電極埋込みが行われる。

【0047】以上の図1から図7の実施例において、溝間のチャネル領域となる部分が低いバイアス状態で完全空乏化する素子を得るためには、その幅と不純物濃度を最適設計する必要がある。具体的に例えば、チャネル領域の不純物濃度を5×1013/cm3 とする。このとき、ゲート電極側から伸びる空乏層の飽和値は5μm 以上となるから、溝を反応性イオンエッチングによって間隔5μm 以下の狭い状態で加工すれば、しきい値の浅い素子が容易に得られる。

【0048】図8は、溝間隔を更に微小値に設定した実施例の素子である。図8(a) に示すように、半導体基板中央部に高抵抗のn- 型ベース層1が設けられている。基板の一方の面にはn- 型ベース層1に達する深さの第1の溝4が、例えば1μm 以下の微小間隔をもって形成されて、この中に第1の絶縁ゲート電極5が埋込み形成されている。基板の他方の面にも同様に微少間隔の第2の溝35がn- 型ベース層1に達する深さに形成されて、ここに第2の絶縁ゲート電極36が埋込み形成されている。

【0049】第1の溝4の間にはn- 型ベース層1に接するn型チャネル層42が形成され、その表面部にn+ 型カソード層7が形成されている。第2の溝35の間にも、n- 型ベース層1に接するn型チャネル層43が形成され、その表面部にp+ 型アノード層3が形成されている。アノード層3にはアノード電極11が形成され、カソード層7にはカソード電極12が形成されている。

【0050】この素子をオン電圧の小さい十分なオン状態にするには、図8(b) に示すように、第1の絶縁ゲート電極5にカソードに対して正の電圧を印加し、第2のゲート電極36にアノードに対して負の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42は高濃度の電子蓄積層42aとなり、ここまで実質的なカソード層となる。第2の絶縁ゲート電極36に挟まれた領域のn型チャネル層43は逆にp型反転層43aとなり、低濃度のアノード層3は高濃度のホール蓄積層となって、これら全体が実質的なアノード層となる。この結果、カソード・アノード間距離が実質的に小さいものとなり、順バイアス時のカソードからの電子注入,アノードからホール注入の効率が大きく向上し、低いオン電圧が得られる。

【0051】この素子をオフにするには、図8(c) に示すように、第1の絶縁ゲート電極5にカソードに対して負の電圧を印加し、第2のゲート電極36にアノードに対して正の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42はp型反転層42bとなり、第2の絶縁ゲート電極36に挟まれた領域のn型チャネル層43は逆に高濃度の電子蓄積層43bとなる。これにより、カソード・アノード間はpnpn構造となって、カソードからの電子注入、アノードからのホール注入が止り、素子はターンオフする。

【0052】この実施例によれば、ターンオン時のキャリア注入効率の向上およびターンオフ時のキャリア注入の抑制が効果的に行われる。なおこの実施例において、ターンオフ時のn- 型ベース層1内のキャリア排出のための構造として、先の各実施例で用いたものを利用することができる。

【0053】図9は、図8の実施例を変形した実施例である。この実施例では、図8のアノード側のn型チャネル層43に代ってp型チャネル層44を用いている。

【0054】この素子をオン状態にするには、図8の実施例と同様、図9(b) に示すように、第1の絶縁ゲート電極5にカソードに対して正の電圧を印加し、第2のゲート電極36にアノードに対して負の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42は高濃度の電子蓄積層42aとなり、第2の絶縁ゲート電極36に挟まれた領域のp型チャネル層44は高濃度のホール蓄積層44aとなる。従って先の実施例と同様に、順バイアス時のカソードからの電子注入,アノードからホール注入の効率が大きく向上し、低いオン電圧が得られる。

【0055】この素子をオフにするには、図9(c) に示すように、第1の絶縁ゲート電極5にカソードに対して負の電圧を印加し、第2のゲート電極36にアノードに対して正の電圧を印加する。このとき、第1の絶縁ゲート電極5に挟まれた領域のn型チャネル層42はp型反転層42bとなり、第2の絶縁ゲート電極36に挟まれた領域のp型チャネル層44はn型反転層44bとなる。これにより、カソード・アノード間はpnpn構造となって、カソードからの電子注入、アノードからのホール注入が止り、素子はターンオフする。

【0056】なお以上において、図1の実施例に対して図2の実施例を示したように、他の実施例についても各部の導電型を逆にして構成することができる。またオン時のエミッタ注入効率を高くするために、エミッタ接合部にヘテロ接合を用いることも有用である。

【0057】次に、埋込み絶縁ゲート構造であって、溝間隔が大きいものであってもノーマリオフ型となる絶縁ゲート型のSIサイリスタの実施例を説明する。

【0058】図10は、その様な実施例のSIサイリスタの断面図である。高抵抗のn- 型ベース層1の一方の面にp型ベース層45が形成され、このp型ベース層45の表面にn+ 型カソード層(ソース層)7が形成されている。n- 型ベース層1の裏面にはp+ 型アノード層(ドレイン層)3が形成されている。カソード側には、n- 型ベース層1に達する深さの溝4が少なくとも一対形成され、この溝4に絶縁ゲート電極5が埋込み形成されている。

【0059】n+ 型カソード層7にはカソード電極12が形成され、p+ 型アノード層3にはアノード電極11が形成されている。またp型ベース層45には直接接続されたゲート電極46が設けられている。

【0060】この実施例の素子は、pnpn構造を有するから、ゲートバイアス零のときはオフであり、ノーマリオフ型となる。絶縁ゲート電極5にカソードに対して正の電圧を印加すると、p型ベース層45の溝4側壁部にn型チャネルが形成されて、n+ 型カソード層7からの電子がn- 型ベース層1に注入される。注入された電子がp+ 型アノード層に達すると、p+ 型アノード層3からはホールが注入され、サイリスタはターンオンする。

【0061】絶縁ゲート電極5をカソードに対して負または零とすることにより、カソード層7からの電子注入が止まり、素子はターンオフする。このとき、n- 型ベース層1内に蓄積されたホールはこのn- 型ベース層1に直接接続されたゲート電極46を介して外部に排出され、高速のターンオフができる。

【0062】なお、ゲート電極46は独立に端子として取り出してもよいし、カソード電極と短絡してもよいが、ツェナーダイオードかまたは、ターンオフ時に導通するように制御されるMOSトランジスタを設けておくことが好ましい。

【0063】この実施例によれば、ノーマリオフ型であって、高速のターンオン,ターンオフができるSIサイリスタが得られる。またオフ時には、n-型ベース層1とp型ベース層45のpn接合部でn- 型ベース層側に空乏層が伸びることによって、高耐圧特性が保証される。

【0064】p+ 型アノード層3の部分を、図に示すようにn+ 型層とすれば、サイリスタではなく、絶縁ゲート型のSIトランジスタとなる。このことは、図11以下の実施例でも同様である。

【0065】図11は、図10の実施例を変形して、溝4をアノード層3に達する深さに形成した実施例である。この実施例では、ターンオン時、n- 型ベース層1の溝4の側壁部に沿って電子蓄積層が形成されるため、速やかにカソード・アノード間が導通する。したがってより高速のターンオンができる。

【0066】また、ターンオフ時、絶縁ゲート電極5にカソードに対して負の電圧を印加すれば、n- ベース層1の溝4側壁部にはp型反転層が形成される。そしてn- 型ベース層1内の蓄積ホールはこのp型反転層を介し、p型ベース層45を介して外部に速やかに排出される。従って、ターンオフ動作も高速に行われる。

【0067】図12〜図15はやはり図10の実施例を変形した実施例であり、p型ベース層45とn+ 型カソード層7の間に低濃度のn-型チャネル層47が設けられている。溝4は、図12ではn- 型チャネル層47の途中まで、図13ではp型ベース層45の途中まで、図1414ではn- 型ベース層1の途中まで、図15ではアノード層3に達する深さまで形成されている。これら図12R>2〜図15の実施例でも、絶縁ゲート電極5にカソードに対して負の電圧を印加して、n- 型チャネル層47の電位を下げてカソード層7からの電子注入を抑制することにより、ターンオフすることができる。

【0068】なお図12の実施例では、絶縁ゲート電極5によってp型ベース層45の電位は制御されないから、ターンオン時にはp型ベース層45に接続されたゲート電極46にカソードに対して正の電圧を印加する。

【0069】図14の実施例では、ターンオン時、絶縁ゲート電極5に印加する正電圧によってp型ベース層45の溝4側壁にn型チャネルが形成されて、高速ターンオンができる。

【0070】図15の実施例では、図11の実施例と同様に、溝4の側壁に形成される蓄積層または反転層によって、高速のターンオン,ターンオフが可能である。

【0071】図16(a) は、図10の実施例について、p型ベース層45からのゲート電極46の取り出し方の具体的構造を示している。図に示すように、ストライプ状にパターン形成されるカソード層7の長手方向端部にp型ベース層45が露出しており、ここにゲート電極46が形成されている。

【0072】図16(b) は、この実施例の素子構造を等価回路で示したものである。ただしこの等価回路は、基本素子がpnpn構造を持つSIサイリスタではなく、npn構造のSIトランジスタの場合である。トランジスタTのドレイン・ソース間にEタイプMOSトランジスタQ1 が接続され、ドレインに直列にDタイプMOSトランジスタQ2 が接続された形になる。EタイプMOSトランジスタQ1 は、p型ベース層45をチャネル領域とするトランジスタであり、DタイプMOSトランジスタQ2 は、絶縁ゲート電極5がn- 型ベース層1中に埋め込まれた部分のn- 型ベース層1をチャネル領域とするトランジスタである。

【0073】図17(a) は、図14の実施例について、p型ベース層45からのゲート電極46の取り出し方の具体的構造を示している。図16と同様に、ストライプ状にパターン形成されるカソード層7およびn- 型チャネル層47の長手方向端部にp型ベース層45が露出しており、ここにゲート電極46が形成されている。

【0074】図17(b) は、この実施例の素子構造を、基本素子がSIトランジスタの場合について等価回路で示したものである。トランジスタTのドレイン・ソース間にEタイプMOSトランジスタQ1 が接続され、ドレインおよびソースにそれぞれ直列にDタイプMOSトランジスタQ2 およびQ3 が接続された形になる。EタイプMOSトランジスタQ1 は、p型ベース層45をチャネル領域とするトランジスタであり、ドレイン側のDタイプMOSトランジスタQ2 は、絶縁ゲート電極5がn- 型ベース層1中に埋め込まれた部分のn- 型ベース層1をチャネル領域とするトランジスタであり、ソース側のDタイプMOSトランジスタQ3 は、n- 型チャネル層47をチャネル領域とするトランジスタである。

【0075】図18(a) (b) は、図10および図16の実施例を変形して、ターンオフ時のホール排出用の縦型MOSトランジスタを導入した実施例である。図18(a) に示すように、ストライプ状の絶縁ゲート電極5の端部に、図1の実施例と同様にして、p型ソース層8、n型チャネル層9およびp型ドレイン層10が形成されて、ゲート電極5を共有する縦型のpチャネルMOSトランジスタが構成されている。

【0076】縦型MOSトランジスタのドレイン電極41は、実際にはカソード電極12と一体に連続的に形成される。カソード層7の端部には、図16或いは図17の実施例と同様にp型ベース層45が露出していて、ここにもゲート電極46が形成されている。ただし、このゲート電極46は必ずしも必要ではない。このゲート電極46を設けなければ、カソード側はドレイン電極41を兼ねてカソード電極12を全面に形成してた単層電極構造とすることができる。

【0077】この様な単層電極構造は、大電力用素子として、圧接電極構造を採用する場合に有利である。

【0078】図18(b) は、基本素子がやはりSIトランジスタである場合についての等価回路を示している。トランジスタTに並列に接続されるMOSトランジスタQ1、ドレインに直列接続されるMOSトランジスタQ2は、先の実施例と同様である。この実施例で導入されたホール排出用の縦型MOSトランジスタは、Q4 として、p型ベース層とソース間に挿入された形になる。

【0079】図19(a) (b) は、図14および図17の実施例を変形して、図18と同様に、ターンオフ時のホール排出用の縦型MOSトランジスタを導入した実施例である。等価回路は、図17(b) に対して、MOSトランジスタQ4 が付加された形になっている。

【0080】図20は、図18の実施例を変形した実施例である。この実施例では、素子のメイン・チャネルとp型ベース層45の露出部、およびターンオフ時のホール排出用縦型MOSトランジスタのチャネル領域を一列に並べて、埋込み絶縁ゲート電極5を、メイン・チャネルを制御するゲート電極(G1 )51 とホール排出用縦型MOSトランジスタのチャネルを制御するゲート電極(G2 )52 とに分離して別々に形成した実施例である。

【0081】この実施例の素子でのターンオフ時の二つのゲートG1 ,G2 の駆動例を図20(b) に示した。図に示すように先ず、ゲートG1 に負の電圧を印加してホール排出用MOSトランジスタを導通状態とし、これに遅れてゲートG2 に負の電圧を印加してメイン・チャネルでの電子注入を止める。

【0082】この実施例のようなゲート駆動によって、ターンオフ時のメイン・チャネルでの電子注入の抑制が効率的になり、高いターンオフ能力が得られる。

【0083】図21は、図19の実施例の素子について同様に、埋込み絶縁ゲート電極5を、メイン・チャネルを制御するゲート電極51 とホール排出用縦型MOSトランジスタのチャネルを制御するゲート電極52 とに分離して別々に形成した実施例である。図21(b) は、図2020(b) と同様のゲート駆動法を示している。

【0084】この実施例によっても、高いターンオフ能力が得られる。

【0085】図22は、図13の実施例の素子において、溝4の間隔を十分に小さく、例えば1μm 以下に設定した実施例である。図22(a) に示すように、n+ 型カソード層7とp型ベース層45の間にはn型ウェル層51(図13のn- 型チャネル層47に相当する)が設けられている。

【0086】この実施例の素子をターンオンするには、図22(b) に示すように、絶縁ゲート電極5にカソードに対して正の電圧を印加する。このとき、n型ウェル層51は全体が高濃度n+ の電子蓄積層51aとなり、実質的にカソード層がp型ベース層45に接する状態となる。この結果カソードの電子注入効率が向上する。

【0087】この実施例の素子をターンオフするには、図22(c) に示すように、絶縁ゲート電極5にカソードに対して負の電圧を印加する。この時、n型ウェル層51は全体が高濃度p+ の反転層51cとなる。これにより、カソードからの電子注入が効果的に抑制される。

【0088】図23は、図22の実施例の溝4をn- 型ベース層1に達する深さまで掘り下げた実施例である。図22の実施例と同様に、ターンオン時は図23(b) に示すようにゲート電極に正の電圧を与え、ターンオフ時は図23(c) に示すようにゲート電極5に負の電圧を与える。この実施例では、ターンオン時、p型ベース層45の側壁にn型チャネルが形成されるために、より高速のターンオン動作が可能になる。

【0089】なお図23の実施例に於いて、溝4の深さは、n- 型ベース層1内に食い込まないように、p型ベース層45とn- 型ベース層1の接合部ぎりぎりの位置までとすることが特性上好ましい。それ以上深くすると、溝4に挟まれた領域でn- 型ベース層1の電位が制御されて、サイリスタ特性が悪化する可能性があるからである。

【0090】図24は、図22の実施例のn型ウェル51の部分をp型ウェル52に置き換えた実施例である。この場合、ターンオン時にはゲート電極5に負の電圧を印加して、図24(b) に示すようにp型ウェル52をn型反転層52aとする。ターンオフ時はゲート電極5に正の電圧を印加して、図24(c) に示すようにp型ウェル52の部分をp型の電子蓄積層52cとする。

【0091】図25は、図23の実施例のn型ウェル51の部分をp型ウェル52に置き換えた実施例である。この場合、ターンオン時にはゲート電極5に負の電圧を印加して、図25(b) に示すようにp型ウェル52をn型反転層52aとする。ターンオフ時はゲート電極5に正の電圧を印加して、図25(c) に示すようにp型ウェル52の部分をp型の電子蓄積層52cとする。

【0092】なおこれら図22〜図25の実施例においても、先の実施例と同様に、n- 型ベース層1内のホール排出用の縦型MOSトランジスタを組み込むことは有効である。

【0093】図26(a) (b) は、図14の実施例のサイリスタ構造の場合の断面図と等価回路図を示している。図26(b) に示すように、サイリスタTh のnpnトランジスタ部分に対して並列にEタイプMOSトランジスタQ1 が入り、カソード側に直列にDタイプMOSトランジスタQ3 が入る。トランジスタQ1 は、p型ベース層45をチャネルとするnチャネルMOSトランジスタであり、Q3 はn- 型チャネル層47をチャネルとするnチャネルMOSトランジスタである。

【0094】図27(a) (b) は、図26(a) (b) の実施例に対して、n- 型ベース層1内のホール排出のための高濃度p+ 型層33を設けた実施例の断面構造と等価回路である。ストライプ状にパターン形成されるn+ 型カソード層7の端部に、p型ベース層45に繋がる深さのp+ 型層33が形成されている。図ではカソード電極を省略しているが、カソード電極はn+ 型カソード層7と同時にp+ 型層33にもコンタクトするように全面に配設される。

【0095】p型ベース層45の横方向抵抗Rが、図27R>7(b) に示すように、サイリスタのp型ベース層をカソードに短絡する抵抗Rとなる。

【0096】図28(a) 〜(c) は、アノード側に埋込み絶縁ゲート電極36を有する絶縁ゲートサイリスタにおいて、p+ 型エミッタ層3とn- 型ベース層1の間に低濃度のp- 型チャネル層54が設けられた実施例である。図28(a) では、絶縁ゲート電極36の埋込み溝35がp+ 型エミッタ層3からp- 型チャネル層54の途中まで達する深さに形成されている。図28(b) では、埋込み溝35がn- 型ベース層1に達する深さに形成され、図28(c) では埋込み溝35がp型ベース層45に達する深さに形成されている。

【0097】これらの実施例によっても、ゲートバイアスは逆になるが、先の図12〜図14の実施例で説明したと同様の原理で高速のターンオン,ターンオフが可能である。

【0098】図29(a) (b) は、図28(b) の実施例について、具体的にp型ベース層からのゲート電極46の取出しの構造と等価回路を示している。ゲート電極46の取り出し構造は、先の図16,図17等の実施例と同様である。等価回路は、図29(b) に示すように、サイリスタTh のアノード側に直列にDタイプのpチャネルMOSトランジスタQ5 が接続された形になる。

【0099】図30は、カソード側に埋込み絶縁ゲート電極5を設けると共に、アノード側にも同様に埋込み絶縁ゲート電極36を設けた別の実施例の絶縁ゲートサイリスタである。p型ベース層45には直接ゲート電極46が接続されている。p+ 型エミッタ層3とn- 型ベース層1の間にはp- 型チャネル層54が設けられている。

【0100】図31は、図30の構造を僅かに変形した実施例で、n+ 型エミッタ層7とp型ベース層45の間にn- 型チャネル層47が形成されている。

【0101】これら図30,図31の実施例においても、ターンオフ時、カソード側からの電子注入とアノード側からのホール注入が抑制でき、高速のターンオフ動作が可能である。

【0102】図32(a) (b) は、図31の素子構造のp型ベース層45からのゲート電極取り出し構造と等価回路を示す。ストライプ状に形成されるn+ 型エミッタ層7の端部に、n- 型ベース層1に達する深さにp+ 型層33が形成され、ここに図示しないゲート電極が接続される。図では、アノード側にも、n- 型ベース層1をアノード電極11に短絡するn+ 型層34が、やはりストライプ状に形成されるp+ 型エミッタ層3の端部に形成されている。

【0103】図33は、図26の実施例の素子構造を基本として、カソード側にエミッタ短絡用のpチャネルMOSトランジスタを組み込んだ実施例である。p型ベース層45上に、n- 型チャネル層47が形成され、さらにn型ウェル層56(n型エミッタ層)が形成されている。このn型ウェル層56表面からn- 型ベース層1に達する深さに溝4が形成されて、ここに絶縁ゲート電極5が埋込み形成されている。n型ウェル層56の溝4の側壁部にp+ 型ドレイン層57が形成され、カソード電極12はn型ウェル層56と同時にこのp+ 型ドレイン層57に接続されている。

【0104】この実施例の素子では、ターンオフ時、絶縁ゲート電極5にカソード電極に対して負の電圧を印加すると、溝4の側壁からn- 型チャネル層47にのびる空乏層によってn型ウェル層45からの電子注入が抑制される。同時に、n型ウェル層56およびn- 型チャネル層47の側壁に形成されるp型チャネルを介してn- 型ベース層1内のホールがカソード電極12に排出される。これにより、高速のターンオフ動作ができる。

【0105】図34は、図33の実施例に加えて、カソード側にもエミッタ短絡用のnチャネルMOSトランジスタを同様の構造をもって組み込んだ実施例である。すなわちn- 型ベース層1のアノード側に、所定厚みのp型ウェル層58(p型エミッタ層)が形成され、これを貫通する形で溝35とこれに埋め込まれた絶縁ゲート電極36が形成される。そしてp型ウェルの溝35の側壁部にn+ 型ドレイン層59が形成される。アノード電極14は、p型ウェル層58と同時にこのn+ 型ドレイン層59に接続される。

【0106】この実施例の素子のターンオフ駆動は、好ましくは次のように行う。まずアノード側のゲート電極36にアノード電極14に対して正の電圧を印加する。これにより、p型ウェル層58の溝35側壁に形成されるn型チャネルを介してn-型ベース層1がアノード電極14に短絡されたアノード短絡状態となり、アノード側からのホール注入が抑制される。その後カソード側のゲート電極5にカソード電極12に対して負の電圧を印加する。これにより、カソード側の電子注入を抑制すると同時に、ホールをカソード電極13に排出する。

【0107】この様なゲート駆動を行うことによって、効率的なターンオフができる。

【0108】図35は、図33の実施例の構造を3次元的に展開した実施例の絶縁ゲートサイリスタである。ストライプ状に埋込み形成される絶縁ゲート電極5に沿って、p型ドレイン層57が複数個に分割されて配置される。図33の素子断面では、絶縁ゲート電極5に挟まれた領域内にn型ウェル層56とp+型ドレイン層57が同時に形成されているのにたいして、この実施例では、図33と同じ素子断面について見ると、在る箇所ではp型ドレイン層57のみ、他の箇所ではn型ウェル層56のみが見える状態になっている。

【0109】図36は、同様に図34の実施例の素子を3次元的に展開した実施例の絶縁ゲートサイリスタである。カソード側のp+ 型ドレイン層57と同様に、アノード側のn+ 型ドレイン層59が、ストライプ状の埋込み絶縁ゲート電極36に沿って複数個に分割配置されている。

【0110】これら図35および図36の実施例では、埋込みゲート電極の間の領域の幅いっぱいをMOSトランジスタのドレイン領域として利用することができる。したがって、図33および図34の実施例と比較すると、溝4および35の間隔を狭くすることが容易である。溝4および35の間隔を狭くすれば、それだけターンオフ時の絶縁ゲート電極側からの空乏化によるキャリア注入の抑制効果が大きくなり、ターンオフ能力の向上が可能になる。

【0111】図37(a) (b) は、図27の実施例の素子構造に更に、カソード側に縦型のnチャネルMOSトランジスタを組み込んだ実施例の素子構造と等価回路である。p型ベース層45上にn- 型チャネル層47,n型ウェル層56が形成され、更にこの上にp型ウェル層61,n+型ソース層62が形成されている。n+ 型ソース層62の表面からn- 型ベース層1に達する深さに溝4が形成されて、絶縁ゲート電極5が埋込み形成されている。これにより、p型ウェル61の溝側壁をチャネル領域とするnチャネルMOSトランジスタQ6 が、図37R>7(b) に示すように、サイリスタのカソードに直列に入った状態になる。またストライプ状のカソード領域の端部には、n- 型ベース層1に達する深いp+ 型層10が拡散形成されている。

【0112】この実施例の素子をターンオンするには、絶縁ゲート電極5にカソード電極に対して正の電圧を印加する。この時、p型ウェル層61とp型ベース層45の溝側壁にn型チャネルが形成され、n+ 型ソース層62から電子がn- 型ベース層1に注入される。この電子注入に対応してp+ 型エミッタ層3からホール注入がなされて、高速にターンオンする。

【0113】ターンオフの際には絶縁ゲート電極5にカソード電極に対して負の電圧を印加する。これによりn型チャネルは消滅してn+ 型ソース層62からの電子注入は止まり、同時にn- 型チャネル層47に広がる空乏層によって電子注入が抑制される。n- 型ベース層1に蓄積していたホールは、p+ 型層10を介してカソード電極に排出される。以上により、素子はターンオフする。

【0114】この実施例によれば、カソード側の電子注入がカソード側に直列に入ったMOSトランジスタの導通状態と、その下のn- 型チャネル層への空乏層の広がりによって効果的に制御されるので、高いターンオフ能力が得られる。

【0115】図38(a) (b) は、図37の素子を変形した実施例の素子断面構造と等価回路である。この実施例では、ストライプ状の埋込みゲート電極5に沿って、n+ 型ソース層62が複数個に分割されて配置されている。したがってカソード側にはp型ウェル層61も露出しており、カソード電極(図では省略している)がn+ 型ソース層62と同時にp型ウェル層61にもコンタクトしている。図37の実施例で設けられているホール排出用のp+ 型層10はこの実施例では設けられていない。

【0116】したがってこの実施例の素子は、図38(b) に示すように、カソード側に直列にnチャネルMOSトランジスタQ6 が入ると同時に、p型ベース層とカソードの間に、p型ウェル層61の抵抗を介してn型ウェル層56およびn- 型チャネル層46をチャネルとするpチャネルMOSトランジスタQ4 が入った形になっている。

【0117】この実施例の素子では、pチャネルMOSトランジスタQ4 がターンオフ時のn- 型ベース層1のホール排出用として機能する。この実施例によると、先の実施例と異なり、n- 型ベース層1のホールが直接カソードに抜ける経路がないので、サイリスタのオン特性を損なうことなく、高いターンオフ能力を実現することができる。

【0118】図39(a) (b) は、さらに図37或いは図38の実施例の素子を変形した実施例の素子構造と等価回路である。この実施例では、埋込み絶縁ゲート電極5を長手方向に複数個に分割して配置し、その長手方向端部に挟まれた領域に、図1の実施例と同様の構造でpチャネルMOSトランジスタを形成している。

【0119】この実施例によっても、オン特性を損なうことなく、優れたターンオフ能力を持つ絶縁ゲート型サイリスタが得られる。またホール排出用のpチャネルMOSトランジスタは、サイリスタ本体の拡散層とは別個の拡散層を利用して形成しているので、その拡散層の不純物濃度をサイリスタ本体とは独立に設定することができ、所望のしきい値等特性の最適化が容易である。

【0120】図40(a) (b) は、図37の素子構造を基本として、これと図32の構造とを組み合わせた実施例の素子構造と等価回路である。アノード側にもp- 型チャネル層54が形成され、埋込み絶縁ゲート電極36が形成されている。ストライプ状ゲート電極36の端部には、アノード側,カソード側にそれぞれ、エミッタ短絡用のp+ 型層33,n+ 型層34が形成されている。

【0121】この実施例の素子も、ターンオフ時、カソード側の電子注入とアノード側のホール注入がそれぞれ、縦型のMOSトランジスタQ6 ,Q5により抑制され、高いターンオフ能力が得られる。

【0122】図41(a) (b) は、カソード側の構造を図3838と同様とし、アノード側の構造を図40と同様とした実施例の素子構造と等価回路である。

【0123】この実施例によっても、ターンオフ時、カソード側の電子注入とアノード側のホール注入がMOSトランジスタQ6 ,Q5 により抑制されて高いターンオフ能力が得られる。しかも、n- 型ベース層のホールが直接カソード電極に抜ける経路はないので、サイリスタのオン特性を損なうことはない。

【0124】図42(a) (b) は、図39と図40の構造を組み合わせた実施例の素子構造と等価回路である。

【0125】この実施例によっても、ターンオフ時、カソード側の電子注入とアノード側のホール注入がMOSトランジスタQ6 ,Q5 により抑制されて高いターンオフ能力が得られる。n- 型ベース層のホールが直接カソード電極に抜ける経路はないので、サイリスタのオン特性を損なうことはない。ホール排出用のpチャネルMOSトランジスタは、サイリスタ本体の拡散層とは別個の拡散層を利用しているので、その拡散層の不純物濃度の最適化が容易である。

【0126】以上の図1から図42までの実施例において、絶縁ゲート電極が埋め込まれる溝の間隔とその領域の不純物濃度は、溝側壁からの空乏層の伸び方を考慮して最適設定される。絶縁ゲート電極により形成される空乏層幅は、絶縁ゲート電極に印加するバイアスが小さい間は反転層の少数キャリアが無視できるのでバイアスに比例して大きくなる。バイアスが大きくなって反転層のキャリアが多くなると、空乏層幅は飽和して一定値になる。この空乏層幅の飽和値は、チャネル層の不純物濃度が低いほど大きいが、例えば、不純物濃度が5×1013/cm3 以下では5μm 以上伸びる。従って反応性イオンエッチングを利用して微細間隔のゲート埋込み用溝を形成すれば、溝間を比較的低いゲートバイアスで完全空乏化して、カソード或いはアノードからのキャリア注入を止めるという制御を容易に行うことができる。

【0127】次に、カソード・エミッタに直列にMOSトランジスタを挿入した構造のEST(Emitter Switched Thyristor)と呼ばれる絶縁ゲート型サイリスタの実施例を説明する。

【0128】図43は、その基本実施例の素子構造であり、従来の図139で示す構造を改良したものである。高抵抗のn型ベース層1の一方にn型バッファ層2を介してp型エミッタ層3が形成されている。n型ベース層1の他方の面にはp型ベース層45が形成され、このp型ベース層45の表面にn型エミッタ層7が形成されている。ストライプ状のn型エミッタ層7の一辺に対向してホール排出用の高濃度p+ 型層71がストライプ状に形成され、このp+ 型層71のn型エミッタ層7側の辺に重なるようにn型ソース層72が形成されている。n型エミッタ層7とn型ソース層72により挟まれた領域のp型ベース層45上にゲート絶縁膜73を介してゲート電極74が形成されている。カソード電極12はn型ソース層72とp+ 型層71に同時にコンタクトして形成され、p型エミッタ層3にはアノード電極11が形成されている。

【0129】ここで、n型ソース層72は、図に示すように、ストライプ状のp+ 型層71に対してその長手方向に複数個に分割されて短冊状をなして、p+ 型層71の端部に配列形成されている。この点で従来の構造と異なる。

【0130】なお図では省略されているが、ゲート電極74と別に素子のターンオン用のゲート電極が必要である。そのためには例えば、p型ベース層45のp型ウェル層71に対向する端部とは反対側(図の左側)のn型エミッタ層7とn型ベース層1で挟まれた領域にゲート絶縁膜を介してゲート電極が設けられる。このことは、以下に示す実施例でも同様である。

【0131】この実施例の絶縁ゲート型サイリスタのターンオン時は、図示しないターンオン用ゲート電極を用いてn型カソード層7からn型ベース層1に電子を注入する。このときゲート電極74には、カソード電極に対して正の電圧を印加する。これによりn型エミッタ層7はn型反転チャネルを介し、n型ソース層72とを介してカソード電極12に接続される。

【0132】ターンオフ時は、ゲート電極74に零または負の電圧を印加する。これにより、n型チャネル層が消失して、n型エミッタ層7はn型ソース層72と切り離されてフローティングとなり、カソードからの電子注入が止まり、素子は高速にターンオフする。

【0133】ターンオフ時、n型ソース層72,p型ベース層45,n型ベース層1およびp型エミッタ層3からなる寄生サイリスタは、n型ベース層1のホールをカソード電極に排出する際の障害になる。n型ソース層72が、もし、p型ウェル層71の辺に沿って連続的に形成されていると、n型エミッタ層7がn型ソース層72から切り離された後にもn型ソース層72からの電子注入が止まらず、ターンオフ能力は著しく小さいものとなる。これに対してこの実施例では、n型ソース層72が複数個に分割されて配置されているから、n型ソース層72からの電子注入量は抑えられ、寄生サイリスタ効果が低減されて高いターンオフ能力が得られる。

【0134】図44〜図47は、図43の実施例の素子構造を基本として、より効果的に寄生バイポーラトランジスタ効果の影響低減を図った実施例である。

【0135】図44(a) では、p型ウェル層71の底部により高濃度のp+ 型層75が設けられている。これにより、p型ベース層45の横方向抵抗が低減されて、寄生サイリスタ効果が抑制される。図44(b) では、n型ベース層1のp型ベース層45との接合部近傍に低キャリアライフタイム層76が設けられている。これにより、n型ベース層1内の過剰ホールの寿命が短くなり、寄生サイリスタ効果が抑制されてターンオフ能力が向上する。

【0136】図45(a) では、アノード側に、n型ベース層1の一部を表面に露出させてアノード電極11に短絡するエミッタ短絡部77が設けられている。これにより、ターンオフ時、アノード側からのホール注入が抑制されるから、やはりターンオフ能力が改善される。

【0137】図45(b) では更に、p型エミッタ層3が選択的に拡散形成されてこの中にn型ソース層78が形成され、p型エミッタ層3のn型ベース層1とn型ソース層78に挟まれた領域にはゲート絶縁膜79を介してゲート電極80が形成されている。この実施例では、ターンオフ時、ゲート電極80にアノードに対して正の電圧を印加することによって、アノード側のエミッタ短絡構造が形成され、高速にターンオフができる。オン状態ではゲート電極80を零バイアスまたは負バイアスとすることにより、エミッタ短絡構造が形成されないから、サイリスタのオン特性を損なうことがない。

【0138】図46(a) は、図45(a) と図44(a) の構造を組み合わせた実施例である。図46(b) は、図45R>5(a) と図44(b) の構造を組み合わせた実施例である。図47(a) は、図45(b) と図44(b) の構造を組み合わせた実施例である。図47(b) は、図45(a) と図44(a) および(b) の構造を組み合わせた実施例である。

【0139】図48は、図47(a) の実施例の素子構造において、カソード側のゲート電極74(G1 )とアノード側のゲート電極80(G2)の駆動信号波形例を示している。オン状態では、カソード側のゲート電極74に正電圧VG1を与えて、n型エミッタ層をチャネルを介し、n型ソース層72を介してカソード電極12に接続した状態とし、アノード側のゲート電極80は零バイアスとしてp型エミッタ層3からの十分なホール注入を維持する。

【0140】ターンオフ時は、まずアノード側のゲート電極80に正電圧VG2を印加してエミッタ短絡状態としてp型エミッタ層3からのホール注入を抑制しておく。その後、カソード側のゲート電極74のバイアス電圧VG1を零に落とすことにより、n型エミッタ層7をカソード電極12から切り離し、n型ベース層1のホールをカソード電極12に排出させる。

【0141】以上のようなタイミングで二つのゲート駆動を行うことによって、高いターンオフ能力が得られる。

【0142】図49は、別の実施例の絶縁ゲート型サイリスタである。この実施例では、p型ベース層45とp型ウェル層71の対向する辺の間に、n型ベース層1が露出した状態としている。更に、p型ベース層45とp型ウェル層71の相対向する辺にそれぞれ、浅い低濃度のp型ウェル層81,82が形成されている。n型エミッタ層7のp型ウェル81側端部には高濃度のn+ 型層83が形成されている。そして、n型エミッタ層7とn型ソース層72により挟まれた領域のp型ウェル層81,82およびこれらp型ウェル層81,82に挟まれた領域に露出しているn型ベース層1を覆うようにゲート絶縁膜73を介してゲート電極74が形成されている。n型ソース層72はこの実施例では、図43の実施例と異なり、ストライプ状のp型ウェル71内では分割されずストライプ状をなして形成されている。

【0143】この実施例の素子でも、オン状態ではゲート電極74にカソードに対して正の電圧が印加される。このとき、p型ウェル層81,82の表面のn型反転チャネルとn型ベース層1を介して、n型エミッタ層7とn型ソース層72が短絡された状態となる。ターンオフ時はゲート電極74に零または負電圧が印加される。これにより、n型エミッタ層7はn型ソース層72から切り離される。

【0144】この実施例の素子では、ターンオン時にn型チャネルが形成されるp型ウェル層81,82がp型ベース層45およびp型ウェル層71とは別に形成されて、所望のしきい値に設定される。従ってp型ウェル層71のn型ソース層72下の部分を十分高濃度として横方向抵抗を小さくし、寄生サイリスタ効果を抑制して、ターンオフ時のホール排出を高速に行うことができる。

【0145】図50は、図49の実施例において、n型ソース層72を図43の実施例と同様に複数個に分割して配置した実施例の部分図である。この実施例によれば、より高いターンオフ能力が得られる。

【0146】図51〜図59は、図49或いは図50の実施例の素子構造に対して、さらにターンオフ能力の改善手段を講じた実施例である。図51の実施例では、図4444(a) と同様に、p型ウェル71の底部に高濃度のp+型層75が設けられている。図52の実施例では、図4444(b) と同様にn型ベース層1のp型ベース層45との接合部近傍に低キャリアライフタイム層76が形成されている。図53の実施例では、アノード側に図45(a)と同様のエミッタ短絡部77が設けられている。図5454の実施例では、図45(b) 同様にアノード側にMOSトランジスタによるエミッタ短絡構造が設けられている。図55の実施例は、図52と図53の実施例の構造を組み合わせたもの、図56の実施例は、図51と図54R>4の実施例の構造を組み合わせたもの、図57の実施例は、図51と図53の実施例の構造を組み合わせたもの、図58の実施例は、図51,図52および図54の実施例の構造を組み合わせたものである。図59は、図5454の構造に対して、p型ベース層45とn型ベース層1の接合部に低キャリアライフタイム層76を設けたものである。

【0147】これらの実施例の絶縁ゲート型サイリスタにおいても、優れたターンオフ能力が得られる。

【0148】図60は、別の実施例の絶縁ゲート型サイリスタである。この実施例では、p型ベース層45とこれに隣接するp型ウェル層71の間に、これらより浅く低濃度のp型チャネル層84が形成されている。p型ベース層45内のn型エミッタ層7のチャネル領域側端部には高濃度のn+ 型層83が形成されている。p型ウェル層71内のn型ソース層72は、チャネル側端部が一部p型チャネル層84の領域に入り込んだ状態で、複数個に分割されることなくストライプ状をなして形成されている。

【0149】この実施例においても、p型チャネル層84をp型ベース層45およびp型ウェル層71とは別に形成することで、n型エミッタ層7の短絡用MOSトランジスタのしきい値を最適設計することができる。そしてp型ベース層45およびp型ウェル層71を十分高濃度とすることよって、高いターンオフ能力を得ることができる。

【0150】図61は、図60の構造を変形した実施例の部分構造図であり、n型ソース層72が複数個に分割されて配列形成されている。図62は同様に図60の構造を変形した実施例の部分構造図であり、p型チャネル層84の一部をn型ベース層1を露出させている。これらの実施例によっても、図60の実施例と同様の効果が得られる。

【0151】図63は、図60の構造を基本として図44R>4(a) と同様に高濃度p+ 型層75を設けた実施例、図64は図60の構造を基本として図44(b) と同様に低キャリアライフタイム層76を設けた実施例、図65は図60の構造を基本として図45(a) と同様にアノード側のエミッタ短絡部77を設けた実施例、図66は図60R>0の構造を基本としてアノード側にも絶縁ゲートを設けた実施例である。更に図67は、図60の構造を基本としてこれに図44(a) および図45(a) の構造を組み合わせた実施例、図68は図60の構造を基本としてこれに図44(b) および図45(b) の構造を組み合わせた実施例である。

【0152】これらの実施例によって、更にターンオフ能力の向上を図った絶縁ゲート型サイリスタが得られる。

【0153】図69は、更に別の実施例の絶縁ゲート型サイリスタである。ここまでの実施例では、n型エミッタ層4のn型ソース層72とは反対側のp型ベース層45の端部にターンオン用絶縁ゲート(図では省略している)が設けられるものとした。この実施例においては、n型ソース層72を挟んでn型エミッタ層と反対側にターンオン用およびホールバイパス用のMOSトランジスタが構成されている。

【0154】すなわちp型ベース層45の端部に浅いp型ウェル層91が形成され、このp型ウェル層91内にp型ベース層45内のn型ソース層72と連続するn型ウェル層92が形成されている。このn型ウェル層92の表面にはp型ソース層93が形成されている。カソード電極12はn型ソース層72と同時にp型ソース層93にコンタクトして形成されている。またp型ソース層93とn型ベース層1の間のp型ウェル層91およびn型ウェル層92の表面を覆うようにゲート絶縁膜94を介してゲート電極95が形成されている。

【0155】なおゲート絶縁膜94およびゲート電極95は、n型ソース層72とn型エミッタ層7間をオン,オフするためのゲート絶縁膜73およびゲート電極74と一体的に形成されていても良い。

【0156】この実施例の素子は、ターンオン時、ゲート電極74および95にカソードに対して正電圧を印加する。これにより、ゲート電極95下のp型ウェル層91の表面反転層を介してn型ウェル層92からn型ベース層1に電子が注入される。同時にゲート電極74下のp型ベース層45表面の反転層を介してn型ソース層72とn型エミッタ層7が短絡され、n型エミッタ層7がカソード電極12に接続される。

【0157】ターンオフ時は、ゲート電極74および95に負電圧を印加する。これにより、n型エミッタ層7とn型ソース層72間が切り離される。また、p型ソース層93とp型ウェル層91間がn型ウェル層92の表面反転層を介して短絡される。このpチャネルMOSトランジスタの動作により、p型ベース層45はp型ウェル層91を介し、p型ソース層93を介してカソード電極12に接続され、ホール排出がなされる。

【0158】この実施例では、オン状態ではホール排出のバイパスがなく、従って優れたオン特性を維持することができる。またn型ソース層72の下は厚いp型ベース層45となっているので、寄生サイリスタ効果の影響は少ない。

【0159】図70は、図69の構造を変形した実施例である。この実施例では、p型ベース層45につながるp型ウェル層91が幅広く形成され、n型ソース層72,n型ウェル層92およびp型ソース層93はすべてこのp型ウェル層91の領域内にが形成されている。幅広く形成されるp型ウェル層75の横方向抵抗を小さくするために、その底部に高濃度p+ 型層75が形成されている。それ以外は、図60の実施例と同様である。

【0160】この実施例の素子動作は図69のそれと同じである。n型ソース層72の下が浅いp型ウェル層91になっているが、その底部にp+ 型層75が設けられているため、寄生サイリスタ効果は抑制される。

【0161】図71は、図70の構造を僅かに変形した実施例である。この実施例では、n型ソース層72の一部にp型ウェル層91を露出させて、カソード電極12を直接p型ウェル層91にコンタクトさせたカソード短絡構造としている。

【0162】この実施例によれば、ターンオフ時のカソード電極へのホール排出がより効果的に行われ、高速のターンオフ動作が可能になる。

【0163】図72は、図70の実施例の構造に対して、アノード側にエミッタ短絡部77を形成した実施例、更に図73は、図70の実施例に対してアノード側に選択的にエミッタ短絡構造を得るためのMOSトランジスタを形成した実施例である。これらの実施例によっても、高速のターンオフ動作が可能になる。

【0164】図74は、図69の実施例の構造を3次元的に展開した実施例である。図75は同様に図70の実施例の構造を3次元的に展開した実施例である。図76は同様に図71の実施例の構造を3次元的に展開した実施例である。図77は同様に図70の実施例の構造を3次元的に展開した実施例である。図78は同様に図73の実施例の構造を3次元的に展開した実施例である。図7979は図78の構造を基本として、p型エミッタ層3を取り囲むように絶縁ゲートトランジスタ構造を設けた実施例である。

【0165】次にカソード側の構造を従来の図139と同じとして、アノード側にカソード側と同様のMOSトランジスタを導入した実施例を、図80〜図87に示す。

【0166】図80の実施例では、アノード側にはp型エミッタ層3が選択的に形成され、これから所定距離離れてn+ 型層100が形成されている。n+ 型層100のp型エミッタ層3側の端部にはp型ソース層101が形成されている。p型ソース層101とp型エミッタ層3の間のn型バッファ層2表面にはゲート絶縁膜102を介してゲート電極103が形成されている。すなわちpチャネルMOSトランジスタが構成されている。アノード電極11は、n+ 型層100とp型ソース層101に同時にコンタクトして形成され、p型エミッタ層3には直接コンタクトしていない。

【0167】この実施例の素子では、ターンオン時、カソード側のゲート電極74にカソードに対して正の電圧が印加され、アノード側のゲート電極103にアノードに対して負の電圧が印加される。これにより、それぞれゲート電極下に形成されるチャネルを介して、n型エミッタ層7はn型ソース層72に、またp型エミッタ層3はp型ソース層101に短絡される。図示しないターンオン用ゲートによりp型ベース層にベース電流が供給されると、素子はターンオンする。

【0168】ターンオフ時は、カソード側のゲート電極74にカソードに対して零または負の電圧が印加され、アノード側のゲート電極103にアノードに対して零または正の電圧が印加される。これにより、n型エミッタ層7はn型ソース層72から切離され、n型エミッタ層7からの電子注入は止まる。また、p型エミッタ層3はp型ソース層101から切離され、p型エミッタ層3からのホール注入は止まる。

【0169】以上のようにしてこの実施例によれば、カソード側,アノード側共にMOSゲートでキャリア注入を制御することによって、高速のターンオフができる。なおこの実施例の素子はターンオフに際して、先に図48R>8で説明したようにアノード側のMOSトランジスタをオフにし、その後カソード側のMOSトランジスタをオフにする、というゲート制御を行うこともできる。これにより、より高いターンオフ能力が得られる。

【0170】図81は、アノード側のMOSトランジスタをnチャネルとした実施例である。p型エミッタ層3に連続するp型ウェル層104が形成され、p型エミッタ層とp型ウェル層104に跨がるようにn型ソース層106が形成され、これから所定距離離れてp型ウェル層104にn型ドレイン層105が形成されている。これらn型ソース層106とn型ドレイン層105の間のp型ウェル層104上にゲート絶縁膜102を介してゲート電極103が形成されて、nチャネルMOSトランジスタが構成されている。n型ソース層106とp型エミッタ層3の間は不純物を高濃度にドープした多結晶シリコン膜或いは金属膜による短絡電極107で短絡されている。

【0171】この実施例では、ターンオン時、カソード側のゲート電極74にカソードに対して正の電圧が印加され、アノード側のゲート電極103にはアノードに対して正の電圧が印加される。これにより、カソード側ではn型エミッタ層7はn型ソース層72と接続されて、電子注入が行われる。アノード側ではn型ドレイン層105とn型ソース層106がつながり、短絡電極107によってp型エミッタ層3はアノード電極11と短絡されて、p型エミッタ層3からのホール注入がなされる。

【0172】ターンオフ時は、カソード側のゲート電極74にカソードに対して零または負の電圧が印加され、アノード側のゲート電極103にアノードに対して零または負の電圧が印加される。これにより、n型エミッタ層7はn型ソース層72から切離され、n型エミッタ層7からの電子注入は止まる。また、p型エミッタ層3はn型ドレイン層105およびアノード電極11から切離され、p型エミッタ層3からのホール注入は止まる。

【0173】この実施例によっても、高いターンオフ能力が得られる。図80の実施例では、ターンオフ時、アノード側ではp型エミッタ層3からのホール注入が止まった後にもp型ソース層101からのホール注入が暫く続くが、この実施例ではゲート制御によってホール注入が完全に止まる。したがって優れたターンオフ能力が得られる。

【0174】図82は、図80の実施例に対して、図44R>4(a) と同様にp型ウェル層71の底部に高濃度p+ 型層75を設けた実施例である。図83は、図80の実施例に対して、アノード側のn型ウェル層100の底部に高濃度n+ 型層108を設けた実施例である。図84は、図82と図83を組み合わせた実施例である。

【0175】図85は、図80の実施例に対して、図44R>4(b) と同様にn型ベース層1のp型ベース層45との接合部近傍に低キャリアライフタイム層76を設けた実施例である。図86は、図80の実施例に対して、n型ベース層1のn型バッファ層2寄りのn+ 型層100下に低キャリアライフタイム層109を設けた実施例である。図87は、図80の実施例に対して、サイリスタの主電流経路のn型ベース層1中央部に低キャリアライフタイム層109を設けた実施例である。

【0176】これら図82〜図87の実施例によって、さらに高いターンオフ能力が得られる。

【0177】次に、再度埋込みゲート構造の絶縁ゲート型サイリスタの実施例を、幾つか説明する。