絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法

【課題】実際のデバイスの絶縁破壊寿命に適合する精度の良いシミュレーションを行って、正確な絶縁膜の絶縁破壊寿命を求めることで、実測データとの対比で欠陥種、欠陥の大きさ等を正確に解析できる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法を提供することを目的とする。

【解決手段】前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求める絶縁破壊寿命シミュレーション方法。

【解決手段】前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求める絶縁破壊寿命シミュレーション方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えばMOSデバイス等の品質評価の際に行われる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法に関する。

【背景技術】

【0002】

MOS(Metal Oxide Semiconductor)トランジスタ、MOSキャパシタ等の半導体デバイスでは、長期信頼性において絶縁体薄膜(以下、絶縁膜ともいう)の品質が絶縁破壊寿命に大きく影響する。

そこで、絶縁膜に印加する電圧が実際のデバイス動作より高い電界ストレス、あるいは、その動作時より高温状態の温度ストレス等の下での加速試験により、例えばTZDB(Time Zero Dielectric Breakdown)やTDDB(Time Dependent Dielectric Breakdown)測定が行われ、絶縁膜の評価が行われる。この中でもTDDB測定は、信頼性(寿命)を評価するものであり、かつTZDBよりも高ストレスを印加することから、近年ウェーハ評価に対してもよく用いられている。

【0003】

これまでに、シリコンウェーハ上に形成されるシリコン酸化膜等の絶縁膜の絶縁破壊については、多くの物理的モデルが研究・提案されている。その中で、電界および温度による金属電極(M)あるいは基板(シリコンウェーハ)(S)の電極から絶縁膜への電子の注入や、絶縁膜中の電流機構等が詳細に調べられ、特にこの電子によって生成される正孔と、当該正孔の膜中への注入、蓄積が、絶縁破壊に大きく影響することが判っている(例えば、非特許文献1,2参照)。

ところで、上記絶縁膜の信頼性評価に広く用いられるMOSキャパシタのTDDB測定では、絶縁膜の絶縁破壊は確率的に生じる。これは、主に絶縁膜の欠陥であるいわゆるウィークスポット、ピンホール、あるいは、正孔や電子の電荷トラップや水素等の不純物が膜中で不均一に分布することによる。

【0004】

そこで、絶縁膜の破壊を確率過程として捉え、数理統計的にシミュレーション予測する確率モデルが提案されている。そのモデルとして、パーコレーションモデル(Percolation Model;浸透モデル)がある(例えば、非特許文献3参照)。これは、例えばシリコン酸化膜をメッシュ構造に分割して微小なセルを形成し、各セルが破壊する確率を想定して、酸化膜の厚さ方向で破壊セルが1列をなしたところで絶縁破壊が起きるとする確率モデルである。

【0005】

上記確率モデルでは、絶縁膜が厚いと実測値からのズレが大きく、薄くなると実測値に良く合うようになってくることが知られている。そのため、この確率モデルを用いた絶縁膜の絶縁破壊シミュレーション予測は、絶縁膜の膜厚がある程度薄い場合に有用となる。このため、厚い酸化膜への適応については、例えば膜中トラップの存在をモデル化するような提案がなされている(例えば、非特許文献4参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2010−62346号公報

【非特許文献】

【0007】

【非特許文献1】「International Journal of High Speed Electronics and Systems」、Vol.11,No.3(2001),pp.849−886

【非特許文献2】「IEEE Transactions on Electron Devices」、 Vol.36,No.11(1989)pp.2462−2465

【非特許文献3】「International Journal of High Speed Electronics and Systems」、Vol.11,No.3(2001),pp.789−848

【非特許文献4】「富士時報」Vol80(6)、2007.pp.457−460

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところが、シリコン酸化膜のような絶縁膜がさらに薄くなると、その絶縁破壊は半導体デバイス基板であるシリコンウェーハ表面の品質に大きく影響を受けるようになる。

特許文献1においては、シリコンウェーハ表面の品質状態(欠陥量、欠陥サイズ、マイクロラフネス)を考慮し、具体的には、モンテカルロ法のコンピュータシミュレーションによる絶縁破壊寿命シミュレーション方法で、シリコンウェーハの表面欠陥を、ウェーハ上にあるセルに対してセルを破壊させる欠陥としてくり込むことで対応している。

【0009】

しかし、実際のシリコンウェーハは、引上げ育成したシリコン単結晶インゴットが薄円盤状にスライスされ、その後、ラッピング、エッチング、鏡面研磨、洗浄等の各種加工の製造工程を経て作製される。このように作製したシリコンウェーハの表面には、単結晶インゴットの引上げ育成時に生じたグローンイン欠陥が存在する。また、引上げ育成において、石英ルツボからシリコン単結晶インゴットに取り込まれて固溶する格子間酸素の析出物(BMD:Bulk Micro Defect)のような欠陥が、微小であれ存在する。また、ウェーハ表面には、原子レベルでの凹凸(以下、マイクロラフネスまたは単にラフネスという)が残存している。さらに、これらのウェーハ製造工程においては、常に汚染の発生が懸念され、デバイス作製工程においても、金属汚染が絶縁膜へ影響することが十分考えられる。

従って、シミュレーションにおいて、基板/絶縁膜界面を考えるだけでは、上記の金属汚染やラフネス等に影響される実際の絶縁破壊との適合が不十分である。

【0010】

上記のような従来の絶縁破壊寿命シミュレーション予測では、実際の絶縁膜周辺の状況が十分考慮されていなかった。

【0011】

本発明は、上記問題点に鑑みてなされたものであって、実際のデバイスの絶縁破壊寿命に適合する精度の良いシミュレーションを行って、正確な絶縁膜の絶縁破壊寿命を求めることで、実測データとの対比で欠陥種、欠陥の大きさ等を正確に解析できる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記目的を達成するために、本発明は、シリコンウェーハと、該シリコンウェーハ上の絶縁膜と、該絶縁膜上の金属電極とを有する構造において、前記絶縁膜の絶縁破壊を確率過程として捉え、前記絶縁膜中に欠陥を乱数にて発生させ、該発生させた欠陥が前記絶縁膜の前記シリコンウェーハとの界面から前記金属電極との界面までつながった時点で前記絶縁膜が絶縁破壊するとしたコンピュータシミュレーションにより、前記絶縁膜の絶縁破壊寿命を求めるシミュレーション方法であって、前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求めることを特徴とする絶縁破壊寿命シミュレーション方法を提供する。

【0013】

このように、シミュレーションする構造における、シリコンウェーハと絶縁膜の界面及び絶縁膜と金属電極の界面に、及び/又は、絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、絶縁膜中に欠陥を乱数にて発生させて絶縁膜の絶縁破壊寿命を求めることで、絶縁破壊に影響する絶縁膜の欠陥やウェーハ表面品質を織り込んだ精度の良いシミュレーションを行って、実際のデバイスに近い絶縁破壊寿命を求めることができる。このため、本発明のシミュレーションを用いて、実際のデバイスの品質や、シリコンウェーハ表面の品質を精度高く評価することができる。

【0014】

このとき、前記予め組み込む欠陥の大きさ、密度又は位置を、実際のシリコンウェーハ、絶縁膜、金属電極又はそれらの界面の欠陥を予測した仮定値とすることが好ましい。

このように、本発明のシミュレーションにおいて、予め組み込む欠陥の大きさ、密度又は位置を、実際のシリコンウェーハ、絶縁膜、金属電極又はそれらの界面の欠陥を予測した仮定値とすることで、より精度の良いシミュレーションを行うことができ、また、当該シミュレーション結果を基に、実際のデバイス中の欠陥量等を正確に評価できる。

【0015】

このとき、前記予め組み込む欠陥の大きさ又は位置を、ポアソン分布に基づいて設定することが好ましい。

このように、本発明のシミュレーションにおいて、予め組み込む欠陥の大きさ又は位置を、ポアソン分布に基づいて設定することで、より精度の良いシミュレーションを行うことができる。

【0016】

このとき、前記絶縁破壊寿命をシミュレーションする絶縁膜の厚さを、10nm以下とすることができる。

このように、絶縁破壊寿命をシミュレーションする絶縁膜の厚さが、10nm以下であるような場合に、本発明であれば、シリコンウェーハ表面の品質の影響を考慮したシミュレーションを行うことができ、実際のデバイスに即した正確な絶縁破壊寿命を求めることができる。

【0017】

また、本発明は、シリコンウェーハ表面の品質評価方法であって、前記シリコンウェーハ上に絶縁膜と金属電極を形成して作製された複数のMOSキャパシタのTDDBの実測データを測定し、本発明の絶縁破壊寿命シミュレーション方法において、前記MOSキャパシタと同じ条件を設定して、前記絶縁膜の絶縁破壊寿命を示すTDDBを求め、該シミュレーションで求めたTDDBと、前記TDDBの実測データとを対比させて、前記シミュレーションで予め組み込んだ欠陥の設定値を基に、前記シリコンウェーハの表面欠陥を評価することを特徴とするシリコンウェーハ表面の品質評価方法を提供する。

【0018】

このようなシリコンウェーハ表面の品質評価方法であれば、本発明のシミュレーション方法で精度良く求めたTDDBと実測データとの対比により、シミュレーションで設定した欠陥を基に、実際のシリコンウェーハの欠陥量やラフネス等を正確に評価することができる。

【発明の効果】

【0019】

以上のように、本発明によれば、実際のデバイスの絶縁破壊に適合するシミュレーションを行うことができ、精度良く絶縁破壊寿命を求めて、実際のシリコンウェーハの表面品質を正確に評価することができる。

【図面の簡単な説明】

【0020】

【図1】本発明の絶縁破壊シミュレーション方法の実施態様の一例を示すフロー図である。

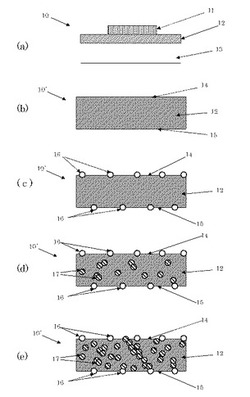

【図2】本発明の絶縁破壊シミュレーション方法において、予め組み込む欠陥の配置の例を示す説明図である。

【図3】実施例1及び比較例1におけるシミュレーションで求めたTDDBと、実測して求めたTDDBのワイブルプロットである。

【図4】実施例2及び比較例2におけるシミュレーションで求めたTDDBと、実測して求めたTDDBのワイブルプロットである。

【発明を実施するための形態】

【0021】

以下、本発明について、実施態様の一例として、図を参照しながら詳細に説明するが、本発明はこれに限定されるものではない。

図1は、本発明の絶縁破壊シミュレーション方法の実施態様の一例を示すフロー図である。図2は、本発明の絶縁破壊シミュレーション方法において、予め組み込む欠陥の配置の例を示す説明図である。

【0022】

まず、本発明において、図1(a)に示すような、シリコンウェーハ13上に絶縁膜12と金属膜11を有する例えばMOS構造10の絶縁破壊寿命を以下のような本発明のシミュレーションで求める。

このようなMOS構造10の絶縁膜12の厚さ等は、評価対象に合わせて適宜設定でき、例えば、本発明の方法であれば、シリコンウェーハ13表面の欠陥等の影響を組み込んだシミュレーションを行うことができるため、絶縁膜12が10nm以下の厚さのものでも精度の良いシミュレーションを行うことができる。

【0023】

本発明のシミュレーション方法に際しては、図1(b)に示すようなMOS構造10’を想定する。当該想定したMOS構造10’は、絶縁膜12、絶縁膜12の金属膜11との界面14、及び、絶縁膜12のシリコンウェーハ13との界面15からなる。

【0024】

そして、図1(c)のように、MOS構造10’に予め欠陥16を組み込む。

この際、図1(c)及び図2(a)のように絶縁膜12の金属膜11との界面14、及び、絶縁膜12のシリコンウェーハ13との界面15に欠陥16を組み込むか、図2(b)に示すように絶縁膜12中に欠陥16を組み込むか、あるいは、図2(c)に示すように界面14,15及び絶縁膜12中に欠陥16を組み込む。

【0025】

このような組み込む欠陥の大きさ、密度又は位置は、実際のシリコンウェーハ、絶縁膜、金属電極、又はそれらの界面の欠陥を予測した仮定値とすることが好ましい。

このときの仮定値の設定は、例えば、大きさをポアソン分布で仮定し、ある密度で繰り込むことで大きさの影響を検討できる。そして、大きさを決定した後、密度を変化させてシミュレーションを繰り返し行う。

このように、実情に合わせて、実際のMOS構造の絶縁膜の界面、絶縁膜中、シリコンウェーハ表面等に存在する欠陥種類を予測した仮定値を決定して、組み込むことで、シミュレーションで求めた値と実測値との対比がより精度良くでき、正確な欠陥評価を行うことができる。

【0026】

例えば、図1(c)、図2(a)のように、界面14,15に等間隔で欠陥を組み込むことで、実際のデバイスにおけるシリコンウェーハ表面のラフネスを再現することができ、ラフネスの影響をシミュレーションすることが可能になる。

また、図2(b)のように、絶縁膜中に欠陥を組み込む場合には、例えば絶縁膜中の欠陥密度を仮定して、組み込むことができる。また、この場合、シリコンウェーハ13との界面15側に欠陥を配置する等して、実際の絶縁膜中に存在する欠陥やトラップ等を再現することができる。

【0027】

また、組み込む欠陥の大きさは、2種類以上としてもよく、実際のデバイスに即して決定することができる。

組み込む欠陥の大きさや配置としては、例えば、実際の欠陥に応じて、ポアソン分布に基づき統計的に設定することが好ましい。ただし、大きさや座標位置を、任意に指定して配置することもできる。

【0028】

そして、絶縁膜12の膜厚、ゲート長等を設定し、絶縁膜12の絶縁破壊を確率過程として捉え、絶縁膜12中に乱数的に欠陥17を発生させ(図1(d))、欠陥16,17が、絶縁膜12のシリコンウェーハ13との界面15から金属電極11との界面14までつながった時点(図1(e))で絶縁膜が破壊するとしたシミュレーションを行う。

このような絶縁破壊までに試行した回数(乱数にて欠陥17を発生させた回数)を絶縁破壊までの時間として、MOS構造10の絶縁破壊寿命を求めることができる。

【0029】

なお、当該試行回数を絶縁破壊までの時間へ換算する際には、例えば、シリコンウェーハ13表面や絶縁膜12に欠陥が存在しない場合の実測値との比較から換算値を求めることができる。ただし、シリコンウェーハ表面等の欠陥の絶縁破壊への影響を評価するのであれば、厳密な換算値は必ずしも必要でなく、任意の換算値を用いて、相対データ比較でも十分な議論が可能である。

また、当該絶縁破壊までのシミュレーションを、実際のシリコンウェーハ上に形成されるMOS構造の所定の個数分(例えば100回以上)繰り返すことで、実際のMOS構造のTDDB測定で得られるワイブルプロットを構築することができる。

【0030】

また、本発明のシミュレーション方法には、モンテカルロ法のようにメッシュで区切る方法よりも実欠陥のイメージに近いS−PLUS関数を用いることが好ましい。

また、本発明でシミュレーションできる絶縁膜12としては、シリコン酸化膜に限られず、シリコン酸窒化膜、シリコン酸化膜とシリコン酸窒化膜の複合膜、高融点金属酸化膜、シリケート膜であってもよい。このような絶縁膜12の種類によって、シミュレーションで発生させる欠陥の大きさ、または予め組み込む欠陥の大きさ、位置等を適宜設定することができる。

【0031】

以上のようなパーコレーションモデルによる本発明のシミュレーション方法であれば、従来の絶縁破壊モデルにおいて取り込めていなかった実際のシリコンウェーハ表面の表面欠陥、マイクロラフネス等の品質状態の影響、さらには、絶縁膜中の欠陥も簡便に組み込んでシミュレーションでき、精度良く絶縁破壊寿命を求めることができる。これにより、実際のシリコンウェーハ表面に形成したシリコン酸化膜等のTDDBの実測値を基に、MOS構造やシリコンウェーハ表面の品質評価を簡易に精度高く行うことができる。

【0032】

本発明のシミュレーション方法を用いてシリコンウェーハ表面の品質評価を行う方法としては、まず、シリコンウェーハ上に絶縁膜と金属電極を形成して作製された複数のMOSキャパシタのTDDBの実測データを測定する。一方、本発明の絶縁破壊寿命シミュレーション方法において、上記実測したMOSキャパシタと同じ条件(絶縁膜の膜厚、ゲート長等)を設定して、絶縁膜の絶縁破壊寿命を示すTDDBを求める。

そして、シミュレーションで求めたTDDBと、TDDBの実測データとを対比させて、本発明のシミュレーションで予め組み込んだ欠陥の設定値を基に、シリコンウェーハの表面欠陥を評価する。

【0033】

具体的には、例えば、シミュレーションにおいて予め組み込む欠陥を0として、シリコンウェーハ表面に欠陥が無い場合のシミュレーションTDDBを求めてワイブルプロットを構築する。一方、実際のシリコンウェーハ表面の実欠陥や表面ラフネスを基に予測される仮定値の欠陥を予め組み込んだ構造でシミュレーションを行い、当該欠陥を組み込んだ場合のシミュレーションTDDBを求めてワイブルプロットを構築する。そして、TDDBの実測データのワイブルプロットを構築して、上記シミュレーションの2つのワイブルプロットとの対比で、相対的に評価することができる。予測した欠陥を組み込んだシミュレーションTDDBのワイブルプロットよりも、欠陥が0としたシミュレーションTDDBのワイブルプロットの方に実測データのワイブルプロットが近ければ、予測した仮定値よりも欠陥が少なく、良好な表面であると評価することができる。

【実施例】

【0034】

以下、実施例及び比較例を示して本発明をより具体的に説明するが、本発明はこれらに限定されるものではない。

(実施例1、比較例1)

シリコンウェーハを材料として、酸化膜厚を5nm、ゲート長を2mmに設定したMOS構造において、酸化膜中で確率かつ経時的にランダムに生成する欠陥の大きさを0.5nmに仮定して設定し、S−PLUS言語で作製したソフトにて当該設定した欠陥を乱数的に発生させ(図1(d))、電極/ウェーハ間で欠陥がつながった時(図1(e))を絶縁破壊したとし、この時までの試行回数を破壊までの時間(寿命)として算出した。このシミュレーションを100回実施し、ワイブルプロットを作製した。

【0035】

なお、シミュレーション回数に制限はないが、実際の測定との関係を考慮すると100回以上は行った方が精度が良い。また、乱数的に発生させる欠陥の大きさについても、5nmに限定されないが、一般的な大きさとして、例えば非特許文献4等にもおおよそ1nm前後であると記載されている。

【0036】

ここで、実施例1では、上記のように乱数にて欠陥を発生させる前に、ウェーハ/酸化膜及び酸化膜/電極の両界面にあらかじめ欠陥を存在させるように組み込んだ。この際、図2(a)に示すように、あらかじめ周期が2nm程度になるように欠陥を両界面に設定する。これによりシリコンウェーハ表面上のラフネスをあらわしていることになる。

一方、比較例1では、欠陥を予め組み込まずにシミュレーションを行った。

【0037】

実施例1,比較例1のシミュレーションにおいて、欠陥がつながるまでに試行した回数を任意の時間単位で横軸にし、縦軸は100回のデータをワイブル表示したグラフを図3(a)に示す。

【0038】

また、比較のために実測データを図3(b)に示す。これは、ラフネスを持つサンプルと、ラフネスのない(非常に小さい)サンプルについてゲート酸化膜5nmで評価を行った結果である。

【0039】

図3(a)から、従来法に比べて実施例1の方が絶縁破壊までの時間が短くなっていることが分かる。また、図3(b)から、実測データにおいて、ラフネスのないものは破壊までの時間(電荷量Qbd)が長く、ラフネスのあるものは破壊までの時間(Qbd)が短くなっている。すなわち、ラフネスを考慮しない比較例1とラフネスを考慮した実施例1に、実測データがそれぞれ対応している。

このように、界面ラフネスの有無について実測データとシミュレーションは良い一致を示しており、本発明により界面ラフネスの影響を繰り込んだ精度の良いシミュレーションが可能となった。

【0040】

(実施例2、比較例2)

シリコンウェーハを材料として、酸化膜厚を15nm、ゲート長を2mmに設定したMOS構造において、酸化膜中で確率かつ経時的にランダムに生成する欠陥の大きさを0.5nmに仮定して設定し、S−PLUS言語で作製したソフトにて当該設定した欠陥を乱数的に発生させ、電極/ウェーハ間で欠陥がつながった時を絶縁破壊したとし、この時までの試行回数を破壊までの時間(寿命)として算出した。このシミュレーションを100回実施し、ワイブルプロットを作製した。

【0041】

ここで、実施例2では、上記のように乱数にて欠陥を発生させる前に、酸化膜中に予め欠陥を存在させるように組み込んだ。この際、図2(b)に示すように、予め大きさ2nmの欠陥を、密度を0.001個/nm2として、乱数を用いて酸化膜中に配置した。これにより、酸化膜の膜中欠陥をあらわしていることになる。

一方、比較例2では、欠陥を予め組み込まずにシミュレーションを行った。

【0042】

実施例2,比較例2のシミュレーションにおいて、欠陥がつながるまでに試行した回数を任意の時間単位で横軸にし、縦軸は100回のデータをワイブル表示したグラフを図4(a)に示す。

【0043】

また、比較のために実測データを図4(b)に示す。これは膜中欠陥を有するサンプルと、膜中欠陥のない(非常に少ない)サンプルについてゲート酸化膜15nmで評価を行った結果である。

【0044】

図4(a)から、従来法の比較例2に比べて実施例2の方が、シミュレーションの絶縁破壊までの時間が短くなっていることが分かる。また、図4(b)から、実測データにおいて、膜中欠陥のないものは破壊までの時間(電荷量Qbd)が長く、膜中欠陥のあるものは破壊までの時間(Qbd)が短くなっている。すなわち、膜中欠陥を考慮しない比較例2と、膜中欠陥を考慮した実施例2に、実測データがそれぞれ対応している。

このように、酸化膜の膜中欠陥の有無について実測データとシミュレーションは良い一致を示しており、本発明により膜中欠陥の影響を繰り込んだ精度の良いシミュレーションが可能となった。

【0045】

なお、上記実施例、比較例では、ワイブルプロットにより絶縁破壊寿命を表したが、絶縁破壊のワイブルプロットに換えて絶縁破壊の累積不良率により統計処理を行うようにしても問題はないため、使用者側で選択されるべきものである。

【0046】

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は、例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

【符号の説明】

【0047】

10、10’…MOS構造、 11…金属電極、 12…絶縁膜、

13…シリコンウェーハ、 14…絶縁膜と金属電極の界面、

15…絶縁膜とシリコンウェーハの界面、 16、17…欠陥、

【技術分野】

【0001】

本発明は、例えばMOSデバイス等の品質評価の際に行われる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法に関する。

【背景技術】

【0002】

MOS(Metal Oxide Semiconductor)トランジスタ、MOSキャパシタ等の半導体デバイスでは、長期信頼性において絶縁体薄膜(以下、絶縁膜ともいう)の品質が絶縁破壊寿命に大きく影響する。

そこで、絶縁膜に印加する電圧が実際のデバイス動作より高い電界ストレス、あるいは、その動作時より高温状態の温度ストレス等の下での加速試験により、例えばTZDB(Time Zero Dielectric Breakdown)やTDDB(Time Dependent Dielectric Breakdown)測定が行われ、絶縁膜の評価が行われる。この中でもTDDB測定は、信頼性(寿命)を評価するものであり、かつTZDBよりも高ストレスを印加することから、近年ウェーハ評価に対してもよく用いられている。

【0003】

これまでに、シリコンウェーハ上に形成されるシリコン酸化膜等の絶縁膜の絶縁破壊については、多くの物理的モデルが研究・提案されている。その中で、電界および温度による金属電極(M)あるいは基板(シリコンウェーハ)(S)の電極から絶縁膜への電子の注入や、絶縁膜中の電流機構等が詳細に調べられ、特にこの電子によって生成される正孔と、当該正孔の膜中への注入、蓄積が、絶縁破壊に大きく影響することが判っている(例えば、非特許文献1,2参照)。

ところで、上記絶縁膜の信頼性評価に広く用いられるMOSキャパシタのTDDB測定では、絶縁膜の絶縁破壊は確率的に生じる。これは、主に絶縁膜の欠陥であるいわゆるウィークスポット、ピンホール、あるいは、正孔や電子の電荷トラップや水素等の不純物が膜中で不均一に分布することによる。

【0004】

そこで、絶縁膜の破壊を確率過程として捉え、数理統計的にシミュレーション予測する確率モデルが提案されている。そのモデルとして、パーコレーションモデル(Percolation Model;浸透モデル)がある(例えば、非特許文献3参照)。これは、例えばシリコン酸化膜をメッシュ構造に分割して微小なセルを形成し、各セルが破壊する確率を想定して、酸化膜の厚さ方向で破壊セルが1列をなしたところで絶縁破壊が起きるとする確率モデルである。

【0005】

上記確率モデルでは、絶縁膜が厚いと実測値からのズレが大きく、薄くなると実測値に良く合うようになってくることが知られている。そのため、この確率モデルを用いた絶縁膜の絶縁破壊シミュレーション予測は、絶縁膜の膜厚がある程度薄い場合に有用となる。このため、厚い酸化膜への適応については、例えば膜中トラップの存在をモデル化するような提案がなされている(例えば、非特許文献4参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2010−62346号公報

【非特許文献】

【0007】

【非特許文献1】「International Journal of High Speed Electronics and Systems」、Vol.11,No.3(2001),pp.849−886

【非特許文献2】「IEEE Transactions on Electron Devices」、 Vol.36,No.11(1989)pp.2462−2465

【非特許文献3】「International Journal of High Speed Electronics and Systems」、Vol.11,No.3(2001),pp.789−848

【非特許文献4】「富士時報」Vol80(6)、2007.pp.457−460

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところが、シリコン酸化膜のような絶縁膜がさらに薄くなると、その絶縁破壊は半導体デバイス基板であるシリコンウェーハ表面の品質に大きく影響を受けるようになる。

特許文献1においては、シリコンウェーハ表面の品質状態(欠陥量、欠陥サイズ、マイクロラフネス)を考慮し、具体的には、モンテカルロ法のコンピュータシミュレーションによる絶縁破壊寿命シミュレーション方法で、シリコンウェーハの表面欠陥を、ウェーハ上にあるセルに対してセルを破壊させる欠陥としてくり込むことで対応している。

【0009】

しかし、実際のシリコンウェーハは、引上げ育成したシリコン単結晶インゴットが薄円盤状にスライスされ、その後、ラッピング、エッチング、鏡面研磨、洗浄等の各種加工の製造工程を経て作製される。このように作製したシリコンウェーハの表面には、単結晶インゴットの引上げ育成時に生じたグローンイン欠陥が存在する。また、引上げ育成において、石英ルツボからシリコン単結晶インゴットに取り込まれて固溶する格子間酸素の析出物(BMD:Bulk Micro Defect)のような欠陥が、微小であれ存在する。また、ウェーハ表面には、原子レベルでの凹凸(以下、マイクロラフネスまたは単にラフネスという)が残存している。さらに、これらのウェーハ製造工程においては、常に汚染の発生が懸念され、デバイス作製工程においても、金属汚染が絶縁膜へ影響することが十分考えられる。

従って、シミュレーションにおいて、基板/絶縁膜界面を考えるだけでは、上記の金属汚染やラフネス等に影響される実際の絶縁破壊との適合が不十分である。

【0010】

上記のような従来の絶縁破壊寿命シミュレーション予測では、実際の絶縁膜周辺の状況が十分考慮されていなかった。

【0011】

本発明は、上記問題点に鑑みてなされたものであって、実際のデバイスの絶縁破壊寿命に適合する精度の良いシミュレーションを行って、正確な絶縁膜の絶縁破壊寿命を求めることで、実測データとの対比で欠陥種、欠陥の大きさ等を正確に解析できる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記目的を達成するために、本発明は、シリコンウェーハと、該シリコンウェーハ上の絶縁膜と、該絶縁膜上の金属電極とを有する構造において、前記絶縁膜の絶縁破壊を確率過程として捉え、前記絶縁膜中に欠陥を乱数にて発生させ、該発生させた欠陥が前記絶縁膜の前記シリコンウェーハとの界面から前記金属電極との界面までつながった時点で前記絶縁膜が絶縁破壊するとしたコンピュータシミュレーションにより、前記絶縁膜の絶縁破壊寿命を求めるシミュレーション方法であって、前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求めることを特徴とする絶縁破壊寿命シミュレーション方法を提供する。

【0013】

このように、シミュレーションする構造における、シリコンウェーハと絶縁膜の界面及び絶縁膜と金属電極の界面に、及び/又は、絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、絶縁膜中に欠陥を乱数にて発生させて絶縁膜の絶縁破壊寿命を求めることで、絶縁破壊に影響する絶縁膜の欠陥やウェーハ表面品質を織り込んだ精度の良いシミュレーションを行って、実際のデバイスに近い絶縁破壊寿命を求めることができる。このため、本発明のシミュレーションを用いて、実際のデバイスの品質や、シリコンウェーハ表面の品質を精度高く評価することができる。

【0014】

このとき、前記予め組み込む欠陥の大きさ、密度又は位置を、実際のシリコンウェーハ、絶縁膜、金属電極又はそれらの界面の欠陥を予測した仮定値とすることが好ましい。

このように、本発明のシミュレーションにおいて、予め組み込む欠陥の大きさ、密度又は位置を、実際のシリコンウェーハ、絶縁膜、金属電極又はそれらの界面の欠陥を予測した仮定値とすることで、より精度の良いシミュレーションを行うことができ、また、当該シミュレーション結果を基に、実際のデバイス中の欠陥量等を正確に評価できる。

【0015】

このとき、前記予め組み込む欠陥の大きさ又は位置を、ポアソン分布に基づいて設定することが好ましい。

このように、本発明のシミュレーションにおいて、予め組み込む欠陥の大きさ又は位置を、ポアソン分布に基づいて設定することで、より精度の良いシミュレーションを行うことができる。

【0016】

このとき、前記絶縁破壊寿命をシミュレーションする絶縁膜の厚さを、10nm以下とすることができる。

このように、絶縁破壊寿命をシミュレーションする絶縁膜の厚さが、10nm以下であるような場合に、本発明であれば、シリコンウェーハ表面の品質の影響を考慮したシミュレーションを行うことができ、実際のデバイスに即した正確な絶縁破壊寿命を求めることができる。

【0017】

また、本発明は、シリコンウェーハ表面の品質評価方法であって、前記シリコンウェーハ上に絶縁膜と金属電極を形成して作製された複数のMOSキャパシタのTDDBの実測データを測定し、本発明の絶縁破壊寿命シミュレーション方法において、前記MOSキャパシタと同じ条件を設定して、前記絶縁膜の絶縁破壊寿命を示すTDDBを求め、該シミュレーションで求めたTDDBと、前記TDDBの実測データとを対比させて、前記シミュレーションで予め組み込んだ欠陥の設定値を基に、前記シリコンウェーハの表面欠陥を評価することを特徴とするシリコンウェーハ表面の品質評価方法を提供する。

【0018】

このようなシリコンウェーハ表面の品質評価方法であれば、本発明のシミュレーション方法で精度良く求めたTDDBと実測データとの対比により、シミュレーションで設定した欠陥を基に、実際のシリコンウェーハの欠陥量やラフネス等を正確に評価することができる。

【発明の効果】

【0019】

以上のように、本発明によれば、実際のデバイスの絶縁破壊に適合するシミュレーションを行うことができ、精度良く絶縁破壊寿命を求めて、実際のシリコンウェーハの表面品質を正確に評価することができる。

【図面の簡単な説明】

【0020】

【図1】本発明の絶縁破壊シミュレーション方法の実施態様の一例を示すフロー図である。

【図2】本発明の絶縁破壊シミュレーション方法において、予め組み込む欠陥の配置の例を示す説明図である。

【図3】実施例1及び比較例1におけるシミュレーションで求めたTDDBと、実測して求めたTDDBのワイブルプロットである。

【図4】実施例2及び比較例2におけるシミュレーションで求めたTDDBと、実測して求めたTDDBのワイブルプロットである。

【発明を実施するための形態】

【0021】

以下、本発明について、実施態様の一例として、図を参照しながら詳細に説明するが、本発明はこれに限定されるものではない。

図1は、本発明の絶縁破壊シミュレーション方法の実施態様の一例を示すフロー図である。図2は、本発明の絶縁破壊シミュレーション方法において、予め組み込む欠陥の配置の例を示す説明図である。

【0022】

まず、本発明において、図1(a)に示すような、シリコンウェーハ13上に絶縁膜12と金属膜11を有する例えばMOS構造10の絶縁破壊寿命を以下のような本発明のシミュレーションで求める。

このようなMOS構造10の絶縁膜12の厚さ等は、評価対象に合わせて適宜設定でき、例えば、本発明の方法であれば、シリコンウェーハ13表面の欠陥等の影響を組み込んだシミュレーションを行うことができるため、絶縁膜12が10nm以下の厚さのものでも精度の良いシミュレーションを行うことができる。

【0023】

本発明のシミュレーション方法に際しては、図1(b)に示すようなMOS構造10’を想定する。当該想定したMOS構造10’は、絶縁膜12、絶縁膜12の金属膜11との界面14、及び、絶縁膜12のシリコンウェーハ13との界面15からなる。

【0024】

そして、図1(c)のように、MOS構造10’に予め欠陥16を組み込む。

この際、図1(c)及び図2(a)のように絶縁膜12の金属膜11との界面14、及び、絶縁膜12のシリコンウェーハ13との界面15に欠陥16を組み込むか、図2(b)に示すように絶縁膜12中に欠陥16を組み込むか、あるいは、図2(c)に示すように界面14,15及び絶縁膜12中に欠陥16を組み込む。

【0025】

このような組み込む欠陥の大きさ、密度又は位置は、実際のシリコンウェーハ、絶縁膜、金属電極、又はそれらの界面の欠陥を予測した仮定値とすることが好ましい。

このときの仮定値の設定は、例えば、大きさをポアソン分布で仮定し、ある密度で繰り込むことで大きさの影響を検討できる。そして、大きさを決定した後、密度を変化させてシミュレーションを繰り返し行う。

このように、実情に合わせて、実際のMOS構造の絶縁膜の界面、絶縁膜中、シリコンウェーハ表面等に存在する欠陥種類を予測した仮定値を決定して、組み込むことで、シミュレーションで求めた値と実測値との対比がより精度良くでき、正確な欠陥評価を行うことができる。

【0026】

例えば、図1(c)、図2(a)のように、界面14,15に等間隔で欠陥を組み込むことで、実際のデバイスにおけるシリコンウェーハ表面のラフネスを再現することができ、ラフネスの影響をシミュレーションすることが可能になる。

また、図2(b)のように、絶縁膜中に欠陥を組み込む場合には、例えば絶縁膜中の欠陥密度を仮定して、組み込むことができる。また、この場合、シリコンウェーハ13との界面15側に欠陥を配置する等して、実際の絶縁膜中に存在する欠陥やトラップ等を再現することができる。

【0027】

また、組み込む欠陥の大きさは、2種類以上としてもよく、実際のデバイスに即して決定することができる。

組み込む欠陥の大きさや配置としては、例えば、実際の欠陥に応じて、ポアソン分布に基づき統計的に設定することが好ましい。ただし、大きさや座標位置を、任意に指定して配置することもできる。

【0028】

そして、絶縁膜12の膜厚、ゲート長等を設定し、絶縁膜12の絶縁破壊を確率過程として捉え、絶縁膜12中に乱数的に欠陥17を発生させ(図1(d))、欠陥16,17が、絶縁膜12のシリコンウェーハ13との界面15から金属電極11との界面14までつながった時点(図1(e))で絶縁膜が破壊するとしたシミュレーションを行う。

このような絶縁破壊までに試行した回数(乱数にて欠陥17を発生させた回数)を絶縁破壊までの時間として、MOS構造10の絶縁破壊寿命を求めることができる。

【0029】

なお、当該試行回数を絶縁破壊までの時間へ換算する際には、例えば、シリコンウェーハ13表面や絶縁膜12に欠陥が存在しない場合の実測値との比較から換算値を求めることができる。ただし、シリコンウェーハ表面等の欠陥の絶縁破壊への影響を評価するのであれば、厳密な換算値は必ずしも必要でなく、任意の換算値を用いて、相対データ比較でも十分な議論が可能である。

また、当該絶縁破壊までのシミュレーションを、実際のシリコンウェーハ上に形成されるMOS構造の所定の個数分(例えば100回以上)繰り返すことで、実際のMOS構造のTDDB測定で得られるワイブルプロットを構築することができる。

【0030】

また、本発明のシミュレーション方法には、モンテカルロ法のようにメッシュで区切る方法よりも実欠陥のイメージに近いS−PLUS関数を用いることが好ましい。

また、本発明でシミュレーションできる絶縁膜12としては、シリコン酸化膜に限られず、シリコン酸窒化膜、シリコン酸化膜とシリコン酸窒化膜の複合膜、高融点金属酸化膜、シリケート膜であってもよい。このような絶縁膜12の種類によって、シミュレーションで発生させる欠陥の大きさ、または予め組み込む欠陥の大きさ、位置等を適宜設定することができる。

【0031】

以上のようなパーコレーションモデルによる本発明のシミュレーション方法であれば、従来の絶縁破壊モデルにおいて取り込めていなかった実際のシリコンウェーハ表面の表面欠陥、マイクロラフネス等の品質状態の影響、さらには、絶縁膜中の欠陥も簡便に組み込んでシミュレーションでき、精度良く絶縁破壊寿命を求めることができる。これにより、実際のシリコンウェーハ表面に形成したシリコン酸化膜等のTDDBの実測値を基に、MOS構造やシリコンウェーハ表面の品質評価を簡易に精度高く行うことができる。

【0032】

本発明のシミュレーション方法を用いてシリコンウェーハ表面の品質評価を行う方法としては、まず、シリコンウェーハ上に絶縁膜と金属電極を形成して作製された複数のMOSキャパシタのTDDBの実測データを測定する。一方、本発明の絶縁破壊寿命シミュレーション方法において、上記実測したMOSキャパシタと同じ条件(絶縁膜の膜厚、ゲート長等)を設定して、絶縁膜の絶縁破壊寿命を示すTDDBを求める。

そして、シミュレーションで求めたTDDBと、TDDBの実測データとを対比させて、本発明のシミュレーションで予め組み込んだ欠陥の設定値を基に、シリコンウェーハの表面欠陥を評価する。

【0033】

具体的には、例えば、シミュレーションにおいて予め組み込む欠陥を0として、シリコンウェーハ表面に欠陥が無い場合のシミュレーションTDDBを求めてワイブルプロットを構築する。一方、実際のシリコンウェーハ表面の実欠陥や表面ラフネスを基に予測される仮定値の欠陥を予め組み込んだ構造でシミュレーションを行い、当該欠陥を組み込んだ場合のシミュレーションTDDBを求めてワイブルプロットを構築する。そして、TDDBの実測データのワイブルプロットを構築して、上記シミュレーションの2つのワイブルプロットとの対比で、相対的に評価することができる。予測した欠陥を組み込んだシミュレーションTDDBのワイブルプロットよりも、欠陥が0としたシミュレーションTDDBのワイブルプロットの方に実測データのワイブルプロットが近ければ、予測した仮定値よりも欠陥が少なく、良好な表面であると評価することができる。

【実施例】

【0034】

以下、実施例及び比較例を示して本発明をより具体的に説明するが、本発明はこれらに限定されるものではない。

(実施例1、比較例1)

シリコンウェーハを材料として、酸化膜厚を5nm、ゲート長を2mmに設定したMOS構造において、酸化膜中で確率かつ経時的にランダムに生成する欠陥の大きさを0.5nmに仮定して設定し、S−PLUS言語で作製したソフトにて当該設定した欠陥を乱数的に発生させ(図1(d))、電極/ウェーハ間で欠陥がつながった時(図1(e))を絶縁破壊したとし、この時までの試行回数を破壊までの時間(寿命)として算出した。このシミュレーションを100回実施し、ワイブルプロットを作製した。

【0035】

なお、シミュレーション回数に制限はないが、実際の測定との関係を考慮すると100回以上は行った方が精度が良い。また、乱数的に発生させる欠陥の大きさについても、5nmに限定されないが、一般的な大きさとして、例えば非特許文献4等にもおおよそ1nm前後であると記載されている。

【0036】

ここで、実施例1では、上記のように乱数にて欠陥を発生させる前に、ウェーハ/酸化膜及び酸化膜/電極の両界面にあらかじめ欠陥を存在させるように組み込んだ。この際、図2(a)に示すように、あらかじめ周期が2nm程度になるように欠陥を両界面に設定する。これによりシリコンウェーハ表面上のラフネスをあらわしていることになる。

一方、比較例1では、欠陥を予め組み込まずにシミュレーションを行った。

【0037】

実施例1,比較例1のシミュレーションにおいて、欠陥がつながるまでに試行した回数を任意の時間単位で横軸にし、縦軸は100回のデータをワイブル表示したグラフを図3(a)に示す。

【0038】

また、比較のために実測データを図3(b)に示す。これは、ラフネスを持つサンプルと、ラフネスのない(非常に小さい)サンプルについてゲート酸化膜5nmで評価を行った結果である。

【0039】

図3(a)から、従来法に比べて実施例1の方が絶縁破壊までの時間が短くなっていることが分かる。また、図3(b)から、実測データにおいて、ラフネスのないものは破壊までの時間(電荷量Qbd)が長く、ラフネスのあるものは破壊までの時間(Qbd)が短くなっている。すなわち、ラフネスを考慮しない比較例1とラフネスを考慮した実施例1に、実測データがそれぞれ対応している。

このように、界面ラフネスの有無について実測データとシミュレーションは良い一致を示しており、本発明により界面ラフネスの影響を繰り込んだ精度の良いシミュレーションが可能となった。

【0040】

(実施例2、比較例2)

シリコンウェーハを材料として、酸化膜厚を15nm、ゲート長を2mmに設定したMOS構造において、酸化膜中で確率かつ経時的にランダムに生成する欠陥の大きさを0.5nmに仮定して設定し、S−PLUS言語で作製したソフトにて当該設定した欠陥を乱数的に発生させ、電極/ウェーハ間で欠陥がつながった時を絶縁破壊したとし、この時までの試行回数を破壊までの時間(寿命)として算出した。このシミュレーションを100回実施し、ワイブルプロットを作製した。

【0041】

ここで、実施例2では、上記のように乱数にて欠陥を発生させる前に、酸化膜中に予め欠陥を存在させるように組み込んだ。この際、図2(b)に示すように、予め大きさ2nmの欠陥を、密度を0.001個/nm2として、乱数を用いて酸化膜中に配置した。これにより、酸化膜の膜中欠陥をあらわしていることになる。

一方、比較例2では、欠陥を予め組み込まずにシミュレーションを行った。

【0042】

実施例2,比較例2のシミュレーションにおいて、欠陥がつながるまでに試行した回数を任意の時間単位で横軸にし、縦軸は100回のデータをワイブル表示したグラフを図4(a)に示す。

【0043】

また、比較のために実測データを図4(b)に示す。これは膜中欠陥を有するサンプルと、膜中欠陥のない(非常に少ない)サンプルについてゲート酸化膜15nmで評価を行った結果である。

【0044】

図4(a)から、従来法の比較例2に比べて実施例2の方が、シミュレーションの絶縁破壊までの時間が短くなっていることが分かる。また、図4(b)から、実測データにおいて、膜中欠陥のないものは破壊までの時間(電荷量Qbd)が長く、膜中欠陥のあるものは破壊までの時間(Qbd)が短くなっている。すなわち、膜中欠陥を考慮しない比較例2と、膜中欠陥を考慮した実施例2に、実測データがそれぞれ対応している。

このように、酸化膜の膜中欠陥の有無について実測データとシミュレーションは良い一致を示しており、本発明により膜中欠陥の影響を繰り込んだ精度の良いシミュレーションが可能となった。

【0045】

なお、上記実施例、比較例では、ワイブルプロットにより絶縁破壊寿命を表したが、絶縁破壊のワイブルプロットに換えて絶縁破壊の累積不良率により統計処理を行うようにしても問題はないため、使用者側で選択されるべきものである。

【0046】

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は、例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

【符号の説明】

【0047】

10、10’…MOS構造、 11…金属電極、 12…絶縁膜、

13…シリコンウェーハ、 14…絶縁膜と金属電極の界面、

15…絶縁膜とシリコンウェーハの界面、 16、17…欠陥、

【特許請求の範囲】

【請求項1】

シリコンウェーハと、該シリコンウェーハ上の絶縁膜と、該絶縁膜上の金属電極とを有する構造において、前記絶縁膜の絶縁破壊を確率過程として捉え、前記絶縁膜中に欠陥を乱数にて発生させ、該発生させた欠陥が前記絶縁膜の前記シリコンウェーハとの界面から前記金属電極との界面までつながった時点で前記絶縁膜が絶縁破壊するとしたコンピュータシミュレーションにより、前記絶縁膜の絶縁破壊寿命を求めるシミュレーション方法であって、

前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求めることを特徴とする絶縁破壊寿命シミュレーション方法。

【請求項2】

前記予め組み込む欠陥の大きさ、密度又は位置を、実際のシリコンウェーハ、絶縁膜、金属電極又はそれらの界面の欠陥を予測した仮定値とすることを特徴とする請求項1に記載の絶縁破壊寿命シミュレーション方法。

【請求項3】

前記予め組み込む欠陥の大きさ又は位置を、ポアソン分布に基づいて設定することを特徴とする請求項1又は請求項2に記載の絶縁破壊寿命シミュレーション方法。

【請求項4】

前記絶縁破壊寿命をシミュレーションする絶縁膜の厚さを、10nm以下とすることを特徴とする請求項1乃至請求項3のいずれか一項に記載の絶縁破壊寿命シミュレーション方法。

【請求項5】

シリコンウェーハ表面の品質評価方法であって、

前記シリコンウェーハ上に絶縁膜と金属電極を形成して作製された複数のMOSキャパシタのTDDBの実測データを測定し、

請求項1乃至請求項4のいずれか一項に記載の絶縁破壊寿命シミュレーション方法において、前記MOSキャパシタと同じ条件を設定して、前記絶縁膜の絶縁破壊寿命を示すTDDBを求め、

該シミュレーションで求めたTDDBと、前記TDDBの実測データとを対比させて、前記シミュレーションで予め組み込んだ欠陥の設定値を基に、前記シリコンウェーハの表面欠陥を評価することを特徴とするシリコンウェーハ表面の品質評価方法。

【請求項1】

シリコンウェーハと、該シリコンウェーハ上の絶縁膜と、該絶縁膜上の金属電極とを有する構造において、前記絶縁膜の絶縁破壊を確率過程として捉え、前記絶縁膜中に欠陥を乱数にて発生させ、該発生させた欠陥が前記絶縁膜の前記シリコンウェーハとの界面から前記金属電極との界面までつながった時点で前記絶縁膜が絶縁破壊するとしたコンピュータシミュレーションにより、前記絶縁膜の絶縁破壊寿命を求めるシミュレーション方法であって、

前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求めることを特徴とする絶縁破壊寿命シミュレーション方法。

【請求項2】

前記予め組み込む欠陥の大きさ、密度又は位置を、実際のシリコンウェーハ、絶縁膜、金属電極又はそれらの界面の欠陥を予測した仮定値とすることを特徴とする請求項1に記載の絶縁破壊寿命シミュレーション方法。

【請求項3】

前記予め組み込む欠陥の大きさ又は位置を、ポアソン分布に基づいて設定することを特徴とする請求項1又は請求項2に記載の絶縁破壊寿命シミュレーション方法。

【請求項4】

前記絶縁破壊寿命をシミュレーションする絶縁膜の厚さを、10nm以下とすることを特徴とする請求項1乃至請求項3のいずれか一項に記載の絶縁破壊寿命シミュレーション方法。

【請求項5】

シリコンウェーハ表面の品質評価方法であって、

前記シリコンウェーハ上に絶縁膜と金属電極を形成して作製された複数のMOSキャパシタのTDDBの実測データを測定し、

請求項1乃至請求項4のいずれか一項に記載の絶縁破壊寿命シミュレーション方法において、前記MOSキャパシタと同じ条件を設定して、前記絶縁膜の絶縁破壊寿命を示すTDDBを求め、

該シミュレーションで求めたTDDBと、前記TDDBの実測データとを対比させて、前記シミュレーションで予め組み込んだ欠陥の設定値を基に、前記シリコンウェーハの表面欠陥を評価することを特徴とするシリコンウェーハ表面の品質評価方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−104561(P2012−104561A)

【公開日】平成24年5月31日(2012.5.31)

【国際特許分類】

【出願番号】特願2010−249919(P2010−249919)

【出願日】平成22年11月8日(2010.11.8)

【出願人】(000190149)信越半導体株式会社 (867)

【Fターム(参考)】

【公開日】平成24年5月31日(2012.5.31)

【国際特許分類】

【出願日】平成22年11月8日(2010.11.8)

【出願人】(000190149)信越半導体株式会社 (867)

【Fターム(参考)】

[ Back to top ]