縦型電界効果トランジスタとその製造方法及び電子機器

【課題】縦型電界効果トランジスタとその製造方法及び電子機器において、基材の材料の選択の幅を広げること。

【解決手段】基材1と、基材1の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極2と、基材1の上に形成され、第1の電極2に重なる開口12を備えた第1の絶縁膜3と、開口12の横の第1の絶縁膜3の上に形成されたゲート電極6と、第1の絶縁膜3の上に形成され、開口12を備えた第2の絶縁膜8と、開口12の横の第2の絶縁膜8の上に形成され、ソース電極とドレイン電極のうちの他方となる第2の電極10と、開口12の側面に形成されたゲート絶縁膜16と、第1の電極2、第2の電極10、及びゲート絶縁膜16上に形成され、酸化物半導体を材料とするチャネル17とを有する縦型電界効果トランジスタによる。

【解決手段】基材1と、基材1の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極2と、基材1の上に形成され、第1の電極2に重なる開口12を備えた第1の絶縁膜3と、開口12の横の第1の絶縁膜3の上に形成されたゲート電極6と、第1の絶縁膜3の上に形成され、開口12を備えた第2の絶縁膜8と、開口12の横の第2の絶縁膜8の上に形成され、ソース電極とドレイン電極のうちの他方となる第2の電極10と、開口12の側面に形成されたゲート絶縁膜16と、第1の電極2、第2の電極10、及びゲート絶縁膜16上に形成され、酸化物半導体を材料とするチャネル17とを有する縦型電界効果トランジスタによる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、縦型電界効果トランジスタとその製造方法及び電子機器に関する。

【背景技術】

【0002】

縦型電界効果トランジスタは、基板の高さ方向にドレイン電極とゲート電極とが隔てられており、それらの電極間に半導体層が介在した構造を有しているため、ドレイン電極とゲート電極との間の耐圧が高いという特徴がある。このような特徴を活かし、縦型電界効果トランジスタは、電源用等の高耐圧トランジスタとして広く使用されている。

【0003】

そのような縦型電界効果トランジスタでは、上記の半導体層がチャネルを兼ねているが、ドレイン電極とゲート電極とを離して高耐圧を実現するには、その半導体層を厚く形成するのが望まれる。

【0004】

但し、その半導体層はエピタキシャル成長法により形成されるので、成長に長時間を要し、プロセスコストが増大するという問題がある。

【0005】

更に、半導体層とその下の基板との間で格子定数の不整合や熱膨張率の相違があると、半導体層に格子欠陥が入る危険性が高くなる。そのような危険をなくすため、上記の縦型電界効果トランジスタでは、半導体層と格子定数や熱膨張率が近い結晶性基板を使用せざるを得ず、使用可能な基板の材料が制限されるという問題もある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭63−101740号公報

【特許文献2】特開2003−110110号公報

【特許文献3】特開昭61−269377号公報

【特許文献4】特開2008−205414号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

縦型電界効果トランジスタとその製造方法及び電子機器において、基材の材料の選択の幅を広げることを目的とする。

【課題を解決するための手段】

【0008】

以下の開示の一観点によれば、基材と、前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、前記開口の側面に形成されたゲート絶縁膜と、前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルとを有する縦型電界効果トランジスタが提供される。

【0009】

更に、その開示の他の観点によれば、基材の上に、ソース電極とドレイン電極のうちの一方となる第1の電極を形成する工程と、前記基材と前記第1の電極のそれぞれの上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の上であって、平面視で前記第1の電極と重なる部分に、ゲート電極を形成する工程と、前記第1の絶縁膜と前記ゲート電極のそれぞれの上に第2の絶縁膜を形成する工程と、前記第2の絶縁膜の上であって、平面視で前記ゲート電極と重なる部分に、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極を形成する工程と、前記第2の電極、前記第2の絶縁膜、前記ゲート電極、及び前記第1の絶縁膜をエッチングして開口を形成することにより、該開口内に前記第1の電極を露出させる工程と、前記エッチングによって前記開口内に露出した前記ゲート電極の側面にゲート絶縁膜を形成する工程と、前記第1の電極、前記ゲート絶縁膜、及び前記第2の電極のそれぞれの上に、酸化物半導体を材料とするチャネルを形成する工程とを有する縦型電界効果トランジスタの製造方法が提供される。

【0010】

そして、その開示の別の観点によれば、配線基板と筐体のいずれかを含む基材と、前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、前記開口の側面に形成されたゲート絶縁膜と、前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルとを備えた縦型電界効果トランジスタを有することを特徴とする電子機器が提供される。

【発明の効果】

【0011】

以下の開示によれば、アモルファス状態でも高い移動度を維持できる酸化物半導体をチャネルの材料に使用するので、チャネルと基材との格子整合を図る必要がなくなり、基材として使用できる材料の選択の幅が広がる。

【図面の簡単な説明】

【0012】

【図1】図1(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その1)である。

【図2】図2(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その2)である。

【図3】図3(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その3)である。

【図4】図4(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その4)である。

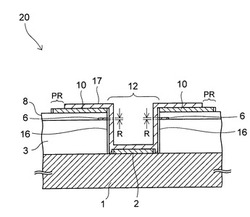

【図5】図5は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その5)である。

【図6】図6は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その1)である。

【図7】図7は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その2)である。

【図8】図8は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その3)である。

【図9】図9は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その4)である。

【図10】図10は、第2実施形態に係る縦型電界効果トランジスタの平面図である。

【図11】図11は、図10のV−V線に沿う断面図である。

【図12】図12は、第3実施形態に係る縦型電界効果トランジスタの平面図である。

【図13】図13は、図12のVI−VI線に沿う断面図である。

【図14】図14(a)、(b)は、第4実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その1)である。

【図15】図15(a)、(b)は、第4実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その2)である。

【図16】図16は、第5実施形態に係る縦型電界効果トランジスタの断面図である。

【図17】図17は、第6実施形態に係る縦型電界効果トランジスタの断面図である。

【発明を実施するための形態】

【0013】

(第1実施形態)

第1実施形態に係る縦型電界効果トランジスタについて、その製造工程を追いながら説明する。

【0014】

図1〜図5は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図であり、図6〜図9はその平面図である。

【0015】

最初に、図1(a)に示すように、銅を材料とする基材1の上に、蒸着法又はスパッタ法によりチタン膜と金膜とをこの順に形成した後、これらの膜をリフトオフ法によりパターニングしてドレイン電極2とする。

【0016】

なお、ドレイン電極2として形成されるチタン膜と金膜の厚さは特に限定されない。チタン膜は、金膜と基材1との密着性を高める密着膜としての機能を有し、約10nm程度の厚さに形成される。また、金膜は、ドレイン電極2の大部分を占めるものであって、約300nm程度の厚さに形成される。

【0017】

次に、図1(b)に示すように、基材1とドレイン電極2のそれぞれの上にポリイミドの塗膜を形成し、それを熱硬化させて第1の絶縁膜3とする。

【0018】

第1の絶縁膜3は、後で完成する縦型電界効果トランジスタの耐圧に応じた膜厚に形成され、本実施形態では1μm〜100μmの膜厚に形成される。

【0019】

続いて、図2(a)に示すように、第1の絶縁膜3の上にチタン膜と金膜とをこの順に形成した後、リフトオフ法によりこれらの膜をパターニングしてゲート電極6を形成する。

【0020】

上記したチタン膜は例えば約10nm程度の厚さに形成され、その上の金膜は例えば300nm程度の厚さに形成される。

【0021】

図6は、本工程を終了後の平面図であり、先の図2(a)は図6のI−I線に沿う断面図に相当する。

【0022】

図6に示すように、ドレイン電極2とゲート電極6の形状は、いずれも平面視で矩形状である。そして、ゲート電極6は、平面視でドレイン電極2と重なるように形成される。

【0023】

次いで、図2(b)に示すように、第1の絶縁膜3とゲート電極6のそれぞれの上にポリイミドの塗膜を形成してそれを熱硬化させることにより、厚さが約0.5μmの第2の絶縁膜8を形成する。

【0024】

続いて、図3(a)に示すように、第2の絶縁膜8の上にソース電極10を形成する。ソース電極10の形成方法は特に限定されないが、本実施形態では第2の絶縁膜8の上にチタン膜と金膜とをこの順に形成した後、リフトオフ法によりこれらの膜をパターニングしてソース電極10を形成する。

【0025】

ソース電極10の厚さも特に限定されず、チタン膜は例えば約10nm程度の厚さに形成され、その上の金膜は例えば300nm程度の厚さに形成される。

【0026】

図7は、本工程を終了した後の平面図であり、先の図3(a)は図7のII−II線に沿う断面図に相当する。

【0027】

図7に示すように、ソース電極10の形状は平面視で矩形状であり、ゲート電極6と重なるようにソース電極10は形成される。

【0028】

次に、図3(b)に示す断面構造を得るまでの工程について説明する。

【0029】

まず、第2の絶縁膜8とソース電極10のそれぞれの上にフォトレジストを塗布し、それを露光、現像することによりレジストパターン11を形成する。

【0030】

そして、そのレジストパターン11をマスクに用いながら、第1の絶縁膜3、ゲート電極6、第2の絶縁膜8、及びソース電極10をエッチングすることにより開口12を形成する。そのようなエッチングにより、開口12内にゲート電極6の側面6xとドレイン電極2が露出すると共に、開口12の横にゲート電極6とソース電極10が残される。

【0031】

本工程のエッチングは膜毎に異なる条件で行われる。例えば、ゲート電極6とソース電極10のエッチングは、Arガスを用いるイオンミリングにより行われる。そして、第1の絶縁膜3と第2の絶縁膜8として形成されたポリイミド膜のエッチングには、フロン系のガスと酸素ガスとの混合ガスをエッチングガスとするドライエッチングが採用される。

【0032】

このエッチングが終了後、レジストパターン11は除去される。

【0033】

上記のように同一のレジストパターン11をマスクにして各絶縁膜3、8とゲート電極6とをドライエッチングすると、ゲート電極6の側面6xと開口12の側面が連続した同一面内に位置するようになる。

【0034】

図8は、本工程を終了した後の平面図であり、先の図3(b)は図8のIII−III線に沿う断面図に相当する。

【0035】

図8に示すように、開口12の形状は平面視で矩形状である。また、その開口12を形成した後では、上記のレジストパターン11とは別のレジストパターンを用いるフォトリソグラフィにより第2の絶縁膜8がパターニングされ、ゲート電極6を電気的に引き出すためのコンタクトホール19が形成される。

【0036】

次に、図4(a)に示すように、ドレイン電極2とソース電極10のそれぞれの上と開口12の側面に、ゲート絶縁膜16として酸化ハフニウム(HFO2)膜をALD(Atomic Layer Deposition)法により約50nm程度の厚さに形成する。

【0037】

ALD法で形成されたゲート絶縁膜16は、スパッタ法等の他の成膜方法で成膜された場合と比較して段差被覆性が良好なため、開口12の側面においてゲート絶縁膜16の厚さは均一となる。

【0038】

その後に、図4(b)に示すように、ドライエッチングでゲート絶縁膜16を異方的にエッチングすることにより、ドレイン電極2とソース電極10の各々の上面からゲート絶縁膜16を除去し、開口12の側面にゲート絶縁膜16を残す。

【0039】

なお、このドライエッチングで使用するエッチングガスは特に限定されないが、本実施形態ではBCl3ガスと酸素ガスとの混合ガスをエッチングガスとして使用する。

【0040】

次に、図5に示すように、基材1の上側全面にチャネル17を10nm〜100nm程度の厚さに形成する。そして、リフトオフ法でチャネル17をパターニングすることにより、開口12内にチャネル17を残しながら、ソース電極10の一部領域PRからチャネル17を除去する。これにより、チャネル17は、ドレイン電極2、ソース電極10、及びゲート絶縁膜16のそれぞれの上にのみ残されることになる。

【0041】

チャネル17の材料の材料として使用する半導体材料は特に限定されない。但し、シリコンは、単結晶状態の場合と比較してアモルファス状態や多結晶状態における移動度が大きく低下するので、高い移動度を維持するために単結晶状態に成膜しなければならず、結晶状態が限定されてしまうという点で不利である。

【0042】

そこで、本実施形態では、アモルファス状態や多結晶状態でも単結晶状態と同程度の移動度を維持できる酸化物半導体をチャネル17の材料として使用し、アモルファス状態にチャネル17を成膜する。

【0043】

このようにアモルファス状態で成膜したチャネル17は、下地との格子整合を図る必要がないため、成膜の対象となる下地が限定されないという利点がある。更に、アモルファス状態であればチャネル17の格子欠陥を懸念する必要もないので、格子欠陥の原因である下地とチャネル17との熱膨張率差を許容できる。

【0044】

これらにより、本実施形態では、基材1、各絶縁膜3、8、及び各電極2、10の材料を選ばずに、これらの上に高い移動度を有するチャネル17を形成することができる。

【0045】

上記した酸化物半導体は特に限定されない。本実施形態では、酸化亜鉛(ZnO)膜をチャネル17として形成する。酸化亜鉛膜は、成膜ガスとしてジエチルジンク(DEZn)と水とを気化してなるガスを使用するALD法により形成し得る。このようにして形成した酸化亜鉛膜は、10cm2/Vs〜100cm2/Vs程度の高い移動度を有する。

【0046】

また、酸化亜鉛に代えて、酸化インジウムガリウム亜鉛(IGZO)、アルミニウムドープ酸化亜鉛(AZO)、及び酸化インジウム亜鉛(IZO)のいずれかも酸化物半導体として使用し得る。

【0047】

以上により、本実施形態に係る縦型電界効果トランジスタ20の基本構造が完成する。

【0048】

図9は、その縦型電界効果トランジスタ20の平面図であり、先の図5は図9のIV−IV線に沿う断面図に相当する。

【0049】

図5に示した縦型電界効果トランジスタ20では、ソース電極10からチャネル17を通じてドレイン電極2にキャリアが流れる。そして、ゲート電極6に印加するゲート電圧を制御することで、ゲート電極6の横のチャネル領域におけるキャリアの流れを制御することができ、これにより縦型電界効果トランジスタ20のオン・オフを制御することができる。

【0050】

上記した本実施形態によれば、図5に示すように、第1の絶縁膜3の厚みを利用してドレイン電極2とゲート電極6とを隔てることで、これらドレイン電極2とゲート電極6との耐圧が確保される。

【0051】

そのため、第1の絶縁膜3の厚みを制御することによりドレイン電極2とゲート電極6との耐圧を簡単に調節するこことができると共に、第1の絶縁膜3を厚くすることで各電極2、6間の耐圧を容易に高めることができる。特に、このような高耐圧化は、第2の絶縁膜8よりも第1の絶縁膜3を厚くすることで実現が容易となる。

【0052】

更に、チャネル領域Rの厚みがゲート長となるため、ゲート長がゲート電極6の厚さと実質的に等しくなる。よって、ゲート長の短縮化のためにフォトリソグラフィでゲート電極を微細加工する必要がなく、ゲート電極6を薄厚化するだけで簡単にサブミクロンオーダーのゲート長を実現できる。

【0053】

そして、チャネル17は、各電極2、10や各絶縁膜3、8の形成後に成膜されるので、チャネル17がプロセスダメージを受け難くなる。

【0054】

しかも、そのチャネル17の材料として使用する酸化物半導体がアモルファス状態でも高い移動度を維持できるので、単結晶状態のチャネル17を形成する必要がない。これにより、プロセスコストの増大を伴うエピタキシャル成長法でチャネル17を形成する必要が無くなると共に、チャネル17の下地として使用し得る基材1の材料の選択の幅が広がる。

【0055】

特に、基材1の材料として、銅等のように熱伝導性の高い導電性材料を使用すると、縦型電界効果トランジスタ20で発生した熱が基材1から外部に速やかに放熱され、縦型電界効果トランジスタ20の放熱効果を高めることができる。

【0056】

導電性材料を使用した基材1としては、例えば、電子機器の金属性の筐体がある。本実施形態に従えば、その金属製の筐体に縦型電界効果トランジスタ20を直接形成することができ、筐体に縦型電界効果トランジスタ20を取り付ける組み立てコストを大幅に削減できる。

【0057】

また、ポリイミドフィルム等の可撓性のある膜を基材1として使用することもできるようになり、可撓性の基材1を利用した新規な構造の縦型電界効果トランジスタ20を作製することもできる。

【0058】

(第2実施形態)

図10は本実施形態に係る縦型電界効果トランジスタ21の平面図であり、図11は図10のV−V線に沿う断面図である。

【0059】

なお、図10及び図11において、第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。また、縦型電界効果トランジスタ21の製造方法についても第1実施形態と同様なので以下ではその説明を省略する。

【0060】

図11に示すように、本実施形態ではチャネル17で開口12を完全に埋め込む。このような埋め込みを実現するには、開口12の直径をチャネル17の膜厚(10nm〜100nm)の2倍以下とすればよい。

【0061】

このようにすると、開口12内のチャネル17が平面視でゲート電極6により囲まれた構造が得られる。この構造はサラウンデッドゲート構造とも呼ばれる。

【0062】

サラウンデッドゲート構造においてゲート電極6にゲート電圧を印加すると、開口12内においてチャネル17の両側からゲート電圧が印加されることになるので、チャネル17を通るキャリアに効果的にゲート電圧を加えることがでる。その結果、ゲート電圧を僅かに変化させただけでもドレイン電流を大きく変化させることができ、縦型電界効果トランジスタ21の相互コンダクタンスを高めることができる。

【0063】

(第3実施形態)

図12は本実施形態に係る縦型電界効果トランジスタ25の平面図であり、図13は図12のVI−VI線に沿う断面図である。

【0064】

なお、図12及び図13において、第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。また、縦型電界効果トランジスタ25の製造方法についても第1実施形態と同様なので以下ではその説明を省略する。

【0065】

図12に示すように、本実施形態に係る縦型電界効果トランジスタ25では、平面視で開口12がドレイン電極2に含まれる。

【0066】

このようにすると、図13に示すように、開口12の底部においてチャネル17がドレイン電極2からはみ出なくなる。そのため、第1実施形態の縦型電界効果トランジスタ25(図5参照)のように、基材1とチャネル17とが不必要に接する部分をなくすことができる。

【0067】

(第4実施形態)

図14〜図15は、本実施形態に係る縦型電界効果トランジスタの製造途中の断面図である。

【0068】

なお、図14〜図15において、第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。

【0069】

本実施形態では、2ステップのエッチングにより開口12の一部をテーパー状に形成する。

【0070】

まず、第1実施形態で説明した図1(a)〜図3(b)の工程に従い、図14(a)のようにソース電極10の上にレジストパターン11を形成する。

【0071】

そして、第1のエッチングステップにおいて、レジストパターン11をマスクにしながら第1の絶縁膜3の途中の深さまでドライエッチングすることにより開口12の上部12aを形成する。

【0072】

本工程のエッチングは膜毎に異なる条件で行われる。例えば、ゲート電極6とソース電極10のエッチングは、Arガスを用いるイオンミリングにより行われる。そして、第1の絶縁膜3と第2の絶縁膜8として形成されたポリイミド膜のエッチングには、フロン系のガスと酸素ガスとの混合ガスをエッチングガスとするドライエッチングが採用される。

【0073】

また、このようなドライエッチングでは各膜が異方的にエッチングされるので、開口12の上部12aの側面は、基材1の主面1aに対して垂直になる。

【0074】

次に、図14(b)に示すように、上記のレジストパターン11を引き続きマスクに使用しながら、第2のエッチングステップで第1の絶縁膜3をウエットエッチングすることにより開口12の下部12bを形成し、開口12内にドレイン電極2の上面を露出させる。

【0075】

そのウエットエッチングで使用するエッチング液は特に限定されない。例えば、第1の絶縁膜3としてポリイミド膜を形成する場合は、そのエッチング液として熱リン酸を使用し得る。

【0076】

ウエットエッチングは等方的に進行するため、開口12の下部12bは、基材1に向けて直径が小さくなるテーパー状となる。

【0077】

この後に、レジストパターン11は除去される。

【0078】

次いで、図15(a)に示すように、第1実施形態の図4(a)及び図4(b)の工程を行うことで、開口12の側面にゲート絶縁膜16を形成する。

【0079】

なお、第1実施形態で説明したように、ソース電極10やドレイン電極2の上に形成されたゲート絶縁膜16はドライエッチングによって除去されるが、開口12の下部12bに形成されたゲート絶縁膜16もそのドライエッチング時に除去される。

【0080】

続いて、図15(b)に示すように、基材1の上側全面にチャネル17を形成した後、リフトオフ法によりチャネル17をパターニングし、ドレイン電極2、ソース電極10、及びゲート絶縁膜16のそれぞれの上にチャネル17を残す。

【0081】

本実施形態では、チャネル17として酸化亜鉛をスパッタ法で堆積させる。

【0082】

このようにスパッタ法を用いると、第1実施形態のようにALD法を用いる場合と比較してチャネル17の段差被覆性が悪くなる。その結果、開口12のテーパー状の下部12bに形成されたチャネル17の膜厚T2を、上部12aに形成されたチャネル17の膜厚T1よりも厚くすることができる。

【0083】

以上により、本実施形態に係る電界効果トランジスタ27の基本構造が完成する。

【0084】

上記した本実施形態によれば、図15(b)に示したように、開口12の上部12aに形成されたチャネル17の膜厚T1と比較して、下部12bに形成されたチャネル17の膜厚T2を厚くすることができる。

【0085】

そのため、下部12bにおけるチャネル17の抵抗が小さくなり、第1実施形態と比較して縦型電界効果トランジスタ27のオン抵抗を低減することが可能となる。

【0086】

また、ゲート電極6の横のチャネル17の膜厚T1を下部12bにおける膜厚T2よりも薄くできるので、ゲート電極6に印加するゲート電圧でチャネル17内のキャリアの流れを効率的に制御することができる。

【0087】

(第5実施形態)

図16は、本実施形態に係る縦型電界効果トランジスタ28の断面図である。なお、図16において、第1実施形態で説明したのと同じ要素には第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0088】

また、本実施形態は、第1実施形態で説明したドレイン電極2とソース電極10の役割を入れ替えるのみであり、第1実施形態と同様の製造方法で縦型電界効果トランジスタ28を作製できるので、その製造方法については省略する。

【0089】

図16に示すように、本実施形態では、基材1の上にソース電極10を形成し、第2の絶縁膜8の上にドレイン電極2を形成する。

【0090】

そして、ゲート電極6とドレイン電極2との耐圧を高めるため、第1の絶縁膜3と比較して第2の絶縁膜8の膜厚を厚くし、ゲート電極6とドレイン電極2との間隔を広める。

【0091】

第1実施形態で説明したように、導電性の基材1としては電子機器の金属製の筐体を使用し得るが、その筐体は接地電位に維持されることが多い。そのため、基材1として筐体を用い、上記のように基材1の上にソース電極10を形成すると、簡単にソース接地回路を実現できる。

【0092】

また、電子機器において筐体は広範な領域を占めるので、ワイヤ等で上記のソース回路の接地を行う場合と比較して、本実施形態ではソース接地回路の接地インダクタンスを低減できるという利点も得られる。特に、無線基地局のパワーアンプでは、ソース接地回路が用いられることが多いので、本実施形態の縦型電界効果トランジスタ28を使用する実益がある。

【0093】

(第6実施形態)

図17は、本実施形態に係る縦型電界効果トランジスタ30の断面図である。なお、図17において、第1〜第6実施形態で説明したのと同じ要素にはこれらの実施形態と同じ符号を付し、以下ではその説明を省略する。

【0094】

本実施形態では、基材1として、絶縁性コア基板31と導体部32とを備えた配線基板を使用する。このうち、絶縁性コア基材31の材料としては、ガラスエポキシ等の有機材料やセラミックを使用し得る。

【0095】

一方、導体部32は、例えば、絶縁性コア基板31の貫通孔31aに埋め込まれた銅を材料とするビア充填体である。

【0096】

このような配線基板は、例えば、電子機器内において半導体パッケージの一部として使用されるものである。

【0097】

第1実施形態で説明したように、チャネル17として形成される酸化物半導体は、成膜の下地を選ばないため、このように導体部32上に直接形成することができる。これにより、配線基板上にチャネル17を直接形成してなる新規な構造の縦型電界効果トランジスタ30を提供することができる。

【0098】

以上説明した各実施形態に関し、更に以下の付記を開示する。

【0099】

(付記1) 基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を有することを特徴とする縦型電界効果トランジスタ。

【0100】

(付記2) 前記開口が、前記チャネルにより完全に埋め込まれたことを特徴とする付記1に記載の縦型電界効果トランジスタ。

【0101】

(付記3) 前記開口が平面視で前記第1の電極に含まれることを特徴とする付記1に記載の縦型電界効果トランジスタ。

【0102】

(付記4) 前記開口は、前記基材に向けて直径が小さくなるテーパー状であって前記第1の絶縁膜に形成された下部と、側面が前記基材の主面に対して垂直であって前記第2の絶縁膜に形成された上部とを有し、

前記下部に形成された前記チャネルが、前記上部に形成された前記チャネルよりも厚いことを特徴とする付記1に記載の縦型電界効果トランジスタ。

【0103】

(付記5) 前記第1の電極は前記ドレイン電極であり、

前記第2の電極は前記ソース電極であり、

前記第1の絶縁膜が前記第2の絶縁膜よりも厚いことを特徴とする付記1乃至付記4のいずれかに記載の縦型電界効果トランジスタ。

【0104】

(付記6) 前記第1の電極は前記ソース電極であり、

前記第2の電極は前記ドレイン電極であり、

前記第2の絶縁膜が前記第1の絶縁膜よりも厚く、

前記基材は導電性を有することを特徴とする付記1乃至付記5のいずれかに記載の縦型電界効果トランジスタ。

【0105】

(付記7) 前記基材は、配線基板又は電気機器の筐体であることを特徴とする付記1乃至付記6のいずれかに記載の縦型電界効果トランジスタ。

【0106】

(付記8) 配線基板と筐体のいずれかを含む基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を備えた縦型電界効果トランジスタを有することを特徴とする電子機器。

【0107】

(付記9) 基材の上に、ソース電極とドレイン電極のうちの一方となる第1の電極を形成する工程と、

前記基材と前記第1の電極のそれぞれの上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の上であって、平面視で前記第1の電極と重なる部分に、ゲート電極を形成する工程と、

前記第1の絶縁膜と前記ゲート電極のそれぞれの上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜の上であって、平面視で前記ゲート電極と重なる部分に、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極を形成する工程と、

前記第2の電極、前記第2の絶縁膜、前記ゲート電極、及び前記第1の絶縁膜をエッチングして開口を形成することにより、該開口内に前記第1の電極を露出させる工程と、

前記エッチングによって前記開口内に露出した前記ゲート電極の側面にゲート絶縁膜を形成する工程と、

前記第1の電極、前記ゲート絶縁膜、及び前記第2の電極のそれぞれの上に、酸化物半導体を材料とするチャネルを形成する工程と、

を有することを特徴とする縦型電界効果トランジスタの製造方法。

【0108】

(付記10) 前記開口を形成する工程は、

ドライエッチングにより、前記第2の絶縁膜と前記ゲート電極とを異方的にエッチングして前記開口の上部を形成する第1のエッチングステップと、

前記第1のエッチングステップの後、ウエットエッチングにより、前記第1の絶縁膜をエッチングして前記開口の下部を形成する第2のエッチングステップとを有し、

前記チャネルを形成する工程は、スパッタ法により前記開口の側面に前記酸化物半導体を堆積させることにより行われることを特徴とする付記9に記載の縦型電界効果トランジスタの製造方法。

【符号の説明】

【0109】

1…基材、1a…主面、2…ドレイン電極、3…第1の絶縁膜、6…ゲート電極、8…第2の絶縁膜、10…ソース電極、11…レジストパターン、12…開口、12a…開口の上部、12b…開口の下部、16…ゲート絶縁膜、17…チャネル、20、21、25、27、30…縦型電界効果トランジスタ、31…絶縁性コア基板、31a…貫通孔、32…導体部。

【技術分野】

【0001】

本発明は、縦型電界効果トランジスタとその製造方法及び電子機器に関する。

【背景技術】

【0002】

縦型電界効果トランジスタは、基板の高さ方向にドレイン電極とゲート電極とが隔てられており、それらの電極間に半導体層が介在した構造を有しているため、ドレイン電極とゲート電極との間の耐圧が高いという特徴がある。このような特徴を活かし、縦型電界効果トランジスタは、電源用等の高耐圧トランジスタとして広く使用されている。

【0003】

そのような縦型電界効果トランジスタでは、上記の半導体層がチャネルを兼ねているが、ドレイン電極とゲート電極とを離して高耐圧を実現するには、その半導体層を厚く形成するのが望まれる。

【0004】

但し、その半導体層はエピタキシャル成長法により形成されるので、成長に長時間を要し、プロセスコストが増大するという問題がある。

【0005】

更に、半導体層とその下の基板との間で格子定数の不整合や熱膨張率の相違があると、半導体層に格子欠陥が入る危険性が高くなる。そのような危険をなくすため、上記の縦型電界効果トランジスタでは、半導体層と格子定数や熱膨張率が近い結晶性基板を使用せざるを得ず、使用可能な基板の材料が制限されるという問題もある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭63−101740号公報

【特許文献2】特開2003−110110号公報

【特許文献3】特開昭61−269377号公報

【特許文献4】特開2008−205414号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

縦型電界効果トランジスタとその製造方法及び電子機器において、基材の材料の選択の幅を広げることを目的とする。

【課題を解決するための手段】

【0008】

以下の開示の一観点によれば、基材と、前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、前記開口の側面に形成されたゲート絶縁膜と、前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルとを有する縦型電界効果トランジスタが提供される。

【0009】

更に、その開示の他の観点によれば、基材の上に、ソース電極とドレイン電極のうちの一方となる第1の電極を形成する工程と、前記基材と前記第1の電極のそれぞれの上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の上であって、平面視で前記第1の電極と重なる部分に、ゲート電極を形成する工程と、前記第1の絶縁膜と前記ゲート電極のそれぞれの上に第2の絶縁膜を形成する工程と、前記第2の絶縁膜の上であって、平面視で前記ゲート電極と重なる部分に、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極を形成する工程と、前記第2の電極、前記第2の絶縁膜、前記ゲート電極、及び前記第1の絶縁膜をエッチングして開口を形成することにより、該開口内に前記第1の電極を露出させる工程と、前記エッチングによって前記開口内に露出した前記ゲート電極の側面にゲート絶縁膜を形成する工程と、前記第1の電極、前記ゲート絶縁膜、及び前記第2の電極のそれぞれの上に、酸化物半導体を材料とするチャネルを形成する工程とを有する縦型電界効果トランジスタの製造方法が提供される。

【0010】

そして、その開示の別の観点によれば、配線基板と筐体のいずれかを含む基材と、前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、前記開口の側面に形成されたゲート絶縁膜と、前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルとを備えた縦型電界効果トランジスタを有することを特徴とする電子機器が提供される。

【発明の効果】

【0011】

以下の開示によれば、アモルファス状態でも高い移動度を維持できる酸化物半導体をチャネルの材料に使用するので、チャネルと基材との格子整合を図る必要がなくなり、基材として使用できる材料の選択の幅が広がる。

【図面の簡単な説明】

【0012】

【図1】図1(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その1)である。

【図2】図2(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その2)である。

【図3】図3(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その3)である。

【図4】図4(a)、(b)は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その4)である。

【図5】図5は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その5)である。

【図6】図6は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その1)である。

【図7】図7は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その2)である。

【図8】図8は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その3)である。

【図9】図9は、第1実施形態に係る縦型電界効果トランジスタの製造途中の平面図(その4)である。

【図10】図10は、第2実施形態に係る縦型電界効果トランジスタの平面図である。

【図11】図11は、図10のV−V線に沿う断面図である。

【図12】図12は、第3実施形態に係る縦型電界効果トランジスタの平面図である。

【図13】図13は、図12のVI−VI線に沿う断面図である。

【図14】図14(a)、(b)は、第4実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その1)である。

【図15】図15(a)、(b)は、第4実施形態に係る縦型電界効果トランジスタの製造途中の断面図(その2)である。

【図16】図16は、第5実施形態に係る縦型電界効果トランジスタの断面図である。

【図17】図17は、第6実施形態に係る縦型電界効果トランジスタの断面図である。

【発明を実施するための形態】

【0013】

(第1実施形態)

第1実施形態に係る縦型電界効果トランジスタについて、その製造工程を追いながら説明する。

【0014】

図1〜図5は、第1実施形態に係る縦型電界効果トランジスタの製造途中の断面図であり、図6〜図9はその平面図である。

【0015】

最初に、図1(a)に示すように、銅を材料とする基材1の上に、蒸着法又はスパッタ法によりチタン膜と金膜とをこの順に形成した後、これらの膜をリフトオフ法によりパターニングしてドレイン電極2とする。

【0016】

なお、ドレイン電極2として形成されるチタン膜と金膜の厚さは特に限定されない。チタン膜は、金膜と基材1との密着性を高める密着膜としての機能を有し、約10nm程度の厚さに形成される。また、金膜は、ドレイン電極2の大部分を占めるものであって、約300nm程度の厚さに形成される。

【0017】

次に、図1(b)に示すように、基材1とドレイン電極2のそれぞれの上にポリイミドの塗膜を形成し、それを熱硬化させて第1の絶縁膜3とする。

【0018】

第1の絶縁膜3は、後で完成する縦型電界効果トランジスタの耐圧に応じた膜厚に形成され、本実施形態では1μm〜100μmの膜厚に形成される。

【0019】

続いて、図2(a)に示すように、第1の絶縁膜3の上にチタン膜と金膜とをこの順に形成した後、リフトオフ法によりこれらの膜をパターニングしてゲート電極6を形成する。

【0020】

上記したチタン膜は例えば約10nm程度の厚さに形成され、その上の金膜は例えば300nm程度の厚さに形成される。

【0021】

図6は、本工程を終了後の平面図であり、先の図2(a)は図6のI−I線に沿う断面図に相当する。

【0022】

図6に示すように、ドレイン電極2とゲート電極6の形状は、いずれも平面視で矩形状である。そして、ゲート電極6は、平面視でドレイン電極2と重なるように形成される。

【0023】

次いで、図2(b)に示すように、第1の絶縁膜3とゲート電極6のそれぞれの上にポリイミドの塗膜を形成してそれを熱硬化させることにより、厚さが約0.5μmの第2の絶縁膜8を形成する。

【0024】

続いて、図3(a)に示すように、第2の絶縁膜8の上にソース電極10を形成する。ソース電極10の形成方法は特に限定されないが、本実施形態では第2の絶縁膜8の上にチタン膜と金膜とをこの順に形成した後、リフトオフ法によりこれらの膜をパターニングしてソース電極10を形成する。

【0025】

ソース電極10の厚さも特に限定されず、チタン膜は例えば約10nm程度の厚さに形成され、その上の金膜は例えば300nm程度の厚さに形成される。

【0026】

図7は、本工程を終了した後の平面図であり、先の図3(a)は図7のII−II線に沿う断面図に相当する。

【0027】

図7に示すように、ソース電極10の形状は平面視で矩形状であり、ゲート電極6と重なるようにソース電極10は形成される。

【0028】

次に、図3(b)に示す断面構造を得るまでの工程について説明する。

【0029】

まず、第2の絶縁膜8とソース電極10のそれぞれの上にフォトレジストを塗布し、それを露光、現像することによりレジストパターン11を形成する。

【0030】

そして、そのレジストパターン11をマスクに用いながら、第1の絶縁膜3、ゲート電極6、第2の絶縁膜8、及びソース電極10をエッチングすることにより開口12を形成する。そのようなエッチングにより、開口12内にゲート電極6の側面6xとドレイン電極2が露出すると共に、開口12の横にゲート電極6とソース電極10が残される。

【0031】

本工程のエッチングは膜毎に異なる条件で行われる。例えば、ゲート電極6とソース電極10のエッチングは、Arガスを用いるイオンミリングにより行われる。そして、第1の絶縁膜3と第2の絶縁膜8として形成されたポリイミド膜のエッチングには、フロン系のガスと酸素ガスとの混合ガスをエッチングガスとするドライエッチングが採用される。

【0032】

このエッチングが終了後、レジストパターン11は除去される。

【0033】

上記のように同一のレジストパターン11をマスクにして各絶縁膜3、8とゲート電極6とをドライエッチングすると、ゲート電極6の側面6xと開口12の側面が連続した同一面内に位置するようになる。

【0034】

図8は、本工程を終了した後の平面図であり、先の図3(b)は図8のIII−III線に沿う断面図に相当する。

【0035】

図8に示すように、開口12の形状は平面視で矩形状である。また、その開口12を形成した後では、上記のレジストパターン11とは別のレジストパターンを用いるフォトリソグラフィにより第2の絶縁膜8がパターニングされ、ゲート電極6を電気的に引き出すためのコンタクトホール19が形成される。

【0036】

次に、図4(a)に示すように、ドレイン電極2とソース電極10のそれぞれの上と開口12の側面に、ゲート絶縁膜16として酸化ハフニウム(HFO2)膜をALD(Atomic Layer Deposition)法により約50nm程度の厚さに形成する。

【0037】

ALD法で形成されたゲート絶縁膜16は、スパッタ法等の他の成膜方法で成膜された場合と比較して段差被覆性が良好なため、開口12の側面においてゲート絶縁膜16の厚さは均一となる。

【0038】

その後に、図4(b)に示すように、ドライエッチングでゲート絶縁膜16を異方的にエッチングすることにより、ドレイン電極2とソース電極10の各々の上面からゲート絶縁膜16を除去し、開口12の側面にゲート絶縁膜16を残す。

【0039】

なお、このドライエッチングで使用するエッチングガスは特に限定されないが、本実施形態ではBCl3ガスと酸素ガスとの混合ガスをエッチングガスとして使用する。

【0040】

次に、図5に示すように、基材1の上側全面にチャネル17を10nm〜100nm程度の厚さに形成する。そして、リフトオフ法でチャネル17をパターニングすることにより、開口12内にチャネル17を残しながら、ソース電極10の一部領域PRからチャネル17を除去する。これにより、チャネル17は、ドレイン電極2、ソース電極10、及びゲート絶縁膜16のそれぞれの上にのみ残されることになる。

【0041】

チャネル17の材料の材料として使用する半導体材料は特に限定されない。但し、シリコンは、単結晶状態の場合と比較してアモルファス状態や多結晶状態における移動度が大きく低下するので、高い移動度を維持するために単結晶状態に成膜しなければならず、結晶状態が限定されてしまうという点で不利である。

【0042】

そこで、本実施形態では、アモルファス状態や多結晶状態でも単結晶状態と同程度の移動度を維持できる酸化物半導体をチャネル17の材料として使用し、アモルファス状態にチャネル17を成膜する。

【0043】

このようにアモルファス状態で成膜したチャネル17は、下地との格子整合を図る必要がないため、成膜の対象となる下地が限定されないという利点がある。更に、アモルファス状態であればチャネル17の格子欠陥を懸念する必要もないので、格子欠陥の原因である下地とチャネル17との熱膨張率差を許容できる。

【0044】

これらにより、本実施形態では、基材1、各絶縁膜3、8、及び各電極2、10の材料を選ばずに、これらの上に高い移動度を有するチャネル17を形成することができる。

【0045】

上記した酸化物半導体は特に限定されない。本実施形態では、酸化亜鉛(ZnO)膜をチャネル17として形成する。酸化亜鉛膜は、成膜ガスとしてジエチルジンク(DEZn)と水とを気化してなるガスを使用するALD法により形成し得る。このようにして形成した酸化亜鉛膜は、10cm2/Vs〜100cm2/Vs程度の高い移動度を有する。

【0046】

また、酸化亜鉛に代えて、酸化インジウムガリウム亜鉛(IGZO)、アルミニウムドープ酸化亜鉛(AZO)、及び酸化インジウム亜鉛(IZO)のいずれかも酸化物半導体として使用し得る。

【0047】

以上により、本実施形態に係る縦型電界効果トランジスタ20の基本構造が完成する。

【0048】

図9は、その縦型電界効果トランジスタ20の平面図であり、先の図5は図9のIV−IV線に沿う断面図に相当する。

【0049】

図5に示した縦型電界効果トランジスタ20では、ソース電極10からチャネル17を通じてドレイン電極2にキャリアが流れる。そして、ゲート電極6に印加するゲート電圧を制御することで、ゲート電極6の横のチャネル領域におけるキャリアの流れを制御することができ、これにより縦型電界効果トランジスタ20のオン・オフを制御することができる。

【0050】

上記した本実施形態によれば、図5に示すように、第1の絶縁膜3の厚みを利用してドレイン電極2とゲート電極6とを隔てることで、これらドレイン電極2とゲート電極6との耐圧が確保される。

【0051】

そのため、第1の絶縁膜3の厚みを制御することによりドレイン電極2とゲート電極6との耐圧を簡単に調節するこことができると共に、第1の絶縁膜3を厚くすることで各電極2、6間の耐圧を容易に高めることができる。特に、このような高耐圧化は、第2の絶縁膜8よりも第1の絶縁膜3を厚くすることで実現が容易となる。

【0052】

更に、チャネル領域Rの厚みがゲート長となるため、ゲート長がゲート電極6の厚さと実質的に等しくなる。よって、ゲート長の短縮化のためにフォトリソグラフィでゲート電極を微細加工する必要がなく、ゲート電極6を薄厚化するだけで簡単にサブミクロンオーダーのゲート長を実現できる。

【0053】

そして、チャネル17は、各電極2、10や各絶縁膜3、8の形成後に成膜されるので、チャネル17がプロセスダメージを受け難くなる。

【0054】

しかも、そのチャネル17の材料として使用する酸化物半導体がアモルファス状態でも高い移動度を維持できるので、単結晶状態のチャネル17を形成する必要がない。これにより、プロセスコストの増大を伴うエピタキシャル成長法でチャネル17を形成する必要が無くなると共に、チャネル17の下地として使用し得る基材1の材料の選択の幅が広がる。

【0055】

特に、基材1の材料として、銅等のように熱伝導性の高い導電性材料を使用すると、縦型電界効果トランジスタ20で発生した熱が基材1から外部に速やかに放熱され、縦型電界効果トランジスタ20の放熱効果を高めることができる。

【0056】

導電性材料を使用した基材1としては、例えば、電子機器の金属性の筐体がある。本実施形態に従えば、その金属製の筐体に縦型電界効果トランジスタ20を直接形成することができ、筐体に縦型電界効果トランジスタ20を取り付ける組み立てコストを大幅に削減できる。

【0057】

また、ポリイミドフィルム等の可撓性のある膜を基材1として使用することもできるようになり、可撓性の基材1を利用した新規な構造の縦型電界効果トランジスタ20を作製することもできる。

【0058】

(第2実施形態)

図10は本実施形態に係る縦型電界効果トランジスタ21の平面図であり、図11は図10のV−V線に沿う断面図である。

【0059】

なお、図10及び図11において、第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。また、縦型電界効果トランジスタ21の製造方法についても第1実施形態と同様なので以下ではその説明を省略する。

【0060】

図11に示すように、本実施形態ではチャネル17で開口12を完全に埋め込む。このような埋め込みを実現するには、開口12の直径をチャネル17の膜厚(10nm〜100nm)の2倍以下とすればよい。

【0061】

このようにすると、開口12内のチャネル17が平面視でゲート電極6により囲まれた構造が得られる。この構造はサラウンデッドゲート構造とも呼ばれる。

【0062】

サラウンデッドゲート構造においてゲート電極6にゲート電圧を印加すると、開口12内においてチャネル17の両側からゲート電圧が印加されることになるので、チャネル17を通るキャリアに効果的にゲート電圧を加えることがでる。その結果、ゲート電圧を僅かに変化させただけでもドレイン電流を大きく変化させることができ、縦型電界効果トランジスタ21の相互コンダクタンスを高めることができる。

【0063】

(第3実施形態)

図12は本実施形態に係る縦型電界効果トランジスタ25の平面図であり、図13は図12のVI−VI線に沿う断面図である。

【0064】

なお、図12及び図13において、第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。また、縦型電界効果トランジスタ25の製造方法についても第1実施形態と同様なので以下ではその説明を省略する。

【0065】

図12に示すように、本実施形態に係る縦型電界効果トランジスタ25では、平面視で開口12がドレイン電極2に含まれる。

【0066】

このようにすると、図13に示すように、開口12の底部においてチャネル17がドレイン電極2からはみ出なくなる。そのため、第1実施形態の縦型電界効果トランジスタ25(図5参照)のように、基材1とチャネル17とが不必要に接する部分をなくすことができる。

【0067】

(第4実施形態)

図14〜図15は、本実施形態に係る縦型電界効果トランジスタの製造途中の断面図である。

【0068】

なお、図14〜図15において、第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。

【0069】

本実施形態では、2ステップのエッチングにより開口12の一部をテーパー状に形成する。

【0070】

まず、第1実施形態で説明した図1(a)〜図3(b)の工程に従い、図14(a)のようにソース電極10の上にレジストパターン11を形成する。

【0071】

そして、第1のエッチングステップにおいて、レジストパターン11をマスクにしながら第1の絶縁膜3の途中の深さまでドライエッチングすることにより開口12の上部12aを形成する。

【0072】

本工程のエッチングは膜毎に異なる条件で行われる。例えば、ゲート電極6とソース電極10のエッチングは、Arガスを用いるイオンミリングにより行われる。そして、第1の絶縁膜3と第2の絶縁膜8として形成されたポリイミド膜のエッチングには、フロン系のガスと酸素ガスとの混合ガスをエッチングガスとするドライエッチングが採用される。

【0073】

また、このようなドライエッチングでは各膜が異方的にエッチングされるので、開口12の上部12aの側面は、基材1の主面1aに対して垂直になる。

【0074】

次に、図14(b)に示すように、上記のレジストパターン11を引き続きマスクに使用しながら、第2のエッチングステップで第1の絶縁膜3をウエットエッチングすることにより開口12の下部12bを形成し、開口12内にドレイン電極2の上面を露出させる。

【0075】

そのウエットエッチングで使用するエッチング液は特に限定されない。例えば、第1の絶縁膜3としてポリイミド膜を形成する場合は、そのエッチング液として熱リン酸を使用し得る。

【0076】

ウエットエッチングは等方的に進行するため、開口12の下部12bは、基材1に向けて直径が小さくなるテーパー状となる。

【0077】

この後に、レジストパターン11は除去される。

【0078】

次いで、図15(a)に示すように、第1実施形態の図4(a)及び図4(b)の工程を行うことで、開口12の側面にゲート絶縁膜16を形成する。

【0079】

なお、第1実施形態で説明したように、ソース電極10やドレイン電極2の上に形成されたゲート絶縁膜16はドライエッチングによって除去されるが、開口12の下部12bに形成されたゲート絶縁膜16もそのドライエッチング時に除去される。

【0080】

続いて、図15(b)に示すように、基材1の上側全面にチャネル17を形成した後、リフトオフ法によりチャネル17をパターニングし、ドレイン電極2、ソース電極10、及びゲート絶縁膜16のそれぞれの上にチャネル17を残す。

【0081】

本実施形態では、チャネル17として酸化亜鉛をスパッタ法で堆積させる。

【0082】

このようにスパッタ法を用いると、第1実施形態のようにALD法を用いる場合と比較してチャネル17の段差被覆性が悪くなる。その結果、開口12のテーパー状の下部12bに形成されたチャネル17の膜厚T2を、上部12aに形成されたチャネル17の膜厚T1よりも厚くすることができる。

【0083】

以上により、本実施形態に係る電界効果トランジスタ27の基本構造が完成する。

【0084】

上記した本実施形態によれば、図15(b)に示したように、開口12の上部12aに形成されたチャネル17の膜厚T1と比較して、下部12bに形成されたチャネル17の膜厚T2を厚くすることができる。

【0085】

そのため、下部12bにおけるチャネル17の抵抗が小さくなり、第1実施形態と比較して縦型電界効果トランジスタ27のオン抵抗を低減することが可能となる。

【0086】

また、ゲート電極6の横のチャネル17の膜厚T1を下部12bにおける膜厚T2よりも薄くできるので、ゲート電極6に印加するゲート電圧でチャネル17内のキャリアの流れを効率的に制御することができる。

【0087】

(第5実施形態)

図16は、本実施形態に係る縦型電界効果トランジスタ28の断面図である。なお、図16において、第1実施形態で説明したのと同じ要素には第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0088】

また、本実施形態は、第1実施形態で説明したドレイン電極2とソース電極10の役割を入れ替えるのみであり、第1実施形態と同様の製造方法で縦型電界効果トランジスタ28を作製できるので、その製造方法については省略する。

【0089】

図16に示すように、本実施形態では、基材1の上にソース電極10を形成し、第2の絶縁膜8の上にドレイン電極2を形成する。

【0090】

そして、ゲート電極6とドレイン電極2との耐圧を高めるため、第1の絶縁膜3と比較して第2の絶縁膜8の膜厚を厚くし、ゲート電極6とドレイン電極2との間隔を広める。

【0091】

第1実施形態で説明したように、導電性の基材1としては電子機器の金属製の筐体を使用し得るが、その筐体は接地電位に維持されることが多い。そのため、基材1として筐体を用い、上記のように基材1の上にソース電極10を形成すると、簡単にソース接地回路を実現できる。

【0092】

また、電子機器において筐体は広範な領域を占めるので、ワイヤ等で上記のソース回路の接地を行う場合と比較して、本実施形態ではソース接地回路の接地インダクタンスを低減できるという利点も得られる。特に、無線基地局のパワーアンプでは、ソース接地回路が用いられることが多いので、本実施形態の縦型電界効果トランジスタ28を使用する実益がある。

【0093】

(第6実施形態)

図17は、本実施形態に係る縦型電界効果トランジスタ30の断面図である。なお、図17において、第1〜第6実施形態で説明したのと同じ要素にはこれらの実施形態と同じ符号を付し、以下ではその説明を省略する。

【0094】

本実施形態では、基材1として、絶縁性コア基板31と導体部32とを備えた配線基板を使用する。このうち、絶縁性コア基材31の材料としては、ガラスエポキシ等の有機材料やセラミックを使用し得る。

【0095】

一方、導体部32は、例えば、絶縁性コア基板31の貫通孔31aに埋め込まれた銅を材料とするビア充填体である。

【0096】

このような配線基板は、例えば、電子機器内において半導体パッケージの一部として使用されるものである。

【0097】

第1実施形態で説明したように、チャネル17として形成される酸化物半導体は、成膜の下地を選ばないため、このように導体部32上に直接形成することができる。これにより、配線基板上にチャネル17を直接形成してなる新規な構造の縦型電界効果トランジスタ30を提供することができる。

【0098】

以上説明した各実施形態に関し、更に以下の付記を開示する。

【0099】

(付記1) 基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を有することを特徴とする縦型電界効果トランジスタ。

【0100】

(付記2) 前記開口が、前記チャネルにより完全に埋め込まれたことを特徴とする付記1に記載の縦型電界効果トランジスタ。

【0101】

(付記3) 前記開口が平面視で前記第1の電極に含まれることを特徴とする付記1に記載の縦型電界効果トランジスタ。

【0102】

(付記4) 前記開口は、前記基材に向けて直径が小さくなるテーパー状であって前記第1の絶縁膜に形成された下部と、側面が前記基材の主面に対して垂直であって前記第2の絶縁膜に形成された上部とを有し、

前記下部に形成された前記チャネルが、前記上部に形成された前記チャネルよりも厚いことを特徴とする付記1に記載の縦型電界効果トランジスタ。

【0103】

(付記5) 前記第1の電極は前記ドレイン電極であり、

前記第2の電極は前記ソース電極であり、

前記第1の絶縁膜が前記第2の絶縁膜よりも厚いことを特徴とする付記1乃至付記4のいずれかに記載の縦型電界効果トランジスタ。

【0104】

(付記6) 前記第1の電極は前記ソース電極であり、

前記第2の電極は前記ドレイン電極であり、

前記第2の絶縁膜が前記第1の絶縁膜よりも厚く、

前記基材は導電性を有することを特徴とする付記1乃至付記5のいずれかに記載の縦型電界効果トランジスタ。

【0105】

(付記7) 前記基材は、配線基板又は電気機器の筐体であることを特徴とする付記1乃至付記6のいずれかに記載の縦型電界効果トランジスタ。

【0106】

(付記8) 配線基板と筐体のいずれかを含む基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を備えた縦型電界効果トランジスタを有することを特徴とする電子機器。

【0107】

(付記9) 基材の上に、ソース電極とドレイン電極のうちの一方となる第1の電極を形成する工程と、

前記基材と前記第1の電極のそれぞれの上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の上であって、平面視で前記第1の電極と重なる部分に、ゲート電極を形成する工程と、

前記第1の絶縁膜と前記ゲート電極のそれぞれの上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜の上であって、平面視で前記ゲート電極と重なる部分に、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極を形成する工程と、

前記第2の電極、前記第2の絶縁膜、前記ゲート電極、及び前記第1の絶縁膜をエッチングして開口を形成することにより、該開口内に前記第1の電極を露出させる工程と、

前記エッチングによって前記開口内に露出した前記ゲート電極の側面にゲート絶縁膜を形成する工程と、

前記第1の電極、前記ゲート絶縁膜、及び前記第2の電極のそれぞれの上に、酸化物半導体を材料とするチャネルを形成する工程と、

を有することを特徴とする縦型電界効果トランジスタの製造方法。

【0108】

(付記10) 前記開口を形成する工程は、

ドライエッチングにより、前記第2の絶縁膜と前記ゲート電極とを異方的にエッチングして前記開口の上部を形成する第1のエッチングステップと、

前記第1のエッチングステップの後、ウエットエッチングにより、前記第1の絶縁膜をエッチングして前記開口の下部を形成する第2のエッチングステップとを有し、

前記チャネルを形成する工程は、スパッタ法により前記開口の側面に前記酸化物半導体を堆積させることにより行われることを特徴とする付記9に記載の縦型電界効果トランジスタの製造方法。

【符号の説明】

【0109】

1…基材、1a…主面、2…ドレイン電極、3…第1の絶縁膜、6…ゲート電極、8…第2の絶縁膜、10…ソース電極、11…レジストパターン、12…開口、12a…開口の上部、12b…開口の下部、16…ゲート絶縁膜、17…チャネル、20、21、25、27、30…縦型電界効果トランジスタ、31…絶縁性コア基板、31a…貫通孔、32…導体部。

【特許請求の範囲】

【請求項1】

基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を有することを特徴とする縦型電界効果トランジスタ。

【請求項2】

前記開口が、前記チャネルにより完全に埋め込まれたことを特徴とする請求項1に記載の縦型電界効果トランジスタ。

【請求項3】

前記開口は、前記基材に向けて直径が小さくなるテーパー状であって前記第1の絶縁膜に形成された下部と、側面が前記基材の主面に対して垂直であって前記第2の絶縁膜に形成された上部とを有し、

前記下部に形成された前記チャネルが、前記上部に形成された前記チャネルよりも厚いことを特徴とする請求項1に記載の縦型電界効果トランジスタ。

【請求項4】

配線基板と筐体のいずれかを含む基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を備えた縦型電界効果トランジスタを有することを特徴とする電子機器。

【請求項5】

基材の上に、ソース電極とドレイン電極のうちの一方となる第1の電極を形成する工程と、

前記基材と前記第1の電極のそれぞれの上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の上であって、平面視で前記第1の電極と重なる部分に、ゲート電極を形成する工程と、

前記第1の絶縁膜と前記ゲート電極のそれぞれの上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜の上であって、平面視で前記ゲート電極と重なる部分に、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極を形成する工程と、

前記第2の電極、前記第2の絶縁膜、前記ゲート電極、及び前記第1の絶縁膜をエッチングして開口を形成することにより、該開口内に前記第1の電極を露出させる工程と、

前記エッチングによって前記開口内に露出した前記ゲート電極の側面にゲート絶縁膜を形成する工程と、

前記第1の電極、前記ゲート絶縁膜、及び前記第2の電極のそれぞれの上に、酸化物半導体を材料とするチャネルを形成する工程と、

を有することを特徴とする縦型電界効果トランジスタの製造方法。

【請求項1】

基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を有することを特徴とする縦型電界効果トランジスタ。

【請求項2】

前記開口が、前記チャネルにより完全に埋め込まれたことを特徴とする請求項1に記載の縦型電界効果トランジスタ。

【請求項3】

前記開口は、前記基材に向けて直径が小さくなるテーパー状であって前記第1の絶縁膜に形成された下部と、側面が前記基材の主面に対して垂直であって前記第2の絶縁膜に形成された上部とを有し、

前記下部に形成された前記チャネルが、前記上部に形成された前記チャネルよりも厚いことを特徴とする請求項1に記載の縦型電界効果トランジスタ。

【請求項4】

配線基板と筐体のいずれかを含む基材と、

前記基材の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極と、

前記基材の上に形成され、前記第1の電極に重なる開口を備えた第1の絶縁膜と、

前記開口の横の前記第1の絶縁膜の上に形成されたゲート電極と、

前記第1の絶縁膜の上に形成され、前記開口を備えた第2の絶縁膜と、

前記開口の横の前記第2の絶縁膜の上に形成され、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極と、

前記開口の側面に形成されたゲート絶縁膜と、

前記第1の電極、前記第2の電極、及び前記ゲート絶縁膜上に形成され、酸化物半導体を材料とするチャネルと、

を備えた縦型電界効果トランジスタを有することを特徴とする電子機器。

【請求項5】

基材の上に、ソース電極とドレイン電極のうちの一方となる第1の電極を形成する工程と、

前記基材と前記第1の電極のそれぞれの上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の上であって、平面視で前記第1の電極と重なる部分に、ゲート電極を形成する工程と、

前記第1の絶縁膜と前記ゲート電極のそれぞれの上に第2の絶縁膜を形成する工程と、

前記第2の絶縁膜の上であって、平面視で前記ゲート電極と重なる部分に、前記ソース電極と前記ドレイン電極のうちの他方となる第2の電極を形成する工程と、

前記第2の電極、前記第2の絶縁膜、前記ゲート電極、及び前記第1の絶縁膜をエッチングして開口を形成することにより、該開口内に前記第1の電極を露出させる工程と、

前記エッチングによって前記開口内に露出した前記ゲート電極の側面にゲート絶縁膜を形成する工程と、

前記第1の電極、前記ゲート絶縁膜、及び前記第2の電極のそれぞれの上に、酸化物半導体を材料とするチャネルを形成する工程と、

を有することを特徴とする縦型電界効果トランジスタの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−174836(P2012−174836A)

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願番号】特願2011−34330(P2011−34330)

【出願日】平成23年2月21日(2011.2.21)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願日】平成23年2月21日(2011.2.21)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]