耐圧保護回路

【課題】スイッチ素子の耐圧保護回路について、損失を抑制しつつ、設計容易性を向上させること。

【解決手段】耐圧保護回路1は、キャパシタC1、C3と、インダクタL1、L2と、スイッチ素子Q3と、制御回路10と、を備える。キャパシタC1の他方の電極には、直流電源Vinの正極が接続され、キャパシタC1はサージ電圧を吸収する。キャパシタC3の一方の電極には、ダイオードD4を介して直流電源Vinの正極が接続される。キャパシタC1の一方の電極には、インダクタL1を介してキャパシタC3の他方の電極が接続されるとともに、スイッチ素子Q3のドレインが接続される。スイッチ素子Q3のソースには、直流電源Vinの負極が接続され、スイッチ素子Q3のゲートには、制御回路10が接続される。制御回路10は、キャパシタC1の端子間電圧が閾値電圧以上であれば、スイッチ素子Q3をスイッチングさせる。

【解決手段】耐圧保護回路1は、キャパシタC1、C3と、インダクタL1、L2と、スイッチ素子Q3と、制御回路10と、を備える。キャパシタC1の他方の電極には、直流電源Vinの正極が接続され、キャパシタC1はサージ電圧を吸収する。キャパシタC3の一方の電極には、ダイオードD4を介して直流電源Vinの正極が接続される。キャパシタC1の一方の電極には、インダクタL1を介してキャパシタC3の他方の電極が接続されるとともに、スイッチ素子Q3のドレインが接続される。スイッチ素子Q3のソースには、直流電源Vinの負極が接続され、スイッチ素子Q3のゲートには、制御回路10が接続される。制御回路10は、キャパシタC1の端子間電圧が閾値電圧以上であれば、スイッチ素子Q3をスイッチングさせる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、耐圧保護回路に関する。

【背景技術】

【0002】

従来、耐圧保護回路として、スナバ回路が用いられている(例えば、特許文献1参照)。

【0003】

<スイッチング回路BBおよび耐圧保護回路100の構成>

図2は、第1の従来例に係る耐圧保護回路100を備えるスイッチング回路BBの回路図である。スイッチング回路BBは、耐圧保護回路100に加えて、キャパシタC2と、ダイオードD2と、スイッチ素子Q1と、トランスTと、直流電源Vinと、を備える。耐圧保護回路100は、キャパシタC1と、ダイオードD1と、抵抗R1と、を備え、いわゆるスナバ回路を形成する。

【0004】

トランスTは、1次巻線W1および2次巻線W2を備える。

【0005】

1次巻線W1の一端には、直流電源Vinの正極が接続され、1次巻線W1の他端には、IGBT(Insulated Gate Bipolar Transistor)で構成されるスイッチ素子Q1のコレクタが接続される。スイッチ素子Q1のエミッタには、直流電源Vinの負極と、基準電位源GNDと、が接続される。スイッチ素子Q1のコレクタには、ダイオードD1のアノードが接続され、ダイオードD1のカソードには、キャパシタC1を介して直流電源Vinの正極が接続される。キャパシタC1には、抵抗R1が並列接続される。

【0006】

2次巻線W2の一端には、ダイオードD2のアノードが接続され、ダイオードD2のカソードには、出力端子OUT1が接続される。2次巻線W2の他端には、出力端子OUT2が接続される。出力端子OUT1と出力端子OUT2とは、キャパシタC2を介して接続される。

【0007】

<スイッチング回路BBおよび耐圧保護回路100の動作>

以上の構成を備えるスイッチング回路BBは、スイッチ素子Q1をスイッチングさせることで2次巻線W2に起電力を発生させ、ダイオードD2で整流し、キャパシタC2で平滑化して、出力端子OUT1、OUT2から出力する。また、スイッチング回路BBは、スイッチング回路BBに発生するサージ電圧を耐圧保護回路100で吸収して、スイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧を超えてしまうのを防止する。

【0008】

図3は、スイッチング回路BBにおけるスイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1を示す図である。VC1は、キャパシタC1の定格電圧を示し、VVinは、直流電源Vinの電源電圧を示す。

【0009】

時刻t1より前の期間では、図示しない制御部によりスイッチ素子Q1をオフ状態にしている。このため、コレクタ−エミッタ間電圧VCEQ1は、電源電圧VVinと略等しい。

【0010】

時刻t1において、図示しない制御部によりスイッチ素子Q1をオン状態にする。これによれば、コレクタ−エミッタ間電圧VCEQ1は、略ゼロまで低下する。

【0011】

時刻t2において、図示しない制御部によりスイッチ素子Q1をオフ状態にする。これによれば、スイッチング回路BBにサージ電圧が発生し、コレクタ−エミッタ間電圧VCEQ1は、図3の一点鎖線で示すように上昇しようとする。しかしながら、このサージ電圧は、ダイオードD1を介してキャパシタC1に印加され、キャパシタC1に吸収される。このため、コレクタ−エミッタ間電圧VCEQ1は、図3の実線で示すように、電源電圧VVinに定格電圧VC1を加算した電圧より高くはならない。

【0012】

以上によれば、耐圧保護回路100は、スイッチング回路BBに発生するサージ電圧を吸収できる。このため、スイッチ素子Q1にサージ電圧が印加されてしまい、コレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧以上になってしまうのを防止できるので、スイッチ素子Q1を耐圧保護できる。

【0013】

ところで、耐圧保護回路100がサージ電圧を吸収すると、キャパシタC1にエネルギーが蓄積される。このキャパシタC1に蓄積されたエネルギーは、抵抗R1により消費される。このため、耐圧保護回路100の損失が大きくなってしまう。

【0014】

<スイッチング回路CCの構成>

図4は、第2の従来例に係る耐圧保護回路100Aを備えるスイッチング回路CCの回路図である。スイッチング回路CCは、図3に示した第1の従来例に係るスイッチング回路BBとは、耐圧保護回路100の代わりに耐圧保護回路100Aを備える点が異なる。なお、スイッチング回路CCにおいて、スイッチング回路BBと同一構成要件については、同一符号を付し、その説明を省略する。

【0015】

<耐圧保護回路100Aの構成>

耐圧保護回路100Aは、キャパシタC1と、ダイオードD1、D3と、インダクタL1と、PチャネルMOSFETで構成されるスイッチ素子Q2と、抵抗R2、R3と、制御回路110と、を備える。

【0016】

抵抗R2と抵抗R3とは直列接続され、これら抵抗R2、R3を直列接続したものは、キャパシタC1と直流電源Vinとを直列接続したものに、並列接続される。具体的には、キャパシタC1の一方の電極には、抵抗R2の一端が接続され、抵抗R2の他端には、抵抗R3の一端が接続され、抵抗R3の他端には、直流電源Vinの負極が接続される。直流電源Vinの正極には、キャパシタC1の他方の電極が接続される。

【0017】

キャパシタC1の一方の電極には、スイッチ素子Q2のソースも接続される。スイッチ素子Q2のドレインには、インダクタL1の一端と、ダイオードD3のアノードと、が接続される。インダクタL1の他端には、直流電源Vinの正極が接続され、ダイオードD3のカソードには、直流電源Vinの負極が接続される。スイッチ素子Q2のゲートには、抵抗R2の他端および抵抗R3の一端に接続された制御回路110が接続される。

【0018】

<スイッチング回路CCの動作>

以上の構成を備えるスイッチング回路CCは、スイッチング回路BBと同様に、スイッチ素子Q1をスイッチングさせることで2次巻線W2に起電力を発生させ、ダイオードD2で整流し、キャパシタC2で平滑化して、出力端子OUT1、OUT2から出力する。また、スイッチング回路CCは、スイッチング回路BBと同様に、スイッチング回路CCに発生するサージ電圧を耐圧保護回路100Aで吸収して、スイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧を超えてしまうのを防止する。

【0019】

<耐圧保護回路100Aの動作>

まず、制御回路110の動作について説明する。制御回路110には、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧を、抵抗R2、R3で抵抗分割したものが、印加される。制御回路110は、印加された電圧が特定電圧以上である場合には、スイッチ素子Q2をオン状態にし、印加された電圧が特定電圧未満である場合には、スイッチ素子Q2をオフ状態にする。

【0020】

次に、以上の制御回路110を備える耐圧保護回路100Aの動作について説明する。耐圧保護回路100Aは、スイッチング回路CCで発生したサージ電圧をキャパシタC1で吸収して、制御回路110に印加される電圧が予め定められた特定電圧まで上昇すると、以下の2つの手順により、キャパシタC1に蓄積されたエネルギーを直流電源Vinに移動させる。

【0021】

スイッチング回路CCで発生したサージ電圧をキャパシタC1で吸収すると、キャパシタC1にエネルギーが蓄えられ、キャパシタC1の端子間電圧が上昇する。すると、制御回路110に印加される電圧も、キャパシタC1の端子間電圧の上昇に応じて上昇する。

【0022】

制御回路110に印加された電圧が特定電圧まで上昇すると、耐圧保護回路100Aは、まず、第1の手順を行う。第1の手順では、制御回路110がスイッチ素子Q2をオン状態にする。すると、キャパシタC1に蓄積されたエネルギーにより、キャパシタC1の一方の電極から、オン状態のスイッチ素子Q2およびインダクタL1を介して、直流電源Vinの正極に電流が流れる。これによれば、キャパシタC1に蓄積されたエネルギーによりインダクタL1に電流が流れ、キャパシタC1に蓄積されたエネルギーがインダクタL1に移動する。このため、キャパシタC1の端子間電圧が低下し、制御回路110に印加される電圧が低下する。

【0023】

次に、制御回路110に印加される電圧が特定電圧未満まで低下すると、耐圧保護回路100Aは、第2の手順を行う。第2の手順では、制御回路110がスイッチ素子Q2をオフ状態にする。すると、インダクタL1に蓄積されたエネルギーにより、インダクタL1の一端からダイオードD3を介して、直流電源Vinの負極に電流が流れる。これによれば、インダクタL1に蓄積されたエネルギーが直流電源Vinに移動する。

【0024】

以上によれば、耐圧保護回路100Aは、スイッチング回路CCに発生するサージ電圧を吸収して、スイッチ素子Q1を耐圧保護できる。

【0025】

また、耐圧保護回路100Aは、サージ電圧を吸収したことによりキャパシタC1に蓄積されたエネルギーを、直流電源Vinに移動させる。このため、耐圧保護回路100Aの損失を抑制できる。

【先行技術文献】

【特許文献】

【0026】

【特許文献1】特開2000−134907号公報

【発明の概要】

【発明が解決しようとする課題】

【0027】

スイッチ素子Q2のソースは、基準電位源GNDより電位の高いキャパシタC1の一方の電極に接続されている。このため、スイッチ素子Q2は、いわゆるハイサイド側のスイッチ素子である。したがって、スイッチ素子Q2を、PチャネルMOSFETで構成する必要がある。しかしながら、このPチャネルMOSFETは、流通している種類が少ないため、耐圧保護回路100Aの設計容易性を向上させることが困難であった。

【0028】

上述の課題を鑑み、本発明は、スイッチ素子の耐圧保護回路について、損失を抑制しつつ、設計容易性を向上させることを目的とする。

【課題を解決するための手段】

【0029】

本発明は、上述の課題を解決するために、以下の事項を提案している。

(1) 本発明は、サージ電圧を吸収する耐圧保護回路(例えば、図1の耐圧保護回路1に相当)であって、2つの電極のうち低電位側の電極に直流電源(例えば、図1の直流電源Vinに相当)の正極が接続され、前記サージ電圧を吸収する第1キャパシタ(例えば、図1のキャパシタC1に相当)と、前記直流電源の正極に一方の電極が接続された第2キャパシタ(例えば、図1のキャパシタC3に相当)と、前記第1キャパシタの2つの電極のうち高電位側の電極と、前記第2キャパシタの他方の電極と、を接続する第1インダクタ(例えば、図1のインダクタL1に相当)と、前記直流電源に並列接続された第2インダクタ(例えば、図1のインダクタL2に相当)と、前記直流電源の負極に第1端子(例えば、後述のソースに相当)が接続され、前記第2キャパシタの他方の電極に第2端子(例えば、後述のドレインに相当)が接続され、当該第1端子を基準とした制御端子(例えば、後述のゲートに相当)の電圧に応じて当該第1端子と当該第2端子とがオンオフする耐圧保護用スイッチ素子(例えば、図1のスイッチ素子Q3に相当)と、前記第1キャパシタの端子間電圧が予め定められた閾値電圧未満である場合には、前記耐圧保護用スイッチ素子をオフ状態にし、当該第1キャパシタの端子間電圧が当該閾値電圧以上である場合には、当該耐圧保護用スイッチ素子をスイッチングさせる制御手段(例えば、図1の制御回路10に相当)と、を備えることを特徴とする耐圧保護回路を提案している。

【0030】

この発明によれば、第1キャパシタの端子間電圧が閾値電圧未満であれば、耐圧保護用スイッチ素子がオフ状態である。これによれば、第1キャパシタと直流電源とを直列接続したものに、第1インダクタと第2キャパシタと第2インダクタとを直列接続したものが、並列接続されることになる。このため、第2キャパシタが充電され、第2キャパシタの端子間電圧は、第1キャパシタの端子間電圧と、直流電源の電源電圧と、を積算した電圧に、略等しくなる。

【0031】

サージ電圧を第1キャパシタが吸収して、第1キャパシタの端子間電圧が閾値電圧以上になると、耐圧保護用スイッチ素子がスイッチングする。

【0032】

まず、上述のスイッチングにより耐圧保護用スイッチ素子がオン状態である場合について説明する。この場合、第1キャパシタの高電位側の電極から、第1インダクタおよびオン状態の耐圧保護用スイッチ素子を介して、直流電源の負極に電流が流れる。また、第1キャパシタの端子間電圧が閾値電圧未満である期間において充電された第2キャパシタの端子間電圧により、第2インダクタから、第2キャパシタおよびオン状態の耐圧保護用スイッチ素子を介して、直流電源の負極に電流が流れる。以上によれば、第1キャパシタに蓄積されたエネルギーにより、第1インダクタおよび第2インダクタに電流が流れ、第1キャパシタに蓄積されたエネルギーが、第1インダクタおよび第2インダクタに移動し、第1インダクタおよび第2インダクタにエネルギーが蓄積されることとなる。

【0033】

次に、上述のスイッチングにより耐圧保護用スイッチ素子がオフ状態である場合について説明する。この場合、第1インダクタに蓄積されたエネルギーにより、第1インダクタから、第2キャパシタを介して、直流電源の正極に電流が流れる。また、第2インダクタに蓄積されたエネルギーにより、第2インダクタから、直流電源の正極に電流が流れる。以上によれば、第1インダクタおよび第2インダクタに蓄積されたエネルギーにより、第1インダクタおよび第2インダクタから直流電源の正極に電流が流れ、第1インダクタおよび第2インダクタに蓄積されたエネルギーが、直流電源に移動することとなる。

【0034】

以上より、サージ電圧を吸収したことにより第1キャパシタに蓄積されたエネルギーを、直流電源に移動させることができる。このため、耐圧保護回路の損失を低減できる。

【0035】

また、第1端子を基準とした制御端子の電圧に応じてオンオフする耐圧保護用スイッチ素子の第1端子は、直流電源の負極に接続される。このため、耐圧保護用スイッチ素子は、いわゆるローサイド側のスイッチ素子である。したがって、この耐圧保護用スイッチ素子を、上述のスイッチ素子Q2のようにPチャネルMOSFETで構成する必要がない。よって、耐圧保護回路の設計容易性を向上させることができる。

【0036】

(2) 本発明は、(1)の耐圧保護回路について、一端(例えば、後述のアノードに相当)から他端(例えば、後述のカソードに相当)に向かって電流を流す一方向性素子(例えば、図1のダイオードD4に相当)を備え、前記一方向性素子の一端には、前記第2キャパシタの一方の電極と、前記第2インダクタと、が接続され、前記一方向性素子の他端には、前記直流電源の正極が接続されることを特徴とする耐圧保護回路を提案している。

【0037】

この発明によれば、(1)の耐圧保護回路において、一方向性素子を設け、直流電源の正極から第2キャパシタや第2インダクタに電流が流れるのを防止する。このため、第1キャパシタに蓄積されたエネルギーを、第1インダクタおよび第2インダクタに的確に移動させ、第1インダクタおよび第2インダクタに蓄積されたエネルギーを、直流電源に的確に移動させることができる。

【0038】

(3) 本発明は、(1)または(2)の耐圧保護回路について、前記耐圧保護用スイッチ素子は、NチャネルMOSFETであることを特徴とする耐圧保護回路を提案している。

【0039】

ここで、NチャネルMOSFETは、BJT(Bipolar Junction Transistor)といった他のスイッチ素子と比べて、スイッチング速度の速い素子である。そこで、この発明によれば、(1)または(2)の耐圧保護回路において、耐圧保護用スイッチ素子をNチャネルMOSFETで構成することとした。このため、耐圧保護用スイッチ素子のオンオフを、第1キャパシタの端子間電圧の変化に対して迅速に追従させることができ、第1キャパシタと、第1インダクタおよび第2インダクタと、直流電源と、の間でのエネルギーの移動を、さらに的確に行うことができる。

【0040】

(4) 本発明は、(1)〜(3)のいずれかの耐圧保護回路について、第1抵抗(例えば、図1の抵抗R2に相当)と、前記第1抵抗に直列接続された第2抵抗(例えば、図1の抵抗R3に相当)と、を備え、前記第1抵抗と前記第2抵抗とを直列接続したものは、前記第1キャパシタと前記直流電源とを直列接続したものに、並列接続され、前記制御手段は、前記第1抵抗と前記第2抵抗との接続点の電圧が予め定められた規定電圧未満である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧未満であるとして、前記耐圧保護用スイッチ素子をオフ状態にし、前記第1抵抗と前記第2抵抗との接続点の電圧が前記規定電圧以上である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧以上であるとして、前記耐圧保護用スイッチ素子をスイッチングさせることを特徴とする耐圧保護回路を提案している。

【0041】

この発明によれば、(1)〜(3)のいずれかの耐圧保護回路において、第1抵抗と、第1抵抗に直列接続された第2抵抗と、を設け、第1抵抗と第2抵抗とを直列接続したものを、第1キャパシタと直流電源とを直列接続したものに、並列接続することとした。また、制御手段により、第1抵抗と第2抵抗との接続点の電圧が規定電圧未満である場合には、第1キャパシタの端子間電圧が閾値電圧未満であるとして、耐圧保護用スイッチ素子をオフ状態にすることとした。また、制御手段により、第1抵抗と第2抵抗との接続点の電圧が規定電圧以上である場合には、第1キャパシタの端子間電圧が閾値電圧以上であるとして、耐圧保護用スイッチ素子をスイッチングさせることとした。このため、第1キャパシタの高電位側の電極が制御手段に直接接続されている場合と比べて、制御手段に印加される電圧レベルを下げることができる。

【発明の効果】

【0042】

本発明によれば、耐圧保護回路の損失を低減できるとともに、耐圧保護回路の設計容易性を向上させることができる。

【図面の簡単な説明】

【0043】

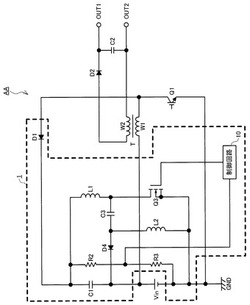

【図1】本発明の一実施形態に係る耐圧保護回路を備えるスイッチング回路の回路図である。

【図2】第1の従来例に係る耐圧保護回路を備えるスイッチング回路の回路図である。

【図3】前記耐圧保護回路の動作を説明するための図である。

【図4】第2の従来例に係る耐圧保護回路を備えるスイッチング回路の回路図である。

【発明を実施するための形態】

【0044】

以下、本発明の実施形態について図面を参照しながら説明する。なお、以下の実施形態における構成要素は適宜、既存の構成要素などとの置き換えが可能であり、また、他の既存の構成要素との組合せを含む様々なバリエーションが可能である。したがって、以下の実施形態の記載をもって、特許請求の範囲に記載された発明の内容を限定するものではない。

【0045】

<スイッチング回路AAの構成>

図1は、本発明の一実施形態に係る耐圧保護回路1を備えるスイッチング回路AAの回路図である。スイッチング回路AAは、図4に示した第2の従来例に係るスイッチング回路CCとは、耐圧保護回路100Aの代わりに耐圧保護回路1を備える点が異なる。なお、スイッチング回路AAにおいて、スイッチング回路CCと同一構成要件については、同一符号を付し、その説明を省略する。

【0046】

<耐圧保護回路1の構成>

耐圧保護回路1は、キャパシタC1、C3と、ダイオードD1、D4と、インダクタL1、L2と、NチャネルMOSFETで構成されるスイッチ素子Q3と、抵抗R2、R3と、制御回路10と、を備える。

【0047】

抵抗R2と抵抗R3とは直列接続され、これら抵抗R2、R3を直列接続したものは、キャパシタC1と直流電源Vinとを直列接続したものに、並列接続される。具体的には、キャパシタC1の一方の電極には、抵抗R2の一端が接続され、抵抗R2の他端には、抵抗R3の一端が接続され、抵抗R3の他端には、直流電源Vinの負極が接続される。直流電源Vinの正極には、キャパシタC1の他方の電極が接続される。

【0048】

キャパシタC1の一方の電極には、インダクタL1の一端も接続される。インダクタL1の他端には、キャパシタC3の他方の電極が接続されるとともに、スイッチ素子Q3のドレインが接続される。

【0049】

直流電源Vinの正極には、ダイオードD4を介してキャパシタC3の一方の電極が接続される。具体的には、直流電源Vinの正極には、ダイオードD4のカソードが接続され、ダイオードD4のアノードには、キャパシタC3の一方の電極が接続される。

【0050】

直流電源Vinには、ダイオードD4を介してインダクタL2が並列接続される。具体的には、直流電源Vinの正極には、ダイオードD4のカソードが接続され、ダイオードD4のアノードには、インダクタL2の一端が接続され、インダクタL2の他端には、直流電源Vinの負極が接続される。

【0051】

スイッチ素子Q3のソースには、直流電源Vinの負極が接続される。スイッチ素子Q3のゲートには、抵抗R2の他端および抵抗R3の一端に接続された制御回路10が接続される。

【0052】

<スイッチング回路AAの動作>

以上の構成を備えるスイッチング回路AAは、スイッチング回路CCと同様に、スイッチ素子Q1をスイッチングさせることで2次巻線W2に起電力を発生させ、ダイオードD2で整流し、キャパシタC2で平滑化して、出力端子OUT1、OUT2から出力する。また、スイッチング回路AAは、スイッチング回路CCと同様に、スイッチング回路AAに発生するサージ電圧を耐圧保護回路1で吸収して、スイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧を超えてしまうのを防止する。

【0053】

<耐圧保護回路1の動作>

まず、制御回路10の動作について説明する。制御回路10には、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧を、抵抗R2、R3で抵抗分割したものが、印加される。制御回路10は、印加された電圧が予め定められた規定電圧未満である場合には、スイッチ素子Q3をオフ状態にし、印加された電圧が規定電圧以上である場合には、予め定められた周波数でスイッチ素子Q3をスイッチングさせる。

【0054】

なお、制御回路10に印加される電圧は、キャパシタC1の端子間電圧に応じて変化することになる。ここで、直流電源Vinの電源電圧VVinが略一定であるとともに、キャパシタC1の端子間電圧が閾値電圧になると、制御回路10に印加される電圧が規定電圧に等しくなるものとすると、制御回路10は、キャパシタC1の端子間電圧が閾値電圧未満である場合には、スイッチ素子Q3をオフ状態にし、キャパシタC1の端子間電圧が閾値電圧以上である場合には、予め定められた周波数でスイッチ素子Q3をスイッチングさせることになる。

【0055】

キャパシタC1の端子間電圧が閾値電圧未満である期間では、制御回路10は、上述のようにスイッチ素子Q3をオフ状態にする。これによれば、キャパシタC1と直流電源Vinとを直列接続したものに、インダクタL1とキャパシタC3とインダクタL2とを直列接続したものが、並列接続されることになる。このため、キャパシタC3が充電され、キャパシタC3の端子間電圧は、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧に略等しくなる。

【0056】

次に、以上の制御回路10を備える耐圧保護回路1の動作について説明する。耐圧保護回路1は、スイッチング回路AAで発生したサージ電圧をキャパシタC1で吸収して、キャパシタC1の端子間電圧が閾値電圧まで上昇すると、スイッチ素子Q3をスイッチングさせて、キャパシタC1に蓄積されたエネルギーを直流電源Vinに移動させる。

【0057】

スイッチング回路AAで発生したサージ電圧をキャパシタC1が吸収すると、キャパシタC1にエネルギーが蓄えられ、キャパシタC1の端子間電圧が上昇する。

【0058】

キャパシタC1の端子間電圧が上述の閾値電圧まで上昇すると、耐圧保護回路1は、制御回路10により、スイッチ素子Q3をスイッチングさせる。

【0059】

上述のスイッチングによりスイッチ素子Q3がオン状態である場合には、キャパシタC1の一方の電極から、インダクタL1およびオン状態のスイッチ素子Q3を介して、直流電源Vinの負極に電流が流れる。また、キャパシタC1の端子間電圧が閾値電圧未満である期間において充電されたキャパシタC3の端子間電圧により、インダクタL2から、キャパシタC3およびオン状態のスイッチ素子Q3を介して、直流電源Vinの負極に電流が流れる。以上によれば、キャパシタC1に蓄積されたエネルギーにより、インダクタL1およびインダクタL2に電流が流れ、キャパシタC1に蓄積されたエネルギーが、インダクタL1およびインダクタL2に移動し、インダクタL1およびインダクタL2にエネルギーが蓄積されることとなる。

【0060】

上述のスイッチングによりスイッチ素子Q3がオフ状態である場合には、インダクタL1に蓄積されたエネルギーにより、インダクタL1から、キャパシタC3およびダイオードD4を介して、直流電源Vinの正極に電流が流れる。また、インダクタL2に蓄積されたエネルギーにより、インダクタL2から、ダイオードD4を介して、直流電源Vinの正極に電流が流れる。以上によれば、インダクタL1およびインダクタL2に蓄積されたエネルギーにより、インダクタL1およびインダクタL2から直流電源Vinの正極に電流が流れ、インダクタL1およびインダクタL2に蓄積されたエネルギーが、直流電源Vinに移動することとなる。

【0061】

以上の耐圧保護回路1によれば、以下の効果を奏することができる。

【0062】

耐圧保護回路1は、スイッチング回路AAでサージ電圧が発生すると、このサージ電圧をキャパシタC1で吸収する。このため、スイッチ素子Q1を耐圧保護できる。

【0063】

また、耐圧保護回路1は、サージ電圧を吸収したことによりキャパシタC1に蓄積されたエネルギーを、直流電源Vinに移動させることができる。このため、耐圧保護回路1の損失を低減できる。

【0064】

また、耐圧保護回路1では、スイッチ素子Q3のソースは、基準電位源GNDに接続される。このため、スイッチ素子Q3は、いわゆるローサイド側のスイッチ素子である。したがって、このスイッチ素子Q3を、図4に示したスイッチ素子Q2のようにPチャネルMOSFETで構成する必要がない。よって、耐圧保護回路1の設計容易性を向上させることができる。

【0065】

また、耐圧保護回路1は、ダイオードD4により、直流電源Vinの正極からキャパシタC3やインダクタL2に電流が流れるのを防止する。このため、キャパシタC1に蓄積されたエネルギーを、インダクタL1およびインダクタL2に的確に移動させ、インダクタL1およびインダクタL2に蓄積されたエネルギーを、直流電源Vinに的確に移動させることができる。

【0066】

また、耐圧保護回路1では、スイッチ素子Q3がNチャネルMOSFETで構成されている。ここで、NチャネルMOSFETは、BJTといった他のスイッチ素子と比べて、スイッチング速度の速い素子である。このため、スイッチ素子Q3のオンオフを、キャパシタC1の端子間電圧の変化に対して迅速に追従させることができ、キャパシタC1と、インダクタL1、L2と、直流電源Vinと、の間でのエネルギーの移動を、さらに的確に行うことができる。

【0067】

また、耐圧保護回路1では、制御回路10に、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧を、抵抗R2、R3で抵抗分割したものが、印加される。このため、制御回路10にキャパシタC1の一方の電極を直接接続した場合、すなわち制御回路10に、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧が印加される場合と比べて、制御回路10に印加される電圧レベルを下げることができる。

【0068】

本発明は、上述の実施形態に限定されるものではなく、この発明の要旨を逸脱しない範囲内で様々な変形や応用が可能である。

【符号の説明】

【0069】

1、100、100A;耐圧保護回路

10、110;制御回路

AA、BB、CC;スイッチング回路

C1〜C3;キャパシタ

D1〜D4;ダイオード

L1、L2;インダクタ

Q1〜Q3;スイッチ素子

R1〜R3;抵抗

T;トランス

Vin;直流電源

【技術分野】

【0001】

本発明は、耐圧保護回路に関する。

【背景技術】

【0002】

従来、耐圧保護回路として、スナバ回路が用いられている(例えば、特許文献1参照)。

【0003】

<スイッチング回路BBおよび耐圧保護回路100の構成>

図2は、第1の従来例に係る耐圧保護回路100を備えるスイッチング回路BBの回路図である。スイッチング回路BBは、耐圧保護回路100に加えて、キャパシタC2と、ダイオードD2と、スイッチ素子Q1と、トランスTと、直流電源Vinと、を備える。耐圧保護回路100は、キャパシタC1と、ダイオードD1と、抵抗R1と、を備え、いわゆるスナバ回路を形成する。

【0004】

トランスTは、1次巻線W1および2次巻線W2を備える。

【0005】

1次巻線W1の一端には、直流電源Vinの正極が接続され、1次巻線W1の他端には、IGBT(Insulated Gate Bipolar Transistor)で構成されるスイッチ素子Q1のコレクタが接続される。スイッチ素子Q1のエミッタには、直流電源Vinの負極と、基準電位源GNDと、が接続される。スイッチ素子Q1のコレクタには、ダイオードD1のアノードが接続され、ダイオードD1のカソードには、キャパシタC1を介して直流電源Vinの正極が接続される。キャパシタC1には、抵抗R1が並列接続される。

【0006】

2次巻線W2の一端には、ダイオードD2のアノードが接続され、ダイオードD2のカソードには、出力端子OUT1が接続される。2次巻線W2の他端には、出力端子OUT2が接続される。出力端子OUT1と出力端子OUT2とは、キャパシタC2を介して接続される。

【0007】

<スイッチング回路BBおよび耐圧保護回路100の動作>

以上の構成を備えるスイッチング回路BBは、スイッチ素子Q1をスイッチングさせることで2次巻線W2に起電力を発生させ、ダイオードD2で整流し、キャパシタC2で平滑化して、出力端子OUT1、OUT2から出力する。また、スイッチング回路BBは、スイッチング回路BBに発生するサージ電圧を耐圧保護回路100で吸収して、スイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧を超えてしまうのを防止する。

【0008】

図3は、スイッチング回路BBにおけるスイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1を示す図である。VC1は、キャパシタC1の定格電圧を示し、VVinは、直流電源Vinの電源電圧を示す。

【0009】

時刻t1より前の期間では、図示しない制御部によりスイッチ素子Q1をオフ状態にしている。このため、コレクタ−エミッタ間電圧VCEQ1は、電源電圧VVinと略等しい。

【0010】

時刻t1において、図示しない制御部によりスイッチ素子Q1をオン状態にする。これによれば、コレクタ−エミッタ間電圧VCEQ1は、略ゼロまで低下する。

【0011】

時刻t2において、図示しない制御部によりスイッチ素子Q1をオフ状態にする。これによれば、スイッチング回路BBにサージ電圧が発生し、コレクタ−エミッタ間電圧VCEQ1は、図3の一点鎖線で示すように上昇しようとする。しかしながら、このサージ電圧は、ダイオードD1を介してキャパシタC1に印加され、キャパシタC1に吸収される。このため、コレクタ−エミッタ間電圧VCEQ1は、図3の実線で示すように、電源電圧VVinに定格電圧VC1を加算した電圧より高くはならない。

【0012】

以上によれば、耐圧保護回路100は、スイッチング回路BBに発生するサージ電圧を吸収できる。このため、スイッチ素子Q1にサージ電圧が印加されてしまい、コレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧以上になってしまうのを防止できるので、スイッチ素子Q1を耐圧保護できる。

【0013】

ところで、耐圧保護回路100がサージ電圧を吸収すると、キャパシタC1にエネルギーが蓄積される。このキャパシタC1に蓄積されたエネルギーは、抵抗R1により消費される。このため、耐圧保護回路100の損失が大きくなってしまう。

【0014】

<スイッチング回路CCの構成>

図4は、第2の従来例に係る耐圧保護回路100Aを備えるスイッチング回路CCの回路図である。スイッチング回路CCは、図3に示した第1の従来例に係るスイッチング回路BBとは、耐圧保護回路100の代わりに耐圧保護回路100Aを備える点が異なる。なお、スイッチング回路CCにおいて、スイッチング回路BBと同一構成要件については、同一符号を付し、その説明を省略する。

【0015】

<耐圧保護回路100Aの構成>

耐圧保護回路100Aは、キャパシタC1と、ダイオードD1、D3と、インダクタL1と、PチャネルMOSFETで構成されるスイッチ素子Q2と、抵抗R2、R3と、制御回路110と、を備える。

【0016】

抵抗R2と抵抗R3とは直列接続され、これら抵抗R2、R3を直列接続したものは、キャパシタC1と直流電源Vinとを直列接続したものに、並列接続される。具体的には、キャパシタC1の一方の電極には、抵抗R2の一端が接続され、抵抗R2の他端には、抵抗R3の一端が接続され、抵抗R3の他端には、直流電源Vinの負極が接続される。直流電源Vinの正極には、キャパシタC1の他方の電極が接続される。

【0017】

キャパシタC1の一方の電極には、スイッチ素子Q2のソースも接続される。スイッチ素子Q2のドレインには、インダクタL1の一端と、ダイオードD3のアノードと、が接続される。インダクタL1の他端には、直流電源Vinの正極が接続され、ダイオードD3のカソードには、直流電源Vinの負極が接続される。スイッチ素子Q2のゲートには、抵抗R2の他端および抵抗R3の一端に接続された制御回路110が接続される。

【0018】

<スイッチング回路CCの動作>

以上の構成を備えるスイッチング回路CCは、スイッチング回路BBと同様に、スイッチ素子Q1をスイッチングさせることで2次巻線W2に起電力を発生させ、ダイオードD2で整流し、キャパシタC2で平滑化して、出力端子OUT1、OUT2から出力する。また、スイッチング回路CCは、スイッチング回路BBと同様に、スイッチング回路CCに発生するサージ電圧を耐圧保護回路100Aで吸収して、スイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧を超えてしまうのを防止する。

【0019】

<耐圧保護回路100Aの動作>

まず、制御回路110の動作について説明する。制御回路110には、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧を、抵抗R2、R3で抵抗分割したものが、印加される。制御回路110は、印加された電圧が特定電圧以上である場合には、スイッチ素子Q2をオン状態にし、印加された電圧が特定電圧未満である場合には、スイッチ素子Q2をオフ状態にする。

【0020】

次に、以上の制御回路110を備える耐圧保護回路100Aの動作について説明する。耐圧保護回路100Aは、スイッチング回路CCで発生したサージ電圧をキャパシタC1で吸収して、制御回路110に印加される電圧が予め定められた特定電圧まで上昇すると、以下の2つの手順により、キャパシタC1に蓄積されたエネルギーを直流電源Vinに移動させる。

【0021】

スイッチング回路CCで発生したサージ電圧をキャパシタC1で吸収すると、キャパシタC1にエネルギーが蓄えられ、キャパシタC1の端子間電圧が上昇する。すると、制御回路110に印加される電圧も、キャパシタC1の端子間電圧の上昇に応じて上昇する。

【0022】

制御回路110に印加された電圧が特定電圧まで上昇すると、耐圧保護回路100Aは、まず、第1の手順を行う。第1の手順では、制御回路110がスイッチ素子Q2をオン状態にする。すると、キャパシタC1に蓄積されたエネルギーにより、キャパシタC1の一方の電極から、オン状態のスイッチ素子Q2およびインダクタL1を介して、直流電源Vinの正極に電流が流れる。これによれば、キャパシタC1に蓄積されたエネルギーによりインダクタL1に電流が流れ、キャパシタC1に蓄積されたエネルギーがインダクタL1に移動する。このため、キャパシタC1の端子間電圧が低下し、制御回路110に印加される電圧が低下する。

【0023】

次に、制御回路110に印加される電圧が特定電圧未満まで低下すると、耐圧保護回路100Aは、第2の手順を行う。第2の手順では、制御回路110がスイッチ素子Q2をオフ状態にする。すると、インダクタL1に蓄積されたエネルギーにより、インダクタL1の一端からダイオードD3を介して、直流電源Vinの負極に電流が流れる。これによれば、インダクタL1に蓄積されたエネルギーが直流電源Vinに移動する。

【0024】

以上によれば、耐圧保護回路100Aは、スイッチング回路CCに発生するサージ電圧を吸収して、スイッチ素子Q1を耐圧保護できる。

【0025】

また、耐圧保護回路100Aは、サージ電圧を吸収したことによりキャパシタC1に蓄積されたエネルギーを、直流電源Vinに移動させる。このため、耐圧保護回路100Aの損失を抑制できる。

【先行技術文献】

【特許文献】

【0026】

【特許文献1】特開2000−134907号公報

【発明の概要】

【発明が解決しようとする課題】

【0027】

スイッチ素子Q2のソースは、基準電位源GNDより電位の高いキャパシタC1の一方の電極に接続されている。このため、スイッチ素子Q2は、いわゆるハイサイド側のスイッチ素子である。したがって、スイッチ素子Q2を、PチャネルMOSFETで構成する必要がある。しかしながら、このPチャネルMOSFETは、流通している種類が少ないため、耐圧保護回路100Aの設計容易性を向上させることが困難であった。

【0028】

上述の課題を鑑み、本発明は、スイッチ素子の耐圧保護回路について、損失を抑制しつつ、設計容易性を向上させることを目的とする。

【課題を解決するための手段】

【0029】

本発明は、上述の課題を解決するために、以下の事項を提案している。

(1) 本発明は、サージ電圧を吸収する耐圧保護回路(例えば、図1の耐圧保護回路1に相当)であって、2つの電極のうち低電位側の電極に直流電源(例えば、図1の直流電源Vinに相当)の正極が接続され、前記サージ電圧を吸収する第1キャパシタ(例えば、図1のキャパシタC1に相当)と、前記直流電源の正極に一方の電極が接続された第2キャパシタ(例えば、図1のキャパシタC3に相当)と、前記第1キャパシタの2つの電極のうち高電位側の電極と、前記第2キャパシタの他方の電極と、を接続する第1インダクタ(例えば、図1のインダクタL1に相当)と、前記直流電源に並列接続された第2インダクタ(例えば、図1のインダクタL2に相当)と、前記直流電源の負極に第1端子(例えば、後述のソースに相当)が接続され、前記第2キャパシタの他方の電極に第2端子(例えば、後述のドレインに相当)が接続され、当該第1端子を基準とした制御端子(例えば、後述のゲートに相当)の電圧に応じて当該第1端子と当該第2端子とがオンオフする耐圧保護用スイッチ素子(例えば、図1のスイッチ素子Q3に相当)と、前記第1キャパシタの端子間電圧が予め定められた閾値電圧未満である場合には、前記耐圧保護用スイッチ素子をオフ状態にし、当該第1キャパシタの端子間電圧が当該閾値電圧以上である場合には、当該耐圧保護用スイッチ素子をスイッチングさせる制御手段(例えば、図1の制御回路10に相当)と、を備えることを特徴とする耐圧保護回路を提案している。

【0030】

この発明によれば、第1キャパシタの端子間電圧が閾値電圧未満であれば、耐圧保護用スイッチ素子がオフ状態である。これによれば、第1キャパシタと直流電源とを直列接続したものに、第1インダクタと第2キャパシタと第2インダクタとを直列接続したものが、並列接続されることになる。このため、第2キャパシタが充電され、第2キャパシタの端子間電圧は、第1キャパシタの端子間電圧と、直流電源の電源電圧と、を積算した電圧に、略等しくなる。

【0031】

サージ電圧を第1キャパシタが吸収して、第1キャパシタの端子間電圧が閾値電圧以上になると、耐圧保護用スイッチ素子がスイッチングする。

【0032】

まず、上述のスイッチングにより耐圧保護用スイッチ素子がオン状態である場合について説明する。この場合、第1キャパシタの高電位側の電極から、第1インダクタおよびオン状態の耐圧保護用スイッチ素子を介して、直流電源の負極に電流が流れる。また、第1キャパシタの端子間電圧が閾値電圧未満である期間において充電された第2キャパシタの端子間電圧により、第2インダクタから、第2キャパシタおよびオン状態の耐圧保護用スイッチ素子を介して、直流電源の負極に電流が流れる。以上によれば、第1キャパシタに蓄積されたエネルギーにより、第1インダクタおよび第2インダクタに電流が流れ、第1キャパシタに蓄積されたエネルギーが、第1インダクタおよび第2インダクタに移動し、第1インダクタおよび第2インダクタにエネルギーが蓄積されることとなる。

【0033】

次に、上述のスイッチングにより耐圧保護用スイッチ素子がオフ状態である場合について説明する。この場合、第1インダクタに蓄積されたエネルギーにより、第1インダクタから、第2キャパシタを介して、直流電源の正極に電流が流れる。また、第2インダクタに蓄積されたエネルギーにより、第2インダクタから、直流電源の正極に電流が流れる。以上によれば、第1インダクタおよび第2インダクタに蓄積されたエネルギーにより、第1インダクタおよび第2インダクタから直流電源の正極に電流が流れ、第1インダクタおよび第2インダクタに蓄積されたエネルギーが、直流電源に移動することとなる。

【0034】

以上より、サージ電圧を吸収したことにより第1キャパシタに蓄積されたエネルギーを、直流電源に移動させることができる。このため、耐圧保護回路の損失を低減できる。

【0035】

また、第1端子を基準とした制御端子の電圧に応じてオンオフする耐圧保護用スイッチ素子の第1端子は、直流電源の負極に接続される。このため、耐圧保護用スイッチ素子は、いわゆるローサイド側のスイッチ素子である。したがって、この耐圧保護用スイッチ素子を、上述のスイッチ素子Q2のようにPチャネルMOSFETで構成する必要がない。よって、耐圧保護回路の設計容易性を向上させることができる。

【0036】

(2) 本発明は、(1)の耐圧保護回路について、一端(例えば、後述のアノードに相当)から他端(例えば、後述のカソードに相当)に向かって電流を流す一方向性素子(例えば、図1のダイオードD4に相当)を備え、前記一方向性素子の一端には、前記第2キャパシタの一方の電極と、前記第2インダクタと、が接続され、前記一方向性素子の他端には、前記直流電源の正極が接続されることを特徴とする耐圧保護回路を提案している。

【0037】

この発明によれば、(1)の耐圧保護回路において、一方向性素子を設け、直流電源の正極から第2キャパシタや第2インダクタに電流が流れるのを防止する。このため、第1キャパシタに蓄積されたエネルギーを、第1インダクタおよび第2インダクタに的確に移動させ、第1インダクタおよび第2インダクタに蓄積されたエネルギーを、直流電源に的確に移動させることができる。

【0038】

(3) 本発明は、(1)または(2)の耐圧保護回路について、前記耐圧保護用スイッチ素子は、NチャネルMOSFETであることを特徴とする耐圧保護回路を提案している。

【0039】

ここで、NチャネルMOSFETは、BJT(Bipolar Junction Transistor)といった他のスイッチ素子と比べて、スイッチング速度の速い素子である。そこで、この発明によれば、(1)または(2)の耐圧保護回路において、耐圧保護用スイッチ素子をNチャネルMOSFETで構成することとした。このため、耐圧保護用スイッチ素子のオンオフを、第1キャパシタの端子間電圧の変化に対して迅速に追従させることができ、第1キャパシタと、第1インダクタおよび第2インダクタと、直流電源と、の間でのエネルギーの移動を、さらに的確に行うことができる。

【0040】

(4) 本発明は、(1)〜(3)のいずれかの耐圧保護回路について、第1抵抗(例えば、図1の抵抗R2に相当)と、前記第1抵抗に直列接続された第2抵抗(例えば、図1の抵抗R3に相当)と、を備え、前記第1抵抗と前記第2抵抗とを直列接続したものは、前記第1キャパシタと前記直流電源とを直列接続したものに、並列接続され、前記制御手段は、前記第1抵抗と前記第2抵抗との接続点の電圧が予め定められた規定電圧未満である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧未満であるとして、前記耐圧保護用スイッチ素子をオフ状態にし、前記第1抵抗と前記第2抵抗との接続点の電圧が前記規定電圧以上である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧以上であるとして、前記耐圧保護用スイッチ素子をスイッチングさせることを特徴とする耐圧保護回路を提案している。

【0041】

この発明によれば、(1)〜(3)のいずれかの耐圧保護回路において、第1抵抗と、第1抵抗に直列接続された第2抵抗と、を設け、第1抵抗と第2抵抗とを直列接続したものを、第1キャパシタと直流電源とを直列接続したものに、並列接続することとした。また、制御手段により、第1抵抗と第2抵抗との接続点の電圧が規定電圧未満である場合には、第1キャパシタの端子間電圧が閾値電圧未満であるとして、耐圧保護用スイッチ素子をオフ状態にすることとした。また、制御手段により、第1抵抗と第2抵抗との接続点の電圧が規定電圧以上である場合には、第1キャパシタの端子間電圧が閾値電圧以上であるとして、耐圧保護用スイッチ素子をスイッチングさせることとした。このため、第1キャパシタの高電位側の電極が制御手段に直接接続されている場合と比べて、制御手段に印加される電圧レベルを下げることができる。

【発明の効果】

【0042】

本発明によれば、耐圧保護回路の損失を低減できるとともに、耐圧保護回路の設計容易性を向上させることができる。

【図面の簡単な説明】

【0043】

【図1】本発明の一実施形態に係る耐圧保護回路を備えるスイッチング回路の回路図である。

【図2】第1の従来例に係る耐圧保護回路を備えるスイッチング回路の回路図である。

【図3】前記耐圧保護回路の動作を説明するための図である。

【図4】第2の従来例に係る耐圧保護回路を備えるスイッチング回路の回路図である。

【発明を実施するための形態】

【0044】

以下、本発明の実施形態について図面を参照しながら説明する。なお、以下の実施形態における構成要素は適宜、既存の構成要素などとの置き換えが可能であり、また、他の既存の構成要素との組合せを含む様々なバリエーションが可能である。したがって、以下の実施形態の記載をもって、特許請求の範囲に記載された発明の内容を限定するものではない。

【0045】

<スイッチング回路AAの構成>

図1は、本発明の一実施形態に係る耐圧保護回路1を備えるスイッチング回路AAの回路図である。スイッチング回路AAは、図4に示した第2の従来例に係るスイッチング回路CCとは、耐圧保護回路100Aの代わりに耐圧保護回路1を備える点が異なる。なお、スイッチング回路AAにおいて、スイッチング回路CCと同一構成要件については、同一符号を付し、その説明を省略する。

【0046】

<耐圧保護回路1の構成>

耐圧保護回路1は、キャパシタC1、C3と、ダイオードD1、D4と、インダクタL1、L2と、NチャネルMOSFETで構成されるスイッチ素子Q3と、抵抗R2、R3と、制御回路10と、を備える。

【0047】

抵抗R2と抵抗R3とは直列接続され、これら抵抗R2、R3を直列接続したものは、キャパシタC1と直流電源Vinとを直列接続したものに、並列接続される。具体的には、キャパシタC1の一方の電極には、抵抗R2の一端が接続され、抵抗R2の他端には、抵抗R3の一端が接続され、抵抗R3の他端には、直流電源Vinの負極が接続される。直流電源Vinの正極には、キャパシタC1の他方の電極が接続される。

【0048】

キャパシタC1の一方の電極には、インダクタL1の一端も接続される。インダクタL1の他端には、キャパシタC3の他方の電極が接続されるとともに、スイッチ素子Q3のドレインが接続される。

【0049】

直流電源Vinの正極には、ダイオードD4を介してキャパシタC3の一方の電極が接続される。具体的には、直流電源Vinの正極には、ダイオードD4のカソードが接続され、ダイオードD4のアノードには、キャパシタC3の一方の電極が接続される。

【0050】

直流電源Vinには、ダイオードD4を介してインダクタL2が並列接続される。具体的には、直流電源Vinの正極には、ダイオードD4のカソードが接続され、ダイオードD4のアノードには、インダクタL2の一端が接続され、インダクタL2の他端には、直流電源Vinの負極が接続される。

【0051】

スイッチ素子Q3のソースには、直流電源Vinの負極が接続される。スイッチ素子Q3のゲートには、抵抗R2の他端および抵抗R3の一端に接続された制御回路10が接続される。

【0052】

<スイッチング回路AAの動作>

以上の構成を備えるスイッチング回路AAは、スイッチング回路CCと同様に、スイッチ素子Q1をスイッチングさせることで2次巻線W2に起電力を発生させ、ダイオードD2で整流し、キャパシタC2で平滑化して、出力端子OUT1、OUT2から出力する。また、スイッチング回路AAは、スイッチング回路CCと同様に、スイッチング回路AAに発生するサージ電圧を耐圧保護回路1で吸収して、スイッチ素子Q1のコレクタ−エミッタ間電圧VCEQ1がスイッチ素子Q1の耐圧を超えてしまうのを防止する。

【0053】

<耐圧保護回路1の動作>

まず、制御回路10の動作について説明する。制御回路10には、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧を、抵抗R2、R3で抵抗分割したものが、印加される。制御回路10は、印加された電圧が予め定められた規定電圧未満である場合には、スイッチ素子Q3をオフ状態にし、印加された電圧が規定電圧以上である場合には、予め定められた周波数でスイッチ素子Q3をスイッチングさせる。

【0054】

なお、制御回路10に印加される電圧は、キャパシタC1の端子間電圧に応じて変化することになる。ここで、直流電源Vinの電源電圧VVinが略一定であるとともに、キャパシタC1の端子間電圧が閾値電圧になると、制御回路10に印加される電圧が規定電圧に等しくなるものとすると、制御回路10は、キャパシタC1の端子間電圧が閾値電圧未満である場合には、スイッチ素子Q3をオフ状態にし、キャパシタC1の端子間電圧が閾値電圧以上である場合には、予め定められた周波数でスイッチ素子Q3をスイッチングさせることになる。

【0055】

キャパシタC1の端子間電圧が閾値電圧未満である期間では、制御回路10は、上述のようにスイッチ素子Q3をオフ状態にする。これによれば、キャパシタC1と直流電源Vinとを直列接続したものに、インダクタL1とキャパシタC3とインダクタL2とを直列接続したものが、並列接続されることになる。このため、キャパシタC3が充電され、キャパシタC3の端子間電圧は、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧に略等しくなる。

【0056】

次に、以上の制御回路10を備える耐圧保護回路1の動作について説明する。耐圧保護回路1は、スイッチング回路AAで発生したサージ電圧をキャパシタC1で吸収して、キャパシタC1の端子間電圧が閾値電圧まで上昇すると、スイッチ素子Q3をスイッチングさせて、キャパシタC1に蓄積されたエネルギーを直流電源Vinに移動させる。

【0057】

スイッチング回路AAで発生したサージ電圧をキャパシタC1が吸収すると、キャパシタC1にエネルギーが蓄えられ、キャパシタC1の端子間電圧が上昇する。

【0058】

キャパシタC1の端子間電圧が上述の閾値電圧まで上昇すると、耐圧保護回路1は、制御回路10により、スイッチ素子Q3をスイッチングさせる。

【0059】

上述のスイッチングによりスイッチ素子Q3がオン状態である場合には、キャパシタC1の一方の電極から、インダクタL1およびオン状態のスイッチ素子Q3を介して、直流電源Vinの負極に電流が流れる。また、キャパシタC1の端子間電圧が閾値電圧未満である期間において充電されたキャパシタC3の端子間電圧により、インダクタL2から、キャパシタC3およびオン状態のスイッチ素子Q3を介して、直流電源Vinの負極に電流が流れる。以上によれば、キャパシタC1に蓄積されたエネルギーにより、インダクタL1およびインダクタL2に電流が流れ、キャパシタC1に蓄積されたエネルギーが、インダクタL1およびインダクタL2に移動し、インダクタL1およびインダクタL2にエネルギーが蓄積されることとなる。

【0060】

上述のスイッチングによりスイッチ素子Q3がオフ状態である場合には、インダクタL1に蓄積されたエネルギーにより、インダクタL1から、キャパシタC3およびダイオードD4を介して、直流電源Vinの正極に電流が流れる。また、インダクタL2に蓄積されたエネルギーにより、インダクタL2から、ダイオードD4を介して、直流電源Vinの正極に電流が流れる。以上によれば、インダクタL1およびインダクタL2に蓄積されたエネルギーにより、インダクタL1およびインダクタL2から直流電源Vinの正極に電流が流れ、インダクタL1およびインダクタL2に蓄積されたエネルギーが、直流電源Vinに移動することとなる。

【0061】

以上の耐圧保護回路1によれば、以下の効果を奏することができる。

【0062】

耐圧保護回路1は、スイッチング回路AAでサージ電圧が発生すると、このサージ電圧をキャパシタC1で吸収する。このため、スイッチ素子Q1を耐圧保護できる。

【0063】

また、耐圧保護回路1は、サージ電圧を吸収したことによりキャパシタC1に蓄積されたエネルギーを、直流電源Vinに移動させることができる。このため、耐圧保護回路1の損失を低減できる。

【0064】

また、耐圧保護回路1では、スイッチ素子Q3のソースは、基準電位源GNDに接続される。このため、スイッチ素子Q3は、いわゆるローサイド側のスイッチ素子である。したがって、このスイッチ素子Q3を、図4に示したスイッチ素子Q2のようにPチャネルMOSFETで構成する必要がない。よって、耐圧保護回路1の設計容易性を向上させることができる。

【0065】

また、耐圧保護回路1は、ダイオードD4により、直流電源Vinの正極からキャパシタC3やインダクタL2に電流が流れるのを防止する。このため、キャパシタC1に蓄積されたエネルギーを、インダクタL1およびインダクタL2に的確に移動させ、インダクタL1およびインダクタL2に蓄積されたエネルギーを、直流電源Vinに的確に移動させることができる。

【0066】

また、耐圧保護回路1では、スイッチ素子Q3がNチャネルMOSFETで構成されている。ここで、NチャネルMOSFETは、BJTといった他のスイッチ素子と比べて、スイッチング速度の速い素子である。このため、スイッチ素子Q3のオンオフを、キャパシタC1の端子間電圧の変化に対して迅速に追従させることができ、キャパシタC1と、インダクタL1、L2と、直流電源Vinと、の間でのエネルギーの移動を、さらに的確に行うことができる。

【0067】

また、耐圧保護回路1では、制御回路10に、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧を、抵抗R2、R3で抵抗分割したものが、印加される。このため、制御回路10にキャパシタC1の一方の電極を直接接続した場合、すなわち制御回路10に、キャパシタC1の端子間電圧と、直流電源Vinの電源電圧VVinと、を積算した電圧が印加される場合と比べて、制御回路10に印加される電圧レベルを下げることができる。

【0068】

本発明は、上述の実施形態に限定されるものではなく、この発明の要旨を逸脱しない範囲内で様々な変形や応用が可能である。

【符号の説明】

【0069】

1、100、100A;耐圧保護回路

10、110;制御回路

AA、BB、CC;スイッチング回路

C1〜C3;キャパシタ

D1〜D4;ダイオード

L1、L2;インダクタ

Q1〜Q3;スイッチ素子

R1〜R3;抵抗

T;トランス

Vin;直流電源

【特許請求の範囲】

【請求項1】

サージ電圧を吸収する耐圧保護回路であって、

2つの電極のうち低電位側の電極に直流電源の正極が接続され、前記サージ電圧を吸収する第1キャパシタと、

前記直流電源の正極に一方の電極が接続された第2キャパシタと、

前記第1キャパシタの2つの電極のうち高電位側の電極と、前記第2キャパシタの他方の電極と、を接続する第1インダクタと、

前記直流電源に並列接続された第2インダクタと、

前記直流電源の負極に第1端子が接続され、前記第2キャパシタの他方の電極に第2端子が接続され、当該第1端子を基準とした制御端子の電圧に応じて当該第1端子と当該第2端子とがオンオフする耐圧保護用スイッチ素子と、

前記第1キャパシタの端子間電圧が予め定められた閾値電圧未満である場合には、前記耐圧保護用スイッチ素子をオフ状態にし、当該第1キャパシタの端子間電圧が当該閾値電圧以上である場合には、当該耐圧保護用スイッチ素子をスイッチングさせる制御手段と、を備えることを特徴とする耐圧保護回路。

【請求項2】

一端から他端に向かって電流を流す一方向性素子を備え、

前記一方向性素子の一端には、前記第2キャパシタの一方の電極と、前記第2インダクタと、が接続され、

前記一方向性素子の他端には、前記直流電源の正極が接続されることを特徴とする請求項1に記載の耐圧保護回路。

【請求項3】

前記耐圧保護用スイッチ素子は、NチャネルMOSFETであることを特徴とする請求項1または2に記載の耐圧保護回路。

【請求項4】

第1抵抗と、

前記第1抵抗に直列接続された第2抵抗と、を備え、

前記第1抵抗と前記第2抵抗とを直列接続したものは、前記第1キャパシタと前記直流電源とを直列接続したものに、並列接続され、

前記制御手段は、

前記第1抵抗と前記第2抵抗との接続点の電圧が予め定められた規定電圧未満である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧未満であるとして、前記耐圧保護用スイッチ素子をオフ状態にし、

前記第1抵抗と前記第2抵抗との接続点の電圧が前記規定電圧以上である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧以上であるとして、前記耐圧保護用スイッチ素子をスイッチングさせることを特徴とする請求項1から3のいずれかに記載の耐圧保護回路。

【請求項1】

サージ電圧を吸収する耐圧保護回路であって、

2つの電極のうち低電位側の電極に直流電源の正極が接続され、前記サージ電圧を吸収する第1キャパシタと、

前記直流電源の正極に一方の電極が接続された第2キャパシタと、

前記第1キャパシタの2つの電極のうち高電位側の電極と、前記第2キャパシタの他方の電極と、を接続する第1インダクタと、

前記直流電源に並列接続された第2インダクタと、

前記直流電源の負極に第1端子が接続され、前記第2キャパシタの他方の電極に第2端子が接続され、当該第1端子を基準とした制御端子の電圧に応じて当該第1端子と当該第2端子とがオンオフする耐圧保護用スイッチ素子と、

前記第1キャパシタの端子間電圧が予め定められた閾値電圧未満である場合には、前記耐圧保護用スイッチ素子をオフ状態にし、当該第1キャパシタの端子間電圧が当該閾値電圧以上である場合には、当該耐圧保護用スイッチ素子をスイッチングさせる制御手段と、を備えることを特徴とする耐圧保護回路。

【請求項2】

一端から他端に向かって電流を流す一方向性素子を備え、

前記一方向性素子の一端には、前記第2キャパシタの一方の電極と、前記第2インダクタと、が接続され、

前記一方向性素子の他端には、前記直流電源の正極が接続されることを特徴とする請求項1に記載の耐圧保護回路。

【請求項3】

前記耐圧保護用スイッチ素子は、NチャネルMOSFETであることを特徴とする請求項1または2に記載の耐圧保護回路。

【請求項4】

第1抵抗と、

前記第1抵抗に直列接続された第2抵抗と、を備え、

前記第1抵抗と前記第2抵抗とを直列接続したものは、前記第1キャパシタと前記直流電源とを直列接続したものに、並列接続され、

前記制御手段は、

前記第1抵抗と前記第2抵抗との接続点の電圧が予め定められた規定電圧未満である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧未満であるとして、前記耐圧保護用スイッチ素子をオフ状態にし、

前記第1抵抗と前記第2抵抗との接続点の電圧が前記規定電圧以上である場合には、前記第1キャパシタの端子間電圧が前記閾値電圧以上であるとして、前記耐圧保護用スイッチ素子をスイッチングさせることを特徴とする請求項1から3のいずれかに記載の耐圧保護回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−85327(P2013−85327A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−221884(P2011−221884)

【出願日】平成23年10月6日(2011.10.6)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月6日(2011.10.6)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

[ Back to top ]