膜厚測定方法

【課題】高い精度の膜厚管理を行いつつ、製品の歩留まり向上及びコスト削減を図ることを目的とする。

【解決手段】透明な半導体基板上に形成された半導体素子に含まれる金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する。

【解決手段】透明な半導体基板上に形成された半導体素子に含まれる金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造工程における膜厚測定方法に関するものである。

【背景技術】

【0002】

半導体素子を製造する工程において、半導体層及び多層配線を基板に対して垂直方向に分離する方法として、中間絶縁層(Inter Layer Dielectric、以下、ILDと称する。)を利用して半導体層と多層配線を分離する方法が知られている。

【0003】

かかるILDは半導体層上に形成されたゲート電極の段差及び配線の段差に起因するカバレージ(すなわち、ゲート電極及び配線の段差表面形状)を滑らかにすることができる。かかる絶縁膜上の高い平坦性を得るために、多層の絶縁膜を形成後にエッチバック処理(すなわち、平坦化工程)を実施している。

【0004】

エッチバック処理後のILDの絶縁膜厚は、その後に形成されるスルーホール長になるため、平坦化工程における膜厚管理は非常に重要な管理項目となっている。ILDの膜厚管理を行う方法としては、半導体層の不純物原子がドープされた領域(以下、活性領域と称する)の絶縁膜厚を光学的に測定する方法が従来から知られている。

【0005】

上述した方法では、以下のような問題点が存在していた。例えば、サファイア基板のような光透過型基板上に半導体層を形成した場合においては、サファイア基板自体が透明であり、且つ、半導体層が数100nmほどの厚みしかないことから、測定に用いる照射光が反射せずに光透過型基板及び半導体層を透過してしまう。ここで、サファイア基板における光透過については図5に示されているように、広範囲の波長領域で光を透過することが確認できる。従って、サファイア基板を代表する光透過型基板を使用した半導体装置においては、活性領域上のILD膜厚を光学的な膜厚測定方法による測定は不可能であった。

【0006】

かかる問題点を解決する方法として、複数のサファイア基板と複数のシリコン基板とを接着剤等で接続し、サファイア基板及びシリコン基板によって形成された基板を1枚の半導体ウエハとし、かかる半導体ウエハ上に半導体層、ILD層を形成して、シリコン基板上に形成された活性領域上のILD膜厚を測定する方法がある。

【0007】

また、光透過型基板における透過光量から膜厚の厚みを相対的に算出する方法が、特許文献1に開示されている。

【特許文献1】特開2004−125470号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、本来の製品(すなわち、サファイア基板を含む半導体装置)として使用されないシリコン基板を1枚の半導体ウエハ内に複数含んでいることから、本来の製品の歩留まりが低下し、且つ、シリコン基板の加工費用も発生することから、本来の製品自体のコストが上昇するという問題点がある。

【0009】

また、本来の製品はサファイア基板を含む半導体装置であることから、従来の方法では本来の製品としての膜厚管理を行っておらず、本来の製品における高い精度の膜厚管理が困難であるという問題点もある。

【0010】

本発明は、以上の如き事情に鑑みてなされたものであり、高い精度の膜厚管理を行いつつ、製品の歩留まり向上及びコスト削減を行うことができる膜厚測定方法を提供する。

【課題を解決するための手段】

【0011】

上述した課題を解決するために、透明な半導体基板、前記半導体基板上に形成されて金属化合物層を含む少なくとも1つの半導体素子及び前記半導体素子を覆う光透過膜からなる半導体装置を測定ステージに載置する載置工程と、前記金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する測定工程と、を有することを特徴とする膜厚測定方法が提供される。

【0012】

また、前記半導体素子は複数であって、前記測定工程においては、前記半導体素子の異なる2つの金属化合物層の各々からの反射光に応じて測定をなしても良い。

【0013】

また、前記金属化合物層の厚みが400nm以上あっても良い。更に、前記半導体素子がFETであって、前記金属化合物層がゲート電極であっても良い。

【発明の効果】

【0014】

透明な半導体基板上に形成された半導体素子に含まれる金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する故、高い精度の膜厚管理を行いつつ、製品の歩留まり向上及びコスト削減を行うことができる。

【発明を実施するための形態】

【0015】

以下、本発明の実施例について添付図面を参照しつつ詳細に説明する。

【実施例】

【0016】

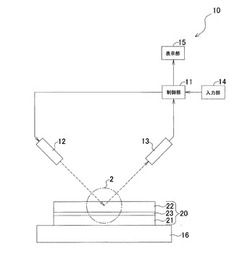

先ず、図1を参照しつつ、本発明の実施例としての膜厚測定方法に使用される膜厚測定装置の一例について詳細に説明する。

【0017】

図1に示されているように、膜厚測定装置10は、例えば、制御部11、制御部11からの指令信号に応じて照射光を照射する光源12及び半導体装置20からの反射光を検出する光検出器13を備えている。また、制御部11には、入力部14が接続されており、入力部14から照射光の照射位置を決定するための半導体装置20の構造データ等のデータを入力することができる。例えば、入力部14はキーボードであっても良い。更に、制御部11には、測定された膜厚データ等を表示するための表示部15が接続されている。光源12及び光検出器13の下方には半導体装置20を載置するための測定ステージ16が設けられている。例えば、測定ステージ16は膜厚測定装置10の固定部材(図示せず)等に固定されていても良い。また、測定ステージ16は、照射光の照射位置決定を容易にするために、位置決め機構(図示せず)によって回転、垂直方向への移動及び水平方向の移動が自在であっても良い。

【0018】

次に、光源12から照射される照射光の照射位置について、図1及び図2を参照しつつ、詳細に説明する。

【0019】

図1に示されているように、例えば、半導体装置20は、透明基板であるサファイア基板21とILD22との間に半導体層23が挟まれた構成である。

【0020】

図2には更に詳細な構造が示されており、約600μmの厚みのサファイア基板上21にシリコン層24、高不純物密度層25a〜25d(以下、いずれかを特定しない場合には、高不純物密度層25と称する)及び低不純物密度層26a〜26d(以下、いずれかを特定しない場合には、低不純物密度層26と称する)によって形成された約100nmの厚みの半導体層23が形成されている。高不純物密度層25a〜25dと高不純物密度層25a〜25dの各々と隣接した低不純物密度層26a〜26dの各々によってソース電極27a、27b(以下、いずれかを特定しない場合には、ソース電極27と称する)又はドレイン電極28a、28b(以下、いずれかを特定しない場合には、ドレイン電極28と称する)が形成されている。具体的には、高不純物密度層25aと低不純物密度層26aとによってソース電極27a、高不純物密度層25bと低不純物密度層26bとによってドレイン電極28a、高不純物密度層25cと低不純物密度層26cとによってソース電極27b、高不純物密度層25dと低不純物密度層26dとによってドレイン電極28bが形成されている。ここで、ソース電極27a及びドレイン電極28aはシリコン層24にホウ素をドープしたp型半導体であり、ソース電極27b及びドレイン電極28bはシリコン層24にリンをドープしたn型半導体である。かかるp型半導体及びn型半導体を1組として、p型半導体及びn型半導体を交互に形成することによって、複数のCMOSが形成されている。なお、高不純物密度層25及び低不純物密度層26を設けることでLDD(Lightly-doped-drain)構造となり、かかるLDD構造を用いることでチャンネル接続部が低濃度となりドレイン近傍での電界の緩和が可能となる。

【0021】

ソース電極27とドレイン電極28との間に位置するシリコン層24上には厚みが数nmのゲート酸化膜29が形成されている。ゲート酸化膜29上には、不純物が高濃度でドープされたポリシリコン層30が形成されている。ポリシリコン層30上には、タングステンシリコン層31が形成されている。タングステンシリコン層31上にはシリコン酸化物からなるキャップ層32が形成されている。また、ゲート酸化膜29、ポリシリコン層30、タングステンシリコン層31及びキャップ層32の周りには、シリコン酸化物からなる側壁層33が形成されている。ゲート酸化膜29、ポリシリコン層30、タングステンシリコン層31、キャップ層32及び側壁層33によって金属化合物層であるゲート電極34が形成されている。例えば、ポリシリコン層30、タングステンシリコン層31及びキャップ層32の各々は、約数100nmの厚みであって、ゲート酸化膜29からキャップ層32までの厚み(すなわち、ゲート構造の段差)は約400〜500nmであっても良い。なお、半導体層22と複数のゲート電極34によってFET(電界効果トランジスタ)である複数の半導体素子が形成されている。

【0022】

半導体層22及びゲート電極34を覆うように約1500nmのILD22が形成されている。例えば、ILD22は、シリコン酸化膜にボロン及びリンを加えた絶縁膜(BPSG:Boron Phosphorus Glass)であっても良い。

【0023】

図2に示されているように、照射光はゲート電極34(すなわち、ゲート電極の最上層に位置するキャップ層32)に照射される。ゲート電極34はその構造上からサファイア基板のように透明ではなく、且つ、その厚みが約400〜500nmであるため、照射光を反射することが可能である。ゲート電極34によって反射された反射光は光検出器13によって検出されることとなる。

【0024】

なお、図2に示された半導体装置20の構造は、SOS(シリコン・オン・サファイア)利用してSOS基板(すなわち、サファイア基板21及びシリコン層24からなる基板)上に半導体素子であるCOMOを集積した構造となっているが、かかる構造に限定されることはない。例えば、サファイア基板21に変えてクォーツ基板を利用してSOQ(シリコン・オン・クォーツ)基板上にCMOSを集積しても良い。また、CMOSの集積に限られず、PMOS又はNMOSのいずれか一方を集積しても良い。更に、半導体装置20は、PMOS又はNMOS等の半導体素子を1つだけ備えていても良い。

【0025】

照射光の照射位置は、ゲート電極34に限られることがなく、シリコンと金属元素からなる化合物層(すんなわち、シリサイド)を含み、所定の厚み(例えば、400nm以上)がある金属化合物層であっても良い。

【0026】

次に、図3を参照しつつ、本発明の実施例としての膜厚測定方法の膜厚測定フローを詳細に説明する。

【0027】

先ず、半導体装置20を測定ステージ16に載置する(ステップS1)。例えば、載置方法としては、ロボットアームの先端に取り付けられた負圧を用いて吸着を行なうチャッカー等を使用して半導体装置20を載置しても良い。また、膜厚測定者が半導体装置20を自らの手で載置しても良い。

【0028】

次に、半導体装置20内の複数あるゲート電極34中から1つを選択し、かかる選択したゲート電極34に光源12からの照射光が照射されるように、光源12及び半導体装置20の位置決めを行う(ステップS2)。本ステップにおいては、あらかじめ制御部11にゲート電極34の配置データである半導体装置20のパターンデータを入力しておき、かかる配置データと載置された半導体装置20のコントラストデータとを比較することで、選択したゲート電極34の位置を正確に把握して位置決めすることができる。なお、位置決めは、光源12及び測定ステージ16を調整することで行われる。

【0029】

位置決めした後、光源12から照射光を照射し(ステップS3)、ゲート電極34からの反射光を光検出器13によって検出する(ステップS4)。光検出器13によって検出された反射光に応じてゲート電極34上のILD22の厚みを演算する(ステップS5)。膜厚の演算方法については、反射光の波長によって演算する方法や、照射光と反射光の位相変化によって演算する方法等の周知の演算方法であって、いずれかの演算方法に限定されることはない。なお、ステップS2からステップS5までを含めて測定工程と称する。

【0030】

ステップS2において位置決めを行ったゲート電極34とは異なるゲート電極34を選択し、再度位置決めを行う(ステップS6)。再位置決め後は、ステップS3からステップS5と同様に位置めさせたゲート電極34に照射光を照射して、ゲート電極34からの反射光を検出して再位置決めされたゲート電極34上のILD22の厚みを演算する(ステップS7、S8、S9)。

【0031】

次に、2つのゲート電圧34上のILD22の厚みの測定結果を平均することで、ゲート電圧34上のILD22の厚みの平均を演算する(ステップS10)。

【0032】

なお、膜厚測定フローにおいては、2つのゲート電圧34上のILD22の厚みの測定を実施しているが、照射光を照射するゲート電圧34の数を増やすことで(すなわち、測定ポイントの増加)、より正確なILD22の厚みを得ることができる。更に、半導体装置20の広範囲におけるゲート電極34上のILD22の厚みを測定することで、ILD22の平坦度の測定も行うことができる。

【0033】

また、試験用のサンプル等を測定する場合には、ゲート電極34を1つしか含まない場合もあるため、そのような場合には、同じゲート電極34において再度位置決めを行い、複数回測定した結果から平均値を演算しても良い。また、ステップS6からステップS10までを省略しても良い。

【0034】

図4は、ゲート電極34上のILD22の厚みとシリコン基板上における活性領域上のILD22の厚みの相関関係を示すグラフである。グラフの横軸はシリコン基板上における活性領域上のILD22の厚みであり、縦軸はゲート電極34上のILD22の厚みである。図4に示されているように、相関係数は0.84であり、両データの相関は十分にあることが判る。かかる相関によって、シリコン基板上における活性領域上のILD22の厚み測定に変えて、本発明の実施例におけるゲート電極34上のILDの厚み測定によってILD22の膜厚管理を行うことができることが判る。

【0035】

以上のように、本実施例による膜厚測定方法によれば、透明な半導体基板上に形成された半導体素子に含まれる金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する故、高い精度の膜厚管理を行いつつ、製品の歩留まり向上及びコスト削減を行うことが可能となる。

【図面の簡単な説明】

【0036】

【図1】本発明の実施例としての膜厚測定方法を実施するため膜厚測定装置の概略構成図である。

【図2】は図1の一点鎖線2によって囲まれた部分の拡大断面図である。

【図3】本発明の実施例としての膜厚測定方法のフローを示したフロー図である。

【図4】ゲート電極上のILDの厚みとシリコン基板上における活性領域上のILDの厚みの相関関係を示したグラフである。

【図5】サファイアの光透過特性を示すグラフである。

【符号の説明】

【0037】

10 膜厚測定装置

11 制御部

12 光源

13 光検出器

16 測定ステージ

20 半導体ウエハ

34 ゲート電極

【技術分野】

【0001】

本発明は、半導体装置の製造工程における膜厚測定方法に関するものである。

【背景技術】

【0002】

半導体素子を製造する工程において、半導体層及び多層配線を基板に対して垂直方向に分離する方法として、中間絶縁層(Inter Layer Dielectric、以下、ILDと称する。)を利用して半導体層と多層配線を分離する方法が知られている。

【0003】

かかるILDは半導体層上に形成されたゲート電極の段差及び配線の段差に起因するカバレージ(すなわち、ゲート電極及び配線の段差表面形状)を滑らかにすることができる。かかる絶縁膜上の高い平坦性を得るために、多層の絶縁膜を形成後にエッチバック処理(すなわち、平坦化工程)を実施している。

【0004】

エッチバック処理後のILDの絶縁膜厚は、その後に形成されるスルーホール長になるため、平坦化工程における膜厚管理は非常に重要な管理項目となっている。ILDの膜厚管理を行う方法としては、半導体層の不純物原子がドープされた領域(以下、活性領域と称する)の絶縁膜厚を光学的に測定する方法が従来から知られている。

【0005】

上述した方法では、以下のような問題点が存在していた。例えば、サファイア基板のような光透過型基板上に半導体層を形成した場合においては、サファイア基板自体が透明であり、且つ、半導体層が数100nmほどの厚みしかないことから、測定に用いる照射光が反射せずに光透過型基板及び半導体層を透過してしまう。ここで、サファイア基板における光透過については図5に示されているように、広範囲の波長領域で光を透過することが確認できる。従って、サファイア基板を代表する光透過型基板を使用した半導体装置においては、活性領域上のILD膜厚を光学的な膜厚測定方法による測定は不可能であった。

【0006】

かかる問題点を解決する方法として、複数のサファイア基板と複数のシリコン基板とを接着剤等で接続し、サファイア基板及びシリコン基板によって形成された基板を1枚の半導体ウエハとし、かかる半導体ウエハ上に半導体層、ILD層を形成して、シリコン基板上に形成された活性領域上のILD膜厚を測定する方法がある。

【0007】

また、光透過型基板における透過光量から膜厚の厚みを相対的に算出する方法が、特許文献1に開示されている。

【特許文献1】特開2004−125470号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、本来の製品(すなわち、サファイア基板を含む半導体装置)として使用されないシリコン基板を1枚の半導体ウエハ内に複数含んでいることから、本来の製品の歩留まりが低下し、且つ、シリコン基板の加工費用も発生することから、本来の製品自体のコストが上昇するという問題点がある。

【0009】

また、本来の製品はサファイア基板を含む半導体装置であることから、従来の方法では本来の製品としての膜厚管理を行っておらず、本来の製品における高い精度の膜厚管理が困難であるという問題点もある。

【0010】

本発明は、以上の如き事情に鑑みてなされたものであり、高い精度の膜厚管理を行いつつ、製品の歩留まり向上及びコスト削減を行うことができる膜厚測定方法を提供する。

【課題を解決するための手段】

【0011】

上述した課題を解決するために、透明な半導体基板、前記半導体基板上に形成されて金属化合物層を含む少なくとも1つの半導体素子及び前記半導体素子を覆う光透過膜からなる半導体装置を測定ステージに載置する載置工程と、前記金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する測定工程と、を有することを特徴とする膜厚測定方法が提供される。

【0012】

また、前記半導体素子は複数であって、前記測定工程においては、前記半導体素子の異なる2つの金属化合物層の各々からの反射光に応じて測定をなしても良い。

【0013】

また、前記金属化合物層の厚みが400nm以上あっても良い。更に、前記半導体素子がFETであって、前記金属化合物層がゲート電極であっても良い。

【発明の効果】

【0014】

透明な半導体基板上に形成された半導体素子に含まれる金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する故、高い精度の膜厚管理を行いつつ、製品の歩留まり向上及びコスト削減を行うことができる。

【発明を実施するための形態】

【0015】

以下、本発明の実施例について添付図面を参照しつつ詳細に説明する。

【実施例】

【0016】

先ず、図1を参照しつつ、本発明の実施例としての膜厚測定方法に使用される膜厚測定装置の一例について詳細に説明する。

【0017】

図1に示されているように、膜厚測定装置10は、例えば、制御部11、制御部11からの指令信号に応じて照射光を照射する光源12及び半導体装置20からの反射光を検出する光検出器13を備えている。また、制御部11には、入力部14が接続されており、入力部14から照射光の照射位置を決定するための半導体装置20の構造データ等のデータを入力することができる。例えば、入力部14はキーボードであっても良い。更に、制御部11には、測定された膜厚データ等を表示するための表示部15が接続されている。光源12及び光検出器13の下方には半導体装置20を載置するための測定ステージ16が設けられている。例えば、測定ステージ16は膜厚測定装置10の固定部材(図示せず)等に固定されていても良い。また、測定ステージ16は、照射光の照射位置決定を容易にするために、位置決め機構(図示せず)によって回転、垂直方向への移動及び水平方向の移動が自在であっても良い。

【0018】

次に、光源12から照射される照射光の照射位置について、図1及び図2を参照しつつ、詳細に説明する。

【0019】

図1に示されているように、例えば、半導体装置20は、透明基板であるサファイア基板21とILD22との間に半導体層23が挟まれた構成である。

【0020】

図2には更に詳細な構造が示されており、約600μmの厚みのサファイア基板上21にシリコン層24、高不純物密度層25a〜25d(以下、いずれかを特定しない場合には、高不純物密度層25と称する)及び低不純物密度層26a〜26d(以下、いずれかを特定しない場合には、低不純物密度層26と称する)によって形成された約100nmの厚みの半導体層23が形成されている。高不純物密度層25a〜25dと高不純物密度層25a〜25dの各々と隣接した低不純物密度層26a〜26dの各々によってソース電極27a、27b(以下、いずれかを特定しない場合には、ソース電極27と称する)又はドレイン電極28a、28b(以下、いずれかを特定しない場合には、ドレイン電極28と称する)が形成されている。具体的には、高不純物密度層25aと低不純物密度層26aとによってソース電極27a、高不純物密度層25bと低不純物密度層26bとによってドレイン電極28a、高不純物密度層25cと低不純物密度層26cとによってソース電極27b、高不純物密度層25dと低不純物密度層26dとによってドレイン電極28bが形成されている。ここで、ソース電極27a及びドレイン電極28aはシリコン層24にホウ素をドープしたp型半導体であり、ソース電極27b及びドレイン電極28bはシリコン層24にリンをドープしたn型半導体である。かかるp型半導体及びn型半導体を1組として、p型半導体及びn型半導体を交互に形成することによって、複数のCMOSが形成されている。なお、高不純物密度層25及び低不純物密度層26を設けることでLDD(Lightly-doped-drain)構造となり、かかるLDD構造を用いることでチャンネル接続部が低濃度となりドレイン近傍での電界の緩和が可能となる。

【0021】

ソース電極27とドレイン電極28との間に位置するシリコン層24上には厚みが数nmのゲート酸化膜29が形成されている。ゲート酸化膜29上には、不純物が高濃度でドープされたポリシリコン層30が形成されている。ポリシリコン層30上には、タングステンシリコン層31が形成されている。タングステンシリコン層31上にはシリコン酸化物からなるキャップ層32が形成されている。また、ゲート酸化膜29、ポリシリコン層30、タングステンシリコン層31及びキャップ層32の周りには、シリコン酸化物からなる側壁層33が形成されている。ゲート酸化膜29、ポリシリコン層30、タングステンシリコン層31、キャップ層32及び側壁層33によって金属化合物層であるゲート電極34が形成されている。例えば、ポリシリコン層30、タングステンシリコン層31及びキャップ層32の各々は、約数100nmの厚みであって、ゲート酸化膜29からキャップ層32までの厚み(すなわち、ゲート構造の段差)は約400〜500nmであっても良い。なお、半導体層22と複数のゲート電極34によってFET(電界効果トランジスタ)である複数の半導体素子が形成されている。

【0022】

半導体層22及びゲート電極34を覆うように約1500nmのILD22が形成されている。例えば、ILD22は、シリコン酸化膜にボロン及びリンを加えた絶縁膜(BPSG:Boron Phosphorus Glass)であっても良い。

【0023】

図2に示されているように、照射光はゲート電極34(すなわち、ゲート電極の最上層に位置するキャップ層32)に照射される。ゲート電極34はその構造上からサファイア基板のように透明ではなく、且つ、その厚みが約400〜500nmであるため、照射光を反射することが可能である。ゲート電極34によって反射された反射光は光検出器13によって検出されることとなる。

【0024】

なお、図2に示された半導体装置20の構造は、SOS(シリコン・オン・サファイア)利用してSOS基板(すなわち、サファイア基板21及びシリコン層24からなる基板)上に半導体素子であるCOMOを集積した構造となっているが、かかる構造に限定されることはない。例えば、サファイア基板21に変えてクォーツ基板を利用してSOQ(シリコン・オン・クォーツ)基板上にCMOSを集積しても良い。また、CMOSの集積に限られず、PMOS又はNMOSのいずれか一方を集積しても良い。更に、半導体装置20は、PMOS又はNMOS等の半導体素子を1つだけ備えていても良い。

【0025】

照射光の照射位置は、ゲート電極34に限られることがなく、シリコンと金属元素からなる化合物層(すんなわち、シリサイド)を含み、所定の厚み(例えば、400nm以上)がある金属化合物層であっても良い。

【0026】

次に、図3を参照しつつ、本発明の実施例としての膜厚測定方法の膜厚測定フローを詳細に説明する。

【0027】

先ず、半導体装置20を測定ステージ16に載置する(ステップS1)。例えば、載置方法としては、ロボットアームの先端に取り付けられた負圧を用いて吸着を行なうチャッカー等を使用して半導体装置20を載置しても良い。また、膜厚測定者が半導体装置20を自らの手で載置しても良い。

【0028】

次に、半導体装置20内の複数あるゲート電極34中から1つを選択し、かかる選択したゲート電極34に光源12からの照射光が照射されるように、光源12及び半導体装置20の位置決めを行う(ステップS2)。本ステップにおいては、あらかじめ制御部11にゲート電極34の配置データである半導体装置20のパターンデータを入力しておき、かかる配置データと載置された半導体装置20のコントラストデータとを比較することで、選択したゲート電極34の位置を正確に把握して位置決めすることができる。なお、位置決めは、光源12及び測定ステージ16を調整することで行われる。

【0029】

位置決めした後、光源12から照射光を照射し(ステップS3)、ゲート電極34からの反射光を光検出器13によって検出する(ステップS4)。光検出器13によって検出された反射光に応じてゲート電極34上のILD22の厚みを演算する(ステップS5)。膜厚の演算方法については、反射光の波長によって演算する方法や、照射光と反射光の位相変化によって演算する方法等の周知の演算方法であって、いずれかの演算方法に限定されることはない。なお、ステップS2からステップS5までを含めて測定工程と称する。

【0030】

ステップS2において位置決めを行ったゲート電極34とは異なるゲート電極34を選択し、再度位置決めを行う(ステップS6)。再位置決め後は、ステップS3からステップS5と同様に位置めさせたゲート電極34に照射光を照射して、ゲート電極34からの反射光を検出して再位置決めされたゲート電極34上のILD22の厚みを演算する(ステップS7、S8、S9)。

【0031】

次に、2つのゲート電圧34上のILD22の厚みの測定結果を平均することで、ゲート電圧34上のILD22の厚みの平均を演算する(ステップS10)。

【0032】

なお、膜厚測定フローにおいては、2つのゲート電圧34上のILD22の厚みの測定を実施しているが、照射光を照射するゲート電圧34の数を増やすことで(すなわち、測定ポイントの増加)、より正確なILD22の厚みを得ることができる。更に、半導体装置20の広範囲におけるゲート電極34上のILD22の厚みを測定することで、ILD22の平坦度の測定も行うことができる。

【0033】

また、試験用のサンプル等を測定する場合には、ゲート電極34を1つしか含まない場合もあるため、そのような場合には、同じゲート電極34において再度位置決めを行い、複数回測定した結果から平均値を演算しても良い。また、ステップS6からステップS10までを省略しても良い。

【0034】

図4は、ゲート電極34上のILD22の厚みとシリコン基板上における活性領域上のILD22の厚みの相関関係を示すグラフである。グラフの横軸はシリコン基板上における活性領域上のILD22の厚みであり、縦軸はゲート電極34上のILD22の厚みである。図4に示されているように、相関係数は0.84であり、両データの相関は十分にあることが判る。かかる相関によって、シリコン基板上における活性領域上のILD22の厚み測定に変えて、本発明の実施例におけるゲート電極34上のILDの厚み測定によってILD22の膜厚管理を行うことができることが判る。

【0035】

以上のように、本実施例による膜厚測定方法によれば、透明な半導体基板上に形成された半導体素子に含まれる金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する故、高い精度の膜厚管理を行いつつ、製品の歩留まり向上及びコスト削減を行うことが可能となる。

【図面の簡単な説明】

【0036】

【図1】本発明の実施例としての膜厚測定方法を実施するため膜厚測定装置の概略構成図である。

【図2】は図1の一点鎖線2によって囲まれた部分の拡大断面図である。

【図3】本発明の実施例としての膜厚測定方法のフローを示したフロー図である。

【図4】ゲート電極上のILDの厚みとシリコン基板上における活性領域上のILDの厚みの相関関係を示したグラフである。

【図5】サファイアの光透過特性を示すグラフである。

【符号の説明】

【0037】

10 膜厚測定装置

11 制御部

12 光源

13 光検出器

16 測定ステージ

20 半導体ウエハ

34 ゲート電極

【特許請求の範囲】

【請求項1】

透明な半導体基板、前記半導体基板上に形成されて金属化合物層を含む少なくとも1つの半導体素子及び前記半導体素子を覆う光透過膜からなる半導体装置を測定ステージに載置する載置工程と、

前記金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する測定工程と、を有することを特徴とする膜厚測定方法。

【請求項2】

前記半導体素子は複数であって、前記測定工程においては、前記半導体素子の異なる2つの金属化合物層の各々からの反射光に応じて測定をなすことを特徴とする請求項1記載の膜厚測定方法。

【請求項3】

前記金属化合物層の厚みが400nm以上であることを特徴とする請求項1又は2記載の膜厚測定方法。

【請求項4】

前記半導体素子がFETであって、前記金属化合物層がゲート電極であることを特徴とする請求項1乃至3のいずれか1に記載の膜厚測定方法。

【請求項1】

透明な半導体基板、前記半導体基板上に形成されて金属化合物層を含む少なくとも1つの半導体素子及び前記半導体素子を覆う光透過膜からなる半導体装置を測定ステージに載置する載置工程と、

前記金属化合層に向けて照射光を照射して、前記金属化合層からの反射光に応じて前記光透過膜の厚みを測定する測定工程と、を有することを特徴とする膜厚測定方法。

【請求項2】

前記半導体素子は複数であって、前記測定工程においては、前記半導体素子の異なる2つの金属化合物層の各々からの反射光に応じて測定をなすことを特徴とする請求項1記載の膜厚測定方法。

【請求項3】

前記金属化合物層の厚みが400nm以上であることを特徴とする請求項1又は2記載の膜厚測定方法。

【請求項4】

前記半導体素子がFETであって、前記金属化合物層がゲート電極であることを特徴とする請求項1乃至3のいずれか1に記載の膜厚測定方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2009−180640(P2009−180640A)

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願番号】特願2008−20622(P2008−20622)

【出願日】平成20年1月31日(2008.1.31)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【出願人】(390008855)OKIセミコンダクタ宮崎株式会社 (151)

【Fターム(参考)】

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願日】平成20年1月31日(2008.1.31)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【出願人】(390008855)OKIセミコンダクタ宮崎株式会社 (151)

【Fターム(参考)】

[ Back to top ]