自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

【発明の詳細な説明】

【技術分野】

【0001】

本実施形態は、半導体構造におけるシリサイド層の形成方法、半導体デバイスの製造方法、および半導体構造物に関する。

【背景技術】

【0002】

半導体構造物およびデバイスは、その構造物の異なる範囲の間で相互接続を形成するために配線層を含むことができる。トレンチとビアのパターンは、配線層を作成するために、絶縁層にパターン化され、金属配線を用いてちりばめられる。シリサイドは、金属配線と半導体構造物の基礎をなすデバイス層との間の電気コンタクトを促進するために、配線層に存在しおよび形成されたビアの底とすることができる。

【0003】

トランジスタを含む半導体構造物は、トランジスタ・ゲートに電位を印加するためのゲート電極構造を持つ。ゲートラスト製造スキームは、ダミーゲートが形成され、トランジスタを形成するのに必要な他のエレメントがダミーゲートのまわりで形成される場合に、ゲートラストの組立てスキームを使用することができる。ダミーゲートは除去され、機能的なゲート構造は、製造プロセスの下流で形成される。機能的なゲート構造の形成は、緻密化(densify)アニーリング(annealing)、窒化後アニーリング、ドライブイン・アニーリングのように、典型的には高温の熱プロセスを要求する。しかしながら、高温プロセスは、シリサイドを含む半導体構造物に存在しえるいくつかの材料へのダメージを引き起こす場合がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−031753号公報

【特許文献2】特開2005−079206号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本実施形態は、半導体構造物におけるシリサイド層の形成方法、半導体デバイスの製造方法、および半導体構造物を提供することを目的とする。

【課題を解決するための手段】

【0006】

第1の実施形態の方法は、自己整合シリサイドを形成するための方法である。第1の実施形態の方法は、初期の半導体構造物を提供する。初期の半導体構造物は、少なくとも一つの不純物領域と、不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、犠牲膜の上に形成された少なくとも一つの絶縁層とを備えた半導体基板を具備する。第1の実施形態の方法は、少なくとも一つの絶縁層にコンタクト開口部を形成し、少なくとも一つの絶縁層の下にある犠牲膜を除去し、少なくとも一つの絶縁層の下にある空隙スペースを残し、空隙スペース内に金属シリサイド前駆体を置き、金属シリサイド前駆体をシリサイド層に変換する。

【0007】

第2の実施形態の方法は、半導体デバイスを製造するための方法である。第2の実施形態の方法は、半導体構造物を提供する。半導体構造物は、半導体基板と、半導体基板上に形成された機能的ゲート構造と、半導体基板上に形成された不純物と、不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、犠牲膜の上に形成された少なくとも一つの絶縁層とを備える。第2の実施形態の方法は、絶縁層上にビア・パターンを、さらに、犠牲膜の上の少なくとも一つの絶縁層にコンタクト開口部をエッチングし、少なくとも一つの絶縁層の下において、犠牲膜を除去して空隙スペースを形成し、空隙スペース内に金属シリサイド前駆体を置き、金属シリサイド前駆体をアニーリングし、金属シリサイド前駆体をシリサイド層に変換する。

【0008】

第3の実施形態の半導体構造物は、機能的なゲート構造と、不純物領域と、シリサイド層と、少なくとも一つの絶縁層とを含む。機能的なゲート構造は、ゲートラストスキームを用いて半導体基板上に形成される。不純物領域は、半導体基板上に形成される。シリサイド層は、不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成され、シリサイドを含む。少なくとも一つの絶縁層は、シリサイド層の上に形成される。少なくとも一つの絶縁層には、ビアおよびコンタクト開口部のパターンが形成される。シリサイド層の面積は、コンタクト開口部の面積より大きい。

【図面の簡単な説明】

【0009】

【図1】図1は、ビアの底に形成されたシリサイド層を持つ半導体構造物を示し、シリサイドは不純物領域の一部を覆う。

【図2】図2は、ビアの底に形成されたシリサイド層を持つ半導体構造物を示し、シリサイドは不純物領域の大部分を覆う。

【図3】図3は、不純物領域の上に形成された犠牲膜を持つ本実施形態の半導体構造物を示す。

【図4】図4は、除去されることで空隙を形成した犠牲膜を持つ本実施形態の半導体構造物を示す。

【図5】図5は、不純物領域の上に形成された金属シリサイド前駆体を持つ本実施形態の半導体構造物を示す。

【図6】図6は、不純物領域の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示す。

【図7】図7は、不純物領域の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示し、シリサイドがビアに形成された金属配線と接触されている。

【図8】図8は、不純物領域の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示し、シリサイドがビアに形成された金属配線と接触されている。

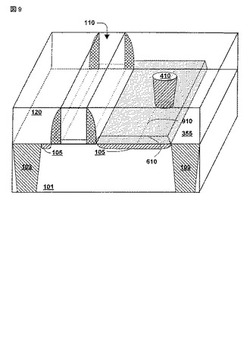

【図9】図9は、不純物領域の大部分の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示し、シリサイド層の面積がシリサイド層を持つ電気コンタクトを生成するビアの面積より大きい。

【図10】図10は、シリサイド層を形成するための典型的な方法論のためのフローチャートを示す。

【発明を実施するための形態】

【0010】

本実施形態は、コンタクト・ビアを通るソース/ドレイン上の自己整合シリサイド(ケイ素化合物)形成に関する。

【0011】

本実施形態において、初期の半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域と、不純物領域および/または付加的な不純物のない基板上の領域の上に形成された犠牲膜と、犠牲膜の上に形成された絶縁層と、絶縁層の上に形成された第2の絶縁層とを備える。ビアは、半導体構造物の第2の絶縁層に、第2の絶縁層の厚さを介してパターン化され、コンタクトの開口部が絶縁層に形成される。次に、絶縁層の下にある犠牲膜の少なくとも一部分は、絶縁層の下の空隙スペースを残して除去される。次に、金属シリサイド前駆体が空隙スペースに配置され、金属シリサイド前駆体はアニーリング処理を通じてシリサイド層へ変換される。

【0012】

電界効果トランジスタは、関連するソースおよびドレイン領域を定義する不純物ドープされたソース/ドレイン領域に対してチャネル中間物を形成することによって、半導体基板上に形成される。チャネルは、ソース/ドレイン領域と異なる導電タイプを持つ。電極は、ソースおよびドレイン領域を持つ電気コンタクトを確立し、ゲート電極は、チャネルを通じて電流を制御するために、チャネル領域へ電界効果ポテンシャルを適用する。半導体製造のゲートラストスキームにおいて、ダミーゲートは、半導体基板上に形成され、これにより、ソース、ドレイン、チャネル領域の自己整合のためにゲート幅を確立する。ソースおよびドレイン領域が作成された後、ダミーゲートは除去され、導電性機能的ゲートの材料に置き換える。

【0013】

シリサイドは、多くの場合、ソースおよびドレインの不純物領域に接触して存在し、それらの領域との電気的接続を促す。シリサイドは、ソースおよびドレイン領域と密着接触して配置されるため、シリサイドは、ダミーゲートの除去に先立って製造プロセスで早く形成できる。しかしながら、機能的なゲート電極の製造で典型的に使用された様々な高温プロセスは、シリサイド材料を、異なるフェーズで再形成または再結晶させることができる。シリサイド材料の再形成は、約400℃未満でのシリサイド材料の形成の後に、約400℃より大きい高温プロセスにさらすことにより生じることができる。シリサイド材料での異なるフェーズの存在の結果、シリサイドの電気抵抗が、望ましくなく増加される場合があり、さらに、シリサイドの構造の欠陥が導かれる場合がある。シリサイド材料への損害を引き起こす場合がある高温プロセスは、緻密化(densify)アニーリング(annealing)、窒化後アニーリング、ドライブイン・アニーリングを含む。

【0014】

高温プロセスによるシリサイド材料への損害を回避するために、シリサイド材料は、機能的なゲート電極の形成の後に導入されることができる。図1は、半導体基板101上に形成されたゲート構造110を持つ半導体構造物を示す。シャロー絶縁トレンチ103は、ソース/ドレイン領域105を持つ隣接するトランジスタ・デバイスを分離する。絶縁層120は、半導体基板101上に形成される。絶縁層は、半導体基板/ウェハの異なる領域間の接続を形成するための金属化された層となるように処理される。ビアとトレンチのパターンは、既知のダマシンおよびデュアルダマシン・プロセスによって金属配線の配置のために絶縁層120に形成されることができる。

【0015】

図1において、ビア130は、ソース/ドレイン領域105と接触するために絶縁層120に形成される。ビア130の形成の後、シリサイド材料140は、ビア130の底で形成されることができ、これによりソース/ドレイン領域105とビア130内に配置される配線との間で、電気的接触を促進する。しかしながら、シリサイド材料140は、ビア130のサイズと等しいソース/ドレイン領域105の小さい領域を覆うのみである。そのため、電気的抵抗率、接触抵抗、および界面抵抗は、シリサイド材料がビアの面積より大きいソース/ドレイン領域の一部分を覆う構造と比較して、増加される。

【0016】

図2は、図1に示される半導体構造物といくつかの構造的特徴を共有する半導体構造物を示す。同じ参照番号は同様の特徴を示す。図2において、ビア230は、ソース/ドレイン領域105の実質的に全体のエリアを覆って示される。そのため、シリサイド材料240は、ソース/ドレイン領域105の実質的に全体の表面の上に配置されることができる。しかしながら、このような大きいサイズのビア230の使用は、付加的なパターンニング、埋め込み(filling)、平坦化(planarization)およびコンタクト形成のステップを必要とし、製造コストを著しく増加させる。さらに、ビア230を埋める配線とゲート構造110との間に発生する短絡の可能性が、大きいビアを使う場合には、急激に増加する。

【0017】

ここに示された実施形態において、方法と構造物は次の特徴を持つとして開示される:1)シリサイド材料は、ダミーゲート電極の除去および機能的ゲート電極の製造後に形成されるため、シリサイド材料は高温プロセスにさらされない。2)シリサイドの面積は、シリサイド材料と接触するビアの面積より大きい。

【0018】

当業者は、デポジティング・マテリアル、マスキング・フォトリトグラフィ、エッチング、インプランティングを含む既知の半導体製造技術が説明されたデバイスまたは構造物を形成するために役立つことを認識するだろう。半導体構造物を形成するための材料のデポジションは、低圧化学蒸着法、化学蒸着法(CVD)、原子層デポジションなどによることができる。明細書中の参照番号は、同じ要素と整合する。

【0019】

「上」「の上」「の下」のようにここで使用される用語は、半導体基板の表面によって定義された面に関して定義される。用語「上」「の上」などは、構成要素が、空間の基準として参照される他の要素よりも半導体基板の面からさらに遠くにあることを示す。用語「の下」および類似の用語は、構成要素が空間基準として参照される他の要素よりも半導体基板の平面に近いことを示す。用語「間に置かれた」「中間の」および類似の用語は、構成要素が、半導体基板の面への距離に関して、空間基準として参照される2つの他の要素の間に位置することを示す。用語「上」「の上」「の下」「間に置かれた」「中間の」などは、相対的な空間的関係のみを示し、いずれの特定の要素についても物理的に接触することを必ずしも示さない。用語「厚さ」は、半導体基板の面に垂直な方角における寸法の特徴を指す。前記の定義は、この文書の全体にわたって適用される。この文書の全体にわたって使用されるように、同様の参考番号は類似構造および特徴を指す。

【0020】

本実施形態を、図を参照して記述する。図3は、半導体基板301上に形成された半導体構造物を示す。本実施形態において、半導体構造物は、その上に形成された側壁(サイドウォール)312を持つ機能的ゲート電極構造310を備え、適切なNまたはP型不純物をドープされたソース/ドレイン領域305を備える。他の実施形態において、ソース/ドレイン領域305は、SiGeおよび/またはSiCを持つとしてもよい。シャロー・トレンチ・アイソレーション(STI)領域303は、同じ基板301上に形成されてもよい隣接するトランジスタ領域を分離する。

【0021】

犠牲膜350は、ソース/ドレイン領域305を形成する半導体基板301の実質的にすべての必要とされるエリア上に存在する。本実施形態において、犠牲膜350は、実質的に、純粋なGe層、または、約50重量%以上の高濃度のGeを含むSiGe層である。他の実施形態において、犠牲膜350は、約50重量%未満の低濃度のGeを含むSiGe層である。さらに他の実施形態において、犠牲膜350は、実質的に、純粋なSi層、または、不純物のドープされたSi層である。犠牲膜350は、取り囲んでいる材料に関して選択的なウェットまたはドライエッチングにより除去できる。犠牲膜350は、エピタクシー成長を含む、いずれかの適切な方法によってソース/ドレイン領域305上に形成することができる。ある実施形態において、犠牲膜の厚みは、約5から約100nmである。他の実施形態において、犠牲膜の厚さは、約15から50nmである。

【0022】

犠牲膜350は、エピタキシャル成長、化学蒸着法、物理蒸着法(physical vapor deposition)、およびめっき法のような、既知の技術で堆積される。特に、エピタキシャル成長技術は、ソース/ドレイン領域305上に犠牲膜350を選択的に堆積することができる。

【0023】

犠牲膜350は、絶縁層355に封じ込められる。絶縁層350は、シリコン酸化物とシリコン窒化物を含むいずれかの適切な絶縁材料を選択することができる。当業者であれば、絶縁層355として他の材料を使用可能であることは理解できるであろう。犠牲膜350は、絶縁層355と比較して、エッチングにより、より大きな割合で選択的に除去される。図3に示されるように、ゲート構造310を含む半導体基板301は、絶縁層360によって覆われる。絶縁層360には、シリコン酸化物、または、シリコン酸化物の誘電率未満の誘電率を持つlow-k材料を用いることができる。

【0024】

図4で、図3に示される構造物は、絶縁層360に形成されたビアおよび/またはトレンチ・パターンを持つように処理される。当業者は、絶縁層360が、そこに形成された任意の適切なトレンチおよび/またはビア・パターンを持つように処理されることができる。ここに示された実施形態の利点を実証する目的で、ビア410は、絶縁層360に形成されて示され、トレンチは例証されていない。ビア410は、プラズマエッチングと反応性イオンエッチングを含む任意の適切な技術を使用して、絶縁層360をエッチングすることにより形成される。ビア410の形成とともに、コンタクト開口部420は絶縁層355に形成される。

【0025】

ビア410およびコンタクト開口部420の形成の後に、実質的な変化がビア410とコンタクト開口部420に発生しないように、犠牲膜350が、適切なエッチングプロセスにより選択的に除去される。ある実施形態において、犠牲膜350は、ウェットエッチングプロセスにより除去される。犠牲膜350が純粋なSi、または、低濃度のGeを持つSiGeから形成される実施形態では、犠牲膜350は、基礎化学物質を含み、約9より大きいpHを持つ水溶液を用いたウェットエッチングによって除去可能である。例えば、水溶液は、アンモニア、テトラメチルアンモニウムヒドロキシド、テトラエチルアンモニウム水酸化物、コリンなどの第4級アミンあるいはアミン基を含む化合物を含むことができる。犠牲膜350が純粋なGe、または、高濃度のGeを持つSiGeから形成される実施形態では、基礎化合物を持つまたは持たない過酸化物を含む水溶液を用いたウェットエッチングによって除去可能である。典型的な過酸化物は、過酸化水素、および過酸化物官能基を含む有機分子を含んでいる。上述されるように、典型的な基礎化合物は、アンモニア、テトラメチルアンモニウムヒドロキシド、テトラエチルアンモニウム水酸化物、コリンなどの第4級アミンおよびアミン基を含む化合物を含む。当業者であれば、犠牲膜350を除去するために、ウェットエッチングのための他の試薬を使用することができることを認識できるだろう。他の実施形態では、犠牲膜はドライ化学エッチングプロセスによって除去される。

【0026】

犠牲フィルム350の選択的な除去の後、空隙スペース430は、絶縁層355のしたに形成される。図4に示される構造物において、ビア410は、コンタクト開口部420および空隙スペース430に導く絶縁層360に形成される。そのため、図4に示される構造物の特徴は、コンタクト開口部420と同様、または、より大きい面積を持つ空隙スペース430にある。図4の例では、空隙スペース430の面積435は、コンタクト開口部420の面積425より大きい。

【0027】

図5に示される構造物において、金属シリサイド前駆体510は、空隙スペース430内に置かれる。典型的な金属シリサイド前駆体は、チタン、コバルト、ニッケル、白金、タングステン、およびそれらの合金から少なくとも1以上を含む。当業者であれば、シリサイドを形成するための前駆体材料として他の金属および合金を使用することができることを認識できるだろう。金属シリサイド前駆体510は、めっき、化学蒸着法および原子層デポジションを含む任意の適切な技術によって空隙スペース430内に置くことができる。金属シリサイド前駆体510のデポジションは、空隙スペース430が適切な厚さを持つ金属シリサイド前駆体で満たされるように実行される。図5に例証されるように、金属シリサイド前駆体は、金属シリサイド前駆体のデポジションとともに、絶縁層360の表面上およびビア410にそって積層される。空隙スペース430の外側のエリアにおける金属シリサイド前駆体材料のデポジションは、デポジションプロセスに付随的であり、ここで説明される利点を達成するために必要ではない。

【0028】

図6において、金属シリサイド前駆体510は、アニーリングプロセスによってシリサイド610に変換される。シリサイドへの金属前駆体の変換のためのアニーリングプロセスは知られている。シリサイド610を形成するシリコン原子は、半導体ウェハ301から始まる。絶縁層360の表面に置かれた金属シリサイド前駆体510は、図6に示される構造物から除かれる。半導体ウェハ301に接触していない金属シリサイド前駆体は、典型的にシリサイドへ変換されない。ウェットエッチングを含む任意の適切な技術が、デポジット後の反応しない金属シリサイド前駆体を除去するために使用されることができる。金属シリサイド前駆体を除去するための薬液は、硫酸と過酸化物との混合物のような酸と過酸化物とを含む混合物や塩酸と硝酸の混合物(王水)のような混合物を含む。金属シリサイド前駆体は、金属シリサイド前駆体がバリア金属または金属配線として使用可能な場合には、除去される必要はない。例えば、シリサイド層の厚さは、約5から約100nmとしてもよい。例えば、シリサイド層の面積は、コンタクト開口部の面積より大きい。例えば、シリサイド層の面積は、コンタクト開口部の面積より少なくとも約30%大きい。このように、シリサイド層の面積をコンタクト開口部の面積より大きくすることにより、電気接触の抵抗値を抑制できる。抵抗値の抑制の程度に応じて、コンタクト開口部の面積とシリサイド層の面積との比は、適宜変更可能である。シリサイド層は、例えば、チタンシリサイド、コバルトシリサイド、ニッケルシリサイド、白金シリサイド、タングステンシリサイド、およびそれらの混合物を含むグループから選択された1以上を含むとしてもよい。

【0029】

図7において、金属配線710は、ビア410内に積層される。金属配線710は、既知のめっき、物理蒸着法、化学蒸着法、ダマシンおよびデュアルダマシン技術を使用して配置されることができる。ある実施形態において、金属配線710は、銅またはタングステンを含む。遷移金属を含む金属バリア層(図示せず)は、絶縁層360から金属配線710を分離するように存在することができ、これにより、絶縁層360への、金属配線710内の、銅のような金属原子の拡散を防ぐ。図8において、金属配線710は、余分な金属材料を除去するために化学機械研磨(CMP)を使用して水平にされ、これにより、最終の金属配線810を形成する。ある実施形態において、金属配線810は銅またはタングステンを含む。

【0030】

図9では、シリサイド層を持つ半導体構造物の特性が例証される。図9において、シリサイド層610は例証の簡素さのために示される。当業者は、典型的な構造物が機能的なゲート電極110の各サイドに隣接して存在する分離のシリサイド層610を持つことを理解するだろう。しかしながら、1つのシリサイド層610が実例の目的のために示されている。ソースまたはドレイン領域として働く不純物領域105は、半導体基板/ウェハ101に埋め込まれて示されている。例証の簡易さのために、絶縁層355の一部は、シリサイド610がよりよく例証されることを可能にするために、切り取って示されている。シリサイド層610は、実質的に全ての不純物領域106を覆っている。ある実施形態において、シリサイド層610は、不純物領域105のエリアの少なくとも約80%を覆う。他の実施形態において、シリサイド層610は、不純物領域105のエリアの少なくとも約90%を覆う。さらに他の実施形態において、不純物領域105のエリアの少なくとも約95%を覆う。

【0031】

シリサイド層610は、金属配線が配置されているまたは配置できるものに、ビア410により接触される。図7−9に示されるように、コンタクトホール420は、シリサイド層360とビア410との間で電気伝達について可能にするために、絶縁層355に存在する。示されるように、ビア410とコンタクトホール420は同様であるが、必ずしも同一サイズではない。

【0032】

ここに開示される実施形態により、図9に示される本実施形態の構造物は、ソース/ドレイン領域105の実質的に全てのエリアの上に形成されたシリサイド層610を持つ。シリサイド層610は、機能的なゲート電極110の製造の後、形成される。ダミーゲート電極を除去し、機能的なゲート電極110を製造する高温プロセスにシリサイド層をさらすことが必要ではないので、より高い抵抗性を持つ異なるフェーズでのシリサイド層の再形成は発生しない。さらに、シリサイド層610と電気的な接触を形成するためのビア410は、ビア410とゲート電極110との間で電気的な短絡を増進するサイズにない。

【0033】

ここで開示された実施形態を十分に説明するために、図10を参照してシリサイド層の形成のステップを説明する。ステップ1002において、初期の半導体構造物は、その上に形成されたソースまたはドレインとして供給するための不純物領域を備えた半導体構造物を持つとして提供される。犠牲膜は、不純物層の上に形成され、絶縁層はさらにこの犠牲膜を覆う。ステップ1004において、ビアとコンタクト開口部は絶縁層に形成される。ステップ1006において、犠牲膜は、絶縁層の下に、空隙スペースを形成するように除去される。ステップ1008において、金属シリサイド前駆体は空隙スペース内に配置される。ステップ1010において、金属シリサイド前駆体材料は、アニーリングプロセスによりシリサイド層へ変換される。

【0034】

上記の本実施形態では、ソース/ドレイン領域に選択的に犠牲膜(例えば高濃度Ge、SiGe、Geなど)を形成しておき、コンタクト開口後に、例えば等方性エッチングなどで犠牲膜のみを除去し、例えば化学蒸着法またはめっきを用いて金属を形成し、ビアより大きいソース/ドレイン領域の範囲に、シリサイド層を形成する。

【0035】

与えられた特徴に対するすべての数字または数範囲に関して、数字またはある範囲からのパラメータは、数範囲を生成するための同じ特徴に対して、他の数字または異なる範囲からのパラメータを結合されてもよい。

【0036】

上記の本実施形態においては、工程の増大を抑制しつつ、コンタクト抵抗の増大を防止することができ、界面抵抗の増大を防止することができる。上記の各種の数値は、このコンタクト抵抗および界面抵抗の増大を適切な範囲で防止可能な範囲で決定することができる。上記の各種の材料は、半導体製造で使用される各種の材料で実現可能であることを表している。

【0037】

ステップの例で、または、別の方法で示された場合を除いて、明細書および特許請求の範囲で使用される、すべての数字、値および/または成分の量を言及する表現、反応条件などは、用語「約」によってすべての実例で修正さえるように理解されるべきである。

【0038】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0039】

301…半導体基板、303…シャロートレンチ絶縁領域、305…ソース/ドレイン領域、310…機能的ゲート電極構造、312…側壁、350…犠牲膜、355…絶縁層、360…絶縁層、410…ビア、420…コンタクト開口部、430…空隙スペース、510…金属シリサイド前駆体、610…シリサイド、710,810…金属配線

【技術分野】

【0001】

本実施形態は、半導体構造におけるシリサイド層の形成方法、半導体デバイスの製造方法、および半導体構造物に関する。

【背景技術】

【0002】

半導体構造物およびデバイスは、その構造物の異なる範囲の間で相互接続を形成するために配線層を含むことができる。トレンチとビアのパターンは、配線層を作成するために、絶縁層にパターン化され、金属配線を用いてちりばめられる。シリサイドは、金属配線と半導体構造物の基礎をなすデバイス層との間の電気コンタクトを促進するために、配線層に存在しおよび形成されたビアの底とすることができる。

【0003】

トランジスタを含む半導体構造物は、トランジスタ・ゲートに電位を印加するためのゲート電極構造を持つ。ゲートラスト製造スキームは、ダミーゲートが形成され、トランジスタを形成するのに必要な他のエレメントがダミーゲートのまわりで形成される場合に、ゲートラストの組立てスキームを使用することができる。ダミーゲートは除去され、機能的なゲート構造は、製造プロセスの下流で形成される。機能的なゲート構造の形成は、緻密化(densify)アニーリング(annealing)、窒化後アニーリング、ドライブイン・アニーリングのように、典型的には高温の熱プロセスを要求する。しかしながら、高温プロセスは、シリサイドを含む半導体構造物に存在しえるいくつかの材料へのダメージを引き起こす場合がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−031753号公報

【特許文献2】特開2005−079206号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本実施形態は、半導体構造物におけるシリサイド層の形成方法、半導体デバイスの製造方法、および半導体構造物を提供することを目的とする。

【課題を解決するための手段】

【0006】

第1の実施形態の方法は、自己整合シリサイドを形成するための方法である。第1の実施形態の方法は、初期の半導体構造物を提供する。初期の半導体構造物は、少なくとも一つの不純物領域と、不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、犠牲膜の上に形成された少なくとも一つの絶縁層とを備えた半導体基板を具備する。第1の実施形態の方法は、少なくとも一つの絶縁層にコンタクト開口部を形成し、少なくとも一つの絶縁層の下にある犠牲膜を除去し、少なくとも一つの絶縁層の下にある空隙スペースを残し、空隙スペース内に金属シリサイド前駆体を置き、金属シリサイド前駆体をシリサイド層に変換する。

【0007】

第2の実施形態の方法は、半導体デバイスを製造するための方法である。第2の実施形態の方法は、半導体構造物を提供する。半導体構造物は、半導体基板と、半導体基板上に形成された機能的ゲート構造と、半導体基板上に形成された不純物と、不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、犠牲膜の上に形成された少なくとも一つの絶縁層とを備える。第2の実施形態の方法は、絶縁層上にビア・パターンを、さらに、犠牲膜の上の少なくとも一つの絶縁層にコンタクト開口部をエッチングし、少なくとも一つの絶縁層の下において、犠牲膜を除去して空隙スペースを形成し、空隙スペース内に金属シリサイド前駆体を置き、金属シリサイド前駆体をアニーリングし、金属シリサイド前駆体をシリサイド層に変換する。

【0008】

第3の実施形態の半導体構造物は、機能的なゲート構造と、不純物領域と、シリサイド層と、少なくとも一つの絶縁層とを含む。機能的なゲート構造は、ゲートラストスキームを用いて半導体基板上に形成される。不純物領域は、半導体基板上に形成される。シリサイド層は、不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成され、シリサイドを含む。少なくとも一つの絶縁層は、シリサイド層の上に形成される。少なくとも一つの絶縁層には、ビアおよびコンタクト開口部のパターンが形成される。シリサイド層の面積は、コンタクト開口部の面積より大きい。

【図面の簡単な説明】

【0009】

【図1】図1は、ビアの底に形成されたシリサイド層を持つ半導体構造物を示し、シリサイドは不純物領域の一部を覆う。

【図2】図2は、ビアの底に形成されたシリサイド層を持つ半導体構造物を示し、シリサイドは不純物領域の大部分を覆う。

【図3】図3は、不純物領域の上に形成された犠牲膜を持つ本実施形態の半導体構造物を示す。

【図4】図4は、除去されることで空隙を形成した犠牲膜を持つ本実施形態の半導体構造物を示す。

【図5】図5は、不純物領域の上に形成された金属シリサイド前駆体を持つ本実施形態の半導体構造物を示す。

【図6】図6は、不純物領域の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示す。

【図7】図7は、不純物領域の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示し、シリサイドがビアに形成された金属配線と接触されている。

【図8】図8は、不純物領域の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示し、シリサイドがビアに形成された金属配線と接触されている。

【図9】図9は、不純物領域の大部分の上に形成されたシリサイド層を持つ本実施形態の半導体構造物を示し、シリサイド層の面積がシリサイド層を持つ電気コンタクトを生成するビアの面積より大きい。

【図10】図10は、シリサイド層を形成するための典型的な方法論のためのフローチャートを示す。

【発明を実施するための形態】

【0010】

本実施形態は、コンタクト・ビアを通るソース/ドレイン上の自己整合シリサイド(ケイ素化合物)形成に関する。

【0011】

本実施形態において、初期の半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域と、不純物領域および/または付加的な不純物のない基板上の領域の上に形成された犠牲膜と、犠牲膜の上に形成された絶縁層と、絶縁層の上に形成された第2の絶縁層とを備える。ビアは、半導体構造物の第2の絶縁層に、第2の絶縁層の厚さを介してパターン化され、コンタクトの開口部が絶縁層に形成される。次に、絶縁層の下にある犠牲膜の少なくとも一部分は、絶縁層の下の空隙スペースを残して除去される。次に、金属シリサイド前駆体が空隙スペースに配置され、金属シリサイド前駆体はアニーリング処理を通じてシリサイド層へ変換される。

【0012】

電界効果トランジスタは、関連するソースおよびドレイン領域を定義する不純物ドープされたソース/ドレイン領域に対してチャネル中間物を形成することによって、半導体基板上に形成される。チャネルは、ソース/ドレイン領域と異なる導電タイプを持つ。電極は、ソースおよびドレイン領域を持つ電気コンタクトを確立し、ゲート電極は、チャネルを通じて電流を制御するために、チャネル領域へ電界効果ポテンシャルを適用する。半導体製造のゲートラストスキームにおいて、ダミーゲートは、半導体基板上に形成され、これにより、ソース、ドレイン、チャネル領域の自己整合のためにゲート幅を確立する。ソースおよびドレイン領域が作成された後、ダミーゲートは除去され、導電性機能的ゲートの材料に置き換える。

【0013】

シリサイドは、多くの場合、ソースおよびドレインの不純物領域に接触して存在し、それらの領域との電気的接続を促す。シリサイドは、ソースおよびドレイン領域と密着接触して配置されるため、シリサイドは、ダミーゲートの除去に先立って製造プロセスで早く形成できる。しかしながら、機能的なゲート電極の製造で典型的に使用された様々な高温プロセスは、シリサイド材料を、異なるフェーズで再形成または再結晶させることができる。シリサイド材料の再形成は、約400℃未満でのシリサイド材料の形成の後に、約400℃より大きい高温プロセスにさらすことにより生じることができる。シリサイド材料での異なるフェーズの存在の結果、シリサイドの電気抵抗が、望ましくなく増加される場合があり、さらに、シリサイドの構造の欠陥が導かれる場合がある。シリサイド材料への損害を引き起こす場合がある高温プロセスは、緻密化(densify)アニーリング(annealing)、窒化後アニーリング、ドライブイン・アニーリングを含む。

【0014】

高温プロセスによるシリサイド材料への損害を回避するために、シリサイド材料は、機能的なゲート電極の形成の後に導入されることができる。図1は、半導体基板101上に形成されたゲート構造110を持つ半導体構造物を示す。シャロー絶縁トレンチ103は、ソース/ドレイン領域105を持つ隣接するトランジスタ・デバイスを分離する。絶縁層120は、半導体基板101上に形成される。絶縁層は、半導体基板/ウェハの異なる領域間の接続を形成するための金属化された層となるように処理される。ビアとトレンチのパターンは、既知のダマシンおよびデュアルダマシン・プロセスによって金属配線の配置のために絶縁層120に形成されることができる。

【0015】

図1において、ビア130は、ソース/ドレイン領域105と接触するために絶縁層120に形成される。ビア130の形成の後、シリサイド材料140は、ビア130の底で形成されることができ、これによりソース/ドレイン領域105とビア130内に配置される配線との間で、電気的接触を促進する。しかしながら、シリサイド材料140は、ビア130のサイズと等しいソース/ドレイン領域105の小さい領域を覆うのみである。そのため、電気的抵抗率、接触抵抗、および界面抵抗は、シリサイド材料がビアの面積より大きいソース/ドレイン領域の一部分を覆う構造と比較して、増加される。

【0016】

図2は、図1に示される半導体構造物といくつかの構造的特徴を共有する半導体構造物を示す。同じ参照番号は同様の特徴を示す。図2において、ビア230は、ソース/ドレイン領域105の実質的に全体のエリアを覆って示される。そのため、シリサイド材料240は、ソース/ドレイン領域105の実質的に全体の表面の上に配置されることができる。しかしながら、このような大きいサイズのビア230の使用は、付加的なパターンニング、埋め込み(filling)、平坦化(planarization)およびコンタクト形成のステップを必要とし、製造コストを著しく増加させる。さらに、ビア230を埋める配線とゲート構造110との間に発生する短絡の可能性が、大きいビアを使う場合には、急激に増加する。

【0017】

ここに示された実施形態において、方法と構造物は次の特徴を持つとして開示される:1)シリサイド材料は、ダミーゲート電極の除去および機能的ゲート電極の製造後に形成されるため、シリサイド材料は高温プロセスにさらされない。2)シリサイドの面積は、シリサイド材料と接触するビアの面積より大きい。

【0018】

当業者は、デポジティング・マテリアル、マスキング・フォトリトグラフィ、エッチング、インプランティングを含む既知の半導体製造技術が説明されたデバイスまたは構造物を形成するために役立つことを認識するだろう。半導体構造物を形成するための材料のデポジションは、低圧化学蒸着法、化学蒸着法(CVD)、原子層デポジションなどによることができる。明細書中の参照番号は、同じ要素と整合する。

【0019】

「上」「の上」「の下」のようにここで使用される用語は、半導体基板の表面によって定義された面に関して定義される。用語「上」「の上」などは、構成要素が、空間の基準として参照される他の要素よりも半導体基板の面からさらに遠くにあることを示す。用語「の下」および類似の用語は、構成要素が空間基準として参照される他の要素よりも半導体基板の平面に近いことを示す。用語「間に置かれた」「中間の」および類似の用語は、構成要素が、半導体基板の面への距離に関して、空間基準として参照される2つの他の要素の間に位置することを示す。用語「上」「の上」「の下」「間に置かれた」「中間の」などは、相対的な空間的関係のみを示し、いずれの特定の要素についても物理的に接触することを必ずしも示さない。用語「厚さ」は、半導体基板の面に垂直な方角における寸法の特徴を指す。前記の定義は、この文書の全体にわたって適用される。この文書の全体にわたって使用されるように、同様の参考番号は類似構造および特徴を指す。

【0020】

本実施形態を、図を参照して記述する。図3は、半導体基板301上に形成された半導体構造物を示す。本実施形態において、半導体構造物は、その上に形成された側壁(サイドウォール)312を持つ機能的ゲート電極構造310を備え、適切なNまたはP型不純物をドープされたソース/ドレイン領域305を備える。他の実施形態において、ソース/ドレイン領域305は、SiGeおよび/またはSiCを持つとしてもよい。シャロー・トレンチ・アイソレーション(STI)領域303は、同じ基板301上に形成されてもよい隣接するトランジスタ領域を分離する。

【0021】

犠牲膜350は、ソース/ドレイン領域305を形成する半導体基板301の実質的にすべての必要とされるエリア上に存在する。本実施形態において、犠牲膜350は、実質的に、純粋なGe層、または、約50重量%以上の高濃度のGeを含むSiGe層である。他の実施形態において、犠牲膜350は、約50重量%未満の低濃度のGeを含むSiGe層である。さらに他の実施形態において、犠牲膜350は、実質的に、純粋なSi層、または、不純物のドープされたSi層である。犠牲膜350は、取り囲んでいる材料に関して選択的なウェットまたはドライエッチングにより除去できる。犠牲膜350は、エピタクシー成長を含む、いずれかの適切な方法によってソース/ドレイン領域305上に形成することができる。ある実施形態において、犠牲膜の厚みは、約5から約100nmである。他の実施形態において、犠牲膜の厚さは、約15から50nmである。

【0022】

犠牲膜350は、エピタキシャル成長、化学蒸着法、物理蒸着法(physical vapor deposition)、およびめっき法のような、既知の技術で堆積される。特に、エピタキシャル成長技術は、ソース/ドレイン領域305上に犠牲膜350を選択的に堆積することができる。

【0023】

犠牲膜350は、絶縁層355に封じ込められる。絶縁層350は、シリコン酸化物とシリコン窒化物を含むいずれかの適切な絶縁材料を選択することができる。当業者であれば、絶縁層355として他の材料を使用可能であることは理解できるであろう。犠牲膜350は、絶縁層355と比較して、エッチングにより、より大きな割合で選択的に除去される。図3に示されるように、ゲート構造310を含む半導体基板301は、絶縁層360によって覆われる。絶縁層360には、シリコン酸化物、または、シリコン酸化物の誘電率未満の誘電率を持つlow-k材料を用いることができる。

【0024】

図4で、図3に示される構造物は、絶縁層360に形成されたビアおよび/またはトレンチ・パターンを持つように処理される。当業者は、絶縁層360が、そこに形成された任意の適切なトレンチおよび/またはビア・パターンを持つように処理されることができる。ここに示された実施形態の利点を実証する目的で、ビア410は、絶縁層360に形成されて示され、トレンチは例証されていない。ビア410は、プラズマエッチングと反応性イオンエッチングを含む任意の適切な技術を使用して、絶縁層360をエッチングすることにより形成される。ビア410の形成とともに、コンタクト開口部420は絶縁層355に形成される。

【0025】

ビア410およびコンタクト開口部420の形成の後に、実質的な変化がビア410とコンタクト開口部420に発生しないように、犠牲膜350が、適切なエッチングプロセスにより選択的に除去される。ある実施形態において、犠牲膜350は、ウェットエッチングプロセスにより除去される。犠牲膜350が純粋なSi、または、低濃度のGeを持つSiGeから形成される実施形態では、犠牲膜350は、基礎化学物質を含み、約9より大きいpHを持つ水溶液を用いたウェットエッチングによって除去可能である。例えば、水溶液は、アンモニア、テトラメチルアンモニウムヒドロキシド、テトラエチルアンモニウム水酸化物、コリンなどの第4級アミンあるいはアミン基を含む化合物を含むことができる。犠牲膜350が純粋なGe、または、高濃度のGeを持つSiGeから形成される実施形態では、基礎化合物を持つまたは持たない過酸化物を含む水溶液を用いたウェットエッチングによって除去可能である。典型的な過酸化物は、過酸化水素、および過酸化物官能基を含む有機分子を含んでいる。上述されるように、典型的な基礎化合物は、アンモニア、テトラメチルアンモニウムヒドロキシド、テトラエチルアンモニウム水酸化物、コリンなどの第4級アミンおよびアミン基を含む化合物を含む。当業者であれば、犠牲膜350を除去するために、ウェットエッチングのための他の試薬を使用することができることを認識できるだろう。他の実施形態では、犠牲膜はドライ化学エッチングプロセスによって除去される。

【0026】

犠牲フィルム350の選択的な除去の後、空隙スペース430は、絶縁層355のしたに形成される。図4に示される構造物において、ビア410は、コンタクト開口部420および空隙スペース430に導く絶縁層360に形成される。そのため、図4に示される構造物の特徴は、コンタクト開口部420と同様、または、より大きい面積を持つ空隙スペース430にある。図4の例では、空隙スペース430の面積435は、コンタクト開口部420の面積425より大きい。

【0027】

図5に示される構造物において、金属シリサイド前駆体510は、空隙スペース430内に置かれる。典型的な金属シリサイド前駆体は、チタン、コバルト、ニッケル、白金、タングステン、およびそれらの合金から少なくとも1以上を含む。当業者であれば、シリサイドを形成するための前駆体材料として他の金属および合金を使用することができることを認識できるだろう。金属シリサイド前駆体510は、めっき、化学蒸着法および原子層デポジションを含む任意の適切な技術によって空隙スペース430内に置くことができる。金属シリサイド前駆体510のデポジションは、空隙スペース430が適切な厚さを持つ金属シリサイド前駆体で満たされるように実行される。図5に例証されるように、金属シリサイド前駆体は、金属シリサイド前駆体のデポジションとともに、絶縁層360の表面上およびビア410にそって積層される。空隙スペース430の外側のエリアにおける金属シリサイド前駆体材料のデポジションは、デポジションプロセスに付随的であり、ここで説明される利点を達成するために必要ではない。

【0028】

図6において、金属シリサイド前駆体510は、アニーリングプロセスによってシリサイド610に変換される。シリサイドへの金属前駆体の変換のためのアニーリングプロセスは知られている。シリサイド610を形成するシリコン原子は、半導体ウェハ301から始まる。絶縁層360の表面に置かれた金属シリサイド前駆体510は、図6に示される構造物から除かれる。半導体ウェハ301に接触していない金属シリサイド前駆体は、典型的にシリサイドへ変換されない。ウェットエッチングを含む任意の適切な技術が、デポジット後の反応しない金属シリサイド前駆体を除去するために使用されることができる。金属シリサイド前駆体を除去するための薬液は、硫酸と過酸化物との混合物のような酸と過酸化物とを含む混合物や塩酸と硝酸の混合物(王水)のような混合物を含む。金属シリサイド前駆体は、金属シリサイド前駆体がバリア金属または金属配線として使用可能な場合には、除去される必要はない。例えば、シリサイド層の厚さは、約5から約100nmとしてもよい。例えば、シリサイド層の面積は、コンタクト開口部の面積より大きい。例えば、シリサイド層の面積は、コンタクト開口部の面積より少なくとも約30%大きい。このように、シリサイド層の面積をコンタクト開口部の面積より大きくすることにより、電気接触の抵抗値を抑制できる。抵抗値の抑制の程度に応じて、コンタクト開口部の面積とシリサイド層の面積との比は、適宜変更可能である。シリサイド層は、例えば、チタンシリサイド、コバルトシリサイド、ニッケルシリサイド、白金シリサイド、タングステンシリサイド、およびそれらの混合物を含むグループから選択された1以上を含むとしてもよい。

【0029】

図7において、金属配線710は、ビア410内に積層される。金属配線710は、既知のめっき、物理蒸着法、化学蒸着法、ダマシンおよびデュアルダマシン技術を使用して配置されることができる。ある実施形態において、金属配線710は、銅またはタングステンを含む。遷移金属を含む金属バリア層(図示せず)は、絶縁層360から金属配線710を分離するように存在することができ、これにより、絶縁層360への、金属配線710内の、銅のような金属原子の拡散を防ぐ。図8において、金属配線710は、余分な金属材料を除去するために化学機械研磨(CMP)を使用して水平にされ、これにより、最終の金属配線810を形成する。ある実施形態において、金属配線810は銅またはタングステンを含む。

【0030】

図9では、シリサイド層を持つ半導体構造物の特性が例証される。図9において、シリサイド層610は例証の簡素さのために示される。当業者は、典型的な構造物が機能的なゲート電極110の各サイドに隣接して存在する分離のシリサイド層610を持つことを理解するだろう。しかしながら、1つのシリサイド層610が実例の目的のために示されている。ソースまたはドレイン領域として働く不純物領域105は、半導体基板/ウェハ101に埋め込まれて示されている。例証の簡易さのために、絶縁層355の一部は、シリサイド610がよりよく例証されることを可能にするために、切り取って示されている。シリサイド層610は、実質的に全ての不純物領域106を覆っている。ある実施形態において、シリサイド層610は、不純物領域105のエリアの少なくとも約80%を覆う。他の実施形態において、シリサイド層610は、不純物領域105のエリアの少なくとも約90%を覆う。さらに他の実施形態において、不純物領域105のエリアの少なくとも約95%を覆う。

【0031】

シリサイド層610は、金属配線が配置されているまたは配置できるものに、ビア410により接触される。図7−9に示されるように、コンタクトホール420は、シリサイド層360とビア410との間で電気伝達について可能にするために、絶縁層355に存在する。示されるように、ビア410とコンタクトホール420は同様であるが、必ずしも同一サイズではない。

【0032】

ここに開示される実施形態により、図9に示される本実施形態の構造物は、ソース/ドレイン領域105の実質的に全てのエリアの上に形成されたシリサイド層610を持つ。シリサイド層610は、機能的なゲート電極110の製造の後、形成される。ダミーゲート電極を除去し、機能的なゲート電極110を製造する高温プロセスにシリサイド層をさらすことが必要ではないので、より高い抵抗性を持つ異なるフェーズでのシリサイド層の再形成は発生しない。さらに、シリサイド層610と電気的な接触を形成するためのビア410は、ビア410とゲート電極110との間で電気的な短絡を増進するサイズにない。

【0033】

ここで開示された実施形態を十分に説明するために、図10を参照してシリサイド層の形成のステップを説明する。ステップ1002において、初期の半導体構造物は、その上に形成されたソースまたはドレインとして供給するための不純物領域を備えた半導体構造物を持つとして提供される。犠牲膜は、不純物層の上に形成され、絶縁層はさらにこの犠牲膜を覆う。ステップ1004において、ビアとコンタクト開口部は絶縁層に形成される。ステップ1006において、犠牲膜は、絶縁層の下に、空隙スペースを形成するように除去される。ステップ1008において、金属シリサイド前駆体は空隙スペース内に配置される。ステップ1010において、金属シリサイド前駆体材料は、アニーリングプロセスによりシリサイド層へ変換される。

【0034】

上記の本実施形態では、ソース/ドレイン領域に選択的に犠牲膜(例えば高濃度Ge、SiGe、Geなど)を形成しておき、コンタクト開口後に、例えば等方性エッチングなどで犠牲膜のみを除去し、例えば化学蒸着法またはめっきを用いて金属を形成し、ビアより大きいソース/ドレイン領域の範囲に、シリサイド層を形成する。

【0035】

与えられた特徴に対するすべての数字または数範囲に関して、数字またはある範囲からのパラメータは、数範囲を生成するための同じ特徴に対して、他の数字または異なる範囲からのパラメータを結合されてもよい。

【0036】

上記の本実施形態においては、工程の増大を抑制しつつ、コンタクト抵抗の増大を防止することができ、界面抵抗の増大を防止することができる。上記の各種の数値は、このコンタクト抵抗および界面抵抗の増大を適切な範囲で防止可能な範囲で決定することができる。上記の各種の材料は、半導体製造で使用される各種の材料で実現可能であることを表している。

【0037】

ステップの例で、または、別の方法で示された場合を除いて、明細書および特許請求の範囲で使用される、すべての数字、値および/または成分の量を言及する表現、反応条件などは、用語「約」によってすべての実例で修正さえるように理解されるべきである。

【0038】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0039】

301…半導体基板、303…シャロートレンチ絶縁領域、305…ソース/ドレイン領域、310…機能的ゲート電極構造、312…側壁、350…犠牲膜、355…絶縁層、360…絶縁層、410…ビア、420…コンタクト開口部、430…空隙スペース、510…金属シリサイド前駆体、610…シリサイド、710,810…金属配線

【特許請求の範囲】

【請求項1】

自己整合シリサイドを形成するための方法において、

少なくとも一つの不純物領域と、前記不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、前記犠牲膜の上に形成された少なくとも一つの絶縁層とを備えた半導体基板を具備する初期の半導体構造物を提供することと、

前記少なくとも一つの絶縁層にコンタクト開口部を形成することと、

前記少なくとも一つの絶縁層の下にある前記犠牲膜を除去し、前記少なくとも一つの絶縁層の下にある空隙スペースを残すことと、

前記空隙スペース内に金属シリサイド前駆体を置くことと、

前記金属シリサイド前駆体をシリサイド層に変換することと

を具備する、方法。

【請求項2】

前記少なくとも一つの絶縁層は、前記犠牲膜の上に形成された少なくとも一つの絶縁層と、前記絶縁層の上に形成された少なくとも一つの絶縁層とを具備する、請求項1の方法。

【請求項3】

前記犠牲膜は、過酸化水素、過酸化物を含む化合物、および基礎の化学物質を含むグループから選択された1以上を具備するエッチング溶液を用いてウェットエッチングプロセスにより除去される、請求項1または2の方法。

【請求項4】

前記犠牲膜は、Ge、SiおよびSiGeを含むグループから選択された1以上を含む、請求項1ないし3の方法。

【請求項5】

前記金属シリサイド前駆体は、チタン、コバルト、ニッケル、白金、タングステン、およびそれらの混合物を含むグループから選択された1以上を具備する、請求項1ないし4の方法。

【請求項6】

前記シリサイド層は、前記コンタクト開口部の面積よりも面積より大きい面積を持つ、請求項1ないし5の方法。

【請求項7】

前記犠牲膜は、過酸化物、アンモニア、テトラメチルアンモニウムヒドロキシド、テトラエチルアンモニウム水酸化物、コリンなどの第4級アミン、およびアミン基を含む化合物を含むグループから選択された1以上を具備する混合物との接触を通じてエッチングにより除去される、請求項1ないし6の方法。

【請求項8】

電気的接触が前記コンタクト開口部を抜けて前記シリサイド層と金属配線との間に形成されるように、ビア・パターンに前記金属配線を置くことをさらに具備する、請求項1ないし7の方法。

【請求項9】

半導体デバイスを製造するための方法において、

半導体基板と、前記半導体基板上に形成された機能的ゲート構造と、前記半導体基板上に形成された不純物と、前記不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、前記犠牲膜の上に形成された少なくとも一つの絶縁層とを備えた半導体構造物を提供することと、

前記絶縁層上にビア・パターンを、さらに、前記犠牲膜の上の前記少なくとも一つの絶縁層にコンタクト開口部をエッチングすることと、

前記少なくとも一つの絶縁層の下において、前記犠牲膜を除去して空隙スペースを形成することと、

前記空隙スペース内に金属シリサイド前駆体を置くことと、

前記金属シリサイド前駆体をアニーリングし、前記金属シリサイド前駆体をシリサイド層に変換することと

を具備する、方法。

【請求項10】

ゲートラストスキームを用いて半導体基板上に形成された機能的なゲート構造と、

前記半導体基板上に形成された不純物領域と、

前記不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成されたシリサイドを含むシリサイド層と、

前記シリサイド層の上に形成された少なくとも一つの絶縁層と

を具備し、

前記少なくとも一つの絶縁層には、ビアおよびコンタクト開口部のパターンが形成されており、

前記シリサイド層の面積は、前記コンタクト開口部の面積より大きい、

ことを特徴とする半導体構造物。

【請求項1】

自己整合シリサイドを形成するための方法において、

少なくとも一つの不純物領域と、前記不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、前記犠牲膜の上に形成された少なくとも一つの絶縁層とを備えた半導体基板を具備する初期の半導体構造物を提供することと、

前記少なくとも一つの絶縁層にコンタクト開口部を形成することと、

前記少なくとも一つの絶縁層の下にある前記犠牲膜を除去し、前記少なくとも一つの絶縁層の下にある空隙スペースを残すことと、

前記空隙スペース内に金属シリサイド前駆体を置くことと、

前記金属シリサイド前駆体をシリサイド層に変換することと

を具備する、方法。

【請求項2】

前記少なくとも一つの絶縁層は、前記犠牲膜の上に形成された少なくとも一つの絶縁層と、前記絶縁層の上に形成された少なくとも一つの絶縁層とを具備する、請求項1の方法。

【請求項3】

前記犠牲膜は、過酸化水素、過酸化物を含む化合物、および基礎の化学物質を含むグループから選択された1以上を具備するエッチング溶液を用いてウェットエッチングプロセスにより除去される、請求項1または2の方法。

【請求項4】

前記犠牲膜は、Ge、SiおよびSiGeを含むグループから選択された1以上を含む、請求項1ないし3の方法。

【請求項5】

前記金属シリサイド前駆体は、チタン、コバルト、ニッケル、白金、タングステン、およびそれらの混合物を含むグループから選択された1以上を具備する、請求項1ないし4の方法。

【請求項6】

前記シリサイド層は、前記コンタクト開口部の面積よりも面積より大きい面積を持つ、請求項1ないし5の方法。

【請求項7】

前記犠牲膜は、過酸化物、アンモニア、テトラメチルアンモニウムヒドロキシド、テトラエチルアンモニウム水酸化物、コリンなどの第4級アミン、およびアミン基を含む化合物を含むグループから選択された1以上を具備する混合物との接触を通じてエッチングにより除去される、請求項1ないし6の方法。

【請求項8】

電気的接触が前記コンタクト開口部を抜けて前記シリサイド層と金属配線との間に形成されるように、ビア・パターンに前記金属配線を置くことをさらに具備する、請求項1ないし7の方法。

【請求項9】

半導体デバイスを製造するための方法において、

半導体基板と、前記半導体基板上に形成された機能的ゲート構造と、前記半導体基板上に形成された不純物と、前記不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成された犠牲膜と、前記犠牲膜の上に形成された少なくとも一つの絶縁層とを備えた半導体構造物を提供することと、

前記絶縁層上にビア・パターンを、さらに、前記犠牲膜の上の前記少なくとも一つの絶縁層にコンタクト開口部をエッチングすることと、

前記少なくとも一つの絶縁層の下において、前記犠牲膜を除去して空隙スペースを形成することと、

前記空隙スペース内に金属シリサイド前駆体を置くことと、

前記金属シリサイド前駆体をアニーリングし、前記金属シリサイド前駆体をシリサイド層に変換することと

を具備する、方法。

【請求項10】

ゲートラストスキームを用いて半導体基板上に形成された機能的なゲート構造と、

前記半導体基板上に形成された不純物領域と、

前記不純物領域または付加的な不純物のない領域のうちの少なくとも一方の上に形成されたシリサイドを含むシリサイド層と、

前記シリサイド層の上に形成された少なくとも一つの絶縁層と

を具備し、

前記少なくとも一つの絶縁層には、ビアおよびコンタクト開口部のパターンが形成されており、

前記シリサイド層の面積は、前記コンタクト開口部の面積より大きい、

ことを特徴とする半導体構造物。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−204841(P2012−204841A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2012−69766(P2012−69766)

【出願日】平成24年3月26日(2012.3.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成24年3月26日(2012.3.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]