薄膜の加工方法、容量素子の製造方法及び半導体装置の製造方法

【目的】非単結晶シリコン薄膜の表面に再現性良く微細な凹凸を形成すること。

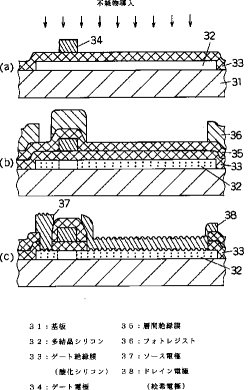

【構成】基板31上に多結晶シリコン薄膜32からなる半導体層を設け、ゲート絶縁膜33で被覆し、ゲート電極34を形成した後ソース・ドレイン領域形成のため不純物導入を行い層間絶縁膜35を形成する。コンタクトホール開口用のフォトレジスト36を形成した後プラズマ中で絶縁膜除去処理を行い、その処理の際、自己整合的に下地の多結晶シリコン表面に微細な凹凸が形成される。その後、ソース電極37及び絵素電極38を形成することにより絵素電極部38には下地の凹凸が転写され微細な凹凸が形成され、ソース電極部37は接合面積が増大して接触抵抗が低減され薄膜トランジスタの高性能化が図れる。半導体メモリーの容量素子の電極や反射型液晶表示装置の絵素電極あるいは半導体/金属接合部の特性改善を実現できる。

【構成】基板31上に多結晶シリコン薄膜32からなる半導体層を設け、ゲート絶縁膜33で被覆し、ゲート電極34を形成した後ソース・ドレイン領域形成のため不純物導入を行い層間絶縁膜35を形成する。コンタクトホール開口用のフォトレジスト36を形成した後プラズマ中で絶縁膜除去処理を行い、その処理の際、自己整合的に下地の多結晶シリコン表面に微細な凹凸が形成される。その後、ソース電極37及び絵素電極38を形成することにより絵素電極部38には下地の凹凸が転写され微細な凹凸が形成され、ソース電極部37は接合面積が増大して接触抵抗が低減され薄膜トランジスタの高性能化が図れる。半導体メモリーの容量素子の電極や反射型液晶表示装置の絵素電極あるいは半導体/金属接合部の特性改善を実現できる。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、半導体メモリー素子のスタックキャパシターや反射型液晶表示装置の絵素電極等に応用可能な技術であって、非単結晶シリコン薄膜表面に微細な凹凸を形成する薄膜の加工方法等に関するものである。

【0002】

【従来の技術】図4に従来の容量素子の断面構成図の一例を示し従来の製造方法を説明する。

【0003】基板41上にまず多結晶シリコン薄膜を堆積し第一の電極42の形状に加工する。次に前記第一の電極42を被覆するように絶縁膜43(酸化シリコン薄膜)を形成する。前記絶縁膜43上に多結晶シリコン薄膜からなる第二の電極44を形成し容量素子を完成する。上記容量素子の容量Cは以下の(数1)で規定される。

【0004】

【数1】C=S・Ei/d数1中のSは容量素子の電極面積、Eiは絶縁膜の誘電率、dは絶縁膜の膜厚である。誘電率Eiの値は絶縁膜固有の値であり、容量Cを増加させるためには電極面積Sを増大させるか、絶縁膜の膜厚dを減少させるかの選択となる。半導体メモリー素子に使用される容量素子に関しては、集積化が進むことにより容量素子のサイズが縮小され、必要な容量を維持するための電極面積Sの確保が困難となる。従って、誘電率Eiの大きな絶縁膜材料を用いたり絶縁膜の膜厚dを減少させることにより容量素子のサイズを縮小しつつ容量Cの増大を図る方法が提案されている。ところが絶縁膜の膜厚を減少させた場合には、リーク電流の増大や信頼性の低下といった問題が発生する。そこで、他の方法として容量素子の電極表面を凹凸状に加工することにより電極表面積を増大させ実効的な容量を増大させる方法も提案されている。この方法は、例えば、エクステンテ゛ィト゛ アフ゛ストラクトオフ゛ サ゛ 21st コンファレンス オン ソリット゛ ステート テ゛ハ゛イシス アント゛ マテリアルス゛ 1989[Extended Abstract of the 21st Conference on Solid State Devices andMaterials, Tokyo, 1989, pp.137-140]に開示されている。

【0005】次に、図5に非晶質シリコン薄膜トランジスタを用いた反射型液晶表示装置の構成断面図の一例を示し、従来の製造方法を説明する。

【0006】基板51上にゲート電極52を形成し,ゲート電極52を被覆するようにゲート絶縁膜53(窒化シリコン薄膜)及び非晶質シリコン薄膜54及びチャネル保護膜55(窒化シリコン薄膜)をプラズマ気相成長法により連続形成する。チャネル保護膜55のパターン化を行った後、薄膜トランジスタのソース及びドレイン領域を形成する。前記薄膜トランジスタを覆う様に保護絶縁膜56を形成する。保護絶縁膜56の所定の位置をエッチング除去し、アルミニウムからなるソース電極57及びドレイン電極58(反射型絵素電極)を形成する。

【0007】本構成では、Alからなる反射型絵素電極57、58を有するが、光の散乱特性を向上させ表示品位を向上させる手法として、Al絵素電極の表面を化学的エッチング法を用いて荒し表面凹凸を形成する方法が提案されている。この方法は、例えばエス アイテ゛ィー 92 タ゛イシ゛ェスト[SID92 Digest pp.437-440]に開示されている。

【0008】

【発明が解決しようとする課題】すなわち、半導体メモリー素子(DRAM等)の高集積化に伴いメモリー素子(セル)のサイズも縮小する必要がある。ところが、セルサイズの縮小は容量素子の電極面積を低下させ容量低下を引き起こし必要時間のデーター保持に支障をきたす。このためメモリーセルのサイズを縮小しつつ容量素子の容量を維持あるいは増大するため、上述のように、容量素子の電極表面を凹凸状に加工することにより電極表面積を増大させ実効的な容量を増大する方法が知られている。また図5に示した反射型液晶表示装置においては反射電極としてアルミニウムを用いる方法が一般的であり、反射電極の入射光に対する散乱特性を向上し表示品質を向上させるためアルミニウム反射電極の表面を荒し凹凸を形成する方法が提案されている。

【0009】しかしながら、従来の電極の表面に凹凸を形成する方法では、微細な凹凸を再現性良く形成することは困難であるという課題がある。

【0010】本発明は、このような従来の方法の課題を考慮し、微細な凹凸を再現性良く形成することのできる薄膜の加工方法等を提供することを目的とするものである。

【0011】

【課題を解決するための手段】本発明は、非単結晶シリコン薄膜上に絶縁膜を形成し、その絶縁膜をプラズマ中でエッチング除去し非単結晶シリコン薄膜表面に微細な凹凸を形成する点にポイントがある。

【0012】また、基板上に形成した第一の電極を前記加工方法で加工することにより表面凹凸を形成し、その第一の電極上に絶縁膜及び第二の電極を形成することにより容量素子が形成可能である。

【0013】また、基板上に薄膜トランジスタの活性層となる非単結晶シリコン薄膜を形成し、前記非単結晶シリコン薄膜を被覆するように絶縁膜を形成し、薄膜トランジスタのソース領域あるいはドレイン領域の少なくとも一部分の絶縁膜を前記加工方法で除去し半導体層表面に凹凸を形成したのち、金属薄膜を形成することにより、例えば、反射型液晶表示装置の絵素電極が形成可能である。

【0014】

【作用】本発明では、非単結晶シリコン薄膜上に絶縁膜である酸化シリコン薄膜を形成する。このとき非単結晶シリコン薄膜の結晶粒界部で優先的に酸化反応が起こり結晶粒界部の酸化が進行する。その後、前記酸化シリコン薄膜をプラズマ中でエッチング除去することにより絶縁膜が除去されると同時に非単結晶シリコン薄膜の結晶粒界部の酸化された領域がエッチングされ粒界部に凹が形成され表面凹凸が増大する。

【0015】本発明の加工方法を用いて作成した表面凹凸は多結晶シリコン薄膜の結晶粒径程度の周期であり、周期は数十nm程度から数μm程度まで多結晶シリコン薄膜の形成条件を変化させることにより容易に制御可能である。従って本発明を用いることにより、従来のフォトリソグラフィー等を用いて形成可能な周期の、十分の一から百分の一の周期で再現性よく表面凹凸を形成することが可能となる。

【0016】また、本発明の加工方法を容量素子の電極の製造に応用することにより絶縁膜と接触する電極表面に微細な凹凸を形成でき、実効的な電極表面積が増大し単位面積当たりの容量を増大することが可能となる。

【0017】また、本容量素子を半導体メモリーに応用することにより集積度を向上させつつ微細化を図ることが可能となる。

【0018】また、上記加工方法を反射型液晶表示装置の絵素電極に用いることにより化学的エッチング法を用いる事なく再現性よく反射電極の表面に凹凸が形成でき散乱特性を向上させることが可能となる。

【0019】

【実施例】以下、本発明の実施例について図面を参照して説明する。

【0020】図1は請求項1に記載の薄膜の加工方法の一実施例である。

【0021】まず、基板11上に多結晶シリコン薄膜12を、減圧気相成長法により形成する。多結晶シリコン薄膜12上に硅素の水素化合物であるシラン(SiH4)と酸素を原料ガスとする常圧気相成長法により酸化シリコン薄膜13を形成する。薄膜13上にフォトレジスト14を用いて第一の電極の反転パターンを形成する。次いで、リアクティブ・イオン・エッチング装置を用いてプラズマ中で前記酸化シリコン薄膜13のエッチング処理を行う。エッチングガスとしてはCF4とCHF3を1:1の比率にて混合したガスを用い、真空度300mTorr(39.9Pa)、高周波電力300Wで処理を行った。フォトレジスト開口部の酸化シリコン薄膜13のエッチングが終了した時点でエッチングを停止しフォトレジスト14を除去する。上記エッチング処理により酸化シリコン薄膜13のエッチングと同時にフォトレジスト(酸化シリコン開口部15)開口部の多結晶シリコン薄膜12に周期数十nmの微細な凹凸が形成される。上記に示したように本実施例の加工方法を用いることによりフォトリソグラフィー等の手法を用いることなく、微細な凹凸を再現性よく形成することが可能となった。なお、凹凸の周期はほぼ多結晶シリコン薄膜12の結晶粒径に対応しており、多結晶シリコン薄膜12の結晶粒径を制御することにより、形成したい凹凸の周期を任意に制御可能になった。

【0022】図2は本発明の請求項7に記載した容量素子の製造方法の一実施例である。

【0023】まず、基板21上に第一の電極となる多結晶シリコン薄膜22を形成する。前記多結晶シリコン薄膜22上にシラン(SiH4)と酸素を原料ガスとして用いる常圧気相成長法により酸化シリコン薄膜23を形成する。ついで第一の電極部を開口するためフォトレジスト24を所定の形状に加工する。図1に説明したリアクティブ・イオン・エッチング法で酸化シリコン薄膜23をエッチング除去すると同時に第一の電極となる多結晶シリコン薄膜22の表面に微細な凹凸を形成する。ついで前記第一の電極を被覆するように減圧気相成長法(LPCVD法)により酸化シリコン薄膜25を形成する。この絶縁膜25上に多結晶シリコンからなる第二の電極26を形成し、容量素子が完成する。本容量素子は第一の電極に形成した表面凹凸により実効的に電極表面積が増大しており第一の電極に表面凹凸を形成しない容量素子に比べて単位面積当りの容量が増大した。また本容量素子を半導体記憶装置(メモリー素子)に用いることにより素子サイズを低減でき集積度の向上を図ることが可能となった。

【0024】図3は本発明の請求項8に記載した反射型液晶表示装置の製造方法の一実施例である。まず、基板31上に多結晶シリコン薄膜32を減圧気相成長法により形成し、フォトリソグラフィー法を用いて島状に加工する。ついでゲート絶縁膜となる酸化シリコン薄膜33をシラン(SiH4)と酸素を原料ガスとする常圧気相成長法を用いて多結晶シリコン薄膜32上に形成する。前記ゲート絶縁膜33上に多結晶シリコンからなるゲート電極34を形成する。ゲート電極34を形成後、イオン注入法を用いてソース・ドレイン領域の不純物導入を行う。導入した不純物の活性化処理を行った後、層間絶縁膜35となる酸化シリコン薄膜を形成する。コンタクトホールを開口するためのレジストパターン36を形成し、ソース領域とドレイン領域(絵素領域)の層間絶縁膜35とゲート絶縁膜33を除去しコンタクトホールを開口する。コンタクトホールの開口にはリアクティブ・イオン・エッチング法を用い、CF4及びCHF3ガスを1:1の比率で混合したガス用いて真空度300mTorr、高周波電力300Wの条件にてエッチングを行う。前記条件にてコンタクトホールを開口すること同時に下地の多結晶シリコン薄膜32の表面に周期数十nm程度の微細な凹凸が形成できる。前記コンタクトホールを開口したのちAl薄膜を堆積する。Al薄膜を堆積後、それをソース配線37及び絵素電極38の形状に加工し薄膜トランジスタが完成する。

【0025】本実施例の製造方法を用いることにより、絵素領域に形成したAl薄膜は反射電極として作用するが本Al薄膜の下地の多結晶シリコン薄膜32には表面に微細な凹凸が形成されているため前記凹凸が上層のAl薄膜37、38にも転写されている。これにより反射型液晶表示装置の絵素電極として用いた場合に、入射光の散乱特性が向上し表示品位が向上した。またソース配線及びドレイン配線と多結晶シリコン薄膜との接触部(コンタクト部)には自己整合的に多結晶シリコン表面に凹凸が形成されるため、金属と半導体接合部においては接合面積が増大し接触抵抗が低減することにより半導体素子の高性能化が図れた。なお、本発明の実施例では薄膜トランジスタに関して説明したが他の半導体装置等に用いても同様の結果を得ることが可能である。

【0026】以上説明したように、本発明の加工方法を用いて形成された表面凹凸はその周期が数十nm程度であり、従来のフォトリソグラフィー等を用いて形成可能な周期の十分の一から百分の一の周期で再現性よく表面凹凸を形成することが可能となった。また本発明の加工方法では絶縁膜のエッチング時に自己整合的に下地薄膜表面に凹凸が形成されるため、工程が低減できると同時に各種半導体装置応用が可能となった。本加工方法を容量素子の電極の製造に応用することにより、電極表面に微細な凹凸を形成することが可能となり、実質的な電極面積が増大し同一面積上に形成した従来の容量素子に比べ容量を増大することが可能となった。また、本容量素子を半導体メモリーに応用することにより集積度を向上させつつ容量を確保することが可能となった。また本発明の加工方法を用いて反射型液晶表示装置を作成したところ、非単結晶シリコン薄膜の表面に微細な凹凸を形成し前記凹凸を反射電極に転写することにより絵素電極の散乱特性が向上でき高画質の液晶表示装置を得ることが可能となった。また、他の半導体装置の製造過程においても、多結晶シリコン薄膜上の絶縁膜をエッチング除去してから金属薄膜を形成する部分では本加工法を用いることにより絶縁膜の除去部の多結晶シリコン薄膜の表面に自己整合的に表面凹凸が形成でき、金属と半導体接合の接合面積を増大でき特性向上が図れた。

【0027】

【発明の効果】以上述べたところから明らかなように、本発明の薄膜の加工方法を用いることにより、薄膜表面に微細な凹凸を再現性良く形成することができる。

【0028】また、その加工方法を利用して、サイズが小さくかつ容量の大きな容量素子を製造する事が出来る。

【0029】また、その加工方法を利用して、半導体装置、例えば液晶表示装置の絵素電極の散乱特性が向上でき高画質の液晶表示装置を得ることが出来る。

【図面の簡単な説明】

【図1】本発明の一実施例の薄膜加工方法を示す工程図である。

【図2】本発明の一実施例の容量素子の製造方法を示す工程図である。

【図3】本発明の一実施例の反射型液晶表示装置の製造方法を示す工程図である。

【図4】従来の容量素子の断面図である。

【図5】従来の反射型液晶表示素子の断面図である。

【符号の説明】

11 基板

12 多結晶シリコン

13 酸化シリコン

14 フォトレジスト

15 酸化シリコン開口部

21 基板

22 第一の電極(多結晶シリコン)

23 酸化シリコン

24 フォトレジスト

25 絶縁膜(酸化シリコン)

26 第二の電極(多結晶シリコン)

31 基板

32 多結晶シリコン

33 ゲート絶縁膜(酸化シリコン)

34 ゲート電極(多結晶シリコン)

35 層間絶縁膜(酸化シリコン)

36 フォトレジスト

37 ソース電極

38 ドレイン電極(絵素電極)

【0001】

【産業上の利用分野】本発明は、半導体メモリー素子のスタックキャパシターや反射型液晶表示装置の絵素電極等に応用可能な技術であって、非単結晶シリコン薄膜表面に微細な凹凸を形成する薄膜の加工方法等に関するものである。

【0002】

【従来の技術】図4に従来の容量素子の断面構成図の一例を示し従来の製造方法を説明する。

【0003】基板41上にまず多結晶シリコン薄膜を堆積し第一の電極42の形状に加工する。次に前記第一の電極42を被覆するように絶縁膜43(酸化シリコン薄膜)を形成する。前記絶縁膜43上に多結晶シリコン薄膜からなる第二の電極44を形成し容量素子を完成する。上記容量素子の容量Cは以下の(数1)で規定される。

【0004】

【数1】C=S・Ei/d数1中のSは容量素子の電極面積、Eiは絶縁膜の誘電率、dは絶縁膜の膜厚である。誘電率Eiの値は絶縁膜固有の値であり、容量Cを増加させるためには電極面積Sを増大させるか、絶縁膜の膜厚dを減少させるかの選択となる。半導体メモリー素子に使用される容量素子に関しては、集積化が進むことにより容量素子のサイズが縮小され、必要な容量を維持するための電極面積Sの確保が困難となる。従って、誘電率Eiの大きな絶縁膜材料を用いたり絶縁膜の膜厚dを減少させることにより容量素子のサイズを縮小しつつ容量Cの増大を図る方法が提案されている。ところが絶縁膜の膜厚を減少させた場合には、リーク電流の増大や信頼性の低下といった問題が発生する。そこで、他の方法として容量素子の電極表面を凹凸状に加工することにより電極表面積を増大させ実効的な容量を増大させる方法も提案されている。この方法は、例えば、エクステンテ゛ィト゛ アフ゛ストラクトオフ゛ サ゛ 21st コンファレンス オン ソリット゛ ステート テ゛ハ゛イシス アント゛ マテリアルス゛ 1989[Extended Abstract of the 21st Conference on Solid State Devices andMaterials, Tokyo, 1989, pp.137-140]に開示されている。

【0005】次に、図5に非晶質シリコン薄膜トランジスタを用いた反射型液晶表示装置の構成断面図の一例を示し、従来の製造方法を説明する。

【0006】基板51上にゲート電極52を形成し,ゲート電極52を被覆するようにゲート絶縁膜53(窒化シリコン薄膜)及び非晶質シリコン薄膜54及びチャネル保護膜55(窒化シリコン薄膜)をプラズマ気相成長法により連続形成する。チャネル保護膜55のパターン化を行った後、薄膜トランジスタのソース及びドレイン領域を形成する。前記薄膜トランジスタを覆う様に保護絶縁膜56を形成する。保護絶縁膜56の所定の位置をエッチング除去し、アルミニウムからなるソース電極57及びドレイン電極58(反射型絵素電極)を形成する。

【0007】本構成では、Alからなる反射型絵素電極57、58を有するが、光の散乱特性を向上させ表示品位を向上させる手法として、Al絵素電極の表面を化学的エッチング法を用いて荒し表面凹凸を形成する方法が提案されている。この方法は、例えばエス アイテ゛ィー 92 タ゛イシ゛ェスト[SID92 Digest pp.437-440]に開示されている。

【0008】

【発明が解決しようとする課題】すなわち、半導体メモリー素子(DRAM等)の高集積化に伴いメモリー素子(セル)のサイズも縮小する必要がある。ところが、セルサイズの縮小は容量素子の電極面積を低下させ容量低下を引き起こし必要時間のデーター保持に支障をきたす。このためメモリーセルのサイズを縮小しつつ容量素子の容量を維持あるいは増大するため、上述のように、容量素子の電極表面を凹凸状に加工することにより電極表面積を増大させ実効的な容量を増大する方法が知られている。また図5に示した反射型液晶表示装置においては反射電極としてアルミニウムを用いる方法が一般的であり、反射電極の入射光に対する散乱特性を向上し表示品質を向上させるためアルミニウム反射電極の表面を荒し凹凸を形成する方法が提案されている。

【0009】しかしながら、従来の電極の表面に凹凸を形成する方法では、微細な凹凸を再現性良く形成することは困難であるという課題がある。

【0010】本発明は、このような従来の方法の課題を考慮し、微細な凹凸を再現性良く形成することのできる薄膜の加工方法等を提供することを目的とするものである。

【0011】

【課題を解決するための手段】本発明は、非単結晶シリコン薄膜上に絶縁膜を形成し、その絶縁膜をプラズマ中でエッチング除去し非単結晶シリコン薄膜表面に微細な凹凸を形成する点にポイントがある。

【0012】また、基板上に形成した第一の電極を前記加工方法で加工することにより表面凹凸を形成し、その第一の電極上に絶縁膜及び第二の電極を形成することにより容量素子が形成可能である。

【0013】また、基板上に薄膜トランジスタの活性層となる非単結晶シリコン薄膜を形成し、前記非単結晶シリコン薄膜を被覆するように絶縁膜を形成し、薄膜トランジスタのソース領域あるいはドレイン領域の少なくとも一部分の絶縁膜を前記加工方法で除去し半導体層表面に凹凸を形成したのち、金属薄膜を形成することにより、例えば、反射型液晶表示装置の絵素電極が形成可能である。

【0014】

【作用】本発明では、非単結晶シリコン薄膜上に絶縁膜である酸化シリコン薄膜を形成する。このとき非単結晶シリコン薄膜の結晶粒界部で優先的に酸化反応が起こり結晶粒界部の酸化が進行する。その後、前記酸化シリコン薄膜をプラズマ中でエッチング除去することにより絶縁膜が除去されると同時に非単結晶シリコン薄膜の結晶粒界部の酸化された領域がエッチングされ粒界部に凹が形成され表面凹凸が増大する。

【0015】本発明の加工方法を用いて作成した表面凹凸は多結晶シリコン薄膜の結晶粒径程度の周期であり、周期は数十nm程度から数μm程度まで多結晶シリコン薄膜の形成条件を変化させることにより容易に制御可能である。従って本発明を用いることにより、従来のフォトリソグラフィー等を用いて形成可能な周期の、十分の一から百分の一の周期で再現性よく表面凹凸を形成することが可能となる。

【0016】また、本発明の加工方法を容量素子の電極の製造に応用することにより絶縁膜と接触する電極表面に微細な凹凸を形成でき、実効的な電極表面積が増大し単位面積当たりの容量を増大することが可能となる。

【0017】また、本容量素子を半導体メモリーに応用することにより集積度を向上させつつ微細化を図ることが可能となる。

【0018】また、上記加工方法を反射型液晶表示装置の絵素電極に用いることにより化学的エッチング法を用いる事なく再現性よく反射電極の表面に凹凸が形成でき散乱特性を向上させることが可能となる。

【0019】

【実施例】以下、本発明の実施例について図面を参照して説明する。

【0020】図1は請求項1に記載の薄膜の加工方法の一実施例である。

【0021】まず、基板11上に多結晶シリコン薄膜12を、減圧気相成長法により形成する。多結晶シリコン薄膜12上に硅素の水素化合物であるシラン(SiH4)と酸素を原料ガスとする常圧気相成長法により酸化シリコン薄膜13を形成する。薄膜13上にフォトレジスト14を用いて第一の電極の反転パターンを形成する。次いで、リアクティブ・イオン・エッチング装置を用いてプラズマ中で前記酸化シリコン薄膜13のエッチング処理を行う。エッチングガスとしてはCF4とCHF3を1:1の比率にて混合したガスを用い、真空度300mTorr(39.9Pa)、高周波電力300Wで処理を行った。フォトレジスト開口部の酸化シリコン薄膜13のエッチングが終了した時点でエッチングを停止しフォトレジスト14を除去する。上記エッチング処理により酸化シリコン薄膜13のエッチングと同時にフォトレジスト(酸化シリコン開口部15)開口部の多結晶シリコン薄膜12に周期数十nmの微細な凹凸が形成される。上記に示したように本実施例の加工方法を用いることによりフォトリソグラフィー等の手法を用いることなく、微細な凹凸を再現性よく形成することが可能となった。なお、凹凸の周期はほぼ多結晶シリコン薄膜12の結晶粒径に対応しており、多結晶シリコン薄膜12の結晶粒径を制御することにより、形成したい凹凸の周期を任意に制御可能になった。

【0022】図2は本発明の請求項7に記載した容量素子の製造方法の一実施例である。

【0023】まず、基板21上に第一の電極となる多結晶シリコン薄膜22を形成する。前記多結晶シリコン薄膜22上にシラン(SiH4)と酸素を原料ガスとして用いる常圧気相成長法により酸化シリコン薄膜23を形成する。ついで第一の電極部を開口するためフォトレジスト24を所定の形状に加工する。図1に説明したリアクティブ・イオン・エッチング法で酸化シリコン薄膜23をエッチング除去すると同時に第一の電極となる多結晶シリコン薄膜22の表面に微細な凹凸を形成する。ついで前記第一の電極を被覆するように減圧気相成長法(LPCVD法)により酸化シリコン薄膜25を形成する。この絶縁膜25上に多結晶シリコンからなる第二の電極26を形成し、容量素子が完成する。本容量素子は第一の電極に形成した表面凹凸により実効的に電極表面積が増大しており第一の電極に表面凹凸を形成しない容量素子に比べて単位面積当りの容量が増大した。また本容量素子を半導体記憶装置(メモリー素子)に用いることにより素子サイズを低減でき集積度の向上を図ることが可能となった。

【0024】図3は本発明の請求項8に記載した反射型液晶表示装置の製造方法の一実施例である。まず、基板31上に多結晶シリコン薄膜32を減圧気相成長法により形成し、フォトリソグラフィー法を用いて島状に加工する。ついでゲート絶縁膜となる酸化シリコン薄膜33をシラン(SiH4)と酸素を原料ガスとする常圧気相成長法を用いて多結晶シリコン薄膜32上に形成する。前記ゲート絶縁膜33上に多結晶シリコンからなるゲート電極34を形成する。ゲート電極34を形成後、イオン注入法を用いてソース・ドレイン領域の不純物導入を行う。導入した不純物の活性化処理を行った後、層間絶縁膜35となる酸化シリコン薄膜を形成する。コンタクトホールを開口するためのレジストパターン36を形成し、ソース領域とドレイン領域(絵素領域)の層間絶縁膜35とゲート絶縁膜33を除去しコンタクトホールを開口する。コンタクトホールの開口にはリアクティブ・イオン・エッチング法を用い、CF4及びCHF3ガスを1:1の比率で混合したガス用いて真空度300mTorr、高周波電力300Wの条件にてエッチングを行う。前記条件にてコンタクトホールを開口すること同時に下地の多結晶シリコン薄膜32の表面に周期数十nm程度の微細な凹凸が形成できる。前記コンタクトホールを開口したのちAl薄膜を堆積する。Al薄膜を堆積後、それをソース配線37及び絵素電極38の形状に加工し薄膜トランジスタが完成する。

【0025】本実施例の製造方法を用いることにより、絵素領域に形成したAl薄膜は反射電極として作用するが本Al薄膜の下地の多結晶シリコン薄膜32には表面に微細な凹凸が形成されているため前記凹凸が上層のAl薄膜37、38にも転写されている。これにより反射型液晶表示装置の絵素電極として用いた場合に、入射光の散乱特性が向上し表示品位が向上した。またソース配線及びドレイン配線と多結晶シリコン薄膜との接触部(コンタクト部)には自己整合的に多結晶シリコン表面に凹凸が形成されるため、金属と半導体接合部においては接合面積が増大し接触抵抗が低減することにより半導体素子の高性能化が図れた。なお、本発明の実施例では薄膜トランジスタに関して説明したが他の半導体装置等に用いても同様の結果を得ることが可能である。

【0026】以上説明したように、本発明の加工方法を用いて形成された表面凹凸はその周期が数十nm程度であり、従来のフォトリソグラフィー等を用いて形成可能な周期の十分の一から百分の一の周期で再現性よく表面凹凸を形成することが可能となった。また本発明の加工方法では絶縁膜のエッチング時に自己整合的に下地薄膜表面に凹凸が形成されるため、工程が低減できると同時に各種半導体装置応用が可能となった。本加工方法を容量素子の電極の製造に応用することにより、電極表面に微細な凹凸を形成することが可能となり、実質的な電極面積が増大し同一面積上に形成した従来の容量素子に比べ容量を増大することが可能となった。また、本容量素子を半導体メモリーに応用することにより集積度を向上させつつ容量を確保することが可能となった。また本発明の加工方法を用いて反射型液晶表示装置を作成したところ、非単結晶シリコン薄膜の表面に微細な凹凸を形成し前記凹凸を反射電極に転写することにより絵素電極の散乱特性が向上でき高画質の液晶表示装置を得ることが可能となった。また、他の半導体装置の製造過程においても、多結晶シリコン薄膜上の絶縁膜をエッチング除去してから金属薄膜を形成する部分では本加工法を用いることにより絶縁膜の除去部の多結晶シリコン薄膜の表面に自己整合的に表面凹凸が形成でき、金属と半導体接合の接合面積を増大でき特性向上が図れた。

【0027】

【発明の効果】以上述べたところから明らかなように、本発明の薄膜の加工方法を用いることにより、薄膜表面に微細な凹凸を再現性良く形成することができる。

【0028】また、その加工方法を利用して、サイズが小さくかつ容量の大きな容量素子を製造する事が出来る。

【0029】また、その加工方法を利用して、半導体装置、例えば液晶表示装置の絵素電極の散乱特性が向上でき高画質の液晶表示装置を得ることが出来る。

【図面の簡単な説明】

【図1】本発明の一実施例の薄膜加工方法を示す工程図である。

【図2】本発明の一実施例の容量素子の製造方法を示す工程図である。

【図3】本発明の一実施例の反射型液晶表示装置の製造方法を示す工程図である。

【図4】従来の容量素子の断面図である。

【図5】従来の反射型液晶表示素子の断面図である。

【符号の説明】

11 基板

12 多結晶シリコン

13 酸化シリコン

14 フォトレジスト

15 酸化シリコン開口部

21 基板

22 第一の電極(多結晶シリコン)

23 酸化シリコン

24 フォトレジスト

25 絶縁膜(酸化シリコン)

26 第二の電極(多結晶シリコン)

31 基板

32 多結晶シリコン

33 ゲート絶縁膜(酸化シリコン)

34 ゲート電極(多結晶シリコン)

35 層間絶縁膜(酸化シリコン)

36 フォトレジスト

37 ソース電極

38 ドレイン電極(絵素電極)

【特許請求の範囲】

【請求項1】非単結晶シリコン薄膜上に絶縁膜を形成する工程と、前記絶縁膜をプラズマ中でエッチング除去することにより、前記非単結晶シリコン薄膜表面に凹凸を形成する工程とを備えたことを特徴とする薄膜の加工方法。

【請求項2】絶縁膜として、酸化シリコン薄膜を用いることを特徴とする請求項1記載の薄膜の加工方法。

【請求項3】絶縁膜として、硅素の水素化合物あるいは硅素の有機化合物を原料ガスとして少なくとも有する気相成長法で形成した酸化シリコン薄膜を用いることを特徴とする請求項1記載の薄膜の加工方法。

【請求項4】プラズマ生成時の雰囲気として、四弗化炭素(CF4)を少なくとも有することを特徴とする請求項1記載の薄膜の加工方法。

【請求項5】プラズマ生成時の雰囲気として、CHF3を少なくとも有することを特徴とする請求項1記載の薄膜の加工方法。

【請求項6】プラズマ生成時の圧力として、真空度が500mTorr以下であることを特徴とする請求項1記載の薄膜の加工方法。

【請求項7】基板上に非単結晶シリコン薄膜からなる第一の電極を形成する工程と、前記第一の電極を被覆するように第一絶縁膜を形成する工程と、前記絶縁膜を請求項1記載の加工方法で除去し前記第一の電極表面に凹凸を形成する工程と、前記第一の電極上に第二絶縁膜を形成する工程と、前記第二絶縁膜上に第二の電極を形成する工程とを少なくとも備えたことを特徴とする容量素子の製造方法。

【請求項8】非単結晶シリコン薄膜上に絶縁膜を形成する工程と、前記絶縁膜の少なくとも一部を請求項1記載の加工方法により選択的に除去する工程と、前記絶縁膜を除去した後、金属薄膜を堆積する工程とを少なくとも備えたことを特徴とする半導体装置の製造方法。

【請求項1】非単結晶シリコン薄膜上に絶縁膜を形成する工程と、前記絶縁膜をプラズマ中でエッチング除去することにより、前記非単結晶シリコン薄膜表面に凹凸を形成する工程とを備えたことを特徴とする薄膜の加工方法。

【請求項2】絶縁膜として、酸化シリコン薄膜を用いることを特徴とする請求項1記載の薄膜の加工方法。

【請求項3】絶縁膜として、硅素の水素化合物あるいは硅素の有機化合物を原料ガスとして少なくとも有する気相成長法で形成した酸化シリコン薄膜を用いることを特徴とする請求項1記載の薄膜の加工方法。

【請求項4】プラズマ生成時の雰囲気として、四弗化炭素(CF4)を少なくとも有することを特徴とする請求項1記載の薄膜の加工方法。

【請求項5】プラズマ生成時の雰囲気として、CHF3を少なくとも有することを特徴とする請求項1記載の薄膜の加工方法。

【請求項6】プラズマ生成時の圧力として、真空度が500mTorr以下であることを特徴とする請求項1記載の薄膜の加工方法。

【請求項7】基板上に非単結晶シリコン薄膜からなる第一の電極を形成する工程と、前記第一の電極を被覆するように第一絶縁膜を形成する工程と、前記絶縁膜を請求項1記載の加工方法で除去し前記第一の電極表面に凹凸を形成する工程と、前記第一の電極上に第二絶縁膜を形成する工程と、前記第二絶縁膜上に第二の電極を形成する工程とを少なくとも備えたことを特徴とする容量素子の製造方法。

【請求項8】非単結晶シリコン薄膜上に絶縁膜を形成する工程と、前記絶縁膜の少なくとも一部を請求項1記載の加工方法により選択的に除去する工程と、前記絶縁膜を除去した後、金属薄膜を堆積する工程とを少なくとも備えたことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図4】

【図5】

【図3】

【図2】

【図4】

【図5】

【図3】

【公開番号】特開平6−267912

【公開日】平成6年(1994)9月22日

【国際特許分類】

【出願番号】特願平5−54187

【出願日】平成5年(1993)3月15日

【出願人】(000005821)松下電器産業株式会社 (73,050)

【公開日】平成6年(1994)9月22日

【国際特許分類】

【出願日】平成5年(1993)3月15日

【出願人】(000005821)松下電器産業株式会社 (73,050)

[ Back to top ]