薄膜キャパシタ構造を備える集積回路パッケージ基板

【課題】パッケージ基板またはインターポーザ基板などの基板などの集積回路パッケージの基板で、焼結セラミックベース構造の上にキャパシタ構造が形成された集積回路パッケージの基板を提供する。

【解決手段】ベース構造12は、複数のビア開口22P、22G、22Sをそこに備える未加工の物質12から形成される。未加工の物質は、焼結セラミック物質になりおよび複数のビア開口を備えるベース構造が焼結セラミックベース構造になるように焼結される。導電性ビア14P、14G、14Sは、焼結セラミックベース構造のそれぞれのビア開口の中に形成される。キャパシタ構造16は、焼結セラミックベース構造の上に形成される。キャパシタ構造の複数の電源24Pおよびグランドプレーン26は、複数のビアに接続される。複数のシリコン基板などのもろい複数の基板内に複数のビア開口をドリルで開ける必要なしに複数のビアに接続されることができる。

【解決手段】ベース構造12は、複数のビア開口22P、22G、22Sをそこに備える未加工の物質12から形成される。未加工の物質は、焼結セラミック物質になりおよび複数のビア開口を備えるベース構造が焼結セラミックベース構造になるように焼結される。導電性ビア14P、14G、14Sは、焼結セラミックベース構造のそれぞれのビア開口の中に形成される。キャパシタ構造16は、焼結セラミックベース構造の上に形成される。キャパシタ構造の複数の電源24Pおよびグランドプレーン26は、複数のビアに接続される。複数のシリコン基板などのもろい複数の基板内に複数のビア開口をドリルで開ける必要なしに複数のビアに接続されることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積回路パッケージの基板内に備えられるキャパシタ構造に関する。

【背景技術】

【0002】

複数の集積回路は、通常、複数のウエハ基板上に製造される。ウエハ基板は、その後、個々の複数のダイに"ダイシング"され、または"シンギュレーション"され、それぞれのダイは、それぞれの集積回路を持つ。ダイは、その後、しばしば中間のインターポーザ基板を伴い、パッケージ基板上に実装される。基板または複数の基板は、結果の集積回路パッケージに構造上の剛性を提供する。パッケージ基板は、同様に、ダイの複数のコンタクトからその上に集積回路パッケージが実装されるキャリア基板上の複数のコンタクトへのx−y変換を提供する。

【0003】

複数の信号は、基板または複数の基板内の複数のコンダクタを介して、ダイの中の集積回路へおよびから提供される。レジスタンス−キャパシタンス−インダクタンス遅延と称される信号遅延は、複数の信号が複数のコンダクタを介して送信される場合にしばしば生じる。レジスタンス−キャパシタンス−インダクタンス遅延を低減するために、ダイの近くにキャパシタが提供される。キャパシタは、集積回路の近くで、電力の貯蔵所として動作する。

【0004】

複数のディスクリートキャパシタは、比較的大きく、したがって、基板上の大きな面積を占める。複数の薄膜は、小さな面積をしめ、多くのキャパシタが形成されることを可能にすることが理解されている。基板の製造の間に複数の薄膜キャパシタを製造することは、複数のディスクリートキャパシタを基板に実装することよりも、同様に単純である。

【0005】

複数のビア開口は、基板のベース構造に製造されなくてはならず、ここに複数の導電性ビアが形成されなくてならず、ここに薄膜キャパシタ構造の複数の電源およびグランドプレーンは接続されなくてはならない。そのような複数のビア開口の形成は、半導体産業の長年にわたる最大の関心事である。これまでは、全ての努力は、シリコンなどの複数の低k値物質内でドリルで複数の開口を開けることに向けられてきた。シリコンは、もろい物質であり、そこにドリルで複数の開口を開けることを難しくする。それぞれの開口は、同様に、個々にドリルで開けられなくてはならず、スループットを低減させる。

【図面の簡単な説明】

【0006】

本発明は、添付の複数の図面への参照を伴う複数の例により説明される。

【0007】

【図1】本発明の一実施形態に従って製造されたインターポーザ基板の側断面図である。

【0008】

【図2】図1のインターポーザ基板を備える集積回路パッケージの側断面図である。

【0009】

【図3】本発明の一実施形態に従って製造されたパッケージ基板の側断面図である。

【0010】

【図4】図3のパッケージ基板を備える集積回路パッケージの側断面図である。

【発明の詳細な説明】

【0011】

集積回路パッケージのパッケージ基板またはインターポーザ基板などの基板の製造が、説明される。ベース構造は、複数のビア開口をそこに備える未加工の物質から形成される。未加工の物質は、その後、未加工の物質が焼結セラミック物質になり、およびベース構造が複数のビア開口を備える焼結セラミックベース構造になるように焼結される。導電性ビアは、焼結セラミックベース構造のそれぞれのビア開口内に形成される。キャパシタ構造は、焼結セラミックベース構造上に形成される。キャパシタ構造の複数の電源およびグランドプレーンは、複数のビアに接続される。そのようなものとして、複数のシリコン基板のような複数のもろい基板内で複数のビア開口をドリルで開ける必要なしに、キャパシタ構造は、形成され、および複数のビアに接続されることができる。焼結セラミック物質は、同様に、熱膨張の低い係数を有し、キャパシタ構造を製造する時の複数の高温処理条件に耐えることができ、および、製造が高価ではない。

【0012】

添付の複数の図面の図1は、本発明の一実施形態の方法に従って構築されたインターポーザ基板10を説明する。インターポーザ基板10は、ベース構造12、複数の導電性ビア14、高k値誘電性物質を有するキャパシタ構造16、低k値誘電性物質18、および複数のコンタクトパッド20を備える。

【0013】

ベース構造12は、はじめに、未加工の焼結されていない物質からできている。未加工の物質は、ベース構造12の形のパッケージであり、複数のビア開口は22は、未加工の物質を突き抜けられる。未加工の物質のハンドリング、パッケージングおよびパンチングは、技術的に知られる。未加工の物質内の複数のパンチングホールの利点は、未加工の物質は、複数のシリコン基板などの他の複数の基板ほどもろくないことである。未加工の物質は、その後、未加工の物質が焼結セラミック物質になりおよびベース構造12が焼結セラミックベース構造12になるように、焼結される。焼結セラミックベース構造12は、複数のビア開口22を備える。複数のビア開口22は、電源ビア開口22P、グランドビア開口22G、および複数の信号ビア開口22Sを有する。複数のビア開口22のそれぞれ1つは、水平な焼結セラミックベース構造12の下面から上面へ拡張する。

【0014】

低k値誘電性物質18は、焼結セラミックベース構造12の上面全体の上に形成される。低k値誘電性物質18は、したがって、複数の電源、グランドおよび信号ビア開口22P、22Gおよび22Sを覆う。低k値誘電性物質18は、一般的に、二酸化シリコンからできており、3と4との間の誘電定数を有する。

【0015】

低k値誘電性物質18は、その後、パターニングされる。低k値誘電性物質18は、例えば、第一に、その部分を覆い、次に露出された複数の部分を焼き払うことでパターニングされる。焼き払われる(またはエッチングされる)複数の部分は、複数の電源およびグランドビア開口22Pおよび22G上に配置されるその複数の部分である。低k値誘電性物質18において、複数の開口は、複数の信号ビア開口22Sが低k値誘電性物質18を通じて垂直に拡張するように、同様に、焼かれる(またはエッチングされる)。

【0016】

キャパシタ構造16は、その後、低k値誘電性物質18が焼き払われた(またはエッチングされた)焼結セラミックベース構造12の上に形成される。つまり、キャパシタ構造16は、複数の電源およびグランドビア開口22Pおよび22Gを備える焼結セラミックベース構造12の上面のエリア上に形成される。キャパシタ構造16は、複数の電源グランドプレーン24および26ならびに誘電性レイヤ28を備える。複数の電源およびグランドプレーンは、一般的に銅またはプラチナからできている。誘電性レイヤ28は、300と900との間の誘電定数を備える高k値誘電性物質からできてもよいが、誘電定数は、3000と同じ高さでもよい。絶縁レイヤ30は、第二のキャパシタンスを追加するためにグランドプレーン26の上部に形成され、誘電性レイヤ28と同じ物質からできている。より多くの複数のレイヤは、余分のキャパシタンスのために追加されることができる。複数のレイヤおよび複数のプレーン24、26、28および30は、複数の電源およびグランドビア開口22Pおよび22Gが全体のキャパシタ構造16を通じて垂直に拡張するように、全てパターニングされる。キャパシタ構造16などの複数の薄膜キャパシタ構造の製造は、技術的に知られる。

【0017】

複数のビア開口22は、全てその後、複数の導電性ビア14で満たされる。複数の導電性ビア14は、一般的に、銅、銀またはタングステンおよびモリブデンの合金などの導電性物質から形成される。複数の導電性ビアは、例えば、複数のビア開口22の中にスパッタ堆積され、メッキされまたはプリントされる。複数の導電性ビア14は、複数のビア開口22P、22Gおよび22Sの中にそれぞれ複数の電源、グランドおよび信号導電性ビア14P、14Gおよび14Sを備える。電源導電性ビア14Pは、電源プレーン24と接触しており、グランドプレーン26とは接触していない。グランド導電性ビア14Gは、グランドプレーン26と接触しており、電源プレーン24とは接触していない。それぞれの信号導電性ビア14Sは、電気的に全ての他の導電性ビア14P、14Gおよび14Sから切断されている。

【0018】

複数のコンタクトパッド20は、キャパシタ構造16および低k値誘電性物質18の上に形成される。それぞれのコンタクトパッド20は、複数の導電性ビア14のそれぞれの1つの上に配置されおよびに電気的に接続される。

【0019】

図2は、本発明の一実施形態に係る集積回路パッケージ34内のインターポーザ基板10を説明する。集積回路パッケージ34は、キャリア基板36、パッケージ基板38、ダイ40ならびに複数の導電性相互接続メンバー42、44、および46のそれぞれの複数の組をさらに備える。

【0020】

パッケージ基板38は、ベース構造48、ベース構造48内の複数の導電性ライン50、ベース構造48の下面に接する複数のコンタクトパッド52、およびベース構造48の上面に接する複数のコンタクトパッド54を有する。ベース構造48は、低k値誘電性物質からできている。与えられる例において、複数の導電性ライン50のそれぞれの1つは、複数のコンタクトパッド52のそれぞれの1つを複数のコンタクトパッド54のそれぞれの1つに相互接続する。複数の導電性ライン50の幾つかは、水平のライン60により相互接続される2つの垂直のビア56および58を有する。水平のライン60の包含は、複数のコンタクトパッド54が複数のコンタクトパッド52に対してオフセットを有することを可能にする。複数の導電性ライン50は、したがって、複数のコンタクトパッド52から複数のコンタクトパッド54へのx−y変換を可能にする。

【0021】

説明されるように、インターポーザ基板10は、焼結セラミックベース構造12の下面に接する複数のコンタクトパッド62をさらに有する。インターポーザ基板10の下面側の複数のコンタクトパッド62からインターポーザ基板10の上面側の複数のコンタクトパッド20へのx−y変換はない。複数のコンタクトパッド62のそれぞれの1つは、複数のパッド54のそれぞれの1つと調和し、複数の導電性相互接続メンバー44のそれぞれの1つは、複数のコンタクトパッド62のそれぞれの1つを複数のコンタクトパッド54のそれぞれの1つと相互接続する。

【0022】

ダイ40は、その下面に形成された集積回路を有する。複数のコンタクトパッド64は、ダイ40の下面に接して形成され、集積回路に電気的に接続される。複数のコンタクトパッド64のそれぞれの1つは、複数のコンタクトパッド20のそれぞれの1つと調和し、複数の導電性相互接続メンバー46のそれぞれの1つにより、そこへ接続される。複数のコンタクトパッド64から複数のコンタクトパッド54へのx−y変換がないことおよび複数のコンタクトパッド54から複数のコンタクトパッド52へのx−y変換があることが、したがって見られる。

【0023】

キャリア基板36は、それぞれのベース構造66およびベース構造66の上面に形成される複数のコンタクトパッド68を有する。複数のコンタクトパッド52のそれぞれの1つは、複数のコンタクトパッド68のそれぞれの1つに足並みを揃え、そこへ複数の導電性相互接続メンバー42のそれぞれの1つにより接続される。

【0024】

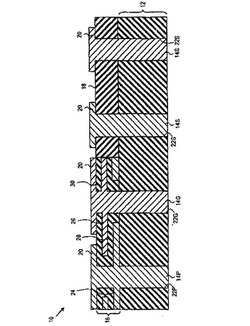

図3は、本発明の他の実施形態に係るパッケージ基板138を説明する。パッケージ基板138は、図1のインターポーザ基板10の焼結セラミックベース構造12、キャパシタ構造16、および複数のコンタクトパッド20と同じ、焼結セラミックベース構造112、キャパシタ構造116、低k値誘電性物質118、および複数のコンタクトパッド120を備える。パッケージ基板138は、複数の導電性ビア14の代わりに複数の導電性ライン150が提供されることが、インターポーザ基板10と異なる。

【0025】

複数の導電性ラインのそれぞれの1つは、2つの垂直のビア156および158ならびに複数のビア156および158を相互接続する水平のライン160を有する。焼結セラミックベース構造112は、水平のライン160が焼結セラミックベース構造112の上面の下に埋められるように段階的に形成される。水平のライン160は、垂直の複数のビア156および158が、水平に互いに対してオフセットを有することを可能にする。水平の複数のライン160は、したがって、垂直の複数のビア156上の垂直の複数のビア158へのx−y変換を可能にする。

【0026】

図4は、パッケージ基板138、キャリア基板136およびダイ140を備える集積回路パッケージを説明する。ダイ140およびキャリア基板136は、図2の集積回路パッケージ34のダイ40およびキャリア基板36と同じである。集積回路パッケージ134は、ダイ140とパッケージ基板138との間に中間のインターポーザ基板がないことが、集積回路パッケージ34と異なる。図2の集積回路パッケージ34において、インターポーザ基板10は、キャパシタ構造16をダイ40の近くに提供し、パッケージ基板38は、x−y変換を提供する。図4の集積回路パッケージ134においては、対照的に、パッケージ基板138が、キャパシタ構造116をダイ140の近くに提供し、x−y変換を提供する。

【0027】

特定の例となる複数の実施形態が説明され、添付の複数の図面が示されたが、そのような複数の実施形態は、単に説明に役立ち、本発明の制限ではないこと、および複数の修正が当業者には思い浮かぶので、複数の本発明は、示されおよび説明される特定の複数の構造および複数の配置に制限されないことは、理解されるべきである。

【技術分野】

【0001】

本発明は、集積回路パッケージの基板内に備えられるキャパシタ構造に関する。

【背景技術】

【0002】

複数の集積回路は、通常、複数のウエハ基板上に製造される。ウエハ基板は、その後、個々の複数のダイに"ダイシング"され、または"シンギュレーション"され、それぞれのダイは、それぞれの集積回路を持つ。ダイは、その後、しばしば中間のインターポーザ基板を伴い、パッケージ基板上に実装される。基板または複数の基板は、結果の集積回路パッケージに構造上の剛性を提供する。パッケージ基板は、同様に、ダイの複数のコンタクトからその上に集積回路パッケージが実装されるキャリア基板上の複数のコンタクトへのx−y変換を提供する。

【0003】

複数の信号は、基板または複数の基板内の複数のコンダクタを介して、ダイの中の集積回路へおよびから提供される。レジスタンス−キャパシタンス−インダクタンス遅延と称される信号遅延は、複数の信号が複数のコンダクタを介して送信される場合にしばしば生じる。レジスタンス−キャパシタンス−インダクタンス遅延を低減するために、ダイの近くにキャパシタが提供される。キャパシタは、集積回路の近くで、電力の貯蔵所として動作する。

【0004】

複数のディスクリートキャパシタは、比較的大きく、したがって、基板上の大きな面積を占める。複数の薄膜は、小さな面積をしめ、多くのキャパシタが形成されることを可能にすることが理解されている。基板の製造の間に複数の薄膜キャパシタを製造することは、複数のディスクリートキャパシタを基板に実装することよりも、同様に単純である。

【0005】

複数のビア開口は、基板のベース構造に製造されなくてはならず、ここに複数の導電性ビアが形成されなくてならず、ここに薄膜キャパシタ構造の複数の電源およびグランドプレーンは接続されなくてはならない。そのような複数のビア開口の形成は、半導体産業の長年にわたる最大の関心事である。これまでは、全ての努力は、シリコンなどの複数の低k値物質内でドリルで複数の開口を開けることに向けられてきた。シリコンは、もろい物質であり、そこにドリルで複数の開口を開けることを難しくする。それぞれの開口は、同様に、個々にドリルで開けられなくてはならず、スループットを低減させる。

【図面の簡単な説明】

【0006】

本発明は、添付の複数の図面への参照を伴う複数の例により説明される。

【0007】

【図1】本発明の一実施形態に従って製造されたインターポーザ基板の側断面図である。

【0008】

【図2】図1のインターポーザ基板を備える集積回路パッケージの側断面図である。

【0009】

【図3】本発明の一実施形態に従って製造されたパッケージ基板の側断面図である。

【0010】

【図4】図3のパッケージ基板を備える集積回路パッケージの側断面図である。

【発明の詳細な説明】

【0011】

集積回路パッケージのパッケージ基板またはインターポーザ基板などの基板の製造が、説明される。ベース構造は、複数のビア開口をそこに備える未加工の物質から形成される。未加工の物質は、その後、未加工の物質が焼結セラミック物質になり、およびベース構造が複数のビア開口を備える焼結セラミックベース構造になるように焼結される。導電性ビアは、焼結セラミックベース構造のそれぞれのビア開口内に形成される。キャパシタ構造は、焼結セラミックベース構造上に形成される。キャパシタ構造の複数の電源およびグランドプレーンは、複数のビアに接続される。そのようなものとして、複数のシリコン基板のような複数のもろい基板内で複数のビア開口をドリルで開ける必要なしに、キャパシタ構造は、形成され、および複数のビアに接続されることができる。焼結セラミック物質は、同様に、熱膨張の低い係数を有し、キャパシタ構造を製造する時の複数の高温処理条件に耐えることができ、および、製造が高価ではない。

【0012】

添付の複数の図面の図1は、本発明の一実施形態の方法に従って構築されたインターポーザ基板10を説明する。インターポーザ基板10は、ベース構造12、複数の導電性ビア14、高k値誘電性物質を有するキャパシタ構造16、低k値誘電性物質18、および複数のコンタクトパッド20を備える。

【0013】

ベース構造12は、はじめに、未加工の焼結されていない物質からできている。未加工の物質は、ベース構造12の形のパッケージであり、複数のビア開口は22は、未加工の物質を突き抜けられる。未加工の物質のハンドリング、パッケージングおよびパンチングは、技術的に知られる。未加工の物質内の複数のパンチングホールの利点は、未加工の物質は、複数のシリコン基板などの他の複数の基板ほどもろくないことである。未加工の物質は、その後、未加工の物質が焼結セラミック物質になりおよびベース構造12が焼結セラミックベース構造12になるように、焼結される。焼結セラミックベース構造12は、複数のビア開口22を備える。複数のビア開口22は、電源ビア開口22P、グランドビア開口22G、および複数の信号ビア開口22Sを有する。複数のビア開口22のそれぞれ1つは、水平な焼結セラミックベース構造12の下面から上面へ拡張する。

【0014】

低k値誘電性物質18は、焼結セラミックベース構造12の上面全体の上に形成される。低k値誘電性物質18は、したがって、複数の電源、グランドおよび信号ビア開口22P、22Gおよび22Sを覆う。低k値誘電性物質18は、一般的に、二酸化シリコンからできており、3と4との間の誘電定数を有する。

【0015】

低k値誘電性物質18は、その後、パターニングされる。低k値誘電性物質18は、例えば、第一に、その部分を覆い、次に露出された複数の部分を焼き払うことでパターニングされる。焼き払われる(またはエッチングされる)複数の部分は、複数の電源およびグランドビア開口22Pおよび22G上に配置されるその複数の部分である。低k値誘電性物質18において、複数の開口は、複数の信号ビア開口22Sが低k値誘電性物質18を通じて垂直に拡張するように、同様に、焼かれる(またはエッチングされる)。

【0016】

キャパシタ構造16は、その後、低k値誘電性物質18が焼き払われた(またはエッチングされた)焼結セラミックベース構造12の上に形成される。つまり、キャパシタ構造16は、複数の電源およびグランドビア開口22Pおよび22Gを備える焼結セラミックベース構造12の上面のエリア上に形成される。キャパシタ構造16は、複数の電源グランドプレーン24および26ならびに誘電性レイヤ28を備える。複数の電源およびグランドプレーンは、一般的に銅またはプラチナからできている。誘電性レイヤ28は、300と900との間の誘電定数を備える高k値誘電性物質からできてもよいが、誘電定数は、3000と同じ高さでもよい。絶縁レイヤ30は、第二のキャパシタンスを追加するためにグランドプレーン26の上部に形成され、誘電性レイヤ28と同じ物質からできている。より多くの複数のレイヤは、余分のキャパシタンスのために追加されることができる。複数のレイヤおよび複数のプレーン24、26、28および30は、複数の電源およびグランドビア開口22Pおよび22Gが全体のキャパシタ構造16を通じて垂直に拡張するように、全てパターニングされる。キャパシタ構造16などの複数の薄膜キャパシタ構造の製造は、技術的に知られる。

【0017】

複数のビア開口22は、全てその後、複数の導電性ビア14で満たされる。複数の導電性ビア14は、一般的に、銅、銀またはタングステンおよびモリブデンの合金などの導電性物質から形成される。複数の導電性ビアは、例えば、複数のビア開口22の中にスパッタ堆積され、メッキされまたはプリントされる。複数の導電性ビア14は、複数のビア開口22P、22Gおよび22Sの中にそれぞれ複数の電源、グランドおよび信号導電性ビア14P、14Gおよび14Sを備える。電源導電性ビア14Pは、電源プレーン24と接触しており、グランドプレーン26とは接触していない。グランド導電性ビア14Gは、グランドプレーン26と接触しており、電源プレーン24とは接触していない。それぞれの信号導電性ビア14Sは、電気的に全ての他の導電性ビア14P、14Gおよび14Sから切断されている。

【0018】

複数のコンタクトパッド20は、キャパシタ構造16および低k値誘電性物質18の上に形成される。それぞれのコンタクトパッド20は、複数の導電性ビア14のそれぞれの1つの上に配置されおよびに電気的に接続される。

【0019】

図2は、本発明の一実施形態に係る集積回路パッケージ34内のインターポーザ基板10を説明する。集積回路パッケージ34は、キャリア基板36、パッケージ基板38、ダイ40ならびに複数の導電性相互接続メンバー42、44、および46のそれぞれの複数の組をさらに備える。

【0020】

パッケージ基板38は、ベース構造48、ベース構造48内の複数の導電性ライン50、ベース構造48の下面に接する複数のコンタクトパッド52、およびベース構造48の上面に接する複数のコンタクトパッド54を有する。ベース構造48は、低k値誘電性物質からできている。与えられる例において、複数の導電性ライン50のそれぞれの1つは、複数のコンタクトパッド52のそれぞれの1つを複数のコンタクトパッド54のそれぞれの1つに相互接続する。複数の導電性ライン50の幾つかは、水平のライン60により相互接続される2つの垂直のビア56および58を有する。水平のライン60の包含は、複数のコンタクトパッド54が複数のコンタクトパッド52に対してオフセットを有することを可能にする。複数の導電性ライン50は、したがって、複数のコンタクトパッド52から複数のコンタクトパッド54へのx−y変換を可能にする。

【0021】

説明されるように、インターポーザ基板10は、焼結セラミックベース構造12の下面に接する複数のコンタクトパッド62をさらに有する。インターポーザ基板10の下面側の複数のコンタクトパッド62からインターポーザ基板10の上面側の複数のコンタクトパッド20へのx−y変換はない。複数のコンタクトパッド62のそれぞれの1つは、複数のパッド54のそれぞれの1つと調和し、複数の導電性相互接続メンバー44のそれぞれの1つは、複数のコンタクトパッド62のそれぞれの1つを複数のコンタクトパッド54のそれぞれの1つと相互接続する。

【0022】

ダイ40は、その下面に形成された集積回路を有する。複数のコンタクトパッド64は、ダイ40の下面に接して形成され、集積回路に電気的に接続される。複数のコンタクトパッド64のそれぞれの1つは、複数のコンタクトパッド20のそれぞれの1つと調和し、複数の導電性相互接続メンバー46のそれぞれの1つにより、そこへ接続される。複数のコンタクトパッド64から複数のコンタクトパッド54へのx−y変換がないことおよび複数のコンタクトパッド54から複数のコンタクトパッド52へのx−y変換があることが、したがって見られる。

【0023】

キャリア基板36は、それぞれのベース構造66およびベース構造66の上面に形成される複数のコンタクトパッド68を有する。複数のコンタクトパッド52のそれぞれの1つは、複数のコンタクトパッド68のそれぞれの1つに足並みを揃え、そこへ複数の導電性相互接続メンバー42のそれぞれの1つにより接続される。

【0024】

図3は、本発明の他の実施形態に係るパッケージ基板138を説明する。パッケージ基板138は、図1のインターポーザ基板10の焼結セラミックベース構造12、キャパシタ構造16、および複数のコンタクトパッド20と同じ、焼結セラミックベース構造112、キャパシタ構造116、低k値誘電性物質118、および複数のコンタクトパッド120を備える。パッケージ基板138は、複数の導電性ビア14の代わりに複数の導電性ライン150が提供されることが、インターポーザ基板10と異なる。

【0025】

複数の導電性ラインのそれぞれの1つは、2つの垂直のビア156および158ならびに複数のビア156および158を相互接続する水平のライン160を有する。焼結セラミックベース構造112は、水平のライン160が焼結セラミックベース構造112の上面の下に埋められるように段階的に形成される。水平のライン160は、垂直の複数のビア156および158が、水平に互いに対してオフセットを有することを可能にする。水平の複数のライン160は、したがって、垂直の複数のビア156上の垂直の複数のビア158へのx−y変換を可能にする。

【0026】

図4は、パッケージ基板138、キャリア基板136およびダイ140を備える集積回路パッケージを説明する。ダイ140およびキャリア基板136は、図2の集積回路パッケージ34のダイ40およびキャリア基板36と同じである。集積回路パッケージ134は、ダイ140とパッケージ基板138との間に中間のインターポーザ基板がないことが、集積回路パッケージ34と異なる。図2の集積回路パッケージ34において、インターポーザ基板10は、キャパシタ構造16をダイ40の近くに提供し、パッケージ基板38は、x−y変換を提供する。図4の集積回路パッケージ134においては、対照的に、パッケージ基板138が、キャパシタ構造116をダイ140の近くに提供し、x−y変換を提供する。

【0027】

特定の例となる複数の実施形態が説明され、添付の複数の図面が示されたが、そのような複数の実施形態は、単に説明に役立ち、本発明の制限ではないこと、および複数の修正が当業者には思い浮かぶので、複数の本発明は、示されおよび説明される特定の複数の構造および複数の配置に制限されないことは、理解されるべきである。

【特許請求の範囲】

【請求項1】

集積回路パッケージの少なくとも一部分を構築する方法であって、

複数のビア開口を備える未加工の物質のベース構造を形成する段階、

前記未加工の物質が焼結セラミック物質になりおよび前記ベース構造が前記複数のビア開口を有する焼結セラミックベース構造になるように前記未加工の物質を焼結する段階、

前記焼結セラミックベース構造のそれぞれのビア開口の中に導電性ビアを形成する段階であって、前記複数のビアは、少なくとも電源ビアおよびグランドビアを有する段階、および

前記焼結セラミックベース構造の上にキャパシタ構造を形成する段階であって、前記キャパシタ構造は、導電性の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ少なくとも前記複数の電源ビアの1つおよび前記複数のグランドビアの1つに電気的に接続する段階

を備える方法。

【請求項2】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンの両方から電気的に切断されている請求項1に記載の方法。

【請求項3】

前記キャパシタ構造の前記誘電性レイヤは、高k値の誘電性物質からできており、前記基板は、第一のおよび第二の複数の部分を有し、前記第一の部分は、前記高k値の誘電性物質を含み、前記第二の部分は、前記高k値を含まず、前記複数の信号ビアは、前記第二の部分に形成される請求項2に記載の方法。

【請求項4】

前記パッケージ基板の上に前記キャパシタ構造を伴う前記ベース構造を実装する段階であって、連帯してインターポーザ基板を形成する段階、および

形成される超小型電子回路を有するダイを前記インターポーザ基板に実装する段階

をさらに備える請求項1に記載の方法。

【請求項5】

キャリア基板との相互接続のために、前記パッケージ基板に接する複数の導電性メンバーを形成する段階をさらに備える請求項4に記載の方法。

【請求項6】

形成される複数のビア開口を有する焼結セラミックベース構造、

少なくとも電源ビアおよびグランドビアを有する、それぞれのビア開口の中の導電性ビア、および

前記焼結セラミックベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、導電性の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記電源ビアおよび前記グランドビアの少なくとも1つに電気的に接続されているキャパシタ構造

を備える集積回路パッケージの基板。

【請求項7】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンから電気的に切断されている請求項6に記載の基板。

【請求項8】

前記キャパシタ構造の前記誘電性レイヤは、高k値の誘電性物質からできており、前記基板は、第一のおよび第二の複数の部分を有しており、前記第一の部分は、前記高k値の誘電性物質を有しており、前記第二の部分は、前記高k値の誘電性物質を有しておらず、前記複数の信号ビアは、前記第二の部分に形成される請求項7に記載の基板。

【請求項9】

集積回路ダイのためのパッケージ基板であって、

水平の複数の誘電性レイヤおよび前記複数の誘電性レイヤの2つの間の、複数の金属コンダクタの少なくとも1つの水平のレイヤを有し、複数の垂直に拡張する複数のビア開口を有するベース構造、

それぞれのビア開口の中の導電性のビアであって、前記複数の導電性のビアは、少なくとも導電性の電源ビアおよび導電性のグランドビアを有するビア、および

前記ベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、水平の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の水平の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記電源ビアおよび前記グランドビアの少なくとも1つに電気的に接続されているキャパシタ構造

を備えるパッケージ基板。

【請求項10】

前記ベース構造は、焼結セラミック物質からできている請求項9に記載のパッケージ基板。

【請求項11】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンから電気的に切断されている請求項9に記載のパッケージ基板。

【請求項12】

前記複数の電源、グランドおよび信号ビアは、それぞれ前記キャパシタ構造の複数の電源、グランドおよび信号コンダクタに接続されている請求項11に記載のパッケージ基板。

【請求項13】

前記ベース構造に接するの第一の複数のコンタクト、および

前記キャパシタ構造の上の第二の複数のコンタクトであって、前記複数の金属コンダクタは、前記第一の複数のコンタクトから前記第二の複数のコンタクトへのx−y変換を作り出す第二の複数のコンタクト

をさらに備える請求項9に記載のパッケージ基板。

【請求項14】

形成された複数のビア開口を含む焼結セラミックベース構造を有する基板、

それぞれのビア開口の中の導電性ビアであって、前記複数の導電性ビアは、少なくとも電源ビアおよびグランドビアを有する導電性ビア、

前記焼結セラミックベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、導電性電源プレーンおよび導電性グランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記複数の電源およぼグランドバイアスの少なくとも1つに電気的に接続されているキャパシタ構造、および

前記基板の上に実装され、形成された集積回路を有するダイ

を備える集積回路パッケージ。

【請求項15】

前記基板は、インターポーザ基板であり、

前記インターポーザ基板が実装されるパッケージ基板をさらに備える請求項14に記載の集積回路パッケージ。

【請求項16】

前記複数のビアは、x−y変換なしに、前記パッケージ基板の上の複数のコンタクトに接続される請求項15に記載の集積回路パッケージ。

【請求項17】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンの両方から電気的に切断されている請求項14に記載の集積回路パッケージ。

【請求項18】

水平の複数の誘電性レイヤおよび前記複数の誘電性レイヤの2つの間の、複数の金属コンダクタの少なくとも1つの水平のレイヤを含み、複数の垂直に拡張する複数のビア開口を含むベース構造を有する基板、

少なくとも電源ビアおよびグランドビアを有する、それぞれのビア開口の中の導電性ビア、

前記ベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、水平の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の水平の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記電源ビアおよび前記グランドビアの少なくとも1つに電気的に接続されているキャパシタ構造、および

前記基板の上に実装され、形成された集積回路を有するダイ

を備える集積回路パッケージ。

【請求項19】

前記ベース構造は、焼結セラミック物質からできている請求項18に記載の集積回路パッケージ。

【請求項20】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンから電気的に切断されている請求項18に記載の集積回路パッケージ。

【請求項21】

前記複数の電源、グランドおよび信号ビアは、それぞれ前記複数の金属コンダクタの複数の電源、グランドおよび信号コンダクタに接続されている請求項20に記載の集積回路パッケージ。

【請求項22】

前記ダイは、介在するインターポーザ基板なしに前記基板に実装される請求項18に記載の集積回路パッケージ。

【請求項1】

集積回路パッケージの少なくとも一部分を構築する方法であって、

複数のビア開口を備える未加工の物質のベース構造を形成する段階、

前記未加工の物質が焼結セラミック物質になりおよび前記ベース構造が前記複数のビア開口を有する焼結セラミックベース構造になるように前記未加工の物質を焼結する段階、

前記焼結セラミックベース構造のそれぞれのビア開口の中に導電性ビアを形成する段階であって、前記複数のビアは、少なくとも電源ビアおよびグランドビアを有する段階、および

前記焼結セラミックベース構造の上にキャパシタ構造を形成する段階であって、前記キャパシタ構造は、導電性の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ少なくとも前記複数の電源ビアの1つおよび前記複数のグランドビアの1つに電気的に接続する段階

を備える方法。

【請求項2】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンの両方から電気的に切断されている請求項1に記載の方法。

【請求項3】

前記キャパシタ構造の前記誘電性レイヤは、高k値の誘電性物質からできており、前記基板は、第一のおよび第二の複数の部分を有し、前記第一の部分は、前記高k値の誘電性物質を含み、前記第二の部分は、前記高k値を含まず、前記複数の信号ビアは、前記第二の部分に形成される請求項2に記載の方法。

【請求項4】

前記パッケージ基板の上に前記キャパシタ構造を伴う前記ベース構造を実装する段階であって、連帯してインターポーザ基板を形成する段階、および

形成される超小型電子回路を有するダイを前記インターポーザ基板に実装する段階

をさらに備える請求項1に記載の方法。

【請求項5】

キャリア基板との相互接続のために、前記パッケージ基板に接する複数の導電性メンバーを形成する段階をさらに備える請求項4に記載の方法。

【請求項6】

形成される複数のビア開口を有する焼結セラミックベース構造、

少なくとも電源ビアおよびグランドビアを有する、それぞれのビア開口の中の導電性ビア、および

前記焼結セラミックベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、導電性の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記電源ビアおよび前記グランドビアの少なくとも1つに電気的に接続されているキャパシタ構造

を備える集積回路パッケージの基板。

【請求項7】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンから電気的に切断されている請求項6に記載の基板。

【請求項8】

前記キャパシタ構造の前記誘電性レイヤは、高k値の誘電性物質からできており、前記基板は、第一のおよび第二の複数の部分を有しており、前記第一の部分は、前記高k値の誘電性物質を有しており、前記第二の部分は、前記高k値の誘電性物質を有しておらず、前記複数の信号ビアは、前記第二の部分に形成される請求項7に記載の基板。

【請求項9】

集積回路ダイのためのパッケージ基板であって、

水平の複数の誘電性レイヤおよび前記複数の誘電性レイヤの2つの間の、複数の金属コンダクタの少なくとも1つの水平のレイヤを有し、複数の垂直に拡張する複数のビア開口を有するベース構造、

それぞれのビア開口の中の導電性のビアであって、前記複数の導電性のビアは、少なくとも導電性の電源ビアおよび導電性のグランドビアを有するビア、および

前記ベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、水平の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の水平の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記電源ビアおよび前記グランドビアの少なくとも1つに電気的に接続されているキャパシタ構造

を備えるパッケージ基板。

【請求項10】

前記ベース構造は、焼結セラミック物質からできている請求項9に記載のパッケージ基板。

【請求項11】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンから電気的に切断されている請求項9に記載のパッケージ基板。

【請求項12】

前記複数の電源、グランドおよび信号ビアは、それぞれ前記キャパシタ構造の複数の電源、グランドおよび信号コンダクタに接続されている請求項11に記載のパッケージ基板。

【請求項13】

前記ベース構造に接するの第一の複数のコンタクト、および

前記キャパシタ構造の上の第二の複数のコンタクトであって、前記複数の金属コンダクタは、前記第一の複数のコンタクトから前記第二の複数のコンタクトへのx−y変換を作り出す第二の複数のコンタクト

をさらに備える請求項9に記載のパッケージ基板。

【請求項14】

形成された複数のビア開口を含む焼結セラミックベース構造を有する基板、

それぞれのビア開口の中の導電性ビアであって、前記複数の導電性ビアは、少なくとも電源ビアおよびグランドビアを有する導電性ビア、

前記焼結セラミックベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、導電性電源プレーンおよび導電性グランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記複数の電源およぼグランドバイアスの少なくとも1つに電気的に接続されているキャパシタ構造、および

前記基板の上に実装され、形成された集積回路を有するダイ

を備える集積回路パッケージ。

【請求項15】

前記基板は、インターポーザ基板であり、

前記インターポーザ基板が実装されるパッケージ基板をさらに備える請求項14に記載の集積回路パッケージ。

【請求項16】

前記複数のビアは、x−y変換なしに、前記パッケージ基板の上の複数のコンタクトに接続される請求項15に記載の集積回路パッケージ。

【請求項17】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンの両方から電気的に切断されている請求項14に記載の集積回路パッケージ。

【請求項18】

水平の複数の誘電性レイヤおよび前記複数の誘電性レイヤの2つの間の、複数の金属コンダクタの少なくとも1つの水平のレイヤを含み、複数の垂直に拡張する複数のビア開口を含むベース構造を有する基板、

少なくとも電源ビアおよびグランドビアを有する、それぞれのビア開口の中の導電性ビア、

前記ベース構造の上のキャパシタ構造であって、前記キャパシタ構造は、水平の電源プレーンおよびグランドプレーンならびに前記電源プレーンと前記グランドプレーンとの間の水平の誘電性レイヤを有し、前記電源プレーンおよび前記グランドプレーンは、それぞれ前記電源ビアおよび前記グランドビアの少なくとも1つに電気的に接続されているキャパシタ構造、および

前記基板の上に実装され、形成された集積回路を有するダイ

を備える集積回路パッケージ。

【請求項19】

前記ベース構造は、焼結セラミック物質からできている請求項18に記載の集積回路パッケージ。

【請求項20】

前記複数のビアは、複数の信号ビアを備え、それぞれの信号ビアは、前記電源プレーンおよび前記グランドプレーンから電気的に切断されている請求項18に記載の集積回路パッケージ。

【請求項21】

前記複数の電源、グランドおよび信号ビアは、それぞれ前記複数の金属コンダクタの複数の電源、グランドおよび信号コンダクタに接続されている請求項20に記載の集積回路パッケージ。

【請求項22】

前記ダイは、介在するインターポーザ基板なしに前記基板に実装される請求項18に記載の集積回路パッケージ。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−84905(P2012−84905A)

【公開日】平成24年4月26日(2012.4.26)

【国際特許分類】

【外国語出願】

【出願番号】特願2011−269359(P2011−269359)

【出願日】平成23年12月8日(2011.12.8)

【分割の表示】特願2006−547214(P2006−547214)の分割

【原出願日】平成16年12月17日(2004.12.17)

【出願人】(591003943)インテル・コーポレーション (1,101)

【公開日】平成24年4月26日(2012.4.26)

【国際特許分類】

【出願番号】特願2011−269359(P2011−269359)

【出願日】平成23年12月8日(2011.12.8)

【分割の表示】特願2006−547214(P2006−547214)の分割

【原出願日】平成16年12月17日(2004.12.17)

【出願人】(591003943)インテル・コーポレーション (1,101)

[ Back to top ]