薄膜コンデンサおよび可変容量コンデンサならびに電子部品

【課題】 耐湿信頼性に優れた薄膜コンデンサおよび可変容量コンデンサならびにそれを用いた電子部品を提供すること。

【解決手段】 支持基板上1に下部電極層2、誘電体層3および上部電極層4を順次被着してなるとともに、これらが絶縁体層5で被覆された容量発生部を設けており、下部電極層2および上部電極層4の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である薄膜コンデンサである。これにより、下部電極層2および上部電極層4の側面からの絶縁体層5の剥がれを有効に防止することができ、高い耐湿信頼性が得られる。

【解決手段】 支持基板上1に下部電極層2、誘電体層3および上部電極層4を順次被着してなるとともに、これらが絶縁体層5で被覆された容量発生部を設けており、下部電極層2および上部電極層4の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である薄膜コンデンサである。これにより、下部電極層2および上部電極層4の側面からの絶縁体層5の剥がれを有効に防止することができ、高い耐湿信頼性が得られる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、誘電体層を薄膜形成方法により形成した薄膜コンデンサ、およびこれを用いた直流バイアス電圧の印加により容量が大きく変化する可変容量コンデンサ、およびこれを複数列に並列接続した薄膜コンデンサアレイ、ならびにこれらを用いた電子部品に関するものである。特に、薄膜コンデンサの電気特性を損なうことなく、かつ容量発生部を被覆する絶縁体層の密着性を向上させることにより、種々の動作環境に対する信頼性を高めた薄膜コンデンサおよび可変容量コンデンサならびに電子部品に関するものである。この電子部品は、特に、耐電力に優れた薄膜コンデンサを用いた高周波用電圧制御型共振器,電圧制御型高周波フィルタ,電圧制御型整合回路素子,電圧制御型アンテナ共用器等に好適なものである。

【背景技術】

【0002】

薄膜コンデンサは、電気絶縁性を有した支持基板上に、薄膜の下部電極層,薄膜誘電体層および薄膜の上部電極層がこの順に積層された構造を有するものが知られている。このような薄膜コンデンサでは、下部電極層および上部電極層がそれぞれスパッタリング法や真空蒸着法等で形成されており、薄膜誘電体層はスパッタリング法やゾルゲル法等で形成されている。また、通常、以下に述べるようなフォトリソグラフィの手法が用いられる。

【0003】

まず、電気絶縁性の支持基板の上面全体に下部電極層となる導体層を形成した後、必要部のみをフォトリソグラフィによってパターニングしたフォトレジストで覆い、その後、ウェットエッチングまたはドライエッチングで不要部を除去して、所定形状の下部電極層を形成する。次に、この支持基板上に薄膜誘電体層となる誘電体層を全面に形成し、下部電極層と同様に、不要部を除去して所定形状の誘電体層を形成する。そして、上部電極層となる導体層を全面に形成し、不要部を除去して所定形状の上部電極層を形成する。また、保護層やハンダ端子部を形成することにより、表面実装が可能な薄膜コンデンサになる。

【0004】

また、薄膜誘電体層の材料としてチタン酸バリウムストロンチウム((BaxSr1−x)yTi1−yO3−z)からなる誘電体材料を用いて、上部電極層と下部電極層との間に所定のバイアス電位を与えることにより薄膜誘電体層の誘電率を変化させて容量を変化させる、いわゆる可変容量薄膜コンデンサも知られており、上記薄膜コンデンサと同様な構造である(例えば、特許文献1を参照。)。

【0005】

この可変容量薄膜コンデンサでは、薄膜誘電体層に直流バイアス電圧を印加することでその誘電率が変化し、その結果として容量が変化するが、この容量変化は高周波領域にも及び、高周波領域でも可変容量薄膜コンデンサとして利用可能となる。このような高周波領域での可変容量薄膜コンデンサの容量変化を利用して、直流バイアス電圧の印加により周波数特性を変化させることができる有用な電子部品が得られる。

【0006】

例えば、上述の可変容量薄膜コンデンサと薄膜インダクタとを組み合わせた電圧制御型薄膜共振器では、直流バイアスの印加により共振周波数を変化させることができる。また、可変容量薄膜コンデンサもしくは電圧制御型薄膜共振器と、薄膜インダクタ,薄膜キャパシタとを組み合わせた電圧制御型薄膜帯域通過フィルタでは、直流バイアス電圧の印加により通過帯域を変化させることができる。また、可変容量薄膜コンデンサはマイクロ波用の電圧制御型電子部品にも利用可能である(例えば、特許文献2を参照。)。

【0007】

上述した薄膜コンデンサおよび可変容量コンデンサならびに電子部品には、電気的な特性のみならず、耐環境特性、例えば高いレベルの耐湿信頼性が要求されるようになってきている。

【特許文献1】特開平11−260667号公報

【特許文献2】特表平8−509103号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

薄膜コンデンサにおいては、容量発生部への外部からの水分の進入を防いで耐湿性を向上させる目的で、下部電極層,誘電体層および上部電極層を被覆する絶縁体層が形成される。絶縁体層の材料としては、水分の透過係数が小さい無機材料や、作製プロセスが簡便な有機材料あるいは樹脂等が例として挙げられる。特に、絶縁体層として二酸化シリコン等の薄膜無機材料を用いた場合には、下部電極層,誘電体層および上部電極層との密着性が悪く、さらに製造プロセスにおいて薄膜に残留する内部応力の影響で、絶縁体層が剥離したり、膜にクラックが生じたりする問題が発生する。

【0009】

さらに、薄膜コンデンサを作製する際には、通常、下部電極層,薄膜誘電体層,上部電極層,絶縁体層の他に、半田拡散防止層や保護層等の他の機能を担う層を順次被着していく。しかし、層の数が多くなればなるほど、フォトリソグラフィでの位置ずれの問題や、エッチングの際の下の層へのダメージといった問題の他、層の数が増えることで応力が増大し、その結果、膜に剥離やクラックが生じるなど、特性不良が発生したり信頼性が低下したりしてしまうという問題点がある。

【0010】

特に、絶縁体層として二酸化シリコンをスパッタリング法またはCVD法によって形成した場合には、支持基板に対して垂直に絶縁体層を形成する材料の粒子が飛来し堆積する。従って、下部電極層および上部電極層の側面が支持基板に対して垂直に加工された場合に、下部電極層および上部電極層の側面には回り込こんでくるエネルギーの小さい粒子のみが付着して成長するため、下部電極層および上部電極層の側面に形成される絶縁体層は剥離しやすくなる。

【0011】

また、薄膜コンデンサをフィルタ,共振器などの構成部品として電子部品に使用するためには、上部電極層と下部電極層との短絡等によるリーク電流が小さいことが求められている。これは、薄膜コンデンサは常に電圧が印加された状態で使用されるので、わずかなリーク電流も素子のショートや誘電特性劣化の原因となるからである。特に、薄膜誘電体層が非常に薄くなった場合には、リーク電流が増大する傾向にあるという問題があった。

【0012】

本発明は上述の諸問題に鑑みて案出されたものであり、本発明の目的は、下部電極層および上部電極層に対する絶縁体層の密着性を向上させることができ、絶縁体層の剥離を防止し、信頼性に優れ、特性不良を抑制することができる薄膜コンデンサおよびそれを用いた可変容量コンデンサを提供することにある。

【0013】

また、本発明の他の目的は、本発明の薄膜コンデンサにおいて、リーク電流を低減させた薄膜コンデンサを提供することにある。

【0014】

さらに本発明の他の目的は、本発明の薄膜コンデンサまたは可変容量コンデンサを用いて、信頼性の高い高周波用の電圧制御型薄膜共振器,電圧制御型薄膜高周波フィルタ,電圧制御型整合回路素子,電圧制御型薄膜アンテナ共用器等の電子部品を提供することにある。

【課題を解決するための手段】

【0015】

本発明の薄膜コンデンサは、1)支持基板上に下部電極層、誘電体層および上部電極層を順次被着してなるとともに、これらが絶縁体層で被覆された容量発生部を設けており、前記下部電極層および前記上部電極層の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることを特徴とするものである。

【0016】

また、本発明の薄膜コンデンサは、2)上記1)の構成において、前記誘電体層は、上面が下面より小さいことを特徴とするものである。

【0017】

また、本発明の薄膜コンデンサは、3)上記1),2)の各構成において、前記誘電体層の下面が前記下部電極層の上面より小さく、前記上部電極層の下面が前記誘電体層の上面より小さいことを特徴とするものである。

【0018】

また、本発明の薄膜コンデンサは、4)上記1)〜3)の各構成において、前記誘電体層は、平面視で前記上部電極層の外側部において、厚さが薄くなっている段部を有することを特徴とするものである。

【0019】

また、本発明の薄膜コンデンサは、5)上記4)の構成において、前記段部は、平面視で前記上部電極層の外周部に、凹部を有することを特徴とするものである。

【0020】

また、本発明の薄膜コンデンサは、6)上記5)の構成において、平面視で前記上部電極層の外周部から前記誘電体層の外周部方向の前記凹部の幅が、前記誘電体層の前記段部における厚さと同じ長さ以上の長さを有することを特徴とするものである。

【0021】

また、本発明の薄膜コンデンサは、7)上記1)〜6)の各構成において、前記誘電体層は、直流バイアス電圧の印加により誘電率が変化する誘電体から成ることを特徴とするものである。

【0022】

また、本発明の可変容量コンデンサは、8)上記7)の構成の本発明の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されていることを特徴とするものである。

【0023】

また、本発明の可変容量コンデンサは、9)上記7)の構成の本発明の薄膜コンデンサが複数個並んだコンデンサ列が複数列、それぞれ対応する前記薄膜コンデンサを並べて並列に配置されているとともに、それら対応する前記薄膜コンデンサ同士を並列接続したことを特徴とするものである。

【0024】

また、本発明の可変容量コンデンサは、10)上記9)の構成において、複数列の前記コンデンサ列は、それぞれ対応する前記薄膜コンデンサが、共通の前記下部電極層上にそれぞれの前記上部電極層が形成されてなることを特徴とするものである。

【0025】

また、本発明の電子部品は、11)上記1)〜7)の構成のいずれかの本発明の薄膜コンデンサまたは上記8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、共振回路の容量素子として用いたことを特徴とするものである。

【0026】

また、本発明の電子部品は、12)上記1)〜7)の構成のいずれかの本発明の薄膜コンデンサまたは上記8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、複数の共振回路同士を接続する容量素子として用いたことを特徴とするものである。

【発明の効果】

【0027】

本発明の薄膜コンデンサによれば、1)支持基板上に下部電極層、誘電体層および上部電極層を順次被着してなるとともに、これらが絶縁体層で被覆された容量発生部を設けており、下部電極層の上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である場合には、下部電極層の側面に被覆される絶縁体層のカバレッジを局所的に向上させることができ、絶縁体層としてエネルギーの大きい粒子が堆積されることとなるため、下部電極層の側面からの絶縁体層の剥離を有効に防止することができる。また、下部電極層の側面が斜面構造を有しているので、これに被覆される絶縁体層の内部応力を低減することができ、絶縁体層の密着性を向上させて剥離を有効に防止することができる。さらに、下部電極層の側面が上下方向に筋状の連続的な凹凸を有するので、アンカー効果により絶縁体層の剥離を効果的に抑制することができる。

【0028】

また、本発明の薄膜コンデンサによれば、1)上部電極層の上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である場合には、同様に上部電極層の側面に被覆される絶縁体層のカバレッジを局所的に向上させることができ、絶縁体層としてエネルギーの大きい粒子が堆積されることとなるため、上部電極層の側面からの絶縁体層の剥離を有効に防止することができる。また、上部電極層の側面が斜面構造を有しているので、これに被覆される絶縁体層の内部応力を低減することができ、絶縁体層の密着性を向上させて剥離を有効に防止することができる。さらに、上部電極層の側面が上下方向に筋状の連続的な凹凸を有するので、アンカー効果により絶縁体層の剥離を効果的に抑制することができる。

【0029】

また、本発明の薄膜コンデンサによれば、1)上部電極層および下部電極層の上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である場合には、同様に下部電極層および上部電極層のそれぞれの側面に対する絶縁体層の密着性を向上させることができ、さらに効果的に絶縁体層の剥離を防止することができる。また、絶縁体層の剥離を防止して耐湿性を向上させることができるので、下部電極層と上部電極層との短絡等によるリーク電流を低減することが可能となる。さらに、絶縁体層の剥離を防止して耐湿性を向上できるので、上部電極層および下部電極層が水分により酸化して電極の抵抗値が変化することがなく、下部電極層,誘電体層,上部電極層および絶縁体層からなる容量発生部のQ値が低下することがない。

【0030】

そのため、耐環境性、例えば耐湿性を充分に確保することができ、長期信頼性に優れた薄膜コンデンサを提供することができる。

【0031】

また、本発明の薄膜コンデンサによれば、2)誘電体層は、上面が下面より小さいことにより、下部電極層および上部電極層と同様に誘電体層の側面に対する絶縁体層の密着性を向上させることができ、耐湿性を向上させることができるので、誘電体層が水分により還元されたりすることを防止することができ、誘電体層の誘電特性の劣化を招くことがなく、高いQ値を維持し得る信頼性に優れた薄膜コンデンサを提供することができる。

【0032】

また、本発明の薄膜コンデンサによれば、3)誘電体層の下面が下部電極層の上面より小さく、上部電極層の下面が誘電体層の上面より小さいことにより、その段差形状によって絶縁体層のアンカー効果を向上させることができ、薄膜コンデンサの耐湿信頼性を向上させることができる。さらに、隣接する容量発生部間の距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0033】

また、本発明の薄膜コンデンサによれば、4)上記1)〜3)の各構成において、誘電体層は、平面視で上部電極層の外側部において、厚さが薄くなっている段部を有することにより、誘電体層の表面を介した上部電極層と下部電極層間との距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0034】

また、本発明の薄膜コンデンサによれば、5)上記4)の構成において、段部は、平面視で前記上部電極層の外周部に、凹部を有することにより、4)の構成に比べて、さらに誘電体層の表面を流れる電流経路が長くなるので、さらに効果的に上部電極層の外周部と下部電極層とを隔てて、上部電極層と下部電極層間との距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0035】

また、本発明の薄膜コンデンサによれば、6)上記5)の構成において、平面視で上部電極層の外周部から誘電体層の外周部方向の凹部の幅が、誘電体層の段部における厚さと同じ長さ以上の長さを有することにより、誘電体層内部を流れる電流経路より、誘電体層表面を流れる電流経路の方が確実に長くなるので、薄膜コンデンサのリーク電流に及ぼす誘電体表面を流れるリーク電流の影響を低減できるので、薄膜コンデンサのリーク電流を低減することが可能となる。そのため、薄膜コンデンサのショートや誘電特性劣化を防ぐことができる。

【0036】

また、本発明の薄膜コンデンサによれば、7)上記1)〜6)の各構成において、誘電体層は、直流バイアス電圧の印加により誘電率が変化する誘電体から成ることにより、可変容量素子として障壁容量を用いた可変容量ダイオードを用いた場合に比べて、高周波でも可変容量コンデンサにおける損失を少なくすることができる。また、容量発生部における各層の側面からの絶縁体層の剥離を防止して、耐湿信頼性に優れた可変容量コンデンサを提供することができる。

【0037】

また、本発明の可変容量コンデンサによれば、8)上記7)の構成の本発明の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されていることにより、各々の可変容量素子である薄膜コンデンサに所定の直流バイアス電圧を印加することができ、これにより、直流バイアス電圧による各々の可変容量素子の容量変化率を最大限に利用することができる。また、可変容量素子が複数個、高周波的に直列接続されているため、可変容量素子に印加される高周波電圧が各々の可変容量素子に分圧されるので、個々の可変容量素子に印加される高周波電圧は分圧されて減少することとなり、これによって、可変容量コンデンサの高周波信号に対する容量変動を小さく抑えることができる。このため、可変容量コンデンサの波形歪みや相互変調歪み等を大幅に抑制することができる。しかも、複数の可変容量素子である薄膜コンデンサが高周波的に直列接続されているため、可変容量素子の誘電体層の膜厚を厚くしたのと同じ効果が得られ、可変容量コンデンサの損失抵抗による単位体積当たりの発熱量を小さくすることができる。この結果、可変容量コンデンサの耐電力を向上させることができる。また、各々の可変容量素子である薄膜コンデンサにおいて容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサのリーク電流を低減させることができるので、耐圧信頼性に優れた可変容量コンデンサを提供することができる。

【0038】

また、本発明の可変容量コンデンサによれば、9)上記7)の構成の本発明の薄膜コンデンサが複数個並んだコンデンサ列が複数列、それぞれ対応する薄膜コンデンサを並べて並列に配置されているとともに、それら対応する薄膜コンデンサ同士を並列接続したことにより、簡便な作製(所望の容量値となる数量だけ薄膜コンデンサを並列配置し、必要に応じて一部の薄膜コンデンサの並列接続を切断すること)により、全体の容量値は並列接続される数(n:自然数)だけ大きくなる(nC)(C:並列接続しないときの容量値)。一方、全体の抵抗値は並列接続される数(n)に従い小さくなる(R/n)(R:並列接続しないときの抵抗値)。コンデンサのQ値はQ=1/(2πfRC)(f:周波数(Hz))で表わされるため、並列接続しない場合と比べて容量値が大きく同等のQ値をもつ薄膜コンデンサを実現できる。また、並列接続された薄膜コンデンサの一部を切断することによって容量値を調整することもできる。また、各々の可変容量素子である薄膜コンデンサにおいて容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサのリーク電流を低減させることができるので、耐圧信頼性に優れた可変容量コンデンサを提供することができる。

【0039】

また、本発明の可変容量コンデンサによれば、10)上記9)の構成において、複数列のコンデンサ列は、等価回路上でバイアスラインおよび補助導体ラインの省略が可能となるため、それぞれ対応する薄膜コンデンサについて共通の下部電極層上にそれぞれの上部電極層を形成することにより、小型化が可能となり、この可変容量コンデンサを実装する実装基板の小型化が可能となる。また、各々の可変容量素子である薄膜コンデンサにおいて容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサのリーク電流を低減させることができるので、耐圧信頼性に優れた可変容量コンデンサを提供することができる。

【0040】

また、本発明の電子部品によれば、11)上記1)〜7)の構成のいずれかの本発明の薄膜コンデンサまたは8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、共振回路の容量素子として用いたことにより、共振回路に必要な様々な容量値に対しても同じQ値の薄膜コンデンサを提供することができるので、共振回路のQ値を大きくし、損失を小さくすることができる。また、可変容量コンデンサを共振回路に用いることにより、電圧を制御することにより複数のコンデンサを用いた場合と同等の複数の容量値が得られるので、少ない部品点数で所望の容量値を得ることができ、かつ本発明の薄膜コンデンサまたは可変容量コンデンサのQ値が高いため、共振回路のQ値を大きくし、損失を小さくすることができる。また、薄膜コンデンサまたは可変容量コンデンサの各容量発生部において容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた電子部品を提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサまたは可変容量コンデンサのリーク電流を低減できるので、耐圧信頼性に優れた電子部品を提供することができる。

【0041】

また、本発明の電子部品によれば、12)上記1)〜7)の構成の本発明の薄膜コンデンサまたは8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、複数の共振回路同士を接続する容量素子として用いたことにより、電圧により容量値の制御が可能となり、共振周波数の変調ができる。さらに、本発明の薄膜コンデンサまたは可変容量コンデンサはQ値が高いので、共振回路のQ値を大きくし、損失を小さくすることができる。また、電圧を制御することにより複数のコンデンサを用いた場合と同等の複数の容量値が得られるので、少ない部品点数で所望の容量値を得ることができ、さらに、薄膜コンデンサまたは可変容量コンデンサの各容量発生部において容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた電子部品を提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサまたは可変容量コンデンサのリーク電流を低減できるので、耐圧信頼性に優れた電子部品を提供することができる。

【発明を実施するための最良の形態】

【0042】

以下に、本発明の実施の形態の例について図面を参照しつつ詳細に説明する。なお、以下に説明する図面において同様の箇所には同じ符号を付すものとする。

【0043】

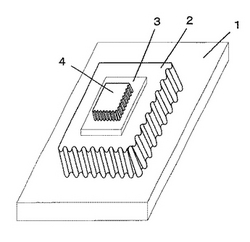

図1は本発明の薄膜コンデンサの実施の形態の一例を模式的に示す断面図であり、容量発生部の数が2の場合の例を示すものである。また、図2は本発明の薄膜コンデンサの実施の形態の一例を模式的に示す斜視図であり、図1における薄膜コンデンサの容量発生部の一部を拡大したものである。

【0044】

図1および図2において、1は支持基板、2は下部電極層、3は下部電極層2上に形成された誘電体層、4は誘電体層3上に形成された上部電極層、5は下部電極層2,誘電体層3および上部電極層4を被覆する絶縁体層、6は下部電極層2,誘電体層3および上部電極層4から構成される容量発生部を直列接続するために設けた引出し電極層、7は容量発生部を被覆する保護層である。図1に示す例においては、下部電極層2および上部電極層4の両方が、上面が下面より小さく、側面が斜面となっている。また、図2に示すように、下部電極層2および上部電極層4の両方が、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面となっている。

【0045】

なお、本発明の薄膜コンデンサは、上記の構成に限定されるものでなく、下部電極層2および上部電極層4の少なくとも一方が、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であればよい。これにより、下部電極層2および上部電極層4の側面に被覆される絶縁体層5によるカバレッジを局所的に向上させることができ、絶縁体層5を形成する際に、材料の粒子が支持基板1の表面に対して垂直に飛来して堆積する場合であっても材料の粒子としてエネルギーの大きい粒子が堆積されることとなるため、絶縁体層5が良好な密着性を有するものとなり、下部電極層2および上部電極層4の側面からの絶縁体層5の剥離を有効に防止することができる。

【0046】

また、下部電極層2および上部電極層4が側面に斜面構造を有しているので、絶縁体層5により下部電極層2および上部電極層4を連続的に被覆することによって、これを被覆する絶縁体層5の内部応力を低減することができ、下部電極層2および上部電極層4の側面に対する絶縁体層5の密着性を向上させて剥離を防止することができる。さらに、下部電極層2および上部電極層4の側面が上下方向に筋状の連続的な凹凸を有するので、アンカー効果により絶縁体層5の剥離を抑制することができる。そして、絶縁体層5の剥離を防止して耐湿性を向上させることができることによって、下部電極層2と上部電極層4との短絡等によるリーク電流を低減することが可能となる。さらに、絶縁体層5の剥離を防止して耐湿性を向上させることができるので、上部電極層2と下部電極層4とが水分により酸化して電極の抵抗値が変化したりすることがなく、下部電極層2、誘電体層3、上部電極層4および絶縁体層5からなる容量発生部のQ値が低下することがない。

【0047】

そのため、本発明の薄膜コンデンサによれば、容量発生部について耐湿性を充分に確保することができ、長期信頼性に優れた薄膜コンデンサを提供することができる。

【0048】

次に、図3は本発明の薄膜コンデンサの実施の形態の他の例を示す模式的な断面図である。図3において図1および図2と同様の箇所には同じ符号を付しているが、図3に示す例では、図1に示した例と同様の構造を有するが、誘電体層3が、上面が下面より小さい台形形状となっている。これにより、誘電体層3の側面に対する絶縁体層5の密着性を向上させることができ、容量発生部の耐湿性をさらに向上させることができるので、誘電体層3が水分により還元されることを防止でき、誘電体層3の誘電特性の劣化を招くことがなく、高いQ値を維持することができる信頼性に優れた薄膜コンデンサを提供することができる。

【0049】

また、誘電体層3は、図2に示す下部電極層2または上部電極層4の形状と同様に、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面となっていると、下部電極層2および上部電極層4の側面と同様にアンカー効果により絶縁体層5の密着性が向上し、薄膜コンデンサの耐湿信頼性を大きく向上させることができるので好ましい。

【0050】

本発明の薄膜コンデンサの実施の形態の例として、図1または図3に示す例のように、誘電体層3の下面が下部電極層2の上面より小さく、上部電極層3の下面が誘電体層3の上面より小さくなっていることが好ましい。これにより、その段差形状により絶縁体層5のアンカー効果をさらに向上させることができ、また下部電極層2および上部電極層4あるいは誘電体層3が側面に斜面構造を有しているので、スパッタリング法またはCVD法により絶縁体層5を形成した場合に、エネルギーの大きい粒子が飛来して下部電極層2および上部電極層4あるいは誘電体層3の斜面に堆積するので、これら各層2,3,4を被覆する絶縁体層5の密着強度を高めることができる。そのため、薄膜コンデンサの耐湿信頼性を向上させることができる。さらに、図3に示す例のように誘電体層3が側面に斜面構造を有していると、図1に示す例のように誘電体層3が側面に斜面構造を有していない場合に比べて、誘電体層3の上面における上部電極層4の端部と誘電体層3の下面における下部電極層2の端部との距離を長くすることができるので、薄膜コンデンサの下部電極層2と上部電極層4との間に生じるリーク電流を低減することが可能となる。

【0051】

次に、図4は本発明の薄膜コンデンサの実施の形態の他の例を示す模式的な要部拡大断面図である。図4において図1および図2と同様の箇所には同じ符号を付している。図4に示す例では、図1に示した例と同様の構造を有するが、誘電体層3が、平面視で上部電極層4の外側部において、厚さが薄くなっている段部21を有している。これにより、上部電極層4から誘電体層3の側面を伝い下部電極層2に流れるリーク電流の経路が、上部電極層4から誘電体層3の段部21までの側面,誘電体層3の段部21の上面,段部21の側面を経由して下部電極層2に至るものとなる。このように、上部電極層4と下部電極層2間との距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0052】

また、図4に示す例のように、本発明の薄膜コンデンサは、誘電体層3の下面が下部電極層2の上面より小さく、上部電極層3の下面が誘電体層3の上面より小さくなっていることが好ましい。これにより、被覆する絶縁体層5の内部応力を低減することができ、下部電極層2および上部電極層4の側面に対する絶縁体層5の密着性を向上させて剥離を防止することができる。

【0053】

さらに、図4に示す例のように、誘電体層3の上面から段部21までの側面および段部21の上面から誘電体層3の下面までの側面の少なくとも一方が斜面構造を有していると、図1に示す誘電体層3のように斜面構造を有していない場合に比べて、誘電体層3の上面における上部電極層4の端部(外周部)と誘電体層3の下面における下部電極層2の端部との距離を長くすることができるので、薄膜コンデンサの下部電極層2と上部電極層4との間に生じるリーク電流を低減することができる。

【0054】

次に、図5は本発明の薄膜コンデンサの実施の形態の更に他の例を示す模式的な要部拡大断面図である。同様に、図5において図1,図2および図4と同様の箇所には同じ符号を付している。図5に示す例では、図4に示した例と同様の構造を有するが、段部21は、平面視で上部電極層4の外周部に、凹部22を有している。これにより、さらに効果的に上部電極層4の外周部と下部電極層2とを隔てて、上部電極層4と下部電極層間2との距離を長くとることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0055】

また、図5に示すように、平面視で上部電極層4の外周部から誘電体層3の外周部方向の凹部22の幅が、誘電体層3の段部21における厚さと同じ長さ以上の長さを有していることが望ましい。(平面視で上部電極層4の外周部から誘電体層3の外周部方向の、凹部22の幅をLとし、誘電体層3の段部21における厚さをWとすると、L≧Wの関係にあることが望ましい。)これにより、誘電体層3内部を流れる電流経路より、誘電体層3表面を流れる電流経路の方を確実に長くすることができるので、薄膜コンデンサのリーク電流に及ぼす誘電体層3表面を流れるリーク電流の影響を低減できるので、結果として薄膜コンデンサのリーク電流を低減することができる。すなわち、上部電極層4の外周部と下部電極層2とを隔てて、上部電極層4と下部電極層2間との距離を長くすることができ、薄膜コンデンサのリーク電流を低減することが可能となる。このため、薄膜コンデンサのショートや誘電特性劣化を防ぐことができる。また、仮に故障したとしても、リーク電流の経路は、誘電体層3の内部にしぼられるので故障解析が簡便である。

【0056】

段部21は、図4に示すように、誘電体層3において、平面視で上部電極層4の外周部から外側全体にかけて形成しても良いし、平面視で上部電極層4の外側の領域の内、上部電極層4の外周部から離れた位置から誘電体層3の外周部にかけて形成しても良い。また、段部21は、図4に示すように一様の厚さでも良いし、図5に示すように段部21の一部において厚さの異なる部分があっても良いし、階段状に厚さが異なるものとしても良い。

【0057】

段部21の厚さに特に制限はないが、段部21において誘電体層3の内部を通るリーク電流が発生しやすくならないように適宜設定すればよい。

【0058】

このような段部21は、後述の上部電極層4をパターニングする工程と誘電体層3をパターニングする工程との間に、フォトレジストを塗布し、フォトリソグラフィの手法により形成したフォトレジスト層を所定の形状にパターニング加工した後、ECR(Electron Cyclotron Resonance)装置等によりドライエッチング加工して所望の厚さとなるように形成すれば良い。また、図4に示すような段部21を形成する場合には、後述する上部電極層4をパターニングする工程において、ECR装置等の通常のドライエッチング装置を用いて、上部電極層4のパターニングが終了した後もエッチングを続け過剰にエッチングを行なうことで、上部電極層4の外側で誘電体層3の厚みを薄くして形成してもよい。このように形成することで、段部21を形成するために新たな工程を必要としないことから、生産性の高い薄膜コンデンサとすることができる。

【0059】

凹部22の断面形状に特に制限はなく、例えば円弧状,その一部が歪んだ形状,矩形状,その角が鈍った形状等とすればよい。このような凹部22は、例えば、上述の段部21を形成した後に、通常のドライエッチング装置を用いてエッチングして形成すればよい。なお、上記段部21を形成する際に、ドライエッチング加工時のガス圧を低圧にするなどして、エッチング異方性を高めて、誘電体層3上における上部電極層4端部のエッチングが過度に行われるようにして凹部22を形成すれば、凹部22を形成するために新たな工程を必要としないため、生産性の高い薄膜コンデンサとすることができる。

【0060】

また、本発明の薄膜コンデンサの誘電体層3が、直流バイアス電圧の印加により誘電率が変化する高Q値の誘電体から成ることにより、可変容量素子として障壁容量を用いた可変容量ダイオードを用いた場合に比べて、高周波でも可変容量コンデンサにおける損失を少なくすることができる可変容量コンデンサとなる。また、絶縁体層5の剥離を防止して耐湿信頼性に優れた可変容量コンデンサを提供することができる。

【0061】

次に、本発明の可変容量コンデンサの実施の形態の例を図6〜図13に示す。図4〜図13は、それぞれ容量発生部である可変容量素子の数が7(上記n=7)の場合の可変容量コンデンサを示したものである。図6は本発明の可変容量コンデンサの実施の形態の一例を模式的に透視状態で示す平面図,図7はその可変容量コンデンサの作製途中段階の様子を模式的に示す平面図,図8は図6におけるA−A’線断面図である。また、図9は本発明の可変容量コンデンサの概略回路図であり,図10はその高周波領域における等価回路図,図11はその低周波(直流を含む)領域における等価回路図である。

【0062】

そして、図12および図13はそれぞれ本発明の可変容量コンデンサの実施の形態の他の例を模式的に示す平面図であり、図12に示す例は、本発明の薄膜コンデンサが7個並んだコンデンサ列が2列、それぞれ対応する薄膜コンデンサを並べて並列に配置されているとともに、それら対応する薄膜コンデンサ同士を並列接続したものである。また、図13に示す例は、2列のコンデンサ列が、それぞれ対応する薄膜コンデンサが共通の下部電極層上にそれぞれの誘電体層および上部電極層が形成されてその配列方向と直交する方向に並列接続されたものである。

【0063】

図6,図7,図12,図13において、同様の箇所には同じ符号を付してあり、1は支持基板,2は支持基板1上の図における左右方向(例えば、高周波信号が後記する入力端子11側から後記する出力端子12側へ伝搬する高周波信号伝搬方向P)に所定間隔を開けて並設した下部電極層、31,32,33,34,35はそれぞれ後記するバイアスラインを構成する導体ライン(31および32はそれぞれ入力端子バイアスラインおよび出力端子バイアスラインであり、33,34,35は補助導体ラインである。)、3は下部電極層2上に形成された誘電体層、4は誘電体層3上に形成された上部電極層、61,62,63,64,65,66はそれぞれ後記するバイアスラインを構成する薄膜抵抗(61,62,63はそれぞれ入力端子バイアスライン31に接続される薄膜抵抗、64,65,66はそれぞれ出力端子バイアスライン32に接続される薄膜抵抗)、5は絶縁体層であって、図における左右方向(高周波信号伝搬方向P)において隣り合う下部電極層2間、隣り合う誘電体層3間、および隣り合う上部電極層4間に設けた絶縁体層である。6は引出し電極層であり、下部電極層2,誘電体層3および上部電極層4から構成される容量発生部である可変容量素子同士を直列接続するために設けた引出し電極層である。7は支持基板1の一部および後記する入出力端子部を除く領域を覆う保護層であり、10は半田拡散防止層であり、111,112は高周波信号の入出力端子となる半田端子部である。なお、この半田拡散防止層10と半田端子部111および112とで、入力端子11および出力端子12をそれぞれ構成している。また、C1〜C7はそれぞれ直流バイアス電圧により容量が変化する容量発生部である薄膜コンデンサからなる可変容量素子を示す。

【0064】

支持基板1は、アルミナセラミックス等のセラミック基板,サファイア等の単結晶基板等が使用可能である。支持基板1には下部電極層2,誘電体層3,上部電極層4を順次、支持基板1の上面に対して全面に成膜する。その後、上部電極層4,誘電体層3,下部電極層2を所定の形状にエッチングして形成する。具体的には、上部電極層4にフォトレジストを塗布後、所定の形状にパターニングし、ドライエッチング加工を行なう。この加工後、レジストを剥離し、引き続き誘電体層3にフォトレジストを塗布し、同様にしてパターニング加工を行ない、下部電極層2にも同様にしてパターニング加工を行なう。

【0065】

このようにして、上部電極層4,誘電体層3,下部電極層2を、所定の形状にエッチング加工してパターニングすることによって、薄膜コンデンサである可変容量素子C1〜C7を形成している。

【0066】

ここで、下部電極層2は、誘電体層3の形成に高温スパッタリングが必要となるため、高融点の材料で構成することが必要である。具体的には、白金(Pt),パラジウム(Pd)が使用可能である。なお、下部電極層2のスパッタリング終了後、下部電極層2は誘電体層3のスパッタリング温度である700〜900℃へ加熱され、誘電体層3のスパッタリング開始まで一定時間保持することにより平坦な膜になる。また、下部電極層2の厚みは、出力端子(半田端子112,半田拡散防止層10)から第7の可変容量素子C7までの抵抗成分や、第1の可変容量素子C1から第2の可変容量素子C2、第3の可変容量素子C3から第4の可変容量素子C4、第5の可変容量素子C5から第6の可変容量素子C6までの抵抗成分、および下部電極層2の連続性を考慮した場合には厚い方が望ましいが、支持基板1との密着性を考慮した場合は、相対的に薄い方が望ましく、両方を考慮して決定される。具体的には、下部電極層2の厚みを0.1μm〜10μmとするとよい。なぜなら、0.1μmよりも薄くすると、電極自身の抵抗が大きくなる他、電極の連続性が確保できなくなる可能性があるからであり、一方、10μmより厚くすると、支持基板1との密着性が低下したり、厚くすることによる下部電極層2の応力が原因で支持基板1の反りを生じさせたりするおそれがあるからである。

【0067】

誘電体層3は、少なくともバリウム(Ba),ストロンチウム(Sr),チタン(Ti)を含有するペロブスカイト型酸化物結晶粒子からなる高誘電率の誘電体層が好適であるが、その他の高誘電率の誘電体層でもよい。この誘電体層3は、上述の下部電極層2の上面に形成されている。例えば、ペロブスカイト型酸化物結晶粒子が得られる誘電体をターゲットとして、スパッタリングを所望の厚みになる時間まで行なう。基板温度を高く、例えば約800℃においてスパッタリングを行なうことにより、スパッタリング後の熱処理を行なうことなく、高誘電率で容量変化率の大きい、低損失の薄膜誘電体層3が得られる。

【0068】

上部電極層4は、スパッタリング法にて成膜される。上部電極層4の材料としては、電極の抵抗を下げるようにするため、比抵抗の小さな金(Au)を用いることが望ましいが、誘電体層3との密着性を向上させるには、Pt等を密着層として誘電体層3と上部電極層4との間の箇所に用いることが望ましい。この上部電極層4の厚みは0.1μm〜10μmとしている。この厚み範囲の下限については、下部電極層2の場合と同様に、電極自身の抵抗を考慮して設定される。また、この厚み範囲の上限については、密着性を考慮して設定される。

【0069】

下部電極層2、誘電体層3および上部電極層4のパターン形成は、フォトレジストを塗布し、フォトリソグラフィの手法により形成したフォトレジスト層を所定の形状にパターニング加工した後、ECR(Electron Cyclotron Resonance)装置等によりドライエッチング加工して行なう。その場合、ECRエッチングにおけるエッチング条件、特にArガス流量およびエッチングガス圧を制御することにより、下部電極層2,誘電体層3および上部電極層4の側面の形状を制御することができ、上記各材料の結晶の配向性によるエッチング速度の異方性を利用して、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面形状を得ることができる。

【0070】

一方、図7に示すように、可変容量素子C1〜C7に直流バイアス電圧を印加するためのバイアスライン31,32が、入力端子側および出力端子側にそれぞれ設けられている。

【0071】

入力端子側バイアスライン31は、可変容量素子C1の入力端部である入力端子11から伸びる導体ラインで構成されている。

【0072】

入力端子側バイアスライン31は、薄膜抵抗61を通して、可変容量素子C2と可変容量素子C3との接続点、すなわち、可変容量素子C2および可変容量素子C3の共通の下部電極層2につながっている。同様に、入力端子側バイアスライン31は薄膜抵抗62を通して、可変容量素子C4と可変容量素子C5との接続点につながっており、入力端子側バイアスライン31は、薄膜抵抗63を通して、可変容量素子C6と可変容量素子C7との接続点までの間に設けられている。

【0073】

また、出力端子側バイアスライン32は、補助導体ライン33と薄膜抵抗64とを通して、可変容量素子C1と可変容量素子C2との接続点、すなわち、可変容量素子C1の上部電極層5と可変容量素子C2の上部電極層5とを接続する引出し電極層6につながっている。同様に、出力端子側バイアスライン32は、補助導体ライン34と薄膜抵抗65とを通して、可変容量素子C3と可変容量素子C4との接続点につながっている。また、出力端子側バイアスライン32は、補助導体ライン35と薄膜抵抗66とを通して、可変容量素子C5と可変容量素子C6との接続点につながっている。

【0074】

以上の可変容量素子C1〜C7と、バイアスライン31,32と、薄膜抵抗61〜66とで構成される可変容量コンデンサの概略回路図を図9に示す。この回路構成に示される通り、入力端子11と出力端子12との間に、印加電圧値によって容量が変化する可変容量素子C1〜C7が順次直列接続され、入力端子11と、偶数番目の可変容量素子とその次の奇数番目の可変容量素子との接続点との間にそれぞれ薄膜抵抗61〜63が設けられ、出力端子12と、偶数番目の可変容量素子とその前の奇数番目の可変容量素子との接続点との間にそれぞれ薄膜抵抗64〜66が設けられている構成になる。なお、図7の回路構成は、簡単のため、補助導体ライン33,34,35を省略している。

【0075】

本発明の可変容量コンデンサを高周波領域で使用する場合は、薄膜抵抗61〜66のインピーダンスに比べて可変容量素子C1〜C7のインピーダンスが十分低いため、薄膜抵抗61〜66はほぼオープン(open)とみなせるので、本発明の可変容量コンデンサの等価回路は、高周波領域では図10に示すように、可変容量素子C1〜C7を直列に接続した回路となる。

【0076】

また、本発明の可変容量コンデンサを低周波領域で使用する場合は、薄膜抵抗61〜66のインピーダンスに比べて可変容量素子C1〜C7のインピーダンスが十分高いため、薄膜抵抗61〜66はほぼショート(short)とみなせるので、本発明の可変容量コンデンサの等価回路は、低周波領域では図11に示すように、可変容量素子C1〜C7を並列に接続した回路となる。

【0077】

入力端子側バイアスライン31,出力端子側バイアスライン32および補助導体ライン33〜35は、上述の下部電極層2,誘電体層3,上部電極層4をそれぞれ形成した後に、その上に新たに成膜して得ることができる。その際には、すでに加工・形成している下部電極層2,誘電体層3,上部電極層4に導体ライン31〜35の成膜・加工による影響が及ぶのを防ぐため、リフトオフ法を用いることが望ましい。あるいは、下部電極層2のパターニングの際に、下部電極層2を導体ライン31〜35を有する形状にパターニングを行なうことによっても形成できる。これによれば、導体ライン31〜35の成膜・加工によるプロセスのばらつきと時間を短縮できる。

【0078】

これらの導体ライン31〜35の材料としては、バイアスラインの抵抗値のばらつきを抑制するために、低抵抗であるAuが望ましい。Auの代わりにPt等の下部電極2と同一の材料を用い、薄膜抵抗61〜66を同一工程で形成してもよい。

【0079】

次に、薄膜抵抗61〜66の材料は、タンタル(Ta)を含む材料とするのが好ましい。その比抵抗は10−3Ωcm以上であることが好ましい。なぜなら、この程度の高い比抵抗であれば、素子形状を大きくすることなく、実現可能な小さな形状の薄膜抵抗を形成可能だからである。

【0080】

薄膜抵抗61〜66の具体的な材料としては、窒化タンタル,TaSiN,Ta−Si−O系を例示することができる。

【0081】

例えば、窒化タンタルを使用する場合であれば、Taをターゲットとして、窒素を加えてスパッタリングを行なうリアクティブスパッタリング法により、所望の組成比抵抗の膜を成膜することができる。スパッタリング条件を適宜選択することにより、膜厚40nm以上で、比抵抗10−3Ωcm以上の膜を作製することができるので好都合である。さらに、スパッタリング終了後、フォトレジストを塗布し、それを所定の形状にパターニングした後に、反応性イオンエッチング(RIE)等のエッチングプロセスにより、簡便にパターニングすることができる。

【0082】

以下、具体例を挙げて説明する。本発明の可変容量コンデンサを、例えば周波数2GHzで使用するものとする。各可変容量素子C1〜C7の容量を7pFとした場合に、高周波領域(1MHz以上)では図10に示したように直列接続とみなせ、低周波数領域(直流から1MHz)では図11に示したように並列接続とみなせるようにするには、各薄膜抵抗61〜66の抵抗値は、約1kΩ以上であればよい。

【0083】

例えば、薄膜抵抗61〜66の材料の比抵抗が10−3Ωcmであるとし、膜厚を50nmとした場合に、薄膜抵抗1個当たりに抵抗値10kΩを得るためには、薄膜抵抗61〜66のアスペクト比(長さ/幅)を50以下にすればよい。これは実現可能なアスペクト比である。従って、素子形状を大きくすることなく、所望の抵抗値を有する薄膜抵抗61〜66を作ることは容易にできる。

【0084】

これら薄膜抵抗61〜66,入力端子側バイアスライン31,出力端子側バイアスライン32および補助導体ライン33〜35は、支持基板1上に直接形成されている。これにより、これらを素子上に形成する際に必要となる下部電極2,上部電極4,引出し電極6との絶縁を確保するための絶縁層が不要となり、素子を構成する層を低減したり、絶縁層の作製工程をなくしたりすることができ、ひいては全体の製造工程を簡略化することができる。従って、可変容量コンデンサの作製を迅速に行なえるようになる。さらに、高抵抗の薄膜抵抗61〜66を用いることにより、薄膜抵抗61〜66の形状を大きくすることなくより小型の素子の作製が可能となる。

【0085】

次に、絶縁体層5は、この上に形成する引出し電極層6と下部電極層2との絶縁を確保するために必要である。さらに、この絶縁体層5は各バイアスライン31〜35や薄膜抵抗61〜66を被覆しており、各バイアスライン31〜35や薄膜抵抗61〜66が酸化されるのを極力防止できる。このため、各バイアスライン31〜35や薄膜抵抗61〜66の抵抗値を、時間が経ってもほぼ一定とすることができ、素子の信頼性が向上する。絶縁体層5の材料は、耐湿性を向上させるために、窒化ケイ素および酸化ケイ素の少なくとも1種類よりなるものとするとよい。これらは、被覆性をよくするために、化学蒸着堆積(CVD)法等により成膜することが望ましい。

【0086】

絶縁体層5は、通常のフォトレジストを用いるドライエッチング法等により、所望の形状にすることができる。ただし、薄膜抵抗64〜66と引出し電極層6との結合を確保するために、出力端子側バイアスライン32および補助導体ライン33〜35の一部を露出させる必要がある。その他では、下部電極層2よりも小さい面積でかつ下部電極層2に半田端子部111,112のみを露出させることが、耐湿性向上の観点から好ましい。

【0087】

次に、引出し電極層6は、上部電極層4同士を連結させて、第1の可変容量素子C1と第2の可変容量素子C2、第3の可変容量素子C3と第4の可変容量素子C4、および、第5の可変容量素子C5と第6の可変容量素子C6の各々を直列接続するものである。

【0088】

さらに、第1の可変容量素子C1と第2の可変容量素子C2、第3の可変容量素子C3と第4の可変容量素子C4、および、第5の可変容量素子C5と第6の可変容量素子C6の各々にまたがる引出し電極層6は、図6に示すように、絶縁体層5の外側でそれぞれ補助導体ライン33,34,35と結合している。また、これら引出し電極層6の材料としては、Au,銅(Cu)等の低抵抗の金属を用いることが望ましい。また、引出し電極層6は、絶縁体層5との密着性をよくするために、Ti,ニッケル(Ni)等の密着層を絶縁体層5と引出し電極層6との間に介在させてもよい。

【0089】

次に、保護層7をフォトリソグラフィで形成する。保護層7は、各可変容量素子C1〜C7を外部から機械的に保護する他、薬品等による汚染からの化学的な保護も可能である。また、保護層9の形成時には、半田端子部111,112を露出するようにする。保護層9の材料としては、耐熱性が高く、段差に対する被覆性が優れたものがよく、具体的には、ポリイミド樹脂やBCB(ベンゾシクロブテン)樹脂等を用いるとよい。

【0090】

半田拡散防止層10は、半田端子形成の際のリフローや実装の際に、半田の電極への拡散を防止するためにスパッタにより形成する。この材料としては半田との反応速度が遅いためNiが好適である。また、半田拡散防止層10の表面には、半田濡れ性を向上させるために、半田濡れ性の高いAu,Cu等を0.1μm程度の厚みに形成してもよい。

【0091】

最後に、半田端子部111,112を形成する。これは、実装を容易にするために形成する。すなわち、半田ペーストを印刷後、リフローを行なうことにより形成する。

【0092】

以上述べた可変容量コンデンサにおいて、可変容量素子C1〜C7が高周波的には(高周波信号から見て)直列接続される。すなわち、上述した高周波領域では図10に示すように可変容量素子C1〜C7が直列接続される。また、各可変容量素子C1〜C7は、主として薄膜抵抗61〜66で設定される抵抗値を有するバイアスラインで接続されることにより、直流的(直流信号から見た場合)には並列接続されている。すなわち、直流を含む低周波領域では、図11に示したように、可変容量素子C1〜C7が並列接続されることになる。

【0093】

また、窒化タンタルを含有し、且つ比抵抗が10−3Ωcm以上の薄膜抵抗61〜66を用いることにより、薄膜抵抗61〜66のアスペクト比を低減して素子の小型化を実現している。さらには、入力端子側バイアスライン31,出力端子側バイアスライン32および補助導体ライン33〜35を支持基板1上に直接形成することにより、素子を構成する層の数の低減を実現している。

【0094】

本発明の可変容量コンデンサにおいては、上述のように、本発明の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されている。これにより、各々の可変容量素子に所定の直流バイアス電圧を印加することができ、直流バイアス電圧による各々の可変容量素子の容量変化率を最大限に利用することができる。また、可変容量素子が複数個、高周波的に直列接続されているため、可変容量素子に印加される高周波電圧が各々の可変容量素子に分圧されるので、個々の可変容量素子に印加される高周波電圧は分圧されて減少することとなり、これによって、可変容量コンデンサの高周波信号に対する容量変動を小さく抑えることができる。このため、可変容量コンデンサの波形歪みや相互変調歪み等を大幅に抑制することができる。しかも、複数の可変容量素子が高周波的に直列接続されているため、可変容量素子の誘電体層の膜厚を厚くしたのと同じ効果が得られ、可変容量コンデンサの損失抵抗による単位体積当たりの発熱量を小さくすることができる。この結果、可変容量コンデンサの耐電力を向上させることができる。また、可変容量コンデンサの下部電極層および上部電極層の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることにより、絶縁体層の剥離を防止して耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、可変容量コンデンサの誘電体層が段部を有するときには、リーク電流を低減し、信頼性の高い可変容量コンデンサを提供することができる。

【0095】

図12および図13は、それぞれ本発明の可変容量コンデンサの実施の形態の他の例の模式的な平面図である。いずれも上部電極層4を図における左右方向(高周波信号伝搬方向P)と平面視で直交する方向(図における上下方向)に並列接続しているが、これら上部電極層4を離間させる距離としては150±100μm(50μm以上250μm以下)が好ましい。なぜなら、この距離が50μm未満であれば、任意の下部電極層2および引出し電極層6において、それぞれ図における左右方向(高周波信号伝搬方向P)に並ぶ2つの容量形成部間を流れる電流の集中を緩和できず、電極の電気抵抗が増加してコンデンサのQ値が減少するからであり、一方、この距離が250μmより長くなれば、電極の電気抵抗の減少が飽和してその効果が見られなくなることに加え、このように構成される薄膜コンデンサアレイのチップサイズが大きくなるからである。

【0096】

また、図における左右方向(高周波信号伝搬方向P)と平面視で直交する方向(図における上下方向)において、下部電極層2の端部から最も近い上部電極層4の端部までの距離は50μmより短いことが好ましい。なぜなら、任意の下部電極層2および引出し電極層6において、それぞれ高周波信号伝搬方向Pに並ぶ2つの容量形成部間を流れる一部の電流経路として下部電極層2および引出し電極層6の端部に流れる経路があるが、高周波信号伝搬方向Pと平面視で直交する方向において、下部電極層2の端部から最も近い上部電極層5の端部までの距離が50μmより長い場合は、この電流経路が長くなり、表皮電極抵抗が増加してコンデンサのQ値が減少するからである。

【0097】

このように、本発明の薄膜コンデンサの複数列を、高周波信号伝搬方向Pに対し平面視で直交する方向に並列接続することにより、電極の抵抗値を低減して容量値を増加させることができ、高いQ値の可変容量コンデンサを得ることができる。また特に、図13に示す例の可変容量コンデンサでは、複数列の薄膜コンデンサ間で、下部電極層2および引出し電極層6を共通にすることにより、さらなる小型化を実現できる。

【0098】

また、上述の本発明の可変容量コンデンサにおいて、その可変容量素子である薄膜コンデンサの下部電極層2および上部電極層4の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面とすること、さらに、誘電体層3は、上面が下面より小さく、誘電体層2の下面が下部電極層2の上面より小さいこと、および上部電極層4は、その下面が誘電体層3の上面より小さい構成とすることにより、各層2,3,4の側面からの絶縁体層5の剥離を防止して耐湿性を向上させることができるので、長期信頼性に優れた可変容量コンデンサを提供することができる。さらに、可変容量コンデンサの誘電体層が段部を有するときには、リーク電流を低減し、信頼性の高い可変容量コンデンサを提供することができる。

【0099】

また、上述の本発明の可変容量コンデンサは、高周波部品の共振回路の一部(LC共振回路の容量成分)として用いたり、この共振回路を結合する容量結合コンデンサとして用いたりすることができる。これにより、可変容量コンデンサの下部電極層2,上部電極層4または引出し電極層6を利用してインダクタを同時に形成したり、支持基板1の周辺領域(可変容量コンデンサが形成されていない領域)にその他の共振回路を形成したりして、可変容量コンデンサを電圧制御型高周波共振回路部品に用いることができる。さらに、本発明の可変容量コンデンサは、前述のような共振回路の複合部品である電圧制御型高周波フィルタ,電圧制御型整合回路素子および電圧制御型薄膜アンテナ共用器等の高周波用電子部品に適用することができる。

【0100】

かくして、本発明の薄膜コンデンサおよび可変容量コンデンサによれば、下部電極層2および上部電極層4の少なくとも一方が、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることにより、下部電極層2および上部電極層4の側面に対する絶縁体層5の密着性を向上させることができ、さらに効果的に絶縁体層5の剥離を防止することができる。また、絶縁体層5の剥離を防止して容量発生部の耐湿性を向上させることができるので、下部電極層2と上部電極層4との短絡等によるリーク電流を低減することが可能となる。さらに、絶縁体層5の剥離を防止して容量発生部の耐湿性を向上させることができるので、下部電極層2および上部電極層4が水分により酸化して電極の抵抗値が変化したりすることがなく、下部電極層2,誘電体層3,上部電極層4および絶縁体層5からなる容量発生部のQ値が低下することがない。

【0101】

そのため、容量発生部について耐湿性を始めとする耐環境性を充分に確保することができ、長期信頼性に優れた薄膜コンデンサおよび可変容量コンデンサを提供することができる。

【0102】

さらに、可変容量コンデンサの誘電体層が段部を有するときには、リーク電流を低減し、信頼性の高い可変容量コンデンサを提供することができる。

【0103】

また、薄膜の誘電体層4がチタン酸バリウムストロンチウム((Bax,Sr1−x)yTi1−yO3−z)からなるときには、薄膜コンデンサである可変容量素子の容量変化率が大きく、損失が小さい可変容量コンデンサを作製することができる。

【0104】

また、入力端子11は、高周波信号の信号入力端子と直流バイアス供給端子とが共用されており、これにより、素子構造が簡略化される。

【0105】

また、本発明の可変容量コンデンサは、少なくとも前記バイアスライン31〜35を被覆し、かつ窒化ケイ素および酸化ケイ素の少なくとも1種類よりなる保護層7を有しているときには、これにより薄膜抵抗61〜66が酸化されるのを防止できるため、バイアスライン31〜35の抵抗値を経時的に一定とすることができ、さらには耐湿性も確保でき、ひいては信頼性の向上した可変容量コンデンサおよびそれを用いた電子部品を提供することができる。

【0106】

さらに、高周波用電圧制御型共振器の一部(共振回路の一部として)、または共振回路同士を結合する手段として本発明の可変容量コンデンサを用いることにより、高周波的には直列接続され、直流的には並列接続された複数個の薄膜コンデンサである可変容量素子を有する可変容量コンデンサを用いて共振器を作製することにより、波形歪みノイズや相互変調歪みノイズが小さく、耐電力に優れた高周波用電圧制御型共振器である高周波部品を実現することができる。また、共振回路を具備した電圧制御型高周波フィルタ,電圧制御型アンテナ共用器においても同様に、高周波的には直列接続され、直流的には並列接続された複数個の薄膜コンデンサである可変容量素子を有する可変容量コンデンサを用いることにより、波形歪みノイズや相互変調歪みノイズが小さく、耐電力に優れた電圧制御型高周波フィルタ,アンテナ共用器を作製することができる。

【0107】

上述した本発明の薄膜コンデンサは、図12に示すように、薄膜コンデンサが複数個並んだコンデンサ列の複数列を、高周波信号伝搬方向Pに対し平面視で直交する方向に対応する薄膜コンデンサ同士を並列接続して薄膜コンデンサアレイに構成することができる。さらに、図13に示すように、複数列のコンデンサ列の並列接続された薄膜コンデンサ間で、下部電極層2を共通にしてもよい。

【実施例】

【0108】

次に、本発明をより具体化した例について説明する。

【0109】

まず、支持基板1としてサファイアのR基板を用い、この支持基板1上に下部電極層2の材料として用いるPtを、基板温度を約500℃にしてスパッタリング法により成膜した。また、薄膜の誘電体層3は、(Ba0.5Sr0.5)TiO3からなるターゲットを用い、基板温度は約800℃、成膜時間は15分でスパッタリング法により成膜した。なお、誘電体層3の成膜開始前に、Ptの下部電極層2を平坦化するためのアニールを、約800℃で15分間保持することにより行なった。この誘電体層3の上に、下部がPt電極層,上部がAu電極層の2層構造からなる上部電極層4をスパッタリング法により成膜した。これらは、同一チャンバー内で大気開放せずに順次成膜した。

【0110】

次に、フォトレジストを塗布し、フォトリソグラフィの手法により形成したフォトレジスト層を所定の形状にパターニング加工した後、ECR装置により上部電極層4を所定形状にエッチングした。その後、同様に誘電体層3および下部電極層2を所定形状にエッチングした。エッチング条件としては、Arガス流量10sccmとし、反応ガス圧力は5×10−2Paを用いた。ここで、下部電極層2の形状は、導体ライン31〜35を含むものとした。

【0111】

次に、薄膜抵抗61〜66として、窒化タンタルをスパッタリング法にて約100℃で成膜した。このスパッタリング後、フォトレジスト層をフォトリソグラフィの手法により所定の形状にした後、RIE装置を用いてエッチングを行ない、フォトレジスト層を除去した。薄膜抵抗61〜66のアスペクト比は全て20とした。

【0112】

次に、絶縁体層5として、SiO2膜をTEOS(テトラエトキシシラン)ガスを原料とするCVD装置により成膜した。その膜上にフォトレジスト層を加工した後、RIEにより所定の形状にエッチングを行なった。

【0113】

次に、引出し電極層6として、NiおよびAuをスパッタリング法にて順次積層して成膜し、所定の形状にパターニング加工を施した。

【0114】

最後に、保護層7,半田拡散防止層10,半田端子111および112を順次形成した。保護層7にはポリイミド樹脂を、半田拡散防止層10にはNiをそれぞれ用いた。

【0115】

このようにして得られた本発明の可変容量コンデンサにおいて、下部電極層2および上部電極層4の側面形状をSEM(Scanning Electro Microscopy:走査型電子顕微鏡)にて観察した結果、いずれの層も上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面形状となっていることが確認された。

【0116】

また、このようにして得られた本発明の可変容量コンデンサについて耐湿性の評価試験を行なったところ、下部電極層2および上部電極層3のそれぞれの側面がほぼ垂直な面となっている比較例ではそれら側面からの絶縁体層5の剥離が発生した場合であっても、下部電極層2および上部電極層3のそれぞれの側面からの絶縁体層5の剥離が発生することがなく、絶縁体層5の剥離を防止して耐湿性を向上させることができることが確認できた。また、その結果、下部電極層2および上部電極層4の側面間の絶縁が十分に確保できることによって、下部電極層2と上部電極層4との短絡等によるリーク電流を低減できることも確認できた。さらに、絶縁体層5の剥離を防止して耐湿性を向上できることにより、上部電極層2および下部電極層4が水分により酸化して電極の抵抗値が変化することがなかったので、比較例のものに比べて、下部電極層2,誘電体層3,上部電極層4および絶縁体層5からなる容量発生部のQ値が低下することもなかった。

【0117】

なお、本発明は以上の実施の形態の例に限定されるものではなく、本発明の要旨を逸脱しない範囲で種々の変更を加えることは何ら差し支えない。

【図面の簡単な説明】

【0118】

【図1】本発明の薄膜コンデンサの実施の形態の一例を模式的に示す断面図である。

【図2】本発明の薄膜コンデンサの実施の形態の一例を模式的に示す斜視図である。

【図3】本発明の薄膜コンデンサの実施の形態の他の例を模式的に示す断面図である。

【図4】本発明の薄膜コンデンサの実施の形態の他の例を模式的に示す断面図である。

【図5】本発明の薄膜コンデンサの実施の形態の他の例を模式的に示す断面図である。

【図6】本発明の可変容量コンデンサの実施の形態の一例を模式的に示す平面図である。

【図7】本発明の可変容量コンデンサの作製途中段階の様子を模式的に示す平面図である。

【図8】図6のA−A’線断面図である。

【図9】本発明の可変容量コンデンサの概略回路図である。

【図10】本発明の可変容量コンデンサの高周波領域における等価回路図である。

【図11】本発明の可変容量コンデンサの低周波(直流を含む)領域における等価回路図である。

【図12】本発明の可変容量コンデンサの実施の形態の他の例を模式的に示す平面図である。

【図13】本発明の可変容量コンデンサの実施の形態の他の例を模式的に示す平面図である。

【符号の説明】

【0119】

1:支持基板

2:下部電極層

31:入力端子側バイアスライン(導体ライン)

32:出力端子側バイアスライン(導体ライン)

33,34,35:補助導体ライン(導体ライン)

3:誘電体層

4:上部電極層

61,62,63,64,65,66:薄膜抵抗

5:絶縁体層

6:引出し電極層

7:保護層

10:半田拡散防止層

111、112:半田端子部

C1,C2,C3,C4,C5,C6,C7:可変容量素子

【技術分野】

【0001】

本発明は、誘電体層を薄膜形成方法により形成した薄膜コンデンサ、およびこれを用いた直流バイアス電圧の印加により容量が大きく変化する可変容量コンデンサ、およびこれを複数列に並列接続した薄膜コンデンサアレイ、ならびにこれらを用いた電子部品に関するものである。特に、薄膜コンデンサの電気特性を損なうことなく、かつ容量発生部を被覆する絶縁体層の密着性を向上させることにより、種々の動作環境に対する信頼性を高めた薄膜コンデンサおよび可変容量コンデンサならびに電子部品に関するものである。この電子部品は、特に、耐電力に優れた薄膜コンデンサを用いた高周波用電圧制御型共振器,電圧制御型高周波フィルタ,電圧制御型整合回路素子,電圧制御型アンテナ共用器等に好適なものである。

【背景技術】

【0002】

薄膜コンデンサは、電気絶縁性を有した支持基板上に、薄膜の下部電極層,薄膜誘電体層および薄膜の上部電極層がこの順に積層された構造を有するものが知られている。このような薄膜コンデンサでは、下部電極層および上部電極層がそれぞれスパッタリング法や真空蒸着法等で形成されており、薄膜誘電体層はスパッタリング法やゾルゲル法等で形成されている。また、通常、以下に述べるようなフォトリソグラフィの手法が用いられる。

【0003】

まず、電気絶縁性の支持基板の上面全体に下部電極層となる導体層を形成した後、必要部のみをフォトリソグラフィによってパターニングしたフォトレジストで覆い、その後、ウェットエッチングまたはドライエッチングで不要部を除去して、所定形状の下部電極層を形成する。次に、この支持基板上に薄膜誘電体層となる誘電体層を全面に形成し、下部電極層と同様に、不要部を除去して所定形状の誘電体層を形成する。そして、上部電極層となる導体層を全面に形成し、不要部を除去して所定形状の上部電極層を形成する。また、保護層やハンダ端子部を形成することにより、表面実装が可能な薄膜コンデンサになる。

【0004】

また、薄膜誘電体層の材料としてチタン酸バリウムストロンチウム((BaxSr1−x)yTi1−yO3−z)からなる誘電体材料を用いて、上部電極層と下部電極層との間に所定のバイアス電位を与えることにより薄膜誘電体層の誘電率を変化させて容量を変化させる、いわゆる可変容量薄膜コンデンサも知られており、上記薄膜コンデンサと同様な構造である(例えば、特許文献1を参照。)。

【0005】

この可変容量薄膜コンデンサでは、薄膜誘電体層に直流バイアス電圧を印加することでその誘電率が変化し、その結果として容量が変化するが、この容量変化は高周波領域にも及び、高周波領域でも可変容量薄膜コンデンサとして利用可能となる。このような高周波領域での可変容量薄膜コンデンサの容量変化を利用して、直流バイアス電圧の印加により周波数特性を変化させることができる有用な電子部品が得られる。

【0006】

例えば、上述の可変容量薄膜コンデンサと薄膜インダクタとを組み合わせた電圧制御型薄膜共振器では、直流バイアスの印加により共振周波数を変化させることができる。また、可変容量薄膜コンデンサもしくは電圧制御型薄膜共振器と、薄膜インダクタ,薄膜キャパシタとを組み合わせた電圧制御型薄膜帯域通過フィルタでは、直流バイアス電圧の印加により通過帯域を変化させることができる。また、可変容量薄膜コンデンサはマイクロ波用の電圧制御型電子部品にも利用可能である(例えば、特許文献2を参照。)。

【0007】

上述した薄膜コンデンサおよび可変容量コンデンサならびに電子部品には、電気的な特性のみならず、耐環境特性、例えば高いレベルの耐湿信頼性が要求されるようになってきている。

【特許文献1】特開平11−260667号公報

【特許文献2】特表平8−509103号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

薄膜コンデンサにおいては、容量発生部への外部からの水分の進入を防いで耐湿性を向上させる目的で、下部電極層,誘電体層および上部電極層を被覆する絶縁体層が形成される。絶縁体層の材料としては、水分の透過係数が小さい無機材料や、作製プロセスが簡便な有機材料あるいは樹脂等が例として挙げられる。特に、絶縁体層として二酸化シリコン等の薄膜無機材料を用いた場合には、下部電極層,誘電体層および上部電極層との密着性が悪く、さらに製造プロセスにおいて薄膜に残留する内部応力の影響で、絶縁体層が剥離したり、膜にクラックが生じたりする問題が発生する。

【0009】

さらに、薄膜コンデンサを作製する際には、通常、下部電極層,薄膜誘電体層,上部電極層,絶縁体層の他に、半田拡散防止層や保護層等の他の機能を担う層を順次被着していく。しかし、層の数が多くなればなるほど、フォトリソグラフィでの位置ずれの問題や、エッチングの際の下の層へのダメージといった問題の他、層の数が増えることで応力が増大し、その結果、膜に剥離やクラックが生じるなど、特性不良が発生したり信頼性が低下したりしてしまうという問題点がある。

【0010】

特に、絶縁体層として二酸化シリコンをスパッタリング法またはCVD法によって形成した場合には、支持基板に対して垂直に絶縁体層を形成する材料の粒子が飛来し堆積する。従って、下部電極層および上部電極層の側面が支持基板に対して垂直に加工された場合に、下部電極層および上部電極層の側面には回り込こんでくるエネルギーの小さい粒子のみが付着して成長するため、下部電極層および上部電極層の側面に形成される絶縁体層は剥離しやすくなる。

【0011】

また、薄膜コンデンサをフィルタ,共振器などの構成部品として電子部品に使用するためには、上部電極層と下部電極層との短絡等によるリーク電流が小さいことが求められている。これは、薄膜コンデンサは常に電圧が印加された状態で使用されるので、わずかなリーク電流も素子のショートや誘電特性劣化の原因となるからである。特に、薄膜誘電体層が非常に薄くなった場合には、リーク電流が増大する傾向にあるという問題があった。

【0012】

本発明は上述の諸問題に鑑みて案出されたものであり、本発明の目的は、下部電極層および上部電極層に対する絶縁体層の密着性を向上させることができ、絶縁体層の剥離を防止し、信頼性に優れ、特性不良を抑制することができる薄膜コンデンサおよびそれを用いた可変容量コンデンサを提供することにある。

【0013】

また、本発明の他の目的は、本発明の薄膜コンデンサにおいて、リーク電流を低減させた薄膜コンデンサを提供することにある。

【0014】

さらに本発明の他の目的は、本発明の薄膜コンデンサまたは可変容量コンデンサを用いて、信頼性の高い高周波用の電圧制御型薄膜共振器,電圧制御型薄膜高周波フィルタ,電圧制御型整合回路素子,電圧制御型薄膜アンテナ共用器等の電子部品を提供することにある。

【課題を解決するための手段】

【0015】

本発明の薄膜コンデンサは、1)支持基板上に下部電極層、誘電体層および上部電極層を順次被着してなるとともに、これらが絶縁体層で被覆された容量発生部を設けており、前記下部電極層および前記上部電極層の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることを特徴とするものである。

【0016】

また、本発明の薄膜コンデンサは、2)上記1)の構成において、前記誘電体層は、上面が下面より小さいことを特徴とするものである。

【0017】

また、本発明の薄膜コンデンサは、3)上記1),2)の各構成において、前記誘電体層の下面が前記下部電極層の上面より小さく、前記上部電極層の下面が前記誘電体層の上面より小さいことを特徴とするものである。

【0018】

また、本発明の薄膜コンデンサは、4)上記1)〜3)の各構成において、前記誘電体層は、平面視で前記上部電極層の外側部において、厚さが薄くなっている段部を有することを特徴とするものである。

【0019】

また、本発明の薄膜コンデンサは、5)上記4)の構成において、前記段部は、平面視で前記上部電極層の外周部に、凹部を有することを特徴とするものである。

【0020】

また、本発明の薄膜コンデンサは、6)上記5)の構成において、平面視で前記上部電極層の外周部から前記誘電体層の外周部方向の前記凹部の幅が、前記誘電体層の前記段部における厚さと同じ長さ以上の長さを有することを特徴とするものである。

【0021】

また、本発明の薄膜コンデンサは、7)上記1)〜6)の各構成において、前記誘電体層は、直流バイアス電圧の印加により誘電率が変化する誘電体から成ることを特徴とするものである。

【0022】

また、本発明の可変容量コンデンサは、8)上記7)の構成の本発明の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されていることを特徴とするものである。

【0023】

また、本発明の可変容量コンデンサは、9)上記7)の構成の本発明の薄膜コンデンサが複数個並んだコンデンサ列が複数列、それぞれ対応する前記薄膜コンデンサを並べて並列に配置されているとともに、それら対応する前記薄膜コンデンサ同士を並列接続したことを特徴とするものである。

【0024】

また、本発明の可変容量コンデンサは、10)上記9)の構成において、複数列の前記コンデンサ列は、それぞれ対応する前記薄膜コンデンサが、共通の前記下部電極層上にそれぞれの前記上部電極層が形成されてなることを特徴とするものである。

【0025】

また、本発明の電子部品は、11)上記1)〜7)の構成のいずれかの本発明の薄膜コンデンサまたは上記8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、共振回路の容量素子として用いたことを特徴とするものである。

【0026】

また、本発明の電子部品は、12)上記1)〜7)の構成のいずれかの本発明の薄膜コンデンサまたは上記8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、複数の共振回路同士を接続する容量素子として用いたことを特徴とするものである。

【発明の効果】

【0027】

本発明の薄膜コンデンサによれば、1)支持基板上に下部電極層、誘電体層および上部電極層を順次被着してなるとともに、これらが絶縁体層で被覆された容量発生部を設けており、下部電極層の上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である場合には、下部電極層の側面に被覆される絶縁体層のカバレッジを局所的に向上させることができ、絶縁体層としてエネルギーの大きい粒子が堆積されることとなるため、下部電極層の側面からの絶縁体層の剥離を有効に防止することができる。また、下部電極層の側面が斜面構造を有しているので、これに被覆される絶縁体層の内部応力を低減することができ、絶縁体層の密着性を向上させて剥離を有効に防止することができる。さらに、下部電極層の側面が上下方向に筋状の連続的な凹凸を有するので、アンカー効果により絶縁体層の剥離を効果的に抑制することができる。

【0028】

また、本発明の薄膜コンデンサによれば、1)上部電極層の上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である場合には、同様に上部電極層の側面に被覆される絶縁体層のカバレッジを局所的に向上させることができ、絶縁体層としてエネルギーの大きい粒子が堆積されることとなるため、上部電極層の側面からの絶縁体層の剥離を有効に防止することができる。また、上部電極層の側面が斜面構造を有しているので、これに被覆される絶縁体層の内部応力を低減することができ、絶縁体層の密着性を向上させて剥離を有効に防止することができる。さらに、上部電極層の側面が上下方向に筋状の連続的な凹凸を有するので、アンカー効果により絶縁体層の剥離を効果的に抑制することができる。

【0029】

また、本発明の薄膜コンデンサによれば、1)上部電極層および下部電極層の上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面である場合には、同様に下部電極層および上部電極層のそれぞれの側面に対する絶縁体層の密着性を向上させることができ、さらに効果的に絶縁体層の剥離を防止することができる。また、絶縁体層の剥離を防止して耐湿性を向上させることができるので、下部電極層と上部電極層との短絡等によるリーク電流を低減することが可能となる。さらに、絶縁体層の剥離を防止して耐湿性を向上できるので、上部電極層および下部電極層が水分により酸化して電極の抵抗値が変化することがなく、下部電極層,誘電体層,上部電極層および絶縁体層からなる容量発生部のQ値が低下することがない。

【0030】

そのため、耐環境性、例えば耐湿性を充分に確保することができ、長期信頼性に優れた薄膜コンデンサを提供することができる。

【0031】

また、本発明の薄膜コンデンサによれば、2)誘電体層は、上面が下面より小さいことにより、下部電極層および上部電極層と同様に誘電体層の側面に対する絶縁体層の密着性を向上させることができ、耐湿性を向上させることができるので、誘電体層が水分により還元されたりすることを防止することができ、誘電体層の誘電特性の劣化を招くことがなく、高いQ値を維持し得る信頼性に優れた薄膜コンデンサを提供することができる。

【0032】

また、本発明の薄膜コンデンサによれば、3)誘電体層の下面が下部電極層の上面より小さく、上部電極層の下面が誘電体層の上面より小さいことにより、その段差形状によって絶縁体層のアンカー効果を向上させることができ、薄膜コンデンサの耐湿信頼性を向上させることができる。さらに、隣接する容量発生部間の距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0033】

また、本発明の薄膜コンデンサによれば、4)上記1)〜3)の各構成において、誘電体層は、平面視で上部電極層の外側部において、厚さが薄くなっている段部を有することにより、誘電体層の表面を介した上部電極層と下部電極層間との距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0034】

また、本発明の薄膜コンデンサによれば、5)上記4)の構成において、段部は、平面視で前記上部電極層の外周部に、凹部を有することにより、4)の構成に比べて、さらに誘電体層の表面を流れる電流経路が長くなるので、さらに効果的に上部電極層の外周部と下部電極層とを隔てて、上部電極層と下部電極層間との距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0035】

また、本発明の薄膜コンデンサによれば、6)上記5)の構成において、平面視で上部電極層の外周部から誘電体層の外周部方向の凹部の幅が、誘電体層の段部における厚さと同じ長さ以上の長さを有することにより、誘電体層内部を流れる電流経路より、誘電体層表面を流れる電流経路の方が確実に長くなるので、薄膜コンデンサのリーク電流に及ぼす誘電体表面を流れるリーク電流の影響を低減できるので、薄膜コンデンサのリーク電流を低減することが可能となる。そのため、薄膜コンデンサのショートや誘電特性劣化を防ぐことができる。

【0036】

また、本発明の薄膜コンデンサによれば、7)上記1)〜6)の各構成において、誘電体層は、直流バイアス電圧の印加により誘電率が変化する誘電体から成ることにより、可変容量素子として障壁容量を用いた可変容量ダイオードを用いた場合に比べて、高周波でも可変容量コンデンサにおける損失を少なくすることができる。また、容量発生部における各層の側面からの絶縁体層の剥離を防止して、耐湿信頼性に優れた可変容量コンデンサを提供することができる。

【0037】

また、本発明の可変容量コンデンサによれば、8)上記7)の構成の本発明の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されていることにより、各々の可変容量素子である薄膜コンデンサに所定の直流バイアス電圧を印加することができ、これにより、直流バイアス電圧による各々の可変容量素子の容量変化率を最大限に利用することができる。また、可変容量素子が複数個、高周波的に直列接続されているため、可変容量素子に印加される高周波電圧が各々の可変容量素子に分圧されるので、個々の可変容量素子に印加される高周波電圧は分圧されて減少することとなり、これによって、可変容量コンデンサの高周波信号に対する容量変動を小さく抑えることができる。このため、可変容量コンデンサの波形歪みや相互変調歪み等を大幅に抑制することができる。しかも、複数の可変容量素子である薄膜コンデンサが高周波的に直列接続されているため、可変容量素子の誘電体層の膜厚を厚くしたのと同じ効果が得られ、可変容量コンデンサの損失抵抗による単位体積当たりの発熱量を小さくすることができる。この結果、可変容量コンデンサの耐電力を向上させることができる。また、各々の可変容量素子である薄膜コンデンサにおいて容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサのリーク電流を低減させることができるので、耐圧信頼性に優れた可変容量コンデンサを提供することができる。

【0038】

また、本発明の可変容量コンデンサによれば、9)上記7)の構成の本発明の薄膜コンデンサが複数個並んだコンデンサ列が複数列、それぞれ対応する薄膜コンデンサを並べて並列に配置されているとともに、それら対応する薄膜コンデンサ同士を並列接続したことにより、簡便な作製(所望の容量値となる数量だけ薄膜コンデンサを並列配置し、必要に応じて一部の薄膜コンデンサの並列接続を切断すること)により、全体の容量値は並列接続される数(n:自然数)だけ大きくなる(nC)(C:並列接続しないときの容量値)。一方、全体の抵抗値は並列接続される数(n)に従い小さくなる(R/n)(R:並列接続しないときの抵抗値)。コンデンサのQ値はQ=1/(2πfRC)(f:周波数(Hz))で表わされるため、並列接続しない場合と比べて容量値が大きく同等のQ値をもつ薄膜コンデンサを実現できる。また、並列接続された薄膜コンデンサの一部を切断することによって容量値を調整することもできる。また、各々の可変容量素子である薄膜コンデンサにおいて容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサのリーク電流を低減させることができるので、耐圧信頼性に優れた可変容量コンデンサを提供することができる。

【0039】

また、本発明の可変容量コンデンサによれば、10)上記9)の構成において、複数列のコンデンサ列は、等価回路上でバイアスラインおよび補助導体ラインの省略が可能となるため、それぞれ対応する薄膜コンデンサについて共通の下部電極層上にそれぞれの上部電極層を形成することにより、小型化が可能となり、この可変容量コンデンサを実装する実装基板の小型化が可能となる。また、各々の可変容量素子である薄膜コンデンサにおいて容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサのリーク電流を低減させることができるので、耐圧信頼性に優れた可変容量コンデンサを提供することができる。

【0040】

また、本発明の電子部品によれば、11)上記1)〜7)の構成のいずれかの本発明の薄膜コンデンサまたは8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、共振回路の容量素子として用いたことにより、共振回路に必要な様々な容量値に対しても同じQ値の薄膜コンデンサを提供することができるので、共振回路のQ値を大きくし、損失を小さくすることができる。また、可変容量コンデンサを共振回路に用いることにより、電圧を制御することにより複数のコンデンサを用いた場合と同等の複数の容量値が得られるので、少ない部品点数で所望の容量値を得ることができ、かつ本発明の薄膜コンデンサまたは可変容量コンデンサのQ値が高いため、共振回路のQ値を大きくし、損失を小さくすることができる。また、薄膜コンデンサまたは可変容量コンデンサの各容量発生部において容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた電子部品を提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサまたは可変容量コンデンサのリーク電流を低減できるので、耐圧信頼性に優れた電子部品を提供することができる。

【0041】

また、本発明の電子部品によれば、12)上記1)〜7)の構成の本発明の薄膜コンデンサまたは8)〜10)の構成のいずれかの本発明の可変容量コンデンサを、複数の共振回路同士を接続する容量素子として用いたことにより、電圧により容量値の制御が可能となり、共振周波数の変調ができる。さらに、本発明の薄膜コンデンサまたは可変容量コンデンサはQ値が高いので、共振回路のQ値を大きくし、損失を小さくすることができる。また、電圧を制御することにより複数のコンデンサを用いた場合と同等の複数の容量値が得られるので、少ない部品点数で所望の容量値を得ることができ、さらに、薄膜コンデンサまたは可変容量コンデンサの各容量発生部において容量発生部からの絶縁体層の剥離を防止することができ、耐湿信頼性に優れた電子部品を提供することができる。さらに、各々の可変容量素子である薄膜コンデンサにおいて、誘電体層に段部を設けた場合には、薄膜コンデンサまたは可変容量コンデンサのリーク電流を低減できるので、耐圧信頼性に優れた電子部品を提供することができる。

【発明を実施するための最良の形態】

【0042】

以下に、本発明の実施の形態の例について図面を参照しつつ詳細に説明する。なお、以下に説明する図面において同様の箇所には同じ符号を付すものとする。

【0043】

図1は本発明の薄膜コンデンサの実施の形態の一例を模式的に示す断面図であり、容量発生部の数が2の場合の例を示すものである。また、図2は本発明の薄膜コンデンサの実施の形態の一例を模式的に示す斜視図であり、図1における薄膜コンデンサの容量発生部の一部を拡大したものである。

【0044】

図1および図2において、1は支持基板、2は下部電極層、3は下部電極層2上に形成された誘電体層、4は誘電体層3上に形成された上部電極層、5は下部電極層2,誘電体層3および上部電極層4を被覆する絶縁体層、6は下部電極層2,誘電体層3および上部電極層4から構成される容量発生部を直列接続するために設けた引出し電極層、7は容量発生部を被覆する保護層である。図1に示す例においては、下部電極層2および上部電極層4の両方が、上面が下面より小さく、側面が斜面となっている。また、図2に示すように、下部電極層2および上部電極層4の両方が、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面となっている。

【0045】

なお、本発明の薄膜コンデンサは、上記の構成に限定されるものでなく、下部電極層2および上部電極層4の少なくとも一方が、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であればよい。これにより、下部電極層2および上部電極層4の側面に被覆される絶縁体層5によるカバレッジを局所的に向上させることができ、絶縁体層5を形成する際に、材料の粒子が支持基板1の表面に対して垂直に飛来して堆積する場合であっても材料の粒子としてエネルギーの大きい粒子が堆積されることとなるため、絶縁体層5が良好な密着性を有するものとなり、下部電極層2および上部電極層4の側面からの絶縁体層5の剥離を有効に防止することができる。

【0046】

また、下部電極層2および上部電極層4が側面に斜面構造を有しているので、絶縁体層5により下部電極層2および上部電極層4を連続的に被覆することによって、これを被覆する絶縁体層5の内部応力を低減することができ、下部電極層2および上部電極層4の側面に対する絶縁体層5の密着性を向上させて剥離を防止することができる。さらに、下部電極層2および上部電極層4の側面が上下方向に筋状の連続的な凹凸を有するので、アンカー効果により絶縁体層5の剥離を抑制することができる。そして、絶縁体層5の剥離を防止して耐湿性を向上させることができることによって、下部電極層2と上部電極層4との短絡等によるリーク電流を低減することが可能となる。さらに、絶縁体層5の剥離を防止して耐湿性を向上させることができるので、上部電極層2と下部電極層4とが水分により酸化して電極の抵抗値が変化したりすることがなく、下部電極層2、誘電体層3、上部電極層4および絶縁体層5からなる容量発生部のQ値が低下することがない。

【0047】

そのため、本発明の薄膜コンデンサによれば、容量発生部について耐湿性を充分に確保することができ、長期信頼性に優れた薄膜コンデンサを提供することができる。

【0048】

次に、図3は本発明の薄膜コンデンサの実施の形態の他の例を示す模式的な断面図である。図3において図1および図2と同様の箇所には同じ符号を付しているが、図3に示す例では、図1に示した例と同様の構造を有するが、誘電体層3が、上面が下面より小さい台形形状となっている。これにより、誘電体層3の側面に対する絶縁体層5の密着性を向上させることができ、容量発生部の耐湿性をさらに向上させることができるので、誘電体層3が水分により還元されることを防止でき、誘電体層3の誘電特性の劣化を招くことがなく、高いQ値を維持することができる信頼性に優れた薄膜コンデンサを提供することができる。

【0049】

また、誘電体層3は、図2に示す下部電極層2または上部電極層4の形状と同様に、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面となっていると、下部電極層2および上部電極層4の側面と同様にアンカー効果により絶縁体層5の密着性が向上し、薄膜コンデンサの耐湿信頼性を大きく向上させることができるので好ましい。

【0050】

本発明の薄膜コンデンサの実施の形態の例として、図1または図3に示す例のように、誘電体層3の下面が下部電極層2の上面より小さく、上部電極層3の下面が誘電体層3の上面より小さくなっていることが好ましい。これにより、その段差形状により絶縁体層5のアンカー効果をさらに向上させることができ、また下部電極層2および上部電極層4あるいは誘電体層3が側面に斜面構造を有しているので、スパッタリング法またはCVD法により絶縁体層5を形成した場合に、エネルギーの大きい粒子が飛来して下部電極層2および上部電極層4あるいは誘電体層3の斜面に堆積するので、これら各層2,3,4を被覆する絶縁体層5の密着強度を高めることができる。そのため、薄膜コンデンサの耐湿信頼性を向上させることができる。さらに、図3に示す例のように誘電体層3が側面に斜面構造を有していると、図1に示す例のように誘電体層3が側面に斜面構造を有していない場合に比べて、誘電体層3の上面における上部電極層4の端部と誘電体層3の下面における下部電極層2の端部との距離を長くすることができるので、薄膜コンデンサの下部電極層2と上部電極層4との間に生じるリーク電流を低減することが可能となる。

【0051】

次に、図4は本発明の薄膜コンデンサの実施の形態の他の例を示す模式的な要部拡大断面図である。図4において図1および図2と同様の箇所には同じ符号を付している。図4に示す例では、図1に示した例と同様の構造を有するが、誘電体層3が、平面視で上部電極層4の外側部において、厚さが薄くなっている段部21を有している。これにより、上部電極層4から誘電体層3の側面を伝い下部電極層2に流れるリーク電流の経路が、上部電極層4から誘電体層3の段部21までの側面,誘電体層3の段部21の上面,段部21の側面を経由して下部電極層2に至るものとなる。このように、上部電極層4と下部電極層2間との距離を長くすることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0052】

また、図4に示す例のように、本発明の薄膜コンデンサは、誘電体層3の下面が下部電極層2の上面より小さく、上部電極層3の下面が誘電体層3の上面より小さくなっていることが好ましい。これにより、被覆する絶縁体層5の内部応力を低減することができ、下部電極層2および上部電極層4の側面に対する絶縁体層5の密着性を向上させて剥離を防止することができる。

【0053】

さらに、図4に示す例のように、誘電体層3の上面から段部21までの側面および段部21の上面から誘電体層3の下面までの側面の少なくとも一方が斜面構造を有していると、図1に示す誘電体層3のように斜面構造を有していない場合に比べて、誘電体層3の上面における上部電極層4の端部(外周部)と誘電体層3の下面における下部電極層2の端部との距離を長くすることができるので、薄膜コンデンサの下部電極層2と上部電極層4との間に生じるリーク電流を低減することができる。

【0054】

次に、図5は本発明の薄膜コンデンサの実施の形態の更に他の例を示す模式的な要部拡大断面図である。同様に、図5において図1,図2および図4と同様の箇所には同じ符号を付している。図5に示す例では、図4に示した例と同様の構造を有するが、段部21は、平面視で上部電極層4の外周部に、凹部22を有している。これにより、さらに効果的に上部電極層4の外周部と下部電極層2とを隔てて、上部電極層4と下部電極層間2との距離を長くとることができるので、薄膜コンデンサのリーク電流を低減することが可能となる。

【0055】

また、図5に示すように、平面視で上部電極層4の外周部から誘電体層3の外周部方向の凹部22の幅が、誘電体層3の段部21における厚さと同じ長さ以上の長さを有していることが望ましい。(平面視で上部電極層4の外周部から誘電体層3の外周部方向の、凹部22の幅をLとし、誘電体層3の段部21における厚さをWとすると、L≧Wの関係にあることが望ましい。)これにより、誘電体層3内部を流れる電流経路より、誘電体層3表面を流れる電流経路の方を確実に長くすることができるので、薄膜コンデンサのリーク電流に及ぼす誘電体層3表面を流れるリーク電流の影響を低減できるので、結果として薄膜コンデンサのリーク電流を低減することができる。すなわち、上部電極層4の外周部と下部電極層2とを隔てて、上部電極層4と下部電極層2間との距離を長くすることができ、薄膜コンデンサのリーク電流を低減することが可能となる。このため、薄膜コンデンサのショートや誘電特性劣化を防ぐことができる。また、仮に故障したとしても、リーク電流の経路は、誘電体層3の内部にしぼられるので故障解析が簡便である。

【0056】

段部21は、図4に示すように、誘電体層3において、平面視で上部電極層4の外周部から外側全体にかけて形成しても良いし、平面視で上部電極層4の外側の領域の内、上部電極層4の外周部から離れた位置から誘電体層3の外周部にかけて形成しても良い。また、段部21は、図4に示すように一様の厚さでも良いし、図5に示すように段部21の一部において厚さの異なる部分があっても良いし、階段状に厚さが異なるものとしても良い。

【0057】

段部21の厚さに特に制限はないが、段部21において誘電体層3の内部を通るリーク電流が発生しやすくならないように適宜設定すればよい。

【0058】

このような段部21は、後述の上部電極層4をパターニングする工程と誘電体層3をパターニングする工程との間に、フォトレジストを塗布し、フォトリソグラフィの手法により形成したフォトレジスト層を所定の形状にパターニング加工した後、ECR(Electron Cyclotron Resonance)装置等によりドライエッチング加工して所望の厚さとなるように形成すれば良い。また、図4に示すような段部21を形成する場合には、後述する上部電極層4をパターニングする工程において、ECR装置等の通常のドライエッチング装置を用いて、上部電極層4のパターニングが終了した後もエッチングを続け過剰にエッチングを行なうことで、上部電極層4の外側で誘電体層3の厚みを薄くして形成してもよい。このように形成することで、段部21を形成するために新たな工程を必要としないことから、生産性の高い薄膜コンデンサとすることができる。

【0059】

凹部22の断面形状に特に制限はなく、例えば円弧状,その一部が歪んだ形状,矩形状,その角が鈍った形状等とすればよい。このような凹部22は、例えば、上述の段部21を形成した後に、通常のドライエッチング装置を用いてエッチングして形成すればよい。なお、上記段部21を形成する際に、ドライエッチング加工時のガス圧を低圧にするなどして、エッチング異方性を高めて、誘電体層3上における上部電極層4端部のエッチングが過度に行われるようにして凹部22を形成すれば、凹部22を形成するために新たな工程を必要としないため、生産性の高い薄膜コンデンサとすることができる。

【0060】

また、本発明の薄膜コンデンサの誘電体層3が、直流バイアス電圧の印加により誘電率が変化する高Q値の誘電体から成ることにより、可変容量素子として障壁容量を用いた可変容量ダイオードを用いた場合に比べて、高周波でも可変容量コンデンサにおける損失を少なくすることができる可変容量コンデンサとなる。また、絶縁体層5の剥離を防止して耐湿信頼性に優れた可変容量コンデンサを提供することができる。

【0061】

次に、本発明の可変容量コンデンサの実施の形態の例を図6〜図13に示す。図4〜図13は、それぞれ容量発生部である可変容量素子の数が7(上記n=7)の場合の可変容量コンデンサを示したものである。図6は本発明の可変容量コンデンサの実施の形態の一例を模式的に透視状態で示す平面図,図7はその可変容量コンデンサの作製途中段階の様子を模式的に示す平面図,図8は図6におけるA−A’線断面図である。また、図9は本発明の可変容量コンデンサの概略回路図であり,図10はその高周波領域における等価回路図,図11はその低周波(直流を含む)領域における等価回路図である。

【0062】

そして、図12および図13はそれぞれ本発明の可変容量コンデンサの実施の形態の他の例を模式的に示す平面図であり、図12に示す例は、本発明の薄膜コンデンサが7個並んだコンデンサ列が2列、それぞれ対応する薄膜コンデンサを並べて並列に配置されているとともに、それら対応する薄膜コンデンサ同士を並列接続したものである。また、図13に示す例は、2列のコンデンサ列が、それぞれ対応する薄膜コンデンサが共通の下部電極層上にそれぞれの誘電体層および上部電極層が形成されてその配列方向と直交する方向に並列接続されたものである。

【0063】

図6,図7,図12,図13において、同様の箇所には同じ符号を付してあり、1は支持基板,2は支持基板1上の図における左右方向(例えば、高周波信号が後記する入力端子11側から後記する出力端子12側へ伝搬する高周波信号伝搬方向P)に所定間隔を開けて並設した下部電極層、31,32,33,34,35はそれぞれ後記するバイアスラインを構成する導体ライン(31および32はそれぞれ入力端子バイアスラインおよび出力端子バイアスラインであり、33,34,35は補助導体ラインである。)、3は下部電極層2上に形成された誘電体層、4は誘電体層3上に形成された上部電極層、61,62,63,64,65,66はそれぞれ後記するバイアスラインを構成する薄膜抵抗(61,62,63はそれぞれ入力端子バイアスライン31に接続される薄膜抵抗、64,65,66はそれぞれ出力端子バイアスライン32に接続される薄膜抵抗)、5は絶縁体層であって、図における左右方向(高周波信号伝搬方向P)において隣り合う下部電極層2間、隣り合う誘電体層3間、および隣り合う上部電極層4間に設けた絶縁体層である。6は引出し電極層であり、下部電極層2,誘電体層3および上部電極層4から構成される容量発生部である可変容量素子同士を直列接続するために設けた引出し電極層である。7は支持基板1の一部および後記する入出力端子部を除く領域を覆う保護層であり、10は半田拡散防止層であり、111,112は高周波信号の入出力端子となる半田端子部である。なお、この半田拡散防止層10と半田端子部111および112とで、入力端子11および出力端子12をそれぞれ構成している。また、C1〜C7はそれぞれ直流バイアス電圧により容量が変化する容量発生部である薄膜コンデンサからなる可変容量素子を示す。

【0064】

支持基板1は、アルミナセラミックス等のセラミック基板,サファイア等の単結晶基板等が使用可能である。支持基板1には下部電極層2,誘電体層3,上部電極層4を順次、支持基板1の上面に対して全面に成膜する。その後、上部電極層4,誘電体層3,下部電極層2を所定の形状にエッチングして形成する。具体的には、上部電極層4にフォトレジストを塗布後、所定の形状にパターニングし、ドライエッチング加工を行なう。この加工後、レジストを剥離し、引き続き誘電体層3にフォトレジストを塗布し、同様にしてパターニング加工を行ない、下部電極層2にも同様にしてパターニング加工を行なう。

【0065】

このようにして、上部電極層4,誘電体層3,下部電極層2を、所定の形状にエッチング加工してパターニングすることによって、薄膜コンデンサである可変容量素子C1〜C7を形成している。

【0066】

ここで、下部電極層2は、誘電体層3の形成に高温スパッタリングが必要となるため、高融点の材料で構成することが必要である。具体的には、白金(Pt),パラジウム(Pd)が使用可能である。なお、下部電極層2のスパッタリング終了後、下部電極層2は誘電体層3のスパッタリング温度である700〜900℃へ加熱され、誘電体層3のスパッタリング開始まで一定時間保持することにより平坦な膜になる。また、下部電極層2の厚みは、出力端子(半田端子112,半田拡散防止層10)から第7の可変容量素子C7までの抵抗成分や、第1の可変容量素子C1から第2の可変容量素子C2、第3の可変容量素子C3から第4の可変容量素子C4、第5の可変容量素子C5から第6の可変容量素子C6までの抵抗成分、および下部電極層2の連続性を考慮した場合には厚い方が望ましいが、支持基板1との密着性を考慮した場合は、相対的に薄い方が望ましく、両方を考慮して決定される。具体的には、下部電極層2の厚みを0.1μm〜10μmとするとよい。なぜなら、0.1μmよりも薄くすると、電極自身の抵抗が大きくなる他、電極の連続性が確保できなくなる可能性があるからであり、一方、10μmより厚くすると、支持基板1との密着性が低下したり、厚くすることによる下部電極層2の応力が原因で支持基板1の反りを生じさせたりするおそれがあるからである。

【0067】

誘電体層3は、少なくともバリウム(Ba),ストロンチウム(Sr),チタン(Ti)を含有するペロブスカイト型酸化物結晶粒子からなる高誘電率の誘電体層が好適であるが、その他の高誘電率の誘電体層でもよい。この誘電体層3は、上述の下部電極層2の上面に形成されている。例えば、ペロブスカイト型酸化物結晶粒子が得られる誘電体をターゲットとして、スパッタリングを所望の厚みになる時間まで行なう。基板温度を高く、例えば約800℃においてスパッタリングを行なうことにより、スパッタリング後の熱処理を行なうことなく、高誘電率で容量変化率の大きい、低損失の薄膜誘電体層3が得られる。

【0068】

上部電極層4は、スパッタリング法にて成膜される。上部電極層4の材料としては、電極の抵抗を下げるようにするため、比抵抗の小さな金(Au)を用いることが望ましいが、誘電体層3との密着性を向上させるには、Pt等を密着層として誘電体層3と上部電極層4との間の箇所に用いることが望ましい。この上部電極層4の厚みは0.1μm〜10μmとしている。この厚み範囲の下限については、下部電極層2の場合と同様に、電極自身の抵抗を考慮して設定される。また、この厚み範囲の上限については、密着性を考慮して設定される。

【0069】

下部電極層2、誘電体層3および上部電極層4のパターン形成は、フォトレジストを塗布し、フォトリソグラフィの手法により形成したフォトレジスト層を所定の形状にパターニング加工した後、ECR(Electron Cyclotron Resonance)装置等によりドライエッチング加工して行なう。その場合、ECRエッチングにおけるエッチング条件、特にArガス流量およびエッチングガス圧を制御することにより、下部電極層2,誘電体層3および上部電極層4の側面の形状を制御することができ、上記各材料の結晶の配向性によるエッチング速度の異方性を利用して、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面形状を得ることができる。

【0070】

一方、図7に示すように、可変容量素子C1〜C7に直流バイアス電圧を印加するためのバイアスライン31,32が、入力端子側および出力端子側にそれぞれ設けられている。

【0071】

入力端子側バイアスライン31は、可変容量素子C1の入力端部である入力端子11から伸びる導体ラインで構成されている。

【0072】

入力端子側バイアスライン31は、薄膜抵抗61を通して、可変容量素子C2と可変容量素子C3との接続点、すなわち、可変容量素子C2および可変容量素子C3の共通の下部電極層2につながっている。同様に、入力端子側バイアスライン31は薄膜抵抗62を通して、可変容量素子C4と可変容量素子C5との接続点につながっており、入力端子側バイアスライン31は、薄膜抵抗63を通して、可変容量素子C6と可変容量素子C7との接続点までの間に設けられている。

【0073】

また、出力端子側バイアスライン32は、補助導体ライン33と薄膜抵抗64とを通して、可変容量素子C1と可変容量素子C2との接続点、すなわち、可変容量素子C1の上部電極層5と可変容量素子C2の上部電極層5とを接続する引出し電極層6につながっている。同様に、出力端子側バイアスライン32は、補助導体ライン34と薄膜抵抗65とを通して、可変容量素子C3と可変容量素子C4との接続点につながっている。また、出力端子側バイアスライン32は、補助導体ライン35と薄膜抵抗66とを通して、可変容量素子C5と可変容量素子C6との接続点につながっている。

【0074】

以上の可変容量素子C1〜C7と、バイアスライン31,32と、薄膜抵抗61〜66とで構成される可変容量コンデンサの概略回路図を図9に示す。この回路構成に示される通り、入力端子11と出力端子12との間に、印加電圧値によって容量が変化する可変容量素子C1〜C7が順次直列接続され、入力端子11と、偶数番目の可変容量素子とその次の奇数番目の可変容量素子との接続点との間にそれぞれ薄膜抵抗61〜63が設けられ、出力端子12と、偶数番目の可変容量素子とその前の奇数番目の可変容量素子との接続点との間にそれぞれ薄膜抵抗64〜66が設けられている構成になる。なお、図7の回路構成は、簡単のため、補助導体ライン33,34,35を省略している。

【0075】

本発明の可変容量コンデンサを高周波領域で使用する場合は、薄膜抵抗61〜66のインピーダンスに比べて可変容量素子C1〜C7のインピーダンスが十分低いため、薄膜抵抗61〜66はほぼオープン(open)とみなせるので、本発明の可変容量コンデンサの等価回路は、高周波領域では図10に示すように、可変容量素子C1〜C7を直列に接続した回路となる。

【0076】

また、本発明の可変容量コンデンサを低周波領域で使用する場合は、薄膜抵抗61〜66のインピーダンスに比べて可変容量素子C1〜C7のインピーダンスが十分高いため、薄膜抵抗61〜66はほぼショート(short)とみなせるので、本発明の可変容量コンデンサの等価回路は、低周波領域では図11に示すように、可変容量素子C1〜C7を並列に接続した回路となる。

【0077】

入力端子側バイアスライン31,出力端子側バイアスライン32および補助導体ライン33〜35は、上述の下部電極層2,誘電体層3,上部電極層4をそれぞれ形成した後に、その上に新たに成膜して得ることができる。その際には、すでに加工・形成している下部電極層2,誘電体層3,上部電極層4に導体ライン31〜35の成膜・加工による影響が及ぶのを防ぐため、リフトオフ法を用いることが望ましい。あるいは、下部電極層2のパターニングの際に、下部電極層2を導体ライン31〜35を有する形状にパターニングを行なうことによっても形成できる。これによれば、導体ライン31〜35の成膜・加工によるプロセスのばらつきと時間を短縮できる。

【0078】

これらの導体ライン31〜35の材料としては、バイアスラインの抵抗値のばらつきを抑制するために、低抵抗であるAuが望ましい。Auの代わりにPt等の下部電極2と同一の材料を用い、薄膜抵抗61〜66を同一工程で形成してもよい。

【0079】

次に、薄膜抵抗61〜66の材料は、タンタル(Ta)を含む材料とするのが好ましい。その比抵抗は10−3Ωcm以上であることが好ましい。なぜなら、この程度の高い比抵抗であれば、素子形状を大きくすることなく、実現可能な小さな形状の薄膜抵抗を形成可能だからである。

【0080】

薄膜抵抗61〜66の具体的な材料としては、窒化タンタル,TaSiN,Ta−Si−O系を例示することができる。

【0081】

例えば、窒化タンタルを使用する場合であれば、Taをターゲットとして、窒素を加えてスパッタリングを行なうリアクティブスパッタリング法により、所望の組成比抵抗の膜を成膜することができる。スパッタリング条件を適宜選択することにより、膜厚40nm以上で、比抵抗10−3Ωcm以上の膜を作製することができるので好都合である。さらに、スパッタリング終了後、フォトレジストを塗布し、それを所定の形状にパターニングした後に、反応性イオンエッチング(RIE)等のエッチングプロセスにより、簡便にパターニングすることができる。

【0082】

以下、具体例を挙げて説明する。本発明の可変容量コンデンサを、例えば周波数2GHzで使用するものとする。各可変容量素子C1〜C7の容量を7pFとした場合に、高周波領域(1MHz以上)では図10に示したように直列接続とみなせ、低周波数領域(直流から1MHz)では図11に示したように並列接続とみなせるようにするには、各薄膜抵抗61〜66の抵抗値は、約1kΩ以上であればよい。

【0083】

例えば、薄膜抵抗61〜66の材料の比抵抗が10−3Ωcmであるとし、膜厚を50nmとした場合に、薄膜抵抗1個当たりに抵抗値10kΩを得るためには、薄膜抵抗61〜66のアスペクト比(長さ/幅)を50以下にすればよい。これは実現可能なアスペクト比である。従って、素子形状を大きくすることなく、所望の抵抗値を有する薄膜抵抗61〜66を作ることは容易にできる。

【0084】

これら薄膜抵抗61〜66,入力端子側バイアスライン31,出力端子側バイアスライン32および補助導体ライン33〜35は、支持基板1上に直接形成されている。これにより、これらを素子上に形成する際に必要となる下部電極2,上部電極4,引出し電極6との絶縁を確保するための絶縁層が不要となり、素子を構成する層を低減したり、絶縁層の作製工程をなくしたりすることができ、ひいては全体の製造工程を簡略化することができる。従って、可変容量コンデンサの作製を迅速に行なえるようになる。さらに、高抵抗の薄膜抵抗61〜66を用いることにより、薄膜抵抗61〜66の形状を大きくすることなくより小型の素子の作製が可能となる。

【0085】

次に、絶縁体層5は、この上に形成する引出し電極層6と下部電極層2との絶縁を確保するために必要である。さらに、この絶縁体層5は各バイアスライン31〜35や薄膜抵抗61〜66を被覆しており、各バイアスライン31〜35や薄膜抵抗61〜66が酸化されるのを極力防止できる。このため、各バイアスライン31〜35や薄膜抵抗61〜66の抵抗値を、時間が経ってもほぼ一定とすることができ、素子の信頼性が向上する。絶縁体層5の材料は、耐湿性を向上させるために、窒化ケイ素および酸化ケイ素の少なくとも1種類よりなるものとするとよい。これらは、被覆性をよくするために、化学蒸着堆積(CVD)法等により成膜することが望ましい。

【0086】

絶縁体層5は、通常のフォトレジストを用いるドライエッチング法等により、所望の形状にすることができる。ただし、薄膜抵抗64〜66と引出し電極層6との結合を確保するために、出力端子側バイアスライン32および補助導体ライン33〜35の一部を露出させる必要がある。その他では、下部電極層2よりも小さい面積でかつ下部電極層2に半田端子部111,112のみを露出させることが、耐湿性向上の観点から好ましい。

【0087】

次に、引出し電極層6は、上部電極層4同士を連結させて、第1の可変容量素子C1と第2の可変容量素子C2、第3の可変容量素子C3と第4の可変容量素子C4、および、第5の可変容量素子C5と第6の可変容量素子C6の各々を直列接続するものである。

【0088】

さらに、第1の可変容量素子C1と第2の可変容量素子C2、第3の可変容量素子C3と第4の可変容量素子C4、および、第5の可変容量素子C5と第6の可変容量素子C6の各々にまたがる引出し電極層6は、図6に示すように、絶縁体層5の外側でそれぞれ補助導体ライン33,34,35と結合している。また、これら引出し電極層6の材料としては、Au,銅(Cu)等の低抵抗の金属を用いることが望ましい。また、引出し電極層6は、絶縁体層5との密着性をよくするために、Ti,ニッケル(Ni)等の密着層を絶縁体層5と引出し電極層6との間に介在させてもよい。

【0089】

次に、保護層7をフォトリソグラフィで形成する。保護層7は、各可変容量素子C1〜C7を外部から機械的に保護する他、薬品等による汚染からの化学的な保護も可能である。また、保護層9の形成時には、半田端子部111,112を露出するようにする。保護層9の材料としては、耐熱性が高く、段差に対する被覆性が優れたものがよく、具体的には、ポリイミド樹脂やBCB(ベンゾシクロブテン)樹脂等を用いるとよい。

【0090】

半田拡散防止層10は、半田端子形成の際のリフローや実装の際に、半田の電極への拡散を防止するためにスパッタにより形成する。この材料としては半田との反応速度が遅いためNiが好適である。また、半田拡散防止層10の表面には、半田濡れ性を向上させるために、半田濡れ性の高いAu,Cu等を0.1μm程度の厚みに形成してもよい。

【0091】

最後に、半田端子部111,112を形成する。これは、実装を容易にするために形成する。すなわち、半田ペーストを印刷後、リフローを行なうことにより形成する。

【0092】

以上述べた可変容量コンデンサにおいて、可変容量素子C1〜C7が高周波的には(高周波信号から見て)直列接続される。すなわち、上述した高周波領域では図10に示すように可変容量素子C1〜C7が直列接続される。また、各可変容量素子C1〜C7は、主として薄膜抵抗61〜66で設定される抵抗値を有するバイアスラインで接続されることにより、直流的(直流信号から見た場合)には並列接続されている。すなわち、直流を含む低周波領域では、図11に示したように、可変容量素子C1〜C7が並列接続されることになる。

【0093】

また、窒化タンタルを含有し、且つ比抵抗が10−3Ωcm以上の薄膜抵抗61〜66を用いることにより、薄膜抵抗61〜66のアスペクト比を低減して素子の小型化を実現している。さらには、入力端子側バイアスライン31,出力端子側バイアスライン32および補助導体ライン33〜35を支持基板1上に直接形成することにより、素子を構成する層の数の低減を実現している。

【0094】

本発明の可変容量コンデンサにおいては、上述のように、本発明の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されている。これにより、各々の可変容量素子に所定の直流バイアス電圧を印加することができ、直流バイアス電圧による各々の可変容量素子の容量変化率を最大限に利用することができる。また、可変容量素子が複数個、高周波的に直列接続されているため、可変容量素子に印加される高周波電圧が各々の可変容量素子に分圧されるので、個々の可変容量素子に印加される高周波電圧は分圧されて減少することとなり、これによって、可変容量コンデンサの高周波信号に対する容量変動を小さく抑えることができる。このため、可変容量コンデンサの波形歪みや相互変調歪み等を大幅に抑制することができる。しかも、複数の可変容量素子が高周波的に直列接続されているため、可変容量素子の誘電体層の膜厚を厚くしたのと同じ効果が得られ、可変容量コンデンサの損失抵抗による単位体積当たりの発熱量を小さくすることができる。この結果、可変容量コンデンサの耐電力を向上させることができる。また、可変容量コンデンサの下部電極層および上部電極層の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることにより、絶縁体層の剥離を防止して耐湿信頼性に優れた可変容量コンデンサを提供することができる。さらに、可変容量コンデンサの誘電体層が段部を有するときには、リーク電流を低減し、信頼性の高い可変容量コンデンサを提供することができる。

【0095】

図12および図13は、それぞれ本発明の可変容量コンデンサの実施の形態の他の例の模式的な平面図である。いずれも上部電極層4を図における左右方向(高周波信号伝搬方向P)と平面視で直交する方向(図における上下方向)に並列接続しているが、これら上部電極層4を離間させる距離としては150±100μm(50μm以上250μm以下)が好ましい。なぜなら、この距離が50μm未満であれば、任意の下部電極層2および引出し電極層6において、それぞれ図における左右方向(高周波信号伝搬方向P)に並ぶ2つの容量形成部間を流れる電流の集中を緩和できず、電極の電気抵抗が増加してコンデンサのQ値が減少するからであり、一方、この距離が250μmより長くなれば、電極の電気抵抗の減少が飽和してその効果が見られなくなることに加え、このように構成される薄膜コンデンサアレイのチップサイズが大きくなるからである。

【0096】

また、図における左右方向(高周波信号伝搬方向P)と平面視で直交する方向(図における上下方向)において、下部電極層2の端部から最も近い上部電極層4の端部までの距離は50μmより短いことが好ましい。なぜなら、任意の下部電極層2および引出し電極層6において、それぞれ高周波信号伝搬方向Pに並ぶ2つの容量形成部間を流れる一部の電流経路として下部電極層2および引出し電極層6の端部に流れる経路があるが、高周波信号伝搬方向Pと平面視で直交する方向において、下部電極層2の端部から最も近い上部電極層5の端部までの距離が50μmより長い場合は、この電流経路が長くなり、表皮電極抵抗が増加してコンデンサのQ値が減少するからである。

【0097】

このように、本発明の薄膜コンデンサの複数列を、高周波信号伝搬方向Pに対し平面視で直交する方向に並列接続することにより、電極の抵抗値を低減して容量値を増加させることができ、高いQ値の可変容量コンデンサを得ることができる。また特に、図13に示す例の可変容量コンデンサでは、複数列の薄膜コンデンサ間で、下部電極層2および引出し電極層6を共通にすることにより、さらなる小型化を実現できる。

【0098】

また、上述の本発明の可変容量コンデンサにおいて、その可変容量素子である薄膜コンデンサの下部電極層2および上部電極層4の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面とすること、さらに、誘電体層3は、上面が下面より小さく、誘電体層2の下面が下部電極層2の上面より小さいこと、および上部電極層4は、その下面が誘電体層3の上面より小さい構成とすることにより、各層2,3,4の側面からの絶縁体層5の剥離を防止して耐湿性を向上させることができるので、長期信頼性に優れた可変容量コンデンサを提供することができる。さらに、可変容量コンデンサの誘電体層が段部を有するときには、リーク電流を低減し、信頼性の高い可変容量コンデンサを提供することができる。

【0099】

また、上述の本発明の可変容量コンデンサは、高周波部品の共振回路の一部(LC共振回路の容量成分)として用いたり、この共振回路を結合する容量結合コンデンサとして用いたりすることができる。これにより、可変容量コンデンサの下部電極層2,上部電極層4または引出し電極層6を利用してインダクタを同時に形成したり、支持基板1の周辺領域(可変容量コンデンサが形成されていない領域)にその他の共振回路を形成したりして、可変容量コンデンサを電圧制御型高周波共振回路部品に用いることができる。さらに、本発明の可変容量コンデンサは、前述のような共振回路の複合部品である電圧制御型高周波フィルタ,電圧制御型整合回路素子および電圧制御型薄膜アンテナ共用器等の高周波用電子部品に適用することができる。

【0100】

かくして、本発明の薄膜コンデンサおよび可変容量コンデンサによれば、下部電極層2および上部電極層4の少なくとも一方が、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることにより、下部電極層2および上部電極層4の側面に対する絶縁体層5の密着性を向上させることができ、さらに効果的に絶縁体層5の剥離を防止することができる。また、絶縁体層5の剥離を防止して容量発生部の耐湿性を向上させることができるので、下部電極層2と上部電極層4との短絡等によるリーク電流を低減することが可能となる。さらに、絶縁体層5の剥離を防止して容量発生部の耐湿性を向上させることができるので、下部電極層2および上部電極層4が水分により酸化して電極の抵抗値が変化したりすることがなく、下部電極層2,誘電体層3,上部電極層4および絶縁体層5からなる容量発生部のQ値が低下することがない。

【0101】

そのため、容量発生部について耐湿性を始めとする耐環境性を充分に確保することができ、長期信頼性に優れた薄膜コンデンサおよび可変容量コンデンサを提供することができる。

【0102】

さらに、可変容量コンデンサの誘電体層が段部を有するときには、リーク電流を低減し、信頼性の高い可変容量コンデンサを提供することができる。

【0103】

また、薄膜の誘電体層4がチタン酸バリウムストロンチウム((Bax,Sr1−x)yTi1−yO3−z)からなるときには、薄膜コンデンサである可変容量素子の容量変化率が大きく、損失が小さい可変容量コンデンサを作製することができる。

【0104】

また、入力端子11は、高周波信号の信号入力端子と直流バイアス供給端子とが共用されており、これにより、素子構造が簡略化される。

【0105】

また、本発明の可変容量コンデンサは、少なくとも前記バイアスライン31〜35を被覆し、かつ窒化ケイ素および酸化ケイ素の少なくとも1種類よりなる保護層7を有しているときには、これにより薄膜抵抗61〜66が酸化されるのを防止できるため、バイアスライン31〜35の抵抗値を経時的に一定とすることができ、さらには耐湿性も確保でき、ひいては信頼性の向上した可変容量コンデンサおよびそれを用いた電子部品を提供することができる。

【0106】

さらに、高周波用電圧制御型共振器の一部(共振回路の一部として)、または共振回路同士を結合する手段として本発明の可変容量コンデンサを用いることにより、高周波的には直列接続され、直流的には並列接続された複数個の薄膜コンデンサである可変容量素子を有する可変容量コンデンサを用いて共振器を作製することにより、波形歪みノイズや相互変調歪みノイズが小さく、耐電力に優れた高周波用電圧制御型共振器である高周波部品を実現することができる。また、共振回路を具備した電圧制御型高周波フィルタ,電圧制御型アンテナ共用器においても同様に、高周波的には直列接続され、直流的には並列接続された複数個の薄膜コンデンサである可変容量素子を有する可変容量コンデンサを用いることにより、波形歪みノイズや相互変調歪みノイズが小さく、耐電力に優れた電圧制御型高周波フィルタ,アンテナ共用器を作製することができる。

【0107】

上述した本発明の薄膜コンデンサは、図12に示すように、薄膜コンデンサが複数個並んだコンデンサ列の複数列を、高周波信号伝搬方向Pに対し平面視で直交する方向に対応する薄膜コンデンサ同士を並列接続して薄膜コンデンサアレイに構成することができる。さらに、図13に示すように、複数列のコンデンサ列の並列接続された薄膜コンデンサ間で、下部電極層2を共通にしてもよい。

【実施例】

【0108】

次に、本発明をより具体化した例について説明する。

【0109】

まず、支持基板1としてサファイアのR基板を用い、この支持基板1上に下部電極層2の材料として用いるPtを、基板温度を約500℃にしてスパッタリング法により成膜した。また、薄膜の誘電体層3は、(Ba0.5Sr0.5)TiO3からなるターゲットを用い、基板温度は約800℃、成膜時間は15分でスパッタリング法により成膜した。なお、誘電体層3の成膜開始前に、Ptの下部電極層2を平坦化するためのアニールを、約800℃で15分間保持することにより行なった。この誘電体層3の上に、下部がPt電極層,上部がAu電極層の2層構造からなる上部電極層4をスパッタリング法により成膜した。これらは、同一チャンバー内で大気開放せずに順次成膜した。

【0110】

次に、フォトレジストを塗布し、フォトリソグラフィの手法により形成したフォトレジスト層を所定の形状にパターニング加工した後、ECR装置により上部電極層4を所定形状にエッチングした。その後、同様に誘電体層3および下部電極層2を所定形状にエッチングした。エッチング条件としては、Arガス流量10sccmとし、反応ガス圧力は5×10−2Paを用いた。ここで、下部電極層2の形状は、導体ライン31〜35を含むものとした。

【0111】

次に、薄膜抵抗61〜66として、窒化タンタルをスパッタリング法にて約100℃で成膜した。このスパッタリング後、フォトレジスト層をフォトリソグラフィの手法により所定の形状にした後、RIE装置を用いてエッチングを行ない、フォトレジスト層を除去した。薄膜抵抗61〜66のアスペクト比は全て20とした。

【0112】

次に、絶縁体層5として、SiO2膜をTEOS(テトラエトキシシラン)ガスを原料とするCVD装置により成膜した。その膜上にフォトレジスト層を加工した後、RIEにより所定の形状にエッチングを行なった。

【0113】

次に、引出し電極層6として、NiおよびAuをスパッタリング法にて順次積層して成膜し、所定の形状にパターニング加工を施した。

【0114】

最後に、保護層7,半田拡散防止層10,半田端子111および112を順次形成した。保護層7にはポリイミド樹脂を、半田拡散防止層10にはNiをそれぞれ用いた。

【0115】

このようにして得られた本発明の可変容量コンデンサにおいて、下部電極層2および上部電極層4の側面形状をSEM(Scanning Electro Microscopy:走査型電子顕微鏡)にて観察した結果、いずれの層も上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面形状となっていることが確認された。

【0116】

また、このようにして得られた本発明の可変容量コンデンサについて耐湿性の評価試験を行なったところ、下部電極層2および上部電極層3のそれぞれの側面がほぼ垂直な面となっている比較例ではそれら側面からの絶縁体層5の剥離が発生した場合であっても、下部電極層2および上部電極層3のそれぞれの側面からの絶縁体層5の剥離が発生することがなく、絶縁体層5の剥離を防止して耐湿性を向上させることができることが確認できた。また、その結果、下部電極層2および上部電極層4の側面間の絶縁が十分に確保できることによって、下部電極層2と上部電極層4との短絡等によるリーク電流を低減できることも確認できた。さらに、絶縁体層5の剥離を防止して耐湿性を向上できることにより、上部電極層2および下部電極層4が水分により酸化して電極の抵抗値が変化することがなかったので、比較例のものに比べて、下部電極層2,誘電体層3,上部電極層4および絶縁体層5からなる容量発生部のQ値が低下することもなかった。

【0117】

なお、本発明は以上の実施の形態の例に限定されるものではなく、本発明の要旨を逸脱しない範囲で種々の変更を加えることは何ら差し支えない。

【図面の簡単な説明】

【0118】

【図1】本発明の薄膜コンデンサの実施の形態の一例を模式的に示す断面図である。

【図2】本発明の薄膜コンデンサの実施の形態の一例を模式的に示す斜視図である。

【図3】本発明の薄膜コンデンサの実施の形態の他の例を模式的に示す断面図である。

【図4】本発明の薄膜コンデンサの実施の形態の他の例を模式的に示す断面図である。

【図5】本発明の薄膜コンデンサの実施の形態の他の例を模式的に示す断面図である。

【図6】本発明の可変容量コンデンサの実施の形態の一例を模式的に示す平面図である。

【図7】本発明の可変容量コンデンサの作製途中段階の様子を模式的に示す平面図である。

【図8】図6のA−A’線断面図である。

【図9】本発明の可変容量コンデンサの概略回路図である。

【図10】本発明の可変容量コンデンサの高周波領域における等価回路図である。

【図11】本発明の可変容量コンデンサの低周波(直流を含む)領域における等価回路図である。

【図12】本発明の可変容量コンデンサの実施の形態の他の例を模式的に示す平面図である。

【図13】本発明の可変容量コンデンサの実施の形態の他の例を模式的に示す平面図である。

【符号の説明】

【0119】

1:支持基板

2:下部電極層

31:入力端子側バイアスライン(導体ライン)

32:出力端子側バイアスライン(導体ライン)

33,34,35:補助導体ライン(導体ライン)

3:誘電体層

4:上部電極層

61,62,63,64,65,66:薄膜抵抗

5:絶縁体層

6:引出し電極層

7:保護層

10:半田拡散防止層

111、112:半田端子部

C1,C2,C3,C4,C5,C6,C7:可変容量素子

【特許請求の範囲】

【請求項1】

支持基板上に下部電極層、誘電体層および上部電極層を順次被着してなるとともに、これらが絶縁体層で被覆された容量発生部を設けており、前記下部電極層および前記上部電極層の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることを特徴とする薄膜コンデンサ。

【請求項2】

前記誘電体層は、上面が下面より小さいことを特徴とする請求項1に記載の薄膜コンデンサ。

【請求項3】

前記誘電体層の下面が前記下部電極層の上面より小さく、前記上部電極層の下面が前記誘電体層の上面より小さいことを特徴とする請求項1または請求項2に記載の薄膜コンデンサ。

【請求項4】

前記誘電体層は、平面視で前記上部電極層の外側部において、厚さが薄くなっている段部を有することを特徴とする請求項1乃至請求項3に記載の薄膜コンデンサ。

【請求項5】

前記段部は、平面視で前記上部電極層の外周部に、凹部を有することを特徴とする請求項4に記載の薄膜コンデンサ。

【請求項6】

平面視で前記上部電極層の外周部から前記誘電体層の外周部方向の前記凹部の幅が、前記誘電体層の前記段部における厚さ以上の長さを有することを特徴とする請求項5に記載の薄膜コンデンサ。

【請求項7】

前記誘電体層は、直流バイアス電圧の印加により誘電率が変化する誘電体から成ることを特徴とする請求項1乃至請求項6のいずれかに記載の薄膜コンデンサ。

【請求項8】

請求項7に記載の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されていることを特徴とする可変容量コンデンサ。

【請求項9】

請求項7に記載の薄膜コンデンサが複数個並んだコンデンサ列が複数列、それぞれ対応する前記薄膜コンデンサを並べて並列に配置されているとともに、それら対応する前記薄膜コンデンサ同士を並列接続したことを特徴とする可変容量コンデンサ。

【請求項10】

複数列の前記コンデンサ列は、それぞれ対応する前記薄膜コンデンサが、共通の前記下部電極層上にそれぞれの前記上部電極層が形成されてなることを特徴とする請求項9に記載の可変容量コンデンサ。

【請求項11】

請求項1乃至請求項7のいずれかに記載の薄膜コンデンサまたは請求項8乃至請求項10のいずれかに記載の可変容量コンデンサを、共振回路の容量素子として用いたことを特徴とする電子部品。

【請求項12】

請求項1乃至請求項7のいずれかに記載の薄膜コンデンサまたは請求項8乃至請求項10のいずれかに記載の可変容量コンデンサを、複数の共振回路同士を接続する容量素子として用いたことを特徴とする電子部品。

【請求項1】

支持基板上に下部電極層、誘電体層および上部電極層を順次被着してなるとともに、これらが絶縁体層で被覆された容量発生部を設けており、前記下部電極層および前記上部電極層の少なくとも一方は、上面が下面より小さく、側面が上下方向に筋状の連続的な凹凸を有する斜面であることを特徴とする薄膜コンデンサ。

【請求項2】

前記誘電体層は、上面が下面より小さいことを特徴とする請求項1に記載の薄膜コンデンサ。

【請求項3】

前記誘電体層の下面が前記下部電極層の上面より小さく、前記上部電極層の下面が前記誘電体層の上面より小さいことを特徴とする請求項1または請求項2に記載の薄膜コンデンサ。

【請求項4】

前記誘電体層は、平面視で前記上部電極層の外側部において、厚さが薄くなっている段部を有することを特徴とする請求項1乃至請求項3に記載の薄膜コンデンサ。

【請求項5】

前記段部は、平面視で前記上部電極層の外周部に、凹部を有することを特徴とする請求項4に記載の薄膜コンデンサ。

【請求項6】

平面視で前記上部電極層の外周部から前記誘電体層の外周部方向の前記凹部の幅が、前記誘電体層の前記段部における厚さ以上の長さを有することを特徴とする請求項5に記載の薄膜コンデンサ。

【請求項7】

前記誘電体層は、直流バイアス電圧の印加により誘電率が変化する誘電体から成ることを特徴とする請求項1乃至請求項6のいずれかに記載の薄膜コンデンサ。

【請求項8】

請求項7に記載の薄膜コンデンサが複数個、直流的に並列接続され、かつ高周波的に直列接続されていることを特徴とする可変容量コンデンサ。

【請求項9】

請求項7に記載の薄膜コンデンサが複数個並んだコンデンサ列が複数列、それぞれ対応する前記薄膜コンデンサを並べて並列に配置されているとともに、それら対応する前記薄膜コンデンサ同士を並列接続したことを特徴とする可変容量コンデンサ。

【請求項10】

複数列の前記コンデンサ列は、それぞれ対応する前記薄膜コンデンサが、共通の前記下部電極層上にそれぞれの前記上部電極層が形成されてなることを特徴とする請求項9に記載の可変容量コンデンサ。

【請求項11】

請求項1乃至請求項7のいずれかに記載の薄膜コンデンサまたは請求項8乃至請求項10のいずれかに記載の可変容量コンデンサを、共振回路の容量素子として用いたことを特徴とする電子部品。

【請求項12】

請求項1乃至請求項7のいずれかに記載の薄膜コンデンサまたは請求項8乃至請求項10のいずれかに記載の可変容量コンデンサを、複数の共振回路同士を接続する容量素子として用いたことを特徴とする電子部品。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2006−196871(P2006−196871A)

【公開日】平成18年7月27日(2006.7.27)

【国際特許分類】

【出願番号】特願2005−328559(P2005−328559)

【出願日】平成17年11月14日(2005.11.14)

【出願人】(000006633)京セラ株式会社 (13,660)

【Fターム(参考)】

【公開日】平成18年7月27日(2006.7.27)

【国際特許分類】

【出願日】平成17年11月14日(2005.11.14)

【出願人】(000006633)京セラ株式会社 (13,660)

【Fターム(参考)】

[ Back to top ]