薄膜コンデンサ及びその製造方法

【課題】高い静電容量を維持しつつ、電極の応力を緩和することにより、信頼性の高い優れた薄膜コンデンサ及びその製造方法を提供する。

【解決手段】本発明による薄膜コンデンサ1は、トレンチ3aが少なくとも一方面に形成された基体と、その基体の少なくとも一方面上に形成された、下部電極、誘電体膜及び上部電極6を含む積層膜とを有しており、上部電極6及び/又は下部電極に、開口部6aが形成されたものである。また、誘電体膜には、パッド電極と下部電極との接続部位に開口部が形成されている。

【解決手段】本発明による薄膜コンデンサ1は、トレンチ3aが少なくとも一方面に形成された基体と、その基体の少なくとも一方面上に形成された、下部電極、誘電体膜及び上部電極6を含む積層膜とを有しており、上部電極6及び/又は下部電極に、開口部6aが形成されたものである。また、誘電体膜には、パッド電極と下部電極との接続部位に開口部が形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜コンデンサ及びその製造方法に関し、特に、トレンチ型の薄膜コンデンサ及びその製造方法に関する。

【背景技術】

【0002】

コンピュータや携帯端末等の電子機器の内部回路には、表面実装型の多種の電子部品が搭載されている。近時、電子機器の更なる高性能化及び小型化の要求に応えるべく、能動素子、受動素子を問わず、各種電子部品の更なる小型化及び薄型(薄膜)化が急務となっている。このような薄膜型の電子部品としては、薄膜形成プロセスを利用した、例えば、薄膜コンデンサ、薄膜インダクタ、薄膜LC複合部品、薄膜集中定数デバイス、薄膜分布デバイス、薄膜積層型複合部品等が挙げられる。

【0003】

これらのなかでも薄膜コンデンサの単位体積(容積)当たりの静電容量を増大させつつ小型化及び薄型化を達成する手法の一つとして、基体にトレンチ(下地段差構造)を形成し、そのトレンチに薄膜コンデンサを形成する方法が提案されている(特許文献1参照)。

【特許文献1】特開平6−325970号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

このようなトレンチ型の薄膜コンデンサでは、形成された薄膜内に応力(膜応力)が発生する問題があり、特に、誘電体膜よりも電極の膜応力が大きい傾向にある。これは、電極の形成過程において、通常、熱処理を行うことから、この熱処理により膜内に歪が蓄積し応力が発生するためである。また、誘電体膜に比べて、基体との間の線膨張係数の差が大きいことも、電極に応力が発生しやすい要因となっている。さらに、電極の抵抗を下げることを企図して電極の膜厚を大きくしようとすると、応力の増大を招いてしまう。

【0005】

かかる薄膜の応力は、基体の反りを誘発し、その結果、薄膜コンデンサの容量変動を引き起こしてしまったり、薄膜が基体から剥離してしまったりといった不都合が生じ得る。また、膜応力は、膜質低下の要因となり、膜の電気的特性自体に影響を及ぼし易い。このような問題は、薄型の基体を用いた近時の薄膜コンデンサにおいて顕著となる。

【0006】

そこで、本発明は上記の事情に鑑みてなされたものであり、その目的は、高い静電容量を維持しつつ、電極の応力を緩和することにより、信頼性の高い優れた薄膜コンデンサ及びその製造方法を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明の薄膜コンデンサは、トレンチが少なくとも一方面に形成された基体と、基体の少なくとも一方面上に形成された、下部電極、誘電体膜及び上部電極を含む積層膜と、上部電極及び/又は下部電極に形成された開口部とを備えるものである。

【0008】

上記構成の薄膜コンデンサでは、上部電極及び/又は下部電極に開口部が形成されていることから、積層膜に熱処理が施されて電極に熱的な歪(伸縮)が印加されても、かかる歪が全体に蓄積されることなく、これら電極に蓄積された応力が開口部において解放され、電極全体の膜応力が緩和される。ここで、開口部とは、上部電極及び/又は下部電極を貫通する貫通孔であっても、上部電極及び/又は下部電極を貫通せずに底面に電極の一部が残存した状態(露呈した状態)の凹部であってもよい。これは、貫通孔以外の凹部であっても、この凹部において応力が少なからず解放されるためである。また、開口部は、上部電極及び下部電極の双方に形成することが好ましいが、上部電極又は下部電極のいずれか一方のみに形成してもよい。

【0009】

上述した開口部の数及び配置は、薄膜コンデンサの容量に影響する。これは、仮に開口部を貫通孔とした場合には、開口部の部位にはコンデンサが形成されないからである。したがって、例えば、トレンチが複数形成されている場合には、開口部は、複数のトレンチの間の領域に形成されることが好ましい。

【0010】

より好ましくは、トレンチが複数形成されており且つそれらの複数のトレンチからなる所定のパターンを有するトレンチ群が、基体の少なくとも一方面に複数形成されており、開口部が、それら複数のトレンチ群の間の領域における上部電極及び/又は下部電極に形成されている。このように、トレンチ群の間の領域にのみ開口部を設けることにより、トレンチ群の内側の領域には開口部の寸法よりも小さい間隔で高密度にトレンチのパターンを配置できるので、薄膜コンデンサの高容量化に資することができる。

【0011】

また、本発明による薄膜コンデンサの製造方法は、本発明の薄膜コンデンサを有効に製造するための方法であって、基体の少なくとも一方面にトレンチを形成する工程と、基体の少なくとも一方面上に、下部電極、誘電体膜及び上部電極を含む積層膜を形成する工程とを有しており、積層膜を形成する工程においては、下部電極及び/又は上部電極に開口部を形成する。

【0012】

上記構成の薄膜コンデンサの製造方法では、上部電極及び/又は下部電極に開口部を形成していることから、電極材料の成膜過程において膜内に蓄積する歪や、成膜後の熱処理に起因して発生する応力は、この開口部において解放され、電極全体の膜応力が緩和される。上述したように、本発明において「開口部」とは、このような電極を貫通する貫通孔であっても、電極を貫通せずに底面に電極の一部を残した状態の凹部であってもよい。

【発明の効果】

【0013】

本発明によれば、上部電極及び/又は下部電極に開口部が形成されていることから、これら電極に蓄積された応力が開口部において解放され、電極全体の膜応力が緩和される。したがって、基体の反り、基体からの薄膜の剥離、膜質低下等を抑制でき、信頼性の高い優れた薄膜コンデンサを実現することができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態について、図面を参照して説明する。なお、図面中、同一の要素には同一の符号を付し、重複する説明を省略する。また、上下左右などの位置関係は、特に断らない限り、図面に示す位置関係に基づくものとする。さらに、図面の寸法比率は、図示の比率に限定されるものではない。また、以下の実施の形態は、本発明を説明するための例示であり、本発明をその実施の形態のみに限定する趣旨ではない。さらに、本発明は、その要旨を逸脱しない限り、さまざまな変形が可能である。

【0015】

<第1実施形態>

図1及び図2は、それぞれ本発明による薄膜コンデンサの好適な一実施形態の概略構成を示す斜視図及び平面図であり、図3は図2におけるIII-III線に沿う断面図である。

【0016】

図1〜図3に示すように、基板2上には、絶縁層3が形成されており、絶縁層3にはトレンチ3aが形成されている。基板2及び絶縁層3から本発明における基体が構成されている。絶縁層3の厚さは、形成すべきトレンチ3aの深さに応じて適宜設定することができる。また、基板2の材料としては、特に制限されず、シリコン基板、アルミナ等のセラミックス基板、ガラスセラミックス基板、ガラス基板、サファイア、MgO、SrTiO3等の単結晶基板等が挙げられ、化学的且つ熱的に安定であり、且つ、応力発生が少なく表面の平滑性を保持し易いものを用いることが好ましい。さらに、絶縁層3の材質も特に制限されず、例えばAl2O3、SiO2、Si等を列挙することができる。

【0017】

さらに、トレンチ3aの内壁上及び絶縁層3上には、下部電極4、誘電体膜5、及び、上部電極6からなる積層膜が形成されている。誘電体膜5には、パッド電極8と下部電極4との接続部位に開口部5aが形成されている。

【0018】

下部電極4及び上部電極6としては、例えば、Cu、Au、Pt、Ag、Sn、Cr、Co、Ni等を含む金属、又はこれらを含む合金等の複合金属が挙げられる。誘電体膜5の材料は特に限定されず、例えば、Al2O3、PbTiO3(PZT)、BaTiO3、BaTiO3、ZrO2、HfO2、Bi4Ti3O12、SrBi2Ta2O9、SiO2等からなる。

【0019】

この積層膜上には、保護膜7が形成されており、保護膜7には2つの開口部7a,7aが形成され、さらに、開口部7a内には下部電極4及び上部電極6が露出している。そして、この開口部7aを埋め込むように、保護膜7上に2つのパッド電極8,8が形成されている。

【0020】

保護膜7は、絶縁材料であれば特に限定されず、例えば、Al2O3、SiO2、SiNなどの無機物とポリイミド、エポキシなどの樹脂からなる。パッド電極8として、例えば、Cu、Au、Pt、Ag、Sn、Cr、Co、Ni等を含む金属、又はこれらを含む複合金属が挙げられる。

【0021】

また、薄膜コンデンサ1には、少なくとも上部電極6又は下部電極4のいずれかに開口部が形成されており、本実施形態では、上部電極6に開口部を形成する例について以下に説明する。

【0022】

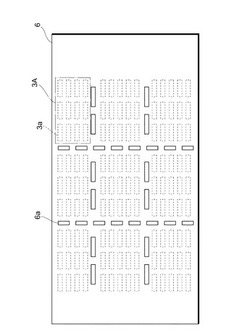

図4は、開口部6aが設けられた上部電極6の構成を示す平面図である。同図に示す如く、上部電極6は、複数のトレンチ3aのパターン構造によって画成される下地の段差構造を被覆するように形成されている。これらのトレンチ3aの形成されていない部位、すなわちトレンチ3a間の領域に、開口部6aが形成されている。

【0023】

この開口部6aは、上部電極6に蓄積された応力を解放させるために配設されたものである。ここで、開口部6aは、このような電極を貫通する貫通孔であっても、電極を貫通せずに底面に電極の一部を残した状態の凹部であってもよい。応力をより多く解放させる観点からは、凹部よりも貫通孔の方が好ましいものの、静電容量をより高める観点からは、貫通孔ではその部位にコンデンサが形成されないため、非貫通型の凹部の方が好ましい。

【0024】

ここで、近時、高い静電容量を得ることを企図して、短いピッチ(間隔)で複数のトレンチ3aが配置される傾向にあり、トレンチ3aのパターン間の狭い領域に開口部6aを形成することが困難な傾向にある。これに対し、図4に示す例では、かかる事情を考慮して、短いピッチで高密度に格子状に配置されたトレンチ3aを有するトレンチ群3Aを設け、このトレンチ群3Aの間の領域をトレンチ3a間に比べて大きく設定して、この領域に開口部6aが形成されている。これにより、高静電容量を維持しつつ、上部電極6の応力を有効に緩和することができる。

【0025】

次に、上記構成の本実施形態に係る薄膜コンデンサの製造方法について、図5〜図11を参照して説明する。

【0026】

図5〜図11は、薄膜コンデンサ1を製造している状態を示す断面図(工程図)である。図5に示すように、基板2上の全面に、絶縁層3を形成する。絶縁層3の形成では、例えばSiからなる基板2上に、スパッタリング法により、Al2O3膜を堆積させる。絶縁層3の厚さは、形成すべきトレンチに応じて設定され、例えば、5μm〜50μmである。

【0027】

次に、図6に示すように、絶縁層3上に、トレンチを形成すべき部位に開口部20aを有するマスク層20を形成する。本実施形態では、マスク層20として、例えば、Ru、または、NiFeからなる金属マスクをパターニングする。Ru、または、NiFe膜の堆積にはスパッタリング法を用いることができ、その膜のパターン化にはサブトラクティブ法又はアディティブ法を用いることができる。サブトラクティグ法を採用する場合には、例えば、SiO2酸化膜付きSiからなる基板2上にスパッタリング法によりNiFe膜を堆積させた後に、NiFe膜上にレジストパターンを形成し、レジストパターンをマスクとしたドライエッチング又はウェットエッチングにより、NiFe膜をパターニングする。これに対して、アディティブ法を採用する場合には、基板2上にレジストパターンを形成した後に、全面にスパッタリング法によりNiFe膜を堆積させて、レジストパターンとともにレジストパターン上の不要なNiFe膜を除去することにより、所望のパターンのNiFe膜を形成する。

【0028】

次いで、図7に示すように、リアクティブイオンエッチング(RIE)により、開口部20a内に露出した絶縁層3を除去して、トレンチ3aを形成した後に、マスク層20を除去する。ここで、図7では、基板2に達するトレンチ3aを示しているが、トレンチ3aは基板2に達していなくてもよい。また、トレンチ3aの形成方法として、イオンミリングを用いてもよい。

【0029】

次に、図8に示すように、トレンチ3aの内壁上及び絶縁層3上に、下部電極4をパターニングする。当該工程では、下部電極4としてCu膜をスパッタリングし、下部電極4のパターニングには、上述したサブトラクティブ法又はアディティブ法を使用する。

【0030】

さらに、図9に示すように、下部電極4及び絶縁層3上に、誘電体膜5をパターニングする。当該工程では、ALD(Atomic Layer Deposition)法によりAl2O3膜を堆積させた後、レジストパターンを用いたエッチングにより、パッド電極8との接続部位におけるAl2O3膜を除去して開口部5aを形成する。

【0031】

それから、図10に示すように、誘電体膜5上に上部電極6をパターニングする。当該工程では、上部電極6としてCu膜をスパッタリングし、上部電極6のパターニングには、上述したサブトラクティブ法又はアディティブ法を使用する。本実施形態では、この上部電極6のパターニングにおいて、上部電極6に開口部6aを形成する。このように、上部電極6に開口部を形成することにより、電極材料の成膜過程において膜内に蓄積する歪や、成膜後の熱処理に起因して発生する応力は、この開口部6aにおいて解放され、上部電極6全体の膜応力が緩和される。

【0032】

次に、図11に示すように、下部電極4、誘電体膜5、及び、上部電極6上に、下部電極4及び上部電極6が露出した開口部7a,7aを備える保護膜7を形成する。保護膜7の形成では、例えば基板2の全面に、例えばスパッタリング法により、Al2O3膜を堆積させた後、レジストパターンを用いたエッチングにより、開口部7a,7aを形成する。

【0033】

以降の工程としては、必要に応じて基板2の裏面を研削して薄膜化した後に、ダイシングにより個々の薄膜コンデンサ1に分割し、薄膜コンデンサ1を得る。

【0034】

このように構成された薄膜コンデンサ1によれば、上部電極6に開口部6aが形成されていることから、上部電極6に蓄積された応力が開口部6aにおいて解放され、上部電極6全体の膜応力が緩和される。したがって、基体の反り、基体からの薄膜の剥離、膜質低下等を抑制でき、信頼性の高い優れた薄膜コンデンサを実現することができる。

【0035】

また、短いピッチで高密度に配置されたトレンチ3aを有するトレンチ群3Aを設定し、このトレンチ群3Aの間の領域をトレンチ3a間に比べて大きく設定して、この領域に開口部6aを形成することにより、トレンチのパターン密度を高めて高静電容量を維持しつつ、上部電極6の応力を緩和することができる。

【0036】

なお、上述したとおり、本発明は、上記の各実施形態に限定されるものではなく、その要旨を変更しない限度において様々な変形が可能である。例えば、上部電極6に設ける開口部6aの形状や、配置に限定はない。ここで、図12〜図14は、上部電極6に設ける開口部6aの他のパターン例を示す平面図である。

【0037】

図12に示すように、円形の開口部6bを形成してもよく、また、図13に示すように、楕円形の開口部6cを形成してもよい。開口部の幾何学的形状は、特に高周波領域において電流のロスに影響すると推察される。このため、開口部を丸みを帯びた形状とすることにより、高周波における薄膜コンデンサ1のインピーダンスを低減することができる。さらに、上部電極6の平面内において同じ形状の開口部を形成する必要はなく、例えば、図14に示すように、長軸方向の異なる開口部6d,6eを形成してもよい。

【0038】

さらに、絶縁層3に形成するトレンチ3aの数及び形状にも制限はなく、例えば、トレンチは、楕円形のような丸みを帯びた開口形状を有していてもよく、閉じていない形状、すなわちトレンチ3aの一端が薄膜コンデンサの外縁にまで延在していてもよい。

【0039】

また、上部電極6の代わりに下部電極4に開口部を形成してもよい。又は、上部電極6及び下部電極4の双方に開口部を形成してもよい。さらに上部電極に形成した開口部と、下部電極に形成した開口部とは、互いに重なりあう位置に配置されても良いし、互いに異なる位置に配置されても良い。

【0040】

またさらに、トレンチ3aの内壁上及び絶縁層3上に下部電極4、誘電体膜5、及び、上部電極6からなる積層膜を多段に(例えば2セット以上)形成してもよい。また、必要に応じて、薄膜コンデンサ1上に窒化シリコンからなる密着層を形成し、この密着層上に絶縁層3を形成してもよい。さらにまた、下部電極4、誘電体膜5、及び、上部電極6からなる積層膜には、更に他の機能層が適宜の位置に形成されていてもよい。加えて、基体の両面にコンデンサ構造を形成してもよく、この場合、トレンチ3a、絶縁層3、並びに、下部電極4、誘電体膜5、及び上部電極6からなる積層膜は、基体の両面に形成される。

【産業上の利用可能性】

【0041】

以上説明した通り、本発明の薄膜コンデンサ及びその製造方法によれば、高い静電容量を維持しつつ、電極の応力を緩和して、信頼性の高い優れた薄膜コンデンサを実現することができるので、薄膜型の電子部品を内蔵する機器、装置、システム、各種デバイス等、特に小型化及び高性能化が要求されるものの製造用途に広く且つ有効に利用することができる。

【図面の簡単な説明】

【0042】

【図1】本発明による薄膜コンデンサ1の好適な一実施形態の概略構成を示す斜視図である。

【図2】本発明による薄膜コンデンサ1の好適な一実施形態の概略構成を示す斜視図である。

【図3】図2におけるIII-III線に沿う断面図である。

【図4】上部電極6の構成を示す平面図である。

【図5】薄膜コンデンサ1を製造している状態を示す断面図である。

【図6】薄膜コンデンサ1を製造している状態を示す断面図である。

【図7】薄膜コンデンサ1を製造している状態を示す断面図である。

【図8】薄膜コンデンサ1を製造している状態を示す断面図である。

【図9】薄膜コンデンサ1を製造している状態を示す断面図である。

【図10】薄膜コンデンサ1を製造している状態を示す断面図である。

【図11】薄膜コンデンサ1を製造している状態を示す断面図である。

【図12】上部電極6に形成される開口部6aの他のパターンを示す平面図である。

【図13】上部電極6に形成される開口部6aの他のパターンを示す平面図である。

【図14】上部電極6に形成される開口部6aの他のパターンを示す平面図である。

【符号の説明】

【0043】

1…薄膜コンデンサ、2…基板、3…絶縁層、3a…トレンチ、3A…トレンチ群、4…下部電極、5…誘電体膜、5a…開口部、6…上部電極、6a,6b,6c,6d,6e…開口部、7…保護膜、7a…開口部、8…パッド電極、20…マスク層、20a…開口部。

【技術分野】

【0001】

本発明は、薄膜コンデンサ及びその製造方法に関し、特に、トレンチ型の薄膜コンデンサ及びその製造方法に関する。

【背景技術】

【0002】

コンピュータや携帯端末等の電子機器の内部回路には、表面実装型の多種の電子部品が搭載されている。近時、電子機器の更なる高性能化及び小型化の要求に応えるべく、能動素子、受動素子を問わず、各種電子部品の更なる小型化及び薄型(薄膜)化が急務となっている。このような薄膜型の電子部品としては、薄膜形成プロセスを利用した、例えば、薄膜コンデンサ、薄膜インダクタ、薄膜LC複合部品、薄膜集中定数デバイス、薄膜分布デバイス、薄膜積層型複合部品等が挙げられる。

【0003】

これらのなかでも薄膜コンデンサの単位体積(容積)当たりの静電容量を増大させつつ小型化及び薄型化を達成する手法の一つとして、基体にトレンチ(下地段差構造)を形成し、そのトレンチに薄膜コンデンサを形成する方法が提案されている(特許文献1参照)。

【特許文献1】特開平6−325970号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

このようなトレンチ型の薄膜コンデンサでは、形成された薄膜内に応力(膜応力)が発生する問題があり、特に、誘電体膜よりも電極の膜応力が大きい傾向にある。これは、電極の形成過程において、通常、熱処理を行うことから、この熱処理により膜内に歪が蓄積し応力が発生するためである。また、誘電体膜に比べて、基体との間の線膨張係数の差が大きいことも、電極に応力が発生しやすい要因となっている。さらに、電極の抵抗を下げることを企図して電極の膜厚を大きくしようとすると、応力の増大を招いてしまう。

【0005】

かかる薄膜の応力は、基体の反りを誘発し、その結果、薄膜コンデンサの容量変動を引き起こしてしまったり、薄膜が基体から剥離してしまったりといった不都合が生じ得る。また、膜応力は、膜質低下の要因となり、膜の電気的特性自体に影響を及ぼし易い。このような問題は、薄型の基体を用いた近時の薄膜コンデンサにおいて顕著となる。

【0006】

そこで、本発明は上記の事情に鑑みてなされたものであり、その目的は、高い静電容量を維持しつつ、電極の応力を緩和することにより、信頼性の高い優れた薄膜コンデンサ及びその製造方法を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明の薄膜コンデンサは、トレンチが少なくとも一方面に形成された基体と、基体の少なくとも一方面上に形成された、下部電極、誘電体膜及び上部電極を含む積層膜と、上部電極及び/又は下部電極に形成された開口部とを備えるものである。

【0008】

上記構成の薄膜コンデンサでは、上部電極及び/又は下部電極に開口部が形成されていることから、積層膜に熱処理が施されて電極に熱的な歪(伸縮)が印加されても、かかる歪が全体に蓄積されることなく、これら電極に蓄積された応力が開口部において解放され、電極全体の膜応力が緩和される。ここで、開口部とは、上部電極及び/又は下部電極を貫通する貫通孔であっても、上部電極及び/又は下部電極を貫通せずに底面に電極の一部が残存した状態(露呈した状態)の凹部であってもよい。これは、貫通孔以外の凹部であっても、この凹部において応力が少なからず解放されるためである。また、開口部は、上部電極及び下部電極の双方に形成することが好ましいが、上部電極又は下部電極のいずれか一方のみに形成してもよい。

【0009】

上述した開口部の数及び配置は、薄膜コンデンサの容量に影響する。これは、仮に開口部を貫通孔とした場合には、開口部の部位にはコンデンサが形成されないからである。したがって、例えば、トレンチが複数形成されている場合には、開口部は、複数のトレンチの間の領域に形成されることが好ましい。

【0010】

より好ましくは、トレンチが複数形成されており且つそれらの複数のトレンチからなる所定のパターンを有するトレンチ群が、基体の少なくとも一方面に複数形成されており、開口部が、それら複数のトレンチ群の間の領域における上部電極及び/又は下部電極に形成されている。このように、トレンチ群の間の領域にのみ開口部を設けることにより、トレンチ群の内側の領域には開口部の寸法よりも小さい間隔で高密度にトレンチのパターンを配置できるので、薄膜コンデンサの高容量化に資することができる。

【0011】

また、本発明による薄膜コンデンサの製造方法は、本発明の薄膜コンデンサを有効に製造するための方法であって、基体の少なくとも一方面にトレンチを形成する工程と、基体の少なくとも一方面上に、下部電極、誘電体膜及び上部電極を含む積層膜を形成する工程とを有しており、積層膜を形成する工程においては、下部電極及び/又は上部電極に開口部を形成する。

【0012】

上記構成の薄膜コンデンサの製造方法では、上部電極及び/又は下部電極に開口部を形成していることから、電極材料の成膜過程において膜内に蓄積する歪や、成膜後の熱処理に起因して発生する応力は、この開口部において解放され、電極全体の膜応力が緩和される。上述したように、本発明において「開口部」とは、このような電極を貫通する貫通孔であっても、電極を貫通せずに底面に電極の一部を残した状態の凹部であってもよい。

【発明の効果】

【0013】

本発明によれば、上部電極及び/又は下部電極に開口部が形成されていることから、これら電極に蓄積された応力が開口部において解放され、電極全体の膜応力が緩和される。したがって、基体の反り、基体からの薄膜の剥離、膜質低下等を抑制でき、信頼性の高い優れた薄膜コンデンサを実現することができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態について、図面を参照して説明する。なお、図面中、同一の要素には同一の符号を付し、重複する説明を省略する。また、上下左右などの位置関係は、特に断らない限り、図面に示す位置関係に基づくものとする。さらに、図面の寸法比率は、図示の比率に限定されるものではない。また、以下の実施の形態は、本発明を説明するための例示であり、本発明をその実施の形態のみに限定する趣旨ではない。さらに、本発明は、その要旨を逸脱しない限り、さまざまな変形が可能である。

【0015】

<第1実施形態>

図1及び図2は、それぞれ本発明による薄膜コンデンサの好適な一実施形態の概略構成を示す斜視図及び平面図であり、図3は図2におけるIII-III線に沿う断面図である。

【0016】

図1〜図3に示すように、基板2上には、絶縁層3が形成されており、絶縁層3にはトレンチ3aが形成されている。基板2及び絶縁層3から本発明における基体が構成されている。絶縁層3の厚さは、形成すべきトレンチ3aの深さに応じて適宜設定することができる。また、基板2の材料としては、特に制限されず、シリコン基板、アルミナ等のセラミックス基板、ガラスセラミックス基板、ガラス基板、サファイア、MgO、SrTiO3等の単結晶基板等が挙げられ、化学的且つ熱的に安定であり、且つ、応力発生が少なく表面の平滑性を保持し易いものを用いることが好ましい。さらに、絶縁層3の材質も特に制限されず、例えばAl2O3、SiO2、Si等を列挙することができる。

【0017】

さらに、トレンチ3aの内壁上及び絶縁層3上には、下部電極4、誘電体膜5、及び、上部電極6からなる積層膜が形成されている。誘電体膜5には、パッド電極8と下部電極4との接続部位に開口部5aが形成されている。

【0018】

下部電極4及び上部電極6としては、例えば、Cu、Au、Pt、Ag、Sn、Cr、Co、Ni等を含む金属、又はこれらを含む合金等の複合金属が挙げられる。誘電体膜5の材料は特に限定されず、例えば、Al2O3、PbTiO3(PZT)、BaTiO3、BaTiO3、ZrO2、HfO2、Bi4Ti3O12、SrBi2Ta2O9、SiO2等からなる。

【0019】

この積層膜上には、保護膜7が形成されており、保護膜7には2つの開口部7a,7aが形成され、さらに、開口部7a内には下部電極4及び上部電極6が露出している。そして、この開口部7aを埋め込むように、保護膜7上に2つのパッド電極8,8が形成されている。

【0020】

保護膜7は、絶縁材料であれば特に限定されず、例えば、Al2O3、SiO2、SiNなどの無機物とポリイミド、エポキシなどの樹脂からなる。パッド電極8として、例えば、Cu、Au、Pt、Ag、Sn、Cr、Co、Ni等を含む金属、又はこれらを含む複合金属が挙げられる。

【0021】

また、薄膜コンデンサ1には、少なくとも上部電極6又は下部電極4のいずれかに開口部が形成されており、本実施形態では、上部電極6に開口部を形成する例について以下に説明する。

【0022】

図4は、開口部6aが設けられた上部電極6の構成を示す平面図である。同図に示す如く、上部電極6は、複数のトレンチ3aのパターン構造によって画成される下地の段差構造を被覆するように形成されている。これらのトレンチ3aの形成されていない部位、すなわちトレンチ3a間の領域に、開口部6aが形成されている。

【0023】

この開口部6aは、上部電極6に蓄積された応力を解放させるために配設されたものである。ここで、開口部6aは、このような電極を貫通する貫通孔であっても、電極を貫通せずに底面に電極の一部を残した状態の凹部であってもよい。応力をより多く解放させる観点からは、凹部よりも貫通孔の方が好ましいものの、静電容量をより高める観点からは、貫通孔ではその部位にコンデンサが形成されないため、非貫通型の凹部の方が好ましい。

【0024】

ここで、近時、高い静電容量を得ることを企図して、短いピッチ(間隔)で複数のトレンチ3aが配置される傾向にあり、トレンチ3aのパターン間の狭い領域に開口部6aを形成することが困難な傾向にある。これに対し、図4に示す例では、かかる事情を考慮して、短いピッチで高密度に格子状に配置されたトレンチ3aを有するトレンチ群3Aを設け、このトレンチ群3Aの間の領域をトレンチ3a間に比べて大きく設定して、この領域に開口部6aが形成されている。これにより、高静電容量を維持しつつ、上部電極6の応力を有効に緩和することができる。

【0025】

次に、上記構成の本実施形態に係る薄膜コンデンサの製造方法について、図5〜図11を参照して説明する。

【0026】

図5〜図11は、薄膜コンデンサ1を製造している状態を示す断面図(工程図)である。図5に示すように、基板2上の全面に、絶縁層3を形成する。絶縁層3の形成では、例えばSiからなる基板2上に、スパッタリング法により、Al2O3膜を堆積させる。絶縁層3の厚さは、形成すべきトレンチに応じて設定され、例えば、5μm〜50μmである。

【0027】

次に、図6に示すように、絶縁層3上に、トレンチを形成すべき部位に開口部20aを有するマスク層20を形成する。本実施形態では、マスク層20として、例えば、Ru、または、NiFeからなる金属マスクをパターニングする。Ru、または、NiFe膜の堆積にはスパッタリング法を用いることができ、その膜のパターン化にはサブトラクティブ法又はアディティブ法を用いることができる。サブトラクティグ法を採用する場合には、例えば、SiO2酸化膜付きSiからなる基板2上にスパッタリング法によりNiFe膜を堆積させた後に、NiFe膜上にレジストパターンを形成し、レジストパターンをマスクとしたドライエッチング又はウェットエッチングにより、NiFe膜をパターニングする。これに対して、アディティブ法を採用する場合には、基板2上にレジストパターンを形成した後に、全面にスパッタリング法によりNiFe膜を堆積させて、レジストパターンとともにレジストパターン上の不要なNiFe膜を除去することにより、所望のパターンのNiFe膜を形成する。

【0028】

次いで、図7に示すように、リアクティブイオンエッチング(RIE)により、開口部20a内に露出した絶縁層3を除去して、トレンチ3aを形成した後に、マスク層20を除去する。ここで、図7では、基板2に達するトレンチ3aを示しているが、トレンチ3aは基板2に達していなくてもよい。また、トレンチ3aの形成方法として、イオンミリングを用いてもよい。

【0029】

次に、図8に示すように、トレンチ3aの内壁上及び絶縁層3上に、下部電極4をパターニングする。当該工程では、下部電極4としてCu膜をスパッタリングし、下部電極4のパターニングには、上述したサブトラクティブ法又はアディティブ法を使用する。

【0030】

さらに、図9に示すように、下部電極4及び絶縁層3上に、誘電体膜5をパターニングする。当該工程では、ALD(Atomic Layer Deposition)法によりAl2O3膜を堆積させた後、レジストパターンを用いたエッチングにより、パッド電極8との接続部位におけるAl2O3膜を除去して開口部5aを形成する。

【0031】

それから、図10に示すように、誘電体膜5上に上部電極6をパターニングする。当該工程では、上部電極6としてCu膜をスパッタリングし、上部電極6のパターニングには、上述したサブトラクティブ法又はアディティブ法を使用する。本実施形態では、この上部電極6のパターニングにおいて、上部電極6に開口部6aを形成する。このように、上部電極6に開口部を形成することにより、電極材料の成膜過程において膜内に蓄積する歪や、成膜後の熱処理に起因して発生する応力は、この開口部6aにおいて解放され、上部電極6全体の膜応力が緩和される。

【0032】

次に、図11に示すように、下部電極4、誘電体膜5、及び、上部電極6上に、下部電極4及び上部電極6が露出した開口部7a,7aを備える保護膜7を形成する。保護膜7の形成では、例えば基板2の全面に、例えばスパッタリング法により、Al2O3膜を堆積させた後、レジストパターンを用いたエッチングにより、開口部7a,7aを形成する。

【0033】

以降の工程としては、必要に応じて基板2の裏面を研削して薄膜化した後に、ダイシングにより個々の薄膜コンデンサ1に分割し、薄膜コンデンサ1を得る。

【0034】

このように構成された薄膜コンデンサ1によれば、上部電極6に開口部6aが形成されていることから、上部電極6に蓄積された応力が開口部6aにおいて解放され、上部電極6全体の膜応力が緩和される。したがって、基体の反り、基体からの薄膜の剥離、膜質低下等を抑制でき、信頼性の高い優れた薄膜コンデンサを実現することができる。

【0035】

また、短いピッチで高密度に配置されたトレンチ3aを有するトレンチ群3Aを設定し、このトレンチ群3Aの間の領域をトレンチ3a間に比べて大きく設定して、この領域に開口部6aを形成することにより、トレンチのパターン密度を高めて高静電容量を維持しつつ、上部電極6の応力を緩和することができる。

【0036】

なお、上述したとおり、本発明は、上記の各実施形態に限定されるものではなく、その要旨を変更しない限度において様々な変形が可能である。例えば、上部電極6に設ける開口部6aの形状や、配置に限定はない。ここで、図12〜図14は、上部電極6に設ける開口部6aの他のパターン例を示す平面図である。

【0037】

図12に示すように、円形の開口部6bを形成してもよく、また、図13に示すように、楕円形の開口部6cを形成してもよい。開口部の幾何学的形状は、特に高周波領域において電流のロスに影響すると推察される。このため、開口部を丸みを帯びた形状とすることにより、高周波における薄膜コンデンサ1のインピーダンスを低減することができる。さらに、上部電極6の平面内において同じ形状の開口部を形成する必要はなく、例えば、図14に示すように、長軸方向の異なる開口部6d,6eを形成してもよい。

【0038】

さらに、絶縁層3に形成するトレンチ3aの数及び形状にも制限はなく、例えば、トレンチは、楕円形のような丸みを帯びた開口形状を有していてもよく、閉じていない形状、すなわちトレンチ3aの一端が薄膜コンデンサの外縁にまで延在していてもよい。

【0039】

また、上部電極6の代わりに下部電極4に開口部を形成してもよい。又は、上部電極6及び下部電極4の双方に開口部を形成してもよい。さらに上部電極に形成した開口部と、下部電極に形成した開口部とは、互いに重なりあう位置に配置されても良いし、互いに異なる位置に配置されても良い。

【0040】

またさらに、トレンチ3aの内壁上及び絶縁層3上に下部電極4、誘電体膜5、及び、上部電極6からなる積層膜を多段に(例えば2セット以上)形成してもよい。また、必要に応じて、薄膜コンデンサ1上に窒化シリコンからなる密着層を形成し、この密着層上に絶縁層3を形成してもよい。さらにまた、下部電極4、誘電体膜5、及び、上部電極6からなる積層膜には、更に他の機能層が適宜の位置に形成されていてもよい。加えて、基体の両面にコンデンサ構造を形成してもよく、この場合、トレンチ3a、絶縁層3、並びに、下部電極4、誘電体膜5、及び上部電極6からなる積層膜は、基体の両面に形成される。

【産業上の利用可能性】

【0041】

以上説明した通り、本発明の薄膜コンデンサ及びその製造方法によれば、高い静電容量を維持しつつ、電極の応力を緩和して、信頼性の高い優れた薄膜コンデンサを実現することができるので、薄膜型の電子部品を内蔵する機器、装置、システム、各種デバイス等、特に小型化及び高性能化が要求されるものの製造用途に広く且つ有効に利用することができる。

【図面の簡単な説明】

【0042】

【図1】本発明による薄膜コンデンサ1の好適な一実施形態の概略構成を示す斜視図である。

【図2】本発明による薄膜コンデンサ1の好適な一実施形態の概略構成を示す斜視図である。

【図3】図2におけるIII-III線に沿う断面図である。

【図4】上部電極6の構成を示す平面図である。

【図5】薄膜コンデンサ1を製造している状態を示す断面図である。

【図6】薄膜コンデンサ1を製造している状態を示す断面図である。

【図7】薄膜コンデンサ1を製造している状態を示す断面図である。

【図8】薄膜コンデンサ1を製造している状態を示す断面図である。

【図9】薄膜コンデンサ1を製造している状態を示す断面図である。

【図10】薄膜コンデンサ1を製造している状態を示す断面図である。

【図11】薄膜コンデンサ1を製造している状態を示す断面図である。

【図12】上部電極6に形成される開口部6aの他のパターンを示す平面図である。

【図13】上部電極6に形成される開口部6aの他のパターンを示す平面図である。

【図14】上部電極6に形成される開口部6aの他のパターンを示す平面図である。

【符号の説明】

【0043】

1…薄膜コンデンサ、2…基板、3…絶縁層、3a…トレンチ、3A…トレンチ群、4…下部電極、5…誘電体膜、5a…開口部、6…上部電極、6a,6b,6c,6d,6e…開口部、7…保護膜、7a…開口部、8…パッド電極、20…マスク層、20a…開口部。

【特許請求の範囲】

【請求項1】

トレンチが少なくとも一方面に形成された基体と、

前記基体の少なくとも一方面上に形成された、下部電極、誘電体膜及び上部電極を含む積層膜と、

前記上部電極及び/又は前記下部電極に形成された開口部と、

を備える薄膜コンデンサ。

【請求項2】

前記トレンチが複数形成されており、

前記開口部は、前記複数のトレンチの間の領域に形成された、

請求項1記載の薄膜コンデンサ。

【請求項3】

前記トレンチが複数形成されており且つ該複数のトレンチからなる所定のパターンを有するトレンチ群が、前記基体の少なくとも一方面に複数設けられており、

前記開口部が、前記複数のトレンチ群の間の領域における前記上部電極及び/又は前記下部電極に形成された、

請求項1記載の薄膜コンデンサ。

【請求項4】

基体の少なくとも一方面にトレンチを形成する工程と、

前記基体の少なくとも一方面上に、下部電極、誘電体膜及び上部電極を含む積層膜を形成する工程と、

を有し、

前記積層膜を形成する工程においては、前記下部電極及び/又は前記上部電極に開口部を形成する、

薄膜コンデンサの製造方法。

【請求項1】

トレンチが少なくとも一方面に形成された基体と、

前記基体の少なくとも一方面上に形成された、下部電極、誘電体膜及び上部電極を含む積層膜と、

前記上部電極及び/又は前記下部電極に形成された開口部と、

を備える薄膜コンデンサ。

【請求項2】

前記トレンチが複数形成されており、

前記開口部は、前記複数のトレンチの間の領域に形成された、

請求項1記載の薄膜コンデンサ。

【請求項3】

前記トレンチが複数形成されており且つ該複数のトレンチからなる所定のパターンを有するトレンチ群が、前記基体の少なくとも一方面に複数設けられており、

前記開口部が、前記複数のトレンチ群の間の領域における前記上部電極及び/又は前記下部電極に形成された、

請求項1記載の薄膜コンデンサ。

【請求項4】

基体の少なくとも一方面にトレンチを形成する工程と、

前記基体の少なくとも一方面上に、下部電極、誘電体膜及び上部電極を含む積層膜を形成する工程と、

を有し、

前記積層膜を形成する工程においては、前記下部電極及び/又は前記上部電極に開口部を形成する、

薄膜コンデンサの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2009−135310(P2009−135310A)

【公開日】平成21年6月18日(2009.6.18)

【国際特許分類】

【出願番号】特願2007−311067(P2007−311067)

【出願日】平成19年11月30日(2007.11.30)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

【公開日】平成21年6月18日(2009.6.18)

【国際特許分類】

【出願日】平成19年11月30日(2007.11.30)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

[ Back to top ]