薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法に関し、特に、フレキシブルな樹脂基板に形成された薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法に関する。

【背景技術】

【0002】

従来から、家庭用の大型テレビからPC、携帯電話に至るまで、LCD(Liquid Crystal Display、液晶ディスプレイ)やPDP(Plasma Display Panel、プラズマディスプレイパネル)、あるいは有機EL(Electro-Luminescence)など、フラットパネルディスプレイが広く普及している。これらのディスプレイには、従来から基板としてガラスが用いられてきたが、ディスプレイの更なる大型化や軽量化、収納性や耐衝撃性の向上などを実現するため、軽量で柔軟なプラスティック基板の適用が望まれる。更に、極めて柔軟性に優れたプラスティック基板が適用されるようになれば、自由に丸めて持ち運べる巻物型のディスプレイや、プロジェクターが不要なスクリーン型の大型ディスプレイなど、種々の新しいディスプレイの実現が可能となる。

【0003】

しかし、プラスティックフィルムなどを基板として用いる場合、耐熱性や耐薬品性がガラスに比べて大きく劣るため、作製プロセスを進める上で種々の制約が生じる。一般に、プラスティックは熱変形が大きく、従来のフォトリソグラフィー法により電極や薄膜トランジスタ、画素電極をパターニングすると、熱工程を重ねるにつれパターニング時にアライメントずれなどが発生し、歩留まりが大幅に低下する。特に、大型基板を用いる程、基板伸縮の影響が大きくなるため、大画面のフレキシブルディスプレイへの適用は極めて困難となる。また高温になるほど熱変形が増大するため、半導体や絶縁膜等に高温処理が必要な材料を適用する場合、加熱が不十分となり易く、これにより特性の劣化や不安定性を誘発する場合がある等の課題もあった。更に、プラスティック材料により薬品による劣化が生じるため、ガラス基板を用いた場合と同じ材料や作製プロセスの適用も困難である。

【0004】

このような課題に対し、ガラス基板上に従来の作製プロセスで配線パターンや薄膜トランジスタを形成し、ガラス基板を溶かしてプラスティック基板上に接着させる手法が提案されている(例えば、特許文献1参照)。また、他の手法とし、ガラス基板に剥離層を設け、その上に従来の手法でパターニングを行い、プラスティック基板に接着した後ガラス基板から剥離させる転写技術も提案されている(例えば、特許文献2〜5参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−323132号公報

【特許文献2】特開2008−159934号公報

【特許文献3】特開2008−159935号公報

【特許文献4】特開2010−10185号公報

【特許文献5】特開2010−10186号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述の特許文献1に記載の方法ではガラス基板を溶かすための薬品を必要とするため適用できるプラスティック材料が限られるだけでなく、工程が複雑になるため高い生産性が得られないという問題があった。

【0007】

また、上述の特許文献2〜5に記載の方法では、剥離させる際に電極や絶縁膜、半導体層などに強い応力が発生し、膜の剥離や配線不良、特性劣化などが発生しやすいという問題があった。

【0008】

そこで、本発明は、上記の点を鑑みてなされたもので、絶縁膜と薄膜トランジスタを形成した導電性ワイヤーを形成し、基板となる樹脂と一体化する工程を導入することにより、大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本発明の一態様に係る薄膜トランジスタは、フレキシブルな樹脂基板に形成された薄膜トランジスタであって、

周面の一部又は全部が導電性材料により覆われたワイヤーと、

前記導電性材料を覆う絶縁膜と、

該絶縁膜を介して前記導電性材料上に形成された薄膜半導体と、が一体的に構成されたゲート・チャネル一体形成部を有し、

該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極が接続されて形成されたことを特徴とする。

【0010】

また、前記ワイヤーは、非導電性材料からなる構成を有してもよい。

【0011】

また、前記ワイヤーの延在方向に沿って、複数の前記薄膜半導体が形成されてもよい。

【0012】

また、前記絶縁膜は、前記ワイヤーの全周を被覆し、前記ワイヤーの周方向においては、1個の薄膜半導体が形成されてもよい。

【0013】

本発明の他の態様に係る薄膜トランジスタアレイ基板は、フレキシブルな樹脂基板にマトリクス状に形成された画素電極と、

前記画素電極に各々対応して設けられた前記薄膜トランジスタと、を有することを特徴とする。

【0014】

本発明の他の態様に係るフレキシブル表示素子は、前記薄膜トランジスタアレイ基板と、

該薄膜トランジスタアレイ基板に対向して配置されたフレキシブルな樹脂基板と、

該樹脂基板と前記薄膜トランジスタアレイ基板との間に、前記画素電極に対応して配置された画素と、を有することを特徴とする。

【0015】

本発明の他の態様に係る薄膜トランジスタアレイ基板の製造方法は、フレキシブルな樹脂基板にマトリクス状に配置された画素電極と該画素電極に対応して設けられた薄膜トランジスタを有する薄膜トランジスタアレイ基板の製造方法であって、

周囲の一部又は全周が導電性材料により被覆されたワイヤーの周囲に絶縁膜を形成するゲート絶縁膜形成工程と、

該絶縁膜上の前記導電性材料が存在する位置を覆うように、薄膜半導体を形成してチャネルを形成するチャネル形成工程とを含み、ゲートとチャネルが一体形成されたゲート・チャネル一体形成部を作製するゲート・チャネル一体形成部作製工程と、

前記ゲート・チャネル一体形成部が樹脂基板の表面又は内部の所定位置に配置されるように、流動体状の樹脂を硬化して樹脂基板を形成する樹脂基板形成工程と、

前記薄膜半導体の両端の位置に、第1及び第2の電極を形成する電極形成工程と、を有することを特徴とする。

【0016】

また、前記樹脂形成工程は、前記ゲート・チャネル一体形成部の両端が固定されて前記所定位置に固定された状態で、前記流動体状の樹脂を硬化してもよい。

【0017】

また、前記樹脂基板形成工程は、前記ゲート・チャネル一体形成部を配置する高さまで第1樹脂基板層を形成する第1樹脂基板層形成工程と、

該樹脂基板上に前記ゲート・チャネル一体形成部を配置する位置決め工程と、

前記ゲート・チャネル一体形成部を埋めるように第2樹脂基板層を形成する第2樹脂基板層形成工程とを有し、

前記電極形成工程は、前記樹脂基板の前記薄膜半導体の両端の位置に開口を形成する開口形成工程を含み、該開口に充填するように前記第1及び第2の電極を形成してもよい。

【発明の効果】

【0018】

本発明によれば、柔軟な基板を用いても配線不良の少ない薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子及びフレキシブル表示装置を提供することができる。

【図面の簡単な説明】

【0019】

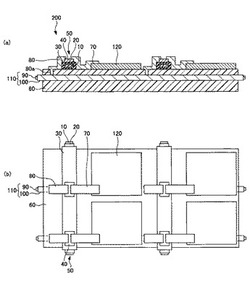

【図1】本発明の実施形態1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図1(a)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図である。図1(b)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【図2】本発明の実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図2(a)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図である。図2(b)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【図3】本発明の実施形態3に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【図4】本発明の実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【図5】ゲート・チャネル一体形成部を樹脂基板層内に配置するための一方式を示したものである。図5(a)は、複数のゲート・チャネル一体形成部を平行に配列し、両端を固定治具により固定した状態を示した図である。図5(b)は、樹脂材料63aを流し込んだ状態を示した図である。図5(c)は、樹脂基板層63を形成した状態を示した図である。

【図6】樹脂基板層の上部にゲート・チャネル一体形成部を配置するための一方式を示した図である。図6(a)は、ゲート・チャネル一体形成部を樹脂材料上に配置する状態を示した図である。図6(b)は、樹脂材料63aを完全に硬化させた状態を示した図である。

【図7】補助ワイヤーを用いたゲート・チャネル一体形成部の設置方法の説明図である。

【図8】実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1段階の一連の工程を示した図である。図8(a)は、樹脂材料供給工程の一例を示した図である。図8(b)は、第1樹脂基板層形成工程の一例を示した図である。図8(c)は、第1樹脂基板層取り出し工程の一例を示した図である。図8(d)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層ビアホール形成工程の一例を示した図である。

【図9】実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2段階の一連の工程を示した図である。図9(a)は、レジスト除去工程の一例を示した図である。図9(b)は、配線用ワイヤー設置工程の一例を示した図である。図9(c)は、微細電極形成工程の一例を示した図である。図9(d)は、第2樹脂基板層用樹脂材料供給の一例を示した図である。

【図10】実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第3段階の一連の工程を示した図である。図10(a)は、第2樹脂基板層形成工程の一例を示した図である。図10(b)は、第2樹脂基板層取り出し工程の一例を示した図である。図10(c)は、第2樹脂基板層ビアホール形成工程の一例を示した図である。図10(d)は、レジスト除去工程の一例を示した図である。

【図11】実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の最終段階の一連の工程を示した図である。図11(a)は、第2樹脂基板層微細電極形成工程の一例を示した図である。図11(b)は、画素電極成膜工程の一例を示した図である。図11(c)は、画素電極パターニング工程の一例を示した図である。図11(d)は、レジスト除去工程の一例を示した図である。

【図12】図8(c)、(d)及び図9(a)、(b)の工程を上面から透過的に示した平面図である。図12(a)は、第1樹脂基板層取り出し工程の平面図である。図12(b)は、第1樹脂基板層ビアホール形成工程〜レジスト除去工程の平面図である。図12(c)は、配線用ワイヤー設置工程の平面図である。

【図13】図9(c)の工程を上面から示した平面図である。図13(a)は、微細電極形成工程の前半の導電膜形成工程を示した平面図である。図13(b)は、微細電極形成工程の後半の導電膜形成工程を示した平面図である。

【図14】ビアホール形成までの工程を示した図である。図14(a)は、図12(a)と同様の第1樹脂基板層取り出し工程の平面図である。図14(b)は、ビアホール形成工程の平面図及び断面図である。

【図15】微細電極と配線用ワイヤーを接続する一連の工程を示した平面図である。図15(a)は、導電膜形成工程を示した図である。図15(b)は、微細電極形成工程の平面図及び断面図である。図15(c)は、配線用ワイヤー設置工程を示した平面図及び断面図である。

【図16】本発明の実施形態5に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。

【図17】本発明の実施形態6に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。

【発明を実施するための形態】

【0020】

以下、図面を参照して、本発明を実施するための形態の説明を行う。

【0021】

〔実施形態1〕

図1は、本発明の実施形態1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図1(a)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図であり、図1(b)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【0022】

なお、薄膜トランジスタアレイ基板は、フレキシブル表示素子の表示素子を含まない駆動側の基板を意味するので、以下の説明において、薄膜トランジスタアレイ基板のことを、フレキシブル表示素子のバックプレーンと呼んでもよいこととする。

【0023】

図1(a)、(b)において、実施例1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板は、第1のワイヤー10と、導電性材料20と、絶縁膜30と、薄膜半導体40と、樹脂基板層60と、第1の微細電極70と、第2の微細電極80と、第2のワイヤー90と、導電性材料100と、画素電極120とを備える。また、第1のワイヤー10と、導電性材料20と、絶縁膜30と、薄膜半導体40とで、ゲート・チャネル一体形成部50を構成する。また、第2のワイヤー90と導電性材料100とで配線用ワイヤー110を構成する。

【0024】

図1(a)において、第1のワイヤー10の周囲を導電性材料20が被覆しており、導電性材料20の周囲を絶縁膜30が被覆している。導電性材料20は、薄膜トランジスタ200のゲートの機能を有し、絶縁膜30はゲート絶縁膜の機能を有する。導電性材料20の直上の位置の絶縁膜30の表面上には、薄膜半導体40が形成されている。薄膜半導体40は、薄膜トランジスタ200のチャネルの機能を果たす。第1のワイヤー10、導電性材料20、絶縁膜30及び薄膜半導体40は、一体的に構成されており、樹脂基板層60の表面上に設けられている。薄膜半導体40の両側には、第1の微細電極70と第2の微細電極80が各々の側に、薄膜半導体40の両端部を覆うように形成されており、薄膜半導体40と電気的に接続されている。第1の微細電極70及び第2の微細電極80は、ソース電極又はドレイン電極の役割を果たす。第1の微細電極70の外側の樹脂基板層60の表面上には、画素電極120が形成され、第1の微細電極70は画素電極120の端部を覆うように形成されて両者は電気的に接続されている。樹脂基板層60の内部には、第2のワイヤー90が、第1のワイヤー10と直交する方向に延在して配置され、第2のワイヤー90の周囲を導電性材料100が被覆しており、配線用ワイヤー110を構成している。導電性材料100には、ビアホール80aを通して第2の微細電極80が接続されている。また、薄膜トランジスタ200は、図1(a)において2個形成されている。

【0025】

図1(b)において、樹脂基板層60の表面上で、第1のワイヤー10、導電性材料20、絶縁膜30が縦方向に延在している。薄膜半導体40は、絶縁膜30上でパターニングされて島状に2個形成されている。第1のワイヤー10、導電性材料20、絶縁膜30及び薄膜半導体40でゲート・チャネル一体形成部50が構成されるが、ゲート・チャネル一体形成部50は、2本平行に配置され、その間に画素電極120が形成されている。第1の微細電極70は、薄膜半導体40と画素電極120を接続するように横方向に形成されている。また、画素電極120、第1及び第2の微細電極70、80及び薄膜半導体40を横方向に貫くように樹脂基板層60の内部に配線用ワイヤー110が配置され、第2の微細電極80との接続が図られている(図1(a)参照)。

【0026】

実施形態1に係る薄膜トランジスタ200は、かかる構成を有するが、ゲート・チャネル一体形成部50が一体となって構成され、樹脂基板層60の所定の位置に置くように配置することができるので、位置合わせが極めて容易であり、配線形成を容易に行うことができる。

【0027】

次に、個々の構成要素の機能について説明する。

【0028】

第1のワイヤー10は、ゲート・チャネル一体形成部50の基材となる役割を果たす部材である。実施形態1に係る薄膜トランジスタ200においては、第1のワイヤー10を中心に配置し、その周囲に導電性材料20、絶縁膜30及び薄膜半導体40を形成してゲート・チャネル一体形成部50を構成するので、樹脂基板層60と別体としてゲート及びチャネルを構成することができる。樹脂基板層60は、プラスティック等の樹脂で構成され、熱に弱く、変形し易い性質を有する。一方、絶縁膜30や薄膜半導体40は、形成のために十分な加熱が必要であり、樹脂基板層60に直接形成すると、樹脂基板層60の耐熱性の問題から、十分な加熱を行うことができない。

【0029】

そこで、本実施形態においては、ゲート・チャネル一体形成部50を樹脂基板層60とは別体として構成し、十分な加熱加工が可能な構成となっている。その際、ゲートとチャネルを形成する基材が必要となるが、第1のワイヤー10は、そのような基材の役割を果たしている。

【0030】

第1のワイヤー10は、種々の材料から構成されてよいが、例えば、絶縁体等の非導電性材料から構成されてもよい。第1のワイヤー10の周囲は、導電性材料20で被覆されるので、導電性材料である必要は無く、所望の材料を用いることができる。例えば、第1のワイヤー10には、絶縁性ワイヤーを用いるようにしてもよい。また、第1のワイヤー10は、例えば、ニッケルや鉄等、種々の金属から成るピアノ線等のように、配線材料に比べて導電性が低い材料が用いられてもよい。なお、ピアノ線等のように、導電性が高くない材料を用いる場合であっても、導電性材料20は、金や銅、アルミニウム等の配線金属レベルの高い導電性を有することが必要とされるため、絶縁性ワイヤーを用いる場合と同様に、導電性材料20による被覆はやはり行うことになる。

【0031】

第1のワイヤー10は、被覆する周囲の導電性膜よりも熱膨張率の低い材料を用いることが好ましい。例えば、ディスプレイ用の配線には比較的導電性が高く安価な銅やアルミニウムなどが用いられるが、第1のワイヤー10自体をそれらの金属材料で構成するよりも、例えば、ピアノ線又はピアノ線より線膨張率が低いワイヤーを第1のワイヤー10として用意し、第1のワイヤー10の周囲をそれらの金属材料で被膜した構成とすることにより、低い線膨張率と高い導電性を両立させることができる。これにより、回路抵抗が低く、熱による性能劣化が低い信頼性の高い素子の作製が可能となる。

【0032】

更に金属を用いた導電性ワイヤーの場合、作製プロセスによっては、金属表面の酸化や薬品による劣化などが大きな課題となる。しかしながら、実施形態1に係る薄膜トランジスタ200においては、第1のワイヤー10と導電性膜20の二層構造にすることにより、作製プロセスに応じて、例えば表面に形成する導電材料に耐薬品性に優れた材料などを自由に選択できるため、それらの問題にも十分対処することが可能である。

【0033】

このように、実施形態1に係る薄膜トランジスタ200は、第1のワイヤー10と導電成膜20の二重構造を採用することにより、第1のワイヤー10と導電性材料20の双方について、用途や製造プロセスに応じた幅広い材料選択が可能な構成となっている。

【0034】

導電性材料20は、ゲート電極としての役割を果たす。導電性材料20は、配線として使用できれば、種々の材料を用いてよいが、例えば、銅、アルミニウム、金、銀といった導電性の高い金属材料を用いてもよい。これらの金属材料は、既に配線用金属材料として用いられている材料であり、導電性材料20に好適に用いることができる。なお、導電性材料20は、第1のワイヤー10の全周を被覆して構成されてもよいし、第1のワイヤーを部分的に覆うように構成されてもよい。

【0035】

上記の第1のワイヤー10と導電性材料20の組み合わせとしては、例えば、表面が銅めっきされたピアノ線等が挙げられる。

【0036】

絶縁膜30は、ゲート絶縁膜として機能することが可能であれば、種々の絶縁性材料を用いることができる。

【0037】

薄膜半導体40は、薄膜トランジスタ200のチャネルとしての役割を果たす箇所である。図1においては、薄膜半導体40は、上面に設けられているが、絶縁膜30を介して導電性材料20の直上にあれば、種々の位置に設けることができる。

【0038】

薄膜半導体40は、有機半導体材料から構成されてもよいし、シリコン又は酸化物からなる無機半導体材料から構成されてもよい。

【0039】

樹脂基板層60は、樹脂から構成されたフレキシブルな基板層であり、例えば、プラスティック基板層で構成されてもよい。

【0040】

第1の微細電極70及び第2の微細電極80は、ソース電極又はドレイン電極としての役割を果たす電極である。第1の微細電極70及び第2の微細電極80は、導電性材料から構成される。例えば、金属材料から構成されてもよい。図1(a)において、第1の微細電極70は、樹脂基板層60の表面同士の接続を行えばよいので、樹脂基板層60の表面上に形成されているが、第2の微細電極80は、樹脂基板層60中にある導電性材料100と接続される必要があるので、樹脂基板層60の中に形成されたビアホール80aに充填されて形成されている。

【0041】

配線用ワイヤー110は、横方向の配線ために設けられ、第2のワイヤー90の周囲を導電性材料100が被覆して構成されている。第2のワイヤー90及び導電性材料100は、第1のワイヤー10及び導電性材料20と同じ材料から構成されてよい。

【0042】

なお、配線用ワイヤー110は、第1のワイヤー10と異なり、熱膨張係数や線膨張率を低下させることに大きな注意を払う必要は必ずしも無く、配線用金属等を用いた導電性ワイヤーを用いることも可能である。配線用金属又はこれに準ずる導電性を有する材料で構成された導電性ワイヤーを用いた場合、導電性材料20、100により必ずしも被膜される必要はない。

【0043】

画素電極120は、画素に電圧を印加するための電極であり、導電膜から構成されてよい。例えば、画素に用いられる表示素子は、用途に応じて種々の素子を用いることができ、液晶素子、有機EL(Electro-luminescence)素子、無機EL素子、電子インク又は電子粉流体を用いることができる。本実施例においては、表示素子が液晶素子である例が挙げられている。

【0044】

実施形態1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板によれば、ゲート・チャネル一体形成部50を樹脂基板層60と別体として構成することにより、十分な加熱加工が可能になるとともに、これを樹脂基板層60の表面上に配置することにより、薄膜トランジスタ200の位置決め形成を容易に行うことができる。

【0045】

〔実施形態2〕

図2は、本発明の実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図2(a)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図であり、図2(b)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【0046】

図2(a)において、実施形態2に係る薄膜トランジスタ201及び薄膜トランジスタアレイ基板は、第1のワイヤー11と、導電性材料21と、絶縁膜31と、薄膜半導体41と、樹脂基板層61と、第1の微細電極71と、第2の微細電極81と、第2のワイヤー91と、導電性材料101と、画素電極121とを有する。また、第1のワイヤー11、導電性材料21、絶縁膜31及び薄膜半導体41は、ゲート・チャネル一体形成部51を構成する。更に、第2のワイヤー91及び導電性材料101は、配線用ワイヤー111を構成する。

【0047】

図2(a)において、実施形態2に係る薄膜トランジスタ201は、第1のワイヤー11、導電性材料21、絶縁膜31及び薄膜半導体41から構成されるゲート・チャネル一体形成分51は、樹脂基板層61の内部に配置されている点で、実施形態1に係る薄膜トランジスタ200と異なっている。また、これに対応し、横方向に延在する配線用ワイヤー111は、樹脂基板層61の表面上に形成されている点で、実施形態1と異なっている。画素電極121が樹脂基板層61の表面上に形成されている点は、実施形態1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板と同様である。また、第1の微細電極71及び第2の微細電極81は、薄膜半導体41の両側を覆うように樹脂基板層61の内部に配置され、上方へと延びている。そして、第1の微細電極71は、ビアホール71aを通して樹脂基板層61の表面上にある画素電極121と接続され、第2の微細電極81は、やはりビアホール81aを通して樹脂基板層60の表面上にある導電性材料101と接続されている。

【0048】

図2(b)において、樹脂基板層61の表面上に、画素電極121と、第2のワイヤー91の周囲の一部又は全面が導電性材料101で被覆された配線用ワイヤー111が2本横方向に延在して配置され、これと直交するようにゲート・チャネル一体形成部51が縦方向に樹脂基板層61の内部に形成された状態が示されている。樹脂基板層61の表面上の2本の配線用ワイヤー111は、画素電極121を挟むように両端に配置されており、各々が互いに重ならないように配置されている。

【0049】

なお、個々の構成要素については、実施形態1と同様であるので、各々の構成要素に実施形態1の参照符号に1加えた参照符号を対応して付し、その説明を省略する。

【0050】

実施形態2に係る薄膜トランジスタ201及び薄膜トランジスタアレイ基板においても、ゲート・チャネル一体形成部51は、樹脂基板層61と別体にして独立して構成することができるので、単独で十分に加熱して加工を行うことができる。そして、樹脂基板層61を形成する際に、樹脂基板層61の内部に埋め込むようにしてゲート・チャネル一体形成部51を配置することにより、樹脂基板層61の内部に容易に薄膜トランジスタ201を形成することができる。

【0051】

また、表示素子を備えた画素を設け、これを薄膜トランジスタ201で駆動することにより、十分な加熱により優れた特性を有するフレキシブル表示素子を構成することができる。

【0052】

〔実施形態3〕

図3は、本発明の実施形態3に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【0053】

図3において、実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板は、第1のワイヤー12と、導電性材料22と、絶縁膜32と、薄膜半導体42と、樹脂基板層62と、第1の微細電極72と、第2の微細電極82と、第2のワイヤー92と、導電性材料102と、画素電極122とを有する。また、第1のワイヤー12、導電性材料22、絶縁膜32及び薄膜半導体42は、ゲート・チャネル一体形成部52を構成する。更に、第2のワイヤー92及び導電性材料102は、配線用ワイヤー112を構成する。

【0054】

ゲート・チャネル一体形成部52の構成は、実施形態1、2に係るゲート・チャネル一体形成部50、51と同様であるので、その説明を省略する。

【0055】

実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板においては、ゲート・チャネル一体形成部52が樹脂基板層62の内部に形成されており、画素電極122が樹脂基板層62の表面上に形成されている点では、実施形態2に係る薄膜トランジスタ201及び薄膜トランジスタアレイ基板と同様であるが、第2のワイヤー92の周囲の一部又は全面が導電性材料102で被覆された配線用ワイヤー112が樹脂基板層62の内部に配置されている点で、実施形態2に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板と異なっている。

【0056】

このように、ゲート・チャネル一体形成部52及び配線用ワイヤー112を樹脂基板層62の内部に配置する構成としてもよい。これにより、第1の微細電極72は上方の画素電極122にビアホール72aを通して接続され、第2の微細電極82はビアホール82aを通して下方の導電性材料112に接続される構成となる。

【0057】

実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板によれば、画素電極122のみ樹脂基板層60の表面に形成されるため、画素面積を広くとることが可能となり、画素の高精細化や、開口率や輝度の向上に有利である。

【0058】

〔実施形態4〕

図4は、本発明の実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【0059】

図4において、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板は、第1のワイヤー13と、導電性材料23と、絶縁膜33と、薄膜半導体43と、樹脂基板層63と、第1の微細電極73と、第2の微細電極83と、第2のワイヤー93と、導電性材料103と、画素電極123とを有する。また、第1のワイヤー13、導電性材料23、絶縁膜33及び薄膜半導体43は、ゲート・チャネル一体形成部53を構成する。更に、第2のワイヤー93と導電性材料103とは、配線用ワイヤー113を構成する。

【0060】

ゲート・チャネル一体形成部53の構成は、実施形態1〜3に係るゲート・チャネル一体形成部50〜52と同様であるので、その説明を省略する。

【0061】

図4において、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板は、ゲート・チャネル一体形成部53及び第2のワイヤー93が導電性材料103で被覆された配線用ワイヤー113が樹脂基板層63の内部に設けられている点で、実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板と同様であるが、配線用ワイヤー113がゲート・チャネル一体形成部53の下方ではなく上方に設けられている点で、実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板と異なっている。

【0062】

このように、配線用ワイヤー113は、ゲート・チャネル一体形成部53より上方の樹脂基板層63の内部に設けてもよい。なお、画素電極123は、実施形態1〜3と同様に、樹脂基板層63の表面上に形成される。かかる配置構成により、第1の微細電極73及び第2の微細電極83の双方ともビアホール73a、83aを通して上方に延び、第1の微細電極73は画素電極123、第2の微細電極83は導電性材料103に接続される。

【0063】

実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板においても、樹脂基板層63の表面には画素電極123しか存在しないので、画素面積を広くとることが可能となり、画素の高精細化や、開口率や輝度の向上に有利な構成となる。

【0064】

以上、実施形態1〜4に係る薄膜トランジスタ200〜203及び薄膜トランジスタアレイ基板について説明したが、実施形態1〜4の何れにおいても、絶縁膜30〜33と薄膜半導体40〜43は樹脂基板層60〜63と一体化される前に第一のワイヤー10〜13上に直接形成され、構成のみ異なるだけで全て同様の機能を持つ。

【0065】

実施形態1〜4に係る薄膜トランジスタアレイ基板の構成により、薄膜トランジスタ200〜203で駆動するあらゆる表示素子において、例えば液晶、有機EL、無機EL、電子インク、電子粉流体などを画素部で駆動することにより、フレキシブル表示素子を構成することが可能となる。その構成は対向電極を含めて既存の素子で用いられているあらゆる構成を適用することが可能である。

【0066】

なお、実施形態1〜4に係る薄膜トランジスタアレイ基板を用いてフレキシブル表示素子を構成するためには、薄膜トランジスタアレイ基板と対向するようにフレキシブルな樹脂基板を配置し、両基板の間であって、薄膜トランジスタアレイ基板の画素電極120〜123に対応する位置に各画素を形成すればよい。各画素は、上述のような表示素子を備えてよい。また、薄膜トランジスタアレイ基板の薄膜トランジスタ200〜203を駆動制御する駆動回路を更に備えることにより、フレキシブル表示装置を構成することができる。

【0067】

ワイヤー10〜13、90〜93は、細長い金属線や金属線の束、あるいは高分子材料を用いた繊維の束などを用いることができるが、その表面を導電性の高い金属や導電性高分子材料などで被膜することで導電性を得ることが可能となるため、特にワイヤー自体は導電性を示す材料を用いる必要はない。

【0068】

また、ワイヤー10〜13、90〜93の断面は円形や楕円形などいかなる形状であっても良く、特に上部に薄膜半導体40〜43を形成するためには長方形など上部が平坦な形状であることが望ましい。

【0069】

ワイヤー10〜13、90〜93の太さは、画素の精細度によって一般的には5μm〜500μm程度の範囲で自由に変えることが可能であるが、パターニングなどの加工処理を容易に行うためには10〜50μm程度の範囲であることが望ましい。また、図1〜4には示されていないが、画素面積を非常に小さくし、画素電極120〜123を樹脂基板層60の表面ではなく、上部が平坦な太いワイヤー10〜13を用いて、画素電極120〜123もワイヤー10〜13上に形成する場合には、画素のサイズに応じて500μm以上のワイヤー10〜13、90〜93を用いても良い。なお、スクリーン型の大型ディスプレイなどに応用する場合には、画素電極をワイヤー上に形成しなくても、500μm以上のワイヤーを用いることが有効である。

【0070】

ワイヤー10〜13、90〜93としては、例えばピアノ線に用いられている材料等から構成され、容易に切断されないものが望ましい。ワイヤー10〜13、90〜93の材料としては、有機・無機あるいはそのハイブリッド構造のいかなる材料を用いても構わないが、熱伸縮が起こりにくい材質を適用することが好ましい。また導電性ワイヤーを絶縁膜で被膜したものであっても良い。

【0071】

ワイヤー10〜13、90〜93上に形成される導電性材料20〜23、100〜103は、ワイヤー10〜13、90〜93の全面を覆うことにより高い導電性を確保することが可能であるが、薄膜半導体40〜43が真上に存在する部分を覆っていればよく、必ずしも全面を覆う必要は無い。導電性材料20〜23、100〜103がワイヤー10〜13、90〜93の一部のみを覆う構成の場合には、ワイヤー10〜13、90〜93の材質は、高分子材料や導電性の低い金属などを適用することが好ましい。

【0072】

例えば、ワイヤー10〜13、90〜93に高分子樹脂等の絶縁性の高い材料を用いた場合には、導電性材料20〜23、100〜103を形成することで所望の位置のみ導電性を付与することが可能となり、導電性を付与したワイヤー10〜13、90〜93の交差部による容量を低減させたり、隣接したTFT(Thin Film Transistor、薄膜トランジスタ)同士を電気的に絶縁させたりするなど、薄膜半導体40〜43の設計の自由度を高めることが可能となる。

【0073】

更に、ワイヤー材料はワイヤー10〜13、90〜93毎に異なる材料を用いても良く、形状もワイヤー10〜13、90〜93毎に異なっていても良いが、デバイスの作製プロセスにおいて熱変形などを抑制するためには、可能な限り同じ材料であることが好ましい。

【0074】

但し、上方に薄膜半導体40〜43や電極70〜73、80〜83を形成しないワイヤーに関しては、ワイヤーの交差部における容量が問題にならない場合においては、ワイヤーそのものを導電性の高い材料で構成することで、その周囲の導電性材料20〜23、100〜103を必ずしも形成する必要はない。

【0075】

ワイヤー上に形成される導電性材料20〜23、100〜103や、導電性の高い材料で構成される場合のワイヤー10〜13、90〜93の材料としては、例えば金、銀、銅、亜鉛、アルミニウム、イリジウム、カルシウム、ニッケル、ベリリウム、マグネシウム、モリブデン、ロジウム、チタン、タンタル、白金、クロム、タングステン、鉄、スズなどの金属やそれらの合金(例えばニクロム、コンスタンタン、黄銅など)や、ITO、ZnO、IGZO等の酸化物、ポリエチレンジオキシチオフェンなどの導電性高分子材料、カーボンナノチューブやフラーレン、グラフェンなど炭素で構成される材料や、これらの複合材料等が考えられるが、ここに記載された材料に限定されるものではなく、種々の材料を適用することが可能である。

【0076】

ワイヤー10〜13上に形成される絶縁膜30〜33は、ディッピングやスプレーコーティング、バーコーティング、ダイコーティング、フレキソ印刷、インクジェット、スパッタ、CVD、真空蒸着、スピンコート法など、あらゆる塗布技術や印刷手法、成膜技術を用いて形成することが可能であるが、ワイヤー10〜13上に被膜された導電性材料20〜23が金属の場合、その金属の陽極酸化により形成することもできる。また必要に応じて絶縁膜30〜33の形成過程で加熱処理をしても良い。

【0077】

絶縁膜30〜33の材料としては、例えば、SiO2、SiN、Ta2O5、Al2O3などの無機材料を用いることが可能である。有機材料としては、光照射をはじめ、熱硬化または反応硬化により形成される、メタクリル樹脂、アクリル樹脂、ウレタン樹脂、ポリ塩化ビニル、酢酸ビニル、フェノール樹脂、エポキシ樹脂、セルロース樹脂、ポリエチレン、ポリエチレンテレフタレート、ポリブチレンテレフタレート、ポリプロピレン、メラミン樹脂、ポリエステル、ポリビニルブチラール、ポリビニルカルバゾール、ポリビニールアセテート、ポリカーボネート、ポリスチレン、ポリスルホン、ポリエーテルスルホン、ポリアリレート、ポリエーテルイミド、アセチルセルロース、シリコーン樹脂、フッ素樹脂、またはこれらの共重合体や変性体などを用いることができる。また、これら以外の高分子樹脂を適用することも可能であり、絶縁性を有するあらゆる材料を適用することができる。

【0078】

絶縁膜30〜33の厚さは、材料の誘電率や絶縁性等を鑑みて自由に設定することが可能であるが、低電圧駆動を実現するためにも20〜300nm程度の範囲で制御することが好ましい。また、絶縁膜30〜33は、ワイヤー10〜13、90〜93を完全に被覆する必要はないが、少なくとも薄膜半導体40〜43及び微細電極70〜73、80〜83が形成される部分は、十分な絶縁性が確保されることが重要である。

【0079】

薄膜半導体40〜43の材料としては、シリコン半導体(poly−Siやa−Siなど)やGaAs、酸化物半導体(InGaZnO、ZnO、GaZnO、ZnO、InO)などの無機半導体材料や、ペンタセンやアントラセンなどの有機半導体など、あらゆる半導体材料を用いることができ、その形成過程において高温での加熱処理を行っても良い。

例えば、InGaZnOを用いた場合には、高い移動度やOn−Off比を確保するためには、300℃程度の熱アニールを行うことが望ましいが、樹脂基板60〜63と一体化する前に熱アニールを行うことで、樹脂基板60〜63の変形を防止することが可能となる。また半導体を加熱する際に、簡易な手法としてはヒーターやオーブンなどで加熱する方法が挙げられるが、紫外線やエキシマレーザーなどを照射する手法など、あらゆる加熱手法を適用することが可能である。

【0080】

なお、耐熱性の低いプラスティック基板を用いた場合は熱伸縮の影響が大きく、絶縁膜30〜33や薄膜半導体40〜43を形成する際に、プラスティック材料によっては100℃以下の加熱でも金属配線のパターンずれが発生し易い。樹脂基板60〜63をガラスに張り付けて加熱する方法を用いても、120℃程度まで加熱するとパターニング不良が生じることもある。それに対して本手法では、樹脂基板60〜63と一体化する前にワイヤー10〜13、90〜93を直接加熱することができるため、樹脂基板層60〜63への直接的なダメージを防ぐことが可能となる。即ち120℃以上の加熱処理を施すことができる。

【0081】

有機半導体材料の成膜方法としては、真空蒸着法やスピンコート法が代表的な手法として挙げられるが、他にもダイコーティング、バーコーティング、シルクスクリーン印刷、樹脂凸版印刷、フレキソ印刷、グラビア印刷、オフセット印刷、インクジェット法などを含む印刷技術など、あらゆる塗布・製膜技術を用いて形成することが可能である。

【0082】

また無機半導体の成膜方法としては、スパッタ法、CVD法、真空蒸着法などが代表的であるが、塗布形成が可能な材料を用いる場合には、ディッピングやスプレーコーティング、バーコーティング、ダイコーティング、フレキソ印刷、インクジェット、スピンコート法など、あらゆる塗布技術や印刷技術、成膜技術を用いて形成することが可能である。

【0083】

薄膜半導体40〜43上に形成される微細電極(ソース・ドレイン電極)80〜83は、必ずしも樹脂材料と一体化する前に形成する必要はないが、予め部分的に形成しておくことも可能となる。

【0084】

また実施形態1〜4において、薄膜半導体40〜43が形成されたワイヤー10〜13と、垂直方向に配列された配線ワイヤー110〜113は、微細電極70〜73、80〜83によって接続されているが、薄膜半導体40〜43上に接触させる構成とすることもできる。その際、金属を介し接触抵抗の大きさを制御したり、導電性の高分子材料を用いて熱圧着したりすることもできる。

【0085】

なお、微細電極70〜73、80〜83によりゲート・チャネル一体形成部50〜53、配線用ワイヤー110〜113や画素電極120〜123と接続する際には、樹脂基板層60〜63上でパターニングすることが必要となるが、レジストの硬化温度程度の加熱処理に留まり、かつパターニング回数も大幅に低減できるため、プラスティック基板上に積層・パターニングで形成する従来技術に比べてアライメントずれによるパターン不良を抑制することができる。

【0086】

また、第二のワイヤー90〜93の代わりに金属や有機導電性高分子などを樹脂基板層60上にパターン形成するデバイス構成とする場合についても、従来法に比べて絶縁膜30〜33や薄膜半導体40〜43を予め形成しておくため、プラスティック基板上でのパターニングの回数が大幅に低減され、かつ半導体や絶縁膜の高温処理を必要としないことから、アライメントずれによるパターン不良を大幅に抑制できる。

【0087】

樹脂基板層60〜63の材料としては、光照射をはじめ、熱硬化または反応硬化により形成される、メタクリル樹脂、アクリル樹脂、ウレタン樹脂、ポリ塩化ビニル、酢酸ビニル、フェノール樹脂、エポキシ樹脂、セルロース樹脂、ポリエチレン、ポリエチレンテレフタレート、ポリブチレンテレフタレート、ポリプロピレン、メラミン樹脂、ポリエステル、ポリビニルブチラール、ポリビニルカルバゾール、ポリビニールアセテート、ポリカーボネート、ポリスチレン、ポリスルホン、ポリエーテルスルホン、ポリアリレート、ポリエーテルイミド、アセチルセルロース、シリコーン樹脂、フッ素樹脂、またはこれらの共重合体や変性体などが挙げられるが、これらの材料に限られるものではない。

【0088】

次に、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板について、ゲート・チャネル一体形成部53を樹脂基板層63と一体化形成する手法について説明する。なお、以下、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイを例に挙げて説明するが、かかる手法は、実施形態1〜4に共通して用いることができる。

【0089】

図5は、ゲート・チャネル一体形成部53を樹脂基板層63内に配置するための一方式を示したものである。

【0090】

図5(a)は、複数のゲート・チャネル一体形成部53を平行に配列し、両端を固定治具140により固定した状態を示した図である。なお、図5(a)においては省略されているが、ゲート・チャネル一体形成部53及び固定治具140は、流動体を保持できる容器内に設置されている。このとき、ワイヤー53には、適度に張力をかけておくことが望ましい。

【0091】

図5(b)は、樹脂材料63aを流し込んだ状態を示した図である。図5(b)に示すように、ゲート・チャネル一体形成部53を平行に配列した状態で樹脂材料63aを流し込んで供給し、ゲート・チャネル一体形成部53を樹脂材料63aに浸漬させる。なお、樹脂材料63aは、硬化前は液体等の流動体状であり、加熱や紫外線の照射で硬化する性質を有する樹脂材料63aを用いる。

【0092】

樹脂材料63aを供給する際、樹脂基板60の厚みを制御するため、ゲート・チャネル一体形成部53の列を密閉容器に入れた状態で樹脂材料63aを流し込むことが望ましい。その際、密閉容器を真空にすることにより、樹脂内部への気泡の混入を抑制することが可能となる。

【0093】

図5(c)は、樹脂基板層63を形成した状態を示した図である。図5(c)に示すように、供給された樹脂材料63aを加熱や紫外線照射等で硬化し、樹脂基板層63を形成する。樹脂基板層63の形成により、ゲート・チャネル一体形成部53が樹脂基板層63内に埋め込まれた状態となる。

【0094】

なお、図5においては、ゲート・チャネル一体形成部53の列の上から樹脂を流し込む一例を示したが、例えば、ゲート・チャネル一体形成部53の列を金型の中に入れ、樹脂材料63aを注入する方法を用いても良い。金型としては、樹脂材料63aの注入口を設けた箱状の容器など、一般的に用いられているあらゆる手法を適用することができる。

【0095】

樹脂材料63aを流し込む際に、例えばダイコーティングやバーコーティング、スクリーン印刷、グラビア印刷、オフセット印刷、樹脂凸版印刷、インクジェット法、フレキソ印刷法、スピンコート法などを用いて膜厚を制御する手法を用いることができるが、これらに限定されるものではなく、あらゆるコーティング技術を適用することができる。また樹脂材料を流し込んだ後、スピンコートにより膜厚を制御する手法を用いることも可能である。

【0096】

樹脂材料63aを硬化させる手法としては、熱硬化法、紫外線や可視光を用いた光硬化法、反応硬化法などを用いることができるが、樹脂材料63aに応じて最適な方法を用いることが重要である。

【0097】

例えば、紫外線硬化性樹脂を用いた場合には、容器内で形成する際にもガラスや石英など紫外線を透過する容器を用いる必要がある。また熱硬化を行う際には、ヒーターを容器として用いたり、熱伝導性の良い容器を適用したりすることにより、的確に樹脂材料63aを硬化させることができる。

【0098】

図6は、樹脂基板層63の上部にゲート・チャネル一体形成部53を配置するための一方式を示した図である。

【0099】

図6(a)は、ゲート・チャネル一体形成部53を樹脂材料63a上に配置する状態を示した図である。図6(a)に示すように、両端を固定治具140で固定されたゲート・チャネル一体形成部53を、硬化前あるいは完全には硬化していない樹脂材料63aの上部に配置する。樹脂材料63aは、ある程度の硬度を有する完全には硬化していない状態であれば、そのままゲート・チャネル一体形成部53を上に載置することができる。

【0100】

図6(b)は、樹脂材料63aを完全に硬化させた状態を示した図である。図6(b)に示すように、樹脂材料63aを硬化させて樹脂基板層63を形成することにより、樹脂基板層63とゲート・チャネル一体形成部53を一体化する。このとき、上部にローラーなどを用いて適度に圧力をかける手法、あるいは固定治具140に圧力をかける手法により、ゲート・チャネル一体形成部53の一部分を基板内に押し込むことが可能となる。なお、ゲート・チャネル一体形成部53にさらに強い圧力をかけると、ゲート・チャネル一体形成部53を基板層内に埋め込むことも可能となる。

【0101】

また、図6は、完全に硬化していない樹脂材料63aの上部に配置する手法を示したものであるが、別の手法としては、柔軟な基板上に薄い樹脂を塗布し、図6の手法と同様に樹脂を硬化させることで、ゲート・チャネル一体形成部53と一体化させることも可能である。

【0102】

また、図6に示した基板上部に設置する手法で一体化した後、さらに樹脂材料63aを上部に塗布して硬化させることで、ゲート・チャネル一体形成部53を樹脂基板層60に埋め込むことが可能となる。このとき、埋め込むための二層目の樹脂材料63aは、必ずしも一層目の樹脂材料63aと同じ材料を用いる必要はない。また、二層目を形成する際には、図5を用いて説明した一層目の形成に用いられる全ての手法を適用することができる。

【0103】

なお、上述の例では、樹脂材料63aを一層目と二層目で二種類適用する手法を説明したが、各層に必要に応じて複数の樹脂材料63aを積層しても良い。また各樹脂層63aの間にバリア性を高める効果などを付加するため、SiO2やSiNなどの無機膜を積層することも可能である。この場合、ゲート・チャネル一体形成部53を配置する部分の樹脂材料63aのみが完全に硬化していなければ一体化できるため、下の層の樹脂材料63aは完全に硬化していても構わない。但し、上部の樹脂材料63aを硬化させる際に熱などにより伸縮がなるべく生じないように、樹脂材料63aを的確に選択することが重要である。

【0104】

互いに垂直なゲート・チャネル一体形成部53とワイヤー93を上下に配置するためには、図5と図6で説明した一段のゲート・チャネル一体形成部53を配置する手法の全ての組み合わせを適用することで実現されるが、最も簡便な方法としては、ゲート・チャネル一体形成部53とワイヤー93の列を所望の距離で上下に配置し、樹脂を流し込むことにより形成する手法が挙げられる。このとき、上下の高さを制御するため、図5と図6で示した固定冶具140を用いてゲート・チャネル一体形成部53及びワイヤー93には適度に張力をかけておくことが望ましい。なお、固定冶具140は上段のワイヤー93と下段のゲート・チャネル一体形成部53で個別に用いても良いが、上下の厚みを的確に制御するためには一つの固定冶具で固定することが望ましい。

【0105】

また、完全に硬化してない樹脂材料63aの内部に上段のワイヤー93と下段のゲート・チャネル一体形成部53を押し込んだあと、樹脂材料63aを硬化させて一体化する手法を用いることができる。この場合も、固定冶具140は上段と下段で個別に用いても、一つの固定冶具で固定するどちらの手法を用いても良い。

【0106】

その他、二段階に埋め込む手法も効果的である。本手法では、まず下段のゲート・チャネル一体形成部53を図5又は図6で説明した何れかの方法にて樹脂基板層63内に埋め込む。次に、上段の配線用ワイヤー113を樹脂基板層63の上部に設置し、必要に応じてその前後にフォトリソグラフィー法などによりビアホール73a、83aを形成し、薄膜半導体43と配線用ワイヤー113を微細配線83により接続する。更に、図5で説明した手法により、上段の配線用ワイヤー113を樹脂基板層63内に埋め込むことにより、上下段のワイヤー93及びゲート・チャネル一体形成部53を樹脂基板層63と一体化させる。

【0107】

なお、下段のみ埋め込みを行い、上段を樹脂基板63上に設置する場合においても、図5と図6で説明した手法を組み合わせることにより一体化することができる。その際、各工程の途中で必要に応じてフォトリソグラフィー法などによりビアホール73a、83aの形成や微細配線による接続を行っても良い。

【0108】

このように、ゲート・チャネル一体形成部53及び配線用ワイヤー113の樹脂基板層60の内部への設置は、種々の方法により行うことができる。なお、図5及び図6においては、実施形態4の例を挙げて説明しているが、実施形態1〜3にも同様に適用することができる。

【0109】

図7は、補助ワイヤーを用いたゲート・チャネル一体形成部53の設置方法を説明するための図である。図7において、ゲート・チャネル一体形成部53に直交して、補助ワイヤー130が設置され、ゲート・チャネル一体形成部53及び補助ワイヤー130の両端部が、固定治具141により固定されている。

【0110】

補助ワイヤー130は、非導電性の材料から構成されるワイヤーである。図7に示すように、ゲート・チャネル一体形成部53を固定する際に、非導電性の補助ワイヤー130をゲート・チャネル一体形成部53と垂直方向に設置して固定冶具141により固定すると、埋め込む際に張力の不均一性によるワイヤー13の面内の歪みなどの影響を低減できるため、より高精度で一体化させることが可能となる。

【0111】

ここで、補助ワイヤー130は一段である必要はなく、例えば、ゲート・チャネル一体形成部53の上下に設置しても、ゲート・チャネル一体形成部53に織り込む形で上下を通しても良い。また、必ずしもゲート・チャネル一体形成部53と垂直方向に設置しなくても良い。

【0112】

なお、図7においては、ゲート・チャネル一体形成部53に補助ワイヤー130を用いた例を挙げて説明したが、配線用ワイヤー113にも同様に適用することができる。更に、実施形態1〜3のゲート・チャネル一体形成部50〜52、配線用ワイヤー110〜112にも同様に適用することができる。

【0113】

画素電極120〜123は、ゲート・チャネル一体形成部50〜53を樹脂基板層60〜63と一体化した後の工程で樹脂基板層60〜63上にパターン形成される。パターニング方法としては、フォトリソグラフィー法を用いたエッチングやリフトオフなどが一般的であるが、塗布形成が可能な電極材料を用いた場合には、インクジェットを含む印刷技術などを用いて直接パターニングすることも可能である。

【0114】

また、画素電極120〜123は、ゲート・チャネル一体形成部50〜53を樹脂基板層60〜63と一体化する前の工程で、ゲート・チャネル一体形成部50〜53上の薄膜半導体40〜43とは別の領域に直接形成することも可能である。また、画素電極120〜123のみをゲート・チャネル一体形成部50〜53上に予め形成しておいて、図5〜7と同様の方法で、樹脂基板層60〜63の上部や内部に設置することも可能である。両手法とも、パターニングプロセスを削減するために有効である。

【0115】

ここで、画素電極120〜123をゲート・チャネル一体形成部50〜53とともに樹脂基板層60〜63の内部に埋め込んだ場合、その上部にドライエッチングなどで開口部を形成することで樹脂基板層60〜63の表面に容易に露出させることができる。

【0116】

また、薄膜半導体40〜43とゲート・チャネル一体形成部50〜53上の微細電極70〜73、80〜83や透明電極との接続、透明電極の形成時には、フォトリソグラフィー法を用いたエッチングなどによるビアホールの形成やパターニング工程が必要となるため、加熱に伴う樹脂基板層60〜63の伸縮が生じる可能性があるが、固定冶具140、141で十分な張力をかけて配線パターンを高精度で維持させることが可能となる。

【0117】

次に、図8〜11を用いて、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法について説明する。

【0118】

図8は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1段階の一連の工程を示した図である。なお、各構成要素には、実施形態4と同様の参照符号を付し、その説明を省略する。

【0119】

図8(a)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の樹脂材料供給工程の一例を示した図である。樹脂材料供給工程においては、ワイヤー13の周囲に導電性材料23、絶縁膜33及び薄膜半導体43が形成されて構成されたゲート・チャネル一体形成部53が樹脂成形用容器150内に配置され、ディスペンサー160を用いて樹脂材料63aが樹脂形成容器150内に流し込まれて供給される。なお、樹脂材料63aの供給量は、ゲート・チャネル一体形成部53を樹脂材料63a中に浸漬できる程度に供給する。

【0120】

図8(b)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層形成工程の一例を示した図である。第1樹脂基板層形成工程においては、樹脂材料63aが硬化され、樹脂基板層63の第1層目である第1樹脂基板層63bが形成される。

【0121】

図8(c)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層取り出し工程の一例を示した図である。第1樹脂基板層取り出し工程においては、樹脂成形用容器150内に形成された第1樹脂基板層63bが取り出される。

【0122】

図8(d)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層ビアホール形成工程の一例を示した図である。第1樹脂基板層ビアホール形成工程においては、第1樹脂基板層63bの表面上にフォトレジスト170が形成され、開口部171から第1樹脂基板層63bをエッチングし、ビアホール83aを形成する。

【0123】

図9は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2段階の一連の工程を示した図である。

【0124】

図9(a)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法のレジスト除去工程の一例を示した図である。レジスト除去工程においては、第1樹脂基板層63bの表面からレジスト170が除去される。第1樹脂基板層63bの表面には、ゲート・チャネル一体形成部53の薄膜半導体43まで到達するビアホール83aが形成されている。

【0125】

図9(b)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の配線用ワイヤー設置工程の一例を示した図である。配線用ワイヤー設置工程においては、ワイヤー93の周囲に導電性材料103が被覆された配線用ワイヤー113が第1樹脂基板層63bの表面上に設置される。

【0126】

図9(c)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の微細電極形成工程の一例を示した図である。微細電極形成工程においては、ソース電極又はドレイン電極となる微細電極83が、ビアホール83aに導電性材料が充填されることにより形成される。これにより、薄膜半導体43の一端と配線用ワイヤー113が接続される。

【0127】

図9(d)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層用樹脂材料供給の一例を示した図である。第2樹脂基板層用樹脂材料供給工程においては、第1樹脂基板層63bを再び樹脂成形用容器150内に配置し、ディスペンサー161を用いて樹脂材料63cを樹脂成形用容器150内に流し込み、第1樹脂基板層63bの表面に樹脂材料63cを供給する。

【0128】

図10は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第3段階の一連の工程を示した図である。

【0129】

図10(a)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層形成工程の一例を示した図である。第2樹脂基板層形成工程においては、供給された樹脂材料63cが硬化され、2層目となる第2樹脂基板層63dが第1樹脂基板層63b上に形成される。

【0130】

図10(b)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層取り出し工程の一例を示した図である。第2樹脂基板層取り出し工程においては、形成された第2樹脂基板層63dが樹脂成形用容器150から取り出される。

【0131】

図10(c)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層ビアホール形成工程の一例を示した図である。第2樹脂基板層ビアホール形成工程においては、第2樹脂基板層63dの表面上にフォトレジスト172が形成され、開口部173から第2樹脂基板層63d及び第1樹脂基板層63bがエッチングされる。第2樹脂基板層63d及び第1樹脂基板層63bのエッチングされた箇所には、ビアホール73aが形成される。

【0132】

図10(d)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法のレジスト除去工程の一例を示した図である。レジスト工程においては、第2樹脂基板層63dの表面からレジスト172が除去される。第2樹脂基板層63dの表面には、薄膜半導体43の他端まで到達するビアホール73aが形成されている。

【0133】

図11は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の最終段階の一連の工程を示した図である。

【0134】

図11(a)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層微細電極形成工程の一例を示した図である。第2樹脂基板層微細電極形成工程においては、ビアホール73aに導電性材料が充填され、微細電極73が形成される。

【0135】

図11(b)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の画素電極成膜工程の一例を示した図である。画素電極成膜工程においては、画素電極123となる導電膜123aが第2樹脂基板層63dの表面に成膜される。成膜方法は、CVD法、蒸着法、スパッタ法等、種々の成膜方法を用いることができる。

【0136】

図11(c)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の画素電極パターニング工程の一例を示した図である。画素電極パターニング工程においては、導電膜123a上にフォトレジスト174が形成され、開口部175からエッチングが行われ、導電膜123aがパターニングされて分割され、画素電極123が形成される。

【0137】

図11(d)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法のレジスト除去工程の一例を示した図である。レジスト除去工程においては、画素電極123の表面からフォトレジスト174が除去される。画素電極123は、各画素及び薄膜トランジスタ203に対応して形成されている。

【0138】

図8〜11で説明した一連のプロセスにおいて、ソース電極又はドレイン電極としての機能を持つ微細電極73、83のパターニングはフォトレジストを用いてウェットエッチング、もしくはドライエッチングなどにより行うことができる。なお、樹脂材料63a、63cを硬化させる手法としては、熱硬化、光硬化、反応硬化など、樹脂材料63a、63cの材料に応じて適切に行うことが可能である。

【0139】

次に、図12及び図13を用いて、図8(c)、(d)及び図9(a)〜(c)で示した工程の上面の状態を説明する。

【0140】

図12は、図8(c)、(d)及び図9(a)、(b)の工程を上面から透過的に示した平面図である。図12(a)は、図8(c)で示した第1樹脂基板層取り出し工程の平面図である。図12(a)において、第1樹脂基板層63bの内部にゲート・チャネル一体形成部53が埋め込まれて設置された状態が示されている。ワイヤー13、導電性材料23及び絶縁膜33は、第1樹脂基板層63bの内部を縦方向に貫通し、薄膜半導体43は、絶縁膜33上の一部の領域に島状に形成されている。

【0141】

図12(b)は、図8(d)及び図9(a)で示した第1樹脂基板層ビアホール形成工程〜レジスト除去工程の平面図である。図12(b)において、第1樹脂基板層63aに、ビアホール83aが形成された状態が示されている。ビアホール83aは、導電性材料を充填したときに薄膜半導体43と接続可能なように、薄膜半導体43と重なり領域43aを有するように形成される。

【0142】

図12(c)は、図9(b)で示した配線用ワイヤー設置工程の平面図である。図12(c)において、第1樹脂基板層63aの表面上に、配線用ワイヤー113が設置された状態が示されている。

【0143】

図13は、図9(c)の工程を上面から示した平面図である。図13(a)は、図9(c)で示した微細電極形成工程の前半の導電膜形成工程を示した平面図である。図13(a)において、第1樹脂基板層63bの表面全体に導電膜83bが成膜された状態が示されている。このように、微細電極83の形成時には、最初は第1樹脂基板層63bの表面全体に導電膜83bが形成される。導電膜83bの形成時に、ビアホール83aが導電膜83bで充填され、微細電極83のビア配線部分が形成される。

【0144】

図13(b)は、図9(c)で示した微細電極形成工程の後半の導電膜形成工程を示した平面図である。図13(b)において、導電膜83bがパターニングされ、ビアホール83aの上部を覆うとともに、配線用ワイヤー113に到達するように延在して形成された微細電極83が示されている。これにより、微細電極83が配線用ワイヤー113に電気的に接続される。このように、的確にパターニングすることにより、微細電極83と配線用ワイヤー113との接続を行うことができる。なお、ここではビアホール83aを形成後に配線用ワイヤー113を設置しているが、必要に応じてビアホール83a形成前に配線用ワイヤー113を設置することもできる。なお、図9(b)及び図9(c)においては、図13(a)の工程が省略されて示されているが、実際には、図13(a)の工程を経て微細電極83が形成される。

【0145】

このように、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法によれば、一般に高温の加熱プロセスを伴う絶縁膜33、薄膜半導体43の形成工程は、ゲート・チャネル一体形成部53を先に独立して作製することにより、十分な加熱温度で加熱プロセスを行うことができ、その後は比較的低温のプロセスで樹脂基板層63の内部にゲート・チャネル一体形成部53を組み込むことができる。更に基板上でのパターニング回数を大幅に低減することができる。よって、樹脂基板層63に加熱変形等を大幅に抑制することが可能となり、良好な動作特性を有する大型の薄膜トランジスタアレイ基板を製造することができる。

【0146】

次に、図14及び図15を用いて、薄膜半導体43と配線用ワイヤー113とを接続する別の手法について説明する。

【0147】

図14は、ビアホール形成までの工程を示した図である。図14(a)は、図12(a)と同様の第1樹脂基板層取り出し工程の平面図である。図14(a)において、第1樹脂基板層63bの内部を貫いて、ゲート・チャネル一体形成部53が設置されている。薄膜半導体43は、絶縁膜33の一部に島状に形成されている。

【0148】

図14(b)は、ビアホール形成工程の平面図及び断面図である。図14(b)の左側の平面図及び右側の断面図において、第1樹脂基板層63aにビアホール83aが形成された状態が示されている。図14(b)の平面図及び断面図に示されるように、ビアホール83aは、平面的には薄膜半導体43と重なり領域43aを有し、深さ的には薄膜半導体43に到達する深さに形成される。なお、ビアホール83aは、フォトレジスト等を用いて形成される。

【0149】

図15は、微細電極と配線用ワイヤーを接続する一連の工程を示した平面図である。図15(a)は、導電膜形成工程を示した図である。導電膜形成工程においては、第1樹脂基板層63bの表面全体を覆うように、導電膜83bが形成される。このとき、ビアホール83aは、導電膜83bにより充填され、ビア配線が形成される。

【0150】

図15(b)は、微細電極形成工程の平面図及び断面図である。微細電極形成工程においては、図15(b)の平面図に示されるように、導電膜83bがフォトレジスト等を用いてパターニングされ、ビアホール83aよりも少し大きい領域を覆うように微細電極83が形成される。

【0151】

図15(c)は、配線用ワイヤー設置工程を示した平面図及び断面図である。配線用ワイヤー設置工程においては、微細電極83の表面上に配線用ワイヤー113が設置される。微細電極の上面に配線用ワイヤー113が接触することで、両者が接続される。

【0152】

ここで、配線用ワイヤー113の導電性材料103と微細電極83との接続を的確に行うために、微細電極83の上面または導電性材料103の表面に、導電性樹脂又は導電性微粒子を含んだ樹脂を塗布し、加熱や光硬化などで接着する手法を用いても良い。更に、導電性材料103や微細電極83の材料自体に、上述の特性を有する材料を適用することもできる。また、パターニング後の微細電極83と配線用ワイヤー113が十分に接触していれば、第2樹脂基板層63d(二層目)を形成する際に導電性を保持したまま両者を十分に固定することができる。

【0153】

このように、微細電極83と配線用ワイヤー113の接続が担保されれば、配線用ワイヤー113は種々の位置に配置することができ、また、それに応じて、微細電極83と配線用ワイヤー113の接続も種々の方法により行うことができる。

【0154】

なお、図12〜15においては、実施形態4の微細電極83と配線用ワイヤー113との接続を例に挙げて説明したが、微細電極73にも同様の方法を適用でき、また、他の実施形態1〜4の微細電極70〜72、80〜82と配線用ワイヤー110〜112との接続にも適用することができる。

【0155】

〔実施形態5〕

図16は、本発明の実施形態5に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。実施形態1〜4においては、1画素を1個のトランジスタで駆動する例を示し、例えば既存の液晶を用いた表示素子などに適用することが可能である。しかしながら、有機ELなどでは、基本的に選択用トランジスタと駆動用トランジスタが必要となり、複数個の薄膜トランジスタで駆動する必要がある。実施形態5においては、2個の薄膜トランジスタを各画素に対応させて設けた例について説明する。

【0156】

図16において、実施形態5に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板は、選択用薄膜トランジスタ204と、駆動用薄膜トランジスタ205とを備える。選択用薄膜トランジスタ204は、画素選択用の薄膜トランジスタであり、駆動用薄膜トランジスタ205は、画素駆動用の薄膜トランジスタである。

【0157】

選択用薄膜トランジスタ204は、ワイヤー14と、ワイヤー14の全面もしくは一部を被膜する導電性材料24と、導電性材料24の周囲を被膜する絶縁膜34と、絶縁膜34の上にパターニングされた薄膜半導体44と、薄膜半導体44の上部に形成された第1の微細電極74及び第2の微細電極84とを有する。ここで、ワイヤー14、導電性材料24、絶縁膜34及び薄膜半導体44から構成されるゲート・チャネル一体形成部53は、内部に薄膜半導体44と垂直方向に配線用ワイヤー115が配置された樹脂基板層64の上部に設置され、かつ一体化されている。

【0158】

また、選択用薄膜トランジスタ204には、配線用ワイヤー114が接続されており、配線用ワイヤー114は、ワイヤー94の周囲を導電性材料104が被覆して構成されている。更に、薄膜トランジスタアレイ基板は、画素電極124を備えている。かかる構成は、基本的に1個の薄膜トランジスタで駆動する実施形態1〜4に係る薄膜トランジスタアレイ基板と同様である。

【0159】

一方、駆動用薄膜トランジスタ205は、ワイヤー15と、導電性材料25と、絶縁膜35と、薄膜半導体45と、第1の微細電極75と、第2の微細電極85とを備える。ここで、ワイヤー15、導電性材料25、絶縁膜35及び薄膜半導体45は、ゲート・チャネル一体形成部55を構成する。

【0160】

また、駆動用薄膜トランジスタ205の第2の微細電極85は、ワイヤー95の周囲が導電性材料106で被覆された配線用ワイヤー115に接続されている。更に、第1の微細電極75は、画素電極124に接続されており、薄膜トランジスタアレイ基板を構成している。

【0161】

ここで、駆動用薄膜トランジスタ205は、備える構成要素自体は第1の薄膜トランジスタ204と同様であるが、ワイヤー15の全周が導電性材料25に被覆されているのではなく、ワイヤー15の表面上の一部の領域に導電性材料25が島状に形成され、ワイヤー15の一部を覆っているに過ぎない点で、選択用薄膜トランジスタ204と異なっている。また、島状の導電性材料25の構成に伴い、絶縁膜35も導電性材料25を覆うように島状に設けられ、薄膜半導体45も、絶縁膜35の上に島状に形成されている点で、選択用薄膜トランジスタ204と異なっている。なお、図16においては、導電性材料25をワイヤー15の上面の一部に形成する構成としたことに伴い、ワイヤー15の上面の面積がワイヤー14よりも数倍広い幅に構成されているが、TFTの特性に応じて自由に設定することが可能である。

【0162】

このように、本実施形態に係る駆動用薄膜トランジスタ205は、ワイヤー15の全周を導電性材料25及び絶縁膜35で覆うではなく、ワイヤー15の一部を導電性材料25及び絶縁材料35で覆い、絶縁膜35上に薄膜半導体45を形成するように構成してもよい。この場合であっても、導電性材料25からなるゲートをゲート酸化膜である絶縁膜35が絶縁し、絶縁膜35上に配置された薄膜半導体45がチャネルとして機能する、というトランジスタの基本的構成を有しているので、薄膜トランジスタ205はトランジスタ機能を果たすことができる。

【0163】

画素選択用トランジスタと、画素駆動用トランジスタの2個のトランジスタを備えた画素回路においては、画素選択用トランジスタの出力端子が、画素駆動用トランジスタのゲートに接続される構成をとる必要がある。よって、画素駆動用トランジスタのゲートは、外部から接続可能なように、総てが被覆されていないことが好ましい。よって、実施形態5に係る駆動用薄膜トランジスタ205においては、ゲートとして機能する導電性材料25の周囲総てを被覆しない構成とするため、十分な面積を有するワイヤー15の表面に、ワイヤー15の一部を覆うよう島状の形状とし、やはり島状の絶縁膜35から容易に露出可能な構成としている。これにより、選択用薄膜トランジスタ204の第1の微細電極74と導電性材料25との接続を容易にし、薄膜トランジスタアレイ基板の全体の構成を簡素化することができる。

【0164】

なお、駆動用薄膜トランジスタ205においても、ゲート・チャネル一体形成部55は独立して加熱プロセスを経て形成される。つまり、導電性材料25、絶縁膜35及び薄膜半導体45は、フレキシブルな樹脂基板層64と一体化される作製プロセスの前に、ワイヤー15の上部に予め形成される。これらの各層の形成方法は、真空蒸着法やCVD法、スパッタ法、各種コーティング技術等により成膜した後、フォトリソグラフィー法によりパターニングする手法が一般的であるが、印刷技術などを用いて直接パターニングを行っても良い。

【0165】

また、実施形態5に係る薄膜トランジスタ204、205及び薄膜トランジスタアレイ基板は、図1に示した実施形態1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板に対応しており、薄膜半導体44、45を形成したワイヤー14、15が樹脂基板層64の上部に設置され、かつ配線用ワイヤー114、115を樹脂基板層64の内部に形成した方式であるが、図2〜4に示した実施形態2〜4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板と対応させて、各々のワイヤーを上下のどの位置に設置しても、基本的に同じ効果を得ることができる。

【0166】

なお、ワイヤー14、15の太さは画素の精細度によって一般的には5μm〜500μm程度の範囲で自由に変えることが可能であるが、パターニングなどの加工処理を容易に行うためには10〜50μm程度の範囲であることが望ましい。また画素電極124もワイヤー74上に形成する場合、画素のサイズに応じて500μm以上のワイヤーを用いても良い。なお、大型のスクリーン型ディスプレイなどに応用する場合、ワイヤーに画素電極を形成しない場合においても500μm以上のワイヤーを用いることが有効である。

【0167】

また、実施形態1〜4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板においては、2本のワイヤー10〜13、90〜93を上下の2段に配置したが、本実施形態に係る薄膜トランジスタ204、205及び薄膜トランジスタアレイ基板においては、ワイヤー14、15、114、115の種類に応じて何段に設置しても良く、その組み合わせは自由に設定することが可能である。またゲート・チャネル一体形成部54、55及び配線用ワイヤー114、115を樹脂基板層64と一体化する手法に関しては、図5〜図7で説明したあらゆる手法を適用することが可能である。

【0168】

図16においては、ワイヤー15上に薄膜半導体45のみ形成してあるが、画素電極124も薄膜半導体45とは別の部分に予め形成しておけば、画素のパターニングによる樹脂基板層64の変形などを抑制することができる。

【0169】

また、同じワイヤー14、15上に形成される薄膜半導体44、45は1画素につき1個である必要はなく、複数の種類かつ異なる形状の薄膜半導体44、45により画素を駆動することが可能である。例えば、ワイヤー上の絶縁膜上に選択用トランジスタの機能を有する薄膜半導体が形成され、さらに別の範囲の絶縁膜上に電極と絶縁膜を積層し、その上部に駆動用トランジスタの機能を示す薄膜半導体が形成されても良い。

【0170】

実施形態5に係る薄膜トランジスタ204、205及び薄膜トランジスタアレイ基板によれば、1画素に対応して画素選択用トランジスタと画素駆動用トランジスタの2個の薄膜トランジスタ204、205を設けることができ、有機EL等の画素駆動に2個のトランジスタを必要とするフレキシブル表示素子に適用することができる。

【0171】

〔実施形態6〕

図17は、本発明の実施形態6に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。実施形態6においては、1つのワイヤー上に2個の薄膜トランジスタを形成した例を示す。

【0172】

図17において、実施形態6に係る薄膜トランジスタ206、207及び薄膜トランジスタアレイ基板は、選択用薄膜トランジスタ206と、駆動用薄膜トランジスタ207とを有する。

【0173】

選択用薄膜トランジスタ206は、ワイヤー16と、導電性材料26と、絶縁膜36と、薄膜半導体46と、第1の微細電極76と、第2の微細電極86とを備える。ここで、ワイヤー16、導電性材料26、絶縁膜36及び薄膜半導体46は、ゲート・チャネル一体形成部56を構成する。

【0174】

駆動用薄膜トランジスタ207は、ワイヤー16と、導電性材料27と、絶縁膜37と、薄膜半導体47と、第1の微細電極77と、第2の微細電極87とを備える。ここで、ワイヤー16、導電性材料27、絶縁膜37及び薄膜半導体47は、ゲート・チャネル一体形成部57を構成する。

【0175】

また、選択用薄膜トランジスタ206の第2の微細電極86は配線用ワイヤー116に接続され、第1の微細電極76は駆動用薄膜トランジスタ207の導電性材料27に接続されている。ここで、配線用ワイヤー116は、ワイヤー96の周囲に導電性材料106が被覆されて構成されている。

【0176】

同様に、駆動用薄膜トランジスタ207の第2の微細電極87は配線用ワイヤー117に接続され、第1の微細電極77は画素電極126に接続されている。なお、配線用ワイヤー117は、ワイヤー97の周囲に導電性材料107が被覆されて構成されている。

【0177】

実施形態6に係る薄膜トランジスタ206、207及び薄膜トランジスタ基板においては、1つの幅が広い共通のワイヤー16の表面上の一部に、ライン状に形成された導電性材料26と絶縁膜36が積層され、その上に選択用トランジスタとして機能する薄膜半導体46が形成されている。また、ワイヤー16の別の領域に、島状に導電性材料27と絶縁膜37を積層し、その上に駆動用トランジスタとして機能する薄膜半導体47が形成されている。このように、1つのワイヤー16上に、2つの薄膜トランジスタ206、207を形成するようにしてもよい。非導電性の材料からなり、2つの導電性材料26、27が配置可能な十分な幅のワイヤー16を用いることにより、選択用薄膜トランジスタ206と駆動用薄膜トランジスタ207を2列に並べて配置形成することができる。

【0178】

実施形態6に係る薄膜トランジスタ206、207においては、ゲート・チャネル一体形成部56、57同士が更に一体形成された構成となる。ゲート・チャネル一体形成部56、57は、実施形態1〜5と同様に、樹脂基板層66とは別個に独立して形成可能であり、樹脂基板層66の形成後に表面上に設置することができる。よって、ゲート・チャネル一体形成部56、57は加熱プロセスで十分に加熱加工した後、樹脂基板層66と一体化することができ、樹脂基板層66の変形を防止することができる。

【0179】

なお、図17では、画素電極126は樹脂基板66上に形成された構成が示されているが、画素電極126を同じワイヤー16上に形成しても良い。

【0180】

また、実施形態1〜6に係る薄膜トランジスタ200〜207及び薄膜トランジスタアレイ基板において、ワイヤー10〜16、110〜117は1本である必要はなく、例えば複数本のワイヤーを束ねて1組のワイヤーとして扱うことができる。その際、異なる材質・形状のワイヤーを組み合わせることも可能である。

【0181】

また、上述の複数のワイヤーを束ねる方法としては、熱硬化性樹脂や光硬化性樹脂などで固める方法や、各々のワイヤーを互いに巻きつける方法などを用いることができる。熱硬化性樹脂や光硬化性樹脂で硬化させる手法を用いる場合には、樹脂の伸縮の影響を抑制するため、ワイヤーを左右から適切な力で引っ張った状態で樹脂を硬化させる手法が効果的である。

【0182】

なお、実施形態1〜6に係る薄膜トランジスタ200〜207及び薄膜トランジスタアレイ基板は、基本的な配線パターンを示したものであって、配線の方向や形状はこれらに限定されるものではなく、自由に設定して良い。また薄膜半導体40〜47上の微細電極70〜77、80〜87も同様に自由に設定して良く、例えばトランジスタのソース・ドレイン電極を櫛形状にするなどあらゆるパターンを適用することが可能である。

【0183】

上述の薄膜トランジスタアレイ基板又はバックプレーンを用いて作製するフレキシブル表示素子は、液晶、有機EL、無機EL、電子インク、電子粉流体など、種々の表示方式で従来用いられる全ての構造を導入することが可能であり、液晶ディスプレイにおいては、例えば配向膜やスペーサー、対抗電極、液晶層、バックライト、偏光板、カラーフィルター、ブラックマトリクス、絶減膜などが挙げられるが、勿論これらに限定されるものではない。

【0184】

また、本実施形態に係るフレキシブル表示素子を用いた表示装置としては、テレビ、パソコン、携帯電話、電子ペーパー、タッチパネル、各種機器に取り付けられた表示モニターなどが挙げられるが、これらに限定されるものではなく、全ての表示装置が含まれる。

【0185】

〔実施例〕

本発明の実施例として、絶縁膜と薄膜トランジスタを形成した導電性ワイヤーを樹脂基板と一体化形成した、フレキシブル表示素子のバックプレーン部分の一部を作製した結果について示す。作製方法は以下の通りである。

【0186】

まず、表面に約2.5μm厚の黄銅がメッキ処理された50μmのピアノ線から成る導電性ワイヤーをガラス板(170mm×110mm)上に配置し、ワイヤー両端をテープにより固定した。その表面に、フッ素樹脂を主成分とする溶液をディッピングし、120〜170℃で加熱してフッ素樹脂を硬化させて導電性膜の周囲に絶縁層を形成した。更に、ワイヤー上にマスクを介してスパッタ装置のホルダーに固定し、50μm厚の酸化物半導体(InGaZnO)をスパッタリング法により成膜した。その後、酸化物半導体を形成した導電性ワイヤー、及び上述の導電性ワイヤーの両端を金属棒に固定し、それらを箱型のプラスティック容器内に固定した。そこにシリコーン樹脂(PDMS)材料を流し込み、100℃以下に加熱して樹脂を硬化させた。

【0187】

以上の方法により作製した、導電性ワイヤーを埋め込んだ樹脂基板を湾曲させたところ、ワイヤーの断線無く丸められることが可能であることが確認された。

【0188】

以上説明したように、本発明の実施形態及び実施例に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板によれば、絶縁膜と薄膜トランジスタを形成した導電性ワイヤーを形成し、基板となる樹脂と一体化する工程を導入することにより、柔軟な基板を用いても配線不良の少ない大面積のフレキシブル表示素子を提供することができる。従って、本発明に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板を適用すれば、自由に丸めて持ち運べる巻物型のディスプレイや、プロジェクターが不要なスクリーン型の大型ディスプレイなど、種々の新しいディスプレイの実現が期待できる。

【0189】

以上、本発明の好ましい実施形態について詳説したが、本発明は、上述した実施形態に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施形態に種々の変形及び置換を加えることができる。

【産業上の利用可能性】

【0190】

本発明は、液晶ディスプレイ、有機ELディスプレイ等を含むフレキシブルディスプレイに利用することができ、特に、大画面のフレキシブルデシィスプレイに利用することができる。

【符号の説明】

【0191】

10〜16、90〜97 ワイヤー

20〜27、100〜107 導電性材料

30〜37 絶縁膜

40〜47 薄膜半導体

50〜57 ゲート・チャネル一体形成部

60〜67 樹脂基板

70〜77、80〜87 微細電極

110〜117 配線用ワイヤー

120〜124、126 画素電極

130 補助ワイヤー

140、141 固定治具

150 樹脂成形用容器

160、161 ディスペンサー

170、172、174 レジスト

171、173、175 開口

200〜207 薄膜トランジスタ

【技術分野】

【0001】

本発明は、薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法に関し、特に、フレキシブルな樹脂基板に形成された薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法に関する。

【背景技術】

【0002】

従来から、家庭用の大型テレビからPC、携帯電話に至るまで、LCD(Liquid Crystal Display、液晶ディスプレイ)やPDP(Plasma Display Panel、プラズマディスプレイパネル)、あるいは有機EL(Electro-Luminescence)など、フラットパネルディスプレイが広く普及している。これらのディスプレイには、従来から基板としてガラスが用いられてきたが、ディスプレイの更なる大型化や軽量化、収納性や耐衝撃性の向上などを実現するため、軽量で柔軟なプラスティック基板の適用が望まれる。更に、極めて柔軟性に優れたプラスティック基板が適用されるようになれば、自由に丸めて持ち運べる巻物型のディスプレイや、プロジェクターが不要なスクリーン型の大型ディスプレイなど、種々の新しいディスプレイの実現が可能となる。

【0003】

しかし、プラスティックフィルムなどを基板として用いる場合、耐熱性や耐薬品性がガラスに比べて大きく劣るため、作製プロセスを進める上で種々の制約が生じる。一般に、プラスティックは熱変形が大きく、従来のフォトリソグラフィー法により電極や薄膜トランジスタ、画素電極をパターニングすると、熱工程を重ねるにつれパターニング時にアライメントずれなどが発生し、歩留まりが大幅に低下する。特に、大型基板を用いる程、基板伸縮の影響が大きくなるため、大画面のフレキシブルディスプレイへの適用は極めて困難となる。また高温になるほど熱変形が増大するため、半導体や絶縁膜等に高温処理が必要な材料を適用する場合、加熱が不十分となり易く、これにより特性の劣化や不安定性を誘発する場合がある等の課題もあった。更に、プラスティック材料により薬品による劣化が生じるため、ガラス基板を用いた場合と同じ材料や作製プロセスの適用も困難である。

【0004】

このような課題に対し、ガラス基板上に従来の作製プロセスで配線パターンや薄膜トランジスタを形成し、ガラス基板を溶かしてプラスティック基板上に接着させる手法が提案されている(例えば、特許文献1参照)。また、他の手法とし、ガラス基板に剥離層を設け、その上に従来の手法でパターニングを行い、プラスティック基板に接着した後ガラス基板から剥離させる転写技術も提案されている(例えば、特許文献2〜5参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−323132号公報

【特許文献2】特開2008−159934号公報

【特許文献3】特開2008−159935号公報

【特許文献4】特開2010−10185号公報

【特許文献5】特開2010−10186号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述の特許文献1に記載の方法ではガラス基板を溶かすための薬品を必要とするため適用できるプラスティック材料が限られるだけでなく、工程が複雑になるため高い生産性が得られないという問題があった。

【0007】

また、上述の特許文献2〜5に記載の方法では、剥離させる際に電極や絶縁膜、半導体層などに強い応力が発生し、膜の剥離や配線不良、特性劣化などが発生しやすいという問題があった。

【0008】

そこで、本発明は、上記の点を鑑みてなされたもので、絶縁膜と薄膜トランジスタを形成した導電性ワイヤーを形成し、基板となる樹脂と一体化する工程を導入することにより、大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本発明の一態様に係る薄膜トランジスタは、フレキシブルな樹脂基板に形成された薄膜トランジスタであって、

周面の一部又は全部が導電性材料により覆われたワイヤーと、

前記導電性材料を覆う絶縁膜と、

該絶縁膜を介して前記導電性材料上に形成された薄膜半導体と、が一体的に構成されたゲート・チャネル一体形成部を有し、

該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極が接続されて形成されたことを特徴とする。

【0010】

また、前記ワイヤーは、非導電性材料からなる構成を有してもよい。

【0011】

また、前記ワイヤーの延在方向に沿って、複数の前記薄膜半導体が形成されてもよい。

【0012】

また、前記絶縁膜は、前記ワイヤーの全周を被覆し、前記ワイヤーの周方向においては、1個の薄膜半導体が形成されてもよい。

【0013】

本発明の他の態様に係る薄膜トランジスタアレイ基板は、フレキシブルな樹脂基板にマトリクス状に形成された画素電極と、

前記画素電極に各々対応して設けられた前記薄膜トランジスタと、を有することを特徴とする。

【0014】

本発明の他の態様に係るフレキシブル表示素子は、前記薄膜トランジスタアレイ基板と、

該薄膜トランジスタアレイ基板に対向して配置されたフレキシブルな樹脂基板と、

該樹脂基板と前記薄膜トランジスタアレイ基板との間に、前記画素電極に対応して配置された画素と、を有することを特徴とする。

【0015】

本発明の他の態様に係る薄膜トランジスタアレイ基板の製造方法は、フレキシブルな樹脂基板にマトリクス状に配置された画素電極と該画素電極に対応して設けられた薄膜トランジスタを有する薄膜トランジスタアレイ基板の製造方法であって、

周囲の一部又は全周が導電性材料により被覆されたワイヤーの周囲に絶縁膜を形成するゲート絶縁膜形成工程と、

該絶縁膜上の前記導電性材料が存在する位置を覆うように、薄膜半導体を形成してチャネルを形成するチャネル形成工程とを含み、ゲートとチャネルが一体形成されたゲート・チャネル一体形成部を作製するゲート・チャネル一体形成部作製工程と、

前記ゲート・チャネル一体形成部が樹脂基板の表面又は内部の所定位置に配置されるように、流動体状の樹脂を硬化して樹脂基板を形成する樹脂基板形成工程と、

前記薄膜半導体の両端の位置に、第1及び第2の電極を形成する電極形成工程と、を有することを特徴とする。

【0016】

また、前記樹脂形成工程は、前記ゲート・チャネル一体形成部の両端が固定されて前記所定位置に固定された状態で、前記流動体状の樹脂を硬化してもよい。

【0017】

また、前記樹脂基板形成工程は、前記ゲート・チャネル一体形成部を配置する高さまで第1樹脂基板層を形成する第1樹脂基板層形成工程と、

該樹脂基板上に前記ゲート・チャネル一体形成部を配置する位置決め工程と、

前記ゲート・チャネル一体形成部を埋めるように第2樹脂基板層を形成する第2樹脂基板層形成工程とを有し、

前記電極形成工程は、前記樹脂基板の前記薄膜半導体の両端の位置に開口を形成する開口形成工程を含み、該開口に充填するように前記第1及び第2の電極を形成してもよい。

【発明の効果】

【0018】

本発明によれば、柔軟な基板を用いても配線不良の少ない薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子及びフレキシブル表示装置を提供することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施形態1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図1(a)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図である。図1(b)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【図2】本発明の実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図2(a)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図である。図2(b)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【図3】本発明の実施形態3に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【図4】本発明の実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【図5】ゲート・チャネル一体形成部を樹脂基板層内に配置するための一方式を示したものである。図5(a)は、複数のゲート・チャネル一体形成部を平行に配列し、両端を固定治具により固定した状態を示した図である。図5(b)は、樹脂材料63aを流し込んだ状態を示した図である。図5(c)は、樹脂基板層63を形成した状態を示した図である。

【図6】樹脂基板層の上部にゲート・チャネル一体形成部を配置するための一方式を示した図である。図6(a)は、ゲート・チャネル一体形成部を樹脂材料上に配置する状態を示した図である。図6(b)は、樹脂材料63aを完全に硬化させた状態を示した図である。

【図7】補助ワイヤーを用いたゲート・チャネル一体形成部の設置方法の説明図である。

【図8】実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1段階の一連の工程を示した図である。図8(a)は、樹脂材料供給工程の一例を示した図である。図8(b)は、第1樹脂基板層形成工程の一例を示した図である。図8(c)は、第1樹脂基板層取り出し工程の一例を示した図である。図8(d)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層ビアホール形成工程の一例を示した図である。

【図9】実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2段階の一連の工程を示した図である。図9(a)は、レジスト除去工程の一例を示した図である。図9(b)は、配線用ワイヤー設置工程の一例を示した図である。図9(c)は、微細電極形成工程の一例を示した図である。図9(d)は、第2樹脂基板層用樹脂材料供給の一例を示した図である。

【図10】実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第3段階の一連の工程を示した図である。図10(a)は、第2樹脂基板層形成工程の一例を示した図である。図10(b)は、第2樹脂基板層取り出し工程の一例を示した図である。図10(c)は、第2樹脂基板層ビアホール形成工程の一例を示した図である。図10(d)は、レジスト除去工程の一例を示した図である。

【図11】実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の最終段階の一連の工程を示した図である。図11(a)は、第2樹脂基板層微細電極形成工程の一例を示した図である。図11(b)は、画素電極成膜工程の一例を示した図である。図11(c)は、画素電極パターニング工程の一例を示した図である。図11(d)は、レジスト除去工程の一例を示した図である。

【図12】図8(c)、(d)及び図9(a)、(b)の工程を上面から透過的に示した平面図である。図12(a)は、第1樹脂基板層取り出し工程の平面図である。図12(b)は、第1樹脂基板層ビアホール形成工程〜レジスト除去工程の平面図である。図12(c)は、配線用ワイヤー設置工程の平面図である。

【図13】図9(c)の工程を上面から示した平面図である。図13(a)は、微細電極形成工程の前半の導電膜形成工程を示した平面図である。図13(b)は、微細電極形成工程の後半の導電膜形成工程を示した平面図である。

【図14】ビアホール形成までの工程を示した図である。図14(a)は、図12(a)と同様の第1樹脂基板層取り出し工程の平面図である。図14(b)は、ビアホール形成工程の平面図及び断面図である。

【図15】微細電極と配線用ワイヤーを接続する一連の工程を示した平面図である。図15(a)は、導電膜形成工程を示した図である。図15(b)は、微細電極形成工程の平面図及び断面図である。図15(c)は、配線用ワイヤー設置工程を示した平面図及び断面図である。

【図16】本発明の実施形態5に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。

【図17】本発明の実施形態6に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。

【発明を実施するための形態】

【0020】

以下、図面を参照して、本発明を実施するための形態の説明を行う。

【0021】

〔実施形態1〕

図1は、本発明の実施形態1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図1(a)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図であり、図1(b)は、実施例1に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【0022】

なお、薄膜トランジスタアレイ基板は、フレキシブル表示素子の表示素子を含まない駆動側の基板を意味するので、以下の説明において、薄膜トランジスタアレイ基板のことを、フレキシブル表示素子のバックプレーンと呼んでもよいこととする。

【0023】

図1(a)、(b)において、実施例1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板は、第1のワイヤー10と、導電性材料20と、絶縁膜30と、薄膜半導体40と、樹脂基板層60と、第1の微細電極70と、第2の微細電極80と、第2のワイヤー90と、導電性材料100と、画素電極120とを備える。また、第1のワイヤー10と、導電性材料20と、絶縁膜30と、薄膜半導体40とで、ゲート・チャネル一体形成部50を構成する。また、第2のワイヤー90と導電性材料100とで配線用ワイヤー110を構成する。

【0024】

図1(a)において、第1のワイヤー10の周囲を導電性材料20が被覆しており、導電性材料20の周囲を絶縁膜30が被覆している。導電性材料20は、薄膜トランジスタ200のゲートの機能を有し、絶縁膜30はゲート絶縁膜の機能を有する。導電性材料20の直上の位置の絶縁膜30の表面上には、薄膜半導体40が形成されている。薄膜半導体40は、薄膜トランジスタ200のチャネルの機能を果たす。第1のワイヤー10、導電性材料20、絶縁膜30及び薄膜半導体40は、一体的に構成されており、樹脂基板層60の表面上に設けられている。薄膜半導体40の両側には、第1の微細電極70と第2の微細電極80が各々の側に、薄膜半導体40の両端部を覆うように形成されており、薄膜半導体40と電気的に接続されている。第1の微細電極70及び第2の微細電極80は、ソース電極又はドレイン電極の役割を果たす。第1の微細電極70の外側の樹脂基板層60の表面上には、画素電極120が形成され、第1の微細電極70は画素電極120の端部を覆うように形成されて両者は電気的に接続されている。樹脂基板層60の内部には、第2のワイヤー90が、第1のワイヤー10と直交する方向に延在して配置され、第2のワイヤー90の周囲を導電性材料100が被覆しており、配線用ワイヤー110を構成している。導電性材料100には、ビアホール80aを通して第2の微細電極80が接続されている。また、薄膜トランジスタ200は、図1(a)において2個形成されている。

【0025】

図1(b)において、樹脂基板層60の表面上で、第1のワイヤー10、導電性材料20、絶縁膜30が縦方向に延在している。薄膜半導体40は、絶縁膜30上でパターニングされて島状に2個形成されている。第1のワイヤー10、導電性材料20、絶縁膜30及び薄膜半導体40でゲート・チャネル一体形成部50が構成されるが、ゲート・チャネル一体形成部50は、2本平行に配置され、その間に画素電極120が形成されている。第1の微細電極70は、薄膜半導体40と画素電極120を接続するように横方向に形成されている。また、画素電極120、第1及び第2の微細電極70、80及び薄膜半導体40を横方向に貫くように樹脂基板層60の内部に配線用ワイヤー110が配置され、第2の微細電極80との接続が図られている(図1(a)参照)。

【0026】

実施形態1に係る薄膜トランジスタ200は、かかる構成を有するが、ゲート・チャネル一体形成部50が一体となって構成され、樹脂基板層60の所定の位置に置くように配置することができるので、位置合わせが極めて容易であり、配線形成を容易に行うことができる。

【0027】

次に、個々の構成要素の機能について説明する。

【0028】

第1のワイヤー10は、ゲート・チャネル一体形成部50の基材となる役割を果たす部材である。実施形態1に係る薄膜トランジスタ200においては、第1のワイヤー10を中心に配置し、その周囲に導電性材料20、絶縁膜30及び薄膜半導体40を形成してゲート・チャネル一体形成部50を構成するので、樹脂基板層60と別体としてゲート及びチャネルを構成することができる。樹脂基板層60は、プラスティック等の樹脂で構成され、熱に弱く、変形し易い性質を有する。一方、絶縁膜30や薄膜半導体40は、形成のために十分な加熱が必要であり、樹脂基板層60に直接形成すると、樹脂基板層60の耐熱性の問題から、十分な加熱を行うことができない。

【0029】

そこで、本実施形態においては、ゲート・チャネル一体形成部50を樹脂基板層60とは別体として構成し、十分な加熱加工が可能な構成となっている。その際、ゲートとチャネルを形成する基材が必要となるが、第1のワイヤー10は、そのような基材の役割を果たしている。

【0030】

第1のワイヤー10は、種々の材料から構成されてよいが、例えば、絶縁体等の非導電性材料から構成されてもよい。第1のワイヤー10の周囲は、導電性材料20で被覆されるので、導電性材料である必要は無く、所望の材料を用いることができる。例えば、第1のワイヤー10には、絶縁性ワイヤーを用いるようにしてもよい。また、第1のワイヤー10は、例えば、ニッケルや鉄等、種々の金属から成るピアノ線等のように、配線材料に比べて導電性が低い材料が用いられてもよい。なお、ピアノ線等のように、導電性が高くない材料を用いる場合であっても、導電性材料20は、金や銅、アルミニウム等の配線金属レベルの高い導電性を有することが必要とされるため、絶縁性ワイヤーを用いる場合と同様に、導電性材料20による被覆はやはり行うことになる。

【0031】

第1のワイヤー10は、被覆する周囲の導電性膜よりも熱膨張率の低い材料を用いることが好ましい。例えば、ディスプレイ用の配線には比較的導電性が高く安価な銅やアルミニウムなどが用いられるが、第1のワイヤー10自体をそれらの金属材料で構成するよりも、例えば、ピアノ線又はピアノ線より線膨張率が低いワイヤーを第1のワイヤー10として用意し、第1のワイヤー10の周囲をそれらの金属材料で被膜した構成とすることにより、低い線膨張率と高い導電性を両立させることができる。これにより、回路抵抗が低く、熱による性能劣化が低い信頼性の高い素子の作製が可能となる。

【0032】

更に金属を用いた導電性ワイヤーの場合、作製プロセスによっては、金属表面の酸化や薬品による劣化などが大きな課題となる。しかしながら、実施形態1に係る薄膜トランジスタ200においては、第1のワイヤー10と導電性膜20の二層構造にすることにより、作製プロセスに応じて、例えば表面に形成する導電材料に耐薬品性に優れた材料などを自由に選択できるため、それらの問題にも十分対処することが可能である。

【0033】

このように、実施形態1に係る薄膜トランジスタ200は、第1のワイヤー10と導電成膜20の二重構造を採用することにより、第1のワイヤー10と導電性材料20の双方について、用途や製造プロセスに応じた幅広い材料選択が可能な構成となっている。

【0034】

導電性材料20は、ゲート電極としての役割を果たす。導電性材料20は、配線として使用できれば、種々の材料を用いてよいが、例えば、銅、アルミニウム、金、銀といった導電性の高い金属材料を用いてもよい。これらの金属材料は、既に配線用金属材料として用いられている材料であり、導電性材料20に好適に用いることができる。なお、導電性材料20は、第1のワイヤー10の全周を被覆して構成されてもよいし、第1のワイヤーを部分的に覆うように構成されてもよい。

【0035】

上記の第1のワイヤー10と導電性材料20の組み合わせとしては、例えば、表面が銅めっきされたピアノ線等が挙げられる。

【0036】

絶縁膜30は、ゲート絶縁膜として機能することが可能であれば、種々の絶縁性材料を用いることができる。

【0037】

薄膜半導体40は、薄膜トランジスタ200のチャネルとしての役割を果たす箇所である。図1においては、薄膜半導体40は、上面に設けられているが、絶縁膜30を介して導電性材料20の直上にあれば、種々の位置に設けることができる。

【0038】

薄膜半導体40は、有機半導体材料から構成されてもよいし、シリコン又は酸化物からなる無機半導体材料から構成されてもよい。

【0039】

樹脂基板層60は、樹脂から構成されたフレキシブルな基板層であり、例えば、プラスティック基板層で構成されてもよい。

【0040】

第1の微細電極70及び第2の微細電極80は、ソース電極又はドレイン電極としての役割を果たす電極である。第1の微細電極70及び第2の微細電極80は、導電性材料から構成される。例えば、金属材料から構成されてもよい。図1(a)において、第1の微細電極70は、樹脂基板層60の表面同士の接続を行えばよいので、樹脂基板層60の表面上に形成されているが、第2の微細電極80は、樹脂基板層60中にある導電性材料100と接続される必要があるので、樹脂基板層60の中に形成されたビアホール80aに充填されて形成されている。

【0041】

配線用ワイヤー110は、横方向の配線ために設けられ、第2のワイヤー90の周囲を導電性材料100が被覆して構成されている。第2のワイヤー90及び導電性材料100は、第1のワイヤー10及び導電性材料20と同じ材料から構成されてよい。

【0042】

なお、配線用ワイヤー110は、第1のワイヤー10と異なり、熱膨張係数や線膨張率を低下させることに大きな注意を払う必要は必ずしも無く、配線用金属等を用いた導電性ワイヤーを用いることも可能である。配線用金属又はこれに準ずる導電性を有する材料で構成された導電性ワイヤーを用いた場合、導電性材料20、100により必ずしも被膜される必要はない。

【0043】

画素電極120は、画素に電圧を印加するための電極であり、導電膜から構成されてよい。例えば、画素に用いられる表示素子は、用途に応じて種々の素子を用いることができ、液晶素子、有機EL(Electro-luminescence)素子、無機EL素子、電子インク又は電子粉流体を用いることができる。本実施例においては、表示素子が液晶素子である例が挙げられている。

【0044】

実施形態1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板によれば、ゲート・チャネル一体形成部50を樹脂基板層60と別体として構成することにより、十分な加熱加工が可能になるとともに、これを樹脂基板層60の表面上に配置することにより、薄膜トランジスタ200の位置決め形成を容易に行うことができる。

【0045】

〔実施形態2〕

図2は、本発明の実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。図2(a)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の断面図であり、図2(b)は、実施形態2に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の平面図である。

【0046】

図2(a)において、実施形態2に係る薄膜トランジスタ201及び薄膜トランジスタアレイ基板は、第1のワイヤー11と、導電性材料21と、絶縁膜31と、薄膜半導体41と、樹脂基板層61と、第1の微細電極71と、第2の微細電極81と、第2のワイヤー91と、導電性材料101と、画素電極121とを有する。また、第1のワイヤー11、導電性材料21、絶縁膜31及び薄膜半導体41は、ゲート・チャネル一体形成部51を構成する。更に、第2のワイヤー91及び導電性材料101は、配線用ワイヤー111を構成する。

【0047】

図2(a)において、実施形態2に係る薄膜トランジスタ201は、第1のワイヤー11、導電性材料21、絶縁膜31及び薄膜半導体41から構成されるゲート・チャネル一体形成分51は、樹脂基板層61の内部に配置されている点で、実施形態1に係る薄膜トランジスタ200と異なっている。また、これに対応し、横方向に延在する配線用ワイヤー111は、樹脂基板層61の表面上に形成されている点で、実施形態1と異なっている。画素電極121が樹脂基板層61の表面上に形成されている点は、実施形態1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板と同様である。また、第1の微細電極71及び第2の微細電極81は、薄膜半導体41の両側を覆うように樹脂基板層61の内部に配置され、上方へと延びている。そして、第1の微細電極71は、ビアホール71aを通して樹脂基板層61の表面上にある画素電極121と接続され、第2の微細電極81は、やはりビアホール81aを通して樹脂基板層60の表面上にある導電性材料101と接続されている。

【0048】

図2(b)において、樹脂基板層61の表面上に、画素電極121と、第2のワイヤー91の周囲の一部又は全面が導電性材料101で被覆された配線用ワイヤー111が2本横方向に延在して配置され、これと直交するようにゲート・チャネル一体形成部51が縦方向に樹脂基板層61の内部に形成された状態が示されている。樹脂基板層61の表面上の2本の配線用ワイヤー111は、画素電極121を挟むように両端に配置されており、各々が互いに重ならないように配置されている。

【0049】

なお、個々の構成要素については、実施形態1と同様であるので、各々の構成要素に実施形態1の参照符号に1加えた参照符号を対応して付し、その説明を省略する。

【0050】

実施形態2に係る薄膜トランジスタ201及び薄膜トランジスタアレイ基板においても、ゲート・チャネル一体形成部51は、樹脂基板層61と別体にして独立して構成することができるので、単独で十分に加熱して加工を行うことができる。そして、樹脂基板層61を形成する際に、樹脂基板層61の内部に埋め込むようにしてゲート・チャネル一体形成部51を配置することにより、樹脂基板層61の内部に容易に薄膜トランジスタ201を形成することができる。

【0051】

また、表示素子を備えた画素を設け、これを薄膜トランジスタ201で駆動することにより、十分な加熱により優れた特性を有するフレキシブル表示素子を構成することができる。

【0052】

〔実施形態3〕

図3は、本発明の実施形態3に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【0053】

図3において、実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板は、第1のワイヤー12と、導電性材料22と、絶縁膜32と、薄膜半導体42と、樹脂基板層62と、第1の微細電極72と、第2の微細電極82と、第2のワイヤー92と、導電性材料102と、画素電極122とを有する。また、第1のワイヤー12、導電性材料22、絶縁膜32及び薄膜半導体42は、ゲート・チャネル一体形成部52を構成する。更に、第2のワイヤー92及び導電性材料102は、配線用ワイヤー112を構成する。

【0054】

ゲート・チャネル一体形成部52の構成は、実施形態1、2に係るゲート・チャネル一体形成部50、51と同様であるので、その説明を省略する。

【0055】

実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板においては、ゲート・チャネル一体形成部52が樹脂基板層62の内部に形成されており、画素電極122が樹脂基板層62の表面上に形成されている点では、実施形態2に係る薄膜トランジスタ201及び薄膜トランジスタアレイ基板と同様であるが、第2のワイヤー92の周囲の一部又は全面が導電性材料102で被覆された配線用ワイヤー112が樹脂基板層62の内部に配置されている点で、実施形態2に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板と異なっている。

【0056】

このように、ゲート・チャネル一体形成部52及び配線用ワイヤー112を樹脂基板層62の内部に配置する構成としてもよい。これにより、第1の微細電極72は上方の画素電極122にビアホール72aを通して接続され、第2の微細電極82はビアホール82aを通して下方の導電性材料112に接続される構成となる。

【0057】

実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板によれば、画素電極122のみ樹脂基板層60の表面に形成されるため、画素面積を広くとることが可能となり、画素の高精細化や、開口率や輝度の向上に有利である。

【0058】

〔実施形態4〕

図4は、本発明の実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した断面図である。

【0059】

図4において、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板は、第1のワイヤー13と、導電性材料23と、絶縁膜33と、薄膜半導体43と、樹脂基板層63と、第1の微細電極73と、第2の微細電極83と、第2のワイヤー93と、導電性材料103と、画素電極123とを有する。また、第1のワイヤー13、導電性材料23、絶縁膜33及び薄膜半導体43は、ゲート・チャネル一体形成部53を構成する。更に、第2のワイヤー93と導電性材料103とは、配線用ワイヤー113を構成する。

【0060】

ゲート・チャネル一体形成部53の構成は、実施形態1〜3に係るゲート・チャネル一体形成部50〜52と同様であるので、その説明を省略する。

【0061】

図4において、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板は、ゲート・チャネル一体形成部53及び第2のワイヤー93が導電性材料103で被覆された配線用ワイヤー113が樹脂基板層63の内部に設けられている点で、実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板と同様であるが、配線用ワイヤー113がゲート・チャネル一体形成部53の下方ではなく上方に設けられている点で、実施形態3に係る薄膜トランジスタ202及び薄膜トランジスタアレイ基板と異なっている。

【0062】

このように、配線用ワイヤー113は、ゲート・チャネル一体形成部53より上方の樹脂基板層63の内部に設けてもよい。なお、画素電極123は、実施形態1〜3と同様に、樹脂基板層63の表面上に形成される。かかる配置構成により、第1の微細電極73及び第2の微細電極83の双方ともビアホール73a、83aを通して上方に延び、第1の微細電極73は画素電極123、第2の微細電極83は導電性材料103に接続される。

【0063】

実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板においても、樹脂基板層63の表面には画素電極123しか存在しないので、画素面積を広くとることが可能となり、画素の高精細化や、開口率や輝度の向上に有利な構成となる。

【0064】

以上、実施形態1〜4に係る薄膜トランジスタ200〜203及び薄膜トランジスタアレイ基板について説明したが、実施形態1〜4の何れにおいても、絶縁膜30〜33と薄膜半導体40〜43は樹脂基板層60〜63と一体化される前に第一のワイヤー10〜13上に直接形成され、構成のみ異なるだけで全て同様の機能を持つ。

【0065】

実施形態1〜4に係る薄膜トランジスタアレイ基板の構成により、薄膜トランジスタ200〜203で駆動するあらゆる表示素子において、例えば液晶、有機EL、無機EL、電子インク、電子粉流体などを画素部で駆動することにより、フレキシブル表示素子を構成することが可能となる。その構成は対向電極を含めて既存の素子で用いられているあらゆる構成を適用することが可能である。

【0066】

なお、実施形態1〜4に係る薄膜トランジスタアレイ基板を用いてフレキシブル表示素子を構成するためには、薄膜トランジスタアレイ基板と対向するようにフレキシブルな樹脂基板を配置し、両基板の間であって、薄膜トランジスタアレイ基板の画素電極120〜123に対応する位置に各画素を形成すればよい。各画素は、上述のような表示素子を備えてよい。また、薄膜トランジスタアレイ基板の薄膜トランジスタ200〜203を駆動制御する駆動回路を更に備えることにより、フレキシブル表示装置を構成することができる。

【0067】

ワイヤー10〜13、90〜93は、細長い金属線や金属線の束、あるいは高分子材料を用いた繊維の束などを用いることができるが、その表面を導電性の高い金属や導電性高分子材料などで被膜することで導電性を得ることが可能となるため、特にワイヤー自体は導電性を示す材料を用いる必要はない。

【0068】

また、ワイヤー10〜13、90〜93の断面は円形や楕円形などいかなる形状であっても良く、特に上部に薄膜半導体40〜43を形成するためには長方形など上部が平坦な形状であることが望ましい。

【0069】

ワイヤー10〜13、90〜93の太さは、画素の精細度によって一般的には5μm〜500μm程度の範囲で自由に変えることが可能であるが、パターニングなどの加工処理を容易に行うためには10〜50μm程度の範囲であることが望ましい。また、図1〜4には示されていないが、画素面積を非常に小さくし、画素電極120〜123を樹脂基板層60の表面ではなく、上部が平坦な太いワイヤー10〜13を用いて、画素電極120〜123もワイヤー10〜13上に形成する場合には、画素のサイズに応じて500μm以上のワイヤー10〜13、90〜93を用いても良い。なお、スクリーン型の大型ディスプレイなどに応用する場合には、画素電極をワイヤー上に形成しなくても、500μm以上のワイヤーを用いることが有効である。

【0070】

ワイヤー10〜13、90〜93としては、例えばピアノ線に用いられている材料等から構成され、容易に切断されないものが望ましい。ワイヤー10〜13、90〜93の材料としては、有機・無機あるいはそのハイブリッド構造のいかなる材料を用いても構わないが、熱伸縮が起こりにくい材質を適用することが好ましい。また導電性ワイヤーを絶縁膜で被膜したものであっても良い。

【0071】

ワイヤー10〜13、90〜93上に形成される導電性材料20〜23、100〜103は、ワイヤー10〜13、90〜93の全面を覆うことにより高い導電性を確保することが可能であるが、薄膜半導体40〜43が真上に存在する部分を覆っていればよく、必ずしも全面を覆う必要は無い。導電性材料20〜23、100〜103がワイヤー10〜13、90〜93の一部のみを覆う構成の場合には、ワイヤー10〜13、90〜93の材質は、高分子材料や導電性の低い金属などを適用することが好ましい。

【0072】

例えば、ワイヤー10〜13、90〜93に高分子樹脂等の絶縁性の高い材料を用いた場合には、導電性材料20〜23、100〜103を形成することで所望の位置のみ導電性を付与することが可能となり、導電性を付与したワイヤー10〜13、90〜93の交差部による容量を低減させたり、隣接したTFT(Thin Film Transistor、薄膜トランジスタ)同士を電気的に絶縁させたりするなど、薄膜半導体40〜43の設計の自由度を高めることが可能となる。

【0073】

更に、ワイヤー材料はワイヤー10〜13、90〜93毎に異なる材料を用いても良く、形状もワイヤー10〜13、90〜93毎に異なっていても良いが、デバイスの作製プロセスにおいて熱変形などを抑制するためには、可能な限り同じ材料であることが好ましい。

【0074】

但し、上方に薄膜半導体40〜43や電極70〜73、80〜83を形成しないワイヤーに関しては、ワイヤーの交差部における容量が問題にならない場合においては、ワイヤーそのものを導電性の高い材料で構成することで、その周囲の導電性材料20〜23、100〜103を必ずしも形成する必要はない。

【0075】

ワイヤー上に形成される導電性材料20〜23、100〜103や、導電性の高い材料で構成される場合のワイヤー10〜13、90〜93の材料としては、例えば金、銀、銅、亜鉛、アルミニウム、イリジウム、カルシウム、ニッケル、ベリリウム、マグネシウム、モリブデン、ロジウム、チタン、タンタル、白金、クロム、タングステン、鉄、スズなどの金属やそれらの合金(例えばニクロム、コンスタンタン、黄銅など)や、ITO、ZnO、IGZO等の酸化物、ポリエチレンジオキシチオフェンなどの導電性高分子材料、カーボンナノチューブやフラーレン、グラフェンなど炭素で構成される材料や、これらの複合材料等が考えられるが、ここに記載された材料に限定されるものではなく、種々の材料を適用することが可能である。

【0076】

ワイヤー10〜13上に形成される絶縁膜30〜33は、ディッピングやスプレーコーティング、バーコーティング、ダイコーティング、フレキソ印刷、インクジェット、スパッタ、CVD、真空蒸着、スピンコート法など、あらゆる塗布技術や印刷手法、成膜技術を用いて形成することが可能であるが、ワイヤー10〜13上に被膜された導電性材料20〜23が金属の場合、その金属の陽極酸化により形成することもできる。また必要に応じて絶縁膜30〜33の形成過程で加熱処理をしても良い。

【0077】

絶縁膜30〜33の材料としては、例えば、SiO2、SiN、Ta2O5、Al2O3などの無機材料を用いることが可能である。有機材料としては、光照射をはじめ、熱硬化または反応硬化により形成される、メタクリル樹脂、アクリル樹脂、ウレタン樹脂、ポリ塩化ビニル、酢酸ビニル、フェノール樹脂、エポキシ樹脂、セルロース樹脂、ポリエチレン、ポリエチレンテレフタレート、ポリブチレンテレフタレート、ポリプロピレン、メラミン樹脂、ポリエステル、ポリビニルブチラール、ポリビニルカルバゾール、ポリビニールアセテート、ポリカーボネート、ポリスチレン、ポリスルホン、ポリエーテルスルホン、ポリアリレート、ポリエーテルイミド、アセチルセルロース、シリコーン樹脂、フッ素樹脂、またはこれらの共重合体や変性体などを用いることができる。また、これら以外の高分子樹脂を適用することも可能であり、絶縁性を有するあらゆる材料を適用することができる。

【0078】

絶縁膜30〜33の厚さは、材料の誘電率や絶縁性等を鑑みて自由に設定することが可能であるが、低電圧駆動を実現するためにも20〜300nm程度の範囲で制御することが好ましい。また、絶縁膜30〜33は、ワイヤー10〜13、90〜93を完全に被覆する必要はないが、少なくとも薄膜半導体40〜43及び微細電極70〜73、80〜83が形成される部分は、十分な絶縁性が確保されることが重要である。

【0079】

薄膜半導体40〜43の材料としては、シリコン半導体(poly−Siやa−Siなど)やGaAs、酸化物半導体(InGaZnO、ZnO、GaZnO、ZnO、InO)などの無機半導体材料や、ペンタセンやアントラセンなどの有機半導体など、あらゆる半導体材料を用いることができ、その形成過程において高温での加熱処理を行っても良い。

例えば、InGaZnOを用いた場合には、高い移動度やOn−Off比を確保するためには、300℃程度の熱アニールを行うことが望ましいが、樹脂基板60〜63と一体化する前に熱アニールを行うことで、樹脂基板60〜63の変形を防止することが可能となる。また半導体を加熱する際に、簡易な手法としてはヒーターやオーブンなどで加熱する方法が挙げられるが、紫外線やエキシマレーザーなどを照射する手法など、あらゆる加熱手法を適用することが可能である。

【0080】

なお、耐熱性の低いプラスティック基板を用いた場合は熱伸縮の影響が大きく、絶縁膜30〜33や薄膜半導体40〜43を形成する際に、プラスティック材料によっては100℃以下の加熱でも金属配線のパターンずれが発生し易い。樹脂基板60〜63をガラスに張り付けて加熱する方法を用いても、120℃程度まで加熱するとパターニング不良が生じることもある。それに対して本手法では、樹脂基板60〜63と一体化する前にワイヤー10〜13、90〜93を直接加熱することができるため、樹脂基板層60〜63への直接的なダメージを防ぐことが可能となる。即ち120℃以上の加熱処理を施すことができる。

【0081】

有機半導体材料の成膜方法としては、真空蒸着法やスピンコート法が代表的な手法として挙げられるが、他にもダイコーティング、バーコーティング、シルクスクリーン印刷、樹脂凸版印刷、フレキソ印刷、グラビア印刷、オフセット印刷、インクジェット法などを含む印刷技術など、あらゆる塗布・製膜技術を用いて形成することが可能である。

【0082】

また無機半導体の成膜方法としては、スパッタ法、CVD法、真空蒸着法などが代表的であるが、塗布形成が可能な材料を用いる場合には、ディッピングやスプレーコーティング、バーコーティング、ダイコーティング、フレキソ印刷、インクジェット、スピンコート法など、あらゆる塗布技術や印刷技術、成膜技術を用いて形成することが可能である。

【0083】

薄膜半導体40〜43上に形成される微細電極(ソース・ドレイン電極)80〜83は、必ずしも樹脂材料と一体化する前に形成する必要はないが、予め部分的に形成しておくことも可能となる。

【0084】

また実施形態1〜4において、薄膜半導体40〜43が形成されたワイヤー10〜13と、垂直方向に配列された配線ワイヤー110〜113は、微細電極70〜73、80〜83によって接続されているが、薄膜半導体40〜43上に接触させる構成とすることもできる。その際、金属を介し接触抵抗の大きさを制御したり、導電性の高分子材料を用いて熱圧着したりすることもできる。

【0085】

なお、微細電極70〜73、80〜83によりゲート・チャネル一体形成部50〜53、配線用ワイヤー110〜113や画素電極120〜123と接続する際には、樹脂基板層60〜63上でパターニングすることが必要となるが、レジストの硬化温度程度の加熱処理に留まり、かつパターニング回数も大幅に低減できるため、プラスティック基板上に積層・パターニングで形成する従来技術に比べてアライメントずれによるパターン不良を抑制することができる。

【0086】

また、第二のワイヤー90〜93の代わりに金属や有機導電性高分子などを樹脂基板層60上にパターン形成するデバイス構成とする場合についても、従来法に比べて絶縁膜30〜33や薄膜半導体40〜43を予め形成しておくため、プラスティック基板上でのパターニングの回数が大幅に低減され、かつ半導体や絶縁膜の高温処理を必要としないことから、アライメントずれによるパターン不良を大幅に抑制できる。

【0087】

樹脂基板層60〜63の材料としては、光照射をはじめ、熱硬化または反応硬化により形成される、メタクリル樹脂、アクリル樹脂、ウレタン樹脂、ポリ塩化ビニル、酢酸ビニル、フェノール樹脂、エポキシ樹脂、セルロース樹脂、ポリエチレン、ポリエチレンテレフタレート、ポリブチレンテレフタレート、ポリプロピレン、メラミン樹脂、ポリエステル、ポリビニルブチラール、ポリビニルカルバゾール、ポリビニールアセテート、ポリカーボネート、ポリスチレン、ポリスルホン、ポリエーテルスルホン、ポリアリレート、ポリエーテルイミド、アセチルセルロース、シリコーン樹脂、フッ素樹脂、またはこれらの共重合体や変性体などが挙げられるが、これらの材料に限られるものではない。

【0088】

次に、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板について、ゲート・チャネル一体形成部53を樹脂基板層63と一体化形成する手法について説明する。なお、以下、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイを例に挙げて説明するが、かかる手法は、実施形態1〜4に共通して用いることができる。

【0089】

図5は、ゲート・チャネル一体形成部53を樹脂基板層63内に配置するための一方式を示したものである。

【0090】

図5(a)は、複数のゲート・チャネル一体形成部53を平行に配列し、両端を固定治具140により固定した状態を示した図である。なお、図5(a)においては省略されているが、ゲート・チャネル一体形成部53及び固定治具140は、流動体を保持できる容器内に設置されている。このとき、ワイヤー53には、適度に張力をかけておくことが望ましい。

【0091】

図5(b)は、樹脂材料63aを流し込んだ状態を示した図である。図5(b)に示すように、ゲート・チャネル一体形成部53を平行に配列した状態で樹脂材料63aを流し込んで供給し、ゲート・チャネル一体形成部53を樹脂材料63aに浸漬させる。なお、樹脂材料63aは、硬化前は液体等の流動体状であり、加熱や紫外線の照射で硬化する性質を有する樹脂材料63aを用いる。

【0092】

樹脂材料63aを供給する際、樹脂基板60の厚みを制御するため、ゲート・チャネル一体形成部53の列を密閉容器に入れた状態で樹脂材料63aを流し込むことが望ましい。その際、密閉容器を真空にすることにより、樹脂内部への気泡の混入を抑制することが可能となる。

【0093】

図5(c)は、樹脂基板層63を形成した状態を示した図である。図5(c)に示すように、供給された樹脂材料63aを加熱や紫外線照射等で硬化し、樹脂基板層63を形成する。樹脂基板層63の形成により、ゲート・チャネル一体形成部53が樹脂基板層63内に埋め込まれた状態となる。

【0094】

なお、図5においては、ゲート・チャネル一体形成部53の列の上から樹脂を流し込む一例を示したが、例えば、ゲート・チャネル一体形成部53の列を金型の中に入れ、樹脂材料63aを注入する方法を用いても良い。金型としては、樹脂材料63aの注入口を設けた箱状の容器など、一般的に用いられているあらゆる手法を適用することができる。

【0095】

樹脂材料63aを流し込む際に、例えばダイコーティングやバーコーティング、スクリーン印刷、グラビア印刷、オフセット印刷、樹脂凸版印刷、インクジェット法、フレキソ印刷法、スピンコート法などを用いて膜厚を制御する手法を用いることができるが、これらに限定されるものではなく、あらゆるコーティング技術を適用することができる。また樹脂材料を流し込んだ後、スピンコートにより膜厚を制御する手法を用いることも可能である。

【0096】

樹脂材料63aを硬化させる手法としては、熱硬化法、紫外線や可視光を用いた光硬化法、反応硬化法などを用いることができるが、樹脂材料63aに応じて最適な方法を用いることが重要である。

【0097】

例えば、紫外線硬化性樹脂を用いた場合には、容器内で形成する際にもガラスや石英など紫外線を透過する容器を用いる必要がある。また熱硬化を行う際には、ヒーターを容器として用いたり、熱伝導性の良い容器を適用したりすることにより、的確に樹脂材料63aを硬化させることができる。

【0098】

図6は、樹脂基板層63の上部にゲート・チャネル一体形成部53を配置するための一方式を示した図である。

【0099】

図6(a)は、ゲート・チャネル一体形成部53を樹脂材料63a上に配置する状態を示した図である。図6(a)に示すように、両端を固定治具140で固定されたゲート・チャネル一体形成部53を、硬化前あるいは完全には硬化していない樹脂材料63aの上部に配置する。樹脂材料63aは、ある程度の硬度を有する完全には硬化していない状態であれば、そのままゲート・チャネル一体形成部53を上に載置することができる。

【0100】

図6(b)は、樹脂材料63aを完全に硬化させた状態を示した図である。図6(b)に示すように、樹脂材料63aを硬化させて樹脂基板層63を形成することにより、樹脂基板層63とゲート・チャネル一体形成部53を一体化する。このとき、上部にローラーなどを用いて適度に圧力をかける手法、あるいは固定治具140に圧力をかける手法により、ゲート・チャネル一体形成部53の一部分を基板内に押し込むことが可能となる。なお、ゲート・チャネル一体形成部53にさらに強い圧力をかけると、ゲート・チャネル一体形成部53を基板層内に埋め込むことも可能となる。

【0101】

また、図6は、完全に硬化していない樹脂材料63aの上部に配置する手法を示したものであるが、別の手法としては、柔軟な基板上に薄い樹脂を塗布し、図6の手法と同様に樹脂を硬化させることで、ゲート・チャネル一体形成部53と一体化させることも可能である。

【0102】

また、図6に示した基板上部に設置する手法で一体化した後、さらに樹脂材料63aを上部に塗布して硬化させることで、ゲート・チャネル一体形成部53を樹脂基板層60に埋め込むことが可能となる。このとき、埋め込むための二層目の樹脂材料63aは、必ずしも一層目の樹脂材料63aと同じ材料を用いる必要はない。また、二層目を形成する際には、図5を用いて説明した一層目の形成に用いられる全ての手法を適用することができる。

【0103】

なお、上述の例では、樹脂材料63aを一層目と二層目で二種類適用する手法を説明したが、各層に必要に応じて複数の樹脂材料63aを積層しても良い。また各樹脂層63aの間にバリア性を高める効果などを付加するため、SiO2やSiNなどの無機膜を積層することも可能である。この場合、ゲート・チャネル一体形成部53を配置する部分の樹脂材料63aのみが完全に硬化していなければ一体化できるため、下の層の樹脂材料63aは完全に硬化していても構わない。但し、上部の樹脂材料63aを硬化させる際に熱などにより伸縮がなるべく生じないように、樹脂材料63aを的確に選択することが重要である。

【0104】

互いに垂直なゲート・チャネル一体形成部53とワイヤー93を上下に配置するためには、図5と図6で説明した一段のゲート・チャネル一体形成部53を配置する手法の全ての組み合わせを適用することで実現されるが、最も簡便な方法としては、ゲート・チャネル一体形成部53とワイヤー93の列を所望の距離で上下に配置し、樹脂を流し込むことにより形成する手法が挙げられる。このとき、上下の高さを制御するため、図5と図6で示した固定冶具140を用いてゲート・チャネル一体形成部53及びワイヤー93には適度に張力をかけておくことが望ましい。なお、固定冶具140は上段のワイヤー93と下段のゲート・チャネル一体形成部53で個別に用いても良いが、上下の厚みを的確に制御するためには一つの固定冶具で固定することが望ましい。

【0105】

また、完全に硬化してない樹脂材料63aの内部に上段のワイヤー93と下段のゲート・チャネル一体形成部53を押し込んだあと、樹脂材料63aを硬化させて一体化する手法を用いることができる。この場合も、固定冶具140は上段と下段で個別に用いても、一つの固定冶具で固定するどちらの手法を用いても良い。

【0106】

その他、二段階に埋め込む手法も効果的である。本手法では、まず下段のゲート・チャネル一体形成部53を図5又は図6で説明した何れかの方法にて樹脂基板層63内に埋め込む。次に、上段の配線用ワイヤー113を樹脂基板層63の上部に設置し、必要に応じてその前後にフォトリソグラフィー法などによりビアホール73a、83aを形成し、薄膜半導体43と配線用ワイヤー113を微細配線83により接続する。更に、図5で説明した手法により、上段の配線用ワイヤー113を樹脂基板層63内に埋め込むことにより、上下段のワイヤー93及びゲート・チャネル一体形成部53を樹脂基板層63と一体化させる。

【0107】

なお、下段のみ埋め込みを行い、上段を樹脂基板63上に設置する場合においても、図5と図6で説明した手法を組み合わせることにより一体化することができる。その際、各工程の途中で必要に応じてフォトリソグラフィー法などによりビアホール73a、83aの形成や微細配線による接続を行っても良い。

【0108】

このように、ゲート・チャネル一体形成部53及び配線用ワイヤー113の樹脂基板層60の内部への設置は、種々の方法により行うことができる。なお、図5及び図6においては、実施形態4の例を挙げて説明しているが、実施形態1〜3にも同様に適用することができる。

【0109】

図7は、補助ワイヤーを用いたゲート・チャネル一体形成部53の設置方法を説明するための図である。図7において、ゲート・チャネル一体形成部53に直交して、補助ワイヤー130が設置され、ゲート・チャネル一体形成部53及び補助ワイヤー130の両端部が、固定治具141により固定されている。

【0110】

補助ワイヤー130は、非導電性の材料から構成されるワイヤーである。図7に示すように、ゲート・チャネル一体形成部53を固定する際に、非導電性の補助ワイヤー130をゲート・チャネル一体形成部53と垂直方向に設置して固定冶具141により固定すると、埋め込む際に張力の不均一性によるワイヤー13の面内の歪みなどの影響を低減できるため、より高精度で一体化させることが可能となる。

【0111】

ここで、補助ワイヤー130は一段である必要はなく、例えば、ゲート・チャネル一体形成部53の上下に設置しても、ゲート・チャネル一体形成部53に織り込む形で上下を通しても良い。また、必ずしもゲート・チャネル一体形成部53と垂直方向に設置しなくても良い。

【0112】

なお、図7においては、ゲート・チャネル一体形成部53に補助ワイヤー130を用いた例を挙げて説明したが、配線用ワイヤー113にも同様に適用することができる。更に、実施形態1〜3のゲート・チャネル一体形成部50〜52、配線用ワイヤー110〜112にも同様に適用することができる。

【0113】

画素電極120〜123は、ゲート・チャネル一体形成部50〜53を樹脂基板層60〜63と一体化した後の工程で樹脂基板層60〜63上にパターン形成される。パターニング方法としては、フォトリソグラフィー法を用いたエッチングやリフトオフなどが一般的であるが、塗布形成が可能な電極材料を用いた場合には、インクジェットを含む印刷技術などを用いて直接パターニングすることも可能である。

【0114】

また、画素電極120〜123は、ゲート・チャネル一体形成部50〜53を樹脂基板層60〜63と一体化する前の工程で、ゲート・チャネル一体形成部50〜53上の薄膜半導体40〜43とは別の領域に直接形成することも可能である。また、画素電極120〜123のみをゲート・チャネル一体形成部50〜53上に予め形成しておいて、図5〜7と同様の方法で、樹脂基板層60〜63の上部や内部に設置することも可能である。両手法とも、パターニングプロセスを削減するために有効である。

【0115】

ここで、画素電極120〜123をゲート・チャネル一体形成部50〜53とともに樹脂基板層60〜63の内部に埋め込んだ場合、その上部にドライエッチングなどで開口部を形成することで樹脂基板層60〜63の表面に容易に露出させることができる。

【0116】

また、薄膜半導体40〜43とゲート・チャネル一体形成部50〜53上の微細電極70〜73、80〜83や透明電極との接続、透明電極の形成時には、フォトリソグラフィー法を用いたエッチングなどによるビアホールの形成やパターニング工程が必要となるため、加熱に伴う樹脂基板層60〜63の伸縮が生じる可能性があるが、固定冶具140、141で十分な張力をかけて配線パターンを高精度で維持させることが可能となる。

【0117】

次に、図8〜11を用いて、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法について説明する。

【0118】

図8は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1段階の一連の工程を示した図である。なお、各構成要素には、実施形態4と同様の参照符号を付し、その説明を省略する。

【0119】

図8(a)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の樹脂材料供給工程の一例を示した図である。樹脂材料供給工程においては、ワイヤー13の周囲に導電性材料23、絶縁膜33及び薄膜半導体43が形成されて構成されたゲート・チャネル一体形成部53が樹脂成形用容器150内に配置され、ディスペンサー160を用いて樹脂材料63aが樹脂形成容器150内に流し込まれて供給される。なお、樹脂材料63aの供給量は、ゲート・チャネル一体形成部53を樹脂材料63a中に浸漬できる程度に供給する。

【0120】

図8(b)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層形成工程の一例を示した図である。第1樹脂基板層形成工程においては、樹脂材料63aが硬化され、樹脂基板層63の第1層目である第1樹脂基板層63bが形成される。

【0121】

図8(c)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層取り出し工程の一例を示した図である。第1樹脂基板層取り出し工程においては、樹脂成形用容器150内に形成された第1樹脂基板層63bが取り出される。

【0122】

図8(d)は、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法の第1樹脂基板層ビアホール形成工程の一例を示した図である。第1樹脂基板層ビアホール形成工程においては、第1樹脂基板層63bの表面上にフォトレジスト170が形成され、開口部171から第1樹脂基板層63bをエッチングし、ビアホール83aを形成する。

【0123】

図9は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2段階の一連の工程を示した図である。

【0124】

図9(a)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法のレジスト除去工程の一例を示した図である。レジスト除去工程においては、第1樹脂基板層63bの表面からレジスト170が除去される。第1樹脂基板層63bの表面には、ゲート・チャネル一体形成部53の薄膜半導体43まで到達するビアホール83aが形成されている。

【0125】

図9(b)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の配線用ワイヤー設置工程の一例を示した図である。配線用ワイヤー設置工程においては、ワイヤー93の周囲に導電性材料103が被覆された配線用ワイヤー113が第1樹脂基板層63bの表面上に設置される。

【0126】

図9(c)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の微細電極形成工程の一例を示した図である。微細電極形成工程においては、ソース電極又はドレイン電極となる微細電極83が、ビアホール83aに導電性材料が充填されることにより形成される。これにより、薄膜半導体43の一端と配線用ワイヤー113が接続される。

【0127】

図9(d)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層用樹脂材料供給の一例を示した図である。第2樹脂基板層用樹脂材料供給工程においては、第1樹脂基板層63bを再び樹脂成形用容器150内に配置し、ディスペンサー161を用いて樹脂材料63cを樹脂成形用容器150内に流し込み、第1樹脂基板層63bの表面に樹脂材料63cを供給する。

【0128】

図10は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第3段階の一連の工程を示した図である。

【0129】

図10(a)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層形成工程の一例を示した図である。第2樹脂基板層形成工程においては、供給された樹脂材料63cが硬化され、2層目となる第2樹脂基板層63dが第1樹脂基板層63b上に形成される。

【0130】

図10(b)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層取り出し工程の一例を示した図である。第2樹脂基板層取り出し工程においては、形成された第2樹脂基板層63dが樹脂成形用容器150から取り出される。

【0131】

図10(c)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層ビアホール形成工程の一例を示した図である。第2樹脂基板層ビアホール形成工程においては、第2樹脂基板層63dの表面上にフォトレジスト172が形成され、開口部173から第2樹脂基板層63d及び第1樹脂基板層63bがエッチングされる。第2樹脂基板層63d及び第1樹脂基板層63bのエッチングされた箇所には、ビアホール73aが形成される。

【0132】

図10(d)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法のレジスト除去工程の一例を示した図である。レジスト工程においては、第2樹脂基板層63dの表面からレジスト172が除去される。第2樹脂基板層63dの表面には、薄膜半導体43の他端まで到達するビアホール73aが形成されている。

【0133】

図11は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の最終段階の一連の工程を示した図である。

【0134】

図11(a)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の第2樹脂基板層微細電極形成工程の一例を示した図である。第2樹脂基板層微細電極形成工程においては、ビアホール73aに導電性材料が充填され、微細電極73が形成される。

【0135】

図11(b)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の画素電極成膜工程の一例を示した図である。画素電極成膜工程においては、画素電極123となる導電膜123aが第2樹脂基板層63dの表面に成膜される。成膜方法は、CVD法、蒸着法、スパッタ法等、種々の成膜方法を用いることができる。

【0136】

図11(c)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法の画素電極パターニング工程の一例を示した図である。画素電極パターニング工程においては、導電膜123a上にフォトレジスト174が形成され、開口部175からエッチングが行われ、導電膜123aがパターニングされて分割され、画素電極123が形成される。

【0137】

図11(d)は、実施形態4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の製造方法のレジスト除去工程の一例を示した図である。レジスト除去工程においては、画素電極123の表面からフォトレジスト174が除去される。画素電極123は、各画素及び薄膜トランジスタ203に対応して形成されている。

【0138】

図8〜11で説明した一連のプロセスにおいて、ソース電極又はドレイン電極としての機能を持つ微細電極73、83のパターニングはフォトレジストを用いてウェットエッチング、もしくはドライエッチングなどにより行うことができる。なお、樹脂材料63a、63cを硬化させる手法としては、熱硬化、光硬化、反応硬化など、樹脂材料63a、63cの材料に応じて適切に行うことが可能である。

【0139】

次に、図12及び図13を用いて、図8(c)、(d)及び図9(a)〜(c)で示した工程の上面の状態を説明する。

【0140】

図12は、図8(c)、(d)及び図9(a)、(b)の工程を上面から透過的に示した平面図である。図12(a)は、図8(c)で示した第1樹脂基板層取り出し工程の平面図である。図12(a)において、第1樹脂基板層63bの内部にゲート・チャネル一体形成部53が埋め込まれて設置された状態が示されている。ワイヤー13、導電性材料23及び絶縁膜33は、第1樹脂基板層63bの内部を縦方向に貫通し、薄膜半導体43は、絶縁膜33上の一部の領域に島状に形成されている。

【0141】

図12(b)は、図8(d)及び図9(a)で示した第1樹脂基板層ビアホール形成工程〜レジスト除去工程の平面図である。図12(b)において、第1樹脂基板層63aに、ビアホール83aが形成された状態が示されている。ビアホール83aは、導電性材料を充填したときに薄膜半導体43と接続可能なように、薄膜半導体43と重なり領域43aを有するように形成される。

【0142】

図12(c)は、図9(b)で示した配線用ワイヤー設置工程の平面図である。図12(c)において、第1樹脂基板層63aの表面上に、配線用ワイヤー113が設置された状態が示されている。

【0143】

図13は、図9(c)の工程を上面から示した平面図である。図13(a)は、図9(c)で示した微細電極形成工程の前半の導電膜形成工程を示した平面図である。図13(a)において、第1樹脂基板層63bの表面全体に導電膜83bが成膜された状態が示されている。このように、微細電極83の形成時には、最初は第1樹脂基板層63bの表面全体に導電膜83bが形成される。導電膜83bの形成時に、ビアホール83aが導電膜83bで充填され、微細電極83のビア配線部分が形成される。

【0144】

図13(b)は、図9(c)で示した微細電極形成工程の後半の導電膜形成工程を示した平面図である。図13(b)において、導電膜83bがパターニングされ、ビアホール83aの上部を覆うとともに、配線用ワイヤー113に到達するように延在して形成された微細電極83が示されている。これにより、微細電極83が配線用ワイヤー113に電気的に接続される。このように、的確にパターニングすることにより、微細電極83と配線用ワイヤー113との接続を行うことができる。なお、ここではビアホール83aを形成後に配線用ワイヤー113を設置しているが、必要に応じてビアホール83a形成前に配線用ワイヤー113を設置することもできる。なお、図9(b)及び図9(c)においては、図13(a)の工程が省略されて示されているが、実際には、図13(a)の工程を経て微細電極83が形成される。

【0145】

このように、実施形態4に係る薄膜トランジスタ203及び薄膜トランジスタアレイ基板の製造方法によれば、一般に高温の加熱プロセスを伴う絶縁膜33、薄膜半導体43の形成工程は、ゲート・チャネル一体形成部53を先に独立して作製することにより、十分な加熱温度で加熱プロセスを行うことができ、その後は比較的低温のプロセスで樹脂基板層63の内部にゲート・チャネル一体形成部53を組み込むことができる。更に基板上でのパターニング回数を大幅に低減することができる。よって、樹脂基板層63に加熱変形等を大幅に抑制することが可能となり、良好な動作特性を有する大型の薄膜トランジスタアレイ基板を製造することができる。

【0146】

次に、図14及び図15を用いて、薄膜半導体43と配線用ワイヤー113とを接続する別の手法について説明する。

【0147】

図14は、ビアホール形成までの工程を示した図である。図14(a)は、図12(a)と同様の第1樹脂基板層取り出し工程の平面図である。図14(a)において、第1樹脂基板層63bの内部を貫いて、ゲート・チャネル一体形成部53が設置されている。薄膜半導体43は、絶縁膜33の一部に島状に形成されている。

【0148】

図14(b)は、ビアホール形成工程の平面図及び断面図である。図14(b)の左側の平面図及び右側の断面図において、第1樹脂基板層63aにビアホール83aが形成された状態が示されている。図14(b)の平面図及び断面図に示されるように、ビアホール83aは、平面的には薄膜半導体43と重なり領域43aを有し、深さ的には薄膜半導体43に到達する深さに形成される。なお、ビアホール83aは、フォトレジスト等を用いて形成される。

【0149】

図15は、微細電極と配線用ワイヤーを接続する一連の工程を示した平面図である。図15(a)は、導電膜形成工程を示した図である。導電膜形成工程においては、第1樹脂基板層63bの表面全体を覆うように、導電膜83bが形成される。このとき、ビアホール83aは、導電膜83bにより充填され、ビア配線が形成される。

【0150】

図15(b)は、微細電極形成工程の平面図及び断面図である。微細電極形成工程においては、図15(b)の平面図に示されるように、導電膜83bがフォトレジスト等を用いてパターニングされ、ビアホール83aよりも少し大きい領域を覆うように微細電極83が形成される。

【0151】

図15(c)は、配線用ワイヤー設置工程を示した平面図及び断面図である。配線用ワイヤー設置工程においては、微細電極83の表面上に配線用ワイヤー113が設置される。微細電極の上面に配線用ワイヤー113が接触することで、両者が接続される。

【0152】

ここで、配線用ワイヤー113の導電性材料103と微細電極83との接続を的確に行うために、微細電極83の上面または導電性材料103の表面に、導電性樹脂又は導電性微粒子を含んだ樹脂を塗布し、加熱や光硬化などで接着する手法を用いても良い。更に、導電性材料103や微細電極83の材料自体に、上述の特性を有する材料を適用することもできる。また、パターニング後の微細電極83と配線用ワイヤー113が十分に接触していれば、第2樹脂基板層63d(二層目)を形成する際に導電性を保持したまま両者を十分に固定することができる。

【0153】

このように、微細電極83と配線用ワイヤー113の接続が担保されれば、配線用ワイヤー113は種々の位置に配置することができ、また、それに応じて、微細電極83と配線用ワイヤー113の接続も種々の方法により行うことができる。

【0154】

なお、図12〜15においては、実施形態4の微細電極83と配線用ワイヤー113との接続を例に挙げて説明したが、微細電極73にも同様の方法を適用でき、また、他の実施形態1〜4の微細電極70〜72、80〜82と配線用ワイヤー110〜112との接続にも適用することができる。

【0155】

〔実施形態5〕

図16は、本発明の実施形態5に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。実施形態1〜4においては、1画素を1個のトランジスタで駆動する例を示し、例えば既存の液晶を用いた表示素子などに適用することが可能である。しかしながら、有機ELなどでは、基本的に選択用トランジスタと駆動用トランジスタが必要となり、複数個の薄膜トランジスタで駆動する必要がある。実施形態5においては、2個の薄膜トランジスタを各画素に対応させて設けた例について説明する。

【0156】

図16において、実施形態5に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板は、選択用薄膜トランジスタ204と、駆動用薄膜トランジスタ205とを備える。選択用薄膜トランジスタ204は、画素選択用の薄膜トランジスタであり、駆動用薄膜トランジスタ205は、画素駆動用の薄膜トランジスタである。

【0157】

選択用薄膜トランジスタ204は、ワイヤー14と、ワイヤー14の全面もしくは一部を被膜する導電性材料24と、導電性材料24の周囲を被膜する絶縁膜34と、絶縁膜34の上にパターニングされた薄膜半導体44と、薄膜半導体44の上部に形成された第1の微細電極74及び第2の微細電極84とを有する。ここで、ワイヤー14、導電性材料24、絶縁膜34及び薄膜半導体44から構成されるゲート・チャネル一体形成部53は、内部に薄膜半導体44と垂直方向に配線用ワイヤー115が配置された樹脂基板層64の上部に設置され、かつ一体化されている。

【0158】

また、選択用薄膜トランジスタ204には、配線用ワイヤー114が接続されており、配線用ワイヤー114は、ワイヤー94の周囲を導電性材料104が被覆して構成されている。更に、薄膜トランジスタアレイ基板は、画素電極124を備えている。かかる構成は、基本的に1個の薄膜トランジスタで駆動する実施形態1〜4に係る薄膜トランジスタアレイ基板と同様である。

【0159】

一方、駆動用薄膜トランジスタ205は、ワイヤー15と、導電性材料25と、絶縁膜35と、薄膜半導体45と、第1の微細電極75と、第2の微細電極85とを備える。ここで、ワイヤー15、導電性材料25、絶縁膜35及び薄膜半導体45は、ゲート・チャネル一体形成部55を構成する。

【0160】

また、駆動用薄膜トランジスタ205の第2の微細電極85は、ワイヤー95の周囲が導電性材料106で被覆された配線用ワイヤー115に接続されている。更に、第1の微細電極75は、画素電極124に接続されており、薄膜トランジスタアレイ基板を構成している。

【0161】

ここで、駆動用薄膜トランジスタ205は、備える構成要素自体は第1の薄膜トランジスタ204と同様であるが、ワイヤー15の全周が導電性材料25に被覆されているのではなく、ワイヤー15の表面上の一部の領域に導電性材料25が島状に形成され、ワイヤー15の一部を覆っているに過ぎない点で、選択用薄膜トランジスタ204と異なっている。また、島状の導電性材料25の構成に伴い、絶縁膜35も導電性材料25を覆うように島状に設けられ、薄膜半導体45も、絶縁膜35の上に島状に形成されている点で、選択用薄膜トランジスタ204と異なっている。なお、図16においては、導電性材料25をワイヤー15の上面の一部に形成する構成としたことに伴い、ワイヤー15の上面の面積がワイヤー14よりも数倍広い幅に構成されているが、TFTの特性に応じて自由に設定することが可能である。

【0162】

このように、本実施形態に係る駆動用薄膜トランジスタ205は、ワイヤー15の全周を導電性材料25及び絶縁膜35で覆うではなく、ワイヤー15の一部を導電性材料25及び絶縁材料35で覆い、絶縁膜35上に薄膜半導体45を形成するように構成してもよい。この場合であっても、導電性材料25からなるゲートをゲート酸化膜である絶縁膜35が絶縁し、絶縁膜35上に配置された薄膜半導体45がチャネルとして機能する、というトランジスタの基本的構成を有しているので、薄膜トランジスタ205はトランジスタ機能を果たすことができる。

【0163】

画素選択用トランジスタと、画素駆動用トランジスタの2個のトランジスタを備えた画素回路においては、画素選択用トランジスタの出力端子が、画素駆動用トランジスタのゲートに接続される構成をとる必要がある。よって、画素駆動用トランジスタのゲートは、外部から接続可能なように、総てが被覆されていないことが好ましい。よって、実施形態5に係る駆動用薄膜トランジスタ205においては、ゲートとして機能する導電性材料25の周囲総てを被覆しない構成とするため、十分な面積を有するワイヤー15の表面に、ワイヤー15の一部を覆うよう島状の形状とし、やはり島状の絶縁膜35から容易に露出可能な構成としている。これにより、選択用薄膜トランジスタ204の第1の微細電極74と導電性材料25との接続を容易にし、薄膜トランジスタアレイ基板の全体の構成を簡素化することができる。

【0164】

なお、駆動用薄膜トランジスタ205においても、ゲート・チャネル一体形成部55は独立して加熱プロセスを経て形成される。つまり、導電性材料25、絶縁膜35及び薄膜半導体45は、フレキシブルな樹脂基板層64と一体化される作製プロセスの前に、ワイヤー15の上部に予め形成される。これらの各層の形成方法は、真空蒸着法やCVD法、スパッタ法、各種コーティング技術等により成膜した後、フォトリソグラフィー法によりパターニングする手法が一般的であるが、印刷技術などを用いて直接パターニングを行っても良い。

【0165】

また、実施形態5に係る薄膜トランジスタ204、205及び薄膜トランジスタアレイ基板は、図1に示した実施形態1に係る薄膜トランジスタ200及び薄膜トランジスタアレイ基板に対応しており、薄膜半導体44、45を形成したワイヤー14、15が樹脂基板層64の上部に設置され、かつ配線用ワイヤー114、115を樹脂基板層64の内部に形成した方式であるが、図2〜4に示した実施形態2〜4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板と対応させて、各々のワイヤーを上下のどの位置に設置しても、基本的に同じ効果を得ることができる。

【0166】

なお、ワイヤー14、15の太さは画素の精細度によって一般的には5μm〜500μm程度の範囲で自由に変えることが可能であるが、パターニングなどの加工処理を容易に行うためには10〜50μm程度の範囲であることが望ましい。また画素電極124もワイヤー74上に形成する場合、画素のサイズに応じて500μm以上のワイヤーを用いても良い。なお、大型のスクリーン型ディスプレイなどに応用する場合、ワイヤーに画素電極を形成しない場合においても500μm以上のワイヤーを用いることが有効である。

【0167】

また、実施形態1〜4に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板においては、2本のワイヤー10〜13、90〜93を上下の2段に配置したが、本実施形態に係る薄膜トランジスタ204、205及び薄膜トランジスタアレイ基板においては、ワイヤー14、15、114、115の種類に応じて何段に設置しても良く、その組み合わせは自由に設定することが可能である。またゲート・チャネル一体形成部54、55及び配線用ワイヤー114、115を樹脂基板層64と一体化する手法に関しては、図5〜図7で説明したあらゆる手法を適用することが可能である。

【0168】

図16においては、ワイヤー15上に薄膜半導体45のみ形成してあるが、画素電極124も薄膜半導体45とは別の部分に予め形成しておけば、画素のパターニングによる樹脂基板層64の変形などを抑制することができる。

【0169】

また、同じワイヤー14、15上に形成される薄膜半導体44、45は1画素につき1個である必要はなく、複数の種類かつ異なる形状の薄膜半導体44、45により画素を駆動することが可能である。例えば、ワイヤー上の絶縁膜上に選択用トランジスタの機能を有する薄膜半導体が形成され、さらに別の範囲の絶縁膜上に電極と絶縁膜を積層し、その上部に駆動用トランジスタの機能を示す薄膜半導体が形成されても良い。

【0170】

実施形態5に係る薄膜トランジスタ204、205及び薄膜トランジスタアレイ基板によれば、1画素に対応して画素選択用トランジスタと画素駆動用トランジスタの2個の薄膜トランジスタ204、205を設けることができ、有機EL等の画素駆動に2個のトランジスタを必要とするフレキシブル表示素子に適用することができる。

【0171】

〔実施形態6〕

図17は、本発明の実施形態6に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板の一例を示した図である。実施形態6においては、1つのワイヤー上に2個の薄膜トランジスタを形成した例を示す。

【0172】

図17において、実施形態6に係る薄膜トランジスタ206、207及び薄膜トランジスタアレイ基板は、選択用薄膜トランジスタ206と、駆動用薄膜トランジスタ207とを有する。

【0173】

選択用薄膜トランジスタ206は、ワイヤー16と、導電性材料26と、絶縁膜36と、薄膜半導体46と、第1の微細電極76と、第2の微細電極86とを備える。ここで、ワイヤー16、導電性材料26、絶縁膜36及び薄膜半導体46は、ゲート・チャネル一体形成部56を構成する。

【0174】

駆動用薄膜トランジスタ207は、ワイヤー16と、導電性材料27と、絶縁膜37と、薄膜半導体47と、第1の微細電極77と、第2の微細電極87とを備える。ここで、ワイヤー16、導電性材料27、絶縁膜37及び薄膜半導体47は、ゲート・チャネル一体形成部57を構成する。

【0175】

また、選択用薄膜トランジスタ206の第2の微細電極86は配線用ワイヤー116に接続され、第1の微細電極76は駆動用薄膜トランジスタ207の導電性材料27に接続されている。ここで、配線用ワイヤー116は、ワイヤー96の周囲に導電性材料106が被覆されて構成されている。

【0176】

同様に、駆動用薄膜トランジスタ207の第2の微細電極87は配線用ワイヤー117に接続され、第1の微細電極77は画素電極126に接続されている。なお、配線用ワイヤー117は、ワイヤー97の周囲に導電性材料107が被覆されて構成されている。

【0177】

実施形態6に係る薄膜トランジスタ206、207及び薄膜トランジスタ基板においては、1つの幅が広い共通のワイヤー16の表面上の一部に、ライン状に形成された導電性材料26と絶縁膜36が積層され、その上に選択用トランジスタとして機能する薄膜半導体46が形成されている。また、ワイヤー16の別の領域に、島状に導電性材料27と絶縁膜37を積層し、その上に駆動用トランジスタとして機能する薄膜半導体47が形成されている。このように、1つのワイヤー16上に、2つの薄膜トランジスタ206、207を形成するようにしてもよい。非導電性の材料からなり、2つの導電性材料26、27が配置可能な十分な幅のワイヤー16を用いることにより、選択用薄膜トランジスタ206と駆動用薄膜トランジスタ207を2列に並べて配置形成することができる。

【0178】

実施形態6に係る薄膜トランジスタ206、207においては、ゲート・チャネル一体形成部56、57同士が更に一体形成された構成となる。ゲート・チャネル一体形成部56、57は、実施形態1〜5と同様に、樹脂基板層66とは別個に独立して形成可能であり、樹脂基板層66の形成後に表面上に設置することができる。よって、ゲート・チャネル一体形成部56、57は加熱プロセスで十分に加熱加工した後、樹脂基板層66と一体化することができ、樹脂基板層66の変形を防止することができる。

【0179】

なお、図17では、画素電極126は樹脂基板66上に形成された構成が示されているが、画素電極126を同じワイヤー16上に形成しても良い。

【0180】

また、実施形態1〜6に係る薄膜トランジスタ200〜207及び薄膜トランジスタアレイ基板において、ワイヤー10〜16、110〜117は1本である必要はなく、例えば複数本のワイヤーを束ねて1組のワイヤーとして扱うことができる。その際、異なる材質・形状のワイヤーを組み合わせることも可能である。

【0181】

また、上述の複数のワイヤーを束ねる方法としては、熱硬化性樹脂や光硬化性樹脂などで固める方法や、各々のワイヤーを互いに巻きつける方法などを用いることができる。熱硬化性樹脂や光硬化性樹脂で硬化させる手法を用いる場合には、樹脂の伸縮の影響を抑制するため、ワイヤーを左右から適切な力で引っ張った状態で樹脂を硬化させる手法が効果的である。

【0182】

なお、実施形態1〜6に係る薄膜トランジスタ200〜207及び薄膜トランジスタアレイ基板は、基本的な配線パターンを示したものであって、配線の方向や形状はこれらに限定されるものではなく、自由に設定して良い。また薄膜半導体40〜47上の微細電極70〜77、80〜87も同様に自由に設定して良く、例えばトランジスタのソース・ドレイン電極を櫛形状にするなどあらゆるパターンを適用することが可能である。

【0183】

上述の薄膜トランジスタアレイ基板又はバックプレーンを用いて作製するフレキシブル表示素子は、液晶、有機EL、無機EL、電子インク、電子粉流体など、種々の表示方式で従来用いられる全ての構造を導入することが可能であり、液晶ディスプレイにおいては、例えば配向膜やスペーサー、対抗電極、液晶層、バックライト、偏光板、カラーフィルター、ブラックマトリクス、絶減膜などが挙げられるが、勿論これらに限定されるものではない。

【0184】

また、本実施形態に係るフレキシブル表示素子を用いた表示装置としては、テレビ、パソコン、携帯電話、電子ペーパー、タッチパネル、各種機器に取り付けられた表示モニターなどが挙げられるが、これらに限定されるものではなく、全ての表示装置が含まれる。

【0185】

〔実施例〕

本発明の実施例として、絶縁膜と薄膜トランジスタを形成した導電性ワイヤーを樹脂基板と一体化形成した、フレキシブル表示素子のバックプレーン部分の一部を作製した結果について示す。作製方法は以下の通りである。

【0186】

まず、表面に約2.5μm厚の黄銅がメッキ処理された50μmのピアノ線から成る導電性ワイヤーをガラス板(170mm×110mm)上に配置し、ワイヤー両端をテープにより固定した。その表面に、フッ素樹脂を主成分とする溶液をディッピングし、120〜170℃で加熱してフッ素樹脂を硬化させて導電性膜の周囲に絶縁層を形成した。更に、ワイヤー上にマスクを介してスパッタ装置のホルダーに固定し、50μm厚の酸化物半導体(InGaZnO)をスパッタリング法により成膜した。その後、酸化物半導体を形成した導電性ワイヤー、及び上述の導電性ワイヤーの両端を金属棒に固定し、それらを箱型のプラスティック容器内に固定した。そこにシリコーン樹脂(PDMS)材料を流し込み、100℃以下に加熱して樹脂を硬化させた。

【0187】

以上の方法により作製した、導電性ワイヤーを埋め込んだ樹脂基板を湾曲させたところ、ワイヤーの断線無く丸められることが可能であることが確認された。

【0188】

以上説明したように、本発明の実施形態及び実施例に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板によれば、絶縁膜と薄膜トランジスタを形成した導電性ワイヤーを形成し、基板となる樹脂と一体化する工程を導入することにより、柔軟な基板を用いても配線不良の少ない大面積のフレキシブル表示素子を提供することができる。従って、本発明に係る薄膜トランジスタ及び薄膜トランジスタアレイ基板を適用すれば、自由に丸めて持ち運べる巻物型のディスプレイや、プロジェクターが不要なスクリーン型の大型ディスプレイなど、種々の新しいディスプレイの実現が期待できる。

【0189】

以上、本発明の好ましい実施形態について詳説したが、本発明は、上述した実施形態に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施形態に種々の変形及び置換を加えることができる。

【産業上の利用可能性】

【0190】

本発明は、液晶ディスプレイ、有機ELディスプレイ等を含むフレキシブルディスプレイに利用することができ、特に、大画面のフレキシブルデシィスプレイに利用することができる。

【符号の説明】

【0191】

10〜16、90〜97 ワイヤー

20〜27、100〜107 導電性材料

30〜37 絶縁膜

40〜47 薄膜半導体

50〜57 ゲート・チャネル一体形成部

60〜67 樹脂基板