薄膜トランジスタおよびその製造方法

【課題】 半導体材料の過剰な消費を抑制でき、適量な半導体材料にて製造が可能であるとともに、ソース電極とドレイン電極の間のリーク電流を抑制することができる薄膜トランジスタの提供。

【解決手段】本発明の薄膜トランジスタは、絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなる薄膜トランジスタであって、前記ドレイン電極の膜厚が1μm以上である。

【解決手段】本発明の薄膜トランジスタは、絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなる薄膜トランジスタであって、前記ドレイン電極の膜厚が1μm以上である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタに係り、特に論理回路等に使用される薄膜トランジスタに関する。

【背景技術】

【0002】

半導体自体を基板としたトランジスタや集積回路などの技術を基礎として、ガラス基板上にアモルファスシリコンやポリシリコンなどを成膜した薄膜トランジスタ(TFT)が製造され、画像表示素子やその駆動回路等に応用されている。このような薄膜トランジスタにおいては、アモルファスシリコン等を400〜500度程度の比較的低い成膜温度で成膜できることにより、基板として石英よりも融点の低い安価なガラスが使用されている。

また、電子ペーパーやRFIDタグなどに対応させるため、フレキシブル化、低コスト化、さらに軽量化などの観点から、電子回路を形成する薄膜トランジスタをフレキシブル基板上に形成する、有機半導体を用いたデバイスの開発が行われている。

この有機半導体を用いた薄膜トランジスタにおいては、成膜温度を室温から200度程度に低減できることから、プラスチック基板を用いた薄膜トランジスタが製造可能になり、軽量かつフレキシブルな論理回路の製造が期待されている。

【0003】

例えば、図8に示すように、プラスチックからなる基板1の上面に長方形状のゲート電極2が形成され、その上にゲート絶縁膜3を挟んでソース電極4およびドレイン電極5が形成され、さらにその上に有機半導体6が形成された薄膜トランジスタ40が知られている。この薄膜トランジスタ40は、プラスチック基板1の上面に順にゲート電極2、ゲート絶縁膜3、長方形状のソース電極4およびドレイン電極5を形成した後、ソース電極4とドレイン電極5を接続するように有機半導体6をディスペンサ等で塗布して形成されるものである。

【0004】

一般に、有機半導体をデバイスの構成として用いる場合、液体でのプロセスが可能となるため、大面積化、印刷法の適用、さらにプラスチック基板の利用が可能となり、フレキシブル化、低コスト化及び軽量化の目的を達成できる利点がある(例えば、非特許文献1参照)。また、低コスト化やフレキシブル化を実現する上においては、半導体のみでなく、ゲート電極、ソース電極、ドレイン電極やゲート絶縁膜も印刷法などにより形成されることが望ましい。

また、印刷法を用いた電極の形成においては、導電性高分子や金属コロイド溶液などを用いた電極パターンの形成に関する開発も行われている(非特許文献2参照)。

【0005】

ところで、上記の薄膜トランジスタ40においては、対向するソース電極4とドレイン電極5の間にディスペンサ等で有機半導体6を塗布した場合、有機半導体6がソース電極4とドレイン電極5の間から流れ出すことにより、有機半導体6を過剰に消費してしまう虞があった。また、ソース電極4とドレイン電極5の間から流出した有機半導体6が、ゲート電極2の存在しない領域にまで拡散することによって、ソース電極4とドレイン電極5の間のリーク電流(off電流)を増大させる虞もあった。

【非特許文献1】Science vo1.265、1684(1994)

【非特許文献2】Thin Solid Films Vol.279、438(2003)

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、上記事情に鑑みてなされたものであって、半導体材料の過剰な消費を抑制でき、適量な半導体材料にて製造が可能であるとともに、ソース電極とドレイン電極の間のリーク電流を抑制することができる薄膜トランジスタを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記の目的を達成するために、本発明は以下の構成を採用した。

本発明の薄膜トランジスタは、絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなる薄膜トランジスタであって、前記ドレイン電極の膜厚が1μm以上であることを特徴とする。

【0008】

かかる構成によれば、半導体材料が塗布される領域の周囲がドレイン電極によって囲われているため、ソース電極とドレイン電極の間に半導体材料を塗布した際に、ドレイン電極の外側に半導体材料が溢れ出していくことをドレイン電極が防止する。これにより、半導体材料の過剰な消費を抑制でき、適量な半導体材料にて製造が可能であるとともに、ソース電極とドレイン電極の間のリーク電流を抑制することができる

【0009】

本発明の薄膜トランジスタは、前記ソース電極が円形状であり、前記ゲート電極および前記ドレイン電極が等幅リング状であり、前記ソース電極と前記ゲート電極と前記ドレイン電極の中心位置が略一致していることを特徴とする。

かかる構成によれば、上記と同様の効果に加え、ソース電極とドレイン電極の間に等幅リング状のチャネル領域が形成されるので、塗布された半導体材料を容易にチャネル領域に流入させることができる。

【0010】

本発明の薄膜トランジスタは、前記半導体層が、有機半導体からなることを特徴とする。

かかる構成によれば、半導体材料をチャネル領域に容易に塗布することができる。また、安価な印刷法を使用することが可能になる。

【0011】

本発明の薄膜トランジスタの製造方法は、絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなり、前記ドレイン電極の膜厚が1μm以上である薄膜トランジスタを製造する方法であって、前記ソース電極および前記ドレイン電極を形成する工程が少なくともスクリーン印刷工程を含み、前記半導体層を形成する工程が少なくともディスペンサ工程またはインクジェット工程を含むことを特徴とする。

かかる方法によれば、リーク電流が少ない薄膜トランジスタを製造することができる。また、印刷方法を採用すれば必要な部分にのみ電極を形成することができるので、製造工程が大幅に削減され、大量に安価に製造することが可能となる。

【0012】

本発明の薄膜トランジスタの製造方法は、前記膜厚が1μm以上のドレイン電極を隔壁として、ディスペンサ工程またはインクジェット工程で形成する半導体層のドレイン電極外への漏れ出しを防止しつつ半導体層をドレイン電極の内側に形成することを特徴とする。

かかる方法によっても、上記と同様の効果が得られる。

【発明の効果】

【0013】

以上に説明したように、本発明の薄膜トランジスタによれば、半導体材料が塗布される領域の周囲がドレイン電極によって囲われているため、ソース電極とドレイン電極の間に有機半導体を塗布した際に、ドレイン電極の外側に半導体材料が溢れ出していくことをドレイン電極が防止する。これにより、半導体材料の過剰な消費を抑制でき、適量な半導体材料にて製造が可能であるとともに、ソース電極とドレイン電極の間のリーク電流を抑制することができる。また、ソース電極とドレイン電極の間に等幅リング状のチャネル領域が形成されるので、塗布された半導体材料が容易にチャネル領域に流入することができる。

また、本発明の薄膜トランジスタの製造方法によれば、リーク電流が少ない薄膜トランジスタを製造することができる。また、印刷方法を採用すれば必要な部分にのみ電極を形成することができるので、製造工程が大幅に削減され、大量に安価に製造することが可能となる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態について図面を参照して説明するが、本発明はこれらに限定されるものではない。

【0015】

(第1の実施形態)

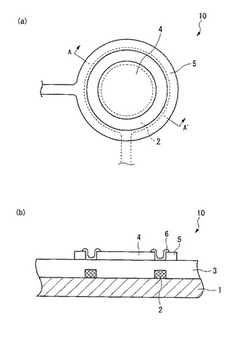

図1(a)は第1の実施形態に係る薄膜トランジスタの平面図、図1(b)は図1(a)のA−A´の断面図、図2(a)〜(d)は製造工程を示す断面図である。

第1の実施形態の薄膜トランジスタ10は、絶縁基板1の上面にゲート電極2が形成され、絶縁基板1とゲート電極2がゲート絶縁膜3で覆われている。ゲート絶縁膜3の上面には、ソース電極4およびドレイン電極5が形成され、ソース電極4とドレイン電極5の間隙が半導体層6で覆われている。

【0016】

絶縁基板1としては、一般的なプラスチック材料を用いることができ、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルスルフォン(PES)、ポリイミド(PI)、ポリエーテルイミド(PEI)、ポリスチレン(PS)、ポリ塩化ビニル(PVC)、ポリエチレン(PE)、ポリプロピレン(PP)、ナイロン等が好適に使用できる。ゲート電極2は、絶縁基板1の上面に、等幅リング状に形成されている。ゲート電極2としては、Al、Cr、Au、Ag、Cu、Ti、Ni等の金属や、ITO等の透明電極が使用できる。ゲート絶縁層3は、絶縁基板1およびゲート電極2を覆うように形成されている。ゲート絶縁層3としては、SiO2、Al2O3、SiN等の無機物や、ポリビニルフェノール、エポキシ、ポリイミド等の有機物を用いることができる。

【0017】

ソース電極4は、ゲート絶縁膜3の上面に円形状に形成されている。ソース電極4の外径は、ゲート電極2の内径より若干大きく形成され、平面視的配置において、ソース電極4の外周部がゲート電極2の内周部に若干重なるように配置されている。ドレイン電極5は、ゲート絶縁膜3の上面であって、ソース電極4と離間してソース電極を囲うように等幅リング状に形成されている。ドレイン電極5の内径は、ゲート電極2の外径より若干小さく形成され、平面視的配置において、ドレイン電極5の内周部がゲート電極2の内周部に若干重なるように配置されている。ゲート電極2とソース電極4とドレイン電極5の中心位置は、ほぼ一致するように配置されている。ソース電極4およびドレイン電極5は、AgペーストやNiペーストなどの導電性ペーストをスクリーン印刷および焼成によって形成される。ゲート絶縁膜3の上面のソース電極4とドレイン電極5によって挟まれた領域には、等幅リング状の間隙が形成される。

【0018】

半導体層6としては、有機半導体を用いることができ、ポリチオフェン誘導体、ポリフェニレンビニレン誘導体、ポリチエニレンビニレン誘導体、ポリアリルアミン誘導体、ポリアセチレン誘導体、アセン誘導体、オリゴチオフェン誘導体等を好適に用いることができる。半導体層6は、ソース電極4の外壁とドレイン電極5によって形成された間隙にこれらの原料の塗布および焼成によって形成される。

【0019】

(第2の実施形態)

図4(a)は第2の実施形態に係る薄膜トランジスタの平面図、図4(b)は図4(a)のA−A´の断面図、である。

第2の実施形態の薄膜トランジスタ20は、第1の実施形態と略同一の構成を有しており、同様の工程にて形成されるが、半導体層6が形成される領域が異なる。すなわち、半導体層6は、ソース電極4の外壁とドレイン電極5の内壁との間に形成されるとともに、ソース電極4を覆うように形成されている。半導体層6を形成する際には、半導体材料をソース電極4の中心位置に塗布する。塗布された半導体材料はソース電極上において流動していき、ソース電極4とドレイン電極5によって形成された間隙に流入する。流入した半導体材料は、等幅リング状に形成されている間隙内でチャネルを形成する。

【0020】

(第3の実施形態)

図5(a)は第3の実施形態に係る薄膜トランジスタの平面図、図5(b)は図5(a)のA−A´の断面図、図2(a)〜(d)および図3(a)〜(d)は製造工程を示す断面図である。

第3の実施形態の薄膜トランジスタ30は、第1の実施形態の薄膜トランジスタに加えて、層間絶縁層7、ビアホール9、ソース配線8が形成されている。第3の実施形態の薄膜トランジスタ30は、第1の実施形態の薄膜トランジスタのソース電極4、ドレイン電極5、半導体層6を覆うように、層間絶縁層7が形成されている。層間絶縁膜7としては、エポキシ、ポリイミド等の有機物を使用することができる。層間絶縁層7には、ソース電極4の上部の位置にビアホール9が形成されている。層間絶縁層7の上面には、ソース配線8が形成され、ビアホール9を介してソース電極4に接続されている。ソース配線8としてはAgペースト、Niペーストや、Al、ITO等が好適に用いられる。

【0021】

上記の第1〜第3の実施形態において、ドレイン電極5は閉ループに形成されており、その高さ(膜厚)は、1μm〜50μmであることが好ましい。さらに好ましくは、5μm〜20μmである。ドレイン電極5の高さ(膜厚)が1μm未満では、ディスペンサやインクジェットあるいはそれに類する方法によって塗布された半導体材料がドレイン電極5の上面を超えて外部に流出して過剰な材料の消費が起こる。また、ドレイン電極5の高さが50μmを超えると、1回の工程でソース電極4およびドレイン電極5を精度良く形成するのが困難になる。また、その上に層間絶縁膜7を形成するのが困難になる。

【0022】

ソース電極4およびドレイン電極5を1回の工程で作製するには、ソース電極4およびドレイン電極5をスクリーン印刷で形成する方法が好適に用いられる。スクリーン印刷によれば、1μm〜50μmの膜厚のソース電極4およびドレイン電極5を形成することが可能である。特に、膜厚が5μm〜20μmの範囲になるように形成する場合には、通常のスクリーン版および通常のインクによって容易に作製できる。また、膜厚を5μm未満にするためには、スクリーン版の乳剤厚を薄くし、かつインクの濃度を薄めることが好ましい。また、膜厚が20μmを超えるようにするためには、スクリーン版の乳剤厚を厚くするか、またはインクの濃度を高めることが好ましい。

【0023】

半導体材料でチャネル領域を形成するには、ディスペンサやインクジェットやそれに類する方法によって半導体材料を間隙の一部に塗布する。図6(a)に示すように、×印で示された位置に塗布された半導体材料は、間隙内において全領域に流動していき、均一な層を形成する。これにより、ソース電極4とドレイン電極5の間にチャネル領域が形成される。

ところが、ドレイン電極の高さが1μm未満の場合、図6(b)に示すように半導体材料はドレイン電極5から溢れ出し、他の領域の電極(例えば、ドレイン電極5’)と連結してしまうので好ましくない。

【0024】

また、ゲート電極2を閉ループに形成することにより、ソース電極4およびドレイン電極5の間の電流経路を完全に遮断でき、off電流を低減できる。また、ソース電極4およびドレイン電極5を形成する版の形状としては、例えば、図7(a)、(b)に示すように、四角形状や円形状の版を用いることができる。

尚、ソース電極4やドレイン電極5の角部の曲率や幅によってチャネル長が大きく変化すると、特性のばらつきが生じることがあり、好ましくない。そのため、ソース電極4とドレイン電極5の間隔(チャネル長)を一定に保つことが望ましく、ソース電極4およびドレイン電極5を形成する版としては円形状の版を用いることが好ましい。特に、ソース電極4が円形、ドレイン電極5が等幅リング形状であり、それらの中心が一致するようにソース電極およびドレイン電極を形成することにより、より高精度にチャネル長を均一にすることができる。

【実施例】

【0025】

(実施例1)

本発明の薄膜トランジスタを製造する場合の実施例1について、図2と図3を用いて説明する。

基板1として、厚さ125μmのポリエチレンナフタレート(PEN)を準備し、Alをスパッタ成膜、フォトリソおよびエッチングによって等幅リング状のゲート電極2を形成した(図2(a))。ゲート電極2の厚さは100nm、内径は200μm、外径は400μmとした。ポリビニルフェノール溶液をスピンコートし、焼成してゲート絶縁膜3を形成した。(図2(b))。ゲート絶縁膜の膜厚は1μmとした。ソース電極4およびドレイン電極5として、Agペーストをスクリーン印刷によって形成した(図2(c))。ソース電極4の厚さは10μm、円の直径は250μmとした。ドレイン電極5の厚さは10μm、内径は350μm、外径は450μmとして等幅リング状に形成した。このようにソース電極4とドレイン電極5を形成したことにより、ソース電極4とドレイン電極5の間には、幅が50μmの等幅リング状の間隙が形成されたことになる。

【0026】

次に、等幅リング状の間隙に適量のポリチオフェン溶液をディスペンサによって塗布した。厚さ10μmのソース電極4およびドレイン電極5が堤防の役割を果たし、間隙のみに効率よく塗布された。その後、ポリチオフェン溶液を焼成することによって半導体層6とした(図2(d))。層間絶縁膜7としてエポキシを塗布および焼成により形成した(図3(a))。層間絶縁膜7の厚さは100μmとした。UV−YAGレーザによって層間絶縁膜7に直径50μmのビアホール用の穴9Aを形成し(図3(b))、ドクターブレードによって穴9AにAgペーストを埋め込み、焼成を行ってビアホール9とした(図3(c))。尚、試料の表面を軽く削って平らにした。最後に、ソース配線8としてAgペーストを印刷および焼成した(図3(d))。このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて10pAであった。

【0027】

(実施例2)

ポリチオフェン溶液の塗布をソース電極4の上面の中心位置に合わせて行った以外は、実施例1と同様の工程によって、薄膜トランジスタを作成した。

このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて10pAであった。

【0028】

(実施例3〜7)

実施例2と同様の工程によって、薄膜トランジスタを作成した。ただし、ソース電極4とドレイン電極5の厚さを、1、5、20、50、60μmとした。

このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、表1に示すような結果になった。

【0029】

【表1】

【0030】

(比較例1)

図8(a)および(b)を用いて、比較例1について説明する。

絶縁基板1として、厚さが125μmのポリエチレンナフタレート(PEN)を準備し、Alをスパッタ成膜、フォトリソおよびエッチングによって長方形状のゲート電極2を形成した。ゲート電極2の厚さは100nm、縦長は1.1mm、横長は100μmとした。次に、ポリビニルフェノール溶液をスピンコートし、焼成してゲート絶縁膜3を形成した。ゲート絶縁膜3の膜厚は1μmとした。次に、長方形のソース電極4とドレイン電極5(ただし、引き出し電極を有する)とをAgペーストをスクリーン印刷することによって形成した。尚、平面視的配置において、ソース電極4およびドレイン電極5の一部がゲート電極に重なるように形成されている。ソース電極4およびドレイン電極5の厚さは10μmとし、長辺は1mm、短辺は100μmとした。対向したソース電極4とドレイン電極5の間には、幅が50μmの間隙が形成された。

【0031】

次に、上述の間隙に適量のポリチオフェン溶液をディスペンサによって塗布した。ポリチオフェン溶液は、ソース電極4およびドレイン電極5の間に流入し、ソース電極4とドレイン電極5の長辺の端部から流出した。その後、ポリチオフェン溶液を焼成することによって半導体層6とした。このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて1nAであった。

【0032】

(比較例2)

比較例として、ソース電極とドレイン電極をCrおよびAuの蒸着およびフォトリソ、エッチングにて0.5μmの厚さに形成した以外は、実施例2と同様の工程で作成した薄膜トランジスタを作成した。ただし、半導体層溶液はドレイン外部に流出し、他の電極にも到達した。

このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて−Id=10pAであったが、他の電極を0Vに接続すると1nAに増大した。

【0033】

以上に示したように、半導体材料が塗布される領域の周囲がドレイン電極によって囲われているため、ソース電極上あるいはソース電極とドレイン電極の間に半導体材料を塗布した際に、ドレイン電極の外側に半導体材料が溢れ出していくことをドレイン電極によって防止できた。すなわち、ドレイン電極が堤防として作用することが分かった。また、ソース電極とドレイン電極の間のリーク電流を抑制することができた。

【図面の簡単な説明】

【0034】

【図1】本発明の薄膜トランジスタの第1の実施形態を示す図であり、(a)は平面図、(b)は(a)のA−A’の断面図である。

【図2】本発明の薄膜トランジスタの製造工程を示す図である。

【図3】本発明の薄膜トランジスタの製造工程を示す図である。

【図4】本発明の薄膜トランジスタの第2の実施形態を示す図であり、(a)は平面図、(b)は(a)のA−A’の断面図である。

【図5】本発明の薄膜トランジスタの第3の実施形態を示す図であり、(a)は平面図、(b)は(a)のA−A’の断面図である。

【図6】半導体材料の流動状態を示す図である。

【図7】ソース電極およびドレイン電極の形状を示す図である。

【図8】従来の薄膜トランジスタを示す図であり、(a)は平面図、(b)は断面図である。

【符号の説明】

【0035】

1・・・絶縁基板、2・・・ゲート電極、3・・・ゲート絶縁膜、4・・・ソース電極、5・・・ドレイン電極、5’・・・他の電極、6・・・半導体層、7・・・層間絶縁層、8・・・ソース配線、9・・・ビアホール、10,20,30,40・・・薄膜トランジスタ

【技術分野】

【0001】

本発明は、薄膜トランジスタに係り、特に論理回路等に使用される薄膜トランジスタに関する。

【背景技術】

【0002】

半導体自体を基板としたトランジスタや集積回路などの技術を基礎として、ガラス基板上にアモルファスシリコンやポリシリコンなどを成膜した薄膜トランジスタ(TFT)が製造され、画像表示素子やその駆動回路等に応用されている。このような薄膜トランジスタにおいては、アモルファスシリコン等を400〜500度程度の比較的低い成膜温度で成膜できることにより、基板として石英よりも融点の低い安価なガラスが使用されている。

また、電子ペーパーやRFIDタグなどに対応させるため、フレキシブル化、低コスト化、さらに軽量化などの観点から、電子回路を形成する薄膜トランジスタをフレキシブル基板上に形成する、有機半導体を用いたデバイスの開発が行われている。

この有機半導体を用いた薄膜トランジスタにおいては、成膜温度を室温から200度程度に低減できることから、プラスチック基板を用いた薄膜トランジスタが製造可能になり、軽量かつフレキシブルな論理回路の製造が期待されている。

【0003】

例えば、図8に示すように、プラスチックからなる基板1の上面に長方形状のゲート電極2が形成され、その上にゲート絶縁膜3を挟んでソース電極4およびドレイン電極5が形成され、さらにその上に有機半導体6が形成された薄膜トランジスタ40が知られている。この薄膜トランジスタ40は、プラスチック基板1の上面に順にゲート電極2、ゲート絶縁膜3、長方形状のソース電極4およびドレイン電極5を形成した後、ソース電極4とドレイン電極5を接続するように有機半導体6をディスペンサ等で塗布して形成されるものである。

【0004】

一般に、有機半導体をデバイスの構成として用いる場合、液体でのプロセスが可能となるため、大面積化、印刷法の適用、さらにプラスチック基板の利用が可能となり、フレキシブル化、低コスト化及び軽量化の目的を達成できる利点がある(例えば、非特許文献1参照)。また、低コスト化やフレキシブル化を実現する上においては、半導体のみでなく、ゲート電極、ソース電極、ドレイン電極やゲート絶縁膜も印刷法などにより形成されることが望ましい。

また、印刷法を用いた電極の形成においては、導電性高分子や金属コロイド溶液などを用いた電極パターンの形成に関する開発も行われている(非特許文献2参照)。

【0005】

ところで、上記の薄膜トランジスタ40においては、対向するソース電極4とドレイン電極5の間にディスペンサ等で有機半導体6を塗布した場合、有機半導体6がソース電極4とドレイン電極5の間から流れ出すことにより、有機半導体6を過剰に消費してしまう虞があった。また、ソース電極4とドレイン電極5の間から流出した有機半導体6が、ゲート電極2の存在しない領域にまで拡散することによって、ソース電極4とドレイン電極5の間のリーク電流(off電流)を増大させる虞もあった。

【非特許文献1】Science vo1.265、1684(1994)

【非特許文献2】Thin Solid Films Vol.279、438(2003)

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、上記事情に鑑みてなされたものであって、半導体材料の過剰な消費を抑制でき、適量な半導体材料にて製造が可能であるとともに、ソース電極とドレイン電極の間のリーク電流を抑制することができる薄膜トランジスタを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記の目的を達成するために、本発明は以下の構成を採用した。

本発明の薄膜トランジスタは、絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなる薄膜トランジスタであって、前記ドレイン電極の膜厚が1μm以上であることを特徴とする。

【0008】

かかる構成によれば、半導体材料が塗布される領域の周囲がドレイン電極によって囲われているため、ソース電極とドレイン電極の間に半導体材料を塗布した際に、ドレイン電極の外側に半導体材料が溢れ出していくことをドレイン電極が防止する。これにより、半導体材料の過剰な消費を抑制でき、適量な半導体材料にて製造が可能であるとともに、ソース電極とドレイン電極の間のリーク電流を抑制することができる

【0009】

本発明の薄膜トランジスタは、前記ソース電極が円形状であり、前記ゲート電極および前記ドレイン電極が等幅リング状であり、前記ソース電極と前記ゲート電極と前記ドレイン電極の中心位置が略一致していることを特徴とする。

かかる構成によれば、上記と同様の効果に加え、ソース電極とドレイン電極の間に等幅リング状のチャネル領域が形成されるので、塗布された半導体材料を容易にチャネル領域に流入させることができる。

【0010】

本発明の薄膜トランジスタは、前記半導体層が、有機半導体からなることを特徴とする。

かかる構成によれば、半導体材料をチャネル領域に容易に塗布することができる。また、安価な印刷法を使用することが可能になる。

【0011】

本発明の薄膜トランジスタの製造方法は、絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなり、前記ドレイン電極の膜厚が1μm以上である薄膜トランジスタを製造する方法であって、前記ソース電極および前記ドレイン電極を形成する工程が少なくともスクリーン印刷工程を含み、前記半導体層を形成する工程が少なくともディスペンサ工程またはインクジェット工程を含むことを特徴とする。

かかる方法によれば、リーク電流が少ない薄膜トランジスタを製造することができる。また、印刷方法を採用すれば必要な部分にのみ電極を形成することができるので、製造工程が大幅に削減され、大量に安価に製造することが可能となる。

【0012】

本発明の薄膜トランジスタの製造方法は、前記膜厚が1μm以上のドレイン電極を隔壁として、ディスペンサ工程またはインクジェット工程で形成する半導体層のドレイン電極外への漏れ出しを防止しつつ半導体層をドレイン電極の内側に形成することを特徴とする。

かかる方法によっても、上記と同様の効果が得られる。

【発明の効果】

【0013】

以上に説明したように、本発明の薄膜トランジスタによれば、半導体材料が塗布される領域の周囲がドレイン電極によって囲われているため、ソース電極とドレイン電極の間に有機半導体を塗布した際に、ドレイン電極の外側に半導体材料が溢れ出していくことをドレイン電極が防止する。これにより、半導体材料の過剰な消費を抑制でき、適量な半導体材料にて製造が可能であるとともに、ソース電極とドレイン電極の間のリーク電流を抑制することができる。また、ソース電極とドレイン電極の間に等幅リング状のチャネル領域が形成されるので、塗布された半導体材料が容易にチャネル領域に流入することができる。

また、本発明の薄膜トランジスタの製造方法によれば、リーク電流が少ない薄膜トランジスタを製造することができる。また、印刷方法を採用すれば必要な部分にのみ電極を形成することができるので、製造工程が大幅に削減され、大量に安価に製造することが可能となる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態について図面を参照して説明するが、本発明はこれらに限定されるものではない。

【0015】

(第1の実施形態)

図1(a)は第1の実施形態に係る薄膜トランジスタの平面図、図1(b)は図1(a)のA−A´の断面図、図2(a)〜(d)は製造工程を示す断面図である。

第1の実施形態の薄膜トランジスタ10は、絶縁基板1の上面にゲート電極2が形成され、絶縁基板1とゲート電極2がゲート絶縁膜3で覆われている。ゲート絶縁膜3の上面には、ソース電極4およびドレイン電極5が形成され、ソース電極4とドレイン電極5の間隙が半導体層6で覆われている。

【0016】

絶縁基板1としては、一般的なプラスチック材料を用いることができ、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルスルフォン(PES)、ポリイミド(PI)、ポリエーテルイミド(PEI)、ポリスチレン(PS)、ポリ塩化ビニル(PVC)、ポリエチレン(PE)、ポリプロピレン(PP)、ナイロン等が好適に使用できる。ゲート電極2は、絶縁基板1の上面に、等幅リング状に形成されている。ゲート電極2としては、Al、Cr、Au、Ag、Cu、Ti、Ni等の金属や、ITO等の透明電極が使用できる。ゲート絶縁層3は、絶縁基板1およびゲート電極2を覆うように形成されている。ゲート絶縁層3としては、SiO2、Al2O3、SiN等の無機物や、ポリビニルフェノール、エポキシ、ポリイミド等の有機物を用いることができる。

【0017】

ソース電極4は、ゲート絶縁膜3の上面に円形状に形成されている。ソース電極4の外径は、ゲート電極2の内径より若干大きく形成され、平面視的配置において、ソース電極4の外周部がゲート電極2の内周部に若干重なるように配置されている。ドレイン電極5は、ゲート絶縁膜3の上面であって、ソース電極4と離間してソース電極を囲うように等幅リング状に形成されている。ドレイン電極5の内径は、ゲート電極2の外径より若干小さく形成され、平面視的配置において、ドレイン電極5の内周部がゲート電極2の内周部に若干重なるように配置されている。ゲート電極2とソース電極4とドレイン電極5の中心位置は、ほぼ一致するように配置されている。ソース電極4およびドレイン電極5は、AgペーストやNiペーストなどの導電性ペーストをスクリーン印刷および焼成によって形成される。ゲート絶縁膜3の上面のソース電極4とドレイン電極5によって挟まれた領域には、等幅リング状の間隙が形成される。

【0018】

半導体層6としては、有機半導体を用いることができ、ポリチオフェン誘導体、ポリフェニレンビニレン誘導体、ポリチエニレンビニレン誘導体、ポリアリルアミン誘導体、ポリアセチレン誘導体、アセン誘導体、オリゴチオフェン誘導体等を好適に用いることができる。半導体層6は、ソース電極4の外壁とドレイン電極5によって形成された間隙にこれらの原料の塗布および焼成によって形成される。

【0019】

(第2の実施形態)

図4(a)は第2の実施形態に係る薄膜トランジスタの平面図、図4(b)は図4(a)のA−A´の断面図、である。

第2の実施形態の薄膜トランジスタ20は、第1の実施形態と略同一の構成を有しており、同様の工程にて形成されるが、半導体層6が形成される領域が異なる。すなわち、半導体層6は、ソース電極4の外壁とドレイン電極5の内壁との間に形成されるとともに、ソース電極4を覆うように形成されている。半導体層6を形成する際には、半導体材料をソース電極4の中心位置に塗布する。塗布された半導体材料はソース電極上において流動していき、ソース電極4とドレイン電極5によって形成された間隙に流入する。流入した半導体材料は、等幅リング状に形成されている間隙内でチャネルを形成する。

【0020】

(第3の実施形態)

図5(a)は第3の実施形態に係る薄膜トランジスタの平面図、図5(b)は図5(a)のA−A´の断面図、図2(a)〜(d)および図3(a)〜(d)は製造工程を示す断面図である。

第3の実施形態の薄膜トランジスタ30は、第1の実施形態の薄膜トランジスタに加えて、層間絶縁層7、ビアホール9、ソース配線8が形成されている。第3の実施形態の薄膜トランジスタ30は、第1の実施形態の薄膜トランジスタのソース電極4、ドレイン電極5、半導体層6を覆うように、層間絶縁層7が形成されている。層間絶縁膜7としては、エポキシ、ポリイミド等の有機物を使用することができる。層間絶縁層7には、ソース電極4の上部の位置にビアホール9が形成されている。層間絶縁層7の上面には、ソース配線8が形成され、ビアホール9を介してソース電極4に接続されている。ソース配線8としてはAgペースト、Niペーストや、Al、ITO等が好適に用いられる。

【0021】

上記の第1〜第3の実施形態において、ドレイン電極5は閉ループに形成されており、その高さ(膜厚)は、1μm〜50μmであることが好ましい。さらに好ましくは、5μm〜20μmである。ドレイン電極5の高さ(膜厚)が1μm未満では、ディスペンサやインクジェットあるいはそれに類する方法によって塗布された半導体材料がドレイン電極5の上面を超えて外部に流出して過剰な材料の消費が起こる。また、ドレイン電極5の高さが50μmを超えると、1回の工程でソース電極4およびドレイン電極5を精度良く形成するのが困難になる。また、その上に層間絶縁膜7を形成するのが困難になる。

【0022】

ソース電極4およびドレイン電極5を1回の工程で作製するには、ソース電極4およびドレイン電極5をスクリーン印刷で形成する方法が好適に用いられる。スクリーン印刷によれば、1μm〜50μmの膜厚のソース電極4およびドレイン電極5を形成することが可能である。特に、膜厚が5μm〜20μmの範囲になるように形成する場合には、通常のスクリーン版および通常のインクによって容易に作製できる。また、膜厚を5μm未満にするためには、スクリーン版の乳剤厚を薄くし、かつインクの濃度を薄めることが好ましい。また、膜厚が20μmを超えるようにするためには、スクリーン版の乳剤厚を厚くするか、またはインクの濃度を高めることが好ましい。

【0023】

半導体材料でチャネル領域を形成するには、ディスペンサやインクジェットやそれに類する方法によって半導体材料を間隙の一部に塗布する。図6(a)に示すように、×印で示された位置に塗布された半導体材料は、間隙内において全領域に流動していき、均一な層を形成する。これにより、ソース電極4とドレイン電極5の間にチャネル領域が形成される。

ところが、ドレイン電極の高さが1μm未満の場合、図6(b)に示すように半導体材料はドレイン電極5から溢れ出し、他の領域の電極(例えば、ドレイン電極5’)と連結してしまうので好ましくない。

【0024】

また、ゲート電極2を閉ループに形成することにより、ソース電極4およびドレイン電極5の間の電流経路を完全に遮断でき、off電流を低減できる。また、ソース電極4およびドレイン電極5を形成する版の形状としては、例えば、図7(a)、(b)に示すように、四角形状や円形状の版を用いることができる。

尚、ソース電極4やドレイン電極5の角部の曲率や幅によってチャネル長が大きく変化すると、特性のばらつきが生じることがあり、好ましくない。そのため、ソース電極4とドレイン電極5の間隔(チャネル長)を一定に保つことが望ましく、ソース電極4およびドレイン電極5を形成する版としては円形状の版を用いることが好ましい。特に、ソース電極4が円形、ドレイン電極5が等幅リング形状であり、それらの中心が一致するようにソース電極およびドレイン電極を形成することにより、より高精度にチャネル長を均一にすることができる。

【実施例】

【0025】

(実施例1)

本発明の薄膜トランジスタを製造する場合の実施例1について、図2と図3を用いて説明する。

基板1として、厚さ125μmのポリエチレンナフタレート(PEN)を準備し、Alをスパッタ成膜、フォトリソおよびエッチングによって等幅リング状のゲート電極2を形成した(図2(a))。ゲート電極2の厚さは100nm、内径は200μm、外径は400μmとした。ポリビニルフェノール溶液をスピンコートし、焼成してゲート絶縁膜3を形成した。(図2(b))。ゲート絶縁膜の膜厚は1μmとした。ソース電極4およびドレイン電極5として、Agペーストをスクリーン印刷によって形成した(図2(c))。ソース電極4の厚さは10μm、円の直径は250μmとした。ドレイン電極5の厚さは10μm、内径は350μm、外径は450μmとして等幅リング状に形成した。このようにソース電極4とドレイン電極5を形成したことにより、ソース電極4とドレイン電極5の間には、幅が50μmの等幅リング状の間隙が形成されたことになる。

【0026】

次に、等幅リング状の間隙に適量のポリチオフェン溶液をディスペンサによって塗布した。厚さ10μmのソース電極4およびドレイン電極5が堤防の役割を果たし、間隙のみに効率よく塗布された。その後、ポリチオフェン溶液を焼成することによって半導体層6とした(図2(d))。層間絶縁膜7としてエポキシを塗布および焼成により形成した(図3(a))。層間絶縁膜7の厚さは100μmとした。UV−YAGレーザによって層間絶縁膜7に直径50μmのビアホール用の穴9Aを形成し(図3(b))、ドクターブレードによって穴9AにAgペーストを埋め込み、焼成を行ってビアホール9とした(図3(c))。尚、試料の表面を軽く削って平らにした。最後に、ソース配線8としてAgペーストを印刷および焼成した(図3(d))。このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて10pAであった。

【0027】

(実施例2)

ポリチオフェン溶液の塗布をソース電極4の上面の中心位置に合わせて行った以外は、実施例1と同様の工程によって、薄膜トランジスタを作成した。

このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて10pAであった。

【0028】

(実施例3〜7)

実施例2と同様の工程によって、薄膜トランジスタを作成した。ただし、ソース電極4とドレイン電極5の厚さを、1、5、20、50、60μmとした。

このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、表1に示すような結果になった。

【0029】

【表1】

【0030】

(比較例1)

図8(a)および(b)を用いて、比較例1について説明する。

絶縁基板1として、厚さが125μmのポリエチレンナフタレート(PEN)を準備し、Alをスパッタ成膜、フォトリソおよびエッチングによって長方形状のゲート電極2を形成した。ゲート電極2の厚さは100nm、縦長は1.1mm、横長は100μmとした。次に、ポリビニルフェノール溶液をスピンコートし、焼成してゲート絶縁膜3を形成した。ゲート絶縁膜3の膜厚は1μmとした。次に、長方形のソース電極4とドレイン電極5(ただし、引き出し電極を有する)とをAgペーストをスクリーン印刷することによって形成した。尚、平面視的配置において、ソース電極4およびドレイン電極5の一部がゲート電極に重なるように形成されている。ソース電極4およびドレイン電極5の厚さは10μmとし、長辺は1mm、短辺は100μmとした。対向したソース電極4とドレイン電極5の間には、幅が50μmの間隙が形成された。

【0031】

次に、上述の間隙に適量のポリチオフェン溶液をディスペンサによって塗布した。ポリチオフェン溶液は、ソース電極4およびドレイン電極5の間に流入し、ソース電極4とドレイン電極5の長辺の端部から流出した。その後、ポリチオフェン溶液を焼成することによって半導体層6とした。このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて1nAであった。

【0032】

(比較例2)

比較例として、ソース電極とドレイン電極をCrおよびAuの蒸着およびフォトリソ、エッチングにて0.5μmの厚さに形成した以外は、実施例2と同様の工程で作成した薄膜トランジスタを作成した。ただし、半導体層溶液はドレイン外部に流出し、他の電極にも到達した。

このように作成した薄膜トランジスタにおいて、リーク電流(off電流)を測定したところ、Vd=−40Vにおいて−Id=10pAであったが、他の電極を0Vに接続すると1nAに増大した。

【0033】

以上に示したように、半導体材料が塗布される領域の周囲がドレイン電極によって囲われているため、ソース電極上あるいはソース電極とドレイン電極の間に半導体材料を塗布した際に、ドレイン電極の外側に半導体材料が溢れ出していくことをドレイン電極によって防止できた。すなわち、ドレイン電極が堤防として作用することが分かった。また、ソース電極とドレイン電極の間のリーク電流を抑制することができた。

【図面の簡単な説明】

【0034】

【図1】本発明の薄膜トランジスタの第1の実施形態を示す図であり、(a)は平面図、(b)は(a)のA−A’の断面図である。

【図2】本発明の薄膜トランジスタの製造工程を示す図である。

【図3】本発明の薄膜トランジスタの製造工程を示す図である。

【図4】本発明の薄膜トランジスタの第2の実施形態を示す図であり、(a)は平面図、(b)は(a)のA−A’の断面図である。

【図5】本発明の薄膜トランジスタの第3の実施形態を示す図であり、(a)は平面図、(b)は(a)のA−A’の断面図である。

【図6】半導体材料の流動状態を示す図である。

【図7】ソース電極およびドレイン電極の形状を示す図である。

【図8】従来の薄膜トランジスタを示す図であり、(a)は平面図、(b)は断面図である。

【符号の説明】

【0035】

1・・・絶縁基板、2・・・ゲート電極、3・・・ゲート絶縁膜、4・・・ソース電極、5・・・ドレイン電極、5’・・・他の電極、6・・・半導体層、7・・・層間絶縁層、8・・・ソース配線、9・・・ビアホール、10,20,30,40・・・薄膜トランジスタ

【特許請求の範囲】

【請求項1】

絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなる薄膜トランジスタであって、前記ドレイン電極の膜厚が1μm以上であることを特徴とする薄膜トランジスタ。

【請求項2】

前記ソース電極が円形状であり、前記ゲート電極および前記ドレイン電極が等幅リング状であり、前記ソース電極と前記ゲート電極と前記ドレイン電極の中心位置が略一致していることを特徴とする請求項1に記載の薄膜トランジスタ。

【請求項3】

前記半導体層が、有機半導体からなることを特徴とする請求項1または2に記載の薄膜トランジスタ。

【請求項4】

絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなり、前記ドレイン電極の膜厚が1μm以上である薄膜トランジスタを製造する方法であって、前記ソース電極および前記ドレイン電極を形成する工程が少なくともスクリーン印刷工程を含み、前記半導体層を形成する工程が少なくともディスペンサ工程またはインクジェット工程を含むことを特徴とする薄膜トランジスタの製造方法。

【請求項5】

前記膜厚が1μm以上のドレイン電極を堤防として、ディスペンサ工程またはインクジェット工程で形成する半導体層のドレイン電極外への漏れ出しを防止しつつ半導体層をドレイン電極の内側に形成することを特徴とする請求項4に記載の薄膜トランジスタの製造方法。

【請求項1】

絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなる薄膜トランジスタであって、前記ドレイン電極の膜厚が1μm以上であることを特徴とする薄膜トランジスタ。

【請求項2】

前記ソース電極が円形状であり、前記ゲート電極および前記ドレイン電極が等幅リング状であり、前記ソース電極と前記ゲート電極と前記ドレイン電極の中心位置が略一致していることを特徴とする請求項1に記載の薄膜トランジスタ。

【請求項3】

前記半導体層が、有機半導体からなることを特徴とする請求項1または2に記載の薄膜トランジスタ。

【請求項4】

絶縁基板上に形成されたゲート電極と、前記絶縁基板と前記ゲート電極を覆うように形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成されたソース電極とドレイン電極と半導体層とを有し、平面視的配置において、前記ソース電極が孤立島パターンに形成されており、前記ドレイン電極が前記ソース電極を取り囲むように配置されており、さらに前記ゲート電極が前記ソース電極と前記ドレイン電極との間隙を埋める位置に配置されてなり、前記ドレイン電極の膜厚が1μm以上である薄膜トランジスタを製造する方法であって、前記ソース電極および前記ドレイン電極を形成する工程が少なくともスクリーン印刷工程を含み、前記半導体層を形成する工程が少なくともディスペンサ工程またはインクジェット工程を含むことを特徴とする薄膜トランジスタの製造方法。

【請求項5】

前記膜厚が1μm以上のドレイン電極を堤防として、ディスペンサ工程またはインクジェット工程で形成する半導体層のドレイン電極外への漏れ出しを防止しつつ半導体層をドレイン電極の内側に形成することを特徴とする請求項4に記載の薄膜トランジスタの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−286718(P2006−286718A)

【公開日】平成18年10月19日(2006.10.19)

【国際特許分類】

【出願番号】特願2005−101402(P2005−101402)

【出願日】平成17年3月31日(2005.3.31)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

【公開日】平成18年10月19日(2006.10.19)

【国際特許分類】

【出願日】平成17年3月31日(2005.3.31)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

[ Back to top ]