薄膜トランジスタおよび電子機器

【課題】性能向上を容易に実現することが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、ゲート電極と、そのゲート電極から分離絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備える。ソース電極とドレイン電極との間においてゲート電極とソース電極およびドレイン電極とが重ならない第1領域における分離絶縁層の厚さは、ゲート電極とソース電極およびドレイン電極のうちの少なくとも一方とが重なる第2領域における分離絶縁層の厚さよりも小さい。

【解決手段】薄膜トランジスタは、ゲート電極と、そのゲート電極から分離絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備える。ソース電極とドレイン電極との間においてゲート電極とソース電極およびドレイン電極とが重ならない第1領域における分離絶縁層の厚さは、ゲート電極とソース電極およびドレイン電極のうちの少なくとも一方とが重なる第2領域における分離絶縁層の厚さよりも小さい。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、半導体層を備えた薄膜トランジスタおよびそれを用いた電子機器に関する。

【背景技術】

【0002】

近年、多様な電子機器に、スイッチング用の素子などとして薄膜トランジスタ(TFT)が用いられている。このTFTとしては、半導体層(チャネル層)の形成材料として無機半導体材料を用いた無機TFTと、有機半導体材料を用いた有機TFTとが知られている。

【0003】

TFTは、ゲート電極と、そのゲート電極からゲート絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備えている。

【0004】

高性能なTFTを得るためには、ゲート電極とソース電極およびドレイン電極との間の絶縁性を確保する必要がある。ゲート電極とソース電極およびドレイン電極との間にリーク電流が流れると、TFTの性能が低下するからである。

【0005】

そこで、ゲート電極とソース電極およびドレイン電極との間の絶縁性を向上させるために、さまざまな検討がなされている。具体的には、ゲート絶縁層の形成材料として、アルキル基とシラン基との双方を置換基として有する有機材料を用いることが提案されている(例えば、特許文献1参照。)。また、ゲート絶縁層を表面改質することが提案されている(例えば、特許文献2参照。)。さらに、ゲート絶縁層の形成材料と半導体層の形成材料との相性を向上させるために、大気圧プラズマ法を用いてゲート絶縁層を形成することが提案されている(例えば、特許文献3参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−216938号公報

【特許文献2】特開2007−194360号公報

【特許文献3】特開2004−103638号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

従来より、ゲート電極とソース電極およびドレイン電極との間の絶縁性を向上させる方策が提案されているが、実現可能性の観点において未だ改善の余地がある。なぜなら、ゲート絶縁層の形成材料として新規な材料を用いると、既存の材料を用いることができないため、材料選択の範囲が狭まってしまうからである。また、ゲート絶縁層を表面改質すると、TFTの製造プロセスが煩雑化すると共に、再現性に問題を残すからである。

【0008】

本技術はかかる問題点に鑑みてなされたもので、その目的は、性能向上を容易に実現することが可能な薄膜トランジスタおよび電子機器を提供することにある。

【課題を解決するための手段】

【0009】

本技術の薄膜トランジスタは、ゲート電極と、そのゲート電極から分離絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備えたものである。ソース電極とドレイン電極との間においてゲート電極とソース電極およびドレイン電極とが重ならない第1領域における分離絶縁層の厚さは、ゲート電極とソース電極およびドレイン電極のうちの少なくとも一方とが重なる第2領域における分離絶縁層の厚さよりも小さい。

【0010】

また、本技術の電子機器は、上記した本技術の薄膜トランジスタを備えたものである。

【発明の効果】

【0011】

本技術の薄膜トランジスタまたは電子機器によれば、半導体層は分離絶縁層を介してゲート電極から離間されており、第1領域における分離絶縁層の厚さは第2領域における分離絶縁層の厚さよりも小さい。よって、薄膜トランジスタおよび電子機器の性能向上を容易に実現できる。

【図面の簡単な説明】

【0012】

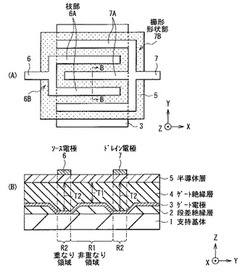

【図1】本技術の一実施形態における薄膜トランジスタの構成を表す平面図および断面図である。

【図2】第1比較例の薄膜トランジスタの構成を表す断面図である。

【図3】第2比較例の薄膜トランジスタの構成を表す断面図である。

【図4】薄膜トランジスタの第1変形例の構成を表す断面図である。

【図5】薄膜トランジスタの第2変形例の構成を表す断面図である。

【図6】薄膜トランジスタの第3変形例の構成を表す断面図である。

【図7】薄膜トランジスタの第4変形例の構成を表す断面図である。

【図8】薄膜トランジスタの第5変形例の構成を表す断面図である。

【図9】薄膜トランジスタの適用例である液晶表示装置の構成を表す断面図である。

【図10】図9に示した液晶表示装置の回路図である。

【図11】薄膜トランジスタの適用例である有機エレクトロルミネセンス(EL)表示装置の構成を表す断面図である。

【図12】図11に示した有機EL表示装置の回路図である。

【図13】薄膜トランジスタの適用例である電子ペーパー表示装置の構成を表す断面図である。

【発明を実施するための形態】

【0013】

以下、本技術の実施形態について、図面を参照して詳細に説明する。なお、説明する順序は、以下の通りである。

1.薄膜トランジスタ

2.変形例

3.薄膜トランジスタの適用例(電子機器)

3−1.液晶表示装置

3−2.有機EL表示装置

3−3.電子ペーパー表示装置

【0014】

<1.薄膜トランジスタ>

まず、本技術の一実施形態の薄膜トランジスタの構成について説明する。図1は薄膜トランジスタの平面構成(A)および断面構成(B)を表しており、(B)に示した断面は(A)に示したB−B線に沿った断面である。なお、(A)では、(B)に示した薄膜トランジスタの構成要素のうちの一部だけを示していると共に、(B)では、薄膜トランジスタの構成の特徴を分かりやすくするために(A)とは縮尺を変更している。

【0015】

ここで説明する薄膜トランジスタは、チャネル層として半導体層5を備えたTFTである。このTFTは、例えば、支持基体1の上に、段差絶縁層2と、ゲート電極3と、ゲート絶縁層4と、半導体層5と、ソース電極6およびドレイン電極7とを備えている。

【0016】

すなわち、図1に示したTFTは、ゲート電極3が半導体層5の下側に配置されると共にソース電極6およびドレイン電極7が半導体層5の上側に配置されたボトムゲート・トップコンタクト型である。なお、「上側」とは支持基体1から遠い側であり、「下側」とは支持基体1に近い側である。

【0017】

以下では、図1(B)に示したように、ソース電極6とドレイン電極7との間においてゲート電極3とソース電極6およびドレイン電極7とが重ならない領域を「非重なり領域R1(第1領域)」とする。また、ゲート電極3とソース電極6およびドレイン電極7とが重なる領域を「重なり領域R2(第2領域)」とする。ここで言う「重なり」の有無は、TFTを上方(図1(A)における紙面の上側)から見た際に、ソース電極6およびドレイン電極7の形成領域とゲート電極3の形成領域とが重なっているか否かを意味している。

【0018】

支持基体1は、例えば、プラスチック材料、金属材料または無機材料などのいずれか1種類または2種類以上により形成されている。

【0019】

プラスチック材料は、例えば、ポリメチルメタクリレート(PMMA)、ポリビニルアルコール(PVA)、ポリビニルフェノール(PVP)、ポリエーテルサルフォン(PES)、ポリカーボネート(PC)、ポリイミド(PI)、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエチルエーテルケトン(PEEK)、ポリアクリレート(PAR)、ポリフェニレンスルフィド(PPS)またはトリアセチルセルロース(TAC)などである。金属材料は、例えば、アルミニウム(Al)、ニッケル(Ni)またはステンレスなどである。無機材料は、例えば、ケイ素(Si)、酸化ケイ素(SiOx )、窒化ケイ素(SiNx )、酸化アルミニウム(AlOx )または他の金属酸化物などである。ただし、酸化ケイ素には、ガラス、石英またはスピンオングラス(SOG)なども含まれる。

【0020】

この支持基体1は、ウェハなどの剛性を有する基板でもよいし、可撓性を有するフィルムまたは箔などでもよい。また、支持基体1の表面の少なくとも一部に、所定の機能を有する1層または2層以上の各種層が設けられていてもよい。この層は、例えば、密着性を確保するためのバッファ層、またはガス放出を防止するためのガスバリア層などである。

【0021】

なお、支持基体1は、単層でもよいし、多層でもよい。多層の場合には、上記した各種材料の層が2層以上積層されている。このように単層でも多層でもよいことは、段差絶縁層2、ゲート電極3、ゲート絶縁層4、半導体層5、ソース電極6およびドレイン電極7および後述する他の構成要素についても同様である。

【0022】

段差絶縁層2は、支持基体1の上に選択的に形成されており、より具体的には、少なくとも非重なり領域R1に配置されている。ただし、段差絶縁層2の形成領域から、重なり領域R2は除かれる。この段差絶縁層2は、ゲート電極3と半導体層5、ソース電極6およびドレイン電極7との間の距離、すなわちゲート電極3と半導体層5等とを離間させる分離絶縁層の厚さを異ならせるものである。この分離絶縁層の詳細については、後述する。また、段差絶縁層2は、例えば、無機絶縁性材料または有機絶縁性材料などのいずれか1種類または2種類以上を含んでいる。無機絶縁性材料は、例えば、酸化ケイ素、窒化ケイ素、酸化アルミニウム、酸化チタン(TiO2 )、酸化ハフニウム(HfOx )またはチタン酸バリウム(BaTiO3 )などである。有機絶縁性材料は、例えば、ポリビニルフェノール(PVP)、ポリビニルアルコール(PVA)、ポリイミド、ポリアミド、ポリエステル、ポリアクリレート、ポリメタクリル酸アクリレート、エポキシ樹脂、ベンゾシクロブテン(BCB)、フッ素樹脂、感光性ポリイミド、感光性ノボラック樹脂またはポリパラキシリレンなどである。

【0023】

なお、図1(B)では、段差絶縁層2の断面形状が台形または略台形である場合を示しているが、その断面形状は特に限定されず、他の形状(例えば矩形など)でもよい。

【0024】

ゲート電極3は、非重なり領域R1に設けられた段差絶縁層2と重なり領域R2(支持基体1)とを覆うように形成されている。このため、ゲート電極3は、非重なり領域R1において、段差絶縁層2とゲート絶縁層4との間に位置している。このゲート電極3は、例えば、金属材料、無機導電性材料、有機導電性材料または炭素材料などのいずれか1種類または2種類以上を含んでいる。

【0025】

金属材料は、例えば、アルミニウム、銅(Cu)、モリブデン(Mo)、チタン(Ti)、クロム(Cr)、ニッケル、パラジウム(Pd)、金(Au)、銀(Ag)、白金(Pt)、タングステン(W)、タンタル(Ta)またはそれらを含む合金などである。無機導電性材料は、例えば、酸化インジウム(In2 O3 )、酸化インジウムスズ(ITO)、酸化インジウム亜鉛(IZO)または酸化亜鉛(ZnO)などである。有機導電性材料は、例えば、ポリエチレンジオキシチオフェン(PEDOT)、ポリスチレンスルホン酸(PSS)またはポリアニリン(PANI)などである。炭素材料は、例えば、グラファイトなどである。なお、ゲート電極3は、例えば、PEDOT/PSSなどの多層でもよい。

【0026】

ゲート絶縁層4は、ゲート電極3の上に形成されており、そのゲート電極3と半導体層5、ソース電極6およびドレイン電極7との間に位置している。このゲート絶縁層4は、例えば、段差絶縁層2と同様の材料を含んでいる。半導体層5に近い側におけるゲート絶縁層4の表面(上面)は、できるだけ平坦であることが好ましい。ゲート絶縁層4の表面平坦性は、半導体層5の電気的特性に影響を与えるからである。より具体的には、ゲート絶縁層4の表面が平坦であると、そのゲート絶縁層4の上に半導体層5も平坦に形成されやすくなる。これにより、半導体層5中における半導体分子の配向性が向上するため、電気的特性が安定化する。

【0027】

中でも、ゲート絶縁層4は、有機絶縁性材料を含んでいることが好ましい。有機絶縁性材料が有機溶媒などに分散または溶解された溶液を用いてゲート絶縁層4を塗布形成できるため、塗布時のレベリング(平坦化)作用によりゲート絶縁層4の表面が平坦化しやすいからである。

【0028】

半導体層5は、ゲート絶縁層4の上に形成されており、無機半導体層でもよいし、有機半導体層でもよい。

【0029】

無機半導体層は、例えば、シリコンなどの無機半導体材料のいずれか1種類または2種類以上を含んでいる。また、無機半導体材料は、ZnOまたはIn2 O3 などにドーパントが添加された透明酸化物などでもよい。

【0030】

有機半導体層は、例えば、以下の有機半導体材料のいずれか1種類または2種類以上を含んでいる。(1)ポリピロール、(2)ポリチオフェン、(3)ポリイソチアナフテンなどのイソチアナフテン、(4)ポリチェニレンビニレンなどのチェニレンビニレン、(5)ポリ(p−フェニレンビニレン)などのポリ(p−フェニレンビニレン)、(6)ポリアニリン、(7)ポリアセチレン、(8)ポリジアセチレン、(9)ポリアズレン、または(10)ポリピレンである。(11)ポリカルバゾール、(12)ポリセレノフェン、(13)ポリフラン、(14)ポリ(p−フェニレン)、(15)ポリインドール、(16)ポリピリダジン、(17)ナフタセン、ペンタセン、ヘキサセン、ヘプタセン、ジベンゾペンタセン、テトラベンゾペンタセン、ピレン、ジベンゾピレン、クリセン、ペリレン、コロネン、テリレン、オバレン、クオテリレンまたはサーカムアントラセンなどのアセン、(18)アセン類のうちの炭素の一部が窒素(N)、硫黄(S)または酸素(O)などの原子、あるいはカルボニル基などの官能基により置換された誘導体、例えば、トリフェノジオキサジン、トリフェノジチアジンまたはヘキサセン−6,15−キノンなど、(19)ポリビニルカルバゾール、ポリフェニレンスルフィドまたはポリビニレンスルフィドなどの高分子材料および多環縮合体、または(20)上記した高分子材料と同じ繰り返し単位を有するオリゴマーである。(21)銅フタロシアニンなどの金属フタロシアニン、(22)テトラチアフルバレン、(23)テトラチアペンタレン、(24)ナフタレン1,4,5,8−テトラカルボン酸ジイミド、N,N’−ビス(4−トリフルオロメチルベンジル)ナフタレン1,4,5,8−テトラカルボン酸ジイミドと共に、N,N’−ビス(1H,1H−ペルフルオロオクチル)、N,N’−ビス(1H,1H−ペルフルオロブチル)またはN,N’−ジオクチルナフタレン1,4,5,8−テトラカルボン酸ジイミド誘導体、(25)ナフタレン2,3,6,7テトラカルボン酸ジイミドなどのナフタレンテトラカルボン酸ジイミド、(26)アントラセン2,3,6,7−テトラカルボン酸ジイミドなどのアントラセンテトラカルボン酸ジイミド類に代表される縮合環テトラカルボン酸ジイミド、(27)C60、C70、C76、C78またはC84などのフラーレン、(28)単層ナノチューブ(SWNT)などのカーボンナノチューブ、(29)メロシアニン色素またはヘミシアニン色素などの色素、または(30)2,9−ジナフチル−ペリキサンテノキサンテンなどのペリキサンテノキサンテン化合物である。

【0031】

この他、有機半導体材料は、上記した一連の材料の誘導体でもよい。誘導体とは、上記した材料に1または2以上の置換基が導入されたものであり、その置換基の種類および導入位置などは、任意である。

【0032】

この半導体層5のうち、非重なり領域R1に位置する部分は、実質的に電気的特性に寄与する部分(いわゆるチャネル部分)である。

【0033】

ソース電極6およびドレイン電極7は、半導体層5の上において互いに離間されるように形成されていると共に、例えば、ゲート電極3と同様の材料を含んでいる。

【0034】

ここで、上記したように、半導体層5は、ゲート電極3から分離絶縁層を介して離間されている。このゲート電極3は、段差絶縁層2とゲート絶縁層4との間に位置しているため、分離絶縁層とは、ここではゲート絶縁層4である。すなわち、分離絶縁層の厚さは、ゲート絶縁層4の厚さにより表される。この半導体層5をゲート電極3から離間させるゲート絶縁層4の厚さは、一定ではなく、場所によって異なっている。

【0035】

具体的には、図1(B)に示したように、段差絶縁層2は、支持基体1の表面のうち、少なくとも非重なり領域R1に形成されており、ゲート電極3は、非重なり領域R1における段差絶縁層2と重なり領域R2(支持基体1)とを被覆している。これにより、ゲート電極3のうち、段差絶縁層2の上に形成されている部分は、支持基体1の上に形成されている部分よりも半導体層5に近づいている。一方、半導体層5に近い側におけるゲート絶縁層4の表面は、ほぼ平坦である。このため、段差絶縁層2の有無により生じる段差を利用して、非重なり領域R1におけるゲート絶縁層4の厚さT1は、重なり領域R2におけるゲート絶縁層4の厚さT2よりも小さくなっている。

【0036】

厚さT1が厚さT2よりも小さいのは、以下の理由による。非重なり領域R1では、ゲート電極3と半導体層5との間の距離が小さくなるため、それらが互いに近づく。これにより、オン電流が減少しにくくなる。一方、重なり領域R2では、ゲート電極3とソース電極6およびドレイン電極7との間の距離が大きくなるため、それらが互いに遠ざかる。これにより、ゲート電極3とソース電極6およびドレイン電極7との間にリーク電流が流れにくくなる。

【0037】

非重なり領域R1におけるゲート絶縁層4の厚さT1と重なり領域R2におけるゲート絶縁層4の厚さT2との大小関係については、3種類の態様が考えられる。第1に、非重なり領域R1の厚さT1は、ゲート電極3とソース電極6との重なり領域R2における厚さT2よりも小さく、かつ、ゲート電極3とドレイン電極7との重なり領域R2における厚さT2よりも小さくなっていてもよい。第2に、非重なり領域R1の厚さT1は、ゲート電極3とソース電極6との重なり領域R2における厚さT2よりも小さくなっている一方で、ゲート電極3とドレイン電極7との重なり領域R2における厚さT2とほぼ同等でもよい。第3に、非重なり領域R1の厚さT1は、ゲート電極3とソース電極6との重なり領域R2における厚さT2とほぼ同等である一方で、ゲート電極3とドレイン電極7との重なり領域R2における厚さT2よりも小さくなっていてもよい。厚さT1が厚さT2よりも小さくなっている箇所が1箇所でも存在すれば、上記した利点が得られるからである。中でも、第1の態様が好ましい。リーク電流の発生確率がより低減するため、より高い効果が得られるからである。

【0038】

なお、ソース電極6およびドレイン電極7の形状(平面形状)は、特に限定されない。ここでは、図1(A)に示したように、ソース電極6は、例えば、一端部側において複数に分岐した枝部6Aを有する櫛形形状部6Bを含んでいると共に、ドレイン電極7も同様に、複数に分岐した枝部7Aを有する櫛形形状部7Bを含んでいる。これに伴い、ソース電極6とドレイン電極7とは、櫛形形状部6B,7Bにおいて互いに噛み合うように配置されている。この「互いに噛み合う」とは、ソース電極6の枝部6A間に設けられた各スペースにドレイン電極7の各枝部7Aが入り込んでいると共に、ドレイン電極7の枝部7A間に設けられた各スペースにソース電極6の各枝部6Aが入り込んでいる状態を意味している。

【0039】

この場合において、ゲート電極3は、例えば、図1(B)に示したように、少なくともソース電極6とドレイン電極7とが互いに噛み合う領域にベタ膜として設けられている。すなわち、ゲート電極3は、ソース電極6とドレイン電極7との間のチャネル領域(非重なり領域R1)ごとに分割形成されているのではなく、複数のチャネル領域を含む領域に全面形成されている。このように複数のチャネル領域を含む領域にゲート電極3がベタ膜として形成されていれば、そのベタ膜のゲート電極3は複数に分割形成されていてもよい。この場合には、ゲート絶縁層4の厚さT1,T2を異ならせることで、ゲート電極3をベタ膜として形成しても上記した利点を得ることができる。

【0040】

なお、ソース電極6またはドレイン電極7のいずれか一方だけが櫛形形状を有していてもよい。より具体的には、例えば、ソース電極6が櫛形形状部6Bを有しているのに対して、ドレイン電極7が非分岐形状(直線状)であってもよい。この場合には、ソース電極6とドレイン電極7とが互いに噛み合うために、ソース電極6の枝部6A間に設けられたスペースにドレイン電極7の一端部が入り込んでいればよい。この場合においても、同様の効果を得ることができる。もちろん、ドレイン電極7が櫛形形状部7Bを有しているのに対して、ソース電極6が非分岐形状であってもよい。

【0041】

次に、図1を参照して、上記したTFTの製造方法について説明する。なお、TFTの各構成要素の形成材料については既に詳細に説明したので、以下では、その形成材料の一例を挙げることとする。

【0042】

TFTを製造する場合には、最初に、ポリイミドなどのプラスチックフィルムの支持基体1の上に、段差絶縁層2を選択的に形成する。この場合には、例えば、支持基体1の表面にフォトレジストを塗布してフォトレジスト膜(図示せず)を形成したのち、フォトリソグラフィ法などを用いてフォトレジスト膜をパターニング(露光および現像)する。このフォトレジストしては、例えば、東京応化工業株式会社製のTELP−P003PMなどを用いることができる。また、少なくとも非重なり領域R1に形成されると共に重なり領域R2に形成されないように、段差絶縁層2の形成位置を位置合わせする。

【0043】

なお、段差絶縁層2を形成する場合には、例えば、支持基体1の表面を覆うように無機絶縁性材料または有機絶縁性材料を成膜したのち、フォトリソグラフィ法以外の方法を用いてパターニングしてもよい。このパターニング方法は、例えば、ドライエッチング法などである。この他、インクジェット法、スクリーン印刷法、オフセット印刷法またはグラビア印刷法などや、ナノインプリント法などを用いて段差絶縁層2を形成してもよい。

【0044】

続いて、非重なり領域R1における段差絶縁層2およびその周辺の重なり領域R2における支持基体1を覆うように、ゲート電極3を形成する。この場合には、例えば、段差絶縁層2および支持基体1を覆うように金属材料層(図示せず)を形成したのち、その金属材料層をパターニングする。

【0045】

金属材料層の形成材料は、例えば、アルミニウムなどであると共に、その形成方法は、例えば、スパッタリング法、蒸着法または化学気相成長(CVD)法などの気相成長法である。また、金属材料層のパターニング方法は、例えば、エッチング法などである。このエッチング法は、イオンミリング法または反応性イオンエッチング(RIE)法などのドライエッチング法でもよいし、ウェットエッチング法でもよい。

【0046】

なお、金属材料層をパターニングする場合には、フォトリソグラフィ法または紫外線描画法などを併用してもよい。この場合には、例えば、金属材料層の表面にフォトレジストを塗布してフォトレジスト膜を形成してから、フォトリソグラフィ法などを用いてフォトレジスト膜をパターニングしたのち、そのフォトレジスト膜をマスクとして金属材料層をエッチングする。ただし、フォトレジスト膜に代えて金属膜などをマスクとして用いてもよい。

【0047】

続いて、ゲート電極3を覆うようにゲート絶縁層4を形成する。この場合には、例えば、PVPが任意の有機溶媒などに溶解された溶液を準備したのち、その溶液を塗布してから乾燥させる。この塗布方法は、例えば、スピンコート法、エアドクタコータ法、ブレードコータ法、ロッドコータ法、ナイフコータ法、スクイズコータ法、リバースロールコータ法、トランスファーロールコータ法、グラビアコータ法、キスコータ法、キャストコータ法、スプレーコータ法、スリットオリフィスコータ法、カレンダーコータ法または浸漬法などである。この場合には、必要に応じて、乾燥速度を向上させるために加熱してもよい。

【0048】

このゲート絶縁層4の形成工程では、流動性を有する溶液の表面が塗布時または塗布後にレベリングされるため、段差絶縁層2の存在に起因して下地の表面が凹凸を有しているにもかかわらず、ゲート絶縁層4の表面が平坦化される。これにより、ゲート絶縁層4の形成時において、非重なり領域R1におけるゲート絶縁層4の厚さT1は、重なり領域R2におけるゲート絶縁層4の厚さT2よりも小さくなる。

【0049】

なお、ゲート電極3を形成するために用いた金属材料層の形成方法と同様の方法を用いて、ゲート絶縁層4を形成してもよい。この場合には、上記したように厚さT1を厚さT2よりも小さくするために、必要に応じて、ゲート絶縁層4の表面を平坦化してもよい。この平坦化方法は、例えば、エッチング法または研磨法なである。

【0050】

続いて、ゲート絶縁層4の上に半導体層5を形成する。この半導体層5として有機半導体層を形成する場合に用いる形成材料は、例えば、ペンタセンなどである。また、半導体層5の形成方法は、例えば、(1)抵抗加熱蒸着法、スパッタリング、蒸着法またはCVD法などの気相成長法、(2)スピンコート法、エアドクタコータ法、ブレードコータ法、ロッドコータ法、ナイフコータ法、スクイズコータ法、リバースロールコータ法、トランスファーロールコータ法、グラビアコータ法、キスコータ法、キャストコータ法、スプレーコータ法、スリットオリフィスコータ法、カレンダーコータ法または浸漬法などの塗布法である。これらの形成方法は、半導体層5の形成材料などの条件に応じて適宜選択可能である。なお、半導体層5の厚さは、特に限定されないが、例えば、50nmである。

【0051】

この半導体層5の形成工程では、平坦なゲート絶縁層4の上に半導体層5が形成されるため、その半導体層5も平坦に形成される。

【0052】

最後に、半導体層5の上に、互いに離間されたソース電極6およびドレイン電極7を形成する。この場合には、例えば、少なくとも半導体層5の表面を覆うように金属材料層(図示せず)を形成したのち、その金属材料層をパターニングする。

【0053】

この金属材料層の形成材料は、例えば、金などであると共に、その形成方法は、例えば、ゲート電極3の形成方法と同様である。ただし、金属材料層のパターニング方法は、半導体層5にダメージを及ぼしにくいウェットエッチング法が好ましい。

【0054】

このTFTによれば、半導体層5が分離絶縁層(ゲート絶縁層4)を介してゲート電極3から離間されている。また、非重なり領域R1におけるゲート絶縁層4の厚さT1は重なり領域R2におけるゲート絶縁層4の厚さT2よりも小さくなっている。よって、以下の理由により、TFTの性能向上を容易に実現できる。

【0055】

図2および図3は、比較例のTFTの構成を表しており、いずれも図1(B)に対応する断面構成を示している。この比較例のTFTは、段差絶縁層2を備えておらず、非重なり領域R1におけるゲート絶縁層4の厚さT3が重なり領域R2におけるゲート絶縁層4の厚さT4と等しいことを除き、図1に示したTFTと同様の構成を有している。ただし、図2では厚さT3,T4=T1であると共に、図3では厚さT3,T4=T2である。

【0056】

図2に示した比較例では、非重なり領域R1において半導体層5がゲート電極3に近づくため、オン電流が増加するが、重なり領域R2においてソース電極6およびドレイン電極7もゲート電極3に近づくため、それらの間にリーク電流が流れやすくなる。また、図3に示した比較例では、重なり領域R2においてソース電極6およびドレイン電極7がゲート電極3から遠ざかるため、それらの間にリーク電流が流れにくくなるが、非重なり領域R1において半導体層5がゲート電極3から遠ざかるため、オン電流が減少する。

【0057】

これに対して、図1に示した本実施形態では、上記したように、重なり領域R2においてソース電極6およびドレイン電極7がゲート電極3から遠ざかるため、それらの間にリーク電流が流れにくくなる。また、非重なり領域R1において半導体層5がゲート電極3に近づくため、オン電流が増加する。しかも、上記した利点は、ゲート絶縁層4の形成材料として既存の材料を用いることができる一方で、表面改質などの煩雑な手法を用いなくも簡単に得られる。よって、TFTの性能向上を容易に実現できるのである。

【0058】

特に、段差絶縁層2が非重なり領域R1だけに形成されていれば、その段差絶縁層2の有無により生じる段差を利用して、厚さT1を厚さT2よりも容易に小さくできる。この場合には、半導体層5に近い側におけるゲート絶縁層4の表面が平坦であれば、段差絶縁層2を利用して確実に厚さT1を厚さT2よりも小さくできる。しかも、半導体層5が有機半導体層である場合には、その半導体層5が平坦であれば、有機半導体分子の配向性が向上するため、TFTの性能をより向上させることができる。

【0059】

<2.変形例>

[TFTの型]

図1(B)では、TFTをボトムゲート・トップコンタクト型にしたが、これに限られない。例えば、TFTは、図4に示したボトムゲート・ボトムコンタクト型、図5に示したトップゲート・トップコンタクト型、または図6に示したトップゲート・ボトムコンタクト型でもよい。これらのTFTの構成および製造方法は、一連の構成要素の積層順が異なることを除き、図1に示したTFTの構成および製造方法と同様である。

【0060】

ボトムゲート・ボトムコンタクト型のTFTは、図4に示したように、支持基体1の上に、段差絶縁層2と、ゲート電極3と、ゲート絶縁層4と、ソース電極6およびドレイン電極7と、半導体層5とをこの順に備えている。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ボトムゲート・トップコンタクト型と同様に、ゲート絶縁層4である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さにより表される。

【0061】

トップゲート・トップコンタクト型のTFTは、図5に示したように、支持基体1の上に、半導体層5と、ソース電極6およびドレイン電極7と、ゲート絶縁層4と、段差絶縁層2と、ゲート電極3とをこの順に備えている。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ボトムゲート・トップコンタクト型とは異なり、ゲート絶縁層4および段差絶縁層2である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さと段差絶縁層2の厚さとの和により表される。

【0062】

トップゲート・ボトムコンタクト型のTFTは、図6に示したように、支持基体1の上に、ソース電極6およびドレイン電極7と、半導体層5と、ゲート絶縁層4と、段差絶縁層2と、ゲート電極3とをこの順に備えている。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、トップゲート・トップコンタクト型と同様に、ゲート絶縁層4および段差絶縁層2である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さと段差絶縁層2の厚さとの和により表される。

【0063】

これらのTFTにおいても、非重なり領域R1における分離絶縁層の厚さT1が重なり領域R2における分離絶縁層の厚さT2よりも小さくなるため、ボトムゲート・トップコンタクト型(図1)と同様の作用および効果を得ることができる。

【0064】

ただし、半導体層5として有機半導体層を備えたTFTでは、上記したように、半導体層5が平坦であると有機半導体分子の配向性が向上する。よって、半導体層5が平坦に形成されやすいボトムゲート・トップコンタクト型またはトップゲート・トップコンタクト型が好ましい。

【0065】

[段差絶縁層の形成位置]

図1(B)では、厚さT1,T2を異ならせるために、支持基体1の上に段差絶縁層2を形成したが、その段差絶縁層2の形成位置を変更してもよい。例えば、ボトムゲート・トップコンタクト型のTFTでは、図7に示したように、ゲート絶縁層4の上の少なくとも重なり領域R2に段差絶縁層2を形成してもよい。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ゲート絶縁層4および段差絶縁層2である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さと段差絶縁層2の厚さとの和により表される。この場合においても、非重なり領域R1における分離絶縁層の厚さT1が重なり領域R2における分離絶縁層の厚さT2よりも小さくなるため、同様の効果を得ることができる。

【0066】

もちろん、図4〜図6に示したTFTにおいて、段差絶縁層2の形成位置を変更してもよい。ただし、半導体層5が有機半導体層である場合には、その半導体層5を平坦化して有機半導体分子の配向性を向上させるために、半導体層5の直下に段差絶縁層2を形成しないことが好ましい。すなわち、ボトムゲート・トップコンタクト型では、図7の構成よりも図1(B)の構成が好ましい。

【0067】

[厚さT1,T2を異ならせる構成]

図1(B)に示したボトムゲート・トップコンタクト型のTFTでは、段差絶縁層2の有無による段差を利用して厚さT1,T2を異ならせるようにしたが、これに限られない。例えば、図8に示したように、段差絶縁層2を形成する代わりに、非重なり領域R1と重なり領域R2とにおいてゲート電極3の厚さを異ならせてもよい。具体的には、厚さT1を厚さT2よりも小さくするために、非重なり領域R1におけるゲート電極3の厚さT5を重なり領域R2におけるゲート電極3の厚さT6を大きくしてもよい。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ゲート絶縁層4である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さにより表される。

【0068】

このゲート電極3を形成する場合には、例えば、非重なり領域R1および重なり領域R2に厚さT5を有するゲート電極3を形成したのち、重なり領域R2におけるゲート電極3をエッチングなどしてもよい。このエッチング法は、例えば、イオンミリング法またはRIE法などのドライエッチング法である。または、例えば、非重なり領域R1および重なり領域R2に厚さT6を有するゲート電極3を形成したのち、非重なり領域R1にゲート電極3を追加形成してもよい。この場合には、非重なり領域R1におけるゲート電極3が2層になる。ただし、非重なり領域R1に形成されるゲート電極3は、2層に限らず、3層以上でもよい。もちろん、非重なり領域R1におけるゲート電極3と重なり領域R2におけるゲート電極3とを別工程において形成してもよい。

【0069】

この場合においても、ゲート電極3の厚さT5,T6の違いを利用して、非重なり領域R1における分離絶縁層の厚さT1が重なり領域R2における分離絶縁層の厚さT2よりも小さくなるため、同様の効果を得ることができる。

【0070】

もちろん、図4および図7に示したボトムゲート型のTFTにおいて、段差絶縁層2を形成する代わりにゲート電極3の厚さを異ならせてもよい。ボトムゲート型であれば、図8に示した場合と同様の作用および効果が得られるからである。この他、段差絶縁層2を形成する代わりに、ゲート電極3の厚さT5,T6を異ならせた場合と同様に、ゲート絶縁層4を形成してからその一部をエッチングしたり、ゲート絶縁層4の一部を2層以上にすることで、厚さT1,T2を異ならせてもよい。

【0071】

なお、図1および図4〜図8などを参照しながら説明した上記一連の態様の1種類または2種類以上を任意に組み合わせてもよい。

【0072】

<3.薄膜トランジスタの適用例(電子機器)>

次に、上記したTFTの適用例について説明する。このTFTは、例えば、以下で説明するように、いくつかの電子機器に適用可能である。

【0073】

<3−1.液晶表示装置>

TFTは、例えば、液晶表示装置に適用される。図9および図10は、それぞれ液晶表示装置の断面構成および回路構成を表している。なお、以下で説明する装置構成(図9)および回路構成(図10)はあくまで一例であるため、それらの構成は適宜変更可能である。

【0074】

ここで説明する液晶表示装置は、例えば、TFTを用いたアクティブマトリクス駆動方式の透過型液晶ディスプレイであり、そのTFTは、スイッチング(画素選択)用の素子として用いられる。この液晶表示装置は、図9に示したように、駆動基板20と対向基板30との間に液晶層41が封入されたものである。

【0075】

駆動基板20は、例えば、支持基板21の一面にTFT22、平坦化絶縁層23および画素電極24がこの順に積層されると共に、TFT22および画素電極24がマトリクス状に配置されたものである。ただし、1画素内に含まれるTFT22の数は、1つでもよいし、2つ以上でもよい。図9および図10では、例えば、1画素内に1つのTFT22が含まれる場合を示している。

【0076】

支持基板21は、例えば、ガラスまたはプラスチック材料などの透過性材料により形成されており、TFT22は、上記したTFTと同様の構成を有している。プラスチック材料の種類は、例えば、上記したTFTについて説明した場合と同様であり、そのことは、以降で説明するプラスチック材料に関しても同様である。平坦化絶縁層23は、例えば、ポリイミドなどの絶縁性樹脂材料を含んでおり、画素電極24は、例えば、ITOなどの透過性導電性材料を含んでいる。なお、画素電極24は、平坦化絶縁層23に設けられたコンタクトホール(図示せず)を通じてTFT22に接続されている。

【0077】

対向基板30は、例えば、支持基板31の一面に対向電極32が全面形成されたものである。支持基板31は、例えば、ガラスまたはプラスチック材料などの透過性材料により形成されており、対向電極32は、例えば、ITOなどの透過性導電性材料を含んでいる。

【0078】

駆動基板20および対向基板30は、液晶層41を挟んで画素電極24と対向電極32とが対向するように配置されていると共に、シール材40により貼り合わされている。液晶層41に含まれる液晶分子の種類は、任意に選択可能である。

【0079】

この他、液晶表示装置は、例えば、位相差板、偏光板、配向膜およびバックライトユニットなどの他の構成要素(いずれも図示せず)を備えていてもよい。

【0080】

液晶表示装置を駆動させるための回路は、例えば、図10に示したように、TFT22および液晶表示素子44(画素電極24、対向電極32および液晶層41を含む素子部)と共に、キャパシタ45を含んでいる。この回路では、行方向に複数の信号線42が配列されていると共に列方向に複数の走査線43が配列されており、それらが交差する位置にTFT22、液晶表示素子44およびキャパシタ45が配置されている。TFT22におけるソース電極、ゲート電極およびドレイン電極の接続先は、図10に示した態様に限らず、任意に変更可能である。信号線42および走査線43は、それぞれ図示しない信号線駆動回路(データドライバ)および走査線駆動回路(走査ドライバ)に接続されている。

【0081】

この液晶表示装置では、TFT22により液晶表示素子44が選択され、画素電極24と対向電極32との間に電界が印加されると、その電界強度に応じて液晶層41における液晶分子の配向状態が変化する。これにより、液晶分子の配向状態に応じて光の透過量(透過率)が制御されるため、画像が表示される。

【0082】

この液晶表示装置によれば、TFT22が上記したTFTと同様の構成を有しているので、既存の材料を用いると共に煩雑な手法を用いなくても、TFT22においてオン電流が増加すると共にリーク電流が流れにくくなる。よって、表示性能を容易に向上させることができる。なお、液晶表示装置は、透過型に限らずに反射型でもよい。

【0083】

<3−2.有機EL表示装置>

TFTは、例えば、有機EL表示装置に適用される。図11および図12は、それぞれ有機EL表示装置の断面構成および回路構成を表している。なお、以下で説明する装置構成(図11)および回路構成(図12)はあくまで一例であるため、それらの構成は適宜変更可能である。

【0084】

ここで説明する有機EL表示装置は、例えば、TFTをスイッチング用の素子として用いたアクティブマトリクス駆動方式の有機ELディスプレイである。この有機EL表示装置は、駆動基板50と対向基板60とが接着層70を介して貼り合わされたものであり、例えば、対向基板60を経由して光を放出するトップエミッション型である。

【0085】

駆動基板50は、例えば、支持基板51の一面にTFT52、保護層53、平坦化絶縁層54、画素分離絶縁層55、画素電極56、有機層57、対向電極58および保護層59がこの順に積層されたものである。TFT52、画素電極56および有機層57は、マトリクス状に配置されている。ただし、1画素内に含まれるTFT52の数は、1つでもよいし、2つ以上でもよい。図11および図12では、例えば、1画素内に2つのTFT52(選択用TFT52Aおよび駆動用TFT52B)が含まれる場合を示している。

【0086】

支持基板51は、例えば、ガラスまたはプラスチック材料などにより形成されている。トップエミッション型では対向基板60から光が取り出されるため、支持基板51は、透過性材料または非透過性材料のいずれにより形成されていてもよい。TFT52は、上記したTFTと同様の構成を有しており、保護層53は、例えば、PVAまたはポリパラキシリレンなどの高分子材料を含んでいる。平坦化絶縁層54および画素分離絶縁層55は、例えば、ポリイミドなどの絶縁性樹脂材料を含んでいる。この画素分離絶縁層55は、例えば、形成工程を簡略化すると共に所望の形状に形成可能にするために、光パターニングまたはリフローなどにより成形可能な感光性樹脂材料を含んでいることが好ましい。なお、保護層53により十分な平坦性が得られていれば、平坦化絶縁層54はなくてもよい。

【0087】

画素電極56は、例えば、アルミニウム、銀、チタンまたはクロムなどの反射性材料を含んでおり、対向電極58は、例えば、ITOまたはIZOなどの透過性導電性材料を含んでいる。ただし、カルシウム(Ca)などの透過性の金属材料またはその合金や、PEDOTなどの透過性の有機導電性材料を含んでいてもよい。有機層57は、赤色、緑色または青色などの光を発生させる発光層を含んでおり、必要に応じて正孔輸送層および電子輸送層などを含む積層構造を有していてもよい。発光層の形成材料は、発生させる光の色に応じて任意に選択可能である。画素電極56および有機層57は、画素分離絶縁層55により分離されながらマトリクス状に配置されているのに対して、対向電極58は、有機層57を介して画素電極56に対向しながら連続的に延在している。保護層59は、例えば、酸化ケイ素、酸化アルミニウム、窒化ケイ素、ポリパラキシリレンまたはウレタンなどの光透過性誘電材料を含んでいる。なお、画素電極56は、保護層53および平坦化絶縁層54に設けられたコンタクトホール(図示せず)を通じてTFT52に接続されている。

【0088】

対向基板60は、例えば、支持基板61の一面にカラーフィルタ62が設けられたものである。支持基板61は、例えば、ガラスまたはブラスチック材料などの透過性材料により形成されており、カラーフィルタ62は、有機層57において発生した光の色に対応する複数の色領域を有している。ただし、カラーフィルタ62はなくてもよい。

【0089】

接着層70は、例えば、熱硬化型樹脂などの接着剤である。

【0090】

有機EL表示装置を駆動させるための回路は、例えば、図12に示したように、TFT52(選択用TFT52Aおよび駆動用TFT52B)および有機EL表示素子73(画素電極56、有機層57および対向電極58を含む素子部)と共に、キャパシタ74を含んでいる。この回路では、複数の信号線71および走査線72が交差する位置に、TFT52、有機EL表示素子73およびキャパシタ74が配置されている。選択用TFT52Aおよび駆動用TFT52Bにおけるソース電極、ゲート電極およびドレイン電極の接続先は、図12に示した態様に限らず、任意に変更可能である。

【0091】

この有機EL表示装置では、例えば、選択用TFT52Aにより有機EL表示素子73が選択されると、その有機EL表示素子73が駆動用TFT52Bにより駆動される。この場合には、画素電極56と対向電極58との間に電界が印加されると、有機層57において光が発生する。これにより、例えば、隣り合う3つの有機EL表示素子73において、それぞれ赤色、緑色または青色の光が発生する。これらの光の合成光が対向基板60を経由して外部へ放出されるため、画像が表示される。

【0092】

この有機EL表示装置によれば、TFT52が上記したTFTと同様の構成を有しているので、液晶表示装置と同様に表示性能を容易に向上させることができる。

【0093】

なお、有機EL表示装置は、トップエミッション型に限らず、駆動基板50を経由して光を放出するボトムエミッション型でもよいし、駆動基板50および対向基板60の双方を経由して光を放出するデュアルエミッション型でもよい。この場合には、画素電極56および対向電極58のうち、光が放出される側の電極が透過性材料により形成され、光が放出されない側の電極が反射性材料により形成されることになる。

【0094】

<3−3.電子ペーパー表示装置>

TFTは、例えば、電子ペーパー表示装置に適用される。図13は、電子ペーパー表示装置の断面構成を表している。なお、以下で説明する装置構成(図13)および図10を参照して説明する回路構成はあくまで一例であるため、それらの構成は適宜変更可能である。

【0095】

ここで説明する電子ペーパー表示装置は、例えば、TFTをスイッチング用の素子として用いたアクティブマトリクス駆動方式の電子ペーパーディスプレイである。この電子ペーパー表示装置は、例えば、駆動基板80と電気泳動素子93を含む対向基板90とが接着層100を介して貼り合わされたものである。

【0096】

駆動基板80は、例えば、支持基板81の一面にTFT82、保護層83、平坦化絶縁層84および画素電極85がこの順に積層されると共に、TFT82および画素電極85がマトリクス状に配置されたものである。支持基板81は、例えば、ガラスまたはプラスチック材料などにより形成されており、TFT82は、上記したTFTと同様の構成を有している。保護層83および平坦化絶縁層84は、例えば、ポリイミドなどの絶縁性樹脂材料を含んでおり、画素電極85は、例えば、銀などの金属材料を含んでいる。なお、画素電極85は、保護層83および平坦化絶縁層84に設けられたコンタクトホール(図示せず)を通じてTFT82に接続されている。また、保護層83により十分な平坦性が得られていれば、平坦化絶縁層84はなくてもよい。

【0097】

対向基板90は、例えば、支持基板91の一面に、対向電極92と、複数の電気泳動素子93を含む層とがこの順に積層されると共に、その対向電極92が全面形成されたものである。支持基板91は、例えば、ガラスまたはプラスチック材料などの透過性材料により形成されており、対向電極92は、例えば、ITOなどの透過性導電性材料を含んでいる。電気泳動素子93は、電気泳動現象を利用してコントラストを生じさせるものであり、その構成は任意である。

【0098】

この他、電子ペーパー表示装置は、例えば、カラーフィルタなどの他の構成要素(図示せず)を備えていてもよい。

【0099】

電子ペーパー表示装置を駆動させるための回路は、例えば、図10に示した液晶表示装置の回路と同様の構成を有している。電子ペーパー表示装置の回路は、TFT22および液晶表示素子44の代わりに、それぞれTFT82および電子ペーパー表示素子(画素電極85、対向電極92および電気泳動素子93を含む素子部)を含んでいる。

【0100】

この電子ペーパー表示装置では、TFT82により電子ペーパー表示素子が選択され、画素電極85と対向電極92との間に電界が印加されると、その電界に応じて電気泳動素子93においてコントラストが生じるため、画像が表示される。

【0101】

この電子ペーパー表示装置によれば、TFT82が上記したTFTと同様の構成を有しているので、液晶表示装置と同様に表示性能を容易に向上させることができる。

【0102】

以上、実施形態を挙げて本技術を説明したが、本技術は実施形態で説明した態様に限定されず、種々の変形が可能である。例えば、本技術の薄膜トランジスタが適用される電子機器は、液晶表示装置、有機EL表示装置または電子ペーパー表示装置に限らず、他の表示装置でもよい。このような他の表示装置としては、例えば、MEMS(Micro Electro Mechanical Systems)表示部(MEMS型ディスプレイ)などが挙げられる。この場合においても、表示性能を向上させることができる。

【0103】

また、例えば、本技術の薄膜トランジスタは、表示装置以外の他の電子機器に適用されてもよい。このような電子機器としては、例えば、センサマトリクス、メモリセンサ、RFIDタグ(Radio Frequency Identification)またはセンサアレイなどが挙げられる。この場合においても、性能向上を図ることができる。

【0104】

なお、本技術は以下のような構成を取ることも可能である。

(1)

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

薄膜トランジスタ。

(2)

前記半導体層は有機半導体層である、

上記(1)に記載の薄膜トランジスタ。

(3)

前記分離絶縁層はゲート絶縁層を含み、そのゲート絶縁層は有機絶縁性材料を含む、

上記(1)または(2)に記載の薄膜トランジスタ。

(4)

前記第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さいと共に、前記ゲート電極と前記ドレイン電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さい、

上記(1)ないし(3)のいずれかに記載の薄膜トランジスタ。

(5)

前記第1領域に設けられた段差絶縁層と、

前記ゲート電極と前記半導体層、前記ソース電極および前記ドレイン電極との間に設けられたゲート絶縁層と

備え、

前記第1領域において前記ゲート電極は、前記段差絶縁層と前記ゲート絶縁層との間に位置し、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

上記(1)ないし(4)のいずれかに記載の薄膜トランジスタ。

(6)

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている

上記(5)に記載の薄膜トランジスタ。

(7)

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記ソース電極および前記ドレイン電極が形成され、

前記ゲート絶縁層、前記ソース電極および前記ドレイン電極の上に前記半導体層が形成されている、

上記(5)に記載の薄膜トランジスタ。

(8)

前記第2領域に設けられた段差絶縁層と、

前記半導体層、前記ソース電極および前記ドレイン電極と前記段差絶縁層との間に設けられたゲート絶縁層と

を備え、

前記第2領域において前記段差絶縁層は、前記ゲート絶縁層と前記ゲート電極との間に位置し、

前記分離絶縁層は前記ゲート絶縁層および前記段差絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さと前記段差絶縁層の厚さとの和により表される、

上記(1)ないし(4)のいずれかに記載の薄膜トランジスタ。

(9)

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成され、

前記半導体層、前記ソース電極および前記ドレイン電極の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

上記(8)に記載の薄膜トランジスタ。

(10)

前記第1領域と、前記第2領域に設けられた前記ソース電極および前記ドレイン電極と、を覆うように前記半導体層が形成され、

前記半導体層の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

上記(8)に記載の薄膜トランジスタ。

(11)

前記第1領域における前記ゲート電極の厚さは、前記第2領域における前記ゲート電極の厚さよりも大きい、

上記(1)ないし(4)のいずれかに記載の薄膜トランジスタ。

(12)

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁層を備え、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

上記(11)に記載の薄膜トランジスタ。

(13)

前記第1領域および前記第2領域に設けられた前記ゲート電極を覆うように前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている、

上記(12)に記載の薄膜トランジスタ。

(14)

前記ソース電極および前記ドレイン電極のうちの少なくとも一方は、複数に分岐した枝部を有する櫛形形状部を含み、

前記ソース電極と前記ドレイン電極とは、前記櫛形形状部において互いに噛み合うように配置されており、

前記ゲート電極は、少なくとも前記ソース電極と前記ドレイン電極部とが互いに噛み合う領域にベタ膜として設けられている、

上記(1)ないし(13)のいずれかに記載の薄膜トランジスタ。

(15)

薄膜トランジスタを備え、その薄膜トランジスタは、

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

電子機器。

【符号の説明】

【0105】

1…支持基体、2…段差絶縁層、3…ゲート電極、4…ゲート絶縁層、5…半導体層、6…ソース電極、7…ドレイン電極、R1…非重なり領域、R2…重なり領域、T1〜T6…厚さ。

【技術分野】

【0001】

本技術は、半導体層を備えた薄膜トランジスタおよびそれを用いた電子機器に関する。

【背景技術】

【0002】

近年、多様な電子機器に、スイッチング用の素子などとして薄膜トランジスタ(TFT)が用いられている。このTFTとしては、半導体層(チャネル層)の形成材料として無機半導体材料を用いた無機TFTと、有機半導体材料を用いた有機TFTとが知られている。

【0003】

TFTは、ゲート電極と、そのゲート電極からゲート絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備えている。

【0004】

高性能なTFTを得るためには、ゲート電極とソース電極およびドレイン電極との間の絶縁性を確保する必要がある。ゲート電極とソース電極およびドレイン電極との間にリーク電流が流れると、TFTの性能が低下するからである。

【0005】

そこで、ゲート電極とソース電極およびドレイン電極との間の絶縁性を向上させるために、さまざまな検討がなされている。具体的には、ゲート絶縁層の形成材料として、アルキル基とシラン基との双方を置換基として有する有機材料を用いることが提案されている(例えば、特許文献1参照。)。また、ゲート絶縁層を表面改質することが提案されている(例えば、特許文献2参照。)。さらに、ゲート絶縁層の形成材料と半導体層の形成材料との相性を向上させるために、大気圧プラズマ法を用いてゲート絶縁層を形成することが提案されている(例えば、特許文献3参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−216938号公報

【特許文献2】特開2007−194360号公報

【特許文献3】特開2004−103638号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

従来より、ゲート電極とソース電極およびドレイン電極との間の絶縁性を向上させる方策が提案されているが、実現可能性の観点において未だ改善の余地がある。なぜなら、ゲート絶縁層の形成材料として新規な材料を用いると、既存の材料を用いることができないため、材料選択の範囲が狭まってしまうからである。また、ゲート絶縁層を表面改質すると、TFTの製造プロセスが煩雑化すると共に、再現性に問題を残すからである。

【0008】

本技術はかかる問題点に鑑みてなされたもので、その目的は、性能向上を容易に実現することが可能な薄膜トランジスタおよび電子機器を提供することにある。

【課題を解決するための手段】

【0009】

本技術の薄膜トランジスタは、ゲート電極と、そのゲート電極から分離絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備えたものである。ソース電極とドレイン電極との間においてゲート電極とソース電極およびドレイン電極とが重ならない第1領域における分離絶縁層の厚さは、ゲート電極とソース電極およびドレイン電極のうちの少なくとも一方とが重なる第2領域における分離絶縁層の厚さよりも小さい。

【0010】

また、本技術の電子機器は、上記した本技術の薄膜トランジスタを備えたものである。

【発明の効果】

【0011】

本技術の薄膜トランジスタまたは電子機器によれば、半導体層は分離絶縁層を介してゲート電極から離間されており、第1領域における分離絶縁層の厚さは第2領域における分離絶縁層の厚さよりも小さい。よって、薄膜トランジスタおよび電子機器の性能向上を容易に実現できる。

【図面の簡単な説明】

【0012】

【図1】本技術の一実施形態における薄膜トランジスタの構成を表す平面図および断面図である。

【図2】第1比較例の薄膜トランジスタの構成を表す断面図である。

【図3】第2比較例の薄膜トランジスタの構成を表す断面図である。

【図4】薄膜トランジスタの第1変形例の構成を表す断面図である。

【図5】薄膜トランジスタの第2変形例の構成を表す断面図である。

【図6】薄膜トランジスタの第3変形例の構成を表す断面図である。

【図7】薄膜トランジスタの第4変形例の構成を表す断面図である。

【図8】薄膜トランジスタの第5変形例の構成を表す断面図である。

【図9】薄膜トランジスタの適用例である液晶表示装置の構成を表す断面図である。

【図10】図9に示した液晶表示装置の回路図である。

【図11】薄膜トランジスタの適用例である有機エレクトロルミネセンス(EL)表示装置の構成を表す断面図である。

【図12】図11に示した有機EL表示装置の回路図である。

【図13】薄膜トランジスタの適用例である電子ペーパー表示装置の構成を表す断面図である。

【発明を実施するための形態】

【0013】

以下、本技術の実施形態について、図面を参照して詳細に説明する。なお、説明する順序は、以下の通りである。

1.薄膜トランジスタ

2.変形例

3.薄膜トランジスタの適用例(電子機器)

3−1.液晶表示装置

3−2.有機EL表示装置

3−3.電子ペーパー表示装置

【0014】

<1.薄膜トランジスタ>

まず、本技術の一実施形態の薄膜トランジスタの構成について説明する。図1は薄膜トランジスタの平面構成(A)および断面構成(B)を表しており、(B)に示した断面は(A)に示したB−B線に沿った断面である。なお、(A)では、(B)に示した薄膜トランジスタの構成要素のうちの一部だけを示していると共に、(B)では、薄膜トランジスタの構成の特徴を分かりやすくするために(A)とは縮尺を変更している。

【0015】

ここで説明する薄膜トランジスタは、チャネル層として半導体層5を備えたTFTである。このTFTは、例えば、支持基体1の上に、段差絶縁層2と、ゲート電極3と、ゲート絶縁層4と、半導体層5と、ソース電極6およびドレイン電極7とを備えている。

【0016】

すなわち、図1に示したTFTは、ゲート電極3が半導体層5の下側に配置されると共にソース電極6およびドレイン電極7が半導体層5の上側に配置されたボトムゲート・トップコンタクト型である。なお、「上側」とは支持基体1から遠い側であり、「下側」とは支持基体1に近い側である。

【0017】

以下では、図1(B)に示したように、ソース電極6とドレイン電極7との間においてゲート電極3とソース電極6およびドレイン電極7とが重ならない領域を「非重なり領域R1(第1領域)」とする。また、ゲート電極3とソース電極6およびドレイン電極7とが重なる領域を「重なり領域R2(第2領域)」とする。ここで言う「重なり」の有無は、TFTを上方(図1(A)における紙面の上側)から見た際に、ソース電極6およびドレイン電極7の形成領域とゲート電極3の形成領域とが重なっているか否かを意味している。

【0018】

支持基体1は、例えば、プラスチック材料、金属材料または無機材料などのいずれか1種類または2種類以上により形成されている。

【0019】

プラスチック材料は、例えば、ポリメチルメタクリレート(PMMA)、ポリビニルアルコール(PVA)、ポリビニルフェノール(PVP)、ポリエーテルサルフォン(PES)、ポリカーボネート(PC)、ポリイミド(PI)、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエチルエーテルケトン(PEEK)、ポリアクリレート(PAR)、ポリフェニレンスルフィド(PPS)またはトリアセチルセルロース(TAC)などである。金属材料は、例えば、アルミニウム(Al)、ニッケル(Ni)またはステンレスなどである。無機材料は、例えば、ケイ素(Si)、酸化ケイ素(SiOx )、窒化ケイ素(SiNx )、酸化アルミニウム(AlOx )または他の金属酸化物などである。ただし、酸化ケイ素には、ガラス、石英またはスピンオングラス(SOG)なども含まれる。

【0020】

この支持基体1は、ウェハなどの剛性を有する基板でもよいし、可撓性を有するフィルムまたは箔などでもよい。また、支持基体1の表面の少なくとも一部に、所定の機能を有する1層または2層以上の各種層が設けられていてもよい。この層は、例えば、密着性を確保するためのバッファ層、またはガス放出を防止するためのガスバリア層などである。

【0021】

なお、支持基体1は、単層でもよいし、多層でもよい。多層の場合には、上記した各種材料の層が2層以上積層されている。このように単層でも多層でもよいことは、段差絶縁層2、ゲート電極3、ゲート絶縁層4、半導体層5、ソース電極6およびドレイン電極7および後述する他の構成要素についても同様である。

【0022】

段差絶縁層2は、支持基体1の上に選択的に形成されており、より具体的には、少なくとも非重なり領域R1に配置されている。ただし、段差絶縁層2の形成領域から、重なり領域R2は除かれる。この段差絶縁層2は、ゲート電極3と半導体層5、ソース電極6およびドレイン電極7との間の距離、すなわちゲート電極3と半導体層5等とを離間させる分離絶縁層の厚さを異ならせるものである。この分離絶縁層の詳細については、後述する。また、段差絶縁層2は、例えば、無機絶縁性材料または有機絶縁性材料などのいずれか1種類または2種類以上を含んでいる。無機絶縁性材料は、例えば、酸化ケイ素、窒化ケイ素、酸化アルミニウム、酸化チタン(TiO2 )、酸化ハフニウム(HfOx )またはチタン酸バリウム(BaTiO3 )などである。有機絶縁性材料は、例えば、ポリビニルフェノール(PVP)、ポリビニルアルコール(PVA)、ポリイミド、ポリアミド、ポリエステル、ポリアクリレート、ポリメタクリル酸アクリレート、エポキシ樹脂、ベンゾシクロブテン(BCB)、フッ素樹脂、感光性ポリイミド、感光性ノボラック樹脂またはポリパラキシリレンなどである。

【0023】

なお、図1(B)では、段差絶縁層2の断面形状が台形または略台形である場合を示しているが、その断面形状は特に限定されず、他の形状(例えば矩形など)でもよい。

【0024】

ゲート電極3は、非重なり領域R1に設けられた段差絶縁層2と重なり領域R2(支持基体1)とを覆うように形成されている。このため、ゲート電極3は、非重なり領域R1において、段差絶縁層2とゲート絶縁層4との間に位置している。このゲート電極3は、例えば、金属材料、無機導電性材料、有機導電性材料または炭素材料などのいずれか1種類または2種類以上を含んでいる。

【0025】

金属材料は、例えば、アルミニウム、銅(Cu)、モリブデン(Mo)、チタン(Ti)、クロム(Cr)、ニッケル、パラジウム(Pd)、金(Au)、銀(Ag)、白金(Pt)、タングステン(W)、タンタル(Ta)またはそれらを含む合金などである。無機導電性材料は、例えば、酸化インジウム(In2 O3 )、酸化インジウムスズ(ITO)、酸化インジウム亜鉛(IZO)または酸化亜鉛(ZnO)などである。有機導電性材料は、例えば、ポリエチレンジオキシチオフェン(PEDOT)、ポリスチレンスルホン酸(PSS)またはポリアニリン(PANI)などである。炭素材料は、例えば、グラファイトなどである。なお、ゲート電極3は、例えば、PEDOT/PSSなどの多層でもよい。

【0026】

ゲート絶縁層4は、ゲート電極3の上に形成されており、そのゲート電極3と半導体層5、ソース電極6およびドレイン電極7との間に位置している。このゲート絶縁層4は、例えば、段差絶縁層2と同様の材料を含んでいる。半導体層5に近い側におけるゲート絶縁層4の表面(上面)は、できるだけ平坦であることが好ましい。ゲート絶縁層4の表面平坦性は、半導体層5の電気的特性に影響を与えるからである。より具体的には、ゲート絶縁層4の表面が平坦であると、そのゲート絶縁層4の上に半導体層5も平坦に形成されやすくなる。これにより、半導体層5中における半導体分子の配向性が向上するため、電気的特性が安定化する。

【0027】

中でも、ゲート絶縁層4は、有機絶縁性材料を含んでいることが好ましい。有機絶縁性材料が有機溶媒などに分散または溶解された溶液を用いてゲート絶縁層4を塗布形成できるため、塗布時のレベリング(平坦化)作用によりゲート絶縁層4の表面が平坦化しやすいからである。

【0028】

半導体層5は、ゲート絶縁層4の上に形成されており、無機半導体層でもよいし、有機半導体層でもよい。

【0029】

無機半導体層は、例えば、シリコンなどの無機半導体材料のいずれか1種類または2種類以上を含んでいる。また、無機半導体材料は、ZnOまたはIn2 O3 などにドーパントが添加された透明酸化物などでもよい。

【0030】

有機半導体層は、例えば、以下の有機半導体材料のいずれか1種類または2種類以上を含んでいる。(1)ポリピロール、(2)ポリチオフェン、(3)ポリイソチアナフテンなどのイソチアナフテン、(4)ポリチェニレンビニレンなどのチェニレンビニレン、(5)ポリ(p−フェニレンビニレン)などのポリ(p−フェニレンビニレン)、(6)ポリアニリン、(7)ポリアセチレン、(8)ポリジアセチレン、(9)ポリアズレン、または(10)ポリピレンである。(11)ポリカルバゾール、(12)ポリセレノフェン、(13)ポリフラン、(14)ポリ(p−フェニレン)、(15)ポリインドール、(16)ポリピリダジン、(17)ナフタセン、ペンタセン、ヘキサセン、ヘプタセン、ジベンゾペンタセン、テトラベンゾペンタセン、ピレン、ジベンゾピレン、クリセン、ペリレン、コロネン、テリレン、オバレン、クオテリレンまたはサーカムアントラセンなどのアセン、(18)アセン類のうちの炭素の一部が窒素(N)、硫黄(S)または酸素(O)などの原子、あるいはカルボニル基などの官能基により置換された誘導体、例えば、トリフェノジオキサジン、トリフェノジチアジンまたはヘキサセン−6,15−キノンなど、(19)ポリビニルカルバゾール、ポリフェニレンスルフィドまたはポリビニレンスルフィドなどの高分子材料および多環縮合体、または(20)上記した高分子材料と同じ繰り返し単位を有するオリゴマーである。(21)銅フタロシアニンなどの金属フタロシアニン、(22)テトラチアフルバレン、(23)テトラチアペンタレン、(24)ナフタレン1,4,5,8−テトラカルボン酸ジイミド、N,N’−ビス(4−トリフルオロメチルベンジル)ナフタレン1,4,5,8−テトラカルボン酸ジイミドと共に、N,N’−ビス(1H,1H−ペルフルオロオクチル)、N,N’−ビス(1H,1H−ペルフルオロブチル)またはN,N’−ジオクチルナフタレン1,4,5,8−テトラカルボン酸ジイミド誘導体、(25)ナフタレン2,3,6,7テトラカルボン酸ジイミドなどのナフタレンテトラカルボン酸ジイミド、(26)アントラセン2,3,6,7−テトラカルボン酸ジイミドなどのアントラセンテトラカルボン酸ジイミド類に代表される縮合環テトラカルボン酸ジイミド、(27)C60、C70、C76、C78またはC84などのフラーレン、(28)単層ナノチューブ(SWNT)などのカーボンナノチューブ、(29)メロシアニン色素またはヘミシアニン色素などの色素、または(30)2,9−ジナフチル−ペリキサンテノキサンテンなどのペリキサンテノキサンテン化合物である。

【0031】

この他、有機半導体材料は、上記した一連の材料の誘導体でもよい。誘導体とは、上記した材料に1または2以上の置換基が導入されたものであり、その置換基の種類および導入位置などは、任意である。

【0032】

この半導体層5のうち、非重なり領域R1に位置する部分は、実質的に電気的特性に寄与する部分(いわゆるチャネル部分)である。

【0033】

ソース電極6およびドレイン電極7は、半導体層5の上において互いに離間されるように形成されていると共に、例えば、ゲート電極3と同様の材料を含んでいる。

【0034】

ここで、上記したように、半導体層5は、ゲート電極3から分離絶縁層を介して離間されている。このゲート電極3は、段差絶縁層2とゲート絶縁層4との間に位置しているため、分離絶縁層とは、ここではゲート絶縁層4である。すなわち、分離絶縁層の厚さは、ゲート絶縁層4の厚さにより表される。この半導体層5をゲート電極3から離間させるゲート絶縁層4の厚さは、一定ではなく、場所によって異なっている。

【0035】

具体的には、図1(B)に示したように、段差絶縁層2は、支持基体1の表面のうち、少なくとも非重なり領域R1に形成されており、ゲート電極3は、非重なり領域R1における段差絶縁層2と重なり領域R2(支持基体1)とを被覆している。これにより、ゲート電極3のうち、段差絶縁層2の上に形成されている部分は、支持基体1の上に形成されている部分よりも半導体層5に近づいている。一方、半導体層5に近い側におけるゲート絶縁層4の表面は、ほぼ平坦である。このため、段差絶縁層2の有無により生じる段差を利用して、非重なり領域R1におけるゲート絶縁層4の厚さT1は、重なり領域R2におけるゲート絶縁層4の厚さT2よりも小さくなっている。

【0036】

厚さT1が厚さT2よりも小さいのは、以下の理由による。非重なり領域R1では、ゲート電極3と半導体層5との間の距離が小さくなるため、それらが互いに近づく。これにより、オン電流が減少しにくくなる。一方、重なり領域R2では、ゲート電極3とソース電極6およびドレイン電極7との間の距離が大きくなるため、それらが互いに遠ざかる。これにより、ゲート電極3とソース電極6およびドレイン電極7との間にリーク電流が流れにくくなる。

【0037】

非重なり領域R1におけるゲート絶縁層4の厚さT1と重なり領域R2におけるゲート絶縁層4の厚さT2との大小関係については、3種類の態様が考えられる。第1に、非重なり領域R1の厚さT1は、ゲート電極3とソース電極6との重なり領域R2における厚さT2よりも小さく、かつ、ゲート電極3とドレイン電極7との重なり領域R2における厚さT2よりも小さくなっていてもよい。第2に、非重なり領域R1の厚さT1は、ゲート電極3とソース電極6との重なり領域R2における厚さT2よりも小さくなっている一方で、ゲート電極3とドレイン電極7との重なり領域R2における厚さT2とほぼ同等でもよい。第3に、非重なり領域R1の厚さT1は、ゲート電極3とソース電極6との重なり領域R2における厚さT2とほぼ同等である一方で、ゲート電極3とドレイン電極7との重なり領域R2における厚さT2よりも小さくなっていてもよい。厚さT1が厚さT2よりも小さくなっている箇所が1箇所でも存在すれば、上記した利点が得られるからである。中でも、第1の態様が好ましい。リーク電流の発生確率がより低減するため、より高い効果が得られるからである。

【0038】

なお、ソース電極6およびドレイン電極7の形状(平面形状)は、特に限定されない。ここでは、図1(A)に示したように、ソース電極6は、例えば、一端部側において複数に分岐した枝部6Aを有する櫛形形状部6Bを含んでいると共に、ドレイン電極7も同様に、複数に分岐した枝部7Aを有する櫛形形状部7Bを含んでいる。これに伴い、ソース電極6とドレイン電極7とは、櫛形形状部6B,7Bにおいて互いに噛み合うように配置されている。この「互いに噛み合う」とは、ソース電極6の枝部6A間に設けられた各スペースにドレイン電極7の各枝部7Aが入り込んでいると共に、ドレイン電極7の枝部7A間に設けられた各スペースにソース電極6の各枝部6Aが入り込んでいる状態を意味している。

【0039】

この場合において、ゲート電極3は、例えば、図1(B)に示したように、少なくともソース電極6とドレイン電極7とが互いに噛み合う領域にベタ膜として設けられている。すなわち、ゲート電極3は、ソース電極6とドレイン電極7との間のチャネル領域(非重なり領域R1)ごとに分割形成されているのではなく、複数のチャネル領域を含む領域に全面形成されている。このように複数のチャネル領域を含む領域にゲート電極3がベタ膜として形成されていれば、そのベタ膜のゲート電極3は複数に分割形成されていてもよい。この場合には、ゲート絶縁層4の厚さT1,T2を異ならせることで、ゲート電極3をベタ膜として形成しても上記した利点を得ることができる。

【0040】

なお、ソース電極6またはドレイン電極7のいずれか一方だけが櫛形形状を有していてもよい。より具体的には、例えば、ソース電極6が櫛形形状部6Bを有しているのに対して、ドレイン電極7が非分岐形状(直線状)であってもよい。この場合には、ソース電極6とドレイン電極7とが互いに噛み合うために、ソース電極6の枝部6A間に設けられたスペースにドレイン電極7の一端部が入り込んでいればよい。この場合においても、同様の効果を得ることができる。もちろん、ドレイン電極7が櫛形形状部7Bを有しているのに対して、ソース電極6が非分岐形状であってもよい。

【0041】

次に、図1を参照して、上記したTFTの製造方法について説明する。なお、TFTの各構成要素の形成材料については既に詳細に説明したので、以下では、その形成材料の一例を挙げることとする。

【0042】

TFTを製造する場合には、最初に、ポリイミドなどのプラスチックフィルムの支持基体1の上に、段差絶縁層2を選択的に形成する。この場合には、例えば、支持基体1の表面にフォトレジストを塗布してフォトレジスト膜(図示せず)を形成したのち、フォトリソグラフィ法などを用いてフォトレジスト膜をパターニング(露光および現像)する。このフォトレジストしては、例えば、東京応化工業株式会社製のTELP−P003PMなどを用いることができる。また、少なくとも非重なり領域R1に形成されると共に重なり領域R2に形成されないように、段差絶縁層2の形成位置を位置合わせする。

【0043】

なお、段差絶縁層2を形成する場合には、例えば、支持基体1の表面を覆うように無機絶縁性材料または有機絶縁性材料を成膜したのち、フォトリソグラフィ法以外の方法を用いてパターニングしてもよい。このパターニング方法は、例えば、ドライエッチング法などである。この他、インクジェット法、スクリーン印刷法、オフセット印刷法またはグラビア印刷法などや、ナノインプリント法などを用いて段差絶縁層2を形成してもよい。

【0044】

続いて、非重なり領域R1における段差絶縁層2およびその周辺の重なり領域R2における支持基体1を覆うように、ゲート電極3を形成する。この場合には、例えば、段差絶縁層2および支持基体1を覆うように金属材料層(図示せず)を形成したのち、その金属材料層をパターニングする。

【0045】

金属材料層の形成材料は、例えば、アルミニウムなどであると共に、その形成方法は、例えば、スパッタリング法、蒸着法または化学気相成長(CVD)法などの気相成長法である。また、金属材料層のパターニング方法は、例えば、エッチング法などである。このエッチング法は、イオンミリング法または反応性イオンエッチング(RIE)法などのドライエッチング法でもよいし、ウェットエッチング法でもよい。

【0046】

なお、金属材料層をパターニングする場合には、フォトリソグラフィ法または紫外線描画法などを併用してもよい。この場合には、例えば、金属材料層の表面にフォトレジストを塗布してフォトレジスト膜を形成してから、フォトリソグラフィ法などを用いてフォトレジスト膜をパターニングしたのち、そのフォトレジスト膜をマスクとして金属材料層をエッチングする。ただし、フォトレジスト膜に代えて金属膜などをマスクとして用いてもよい。

【0047】

続いて、ゲート電極3を覆うようにゲート絶縁層4を形成する。この場合には、例えば、PVPが任意の有機溶媒などに溶解された溶液を準備したのち、その溶液を塗布してから乾燥させる。この塗布方法は、例えば、スピンコート法、エアドクタコータ法、ブレードコータ法、ロッドコータ法、ナイフコータ法、スクイズコータ法、リバースロールコータ法、トランスファーロールコータ法、グラビアコータ法、キスコータ法、キャストコータ法、スプレーコータ法、スリットオリフィスコータ法、カレンダーコータ法または浸漬法などである。この場合には、必要に応じて、乾燥速度を向上させるために加熱してもよい。

【0048】

このゲート絶縁層4の形成工程では、流動性を有する溶液の表面が塗布時または塗布後にレベリングされるため、段差絶縁層2の存在に起因して下地の表面が凹凸を有しているにもかかわらず、ゲート絶縁層4の表面が平坦化される。これにより、ゲート絶縁層4の形成時において、非重なり領域R1におけるゲート絶縁層4の厚さT1は、重なり領域R2におけるゲート絶縁層4の厚さT2よりも小さくなる。

【0049】

なお、ゲート電極3を形成するために用いた金属材料層の形成方法と同様の方法を用いて、ゲート絶縁層4を形成してもよい。この場合には、上記したように厚さT1を厚さT2よりも小さくするために、必要に応じて、ゲート絶縁層4の表面を平坦化してもよい。この平坦化方法は、例えば、エッチング法または研磨法なである。

【0050】

続いて、ゲート絶縁層4の上に半導体層5を形成する。この半導体層5として有機半導体層を形成する場合に用いる形成材料は、例えば、ペンタセンなどである。また、半導体層5の形成方法は、例えば、(1)抵抗加熱蒸着法、スパッタリング、蒸着法またはCVD法などの気相成長法、(2)スピンコート法、エアドクタコータ法、ブレードコータ法、ロッドコータ法、ナイフコータ法、スクイズコータ法、リバースロールコータ法、トランスファーロールコータ法、グラビアコータ法、キスコータ法、キャストコータ法、スプレーコータ法、スリットオリフィスコータ法、カレンダーコータ法または浸漬法などの塗布法である。これらの形成方法は、半導体層5の形成材料などの条件に応じて適宜選択可能である。なお、半導体層5の厚さは、特に限定されないが、例えば、50nmである。

【0051】

この半導体層5の形成工程では、平坦なゲート絶縁層4の上に半導体層5が形成されるため、その半導体層5も平坦に形成される。

【0052】

最後に、半導体層5の上に、互いに離間されたソース電極6およびドレイン電極7を形成する。この場合には、例えば、少なくとも半導体層5の表面を覆うように金属材料層(図示せず)を形成したのち、その金属材料層をパターニングする。

【0053】

この金属材料層の形成材料は、例えば、金などであると共に、その形成方法は、例えば、ゲート電極3の形成方法と同様である。ただし、金属材料層のパターニング方法は、半導体層5にダメージを及ぼしにくいウェットエッチング法が好ましい。

【0054】

このTFTによれば、半導体層5が分離絶縁層(ゲート絶縁層4)を介してゲート電極3から離間されている。また、非重なり領域R1におけるゲート絶縁層4の厚さT1は重なり領域R2におけるゲート絶縁層4の厚さT2よりも小さくなっている。よって、以下の理由により、TFTの性能向上を容易に実現できる。

【0055】

図2および図3は、比較例のTFTの構成を表しており、いずれも図1(B)に対応する断面構成を示している。この比較例のTFTは、段差絶縁層2を備えておらず、非重なり領域R1におけるゲート絶縁層4の厚さT3が重なり領域R2におけるゲート絶縁層4の厚さT4と等しいことを除き、図1に示したTFTと同様の構成を有している。ただし、図2では厚さT3,T4=T1であると共に、図3では厚さT3,T4=T2である。

【0056】

図2に示した比較例では、非重なり領域R1において半導体層5がゲート電極3に近づくため、オン電流が増加するが、重なり領域R2においてソース電極6およびドレイン電極7もゲート電極3に近づくため、それらの間にリーク電流が流れやすくなる。また、図3に示した比較例では、重なり領域R2においてソース電極6およびドレイン電極7がゲート電極3から遠ざかるため、それらの間にリーク電流が流れにくくなるが、非重なり領域R1において半導体層5がゲート電極3から遠ざかるため、オン電流が減少する。

【0057】

これに対して、図1に示した本実施形態では、上記したように、重なり領域R2においてソース電極6およびドレイン電極7がゲート電極3から遠ざかるため、それらの間にリーク電流が流れにくくなる。また、非重なり領域R1において半導体層5がゲート電極3に近づくため、オン電流が増加する。しかも、上記した利点は、ゲート絶縁層4の形成材料として既存の材料を用いることができる一方で、表面改質などの煩雑な手法を用いなくも簡単に得られる。よって、TFTの性能向上を容易に実現できるのである。

【0058】

特に、段差絶縁層2が非重なり領域R1だけに形成されていれば、その段差絶縁層2の有無により生じる段差を利用して、厚さT1を厚さT2よりも容易に小さくできる。この場合には、半導体層5に近い側におけるゲート絶縁層4の表面が平坦であれば、段差絶縁層2を利用して確実に厚さT1を厚さT2よりも小さくできる。しかも、半導体層5が有機半導体層である場合には、その半導体層5が平坦であれば、有機半導体分子の配向性が向上するため、TFTの性能をより向上させることができる。

【0059】

<2.変形例>

[TFTの型]

図1(B)では、TFTをボトムゲート・トップコンタクト型にしたが、これに限られない。例えば、TFTは、図4に示したボトムゲート・ボトムコンタクト型、図5に示したトップゲート・トップコンタクト型、または図6に示したトップゲート・ボトムコンタクト型でもよい。これらのTFTの構成および製造方法は、一連の構成要素の積層順が異なることを除き、図1に示したTFTの構成および製造方法と同様である。

【0060】

ボトムゲート・ボトムコンタクト型のTFTは、図4に示したように、支持基体1の上に、段差絶縁層2と、ゲート電極3と、ゲート絶縁層4と、ソース電極6およびドレイン電極7と、半導体層5とをこの順に備えている。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ボトムゲート・トップコンタクト型と同様に、ゲート絶縁層4である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さにより表される。

【0061】

トップゲート・トップコンタクト型のTFTは、図5に示したように、支持基体1の上に、半導体層5と、ソース電極6およびドレイン電極7と、ゲート絶縁層4と、段差絶縁層2と、ゲート電極3とをこの順に備えている。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ボトムゲート・トップコンタクト型とは異なり、ゲート絶縁層4および段差絶縁層2である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さと段差絶縁層2の厚さとの和により表される。

【0062】

トップゲート・ボトムコンタクト型のTFTは、図6に示したように、支持基体1の上に、ソース電極6およびドレイン電極7と、半導体層5と、ゲート絶縁層4と、段差絶縁層2と、ゲート電極3とをこの順に備えている。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、トップゲート・トップコンタクト型と同様に、ゲート絶縁層4および段差絶縁層2である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さと段差絶縁層2の厚さとの和により表される。

【0063】

これらのTFTにおいても、非重なり領域R1における分離絶縁層の厚さT1が重なり領域R2における分離絶縁層の厚さT2よりも小さくなるため、ボトムゲート・トップコンタクト型(図1)と同様の作用および効果を得ることができる。

【0064】

ただし、半導体層5として有機半導体層を備えたTFTでは、上記したように、半導体層5が平坦であると有機半導体分子の配向性が向上する。よって、半導体層5が平坦に形成されやすいボトムゲート・トップコンタクト型またはトップゲート・トップコンタクト型が好ましい。

【0065】

[段差絶縁層の形成位置]

図1(B)では、厚さT1,T2を異ならせるために、支持基体1の上に段差絶縁層2を形成したが、その段差絶縁層2の形成位置を変更してもよい。例えば、ボトムゲート・トップコンタクト型のTFTでは、図7に示したように、ゲート絶縁層4の上の少なくとも重なり領域R2に段差絶縁層2を形成してもよい。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ゲート絶縁層4および段差絶縁層2である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さと段差絶縁層2の厚さとの和により表される。この場合においても、非重なり領域R1における分離絶縁層の厚さT1が重なり領域R2における分離絶縁層の厚さT2よりも小さくなるため、同様の効果を得ることができる。

【0066】

もちろん、図4〜図6に示したTFTにおいて、段差絶縁層2の形成位置を変更してもよい。ただし、半導体層5が有機半導体層である場合には、その半導体層5を平坦化して有機半導体分子の配向性を向上させるために、半導体層5の直下に段差絶縁層2を形成しないことが好ましい。すなわち、ボトムゲート・トップコンタクト型では、図7の構成よりも図1(B)の構成が好ましい。

【0067】

[厚さT1,T2を異ならせる構成]

図1(B)に示したボトムゲート・トップコンタクト型のTFTでは、段差絶縁層2の有無による段差を利用して厚さT1,T2を異ならせるようにしたが、これに限られない。例えば、図8に示したように、段差絶縁層2を形成する代わりに、非重なり領域R1と重なり領域R2とにおいてゲート電極3の厚さを異ならせてもよい。具体的には、厚さT1を厚さT2よりも小さくするために、非重なり領域R1におけるゲート電極3の厚さT5を重なり領域R2におけるゲート電極3の厚さT6を大きくしてもよい。このTFTにおいて厚さT1,T2に違いをもたらす分離絶縁層は、ゲート絶縁層4である。このため、分離絶縁層の厚さは、ゲート絶縁層4の厚さにより表される。

【0068】

このゲート電極3を形成する場合には、例えば、非重なり領域R1および重なり領域R2に厚さT5を有するゲート電極3を形成したのち、重なり領域R2におけるゲート電極3をエッチングなどしてもよい。このエッチング法は、例えば、イオンミリング法またはRIE法などのドライエッチング法である。または、例えば、非重なり領域R1および重なり領域R2に厚さT6を有するゲート電極3を形成したのち、非重なり領域R1にゲート電極3を追加形成してもよい。この場合には、非重なり領域R1におけるゲート電極3が2層になる。ただし、非重なり領域R1に形成されるゲート電極3は、2層に限らず、3層以上でもよい。もちろん、非重なり領域R1におけるゲート電極3と重なり領域R2におけるゲート電極3とを別工程において形成してもよい。

【0069】

この場合においても、ゲート電極3の厚さT5,T6の違いを利用して、非重なり領域R1における分離絶縁層の厚さT1が重なり領域R2における分離絶縁層の厚さT2よりも小さくなるため、同様の効果を得ることができる。

【0070】

もちろん、図4および図7に示したボトムゲート型のTFTにおいて、段差絶縁層2を形成する代わりにゲート電極3の厚さを異ならせてもよい。ボトムゲート型であれば、図8に示した場合と同様の作用および効果が得られるからである。この他、段差絶縁層2を形成する代わりに、ゲート電極3の厚さT5,T6を異ならせた場合と同様に、ゲート絶縁層4を形成してからその一部をエッチングしたり、ゲート絶縁層4の一部を2層以上にすることで、厚さT1,T2を異ならせてもよい。

【0071】

なお、図1および図4〜図8などを参照しながら説明した上記一連の態様の1種類または2種類以上を任意に組み合わせてもよい。

【0072】

<3.薄膜トランジスタの適用例(電子機器)>

次に、上記したTFTの適用例について説明する。このTFTは、例えば、以下で説明するように、いくつかの電子機器に適用可能である。

【0073】

<3−1.液晶表示装置>

TFTは、例えば、液晶表示装置に適用される。図9および図10は、それぞれ液晶表示装置の断面構成および回路構成を表している。なお、以下で説明する装置構成(図9)および回路構成(図10)はあくまで一例であるため、それらの構成は適宜変更可能である。

【0074】

ここで説明する液晶表示装置は、例えば、TFTを用いたアクティブマトリクス駆動方式の透過型液晶ディスプレイであり、そのTFTは、スイッチング(画素選択)用の素子として用いられる。この液晶表示装置は、図9に示したように、駆動基板20と対向基板30との間に液晶層41が封入されたものである。

【0075】

駆動基板20は、例えば、支持基板21の一面にTFT22、平坦化絶縁層23および画素電極24がこの順に積層されると共に、TFT22および画素電極24がマトリクス状に配置されたものである。ただし、1画素内に含まれるTFT22の数は、1つでもよいし、2つ以上でもよい。図9および図10では、例えば、1画素内に1つのTFT22が含まれる場合を示している。

【0076】

支持基板21は、例えば、ガラスまたはプラスチック材料などの透過性材料により形成されており、TFT22は、上記したTFTと同様の構成を有している。プラスチック材料の種類は、例えば、上記したTFTについて説明した場合と同様であり、そのことは、以降で説明するプラスチック材料に関しても同様である。平坦化絶縁層23は、例えば、ポリイミドなどの絶縁性樹脂材料を含んでおり、画素電極24は、例えば、ITOなどの透過性導電性材料を含んでいる。なお、画素電極24は、平坦化絶縁層23に設けられたコンタクトホール(図示せず)を通じてTFT22に接続されている。

【0077】

対向基板30は、例えば、支持基板31の一面に対向電極32が全面形成されたものである。支持基板31は、例えば、ガラスまたはプラスチック材料などの透過性材料により形成されており、対向電極32は、例えば、ITOなどの透過性導電性材料を含んでいる。

【0078】

駆動基板20および対向基板30は、液晶層41を挟んで画素電極24と対向電極32とが対向するように配置されていると共に、シール材40により貼り合わされている。液晶層41に含まれる液晶分子の種類は、任意に選択可能である。

【0079】

この他、液晶表示装置は、例えば、位相差板、偏光板、配向膜およびバックライトユニットなどの他の構成要素(いずれも図示せず)を備えていてもよい。

【0080】

液晶表示装置を駆動させるための回路は、例えば、図10に示したように、TFT22および液晶表示素子44(画素電極24、対向電極32および液晶層41を含む素子部)と共に、キャパシタ45を含んでいる。この回路では、行方向に複数の信号線42が配列されていると共に列方向に複数の走査線43が配列されており、それらが交差する位置にTFT22、液晶表示素子44およびキャパシタ45が配置されている。TFT22におけるソース電極、ゲート電極およびドレイン電極の接続先は、図10に示した態様に限らず、任意に変更可能である。信号線42および走査線43は、それぞれ図示しない信号線駆動回路(データドライバ)および走査線駆動回路(走査ドライバ)に接続されている。

【0081】

この液晶表示装置では、TFT22により液晶表示素子44が選択され、画素電極24と対向電極32との間に電界が印加されると、その電界強度に応じて液晶層41における液晶分子の配向状態が変化する。これにより、液晶分子の配向状態に応じて光の透過量(透過率)が制御されるため、画像が表示される。

【0082】

この液晶表示装置によれば、TFT22が上記したTFTと同様の構成を有しているので、既存の材料を用いると共に煩雑な手法を用いなくても、TFT22においてオン電流が増加すると共にリーク電流が流れにくくなる。よって、表示性能を容易に向上させることができる。なお、液晶表示装置は、透過型に限らずに反射型でもよい。

【0083】

<3−2.有機EL表示装置>

TFTは、例えば、有機EL表示装置に適用される。図11および図12は、それぞれ有機EL表示装置の断面構成および回路構成を表している。なお、以下で説明する装置構成(図11)および回路構成(図12)はあくまで一例であるため、それらの構成は適宜変更可能である。

【0084】

ここで説明する有機EL表示装置は、例えば、TFTをスイッチング用の素子として用いたアクティブマトリクス駆動方式の有機ELディスプレイである。この有機EL表示装置は、駆動基板50と対向基板60とが接着層70を介して貼り合わされたものであり、例えば、対向基板60を経由して光を放出するトップエミッション型である。

【0085】

駆動基板50は、例えば、支持基板51の一面にTFT52、保護層53、平坦化絶縁層54、画素分離絶縁層55、画素電極56、有機層57、対向電極58および保護層59がこの順に積層されたものである。TFT52、画素電極56および有機層57は、マトリクス状に配置されている。ただし、1画素内に含まれるTFT52の数は、1つでもよいし、2つ以上でもよい。図11および図12では、例えば、1画素内に2つのTFT52(選択用TFT52Aおよび駆動用TFT52B)が含まれる場合を示している。

【0086】

支持基板51は、例えば、ガラスまたはプラスチック材料などにより形成されている。トップエミッション型では対向基板60から光が取り出されるため、支持基板51は、透過性材料または非透過性材料のいずれにより形成されていてもよい。TFT52は、上記したTFTと同様の構成を有しており、保護層53は、例えば、PVAまたはポリパラキシリレンなどの高分子材料を含んでいる。平坦化絶縁層54および画素分離絶縁層55は、例えば、ポリイミドなどの絶縁性樹脂材料を含んでいる。この画素分離絶縁層55は、例えば、形成工程を簡略化すると共に所望の形状に形成可能にするために、光パターニングまたはリフローなどにより成形可能な感光性樹脂材料を含んでいることが好ましい。なお、保護層53により十分な平坦性が得られていれば、平坦化絶縁層54はなくてもよい。

【0087】

画素電極56は、例えば、アルミニウム、銀、チタンまたはクロムなどの反射性材料を含んでおり、対向電極58は、例えば、ITOまたはIZOなどの透過性導電性材料を含んでいる。ただし、カルシウム(Ca)などの透過性の金属材料またはその合金や、PEDOTなどの透過性の有機導電性材料を含んでいてもよい。有機層57は、赤色、緑色または青色などの光を発生させる発光層を含んでおり、必要に応じて正孔輸送層および電子輸送層などを含む積層構造を有していてもよい。発光層の形成材料は、発生させる光の色に応じて任意に選択可能である。画素電極56および有機層57は、画素分離絶縁層55により分離されながらマトリクス状に配置されているのに対して、対向電極58は、有機層57を介して画素電極56に対向しながら連続的に延在している。保護層59は、例えば、酸化ケイ素、酸化アルミニウム、窒化ケイ素、ポリパラキシリレンまたはウレタンなどの光透過性誘電材料を含んでいる。なお、画素電極56は、保護層53および平坦化絶縁層54に設けられたコンタクトホール(図示せず)を通じてTFT52に接続されている。

【0088】

対向基板60は、例えば、支持基板61の一面にカラーフィルタ62が設けられたものである。支持基板61は、例えば、ガラスまたはブラスチック材料などの透過性材料により形成されており、カラーフィルタ62は、有機層57において発生した光の色に対応する複数の色領域を有している。ただし、カラーフィルタ62はなくてもよい。

【0089】

接着層70は、例えば、熱硬化型樹脂などの接着剤である。

【0090】

有機EL表示装置を駆動させるための回路は、例えば、図12に示したように、TFT52(選択用TFT52Aおよび駆動用TFT52B)および有機EL表示素子73(画素電極56、有機層57および対向電極58を含む素子部)と共に、キャパシタ74を含んでいる。この回路では、複数の信号線71および走査線72が交差する位置に、TFT52、有機EL表示素子73およびキャパシタ74が配置されている。選択用TFT52Aおよび駆動用TFT52Bにおけるソース電極、ゲート電極およびドレイン電極の接続先は、図12に示した態様に限らず、任意に変更可能である。

【0091】

この有機EL表示装置では、例えば、選択用TFT52Aにより有機EL表示素子73が選択されると、その有機EL表示素子73が駆動用TFT52Bにより駆動される。この場合には、画素電極56と対向電極58との間に電界が印加されると、有機層57において光が発生する。これにより、例えば、隣り合う3つの有機EL表示素子73において、それぞれ赤色、緑色または青色の光が発生する。これらの光の合成光が対向基板60を経由して外部へ放出されるため、画像が表示される。

【0092】

この有機EL表示装置によれば、TFT52が上記したTFTと同様の構成を有しているので、液晶表示装置と同様に表示性能を容易に向上させることができる。

【0093】

なお、有機EL表示装置は、トップエミッション型に限らず、駆動基板50を経由して光を放出するボトムエミッション型でもよいし、駆動基板50および対向基板60の双方を経由して光を放出するデュアルエミッション型でもよい。この場合には、画素電極56および対向電極58のうち、光が放出される側の電極が透過性材料により形成され、光が放出されない側の電極が反射性材料により形成されることになる。

【0094】

<3−3.電子ペーパー表示装置>

TFTは、例えば、電子ペーパー表示装置に適用される。図13は、電子ペーパー表示装置の断面構成を表している。なお、以下で説明する装置構成(図13)および図10を参照して説明する回路構成はあくまで一例であるため、それらの構成は適宜変更可能である。

【0095】

ここで説明する電子ペーパー表示装置は、例えば、TFTをスイッチング用の素子として用いたアクティブマトリクス駆動方式の電子ペーパーディスプレイである。この電子ペーパー表示装置は、例えば、駆動基板80と電気泳動素子93を含む対向基板90とが接着層100を介して貼り合わされたものである。

【0096】

駆動基板80は、例えば、支持基板81の一面にTFT82、保護層83、平坦化絶縁層84および画素電極85がこの順に積層されると共に、TFT82および画素電極85がマトリクス状に配置されたものである。支持基板81は、例えば、ガラスまたはプラスチック材料などにより形成されており、TFT82は、上記したTFTと同様の構成を有している。保護層83および平坦化絶縁層84は、例えば、ポリイミドなどの絶縁性樹脂材料を含んでおり、画素電極85は、例えば、銀などの金属材料を含んでいる。なお、画素電極85は、保護層83および平坦化絶縁層84に設けられたコンタクトホール(図示せず)を通じてTFT82に接続されている。また、保護層83により十分な平坦性が得られていれば、平坦化絶縁層84はなくてもよい。

【0097】

対向基板90は、例えば、支持基板91の一面に、対向電極92と、複数の電気泳動素子93を含む層とがこの順に積層されると共に、その対向電極92が全面形成されたものである。支持基板91は、例えば、ガラスまたはプラスチック材料などの透過性材料により形成されており、対向電極92は、例えば、ITOなどの透過性導電性材料を含んでいる。電気泳動素子93は、電気泳動現象を利用してコントラストを生じさせるものであり、その構成は任意である。

【0098】

この他、電子ペーパー表示装置は、例えば、カラーフィルタなどの他の構成要素(図示せず)を備えていてもよい。

【0099】

電子ペーパー表示装置を駆動させるための回路は、例えば、図10に示した液晶表示装置の回路と同様の構成を有している。電子ペーパー表示装置の回路は、TFT22および液晶表示素子44の代わりに、それぞれTFT82および電子ペーパー表示素子(画素電極85、対向電極92および電気泳動素子93を含む素子部)を含んでいる。

【0100】

この電子ペーパー表示装置では、TFT82により電子ペーパー表示素子が選択され、画素電極85と対向電極92との間に電界が印加されると、その電界に応じて電気泳動素子93においてコントラストが生じるため、画像が表示される。

【0101】

この電子ペーパー表示装置によれば、TFT82が上記したTFTと同様の構成を有しているので、液晶表示装置と同様に表示性能を容易に向上させることができる。

【0102】

以上、実施形態を挙げて本技術を説明したが、本技術は実施形態で説明した態様に限定されず、種々の変形が可能である。例えば、本技術の薄膜トランジスタが適用される電子機器は、液晶表示装置、有機EL表示装置または電子ペーパー表示装置に限らず、他の表示装置でもよい。このような他の表示装置としては、例えば、MEMS(Micro Electro Mechanical Systems)表示部(MEMS型ディスプレイ)などが挙げられる。この場合においても、表示性能を向上させることができる。

【0103】

また、例えば、本技術の薄膜トランジスタは、表示装置以外の他の電子機器に適用されてもよい。このような電子機器としては、例えば、センサマトリクス、メモリセンサ、RFIDタグ(Radio Frequency Identification)またはセンサアレイなどが挙げられる。この場合においても、性能向上を図ることができる。

【0104】

なお、本技術は以下のような構成を取ることも可能である。

(1)

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

薄膜トランジスタ。

(2)

前記半導体層は有機半導体層である、

上記(1)に記載の薄膜トランジスタ。

(3)

前記分離絶縁層はゲート絶縁層を含み、そのゲート絶縁層は有機絶縁性材料を含む、

上記(1)または(2)に記載の薄膜トランジスタ。

(4)

前記第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さいと共に、前記ゲート電極と前記ドレイン電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さい、

上記(1)ないし(3)のいずれかに記載の薄膜トランジスタ。

(5)

前記第1領域に設けられた段差絶縁層と、

前記ゲート電極と前記半導体層、前記ソース電極および前記ドレイン電極との間に設けられたゲート絶縁層と

備え、

前記第1領域において前記ゲート電極は、前記段差絶縁層と前記ゲート絶縁層との間に位置し、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

上記(1)ないし(4)のいずれかに記載の薄膜トランジスタ。

(6)

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている

上記(5)に記載の薄膜トランジスタ。

(7)

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記ソース電極および前記ドレイン電極が形成され、

前記ゲート絶縁層、前記ソース電極および前記ドレイン電極の上に前記半導体層が形成されている、

上記(5)に記載の薄膜トランジスタ。

(8)

前記第2領域に設けられた段差絶縁層と、

前記半導体層、前記ソース電極および前記ドレイン電極と前記段差絶縁層との間に設けられたゲート絶縁層と

を備え、

前記第2領域において前記段差絶縁層は、前記ゲート絶縁層と前記ゲート電極との間に位置し、

前記分離絶縁層は前記ゲート絶縁層および前記段差絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さと前記段差絶縁層の厚さとの和により表される、

上記(1)ないし(4)のいずれかに記載の薄膜トランジスタ。

(9)

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成され、

前記半導体層、前記ソース電極および前記ドレイン電極の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

上記(8)に記載の薄膜トランジスタ。

(10)

前記第1領域と、前記第2領域に設けられた前記ソース電極および前記ドレイン電極と、を覆うように前記半導体層が形成され、

前記半導体層の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

上記(8)に記載の薄膜トランジスタ。

(11)

前記第1領域における前記ゲート電極の厚さは、前記第2領域における前記ゲート電極の厚さよりも大きい、

上記(1)ないし(4)のいずれかに記載の薄膜トランジスタ。

(12)

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁層を備え、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

上記(11)に記載の薄膜トランジスタ。

(13)

前記第1領域および前記第2領域に設けられた前記ゲート電極を覆うように前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている、

上記(12)に記載の薄膜トランジスタ。

(14)

前記ソース電極および前記ドレイン電極のうちの少なくとも一方は、複数に分岐した枝部を有する櫛形形状部を含み、

前記ソース電極と前記ドレイン電極とは、前記櫛形形状部において互いに噛み合うように配置されており、

前記ゲート電極は、少なくとも前記ソース電極と前記ドレイン電極部とが互いに噛み合う領域にベタ膜として設けられている、

上記(1)ないし(13)のいずれかに記載の薄膜トランジスタ。

(15)

薄膜トランジスタを備え、その薄膜トランジスタは、

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

電子機器。

【符号の説明】

【0105】

1…支持基体、2…段差絶縁層、3…ゲート電極、4…ゲート絶縁層、5…半導体層、6…ソース電極、7…ドレイン電極、R1…非重なり領域、R2…重なり領域、T1〜T6…厚さ。

【特許請求の範囲】

【請求項1】

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

薄膜トランジスタ。

【請求項2】

前記半導体層は有機半導体層である、

請求項1記載の薄膜トランジスタ。

【請求項3】

前記分離絶縁層はゲート絶縁層を含み、そのゲート絶縁層は有機絶縁性材料を含む、

請求項1記載の薄膜トランジスタ。

【請求項4】

前記第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さいと共に、前記ゲート電極と前記ドレイン電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さい、

請求項1記載の薄膜トランジスタ。

【請求項5】

前記第1領域に設けられた段差絶縁層と、

前記ゲート電極と前記半導体層、前記ソース電極および前記ドレイン電極との間に設けられたゲート絶縁層と

備え、

前記第1領域において前記ゲート電極は、前記段差絶縁層と前記ゲート絶縁層との間に位置し、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

請求項1記載の薄膜トランジスタ。

【請求項6】

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている

請求項5記載の薄膜トランジスタ。

【請求項7】

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記ソース電極および前記ドレイン電極が形成され、

前記ゲート絶縁層、前記ソース電極および前記ドレイン電極の上に前記半導体層が形成されている、

請求項5記載の薄膜トランジスタ。

【請求項8】

前記第2領域に設けられた段差絶縁層と、

前記半導体層、前記ソース電極および前記ドレイン電極と前記段差絶縁層との間に設けられたゲート絶縁層と

を備え、

前記第2領域において前記段差絶縁層は、前記ゲート絶縁層と前記ゲート電極との間に位置し、

前記分離絶縁層は前記ゲート絶縁層および前記段差絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さと前記段差絶縁層の厚さとの和により表される、

請求項1記載の薄膜トランジスタ。

【請求項9】

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成され、

前記半導体層、前記ソース電極および前記ドレイン電極の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

請求項8記載の薄膜トランジスタ。

【請求項10】

前記第1領域と、前記第2領域に設けられた前記ソース電極および前記ドレイン電極と、を覆うように前記半導体層が形成され、

前記半導体層の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

請求項8記載の薄膜トランジスタ。

【請求項11】

前記第1領域における前記ゲート電極の厚さは、前記第2領域における前記ゲート電極の厚さよりも大きい、

請求項1記載の薄膜トランジスタ。

【請求項12】

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁層を備え、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

請求項11記載の薄膜トランジスタ。

【請求項13】

前記第1領域および前記第2領域に設けられた前記ゲート電極を覆うように前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている、

請求項12記載の薄膜トランジスタ。

【請求項14】

前記ソース電極および前記ドレイン電極のうちの少なくとも一方は、複数に分岐した枝部を有する櫛形形状部を含み、

前記ソース電極と前記ドレイン電極とは、前記櫛形形状部において互いに噛み合うように配置されており、

前記ゲート電極は、少なくとも前記ソース電極と前記ドレイン電極部とが互いに噛み合う領域にベタ膜として設けられている、

請求項1記載の薄膜トランジスタ。

【請求項15】

薄膜トランジスタを備え、その薄膜トランジスタは、

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

電子機器。

【請求項1】

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

薄膜トランジスタ。

【請求項2】

前記半導体層は有機半導体層である、

請求項1記載の薄膜トランジスタ。

【請求項3】

前記分離絶縁層はゲート絶縁層を含み、そのゲート絶縁層は有機絶縁性材料を含む、

請求項1記載の薄膜トランジスタ。

【請求項4】

前記第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さいと共に、前記ゲート電極と前記ドレイン電極とが重なる前記第2領域における前記分離絶縁層の厚さよりも小さい、

請求項1記載の薄膜トランジスタ。

【請求項5】

前記第1領域に設けられた段差絶縁層と、

前記ゲート電極と前記半導体層、前記ソース電極および前記ドレイン電極との間に設けられたゲート絶縁層と

備え、

前記第1領域において前記ゲート電極は、前記段差絶縁層と前記ゲート絶縁層との間に位置し、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

請求項1記載の薄膜トランジスタ。

【請求項6】

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている

請求項5記載の薄膜トランジスタ。

【請求項7】

前記第1領域に設けられた前記段差絶縁層と、前記第2領域と、を覆うように前記ゲート電極が形成され、

前記ゲート電極の上に前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記ソース電極および前記ドレイン電極が形成され、

前記ゲート絶縁層、前記ソース電極および前記ドレイン電極の上に前記半導体層が形成されている、

請求項5記載の薄膜トランジスタ。

【請求項8】

前記第2領域に設けられた段差絶縁層と、

前記半導体層、前記ソース電極および前記ドレイン電極と前記段差絶縁層との間に設けられたゲート絶縁層と

を備え、

前記第2領域において前記段差絶縁層は、前記ゲート絶縁層と前記ゲート電極との間に位置し、

前記分離絶縁層は前記ゲート絶縁層および前記段差絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さと前記段差絶縁層の厚さとの和により表される、

請求項1記載の薄膜トランジスタ。

【請求項9】

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成され、

前記半導体層、前記ソース電極および前記ドレイン電極の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

請求項8記載の薄膜トランジスタ。

【請求項10】

前記第1領域と、前記第2領域に設けられた前記ソース電極および前記ドレイン電極と、を覆うように前記半導体層が形成され、

前記半導体層の上に前記ゲート絶縁層が形成され、

前記第2領域において前記ゲート絶縁層の上に前記段差絶縁層が形成され、

前記ゲート絶縁層と、前記第2領域に設けられた前記段差絶縁層と、を覆うように前記ゲート電極が形成されている、

請求項8記載の薄膜トランジスタ。

【請求項11】

前記第1領域における前記ゲート電極の厚さは、前記第2領域における前記ゲート電極の厚さよりも大きい、

請求項1記載の薄膜トランジスタ。

【請求項12】

前記ゲート電極と前記半導体層との間に設けられたゲート絶縁層を備え、

前記分離絶縁層は前記ゲート絶縁層であり、その分離絶縁層の厚さは前記ゲート絶縁層の厚さにより表される、

請求項11記載の薄膜トランジスタ。

【請求項13】

前記第1領域および前記第2領域に設けられた前記ゲート電極を覆うように前記ゲート絶縁層が形成され、

前記ゲート絶縁層の上に前記半導体層が形成され、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成されている、

請求項12記載の薄膜トランジスタ。

【請求項14】

前記ソース電極および前記ドレイン電極のうちの少なくとも一方は、複数に分岐した枝部を有する櫛形形状部を含み、

前記ソース電極と前記ドレイン電極とは、前記櫛形形状部において互いに噛み合うように配置されており、

前記ゲート電極は、少なくとも前記ソース電極と前記ドレイン電極部とが互いに噛み合う領域にベタ膜として設けられている、

請求項1記載の薄膜トランジスタ。

【請求項15】

薄膜トランジスタを備え、その薄膜トランジスタは、

ゲート電極と、

そのゲート電極から分離絶縁層を介して離間された半導体層と、

その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極と

を備え、

前記ソース電極と前記ドレイン電極との間において前記ゲート電極と前記ソース電極および前記ドレイン電極とが重ならない第1領域における前記分離絶縁層の厚さは、前記ゲート電極と前記ソース電極および前記ドレイン電極のうちの少なくとも一方とが重なる第2領域における前記分離絶縁層の厚さよりも小さい、

電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−62307(P2013−62307A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−198457(P2011−198457)

【出願日】平成23年9月12日(2011.9.12)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月12日(2011.9.12)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]