薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置に関する。

【背景技術】

【0002】

現在、一般的な平面薄型画像表示装置(Flat Panel Display;FPD)は非晶質シリコンや多結晶シリコンを活性層に用いた電界効果トランジスタのアクティブマトリックスにより駆動されている。

【0003】

一方、FPDのさらなる薄型化、軽量化、耐破損性の向上を求めて、ガラス基板の替わりに樹脂基板を用いる試みが近年なされている。

【0004】

しかし、上述のシリコン薄膜を用いるトランジスタの製造は、比較的高温の熱工程を要し、一般的に耐熱性の低い樹脂基板上に直接形成することは困難である。

【0005】

そこで、低温形成が可能な酸化物半導体を活性層とした薄膜トランジスタの開発が活発に行われている(例えば、特許文献1)。

【0006】

そして、上述の酸化物半導体を活性層とした薄膜トランジスタのゲート絶縁層としては、例えばプラズマCVD法やマグネトロンスパッタ法で形成した酸化シリコン、窒化シリコン等の単膜またはそれらを積層した膜が用いられている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2006−165532号公報

【特許文献2】特開2007−73697号公報

【0008】

しかし、プラズマCVD法やマグネトロンスパッタ法で樹脂基板上に低温成膜したゲート絶縁層は、基板との密着性が低いため、基板からゲート絶縁層が剥がれやすく、信頼性の高い薄膜トランジスタが得られないという問題があった。

【0009】

よって、基板とゲート絶縁層との間に密着層を設ける必要があるが、密着層を設けるために工程を一つ増加させることによる製造コストの増加が懸念される。

【発明の概要】

【発明が解決しようとする課題】

【0010】

そこで本発明では、上記のような要求を解決するため、基板とゲート絶縁層間に、工程数を増加させることなく密着層を形成することにより、高品質で低コストの薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、上記の課題を解決するために、以下の構成を採用した。

【0012】

第1の発明は、ボトムゲート型の薄膜トランジスタである。当該ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。

【0013】

第2の発明は、上記第1の発明において、金属は、Alを含む金属であることを特徴とする。

【0014】

第3の発明は、上記第1または第2の発明において、ゲート電極の膜厚は、10nm以上100nm以下であることを特徴とする。

【0015】

第4の発明は、上記第1または第2の発明において、ゲート絶縁層は、酸化シリコン、窒化シリコン、シリコンオキシナイトライドの少なくとも何れか一種の化合物を含むことを特徴とする。

【0016】

第5の発明は、上記第1または第2の発明において、ゲート絶縁層上に金属酸化物半導体層を、さらに備える。また、金属酸化物半導体層は、In、Zn、Gaの少なくとも何れか一種の元素を含むことを特徴とする。

【0017】

第6の発明は、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備えるボトムゲート型の薄膜トランジスタの製造方法である。当該製造方法は、樹脂基板上に金属を含む膜を成膜する金属膜成膜工程と、樹脂基板上においてゲート電極となる部分をレジストで覆うレジスト被覆工程と、樹脂基板を高温水処理する高温水処理工程と、レジストで覆われていない樹脂基板上の金属を含む膜をオキシ水酸化するオキシ水酸化工程とを備える。

【0018】

第7の発明は、上記第6の発明において、金属は、Alを含む金属であることを特徴とする。

【0019】

第8の発明は、上記第6または第7の発明において、高温水処理工程は、レジストで覆われている部分にゲート電極と、レジストで覆われていない部分に絶縁性密着層とを形成することを特徴とする。

【0020】

第9の発明は、上記第6または第7の発明において、高温水処理工程における高温水処理時の温度は、100℃以上180℃以下であることを特徴とする。

【0021】

第10の発明は、画像表示装置である。当該画像表示装置は、上記第1乃至5の何れか1に記載のボトムゲート型の薄膜トランジスタのアレイと画像表示媒体とからなることを特徴とする。

【0022】

第11の発明は、上記第10の発明において、画像表示媒体は、電気泳動方式によるものであることを特徴とする。

【発明の効果】

【0023】

本発明によれば、本発明によれば、高品質で低コストの薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置を提供することが可能となる。つまり、ゲート電極を金属、絶縁性密着層をゲート電極に含まれる金属のオキシ水酸化物を含むものとすることで、十分な導電性を有するゲート電極と、基板およびゲート絶縁層に対し高密着性を有する絶縁性密着層を持つ薄膜トランジスタを得ることが可能となる。

【0024】

また、ゲート電極の膜厚を10nm以上、100nm以下とすることで、十分な導電性を持つゲート電極と十分な絶縁性を有する密着層を得ることが可能となる。10nm未満であると島状成長により膜中に膜が形成されていない部分が生じるという問題が起こりうる。また100nmを越えると、Alを含む金属材料を膜内部まで完全にオキシ水酸化することが困難となり、十分な絶縁性を有する密着層を得ることができない。

【0025】

また、ゲート絶縁層を、酸化シリコン、窒化シリコン、シリコンオキシナイトライド、酸化アルミ二ウムのいずれか一種の化合物を含む材料で形成することで、ゲート絶縁層として十分な耐電圧を持たせることができる。

【0026】

また、金属酸化物半導体層をIn、Zn、Gaのいずれか一種を含む材料で形成することで樹脂基板上に低温で高品質な薄膜トランジスタを形成することができる。

【0027】

また、基板上に金属を含む膜を成膜する工程、ゲート電極となる部分をレジストで覆う工程と、基板を高温水処理し、非レジスト被覆部の金属を含む膜をオキシ水酸化する工程を含むことで、非レジスト被覆部には絶縁性密着層、レジスト被覆部には金属ゲート電極が形成され、ゲート電極と密着層とを同時に形成することが可能となる。つまり樹脂基板上に、工程数を増やすことなく、ゲート絶縁層と絶縁性密着層とを形成することが可能となる。

【0028】

また、Alを含む金属材料への高温水処理時の温度を100℃以上とすることで、密着層となる領域を十分にオキシ水酸化することが可能となる。また180℃以下とすることで、安価な樹脂基板を用いても基板にダメージを与えることなく処理を行うことが可能となる。

【図面の簡単な説明】

【0029】

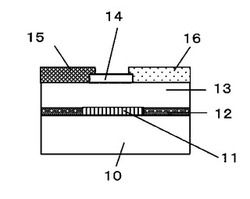

【図1】本発明の一実施形態に係る薄膜トランジスタの構造を表す概略断面図

【図2】本発明の他の実施形態に係る薄膜トランジスタの構造を表す概略断面図

【図3】実施例1、2および比較例2、3に係る薄膜トランジスタの構造を表す概略断面図

【図4】実施例1、2および比較例2、3に係る薄膜トランジスタアレイ基板の一素子を示す概略断面図

【図5】実施例1、2および比較例2、3に係る薄膜トランジスタを用いた画像表示装置の一画素を示す概略断面図

【図6】比較例1に係る薄膜トランジスタの構造を表す概略断面図

【発明を実施するための形態】

【0030】

以下、図面を参照しつつ、本発明の一実施形態に係る薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置について説明する。なお、以下では、本発明の一実施形態に係る薄膜トランジスタとその製造方法について説明した後、薄膜トランジスタを用いた画像表示装置について説明する。

【0031】

〈薄膜トランジスタ〉

まず、本発明の一実施形態に係る薄膜トランジスタについて説明する。以下の説明において、同一構成要素には同一符号を付け、重複する説明は省略する。また、以下に説明する薄膜トランジスタの構成は一例であって、本発明に係る薄膜トランジスタはこの構成に限定されるものではない。

【0032】

図1に本発明の一実施形態に係る薄膜トランジスタの一例を示す。本実施形態に係る薄膜トランジスタは、樹脂基板10上にゲート電極11、絶縁性の密着層12(絶縁性密着層12と称すことがある)、ゲート絶縁層13、金属酸化物半導体層14、ソース電極15、およびドレイン電極16を備えているボトムゲート−トップコンタクト型の薄膜トランジスタである。

【0033】

また、図2に本発明の他の実施形態に係る薄膜トランジスタの概略断面図の一例を示す。本実施形態に係る薄膜トランジスタは、樹脂基板10上にゲート電極11、絶縁性の密着層12(絶縁性密着層12と称すことがある)、ゲート絶縁層13、金属酸化物半導体層14、ソース電極15およびドレイン電極16を備えているボトムゲート−ボトムコンタクト型の薄膜トランジスタである。

【0034】

上記樹脂基板10には、例えば、ポリメチルメタクリレート、ポリアクリレート、ポリカーボネート、ポリスチレン、ポリエチレンサルファイド、ポリエーテルスルホン(PES)、ポリオレフィン、ポリエチレンテレフタレート、ポリエチレンナフタレート(PEN)、シクロオレフィンポリマー、ポリエーテルサルフェン、トリアセチルセルロース、ポリビニルフルオライドフィルム、エチレン-テトラフルオロエチレン共重合樹脂、耐候性ポリエチレンテレフタレート、耐候性ポリプロピレン、ガラス繊維強化アクリル樹脂フィルム、ガラス繊維強化ポリカーボネート、透明性ポリイミド、フッ素系樹脂、環状ポリオレフィン系樹脂等を使用することができる。これらの基板は単独で使用することもでき、二種以上を積層した複合基板を使用することもできる。また樹脂基板10上にカラーフィルタが形成された基板を使用することもできる。

【0035】

上記ゲート電極11には、Alを含む金属が用いられる。具体的にはAl、Al−Nd、Al−Ni等が挙げられる。これらの電極は、スパッタ法、真空蒸着法等で形成することができるが、これらの方法に限定されるものではない。なお、ゲート電極11の膜厚は10nm以上100nm以下であることが好ましい。

【0036】

上記絶縁性密着層12には、ゲート電極11に含まれる金属と同じ金属、この実施形態ではAlを含む金属のオキシ水酸化物が用いられる。当該絶縁性密着層12は、ゲート電極11を構成するAlを含む金属材料を、高温水処理を用いてオキシ水酸化することにより形成される。なお、絶縁性密着層12の抵抗率は1.0×10-11Ω・cm以下、好ましくは1.0×10-13Ω・cm以下である。また、絶縁性密着層12は、樹脂基板10に設けられたゲート電極11と、樹脂基板10上において同一平面上にある(例えば図1参照)。

【0037】

上記ゲート絶縁層13には、酸化シリコン、窒化シリコン、シリコンオキシナイトライド等を用いるのが好ましい。これらの材料を用いることで、上述した絶縁性密着層12との密着性が高くなり、安価でかつ十分な絶縁性を持つ膜を得ることができる。なお、ゲート絶縁層13はスパッタ法、プラズマCVD(Chemical Vapor Deposition)法または原子層堆積法で形成されることが好ましいが、これらの方法に限定されるものではない。

【0038】

上記金属酸化物半導体層14としては、例えば亜鉛、インジウム、ガリウムのうち少なくとも一種類以上の元素を含む酸化物が挙げられる。なお、当該酸化物として、具体的には、酸化亜鉛、酸化インジウム、酸化インジウム亜鉛、酸化亜鉛ガリウムインジウム(In―Ga―Zn―O)等公知の材料が挙げられるがこれらに限定されるものではない。また、金属酸化物半導体層14の膜厚は少なくとも10nm以上が望ましい。10nmを下回ると、小さいと島状成長により、膜中に半導体が形成されていない部分が生じるという問題が起こることがある。

【0039】

上記ソース電極15およびドレイン電極16には、Au、Ag、Cu、Cr、Al、Mg、Li、Moなどの低抵抗金属材料が好適に用いられる。また酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化カドミウム(CdO)、酸化インジウムカドミウム(CdIn2O4)、酸化カドミウムスズ(Cd2SnO4)、酸化亜鉛スズ(Zn2SnO4)、酸化インジウム亜鉛(In−Zn−O)等の酸化物材料も好適に用いられる。

【0040】

また、これら酸化物材料に不純物をドープすることも導電率を上げるために好ましい。例えば、酸化インジウムにスズやモリブデン、チタンをドープしたもの、酸化スズにアンチモンやフッ素をドープしたもの、酸化亜鉛にインジウム、アルミニウム、ガリウムをドープしたものなどである。この中では特に酸化インジウムにスズをドープした酸化インジウムスズ(通称ITO)が低い抵抗率のために特に好適に用いられる。またポリエチレンジオキシチオフェン(PEDOT)等の有機導電性材料も好適に用いることができる。

【0041】

なお、ゲート電極11、ソース電極15、およびドレイン電極16は全て同じ材料であっても構わないし、また全て違う材料であっても構わない。しかし、薄膜トランジスタの製造における工程数を減らすためにソース電極15とドレイン電極16とは同一の材料であることがより望ましい。これらの電極は、真空蒸着法、スパッタ法、レーザーアブレーション法、プラズマCVD(Chemical Vapor Deposition)法、光CVD法、ホットワイヤーCVD法等で形成される。また上述の導電性材料をインキ状、ペースト状にしたものをスクリーン印刷、凸版印刷、インクジェット法等で塗布し、焼成して形成することもできるが、これらに限定されるものではない。

【0042】

〈薄膜トランジスタの製造方法〉

次に、本発明の一実施形態に係る薄膜トランジスタの製造方法の一例について説明する。

【0043】

まず、樹脂基板10上に、スパッタ法によりAlを成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、高温水処理を行う。そして、処理後、レジストを剥離し、ゲート電極11、および絶縁性密着層12を形成する。

【0044】

次に、プラズマCVD法によりSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成し、次いで、スパッタ法によりInGaZnOからなる金属酸化物半導体層14を室温にて成膜する。

【0045】

最後に、スパッタ法によりMoを成膜し、フォトリソグラフィー法によりレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成する。

【0046】

以上が本発明の一実施形態に係る薄膜トランジスタの製造方法の一例である。

【0047】

〈薄膜トランジスタを用いた画像表示装置〉

次に、薄膜トランジスタを用いた画像表示装置について説明する。

【0048】

画像表示装置は、薄膜トランジスタアレイ基板21と、対向電極23との間に電気泳動媒体22が挟まれているものである(図5参照)。なお、上記薄膜トランジスタアレイ基板21は、薄膜トランジスタのソース電極15およびドレイン電極16上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20が形成してなるものである(図4参照)。

【実施例】

【0049】

以下、本発明を実施例1、2および比較例1〜3に基づき説明する。

【0050】

(実施例1)

実施例1では図3に示すような薄膜トランジスタ、図4に示すような薄膜トランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0051】

まず、樹脂基板10としてPEN基材(膜厚125μm)を用い、当該PEN基板上に、DCマグネトロンスパッタ装置を用いて室温にてAlを成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、100℃で10分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0052】

次に、プラズマCVD装置を用いてSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成した。なお、ゲート絶縁層13の形成にあっては、原料ガスとしてSiH4=50SCCM、NH3=50SCCMを流し、投入電力300W、成膜圧力3.0Pa、基板温度は150℃として成膜した。

【0053】

次に、DCマグネトロンスパッタ装置を用いてInGaZnOからなる金属酸化物半導体層14を室温で成膜(膜厚40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=2SCCM、成膜圧力は1.0Paとした。

【0054】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温で成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0055】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0056】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した。その結果、薄膜トランジスタのトランジスタ特性は、移動度8cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は6桁、ゲート電圧20V時のゲートリーク電流は4.2×10-11Aであり、良好なトランジスタ特性を示した。

【0057】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上に、SiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0058】

なお、当該薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0059】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、良好に表示ができた。

【0060】

(実施例2)

実施例2では図3に示すような薄膜トランジスタ、図4に示すような薄膜トランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0061】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAl−Nd合金を室温にて成膜(膜厚100nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、100℃で20分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al−Nd成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0062】

次に、マグネトロンスパッタ装置を用いてSiO2を成膜(膜厚300nm)し、ゲート絶縁層13を形成した。なお、ゲート絶縁層13の形成にあっては、成膜時の投入電力は500W、成膜圧力1.0Pa、基板温度は室温とした。

【0063】

次に、スパッタ法を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(膜厚40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=1SCCM、成膜圧力は1.0Paとした。

【0064】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0065】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0066】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した薄膜トランジスタのトランジスタ特性は、移動度7cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は6桁、ゲート電圧20V時のゲートリーク電流は2.2×10-11Aであり、良好なトランジスタ特性を示した。

【0067】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0068】

なお、当該薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0069】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、良好に表示ができた。

【0070】

(比較例1)

比較例1では図6に示すような薄膜トランジスタを作製した。

【0071】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAl−Nd合金を室温にて成膜(100nm)し、フォトリソグラフィー法を用いてレジストパターンを形成し、非レジスト被覆部をウェットエッチング法を用いて除去し、最後にレジストを剥離して、ゲート電極11およびキャパシタ電極17を形成した。なお、Al−Nd成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0072】

次に、マグネトロンスパッタ装置を用いてSiO2を成膜(300nm)し、ゲート絶縁層13を形成した。ゲート絶縁層13の形成にあっては、成膜時の投入電力は500W、成膜圧力1.0Pa、基板温度は室温とした。

【0073】

次に、スパッタ法を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=1SCCM、成膜圧力は1.0Paとした。

【0074】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図6参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0075】

このようにして製造した薄膜トランジスタは、目視で一部の基板10−ゲート絶縁層13間での剥離が観察された。また、このようにして製造した薄膜トランジスタの樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類5[剥がれの程度が分類4(塗膜がカットの縁に沿って、部分的又は全面的に大はがれを生じており、および/または数箇所の目が部分的または全面的にはがれている。クロスカット部分で影響を受けるのは、明確に35%を越えるが65%を上回ることはない。)]にあてはまり、密着不良であることが確認された。

【0076】

また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて測定した薄膜トランジスタのトランジスタ特性を測定した結果、ゲートリーク電流が5.0×10-5Aであり、トランジスタ特性を得ることはできなかった。

【0077】

(比較例2)

比較例2では図3に示すような薄膜トランジスタ素子、図4に示すようなトランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0078】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAlを室温にて成膜(膜厚120nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、100℃で30分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0079】

次に、プラズマCVD装置を用いてSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成した。なお、ゲート絶縁層13の形成にあっては、原料ガスとしてSiH4=50SCCM、NH3=50SCCMを流し、投入電力300W、成膜圧力3.0Pa、基板温度は150℃として成膜した。

【0080】

次に、DCマグネトロンスパッタ装置を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(膜厚40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=2SCCM、成膜圧力は1.0Paとした。

【0081】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0082】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて、ゲート絶縁層13と樹脂基板10との間の密着性を評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0083】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した薄膜トランジスタのトランジスタ特性は、移動度7cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は5桁、ゲート電圧20V時のゲートリーク電流は3.8×10-10Aであり、良好なトランジスタ特性を示した。

【0084】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0085】

なお、薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0086】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、隣合う画素間で電気的相互作用が生じ、良好な駆動ができなかった。

【0087】

(比較例3)

比較例3では図3に示すような薄膜トランジスタ、図4に示すような薄膜トランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0088】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAlを室温にて成膜(膜厚100nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、80℃で30分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0089】

次に、プラズマCVD装置を用いてSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成した。ゲート絶縁層13の形成にあっては、原料ガスとしてSiH4=50SCCM、NH3=50SCCMを流し、投入電力300W、成膜圧力3.0Pa、基板温度は150℃として成膜した。

【0090】

次に、DCマグネトロンスパッタ装置を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=2SCCM、成膜圧力は1.0Paとした。

【0091】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0092】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0093】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した薄膜トランジスタのトランジスタ特性は、移動度6cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は5桁、ゲート電圧20V時のゲートリーク電流は3.6×10-10Aであり、良好なトランジスタ特性を示した。

【0094】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0095】

なお、当該薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0096】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、隣合う画素間で電気的相互作用が生じ、良好な駆動ができなかった。

【産業上の利用可能性】

【0097】

本発明に係る薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置は、フレキシブル電子ペーパー、LCD、有機ELディスプレイ、ICタグ等のスイッチング素子等として利用できる。

【符号の説明】

【0098】

10 樹脂基板

11 ゲート電極

12 絶縁性密着層

13 ゲート絶縁層

14 金属酸化物半導体層

15 ソース電極

16 ドレイン電極

17 キャパシタ電極

18 封止層

19 層間絶縁層

20 画素電極

21 トランジスタアレイ基板

22 電気泳動媒体

23 対向電極

【技術分野】

【0001】

本発明は、薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置に関する。

【背景技術】

【0002】

現在、一般的な平面薄型画像表示装置(Flat Panel Display;FPD)は非晶質シリコンや多結晶シリコンを活性層に用いた電界効果トランジスタのアクティブマトリックスにより駆動されている。

【0003】

一方、FPDのさらなる薄型化、軽量化、耐破損性の向上を求めて、ガラス基板の替わりに樹脂基板を用いる試みが近年なされている。

【0004】

しかし、上述のシリコン薄膜を用いるトランジスタの製造は、比較的高温の熱工程を要し、一般的に耐熱性の低い樹脂基板上に直接形成することは困難である。

【0005】

そこで、低温形成が可能な酸化物半導体を活性層とした薄膜トランジスタの開発が活発に行われている(例えば、特許文献1)。

【0006】

そして、上述の酸化物半導体を活性層とした薄膜トランジスタのゲート絶縁層としては、例えばプラズマCVD法やマグネトロンスパッタ法で形成した酸化シリコン、窒化シリコン等の単膜またはそれらを積層した膜が用いられている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2006−165532号公報

【特許文献2】特開2007−73697号公報

【0008】

しかし、プラズマCVD法やマグネトロンスパッタ法で樹脂基板上に低温成膜したゲート絶縁層は、基板との密着性が低いため、基板からゲート絶縁層が剥がれやすく、信頼性の高い薄膜トランジスタが得られないという問題があった。

【0009】

よって、基板とゲート絶縁層との間に密着層を設ける必要があるが、密着層を設けるために工程を一つ増加させることによる製造コストの増加が懸念される。

【発明の概要】

【発明が解決しようとする課題】

【0010】

そこで本発明では、上記のような要求を解決するため、基板とゲート絶縁層間に、工程数を増加させることなく密着層を形成することにより、高品質で低コストの薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、上記の課題を解決するために、以下の構成を採用した。

【0012】

第1の発明は、ボトムゲート型の薄膜トランジスタである。当該ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。

【0013】

第2の発明は、上記第1の発明において、金属は、Alを含む金属であることを特徴とする。

【0014】

第3の発明は、上記第1または第2の発明において、ゲート電極の膜厚は、10nm以上100nm以下であることを特徴とする。

【0015】

第4の発明は、上記第1または第2の発明において、ゲート絶縁層は、酸化シリコン、窒化シリコン、シリコンオキシナイトライドの少なくとも何れか一種の化合物を含むことを特徴とする。

【0016】

第5の発明は、上記第1または第2の発明において、ゲート絶縁層上に金属酸化物半導体層を、さらに備える。また、金属酸化物半導体層は、In、Zn、Gaの少なくとも何れか一種の元素を含むことを特徴とする。

【0017】

第6の発明は、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備えるボトムゲート型の薄膜トランジスタの製造方法である。当該製造方法は、樹脂基板上に金属を含む膜を成膜する金属膜成膜工程と、樹脂基板上においてゲート電極となる部分をレジストで覆うレジスト被覆工程と、樹脂基板を高温水処理する高温水処理工程と、レジストで覆われていない樹脂基板上の金属を含む膜をオキシ水酸化するオキシ水酸化工程とを備える。

【0018】

第7の発明は、上記第6の発明において、金属は、Alを含む金属であることを特徴とする。

【0019】

第8の発明は、上記第6または第7の発明において、高温水処理工程は、レジストで覆われている部分にゲート電極と、レジストで覆われていない部分に絶縁性密着層とを形成することを特徴とする。

【0020】

第9の発明は、上記第6または第7の発明において、高温水処理工程における高温水処理時の温度は、100℃以上180℃以下であることを特徴とする。

【0021】

第10の発明は、画像表示装置である。当該画像表示装置は、上記第1乃至5の何れか1に記載のボトムゲート型の薄膜トランジスタのアレイと画像表示媒体とからなることを特徴とする。

【0022】

第11の発明は、上記第10の発明において、画像表示媒体は、電気泳動方式によるものであることを特徴とする。

【発明の効果】

【0023】

本発明によれば、本発明によれば、高品質で低コストの薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置を提供することが可能となる。つまり、ゲート電極を金属、絶縁性密着層をゲート電極に含まれる金属のオキシ水酸化物を含むものとすることで、十分な導電性を有するゲート電極と、基板およびゲート絶縁層に対し高密着性を有する絶縁性密着層を持つ薄膜トランジスタを得ることが可能となる。

【0024】

また、ゲート電極の膜厚を10nm以上、100nm以下とすることで、十分な導電性を持つゲート電極と十分な絶縁性を有する密着層を得ることが可能となる。10nm未満であると島状成長により膜中に膜が形成されていない部分が生じるという問題が起こりうる。また100nmを越えると、Alを含む金属材料を膜内部まで完全にオキシ水酸化することが困難となり、十分な絶縁性を有する密着層を得ることができない。

【0025】

また、ゲート絶縁層を、酸化シリコン、窒化シリコン、シリコンオキシナイトライド、酸化アルミ二ウムのいずれか一種の化合物を含む材料で形成することで、ゲート絶縁層として十分な耐電圧を持たせることができる。

【0026】

また、金属酸化物半導体層をIn、Zn、Gaのいずれか一種を含む材料で形成することで樹脂基板上に低温で高品質な薄膜トランジスタを形成することができる。

【0027】

また、基板上に金属を含む膜を成膜する工程、ゲート電極となる部分をレジストで覆う工程と、基板を高温水処理し、非レジスト被覆部の金属を含む膜をオキシ水酸化する工程を含むことで、非レジスト被覆部には絶縁性密着層、レジスト被覆部には金属ゲート電極が形成され、ゲート電極と密着層とを同時に形成することが可能となる。つまり樹脂基板上に、工程数を増やすことなく、ゲート絶縁層と絶縁性密着層とを形成することが可能となる。

【0028】

また、Alを含む金属材料への高温水処理時の温度を100℃以上とすることで、密着層となる領域を十分にオキシ水酸化することが可能となる。また180℃以下とすることで、安価な樹脂基板を用いても基板にダメージを与えることなく処理を行うことが可能となる。

【図面の簡単な説明】

【0029】

【図1】本発明の一実施形態に係る薄膜トランジスタの構造を表す概略断面図

【図2】本発明の他の実施形態に係る薄膜トランジスタの構造を表す概略断面図

【図3】実施例1、2および比較例2、3に係る薄膜トランジスタの構造を表す概略断面図

【図4】実施例1、2および比較例2、3に係る薄膜トランジスタアレイ基板の一素子を示す概略断面図

【図5】実施例1、2および比較例2、3に係る薄膜トランジスタを用いた画像表示装置の一画素を示す概略断面図

【図6】比較例1に係る薄膜トランジスタの構造を表す概略断面図

【発明を実施するための形態】

【0030】

以下、図面を参照しつつ、本発明の一実施形態に係る薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置について説明する。なお、以下では、本発明の一実施形態に係る薄膜トランジスタとその製造方法について説明した後、薄膜トランジスタを用いた画像表示装置について説明する。

【0031】

〈薄膜トランジスタ〉

まず、本発明の一実施形態に係る薄膜トランジスタについて説明する。以下の説明において、同一構成要素には同一符号を付け、重複する説明は省略する。また、以下に説明する薄膜トランジスタの構成は一例であって、本発明に係る薄膜トランジスタはこの構成に限定されるものではない。

【0032】

図1に本発明の一実施形態に係る薄膜トランジスタの一例を示す。本実施形態に係る薄膜トランジスタは、樹脂基板10上にゲート電極11、絶縁性の密着層12(絶縁性密着層12と称すことがある)、ゲート絶縁層13、金属酸化物半導体層14、ソース電極15、およびドレイン電極16を備えているボトムゲート−トップコンタクト型の薄膜トランジスタである。

【0033】

また、図2に本発明の他の実施形態に係る薄膜トランジスタの概略断面図の一例を示す。本実施形態に係る薄膜トランジスタは、樹脂基板10上にゲート電極11、絶縁性の密着層12(絶縁性密着層12と称すことがある)、ゲート絶縁層13、金属酸化物半導体層14、ソース電極15およびドレイン電極16を備えているボトムゲート−ボトムコンタクト型の薄膜トランジスタである。

【0034】

上記樹脂基板10には、例えば、ポリメチルメタクリレート、ポリアクリレート、ポリカーボネート、ポリスチレン、ポリエチレンサルファイド、ポリエーテルスルホン(PES)、ポリオレフィン、ポリエチレンテレフタレート、ポリエチレンナフタレート(PEN)、シクロオレフィンポリマー、ポリエーテルサルフェン、トリアセチルセルロース、ポリビニルフルオライドフィルム、エチレン-テトラフルオロエチレン共重合樹脂、耐候性ポリエチレンテレフタレート、耐候性ポリプロピレン、ガラス繊維強化アクリル樹脂フィルム、ガラス繊維強化ポリカーボネート、透明性ポリイミド、フッ素系樹脂、環状ポリオレフィン系樹脂等を使用することができる。これらの基板は単独で使用することもでき、二種以上を積層した複合基板を使用することもできる。また樹脂基板10上にカラーフィルタが形成された基板を使用することもできる。

【0035】

上記ゲート電極11には、Alを含む金属が用いられる。具体的にはAl、Al−Nd、Al−Ni等が挙げられる。これらの電極は、スパッタ法、真空蒸着法等で形成することができるが、これらの方法に限定されるものではない。なお、ゲート電極11の膜厚は10nm以上100nm以下であることが好ましい。

【0036】

上記絶縁性密着層12には、ゲート電極11に含まれる金属と同じ金属、この実施形態ではAlを含む金属のオキシ水酸化物が用いられる。当該絶縁性密着層12は、ゲート電極11を構成するAlを含む金属材料を、高温水処理を用いてオキシ水酸化することにより形成される。なお、絶縁性密着層12の抵抗率は1.0×10-11Ω・cm以下、好ましくは1.0×10-13Ω・cm以下である。また、絶縁性密着層12は、樹脂基板10に設けられたゲート電極11と、樹脂基板10上において同一平面上にある(例えば図1参照)。

【0037】

上記ゲート絶縁層13には、酸化シリコン、窒化シリコン、シリコンオキシナイトライド等を用いるのが好ましい。これらの材料を用いることで、上述した絶縁性密着層12との密着性が高くなり、安価でかつ十分な絶縁性を持つ膜を得ることができる。なお、ゲート絶縁層13はスパッタ法、プラズマCVD(Chemical Vapor Deposition)法または原子層堆積法で形成されることが好ましいが、これらの方法に限定されるものではない。

【0038】

上記金属酸化物半導体層14としては、例えば亜鉛、インジウム、ガリウムのうち少なくとも一種類以上の元素を含む酸化物が挙げられる。なお、当該酸化物として、具体的には、酸化亜鉛、酸化インジウム、酸化インジウム亜鉛、酸化亜鉛ガリウムインジウム(In―Ga―Zn―O)等公知の材料が挙げられるがこれらに限定されるものではない。また、金属酸化物半導体層14の膜厚は少なくとも10nm以上が望ましい。10nmを下回ると、小さいと島状成長により、膜中に半導体が形成されていない部分が生じるという問題が起こることがある。

【0039】

上記ソース電極15およびドレイン電極16には、Au、Ag、Cu、Cr、Al、Mg、Li、Moなどの低抵抗金属材料が好適に用いられる。また酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化カドミウム(CdO)、酸化インジウムカドミウム(CdIn2O4)、酸化カドミウムスズ(Cd2SnO4)、酸化亜鉛スズ(Zn2SnO4)、酸化インジウム亜鉛(In−Zn−O)等の酸化物材料も好適に用いられる。

【0040】

また、これら酸化物材料に不純物をドープすることも導電率を上げるために好ましい。例えば、酸化インジウムにスズやモリブデン、チタンをドープしたもの、酸化スズにアンチモンやフッ素をドープしたもの、酸化亜鉛にインジウム、アルミニウム、ガリウムをドープしたものなどである。この中では特に酸化インジウムにスズをドープした酸化インジウムスズ(通称ITO)が低い抵抗率のために特に好適に用いられる。またポリエチレンジオキシチオフェン(PEDOT)等の有機導電性材料も好適に用いることができる。

【0041】

なお、ゲート電極11、ソース電極15、およびドレイン電極16は全て同じ材料であっても構わないし、また全て違う材料であっても構わない。しかし、薄膜トランジスタの製造における工程数を減らすためにソース電極15とドレイン電極16とは同一の材料であることがより望ましい。これらの電極は、真空蒸着法、スパッタ法、レーザーアブレーション法、プラズマCVD(Chemical Vapor Deposition)法、光CVD法、ホットワイヤーCVD法等で形成される。また上述の導電性材料をインキ状、ペースト状にしたものをスクリーン印刷、凸版印刷、インクジェット法等で塗布し、焼成して形成することもできるが、これらに限定されるものではない。

【0042】

〈薄膜トランジスタの製造方法〉

次に、本発明の一実施形態に係る薄膜トランジスタの製造方法の一例について説明する。

【0043】

まず、樹脂基板10上に、スパッタ法によりAlを成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、高温水処理を行う。そして、処理後、レジストを剥離し、ゲート電極11、および絶縁性密着層12を形成する。

【0044】

次に、プラズマCVD法によりSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成し、次いで、スパッタ法によりInGaZnOからなる金属酸化物半導体層14を室温にて成膜する。

【0045】

最後に、スパッタ法によりMoを成膜し、フォトリソグラフィー法によりレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成する。

【0046】

以上が本発明の一実施形態に係る薄膜トランジスタの製造方法の一例である。

【0047】

〈薄膜トランジスタを用いた画像表示装置〉

次に、薄膜トランジスタを用いた画像表示装置について説明する。

【0048】

画像表示装置は、薄膜トランジスタアレイ基板21と、対向電極23との間に電気泳動媒体22が挟まれているものである(図5参照)。なお、上記薄膜トランジスタアレイ基板21は、薄膜トランジスタのソース電極15およびドレイン電極16上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20が形成してなるものである(図4参照)。

【実施例】

【0049】

以下、本発明を実施例1、2および比較例1〜3に基づき説明する。

【0050】

(実施例1)

実施例1では図3に示すような薄膜トランジスタ、図4に示すような薄膜トランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0051】

まず、樹脂基板10としてPEN基材(膜厚125μm)を用い、当該PEN基板上に、DCマグネトロンスパッタ装置を用いて室温にてAlを成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、100℃で10分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0052】

次に、プラズマCVD装置を用いてSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成した。なお、ゲート絶縁層13の形成にあっては、原料ガスとしてSiH4=50SCCM、NH3=50SCCMを流し、投入電力300W、成膜圧力3.0Pa、基板温度は150℃として成膜した。

【0053】

次に、DCマグネトロンスパッタ装置を用いてInGaZnOからなる金属酸化物半導体層14を室温で成膜(膜厚40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=2SCCM、成膜圧力は1.0Paとした。

【0054】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温で成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0055】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0056】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した。その結果、薄膜トランジスタのトランジスタ特性は、移動度8cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は6桁、ゲート電圧20V時のゲートリーク電流は4.2×10-11Aであり、良好なトランジスタ特性を示した。

【0057】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上に、SiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0058】

なお、当該薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0059】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、良好に表示ができた。

【0060】

(実施例2)

実施例2では図3に示すような薄膜トランジスタ、図4に示すような薄膜トランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0061】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAl−Nd合金を室温にて成膜(膜厚100nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、100℃で20分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al−Nd成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0062】

次に、マグネトロンスパッタ装置を用いてSiO2を成膜(膜厚300nm)し、ゲート絶縁層13を形成した。なお、ゲート絶縁層13の形成にあっては、成膜時の投入電力は500W、成膜圧力1.0Pa、基板温度は室温とした。

【0063】

次に、スパッタ法を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(膜厚40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=1SCCM、成膜圧力は1.0Paとした。

【0064】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0065】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0066】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した薄膜トランジスタのトランジスタ特性は、移動度7cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は6桁、ゲート電圧20V時のゲートリーク電流は2.2×10-11Aであり、良好なトランジスタ特性を示した。

【0067】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0068】

なお、当該薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0069】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、良好に表示ができた。

【0070】

(比較例1)

比較例1では図6に示すような薄膜トランジスタを作製した。

【0071】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAl−Nd合金を室温にて成膜(100nm)し、フォトリソグラフィー法を用いてレジストパターンを形成し、非レジスト被覆部をウェットエッチング法を用いて除去し、最後にレジストを剥離して、ゲート電極11およびキャパシタ電極17を形成した。なお、Al−Nd成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0072】

次に、マグネトロンスパッタ装置を用いてSiO2を成膜(300nm)し、ゲート絶縁層13を形成した。ゲート絶縁層13の形成にあっては、成膜時の投入電力は500W、成膜圧力1.0Pa、基板温度は室温とした。

【0073】

次に、スパッタ法を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=1SCCM、成膜圧力は1.0Paとした。

【0074】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図6参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0075】

このようにして製造した薄膜トランジスタは、目視で一部の基板10−ゲート絶縁層13間での剥離が観察された。また、このようにして製造した薄膜トランジスタの樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類5[剥がれの程度が分類4(塗膜がカットの縁に沿って、部分的又は全面的に大はがれを生じており、および/または数箇所の目が部分的または全面的にはがれている。クロスカット部分で影響を受けるのは、明確に35%を越えるが65%を上回ることはない。)]にあてはまり、密着不良であることが確認された。

【0076】

また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて測定した薄膜トランジスタのトランジスタ特性を測定した結果、ゲートリーク電流が5.0×10-5Aであり、トランジスタ特性を得ることはできなかった。

【0077】

(比較例2)

比較例2では図3に示すような薄膜トランジスタ素子、図4に示すようなトランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0078】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAlを室温にて成膜(膜厚120nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、100℃で30分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0079】

次に、プラズマCVD装置を用いてSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成した。なお、ゲート絶縁層13の形成にあっては、原料ガスとしてSiH4=50SCCM、NH3=50SCCMを流し、投入電力300W、成膜圧力3.0Pa、基板温度は150℃として成膜した。

【0080】

次に、DCマグネトロンスパッタ装置を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(膜厚40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=2SCCM、成膜圧力は1.0Paとした。

【0081】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0082】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて、ゲート絶縁層13と樹脂基板10との間の密着性を評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0083】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した薄膜トランジスタのトランジスタ特性は、移動度7cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は5桁、ゲート電圧20V時のゲートリーク電流は3.8×10-10Aであり、良好なトランジスタ特性を示した。

【0084】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0085】

なお、薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0086】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、隣合う画素間で電気的相互作用が生じ、良好な駆動ができなかった。

【0087】

(比較例3)

比較例3では図3に示すような薄膜トランジスタ、図4に示すような薄膜トランジスタアレイ基板、および図5に示すような画像表示装置を作製した。

【0088】

まず、樹脂基板10としてPEN基材(厚さ125μm)上に、DCマグネトロンスパッタ装置を用いてAlを室温にて成膜(膜厚100nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、80℃で30分の高温水処理を行った。処理後、レジストを剥離し、ゲート電極11、キャパシタ電極17、および絶縁性密着層12を形成した。なお、Al成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。

【0089】

次に、プラズマCVD装置を用いてSiNxを成膜(膜厚500nm)し、ゲート絶縁層13を形成した。ゲート絶縁層13の形成にあっては、原料ガスとしてSiH4=50SCCM、NH3=50SCCMを流し、投入電力300W、成膜圧力3.0Pa、基板温度は150℃として成膜した。

【0090】

次に、DCマグネトロンスパッタ装置を用いてInGaZnOからなる金属酸化物半導体層14を室温にて成膜(40nm)した。なお、金属酸化物半導体層14の成膜にあっては、成膜時の投入電力は100W、ガス流量はAr=100SCCM、O2=2SCCM、成膜圧力は1.0Paとした。

【0091】

最後に、DCマグネトロンスパッタ装置を用いてMoを室温にて成膜(膜厚80nm)し、フォトリソグラフィー法を用いてレジストパターンを形成した後に、ドライエッチング、剥離を行い、ソース電極15とドレイン電極16とを形成して、薄膜トランジスタを得た(図3参照)。なお、Mo成膜時の投入電力は200W、ガス流量はAr=50SCCM、成膜圧力は1.0Paとした。ソース/ドレイン電極間の長さは20μmであり、ソース/ドレイン電極間の幅は5μmである。

【0092】

このようにして製造した薄膜トランジスタの絶縁性密着層12を介した樹脂基板10とゲート絶縁層13との間の密着性を、JIS−K−5600(1999)5−6付着性(クロスカット法)試験に準じて評価した。その結果、分類0(カットの縁が完全に滑らかで、どの格子の目にもはがれがない)にあてはまる良好な密着性を示した。

【0093】

なお、クロスカットは隙間1mmカッターガイドを用いて行った。また、半導体パラメータアナライザ(Keithlay製 SCS4200)を用いて、ゲート電圧を−10V〜+20V、ドレイン電圧を5Vとして測定した薄膜トランジスタのトランジスタ特性は、移動度6cm2/Vs、ソース/ドレイン電極間に10Vの電圧が印加されたときのON/OFF比は5桁、ゲート電圧20V時のゲートリーク電流は3.6×10-10Aであり、良好なトランジスタ特性を示した。

【0094】

次に、上述した製造方法で、ソース/ドレイン電極まで形成し薄膜トランジスタの上にSiOxからなる封止層18、ポリマーからなる層間絶縁層19、ITOからなる画素電極20を形成し、図4に示すような薄膜トランジスタアレイ基板21を得た。

【0095】

なお、当該薄膜トランジスタアレイ基板21は、1画素のサイズが125μm×125μmであり、この画素が480×640個あるものである。

【0096】

次に、図5に示すような画像表示装置を、トランジスタアレイ基板21と対向電極23との間に電気泳動媒体22を挟んで作製し、駆動を行ったところ、隣合う画素間で電気的相互作用が生じ、良好な駆動ができなかった。

【産業上の利用可能性】

【0097】

本発明に係る薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置は、フレキシブル電子ペーパー、LCD、有機ELディスプレイ、ICタグ等のスイッチング素子等として利用できる。

【符号の説明】

【0098】

10 樹脂基板

11 ゲート電極

12 絶縁性密着層

13 ゲート絶縁層

14 金属酸化物半導体層

15 ソース電極

16 ドレイン電極

17 キャパシタ電極

18 封止層

19 層間絶縁層

20 画素電極

21 トランジスタアレイ基板

22 電気泳動媒体

23 対向電極

【特許請求の範囲】

【請求項1】

ボトムゲート型の薄膜トランジスタであって、

樹脂基板と、

前記樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、

前記ゲート電極と前記絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備え、

前記ゲート電極は、金属を含み、

前記絶縁性密着層は、前記ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする、薄膜トランジスタ。

【請求項2】

前記金属は、Alを含む金属であることを特徴とする、請求項1に記載の薄膜トランジスタ。

【請求項3】

前記ゲート電極の膜厚は、10nm以上100nm以下であることを特徴とする、請求項1または2に記載の薄膜トランジスタ。

【請求項4】

前記ゲート絶縁層は、酸化シリコン、窒化シリコン、シリコンオキシナイトライドの少なくとも何れか一種の化合物を含むことを特徴とする、請求項1または2に記載の薄膜トランジスタ。

【請求項5】

前記ゲート絶縁層上に金属酸化物半導体層を、さらに備え、

前記金属酸化物半導体層は、In、Zn、Gaの少なくとも何れか一種の元素を含むことを特徴とする、請求項1または2に記載の薄膜トランジスタ。

【請求項6】

ボトムゲート型の薄膜トランジスタの製造方法であって、

前記薄膜トランジスタは、

樹脂基板と、

前記樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、

前記ゲート電極と前記絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備え、

前記製造方法は、

前記樹脂基板上に金属を含む膜を成膜する金属膜成膜工程と、

前記樹脂基板上において前記ゲート電極となる部分をレジストで覆うレジスト被覆工程と、

前記樹脂基板を高温水処理する高温水処理工程と、

前記レジストで覆われていない前記樹脂基板上の前記金属を含む膜をオキシ水酸化するオキシ水酸化工程とを備える、薄膜トランジスタの製造方法。

【請求項7】

前記金属は、Alを含む金属であることを特徴とする、請求項6に記載の薄膜トランジスタの製造方法。

【請求項8】

前記高温水処理工程は、前記レジストで覆われている部分にゲート電極と、前記レジストで覆われていない部分に前記絶縁性密着層とを形成することを特徴とする、請求項6または7に記載の薄膜トランジスタの製造方法。

【請求項9】

前記高温水処理工程における前記高温水処理時の温度は、100℃以上180℃以下であることを特徴とする、請求項6または7に記載の薄膜トランジスタの製造方法。

【請求項10】

請求項1乃至5のいずれか1に記載の薄膜トランジスタのアレイと画像表示媒体とからなることを特徴とする画像表示装置。

【請求項11】

前記画像表示媒体は、電気泳動方式によるものであることを特徴とする、請求項10に記載の画像表示装置。

【請求項1】

ボトムゲート型の薄膜トランジスタであって、

樹脂基板と、

前記樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、

前記ゲート電極と前記絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備え、

前記ゲート電極は、金属を含み、

前記絶縁性密着層は、前記ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする、薄膜トランジスタ。

【請求項2】

前記金属は、Alを含む金属であることを特徴とする、請求項1に記載の薄膜トランジスタ。

【請求項3】

前記ゲート電極の膜厚は、10nm以上100nm以下であることを特徴とする、請求項1または2に記載の薄膜トランジスタ。

【請求項4】

前記ゲート絶縁層は、酸化シリコン、窒化シリコン、シリコンオキシナイトライドの少なくとも何れか一種の化合物を含むことを特徴とする、請求項1または2に記載の薄膜トランジスタ。

【請求項5】

前記ゲート絶縁層上に金属酸化物半導体層を、さらに備え、

前記金属酸化物半導体層は、In、Zn、Gaの少なくとも何れか一種の元素を含むことを特徴とする、請求項1または2に記載の薄膜トランジスタ。

【請求項6】

ボトムゲート型の薄膜トランジスタの製造方法であって、

前記薄膜トランジスタは、

樹脂基板と、

前記樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、

前記ゲート電極と前記絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備え、

前記製造方法は、

前記樹脂基板上に金属を含む膜を成膜する金属膜成膜工程と、

前記樹脂基板上において前記ゲート電極となる部分をレジストで覆うレジスト被覆工程と、

前記樹脂基板を高温水処理する高温水処理工程と、

前記レジストで覆われていない前記樹脂基板上の前記金属を含む膜をオキシ水酸化するオキシ水酸化工程とを備える、薄膜トランジスタの製造方法。

【請求項7】

前記金属は、Alを含む金属であることを特徴とする、請求項6に記載の薄膜トランジスタの製造方法。

【請求項8】

前記高温水処理工程は、前記レジストで覆われている部分にゲート電極と、前記レジストで覆われていない部分に前記絶縁性密着層とを形成することを特徴とする、請求項6または7に記載の薄膜トランジスタの製造方法。

【請求項9】

前記高温水処理工程における前記高温水処理時の温度は、100℃以上180℃以下であることを特徴とする、請求項6または7に記載の薄膜トランジスタの製造方法。

【請求項10】

請求項1乃至5のいずれか1に記載の薄膜トランジスタのアレイと画像表示媒体とからなることを特徴とする画像表示装置。

【請求項11】

前記画像表示媒体は、電気泳動方式によるものであることを特徴とする、請求項10に記載の画像表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−204398(P2012−204398A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−64918(P2011−64918)

【出願日】平成23年3月23日(2011.3.23)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月23日(2011.3.23)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

[ Back to top ]