薄膜トランジスタとその製造方法

【課題】トランジスタの素子形成に自己整合技術を用いて、高速応答性が良く高密度化が容易であり、高性能な薄膜トランジスタとその製造方法を提供する。

【解決手段】透光性のある透明基板32と、透明基板32上に形成された不透明なゲート電極34を有する。不透明なゲート電極34と相補的に対向するように自己整合して形成されたソース電極42及びドレイン電極44を備える。ゲート電極34と、ソース電極42及びドレイン電極44間に、透光性のゲート絶縁膜36及び透明半導体層40を備える。

【解決手段】透光性のある透明基板32と、透明基板32上に形成された不透明なゲート電極34を有する。不透明なゲート電極34と相補的に対向するように自己整合して形成されたソース電極42及びドレイン電極44を備える。ゲート電極34と、ソース電極42及びドレイン電極44間に、透光性のゲート絶縁膜36及び透明半導体層40を備える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、透明半導体を用いて自己整合的にトランジスタ素子を形成する薄膜トランジスタとその製造方法に関する。

【背景技術】

【0002】

従来、ガラス基板上にアモルファスシリコンやポリシリコンなどを成膜した薄膜トランジスタ(TFT)が、液晶ディスプレイのドライバ等に応用されている。このような薄膜トランジスタにおいては、アモルファスシリコン等を400〜500℃程度の比較的低い成膜温度で形成可能なことから、比較的融点が低い安価なガラスが基板として使用されている。

【0003】

一方、大面積化可能、超薄型、軽量、フレキシブル化を図る場合、半導体材料として酸化物半導体を選択することが出来る。酸化物半導体材料としては、例えば、細野らによる論文(非特許文献1)に開示されているような非晶質In-Ga-Zn-O(a-IGZO)半導体などがある。また、薄膜トランジスタの集積回路試作も実施されており、伝搬遅延時間0.24 μs/stageの性能や、有機EL素子駆動に用いた例も報告されている(非特許文献2)。

【0004】

さらに、大面積化が可能、超薄型、軽量、フレキシブルの特徴を有するフレキシブルエレクトロニクス技術においては、電子回路を形成する薄膜トランジスタをフレキシブル基板上に形成する技術の開発が行われている。そのスイッチングデバイスとしては、これまで有機半導体を用いたトランジスタが有力候補として検討され、現在低分子有機材料系ペンタセンを中心に検討が進められている。

【0005】

この有機薄膜トランジスタの構造は、例えばプラスチックからなる基板の上面に長方形状のゲート電極が形成され、その上にゲート絶縁膜を挟んでソース電極およびドレイン電極が形成され、さらにその上に有機半導体が形成されている。このような薄膜トランジスタにおいては、ソース電極とドレイン電極がスクリーン印刷によって形成されるが、スクリーン印刷においては、ソース電極とドレイン電極およびゲート電極の位置合わせ精度が悪いことを考慮し、電極の重なりが大きく設計される。そのため、電極間の静電容量が大きく、薄膜トランジスタの応答速度が悪くなるものであった。

【0006】

このような問題を解決する方法として、特許文献1、2、3、及び非特許文献3、4に開示されているように、背面露光により自己整合的に素子を形成する方法が提案されている。また、特許文献4には、ゲート電極をマスクとして自己整合的に絶縁膜を形成した薄膜トランジスタとその製造方法が開示されている。特許文献1,2や非特許文献3には、アモルファスシリコン(a-Si)を用いた薄膜トランジスタの製造方法が開示され、特許文献3、4には、酸化物半導体を用いた例が開示されている。さらに、特許文献4及び非特許文献4には、有機半導体を用いて薄膜トランジスタを形成した例が開示されている。

【0007】

非特許文献3に開示された背面露光を利用した薄膜トランジスタの製造方法を以下に説明する。図4に示すように、まず、ガラス基板2の上面に長方形状のゲート電極4を形成し、その上にSiO2のゲート絶縁膜6を形成し、さらにその上に薄いアモルファスシリコン層8を形成する(図4(a))。次に、フォトレジストを塗布した後、水銀ランプ等により裏面露光によって、ゲート電極4に自己整合したレジストパターン10を形成する(図4(b))。この状態で、ソース電極12とドレイン電極14が形成される位置とレジストパターン10を覆うようにアルミニウムを蒸着した後、レジストパターン10をその上の蒸着物ごとリフトオフして、ソース電極12とドレイン電極14を形成する(図4(c))。最後に、アモルファスシリコン層18及びSiO2の絶縁膜16を形成し、所定のパターンに成形する(図4(d))。これにより、ゲート電極4に対するソース電極12よびドレイン電極14の位置合わせ精度を、自己整合的に向上させることができる。

【0008】

次に、非特許文献4に開示された、有機半導体ペンタセンを用いた薄膜トランジスタの製造方法について、以下に説明する。この方法では、図5に示すように、ガラス基板2の上面に長方形状のゲート電極4を形成し、その上にAl2O3のゲート絶縁膜6を形成し、その上にフォトレジストを塗布した後(図5(a))、紫外線ランプ等による裏面露光によってゲート電極4に自己整合したレジストパターン10を残す(図5(b))。次に、ソース電極12とドレイン電極14が形成される位置とレジストパターン10を覆うように、Cr及びAuの各薄い層から成る電極金属20を形成する(図5(c))。この後、レジストパターン10をその上の蒸着物である電極金属20ごとリフトオフして、ソース電極12とドレイン電極14を形成し(図5(d))、有機半導体ペンタセン22を蒸着し(図5(e))、所定のパターンに成形する。この方法でも、自己整合的にゲート電極4に対するソース電極12よびドレイン電極14の位置合わせ精度を向上させることができる。

【特許文献1】特開昭58−33872号公報

【特許文献2】特開昭64−72163号公報

【特許文献3】特開2006−286719号公報

【特許文献4】特開2007−220817号公報

【非特許文献1】Japanese Journal of AppliedPhysics, vol.45, No.5B, pp.4303-4308 (2006)

【非特許文献2】Journal of Society forInformation Display, vol.15, No.11, pp.915-921 (1997)

【非特許文献3】IEEE Electron Device Letters,vol.EDL-3, No. 7, JULY pp.187-189 (1982)

【非特許文献4】Japanese Journal of AppliedPhysics, vol.43, No.4B, pp.2323-2325 (2004)

【発明の開示】

【発明が解決しようとする課題】

【0009】

上記従来の背面露光法による薄膜トランジスタの構造では、特許文献1,2,3及び非特許文献3,4においては、ゲート絶縁膜形成後、AlやCr/Auのソース電極やドレイン電極を形成し、その後アモルファス半導体や有機半導体等をソース/ドレイン電極間に形成している。従って、理想的には綺麗にしたい絶縁膜/半導体界面形成が不連続となり、トランジスタ特性を最良の状態に保ちにくいものであった。また、特許文献4では、ゲート電極を、マスクとしてエッチングを行うので、素子への悪影響の恐れがある。

【0010】

さらに、トランジスタの高性能化を考えると、アライメントマージンの増大によるトランジスタ占有面積の増大が、ディスプレイパネルの開口率向上に影響し、集積回路のチップ面積増大に繋がり、ディスプレイパネルの高精細化や開口率の向上の妨げとなっていた。また、上記従来の構造のトランジスタの寄生容量が、トランジスタのスイッチング特性の向上の妨げとなっていた。

【0011】

この発明は、上記背景技術の問題に鑑みて成されたもので、トランジスタの素子形成に自己整合技術を用いて、高速応答性が良く高密度化が容易であり、高性能な薄膜トランジスタとその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明では、半導体活性層として透明酸化物半導体を用いることで、従来フレキシブル基板上に形成されてきた有機半導体より高い電子移動度を実現する。かつ半導体層が透明である点を利用し、ゲート電極を光露光時のマスクとして利用し、基板背面より露光する背面露光法を用いた薄膜トランジスタとその製造方法を提供するものである。

【0013】

本発明は、透光性のあるガラスやプラスチック等の透明基板と、この透明基板上に形成された不透明な電極と、この不透明な電極と相補的に対向するように自己整合して形成された他方の電極と、前記各電極間に位置した透光性の絶縁膜及び透明半導体層とを備えた薄膜トランジスタである。

【0014】

前記不透明な電極はゲート電極であり、前記他方の電極は、ソース電極及びドレイン電極であり、前記ソース電極及びドレイン電極の間隔が、前記ゲート電極の幅と自己整合的に形成されたものである。

【0015】

または、前記不透明な電極は、ソース電極及びドレイン電極であり、前記他方の電極は、前記ソース電極及びドレイン電極の間隔に対応して自己整合的に形成されたゲート電極である。

【0016】

また本発明は、透光性のあるガラスやプラスチック等の透明基板上に不透明な電極を所定の形状で形成し、この不透明な電極に重ねて透光性の絶縁膜及び透明半導体層を積層し、その上に前記不透明な電極に相補的に対向するように、自己整合させて他方の電極を形成する薄膜トランジスタの製造方法である。

【0017】

前記不透明な電極はゲート電極であり、このゲート電極に重ねて、前記絶縁膜及び透明半導体層を積層し、前記ゲート電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ゲート電極に対応したソース電極及びドレイン電極を自己整合的に形成するものである。

【0018】

前記不透明な電極はソース電極及びドレイン電極であり、このソース電極及びドレイン電極に重ねて、前記透明半導体層と前記絶縁膜を順に積層して所定形状に形成し、前記ソース電極及びドレイン電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ソース電極及びドレイン電極間の間隔に対応したソース電極及びドレイン電極を自己整合的に形成するものである。

【発明の効果】

【0019】

この発明の薄膜トランジスタとその製造方法によれば、従来のフレキシブル基板上に形成された薄膜トランジスタと比較して、応答性が良く高密度化も容易な高性能な薄膜トランジスタを形成することができる。

【発明を実施するための最良の形態】

【0020】

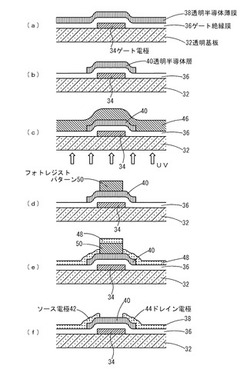

以下、この発明の一実施形態について、図面を基にして説明する。この実施形態の薄膜トランジスタは、ボトムゲート型の構造であり、透明半導体を用いて自己整合的に各素子が形成されたもので、図1(f)に示すように、ガラスや透明プラスチック等の透明基板32の上面にNi−Cr、Cr−Ti、Ta等の金属により長方形状の不透明なゲート電極34が形成されている。ゲート電極34上には、Ta2O5、SiO2、またはAl2O3等の透光性のゲート絶縁膜36が形成され、その上にIn2O3(ITO)やZnO、SnO2、In2O3−ZnOの金属酸化物等から成る透明半導体層40が設けられている。透明半導体層40はゲート電極34よりより幅広く形成され、ゲート電極34の両側に跨る。透明半導体層40の両端部には、Cr/Au等のソース電極42とドレイン電極44が、ゲート電極34の幅よりも僅かに狭い間隔を空けて、高精度に自己整合的に形成されている。

【0021】

この第一実施形態の薄膜トランジスタの製造工程は、透明基板32の上面一面にゲート電極材料をスパッタリング等により形成して、リソグラフィ工程の後、不透明なゲート電極34をドライエッチング等により長方形に形成する。次に、レジストの剥離・洗浄の後、透光性のゲート絶縁膜36を形成し、さらにその上に、蒸着やスパッタリング等により透明半導体薄膜38を形成する(図1(a))。この透明半導体薄膜38の厚みは、特に限定されないが、例えば、約20〜250nmに形成され、好ましくは、50〜150nm程度に形成される。

【0022】

ここで、ゲート絶縁膜36、透明半導体材料層38の形成は連続して行われるため、トランジスタ界面の清浄化が可能となり、電子または正孔の移動度の向上、所定のしきい電圧の適正化が成され、トランジスタの信頼性向上に繋がる。

【0023】

続いて、リソグラフィ工程、エッチング等を経て、透明半導体薄膜38から、透明半導体層40のパターニングを行い(図1(b)、透明半導体薄膜38の余分な部位を分離する。その後、ポジ型フォトレジスト46を全面形成し、透明基板32の背面側から、紫外線ランプ等により露光を行う(図1(c))。このとき、紫外線に対して透明性の高い透明半導体を選択することにより、フォトレジスト46が露光される。そして、現像を行うことにより、光の回折等の影響でゲート電極34より約0.5μm程度内側に入り込んだフォトレジストパターン50が形成される(図1(d)。

【0024】

次に、透明半導体に対してオーミック接触を行うことが可能な、AlやCr−Au等の電極金属48を一面に形成する(図1(e)。最後に、フォトレジストパターン50を除去して、フォトレジストパターン50上の電極金属48をリフトオフする(図1(f)。これにより、透明酸化物半導体を用いたボトムゲート型の薄膜トランジスタ構造が完成する。

【0025】

この実施形態の薄膜トランジスタによれば、ゲート絶縁膜36と透明半導体薄膜38の形成が連続して行われ、透明半導体層40のトランジスタ界面が清浄に維持され、透明半導体薄膜38の電子または正孔の移動度が向上し、所定のしきい電圧の適正化が成される。また、ソース電極42とドレイン電極44は、自己整合的に形成されるので、ゲート電極34の両端は、ソース・ドレイン領域の端部と膜厚方向に揃った位置に存在する。さらに、ソース電極42とドレイン電極44の内側端部は、ゲート電極34の両端部より最小限内側の位置に設定可能である。これにより、ソース・ドレイン領域とゲート電極34間には寄生容量が生じず、動作速度の向上を図ることができる。

【0026】

次に、この発明の薄膜トランジスタとその製造方法の第二実施形態について図2を基にして説明する。ここで、上記実施形態と同様の部材は、同一の符号を付して説明する。この実施形態の薄膜トランジスタは、上記実施形態と同様に、透明半導体を用いて自己整合的に各素子が形成されたもので、図2(d)に示すように、トップゲート型の構造に形成されている。ガラスや透明プラスチック等の透明基板32の上面には、AlやCr/Au等のソース電極42とドレイン電極44が形成されている。ソース電極42とドレイン電極44上には、In2O3(ITO)やZnO、SnO2、In2O3−ZnOの金属酸化物等から成る透明半導体層40が設けられている。透明半導体層40は、ソース電極42とドレイン電極44に跨って各々積層するように、ソース電極42とドレイン電極44との間隔より広く形成されている。透明半導体層40上には、同形状にTa2O5、SiO2、またはAl2O3等の透光性のゲート絶縁膜36が形成されている。そして、ソース電極42とドレイン電極44の両端部に対応するように、ソース電極42とドレイン電極44の間隔より僅かに広いゲート電極34が形成されている。ゲート電極は、Ni−Cr、Cr−Ti、Ta等の金属により長方形状に形成されている。

【0027】

この第二実施形態の薄膜トランジスタの製造工程は、透明基板32の上面一面にソース電極42及びドレイン電極44の材料を、蒸着やスパッタリング等により形成して、リソグラフィ工程の後ドライエッチング等により、不透明なソース電極42及びドレイン電極44を形成する。次に、レジストの剥離・洗浄の後、透明半導体薄膜、ゲート絶縁膜を連続的に一面に形成し、所定形状にパターニングを行い、余分な透明半導体薄膜及びゲート絶縁膜を分離して、所定形状の透明半導体層40とゲート絶縁膜36を形成する。この透明半導体薄膜の厚みは、特に限定されないが、例えば、約20〜250nmに形成され、好ましくは、50〜150nm程度に形成される。さらに、ポジ形フォトレジスト52を一面に形成し、背面露光を実施する(図2(a))。

【0028】

この後、現像を行うことで、後述するゲート電極34に対対応した開口部を形成する(図2(b))。開口部は、光の回折等の影響でソース電極42及びドレイン電極44間隔より約0.5μm程度外側に広く開口したフォトレジストパターン54が形成される(図2(b))。そして、蒸着やスパッタリング等により、ゲート電極34用のNi−Cr、Cr−Ti、Ta等の金属を一面に形成する(図2(c))。

【0029】

最後に、フォトレジストパターン54を除去して、フォトレジストパターン54上のゲート電極金属をリフトオフする(図2(d))。これにより、透明酸化物半導体を用いたトップゲート型の薄膜トランジスタ構造が完成する。

【0030】

この実施形態の薄膜トランジスタによれば、上記実施形態と同様の効果を有し、さらに、トップゲート型の薄膜トランジスタは、透明半導体層40の上部にゲート絶縁膜を設ける構造を有するので、透明半導体層40の上部の結晶性の良好な領域を活性層として用いることができる。

【0031】

なお、この発明の薄膜トランジスタは、上記実施形態に限定されるものではなく、透明半導体は、金属酸化物以外のセラミックス透明半導体やその他透明な半導体を利用することも可能である。また、各部材の形状や素材など適宜変更可能である。

【実施例1】

【0032】

以下に、図1に示すプロセスにより、透明酸化物半導体を用いて製造した自己整合型の薄膜トランジスタの、ドレイン電流−ドレイン電圧特性を示す。使用した半導体はIZO(出光興産製)200Åである。アニール温度は150℃からトランジスタ特性が発現し、今回の特性では300℃でアニールを行った。ゲート電極はTA50nm、絶縁膜はTa2O5の薄膜150nm、ソース/ドレイン電極は、Cr5nm/Au50nmである。トランジスタの移動度として18.5 cm2/Vs、オンオフ比4.5×107が得られた。これより、自己整合プロセスを導入して、優れた特性の透明酸化物半導体による薄膜トランジスタの、動作を確認することができた。

【図面の簡単な説明】

【0033】

【図1】この発明の第一実施形態の自己整合透明半導体トランジスタの製造方法を示す概略工程図である。

【図2】この発明の第二実施形態の自己整合透明半導体トランジスタの製造方法を示す概略工程図である。

【図3】この発明の自己整合透明半導体トランジスタの実施例による測定結果を示すグラフである。

【図4】従来の自己整合によるトランジスタの製造方法を示す概略工程図である。

【図5】他の従来の自己整合によるトランジスタの製造方法を示す概略工程図である。

【符号の説明】

【0034】

32 透明基板

34 ゲート電極

36 ゲート絶縁膜

38 透明半導体薄膜

40 透明半導体層

42 ソース電極

44 ドレイン電極

50,54 フォトレジストパターン

【技術分野】

【0001】

この発明は、透明半導体を用いて自己整合的にトランジスタ素子を形成する薄膜トランジスタとその製造方法に関する。

【背景技術】

【0002】

従来、ガラス基板上にアモルファスシリコンやポリシリコンなどを成膜した薄膜トランジスタ(TFT)が、液晶ディスプレイのドライバ等に応用されている。このような薄膜トランジスタにおいては、アモルファスシリコン等を400〜500℃程度の比較的低い成膜温度で形成可能なことから、比較的融点が低い安価なガラスが基板として使用されている。

【0003】

一方、大面積化可能、超薄型、軽量、フレキシブル化を図る場合、半導体材料として酸化物半導体を選択することが出来る。酸化物半導体材料としては、例えば、細野らによる論文(非特許文献1)に開示されているような非晶質In-Ga-Zn-O(a-IGZO)半導体などがある。また、薄膜トランジスタの集積回路試作も実施されており、伝搬遅延時間0.24 μs/stageの性能や、有機EL素子駆動に用いた例も報告されている(非特許文献2)。

【0004】

さらに、大面積化が可能、超薄型、軽量、フレキシブルの特徴を有するフレキシブルエレクトロニクス技術においては、電子回路を形成する薄膜トランジスタをフレキシブル基板上に形成する技術の開発が行われている。そのスイッチングデバイスとしては、これまで有機半導体を用いたトランジスタが有力候補として検討され、現在低分子有機材料系ペンタセンを中心に検討が進められている。

【0005】

この有機薄膜トランジスタの構造は、例えばプラスチックからなる基板の上面に長方形状のゲート電極が形成され、その上にゲート絶縁膜を挟んでソース電極およびドレイン電極が形成され、さらにその上に有機半導体が形成されている。このような薄膜トランジスタにおいては、ソース電極とドレイン電極がスクリーン印刷によって形成されるが、スクリーン印刷においては、ソース電極とドレイン電極およびゲート電極の位置合わせ精度が悪いことを考慮し、電極の重なりが大きく設計される。そのため、電極間の静電容量が大きく、薄膜トランジスタの応答速度が悪くなるものであった。

【0006】

このような問題を解決する方法として、特許文献1、2、3、及び非特許文献3、4に開示されているように、背面露光により自己整合的に素子を形成する方法が提案されている。また、特許文献4には、ゲート電極をマスクとして自己整合的に絶縁膜を形成した薄膜トランジスタとその製造方法が開示されている。特許文献1,2や非特許文献3には、アモルファスシリコン(a-Si)を用いた薄膜トランジスタの製造方法が開示され、特許文献3、4には、酸化物半導体を用いた例が開示されている。さらに、特許文献4及び非特許文献4には、有機半導体を用いて薄膜トランジスタを形成した例が開示されている。

【0007】

非特許文献3に開示された背面露光を利用した薄膜トランジスタの製造方法を以下に説明する。図4に示すように、まず、ガラス基板2の上面に長方形状のゲート電極4を形成し、その上にSiO2のゲート絶縁膜6を形成し、さらにその上に薄いアモルファスシリコン層8を形成する(図4(a))。次に、フォトレジストを塗布した後、水銀ランプ等により裏面露光によって、ゲート電極4に自己整合したレジストパターン10を形成する(図4(b))。この状態で、ソース電極12とドレイン電極14が形成される位置とレジストパターン10を覆うようにアルミニウムを蒸着した後、レジストパターン10をその上の蒸着物ごとリフトオフして、ソース電極12とドレイン電極14を形成する(図4(c))。最後に、アモルファスシリコン層18及びSiO2の絶縁膜16を形成し、所定のパターンに成形する(図4(d))。これにより、ゲート電極4に対するソース電極12よびドレイン電極14の位置合わせ精度を、自己整合的に向上させることができる。

【0008】

次に、非特許文献4に開示された、有機半導体ペンタセンを用いた薄膜トランジスタの製造方法について、以下に説明する。この方法では、図5に示すように、ガラス基板2の上面に長方形状のゲート電極4を形成し、その上にAl2O3のゲート絶縁膜6を形成し、その上にフォトレジストを塗布した後(図5(a))、紫外線ランプ等による裏面露光によってゲート電極4に自己整合したレジストパターン10を残す(図5(b))。次に、ソース電極12とドレイン電極14が形成される位置とレジストパターン10を覆うように、Cr及びAuの各薄い層から成る電極金属20を形成する(図5(c))。この後、レジストパターン10をその上の蒸着物である電極金属20ごとリフトオフして、ソース電極12とドレイン電極14を形成し(図5(d))、有機半導体ペンタセン22を蒸着し(図5(e))、所定のパターンに成形する。この方法でも、自己整合的にゲート電極4に対するソース電極12よびドレイン電極14の位置合わせ精度を向上させることができる。

【特許文献1】特開昭58−33872号公報

【特許文献2】特開昭64−72163号公報

【特許文献3】特開2006−286719号公報

【特許文献4】特開2007−220817号公報

【非特許文献1】Japanese Journal of AppliedPhysics, vol.45, No.5B, pp.4303-4308 (2006)

【非特許文献2】Journal of Society forInformation Display, vol.15, No.11, pp.915-921 (1997)

【非特許文献3】IEEE Electron Device Letters,vol.EDL-3, No. 7, JULY pp.187-189 (1982)

【非特許文献4】Japanese Journal of AppliedPhysics, vol.43, No.4B, pp.2323-2325 (2004)

【発明の開示】

【発明が解決しようとする課題】

【0009】

上記従来の背面露光法による薄膜トランジスタの構造では、特許文献1,2,3及び非特許文献3,4においては、ゲート絶縁膜形成後、AlやCr/Auのソース電極やドレイン電極を形成し、その後アモルファス半導体や有機半導体等をソース/ドレイン電極間に形成している。従って、理想的には綺麗にしたい絶縁膜/半導体界面形成が不連続となり、トランジスタ特性を最良の状態に保ちにくいものであった。また、特許文献4では、ゲート電極を、マスクとしてエッチングを行うので、素子への悪影響の恐れがある。

【0010】

さらに、トランジスタの高性能化を考えると、アライメントマージンの増大によるトランジスタ占有面積の増大が、ディスプレイパネルの開口率向上に影響し、集積回路のチップ面積増大に繋がり、ディスプレイパネルの高精細化や開口率の向上の妨げとなっていた。また、上記従来の構造のトランジスタの寄生容量が、トランジスタのスイッチング特性の向上の妨げとなっていた。

【0011】

この発明は、上記背景技術の問題に鑑みて成されたもので、トランジスタの素子形成に自己整合技術を用いて、高速応答性が良く高密度化が容易であり、高性能な薄膜トランジスタとその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明では、半導体活性層として透明酸化物半導体を用いることで、従来フレキシブル基板上に形成されてきた有機半導体より高い電子移動度を実現する。かつ半導体層が透明である点を利用し、ゲート電極を光露光時のマスクとして利用し、基板背面より露光する背面露光法を用いた薄膜トランジスタとその製造方法を提供するものである。

【0013】

本発明は、透光性のあるガラスやプラスチック等の透明基板と、この透明基板上に形成された不透明な電極と、この不透明な電極と相補的に対向するように自己整合して形成された他方の電極と、前記各電極間に位置した透光性の絶縁膜及び透明半導体層とを備えた薄膜トランジスタである。

【0014】

前記不透明な電極はゲート電極であり、前記他方の電極は、ソース電極及びドレイン電極であり、前記ソース電極及びドレイン電極の間隔が、前記ゲート電極の幅と自己整合的に形成されたものである。

【0015】

または、前記不透明な電極は、ソース電極及びドレイン電極であり、前記他方の電極は、前記ソース電極及びドレイン電極の間隔に対応して自己整合的に形成されたゲート電極である。

【0016】

また本発明は、透光性のあるガラスやプラスチック等の透明基板上に不透明な電極を所定の形状で形成し、この不透明な電極に重ねて透光性の絶縁膜及び透明半導体層を積層し、その上に前記不透明な電極に相補的に対向するように、自己整合させて他方の電極を形成する薄膜トランジスタの製造方法である。

【0017】

前記不透明な電極はゲート電極であり、このゲート電極に重ねて、前記絶縁膜及び透明半導体層を積層し、前記ゲート電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ゲート電極に対応したソース電極及びドレイン電極を自己整合的に形成するものである。

【0018】

前記不透明な電極はソース電極及びドレイン電極であり、このソース電極及びドレイン電極に重ねて、前記透明半導体層と前記絶縁膜を順に積層して所定形状に形成し、前記ソース電極及びドレイン電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ソース電極及びドレイン電極間の間隔に対応したソース電極及びドレイン電極を自己整合的に形成するものである。

【発明の効果】

【0019】

この発明の薄膜トランジスタとその製造方法によれば、従来のフレキシブル基板上に形成された薄膜トランジスタと比較して、応答性が良く高密度化も容易な高性能な薄膜トランジスタを形成することができる。

【発明を実施するための最良の形態】

【0020】

以下、この発明の一実施形態について、図面を基にして説明する。この実施形態の薄膜トランジスタは、ボトムゲート型の構造であり、透明半導体を用いて自己整合的に各素子が形成されたもので、図1(f)に示すように、ガラスや透明プラスチック等の透明基板32の上面にNi−Cr、Cr−Ti、Ta等の金属により長方形状の不透明なゲート電極34が形成されている。ゲート電極34上には、Ta2O5、SiO2、またはAl2O3等の透光性のゲート絶縁膜36が形成され、その上にIn2O3(ITO)やZnO、SnO2、In2O3−ZnOの金属酸化物等から成る透明半導体層40が設けられている。透明半導体層40はゲート電極34よりより幅広く形成され、ゲート電極34の両側に跨る。透明半導体層40の両端部には、Cr/Au等のソース電極42とドレイン電極44が、ゲート電極34の幅よりも僅かに狭い間隔を空けて、高精度に自己整合的に形成されている。

【0021】

この第一実施形態の薄膜トランジスタの製造工程は、透明基板32の上面一面にゲート電極材料をスパッタリング等により形成して、リソグラフィ工程の後、不透明なゲート電極34をドライエッチング等により長方形に形成する。次に、レジストの剥離・洗浄の後、透光性のゲート絶縁膜36を形成し、さらにその上に、蒸着やスパッタリング等により透明半導体薄膜38を形成する(図1(a))。この透明半導体薄膜38の厚みは、特に限定されないが、例えば、約20〜250nmに形成され、好ましくは、50〜150nm程度に形成される。

【0022】

ここで、ゲート絶縁膜36、透明半導体材料層38の形成は連続して行われるため、トランジスタ界面の清浄化が可能となり、電子または正孔の移動度の向上、所定のしきい電圧の適正化が成され、トランジスタの信頼性向上に繋がる。

【0023】

続いて、リソグラフィ工程、エッチング等を経て、透明半導体薄膜38から、透明半導体層40のパターニングを行い(図1(b)、透明半導体薄膜38の余分な部位を分離する。その後、ポジ型フォトレジスト46を全面形成し、透明基板32の背面側から、紫外線ランプ等により露光を行う(図1(c))。このとき、紫外線に対して透明性の高い透明半導体を選択することにより、フォトレジスト46が露光される。そして、現像を行うことにより、光の回折等の影響でゲート電極34より約0.5μm程度内側に入り込んだフォトレジストパターン50が形成される(図1(d)。

【0024】

次に、透明半導体に対してオーミック接触を行うことが可能な、AlやCr−Au等の電極金属48を一面に形成する(図1(e)。最後に、フォトレジストパターン50を除去して、フォトレジストパターン50上の電極金属48をリフトオフする(図1(f)。これにより、透明酸化物半導体を用いたボトムゲート型の薄膜トランジスタ構造が完成する。

【0025】

この実施形態の薄膜トランジスタによれば、ゲート絶縁膜36と透明半導体薄膜38の形成が連続して行われ、透明半導体層40のトランジスタ界面が清浄に維持され、透明半導体薄膜38の電子または正孔の移動度が向上し、所定のしきい電圧の適正化が成される。また、ソース電極42とドレイン電極44は、自己整合的に形成されるので、ゲート電極34の両端は、ソース・ドレイン領域の端部と膜厚方向に揃った位置に存在する。さらに、ソース電極42とドレイン電極44の内側端部は、ゲート電極34の両端部より最小限内側の位置に設定可能である。これにより、ソース・ドレイン領域とゲート電極34間には寄生容量が生じず、動作速度の向上を図ることができる。

【0026】

次に、この発明の薄膜トランジスタとその製造方法の第二実施形態について図2を基にして説明する。ここで、上記実施形態と同様の部材は、同一の符号を付して説明する。この実施形態の薄膜トランジスタは、上記実施形態と同様に、透明半導体を用いて自己整合的に各素子が形成されたもので、図2(d)に示すように、トップゲート型の構造に形成されている。ガラスや透明プラスチック等の透明基板32の上面には、AlやCr/Au等のソース電極42とドレイン電極44が形成されている。ソース電極42とドレイン電極44上には、In2O3(ITO)やZnO、SnO2、In2O3−ZnOの金属酸化物等から成る透明半導体層40が設けられている。透明半導体層40は、ソース電極42とドレイン電極44に跨って各々積層するように、ソース電極42とドレイン電極44との間隔より広く形成されている。透明半導体層40上には、同形状にTa2O5、SiO2、またはAl2O3等の透光性のゲート絶縁膜36が形成されている。そして、ソース電極42とドレイン電極44の両端部に対応するように、ソース電極42とドレイン電極44の間隔より僅かに広いゲート電極34が形成されている。ゲート電極は、Ni−Cr、Cr−Ti、Ta等の金属により長方形状に形成されている。

【0027】

この第二実施形態の薄膜トランジスタの製造工程は、透明基板32の上面一面にソース電極42及びドレイン電極44の材料を、蒸着やスパッタリング等により形成して、リソグラフィ工程の後ドライエッチング等により、不透明なソース電極42及びドレイン電極44を形成する。次に、レジストの剥離・洗浄の後、透明半導体薄膜、ゲート絶縁膜を連続的に一面に形成し、所定形状にパターニングを行い、余分な透明半導体薄膜及びゲート絶縁膜を分離して、所定形状の透明半導体層40とゲート絶縁膜36を形成する。この透明半導体薄膜の厚みは、特に限定されないが、例えば、約20〜250nmに形成され、好ましくは、50〜150nm程度に形成される。さらに、ポジ形フォトレジスト52を一面に形成し、背面露光を実施する(図2(a))。

【0028】

この後、現像を行うことで、後述するゲート電極34に対対応した開口部を形成する(図2(b))。開口部は、光の回折等の影響でソース電極42及びドレイン電極44間隔より約0.5μm程度外側に広く開口したフォトレジストパターン54が形成される(図2(b))。そして、蒸着やスパッタリング等により、ゲート電極34用のNi−Cr、Cr−Ti、Ta等の金属を一面に形成する(図2(c))。

【0029】

最後に、フォトレジストパターン54を除去して、フォトレジストパターン54上のゲート電極金属をリフトオフする(図2(d))。これにより、透明酸化物半導体を用いたトップゲート型の薄膜トランジスタ構造が完成する。

【0030】

この実施形態の薄膜トランジスタによれば、上記実施形態と同様の効果を有し、さらに、トップゲート型の薄膜トランジスタは、透明半導体層40の上部にゲート絶縁膜を設ける構造を有するので、透明半導体層40の上部の結晶性の良好な領域を活性層として用いることができる。

【0031】

なお、この発明の薄膜トランジスタは、上記実施形態に限定されるものではなく、透明半導体は、金属酸化物以外のセラミックス透明半導体やその他透明な半導体を利用することも可能である。また、各部材の形状や素材など適宜変更可能である。

【実施例1】

【0032】

以下に、図1に示すプロセスにより、透明酸化物半導体を用いて製造した自己整合型の薄膜トランジスタの、ドレイン電流−ドレイン電圧特性を示す。使用した半導体はIZO(出光興産製)200Åである。アニール温度は150℃からトランジスタ特性が発現し、今回の特性では300℃でアニールを行った。ゲート電極はTA50nm、絶縁膜はTa2O5の薄膜150nm、ソース/ドレイン電極は、Cr5nm/Au50nmである。トランジスタの移動度として18.5 cm2/Vs、オンオフ比4.5×107が得られた。これより、自己整合プロセスを導入して、優れた特性の透明酸化物半導体による薄膜トランジスタの、動作を確認することができた。

【図面の簡単な説明】

【0033】

【図1】この発明の第一実施形態の自己整合透明半導体トランジスタの製造方法を示す概略工程図である。

【図2】この発明の第二実施形態の自己整合透明半導体トランジスタの製造方法を示す概略工程図である。

【図3】この発明の自己整合透明半導体トランジスタの実施例による測定結果を示すグラフである。

【図4】従来の自己整合によるトランジスタの製造方法を示す概略工程図である。

【図5】他の従来の自己整合によるトランジスタの製造方法を示す概略工程図である。

【符号の説明】

【0034】

32 透明基板

34 ゲート電極

36 ゲート絶縁膜

38 透明半導体薄膜

40 透明半導体層

42 ソース電極

44 ドレイン電極

50,54 フォトレジストパターン

【特許請求の範囲】

【請求項1】

透光性のある透明基板と、この透明基板上に形成された不透明な電極と、この不透明な電極と相補的に対向するように自己整合して形成された他方の電極と、前記各電極間に位置した透光性の絶縁膜及び透明半導体層とを備えたことを特徴とする薄膜トランジスタ。

【請求項2】

前記不透明な電極はゲート電極であり、前記他方の電極は、ソース電極及びドレイン電極であり、前記ソース電極及びドレイン電極の間隔が、前記ゲート電極の幅と自己整合的に形成されたものである請求項1記載の薄膜トランジスタ。

【請求項3】

前記不透明な電極は、ソース電極及びドレイン電極であり、前記他方の電極は、前記ソース電極及びドレイン電極の間隔に対応して自己整合的に形成されたゲート電極である請求項1記載の薄膜トランジスタ。

【請求項4】

透光性のある透明基板上に不透明な電極を所定の形状で形成し、この不透明な電極に重ねて透光性の絶縁膜及び透明半導体層を積層し、その上に前記不透明な電極に相補的に対向するように、自己整合させて他方の電極を形成することを特徴とする薄膜トランジスタの製造方法。

【請求項5】

前記不透明な電極はゲート電極であり、このゲート電極に重ねて、前記絶縁膜及び透明半導体層を積層し、前記ゲート電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ゲート電極に対応したソース電極及びドレイン電極を自己整合的に形成する請求項4記載の薄膜トランジスタの製造方法。

【請求項6】

前記不透明な電極はソース電極及びドレイン電極であり、このソース電極及びドレイン電極に重ねて、前記透明半導体層と前記絶縁膜を順に積層して所定形状に形成し、前記ソース電極及びドレイン電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ソース電極及びドレイン電極間の間隔に対応したソース電極及びドレイン電極を自己整合的に形成する請求項4記載の薄膜トランジスタの製造方法。

【請求項1】

透光性のある透明基板と、この透明基板上に形成された不透明な電極と、この不透明な電極と相補的に対向するように自己整合して形成された他方の電極と、前記各電極間に位置した透光性の絶縁膜及び透明半導体層とを備えたことを特徴とする薄膜トランジスタ。

【請求項2】

前記不透明な電極はゲート電極であり、前記他方の電極は、ソース電極及びドレイン電極であり、前記ソース電極及びドレイン電極の間隔が、前記ゲート電極の幅と自己整合的に形成されたものである請求項1記載の薄膜トランジスタ。

【請求項3】

前記不透明な電極は、ソース電極及びドレイン電極であり、前記他方の電極は、前記ソース電極及びドレイン電極の間隔に対応して自己整合的に形成されたゲート電極である請求項1記載の薄膜トランジスタ。

【請求項4】

透光性のある透明基板上に不透明な電極を所定の形状で形成し、この不透明な電極に重ねて透光性の絶縁膜及び透明半導体層を積層し、その上に前記不透明な電極に相補的に対向するように、自己整合させて他方の電極を形成することを特徴とする薄膜トランジスタの製造方法。

【請求項5】

前記不透明な電極はゲート電極であり、このゲート電極に重ねて、前記絶縁膜及び透明半導体層を積層し、前記ゲート電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ゲート電極に対応したソース電極及びドレイン電極を自己整合的に形成する請求項4記載の薄膜トランジスタの製造方法。

【請求項6】

前記不透明な電極はソース電極及びドレイン電極であり、このソース電極及びドレイン電極に重ねて、前記透明半導体層と前記絶縁膜を順に積層して所定形状に形成し、前記ソース電極及びドレイン電極に対応したフォトレジストパターンを形成し、このフォトレジストパターンを含む一面に電極材料を積層し、この後、前記フォトレジストパターンを除去して前記フォトレジストパターン上の前記電極材料をリフトオフし、前記ソース電極及びドレイン電極間の間隔に対応したソース電極及びドレイン電極を自己整合的に形成する請求項4記載の薄膜トランジスタの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2009−206388(P2009−206388A)

【公開日】平成21年9月10日(2009.9.10)

【国際特許分類】

【出願番号】特願2008−49196(P2008−49196)

【出願日】平成20年2月29日(2008.2.29)

【出願人】(305060567)国立大学法人富山大学 (194)

【Fターム(参考)】

【公開日】平成21年9月10日(2009.9.10)

【国際特許分類】

【出願日】平成20年2月29日(2008.2.29)

【出願人】(305060567)国立大学法人富山大学 (194)

【Fターム(参考)】

[ Back to top ]