薄膜トランジスタ表示板及びその製造方法

【課題】酸化物半導体を使用する薄膜トランジスタの特性を向上させることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ表示板を提供する。本発明の一実施形態に係る薄膜トランジスタ表示板は、基板の上に配置するゲート配線層、前記ゲート配線層の上に配置する酸化物半導体層、及び前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、前記データ配線層は銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む。

【解決手段】薄膜トランジスタ表示板を提供する。本発明の一実施形態に係る薄膜トランジスタ表示板は、基板の上に配置するゲート配線層、前記ゲート配線層の上に配置する酸化物半導体層、及び前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、前記データ配線層は銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタ表示板及びその製造方法に関する。

【背景技術】

【0002】

一般に、液晶表示装置や有機発光表示装置などの平板表示装置は、複数対の電界生成電極と、その間に挿入されている電気光学(electro−optical)活性層とを含む。液晶表示装置の場合電気光学活性層として液晶層を含み、有機発光表示装置の場合電気光学活性層として有機発光層を含む。

【0003】

一対になる電界生成電極のうちの一つは、通常、スイッチング素子に接続されて電気信号の印加を受け、電気光学活性層はこの電気信号を光学信号に変換することによって映像が表示される。

【0004】

平板表示装置においては、スイッチング素子として三端子素子の薄膜トランジスタ(thin film transistor、TFT)を使用し、この薄膜トランジスタを制御するための走査信号を伝達するゲート線(gate line)と、画素電極に印加される信号を伝達するデータ線(data line)などの信号線が平板表示装置に具備される。

【0005】

一方、表示装置の面積が大きくなることによって、高速駆動を実現するために酸化物半導体技術が研究されており、信号線の抵抗を減少させる方法が研究されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】韓国出願公開2010-0118838号明細書

【発明の概要】

【発明が解決しようとする課題】

【0007】

信号線の抵抗を減少させるために、銅とチタニウムの二重膜で信号線を形成する方法が研究されている。しかし、チタニウムと酸化物半導体との界面で発生する異物性欠陥によって薄膜トランジスタの特性が低下する恐れがある。

【0008】

そこで、本発明の目的は、酸化物半導体を使用する薄膜トランジスタの特性を向上させることができる薄膜トランジスタ表示板及びその製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明の一実施形態に係る薄膜トランジスタ表示板は、基板の上に配置するゲート配線層、前記ゲート配線層の上に配置する酸化物半導体層、及び前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、前記データ配線層は銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む。

【0010】

前記キャッピング層は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つを含む銅合金、または銅、アルミニウム、マグネシウムの合金とすることができる。

【0011】

前記キャッピング層は銅マンガン合金を含むことができる。

【0012】

前記酸化物半導体層は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含むことができる。

【0013】

前記データ配線層は、前記主配線層の下に配置するバリア層をさらに含むことができる。

【0014】

前記バリア層は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成された物質を含むことができる。

【0015】

前記バリア層の中で銅と合金を形成する物質は10at%以上の含有量を有することができる。

【0016】

前記データ配線層は、前記ゲート線と交差して、ソース電極を含むデータ線及び前記ソース電極と対向するドレイン電極を含むことができる。

【0017】

前記データ線及び前記ドレイン電極を覆って、前記ドレイン電極の一部を露出させるコンタクトホールを有する保護膜、及び前記コンタクトホールによって前記ドレイン電極と電気的に接続されている画素電極をさらに含むことができる。

【0018】

前記保護膜は酸化ケイ素を含むことができる。

【0019】

本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法は、基板の上にゲート線を形成する段階、前記ゲート線を覆うゲート絶縁膜を形成する段階、前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、前記第2金属膜の上に、第1領域と、前記第1領域より厚さが厚い第2領域とを有する第1感光膜パターンを形成する段階、前記第1感光膜パターンをマスクとして前記第2金属膜と前記第1金属膜を共にエッチングする段階、前記第1感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階、前記第1感光膜パターンをエッチバックして第2感光膜パターンを形成する段階、及び前記第2感光膜パターンをマスクとして前記第1金属膜及び前記2金属膜を同時にウェットエッチングして、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階を含む。

【0020】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成することができる。

【0021】

前記第1金属膜は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成することができる。

【0022】

前記第1金属膜の中で銅と合金を形成する物質は25at%以上の含有量を有するように形成することができる。

【0023】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含むことができる。

【0024】

前記第3金属膜は銅合金で形成することができる。

【0025】

前記第3金属膜は、前記第2感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をウェットエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含むことができる。

【0026】

本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法は、配線部とチャネル部を含む基板の上にゲート線を形成する段階、前記ゲート線を覆うゲート絶縁膜を形成する段階、前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、前記第2金属膜の上に前記チャネル部に対応する位置にオープン部を有する第1感光膜パターンを形成する段階、前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜を共にエッチングして、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階、前記第1感光膜パターンを除去する段階、前記データ配線層を覆う第2感光膜パターンを形成する段階、及び前記第2感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階を含む。

【0027】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成することができる。

【0028】

前記第1金属膜は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成することができる。

【0029】

前記第1金属膜の中で銅と合金を形成する物質は25a%以上の含有量を有するように形成することができる。

【0030】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含むことができる。

【0031】

前記第3金属膜は銅合金で形成することができる。

【0032】

前記第3金属膜は、前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含むことができる。

【発明の効果】

【0033】

このように本発明の一実施形態によれば、酸化物半導体と信号線の間に安定した接触が行われて、薄膜トランジスタの特性を向上させることができる。

【0034】

また、本発明の他の実施形態によれば、薄膜トランジスタ表示板の製造過程で多層に形成された信号線を一括エッチングすることによって、工程を単純化することができる。

【0035】

さらに、本発明の他の実施形態によれば、薄膜トランジスタ表示板の製造過程で発生するスキュー(skew)を減少して、チャネルの長さを調節することができる。

【図面の簡単な説明】

【0036】

【図1】本発明の一実施形態に係る薄膜トランジスタ表示板の一画素を示した配置図である。

【図2】図1のII−II線に沿った断面図である。

【図3】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法について説明するための図1のII−II線に沿った断面図である。

【図4】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図5】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図6】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図7】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図8】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図9】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図10】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図11】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図12】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図13】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【発明を実施するための形態】

【0037】

添付した図面を参照して、本発明の好ましい実施形態について詳細に説明する。しかし、本発明はここで説明される実施形態に限定されず、他の形態に具体化することもできる。むしろ、ここで紹介される実施形態は、開示された内容が徹底でかつ完全なものとなるようにし、なお、当業者に本発明の思想が十分に伝達されるようにするために提供させるものである。

【0038】

図面において、層及び領域の厚さは明確性のために誇張して示した。また、層が他の層または基板の「上」にあるという場合に、それは他の層または基板の上に直接形成されるか、またはこれらの間に第3の層が介されることも可能である。明細書の全体にわたって同一の参照番号に表示された部分は同一の構成要素を意味する。

【0039】

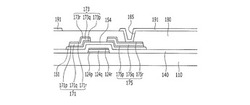

図1は、本発明の一実施形態に係る薄膜トランジスタ表示板の一画素を示した配置図である。図2は、図1のII−II線に沿った断面図である。

【0040】

図1及び図2を参照すれば、透明なガラスまたはプラスチックなどからなる絶縁基板110の上に複数のゲート線121が形成されている。

【0041】

ゲート線121は、ゲート信号を伝達し、主に横方向に延びている。各ゲート線121はゲート線121から突出した複数のゲート電極124を含む。

【0042】

ゲート線121及びゲート電極124は、第1層121p、124p、第2層121q、124q、及び第3層121r、124rに形成された三重膜構造を有することができる。第1層121p、124p、第2層121q、124q、及び第3層121r、124rは、それぞれアルミニウム(Al)とアルミニウム合金などアルミニウム系の金属、銀(Ag)と銀合金など銀系の金属、銅(Cu)と銅合金など銅系の金属、モリブデン(Mo)とモリブデン合金などモリブデン系の金属、クロム(Cr)、チタニウム(Ti)、タンタル(Ta)、マンガン(Mn)などからなることができる。

【0043】

また、第1層121p、124p、第2層121q、124q、及び第3層121r、124rは、互いに物理的性質が異なる膜を組合わせて形成することができる。本実施形態ではゲート線121及びゲート電極124が三重膜に形成されることと説明したが、ここに限定されず、単一膜または二重膜形態も可能である。

【0044】

ゲート線121の上には酸化ケイ素または窒化ケイ素などの絶縁物質からなるゲート絶縁膜140を配置する。

【0045】

ゲート絶縁膜140の上には複数の酸化物半導体151が形成されている。酸化物半導体151は、主に縦方向に延びて、ゲート電極124に向かって延び出た複数の突出部(projection)154を含む。

【0046】

酸化物半導体151は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含む。

【0047】

酸化物半導体151及びゲート絶縁膜140の上には複数のデータ線171と複数のドレイン電極175が形成されている。

【0048】

データ線171は、データ信号を伝達し、主に縦方向に延びてゲート線121と交差する。各データ線171は、ゲート電極124に向かって延びて、U字状を有する複数のソース電極173を含む。

【0049】

ドレイン電極175は、データ線171と分離されて、ソース電極173のU字状の中間で上部に向かって延長されている。

【0050】

ソース電極173を含むデータ線171及びドレイン電極175は、バリア層171p、173p、175p、主配線層171q、173q、175q、及びキャッピング層171r、173r、175rの三重膜構造を有する。バリア層171p、173p、175pは銅合金からなり、主配線層171q、173q、175qは銅からなり、キャッピング層171r、173r、175rは銅合金からなる。

【0051】

本実施形態とは異なって、キャッピング層171r、173r、175rは省略されて、データ線171及びドレイン電極175は、バリア層171p、173p、175pと、主配線層171q、173q、175qの二重膜に形成することができる。

【0052】

他の実施形態においては、バリア層171p、173p、175pが省略されて、データ線171及びドレイン電極175は主配線層171q、173q、175qとキャッピング層171r、173r、175rの二重膜に形成されることもできる。

【0053】

バリア層171p、173p、175p及びキャッピング層171r、173r、175rは、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成することができる。キャッピング層171r、173r、175rは、銅、マグネシウム、アルミニウムの合金で形成することができる。

【0054】

バリア層171p、173p、175pは銅合金で形成することによって、既にバリア層としてチタニウムを用いて発生する異物性欠陥を減らすことができる。ここで、異物性欠陥とは、酸素と結合しようとするチタニウムの性質ため、酸化物半導体の金属成分のうちの一部が析出されて、酸化物半導体とバリア層の間の界面で突起が形成されることをいう。これによって薄膜トランジスタの特性が悪くなる可能性がある。

【0055】

バリア層171p、173p、175pを形成する物質中、銅と合金を形成する物質は10at%以上の含有量を有することができる。例えば、銅と合金を形成するマンガン(Mn)がバリア層171p、173p、175pに10at%以上含まれる場合に、酸化物半導体層の電荷移動度が向上して、高解像度と高速駆動が可能になる。

【0056】

実験結果、マンガン(Mn)がバリア層171p、173p、175pに4at%含まれている場合の電荷移動度が3.65(cm2/Vs)であり、バリア層171p、173p、175pにマンガン(Mn)が10at%含まれている場合の電荷移動度が6.25(cm2/Vs)と現れた。このように、銅に含まれているマンガンの含有量を増加させるほど、薄膜トランジスタの特性が改善されることが確認できた。

【0057】

酸化物半導体層151の突出部154には、ソース電極173とドレイン電極175の間にデータ線171及びドレイン電極175によって覆われずに露出した部分がある。酸化物半導体層151は、突出部154の露出した部分を除いて、データ線171及びドレイン電極175と実質的に同一の平面パターンを有する。

【0058】

一つのゲート電極124、一つのソース電極173、及び一つのドレイン電極175は、酸化物半導体層151の突出部154と共に一つの薄膜トランジスタ(thin film transistor、TFT)を構成し、薄膜トランジスタのチャネルはソース電極173とドレイン電極175の間の突出部154に形成される。

【0059】

データ線171、ドレイン電極175、及び露出した半導体層の突出部154部分の上には保護膜(passivation layer)180が形成されている。保護膜180は、窒化ケイ素や酸化ケイ素などの無機絶縁物、有機絶縁物、低誘電率絶縁物などからなる。

【0060】

酸化ケイ素で形成された保護膜の蒸着時、銅で形成された主配線層171q、173q、175qが保護膜180と直接接触して生成される銅酸化物(CuOx)によってリフティング(lifting)が発生するか、または保護膜180に後述するコンタクトホール185を形成する時、腐蝕が起こりうる。しかし、本実施形態によれば、保護膜180の下部にキャッピング層171r、173r、175rを配置することによって、データ線171とドレイン電極175のリフティング及び腐食を防止することができる。

【0061】

保護膜180にはドレイン電極175の一端を露出する複数のコンタクトホール185が形成されている。

【0062】

保護膜180の上には複数の画素電極(pixel electrode)191が形成されている。画素電極191はコンタクトホール185によってドレイン電極175と物理的、電気的に接続されており、ドレイン電極175からデータ電圧の印加を受ける。データ電圧が印加された画素電極191は共通電圧の印加を受ける共通電極(図示せずが、対向表示板に形成されるか、または薄膜トランジスタ表示板に形成される)と共に電界を生成することによって、二つの電極間の液晶層(図示せず)の液晶分子の方向を決定する。画素電極191と共通電極は、キャパシタ[以下、「液晶キャパシタ(liquid crystal capacitor)」という]を構成して、薄膜トランジスタがターンオフされた後にも印加された電圧を維持する。

【0063】

画素電極191は維持電極線(図示せず)と重畳してストレージキャパシタ(storage capacitor)を形成することができ、これによって液晶キャパシタの電圧維持能力を強化することができる。

【0064】

画素電極191はITOまたはIZOなどの透明導電体で形成することができる。

【0065】

図3乃至図9は、本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【0066】

図3を参照すれば、透明なガラスまたはプラスチックなどからなる絶縁基板110の上に、図1、2で説明したゲート配線用金属膜をスパッタリング方法などを利用して積層した後に、これをパターニングして、ゲート線121及びゲート電極124を形成する。

【0067】

図4を参照すれば、ゲート線121及びゲート電極124の上にゲート絶縁膜140、酸化物半導体層150、第1金属膜170p、第2金属膜170q、及び第3金属膜170rを積層する。

【0068】

酸化物半導体層170は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含む物質で形成することができる。第1金属膜170pは、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成することができる。第2金属膜170qは銅で形成することができ、第3金属膜170rは、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金、または銅、アルミニウム、マグネシウムの合金で形成することができる。

【0069】

第3金属膜10rの上に感光膜(photo resist)を形成した後にパターニングして、第1感光膜パターン50を形成する。第1感光膜パターン50は、厚い第1領域50aと、相対的に薄い第2領域50bを有する。第1感光膜パターン50の厚さの差は、マスクを利用して照射する光の量を調節するか、またはリフロー方法を利用して形成することができる。光の量を調節する場合には、マスクにスリットパターンまたは格子パターンや半透明層が形成されていてもよい。厚さの薄い第2領域50bは、薄膜トランジスタのチャネル領域が形成される位置に対応する。

【0070】

図5を参照すれば、第1感光膜パターン50をマスクとして第1金属膜170p、第2金属膜170q、第3金属膜170r、及び酸化物半導体層150を同時にエッチングする。ここで用いるエッチング液は、第1金属膜170p、第2金属膜170q、第3金属膜170r、及び酸化物半導体層150を共にエッチングすることができるエッチング液(etchant)を用いることができる。

【0071】

図6を参照すれば、エッチバック(etch back)を行って第1感光膜パターン50の第2部分50bを除去する。この時、第1部分50aも共にエッチングされて幅及び高さが減り、第2感光膜パターン51が形成される。第2感光膜パターン51は、図5における第1感光膜パターン50が形成された領域A、B、Cに比べて狭い領域A'、B'、C'に形成されている。

【0072】

図7を参照すれば、第2感光膜パターン51をマスクとして第2感光膜パターン51の第2領域A'に位置する第1金属膜170p、第2金属膜170q、及び第3金属膜170rをエッチングする。ここで用いるエッチング液は、図5で用いるエッチング液とは異なるエッチング液を用いなければならない。なぜなら、第2領域A'の酸化物半導体層150がエッチングされてはいけないためである。

【0073】

この時、第1金属膜170p、第2金属膜170q、及び第3金属膜170rがチャネル領域154を介して分離されて、データ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rが形成される。また、酸化物半導体層150の上部面が露出して、チャネル領域を形成する酸化物半導体154が形成される。

【0074】

このように厚さが異なる感光膜パターンを利用すれば、酸化物半導体154はチャネル領域を除いてデータ線171、ソース電極173、及びドレイン電極175と実質的に同一の平面パターンを有する。

【0075】

その後、図8を参照すれば、アッシング(ashing)によって第2感光膜パターン51を除去する。

【0076】

次に、図9を参照すれば、有機物質または無機物質で保護膜180を形成し、感光膜パターンを利用してドレイン電極175を露出させるコンタクトホール185を形成する。保護膜180の形成後に、酸化物半導体154の特性を改善させるために熱処理が行ってもよい。

【0077】

その後、図2に示したように、ITOまたはIZOのような透明導電体を積層してパターニングし、露出したドレイン電極175と電気的に接触する画素電極191を形成する。

【0078】

図10乃至図13は、本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【0079】

図10を参照すれば、図3〜図9で説明した実施形態と同様に、ゲート線121及びゲート電極124を形成した後に、ゲート絶縁膜140、酸化物半導体層150、第1金属膜170p、第2金属膜170q、及び第3金属膜170rを積層する。

【0080】

次に、第3金属膜170rの上に感光膜を形成した後にパターニングして、第1感光膜パターン50aを形成する。図3乃至図9で説明した実施形態の第1感光膜パターン50とは異なって、チャネル領域に対応する部分に位置する第3金属膜170rの上部面を露出するオープン部(opening)を有するように、第1感光膜パターン51aを形成する。

【0081】

図11を参照すれば、第1感光膜パターン50aをマスクとして第1金属膜170p、第2金属膜170q、及び第3金属膜170rをエッチングする。ここで、オープン部によって露出した部分の第3金属膜170r、第2金属膜170q、及び第1金属膜170pも順次にエッチングされて、チャネル領域が形成される位置の酸化物半導体層150が露出される。

【0082】

この時、第1金属膜170p、第2金属膜170q、及び第3金属膜170rがチャネル領域CHを介して分離されて、データ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rを含むデータ配線層が形成される。データ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rそれぞれは、酸化物半導体層150の上に位置するバリア層171p、173p、175r、バリア層171p、173p、175pの上に位置する主配線層171q、173q、175q、及び主配線層171q、173q、175qの上に位置するキャッピング層171r、173r、175rを有する。

【0083】

図12を参照すれば、第1感光膜パターン50aを除去して、第2感光膜パターン50bを形成する。第2感光膜パターン50bは、データ線171p、171q、171r、ソース電極173p、173q、173r、ドレイン電極175p、175q、175r、及びチャネル領域に対応する露出した酸化物半導体層150を覆うように形成される。

【0084】

図13を参照すれば、第2感光膜パターン50bをマスクとして酸化物半導体層150をエッチングし、チャネル領域を除いてデータ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rと実質的に同一の平面パターンを有する酸化物半導体154を形成する。チャネル領域に対応する酸化物半導体層150は、第2感光膜パターン50bによって覆われているため保護される。

【0085】

そして、第2感光膜パターン50bを除去する。

【0086】

この後の工程は、図9で説明した実施形態と同様に、コンタクトホールを有する保護膜を形成した後、保護膜のコンタクトホールによってドレイン電極と電気的に接続されるように保護膜の上に画素電極を形成する。

【0087】

本実施形態によれば、データ配線層と酸化物半導体層のエッチングを分離して行うことによって、三重膜のデータ配線層を形成する時に発生するスキュー(skew)のために酸化物半導体層の側壁がデータ配線層の側壁と一致せずに突出することを最小化することができる。

【0088】

以上、本発明の好ましい実施形態について詳細に説明したが、本発明の権利範囲はこれに限定されず、次の請求範囲で定義している本発明の基本概念を利用した当業者の種々の変形及び改良形態も本発明の権利範囲に属するものである。

【符号の説明】

【0089】

121 ゲート線

124 ゲート電極

154 酸化物半導体

171 データ線

173 ソース電極

175 ドレイン電極

【技術分野】

【0001】

本発明は、薄膜トランジスタ表示板及びその製造方法に関する。

【背景技術】

【0002】

一般に、液晶表示装置や有機発光表示装置などの平板表示装置は、複数対の電界生成電極と、その間に挿入されている電気光学(electro−optical)活性層とを含む。液晶表示装置の場合電気光学活性層として液晶層を含み、有機発光表示装置の場合電気光学活性層として有機発光層を含む。

【0003】

一対になる電界生成電極のうちの一つは、通常、スイッチング素子に接続されて電気信号の印加を受け、電気光学活性層はこの電気信号を光学信号に変換することによって映像が表示される。

【0004】

平板表示装置においては、スイッチング素子として三端子素子の薄膜トランジスタ(thin film transistor、TFT)を使用し、この薄膜トランジスタを制御するための走査信号を伝達するゲート線(gate line)と、画素電極に印加される信号を伝達するデータ線(data line)などの信号線が平板表示装置に具備される。

【0005】

一方、表示装置の面積が大きくなることによって、高速駆動を実現するために酸化物半導体技術が研究されており、信号線の抵抗を減少させる方法が研究されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】韓国出願公開2010-0118838号明細書

【発明の概要】

【発明が解決しようとする課題】

【0007】

信号線の抵抗を減少させるために、銅とチタニウムの二重膜で信号線を形成する方法が研究されている。しかし、チタニウムと酸化物半導体との界面で発生する異物性欠陥によって薄膜トランジスタの特性が低下する恐れがある。

【0008】

そこで、本発明の目的は、酸化物半導体を使用する薄膜トランジスタの特性を向上させることができる薄膜トランジスタ表示板及びその製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明の一実施形態に係る薄膜トランジスタ表示板は、基板の上に配置するゲート配線層、前記ゲート配線層の上に配置する酸化物半導体層、及び前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、前記データ配線層は銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む。

【0010】

前記キャッピング層は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つを含む銅合金、または銅、アルミニウム、マグネシウムの合金とすることができる。

【0011】

前記キャッピング層は銅マンガン合金を含むことができる。

【0012】

前記酸化物半導体層は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含むことができる。

【0013】

前記データ配線層は、前記主配線層の下に配置するバリア層をさらに含むことができる。

【0014】

前記バリア層は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成された物質を含むことができる。

【0015】

前記バリア層の中で銅と合金を形成する物質は10at%以上の含有量を有することができる。

【0016】

前記データ配線層は、前記ゲート線と交差して、ソース電極を含むデータ線及び前記ソース電極と対向するドレイン電極を含むことができる。

【0017】

前記データ線及び前記ドレイン電極を覆って、前記ドレイン電極の一部を露出させるコンタクトホールを有する保護膜、及び前記コンタクトホールによって前記ドレイン電極と電気的に接続されている画素電極をさらに含むことができる。

【0018】

前記保護膜は酸化ケイ素を含むことができる。

【0019】

本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法は、基板の上にゲート線を形成する段階、前記ゲート線を覆うゲート絶縁膜を形成する段階、前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、前記第2金属膜の上に、第1領域と、前記第1領域より厚さが厚い第2領域とを有する第1感光膜パターンを形成する段階、前記第1感光膜パターンをマスクとして前記第2金属膜と前記第1金属膜を共にエッチングする段階、前記第1感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階、前記第1感光膜パターンをエッチバックして第2感光膜パターンを形成する段階、及び前記第2感光膜パターンをマスクとして前記第1金属膜及び前記2金属膜を同時にウェットエッチングして、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階を含む。

【0020】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成することができる。

【0021】

前記第1金属膜は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成することができる。

【0022】

前記第1金属膜の中で銅と合金を形成する物質は25at%以上の含有量を有するように形成することができる。

【0023】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含むことができる。

【0024】

前記第3金属膜は銅合金で形成することができる。

【0025】

前記第3金属膜は、前記第2感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をウェットエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含むことができる。

【0026】

本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法は、配線部とチャネル部を含む基板の上にゲート線を形成する段階、前記ゲート線を覆うゲート絶縁膜を形成する段階、前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、前記第2金属膜の上に前記チャネル部に対応する位置にオープン部を有する第1感光膜パターンを形成する段階、前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜を共にエッチングして、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階、前記第1感光膜パターンを除去する段階、前記データ配線層を覆う第2感光膜パターンを形成する段階、及び前記第2感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階を含む。

【0027】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成することができる。

【0028】

前記第1金属膜は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成することができる。

【0029】

前記第1金属膜の中で銅と合金を形成する物質は25a%以上の含有量を有するように形成することができる。

【0030】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含むことができる。

【0031】

前記第3金属膜は銅合金で形成することができる。

【0032】

前記第3金属膜は、前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含むことができる。

【発明の効果】

【0033】

このように本発明の一実施形態によれば、酸化物半導体と信号線の間に安定した接触が行われて、薄膜トランジスタの特性を向上させることができる。

【0034】

また、本発明の他の実施形態によれば、薄膜トランジスタ表示板の製造過程で多層に形成された信号線を一括エッチングすることによって、工程を単純化することができる。

【0035】

さらに、本発明の他の実施形態によれば、薄膜トランジスタ表示板の製造過程で発生するスキュー(skew)を減少して、チャネルの長さを調節することができる。

【図面の簡単な説明】

【0036】

【図1】本発明の一実施形態に係る薄膜トランジスタ表示板の一画素を示した配置図である。

【図2】図1のII−II線に沿った断面図である。

【図3】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法について説明するための図1のII−II線に沿った断面図である。

【図4】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図5】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図6】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図7】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図8】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図9】本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図10】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図11】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図12】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【図13】本発明のまた他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【発明を実施するための形態】

【0037】

添付した図面を参照して、本発明の好ましい実施形態について詳細に説明する。しかし、本発明はここで説明される実施形態に限定されず、他の形態に具体化することもできる。むしろ、ここで紹介される実施形態は、開示された内容が徹底でかつ完全なものとなるようにし、なお、当業者に本発明の思想が十分に伝達されるようにするために提供させるものである。

【0038】

図面において、層及び領域の厚さは明確性のために誇張して示した。また、層が他の層または基板の「上」にあるという場合に、それは他の層または基板の上に直接形成されるか、またはこれらの間に第3の層が介されることも可能である。明細書の全体にわたって同一の参照番号に表示された部分は同一の構成要素を意味する。

【0039】

図1は、本発明の一実施形態に係る薄膜トランジスタ表示板の一画素を示した配置図である。図2は、図1のII−II線に沿った断面図である。

【0040】

図1及び図2を参照すれば、透明なガラスまたはプラスチックなどからなる絶縁基板110の上に複数のゲート線121が形成されている。

【0041】

ゲート線121は、ゲート信号を伝達し、主に横方向に延びている。各ゲート線121はゲート線121から突出した複数のゲート電極124を含む。

【0042】

ゲート線121及びゲート電極124は、第1層121p、124p、第2層121q、124q、及び第3層121r、124rに形成された三重膜構造を有することができる。第1層121p、124p、第2層121q、124q、及び第3層121r、124rは、それぞれアルミニウム(Al)とアルミニウム合金などアルミニウム系の金属、銀(Ag)と銀合金など銀系の金属、銅(Cu)と銅合金など銅系の金属、モリブデン(Mo)とモリブデン合金などモリブデン系の金属、クロム(Cr)、チタニウム(Ti)、タンタル(Ta)、マンガン(Mn)などからなることができる。

【0043】

また、第1層121p、124p、第2層121q、124q、及び第3層121r、124rは、互いに物理的性質が異なる膜を組合わせて形成することができる。本実施形態ではゲート線121及びゲート電極124が三重膜に形成されることと説明したが、ここに限定されず、単一膜または二重膜形態も可能である。

【0044】

ゲート線121の上には酸化ケイ素または窒化ケイ素などの絶縁物質からなるゲート絶縁膜140を配置する。

【0045】

ゲート絶縁膜140の上には複数の酸化物半導体151が形成されている。酸化物半導体151は、主に縦方向に延びて、ゲート電極124に向かって延び出た複数の突出部(projection)154を含む。

【0046】

酸化物半導体151は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含む。

【0047】

酸化物半導体151及びゲート絶縁膜140の上には複数のデータ線171と複数のドレイン電極175が形成されている。

【0048】

データ線171は、データ信号を伝達し、主に縦方向に延びてゲート線121と交差する。各データ線171は、ゲート電極124に向かって延びて、U字状を有する複数のソース電極173を含む。

【0049】

ドレイン電極175は、データ線171と分離されて、ソース電極173のU字状の中間で上部に向かって延長されている。

【0050】

ソース電極173を含むデータ線171及びドレイン電極175は、バリア層171p、173p、175p、主配線層171q、173q、175q、及びキャッピング層171r、173r、175rの三重膜構造を有する。バリア層171p、173p、175pは銅合金からなり、主配線層171q、173q、175qは銅からなり、キャッピング層171r、173r、175rは銅合金からなる。

【0051】

本実施形態とは異なって、キャッピング層171r、173r、175rは省略されて、データ線171及びドレイン電極175は、バリア層171p、173p、175pと、主配線層171q、173q、175qの二重膜に形成することができる。

【0052】

他の実施形態においては、バリア層171p、173p、175pが省略されて、データ線171及びドレイン電極175は主配線層171q、173q、175qとキャッピング層171r、173r、175rの二重膜に形成されることもできる。

【0053】

バリア層171p、173p、175p及びキャッピング層171r、173r、175rは、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成することができる。キャッピング層171r、173r、175rは、銅、マグネシウム、アルミニウムの合金で形成することができる。

【0054】

バリア層171p、173p、175pは銅合金で形成することによって、既にバリア層としてチタニウムを用いて発生する異物性欠陥を減らすことができる。ここで、異物性欠陥とは、酸素と結合しようとするチタニウムの性質ため、酸化物半導体の金属成分のうちの一部が析出されて、酸化物半導体とバリア層の間の界面で突起が形成されることをいう。これによって薄膜トランジスタの特性が悪くなる可能性がある。

【0055】

バリア層171p、173p、175pを形成する物質中、銅と合金を形成する物質は10at%以上の含有量を有することができる。例えば、銅と合金を形成するマンガン(Mn)がバリア層171p、173p、175pに10at%以上含まれる場合に、酸化物半導体層の電荷移動度が向上して、高解像度と高速駆動が可能になる。

【0056】

実験結果、マンガン(Mn)がバリア層171p、173p、175pに4at%含まれている場合の電荷移動度が3.65(cm2/Vs)であり、バリア層171p、173p、175pにマンガン(Mn)が10at%含まれている場合の電荷移動度が6.25(cm2/Vs)と現れた。このように、銅に含まれているマンガンの含有量を増加させるほど、薄膜トランジスタの特性が改善されることが確認できた。

【0057】

酸化物半導体層151の突出部154には、ソース電極173とドレイン電極175の間にデータ線171及びドレイン電極175によって覆われずに露出した部分がある。酸化物半導体層151は、突出部154の露出した部分を除いて、データ線171及びドレイン電極175と実質的に同一の平面パターンを有する。

【0058】

一つのゲート電極124、一つのソース電極173、及び一つのドレイン電極175は、酸化物半導体層151の突出部154と共に一つの薄膜トランジスタ(thin film transistor、TFT)を構成し、薄膜トランジスタのチャネルはソース電極173とドレイン電極175の間の突出部154に形成される。

【0059】

データ線171、ドレイン電極175、及び露出した半導体層の突出部154部分の上には保護膜(passivation layer)180が形成されている。保護膜180は、窒化ケイ素や酸化ケイ素などの無機絶縁物、有機絶縁物、低誘電率絶縁物などからなる。

【0060】

酸化ケイ素で形成された保護膜の蒸着時、銅で形成された主配線層171q、173q、175qが保護膜180と直接接触して生成される銅酸化物(CuOx)によってリフティング(lifting)が発生するか、または保護膜180に後述するコンタクトホール185を形成する時、腐蝕が起こりうる。しかし、本実施形態によれば、保護膜180の下部にキャッピング層171r、173r、175rを配置することによって、データ線171とドレイン電極175のリフティング及び腐食を防止することができる。

【0061】

保護膜180にはドレイン電極175の一端を露出する複数のコンタクトホール185が形成されている。

【0062】

保護膜180の上には複数の画素電極(pixel electrode)191が形成されている。画素電極191はコンタクトホール185によってドレイン電極175と物理的、電気的に接続されており、ドレイン電極175からデータ電圧の印加を受ける。データ電圧が印加された画素電極191は共通電圧の印加を受ける共通電極(図示せずが、対向表示板に形成されるか、または薄膜トランジスタ表示板に形成される)と共に電界を生成することによって、二つの電極間の液晶層(図示せず)の液晶分子の方向を決定する。画素電極191と共通電極は、キャパシタ[以下、「液晶キャパシタ(liquid crystal capacitor)」という]を構成して、薄膜トランジスタがターンオフされた後にも印加された電圧を維持する。

【0063】

画素電極191は維持電極線(図示せず)と重畳してストレージキャパシタ(storage capacitor)を形成することができ、これによって液晶キャパシタの電圧維持能力を強化することができる。

【0064】

画素電極191はITOまたはIZOなどの透明導電体で形成することができる。

【0065】

図3乃至図9は、本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【0066】

図3を参照すれば、透明なガラスまたはプラスチックなどからなる絶縁基板110の上に、図1、2で説明したゲート配線用金属膜をスパッタリング方法などを利用して積層した後に、これをパターニングして、ゲート線121及びゲート電極124を形成する。

【0067】

図4を参照すれば、ゲート線121及びゲート電極124の上にゲート絶縁膜140、酸化物半導体層150、第1金属膜170p、第2金属膜170q、及び第3金属膜170rを積層する。

【0068】

酸化物半導体層170は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含む物質で形成することができる。第1金属膜170pは、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成することができる。第2金属膜170qは銅で形成することができ、第3金属膜170rは、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金、または銅、アルミニウム、マグネシウムの合金で形成することができる。

【0069】

第3金属膜10rの上に感光膜(photo resist)を形成した後にパターニングして、第1感光膜パターン50を形成する。第1感光膜パターン50は、厚い第1領域50aと、相対的に薄い第2領域50bを有する。第1感光膜パターン50の厚さの差は、マスクを利用して照射する光の量を調節するか、またはリフロー方法を利用して形成することができる。光の量を調節する場合には、マスクにスリットパターンまたは格子パターンや半透明層が形成されていてもよい。厚さの薄い第2領域50bは、薄膜トランジスタのチャネル領域が形成される位置に対応する。

【0070】

図5を参照すれば、第1感光膜パターン50をマスクとして第1金属膜170p、第2金属膜170q、第3金属膜170r、及び酸化物半導体層150を同時にエッチングする。ここで用いるエッチング液は、第1金属膜170p、第2金属膜170q、第3金属膜170r、及び酸化物半導体層150を共にエッチングすることができるエッチング液(etchant)を用いることができる。

【0071】

図6を参照すれば、エッチバック(etch back)を行って第1感光膜パターン50の第2部分50bを除去する。この時、第1部分50aも共にエッチングされて幅及び高さが減り、第2感光膜パターン51が形成される。第2感光膜パターン51は、図5における第1感光膜パターン50が形成された領域A、B、Cに比べて狭い領域A'、B'、C'に形成されている。

【0072】

図7を参照すれば、第2感光膜パターン51をマスクとして第2感光膜パターン51の第2領域A'に位置する第1金属膜170p、第2金属膜170q、及び第3金属膜170rをエッチングする。ここで用いるエッチング液は、図5で用いるエッチング液とは異なるエッチング液を用いなければならない。なぜなら、第2領域A'の酸化物半導体層150がエッチングされてはいけないためである。

【0073】

この時、第1金属膜170p、第2金属膜170q、及び第3金属膜170rがチャネル領域154を介して分離されて、データ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rが形成される。また、酸化物半導体層150の上部面が露出して、チャネル領域を形成する酸化物半導体154が形成される。

【0074】

このように厚さが異なる感光膜パターンを利用すれば、酸化物半導体154はチャネル領域を除いてデータ線171、ソース電極173、及びドレイン電極175と実質的に同一の平面パターンを有する。

【0075】

その後、図8を参照すれば、アッシング(ashing)によって第2感光膜パターン51を除去する。

【0076】

次に、図9を参照すれば、有機物質または無機物質で保護膜180を形成し、感光膜パターンを利用してドレイン電極175を露出させるコンタクトホール185を形成する。保護膜180の形成後に、酸化物半導体154の特性を改善させるために熱処理が行ってもよい。

【0077】

その後、図2に示したように、ITOまたはIZOのような透明導電体を積層してパターニングし、露出したドレイン電極175と電気的に接触する画素電極191を形成する。

【0078】

図10乃至図13は、本発明の他の実施形態に係る薄膜トランジスタ表示板の製造方法を説明するための図1のII−II線に沿った断面図である。

【0079】

図10を参照すれば、図3〜図9で説明した実施形態と同様に、ゲート線121及びゲート電極124を形成した後に、ゲート絶縁膜140、酸化物半導体層150、第1金属膜170p、第2金属膜170q、及び第3金属膜170rを積層する。

【0080】

次に、第3金属膜170rの上に感光膜を形成した後にパターニングして、第1感光膜パターン50aを形成する。図3乃至図9で説明した実施形態の第1感光膜パターン50とは異なって、チャネル領域に対応する部分に位置する第3金属膜170rの上部面を露出するオープン部(opening)を有するように、第1感光膜パターン51aを形成する。

【0081】

図11を参照すれば、第1感光膜パターン50aをマスクとして第1金属膜170p、第2金属膜170q、及び第3金属膜170rをエッチングする。ここで、オープン部によって露出した部分の第3金属膜170r、第2金属膜170q、及び第1金属膜170pも順次にエッチングされて、チャネル領域が形成される位置の酸化物半導体層150が露出される。

【0082】

この時、第1金属膜170p、第2金属膜170q、及び第3金属膜170rがチャネル領域CHを介して分離されて、データ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rを含むデータ配線層が形成される。データ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rそれぞれは、酸化物半導体層150の上に位置するバリア層171p、173p、175r、バリア層171p、173p、175pの上に位置する主配線層171q、173q、175q、及び主配線層171q、173q、175qの上に位置するキャッピング層171r、173r、175rを有する。

【0083】

図12を参照すれば、第1感光膜パターン50aを除去して、第2感光膜パターン50bを形成する。第2感光膜パターン50bは、データ線171p、171q、171r、ソース電極173p、173q、173r、ドレイン電極175p、175q、175r、及びチャネル領域に対応する露出した酸化物半導体層150を覆うように形成される。

【0084】

図13を参照すれば、第2感光膜パターン50bをマスクとして酸化物半導体層150をエッチングし、チャネル領域を除いてデータ線171p、171q、171r、ソース電極173p、173q、173r、及びドレイン電極175p、175q、175rと実質的に同一の平面パターンを有する酸化物半導体154を形成する。チャネル領域に対応する酸化物半導体層150は、第2感光膜パターン50bによって覆われているため保護される。

【0085】

そして、第2感光膜パターン50bを除去する。

【0086】

この後の工程は、図9で説明した実施形態と同様に、コンタクトホールを有する保護膜を形成した後、保護膜のコンタクトホールによってドレイン電極と電気的に接続されるように保護膜の上に画素電極を形成する。

【0087】

本実施形態によれば、データ配線層と酸化物半導体層のエッチングを分離して行うことによって、三重膜のデータ配線層を形成する時に発生するスキュー(skew)のために酸化物半導体層の側壁がデータ配線層の側壁と一致せずに突出することを最小化することができる。

【0088】

以上、本発明の好ましい実施形態について詳細に説明したが、本発明の権利範囲はこれに限定されず、次の請求範囲で定義している本発明の基本概念を利用した当業者の種々の変形及び改良形態も本発明の権利範囲に属するものである。

【符号の説明】

【0089】

121 ゲート線

124 ゲート電極

154 酸化物半導体

171 データ線

173 ソース電極

175 ドレイン電極

【特許請求の範囲】

【請求項1】

基板の上に配置するゲート配線層、

前記ゲート配線層の上に配置する酸化物半導体層、及び

前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、

前記データ配線層は、銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む薄膜トランジスタ表示板。

【請求項2】

前記キャッピング層は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つを含む銅合金、または銅、アルミニウム、マグネシウムの合金である、請求項1に記載の薄膜トランジスタ表示板。

【請求項3】

前記キャッピング層は銅マンガン合金を含む、請求項2に記載の薄膜トランジスタ表示板。

【請求項4】

前記酸化物半導体層は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含む、請求項3に記載の薄膜トランジスタ表示板。

【請求項5】

前記データ配線層は、前記主配線層の下に配置するバリア層をさらに含む、請求項1に記載の薄膜トランジスタ表示板。

【請求項6】

前記バリア層は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成された物質を含む、請求項5に記載の薄膜トランジスタ表示板。

【請求項7】

前記バリア層の中で銅と合金を形成する物質は10at%以上の含有量を有する、請求項6に記載の薄膜トランジスタ表示板。

【請求項8】

前記データ配線層は、前記ゲート線と交差して、ソース電極を含むデータ線、及び前記ソース電極と対向するドレイン電極を含む、請求項3に記載の薄膜トランジスタ表示板。

【請求項9】

前記データ線及び前記ドレイン電極を覆って、前記ドレイン電極の一部を露出させるコンタクトホールを有する保護膜、及び

前記コンタクトホールによって前記ドレイン電極と電気的に接続されている画素電極をさらに含む、請求項8に記載の薄膜トランジスタ表示板。

【請求項10】

前記保護膜は酸化ケイ素を含む、請求項9に記載の薄膜トランジスタ表示板。

【請求項11】

基板の上にゲート線を形成する段階、

前記ゲート線を覆うゲート絶縁膜を形成する段階、

前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、

前記第2金属膜の上に、第1領域と、前記第1領域より厚さが厚い第2領域とを有する第1感光膜パターンを形成する段階、

前記第1感光膜パターンをマスクとして前記第2金属膜と前記第1金属膜を共にエッチングする段階、

前記第1感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階、

前記第1感光膜パターンをエッチバックして第2感光膜パターンを形成する段階、及び

前記第2感光膜パターンをマスクとして前記第1金属膜及び前記2金属膜を同時にウェットエッチングし、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階を含む薄膜トランジスタ表示板の製造方法。

【請求項12】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成する、請求項11に記載の薄膜トランジスタ表示板の製造方法。

【請求項13】

前記第1金属膜は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成する、請求項12に記載の薄膜トランジスタ表示板の製造方法。

【請求項14】

前記第1金属膜の中で銅と合金を形成する物質は25at%以上の含有量を有するように形成する、請求項13に記載の薄膜トランジスタ表示板の製造方法。

【請求項15】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含む、請求項11に記載の薄膜トランジスタ表示板の製造方法。

【請求項16】

前記第3金属膜は銅合金で形成する、請求項15に記載の薄膜トランジスタ表示板の製造方法。

【請求項17】

前記第3金属膜は、前記第2感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をウェットエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含む、請求項16に記載の薄膜トランジスタ表示板の製造方法。

【請求項18】

配線部とチャネル部を含む基板の上にゲート線を形成する段階、

前記ゲート線を覆うゲート絶縁膜を形成する段階、

前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、

前記第2金属膜の上に前記チャネル部に対応する位置にオープン部を有する第1感光膜パターンを形成する段階、

前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜を共にエッチングして、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階、

前記第1感光膜パターンを除去する段階、

前記データ配線層を覆う第2感光膜パターンを形成する段階、及び

前記第2感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階を含む薄膜トランジスタ表示板の製造方法。

【請求項19】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成する、請求項18に記載の薄膜トランジスタ表示板の製造方法。

【請求項20】

前記第1金属膜は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成する、請求項19に記載の薄膜トランジスタ表示板の製造方法。

【請求項21】

前記第1金属膜の中で銅と合金を形成する物質は25a%以上の含有量を有するように形成する、請求項20に記載の薄膜トランジスタ表示板の製造方法。

【請求項22】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含む、請求項21に記載の薄膜トランジスタ表示板の製造方法。

【請求項23】

前記第3金属膜は銅合金で形成する、請求項22に記載の薄膜トランジスタ表示板の製造方法。

【請求項24】

前記第3金属膜は、前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含む、請求項23に記載の薄膜トランジスタ表示板の製造方法。

【請求項1】

基板の上に配置するゲート配線層、

前記ゲート配線層の上に配置する酸化物半導体層、及び

前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、

前記データ配線層は、銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む薄膜トランジスタ表示板。

【請求項2】

前記キャッピング層は、バナジウム(V)、チタニウム(Ti)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つを含む銅合金、または銅、アルミニウム、マグネシウムの合金である、請求項1に記載の薄膜トランジスタ表示板。

【請求項3】

前記キャッピング層は銅マンガン合金を含む、請求項2に記載の薄膜トランジスタ表示板。

【請求項4】

前記酸化物半導体層は、亜鉛(Zn)、インジウム(In)、錫(Sn)、ガリウム(Ga)、及びハフニウム(Hf)のうちの少なくとも一つを含む、請求項3に記載の薄膜トランジスタ表示板。

【請求項5】

前記データ配線層は、前記主配線層の下に配置するバリア層をさらに含む、請求項1に記載の薄膜トランジスタ表示板。

【請求項6】

前記バリア層は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)のうちの少なくとも一つと銅の合金で形成された物質を含む、請求項5に記載の薄膜トランジスタ表示板。

【請求項7】

前記バリア層の中で銅と合金を形成する物質は10at%以上の含有量を有する、請求項6に記載の薄膜トランジスタ表示板。

【請求項8】

前記データ配線層は、前記ゲート線と交差して、ソース電極を含むデータ線、及び前記ソース電極と対向するドレイン電極を含む、請求項3に記載の薄膜トランジスタ表示板。

【請求項9】

前記データ線及び前記ドレイン電極を覆って、前記ドレイン電極の一部を露出させるコンタクトホールを有する保護膜、及び

前記コンタクトホールによって前記ドレイン電極と電気的に接続されている画素電極をさらに含む、請求項8に記載の薄膜トランジスタ表示板。

【請求項10】

前記保護膜は酸化ケイ素を含む、請求項9に記載の薄膜トランジスタ表示板。

【請求項11】

基板の上にゲート線を形成する段階、

前記ゲート線を覆うゲート絶縁膜を形成する段階、

前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、

前記第2金属膜の上に、第1領域と、前記第1領域より厚さが厚い第2領域とを有する第1感光膜パターンを形成する段階、

前記第1感光膜パターンをマスクとして前記第2金属膜と前記第1金属膜を共にエッチングする段階、

前記第1感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階、

前記第1感光膜パターンをエッチバックして第2感光膜パターンを形成する段階、及び

前記第2感光膜パターンをマスクとして前記第1金属膜及び前記2金属膜を同時にウェットエッチングし、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階を含む薄膜トランジスタ表示板の製造方法。

【請求項12】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成する、請求項11に記載の薄膜トランジスタ表示板の製造方法。

【請求項13】

前記第1金属膜は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成する、請求項12に記載の薄膜トランジスタ表示板の製造方法。

【請求項14】

前記第1金属膜の中で銅と合金を形成する物質は25at%以上の含有量を有するように形成する、請求項13に記載の薄膜トランジスタ表示板の製造方法。

【請求項15】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含む、請求項11に記載の薄膜トランジスタ表示板の製造方法。

【請求項16】

前記第3金属膜は銅合金で形成する、請求項15に記載の薄膜トランジスタ表示板の製造方法。

【請求項17】

前記第3金属膜は、前記第2感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をウェットエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含む、請求項16に記載の薄膜トランジスタ表示板の製造方法。

【請求項18】

配線部とチャネル部を含む基板の上にゲート線を形成する段階、

前記ゲート線を覆うゲート絶縁膜を形成する段階、

前記ゲート絶縁膜の上に酸化物半導体層、第1金属膜、及び第2金属膜を連続的に積層する段階、

前記第2金属膜の上に前記チャネル部に対応する位置にオープン部を有する第1感光膜パターンを形成する段階、

前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜を共にエッチングして、バリア層及び前記バリア層の上に位置する主配線層を含むデータ配線層を形成する段階、

前記第1感光膜パターンを除去する段階、

前記データ配線層を覆う第2感光膜パターンを形成する段階、及び

前記第2感光膜パターンをマスクとして前記酸化物半導体層をエッチングする段階を含む薄膜トランジスタ表示板の製造方法。

【請求項19】

前記第1金属膜は銅合金で形成し、前記第2金属膜は銅で形成する、請求項18に記載の薄膜トランジスタ表示板の製造方法。

【請求項20】

前記第1金属膜は、バナジウム(V)、ジルコニウム(Zr)、タンタル(Ta)、マンガン(Mn)、マグネシウム(Mg)、クロム(Cr)、モリブデン(Mo)、コバルト(Co)、ニオビウム(Nb)、及びニッケル(Ni)の中から選択した少なくとも一つと銅の合金で形成する、請求項19に記載の薄膜トランジスタ表示板の製造方法。

【請求項21】

前記第1金属膜の中で銅と合金を形成する物質は25a%以上の含有量を有するように形成する、請求項20に記載の薄膜トランジスタ表示板の製造方法。

【請求項22】

前記ゲート絶縁膜の上に前記第2金属膜を積層した後に第3金属膜を積層する段階をさらに含む、請求項21に記載の薄膜トランジスタ表示板の製造方法。

【請求項23】

前記第3金属膜は銅合金で形成する、請求項22に記載の薄膜トランジスタ表示板の製造方法。

【請求項24】

前記第3金属膜は、前記第1感光膜パターンをマスクとして前記第1金属膜及び前記第2金属膜をエッチングする時に共にエッチングされて、前記主配線層の上にキャッピング層を形成する段階をさらに含む、請求項23に記載の薄膜トランジスタ表示板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−33927(P2013−33927A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2012−105272(P2012−105272)

【出願日】平成24年5月2日(2012.5.2)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成24年5月2日(2012.5.2)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]