薄膜トランジスタ

【課題】電界効果移動度が高く、オン電流が大きい薄膜トランジスタを提供する。

【解決手段】ゲート電極と、ゲート電極を覆って設けられたゲート絶縁層と、ゲート絶縁層上に、ゲート電極と重畳して設けられた半導体層と、半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層上に設けられた配線層と、を有し、ソース領域及びドレイン領域の幅は、半導体層の幅よりも小さく、半導体層の幅は、少なくともソース領域とドレイン領域の間において拡大された薄膜トランジスタとする。

【解決手段】ゲート電極と、ゲート電極を覆って設けられたゲート絶縁層と、ゲート絶縁層上に、ゲート電極と重畳して設けられた半導体層と、半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層上に設けられた配線層と、を有し、ソース領域及びドレイン領域の幅は、半導体層の幅よりも小さく、半導体層の幅は、少なくともソース領域とドレイン領域の間において拡大された薄膜トランジスタとする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタに関する。特に、薄膜トランジスタが設けられた表示装置に関する。

【背景技術】

【0002】

近年、絶縁性表面を有する基板(例えば、ガラス基板)上の半導体薄膜(厚さ数nm〜数百nm程度)によって構成された薄膜トランジスタ(以下、TFTという。)が注目されている。TFTは、IC(Integrated Circuit)及び電気光学装置のような電子デバイスに広く応用されている。特に、液晶表示装置などに代表される、画像表示装置のスイッチング素子として開発が急がれている。液晶表示装置などの画像表示装置では、スイッチング素子として、主に非晶質半導体膜または多結晶半導体膜を用いたTFTが用いられている。

【0003】

非晶質半導体膜を用いたTFTは、移動度が低い。つまり、電流駆動能力が低い。そのため、非晶質半導体膜を用いたTFTにより保護回路を形成するに際して、十分な静電破壊対策をするにはサイズの大きいトランジスタを形成する必要があり、狭額縁化を阻害してしまうという問題がある。更には、サイズの大きいトランジスタを形成することでゲート電極に電気的に接続される走査線と、ソース電極またはドレイン電極に電気的に接続される信号線との間の寄生容量が増大してしまい、消費電力の増大を招くという問題もある。

【0004】

一方で、多結晶半導体膜を用いたTFTは、非晶質半導体膜を用いたTFTに比べて移動度が2桁以上高く、液晶表示装置の画素部とその周辺の駆動回路を同一基板上に形成できる。しかしながら、多結晶半導体膜を用いたTFTは、非晶質半導体膜を用いたTFTに比べて、半導体膜の結晶化及び不純物元素の導入(ドーピング)などにより工程が複雑化する。そのため、歩留まりが低く、コストが高いという問題がある。多結晶半導体膜の形成方法としては、例えば、パルス発振のエキシマレーザビームの形状を光学系により線状に加工し、非晶質半導体膜に対して線状のレーザビームを走査させつつ照射して結晶化する技術が広く知られている。

【0005】

ところで、画像表示装置のスイッチング素子としては、非晶質半導体膜を用いたTFTまたは多結晶半導体膜を用いたTFTの他に、微結晶半導体膜を用いたTFTが知られている(例えば、特許文献1を参照)。しかし、微結晶半導体膜を用いたTFTでは、十分なオン電流を得ることが困難である。そのため、非晶質半導体膜または微結晶半導体膜を用いたTFTにおいて、十分なオン電流を得るための様々な開発が行われてきた。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−44134号公報

【特許文献2】米国特許4,409,134号

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一態様は、従来よりもオン電流が大きく、電界効果移動度が大きいTFTを提供することを課題とする。

【課題を解決するための手段】

【0008】

本発明の一態様は、ソースとドレインの間における半導体層のアイランド幅を拡大したTFTである。

【発明の効果】

【0009】

TFTのオン電流を十分に大きくすることができる。

【0010】

TFTの電界効果移動度を十分に大きくすることができる。

【図面の簡単な説明】

【0011】

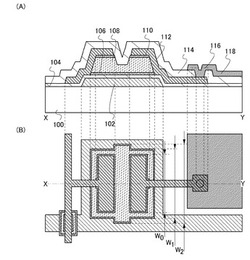

【図1】TFT及び表示装置を説明する図。

【図2】TFT及び表示装置を説明する図。

【図3】TFT及び表示装置を説明する図。

【図4】TFT及び表示装置を説明する図。

【図5】TFT及び表示装置を説明する図。

【図6】TFT及び表示装置を説明する図。

【図7】TFT及び表示装置を説明する図。

【図8】計算結果を説明する図。

【図9】計算結果を説明する図。

【図10】計算結果を説明する図。

【図11】TFT及び表示装置の作製方法を説明する図。

【図12】TFT及び表示装置の作製方法を説明する図。

【図13】TFT及び表示装置の作製方法を説明する図。

【図14】TFT及び表示装置の作製方法を説明する図。

【図15】TFT及び表示装置を説明する図。

【図16】表示装置を説明する図。

【図17】表示装置を説明する図。

【図18】表示装置を説明する図。

【図19】電子機器を説明する図。

【図20】電子機器を説明する図。

【図21】電子機器を説明する図。

【発明を実施するための形態】

【0012】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、説明中に図面を参照するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0013】

(実施の形態1)

本実施の形態では、本発明の一態様であるTFTについて、図面を参照して説明する。

【0014】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されていることを特徴とする薄膜トランジスタである。ここで、ゲート電極は第1の配線層により形成され、ソース電極及びドレイン電極は第2の配線層により形成され、以下同様である。

【0015】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられた配線層と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大されていることを特徴とする薄膜トランジスタである。

【0016】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短いことを特徴とする薄膜トランジスタである。

【0017】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大され、前記ソース領域と前記ドレイン領域上にはソース電極及びドレイン電極が設けられ、該ソース電極及びドレイン電極の一方には選択的に形成された画素電極層が接続されていることを特徴とする表示装置である。

【0018】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大され、前記ソース領域と前記ドレイン領域上にはソース電極及びドレイン電極が設けられ、ソース電極及びドレイン電極の一方には選択的に形成された画素電極層が接続されていることを特徴とする表示装置である。

【0019】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短く、前記ソース領域と前記ドレイン領域上にはソース電極及びドレイン電極が設けられ、該ソース電極及びドレイン電極の一方には選択的に形成された画素電極層が接続されていることを特徴とする表示装置である。

【0020】

図1は、本実施の形態のTFTの一例を示す。図1(A)には断面図を示し、図1(B)には上面図を示す。なお、図1(A)は、図1(B)に示すX−Yにおける断面図である。

【0021】

図1に示すTFTは、基板100上の第1の配線層102を覆ってゲート絶縁層104が設けられ、ゲート絶縁層104上には第1の半導体層106が設けられ、第1の半導体層106上には第2の半導体層108が設けられ、第2の半導体層108上には不純物半導体層110を介して第2の配線層112が設けられている(図1(A)を参照)。ここで、不純物半導体層110は、第2の半導体層108と第2の配線層112をオーミック接触させるために設けられているものである。第2の配線層112は、ソース電極と、ドレイン電極と、ソース配線と、を構成する。なお、当該TFTは保護層114によって覆われていることが好ましい。当該TFTを表示装置の画素トランジスタとして用いる場合には、図1に示すように保護層114に開口部116を設け、開口部116を介して第2の配線層112に接続されるように画素電極層118を設ければよい。

【0022】

基板100は、基板100上に形成される薄膜(結晶性シリコンなど)の形成工程に耐えうる程度の耐熱性及び耐薬品性などを有していればよく、特定の材料からなる基板に限定されるものではない。具体的には、ガラス基板、石英基板、ステンレス基板及びシリコン基板が挙げられる。なお、図1に示すように、TFTを表示装置に適用する場合には、基板100には透光性を有する基板を用いればよく、例えばガラス基板または石英基板を用いればよい。基板100がマザーガラスの場合には、第1世代(例えば、320mm×400mm)〜第10世代(例えば、2950mm×3400mm)のものを用いればよいがこれに限定されるものではない。

【0023】

第1の配線層102は、導電性材料により形成することができ、単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、Mo、Ti、Cr、Ta、W、Al、Cu、Nd若しくはScなどの金属材料またはこれらを主成分とする合金材料により形成することができる。なお、第1の配線層102は、少なくともゲート電極及びゲート配線を構成する。

【0024】

ゲート絶縁層104は、絶縁性材料により形成することができ、単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、酸化シリコン、窒化シリコン、酸化窒化シリコンまたは窒化酸化シリコンによって形成することができる。第1の半導体層106が結晶性半導体層である場合には、少なくとも第1の半導体層106に接するゲート絶縁層104は、酸化シリコン層とすることが好ましい。ゲート絶縁層104として酸化シリコン層を形成する場合には、形成ガスに珪酸エチル(TEOS:化学式Si(OC2H5)4)を用いた酸化シリコン層により形成することが好ましい。

【0025】

なお、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合に、組成範囲として酸素が50〜70原子%、窒素が0.5〜15原子%、シリコンが25〜35原子%、水素が0.1〜10原子%の範囲で含まれるものをいう。

【0026】

なお、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、組成範囲として酸素が5〜30原子%、窒素が20〜55原子%、シリコンが25〜35原子%、水素が10〜30原子%の範囲で含まれるものをいう。ただし、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0027】

第1の半導体層106は、結晶性半導体により形成するとよい。結晶性半導体には、多結晶半導体または微結晶半導体などを含むが、結晶化工程が不要な微結晶半導体により形成することが好ましい。

【0028】

ここで、微結晶半導体とは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体をいう。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な半導体であり、結晶粒径が2nm以上200nm以下、好ましくは10nm以上80nm以下、より好ましくは、20nm以上50nm以下の柱状結晶または針状結晶が基板表面に対して法線方向に成長している半導体である。このため、柱状結晶または針状結晶の界面には、結晶粒界が形成される場合もある。

【0029】

微結晶半導体の一である微結晶シリコンでは、そのラマンスペクトルのピークが単結晶シリコンを示す520cm−1よりも低波数側にシフトしている。すなわち、単結晶シリコンを示す520cm−1とアモルファスシリコンを示す480cm−1の間に微結晶シリコンのラマンスペクトルのピークがある。そして、未結合手(ダングリングボンド)を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、He、Ar、Kr、またはNeなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体が得られる。このような微結晶半導体に関する記述は、例えば、米国特許4,409,134号で開示されている。

【0030】

そして、第1の半導体層106に含まれる酸素及び窒素の濃度(二次イオン質量分析法による測定値)を、1×1018cm−3未満とすると、第1の半導体層106の結晶性を高めることができる。

【0031】

第2の半導体層108は、第1の半導体層106に接して設けられており、第1の半導体層106よりもキャリア移動度が低い材料により設けるとよい。第2の半導体層108によりオフ電流を低減することができる。

【0032】

例えば、第1の半導体層106として結晶性半導体層を形成し、第2の半導体層108として、非晶質半導体と微小半導体結晶粒を有する半導体層を形成するとよい。TFTがオンすると第1の半導体層106に流れる電流が支配的であり、TFTがオフすると第2の半導体層108に流れる電流が支配的である。第2の半導体層108を「非晶質半導体と微小半導体結晶粒を有する半導体層」とすることで、オン電流の低下を防ぐこともできる。そのため、第1の半導体層106を結晶性半導体層とし、第2の半導体層108を「非晶質半導体と微小半導体結晶粒を有する半導体層」とすることで、オンオフ比が高いTFTを得ることができる。

【0033】

上記説明した第2の半導体層108の好ましい形態の一である「非晶質半導体と微小半導体結晶粒を有する半導体層」は、非晶質半導体と微小半導体結晶粒を有し、従来の非晶質半導体と比較して、CPM(Constant photocurrent method)やフォトルミネッセンス分光測定で測定されるUrbach端のエネルギーが小さく、欠陥吸収スペクトル量が少ない半導体層である。すなわち、従来の非晶質半導体と比較して欠陥が少なく、価電子帯のバンド端(移動度端)における準位のテイル(裾)の傾きが急峻である秩序性の高い半導体層である。

【0034】

ただし、第2の半導体層108は、上記説明に限定されず、非晶質半導体により形成してもよい。第2の半導体層108は、少なくとも第1の半導体層106よりもキャリア移動度の低い材料により設ければよく、非晶質半導体、またはハロゲンを有する非晶質半導体、または窒素を有する非晶質半導体により形成してもよい。非晶質半導体としては、アモルファスシリコンが挙げられる。

【0035】

第1の半導体層106と第2の半導体層108の界面領域は、好ましくは、微結晶半導体領域、及び当該微結晶半導体領域の間に充填される非晶質半導体を有する。具体的には、第1の半導体層106から凸状に伸びた微結晶半導体領域と、第2の半導体層108と同様の半導体と、で形成される。このとき、第1の半導体層106と第2の半導体層108の界面領域には錐形状の微結晶半導体領域を有するため、第2の配線層112に電圧を印加したときの縦方向(厚さ方向)の抵抗(すなわち、第2の半導体層108と、不純物半導体層110により構成されるソース領域またはドレイン領域と、の間の抵抗)を低くすることができ、TFTのオン電流を高めることが可能である。なお、ここで界面領域とは、厚さ方向における界面の近傍の領域をいう。

【0036】

第1の半導体層106と第2の半導体層108の界面領域は、ゲート絶縁層104から第2の半導体層108に向かって先端が狭くなる凸状の結晶粒により大部分が構成されているとよい。または、ゲート絶縁層104から第2の半導体層108に向かって幅が広がる凸状の結晶粒により大部分が構成されているとよい。

【0037】

第1の半導体層106と第2の半導体層108の界面領域において、微結晶半導体領域が、ゲート絶縁層104から第2の半導体層108に向けて、先端が狭まる凸状の結晶粒の場合は、第1の半導体層106側のほうが、第2の半導体層108側と比較して、微結晶半導体領域の割合が高い。微結晶半導体領域は、第1の半導体層106の表面から厚さ方向に成長するが、原料ガスにおけるシランに対する水素の流量が小さく、または窒素を含む原料ガスの濃度が高いと、微結晶半導体領域における結晶成長が抑制され、結晶粒は錐状になり、堆積されて形成される半導体は、大部分が非晶質となる。

【0038】

第2の半導体層108は、電界を緩和してオフ電流を低減する層として機能する。ここでは、第2の半導体層108を、従来の非晶質半導体と比較して欠陥が少なく、価電子帯のバンド端(移動度端)における準位のテール(裾)の傾きが急峻である秩序性の高い半導体膜を加工して形成する場合について説明する。このような半導体膜は、結晶性半導体膜の形成ガス中に、好ましくは窒素を含むガスを混合させ、結晶性半導体膜の成膜条件よりも堆積性ガス(例えば、シランガス)に対する水素の流量比を小さくし、プラズマCVD法を用いることで、結晶成長が抑制されて形成される。なお、第2の半導体層108には、好ましくは窒素が1×1020cm−3乃至1×1021cm−3で含まれる。ここで、窒素は、NH基またはNH2基の状態で存在することが好ましい。半導体原子のダングリングボンドが窒素原子若しくはNH基で架橋され、またはNH2基で終端されてキャリアが流れやすくなるためである。特に、隣り合う二つのシリコン原子のダングリングボンドをNH基により架橋することでキャリア移動度が向上し、オン電流が増大する。なお、NH2基は主に半導体内部のダングリングボンドの終端に寄与する。この結果、結晶粒界や欠陥に起因するトラップ準位密度を小さくし、ポテンシャル障壁を消失させ若しくは低減させることができる。そのため、キャリアが散乱、トラップ、若しくは再結合されにくくなることで、キャリア移動度が向上し、TFTは十分な電界効果移動度とオン電流を得ることができる。

【0039】

更には、ダングリングボンドが、窒素原子若しくはNH基によって架橋され、またはNH2基によって終端されることで、半導体のバンドギャップ中央付近に形成されるトラップ準位が消失し若しくはその数が少なくなる。そのため、このトラップ準位に起因する間接トンネル電流(例えば、Shockley Read Hall電流、Trap Assisted Tunneling電流、Poole Frenkel電流)を抑えることができ、オフ電流をも低減することができる。

【0040】

上記説明した第2の半導体層108を設けることで、オン/オフ比が高いTFTを得ることができる。なお、このとき、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよく、結晶性半導体膜を形成する時よりも希釈ガスの流量比を小さくするとよい。

【0041】

更には、上記の界面領域の酸素濃度を低減することにより、微結晶半導体領域と非晶質半導体領域との界面や、結晶粒同士の界面における欠陥、キャリアの移動を阻害する結合を低減することができる。

【0042】

または、上記説明に限定されず、第2の半導体層108を有さない構成としてもよい。この場合には、上記した界面領域が第1の半導体層106と不純物半導体層110の間に設けられるとよい。この界面領域には、微結晶半導体領域と、当該微結晶半導体領域の間に充填された非晶質半導体領域を有する。微結晶半導体領域は第1の半導体層106から伸びた微結晶半導体により形成される。このとき、非晶質半導体領域に対する微結晶半導体領域の割合は小さいことが好ましい。さらには、対となる不純物半導体層110の間(ソース領域とドレイン領域の間)、すなわちキャリアが流れる領域においては、微結晶半導体領域の割合が小さいことが好ましい。TFTのオフ電流を低減することができるためである。そして、上記の界面領域では第2の配線層112に電圧を印加したときの縦方向(厚さ方向)の抵抗が低いため、TFTのオン電流を大きくすることが可能である。

【0043】

不純物半導体層110は、第1の半導体層106または第2の半導体層108と、第2の配線層112と、をオーミック接触させることを目的として設ける層であり、形成ガスに一導電型を付与する不純物元素を含む気体を加えて形成することができる。導電型がn型のTFTを形成する場合には、例えば不純物元素としてリンを添加すればよく、水素化シリコンにフォスフィンなどのn型の導電型を付与する不純物元素を含む気体を加えればよい。導電型がp型のTFTを形成する場合には、例えば不純物元素としてボロンを添加すればよく、水素化シリコンにジボランなどのp型の導電型を付与する不純物元素を含む気体を加えればよい。なお、不純物半導体層110の結晶性は特に限定されず、結晶性半導体であってもよいし、非晶質半導体であってもよいが、結晶性半導体により設けることが好ましい。不純物半導体層110を結晶性半導体層により設けることで、オン電流が大きくなるからである。

【0044】

第2の配線層112は、導電性材料により単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、第1の配線層102と同様の材料により形成することができる。

【0045】

保護層114は、ゲート絶縁層104と同様に形成することができるが、窒化シリコンにより形成することが特に好ましい。特に、大気中に浮遊する有機物や金属、水蒸気などの汚染源となりうる物質の侵入を防ぐことができるよう、緻密な窒化シリコン層とすることが好ましい。

【0046】

画素電極層118は、透光性を有する導電性高分子(導電性ポリマーともいう。)を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆるπ電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、またはこれらの2種以上の共重合体などがあげられる。

【0047】

画素電極層118は、例えば、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOという。)、インジウム亜鉛酸化物または酸化シリコンを添加したインジウム錫酸化物などを用いて形成してもよい。

【0048】

なお、図1に示すTFTは、第1の配線層102と接続される走査線と第2の配線層112と接続される信号線が交差する部分において、走査線と信号線の間に第1の半導体層106、第2の半導体層108(以下、第1の半導体層106または第2の半導体層108を単に半導体層ともいう)、及び不純物半導体層110が設けられているため、走査線と信号線の間に生じる寄生容量を低減することができる。ここで、少なくとも走査線と信号線の間に設けられる第1の半導体層106は、走査線と信号線の間に生じる寄生容量をさらに低減させるため、重畳する走査線からはみ出すように設けられることが好ましい。

【0049】

次に、図1乃至図6に示すTFTを比較する。図1に示すTFTにおいて、ソース領域及びドレイン領域の幅はソースドレイン幅W0と表し、半導体層の内側の幅は最小アイランド幅W1と表し、半導体層の外側の幅は最大アイランド幅W2と表す(W0<W1<W2)。このようにソース領域とドレイン領域の間においてチャネル形成領域を拡大することで、TFTの電界効果移動度を向上させ、オン電流を大きくすることができる。

【0050】

図1に示すTFTの半導体層はソース領域とドレイン領域の間においてのみチャネル形成領域を拡大したものであるが、図2に示すTFTは、半導体層が拡大された領域をチャネル長方向に拡げたものである。この重なった部分をオフセット領域と呼び、オフセット領域のチャネル長方向の長さをL0と表す。すなわち、図2に示すTFTは、図1に示すTFTに対して、半導体層の拡大領域をチャネル長方向に2L0だけ拡げたものである。

【0051】

図1及び図2に示すTFTは、図5に示す最小アイランド幅W1のTFTよりも電界効果移動度が高く、オン電流が大きい。

【0052】

なお、図1、図2及び図5に示すTFTのオン電流について計算を行うと、図2に示すTFTのオン電流が最も大きく、図5に示すTFTのオン電流が最も小さくなる。

【0053】

ここで、半導体層の拡大領域をチャネル長方向に拡げたTFTにおける電流密度の分布について計算を行った。ここで、ゲート電圧は15Vとし、ドレイン電圧は10Vとした。半導体層のサイズについては、チャネル長方向は50μmとし、チャネル長に垂直な方向はソースドレイン幅W0=10μm、最小アイランド幅W1=20μm、最大アイランド幅W2=30μmとしてオフセット領域のチャネル長方向の長さL0の変化に対する電流密度の分布の変化を調べた。なお、ここで、簡単のために、第1の半導体層106と第2の半導体層108は、単一の非晶質半導体層により設けられているものと仮定して計算を行った。

【0054】

なお、ゲート電圧とは、ソース電極の電位とゲート電極の電位との電位差をいう。ドレイン電圧とは、ソース電極の電位とドレイン電極の電位との電位差をいう。ここで、ゲート電圧及びドレイン電圧は、ソース電極の電位を基準とする。

【0055】

図8は、オフセット領域のチャネル長方向の長さL0を概ね2μmとしたときの電流密度の分布を表す。図9は、オフセット領域のチャネル長方向の長さL0を概ね10μmとしたときの電流密度の分布を示す。図10は、オフセット領域のチャネル長方向の長さL0を概ね16μmとしたときの電流密度の分布を示す。図8ではオフセット領域のチャネル長方向の長さL0の長さが短く、電流密度が高い領域が半導体層の外縁の近傍まで拡がっているため、電流が回り込むための十分な領域を確保することができていない。一方で、図10では、半導体層の外縁の近傍に電流が流れないため、この領域を十分に活用できていない。従って、図9に示すTFTが最適であるといえる。すなわち、半導体層のチャネル長方向の半分程度を拡大領域とすることが好ましい。

【0056】

なお、図7に示すように、上面図におけるゲート電極の形状を半導体層の形状にあわせて加工することで、開口率を向上させることが可能である。

【0057】

なお、図1、図2及び図5に示すTFTでは、第2の半導体層の一部(側面)と配線層が接するため、この接する部分がオフ電流を上昇させる一因となりうる。従って、配線層の少なくとも第2の半導体層と接する部分は、仕事関数の小さい材料により形成することが好ましく、特にイットリア、チタン、または窒化チタンにより形成することが好ましい。

【0058】

なお、上記で参照した図1、図2及び図5に示すTFTは、半導体層の全面がゲート電極と重畳して遮光されているため、光電流による影響が小さい。ただし、これに限定されず、図3、図4及び図6に示すように、必ずしも半導体層の全面がゲート電極と重畳していなくてもよい。

【0059】

図3に示すTFTは、基板200上に第1の配線層202と、第1の半導体層206と、第2の半導体層208と、第1の配線層202と第1の半導体層206の間に接して設けられたゲート絶縁層204と、第2の半導体層208に接して設けられた不純物半導体層210と、不純物半導体層210及び第2の半導体層208に一部が接して設けられた第2の配線層212と、を有するものであって、第1の配線層202により構成されるゲート電極は半導体層の一部と重畳している。そして、図1と同様に、当該TFTは保護層214によって覆われ、保護層214に設けた開口部216を介して第2の配線層212に接続されるように画素電極層218を設けた形態を示す。第2の半導体層208は、第1の半導体層206に接して設けられており、第1の半導体層206よりもキャリア移動度が低い材料により設けるとよい。

【0060】

なお、基板200は、図1における基板100に相当する。第1の配線層202は、図1における第1の配線層102に相当する。ゲート絶縁層204は、図1におけるゲート絶縁層104に相当する。第1の半導体層206は、図1における第1の半導体層106に相当する。第2の半導体層208は、図1における第2の半導体層108に相当する。不純物半導体層210は、図1における不純物半導体層110に相当する。第2の配線層212は、図1における第2の配線層112に相当する。保護層214は、図1における保護層114に相当する。開口部216は、図1における開口部116に相当する。画素電極層218は、図1における画素電極層118に相当する。

【0061】

図3に示すTFTの半導体層はソース領域とドレイン領域の間においてのみチャネル形成領域を拡大したものであるが、図4に示すTFTは、半導体層が拡大された領域をチャネル長方向に拡げたものであり、半導体層が拡大された領域の一部がソース領域及びドレイン領域と重なっている。この重なった部分をオフセット領域と呼び、図2と同様にチャネル長方向にソース領域及びドレイン領域とそれぞれ長さLoだけ重なっている。すなわち、図4に示すTFTは、図3に示すTFTに対して、半導体層の拡大領域をチャネル長方向に2Loだけ拡げたものである。

【0062】

図3及び図4に示すTFTは、図6に示す最小アイランド幅W1のTFTよりも電界効果移動度が高く、オン電流が大きい。

【0063】

なお、図3、図4及び図6に示すTFTを比較すると、図4に示すTFTのオン電流が最も大きく、図6に示すTFTのオン電流が最も小さくなる。

【0064】

ここで、図1に示すTFTの作製方法について図面を参照して説明する。

【0065】

まず、基板100上に第1の配線層102を形成する。基板100は、ここではガラス基板を用いる(図11(A)を参照)。

【0066】

第1の配線層102は、スパッタリング法または真空蒸着法により基板100上に導電層を形成し、該導電層上にフォトリソグラフィ法またはインクジェット法などによりマスクを形成し、該マスクを用いて導電層をエッチングすることで形成することができる(図11(A)を参照)。または、第1の配線層102は、Ag、Au若しくはCuなどの導電性粒子を含むナノペーストを、インクジェット法により基板上に吐出して焼成することで形成することもできる。なお、第1の配線層102と基板100との密着性を向上させ、第1の配線層102を構成する材料の拡散を防ぐバリアメタルとして、上記の金属材料の窒化物層を、基板100と、第1の配線層102との間に設けてもよい。ここでは、基板100上に導電層を形成し、フォトマスクを用いて形成したレジストマスクによりエッチングすることで第1の配線層102を形成する。

【0067】

なお、第1の配線層102上には、後の工程で半導体層及びソース配線(信号線)を形成するため、段差の箇所における配線切れ防止のため側面がテーパーを有するように加工することが好ましい。この工程でゲート配線(走査線)も同時に形成することができる。更には、画素部が有する容量線も形成することができる。なお、走査線とは、画素を選択する配線をいう。

【0068】

次に、第1の配線層102を覆ってゲート絶縁層104を形成し、ゲート絶縁層104上に第1の半導体層106となる第1の半導体膜150、第2の半導体層108となる第2の半導体膜152、及び不純物半導体層110となる不純物半導体膜154を順に積層して形成する(図11(B)を参照)。なお、少なくとも、ゲート絶縁層104となる膜、第1の半導体膜150及び第2の半導体膜152を連続して成膜することが好ましい。更に好ましくは、不純物半導体膜154まで連続して成膜する。少なくとも、ゲート絶縁層104、第1の半導体膜150及び第2の半導体膜152を大気に触れさせることなく連続して成膜することで、大気成分や大気中に浮遊する不純物元素によりこれらの層が汚染されずに、積層膜の各層の界面を形成することができる。そのため、TFTの電気的特性のばらつきを低減することができ、信頼性の高いTFTを歩留まりよく作製することができる。

【0069】

ゲート絶縁層104は、CVD法またはスパッタリング法などを用いて形成することができる。例えば、ゲート絶縁層104は、50nm以上、好ましくは50nm以上400nm以下、より好ましくは150nm以上300nm以下となるように形成する。

【0070】

なお、ゲート絶縁層104の形成後、第1の半導体膜150の成膜前に、密着性を向上させ、または酸化を防止するための層をゲート絶縁層104上に形成してもよい。このような酸化防止などを目的として設けられる層として、例えば、酸化窒化シリコン層を窒化シリコン層により挟んだ積層構造の層が挙げられる。

【0071】

第1の半導体膜150は、ここではプラズマCVD法などを用いて微結晶シリコンにより形成することができる。なお、第1の半導体膜150の厚さは、10nm以上500nm以下とすればよい。微結晶半導体膜の厚さは、例えば、成膜工程におけるシランの流量と成膜時間により調整することができる。そして、成膜時には、酸素または窒素に代表される結晶化を阻害する成分を低減させ、シランなどの堆積性ガスの流量に対する水素などの希釈ガスの流量を大きくするとよい。このとき、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよい。このように形成することで、所謂、微結晶半導体層が形成される。

【0072】

なお、本実施の形態の結晶性半導体層のキャリア移動度は、非晶質半導体層のキャリア移動度の約2倍以上20倍以下である。そのため、結晶性半導体層により形成されるTFTでは、非晶質半導体層を用いたTFTと比較して、Id−Vg曲線における立ち上がり部分の傾きが急峻となる。ここで、Idはドレイン電流であり、Vgはゲート電圧である。なお、ドレイン電流とは、ソース電極とドレイン電極の間に流れる電流をいう。従って、結晶性半導体層をチャネル形成領域に用いたTFTは、スイッチング素子としての応答性に優れ、高速動作が可能である。表示装置のスイッチング素子として、結晶性半導体層をチャネル形成領域に用いたTFTを用いると、チャネル形成領域の面積(即ちTFTの面積)を縮小することもできる。そして、駆動回路の一部または全体を画素部と同じ基板上に一体形成し、システムオンパネルを形成することもできる。

【0073】

ところで、結晶性半導体層は、価電子制御を目的とした不純物元素を添加せずとも弱いn型の電気伝導性を示すことが多い。そのため、TFTのチャネル形成領域として機能する結晶性半導体層には、p型を付与する不純物元素(例えば、ボロン)を成膜と同時に、または成膜した後に添加することで閾値電圧Vthを調整してもよい。p型を付与する不純物元素として例えばボロンがあり、ジボラン(化学式:B2H6)、3フッ化ボロン(化学式:BF3)などの不純物元素を含む気体を1ppm〜1000ppm、好ましくは1〜100ppmの割合で水素化シリコンに含ませることで形成するとよい。そして、結晶性半導体層中のボロンの濃度を、例えば1×1014〜6×1016cm−3とするとよい。

【0074】

なお、第1の半導体膜150を形成する前に、プラズマCVD装置の反応室内を排気しつつ、シリコンまたはゲルマニウムを含む堆積性気体を導入して、反応室内の不純物元素を除去することで、成膜される膜の界面における不純物元素を低減することが可能であり、TFTの電気的特性を向上させることができる。

【0075】

第2の半導体膜152は、第2の半導体層108となるものである。第2の半導体膜152は、プラズマCVD装置の反応室内において、シリコンを含む堆積性気体と水素を混合し、グロー放電プラズマにより形成する。このとき、第1の半導体膜150の成膜条件よりも、シリコンを含む堆積性気体に対する水素の流量を減らして結晶成長を低減する条件で成膜することで、第2の半導体層108の半導体膜における結晶成長が抑制され、オフ電流の低減に寄与するバッファ層を形成することができる。

【0076】

ここで、第2の半導体層108が、従来の非晶質半導体と比較して欠陥が少なく価電子帯のバンド端(移動度端)における準位のテイル(裾)の傾きが急峻である秩序性の高い半導体により形成される場合について説明する。このような半導体層は、上記した結晶性半導体膜の形成ガス中に窒素を含むガスを混合させ、好ましくは第1の半導体膜150の成膜条件よりも堆積性気体に対する水素の流量比を小さくし、プラズマCVD法を用いることで、第2の半導体膜152における結晶成長が抑制されることで形成される。このとき、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよい。

【0077】

なお、第2の半導体膜152の成膜初期には、第1の半導体膜150の成膜条件よりもシリコンを含む堆積性気体に対する水素の流量を減らすことで、第2の半導体層108に微結晶半導体領域を残存させることができる。または、上記条件よりも、シリコンを含む堆積性気体に対する水素の流量を更に減らしていくことで、第2の半導体層108を、非晶質半導体を含む層とすることができる。または、上記条件よりも、シリコンを含む堆積性気体に対する水素の流量を更に減らし、且つ窒素を含むガスを混合させることで、第2の半導体層108の非晶質半導体領域を大きく形成することができる。

【0078】

なお、第2の半導体膜152の成膜初期においては、第1の半導体膜150を種結晶として、全体に膜が堆積される。その後は部分的に結晶成長が抑制され、錐状の微結晶半導体領域が成長する(成膜中期)。さらに、錐状の微結晶半導体領域の結晶成長が抑制され、上側に微結晶半導体領域を含まない第2の半導体膜152が形成される(成膜後期)。

【0079】

不純物半導体層110は、不純物半導体膜154を形成し、これをエッチングして形成することができる。不純物半導体層110として導電型がn型のTFTを形成する場合には、材料ガス中に、例えば不純物元素としてリンを添加すればよく、例えば水素化シリコンにフォスフィンを含む気体を加えることで形成することができる。または、導電型がp型のTFTを形成する場合には、材料ガス中に、例えば不純物元素としてボロンを添加すればよく、例えば水素化シリコンにジボランを含む気体を加えることで形成することができる。不純物半導体層110は、結晶性半導体または非晶質半導体のどちらで形成してもよいが、好ましくは結晶性半導体により形成する。不純物半導体層110は第2の半導体層108と第2の配線層112とがオーミック接触できる厚さとすればよく、概ね2nm以上60nm以下の厚さで形成するとよい。不純物半導体層110を可能な範囲で薄くすると、スループットを向上させることができる。なお、不純物半導体層110を結晶性半導体により形成する場合には、酸素または窒素に代表される結晶化を阻害する成分を低減させ、シランなどの堆積性ガスの流量に対する水素などの希釈ガスの流量を大きくすることで形成することができる。このとき、不純物半導体層110を非晶質半導体により形成する場合には、堆積性ガスの流量に対する希釈ガスの流量を1倍以上10倍以下、好ましくは1倍以上5倍以下とすればよいが、結晶性半導体により形成する場合には、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよい。このように形成することで、所謂、微結晶半導体層が形成される。

【0080】

なお、上述したように、ゲート絶縁層104から不純物半導体膜154までは連続して成膜することが好ましい(図11(B)を参照)。マルチチャンバーのCVD装置を用いると、堆積する膜の種類毎に反応室を配することが可能であり、複数の異なる種類の膜を大気に触れさせることなく連続して成膜することができる。

【0081】

図14は、複数の反応室を備えたマルチ・チャンバー・プラズマCVD装置の一例の上断面を示す模式図である。この装置は、共通室272、ロード/アンロード室270、第1反応室250a、第2反応室250b、第3反応室250c及び第4反応室250dを備えている。ロード/アンロード室270のカセットに基板100が装填されると、共通室272の搬送機構276によって各反応室に基板100が搬出入される。共通室272と各反応室及びロード/アンロード室との間にはゲートバルブ274が備えられ、各反応室で行われる処理が互いに干渉しないように構成されている。各反応室は成膜する薄膜の種類に応じて使い分けることができる。例えば、第1反応室250aでは絶縁膜を成膜し、第2反応室250b及び第4反応室250dでは半導体膜を成膜し、第3反応室250cでは一導電型を付与する不純物元素が添加された半導体膜を成膜する。それぞれの薄膜は最適な成膜温度が異なるので、反応室を分けておくことで成膜温度の管理が容易となり、各薄膜を最適な温度で成膜することができる。さらに、同じ膜種を繰り返し成膜することができるので、成膜履歴に係る残留物の影響を排除することができる。なお、一の反応室で一の膜を成膜する構成としてもよいし、結晶性半導体膜と非晶質半導体膜のように、一の反応室で複数の膜を成膜する構成としてもよい。

【0082】

各反応室には、排気手段としてターボ分子ポンプ264とドライポンプ266が接続されている。排気手段はこれらの真空ポンプの組み合わせに限定されるものではなく、概略10−5Paから10−1Paの真空度まで排気できるものであれば他の真空ポンプを用いてもよい。ただし、第2反応室250bでは、反応室内の圧力を概略10−5Pa以下まで到達させることができるようにクライオポンプ268が接続されていることが好ましい。これらの排気手段と各反応室との間にはバタフライバルブ260及びコンダクタンスバルブ262の一方または双方が設けられている。バタフライバルブ260を用いることで排気手段と反応室を遮断することができる。そして、コンダクタンスバルブ262を用いることで排気速度を調整し、各反応室の圧力を調節することができる。

【0083】

なお、第2反応室250bに接続されているクライオポンプ268を用いることで、反応室内の圧力を10−5Paよりも低い圧力(望ましくは超高真空)とすることも可能である。本実施の形態では、第2反応室250b内を10−5Paよりも低い圧力にすることで、半導体膜中への酸素などの大気成分の混入を防止することができる。その結果、半導体膜に含まれる酸素濃度を1×1016cm−3以下とすることができる。

【0084】

ガス供給手段258は、成膜ガスが充填されているシリンダ、ストップバルブ及びマスフローコントローラなどで構成されている。ガス供給手段258aは第1反応室250aに接続され、絶縁膜を成膜するためのガスを供給する。ガス供給手段258bは第2反応室250bに接続され、半導体膜を成膜するためのガスを供給する。ガス供給手段258cは第3反応室250cに接続され、例えばn型の導電型を付与する不純物元素が添加された半導体材料ガスを供給する。ガス供給手段258dは第4反応室250dに接続され、半導体膜を成膜するためのガスを供給する。ガス供給手段258eはArを供給する。ガス供給手段258fは反応室内のクリーニングに用いるエッチングガス(ここではNF3ガス)を供給する。Arガスとクリーニングに用いるエッチングガスはすべての反応室において用いられるため、ガス供給手段258eとガス供給手段258fはすべての反応室に接続されていることが好ましい。

【0085】

なお、各反応室にはプラズマを生成するための高周波電力供給手段が連結されている。ここで、高周波電力供給手段には高周波電源252と整合器254が含まれる。ただし、これに限定されず、マイクロ波発生部が接続されていてもよい。発生させるプラズマとしては、例えばRFプラズマ、VHFプラズマ、マイクロ波プラズマが挙げられる。なお、RFプラズマとVHFプラズマを同時に発生させる(2周波励起させる)ことで堆積率が向上するため好ましい。

【0086】

なお、ここで用いるプラズマはパルス変調プラズマであることが好ましい。パルス変調プラズマを用いることで、成膜時の堆積率が向上し、成膜時に発生するパーティクルを低減し、成膜される半導体膜の膜質及び厚さの均一性を向上させることができる。更には、プラズマ発生時の紫外線量を低減することができ、成膜される半導体膜中の欠陥数を低減することができる。

【0087】

なお、同一の反応室内において、結晶性半導体膜、非晶質半導体膜、及び一導電型を付与する不純物元素が添加された不純物半導体膜を連続して成膜してもよい。具体的には、ゲート絶縁膜が形成された基板を反応室内に搬入し、そこで結晶性半導体膜、非晶質半導体膜、及び一導電型を付与する不純物元素が添加された半導体膜(不純物半導体膜)を連続して成膜する。同一の反応室内で結晶性半導体膜及び非晶質半導体膜を連続して成膜することで、結晶歪の少ない界面を形成することが可能である。そのため、界面に意図しない準位が形成されることを防ぐことができる。そして、界面に混入しうる大気成分を低減することができる。

【0088】

なお、図示しないが、図14に示すマルチ・チャンバー・プラズマCVD装置には予備室が連結されていてもよい。成膜前に予備室で基板を加熱しておくと、各反応室における成膜までの加熱時間を短縮することが可能であり、スループットを向上させることができる。

【0089】

なお、上記説明したように連続して成膜することで、汚染源となりうる不純物元素によって界面が汚染されることなく、複数の膜を積層して形成することができる。そのため、TFTの電気的特性のばらつきを低減することができる。

【0090】

上記に示すプラズマCVD装置を用いることで、各反応室で一種類の膜または組成の類似する複数種の膜を成膜することが可能であり、且つ大気に曝すことなく連続成膜することができる。そのため、既に成膜した膜の残留物及び大気に浮遊する不純物元素によって界面が汚染されることなく、複数の膜を積層して形成することができる。

【0091】

プラズマCVD装置の反応室内は、フッ素ラジカルでクリーニングするとよい。そして、成膜前に反応室内に保護膜を成膜することが好ましい。

【0092】

なお、用いることのできる装置は上記の図14に示すものに限定されない。例えば、二の反応室が設けられたCVD装置を用いてもよい。このとき、一方の反応室(第1反応室)は、形成ガスに珪酸エチル(TEOS:化学式Si(OC2H5)4)を用いた酸化シリコン膜の形成に用いる反応室とし、他方の反応室(第2の反応室)は、窒化シリコン膜、シリコン膜及び一導電型の不純物元素を含むシリコン膜の形成に用いる反応室とすればよい。または、前記第2の反応室のみを有する装置を用いてもよい。

【0093】

次に、不純物半導体層110となる不純物半導体膜154上にレジストマスク156を形成する(図11(C)を参照)。レジストマスク156は、フォトリソグラフィ法により形成することができる。または、インクジェット法などにより形成してもよい。または、コスト低減を目的として、印刷法により形成してもよいし、印刷法により形成した後にレーザー加工を行ってもよい。

【0094】

次に、レジストマスク156を用いて、第1の半導体膜150、第2の半導体膜152、及び不純物半導体膜154をエッチングする。この処理により、これらの膜を素子毎に分離して、第1の半導体層106、第2の半導体層158及び不純物半導体層160を形成する(図12(A)を参照)。その後、レジストマスク156を除去する。

【0095】

なお、このエッチング処理では、第1の半導体層106、第2の半導体層158及び不純物半導体層160が積層された積層体162がテーパー形状となるようにエッチングを行うことが好ましい。テーパー角は30°以上90°以下、好ましくは40°以上80°以下とする。積層体162をテーパー形状とすることで、後の工程でこれらの上に形成される層(例えば、導電膜164)の被覆性を向上させることができ、配線切れなどを防止することができる。

【0096】

次に、積層体162上に導電膜164を形成する(図12(B)を参照)。導電膜164は、スパッタリング法または真空蒸着法などを用いて形成すればよい。または、導電膜164は、Ag、AuまたはCuなどの導電性ナノペーストを用いてスクリーン印刷法またはインクジェット法などを用いて吐出し、焼成することで形成してもよい。

【0097】

次に、導電膜164上にレジストマスク166を形成する(図12(C)を参照)。レジストマスク166は、レジストマスク156と同様にフォトリソグラフィ法またはインクジェット法により形成することができる。または、コスト低減を目的として、印刷法により形成してもよいし、印刷法により形成した後にレーザー加工を行ってもよい。または、レジストマスクのサイズを調整するために酸素プラズマによるアッシングを行ってもよい。

【0098】

次に、レジストマスク166を用いて導電膜164をエッチングし、導電膜164をパターン形成して第2の配線層112を形成する。エッチングにはウエットエッチングを用いることが好ましい。ウエットエッチングにより、導電膜164のうち、レジストマスク166から露出された部分が等方的にエッチングされる。その結果、導電膜はレジストマスク166の側面よりも内側まで後退し、第2の配線層112が形成される。この第2の配線層112はTFTのソース電極及びドレイン電極のみならず、信号線も構成する。

【0099】

次に、レジストマスク166が形成された状態で、第2の半導体層158及び不純物半導体層160をエッチングしてバックチャネル部を形成する。これにより、第2の半導体層158は一部を残してエッチングされ、第2の半導体層108及び不純物半導体層110が形成される。

【0100】

ここで、エッチングはドライエッチングにより行うとよく、特に、酸素を含んだガスによるドライエッチングを行うとよい。酸素を含んだガスにより、レジストを後退させつつ不純物半導体層110と第2の半導体層108をエッチングすることができ、不純物半導体層110と、第2の半導体層108をテーパー形状にすることができるからである。エッチングガスとしては、例えば、4フッ化メタン(化学式:CF4)に酸素を含ませたエッチングガスまたは塩素に酸素を含ませたエッチングガスを用いる。不純物半導体層110と、第2の半導体層108をテーパー形状にすることで電界の集中を防ぎ、オフ電流を低減させることができる。

【0101】

第2の半導体層108では、一部がエッチングされて凹部が設けられているが、凹部と重畳する第2の半導体層108の少なくとも一部が残存する厚さとすることが好ましい。不純物半導体層110と重畳する部分の第2の半導体層108は、ソース領域及びドレイン領域の形成プロセスにおいてエッチングされないが、この部分の厚さは概ね80nm以上500nm以下とするとよく、好ましくは150nm以上400nm以下であり、更に好ましくは200nm以上300nm以下である。上記のように、第2の半導体層108を十分に厚くすることで、第1の半導体層106への不純物元素の混入などを防止することができる。このように、第2の半導体層108は、第1の半導体層106の保護層としても機能する。

【0102】

次に、レジストマスク166を除去する。

【0103】

なお、ここまでの工程により生じた、バックチャネル部に存在する残渣及びレジストマスク166の除去に用いたレジスト剥離液の成分などは電気的特性に影響を与えることが多い。そのため、これらを除去することを目的として、レジストマスク166を除去した後に、更なるエッチング、プラズマ処理及び洗浄のいずれか一または複数の工程を用いることで、電気的特性が良好な(例えば、オフ電流が小さい)TFTを作製することができる。

【0104】

以上の工程により、図1に示すボトムゲート型のTFTを形成することができる(図13(A)を参照)。なお、図2乃至図7に示すボトムゲート型のTFTについても作製工程は上記と同様である。

【0105】

次に、上記のように作製したTFTを覆って保護層114を形成する(図13(B)を参照)。保護層114は、ゲート絶縁層104と同様に形成することができる。

【0106】

なお、図1に示すTFTは画素トランジスタとして用いることができるため、ソース電極及びドレイン電極の一方が画素電極に接続されている。図1に示すTFTにおいては、ソース電極及びドレイン電極の一方が、保護層114に設けられた開口部116を介して画素電極層118に接続されている。

【0107】

画素電極層118は、スパッタリング法などを用いて形成することができる。ここでは、ITOをスパッタリング法により形成すればよい。

【0108】

画素電極層118は、第2の配線層112などと同様に、全面に形成した後にレジストマスクなどを用いてエッチングを行い、パターン形成すればよい(図13(C)を参照)。

【0109】

なお、図示していないが、保護層114と画素電極層118との間に、画素電極層118の被形成面の平坦化を目的として、スピンコーティング法などにより有機樹脂層を形成してもよい。

【0110】

なお、上記した説明では、ゲート電極と走査線とが同一の工程で形成され、ソース電極及びドレイン電極と信号線とが同一の工程で形成される場合について説明したが、開示する発明はこれに限定されない。電極と、該電極に接続される配線を別工程により形成してもよい。

【0111】

なお、本実施の形態では、半導体材料としてシリコンを用いた場合について説明したが、これに限定されず、酸化物半導体を用いてもよいし、有機半導体を用いてもよい。

【0112】

なお、本実施の形態では逆スタガ型のTFTについて説明したが、これに限定されず、コプラナ型であってもよい。

【0113】

なお、本実施の形態では半導体材料としてシリコンを用いたが、これに限定されず、ゲルマニウムを用いてもよい。シランに代えて、GeH4、Ge2H6などの堆積性気体を用いればよい。

【0114】

なお、上記説明に限定されず、TFTはU字型(コの字型または馬蹄型)であってもよい。図15は、U字型のTFTを示す。

【0115】

なお、断面構造は、図1に示すものと同様である。基板300は、図1における基板100に相当する。第1の配線層302は、図1における第1の配線層102に相当する。ゲート絶縁層304は、図1におけるゲート絶縁層104に相当する。第1の半導体層306は、図1における第1の半導体層106に相当する。第2の半導体層308は、図1における第2の半導体層108に相当する。不純物半導体層310は、図1における不純物半導体層110に相当する。第2の配線層312は、図1における第2の配線層112に相当する。保護層314は、図1における保護層114に相当する。開口部316は、図1における開口部116に相当する。画素電極層318は、図1における画素電極層118に相当する。なお、図15(A)及び(B)においても、図1と同様に走査線と信号線の間に半導体層が設けられているが、図15(A)及び(B)では、走査線の一部が細く加工され、走査線と信号線の間の寄生容量が更に低減されている。

【0116】

TFTを図15(A)に示す形状とすることで、該TFTの最大アイランド幅を拡大することができ、オン電流を大きくすることができる。更には、電気的特性のばらつきを低減することができる。この場合には点線で囲まれた領域に電流が回り込むため、オン電流を大きくすることができる。

【0117】

または、TFTを図15(B)に示す形状としてもよい。この場合にも点線で囲まれた領域を電流が回り込むため、オン電流を大きくすることができる。更には、第1の配線層により構成されるゲート電極の占有面積を縮小することができるため、開口率を向上させることができる。

【0118】

以上、本実施の形態にて説明したように、半導体層のアイランド幅を部分的に拡大することで、第1の配線層と第2の配線層の間の寄生容量を増加させることなくオン電流を大きくすることができる。そのため、本実施の形態のTFTを画素TFTに適用すると、画素を高速動作させることができる。または、半導体層の最大アイランド幅を変えることなくソースドレイン幅を狭くすることができるため、第1の配線層と第2の配線層の間の寄生容量を低減させることができる。そのため、本実施の形態のTFTを画素TFTに適用すると、配線遅延を抑制し、画素を高速動作させることができる。

【0119】

(実施の形態2)

本実施の形態では、実施の形態1にて説明したTFTを搭載した表示パネルまたは発光パネルの一形態について、図面を参照して説明する。

【0120】

本実施の形態の表示装置または発光装置では、画素部に接続される信号線駆動回路及び走査線駆動回路は別の基板(例えば、半導体基板またはSOI基板など)上に設けて接続してもよいし、画素回路と同一基板上に形成してもよい。

【0121】

なお、別途形成した場合の接続方法は特に限定されるものではなく、公知のCOG法、ワイヤボンディング法またはTAB法などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、特に限定されない。または、コントローラ、CPU及びメモリなどを別途形成し、画素回路に接続してもよい。

【0122】

図16は、表示装置のブロック図を示す。図16に示す表示装置は、表示素子を備えた画素を複数有する画素部400と、各画素を選択する走査線駆動回路402と、選択された画素へのビデオ信号の入力を制御する信号線駆動回路403と、を有する。

【0123】

なお、開示する発明の一である表示装置は図16に示す形態に限定されない。すなわち、信号線駆動回路は、シフトレジスタとアナログスイッチのみを有する形態に限定されない。シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワなど、他の回路を有していてもよい。なお、シフトレジスタ及びアナログスイッチは必ずしも設ける必要はなく、例えば、シフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を有していてもよいし、アナログスイッチの代わりにラッチなどを有していてもよい。

【0124】

図16に示す信号線駆動回路403は、シフトレジスタ404及びアナログスイッチ405を有する。シフトレジスタ404には、クロック信号(CLK)とスタートパルス信号(SP)とが入力されている。クロック信号(CLK)とスタートパルス信号(SP)とが入力されると、シフトレジスタ404においてタイミング信号が生成され、アナログスイッチ405に入力される。

【0125】

なお、アナログスイッチ405には、ビデオ信号(video signal)が供給される。アナログスイッチ405は、入力されるタイミング信号に従ってビデオ信号をサンプリングし、後段の信号線に供給する。

【0126】

図16に示す走査線駆動回路402は、シフトレジスタ406及びバッファ407を有する。更には、レベルシフタを有していてもよい。走査線駆動回路402において、シフトレジスタ406にクロック信号(CLK)及びスタートパルス信号(SP)が入力されることによって、選択信号が生成される。生成された選択信号はバッファ407において緩衝増幅され、対応する走査線に供給される。一の走査線には、1ラインのすべての画素トランジスタのゲートが接続されている。そして、動作時には1ライン分の画素トランジスタを一斉にオンにしなくてはならないので、バッファ407は大きな電流を流すことが可能な構成とする。

【0127】

フルカラーの表示装置において、R(赤)、G(緑)、B(青)に対応するビデオ信号を、順にサンプリングして対応する信号線に供給する場合、シフトレジスタ404とアナログスイッチ405とを接続するための端子数は、アナログスイッチ405と画素部400の信号線を接続するための端子数の1/3程度に相当する。よって、アナログスイッチ405を画素部400と同一基板上に形成することで、アナログスイッチ405を画素部400と異なる基板上に形成した場合に比べて、別途形成した基板の接続に用いる端子の数を抑えることができ、接続不良の発生確率を抑えて歩留まりを高めることができる。

【0128】

なお、図16の走査線駆動回路402は、シフトレジスタ406及びバッファ407を有するが、これに限定されず、シフトレジスタ406のみで走査線駆動回路402を構成してもよい。

【0129】

なお、図16に示す構成は、表示装置の一形態を示したものであり、信号線駆動回路と走査線駆動回路の構成はこれに限定されない。

【0130】

次に、表示装置の一形態に相当する液晶表示パネル及び発光パネルの外観について、図17及び図18を参照して説明する。図17(A)は、第1の基板411上に形成された結晶性半導体層を有するTFT420及び液晶素子423を、第2の基板416との間にシール材415によって封止した、パネルの上面図を示す。図17(B)は、図17(A)のK−Lにおける断面図に相当する。図18は発光装置の場合を示す。なお、図18は、図17と異なる部分についてのみ符号を付している。

【0131】

第1の基板411上に設けられた画素部412と、走査線駆動回路414と、を囲んで、シール材415が設けられている。そして、画素部412及び走査線駆動回路414の上に第2の基板416が設けられている。よって画素部412及び走査線駆動回路414は、第1の基板411とシール材415と第2の基板416とによって、液晶層418または充填材431と共に封止されている。そして、第1の基板411上のシール材415によって囲まれている領域とは異なる領域に信号線駆動回路413が実装されている。なお、信号線駆動回路413は、別途用意された基板上に結晶性半導体層を有するTFTにより設けられたものである。なお、本実施の形態では、結晶性半導体層を有するTFTを用いた信号線駆動回路413を、第1の基板411に貼り合わせる場合について説明するが、単結晶半導体を用いたTFTで信号線駆動回路を形成し、貼り合わせることが好ましい。図17では、信号線駆動回路413に含まれる、結晶性半導体層で形成されたTFT419を例示する。

【0132】

第1の基板411上に設けられた画素部412は、複数のTFTを有しており、図17(B)には、画素部412に含まれるTFT420を例示している。なお、本実施の形態の発光装置においては、TFT420は駆動用トランジスタであってもよいし、電流制御用トランジスタであってもよいし、消去用トランジスタであってもよい。TFT420は実施の形態1で説明した結晶性半導体層を用いたTFTに相当する。

【0133】

液晶素子423が有する画素電極422は、TFT420と配線428を介して電気的に接続されている。そして、液晶素子423の対向電極427は第2の基板416上に設けられている。画素電極422と対向電極427と液晶層418が重なっている部分が、液晶素子423に相当する。

【0134】

発光素子430が有する画素電極は、TFT420のソース電極またはドレイン電極と、配線を介して電気的に接続されている。そして本実施の形態では、発光素子430の共通電極と透光性を有する導電性材料層が電気的に接続されている。なお、発光素子430の構成は、本実施の形態に示した構成に限定されない。発光素子430の構成は、発光素子430から取り出す光の方向や、TFT420の極性などに応じて決定することができる。

【0135】

なお、第1の基板411及び第2の基板416の材料としては、ガラス、金属(例えばステンレス)、セラミックスまたはプラスチックなどを用いることができる。プラスチックとしては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルム、またはアクリル樹脂フィルムなどを用いることができる。または、アルミニウム箔をPVFフィルムやポリエステルフィルムで挟んだ構造のシートを用いてもよい。

【0136】

なお、スペーサ421はビーズスペーサであり、画素電極422と対向電極427との間に一定の距離(セルギャップ)を確保するために設けられている。なお、絶縁層を選択的にエッチングすることで得られるスペーサ(ポストスペーサ)を用いていてもよい。

【0137】

なお、別途形成された信号線駆動回路413と、走査線駆動回路414及び画素部412に与えられる各種の信号(電位)は、FPC417(Flexible Printed Circuit)から引き回し配線424及び引き回し配線425を介して供給される。

【0138】

本実施の形態では、接続端子426が、液晶素子423が有する画素電極422と同じ導電層から形成されている。そして、引き回し配線424及び引き回し配線425は、配線428と同じ導電層で形成されている。

【0139】

接続端子426とFPC417が有する端子は、異方性導電層429を介して電気的に接続されている。

【0140】

なお、図示していないが、本実施の形態に示した液晶表示装置は、配向膜及び偏光板を有し、更にカラーフィルタや遮光層などを有していてもよい。

【0141】

なお、発光素子430からの光の取り出し方向に位置する基板である第2の基板は透光性の基板を用いる。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムなどの透光性を有する材料からなる基板を用いる。発光素子430からの光の取り出し方向が第1の基板の方向である場合には、第1の基板として透光性基板を用いる。

【0142】

なお、充填材431としては、窒素やArなどの不活性な気体、紫外線硬化樹脂または熱硬化樹脂などを用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラール)またはEVA(エチレンビニルアセテート)などを用いることができる。ここでは、例えば、窒素を用いるとよい。

【0143】

なお、発光素子の射出面に偏光板、円偏光板(楕円偏光板を含む)、位相差板(λ/4板、λ/2板)またはカラーフィルタなどの光学フィルムを適宜設けてもよい。更には、偏光板または円偏光板に反射防止層を設けてもよい。

【0144】

(実施の形態3)

本実施の形態は、実施の形態2にて説明した方法により作製した表示パネルまたは表示装置を表示部として組み込んだ電子機器について図19乃至図21を参照して説明する。このような電子機器としては、例えば、ビデオカメラ若しくはデジタルカメラなどのカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍など)が挙げられる。それらの一例を図19に示す。

【0145】

図19(A)はテレビジョン装置を示す。表示パネルを筐体に組み込むことで、図19(A)に示すテレビジョン装置を完成させることができる。実施の形態2にて説明した作製方法を適用した表示パネルにより主画面503が形成され、その他付属設備としてスピーカ部509、操作スイッチなどが備えられている。

【0146】

図19(A)に示すように、筐体501に実施の形態2にて説明した作製方法を適用した表示用パネル502が組み込まれ、受信機505により一般のテレビ放送の受信をはじめ、モデム504を介して有線または無線による通信ネットワークに接続することにより片方向(送信者から受信者)または双方向(送信者と受信者間、または受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチまたはリモコン操作機506により行うことが可能であり、このリモコン操作機506にも、出力する情報を表示する表示部507が設けられていてもよい。

【0147】

なお、テレビジョン装置にも、主画面503の他にサブ画面508を第2の表示パネルで形成し、チャンネルや音量などを表示する構成が付加されていてもよい。

【0148】

図20は、テレビジョン装置の主要な構成を示すブロック図を示している。表示パネル520には、画素部521が形成されている。信号線駆動回路522と走査線駆動回路523は、表示パネル520にCOG方式により実装されていてもよい。

【0149】

その他の外部回路の構成として、映像信号の入力側では、チューナ524で受信した信号のうち、映像信号を増幅する映像信号増幅回路525と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路526と、その映像信号を適切な入力仕様に変換するためのコントロール回路527などを有している。コントロール回路527は、走査線駆動回路523と信号線駆動回路522にそれぞれ信号を出力する。デジタル駆動する場合には、信号線側に信号分割回路528を設け、入力デジタル信号を整数個に分割して供給する構成としてもよい。

【0150】

チューナ524で受信した信号のうち、音声信号は、音声信号増幅回路529に送られ、その出力は音声信号処理回路530を経てスピーカ533に供給される。制御回路531は受信局(受信周波数)、音量の制御信号を入力部532から受け、チューナ524及び音声信号処理回路530に信号を送出する。

【0151】

勿論、本発明の一形態である表示装置はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤、または街頭における広告表示盤などの大面積の表示媒体にも適用することができる。そのため、これらの表示媒体の表示品質を向上させることができる。

【0152】

主画面503及びサブ画面508の一方または双方に、実施の形態2で説明した作製方法を適用した表示パネルまたは表示装置を用いることで、テレビ装置の表示品質を高めることができる。

【0153】

図19(B)に示す携帯型のコンピュータは、本体511及び表示部512などを有する。表示部512に、実施の形態2で説明した表示装置の作製方法を適用した表示パネルまたは表示装置を用いることで、コンピュータの表示部の表示品質を高めることができる。

【0154】

図21は、携帯電話の一例を示し、図21(A)が正面図、図21(B)が背面図、図21(C)が2つの筐体をスライドさせたときの正面図である。図21に示す携帯電話は、筐体541及び筐体542二つの筐体で構成されている。図21に示す携帯電話は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能な所謂スマートフォンである。

【0155】

筐体541は、表示部543、スピーカ544、マイクロフォン545、操作キー546、ポインティングデバイス547、表面カメラ用レンズ548、外部接続端子ジャック549及びイヤホン端子550などを備え、筐体542は、キーボード551、外部メモリスロット552、裏面カメラ553、ライト554などにより構成されている。アンテナは筐体541に内蔵されている。

【0156】

なお、図21に示す携帯電話は、上記の構成に加えて、非接触型ICチップ、小型記録装置などを内蔵していてもよい。

【0157】

重なり合った筐体541と筐体542(図21(A)に示す。)は、スライドさせることが可能であり、スライドさせることで図21(C)のように展開する。表示部543には、実施の形態2で説明した表示装置の作製方法を適用した表示パネルまたは表示装置を組み込むことが可能である。なお、表示部543と表面カメラ用レンズ548を同一の面に備えているため、テレビ電話としての使用が可能である。更には、表示部543をファインダーとして用いることで、裏面カメラ553及びライト554で静止画及び動画の撮影が可能である。

【0158】

スピーカ544及びマイクロフォン545を用いることで、図21に示す携帯電話は、音声記録装置(録音装置)または音声再生装置として使用することができる。または、操作キー546により、電話の発着信操作、電子メールなどの簡単な情報入力操作、表示部に表示する画面のスクロール操作、表示部に表示する情報の選択などを行うカーソルの移動操作などが可能である。

【0159】

なお、書類の作成、携帯情報端末としての使用など、取り扱う情報が多い場合は、キーボード551を用いると便利である。更に、重なり合った筐体541と筐体542(図21(A)を参照)をスライドさせることで、図21(C)のように展開させることができる。携帯情報端末として使用する場合には、キーボード551及びポインティングデバイス547を用いて、円滑な操作でマウスの操作が可能である。外部接続端子ジャック549はACアダプタ及びUSBケーブルなどの各種ケーブルと接続可能であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。なお、外部メモリスロット552に記録媒体を挿入することで、より大量のデータ保存及び移動が可能になる。

【0160】

筐体542の裏面(図21(B)を参照)には、裏面カメラ553及びライト554を備え、表示部543をファインダーとして静止画及び動画の撮影が可能である。

【0161】

なお、上記の機能構成に加えて、赤外線通信機能、USBポート、テレビワンセグ受信機能、非接触ICチップまたはイヤホンジャックなどを備えたものであってもよい。

【0162】

本実施の形態にて説明した各種電子機器は、実施の形態1にて説明したTFT及び実施の形態2にて説明した表示装置の作製方法を適用して作製することができる。従って、作製コストを増大させることなく、表示部の表示品質の高い電子機器を作製することができる。

【符号の説明】

【0163】

100 基板

102 第1の配線層

104 ゲート絶縁層

106 第1の半導体層

108 第2の半導体層

110 不純物半導体層

112 第2の配線層

114 保護層

116 開口部

118 画素電極層

150 第1の半導体膜

152 第2の半導体膜

154 不純物半導体膜

156 レジストマスク

158 第2の半導体層

160 不純物半導体層

162 積層体

164 導電膜

166 レジストマスク

200 基板

202 第1の配線層

204 ゲート絶縁層

206 第1の半導体層

208 第2の半導体層

210 不純物半導体層

212 第2の配線層

214 保護層

216 開口部

218 画素電極層

250a 第1反応室

250b 第2反応室

250c 第3反応室

250d 第4反応室

252 高周波電源

254 整合器

258 ガス供給手段

258a ガス供給手段

258b ガス供給手段

258c ガス供給手段

258d ガス供給手段

258e ガス供給手段

258f ガス供給手段

260 バタフライバルブ

262 コンダクタンスバルブ

264 ターボ分子ポンプ

266 ドライポンプ

268 クライオポンプ

270 ロード/アンロード室

272 共通室

274 ゲートバルブ

276 搬送機構

300 基板

302 第1の配線層

304 ゲート絶縁層

306 第1の半導体層

308 第2の半導体層

310 不純物半導体層

312 第2の配線層

314 保護層

316 開口部

318 画素電極層

400 画素部

402 走査線駆動回路

403 信号線駆動回路

404 シフトレジスタ

405 アナログスイッチ

406 シフトレジスタ

407 バッファ

411 基板

412 画素部

413 信号線駆動回路

414 走査線駆動回路

415 シール材

416 基板

417 FPC

418 液晶層

419 TFT

420 TFT

421 スペーサ

422 画素電極

423 液晶素子

424 配線

425 配線

426 接続端子

427 対向電極

428 配線

429 異方性導電層

430 発光素子

431 充填材

501 筐体

502 表示用パネル

503 主画面

504 モデム

505 受信機

506 リモコン操作機

507 表示部

508 サブ画面

509 スピーカ部

511 本体

512 表示部

520 表示パネル

521 画素部

522 信号線駆動回路

523 走査線駆動回路

524 チューナ

525 映像信号増幅回路

526 映像信号処理回路

527 コントロール回路

528 信号分割回路

529 音声信号増幅回路

530 音声信号処理回路

531 制御回路

532 入力部

533 スピーカ

541 筐体

542 筐体

543 表示部

544 スピーカ

545 マイクロフォン

546 操作キー

547 ポインティングデバイス

548 表面カメラ用レンズ

549 外部接続端子ジャック

550 イヤホン端子

551 キーボード

552 外部メモリスロット

553 裏面カメラ

554 ライト

【技術分野】

【0001】

本発明は、薄膜トランジスタに関する。特に、薄膜トランジスタが設けられた表示装置に関する。

【背景技術】

【0002】

近年、絶縁性表面を有する基板(例えば、ガラス基板)上の半導体薄膜(厚さ数nm〜数百nm程度)によって構成された薄膜トランジスタ(以下、TFTという。)が注目されている。TFTは、IC(Integrated Circuit)及び電気光学装置のような電子デバイスに広く応用されている。特に、液晶表示装置などに代表される、画像表示装置のスイッチング素子として開発が急がれている。液晶表示装置などの画像表示装置では、スイッチング素子として、主に非晶質半導体膜または多結晶半導体膜を用いたTFTが用いられている。

【0003】

非晶質半導体膜を用いたTFTは、移動度が低い。つまり、電流駆動能力が低い。そのため、非晶質半導体膜を用いたTFTにより保護回路を形成するに際して、十分な静電破壊対策をするにはサイズの大きいトランジスタを形成する必要があり、狭額縁化を阻害してしまうという問題がある。更には、サイズの大きいトランジスタを形成することでゲート電極に電気的に接続される走査線と、ソース電極またはドレイン電極に電気的に接続される信号線との間の寄生容量が増大してしまい、消費電力の増大を招くという問題もある。

【0004】

一方で、多結晶半導体膜を用いたTFTは、非晶質半導体膜を用いたTFTに比べて移動度が2桁以上高く、液晶表示装置の画素部とその周辺の駆動回路を同一基板上に形成できる。しかしながら、多結晶半導体膜を用いたTFTは、非晶質半導体膜を用いたTFTに比べて、半導体膜の結晶化及び不純物元素の導入(ドーピング)などにより工程が複雑化する。そのため、歩留まりが低く、コストが高いという問題がある。多結晶半導体膜の形成方法としては、例えば、パルス発振のエキシマレーザビームの形状を光学系により線状に加工し、非晶質半導体膜に対して線状のレーザビームを走査させつつ照射して結晶化する技術が広く知られている。

【0005】

ところで、画像表示装置のスイッチング素子としては、非晶質半導体膜を用いたTFTまたは多結晶半導体膜を用いたTFTの他に、微結晶半導体膜を用いたTFTが知られている(例えば、特許文献1を参照)。しかし、微結晶半導体膜を用いたTFTでは、十分なオン電流を得ることが困難である。そのため、非晶質半導体膜または微結晶半導体膜を用いたTFTにおいて、十分なオン電流を得るための様々な開発が行われてきた。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−44134号公報

【特許文献2】米国特許4,409,134号

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一態様は、従来よりもオン電流が大きく、電界効果移動度が大きいTFTを提供することを課題とする。

【課題を解決するための手段】

【0008】

本発明の一態様は、ソースとドレインの間における半導体層のアイランド幅を拡大したTFTである。

【発明の効果】

【0009】

TFTのオン電流を十分に大きくすることができる。

【0010】

TFTの電界効果移動度を十分に大きくすることができる。

【図面の簡単な説明】

【0011】

【図1】TFT及び表示装置を説明する図。

【図2】TFT及び表示装置を説明する図。

【図3】TFT及び表示装置を説明する図。

【図4】TFT及び表示装置を説明する図。

【図5】TFT及び表示装置を説明する図。

【図6】TFT及び表示装置を説明する図。

【図7】TFT及び表示装置を説明する図。

【図8】計算結果を説明する図。

【図9】計算結果を説明する図。

【図10】計算結果を説明する図。

【図11】TFT及び表示装置の作製方法を説明する図。

【図12】TFT及び表示装置の作製方法を説明する図。

【図13】TFT及び表示装置の作製方法を説明する図。

【図14】TFT及び表示装置の作製方法を説明する図。

【図15】TFT及び表示装置を説明する図。

【図16】表示装置を説明する図。

【図17】表示装置を説明する図。

【図18】表示装置を説明する図。

【図19】電子機器を説明する図。

【図20】電子機器を説明する図。

【図21】電子機器を説明する図。

【発明を実施するための形態】

【0012】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、説明中に図面を参照するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0013】

(実施の形態1)

本実施の形態では、本発明の一態様であるTFTについて、図面を参照して説明する。

【0014】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されていることを特徴とする薄膜トランジスタである。ここで、ゲート電極は第1の配線層により形成され、ソース電極及びドレイン電極は第2の配線層により形成され、以下同様である。

【0015】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられた配線層と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大されていることを特徴とする薄膜トランジスタである。

【0016】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短いことを特徴とする薄膜トランジスタである。

【0017】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大され、前記ソース領域と前記ドレイン領域上にはソース電極及びドレイン電極が設けられ、該ソース電極及びドレイン電極の一方には選択的に形成された画素電極層が接続されていることを特徴とする表示装置である。

【0018】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大され、前記ソース領域と前記ドレイン領域上にはソース電極及びドレイン電極が設けられ、ソース電極及びドレイン電極の一方には選択的に形成された画素電極層が接続されていることを特徴とする表示装置である。

【0019】

本発明の一態様は、ゲート電極と、前記ゲート電極を覆って設けられたゲート絶縁層と、前記ゲート絶縁層上に、前記ゲート電極と重畳して設けられた半導体層と、前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、前記不純物半導体層上に設けられたソース電極及びドレイン電極と、を有し、前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短く、前記ソース領域と前記ドレイン領域上にはソース電極及びドレイン電極が設けられ、該ソース電極及びドレイン電極の一方には選択的に形成された画素電極層が接続されていることを特徴とする表示装置である。

【0020】

図1は、本実施の形態のTFTの一例を示す。図1(A)には断面図を示し、図1(B)には上面図を示す。なお、図1(A)は、図1(B)に示すX−Yにおける断面図である。

【0021】

図1に示すTFTは、基板100上の第1の配線層102を覆ってゲート絶縁層104が設けられ、ゲート絶縁層104上には第1の半導体層106が設けられ、第1の半導体層106上には第2の半導体層108が設けられ、第2の半導体層108上には不純物半導体層110を介して第2の配線層112が設けられている(図1(A)を参照)。ここで、不純物半導体層110は、第2の半導体層108と第2の配線層112をオーミック接触させるために設けられているものである。第2の配線層112は、ソース電極と、ドレイン電極と、ソース配線と、を構成する。なお、当該TFTは保護層114によって覆われていることが好ましい。当該TFTを表示装置の画素トランジスタとして用いる場合には、図1に示すように保護層114に開口部116を設け、開口部116を介して第2の配線層112に接続されるように画素電極層118を設ければよい。

【0022】

基板100は、基板100上に形成される薄膜(結晶性シリコンなど)の形成工程に耐えうる程度の耐熱性及び耐薬品性などを有していればよく、特定の材料からなる基板に限定されるものではない。具体的には、ガラス基板、石英基板、ステンレス基板及びシリコン基板が挙げられる。なお、図1に示すように、TFTを表示装置に適用する場合には、基板100には透光性を有する基板を用いればよく、例えばガラス基板または石英基板を用いればよい。基板100がマザーガラスの場合には、第1世代(例えば、320mm×400mm)〜第10世代(例えば、2950mm×3400mm)のものを用いればよいがこれに限定されるものではない。

【0023】

第1の配線層102は、導電性材料により形成することができ、単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、Mo、Ti、Cr、Ta、W、Al、Cu、Nd若しくはScなどの金属材料またはこれらを主成分とする合金材料により形成することができる。なお、第1の配線層102は、少なくともゲート電極及びゲート配線を構成する。

【0024】

ゲート絶縁層104は、絶縁性材料により形成することができ、単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、酸化シリコン、窒化シリコン、酸化窒化シリコンまたは窒化酸化シリコンによって形成することができる。第1の半導体層106が結晶性半導体層である場合には、少なくとも第1の半導体層106に接するゲート絶縁層104は、酸化シリコン層とすることが好ましい。ゲート絶縁層104として酸化シリコン層を形成する場合には、形成ガスに珪酸エチル(TEOS:化学式Si(OC2H5)4)を用いた酸化シリコン層により形成することが好ましい。

【0025】

なお、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合に、組成範囲として酸素が50〜70原子%、窒素が0.5〜15原子%、シリコンが25〜35原子%、水素が0.1〜10原子%の範囲で含まれるものをいう。

【0026】

なお、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、組成範囲として酸素が5〜30原子%、窒素が20〜55原子%、シリコンが25〜35原子%、水素が10〜30原子%の範囲で含まれるものをいう。ただし、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0027】

第1の半導体層106は、結晶性半導体により形成するとよい。結晶性半導体には、多結晶半導体または微結晶半導体などを含むが、結晶化工程が不要な微結晶半導体により形成することが好ましい。

【0028】

ここで、微結晶半導体とは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造の半導体をいう。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な半導体であり、結晶粒径が2nm以上200nm以下、好ましくは10nm以上80nm以下、より好ましくは、20nm以上50nm以下の柱状結晶または針状結晶が基板表面に対して法線方向に成長している半導体である。このため、柱状結晶または針状結晶の界面には、結晶粒界が形成される場合もある。

【0029】

微結晶半導体の一である微結晶シリコンでは、そのラマンスペクトルのピークが単結晶シリコンを示す520cm−1よりも低波数側にシフトしている。すなわち、単結晶シリコンを示す520cm−1とアモルファスシリコンを示す480cm−1の間に微結晶シリコンのラマンスペクトルのピークがある。そして、未結合手(ダングリングボンド)を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、He、Ar、Kr、またはNeなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体が得られる。このような微結晶半導体に関する記述は、例えば、米国特許4,409,134号で開示されている。

【0030】

そして、第1の半導体層106に含まれる酸素及び窒素の濃度(二次イオン質量分析法による測定値)を、1×1018cm−3未満とすると、第1の半導体層106の結晶性を高めることができる。

【0031】

第2の半導体層108は、第1の半導体層106に接して設けられており、第1の半導体層106よりもキャリア移動度が低い材料により設けるとよい。第2の半導体層108によりオフ電流を低減することができる。

【0032】

例えば、第1の半導体層106として結晶性半導体層を形成し、第2の半導体層108として、非晶質半導体と微小半導体結晶粒を有する半導体層を形成するとよい。TFTがオンすると第1の半導体層106に流れる電流が支配的であり、TFTがオフすると第2の半導体層108に流れる電流が支配的である。第2の半導体層108を「非晶質半導体と微小半導体結晶粒を有する半導体層」とすることで、オン電流の低下を防ぐこともできる。そのため、第1の半導体層106を結晶性半導体層とし、第2の半導体層108を「非晶質半導体と微小半導体結晶粒を有する半導体層」とすることで、オンオフ比が高いTFTを得ることができる。

【0033】

上記説明した第2の半導体層108の好ましい形態の一である「非晶質半導体と微小半導体結晶粒を有する半導体層」は、非晶質半導体と微小半導体結晶粒を有し、従来の非晶質半導体と比較して、CPM(Constant photocurrent method)やフォトルミネッセンス分光測定で測定されるUrbach端のエネルギーが小さく、欠陥吸収スペクトル量が少ない半導体層である。すなわち、従来の非晶質半導体と比較して欠陥が少なく、価電子帯のバンド端(移動度端)における準位のテイル(裾)の傾きが急峻である秩序性の高い半導体層である。

【0034】

ただし、第2の半導体層108は、上記説明に限定されず、非晶質半導体により形成してもよい。第2の半導体層108は、少なくとも第1の半導体層106よりもキャリア移動度の低い材料により設ければよく、非晶質半導体、またはハロゲンを有する非晶質半導体、または窒素を有する非晶質半導体により形成してもよい。非晶質半導体としては、アモルファスシリコンが挙げられる。

【0035】

第1の半導体層106と第2の半導体層108の界面領域は、好ましくは、微結晶半導体領域、及び当該微結晶半導体領域の間に充填される非晶質半導体を有する。具体的には、第1の半導体層106から凸状に伸びた微結晶半導体領域と、第2の半導体層108と同様の半導体と、で形成される。このとき、第1の半導体層106と第2の半導体層108の界面領域には錐形状の微結晶半導体領域を有するため、第2の配線層112に電圧を印加したときの縦方向(厚さ方向)の抵抗(すなわち、第2の半導体層108と、不純物半導体層110により構成されるソース領域またはドレイン領域と、の間の抵抗)を低くすることができ、TFTのオン電流を高めることが可能である。なお、ここで界面領域とは、厚さ方向における界面の近傍の領域をいう。

【0036】

第1の半導体層106と第2の半導体層108の界面領域は、ゲート絶縁層104から第2の半導体層108に向かって先端が狭くなる凸状の結晶粒により大部分が構成されているとよい。または、ゲート絶縁層104から第2の半導体層108に向かって幅が広がる凸状の結晶粒により大部分が構成されているとよい。

【0037】

第1の半導体層106と第2の半導体層108の界面領域において、微結晶半導体領域が、ゲート絶縁層104から第2の半導体層108に向けて、先端が狭まる凸状の結晶粒の場合は、第1の半導体層106側のほうが、第2の半導体層108側と比較して、微結晶半導体領域の割合が高い。微結晶半導体領域は、第1の半導体層106の表面から厚さ方向に成長するが、原料ガスにおけるシランに対する水素の流量が小さく、または窒素を含む原料ガスの濃度が高いと、微結晶半導体領域における結晶成長が抑制され、結晶粒は錐状になり、堆積されて形成される半導体は、大部分が非晶質となる。

【0038】

第2の半導体層108は、電界を緩和してオフ電流を低減する層として機能する。ここでは、第2の半導体層108を、従来の非晶質半導体と比較して欠陥が少なく、価電子帯のバンド端(移動度端)における準位のテール(裾)の傾きが急峻である秩序性の高い半導体膜を加工して形成する場合について説明する。このような半導体膜は、結晶性半導体膜の形成ガス中に、好ましくは窒素を含むガスを混合させ、結晶性半導体膜の成膜条件よりも堆積性ガス(例えば、シランガス)に対する水素の流量比を小さくし、プラズマCVD法を用いることで、結晶成長が抑制されて形成される。なお、第2の半導体層108には、好ましくは窒素が1×1020cm−3乃至1×1021cm−3で含まれる。ここで、窒素は、NH基またはNH2基の状態で存在することが好ましい。半導体原子のダングリングボンドが窒素原子若しくはNH基で架橋され、またはNH2基で終端されてキャリアが流れやすくなるためである。特に、隣り合う二つのシリコン原子のダングリングボンドをNH基により架橋することでキャリア移動度が向上し、オン電流が増大する。なお、NH2基は主に半導体内部のダングリングボンドの終端に寄与する。この結果、結晶粒界や欠陥に起因するトラップ準位密度を小さくし、ポテンシャル障壁を消失させ若しくは低減させることができる。そのため、キャリアが散乱、トラップ、若しくは再結合されにくくなることで、キャリア移動度が向上し、TFTは十分な電界効果移動度とオン電流を得ることができる。

【0039】

更には、ダングリングボンドが、窒素原子若しくはNH基によって架橋され、またはNH2基によって終端されることで、半導体のバンドギャップ中央付近に形成されるトラップ準位が消失し若しくはその数が少なくなる。そのため、このトラップ準位に起因する間接トンネル電流(例えば、Shockley Read Hall電流、Trap Assisted Tunneling電流、Poole Frenkel電流)を抑えることができ、オフ電流をも低減することができる。

【0040】

上記説明した第2の半導体層108を設けることで、オン/オフ比が高いTFTを得ることができる。なお、このとき、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよく、結晶性半導体膜を形成する時よりも希釈ガスの流量比を小さくするとよい。

【0041】

更には、上記の界面領域の酸素濃度を低減することにより、微結晶半導体領域と非晶質半導体領域との界面や、結晶粒同士の界面における欠陥、キャリアの移動を阻害する結合を低減することができる。

【0042】

または、上記説明に限定されず、第2の半導体層108を有さない構成としてもよい。この場合には、上記した界面領域が第1の半導体層106と不純物半導体層110の間に設けられるとよい。この界面領域には、微結晶半導体領域と、当該微結晶半導体領域の間に充填された非晶質半導体領域を有する。微結晶半導体領域は第1の半導体層106から伸びた微結晶半導体により形成される。このとき、非晶質半導体領域に対する微結晶半導体領域の割合は小さいことが好ましい。さらには、対となる不純物半導体層110の間(ソース領域とドレイン領域の間)、すなわちキャリアが流れる領域においては、微結晶半導体領域の割合が小さいことが好ましい。TFTのオフ電流を低減することができるためである。そして、上記の界面領域では第2の配線層112に電圧を印加したときの縦方向(厚さ方向)の抵抗が低いため、TFTのオン電流を大きくすることが可能である。

【0043】

不純物半導体層110は、第1の半導体層106または第2の半導体層108と、第2の配線層112と、をオーミック接触させることを目的として設ける層であり、形成ガスに一導電型を付与する不純物元素を含む気体を加えて形成することができる。導電型がn型のTFTを形成する場合には、例えば不純物元素としてリンを添加すればよく、水素化シリコンにフォスフィンなどのn型の導電型を付与する不純物元素を含む気体を加えればよい。導電型がp型のTFTを形成する場合には、例えば不純物元素としてボロンを添加すればよく、水素化シリコンにジボランなどのp型の導電型を付与する不純物元素を含む気体を加えればよい。なお、不純物半導体層110の結晶性は特に限定されず、結晶性半導体であってもよいし、非晶質半導体であってもよいが、結晶性半導体により設けることが好ましい。不純物半導体層110を結晶性半導体層により設けることで、オン電流が大きくなるからである。

【0044】

第2の配線層112は、導電性材料により単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、第1の配線層102と同様の材料により形成することができる。

【0045】

保護層114は、ゲート絶縁層104と同様に形成することができるが、窒化シリコンにより形成することが特に好ましい。特に、大気中に浮遊する有機物や金属、水蒸気などの汚染源となりうる物質の侵入を防ぐことができるよう、緻密な窒化シリコン層とすることが好ましい。

【0046】

画素電極層118は、透光性を有する導電性高分子(導電性ポリマーともいう。)を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆるπ電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、またはこれらの2種以上の共重合体などがあげられる。

【0047】

画素電極層118は、例えば、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOという。)、インジウム亜鉛酸化物または酸化シリコンを添加したインジウム錫酸化物などを用いて形成してもよい。

【0048】

なお、図1に示すTFTは、第1の配線層102と接続される走査線と第2の配線層112と接続される信号線が交差する部分において、走査線と信号線の間に第1の半導体層106、第2の半導体層108(以下、第1の半導体層106または第2の半導体層108を単に半導体層ともいう)、及び不純物半導体層110が設けられているため、走査線と信号線の間に生じる寄生容量を低減することができる。ここで、少なくとも走査線と信号線の間に設けられる第1の半導体層106は、走査線と信号線の間に生じる寄生容量をさらに低減させるため、重畳する走査線からはみ出すように設けられることが好ましい。

【0049】

次に、図1乃至図6に示すTFTを比較する。図1に示すTFTにおいて、ソース領域及びドレイン領域の幅はソースドレイン幅W0と表し、半導体層の内側の幅は最小アイランド幅W1と表し、半導体層の外側の幅は最大アイランド幅W2と表す(W0<W1<W2)。このようにソース領域とドレイン領域の間においてチャネル形成領域を拡大することで、TFTの電界効果移動度を向上させ、オン電流を大きくすることができる。

【0050】

図1に示すTFTの半導体層はソース領域とドレイン領域の間においてのみチャネル形成領域を拡大したものであるが、図2に示すTFTは、半導体層が拡大された領域をチャネル長方向に拡げたものである。この重なった部分をオフセット領域と呼び、オフセット領域のチャネル長方向の長さをL0と表す。すなわち、図2に示すTFTは、図1に示すTFTに対して、半導体層の拡大領域をチャネル長方向に2L0だけ拡げたものである。

【0051】

図1及び図2に示すTFTは、図5に示す最小アイランド幅W1のTFTよりも電界効果移動度が高く、オン電流が大きい。

【0052】

なお、図1、図2及び図5に示すTFTのオン電流について計算を行うと、図2に示すTFTのオン電流が最も大きく、図5に示すTFTのオン電流が最も小さくなる。

【0053】

ここで、半導体層の拡大領域をチャネル長方向に拡げたTFTにおける電流密度の分布について計算を行った。ここで、ゲート電圧は15Vとし、ドレイン電圧は10Vとした。半導体層のサイズについては、チャネル長方向は50μmとし、チャネル長に垂直な方向はソースドレイン幅W0=10μm、最小アイランド幅W1=20μm、最大アイランド幅W2=30μmとしてオフセット領域のチャネル長方向の長さL0の変化に対する電流密度の分布の変化を調べた。なお、ここで、簡単のために、第1の半導体層106と第2の半導体層108は、単一の非晶質半導体層により設けられているものと仮定して計算を行った。

【0054】

なお、ゲート電圧とは、ソース電極の電位とゲート電極の電位との電位差をいう。ドレイン電圧とは、ソース電極の電位とドレイン電極の電位との電位差をいう。ここで、ゲート電圧及びドレイン電圧は、ソース電極の電位を基準とする。

【0055】

図8は、オフセット領域のチャネル長方向の長さL0を概ね2μmとしたときの電流密度の分布を表す。図9は、オフセット領域のチャネル長方向の長さL0を概ね10μmとしたときの電流密度の分布を示す。図10は、オフセット領域のチャネル長方向の長さL0を概ね16μmとしたときの電流密度の分布を示す。図8ではオフセット領域のチャネル長方向の長さL0の長さが短く、電流密度が高い領域が半導体層の外縁の近傍まで拡がっているため、電流が回り込むための十分な領域を確保することができていない。一方で、図10では、半導体層の外縁の近傍に電流が流れないため、この領域を十分に活用できていない。従って、図9に示すTFTが最適であるといえる。すなわち、半導体層のチャネル長方向の半分程度を拡大領域とすることが好ましい。

【0056】

なお、図7に示すように、上面図におけるゲート電極の形状を半導体層の形状にあわせて加工することで、開口率を向上させることが可能である。

【0057】

なお、図1、図2及び図5に示すTFTでは、第2の半導体層の一部(側面)と配線層が接するため、この接する部分がオフ電流を上昇させる一因となりうる。従って、配線層の少なくとも第2の半導体層と接する部分は、仕事関数の小さい材料により形成することが好ましく、特にイットリア、チタン、または窒化チタンにより形成することが好ましい。

【0058】

なお、上記で参照した図1、図2及び図5に示すTFTは、半導体層の全面がゲート電極と重畳して遮光されているため、光電流による影響が小さい。ただし、これに限定されず、図3、図4及び図6に示すように、必ずしも半導体層の全面がゲート電極と重畳していなくてもよい。

【0059】

図3に示すTFTは、基板200上に第1の配線層202と、第1の半導体層206と、第2の半導体層208と、第1の配線層202と第1の半導体層206の間に接して設けられたゲート絶縁層204と、第2の半導体層208に接して設けられた不純物半導体層210と、不純物半導体層210及び第2の半導体層208に一部が接して設けられた第2の配線層212と、を有するものであって、第1の配線層202により構成されるゲート電極は半導体層の一部と重畳している。そして、図1と同様に、当該TFTは保護層214によって覆われ、保護層214に設けた開口部216を介して第2の配線層212に接続されるように画素電極層218を設けた形態を示す。第2の半導体層208は、第1の半導体層206に接して設けられており、第1の半導体層206よりもキャリア移動度が低い材料により設けるとよい。

【0060】

なお、基板200は、図1における基板100に相当する。第1の配線層202は、図1における第1の配線層102に相当する。ゲート絶縁層204は、図1におけるゲート絶縁層104に相当する。第1の半導体層206は、図1における第1の半導体層106に相当する。第2の半導体層208は、図1における第2の半導体層108に相当する。不純物半導体層210は、図1における不純物半導体層110に相当する。第2の配線層212は、図1における第2の配線層112に相当する。保護層214は、図1における保護層114に相当する。開口部216は、図1における開口部116に相当する。画素電極層218は、図1における画素電極層118に相当する。

【0061】

図3に示すTFTの半導体層はソース領域とドレイン領域の間においてのみチャネル形成領域を拡大したものであるが、図4に示すTFTは、半導体層が拡大された領域をチャネル長方向に拡げたものであり、半導体層が拡大された領域の一部がソース領域及びドレイン領域と重なっている。この重なった部分をオフセット領域と呼び、図2と同様にチャネル長方向にソース領域及びドレイン領域とそれぞれ長さLoだけ重なっている。すなわち、図4に示すTFTは、図3に示すTFTに対して、半導体層の拡大領域をチャネル長方向に2Loだけ拡げたものである。

【0062】

図3及び図4に示すTFTは、図6に示す最小アイランド幅W1のTFTよりも電界効果移動度が高く、オン電流が大きい。

【0063】

なお、図3、図4及び図6に示すTFTを比較すると、図4に示すTFTのオン電流が最も大きく、図6に示すTFTのオン電流が最も小さくなる。

【0064】

ここで、図1に示すTFTの作製方法について図面を参照して説明する。

【0065】

まず、基板100上に第1の配線層102を形成する。基板100は、ここではガラス基板を用いる(図11(A)を参照)。

【0066】

第1の配線層102は、スパッタリング法または真空蒸着法により基板100上に導電層を形成し、該導電層上にフォトリソグラフィ法またはインクジェット法などによりマスクを形成し、該マスクを用いて導電層をエッチングすることで形成することができる(図11(A)を参照)。または、第1の配線層102は、Ag、Au若しくはCuなどの導電性粒子を含むナノペーストを、インクジェット法により基板上に吐出して焼成することで形成することもできる。なお、第1の配線層102と基板100との密着性を向上させ、第1の配線層102を構成する材料の拡散を防ぐバリアメタルとして、上記の金属材料の窒化物層を、基板100と、第1の配線層102との間に設けてもよい。ここでは、基板100上に導電層を形成し、フォトマスクを用いて形成したレジストマスクによりエッチングすることで第1の配線層102を形成する。

【0067】

なお、第1の配線層102上には、後の工程で半導体層及びソース配線(信号線)を形成するため、段差の箇所における配線切れ防止のため側面がテーパーを有するように加工することが好ましい。この工程でゲート配線(走査線)も同時に形成することができる。更には、画素部が有する容量線も形成することができる。なお、走査線とは、画素を選択する配線をいう。

【0068】

次に、第1の配線層102を覆ってゲート絶縁層104を形成し、ゲート絶縁層104上に第1の半導体層106となる第1の半導体膜150、第2の半導体層108となる第2の半導体膜152、及び不純物半導体層110となる不純物半導体膜154を順に積層して形成する(図11(B)を参照)。なお、少なくとも、ゲート絶縁層104となる膜、第1の半導体膜150及び第2の半導体膜152を連続して成膜することが好ましい。更に好ましくは、不純物半導体膜154まで連続して成膜する。少なくとも、ゲート絶縁層104、第1の半導体膜150及び第2の半導体膜152を大気に触れさせることなく連続して成膜することで、大気成分や大気中に浮遊する不純物元素によりこれらの層が汚染されずに、積層膜の各層の界面を形成することができる。そのため、TFTの電気的特性のばらつきを低減することができ、信頼性の高いTFTを歩留まりよく作製することができる。

【0069】

ゲート絶縁層104は、CVD法またはスパッタリング法などを用いて形成することができる。例えば、ゲート絶縁層104は、50nm以上、好ましくは50nm以上400nm以下、より好ましくは150nm以上300nm以下となるように形成する。

【0070】

なお、ゲート絶縁層104の形成後、第1の半導体膜150の成膜前に、密着性を向上させ、または酸化を防止するための層をゲート絶縁層104上に形成してもよい。このような酸化防止などを目的として設けられる層として、例えば、酸化窒化シリコン層を窒化シリコン層により挟んだ積層構造の層が挙げられる。

【0071】

第1の半導体膜150は、ここではプラズマCVD法などを用いて微結晶シリコンにより形成することができる。なお、第1の半導体膜150の厚さは、10nm以上500nm以下とすればよい。微結晶半導体膜の厚さは、例えば、成膜工程におけるシランの流量と成膜時間により調整することができる。そして、成膜時には、酸素または窒素に代表される結晶化を阻害する成分を低減させ、シランなどの堆積性ガスの流量に対する水素などの希釈ガスの流量を大きくするとよい。このとき、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよい。このように形成することで、所謂、微結晶半導体層が形成される。

【0072】

なお、本実施の形態の結晶性半導体層のキャリア移動度は、非晶質半導体層のキャリア移動度の約2倍以上20倍以下である。そのため、結晶性半導体層により形成されるTFTでは、非晶質半導体層を用いたTFTと比較して、Id−Vg曲線における立ち上がり部分の傾きが急峻となる。ここで、Idはドレイン電流であり、Vgはゲート電圧である。なお、ドレイン電流とは、ソース電極とドレイン電極の間に流れる電流をいう。従って、結晶性半導体層をチャネル形成領域に用いたTFTは、スイッチング素子としての応答性に優れ、高速動作が可能である。表示装置のスイッチング素子として、結晶性半導体層をチャネル形成領域に用いたTFTを用いると、チャネル形成領域の面積(即ちTFTの面積)を縮小することもできる。そして、駆動回路の一部または全体を画素部と同じ基板上に一体形成し、システムオンパネルを形成することもできる。

【0073】

ところで、結晶性半導体層は、価電子制御を目的とした不純物元素を添加せずとも弱いn型の電気伝導性を示すことが多い。そのため、TFTのチャネル形成領域として機能する結晶性半導体層には、p型を付与する不純物元素(例えば、ボロン)を成膜と同時に、または成膜した後に添加することで閾値電圧Vthを調整してもよい。p型を付与する不純物元素として例えばボロンがあり、ジボラン(化学式:B2H6)、3フッ化ボロン(化学式:BF3)などの不純物元素を含む気体を1ppm〜1000ppm、好ましくは1〜100ppmの割合で水素化シリコンに含ませることで形成するとよい。そして、結晶性半導体層中のボロンの濃度を、例えば1×1014〜6×1016cm−3とするとよい。

【0074】

なお、第1の半導体膜150を形成する前に、プラズマCVD装置の反応室内を排気しつつ、シリコンまたはゲルマニウムを含む堆積性気体を導入して、反応室内の不純物元素を除去することで、成膜される膜の界面における不純物元素を低減することが可能であり、TFTの電気的特性を向上させることができる。

【0075】

第2の半導体膜152は、第2の半導体層108となるものである。第2の半導体膜152は、プラズマCVD装置の反応室内において、シリコンを含む堆積性気体と水素を混合し、グロー放電プラズマにより形成する。このとき、第1の半導体膜150の成膜条件よりも、シリコンを含む堆積性気体に対する水素の流量を減らして結晶成長を低減する条件で成膜することで、第2の半導体層108の半導体膜における結晶成長が抑制され、オフ電流の低減に寄与するバッファ層を形成することができる。

【0076】

ここで、第2の半導体層108が、従来の非晶質半導体と比較して欠陥が少なく価電子帯のバンド端(移動度端)における準位のテイル(裾)の傾きが急峻である秩序性の高い半導体により形成される場合について説明する。このような半導体層は、上記した結晶性半導体膜の形成ガス中に窒素を含むガスを混合させ、好ましくは第1の半導体膜150の成膜条件よりも堆積性気体に対する水素の流量比を小さくし、プラズマCVD法を用いることで、第2の半導体膜152における結晶成長が抑制されることで形成される。このとき、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよい。

【0077】

なお、第2の半導体膜152の成膜初期には、第1の半導体膜150の成膜条件よりもシリコンを含む堆積性気体に対する水素の流量を減らすことで、第2の半導体層108に微結晶半導体領域を残存させることができる。または、上記条件よりも、シリコンを含む堆積性気体に対する水素の流量を更に減らしていくことで、第2の半導体層108を、非晶質半導体を含む層とすることができる。または、上記条件よりも、シリコンを含む堆積性気体に対する水素の流量を更に減らし、且つ窒素を含むガスを混合させることで、第2の半導体層108の非晶質半導体領域を大きく形成することができる。

【0078】

なお、第2の半導体膜152の成膜初期においては、第1の半導体膜150を種結晶として、全体に膜が堆積される。その後は部分的に結晶成長が抑制され、錐状の微結晶半導体領域が成長する(成膜中期)。さらに、錐状の微結晶半導体領域の結晶成長が抑制され、上側に微結晶半導体領域を含まない第2の半導体膜152が形成される(成膜後期)。

【0079】

不純物半導体層110は、不純物半導体膜154を形成し、これをエッチングして形成することができる。不純物半導体層110として導電型がn型のTFTを形成する場合には、材料ガス中に、例えば不純物元素としてリンを添加すればよく、例えば水素化シリコンにフォスフィンを含む気体を加えることで形成することができる。または、導電型がp型のTFTを形成する場合には、材料ガス中に、例えば不純物元素としてボロンを添加すればよく、例えば水素化シリコンにジボランを含む気体を加えることで形成することができる。不純物半導体層110は、結晶性半導体または非晶質半導体のどちらで形成してもよいが、好ましくは結晶性半導体により形成する。不純物半導体層110は第2の半導体層108と第2の配線層112とがオーミック接触できる厚さとすればよく、概ね2nm以上60nm以下の厚さで形成するとよい。不純物半導体層110を可能な範囲で薄くすると、スループットを向上させることができる。なお、不純物半導体層110を結晶性半導体により形成する場合には、酸素または窒素に代表される結晶化を阻害する成分を低減させ、シランなどの堆積性ガスの流量に対する水素などの希釈ガスの流量を大きくすることで形成することができる。このとき、不純物半導体層110を非晶質半導体により形成する場合には、堆積性ガスの流量に対する希釈ガスの流量を1倍以上10倍以下、好ましくは1倍以上5倍以下とすればよいが、結晶性半導体により形成する場合には、堆積性ガスの流量に対する希釈ガスの流量を10倍以上2000倍以下、好ましくは50倍以上200倍以下とすればよい。このように形成することで、所謂、微結晶半導体層が形成される。

【0080】

なお、上述したように、ゲート絶縁層104から不純物半導体膜154までは連続して成膜することが好ましい(図11(B)を参照)。マルチチャンバーのCVD装置を用いると、堆積する膜の種類毎に反応室を配することが可能であり、複数の異なる種類の膜を大気に触れさせることなく連続して成膜することができる。

【0081】

図14は、複数の反応室を備えたマルチ・チャンバー・プラズマCVD装置の一例の上断面を示す模式図である。この装置は、共通室272、ロード/アンロード室270、第1反応室250a、第2反応室250b、第3反応室250c及び第4反応室250dを備えている。ロード/アンロード室270のカセットに基板100が装填されると、共通室272の搬送機構276によって各反応室に基板100が搬出入される。共通室272と各反応室及びロード/アンロード室との間にはゲートバルブ274が備えられ、各反応室で行われる処理が互いに干渉しないように構成されている。各反応室は成膜する薄膜の種類に応じて使い分けることができる。例えば、第1反応室250aでは絶縁膜を成膜し、第2反応室250b及び第4反応室250dでは半導体膜を成膜し、第3反応室250cでは一導電型を付与する不純物元素が添加された半導体膜を成膜する。それぞれの薄膜は最適な成膜温度が異なるので、反応室を分けておくことで成膜温度の管理が容易となり、各薄膜を最適な温度で成膜することができる。さらに、同じ膜種を繰り返し成膜することができるので、成膜履歴に係る残留物の影響を排除することができる。なお、一の反応室で一の膜を成膜する構成としてもよいし、結晶性半導体膜と非晶質半導体膜のように、一の反応室で複数の膜を成膜する構成としてもよい。

【0082】

各反応室には、排気手段としてターボ分子ポンプ264とドライポンプ266が接続されている。排気手段はこれらの真空ポンプの組み合わせに限定されるものではなく、概略10−5Paから10−1Paの真空度まで排気できるものであれば他の真空ポンプを用いてもよい。ただし、第2反応室250bでは、反応室内の圧力を概略10−5Pa以下まで到達させることができるようにクライオポンプ268が接続されていることが好ましい。これらの排気手段と各反応室との間にはバタフライバルブ260及びコンダクタンスバルブ262の一方または双方が設けられている。バタフライバルブ260を用いることで排気手段と反応室を遮断することができる。そして、コンダクタンスバルブ262を用いることで排気速度を調整し、各反応室の圧力を調節することができる。

【0083】

なお、第2反応室250bに接続されているクライオポンプ268を用いることで、反応室内の圧力を10−5Paよりも低い圧力(望ましくは超高真空)とすることも可能である。本実施の形態では、第2反応室250b内を10−5Paよりも低い圧力にすることで、半導体膜中への酸素などの大気成分の混入を防止することができる。その結果、半導体膜に含まれる酸素濃度を1×1016cm−3以下とすることができる。

【0084】

ガス供給手段258は、成膜ガスが充填されているシリンダ、ストップバルブ及びマスフローコントローラなどで構成されている。ガス供給手段258aは第1反応室250aに接続され、絶縁膜を成膜するためのガスを供給する。ガス供給手段258bは第2反応室250bに接続され、半導体膜を成膜するためのガスを供給する。ガス供給手段258cは第3反応室250cに接続され、例えばn型の導電型を付与する不純物元素が添加された半導体材料ガスを供給する。ガス供給手段258dは第4反応室250dに接続され、半導体膜を成膜するためのガスを供給する。ガス供給手段258eはArを供給する。ガス供給手段258fは反応室内のクリーニングに用いるエッチングガス(ここではNF3ガス)を供給する。Arガスとクリーニングに用いるエッチングガスはすべての反応室において用いられるため、ガス供給手段258eとガス供給手段258fはすべての反応室に接続されていることが好ましい。

【0085】

なお、各反応室にはプラズマを生成するための高周波電力供給手段が連結されている。ここで、高周波電力供給手段には高周波電源252と整合器254が含まれる。ただし、これに限定されず、マイクロ波発生部が接続されていてもよい。発生させるプラズマとしては、例えばRFプラズマ、VHFプラズマ、マイクロ波プラズマが挙げられる。なお、RFプラズマとVHFプラズマを同時に発生させる(2周波励起させる)ことで堆積率が向上するため好ましい。

【0086】

なお、ここで用いるプラズマはパルス変調プラズマであることが好ましい。パルス変調プラズマを用いることで、成膜時の堆積率が向上し、成膜時に発生するパーティクルを低減し、成膜される半導体膜の膜質及び厚さの均一性を向上させることができる。更には、プラズマ発生時の紫外線量を低減することができ、成膜される半導体膜中の欠陥数を低減することができる。

【0087】

なお、同一の反応室内において、結晶性半導体膜、非晶質半導体膜、及び一導電型を付与する不純物元素が添加された不純物半導体膜を連続して成膜してもよい。具体的には、ゲート絶縁膜が形成された基板を反応室内に搬入し、そこで結晶性半導体膜、非晶質半導体膜、及び一導電型を付与する不純物元素が添加された半導体膜(不純物半導体膜)を連続して成膜する。同一の反応室内で結晶性半導体膜及び非晶質半導体膜を連続して成膜することで、結晶歪の少ない界面を形成することが可能である。そのため、界面に意図しない準位が形成されることを防ぐことができる。そして、界面に混入しうる大気成分を低減することができる。

【0088】

なお、図示しないが、図14に示すマルチ・チャンバー・プラズマCVD装置には予備室が連結されていてもよい。成膜前に予備室で基板を加熱しておくと、各反応室における成膜までの加熱時間を短縮することが可能であり、スループットを向上させることができる。

【0089】

なお、上記説明したように連続して成膜することで、汚染源となりうる不純物元素によって界面が汚染されることなく、複数の膜を積層して形成することができる。そのため、TFTの電気的特性のばらつきを低減することができる。

【0090】

上記に示すプラズマCVD装置を用いることで、各反応室で一種類の膜または組成の類似する複数種の膜を成膜することが可能であり、且つ大気に曝すことなく連続成膜することができる。そのため、既に成膜した膜の残留物及び大気に浮遊する不純物元素によって界面が汚染されることなく、複数の膜を積層して形成することができる。

【0091】

プラズマCVD装置の反応室内は、フッ素ラジカルでクリーニングするとよい。そして、成膜前に反応室内に保護膜を成膜することが好ましい。

【0092】

なお、用いることのできる装置は上記の図14に示すものに限定されない。例えば、二の反応室が設けられたCVD装置を用いてもよい。このとき、一方の反応室(第1反応室)は、形成ガスに珪酸エチル(TEOS:化学式Si(OC2H5)4)を用いた酸化シリコン膜の形成に用いる反応室とし、他方の反応室(第2の反応室)は、窒化シリコン膜、シリコン膜及び一導電型の不純物元素を含むシリコン膜の形成に用いる反応室とすればよい。または、前記第2の反応室のみを有する装置を用いてもよい。

【0093】

次に、不純物半導体層110となる不純物半導体膜154上にレジストマスク156を形成する(図11(C)を参照)。レジストマスク156は、フォトリソグラフィ法により形成することができる。または、インクジェット法などにより形成してもよい。または、コスト低減を目的として、印刷法により形成してもよいし、印刷法により形成した後にレーザー加工を行ってもよい。

【0094】

次に、レジストマスク156を用いて、第1の半導体膜150、第2の半導体膜152、及び不純物半導体膜154をエッチングする。この処理により、これらの膜を素子毎に分離して、第1の半導体層106、第2の半導体層158及び不純物半導体層160を形成する(図12(A)を参照)。その後、レジストマスク156を除去する。

【0095】

なお、このエッチング処理では、第1の半導体層106、第2の半導体層158及び不純物半導体層160が積層された積層体162がテーパー形状となるようにエッチングを行うことが好ましい。テーパー角は30°以上90°以下、好ましくは40°以上80°以下とする。積層体162をテーパー形状とすることで、後の工程でこれらの上に形成される層(例えば、導電膜164)の被覆性を向上させることができ、配線切れなどを防止することができる。

【0096】

次に、積層体162上に導電膜164を形成する(図12(B)を参照)。導電膜164は、スパッタリング法または真空蒸着法などを用いて形成すればよい。または、導電膜164は、Ag、AuまたはCuなどの導電性ナノペーストを用いてスクリーン印刷法またはインクジェット法などを用いて吐出し、焼成することで形成してもよい。

【0097】

次に、導電膜164上にレジストマスク166を形成する(図12(C)を参照)。レジストマスク166は、レジストマスク156と同様にフォトリソグラフィ法またはインクジェット法により形成することができる。または、コスト低減を目的として、印刷法により形成してもよいし、印刷法により形成した後にレーザー加工を行ってもよい。または、レジストマスクのサイズを調整するために酸素プラズマによるアッシングを行ってもよい。

【0098】

次に、レジストマスク166を用いて導電膜164をエッチングし、導電膜164をパターン形成して第2の配線層112を形成する。エッチングにはウエットエッチングを用いることが好ましい。ウエットエッチングにより、導電膜164のうち、レジストマスク166から露出された部分が等方的にエッチングされる。その結果、導電膜はレジストマスク166の側面よりも内側まで後退し、第2の配線層112が形成される。この第2の配線層112はTFTのソース電極及びドレイン電極のみならず、信号線も構成する。

【0099】

次に、レジストマスク166が形成された状態で、第2の半導体層158及び不純物半導体層160をエッチングしてバックチャネル部を形成する。これにより、第2の半導体層158は一部を残してエッチングされ、第2の半導体層108及び不純物半導体層110が形成される。

【0100】

ここで、エッチングはドライエッチングにより行うとよく、特に、酸素を含んだガスによるドライエッチングを行うとよい。酸素を含んだガスにより、レジストを後退させつつ不純物半導体層110と第2の半導体層108をエッチングすることができ、不純物半導体層110と、第2の半導体層108をテーパー形状にすることができるからである。エッチングガスとしては、例えば、4フッ化メタン(化学式:CF4)に酸素を含ませたエッチングガスまたは塩素に酸素を含ませたエッチングガスを用いる。不純物半導体層110と、第2の半導体層108をテーパー形状にすることで電界の集中を防ぎ、オフ電流を低減させることができる。

【0101】

第2の半導体層108では、一部がエッチングされて凹部が設けられているが、凹部と重畳する第2の半導体層108の少なくとも一部が残存する厚さとすることが好ましい。不純物半導体層110と重畳する部分の第2の半導体層108は、ソース領域及びドレイン領域の形成プロセスにおいてエッチングされないが、この部分の厚さは概ね80nm以上500nm以下とするとよく、好ましくは150nm以上400nm以下であり、更に好ましくは200nm以上300nm以下である。上記のように、第2の半導体層108を十分に厚くすることで、第1の半導体層106への不純物元素の混入などを防止することができる。このように、第2の半導体層108は、第1の半導体層106の保護層としても機能する。

【0102】

次に、レジストマスク166を除去する。

【0103】

なお、ここまでの工程により生じた、バックチャネル部に存在する残渣及びレジストマスク166の除去に用いたレジスト剥離液の成分などは電気的特性に影響を与えることが多い。そのため、これらを除去することを目的として、レジストマスク166を除去した後に、更なるエッチング、プラズマ処理及び洗浄のいずれか一または複数の工程を用いることで、電気的特性が良好な(例えば、オフ電流が小さい)TFTを作製することができる。

【0104】

以上の工程により、図1に示すボトムゲート型のTFTを形成することができる(図13(A)を参照)。なお、図2乃至図7に示すボトムゲート型のTFTについても作製工程は上記と同様である。

【0105】

次に、上記のように作製したTFTを覆って保護層114を形成する(図13(B)を参照)。保護層114は、ゲート絶縁層104と同様に形成することができる。

【0106】

なお、図1に示すTFTは画素トランジスタとして用いることができるため、ソース電極及びドレイン電極の一方が画素電極に接続されている。図1に示すTFTにおいては、ソース電極及びドレイン電極の一方が、保護層114に設けられた開口部116を介して画素電極層118に接続されている。

【0107】

画素電極層118は、スパッタリング法などを用いて形成することができる。ここでは、ITOをスパッタリング法により形成すればよい。

【0108】

画素電極層118は、第2の配線層112などと同様に、全面に形成した後にレジストマスクなどを用いてエッチングを行い、パターン形成すればよい(図13(C)を参照)。

【0109】

なお、図示していないが、保護層114と画素電極層118との間に、画素電極層118の被形成面の平坦化を目的として、スピンコーティング法などにより有機樹脂層を形成してもよい。

【0110】

なお、上記した説明では、ゲート電極と走査線とが同一の工程で形成され、ソース電極及びドレイン電極と信号線とが同一の工程で形成される場合について説明したが、開示する発明はこれに限定されない。電極と、該電極に接続される配線を別工程により形成してもよい。

【0111】

なお、本実施の形態では、半導体材料としてシリコンを用いた場合について説明したが、これに限定されず、酸化物半導体を用いてもよいし、有機半導体を用いてもよい。

【0112】

なお、本実施の形態では逆スタガ型のTFTについて説明したが、これに限定されず、コプラナ型であってもよい。

【0113】

なお、本実施の形態では半導体材料としてシリコンを用いたが、これに限定されず、ゲルマニウムを用いてもよい。シランに代えて、GeH4、Ge2H6などの堆積性気体を用いればよい。

【0114】

なお、上記説明に限定されず、TFTはU字型(コの字型または馬蹄型)であってもよい。図15は、U字型のTFTを示す。

【0115】

なお、断面構造は、図1に示すものと同様である。基板300は、図1における基板100に相当する。第1の配線層302は、図1における第1の配線層102に相当する。ゲート絶縁層304は、図1におけるゲート絶縁層104に相当する。第1の半導体層306は、図1における第1の半導体層106に相当する。第2の半導体層308は、図1における第2の半導体層108に相当する。不純物半導体層310は、図1における不純物半導体層110に相当する。第2の配線層312は、図1における第2の配線層112に相当する。保護層314は、図1における保護層114に相当する。開口部316は、図1における開口部116に相当する。画素電極層318は、図1における画素電極層118に相当する。なお、図15(A)及び(B)においても、図1と同様に走査線と信号線の間に半導体層が設けられているが、図15(A)及び(B)では、走査線の一部が細く加工され、走査線と信号線の間の寄生容量が更に低減されている。

【0116】

TFTを図15(A)に示す形状とすることで、該TFTの最大アイランド幅を拡大することができ、オン電流を大きくすることができる。更には、電気的特性のばらつきを低減することができる。この場合には点線で囲まれた領域に電流が回り込むため、オン電流を大きくすることができる。

【0117】

または、TFTを図15(B)に示す形状としてもよい。この場合にも点線で囲まれた領域を電流が回り込むため、オン電流を大きくすることができる。更には、第1の配線層により構成されるゲート電極の占有面積を縮小することができるため、開口率を向上させることができる。

【0118】

以上、本実施の形態にて説明したように、半導体層のアイランド幅を部分的に拡大することで、第1の配線層と第2の配線層の間の寄生容量を増加させることなくオン電流を大きくすることができる。そのため、本実施の形態のTFTを画素TFTに適用すると、画素を高速動作させることができる。または、半導体層の最大アイランド幅を変えることなくソースドレイン幅を狭くすることができるため、第1の配線層と第2の配線層の間の寄生容量を低減させることができる。そのため、本実施の形態のTFTを画素TFTに適用すると、配線遅延を抑制し、画素を高速動作させることができる。

【0119】

(実施の形態2)

本実施の形態では、実施の形態1にて説明したTFTを搭載した表示パネルまたは発光パネルの一形態について、図面を参照して説明する。

【0120】

本実施の形態の表示装置または発光装置では、画素部に接続される信号線駆動回路及び走査線駆動回路は別の基板(例えば、半導体基板またはSOI基板など)上に設けて接続してもよいし、画素回路と同一基板上に形成してもよい。

【0121】

なお、別途形成した場合の接続方法は特に限定されるものではなく、公知のCOG法、ワイヤボンディング法またはTAB法などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、特に限定されない。または、コントローラ、CPU及びメモリなどを別途形成し、画素回路に接続してもよい。

【0122】

図16は、表示装置のブロック図を示す。図16に示す表示装置は、表示素子を備えた画素を複数有する画素部400と、各画素を選択する走査線駆動回路402と、選択された画素へのビデオ信号の入力を制御する信号線駆動回路403と、を有する。

【0123】

なお、開示する発明の一である表示装置は図16に示す形態に限定されない。すなわち、信号線駆動回路は、シフトレジスタとアナログスイッチのみを有する形態に限定されない。シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワなど、他の回路を有していてもよい。なお、シフトレジスタ及びアナログスイッチは必ずしも設ける必要はなく、例えば、シフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を有していてもよいし、アナログスイッチの代わりにラッチなどを有していてもよい。

【0124】

図16に示す信号線駆動回路403は、シフトレジスタ404及びアナログスイッチ405を有する。シフトレジスタ404には、クロック信号(CLK)とスタートパルス信号(SP)とが入力されている。クロック信号(CLK)とスタートパルス信号(SP)とが入力されると、シフトレジスタ404においてタイミング信号が生成され、アナログスイッチ405に入力される。

【0125】

なお、アナログスイッチ405には、ビデオ信号(video signal)が供給される。アナログスイッチ405は、入力されるタイミング信号に従ってビデオ信号をサンプリングし、後段の信号線に供給する。

【0126】

図16に示す走査線駆動回路402は、シフトレジスタ406及びバッファ407を有する。更には、レベルシフタを有していてもよい。走査線駆動回路402において、シフトレジスタ406にクロック信号(CLK)及びスタートパルス信号(SP)が入力されることによって、選択信号が生成される。生成された選択信号はバッファ407において緩衝増幅され、対応する走査線に供給される。一の走査線には、1ラインのすべての画素トランジスタのゲートが接続されている。そして、動作時には1ライン分の画素トランジスタを一斉にオンにしなくてはならないので、バッファ407は大きな電流を流すことが可能な構成とする。

【0127】

フルカラーの表示装置において、R(赤)、G(緑)、B(青)に対応するビデオ信号を、順にサンプリングして対応する信号線に供給する場合、シフトレジスタ404とアナログスイッチ405とを接続するための端子数は、アナログスイッチ405と画素部400の信号線を接続するための端子数の1/3程度に相当する。よって、アナログスイッチ405を画素部400と同一基板上に形成することで、アナログスイッチ405を画素部400と異なる基板上に形成した場合に比べて、別途形成した基板の接続に用いる端子の数を抑えることができ、接続不良の発生確率を抑えて歩留まりを高めることができる。

【0128】

なお、図16の走査線駆動回路402は、シフトレジスタ406及びバッファ407を有するが、これに限定されず、シフトレジスタ406のみで走査線駆動回路402を構成してもよい。

【0129】

なお、図16に示す構成は、表示装置の一形態を示したものであり、信号線駆動回路と走査線駆動回路の構成はこれに限定されない。

【0130】

次に、表示装置の一形態に相当する液晶表示パネル及び発光パネルの外観について、図17及び図18を参照して説明する。図17(A)は、第1の基板411上に形成された結晶性半導体層を有するTFT420及び液晶素子423を、第2の基板416との間にシール材415によって封止した、パネルの上面図を示す。図17(B)は、図17(A)のK−Lにおける断面図に相当する。図18は発光装置の場合を示す。なお、図18は、図17と異なる部分についてのみ符号を付している。

【0131】

第1の基板411上に設けられた画素部412と、走査線駆動回路414と、を囲んで、シール材415が設けられている。そして、画素部412及び走査線駆動回路414の上に第2の基板416が設けられている。よって画素部412及び走査線駆動回路414は、第1の基板411とシール材415と第2の基板416とによって、液晶層418または充填材431と共に封止されている。そして、第1の基板411上のシール材415によって囲まれている領域とは異なる領域に信号線駆動回路413が実装されている。なお、信号線駆動回路413は、別途用意された基板上に結晶性半導体層を有するTFTにより設けられたものである。なお、本実施の形態では、結晶性半導体層を有するTFTを用いた信号線駆動回路413を、第1の基板411に貼り合わせる場合について説明するが、単結晶半導体を用いたTFTで信号線駆動回路を形成し、貼り合わせることが好ましい。図17では、信号線駆動回路413に含まれる、結晶性半導体層で形成されたTFT419を例示する。

【0132】

第1の基板411上に設けられた画素部412は、複数のTFTを有しており、図17(B)には、画素部412に含まれるTFT420を例示している。なお、本実施の形態の発光装置においては、TFT420は駆動用トランジスタであってもよいし、電流制御用トランジスタであってもよいし、消去用トランジスタであってもよい。TFT420は実施の形態1で説明した結晶性半導体層を用いたTFTに相当する。

【0133】

液晶素子423が有する画素電極422は、TFT420と配線428を介して電気的に接続されている。そして、液晶素子423の対向電極427は第2の基板416上に設けられている。画素電極422と対向電極427と液晶層418が重なっている部分が、液晶素子423に相当する。

【0134】

発光素子430が有する画素電極は、TFT420のソース電極またはドレイン電極と、配線を介して電気的に接続されている。そして本実施の形態では、発光素子430の共通電極と透光性を有する導電性材料層が電気的に接続されている。なお、発光素子430の構成は、本実施の形態に示した構成に限定されない。発光素子430の構成は、発光素子430から取り出す光の方向や、TFT420の極性などに応じて決定することができる。

【0135】

なお、第1の基板411及び第2の基板416の材料としては、ガラス、金属(例えばステンレス)、セラミックスまたはプラスチックなどを用いることができる。プラスチックとしては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルム、またはアクリル樹脂フィルムなどを用いることができる。または、アルミニウム箔をPVFフィルムやポリエステルフィルムで挟んだ構造のシートを用いてもよい。

【0136】

なお、スペーサ421はビーズスペーサであり、画素電極422と対向電極427との間に一定の距離(セルギャップ)を確保するために設けられている。なお、絶縁層を選択的にエッチングすることで得られるスペーサ(ポストスペーサ)を用いていてもよい。

【0137】

なお、別途形成された信号線駆動回路413と、走査線駆動回路414及び画素部412に与えられる各種の信号(電位)は、FPC417(Flexible Printed Circuit)から引き回し配線424及び引き回し配線425を介して供給される。

【0138】

本実施の形態では、接続端子426が、液晶素子423が有する画素電極422と同じ導電層から形成されている。そして、引き回し配線424及び引き回し配線425は、配線428と同じ導電層で形成されている。

【0139】

接続端子426とFPC417が有する端子は、異方性導電層429を介して電気的に接続されている。

【0140】

なお、図示していないが、本実施の形態に示した液晶表示装置は、配向膜及び偏光板を有し、更にカラーフィルタや遮光層などを有していてもよい。

【0141】

なお、発光素子430からの光の取り出し方向に位置する基板である第2の基板は透光性の基板を用いる。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムなどの透光性を有する材料からなる基板を用いる。発光素子430からの光の取り出し方向が第1の基板の方向である場合には、第1の基板として透光性基板を用いる。

【0142】

なお、充填材431としては、窒素やArなどの不活性な気体、紫外線硬化樹脂または熱硬化樹脂などを用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラール)またはEVA(エチレンビニルアセテート)などを用いることができる。ここでは、例えば、窒素を用いるとよい。

【0143】

なお、発光素子の射出面に偏光板、円偏光板(楕円偏光板を含む)、位相差板(λ/4板、λ/2板)またはカラーフィルタなどの光学フィルムを適宜設けてもよい。更には、偏光板または円偏光板に反射防止層を設けてもよい。

【0144】

(実施の形態3)

本実施の形態は、実施の形態2にて説明した方法により作製した表示パネルまたは表示装置を表示部として組み込んだ電子機器について図19乃至図21を参照して説明する。このような電子機器としては、例えば、ビデオカメラ若しくはデジタルカメラなどのカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍など)が挙げられる。それらの一例を図19に示す。

【0145】

図19(A)はテレビジョン装置を示す。表示パネルを筐体に組み込むことで、図19(A)に示すテレビジョン装置を完成させることができる。実施の形態2にて説明した作製方法を適用した表示パネルにより主画面503が形成され、その他付属設備としてスピーカ部509、操作スイッチなどが備えられている。

【0146】

図19(A)に示すように、筐体501に実施の形態2にて説明した作製方法を適用した表示用パネル502が組み込まれ、受信機505により一般のテレビ放送の受信をはじめ、モデム504を介して有線または無線による通信ネットワークに接続することにより片方向(送信者から受信者)または双方向(送信者と受信者間、または受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチまたはリモコン操作機506により行うことが可能であり、このリモコン操作機506にも、出力する情報を表示する表示部507が設けられていてもよい。

【0147】

なお、テレビジョン装置にも、主画面503の他にサブ画面508を第2の表示パネルで形成し、チャンネルや音量などを表示する構成が付加されていてもよい。

【0148】

図20は、テレビジョン装置の主要な構成を示すブロック図を示している。表示パネル520には、画素部521が形成されている。信号線駆動回路522と走査線駆動回路523は、表示パネル520にCOG方式により実装されていてもよい。

【0149】

その他の外部回路の構成として、映像信号の入力側では、チューナ524で受信した信号のうち、映像信号を増幅する映像信号増幅回路525と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路526と、その映像信号を適切な入力仕様に変換するためのコントロール回路527などを有している。コントロール回路527は、走査線駆動回路523と信号線駆動回路522にそれぞれ信号を出力する。デジタル駆動する場合には、信号線側に信号分割回路528を設け、入力デジタル信号を整数個に分割して供給する構成としてもよい。

【0150】

チューナ524で受信した信号のうち、音声信号は、音声信号増幅回路529に送られ、その出力は音声信号処理回路530を経てスピーカ533に供給される。制御回路531は受信局(受信周波数)、音量の制御信号を入力部532から受け、チューナ524及び音声信号処理回路530に信号を送出する。

【0151】

勿論、本発明の一形態である表示装置はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤、または街頭における広告表示盤などの大面積の表示媒体にも適用することができる。そのため、これらの表示媒体の表示品質を向上させることができる。

【0152】

主画面503及びサブ画面508の一方または双方に、実施の形態2で説明した作製方法を適用した表示パネルまたは表示装置を用いることで、テレビ装置の表示品質を高めることができる。

【0153】

図19(B)に示す携帯型のコンピュータは、本体511及び表示部512などを有する。表示部512に、実施の形態2で説明した表示装置の作製方法を適用した表示パネルまたは表示装置を用いることで、コンピュータの表示部の表示品質を高めることができる。

【0154】

図21は、携帯電話の一例を示し、図21(A)が正面図、図21(B)が背面図、図21(C)が2つの筐体をスライドさせたときの正面図である。図21に示す携帯電話は、筐体541及び筐体542二つの筐体で構成されている。図21に示す携帯電話は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能な所謂スマートフォンである。

【0155】

筐体541は、表示部543、スピーカ544、マイクロフォン545、操作キー546、ポインティングデバイス547、表面カメラ用レンズ548、外部接続端子ジャック549及びイヤホン端子550などを備え、筐体542は、キーボード551、外部メモリスロット552、裏面カメラ553、ライト554などにより構成されている。アンテナは筐体541に内蔵されている。

【0156】

なお、図21に示す携帯電話は、上記の構成に加えて、非接触型ICチップ、小型記録装置などを内蔵していてもよい。

【0157】

重なり合った筐体541と筐体542(図21(A)に示す。)は、スライドさせることが可能であり、スライドさせることで図21(C)のように展開する。表示部543には、実施の形態2で説明した表示装置の作製方法を適用した表示パネルまたは表示装置を組み込むことが可能である。なお、表示部543と表面カメラ用レンズ548を同一の面に備えているため、テレビ電話としての使用が可能である。更には、表示部543をファインダーとして用いることで、裏面カメラ553及びライト554で静止画及び動画の撮影が可能である。

【0158】

スピーカ544及びマイクロフォン545を用いることで、図21に示す携帯電話は、音声記録装置(録音装置)または音声再生装置として使用することができる。または、操作キー546により、電話の発着信操作、電子メールなどの簡単な情報入力操作、表示部に表示する画面のスクロール操作、表示部に表示する情報の選択などを行うカーソルの移動操作などが可能である。

【0159】

なお、書類の作成、携帯情報端末としての使用など、取り扱う情報が多い場合は、キーボード551を用いると便利である。更に、重なり合った筐体541と筐体542(図21(A)を参照)をスライドさせることで、図21(C)のように展開させることができる。携帯情報端末として使用する場合には、キーボード551及びポインティングデバイス547を用いて、円滑な操作でマウスの操作が可能である。外部接続端子ジャック549はACアダプタ及びUSBケーブルなどの各種ケーブルと接続可能であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。なお、外部メモリスロット552に記録媒体を挿入することで、より大量のデータ保存及び移動が可能になる。

【0160】

筐体542の裏面(図21(B)を参照)には、裏面カメラ553及びライト554を備え、表示部543をファインダーとして静止画及び動画の撮影が可能である。

【0161】

なお、上記の機能構成に加えて、赤外線通信機能、USBポート、テレビワンセグ受信機能、非接触ICチップまたはイヤホンジャックなどを備えたものであってもよい。

【0162】

本実施の形態にて説明した各種電子機器は、実施の形態1にて説明したTFT及び実施の形態2にて説明した表示装置の作製方法を適用して作製することができる。従って、作製コストを増大させることなく、表示部の表示品質の高い電子機器を作製することができる。

【符号の説明】

【0163】

100 基板

102 第1の配線層

104 ゲート絶縁層

106 第1の半導体層

108 第2の半導体層

110 不純物半導体層

112 第2の配線層

114 保護層

116 開口部

118 画素電極層

150 第1の半導体膜

152 第2の半導体膜

154 不純物半導体膜

156 レジストマスク

158 第2の半導体層

160 不純物半導体層

162 積層体

164 導電膜

166 レジストマスク

200 基板

202 第1の配線層

204 ゲート絶縁層

206 第1の半導体層

208 第2の半導体層

210 不純物半導体層

212 第2の配線層

214 保護層

216 開口部

218 画素電極層

250a 第1反応室

250b 第2反応室

250c 第3反応室

250d 第4反応室

252 高周波電源

254 整合器

258 ガス供給手段

258a ガス供給手段

258b ガス供給手段

258c ガス供給手段

258d ガス供給手段

258e ガス供給手段

258f ガス供給手段

260 バタフライバルブ

262 コンダクタンスバルブ

264 ターボ分子ポンプ

266 ドライポンプ

268 クライオポンプ

270 ロード/アンロード室

272 共通室

274 ゲートバルブ

276 搬送機構

300 基板

302 第1の配線層

304 ゲート絶縁層

306 第1の半導体層

308 第2の半導体層

310 不純物半導体層

312 第2の配線層

314 保護層

316 開口部

318 画素電極層

400 画素部

402 走査線駆動回路

403 信号線駆動回路

404 シフトレジスタ

405 アナログスイッチ

406 シフトレジスタ

407 バッファ

411 基板

412 画素部

413 信号線駆動回路

414 走査線駆動回路

415 シール材

416 基板

417 FPC

418 液晶層

419 TFT

420 TFT

421 スペーサ

422 画素電極

423 液晶素子

424 配線

425 配線

426 接続端子

427 対向電極

428 配線

429 異方性導電層

430 発光素子

431 充填材

501 筐体

502 表示用パネル

503 主画面

504 モデム

505 受信機

506 リモコン操作機

507 表示部

508 サブ画面

509 スピーカ部

511 本体

512 表示部

520 表示パネル

521 画素部

522 信号線駆動回路

523 走査線駆動回路

524 チューナ

525 映像信号増幅回路

526 映像信号処理回路

527 コントロール回路

528 信号分割回路

529 音声信号増幅回路

530 音声信号処理回路

531 制御回路

532 入力部

533 スピーカ

541 筐体

542 筐体

543 表示部

544 スピーカ

545 マイクロフォン

546 操作キー

547 ポインティングデバイス

548 表面カメラ用レンズ

549 外部接続端子ジャック

550 イヤホン端子

551 キーボード

552 外部メモリスロット

553 裏面カメラ

554 ライト

【特許請求の範囲】

【請求項1】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されていることを特徴とする薄膜トランジスタ。

【請求項2】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大されていることを特徴とする薄膜トランジスタ。

【請求項3】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、

前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短いことを特徴とする薄膜トランジスタ。

【請求項4】

請求項1乃至請求項3のいずれか一において、

前記半導体層は、結晶性半導体層と非晶質を含む半導体層が積層して設けられ、

前記結晶性半導体層が有する結晶粒は、前記非晶質を含む半導体層に延びた錐状の結晶粒であることを特徴とする薄膜トランジスタ。

【請求項5】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大され、

前記ソース領域と前記ドレイン領域上には第2の配線層が設けられ、該第2の配線層には選択的に形成された画素電極層が接続されていることを特徴とする表示装置。

【請求項6】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大され、

前記ソース領域と前記ドレイン領域上には第2の配線層が設けられ、該第2の配線層には選択的に形成された画素電極層が接続されていることを特徴とする表示装置。

【請求項7】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、

前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短く、

前記ソース領域と前記ドレイン領域上には第2の配線層が設けられ、該第2の配線層には選択的に形成された画素電極層が接続されていることを特徴とする表示装置。

【請求項8】

請求項5乃至請求項7のいずれか一において、

前記半導体層は、結晶性半導体層と非晶質を含む半導体層が積層して設けられ、

前記結晶性半導体層が有する結晶粒は、前記非晶質を含む半導体層に延びた錐状の結晶粒であることを特徴とする表示装置。

【請求項1】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されていることを特徴とする薄膜トランジスタ。

【請求項2】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大されていることを特徴とする薄膜トランジスタ。

【請求項3】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、

前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短いことを特徴とする薄膜トランジスタ。

【請求項4】

請求項1乃至請求項3のいずれか一において、

前記半導体層は、結晶性半導体層と非晶質を含む半導体層が積層して設けられ、

前記結晶性半導体層が有する結晶粒は、前記非晶質を含む半導体層に延びた錐状の結晶粒であることを特徴とする薄膜トランジスタ。

【請求項5】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大され、

前記ソース領域と前記ドレイン領域上には第2の配線層が設けられ、該第2の配線層には選択的に形成された画素電極層が接続されていることを特徴とする表示装置。

【請求項6】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、前記ソース領域と前記ドレイン領域の間においてのみ拡大され、

前記ソース領域と前記ドレイン領域上には第2の配線層が設けられ、該第2の配線層には選択的に形成された画素電極層が接続されていることを特徴とする表示装置。

【請求項7】

第1の配線層と、

前記第1の配線層を覆って設けられたゲート絶縁層と、

前記ゲート絶縁層上に、前記第1の配線層と重畳して設けられた半導体層と、

前記半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、

前記不純物半導体層上に設けられた第2の配線層と、を有し、

前記ソース領域及び前記ドレイン領域の幅は、前記半導体層の幅よりも狭く、

前記半導体層の幅は、少なくとも前記ソース領域と前記ドレイン領域の間において拡大されており、

前記ソース領域と前記ドレイン領域との間の長さは、前記半導体層の拡大された領域の長さよりも短く、

前記ソース領域と前記ドレイン領域上には第2の配線層が設けられ、該第2の配線層には選択的に形成された画素電極層が接続されていることを特徴とする表示装置。

【請求項8】

請求項5乃至請求項7のいずれか一において、

前記半導体層は、結晶性半導体層と非晶質を含む半導体層が積層して設けられ、

前記結晶性半導体層が有する結晶粒は、前記非晶質を含む半導体層に延びた錐状の結晶粒であることを特徴とする表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図8】

【図9】

【図10】

【公開番号】特開2010−251732(P2010−251732A)

【公開日】平成22年11月4日(2010.11.4)

【国際特許分類】

【出願番号】特願2010−68635(P2010−68635)

【出願日】平成22年3月24日(2010.3.24)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成22年11月4日(2010.11.4)

【国際特許分類】