薄膜トランジスタ

【課題】バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供する。

【解決手段】表示装置用のボトムゲート型の薄膜トランジスタであって、基板1と、ゲート電極配線2と、ゲート絶縁膜3と、チャネルとなる第1の半導体層4と、第1及び第2のコンタクト層5a、5bとなる第2の半導体層と、ソース又はドレイン電極配線7a、7bとを有し、ソース又はドレイン電極配線7a、7bに対して露出する第2の半導体層の露出部に、絶縁性半導体層6a、6bが形成されている。

【解決手段】表示装置用のボトムゲート型の薄膜トランジスタであって、基板1と、ゲート電極配線2と、ゲート絶縁膜3と、チャネルとなる第1の半導体層4と、第1及び第2のコンタクト層5a、5bとなる第2の半導体層と、ソース又はドレイン電極配線7a、7bとを有し、ソース又はドレイン電極配線7a、7bに対して露出する第2の半導体層の露出部に、絶縁性半導体層6a、6bが形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置用の薄膜トランジスタに関する。

【背景技術】

【0002】

表示装置では、画素電極および薄膜トランジスタ(TFT)等を有する画素がマトリクス状に形成されたTFT基板と、TFT基板に対向して、TFT基板の画素電極と対応する場所にカラーフィルタ等が形成された対向基板が配置される。液晶表示装置では、TFT基板と対向基板の間に液晶が挟持されている。そして液晶分子による光の透過率を画素毎に制御することによって画像を形成している。

【0003】

液晶パネルの大型化・高精細化に伴い、液晶表示装置で用いる薄膜トランジスタの改良が進められている(例えば、特許文献1)。特許文献1には、薄膜トランジスタのオフ電流を低減させ、オン電流を向上させ、電気的特性のばらつきを低減させるために、ボトムゲート(逆スタガ)・チャネルエッチ型の薄膜トランジスタの作製方法において、ソース電極及びドレイン電極から露出する一導電型を付与する不純物元素を含む半導体層、及びその下に接して形成されている層にある非晶質半導体層の一部を第1のドライエッチングにより除去し、第1のドライエッチングにより露出した非晶質半導体層の一部を第2のドライエッチングにより除去し、第2のドライエッチングにより露出した非晶質半導体層の表面にプラズマ処理を行うことにより変質層を形成する技術が開示されている。

【0004】

本特許文献1の薄膜トランジスタの一実施形態を図11に示す。基板201上にはゲート電極層202及びゲート絶縁膜203が形成されている。さらにゲート絶縁膜203上には素子毎の分離により、所望の形状にパターン加工された半導体層209及び不純物半導体層210a、210bが形成されている。半導体層209は非晶質構造を有しており、不純物半導体層210a、210bには一導電型を付与する不純物元素が添加されている。ゲート絶縁膜203および不純物半導体層210a、210b上には、不純物半導体層210a、210b、半導体層209の側面を覆うように、所望の形状にパターン加工された一対の配線層213a、213bが形成されている。一対の配線層213a、213bは離間しており、ソース電極213aおよびドレイン電極213bを構成している。また所望の形状にパターン加工された一対の不純物半導体層210a、210bは離間しており、ソース領域210aおよびドレイン領域210bを構成している。さらに一対の不純物半導体層210a、210bの離間部に位置し、エッチングされて凹部が形成された半導体層209上には変質層(絶縁層214)が形成されている。また、保護絶縁膜として絶縁層215が形成されている。

【0005】

凹部を有する半導体層209は、一対の不純物半導体層210a、210bを第1のドライエッチングによって離間形成した後、レジストマスクが形成されたままの状態で、第2のドライエッチングを行うことによって形成している。第2のドライエッチングは、露出している半導体層209にダメージが入らず、且つ該半導体層209に対するエッチングレートが低い条件で行われている。次いで、半導体層209の凹部にはレジストマスクが形成された状態で、水プラズマ処理を行っている。水プラズマ処理は、反応空間に水蒸気(H2O蒸気)に代表される水を主成分とするガスを導入し、水プラズマを生成して実施している。水プラズマ処理を行うことにより、半導体層209の凹部の表面に変質層(絶縁層214)を形成している。

【0006】

第2のドライエッチングにより、露出した半導体層209上に存在する残渣などの不純物を除去することができる。また、水プラズマ処理により、ドライエッチングの際に半導体層209の凹部の表面に形成されたダングリングボンドをOH遊離基で終端化し、欠陥を回復させることができる。また、凹部の表面と絶縁層215の界面を良質にすることができる。この結果、薄膜トランジスタのオン電流向上、オフ電流低減、及びトランジスタ特性のばらつき抑制を実現することができる。

【0007】

さらに、レジストマスクを水プラズマに曝すことにより、基板に存在するコロージョン発生の原因となる塩素等を水プラズマから得られた生成物によって除去することができる。また、金属膜からなる配線にコロージョンの発生を抑制することができる。これにより、薄膜トランジスタではオフ電流の低下、移動度など電気的特性の向上が可能である。

【0008】

このようなオン電流が高く、オフ電流が低く、スイッチング特性に優れ、さらに素子間、基板間、ロット間の電気的特性のばらつきが小さい薄膜トランジスタを用いることにより、画質の向上した表示装置を作製することができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2009−283919号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

現在、携帯電話やデジタルカメラ、タブレットPCなどに用いられる中小型液晶パネルの高精細化に伴ってバックライトの輝度が大幅に上昇している。このため、ボトムゲート型a−SiTFTを用いた液晶パネルでは光リーク電流の増大を抑制すべく、バックライトから直接a−Si層に入射する光に対して、a−Si層をゲート電極によって完全に、あるいは少なくとも一部を遮光する対策が取られている。しかしながら、バックライトの更なる輝度の上昇に伴い、TFTに入射する直接光だけでなく、TFT基板と対向して設けられたカラ―フィルタ側基板のブラックマトリックス(BM)で反射してTFT上部から迷光として入射する間接光が無視できなくなってきており、TFT上部に遮光メタルを追加で設ける等の方法が行われる場合があるが、プロセス工程数が増加してしまう問題がある。間接光の光リーク電流への影響は、従来はバックライトの輝度があまり高くなかったことから特に大きな問題にはなっていなかったが、バックライトの輝度向上が図られる高精細パネルでは無視できなくなっている。以上から、a−SiTFTによる高精細パネルの実現には、間接光への対策が不可欠となっている。

【0011】

そこで、間接光の影響の観点から特許文献1の薄膜トランジスタの検討を行った。本特許文献1の薄膜トランジスタでは、一対の配線層213a、213bの離間部において不純物半導体層210a、210bが表面に露出している。この不純物半導体層210a、210bの露出部には、水プラズマ処理後、半導体層209の凹部のような変質層(絶縁層214)は形成されていない。このため、ソース領域210aとドレイン領域210bの間の距離がバックチャネル長(Lb)となる。よって、ソース電極213aとドレイン電極213bの間の距離(チャネル長Lc)よりも短いことから、ソース領域210aとドレイン領域210bの間のバックチャネル部に、光照射時、リーク電流が流れやすいという問題のあることが分かった。

【0012】

また、露出部の不純物半導体層210a、210bにはバイアスがかかりやすくなっている。よって、正のドレイン電圧をドレインに印加したとき、ドレイン領域側の不純物半導体層210bと半導体層209の界面とその周辺では空乏層が形成されやすくなっている。さらに、不純物半導体層210bでは電子が輸送されやすく正孔とは再結合しにくくなっている。従って、TFTの表面側に間接光が入射されると光リーク電流が増大しやすいという問題がある。

【0013】

なお、水プラズマ処理を実施していれば不純物半導体層210a、210bの露出部にも変質層が形成される可能性はあるが、図や記述によれば、本公知例での水プラズマ処理では、不純物半導体層210a、210bの露出部を全層的に変質層とすることは難しい。不純物半導体層210a、210bの表面側に変質層が形成されるとしても、その膜厚は半導体層209の凹部に形成された変質層214の膜厚に近いものとなる。その理由は、水プラズマ処理の条件は半導体層209の凹部に変質層214が数nm形成されるような条件であり、一方、不純物半導体層210a、210bの膜厚は30nm以上100nm以下程度だからである。また不純物半導体層210a、210bは非晶質半導体、結晶粒を含む非晶質半導体、または微結晶半導体といった膜質であるが、露出した不純物半導体層210a、210bを全層的に変質層化するための膜質制御は行われていないからである。表面側のみに変質層が形成された状態では、殆ど形成されていない場合と同様に、不純物半導体層210a、210bにはバイアスがかかりやすく、特に不純物半導体層210bに輸送される電子は正孔と再結合しにくいことから、TFTの表面側に間接光が入射されると光リーク電流は増大しやすい。

【0014】

本発明の目的は、バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供することにある。

【課題を解決するための手段】

【0015】

上記目的を達成するための一実施形態として、表示装置用のボトムゲート型の薄膜トランジスタであって、基板と、前記基板上に形成されたゲート電極配線と、前記ゲート電極配線上に形成されたゲート絶縁膜と、前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタとする。

【0016】

また、表示装置用のボトムゲート・チャネルエッチ型の薄膜トランジスタであって、 基板と、前記基板上に形成されたゲート電極配線と、前記ゲート電極配線上に形成されたゲート絶縁膜と、前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、前記基板は、液晶を介して、ブラックマトリクスを備えた対向基板と対向して配置されるものであり、前記第1の半導体層の厚さは、前記第2の半導体層や前記絶縁性半導体層が形成されている領域よりも形成されていない領域の方が薄く、鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタとする。

【発明の効果】

【0017】

本発明によれば、ソース・ドレイン電極に対して露出しているコンタクト層の領域を絶縁化させることにより、バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供することができる。

【図面の簡単な説明】

【0018】

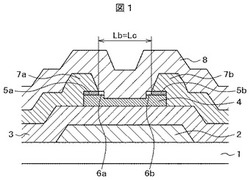

【図1】本発明の第1の実施例に係る薄膜トランジスタの断面図である。

【図2】本発明の第1の実施例に係る薄膜トランジスタを含む表示装置における表示部の部分拡大平面図である。

【図3(a)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(ゲート電極形成)を示す断面図である。

【図3(b)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(ゲート絶縁膜とチャネル層及びチャネル層へのコンタクト層形成)を示す断面図である。

【図3(c)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(チャネル層及びコンタクト層の加工後、ソース電極・ドレイン電極用の金属膜形成)を示す断面図である。

【図3(d)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(金属膜とコンタクト層加工用のレジストパターン形成)を示す断面図である。

【図3(e)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(金属膜の加工)を示す断面図である。

【図3(f)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(コンタクト層の加工)を示す断面図である。

【図3(g)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(露出したコンタクト層を絶縁化)を示す断面図である。

【図4】a−SiTFTの一般的な薄膜トランジスタの光リーク電流(ドレイン電流)のチャネル長依存性の一例を示す図である。

【図5】本発明の第1の実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を示す図である。

【図6】本発明の第1の実施例に係る薄膜トランジスタを用いた液晶表示装置の要部断面図である。

【図7】本発明の第2の実施例に係る薄膜トランジスタの断面図である。

【図8】本発明の第2の実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を示す図である。

【図9】本発明の第3の実施例に係る薄膜トランジスタの断面図である。

【図10】本発明の第4の実施例に係る薄膜トランジスタの断面図である。

【図11】従来の薄膜トランジスタの一例を示す断面図である。

【発明を実施するための形態】

【0019】

発明者等は、上記目的を達成するためにバックライトの間接光によるリーク電流が主に素子のどの部分で発生しているか、どうすれば発生原因を低減・防止できるかについて検討した。その結果、間接光による光リーク電流はa−Si層、特にドレイン電極近傍やソース電極近傍のコンタクト層との界面付近に光が入射されると増大しやすいことが分かった。この理由は、a−Si層とコンタクト層の界面とその周辺に形成されている空乏層では、光が入射して発生したキャリア(電子−正孔対)が、内部電界により特に電子がドレイン電極に輸送されやすいからである。よって、光リーク電流の発生を抑制するには、プロセス工程数を増やさないことを前提とすると同界面をドレイン電極、ソース電極によって遮光することが最も有効となる。しかし、この実現はプロセス技術的には難しい。チャネルエッチ型のa−SiTFTでは、ソース・ドレイン電極の加工は、一般に、チャネル形成領域に開口部を有するレジストパターンをマスクとして金属膜をウェットエッチングすることによって行う。このため、金属膜は等方的にエッチングされ、レジストパターンの開口幅よりもソース・ドレイン電極の開口幅の方が拡がってしまう。一方、チャネルエッチ部におけるコンタクト層除去は、チャネル形成領域に開口部を有するレジストパターンが形成された状態でドライエッチングによって行う。このとき、通常の条件ではレジストパターンの開口幅とコンタクト層のエッチング領域幅はほぼ同等となる。従って、チャネルエッチ領域ではソース・ドレイン電極からa−Si層とコンタクト層の界面が露出してしまう。なお、ドライエッチング条件の工夫によって隠すことは技術的に全く不可能ではないが、a−Si膜の膜厚が薄くなる、エッチングダメージが入る等によりTFT特性が大きく悪化しやすい。

【0020】

以上から、間接光による光リーク電流は、チャネルエッチ領域にコンタクト層が露出した状態でも抑制できることが望ましい。それには、以下を実現することが好適である。

(1)ソース電極とドレイン電極の間の距離(バックチャネル長)を増大させる。

(2)コンタクト層とa−Si界面に形成される空乏層幅を拡がりにくくする。

(3)コンタクト層を流れる電子を正孔と再結合させ易くする。

【0021】

本発明では、(1)〜(3)を実現するために、コンタクト層のチャネルエッチ領域に露出している部分を絶縁化させたTFTトランジスタとする。コンタクト層を形成後、プロセス技術にて絶縁性半導体層を形成し、コンタクト層は制御された膜質や膜厚にて予め成膜されている。なお、コンタクト層を全層的に絶縁化することが望ましい。

【0022】

以下、本発明を実施例により詳細に説明する。

【実施例1】

【0023】

本発明の第1の実施例を図1〜図6を用いて説明する。なお、同一符号は同一の構成要素を示す。

本発明の第1の実施例となる薄膜トランジスタ(TFT)の断面構造を示す。本TFTはゲート遮光構造を有するボトムゲート・チャネルエッチ型となっている。本TFTは、絶縁基板1、ゲート電極配線2、ゲート絶縁膜3、チャネル層となる半導体層4、コンタクト層となる第1導電型半導体層5a、5b、絶縁性半導体層6a、6b、ソース電極配線7a、ドレイン電極配線7b、保護膜8を有する。

【0024】

本実施例では、ゲート絶縁膜3として窒化シリコン膜(SiN膜)、半導体層4として非晶質シリコン膜(a−Si膜)、第1導電型半導体膜5a、5bとしてP(リン)ドープn型微結晶Si膜、絶縁性半導体膜6a、6bとしてシリコン窒化物を形成しているが、これらの膜種は以下に記載するようにこの限りではない。

【0025】

図2は、本発明の第1の実施例に係るTFTを含む画像表示装置における表示部の部分拡大平面図である。表示部はTFTと透明導電膜から成る透明電極502によって形成している。TFTには図1に示したものを形成しており、図2にはゲート電極配線2、半導体層4、絶縁性半導体膜6a、6b、ソース電極配線7a、ドレイン電極配線7bを示す。なお、TFTにはゲート絶縁膜3や保護膜8も形成されているが、平面構造を明確に示すため、図2では省略した。また、コンタクト層となる第1導電型半導体層5a、5bは、ソース電極配線7a、及びドレイン電極配線7bの下に形成されている(本図では見えない)。

なお、図2ではTFTは図1に示した構成のものを示したものであるが、他の実施例に示したTFTであってもよい。

【0026】

次に、図1に示すTFTの代表的な製造方法について図3(a)〜図3(g)を用いて説明する。まず、図3(a)に示すように、絶縁基板1上にゲート電極配線2をパターニング形成する。絶縁基板1には、例えばガラス基板を用いる。また、ゲート電極配線2には、材料として例えばNb、Mo、W、Ta、Cr、Ti、Fe、Ni、Co等の金属やそれらの合金、及びそれらの積層を用いる。または、本実施例ではTFT作製の上限温度をトータルプロセスにおいて低下させられることから、AlやCu等の低抵抗金属を用いることも可能である。成膜は例えばスパッタリング法で行う。膜厚は配線抵抗が大きくならない程度のものが必要であり、本実施例では200nmとしているが、例えば50〜400nmであっても構わない。但し、バックライトの直接光に対する対策の観点からは200〜400nmが望ましい。パターン加工はホトリソグラフィにより行う。このとき、ゲート電極配線2の幅が半導体層4の幅よりも大きくなるように加工される。

【0027】

次に、ゲート電極配線2を形成した基板上に、ゲート絶縁膜3、半導体膜104、及び第1導電型半導体膜105を成膜する(図3(b))。ゲート絶縁膜3と半導体膜104の界面、及び半導体膜104と第1導電型半導体膜105の界面が酸素(O)やカーボン(C)等によって汚染されるのを防ぐため、ゲート絶縁膜3、半導体膜104、及び第1導電型半導体膜105は1台の成膜装置において連続成膜されるのが望ましい。成膜装置は1チャンバでも、真空搬送可能であれば複数チャンバから構成されていても構わない。第1導電型の不純物はチャンバに残留しやすいことから、第1導電型不純物が取り込まれるのを防ぐため、ゲート絶縁膜3や半導体膜104は第1導電型半導体膜105とは別チャンバで成膜すればなお好適である。

【0028】

ゲート絶縁膜3には例えば窒化シリコン(SiN)膜、酸化シリコン(SiO)膜、酸窒化シリコン(SiON)膜やそれらの積層膜を用いることが可能である。なお、本実施例のように半導体膜104のゲート絶縁膜3側にa−Si膜を形成している場合は、a−Si膜の酸化を防止して界面膜質を良好にするためにゲート絶縁膜3の少なくとも半導体膜104側にはSiN膜を形成するのが望ましい。

【0029】

SiN膜の成膜には、PECVD(Plasma-Enhanced Chemical Vapor Deposition)法を用いるのが好適である。ただし、PECVD法以外の、例えば成膜温度が低い熱CVDや光CVD法等も利用可能である。PECVD装置には平行平板型の電極構造のものや、アンテナ型の電極構造のもの等を使用すればよい。PECVD法によってSiN膜を成膜するには、原料ガスとしてSiH4(モノシラン)、NH3(アンモニア)を供給するのが代表的である。さらに成膜時、例えばN2(窒素)、H2(水素)、He(ヘリウム)、Ar(アルゴン)などのキャリアガスを原料ガスと同時に供給してもよい。これらのガス流量比は装置能力や基板面積に応じて選択される。PECVDのRF周波数は13.56MHzが代表的であるが、これら以外の周波数を使用することも可能である。RFパワーは装置サイズや基板面積に応じて選択される。また平行平板型のPECVD装置を用いた場合、電極間距離は安定してプラズマ放電が維持されるように調整すればよい。成膜温度は室温以上を適用可能であるが、ゲート絶縁膜としての耐圧を確保できる膜質を得るために200℃以上が好適である。さらに、膜中に取り込まれているHが脱離するのを抑制するために成膜温度を400℃以下とするのが好適である。また成膜圧力については適用するRF周波数や電極仕様に応じて制御される必要がある。また、膜厚は、ゲート耐圧を確保し、さらにゲート電極配線2の側方端部で膜厚が薄くなることを防止するため、ゲート電極配線2と同等以上であることが望ましく、例えば100nmから400nmとすればよい。

【0030】

成膜条件の代表例を以下に示す。

・装置:平行平板型プラズマCVD ・ガス流量比:SiH4/NH3/N2=1/10/50など

・RF周波数:13.56MHz ・RFパワー密度0.5〜1.0W/cm2 ・電極間隔:20mm前後 ・基板温度:300℃

・成膜圧力:100〜400Pa

一方、半導体膜104のゲート絶縁膜3側に微結晶Siや多結晶Siを形成する場合は、TFTのしきい値電圧シフトが抑制されることから、ゲート絶縁膜3の半導体膜104側にはSiOやSiONを形成するのが望ましい。これらの成膜にもPECVD法を用いるのが好適であるが、スパッタリング法やプラズマ酸化、光酸化などを適用しても構わない。PECVD法によって例えばSiO膜を成膜するには、原料ガスとしてSiH4、N2O(亜酸化窒素)を供給するのが代表的である。さらに成膜時、例えばHe、Arなどのキャリアガスを原料ガスと同時に供給してもよい。PECVD装置、RF周波数、RFパワー、電極間距離、成膜温度、成膜圧力は上記SiNの場合を参考にして選択すればよい。

【0031】

チャネル層となる半導体層には、例えばa−Si、微結晶Si、多結晶Si、及びこれらの積層(a−Si積層、微結晶Si積層、微結晶Siとa−Siの積層など)を用いることが可能である。なお本実施例では、ボトムゲート・チャネルエッチ型のTFTにおいて一般的に用いられることから、半導体膜104としてa−Siを形成している。

【0032】

a−Si膜の成膜にはPECVD法を用いるのが好適である。ただし、PECVD法以外の、例えば熱CVDや光CVD法等も利用可能である。PECVD装置、RF周波数、RFパワー、電極間距離、成膜圧力は上記SiNの場合を参考にすればよい。PECVD法によってa−Si膜を成膜するには、原料ガスとしてSiH4を供給するのが代表的であるが、例えばSi2H6(ジシラン)などの高次のSi水素化ガス(SinH2n+2:n>1)やSiF4(フッ化シラン)などのSiハロゲン化ガスを供給しても良い。さらに成膜時、例えばH2、He、Arなどのキャリアガスを原料ガスと同時に供給してもよい。これらのガス流量比は装置サイズや基板面積に応じて選択される。成膜温度は室温以上を適用可能であるが、欠陥準位密度の少ない膜を形成するには200℃以上が好適である。さらに、膜中に取り込まれているHが脱離するのを抑制するために400℃以下とするのが好適である。

【0033】

成膜条件の代表例を以下に示す。

・装置:平行平板型プラズマCVD ・ガス流量比:SiH4/H2=1/4など

・RF周波数:13.56MHz ・RFパワー密度0.1W/cm2前後 ・電極間隔:20mm前後 ・基板温度:300℃

・成膜圧力:100〜400Pa

半導体膜104では少なくとも一部、特にゲート絶縁膜3側において微結晶Siや多結晶Siを適用することも可能である。微結晶Siを成膜するにはPECVD法を用いるのが好適である。ただし、PECVD法以外の、例えば熱CVDや光CVD法等も利用可能である。PECVD装置には平行平板型の電極構造のものや、アンテナ型の電極構造のもの等を使用可能である。PECVD法によって微結晶Si膜を形成するには、原料ガスとして例えばSiH4やSi2H6などのSi水素化ガス(SinH2n+2:n>1)を供給する。又は、例えばSiF4(フッ化シラン)などのSiのロゲン化ガスを供給しても良い。さらに微結晶Siの成膜には、原子状HによるSi原子のネットワーク再配列の促進や過剰なアモルファスSi成分の除去が必要であることからH2をキャリアガスとして供給する。これらのガス流量比は装置能力や基板面積に応じて選択されるが、SiH4流量に対してH2流量が10倍以上あれば好適である。また、Si原料ガスやH2と共にHe、Arなどのガスと供給することも可能である。PECVDのRF周波数は13.56MHzでも可能であるが、微結晶Siの成膜にはa−Siを成膜するときよりもSi原料ガスやH2の分解がより重要であることから、27.12MHzなどの高周波を利用できれば好適である。RFパワーと成膜圧力は装置能力や基板面積に応じて選択される。成膜チャンバ内の成長雰囲気中の原子状H密度を増大させて微結晶Siを成膜するには低パワー(0.01〜0.3W/cm2)と低圧力(10〜150Pa)の条件が望ましい。あるいはSi原料ガスの分解を促進させて微結晶Siを成膜するには高パワー(1〜2W/cm2)と高圧力(400〜1330Pa)の条件が望ましい。平行平板型のPECVD装置を用いた場合、電極間距離は安定してプラズマ放電が維持されるように調整すればよい。成膜温度は室温以上を適用可能であるが、Si原料ガスから発生した成膜種の反応を促進させて欠陥準位密度の少ない微結晶Si膜を形成するには100℃以上が好適である。さらに、低欠陥準位密度を維持するために水素化された微結晶Si膜を形成するには、成膜温度を400℃以下とするのが好適である。また、H濃度は、欠陥密度を低減させて良好なTFT特性を実現し、さらに後述の、絶縁性半導体層6a、6bを形成する際のプラズマ処理やO2アッシングによって窒化や酸化されにくくするため、1x1020cm−3以上、5x1021cm−3以下が望ましい。

【0034】

多結晶Si膜としては、1つの成膜装置で連続成膜することが難しくなるが、例えばレーザーアニール法、RTA法、反応性熱CVD法等で形成した膜を適用することが可能である。

【0035】

コンタクト層となる第1導電型半導体膜105では、第1導電型のドーピング不純物として例えばP(リン)が添加されている。膜質は微結晶Siが好適であるが、a−Si、及びこれらの積層も可能である。なお本実施例では、後述の絶縁性半導体層6a、6bが形成されやすく、比較的少ないドーピング濃度で良好なコンタクト特性が得られる膜としてPドープ微結晶Siを形成している。a−Siよりも微結晶Siである方が、膜中に結晶粒界を多く含み、さらに含有水素濃度を低下させられることから、N2、N2O、O2等によるプラズマ処理やレジスト除去時のO2アッシング等により窒化や酸化が促進されやすい。また、微結晶Si化を図ることによってa−Si膜を適用する場合よりも導電率を1桁以上向上させることができることから、一定程度のドーピング濃度が確保されていればコンタクト層の抵抗は充分低下する(a−Siの場合よりもドーピング濃度を低下できる)。

【0036】

Pドープ微結晶Siの成膜は、半導体膜104として微結晶Siを形成する場合と同様の装置で良い。PECVD法で成膜する場合、SiH4などのSi原料ガスとH2に追加してドーピングガスとしてホスフィン(PH3)、またはその水素希釈ガス(PH3/H2)を供給すれば良い。ガス流量比はSiH4流量に対してH2流量が10倍以上、PH3の実流量が0.01倍程度であれば好適である。また、これらのガスと共にHe、Arなどを供給することも可能である。RF周波数については、半導体膜104として微結晶Siを形成する場合と同様で良い。RFパワーと成膜圧力は、微結晶化の促進と導電率の向上のため、半導体膜104として低パワー・低圧力の条件で微結晶Siを形成するときよりもやや上昇させる方が望ましい(RFパワー0.2〜1W/cm2、圧力150〜532Pa)。電極間距離は、平行平板型のPECVD装置を用いた場合、安定してプラズマ放電が維持されるように調整すればよい。成膜温度は室温以上を適用可能であるが、導電率を向上させるには100℃以上が好適である。さらに、低欠陥準位密度を維持するために水素化された微結晶Si膜を形成するには、成膜温度を400℃以下とするのが好適である。

【0037】

膜厚は、薄い方が絶縁性半導体層6a、6bは形成されやすいが、薄すぎると成膜初期の微結晶Siの膜質が良くないことから導電率が上昇しやすい。このため、導電率の上昇をも抑制すべく、15〜30nmが好適である。

【0038】

ドーピング濃度は、低抵抗なコンタクト層を形成するために1x1018cm−3以上が望ましい。ただし、あまり高濃度にしてしまうと、TFTにおいて正のドレイン電圧を印加したときにドレイン領域側のコンタクト層5bと半導体層4の界面とその周辺において空乏層が拡がりやすくなってしまう。また高濃度の膜から形成された絶縁性半導体層6bでは電子が輸送されやすくなり正孔との再結合しにくくなってしまう。微結晶Si化よってコンタクト層の低抵抗は一定程度確保されている。従って、ドーピング濃度は1x1020cm−3以下が望ましい。

【0039】

H濃度は膜中の欠陥準位密度低減のために1x1020cm−3以上が望ましい。また高濃度では結晶性が悪化しやすく、さらに絶縁性半導体層6a、6bを形成する際のプラズマ処理やO2アッシングによって窒化や酸化されやすくするには3x1021cm−3以下が望ましい。なお、半導体膜104に含まれる水素濃度をコンタクト層となる第1導電型半導体膜105に含まれる水素濃度よりも高濃度とすることにより、半導体膜104表面に形成される絶縁性半導体層の厚さを絶縁性半導体層6a、6bよりも薄く形成することができる。

結晶粒径については、大きな粒径では絶縁性半導体層6a、6bを形成する際のプラズマ処理やO2アッシングによって窒化や酸化されにくくなってしまうことから、5〜50nm程度が好適である。

結晶相の体積分率に関しては、導電性の確保のため、50%以上が好適である。

成膜条件の代表例を以下に示す。ここでは、PECVDでの放電を立ちやすくし、さらに成膜開始直後から結晶性が良好な膜を形成できる効果があることからAr添加した例を示している。(Arを添加しない成膜では成膜初期に結晶性の悪いインキュベーション層が形成されやすく、さらに過度に水素濃度が高くなりやすい傾向がある。これに対してArを添加すれば、プラズマ中のArイオンの効果により成膜初期からインキュベーション層なく柱状構造の微結晶Si膜が成長しやすい。さらに、水素濃度の過剰な増大が抑制されやすい。ただし、過剰なAr添加は微結晶化を阻害するので注意が必要である。)

・装置:平行平板型プラズマCVD ・ガス流量比:SiH4/H2/Ar/PH3=1/100/10/0.01

・RF周波数:13.56MHz ・RFパワー密度0.3W/cm2前後 ・電極間隔:20mm前後 ・基板温度:300℃

・成膜圧力:300Pa前後

コンタクト層の代表的な膜質は、P濃度:約5x1019cm−3、H濃度:約5x1020cm−3、結晶粒径:約10nm、結晶層の体積率:約60%、膜厚:約15nmのPドープ微結晶Siとなる。

【0040】

なお、Pドープ微結晶Siの成膜直後に、同じPECVD装置内で同じ基板温度で放電させずに例えばArガスを流しながら基板を加熱放置するのが好適である。本目的は、Pドープ微結晶Si膜中から過剰な水素を脱離させることである。基板温度は300℃、成膜圧力は133Paであり、Pドープ微結晶Si成膜中と同じとすることが可能である。放置時間は例えば2分である。さらに、この他にもSi原子のネットワーク再配列の促進や過剰なアモルファスSi成分の除去のため、原子状H雰囲気中でのアニール処理や低ダメージのH2プラズマ処理を実施するのが好適である。

【0041】

第1導電型半導体膜105には少なくとも一部においてPドープa−Siを適用することも可能である。成膜方法、装置、ガス種、RF周波数、成膜温度については上記のPドープ微結晶Siを形成する場合を参考にすればよい。ガス流量比は装置能力や基板面積に応じて選択されるが、SiH4流量に対してH2流量が5倍程度、PH3の実流量が0.01倍程度であれば好適である。RFパワーと成膜圧力についても装置能力や基板面積に応じて選択されるが、例えば0.1W/cm2、266Paである。電極間距離は、平行平板型のPECVD装置を用いた場合、安定してプラズマ放電が維持されるように調整すればよい。

【0042】

次に、ホトリソグラフィによるパターン形成とその後のドライエッチングにより、第1導電型の半導体膜105と半導体膜104をアイランド状に加工する(図3(c))。このとき、アイランド長はゲート電極長よりも狭くなるように形成される。

【0043】

この後、ソース・ドレイン電極配線を形成するため、基板上に金属膜107を堆積する(図3(c))。金属膜107の材料としてはNb、Mo、W、Ta、Cr、Ti、Fe、Ni、Co等やこれらの合金及びそれらの金属の積層膜を用いることが可能である。また本実施例ではTFT作製の上限温度をトータルプロセスにおいて低下させられることから、AlやCu等の低抵抗金属を用いることも可能である。金属膜107の形成には、例えばスパッタリング法を用いることができる。膜厚は、材料によるが配線抵抗低減のため500nm程度とすればよい。

【0044】

次に、図3(d)に示すように、金属膜107と第1導電型の半導体膜105を加工するため、基板上にレジストを塗布し、ホトリソグラフィによりレジストパターン10を形成する。次に、レジストパターン10をマスクとしたウェットエッチングによってレジストパターン10の開口部の金属膜107を除去し、ソース電極配線7aとドレイン電極配線7bを形成する(図3(e))。金属膜は等方的にエッチングされることから、レジストパターン10の開口幅よりもソース・ドレイン電極の開口幅の方が拡がっている。引き続き,レジストパターン10の開口部の第1導電型半導体膜105と半導体膜104の一部をドライエッチングによって除去することにより,ソース領域のコンタクト層5a、ドレイン領域のコンタクト層5b、及び半導体層4を形成する(図3(f))。ドライエッチングによる除去では、通常の条件ではレジストパターン10の開口幅とコンタクト層5a、5b、半導体層4のエッチング領域幅はほぼ同等となる。

【0045】

次に、ソース電極配線7aとドレイン電極配線7bの離間部において、ソース領域のコンタクト層5aとドレイン領域のコンタクト層5bの露出部に絶縁性半導体層6a、6bを形成する(図3(g))。絶縁性半導体層6a、6bは、レジストパターン10を除去し、次の保護膜8(図1参照)を成膜する前にプラズマ処理を実施して形成するのが好適である。さらにこれと併用して、レジストパターン10のO2(酸素)によるアッシング時にソース領域のコンタクト層5aとドレイン領域のコンタクト層5bの露出部を酸化(絶縁化)して絶縁性半導体層6a、6bを形成してもよい。但し、レジストパターン10のO2アッシング単独では充分な絶縁性半導体層6a、6bを形成できない可能性がある。このため、プラズマ処理との併用が望ましい。プラズマ処理は、保護膜8をPECVD法によって成膜する場合は、同じ装置のチャンバにおいて実施することが可能である。なお、露出されたコンタクト層5a、5bは厚さ方向に全て絶縁性半導体層とすることが最適だが、必要な厚さが確保されていればコンタクト層の抵抗が高くなるためリーク電流低減の効果を得ることができる。

【0046】

プラズマ処理ではN2、N2O、O2といったガスを供給すればよい。成膜条件の代表例を以下に示す。

・装置:平行平板型プラズマCVD ・ガス流量:N2=500sccmなど・RF周波数:13.56MHz ・RFパワー密度0.2W/cm2以上

・電極間隔:20mm前後・基板温度:300℃・成膜圧力:50〜266Pa・処理時間:10分

本実施例では、コンタクト層5a、5bは選択された膜質と膜厚にて形成しているので、このプラズマ処理により絶縁性半導体層6a、6bが形成される。また、このプラズマ処理によって半導体層4の凹部についても絶縁性半導体層が形成されるが、本実施例では半導体層4は数%オーダーでHを含むa−Siからなることから、Pドープ微結晶Siからなるコンタクト層5a、5bよりも絶縁化されにくく形成される層の膜厚は薄い。さらに、本プラズマ処理の後、次の保護膜8を成膜する間に例えばH2プラズマ処理等を行えば、半導体層4の凹部に形成された絶縁性半導体層はさらに薄くなる。なお、半導体層4の凹部では絶縁性半導体層の膜厚が薄いことから、図1や図3には未記載とした。

【0047】

最後に,基板上に保護膜8を形成する。この膜には例えばPECVD法により形成されるSiN膜やSiO膜を適用すればよい。スパッタ法で形成したそれらの膜を適用することも可能である。本実施例ではPECVD法によるSiN膜を適用しており,RF周波数13.56MHz,ガスとしてSiH4、NH3、N2を用い,成膜温度は300℃としている。以上により,図1に示す断面構造のTFTが完成する。

【0048】

図1に示すように、コンタクト層の露出部には絶縁性半導体層6a、6bが形成されている。このため、バックチャネル長(Lb)はソース電極とドレイン電極の間の距離、すなわちチャネル長(Lc)と同じになる。バックチャネル長が長くなることによりリーク電流(ドレイン電流)を低減できることを、図4を用いて説明する。図4は表面側から間接光相当の照度で光照射した一般的なa−SiTFTにおいて、ゲート電圧−5Vを印加したときの光リーク電流のチャネル長依存性を評価した結果である。このゲート電圧のときの光リーク電流はバックチャネルを流れると推測されている。本結果から、チャネル長の増加に伴い、バックチャネルを流れる光リーク電流は低下していることが分かる。チャネルエッチ部の開口部に露出しているコンタクト層の長さは、ソース領域側とドレイン領域側の両方の長さを足し合わせると、約0.4〜1μmとなる場合が多い。このため、露出部に絶縁性半導体層6a、6bを形成すれば、バックチャネル長が増大する効果によって光リーク電流が最大約4/5に低下する。

【0049】

次に、本実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を図5に示す。光はTFT表面側から間接光相当の照度で照射している。コンタクト層のドーピング濃度や膜質を制御して絶縁性半導体層6a、6bを形成した本実施例のTFTでは、およそゲート電圧−10<Vg<0Vにおいてドレイン電流Idが上昇しにくく、光リーク電流が抑制されていることが分かる。0本結果では、同ゲート電圧の範囲において光リーク電流が約40%低下した。

即ち、コンタクト層5a、5bではドーピング濃度を制御しており、且つその露出部には絶縁性半導体層6a、6bを形成していることから、正のドレイン電圧を印加したときでもドレイン領域側のコンタクト層6bと半導体層4の界面とその周辺(特にチャネルエッチ領域側)において空乏層は拡がりにくいこと、また、絶縁性半導体層6bでは電子が輸送されにくくなっていることから正孔との再結合が生じやすいこと等により、本実施例のTFTでは光リーク電流が上昇しにくいという効果が得られたものと考えられる。また、絶縁性半導体層6a、6bの形成によってコンタクト面積が低下するが、コンタクト層の膜質制御によってソース・ドレイン抵抗の上昇が抑制されていることから、TFT特性(特にオン電流)の低下が少ない。図6から、TFTのオン特性(Vg>0V)が若干低下しているが、実用上問題ないレベルであることが分かる。

【0050】

次に本実施例のTFTを用いて表示装置を作製した。図6は、液晶表示装置への適用例であり、本発実施例に係るTFTを用いた液晶表示装置の要部断面図である。液晶516を挟持して基板1と基板510が対向して配置されている。基板1側には、図1に示した本実施例のTFTが形成されている。また層間絶縁膜501、及びコンタクトホールを有する。さらに、透明導電膜からなる画素電極502を有する。画素電極502は、ITO膜をスパッタリング法で形成し、ホトリソグラフィを用いて加工したものである。本実施例では膜厚を70nmとしている。更に、画素電極(透明電極)502上に配向膜503を有する。一方、基板510の上には、ブラックマトリックス(BM)511、カラーフィルタ層512、オーバーコート層513、ITO膜からなる対向電極514、配向膜515が順番に形成されている。

【0051】

本液晶表示装置を用いてバックライトの間接光の影響を調べた結果、TFTの光リーク電流増大起因する表示不良の発生が低減されることが分かった。

なお、図6ではTFTは図1に示した構成のものを示したものであるが、他の実施例に示したTFTであってもよい。

以上、本実施例によれば、バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供することができる。

【実施例2】

【0052】

本発明の第2の実施例について図7と図8を用いて説明する。なお、実施例1に記載され本実施例に未記載の事項は特段の事情が無い限り本実施例にも適用することができる。

【0053】

図7は、本実施例に係る薄膜トランジスタの断面図である。実施例1とは、コンタクト層が2層になっている点が異なる。第1の第1導電型半導体層からなる第1のコンタクト層15a、15bと第2の第1導電型半導体層からなる第2のコンタクト層16a、16bから形成されている。

【0054】

第1のコンタクト層15a、15b、第2のコンタクト層16a、16bには第1導電型のドーピング不純物として例えばPが添加されている。膜質は微結晶Si、a−Si、及びこれらの積層が可能である。これらの形成方法は第1の実施例を参考にすればよい。本実施例では、第1のコンタクト層15a、15bとしてPドープ微結晶Siを形成しており、第2のコンタクト層16aと16bとしてPドープa−Siを形成している。

【0055】

実施例1では、ドレイン電極側のコンタクト層にはPドープ微結晶Siからなるコンタクト層5bしか形成していなかった。このため、コンタクト層5bとドレイン電極配線7bの界面において価電子帯側に形成されるエネルギー障壁が低く、正孔が流れやすかった。従って、図5のように、ゲート電圧が例えば−20V<Vg<−10Vの範囲では光リーク電流が増大して見えていた(本リーク電流は光照射に起因するものではないが、リーク電流は光起因のものと足し合わせになる)。これに対し、本実施例では、Pドープa−Siからなる第2のコンタクト層16bを、Pドープ微結晶Siからなる第1のコンタクト層15bとドレイン電極配線7bの間に形成している。これにより、コンタクト層16bとドレイン電極配線7bの界面において価電子帯側に形成されるエネルギー障壁を高くし、正孔の流れを抑制することができる。図8に本実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を示す。図8に示すように、ゲート電圧が例えば−20V<Vg<−10Vの範囲ではリーク電流が低下することが分かる。

【0056】

本実施例のTFTを図6に示す液晶表示装置に適用した結果、実施例1に比べ、表示不良の発生がさらに低減されることが分かった。

以上、本実施例によれば、実施例1と同様の効果を得ることができる。また、露出するコンタクト層を微結晶Siとa−Siの2層構造とすることにより、よりリーク電流を低減することができる。

【実施例3】

【0057】

本発明の第3の実施例について図9を用いて説明する。なお、実施例1又は2に記載され本実施例に未記載の事項は特段の事情が無い限り本実施例にも適用することができる。

【0058】

図9は、本実施例に係る薄膜トランジスタの断面図である。本実施例では、TFTのチャネル層となる半導体層4とソース・ドレイン電極配線7a、7bの側壁にサイド絶縁膜50を形成している。サイド絶縁膜50は例えばシリコン酸化膜からなる。TFTのチャネル層とコンタクト層を例えばドライエッチング法によりアイランド加工した後、表面に残存するレジストをO2アッシングすることによって、レジスト除去とともにサイド酸化膜は形成される。

【0059】

特に本実施例のようなゲート遮光構造のボトムゲートTFTでは、負のゲート電圧が増大してドレイン電極に高電界が印加されたとき、チャネル層4の側壁とドレイン電極7b間でリーク電流が流れやすい。特にチャネル層が微結晶Siや多結晶Siから成る場合は、チャネル層4の側壁とドレイン電極配線7bの界面において価電子帯側に形成されるエネルギー障壁が低く、正孔が流れやすいことからリーク電流が増大しやすい。サイド絶縁膜50にはこのリーク電流が流れるのをブロックする効果がある。

【0060】

本実施例のTFTを図6に示す液晶表示装置に適用した結果、実施例2に比べ、表示不良の発生がさらに低減されることが分かった。

以上、本実施例によれば、実施例1と同様の効果を得ることができる。また、チャネル層となる半導体層とドレイン電極配線の側壁にサイド絶縁膜を形成することにより、よりリーク電流を低減することができる。

【実施例4】

【0061】

本発明の第4の実施例について図10を用いて説明する。なお、実施例1乃至3のいずれかに記載され本実施例に未記載の事項は特段の事情が無い限り本実施例にも適用することができる。

【0062】

図10は、本実施例に係る薄膜トランジスタの断面図である。ゲート遮光構造を有するボトムゲート・チャネルエッチストッパ型のコンタクト層の露出部に、実施例1に記載した方法と同様にして絶縁性半導体膜を形成している。

【0063】

本実施例のTFTは、絶縁基板301、ゲート電極配線302、ゲート絶縁膜303、チャネル層となる半導体層304、絶縁膜からなるストッパ層305、コンタクト層となる第1導電型半導体層306a、306b、ソース電極配線307a、ドレイン電極配線307、絶縁性半導体層308a、308b、保護膜309から成る。ストッパ層305には半導体層304にHを拡散しやすくするため、SiN膜が好適である。以上の形成方法は第1の実施例を参考にすればよい。

【0064】

コンタクト層306a、306bが開口部に露出している場合、TFTの表面側から間接光が入射したとき、コンタクト層306a、306bの露出部においてキャリア(電子−正孔対)が発生しやすく、ドレインに正の電圧を印加したときドレイン電極側では電子がドレイン電極配線307bに流れやすい。このため、光リーク電流が上昇しやすい。これに対して本実施例では、コンタクト層306a、306bの露出部に絶縁性半導体層308a、308bを形成している。絶縁性半導体層308a、308bでは光照射によるキャリア(電子−正孔対)の発生は少なく、電子がドレイン電極配線307b側に輸送されにくいことから、光リーク電流の上昇が抑制される。

【0065】

なお本構造のTFTでは、実施例1に比べてストッパ層305を形成するために、成膜工程、ホトリソグラフィ工程、エッチング工程が増えてしまう。しかし、上記やa−Si層の膜厚を薄くできる利点もあることから、実施例1に対しても光リーク電流の上昇が抑制されやすい。

【0066】

本実施例のTFTを図6に示す液晶表示装置に適用し、バックライトの間接光の影響を調べた結果、TFTの光リーク電流増大起因する表示不良の発生が低減されることが分かった。

以上、本実施例によれば、実施例1と同様の効果を得ることができる。また、ストッパ層を設けることにより、よりリーク電流を低減することができる。

【0067】

なお、本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。例えば、上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施例の構成の一部を他の実施例の構成に置き換えることも可能であり、また、ある実施例の構成に他の実施例の構成を加えることも可能である。また、各実施例の構成の一部について、他の構成の追加・削除・置換をすることが可能である。

【符号の説明】

【0068】

1…絶縁基板、2…ゲート電極配線、3…ゲート絶縁膜、4…チャネルとなる半導体層、5a、5b…コンタクト層となる第1導電型半導体層、6a、6b…絶縁性半導体層、7a…ソース電極配線、7b…ドレイン電極配線、8…保護膜、10…レジストパターン、15a、15b…第1の第1導電型半導体層からなる第1のコンタクト層、16a、16b…第2の第1導電型半導体層からなる第2のコンタクト層、50…サイド絶縁膜、104…半導体膜、105…第1導電型半導体膜、107…金属膜、201…基板、202…ゲート電極層、203…ゲート絶縁膜、209…半導体層、210a、210b…不純物半導体層(ソース領域、ドレイン領域)、213a…ソース電極、213b…ドレイン電極、214…変質層(絶縁層)、215…絶縁層、301…絶縁基板、302…ゲート電極配線、303…ゲート絶縁膜、304…チャネル層となる半導体層、305…ストッパ層、306a、306b…コンタクト層となる第1導電型半導体層、307a…ソース電極配線、307b…ドレイン電極配線、308a、308b…絶縁性半導体層、309…保護膜、501…層間絶縁膜、502…透明電極(画素電極)、503…配向膜、510…基板、511…ブラックマトリックス(BM)、512…カラーフィルタ層、513…オーバーコート層、514…対向電極、515…配向膜、516…液晶。

【技術分野】

【0001】

本発明は、表示装置用の薄膜トランジスタに関する。

【背景技術】

【0002】

表示装置では、画素電極および薄膜トランジスタ(TFT)等を有する画素がマトリクス状に形成されたTFT基板と、TFT基板に対向して、TFT基板の画素電極と対応する場所にカラーフィルタ等が形成された対向基板が配置される。液晶表示装置では、TFT基板と対向基板の間に液晶が挟持されている。そして液晶分子による光の透過率を画素毎に制御することによって画像を形成している。

【0003】

液晶パネルの大型化・高精細化に伴い、液晶表示装置で用いる薄膜トランジスタの改良が進められている(例えば、特許文献1)。特許文献1には、薄膜トランジスタのオフ電流を低減させ、オン電流を向上させ、電気的特性のばらつきを低減させるために、ボトムゲート(逆スタガ)・チャネルエッチ型の薄膜トランジスタの作製方法において、ソース電極及びドレイン電極から露出する一導電型を付与する不純物元素を含む半導体層、及びその下に接して形成されている層にある非晶質半導体層の一部を第1のドライエッチングにより除去し、第1のドライエッチングにより露出した非晶質半導体層の一部を第2のドライエッチングにより除去し、第2のドライエッチングにより露出した非晶質半導体層の表面にプラズマ処理を行うことにより変質層を形成する技術が開示されている。

【0004】

本特許文献1の薄膜トランジスタの一実施形態を図11に示す。基板201上にはゲート電極層202及びゲート絶縁膜203が形成されている。さらにゲート絶縁膜203上には素子毎の分離により、所望の形状にパターン加工された半導体層209及び不純物半導体層210a、210bが形成されている。半導体層209は非晶質構造を有しており、不純物半導体層210a、210bには一導電型を付与する不純物元素が添加されている。ゲート絶縁膜203および不純物半導体層210a、210b上には、不純物半導体層210a、210b、半導体層209の側面を覆うように、所望の形状にパターン加工された一対の配線層213a、213bが形成されている。一対の配線層213a、213bは離間しており、ソース電極213aおよびドレイン電極213bを構成している。また所望の形状にパターン加工された一対の不純物半導体層210a、210bは離間しており、ソース領域210aおよびドレイン領域210bを構成している。さらに一対の不純物半導体層210a、210bの離間部に位置し、エッチングされて凹部が形成された半導体層209上には変質層(絶縁層214)が形成されている。また、保護絶縁膜として絶縁層215が形成されている。

【0005】

凹部を有する半導体層209は、一対の不純物半導体層210a、210bを第1のドライエッチングによって離間形成した後、レジストマスクが形成されたままの状態で、第2のドライエッチングを行うことによって形成している。第2のドライエッチングは、露出している半導体層209にダメージが入らず、且つ該半導体層209に対するエッチングレートが低い条件で行われている。次いで、半導体層209の凹部にはレジストマスクが形成された状態で、水プラズマ処理を行っている。水プラズマ処理は、反応空間に水蒸気(H2O蒸気)に代表される水を主成分とするガスを導入し、水プラズマを生成して実施している。水プラズマ処理を行うことにより、半導体層209の凹部の表面に変質層(絶縁層214)を形成している。

【0006】

第2のドライエッチングにより、露出した半導体層209上に存在する残渣などの不純物を除去することができる。また、水プラズマ処理により、ドライエッチングの際に半導体層209の凹部の表面に形成されたダングリングボンドをOH遊離基で終端化し、欠陥を回復させることができる。また、凹部の表面と絶縁層215の界面を良質にすることができる。この結果、薄膜トランジスタのオン電流向上、オフ電流低減、及びトランジスタ特性のばらつき抑制を実現することができる。

【0007】

さらに、レジストマスクを水プラズマに曝すことにより、基板に存在するコロージョン発生の原因となる塩素等を水プラズマから得られた生成物によって除去することができる。また、金属膜からなる配線にコロージョンの発生を抑制することができる。これにより、薄膜トランジスタではオフ電流の低下、移動度など電気的特性の向上が可能である。

【0008】

このようなオン電流が高く、オフ電流が低く、スイッチング特性に優れ、さらに素子間、基板間、ロット間の電気的特性のばらつきが小さい薄膜トランジスタを用いることにより、画質の向上した表示装置を作製することができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2009−283919号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

現在、携帯電話やデジタルカメラ、タブレットPCなどに用いられる中小型液晶パネルの高精細化に伴ってバックライトの輝度が大幅に上昇している。このため、ボトムゲート型a−SiTFTを用いた液晶パネルでは光リーク電流の増大を抑制すべく、バックライトから直接a−Si層に入射する光に対して、a−Si層をゲート電極によって完全に、あるいは少なくとも一部を遮光する対策が取られている。しかしながら、バックライトの更なる輝度の上昇に伴い、TFTに入射する直接光だけでなく、TFT基板と対向して設けられたカラ―フィルタ側基板のブラックマトリックス(BM)で反射してTFT上部から迷光として入射する間接光が無視できなくなってきており、TFT上部に遮光メタルを追加で設ける等の方法が行われる場合があるが、プロセス工程数が増加してしまう問題がある。間接光の光リーク電流への影響は、従来はバックライトの輝度があまり高くなかったことから特に大きな問題にはなっていなかったが、バックライトの輝度向上が図られる高精細パネルでは無視できなくなっている。以上から、a−SiTFTによる高精細パネルの実現には、間接光への対策が不可欠となっている。

【0011】

そこで、間接光の影響の観点から特許文献1の薄膜トランジスタの検討を行った。本特許文献1の薄膜トランジスタでは、一対の配線層213a、213bの離間部において不純物半導体層210a、210bが表面に露出している。この不純物半導体層210a、210bの露出部には、水プラズマ処理後、半導体層209の凹部のような変質層(絶縁層214)は形成されていない。このため、ソース領域210aとドレイン領域210bの間の距離がバックチャネル長(Lb)となる。よって、ソース電極213aとドレイン電極213bの間の距離(チャネル長Lc)よりも短いことから、ソース領域210aとドレイン領域210bの間のバックチャネル部に、光照射時、リーク電流が流れやすいという問題のあることが分かった。

【0012】

また、露出部の不純物半導体層210a、210bにはバイアスがかかりやすくなっている。よって、正のドレイン電圧をドレインに印加したとき、ドレイン領域側の不純物半導体層210bと半導体層209の界面とその周辺では空乏層が形成されやすくなっている。さらに、不純物半導体層210bでは電子が輸送されやすく正孔とは再結合しにくくなっている。従って、TFTの表面側に間接光が入射されると光リーク電流が増大しやすいという問題がある。

【0013】

なお、水プラズマ処理を実施していれば不純物半導体層210a、210bの露出部にも変質層が形成される可能性はあるが、図や記述によれば、本公知例での水プラズマ処理では、不純物半導体層210a、210bの露出部を全層的に変質層とすることは難しい。不純物半導体層210a、210bの表面側に変質層が形成されるとしても、その膜厚は半導体層209の凹部に形成された変質層214の膜厚に近いものとなる。その理由は、水プラズマ処理の条件は半導体層209の凹部に変質層214が数nm形成されるような条件であり、一方、不純物半導体層210a、210bの膜厚は30nm以上100nm以下程度だからである。また不純物半導体層210a、210bは非晶質半導体、結晶粒を含む非晶質半導体、または微結晶半導体といった膜質であるが、露出した不純物半導体層210a、210bを全層的に変質層化するための膜質制御は行われていないからである。表面側のみに変質層が形成された状態では、殆ど形成されていない場合と同様に、不純物半導体層210a、210bにはバイアスがかかりやすく、特に不純物半導体層210bに輸送される電子は正孔と再結合しにくいことから、TFTの表面側に間接光が入射されると光リーク電流は増大しやすい。

【0014】

本発明の目的は、バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供することにある。

【課題を解決するための手段】

【0015】

上記目的を達成するための一実施形態として、表示装置用のボトムゲート型の薄膜トランジスタであって、基板と、前記基板上に形成されたゲート電極配線と、前記ゲート電極配線上に形成されたゲート絶縁膜と、前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタとする。

【0016】

また、表示装置用のボトムゲート・チャネルエッチ型の薄膜トランジスタであって、 基板と、前記基板上に形成されたゲート電極配線と、前記ゲート電極配線上に形成されたゲート絶縁膜と、前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、前記基板は、液晶を介して、ブラックマトリクスを備えた対向基板と対向して配置されるものであり、前記第1の半導体層の厚さは、前記第2の半導体層や前記絶縁性半導体層が形成されている領域よりも形成されていない領域の方が薄く、鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタとする。

【発明の効果】

【0017】

本発明によれば、ソース・ドレイン電極に対して露出しているコンタクト層の領域を絶縁化させることにより、バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供することができる。

【図面の簡単な説明】

【0018】

【図1】本発明の第1の実施例に係る薄膜トランジスタの断面図である。

【図2】本発明の第1の実施例に係る薄膜トランジスタを含む表示装置における表示部の部分拡大平面図である。

【図3(a)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(ゲート電極形成)を示す断面図である。

【図3(b)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(ゲート絶縁膜とチャネル層及びチャネル層へのコンタクト層形成)を示す断面図である。

【図3(c)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(チャネル層及びコンタクト層の加工後、ソース電極・ドレイン電極用の金属膜形成)を示す断面図である。

【図3(d)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(金属膜とコンタクト層加工用のレジストパターン形成)を示す断面図である。

【図3(e)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(金属膜の加工)を示す断面図である。

【図3(f)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(コンタクト層の加工)を示す断面図である。

【図3(g)】本発明の第1の実施例に係る薄膜トランジスタの製造工程(露出したコンタクト層を絶縁化)を示す断面図である。

【図4】a−SiTFTの一般的な薄膜トランジスタの光リーク電流(ドレイン電流)のチャネル長依存性の一例を示す図である。

【図5】本発明の第1の実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を示す図である。

【図6】本発明の第1の実施例に係る薄膜トランジスタを用いた液晶表示装置の要部断面図である。

【図7】本発明の第2の実施例に係る薄膜トランジスタの断面図である。

【図8】本発明の第2の実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を示す図である。

【図9】本発明の第3の実施例に係る薄膜トランジスタの断面図である。

【図10】本発明の第4の実施例に係る薄膜トランジスタの断面図である。

【図11】従来の薄膜トランジスタの一例を示す断面図である。

【発明を実施するための形態】

【0019】

発明者等は、上記目的を達成するためにバックライトの間接光によるリーク電流が主に素子のどの部分で発生しているか、どうすれば発生原因を低減・防止できるかについて検討した。その結果、間接光による光リーク電流はa−Si層、特にドレイン電極近傍やソース電極近傍のコンタクト層との界面付近に光が入射されると増大しやすいことが分かった。この理由は、a−Si層とコンタクト層の界面とその周辺に形成されている空乏層では、光が入射して発生したキャリア(電子−正孔対)が、内部電界により特に電子がドレイン電極に輸送されやすいからである。よって、光リーク電流の発生を抑制するには、プロセス工程数を増やさないことを前提とすると同界面をドレイン電極、ソース電極によって遮光することが最も有効となる。しかし、この実現はプロセス技術的には難しい。チャネルエッチ型のa−SiTFTでは、ソース・ドレイン電極の加工は、一般に、チャネル形成領域に開口部を有するレジストパターンをマスクとして金属膜をウェットエッチングすることによって行う。このため、金属膜は等方的にエッチングされ、レジストパターンの開口幅よりもソース・ドレイン電極の開口幅の方が拡がってしまう。一方、チャネルエッチ部におけるコンタクト層除去は、チャネル形成領域に開口部を有するレジストパターンが形成された状態でドライエッチングによって行う。このとき、通常の条件ではレジストパターンの開口幅とコンタクト層のエッチング領域幅はほぼ同等となる。従って、チャネルエッチ領域ではソース・ドレイン電極からa−Si層とコンタクト層の界面が露出してしまう。なお、ドライエッチング条件の工夫によって隠すことは技術的に全く不可能ではないが、a−Si膜の膜厚が薄くなる、エッチングダメージが入る等によりTFT特性が大きく悪化しやすい。

【0020】

以上から、間接光による光リーク電流は、チャネルエッチ領域にコンタクト層が露出した状態でも抑制できることが望ましい。それには、以下を実現することが好適である。

(1)ソース電極とドレイン電極の間の距離(バックチャネル長)を増大させる。

(2)コンタクト層とa−Si界面に形成される空乏層幅を拡がりにくくする。

(3)コンタクト層を流れる電子を正孔と再結合させ易くする。

【0021】

本発明では、(1)〜(3)を実現するために、コンタクト層のチャネルエッチ領域に露出している部分を絶縁化させたTFTトランジスタとする。コンタクト層を形成後、プロセス技術にて絶縁性半導体層を形成し、コンタクト層は制御された膜質や膜厚にて予め成膜されている。なお、コンタクト層を全層的に絶縁化することが望ましい。

【0022】

以下、本発明を実施例により詳細に説明する。

【実施例1】

【0023】

本発明の第1の実施例を図1〜図6を用いて説明する。なお、同一符号は同一の構成要素を示す。

本発明の第1の実施例となる薄膜トランジスタ(TFT)の断面構造を示す。本TFTはゲート遮光構造を有するボトムゲート・チャネルエッチ型となっている。本TFTは、絶縁基板1、ゲート電極配線2、ゲート絶縁膜3、チャネル層となる半導体層4、コンタクト層となる第1導電型半導体層5a、5b、絶縁性半導体層6a、6b、ソース電極配線7a、ドレイン電極配線7b、保護膜8を有する。

【0024】

本実施例では、ゲート絶縁膜3として窒化シリコン膜(SiN膜)、半導体層4として非晶質シリコン膜(a−Si膜)、第1導電型半導体膜5a、5bとしてP(リン)ドープn型微結晶Si膜、絶縁性半導体膜6a、6bとしてシリコン窒化物を形成しているが、これらの膜種は以下に記載するようにこの限りではない。

【0025】

図2は、本発明の第1の実施例に係るTFTを含む画像表示装置における表示部の部分拡大平面図である。表示部はTFTと透明導電膜から成る透明電極502によって形成している。TFTには図1に示したものを形成しており、図2にはゲート電極配線2、半導体層4、絶縁性半導体膜6a、6b、ソース電極配線7a、ドレイン電極配線7bを示す。なお、TFTにはゲート絶縁膜3や保護膜8も形成されているが、平面構造を明確に示すため、図2では省略した。また、コンタクト層となる第1導電型半導体層5a、5bは、ソース電極配線7a、及びドレイン電極配線7bの下に形成されている(本図では見えない)。

なお、図2ではTFTは図1に示した構成のものを示したものであるが、他の実施例に示したTFTであってもよい。

【0026】

次に、図1に示すTFTの代表的な製造方法について図3(a)〜図3(g)を用いて説明する。まず、図3(a)に示すように、絶縁基板1上にゲート電極配線2をパターニング形成する。絶縁基板1には、例えばガラス基板を用いる。また、ゲート電極配線2には、材料として例えばNb、Mo、W、Ta、Cr、Ti、Fe、Ni、Co等の金属やそれらの合金、及びそれらの積層を用いる。または、本実施例ではTFT作製の上限温度をトータルプロセスにおいて低下させられることから、AlやCu等の低抵抗金属を用いることも可能である。成膜は例えばスパッタリング法で行う。膜厚は配線抵抗が大きくならない程度のものが必要であり、本実施例では200nmとしているが、例えば50〜400nmであっても構わない。但し、バックライトの直接光に対する対策の観点からは200〜400nmが望ましい。パターン加工はホトリソグラフィにより行う。このとき、ゲート電極配線2の幅が半導体層4の幅よりも大きくなるように加工される。

【0027】

次に、ゲート電極配線2を形成した基板上に、ゲート絶縁膜3、半導体膜104、及び第1導電型半導体膜105を成膜する(図3(b))。ゲート絶縁膜3と半導体膜104の界面、及び半導体膜104と第1導電型半導体膜105の界面が酸素(O)やカーボン(C)等によって汚染されるのを防ぐため、ゲート絶縁膜3、半導体膜104、及び第1導電型半導体膜105は1台の成膜装置において連続成膜されるのが望ましい。成膜装置は1チャンバでも、真空搬送可能であれば複数チャンバから構成されていても構わない。第1導電型の不純物はチャンバに残留しやすいことから、第1導電型不純物が取り込まれるのを防ぐため、ゲート絶縁膜3や半導体膜104は第1導電型半導体膜105とは別チャンバで成膜すればなお好適である。

【0028】

ゲート絶縁膜3には例えば窒化シリコン(SiN)膜、酸化シリコン(SiO)膜、酸窒化シリコン(SiON)膜やそれらの積層膜を用いることが可能である。なお、本実施例のように半導体膜104のゲート絶縁膜3側にa−Si膜を形成している場合は、a−Si膜の酸化を防止して界面膜質を良好にするためにゲート絶縁膜3の少なくとも半導体膜104側にはSiN膜を形成するのが望ましい。

【0029】

SiN膜の成膜には、PECVD(Plasma-Enhanced Chemical Vapor Deposition)法を用いるのが好適である。ただし、PECVD法以外の、例えば成膜温度が低い熱CVDや光CVD法等も利用可能である。PECVD装置には平行平板型の電極構造のものや、アンテナ型の電極構造のもの等を使用すればよい。PECVD法によってSiN膜を成膜するには、原料ガスとしてSiH4(モノシラン)、NH3(アンモニア)を供給するのが代表的である。さらに成膜時、例えばN2(窒素)、H2(水素)、He(ヘリウム)、Ar(アルゴン)などのキャリアガスを原料ガスと同時に供給してもよい。これらのガス流量比は装置能力や基板面積に応じて選択される。PECVDのRF周波数は13.56MHzが代表的であるが、これら以外の周波数を使用することも可能である。RFパワーは装置サイズや基板面積に応じて選択される。また平行平板型のPECVD装置を用いた場合、電極間距離は安定してプラズマ放電が維持されるように調整すればよい。成膜温度は室温以上を適用可能であるが、ゲート絶縁膜としての耐圧を確保できる膜質を得るために200℃以上が好適である。さらに、膜中に取り込まれているHが脱離するのを抑制するために成膜温度を400℃以下とするのが好適である。また成膜圧力については適用するRF周波数や電極仕様に応じて制御される必要がある。また、膜厚は、ゲート耐圧を確保し、さらにゲート電極配線2の側方端部で膜厚が薄くなることを防止するため、ゲート電極配線2と同等以上であることが望ましく、例えば100nmから400nmとすればよい。

【0030】

成膜条件の代表例を以下に示す。

・装置:平行平板型プラズマCVD ・ガス流量比:SiH4/NH3/N2=1/10/50など

・RF周波数:13.56MHz ・RFパワー密度0.5〜1.0W/cm2 ・電極間隔:20mm前後 ・基板温度:300℃

・成膜圧力:100〜400Pa

一方、半導体膜104のゲート絶縁膜3側に微結晶Siや多結晶Siを形成する場合は、TFTのしきい値電圧シフトが抑制されることから、ゲート絶縁膜3の半導体膜104側にはSiOやSiONを形成するのが望ましい。これらの成膜にもPECVD法を用いるのが好適であるが、スパッタリング法やプラズマ酸化、光酸化などを適用しても構わない。PECVD法によって例えばSiO膜を成膜するには、原料ガスとしてSiH4、N2O(亜酸化窒素)を供給するのが代表的である。さらに成膜時、例えばHe、Arなどのキャリアガスを原料ガスと同時に供給してもよい。PECVD装置、RF周波数、RFパワー、電極間距離、成膜温度、成膜圧力は上記SiNの場合を参考にして選択すればよい。

【0031】

チャネル層となる半導体層には、例えばa−Si、微結晶Si、多結晶Si、及びこれらの積層(a−Si積層、微結晶Si積層、微結晶Siとa−Siの積層など)を用いることが可能である。なお本実施例では、ボトムゲート・チャネルエッチ型のTFTにおいて一般的に用いられることから、半導体膜104としてa−Siを形成している。

【0032】

a−Si膜の成膜にはPECVD法を用いるのが好適である。ただし、PECVD法以外の、例えば熱CVDや光CVD法等も利用可能である。PECVD装置、RF周波数、RFパワー、電極間距離、成膜圧力は上記SiNの場合を参考にすればよい。PECVD法によってa−Si膜を成膜するには、原料ガスとしてSiH4を供給するのが代表的であるが、例えばSi2H6(ジシラン)などの高次のSi水素化ガス(SinH2n+2:n>1)やSiF4(フッ化シラン)などのSiハロゲン化ガスを供給しても良い。さらに成膜時、例えばH2、He、Arなどのキャリアガスを原料ガスと同時に供給してもよい。これらのガス流量比は装置サイズや基板面積に応じて選択される。成膜温度は室温以上を適用可能であるが、欠陥準位密度の少ない膜を形成するには200℃以上が好適である。さらに、膜中に取り込まれているHが脱離するのを抑制するために400℃以下とするのが好適である。

【0033】

成膜条件の代表例を以下に示す。

・装置:平行平板型プラズマCVD ・ガス流量比:SiH4/H2=1/4など

・RF周波数:13.56MHz ・RFパワー密度0.1W/cm2前後 ・電極間隔:20mm前後 ・基板温度:300℃

・成膜圧力:100〜400Pa

半導体膜104では少なくとも一部、特にゲート絶縁膜3側において微結晶Siや多結晶Siを適用することも可能である。微結晶Siを成膜するにはPECVD法を用いるのが好適である。ただし、PECVD法以外の、例えば熱CVDや光CVD法等も利用可能である。PECVD装置には平行平板型の電極構造のものや、アンテナ型の電極構造のもの等を使用可能である。PECVD法によって微結晶Si膜を形成するには、原料ガスとして例えばSiH4やSi2H6などのSi水素化ガス(SinH2n+2:n>1)を供給する。又は、例えばSiF4(フッ化シラン)などのSiのロゲン化ガスを供給しても良い。さらに微結晶Siの成膜には、原子状HによるSi原子のネットワーク再配列の促進や過剰なアモルファスSi成分の除去が必要であることからH2をキャリアガスとして供給する。これらのガス流量比は装置能力や基板面積に応じて選択されるが、SiH4流量に対してH2流量が10倍以上あれば好適である。また、Si原料ガスやH2と共にHe、Arなどのガスと供給することも可能である。PECVDのRF周波数は13.56MHzでも可能であるが、微結晶Siの成膜にはa−Siを成膜するときよりもSi原料ガスやH2の分解がより重要であることから、27.12MHzなどの高周波を利用できれば好適である。RFパワーと成膜圧力は装置能力や基板面積に応じて選択される。成膜チャンバ内の成長雰囲気中の原子状H密度を増大させて微結晶Siを成膜するには低パワー(0.01〜0.3W/cm2)と低圧力(10〜150Pa)の条件が望ましい。あるいはSi原料ガスの分解を促進させて微結晶Siを成膜するには高パワー(1〜2W/cm2)と高圧力(400〜1330Pa)の条件が望ましい。平行平板型のPECVD装置を用いた場合、電極間距離は安定してプラズマ放電が維持されるように調整すればよい。成膜温度は室温以上を適用可能であるが、Si原料ガスから発生した成膜種の反応を促進させて欠陥準位密度の少ない微結晶Si膜を形成するには100℃以上が好適である。さらに、低欠陥準位密度を維持するために水素化された微結晶Si膜を形成するには、成膜温度を400℃以下とするのが好適である。また、H濃度は、欠陥密度を低減させて良好なTFT特性を実現し、さらに後述の、絶縁性半導体層6a、6bを形成する際のプラズマ処理やO2アッシングによって窒化や酸化されにくくするため、1x1020cm−3以上、5x1021cm−3以下が望ましい。

【0034】

多結晶Si膜としては、1つの成膜装置で連続成膜することが難しくなるが、例えばレーザーアニール法、RTA法、反応性熱CVD法等で形成した膜を適用することが可能である。

【0035】

コンタクト層となる第1導電型半導体膜105では、第1導電型のドーピング不純物として例えばP(リン)が添加されている。膜質は微結晶Siが好適であるが、a−Si、及びこれらの積層も可能である。なお本実施例では、後述の絶縁性半導体層6a、6bが形成されやすく、比較的少ないドーピング濃度で良好なコンタクト特性が得られる膜としてPドープ微結晶Siを形成している。a−Siよりも微結晶Siである方が、膜中に結晶粒界を多く含み、さらに含有水素濃度を低下させられることから、N2、N2O、O2等によるプラズマ処理やレジスト除去時のO2アッシング等により窒化や酸化が促進されやすい。また、微結晶Si化を図ることによってa−Si膜を適用する場合よりも導電率を1桁以上向上させることができることから、一定程度のドーピング濃度が確保されていればコンタクト層の抵抗は充分低下する(a−Siの場合よりもドーピング濃度を低下できる)。

【0036】

Pドープ微結晶Siの成膜は、半導体膜104として微結晶Siを形成する場合と同様の装置で良い。PECVD法で成膜する場合、SiH4などのSi原料ガスとH2に追加してドーピングガスとしてホスフィン(PH3)、またはその水素希釈ガス(PH3/H2)を供給すれば良い。ガス流量比はSiH4流量に対してH2流量が10倍以上、PH3の実流量が0.01倍程度であれば好適である。また、これらのガスと共にHe、Arなどを供給することも可能である。RF周波数については、半導体膜104として微結晶Siを形成する場合と同様で良い。RFパワーと成膜圧力は、微結晶化の促進と導電率の向上のため、半導体膜104として低パワー・低圧力の条件で微結晶Siを形成するときよりもやや上昇させる方が望ましい(RFパワー0.2〜1W/cm2、圧力150〜532Pa)。電極間距離は、平行平板型のPECVD装置を用いた場合、安定してプラズマ放電が維持されるように調整すればよい。成膜温度は室温以上を適用可能であるが、導電率を向上させるには100℃以上が好適である。さらに、低欠陥準位密度を維持するために水素化された微結晶Si膜を形成するには、成膜温度を400℃以下とするのが好適である。

【0037】

膜厚は、薄い方が絶縁性半導体層6a、6bは形成されやすいが、薄すぎると成膜初期の微結晶Siの膜質が良くないことから導電率が上昇しやすい。このため、導電率の上昇をも抑制すべく、15〜30nmが好適である。

【0038】

ドーピング濃度は、低抵抗なコンタクト層を形成するために1x1018cm−3以上が望ましい。ただし、あまり高濃度にしてしまうと、TFTにおいて正のドレイン電圧を印加したときにドレイン領域側のコンタクト層5bと半導体層4の界面とその周辺において空乏層が拡がりやすくなってしまう。また高濃度の膜から形成された絶縁性半導体層6bでは電子が輸送されやすくなり正孔との再結合しにくくなってしまう。微結晶Si化よってコンタクト層の低抵抗は一定程度確保されている。従って、ドーピング濃度は1x1020cm−3以下が望ましい。

【0039】

H濃度は膜中の欠陥準位密度低減のために1x1020cm−3以上が望ましい。また高濃度では結晶性が悪化しやすく、さらに絶縁性半導体層6a、6bを形成する際のプラズマ処理やO2アッシングによって窒化や酸化されやすくするには3x1021cm−3以下が望ましい。なお、半導体膜104に含まれる水素濃度をコンタクト層となる第1導電型半導体膜105に含まれる水素濃度よりも高濃度とすることにより、半導体膜104表面に形成される絶縁性半導体層の厚さを絶縁性半導体層6a、6bよりも薄く形成することができる。

結晶粒径については、大きな粒径では絶縁性半導体層6a、6bを形成する際のプラズマ処理やO2アッシングによって窒化や酸化されにくくなってしまうことから、5〜50nm程度が好適である。

結晶相の体積分率に関しては、導電性の確保のため、50%以上が好適である。

成膜条件の代表例を以下に示す。ここでは、PECVDでの放電を立ちやすくし、さらに成膜開始直後から結晶性が良好な膜を形成できる効果があることからAr添加した例を示している。(Arを添加しない成膜では成膜初期に結晶性の悪いインキュベーション層が形成されやすく、さらに過度に水素濃度が高くなりやすい傾向がある。これに対してArを添加すれば、プラズマ中のArイオンの効果により成膜初期からインキュベーション層なく柱状構造の微結晶Si膜が成長しやすい。さらに、水素濃度の過剰な増大が抑制されやすい。ただし、過剰なAr添加は微結晶化を阻害するので注意が必要である。)

・装置:平行平板型プラズマCVD ・ガス流量比:SiH4/H2/Ar/PH3=1/100/10/0.01

・RF周波数:13.56MHz ・RFパワー密度0.3W/cm2前後 ・電極間隔:20mm前後 ・基板温度:300℃

・成膜圧力:300Pa前後

コンタクト層の代表的な膜質は、P濃度:約5x1019cm−3、H濃度:約5x1020cm−3、結晶粒径:約10nm、結晶層の体積率:約60%、膜厚:約15nmのPドープ微結晶Siとなる。

【0040】

なお、Pドープ微結晶Siの成膜直後に、同じPECVD装置内で同じ基板温度で放電させずに例えばArガスを流しながら基板を加熱放置するのが好適である。本目的は、Pドープ微結晶Si膜中から過剰な水素を脱離させることである。基板温度は300℃、成膜圧力は133Paであり、Pドープ微結晶Si成膜中と同じとすることが可能である。放置時間は例えば2分である。さらに、この他にもSi原子のネットワーク再配列の促進や過剰なアモルファスSi成分の除去のため、原子状H雰囲気中でのアニール処理や低ダメージのH2プラズマ処理を実施するのが好適である。

【0041】

第1導電型半導体膜105には少なくとも一部においてPドープa−Siを適用することも可能である。成膜方法、装置、ガス種、RF周波数、成膜温度については上記のPドープ微結晶Siを形成する場合を参考にすればよい。ガス流量比は装置能力や基板面積に応じて選択されるが、SiH4流量に対してH2流量が5倍程度、PH3の実流量が0.01倍程度であれば好適である。RFパワーと成膜圧力についても装置能力や基板面積に応じて選択されるが、例えば0.1W/cm2、266Paである。電極間距離は、平行平板型のPECVD装置を用いた場合、安定してプラズマ放電が維持されるように調整すればよい。

【0042】

次に、ホトリソグラフィによるパターン形成とその後のドライエッチングにより、第1導電型の半導体膜105と半導体膜104をアイランド状に加工する(図3(c))。このとき、アイランド長はゲート電極長よりも狭くなるように形成される。

【0043】

この後、ソース・ドレイン電極配線を形成するため、基板上に金属膜107を堆積する(図3(c))。金属膜107の材料としてはNb、Mo、W、Ta、Cr、Ti、Fe、Ni、Co等やこれらの合金及びそれらの金属の積層膜を用いることが可能である。また本実施例ではTFT作製の上限温度をトータルプロセスにおいて低下させられることから、AlやCu等の低抵抗金属を用いることも可能である。金属膜107の形成には、例えばスパッタリング法を用いることができる。膜厚は、材料によるが配線抵抗低減のため500nm程度とすればよい。

【0044】

次に、図3(d)に示すように、金属膜107と第1導電型の半導体膜105を加工するため、基板上にレジストを塗布し、ホトリソグラフィによりレジストパターン10を形成する。次に、レジストパターン10をマスクとしたウェットエッチングによってレジストパターン10の開口部の金属膜107を除去し、ソース電極配線7aとドレイン電極配線7bを形成する(図3(e))。金属膜は等方的にエッチングされることから、レジストパターン10の開口幅よりもソース・ドレイン電極の開口幅の方が拡がっている。引き続き,レジストパターン10の開口部の第1導電型半導体膜105と半導体膜104の一部をドライエッチングによって除去することにより,ソース領域のコンタクト層5a、ドレイン領域のコンタクト層5b、及び半導体層4を形成する(図3(f))。ドライエッチングによる除去では、通常の条件ではレジストパターン10の開口幅とコンタクト層5a、5b、半導体層4のエッチング領域幅はほぼ同等となる。

【0045】

次に、ソース電極配線7aとドレイン電極配線7bの離間部において、ソース領域のコンタクト層5aとドレイン領域のコンタクト層5bの露出部に絶縁性半導体層6a、6bを形成する(図3(g))。絶縁性半導体層6a、6bは、レジストパターン10を除去し、次の保護膜8(図1参照)を成膜する前にプラズマ処理を実施して形成するのが好適である。さらにこれと併用して、レジストパターン10のO2(酸素)によるアッシング時にソース領域のコンタクト層5aとドレイン領域のコンタクト層5bの露出部を酸化(絶縁化)して絶縁性半導体層6a、6bを形成してもよい。但し、レジストパターン10のO2アッシング単独では充分な絶縁性半導体層6a、6bを形成できない可能性がある。このため、プラズマ処理との併用が望ましい。プラズマ処理は、保護膜8をPECVD法によって成膜する場合は、同じ装置のチャンバにおいて実施することが可能である。なお、露出されたコンタクト層5a、5bは厚さ方向に全て絶縁性半導体層とすることが最適だが、必要な厚さが確保されていればコンタクト層の抵抗が高くなるためリーク電流低減の効果を得ることができる。

【0046】

プラズマ処理ではN2、N2O、O2といったガスを供給すればよい。成膜条件の代表例を以下に示す。

・装置:平行平板型プラズマCVD ・ガス流量:N2=500sccmなど・RF周波数:13.56MHz ・RFパワー密度0.2W/cm2以上

・電極間隔:20mm前後・基板温度:300℃・成膜圧力:50〜266Pa・処理時間:10分

本実施例では、コンタクト層5a、5bは選択された膜質と膜厚にて形成しているので、このプラズマ処理により絶縁性半導体層6a、6bが形成される。また、このプラズマ処理によって半導体層4の凹部についても絶縁性半導体層が形成されるが、本実施例では半導体層4は数%オーダーでHを含むa−Siからなることから、Pドープ微結晶Siからなるコンタクト層5a、5bよりも絶縁化されにくく形成される層の膜厚は薄い。さらに、本プラズマ処理の後、次の保護膜8を成膜する間に例えばH2プラズマ処理等を行えば、半導体層4の凹部に形成された絶縁性半導体層はさらに薄くなる。なお、半導体層4の凹部では絶縁性半導体層の膜厚が薄いことから、図1や図3には未記載とした。

【0047】

最後に,基板上に保護膜8を形成する。この膜には例えばPECVD法により形成されるSiN膜やSiO膜を適用すればよい。スパッタ法で形成したそれらの膜を適用することも可能である。本実施例ではPECVD法によるSiN膜を適用しており,RF周波数13.56MHz,ガスとしてSiH4、NH3、N2を用い,成膜温度は300℃としている。以上により,図1に示す断面構造のTFTが完成する。

【0048】

図1に示すように、コンタクト層の露出部には絶縁性半導体層6a、6bが形成されている。このため、バックチャネル長(Lb)はソース電極とドレイン電極の間の距離、すなわちチャネル長(Lc)と同じになる。バックチャネル長が長くなることによりリーク電流(ドレイン電流)を低減できることを、図4を用いて説明する。図4は表面側から間接光相当の照度で光照射した一般的なa−SiTFTにおいて、ゲート電圧−5Vを印加したときの光リーク電流のチャネル長依存性を評価した結果である。このゲート電圧のときの光リーク電流はバックチャネルを流れると推測されている。本結果から、チャネル長の増加に伴い、バックチャネルを流れる光リーク電流は低下していることが分かる。チャネルエッチ部の開口部に露出しているコンタクト層の長さは、ソース領域側とドレイン領域側の両方の長さを足し合わせると、約0.4〜1μmとなる場合が多い。このため、露出部に絶縁性半導体層6a、6bを形成すれば、バックチャネル長が増大する効果によって光リーク電流が最大約4/5に低下する。

【0049】

次に、本実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を図5に示す。光はTFT表面側から間接光相当の照度で照射している。コンタクト層のドーピング濃度や膜質を制御して絶縁性半導体層6a、6bを形成した本実施例のTFTでは、およそゲート電圧−10<Vg<0Vにおいてドレイン電流Idが上昇しにくく、光リーク電流が抑制されていることが分かる。0本結果では、同ゲート電圧の範囲において光リーク電流が約40%低下した。

即ち、コンタクト層5a、5bではドーピング濃度を制御しており、且つその露出部には絶縁性半導体層6a、6bを形成していることから、正のドレイン電圧を印加したときでもドレイン領域側のコンタクト層6bと半導体層4の界面とその周辺(特にチャネルエッチ領域側)において空乏層は拡がりにくいこと、また、絶縁性半導体層6bでは電子が輸送されにくくなっていることから正孔との再結合が生じやすいこと等により、本実施例のTFTでは光リーク電流が上昇しにくいという効果が得られたものと考えられる。また、絶縁性半導体層6a、6bの形成によってコンタクト面積が低下するが、コンタクト層の膜質制御によってソース・ドレイン抵抗の上昇が抑制されていることから、TFT特性(特にオン電流)の低下が少ない。図6から、TFTのオン特性(Vg>0V)が若干低下しているが、実用上問題ないレベルであることが分かる。

【0050】

次に本実施例のTFTを用いて表示装置を作製した。図6は、液晶表示装置への適用例であり、本発実施例に係るTFTを用いた液晶表示装置の要部断面図である。液晶516を挟持して基板1と基板510が対向して配置されている。基板1側には、図1に示した本実施例のTFTが形成されている。また層間絶縁膜501、及びコンタクトホールを有する。さらに、透明導電膜からなる画素電極502を有する。画素電極502は、ITO膜をスパッタリング法で形成し、ホトリソグラフィを用いて加工したものである。本実施例では膜厚を70nmとしている。更に、画素電極(透明電極)502上に配向膜503を有する。一方、基板510の上には、ブラックマトリックス(BM)511、カラーフィルタ層512、オーバーコート層513、ITO膜からなる対向電極514、配向膜515が順番に形成されている。

【0051】

本液晶表示装置を用いてバックライトの間接光の影響を調べた結果、TFTの光リーク電流増大起因する表示不良の発生が低減されることが分かった。

なお、図6ではTFTは図1に示した構成のものを示したものであるが、他の実施例に示したTFTであってもよい。

以上、本実施例によれば、バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供することができる。

【実施例2】

【0052】

本発明の第2の実施例について図7と図8を用いて説明する。なお、実施例1に記載され本実施例に未記載の事項は特段の事情が無い限り本実施例にも適用することができる。

【0053】

図7は、本実施例に係る薄膜トランジスタの断面図である。実施例1とは、コンタクト層が2層になっている点が異なる。第1の第1導電型半導体層からなる第1のコンタクト層15a、15bと第2の第1導電型半導体層からなる第2のコンタクト層16a、16bから形成されている。

【0054】

第1のコンタクト層15a、15b、第2のコンタクト層16a、16bには第1導電型のドーピング不純物として例えばPが添加されている。膜質は微結晶Si、a−Si、及びこれらの積層が可能である。これらの形成方法は第1の実施例を参考にすればよい。本実施例では、第1のコンタクト層15a、15bとしてPドープ微結晶Siを形成しており、第2のコンタクト層16aと16bとしてPドープa−Siを形成している。

【0055】

実施例1では、ドレイン電極側のコンタクト層にはPドープ微結晶Siからなるコンタクト層5bしか形成していなかった。このため、コンタクト層5bとドレイン電極配線7bの界面において価電子帯側に形成されるエネルギー障壁が低く、正孔が流れやすかった。従って、図5のように、ゲート電圧が例えば−20V<Vg<−10Vの範囲では光リーク電流が増大して見えていた(本リーク電流は光照射に起因するものではないが、リーク電流は光起因のものと足し合わせになる)。これに対し、本実施例では、Pドープa−Siからなる第2のコンタクト層16bを、Pドープ微結晶Siからなる第1のコンタクト層15bとドレイン電極配線7bの間に形成している。これにより、コンタクト層16bとドレイン電極配線7bの界面において価電子帯側に形成されるエネルギー障壁を高くし、正孔の流れを抑制することができる。図8に本実施例に係るa−SiTFTと従来のa−SiTFTに光照射してTFT特性を評価した結果の一例を示す。図8に示すように、ゲート電圧が例えば−20V<Vg<−10Vの範囲ではリーク電流が低下することが分かる。

【0056】

本実施例のTFTを図6に示す液晶表示装置に適用した結果、実施例1に比べ、表示不良の発生がさらに低減されることが分かった。

以上、本実施例によれば、実施例1と同様の効果を得ることができる。また、露出するコンタクト層を微結晶Siとa−Siの2層構造とすることにより、よりリーク電流を低減することができる。

【実施例3】

【0057】

本発明の第3の実施例について図9を用いて説明する。なお、実施例1又は2に記載され本実施例に未記載の事項は特段の事情が無い限り本実施例にも適用することができる。

【0058】

図9は、本実施例に係る薄膜トランジスタの断面図である。本実施例では、TFTのチャネル層となる半導体層4とソース・ドレイン電極配線7a、7bの側壁にサイド絶縁膜50を形成している。サイド絶縁膜50は例えばシリコン酸化膜からなる。TFTのチャネル層とコンタクト層を例えばドライエッチング法によりアイランド加工した後、表面に残存するレジストをO2アッシングすることによって、レジスト除去とともにサイド酸化膜は形成される。

【0059】

特に本実施例のようなゲート遮光構造のボトムゲートTFTでは、負のゲート電圧が増大してドレイン電極に高電界が印加されたとき、チャネル層4の側壁とドレイン電極7b間でリーク電流が流れやすい。特にチャネル層が微結晶Siや多結晶Siから成る場合は、チャネル層4の側壁とドレイン電極配線7bの界面において価電子帯側に形成されるエネルギー障壁が低く、正孔が流れやすいことからリーク電流が増大しやすい。サイド絶縁膜50にはこのリーク電流が流れるのをブロックする効果がある。

【0060】

本実施例のTFTを図6に示す液晶表示装置に適用した結果、実施例2に比べ、表示不良の発生がさらに低減されることが分かった。

以上、本実施例によれば、実施例1と同様の効果を得ることができる。また、チャネル層となる半導体層とドレイン電極配線の側壁にサイド絶縁膜を形成することにより、よりリーク電流を低減することができる。

【実施例4】

【0061】

本発明の第4の実施例について図10を用いて説明する。なお、実施例1乃至3のいずれかに記載され本実施例に未記載の事項は特段の事情が無い限り本実施例にも適用することができる。

【0062】

図10は、本実施例に係る薄膜トランジスタの断面図である。ゲート遮光構造を有するボトムゲート・チャネルエッチストッパ型のコンタクト層の露出部に、実施例1に記載した方法と同様にして絶縁性半導体膜を形成している。

【0063】

本実施例のTFTは、絶縁基板301、ゲート電極配線302、ゲート絶縁膜303、チャネル層となる半導体層304、絶縁膜からなるストッパ層305、コンタクト層となる第1導電型半導体層306a、306b、ソース電極配線307a、ドレイン電極配線307、絶縁性半導体層308a、308b、保護膜309から成る。ストッパ層305には半導体層304にHを拡散しやすくするため、SiN膜が好適である。以上の形成方法は第1の実施例を参考にすればよい。

【0064】

コンタクト層306a、306bが開口部に露出している場合、TFTの表面側から間接光が入射したとき、コンタクト層306a、306bの露出部においてキャリア(電子−正孔対)が発生しやすく、ドレインに正の電圧を印加したときドレイン電極側では電子がドレイン電極配線307bに流れやすい。このため、光リーク電流が上昇しやすい。これに対して本実施例では、コンタクト層306a、306bの露出部に絶縁性半導体層308a、308bを形成している。絶縁性半導体層308a、308bでは光照射によるキャリア(電子−正孔対)の発生は少なく、電子がドレイン電極配線307b側に輸送されにくいことから、光リーク電流の上昇が抑制される。

【0065】

なお本構造のTFTでは、実施例1に比べてストッパ層305を形成するために、成膜工程、ホトリソグラフィ工程、エッチング工程が増えてしまう。しかし、上記やa−Si層の膜厚を薄くできる利点もあることから、実施例1に対しても光リーク電流の上昇が抑制されやすい。

【0066】

本実施例のTFTを図6に示す液晶表示装置に適用し、バックライトの間接光の影響を調べた結果、TFTの光リーク電流増大起因する表示不良の発生が低減されることが分かった。

以上、本実施例によれば、実施例1と同様の効果を得ることができる。また、ストッパ層を設けることにより、よりリーク電流を低減することができる。

【0067】

なお、本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。例えば、上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施例の構成の一部を他の実施例の構成に置き換えることも可能であり、また、ある実施例の構成に他の実施例の構成を加えることも可能である。また、各実施例の構成の一部について、他の構成の追加・削除・置換をすることが可能である。

【符号の説明】

【0068】

1…絶縁基板、2…ゲート電極配線、3…ゲート絶縁膜、4…チャネルとなる半導体層、5a、5b…コンタクト層となる第1導電型半導体層、6a、6b…絶縁性半導体層、7a…ソース電極配線、7b…ドレイン電極配線、8…保護膜、10…レジストパターン、15a、15b…第1の第1導電型半導体層からなる第1のコンタクト層、16a、16b…第2の第1導電型半導体層からなる第2のコンタクト層、50…サイド絶縁膜、104…半導体膜、105…第1導電型半導体膜、107…金属膜、201…基板、202…ゲート電極層、203…ゲート絶縁膜、209…半導体層、210a、210b…不純物半導体層(ソース領域、ドレイン領域)、213a…ソース電極、213b…ドレイン電極、214…変質層(絶縁層)、215…絶縁層、301…絶縁基板、302…ゲート電極配線、303…ゲート絶縁膜、304…チャネル層となる半導体層、305…ストッパ層、306a、306b…コンタクト層となる第1導電型半導体層、307a…ソース電極配線、307b…ドレイン電極配線、308a、308b…絶縁性半導体層、309…保護膜、501…層間絶縁膜、502…透明電極(画素電極)、503…配向膜、510…基板、511…ブラックマトリックス(BM)、512…カラーフィルタ層、513…オーバーコート層、514…対向電極、515…配向膜、516…液晶。

【特許請求の範囲】

【請求項1】

表示装置用のボトムゲート型の薄膜トランジスタであって、

基板と、

前記基板上に形成されたゲート電極配線と、

前記ゲート電極配線上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、

前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、

前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、

鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタ。

【請求項2】

請求項1記載の薄膜トランジスタにおいて、

前記第1の半導体層は水素を含み、非晶質Si、微結晶Si、多結晶Si又はこれらの積層膜であることを特徴とする薄膜トランジスタ。

【請求項3】

請求項2記載の薄膜トランジスタにおいて、

前記第1の半導体層の水素濃度は、1×1020cm−3以上、5×1021cm−3以下であることを特徴とする薄膜トランジスタ。

【請求項4】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層は、微結晶Si又は非晶質Siであることを特徴とする薄膜トランジスタ。

【請求項5】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層は、15〜30nmの厚さを有することを特徴とする薄膜トランジスタ。

【請求項6】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層の不純物濃度は、1×1018cm−3以上、1×1020cm−3以下であることを特徴とする薄膜トランジスタ。

【請求項7】

請求項1記載の薄膜トランジスタにおいて、

前記絶縁性半導体層は、窒素や酸素を含むことを特徴とする薄膜トランジスタ。

【請求項8】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層は、前記第1の半導体層側が微結晶Si層、前記ソース電極配線又はドレイン電極配線側が非晶質Si層の2層膜であることを特徴とする薄膜トランジスタ。

【請求項9】

請求項1記載の薄膜トランジスタにおいて、

前記第1の半導体層の側壁にはサイド絶縁膜が形成されていることを特徴とする薄膜トランジスタ。

【請求項10】

請求項1記載の薄膜トランジスタにおいて、

前記第1の半導体層の上には絶縁膜からなるストッパ層が更に形成され、

前記絶縁性半導体層が形成されている前記第2の半導体層端部は、前記ストッパ層の上部まで延伸して形成されていることを特徴とする薄膜トランジスタ。

【請求項11】

表示装置用のボトムゲート・チャネルエッチ型の薄膜トランジスタであって、

基板と、

前記基板上に形成されたゲート電極配線と、

前記ゲート電極配線上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、

前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、

前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、

前記基板は、液晶を介して、ブラックマトリクスを備えた対向基板と対向して配置されるものであり、

前記第1の半導体層の厚さは、前記第2の半導体層や前記絶縁性半導体層が形成されている領域よりも形成されていない領域の方が薄く、

鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタ。

【請求項1】

表示装置用のボトムゲート型の薄膜トランジスタであって、

基板と、

前記基板上に形成されたゲート電極配線と、

前記ゲート電極配線上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、

前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、

前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、

鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタ。

【請求項2】

請求項1記載の薄膜トランジスタにおいて、

前記第1の半導体層は水素を含み、非晶質Si、微結晶Si、多結晶Si又はこれらの積層膜であることを特徴とする薄膜トランジスタ。

【請求項3】

請求項2記載の薄膜トランジスタにおいて、

前記第1の半導体層の水素濃度は、1×1020cm−3以上、5×1021cm−3以下であることを特徴とする薄膜トランジスタ。

【請求項4】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層は、微結晶Si又は非晶質Siであることを特徴とする薄膜トランジスタ。

【請求項5】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層は、15〜30nmの厚さを有することを特徴とする薄膜トランジスタ。

【請求項6】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層の不純物濃度は、1×1018cm−3以上、1×1020cm−3以下であることを特徴とする薄膜トランジスタ。

【請求項7】

請求項1記載の薄膜トランジスタにおいて、

前記絶縁性半導体層は、窒素や酸素を含むことを特徴とする薄膜トランジスタ。

【請求項8】

請求項1記載の薄膜トランジスタにおいて、

前記第2の半導体層は、前記第1の半導体層側が微結晶Si層、前記ソース電極配線又はドレイン電極配線側が非晶質Si層の2層膜であることを特徴とする薄膜トランジスタ。

【請求項9】

請求項1記載の薄膜トランジスタにおいて、

前記第1の半導体層の側壁にはサイド絶縁膜が形成されていることを特徴とする薄膜トランジスタ。

【請求項10】

請求項1記載の薄膜トランジスタにおいて、

前記第1の半導体層の上には絶縁膜からなるストッパ層が更に形成され、

前記絶縁性半導体層が形成されている前記第2の半導体層端部は、前記ストッパ層の上部まで延伸して形成されていることを特徴とする薄膜トランジスタ。

【請求項11】

表示装置用のボトムゲート・チャネルエッチ型の薄膜トランジスタであって、

基板と、

前記基板上に形成されたゲート電極配線と、

前記ゲート電極配線上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜を介して前記ゲート電極配線上に形成されたチャネルとなる第1の半導体層と、

前記半導体層上に互いに離間して形成され、第1及び第2のコンタクト層となる第2の半導体層と、

前記第2の半導体層を介して前記第1の半導体層上に形成されたソース電極配線又はドレイン電極配線と、を有し、

前記基板は、液晶を介して、ブラックマトリクスを備えた対向基板と対向して配置されるものであり、

前記第1の半導体層の厚さは、前記第2の半導体層や前記絶縁性半導体層が形成されている領域よりも形成されていない領域の方が薄く、

鉛直上方から見て、前記ソース電極配線又は前記ドレイン電極配線に対して露出する前記第2の半導体層の露出部には、絶縁性半導体層が形成されていることを特徴とする薄膜トランジスタ。

【図1】

【図2】

【図3(a)】

【図3(b)】

【図3(c)】

【図3(d)】

【図3(e)】

【図3(f)】

【図3(g)】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3(a)】

【図3(b)】

【図3(c)】

【図3(d)】

【図3(e)】

【図3(f)】

【図3(g)】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−105873(P2013−105873A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−248427(P2011−248427)

【出願日】平成23年11月14日(2011.11.14)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月14日(2011.11.14)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

[ Back to top ]