薄膜形成基板、薄膜形成方法、及び表示装置の製造方法

【課題】基板に生じるクラックの発生を防止した薄膜形成方法を提供する。

【解決手段】薄膜形成方法は、基板を準備する基板準備工程と、基板上に第1薄膜を形成する第1薄膜形成工程と、第1薄膜に対して光線を相対走査して照射することにより、第1薄膜を結晶化する結晶化工程と、結晶化工程において第1薄膜に生じる熱の基板への伝導量を低下させる緩和層を、結晶化工程の前に、基板の端部領域及び基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

【解決手段】薄膜形成方法は、基板を準備する基板準備工程と、基板上に第1薄膜を形成する第1薄膜形成工程と、第1薄膜に対して光線を相対走査して照射することにより、第1薄膜を結晶化する結晶化工程と、結晶化工程において第1薄膜に生じる熱の基板への伝導量を低下させる緩和層を、結晶化工程の前に、基板の端部領域及び基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜形成基板及びその製造方法に関し、特に、表示装置の画素回路が形成された薄膜形成基板及びその製造方法に関するものである。

【背景技術】

【0002】

近年、液晶ディスプレイに変わる次世代フラットパネルディスプレイの一つとしての有機材料のEL(Electro luminescence)を利用した有機ELディスプレイが注目されている。

【0003】

有機ELディスプレイは、電圧駆動型の液晶ディスプレイと異なり、電流駆動型のディスプレイデバイスである。このことから、アクティブマトリクス方式の表示装置の駆動回路として優れた特性を有する薄膜トランジスタ(TFT:Thin Film Transistor)の開発が急がれている。薄膜トランジスタは、画素を選択するスイッチング素子、或いは画素を駆動する駆動トランジスタ等として用いられる。

【0004】

従来の薄膜トランジスタ及びその製造方法は、例えば、特許文献1及び特許文献2に開示されている。特許文献1、2によれば、薄膜トランジスタは、基板上に薄膜を順次積層することによって形成される。また、薄膜トランジスタのオン特性を向上させるために、チャネル領域となる半導体膜にレーザを照射して、多結晶化することが知られている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−332303号公報

【特許文献2】特開平5−21344号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記方法で製造された薄膜トランジスタには、図13に示されるように、基板の表面から内部に向かって延びるクラックが大量発生する課題がある。このクラックの発生原因の一例を、図14を用いて説明する。

【0007】

まず、基板900の表面には、最初からマイクロクラック910が存在する。このマイクロクラック910は、基板900に必ず存在するものであり、薄膜トランジスタの性能に影響を与えるものではない。しかしながら、基板900上に積層された半導体膜にレーザを照射することによって基板900が高温になり、冷却することによって基板900に図14の矢印の方向の引張応力が生じる。そして、この引張応力によって、マイクロクラック910が伸展して大きなクラック920になると考えられる。

【0008】

この課題は、マイクロクラック910が多い基板周辺部において特に顕著である。また、冷却時にクラック920が生じなくとも、基板900に引張応力が残留していることにより、基板900を切断する際にクラックが大量発生する課題がある。

【0009】

本発明は、上記の課題に鑑みてなされたものであり、基板に生じるクラックの発生を防止した薄膜形成基板及び薄膜形成方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の一形態に係る薄膜形成方法は、基板を準備する基板準備工程と、前記基板上に第1薄膜を形成する第1薄膜形成工程と、前記第1薄膜に対して光線を相対走査して照射することにより、前記第1薄膜を結晶化する結晶化工程と、前記結晶化工程において前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層を、前記結晶化工程の前に、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

【発明の効果】

【0011】

本発明によれば、基板に生じるクラックの発生を防止した薄膜形成基板及び薄膜形成方法を得ることができる。

【図面の簡単な説明】

【0012】

【図1】図1は、実施の形態1に係る薄膜半導体装置の構造を示す断面図である。

【図2A】図2Aは、実施の形態に係る薄膜半導体装置の製造方法における基板準備工程を模式的に示した断面図である。

【図2B】図2Bは、実施の形態1に係る薄膜半導体装置の製造方法におけるゲート電極/緩和層形成工程を模式的に示した断面図である。

【図2C】図2Cは、実施の形態1に係る薄膜半導体装置の製造方法におけるゲート絶縁膜形成工程を模式的に示した断面図である。

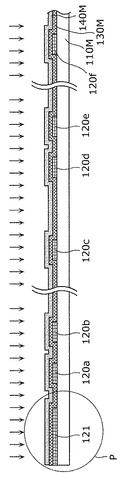

【図2D】図2Dは、実施の形態1に係る薄膜半導体装置の製造方法におけるシリコン薄膜形成工程を模式的に示した断面図である。

【図2E】図2Eは、実施の形態1に係る薄膜半導体装置の製造方法におけるチャネル層形成工程を模式的に示した断面図である。

【図2F】図2Fは、実施の形態1に係る薄膜半導体装置の製造方法におけるチャネル保護層形成工程を模式的に示した断面図である。

【図2G】図2Gは、実施の形態1に係る薄膜半導体装置の製造方法におけるソース電極/ドレイン電極形成工程を模式的に示した断面図である。

【図2H】図2Hは、実施の形態1に係る薄膜半導体装置の製造方法における層間絶縁膜形成工程を模式的に示した断面図である。

【図2I】図2Iは、実施の形態1に係る薄膜半導体装置の製造方法におけるEL層形成工程を模式的に示した断面図である。

【図2J】図2Jは、実施の形態1に係る薄膜半導体装置の製造方法における前面ガラス取り付け工程を模式的に示した断面図である。

【図2K】図2Kは、実施の形態1に係る薄膜半導体装置の製造方法における切断工程を模式的に示した断面図である。

【図3A】図3Aは、緩和層を設けない場合の図2DのP部の拡大断面図である。

【図3B】図3Bは、緩和層を設けた場合の図2DのP部の拡大断面図である。

【図3C】図3Cは、緩和層の位置を示すマザー基板110Mの平面図である。

【図4】図4は、シリコン薄膜のレーザ光の吸収率を示す図である。

【図5】図5は、実施の形態2に係る薄膜半導体装置の構造を示す断面図である。

【図6A】図6Aは、実施の形態2に係る薄膜半導体装置の製造方法におけるゲート電極形成工程を模式的に示した断面図である。

【図6B】図6Bは、実施の形態2に係る薄膜半導体装置の製造方法における緩和層形成工程を模式的に示した断面図である。

【図7】図7は、アンダーコート層の膜厚とシリコン薄膜を結晶化する際のマザー基板の表面温度との関係を示す図である。

【図8】図8は、実施の形態3に係る薄膜半導体装置の構造を示す断面図である。

【図9A】図9Aは、実施の形態3に係る薄膜半導体装置の製造方法における緩和層形成工程を模式的に示した断面図である。

【図9B】図9Bは、実施の形態3に係る薄膜半導体装置の製造方法における結晶化工程を模式的に示した断面図である。

【図9C】図9Cは、実施の形態3に係る薄膜半導体装置の製造方法におけるチャネル層形成工程を模式的に示した断面図である。

【図10A】図10Aは、緩和層が形成される位置の一例を示すマザー基板の平面図である。

【図10B】図10Bは、緩和層が形成される位置の一例を示すマザー基板の平面図である。

【図11】図11は、本発明の実施の形態に係る薄膜半導体装置を用いた画素の回路構成を示す図である。

【図12】図12は、従来の薄膜半導体装置の構成を示す断面図である。

【図13】図13は、クラックが発生した基板の断面の様子を示す図である。

【図14】図14は、基板にクラックが発生する理由を説明するための図である。

【発明を実施するための形態】

【0013】

本発明の一形態に係る薄膜形成方法は、基板を準備する基板準備工程と、前記基板上に第1薄膜を形成する第1薄膜形成工程と、前記第1薄膜に対して光線を相対走査して照射することにより、前記第1薄膜を結晶化する結晶化工程と、前記結晶化工程において前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層を、前記結晶化工程の前に、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

【0014】

上記のように、第1薄膜に生じる熱の伝導量を低下させる緩和層を基板の一部に設けることにより、緩和層が重畳する位置において、基板にクラックが生じるのを有効に防止することができる。なお、「第1薄膜」は、例えば、薄膜トランジスタ(薄膜半導体装置)のチャネル層となるシリコン薄膜であってもよい。

【0015】

また、前記緩和層は、前記基板と前記第1薄膜との間に形成され、前記緩和層に重畳する位置の前記第1薄膜の前記光線の吸収率を低下させることによって、前記基板への熱伝導量を低下させるものであってもよい。

【0016】

また、前記緩和層は、前記光線を反射する材料で形成され、前記第1薄膜に照射される前記光線と、前記緩和層で反射された光線とを光学干渉させることによって、前記第1薄膜の前記光線の吸収率を低下させるものであってもよい。

【0017】

また、前記緩和層は、金属材料で形成されてもよい。

【0018】

さらに、該薄膜形成方法は、前記基板と前記第1薄膜との間に第2薄膜を形成する第2薄膜形成工程を含んでもよい。そして、前記緩和層は、前記第1及び第2薄膜の平均膜厚が前記基板の中央領域より10%〜20%薄い前記基板の端領域にのみ形成されてもよい。なお、「第2薄膜」は、例えば、薄膜トランジスタ(薄膜半導体装置)のゲート絶縁膜であってもよい。

【0019】

また、前記緩和層は、膜厚が500nm〜1000nmであり、前記基板と前記第1薄膜との間に形成されてもよい。

【0020】

また、前記緩和層は、無機材料で形成されてもよい。

【0021】

さらに、前記緩和層は、有機材料と無機材料との混合材料であってもよい。

【0022】

さらに、該薄膜形成方法は、前記基板上に第3薄膜を形成する第3薄膜形成工程を含んでもよい。そして、前記緩和層は、前記第1及び第3薄膜の間に形成されてもよい。なお、「第3薄膜」は、例えば、薄膜トランジスタ(薄膜半導体装置)のアンダーコート層であってもよい。

【0023】

また、前記第3薄膜は、酸化珪素膜であってもよく、前記緩和層は、SOG(Spin On Glass)膜であってもよい。

【0024】

また、前記緩和層は、前記第1薄膜上に形成され、前記光線を遮光することによって、前記第1薄膜から前記基板への熱伝導量を低下させるものであってもよい。

【0025】

また、前記緩和層は、金属材料で形成されてもよい。

【0026】

具体的には、前記金属材料は、MoW、W、Ta、Cr、Cu、Alのいずれかを含んでもよい。

【0027】

また、前記緩和層の前記光線の反射率は、60%以上であってもよい。

【0028】

また、前記結晶化工程で結晶化された前記第1薄膜に含まれる結晶粒の平均粒径は、50nm以上、1μm以下であってもよい。

【0029】

また、前記光線は、連続発振のレーザ光線であってもよく、前記レーザ光線の波長は、532nmであってもよい。

【0030】

さらに、前記薄膜形成方法は、前記結晶化工程の後に、前記緩和層に重畳する位置に切断線が位置するように、前記基板を切断する工程を含んでもよい。

【0031】

また、前記基板は、クラック、チッビンク、切欠、のいずれかを有してもよい。

【0032】

また、前記緩和層は、前記基板の端部のうち、前記光線の相対走査方向に交差する側の端部にのみ形成されてもよい。

【0033】

また、前記第1薄膜は、シリコンを含有する材料で構成されてもよい。

【0034】

本発明の一形態に係る表示装置の製造方法は、上記記載の薄膜形成方法を含む。

【0035】

本発明の一形態に係る薄膜形成基板は、基板と、前記基板上に形成され、光線が照射されることによって結晶化された第1薄膜と、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に、前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層とを備える。

【0036】

(実施の形態1)

図1を参照して、本発明の実施の形態1に係る薄膜形成基板の構成を説明する。図1は、本実施の形態1に係る薄膜形成基板の一例である薄膜半導体装置100の模式的な構成を示す断面図である。

【0037】

薄膜半導体装置100は、図1に示されるように、基板110と、ゲート電極120a、120b、120c及び緩和層121と、ゲート絶縁膜130と、チャネル層140a、140b、140cと、チャネル保護層150a、150b、150cと、ソース電極161a、161b、161c及びドレイン電極162a、162b、162cと、層間絶縁膜170と、EL層180と、前面ガラス190とを、この順に積層して構成される。

【0038】

図1に示される薄膜半導体装置100は、例えば、複数の画素を有する表示パネルである。そして、薄膜半導体装置100には、画素毎にボトムゲート型の薄膜トランジスタが形成されている。

【0039】

基板110は、例えば、石英ガラス、無アルカリガラス、高耐熱性ガラス等のガラス材料からなるガラス基板である。なお、ガラス基板の中に含まれるナトリウムやリン等の不純物がチャネル層140a、140b、140cに侵入することを防止するために、基板110上にシリコン窒化膜(SiNx)、酸化シリコン(SiOy)又はシリコン酸窒化膜(SiOyNx)等からなるアンダーコート層を形成してもよい。また、アンダーコート層は、レーザアニールなどの高温熱処理プロセスにおいて、基板110への熱の影響を緩和させる役割を担うこともある。アンダーコート層の膜厚は、例えば100nm〜2000nm程度とすることができる。

【0040】

ゲート電極120aは、基板110上に所定形状でパターン形成される。ゲート電極120aを構成する材料としては、例えば、モリブデン(Mo)、タンタル(Ta)、アルミニウム(Al)、銅(Cu)、タングステン(W)、チタン(Ti)、クロム(Cr)、及びモリブデンタングステン(MoW)等を用いることができる。ゲート電極120aの膜厚は、例えば20〜500nm程度とすることができる。ゲート電極120b、120cについても同様である。

【0041】

実施の形態1に係る緩和層121は、基板110上の端部領域にパターン形成される。より具体的には、緩和層121は、ゲート電極120a〜120cと同一の層に、ゲート電極120a〜120cと同一の材料で形成される。なお、図1では、基板110上の一方側(図1の左側)の端部にのみ緩和層121を設けた例を示したが、これに限ることなく、他方側(図1の右側)の端部にも緩和層121を設けてもよい。さらには、図1の手前側及び奥側の端部にも緩和層121を設けてもよい。

【0042】

この緩和層121は、薄膜半導体装置100を搬送する際の外力、あるいは薄膜半導体装置100が長期期間で使用される際の熱応力等で基板110に作用する応力を緩和する応力緩和層として機能する。すなわち、薄膜半導体装置100に作用する外力、熱応力によって基板110にクラックが発生、伸展するのを有効に防止することができる。

【0043】

ゲート絶縁膜130は、ゲート電極120a、120b、120c及び緩和層121を覆うように、基板110の上面全域に形成される。ゲート絶縁膜130を構成する材料としては、例えば、酸化シリコン(SiOy)、窒化シリコン(SiNx)、シリコン酸窒化膜(SiOyNx)、酸化アルミニウム(AlOz)又は酸化タンタル(TaOw)の単層膜又はこれらの積層膜によって構成することができる。ゲート絶縁膜130の膜厚は、例えば50nm〜300nmとすることができる。

【0044】

なお、本実施の形態1では、後述するようにチャネル層140a、140b、140cを結晶性シリコン薄膜で形成しているので、ゲート絶縁膜130に酸化シリコンを用いることが好ましい。酸化シリコンは、チャネル層140a、140b、140cとゲート絶縁膜130との界面状態を良好にするのに適しており、これによって薄膜半導体装置100の閾値電圧特性が向上する。

【0045】

チャネル層140aは、ゲート絶縁膜130上のゲート電極120aに重畳する位置にパターン形成される半導体膜であって、ゲート電極120aの電圧によってキャリアの移動が制御される領域である所定のチャネル領域を有する。なお、チャネル層140b、140cについても同様である。チャネル層140a〜140cの膜厚は、例えば、30nm〜100nm程度とすることができる。

【0046】

チャネル層140a〜140cは、結晶性の組織構造を有する結晶性シリコン薄膜であって、例えば、非結晶性の非晶質シリコン(アモルファスシリコン)を結晶化することによって形成することができる。また、チャネル層140a〜140cには、平均結晶粒径が100nm以上の多結晶、あるいは、平均結晶粒径が10nm〜100nmのマイクロクリスタル(μc)と呼ばれる微結晶が含まれる。さらに、チャネル層140a〜140cに含まれるシリコン結晶の主面方位は[100]であることが好ましい。これにより、結晶性に優れたチャネル層140a〜140cを形成することができる。

【0047】

チャネル保護層150aは、チャネル層140a上に形成され、チャネル層140aを保護するチャネルエッチングストッパ(CES)層として機能する。すなわち、チャネル保護層150aは、ソース電極161a及びドレイン電極162aのエッチング処理時において、チャネル層140aがエッチングされることを防止する機能を有する。チャネル保護層150b、150cも同様である。

【0048】

チャネル保護層150a〜150cを形成する材料には、例えば、シリコン、酸素及びカーボンを含む有機材料を主として含有する有機材料を用いることができる。本実施の形態1におけるチャネル保護層150a〜150cは、感光性塗布型の有機材料をパターニング及び固化することによって形成することができる。

【0049】

また、チャネル保護層150a〜150cを構成する有機材料には、例えば、有機樹脂材料、界面活性剤、溶媒及び感光剤が含まれる。有機樹脂材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン等の中の1種又は複数種からなる感光性又は非感光性の有機樹脂材料を用いることができる。界面活性剤としては、シロキサン等のシリコン化合物からなる界面活性剤を用いることができる。溶媒としては、プロピレングリコールモノメチルエーテルアセテート又は1,4−ジオキサン等の有機溶媒を用いることができる。また、感光剤としては、ナフトキノンジアジト等のポジ型感光剤を用いることができる。なお、感光剤には、炭素だけではなく硫黄も含まれている。

【0050】

チャネル保護層150a〜150cを形成する場合、上記の有機材料をスピンコート法等の塗布法を用いて形成することができる。なお、チャネル保護層150a〜150cの形成には、塗布法だけではなく、滴吐出法等その他の方法を用いることもできる。例えば、スクリーン印刷やオフセット印刷等の所定のパターンを形成することができる印刷法等を用いることにより、所定形状の有機材料を選択的に形成することもできる。

【0051】

チャネル保護層150a〜150cの膜厚は、例えば、300nm〜1000nmとすることができる。チャネル保護層150a〜150cの膜厚の下限は、エッチングによるマージン及びチャネル保護層150a〜150c中の固定電荷の影響を抑制すること等を考慮して決定される。また、チャネル保護層150a〜150cの膜厚の上限は、段差の増大に伴うソース電極161a〜161c及びドレイン電極162a〜162cの製造プロセスの信頼性の低下を抑制することを考慮して決定される。

【0052】

ソース電極161a及びドレイン電極162aは、チャネル保護層150a上のチャネル層140aに重畳する位置にパターン形成される。また、ソース電極161aとドレイン電極162aとは、互いに所定の間隔をあけて対向配置される。ソース電極161b、161c及びドレイン電極162b、162cも同様である。

【0053】

本実施の形態1において、ソース電極161a及びドレイン電極162aは、導電性材料及びその合金等の単層構造又は多層構造とすることができる。例えば、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)、銅(Cu)、タンタル(Ta)、チタン(Ti)及びクロム(Cr)等によって構成される。本実施の形態1では、ソース電極161a及びドレイン電極162aは、MoW/Al/MoWの三層構造によって形成されている。ソース電極161a及びドレイン電極162aの膜厚は、例えば、100nm〜500nm程度とすることができる。

【0054】

なお、チャネル層140aとチャネル保護層150aとの間に、さらにバックチャネル層(図示省略)を形成してもよい。バックチャネル層は、例えば、意図的に不純物のドーピングを行っていないアモルファスシリコン膜(真性アモルファスシリコン)によって形成されている。このバックチャネル層は、局在準位密度(トラップ密度)がチャネル層140aより高い。すなわち、バックチャネル層の負キャリアの電荷密度によってチャネル保護層150aの正の固定電荷を相殺して電界遮蔽を行うことができる。これにより、バックチャネルの形成を抑制することができ、オフ時のリーク電流を抑制することができるので、薄膜トランジスタのオフ特性が向上する。

【0055】

また、チャネル保護層150aとソース電極161a及びドレイン電極162aとの間に、さらにコンタクト層(図示省略)を形成してもよい。コンタクト層は、不純物を高濃度に含む非晶質半導体膜であり、1×1019[atm/cm3]以上の高濃度の不純物を含むn+層である。より具体的には、コンタクト層は、アモルファスシリコンに不純物としてリン(P)をドーピングしたn型半導体膜によって構成することができる。また、コンタクト層の膜厚は、例えば5nm〜100nmとすることができる。

【0056】

さらに、コンタクト層は、下層の低濃度の電界緩和層(n−層)と上層の高濃度のコンタクト層(n+層)との2層から構成されてもよい。低濃度の電界緩和層には、1×1017[atm/cm3]程度のリンがドーピングされている。上記2層は、CVD(Chemical Vapor Deposition)装置において連続的に形成することが可能である。

【0057】

層間絶縁膜170は、ソース電極161a、161b、161c及びドレイン電極162a、162b、162cを覆うように、基板110の上面全域に積層される。層間絶縁膜170を構成する材料としては、例えば、酸化シリコン(SiOy)、窒化シリコン(SiNx)、シリコン酸窒化膜(SiOyNx)、酸化アルミニウム(AlOz)又は酸化タンタル(TaOw)の単層膜又はこれらの積層膜によって構成することができる。また、層間絶縁膜170は、その上面が平坦になる平坦化膜として機能する。

【0058】

EL層180は、画素毎に形成される陽極と、画素毎に形成される発光層と、全画素に共通に形成される陰極とで形成される。また、隣接する陽極(発光層)の間には、バンクが形成されている。

【0059】

陽極は、例えば、モリブデン、アルミニウム、金、銀、銅などの導電性金属若しくはそれらの合金、PEDOT:PSSなどの有機導電性材料、酸化亜鉛、又は、鉛添加酸化インジウムのいずれかで形成される反射電極である。一方、陰極は、例えば、ITO、SnO2、In2O3、ZnO又はこれらの組み合わせなどで形成される透明電極である。

【0060】

発光層は、正孔注入層、正孔輸送層、発光層、電子輸送層、及び電子注入層などの各層を積層して構成される。例えば、正孔注入層として銅フタロシアニンを、正孔輸送層としてα−NPD(Bis[N−(1−Naphthyl)−N−Phenyl]benzidine)を、発光層としてAlq3(tris(8−hydroxyquinoline)aluminum)を、電子輸送層としてオキサゾール誘導体を、電子注入層としてAlq3を用いることができる。

【0061】

前面ガラス190は、EL層180上に積層される透明ガラスである。この前面ガラス190は、EL層180を保護するためのものであり、例えば、基板110と同一の材料で形成することができる。なお、前面ガラス190を構成する材料はガラスに限定されず、透明樹脂等を用いてもよい。

【0062】

次に、図2A〜図2Kを参照して、本発明の実施の形態1に係る薄膜半導体装置の製造方法を説明する。図2A〜図2Kは、本発明の実施の形態1に係る薄膜半導体装置の製造方法における各工程の構成を模式的に示した断面図である。

【0063】

まず、図2Aに示されるように、マザー基板110Mを準備する。このマザー基板110Mは、例えば、図1の基板110の数倍の大きさであって、例えば、薄膜トランジスタを形成した後に、基板110の大きさに切断される。より具体的には、マザー基板110Mは、2200mm×2500mmのG8基板であってもよい。なお、マザー基板110Mには、マイクロクラック、チッビング、切欠等が含まれている。これらは、マザー基板110Mの製造工程や搬送時に形成されるものであり、薄膜半導体装置100の性能には直接影響しない程度の傷である。

【0064】

また、ゲート電極120a〜120fを形成する前に、プラズマCVD等によってマザー基板110M上にシリコン窒化膜、シリコン酸化膜、及びシリコン酸窒化膜などからなるアンダーコート層を形成してもよい。

【0065】

次に、図2Bに示されるように、マザー基板110M上に、所定形状のゲート電極120a、120b、120c、120d、120e、120f及び緩和層121を形成する。例えば、マザー基板110M上にMoWからなるゲート金属膜をスパッタによって成膜し、フォトリソグラフィ法及びウェットエッチング法を用いてゲート金属膜をパターニングすることにより、所定形状のゲート電極120a〜120f及び緩和層121を形成することができる。MoWのウェットエッチングは、例えば、リン酸(HPO4)、硝酸(HNO3)、酢酸(CH3COOH)及び水を所定の配合で混合した薬液を用いて行うことができる。

【0066】

次に、図2Cに示されるように、ゲート電極120a〜120f及び緩和層121を覆うように、マザー基板110Mの上面全域にゲート絶縁膜130Mを形成する。例えば、酸化シリコンからなるゲート絶縁膜130MをプラズマCVD等によって成膜する。酸化シリコンは、例えば、シランガス(SiH4)と亜酸化窒素ガス(N2O)とを所定の濃度比で導入することで、成膜することができる。

【0067】

次に、図2Dに示されるように、ゲート絶縁膜130Mの上面全域に、非晶質のシリコン薄膜140Mを形成する。例えば、シリコン薄膜140Mは、アモルファスシリコン(非晶質シリコン)をプラズマCVD等によって成膜することができる。なお、シリコン薄膜140Mは、例えば、シランガス(SiH4)と水素ガス(H2)とを所定の濃度比で導入することで、成膜することができる。そして、成膜されたシリコン薄膜140Mには、500℃の脱水素アニール処理が施される。

【0068】

そして、図2Dに示されるように、シリコン薄膜140Mをレーザアニールして結晶化させる。例えば、ビーム形状が5mm×30μmで、波長が400nm〜900nm(より好ましくは、532nm)のCWレーザをシリコン薄膜140Mに照射することにより、シリコン薄膜140Mをアモルファスシリコンの融点である1414℃以上の温度範囲に上昇させる。これにより、溶融範囲を経て結晶化したシリコンは、溶融して体積が縮小した後に体積膨張を伴って結晶化し、平均粒径が50nm以上、1μm以下のp−Si(多結晶シリコン)となる。

【0069】

シリコン薄膜140Mを結晶化させる工程を、図3A〜図3Cを参照して詳しく説明する。図3A及び図3Bは、図2DのP部の拡大断面図であって、緩和層121を設けない場合(図3A)と、緩和層121を設けた場合(図3B)とを示す図である。図3Cは、緩和層121の位置を示すマザー基板110Mの平面図である。

【0070】

まず、緩和層121を設けずにゲート絶縁膜130M及びシリコン薄膜140MをプラズマCVDで成膜した場合、図3Aに示されるように、マザー基板110Mの端部において、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が薄くなる。マザー基板110Mの端部領域におけるゲート絶縁膜130M及びシリコン薄膜140Mの膜厚は、マザー基板110Mの中央領域の膜厚と比較して10%〜20%薄くなる。但し、図3Aでは、説明のために膜厚の差を誇張して図示している。これは、プラズマCVD装置が発生させるプラズマの密度が中央部(マザー基板110Mの中央領域に相当)で密となり、周辺部(マザー基板110Mの端部領域に相当)で疎となることが一因である。

【0071】

そこで、本実施の形態1に係る薄膜半導体装置100では、図3B及び図3Cに示されるように、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が薄くなるマザー基板110Mの端部領域に緩和層121を設けている。そして、シリコン薄膜140Mが形成されたマザー基板110Mに対して、例えば図3Cに示されるようにレーザ光を相対走査することにより、シリコン薄膜140Mを結晶化する。

【0072】

より具体的には、例えば、マザー基板110Mを載置したステージ(図示省略)を第1の方向(例えば、図3Cの左右方向)に移動させながら、発振装置からCWレーザを出力し、ステージが移動の向きを変えるタイミング(移動方向が左方向から右方向に変わるタイミング、又は移動方向が右方向から左方向に変わるタイミング)毎に、発振装置を第1の方向に直交する方向(例えば、図3Cの上下方向)にCWレーザの幅だけ移動させる。この動作を繰り返すことによって、CWレーザをシリコン薄膜140Mの上面全域に照射することができる。

【0073】

なお、上述の照射方法は一例であって、例えば、ステージを完全に固定させた状態で発振装置のみを移動させてもよいし、その逆であってもよい。すなわち、発振装置とステージとを相対的に移動させることにより、レーザ光でシリコン薄膜140Mの上面全域を走査すればよい。

【0074】

次に、図4を参照して、波長532nmの連続発振レーザでシリコン薄膜140Mをアニールする場合において、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚の変化に伴って、シリコン薄膜140Mのレーザ光の吸収率が変化する様子を説明する。図4は、シリコン薄膜140Mのレーザ光の吸収率を示す図であって、緩和層121を設けない場合(破線)と、緩和層121を設けた場合(実線)とを比較した図である。

【0075】

図4を参照すれば明らかなように、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が薄い(例えば、中央領域に比べて3%以上薄い、より好ましくは中央領域に比べて10%〜20%薄い)マザー基板110Mの端部領域に緩和層121を設けることにより、緩和層121を設けない場合と比較して、シリコン薄膜140Mのレーザ光の吸収率を低下させることができる。これは、シリコン薄膜140Mに入射するレーザ光の一部が金属薄膜である緩和層121で反射され、入射光と反射光とがシリコン薄膜140M内で光学干渉することによって、シリコン薄膜140Mの吸収率が低下するものと考えられる。

【0076】

その結果、レーザアニール工程において、緩和層121が形成されていない領域のシリコン薄膜140Mは、アモルファスシリコンの融点である1414℃以上の温度範囲まで上昇し、結晶化して多結晶シリコン層となる。一方、緩和層121が形成されている領域(端部領域)のシリコン薄膜140Mは、緩和層121が形成されていない領域(中央領域)のシリコン薄膜140Mより、低い温度までしか上昇しない。そのため、緩和層121が形成されている領域のシリコン薄膜140Mは結晶化しない可能性があるが、この領域のシリコン薄膜140Mは後の工程で除去されるので、問題ない。

【0077】

また、上記のように、シリコン薄膜140Mの中央領域と端部領域とで温度差が生まれるので、端部領域のシリコン薄膜140Mからマザー基板110Mに伝わる熱量は、中央領域における熱伝導量より少なくなる。そのため、冷却時において、マザー基板110Mに発生する引張応力を低減することができるので、マイクロクラックの多い端部領域でマザー基板110Mにクラックが発生するのを有効に防止することができる。

【0078】

但し、図4に示されるように、緩和層121を設けない場合、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が厚くなるほど、レーザ光の吸収率が低下している。一方、緩和層121を設けた場合、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が厚くなるほど、レーザ光の吸収率が上昇している。そして、膜厚低下率が0%の場合、緩和層121を設けた場合の方が吸収率が高くなっている。従って、実施の形態1においては、図3Cに示されるように、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が低下するマザー基板110Mの端部領域にのみ緩和層121を形成するのが望ましい。

【0079】

なお、本実施の形態1では、連続発振レーザを用いたレーザアニールによってシリコン薄膜140Mを結晶化させたが、結晶化の方法としては、波長370〜900nm程度のパルスレーザを用いたレーザアニール法、エキシマレーザを用いたレーザアニール法、又は急速熱処理(RTP)によるアニール法を用いても構わない。

【0080】

その後、シリコン薄膜140Mに対して水素プラズマ処理を行うことにより、シリコン薄膜140Mのシリコン原子に対して水素化処理を行う。水素プラズマ処理は、例えばH2、H2/アルゴン(Ar)等の水素ガスを含むガスを原料として高周波(RF)電力により水素プラズマを発生させて、当該水素プラズマをシリコン薄膜140Mに照射することにより行われる。この水素プラズマ処理によって、シリコン原子のダングリングボンド(欠陥)が水素終端され、シリコン薄膜140Mの結晶欠陥密度が低減して結晶性が向上する。

【0081】

次に、図2Eに示されるように、結晶化されたシリコン薄膜140Mをパターニングすることにより、ゲート電極120a〜120fそれぞれに重畳する位置にチャネル層140a、140b、140c、140d、140e、140fをパターン形成する。

【0082】

次に、図2Fに示すように、チャネル層140a〜140f上に、チャネル保護層150a、150b、150c、150d、150e、150fを形成する。この場合、まず、所定の塗布方式によってチャネル保護層150a〜150fを形成するための所定の有機材料を塗布し、スピンコートやスリットコートを行うことによって、チャネル層140a〜140fを覆うように、マザー基板110Mの上面全域に絶縁膜を成膜する。有機材料の膜厚は、有機材料の粘度やコーティング条件(回転数、ブレードの速度など)で制御することができる。なお、絶縁膜の材料としては、シリコン、酸素及びカーボンを含む感光性塗布型の有機材料を用いることができる。

【0083】

その後、絶縁膜に対して約110℃の温度で約60秒間のプリベークを行って絶縁膜を仮焼成する。これにより、絶縁膜に含まれる溶剤が気化する。その後、フォトマスクを用いた露光と現像とを行うことによって絶縁膜をパターニングし、所定形状のチャネル保護層150a〜150fを形成する。その後、パターン形成されたチャネル保護層150a〜150fに対して280℃〜300℃の温度で約1時間のポストベークを行って、チャネル保護層150a〜150fを本焼成して固化する。これにより、チャネル保護層150a〜150f中の有機成分の一部が気化及び分解して膜質が改善されたチャネル保護層150a〜150fを形成することができる。

【0084】

次に、図2Gに示すように、チャネル保護層150a〜150f上に、ソース電極161a、161b、161c、161d、161e、161f及びドレイン電極162a、162b、162c、162d、162e、162fをパターン形成する。この場合、まず、ソース電極161a〜161f及びドレイン電極162a〜162fとなる材料で構成されたソースドレイン金属膜を、例えばスパッタによって成膜する。その後、ソースドレイン金属膜上に所定形状にパターニングされたレジストを形成し、ウェットエッチングを施すことによってソースドレイン金属膜をパターニングする。このとき、チャネル保護層150a〜150fがエッチングストッパとしてチャネル層140a〜140fを保護する。その後、レジストを除去することにより、所定形状のソース電極161a〜161f及びドレイン電極162a〜162fを形成することができる。

【0085】

次に、図2Hに示されるように、ソース電極161a〜161f及びドレイン電極162a〜162fを覆うように、マザー基板110Mの上面全域に層間絶縁膜170Mを形成する。具体的には、例えば、プラズマCVD法により、マザー基板110Mの全域にわたって、窒化シリコンからなる層間絶縁膜170Mを堆積する。

【0086】

次に、図2Iに示されるように、層間絶縁膜170M上に、EL層180を形成する。具体的には、まず、層間絶縁膜170M上に、陽極と発光層とを画素毎に形成し、その上に全画素共通の陰極を形成する。また、発光層は、正孔注入層、正孔輸送層、有機発光層、及び電子輸送層の積層構造体として形成される。

【0087】

次に、図2Jに示されるように、EL層180上に、前面ガラス190を積層する。前面ガラス190は、EL層180から出力される光を透過させる透明ガラスであり、透明樹脂等でEL層180に接着される。

【0088】

そして最後に、図2Kに示されるように、各種薄膜が積層されたマザー基板110Mを所定の大きさに切断する。具体的には、図2Jに示される端部領域(周縁領域)の一部を切り落とすと共に、切断線がスクライブ領域上に位置するようにマザー基板110Mを切断することによって、図2Kに示される薄膜半導体装置100A、100Bを得ることができる。

【0089】

なお、マザー基板110Mの切断方法は特に限定されないが、例えば、ダイヤモンドカッター等で切断してもよい。または前面ガラス190の表面に切欠溝を形成し、その切欠溝に沿って折曲力を加えることによって分断してもよい。

【0090】

上記のように、マザー基板110Mの端部領域に緩和層121を設けた状態でシリコン薄膜140Mを結晶化することにより、端部領域におけるシリコン薄膜140Mからマザー基板110Mへの熱伝導量を大幅に低下させることができる。その結果、結晶化後の冷却工程において、少なくともマザー基板110Mの端部領域に発生する引張応力を低減することができるので、マイクロクラックの多い端部領域でマザー基板110Mにクラックが発生するのを有効に防止することができる。

【0091】

(実施の形態2)

次に、図5を参照して、実施の形態2に係る薄膜半導体装置の構成を説明する。図5は、実施の形態2に係る薄膜半導体装置200の断面図である。なお、実施の形態1と同一の構成要素には同一の参照番号を付し、詳しい説明は省略する。

【0092】

図5に示される薄膜半導体装置200は、緩和層122が基板110の両端部に設けられている点、及び緩和層122がゲート電極120a〜120cと異なる材料で形成されている点が実施の形態1と相違する。

【0093】

実施の形態2に係る緩和層122は、例えば、プラズマCVD法又はスパッタによって、SiO2、SiN等の無機材料を基板110上のゲート電極120a〜120cと同一の層に成膜し、所定の形状にパターニングすることによって形成することができる。または、緩和層122は、無機材料と有機材料との混合材料であるSOG(Spin On Glass:塗布ガラス)を基板110上に塗布し、露光、現像、及びベーク工程を経て形成することができる。なお、実施の形態2に係る緩和層122は、例えば、500nm〜1000nm程度の膜厚とするのが望ましい。

【0094】

次に、図6A及び図6Bを参照して、実施の形態2に係る薄膜半導体装置の製造方法を説明する。図6A及び図6Bは、本発明の実施の形態2に係る薄膜半導体装置の製造方法であって、実施の形態1の図2Bのゲート電極/緩和層形成工程に相当する工程の構成を模式的に示した断面図である。なお、その他の工程は実施の形態1とほぼ共通するので、再度の説明は省略する。

【0095】

まず、図6Aに示されるように、マザー基板110M上に、所定形状のゲート電極120a〜120fを形成する。ゲート電極120a〜120fの形成方法は、実施の形態1と同じであってよい。

【0096】

次に、図6Bに示されるように、マザー基板110M上の端部領域及びスクライブ領域に所定形状の緩和層122を形成する。より具体的には、例えば、緩和層122となるSOGを基板110上に塗布し、フォトマスクを用いた露光と現像とを行うことによって所定の形状にパターニングする。その後、パターン形成された緩和層122をベークすることにより、緩和層122が本焼成して固化する。

【0097】

その後、図2Cに示されるようにゲート絶縁膜130が形成され、図2Dに示されるようにシリコン薄膜140Mが形成されて結晶化される。このとき、実施の形態2に係る緩和層122がシリコン薄膜140Mからマザー基板110Mへの熱伝導量を低下させる仕組みを、図7を参照して説明する。図7は、マザー基板110M上に形成されるアンダーコート層の膜厚とシリコン薄膜140Mを結晶化する際のマザー基板110Mの表面温度との関係を示す図である。

【0098】

図7を参照すれば明らかなように、アンダーコート層の膜厚が厚い程、マザー基板110Mの表面温度が低下している。これは、シリコン薄膜140Mからアンダーコート層を経由してマザー基板110Mに到達する熱が、アンダーコート層の側面から徐々に放熱されるためだと考えられる。そして、実施の形態2に係る緩和層122は、図7のアンダーコート層と同一の役割を担っている。すなわち、実施の形態2に係る緩和層122は、シリコン薄膜140Mからマザー基板110Mへの熱伝導量を低下させる。そして、緩和層122の膜厚は、図7でマザー基板110Mの表面温度が1100℃を下回る500nm以上に設定するのが望ましい。

【0099】

なお、図7に示されるように、シリコン薄膜140Mからマザー基板110Mへの熱伝導量を十分に低下させるためには、アンダーコート層の膜厚を500nm以上にすればよく、必ずしも緩和層122を設ける必要はないとも考えられる。しかしながら、アンダーコート層は、マザー基板110Mの上面全域に均一な膜厚で成膜するために、プラズマCVD法等を用いる必要がある。そのため、膜厚を厚くしようとすると成膜に時間がかかるという課題を生じる。

【0100】

これに対して、緩和層122は、TFT等が形成されない端部領域やスクライブ領域にのみ形成されるので、アンダーコート層と比較して膜厚のばらつきを気にする必要がない。そこで、図6Bに示されるように緩和層122を別工程で形成するとしても、アンダーコート層の膜厚を厚くするよりも製造時間を短縮することができる。

【0101】

上記のように、実施の形態2に係る製造方法では、ゲート電極120a〜120fと緩和層122とが別工程で形成される点で実施の形態1に係る製造方法と相違する。なお、図6Aに示されるゲート電極形成工程と、図6Bに示される緩和層形成工程とは、上記の実行順序に限定されず、緩和層形成工程を先に実行し、ゲート電極形成工程を後に実行してもよい。

【0102】

また、実施の形態2に係る製造方法では、緩和層122をマザー基板110Mの端部領域のみならず、スクライブ領域にも形成している点で実施の形態1に係る製造方法と相違する。なお、スクライブ領域とは、マザー基板110Mの切断工程において、切断線が通る領域を指す。すなわち、切断工程においてマザー基板110Mを4つに切断する場合、例えば、図10Aの参照番号163で示される領域に緩和層122が形成される。

【0103】

そして、実施の形態2の切断工程における切断線は、スクライブ領域に形成された緩和層122上を通る。これにより、切断時に基板110にクラックが発生するのを有効に防止することができる。なお、緩和層122の幅は5mm〜10mm程度であるのに対して、図2Kに示される切断線の幅は1〜2mm程度であるので、マザー基板110Mを緩和層122上で切断したとしても、図5に示されるように、薄膜半導体装置200のスクライブ領域に接する側の端部にも緩和層122が残留する。

【0104】

なお、上記の例では、前面ガラス190を取り付けた後に切断工程を実行する方法を説明したが、切断工程のタイミングは、シリコン薄膜形成工程の後であれば、これに限定されない。例えば、層間絶縁膜170Mを形成した後に切断し、その後の工程(EL層形成工程、前面ガラス取付工程等)は、個々の薄膜半導体装置に対して別々に行なってもよい。これにより、切断時に基板110にクラックが生じて薄膜半導体装置を廃棄せざるを得なくなったとしても、切断工程以降の工程が無駄になるのを防ぐことができる。

【0105】

しかしながら、本実施の形態2においては、クラックの生じやすい基板110のスクライブ領域にも緩和層122を設けたことにより、切断時に基板110にクラックが発生するのを有効に防止している。そのため、上記のように前面ガラス190を取り付けた後に切断する場合でも工程の無駄を心配する必要がない。

【0106】

また、図5に示される薄膜半導体装置200は、ゲート電極120a〜120fと緩和層122とを同一の層に形成したが、上記の例に限定されず、例えば、ゲート絶縁膜130とシリコン薄膜140M(後にチャネル層140a〜140cとなる)との間に緩和層122を設けてもよい。すなわち、実施の形態2に係る緩和層122は、シリコン薄膜140Mを結晶化する際に、シリコン薄膜140Mより下の層に形成されていればよい。

【0107】

(実施の形態3)

次に、図8を参照して、実施の形態3に係る薄膜半導体装置の構成を説明する。図8は、実施の形態3に係る薄膜半導体装置300の断面図である。なお、実施の形態1、2と同一の構成要素には同一の参照番号を付し、詳しい説明は省略する。

【0108】

図8に示される薄膜半導体装置300は、緩和層163が基板110の両端部に設けられている点、及び緩和層163がゲート電極120a〜120cと異なる材料で形成されている点で実施の形態1と相違する。また、図8に示される薄膜半導体装置300は、緩和層163の直下に非晶質シリコン層141が形成されている点で実施の形態1、2と相違する。

【0109】

実施の形態3に係る緩和層163は、基板110上のチャネル層140a〜140cより上の層に、金属材料を所定の形状にパターニングすることによって形成することができる。緩和層163は、表1に示されるような反射率の高い金属を用いることができ、例えば、ソース電極161a〜161c及びドレイン電極162a〜162cと同一の材料で形成してもよい。なお、表1は、緩和層163の材料となり得る金属材料の波長532nmのレーザ光の反射率を示す表である。

【0110】

【表1】

【0111】

次に、図9A〜図9C、図10A、及び図10Bを参照して、実施の形態3に係る薄膜半導体装置の製造方法を説明する。図9A〜図9Cは、本発明の実施の形態3に係る薄膜半導体装置の製造方法であって、実施の形態1の図2Dのシリコン薄膜形成工程および図2Eのチャネル層形成工程に相当する工程の構成を模式的に示した断面図である。図10A及び図10Bは、緩和層163が形成される位置を示す平面図である。なお、その他の工程は実施の形態1とほぼ共通するので、再度の説明は省略する。但し、実施の形態3においては、図2Bに示される工程で緩和層163は形成されない。

【0112】

まず、図9A及び図10Aに示されるように、シリコン薄膜140M上の端部領域及びスクライブ領域に所定形状の緩和層163を形成する。緩和層163となる材料で構成された金属膜を、例えばスパッタによって成膜する。その後、金属膜上に所定形状にパターニングされたレジストを形成し、ウェットエッチングを施すことによって金属膜をパターニングする。

【0113】

次に、図9B及び図10Aに示されるように、一部が緩和層163で覆われたシリコン薄膜140Mの上面全域にレーザ光を照射することにより、シリコン薄膜140Mを結晶化する。その結果、図9Bに示されるように、シリコン薄膜140Mの緩和層163で覆われていない領域は、結晶化されて多結晶シリコン層140となる。

【0114】

一方、表1に示されるレーザ光の反射率の高い金属材料は、表2に示されるように、レーザ光の透過率が極めて低い。その結果、シリコン薄膜140Mの緩和層163で覆われている領域は、緩和層163によってレーザ光が遮光されるので温度がほとんど上昇しないので、この領域におけるシリコン薄膜140Mからマザー基板110Mへの熱伝導量を低下させることができる。また、結果として、シリコン薄膜140Mの緩和層163で覆われている領域は、結晶化されずに非晶質シリコン層141のままとなる。

【0115】

【表2】

【0116】

なお、図10Aでは、シリコン薄膜140Mの全域にレーザ光を照射する例を示したが、必ずしもシリコン薄膜140Mの全域に照射する必要はない。例えば、図10Bに示されるように、マザー基板110Mの2組の対辺のうちの一方側(短辺側)のみに緩和層163を形成した場合、図10Bに示されるように、緩和層163が形成されなかった側(長辺側)の端部(図10Bの非ハッチング領域)をレーザ光の照射範囲から除外してもよい。

【0117】

この場合、レーザ光を、照射範囲から除外する辺と平行な方向(図10Bの例では、左右方向)に走査するのが望ましい。これにより、レーザ光の照射開始位置と照射終了位置とを調整すれば、緩和層163が形成されなかった側の端部を容易に照射範囲から除外することができる。これは、実施の形態1、2についても同様である。

【0118】

次に、図9Cに示されるように、多結晶シリコン層140をパターニングすることにより、ゲート電極120a〜120fそれぞれに重畳する位置にチャネル層140a、140b、140c、140d、140e、140fをパターン形成する。このとき、非晶質シリコン層141は、緩和層163がマスクとして機能するために、除去されずに残る。一方、図9Cのチャネル層形成工程に先立って緩和層163を除去すれば、チャネル層形成工程で非晶質シリコン層141を除去することができる。しかしながら、非晶質シリコン層141及び緩和層163は、薄膜半導体装置300が完成した後に応力緩和層として機能するので、残しておくのが望ましい。

【0119】

次に、上記の各実施の形態1〜3に係る薄膜半導体装置100、200、300を表示装置に適用した例について、図11を用いて説明する。なお、本実施の形態では、有機EL表示装置への適用例について説明する。図11は、本発明の実施の形態に係る有機EL表示装置の一部切り欠き斜視図である。

【0120】

図11に示すように、有機EL表示装置10は、アクティブマトリクス基板(TFTアレイ基板)11と、アクティブマトリクス基板11においてマトリクス状に複数配置された画素12と、画素12に接続され、アクティブマトリクス基板11上にアレイ状に複数配置された画素回路13と、画素12と画素回路13の上に順次積層された陽極14、有機EL層15及び陰極16(透明電極)と、各画素回路13と制御回路(不図示)とを接続する複数本のソース線17及びゲート線18とを備える。有機EL層15は、電子輸送層、発光層、正孔輸送層等の各層が積層されて構成されている。

【0121】

なお、図1の薄膜半導体装置100、200、300に形成された複数の薄膜トランジスタは、図11の画素回路13それぞれに形成されるスイッチングトランジスタ又は駆動トランジスタに相当する。また、図1のEL層180は、図11の陽極、有機EL層15、及び陰極16に相当する。

【0122】

次に、上記有機EL表示装置10における画素12の回路構成について、図12を用いて説明する。図12は、本発明の実施の形態に係る薄膜半導体装置100、200、300を用いた画素の回路構成を示す図である。

【0123】

図12に示すように、画素12は、駆動トランジスタ21と、スイッチングトランジスタ22と、有機EL素子23と、コンデンサ24とを備える。駆動トランジスタ21は、有機EL素子23を駆動するトランジスタであり、また、スイッチングトランジスタ22は、画素12を選択するためのトランジスタである。

【0124】

スイッチングトランジスタ22のソース電極22Sは、ソース線17に接続され、ゲート電極22Gは、ゲート線18に接続され、ドレイン電極22Dは、コンデンサ24及び駆動トランジスタ21のゲート電極21Gに接続されている。また、駆動トランジスタ21のドレイン電極21Dは、電源線25に接続され、ソース電極21Sは有機EL素子23のアノードに接続されている。

【0125】

この構成において、ゲート線18にゲート信号が入力され、スイッチングトランジスタ22をオン状態にすると、ソース線17を介して供給された信号電圧がコンデンサ24に書き込まれる。そして、コンデンサ24に書き込まれた保持電圧は、1フレーム期間を通じて保持される。この保持電圧により、駆動トランジスタ21のコンダクタンスがアナログ的に変化し、発光階調に対応した駆動電流が、有機EL素子23のアノードからカソードへと流れる。これにより、有機EL素子23が発光し、所定の画像を表示することができる。

【0126】

なお、本実施の形態では、有機EL素子を用いた有機EL表示装置について説明したが、液晶表示装置等、アクティブマトリクス基板が用いられる他の表示装置にも適用することができる。また、このように構成される表示装置については、フラットパネルディスプレイとして利用することができ、テレビジョンセット、パーソナルコンピュータ、携帯電話などのあらゆる表示パネルを有する電子機器に適用することができる。

【0127】

以上、図面を参照してこの発明の実施形態を説明したが、この発明は、図示した実施形態のものに限定されない。図示した実施形態に対して、この発明と同一の範囲内において、あるいは均等の範囲内において、種々の修正や変形を加えることが可能である。

【産業上の利用可能性】

【0128】

本発明は、表示装置に画素回路等に用いられる薄膜半導体装置に有利に利用される。

【符号の説明】

【0129】

10 有機EL表示装置

11 アクティブマトリクス基板

12 画素

13 画素回路

14 陽極

15 有機EL層

16 陰極

17 ソース線

18 ゲート線

21 駆動トランジスタ

22 スイッチングトランジスタ

21G,22G,120a,120b,120c,120d,120e,120f ゲート電極

21S,22S,161a,161b,161c,161d,161e,161f ソース電極

21D,22D,162a,162b,162c,162d,162e,162f ドレイン電極

23 有機EL素子

24 コンデンサ

100,100A,100B,200,300 薄膜半導体装置

110,900 基板

121,122,163 緩和層

130,130M ゲート絶縁膜

140 多結晶シリコン層

140a,140b,140c,140d,140e,140f チャネル層

140M シリコン薄膜

141 非晶質シリコン層

150a,150b,150c,150d,150e,150f チャネル保護層

170,170A,170B,170M 層間絶縁膜

180,180A,180B,180M EL層

190,190A,190B,190M 前面ガラス

910 マイクロクラック

920 クラック

【技術分野】

【0001】

本発明は、薄膜形成基板及びその製造方法に関し、特に、表示装置の画素回路が形成された薄膜形成基板及びその製造方法に関するものである。

【背景技術】

【0002】

近年、液晶ディスプレイに変わる次世代フラットパネルディスプレイの一つとしての有機材料のEL(Electro luminescence)を利用した有機ELディスプレイが注目されている。

【0003】

有機ELディスプレイは、電圧駆動型の液晶ディスプレイと異なり、電流駆動型のディスプレイデバイスである。このことから、アクティブマトリクス方式の表示装置の駆動回路として優れた特性を有する薄膜トランジスタ(TFT:Thin Film Transistor)の開発が急がれている。薄膜トランジスタは、画素を選択するスイッチング素子、或いは画素を駆動する駆動トランジスタ等として用いられる。

【0004】

従来の薄膜トランジスタ及びその製造方法は、例えば、特許文献1及び特許文献2に開示されている。特許文献1、2によれば、薄膜トランジスタは、基板上に薄膜を順次積層することによって形成される。また、薄膜トランジスタのオン特性を向上させるために、チャネル領域となる半導体膜にレーザを照射して、多結晶化することが知られている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−332303号公報

【特許文献2】特開平5−21344号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記方法で製造された薄膜トランジスタには、図13に示されるように、基板の表面から内部に向かって延びるクラックが大量発生する課題がある。このクラックの発生原因の一例を、図14を用いて説明する。

【0007】

まず、基板900の表面には、最初からマイクロクラック910が存在する。このマイクロクラック910は、基板900に必ず存在するものであり、薄膜トランジスタの性能に影響を与えるものではない。しかしながら、基板900上に積層された半導体膜にレーザを照射することによって基板900が高温になり、冷却することによって基板900に図14の矢印の方向の引張応力が生じる。そして、この引張応力によって、マイクロクラック910が伸展して大きなクラック920になると考えられる。

【0008】

この課題は、マイクロクラック910が多い基板周辺部において特に顕著である。また、冷却時にクラック920が生じなくとも、基板900に引張応力が残留していることにより、基板900を切断する際にクラックが大量発生する課題がある。

【0009】

本発明は、上記の課題に鑑みてなされたものであり、基板に生じるクラックの発生を防止した薄膜形成基板及び薄膜形成方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の一形態に係る薄膜形成方法は、基板を準備する基板準備工程と、前記基板上に第1薄膜を形成する第1薄膜形成工程と、前記第1薄膜に対して光線を相対走査して照射することにより、前記第1薄膜を結晶化する結晶化工程と、前記結晶化工程において前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層を、前記結晶化工程の前に、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

【発明の効果】

【0011】

本発明によれば、基板に生じるクラックの発生を防止した薄膜形成基板及び薄膜形成方法を得ることができる。

【図面の簡単な説明】

【0012】

【図1】図1は、実施の形態1に係る薄膜半導体装置の構造を示す断面図である。

【図2A】図2Aは、実施の形態に係る薄膜半導体装置の製造方法における基板準備工程を模式的に示した断面図である。

【図2B】図2Bは、実施の形態1に係る薄膜半導体装置の製造方法におけるゲート電極/緩和層形成工程を模式的に示した断面図である。

【図2C】図2Cは、実施の形態1に係る薄膜半導体装置の製造方法におけるゲート絶縁膜形成工程を模式的に示した断面図である。

【図2D】図2Dは、実施の形態1に係る薄膜半導体装置の製造方法におけるシリコン薄膜形成工程を模式的に示した断面図である。

【図2E】図2Eは、実施の形態1に係る薄膜半導体装置の製造方法におけるチャネル層形成工程を模式的に示した断面図である。

【図2F】図2Fは、実施の形態1に係る薄膜半導体装置の製造方法におけるチャネル保護層形成工程を模式的に示した断面図である。

【図2G】図2Gは、実施の形態1に係る薄膜半導体装置の製造方法におけるソース電極/ドレイン電極形成工程を模式的に示した断面図である。

【図2H】図2Hは、実施の形態1に係る薄膜半導体装置の製造方法における層間絶縁膜形成工程を模式的に示した断面図である。

【図2I】図2Iは、実施の形態1に係る薄膜半導体装置の製造方法におけるEL層形成工程を模式的に示した断面図である。

【図2J】図2Jは、実施の形態1に係る薄膜半導体装置の製造方法における前面ガラス取り付け工程を模式的に示した断面図である。

【図2K】図2Kは、実施の形態1に係る薄膜半導体装置の製造方法における切断工程を模式的に示した断面図である。

【図3A】図3Aは、緩和層を設けない場合の図2DのP部の拡大断面図である。

【図3B】図3Bは、緩和層を設けた場合の図2DのP部の拡大断面図である。

【図3C】図3Cは、緩和層の位置を示すマザー基板110Mの平面図である。

【図4】図4は、シリコン薄膜のレーザ光の吸収率を示す図である。

【図5】図5は、実施の形態2に係る薄膜半導体装置の構造を示す断面図である。

【図6A】図6Aは、実施の形態2に係る薄膜半導体装置の製造方法におけるゲート電極形成工程を模式的に示した断面図である。

【図6B】図6Bは、実施の形態2に係る薄膜半導体装置の製造方法における緩和層形成工程を模式的に示した断面図である。

【図7】図7は、アンダーコート層の膜厚とシリコン薄膜を結晶化する際のマザー基板の表面温度との関係を示す図である。

【図8】図8は、実施の形態3に係る薄膜半導体装置の構造を示す断面図である。

【図9A】図9Aは、実施の形態3に係る薄膜半導体装置の製造方法における緩和層形成工程を模式的に示した断面図である。

【図9B】図9Bは、実施の形態3に係る薄膜半導体装置の製造方法における結晶化工程を模式的に示した断面図である。

【図9C】図9Cは、実施の形態3に係る薄膜半導体装置の製造方法におけるチャネル層形成工程を模式的に示した断面図である。

【図10A】図10Aは、緩和層が形成される位置の一例を示すマザー基板の平面図である。

【図10B】図10Bは、緩和層が形成される位置の一例を示すマザー基板の平面図である。

【図11】図11は、本発明の実施の形態に係る薄膜半導体装置を用いた画素の回路構成を示す図である。

【図12】図12は、従来の薄膜半導体装置の構成を示す断面図である。

【図13】図13は、クラックが発生した基板の断面の様子を示す図である。

【図14】図14は、基板にクラックが発生する理由を説明するための図である。

【発明を実施するための形態】

【0013】

本発明の一形態に係る薄膜形成方法は、基板を準備する基板準備工程と、前記基板上に第1薄膜を形成する第1薄膜形成工程と、前記第1薄膜に対して光線を相対走査して照射することにより、前記第1薄膜を結晶化する結晶化工程と、前記結晶化工程において前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層を、前記結晶化工程の前に、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

【0014】

上記のように、第1薄膜に生じる熱の伝導量を低下させる緩和層を基板の一部に設けることにより、緩和層が重畳する位置において、基板にクラックが生じるのを有効に防止することができる。なお、「第1薄膜」は、例えば、薄膜トランジスタ(薄膜半導体装置)のチャネル層となるシリコン薄膜であってもよい。

【0015】

また、前記緩和層は、前記基板と前記第1薄膜との間に形成され、前記緩和層に重畳する位置の前記第1薄膜の前記光線の吸収率を低下させることによって、前記基板への熱伝導量を低下させるものであってもよい。

【0016】

また、前記緩和層は、前記光線を反射する材料で形成され、前記第1薄膜に照射される前記光線と、前記緩和層で反射された光線とを光学干渉させることによって、前記第1薄膜の前記光線の吸収率を低下させるものであってもよい。

【0017】

また、前記緩和層は、金属材料で形成されてもよい。

【0018】

さらに、該薄膜形成方法は、前記基板と前記第1薄膜との間に第2薄膜を形成する第2薄膜形成工程を含んでもよい。そして、前記緩和層は、前記第1及び第2薄膜の平均膜厚が前記基板の中央領域より10%〜20%薄い前記基板の端領域にのみ形成されてもよい。なお、「第2薄膜」は、例えば、薄膜トランジスタ(薄膜半導体装置)のゲート絶縁膜であってもよい。

【0019】

また、前記緩和層は、膜厚が500nm〜1000nmであり、前記基板と前記第1薄膜との間に形成されてもよい。

【0020】

また、前記緩和層は、無機材料で形成されてもよい。

【0021】

さらに、前記緩和層は、有機材料と無機材料との混合材料であってもよい。

【0022】

さらに、該薄膜形成方法は、前記基板上に第3薄膜を形成する第3薄膜形成工程を含んでもよい。そして、前記緩和層は、前記第1及び第3薄膜の間に形成されてもよい。なお、「第3薄膜」は、例えば、薄膜トランジスタ(薄膜半導体装置)のアンダーコート層であってもよい。

【0023】

また、前記第3薄膜は、酸化珪素膜であってもよく、前記緩和層は、SOG(Spin On Glass)膜であってもよい。

【0024】

また、前記緩和層は、前記第1薄膜上に形成され、前記光線を遮光することによって、前記第1薄膜から前記基板への熱伝導量を低下させるものであってもよい。

【0025】

また、前記緩和層は、金属材料で形成されてもよい。

【0026】

具体的には、前記金属材料は、MoW、W、Ta、Cr、Cu、Alのいずれかを含んでもよい。

【0027】

また、前記緩和層の前記光線の反射率は、60%以上であってもよい。

【0028】

また、前記結晶化工程で結晶化された前記第1薄膜に含まれる結晶粒の平均粒径は、50nm以上、1μm以下であってもよい。

【0029】

また、前記光線は、連続発振のレーザ光線であってもよく、前記レーザ光線の波長は、532nmであってもよい。

【0030】

さらに、前記薄膜形成方法は、前記結晶化工程の後に、前記緩和層に重畳する位置に切断線が位置するように、前記基板を切断する工程を含んでもよい。

【0031】

また、前記基板は、クラック、チッビンク、切欠、のいずれかを有してもよい。

【0032】

また、前記緩和層は、前記基板の端部のうち、前記光線の相対走査方向に交差する側の端部にのみ形成されてもよい。

【0033】

また、前記第1薄膜は、シリコンを含有する材料で構成されてもよい。

【0034】

本発明の一形態に係る表示装置の製造方法は、上記記載の薄膜形成方法を含む。

【0035】

本発明の一形態に係る薄膜形成基板は、基板と、前記基板上に形成され、光線が照射されることによって結晶化された第1薄膜と、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に、前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層とを備える。

【0036】

(実施の形態1)

図1を参照して、本発明の実施の形態1に係る薄膜形成基板の構成を説明する。図1は、本実施の形態1に係る薄膜形成基板の一例である薄膜半導体装置100の模式的な構成を示す断面図である。

【0037】

薄膜半導体装置100は、図1に示されるように、基板110と、ゲート電極120a、120b、120c及び緩和層121と、ゲート絶縁膜130と、チャネル層140a、140b、140cと、チャネル保護層150a、150b、150cと、ソース電極161a、161b、161c及びドレイン電極162a、162b、162cと、層間絶縁膜170と、EL層180と、前面ガラス190とを、この順に積層して構成される。

【0038】

図1に示される薄膜半導体装置100は、例えば、複数の画素を有する表示パネルである。そして、薄膜半導体装置100には、画素毎にボトムゲート型の薄膜トランジスタが形成されている。

【0039】

基板110は、例えば、石英ガラス、無アルカリガラス、高耐熱性ガラス等のガラス材料からなるガラス基板である。なお、ガラス基板の中に含まれるナトリウムやリン等の不純物がチャネル層140a、140b、140cに侵入することを防止するために、基板110上にシリコン窒化膜(SiNx)、酸化シリコン(SiOy)又はシリコン酸窒化膜(SiOyNx)等からなるアンダーコート層を形成してもよい。また、アンダーコート層は、レーザアニールなどの高温熱処理プロセスにおいて、基板110への熱の影響を緩和させる役割を担うこともある。アンダーコート層の膜厚は、例えば100nm〜2000nm程度とすることができる。

【0040】

ゲート電極120aは、基板110上に所定形状でパターン形成される。ゲート電極120aを構成する材料としては、例えば、モリブデン(Mo)、タンタル(Ta)、アルミニウム(Al)、銅(Cu)、タングステン(W)、チタン(Ti)、クロム(Cr)、及びモリブデンタングステン(MoW)等を用いることができる。ゲート電極120aの膜厚は、例えば20〜500nm程度とすることができる。ゲート電極120b、120cについても同様である。

【0041】

実施の形態1に係る緩和層121は、基板110上の端部領域にパターン形成される。より具体的には、緩和層121は、ゲート電極120a〜120cと同一の層に、ゲート電極120a〜120cと同一の材料で形成される。なお、図1では、基板110上の一方側(図1の左側)の端部にのみ緩和層121を設けた例を示したが、これに限ることなく、他方側(図1の右側)の端部にも緩和層121を設けてもよい。さらには、図1の手前側及び奥側の端部にも緩和層121を設けてもよい。

【0042】

この緩和層121は、薄膜半導体装置100を搬送する際の外力、あるいは薄膜半導体装置100が長期期間で使用される際の熱応力等で基板110に作用する応力を緩和する応力緩和層として機能する。すなわち、薄膜半導体装置100に作用する外力、熱応力によって基板110にクラックが発生、伸展するのを有効に防止することができる。

【0043】

ゲート絶縁膜130は、ゲート電極120a、120b、120c及び緩和層121を覆うように、基板110の上面全域に形成される。ゲート絶縁膜130を構成する材料としては、例えば、酸化シリコン(SiOy)、窒化シリコン(SiNx)、シリコン酸窒化膜(SiOyNx)、酸化アルミニウム(AlOz)又は酸化タンタル(TaOw)の単層膜又はこれらの積層膜によって構成することができる。ゲート絶縁膜130の膜厚は、例えば50nm〜300nmとすることができる。

【0044】

なお、本実施の形態1では、後述するようにチャネル層140a、140b、140cを結晶性シリコン薄膜で形成しているので、ゲート絶縁膜130に酸化シリコンを用いることが好ましい。酸化シリコンは、チャネル層140a、140b、140cとゲート絶縁膜130との界面状態を良好にするのに適しており、これによって薄膜半導体装置100の閾値電圧特性が向上する。

【0045】

チャネル層140aは、ゲート絶縁膜130上のゲート電極120aに重畳する位置にパターン形成される半導体膜であって、ゲート電極120aの電圧によってキャリアの移動が制御される領域である所定のチャネル領域を有する。なお、チャネル層140b、140cについても同様である。チャネル層140a〜140cの膜厚は、例えば、30nm〜100nm程度とすることができる。

【0046】

チャネル層140a〜140cは、結晶性の組織構造を有する結晶性シリコン薄膜であって、例えば、非結晶性の非晶質シリコン(アモルファスシリコン)を結晶化することによって形成することができる。また、チャネル層140a〜140cには、平均結晶粒径が100nm以上の多結晶、あるいは、平均結晶粒径が10nm〜100nmのマイクロクリスタル(μc)と呼ばれる微結晶が含まれる。さらに、チャネル層140a〜140cに含まれるシリコン結晶の主面方位は[100]であることが好ましい。これにより、結晶性に優れたチャネル層140a〜140cを形成することができる。

【0047】

チャネル保護層150aは、チャネル層140a上に形成され、チャネル層140aを保護するチャネルエッチングストッパ(CES)層として機能する。すなわち、チャネル保護層150aは、ソース電極161a及びドレイン電極162aのエッチング処理時において、チャネル層140aがエッチングされることを防止する機能を有する。チャネル保護層150b、150cも同様である。

【0048】

チャネル保護層150a〜150cを形成する材料には、例えば、シリコン、酸素及びカーボンを含む有機材料を主として含有する有機材料を用いることができる。本実施の形態1におけるチャネル保護層150a〜150cは、感光性塗布型の有機材料をパターニング及び固化することによって形成することができる。

【0049】

また、チャネル保護層150a〜150cを構成する有機材料には、例えば、有機樹脂材料、界面活性剤、溶媒及び感光剤が含まれる。有機樹脂材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン等の中の1種又は複数種からなる感光性又は非感光性の有機樹脂材料を用いることができる。界面活性剤としては、シロキサン等のシリコン化合物からなる界面活性剤を用いることができる。溶媒としては、プロピレングリコールモノメチルエーテルアセテート又は1,4−ジオキサン等の有機溶媒を用いることができる。また、感光剤としては、ナフトキノンジアジト等のポジ型感光剤を用いることができる。なお、感光剤には、炭素だけではなく硫黄も含まれている。

【0050】

チャネル保護層150a〜150cを形成する場合、上記の有機材料をスピンコート法等の塗布法を用いて形成することができる。なお、チャネル保護層150a〜150cの形成には、塗布法だけではなく、滴吐出法等その他の方法を用いることもできる。例えば、スクリーン印刷やオフセット印刷等の所定のパターンを形成することができる印刷法等を用いることにより、所定形状の有機材料を選択的に形成することもできる。

【0051】

チャネル保護層150a〜150cの膜厚は、例えば、300nm〜1000nmとすることができる。チャネル保護層150a〜150cの膜厚の下限は、エッチングによるマージン及びチャネル保護層150a〜150c中の固定電荷の影響を抑制すること等を考慮して決定される。また、チャネル保護層150a〜150cの膜厚の上限は、段差の増大に伴うソース電極161a〜161c及びドレイン電極162a〜162cの製造プロセスの信頼性の低下を抑制することを考慮して決定される。

【0052】

ソース電極161a及びドレイン電極162aは、チャネル保護層150a上のチャネル層140aに重畳する位置にパターン形成される。また、ソース電極161aとドレイン電極162aとは、互いに所定の間隔をあけて対向配置される。ソース電極161b、161c及びドレイン電極162b、162cも同様である。

【0053】

本実施の形態1において、ソース電極161a及びドレイン電極162aは、導電性材料及びその合金等の単層構造又は多層構造とすることができる。例えば、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)、銅(Cu)、タンタル(Ta)、チタン(Ti)及びクロム(Cr)等によって構成される。本実施の形態1では、ソース電極161a及びドレイン電極162aは、MoW/Al/MoWの三層構造によって形成されている。ソース電極161a及びドレイン電極162aの膜厚は、例えば、100nm〜500nm程度とすることができる。

【0054】

なお、チャネル層140aとチャネル保護層150aとの間に、さらにバックチャネル層(図示省略)を形成してもよい。バックチャネル層は、例えば、意図的に不純物のドーピングを行っていないアモルファスシリコン膜(真性アモルファスシリコン)によって形成されている。このバックチャネル層は、局在準位密度(トラップ密度)がチャネル層140aより高い。すなわち、バックチャネル層の負キャリアの電荷密度によってチャネル保護層150aの正の固定電荷を相殺して電界遮蔽を行うことができる。これにより、バックチャネルの形成を抑制することができ、オフ時のリーク電流を抑制することができるので、薄膜トランジスタのオフ特性が向上する。

【0055】

また、チャネル保護層150aとソース電極161a及びドレイン電極162aとの間に、さらにコンタクト層(図示省略)を形成してもよい。コンタクト層は、不純物を高濃度に含む非晶質半導体膜であり、1×1019[atm/cm3]以上の高濃度の不純物を含むn+層である。より具体的には、コンタクト層は、アモルファスシリコンに不純物としてリン(P)をドーピングしたn型半導体膜によって構成することができる。また、コンタクト層の膜厚は、例えば5nm〜100nmとすることができる。

【0056】

さらに、コンタクト層は、下層の低濃度の電界緩和層(n−層)と上層の高濃度のコンタクト層(n+層)との2層から構成されてもよい。低濃度の電界緩和層には、1×1017[atm/cm3]程度のリンがドーピングされている。上記2層は、CVD(Chemical Vapor Deposition)装置において連続的に形成することが可能である。

【0057】

層間絶縁膜170は、ソース電極161a、161b、161c及びドレイン電極162a、162b、162cを覆うように、基板110の上面全域に積層される。層間絶縁膜170を構成する材料としては、例えば、酸化シリコン(SiOy)、窒化シリコン(SiNx)、シリコン酸窒化膜(SiOyNx)、酸化アルミニウム(AlOz)又は酸化タンタル(TaOw)の単層膜又はこれらの積層膜によって構成することができる。また、層間絶縁膜170は、その上面が平坦になる平坦化膜として機能する。

【0058】

EL層180は、画素毎に形成される陽極と、画素毎に形成される発光層と、全画素に共通に形成される陰極とで形成される。また、隣接する陽極(発光層)の間には、バンクが形成されている。

【0059】

陽極は、例えば、モリブデン、アルミニウム、金、銀、銅などの導電性金属若しくはそれらの合金、PEDOT:PSSなどの有機導電性材料、酸化亜鉛、又は、鉛添加酸化インジウムのいずれかで形成される反射電極である。一方、陰極は、例えば、ITO、SnO2、In2O3、ZnO又はこれらの組み合わせなどで形成される透明電極である。

【0060】

発光層は、正孔注入層、正孔輸送層、発光層、電子輸送層、及び電子注入層などの各層を積層して構成される。例えば、正孔注入層として銅フタロシアニンを、正孔輸送層としてα−NPD(Bis[N−(1−Naphthyl)−N−Phenyl]benzidine)を、発光層としてAlq3(tris(8−hydroxyquinoline)aluminum)を、電子輸送層としてオキサゾール誘導体を、電子注入層としてAlq3を用いることができる。

【0061】

前面ガラス190は、EL層180上に積層される透明ガラスである。この前面ガラス190は、EL層180を保護するためのものであり、例えば、基板110と同一の材料で形成することができる。なお、前面ガラス190を構成する材料はガラスに限定されず、透明樹脂等を用いてもよい。

【0062】

次に、図2A〜図2Kを参照して、本発明の実施の形態1に係る薄膜半導体装置の製造方法を説明する。図2A〜図2Kは、本発明の実施の形態1に係る薄膜半導体装置の製造方法における各工程の構成を模式的に示した断面図である。

【0063】

まず、図2Aに示されるように、マザー基板110Mを準備する。このマザー基板110Mは、例えば、図1の基板110の数倍の大きさであって、例えば、薄膜トランジスタを形成した後に、基板110の大きさに切断される。より具体的には、マザー基板110Mは、2200mm×2500mmのG8基板であってもよい。なお、マザー基板110Mには、マイクロクラック、チッビング、切欠等が含まれている。これらは、マザー基板110Mの製造工程や搬送時に形成されるものであり、薄膜半導体装置100の性能には直接影響しない程度の傷である。

【0064】

また、ゲート電極120a〜120fを形成する前に、プラズマCVD等によってマザー基板110M上にシリコン窒化膜、シリコン酸化膜、及びシリコン酸窒化膜などからなるアンダーコート層を形成してもよい。

【0065】

次に、図2Bに示されるように、マザー基板110M上に、所定形状のゲート電極120a、120b、120c、120d、120e、120f及び緩和層121を形成する。例えば、マザー基板110M上にMoWからなるゲート金属膜をスパッタによって成膜し、フォトリソグラフィ法及びウェットエッチング法を用いてゲート金属膜をパターニングすることにより、所定形状のゲート電極120a〜120f及び緩和層121を形成することができる。MoWのウェットエッチングは、例えば、リン酸(HPO4)、硝酸(HNO3)、酢酸(CH3COOH)及び水を所定の配合で混合した薬液を用いて行うことができる。

【0066】

次に、図2Cに示されるように、ゲート電極120a〜120f及び緩和層121を覆うように、マザー基板110Mの上面全域にゲート絶縁膜130Mを形成する。例えば、酸化シリコンからなるゲート絶縁膜130MをプラズマCVD等によって成膜する。酸化シリコンは、例えば、シランガス(SiH4)と亜酸化窒素ガス(N2O)とを所定の濃度比で導入することで、成膜することができる。

【0067】

次に、図2Dに示されるように、ゲート絶縁膜130Mの上面全域に、非晶質のシリコン薄膜140Mを形成する。例えば、シリコン薄膜140Mは、アモルファスシリコン(非晶質シリコン)をプラズマCVD等によって成膜することができる。なお、シリコン薄膜140Mは、例えば、シランガス(SiH4)と水素ガス(H2)とを所定の濃度比で導入することで、成膜することができる。そして、成膜されたシリコン薄膜140Mには、500℃の脱水素アニール処理が施される。

【0068】

そして、図2Dに示されるように、シリコン薄膜140Mをレーザアニールして結晶化させる。例えば、ビーム形状が5mm×30μmで、波長が400nm〜900nm(より好ましくは、532nm)のCWレーザをシリコン薄膜140Mに照射することにより、シリコン薄膜140Mをアモルファスシリコンの融点である1414℃以上の温度範囲に上昇させる。これにより、溶融範囲を経て結晶化したシリコンは、溶融して体積が縮小した後に体積膨張を伴って結晶化し、平均粒径が50nm以上、1μm以下のp−Si(多結晶シリコン)となる。

【0069】

シリコン薄膜140Mを結晶化させる工程を、図3A〜図3Cを参照して詳しく説明する。図3A及び図3Bは、図2DのP部の拡大断面図であって、緩和層121を設けない場合(図3A)と、緩和層121を設けた場合(図3B)とを示す図である。図3Cは、緩和層121の位置を示すマザー基板110Mの平面図である。

【0070】

まず、緩和層121を設けずにゲート絶縁膜130M及びシリコン薄膜140MをプラズマCVDで成膜した場合、図3Aに示されるように、マザー基板110Mの端部において、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が薄くなる。マザー基板110Mの端部領域におけるゲート絶縁膜130M及びシリコン薄膜140Mの膜厚は、マザー基板110Mの中央領域の膜厚と比較して10%〜20%薄くなる。但し、図3Aでは、説明のために膜厚の差を誇張して図示している。これは、プラズマCVD装置が発生させるプラズマの密度が中央部(マザー基板110Mの中央領域に相当)で密となり、周辺部(マザー基板110Mの端部領域に相当)で疎となることが一因である。

【0071】

そこで、本実施の形態1に係る薄膜半導体装置100では、図3B及び図3Cに示されるように、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が薄くなるマザー基板110Mの端部領域に緩和層121を設けている。そして、シリコン薄膜140Mが形成されたマザー基板110Mに対して、例えば図3Cに示されるようにレーザ光を相対走査することにより、シリコン薄膜140Mを結晶化する。

【0072】

より具体的には、例えば、マザー基板110Mを載置したステージ(図示省略)を第1の方向(例えば、図3Cの左右方向)に移動させながら、発振装置からCWレーザを出力し、ステージが移動の向きを変えるタイミング(移動方向が左方向から右方向に変わるタイミング、又は移動方向が右方向から左方向に変わるタイミング)毎に、発振装置を第1の方向に直交する方向(例えば、図3Cの上下方向)にCWレーザの幅だけ移動させる。この動作を繰り返すことによって、CWレーザをシリコン薄膜140Mの上面全域に照射することができる。

【0073】

なお、上述の照射方法は一例であって、例えば、ステージを完全に固定させた状態で発振装置のみを移動させてもよいし、その逆であってもよい。すなわち、発振装置とステージとを相対的に移動させることにより、レーザ光でシリコン薄膜140Mの上面全域を走査すればよい。

【0074】

次に、図4を参照して、波長532nmの連続発振レーザでシリコン薄膜140Mをアニールする場合において、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚の変化に伴って、シリコン薄膜140Mのレーザ光の吸収率が変化する様子を説明する。図4は、シリコン薄膜140Mのレーザ光の吸収率を示す図であって、緩和層121を設けない場合(破線)と、緩和層121を設けた場合(実線)とを比較した図である。

【0075】

図4を参照すれば明らかなように、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が薄い(例えば、中央領域に比べて3%以上薄い、より好ましくは中央領域に比べて10%〜20%薄い)マザー基板110Mの端部領域に緩和層121を設けることにより、緩和層121を設けない場合と比較して、シリコン薄膜140Mのレーザ光の吸収率を低下させることができる。これは、シリコン薄膜140Mに入射するレーザ光の一部が金属薄膜である緩和層121で反射され、入射光と反射光とがシリコン薄膜140M内で光学干渉することによって、シリコン薄膜140Mの吸収率が低下するものと考えられる。

【0076】

その結果、レーザアニール工程において、緩和層121が形成されていない領域のシリコン薄膜140Mは、アモルファスシリコンの融点である1414℃以上の温度範囲まで上昇し、結晶化して多結晶シリコン層となる。一方、緩和層121が形成されている領域(端部領域)のシリコン薄膜140Mは、緩和層121が形成されていない領域(中央領域)のシリコン薄膜140Mより、低い温度までしか上昇しない。そのため、緩和層121が形成されている領域のシリコン薄膜140Mは結晶化しない可能性があるが、この領域のシリコン薄膜140Mは後の工程で除去されるので、問題ない。

【0077】

また、上記のように、シリコン薄膜140Mの中央領域と端部領域とで温度差が生まれるので、端部領域のシリコン薄膜140Mからマザー基板110Mに伝わる熱量は、中央領域における熱伝導量より少なくなる。そのため、冷却時において、マザー基板110Mに発生する引張応力を低減することができるので、マイクロクラックの多い端部領域でマザー基板110Mにクラックが発生するのを有効に防止することができる。

【0078】

但し、図4に示されるように、緩和層121を設けない場合、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が厚くなるほど、レーザ光の吸収率が低下している。一方、緩和層121を設けた場合、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が厚くなるほど、レーザ光の吸収率が上昇している。そして、膜厚低下率が0%の場合、緩和層121を設けた場合の方が吸収率が高くなっている。従って、実施の形態1においては、図3Cに示されるように、ゲート絶縁膜130M及びシリコン薄膜140Mの膜厚が低下するマザー基板110Mの端部領域にのみ緩和層121を形成するのが望ましい。

【0079】

なお、本実施の形態1では、連続発振レーザを用いたレーザアニールによってシリコン薄膜140Mを結晶化させたが、結晶化の方法としては、波長370〜900nm程度のパルスレーザを用いたレーザアニール法、エキシマレーザを用いたレーザアニール法、又は急速熱処理(RTP)によるアニール法を用いても構わない。

【0080】

その後、シリコン薄膜140Mに対して水素プラズマ処理を行うことにより、シリコン薄膜140Mのシリコン原子に対して水素化処理を行う。水素プラズマ処理は、例えばH2、H2/アルゴン(Ar)等の水素ガスを含むガスを原料として高周波(RF)電力により水素プラズマを発生させて、当該水素プラズマをシリコン薄膜140Mに照射することにより行われる。この水素プラズマ処理によって、シリコン原子のダングリングボンド(欠陥)が水素終端され、シリコン薄膜140Mの結晶欠陥密度が低減して結晶性が向上する。

【0081】

次に、図2Eに示されるように、結晶化されたシリコン薄膜140Mをパターニングすることにより、ゲート電極120a〜120fそれぞれに重畳する位置にチャネル層140a、140b、140c、140d、140e、140fをパターン形成する。

【0082】

次に、図2Fに示すように、チャネル層140a〜140f上に、チャネル保護層150a、150b、150c、150d、150e、150fを形成する。この場合、まず、所定の塗布方式によってチャネル保護層150a〜150fを形成するための所定の有機材料を塗布し、スピンコートやスリットコートを行うことによって、チャネル層140a〜140fを覆うように、マザー基板110Mの上面全域に絶縁膜を成膜する。有機材料の膜厚は、有機材料の粘度やコーティング条件(回転数、ブレードの速度など)で制御することができる。なお、絶縁膜の材料としては、シリコン、酸素及びカーボンを含む感光性塗布型の有機材料を用いることができる。

【0083】

その後、絶縁膜に対して約110℃の温度で約60秒間のプリベークを行って絶縁膜を仮焼成する。これにより、絶縁膜に含まれる溶剤が気化する。その後、フォトマスクを用いた露光と現像とを行うことによって絶縁膜をパターニングし、所定形状のチャネル保護層150a〜150fを形成する。その後、パターン形成されたチャネル保護層150a〜150fに対して280℃〜300℃の温度で約1時間のポストベークを行って、チャネル保護層150a〜150fを本焼成して固化する。これにより、チャネル保護層150a〜150f中の有機成分の一部が気化及び分解して膜質が改善されたチャネル保護層150a〜150fを形成することができる。

【0084】

次に、図2Gに示すように、チャネル保護層150a〜150f上に、ソース電極161a、161b、161c、161d、161e、161f及びドレイン電極162a、162b、162c、162d、162e、162fをパターン形成する。この場合、まず、ソース電極161a〜161f及びドレイン電極162a〜162fとなる材料で構成されたソースドレイン金属膜を、例えばスパッタによって成膜する。その後、ソースドレイン金属膜上に所定形状にパターニングされたレジストを形成し、ウェットエッチングを施すことによってソースドレイン金属膜をパターニングする。このとき、チャネル保護層150a〜150fがエッチングストッパとしてチャネル層140a〜140fを保護する。その後、レジストを除去することにより、所定形状のソース電極161a〜161f及びドレイン電極162a〜162fを形成することができる。

【0085】

次に、図2Hに示されるように、ソース電極161a〜161f及びドレイン電極162a〜162fを覆うように、マザー基板110Mの上面全域に層間絶縁膜170Mを形成する。具体的には、例えば、プラズマCVD法により、マザー基板110Mの全域にわたって、窒化シリコンからなる層間絶縁膜170Mを堆積する。

【0086】

次に、図2Iに示されるように、層間絶縁膜170M上に、EL層180を形成する。具体的には、まず、層間絶縁膜170M上に、陽極と発光層とを画素毎に形成し、その上に全画素共通の陰極を形成する。また、発光層は、正孔注入層、正孔輸送層、有機発光層、及び電子輸送層の積層構造体として形成される。

【0087】

次に、図2Jに示されるように、EL層180上に、前面ガラス190を積層する。前面ガラス190は、EL層180から出力される光を透過させる透明ガラスであり、透明樹脂等でEL層180に接着される。

【0088】

そして最後に、図2Kに示されるように、各種薄膜が積層されたマザー基板110Mを所定の大きさに切断する。具体的には、図2Jに示される端部領域(周縁領域)の一部を切り落とすと共に、切断線がスクライブ領域上に位置するようにマザー基板110Mを切断することによって、図2Kに示される薄膜半導体装置100A、100Bを得ることができる。

【0089】

なお、マザー基板110Mの切断方法は特に限定されないが、例えば、ダイヤモンドカッター等で切断してもよい。または前面ガラス190の表面に切欠溝を形成し、その切欠溝に沿って折曲力を加えることによって分断してもよい。

【0090】

上記のように、マザー基板110Mの端部領域に緩和層121を設けた状態でシリコン薄膜140Mを結晶化することにより、端部領域におけるシリコン薄膜140Mからマザー基板110Mへの熱伝導量を大幅に低下させることができる。その結果、結晶化後の冷却工程において、少なくともマザー基板110Mの端部領域に発生する引張応力を低減することができるので、マイクロクラックの多い端部領域でマザー基板110Mにクラックが発生するのを有効に防止することができる。

【0091】

(実施の形態2)

次に、図5を参照して、実施の形態2に係る薄膜半導体装置の構成を説明する。図5は、実施の形態2に係る薄膜半導体装置200の断面図である。なお、実施の形態1と同一の構成要素には同一の参照番号を付し、詳しい説明は省略する。

【0092】

図5に示される薄膜半導体装置200は、緩和層122が基板110の両端部に設けられている点、及び緩和層122がゲート電極120a〜120cと異なる材料で形成されている点が実施の形態1と相違する。

【0093】

実施の形態2に係る緩和層122は、例えば、プラズマCVD法又はスパッタによって、SiO2、SiN等の無機材料を基板110上のゲート電極120a〜120cと同一の層に成膜し、所定の形状にパターニングすることによって形成することができる。または、緩和層122は、無機材料と有機材料との混合材料であるSOG(Spin On Glass:塗布ガラス)を基板110上に塗布し、露光、現像、及びベーク工程を経て形成することができる。なお、実施の形態2に係る緩和層122は、例えば、500nm〜1000nm程度の膜厚とするのが望ましい。

【0094】

次に、図6A及び図6Bを参照して、実施の形態2に係る薄膜半導体装置の製造方法を説明する。図6A及び図6Bは、本発明の実施の形態2に係る薄膜半導体装置の製造方法であって、実施の形態1の図2Bのゲート電極/緩和層形成工程に相当する工程の構成を模式的に示した断面図である。なお、その他の工程は実施の形態1とほぼ共通するので、再度の説明は省略する。

【0095】

まず、図6Aに示されるように、マザー基板110M上に、所定形状のゲート電極120a〜120fを形成する。ゲート電極120a〜120fの形成方法は、実施の形態1と同じであってよい。

【0096】

次に、図6Bに示されるように、マザー基板110M上の端部領域及びスクライブ領域に所定形状の緩和層122を形成する。より具体的には、例えば、緩和層122となるSOGを基板110上に塗布し、フォトマスクを用いた露光と現像とを行うことによって所定の形状にパターニングする。その後、パターン形成された緩和層122をベークすることにより、緩和層122が本焼成して固化する。

【0097】

その後、図2Cに示されるようにゲート絶縁膜130が形成され、図2Dに示されるようにシリコン薄膜140Mが形成されて結晶化される。このとき、実施の形態2に係る緩和層122がシリコン薄膜140Mからマザー基板110Mへの熱伝導量を低下させる仕組みを、図7を参照して説明する。図7は、マザー基板110M上に形成されるアンダーコート層の膜厚とシリコン薄膜140Mを結晶化する際のマザー基板110Mの表面温度との関係を示す図である。

【0098】

図7を参照すれば明らかなように、アンダーコート層の膜厚が厚い程、マザー基板110Mの表面温度が低下している。これは、シリコン薄膜140Mからアンダーコート層を経由してマザー基板110Mに到達する熱が、アンダーコート層の側面から徐々に放熱されるためだと考えられる。そして、実施の形態2に係る緩和層122は、図7のアンダーコート層と同一の役割を担っている。すなわち、実施の形態2に係る緩和層122は、シリコン薄膜140Mからマザー基板110Mへの熱伝導量を低下させる。そして、緩和層122の膜厚は、図7でマザー基板110Mの表面温度が1100℃を下回る500nm以上に設定するのが望ましい。

【0099】

なお、図7に示されるように、シリコン薄膜140Mからマザー基板110Mへの熱伝導量を十分に低下させるためには、アンダーコート層の膜厚を500nm以上にすればよく、必ずしも緩和層122を設ける必要はないとも考えられる。しかしながら、アンダーコート層は、マザー基板110Mの上面全域に均一な膜厚で成膜するために、プラズマCVD法等を用いる必要がある。そのため、膜厚を厚くしようとすると成膜に時間がかかるという課題を生じる。

【0100】

これに対して、緩和層122は、TFT等が形成されない端部領域やスクライブ領域にのみ形成されるので、アンダーコート層と比較して膜厚のばらつきを気にする必要がない。そこで、図6Bに示されるように緩和層122を別工程で形成するとしても、アンダーコート層の膜厚を厚くするよりも製造時間を短縮することができる。

【0101】

上記のように、実施の形態2に係る製造方法では、ゲート電極120a〜120fと緩和層122とが別工程で形成される点で実施の形態1に係る製造方法と相違する。なお、図6Aに示されるゲート電極形成工程と、図6Bに示される緩和層形成工程とは、上記の実行順序に限定されず、緩和層形成工程を先に実行し、ゲート電極形成工程を後に実行してもよい。

【0102】

また、実施の形態2に係る製造方法では、緩和層122をマザー基板110Mの端部領域のみならず、スクライブ領域にも形成している点で実施の形態1に係る製造方法と相違する。なお、スクライブ領域とは、マザー基板110Mの切断工程において、切断線が通る領域を指す。すなわち、切断工程においてマザー基板110Mを4つに切断する場合、例えば、図10Aの参照番号163で示される領域に緩和層122が形成される。

【0103】

そして、実施の形態2の切断工程における切断線は、スクライブ領域に形成された緩和層122上を通る。これにより、切断時に基板110にクラックが発生するのを有効に防止することができる。なお、緩和層122の幅は5mm〜10mm程度であるのに対して、図2Kに示される切断線の幅は1〜2mm程度であるので、マザー基板110Mを緩和層122上で切断したとしても、図5に示されるように、薄膜半導体装置200のスクライブ領域に接する側の端部にも緩和層122が残留する。

【0104】

なお、上記の例では、前面ガラス190を取り付けた後に切断工程を実行する方法を説明したが、切断工程のタイミングは、シリコン薄膜形成工程の後であれば、これに限定されない。例えば、層間絶縁膜170Mを形成した後に切断し、その後の工程(EL層形成工程、前面ガラス取付工程等)は、個々の薄膜半導体装置に対して別々に行なってもよい。これにより、切断時に基板110にクラックが生じて薄膜半導体装置を廃棄せざるを得なくなったとしても、切断工程以降の工程が無駄になるのを防ぐことができる。

【0105】

しかしながら、本実施の形態2においては、クラックの生じやすい基板110のスクライブ領域にも緩和層122を設けたことにより、切断時に基板110にクラックが発生するのを有効に防止している。そのため、上記のように前面ガラス190を取り付けた後に切断する場合でも工程の無駄を心配する必要がない。

【0106】

また、図5に示される薄膜半導体装置200は、ゲート電極120a〜120fと緩和層122とを同一の層に形成したが、上記の例に限定されず、例えば、ゲート絶縁膜130とシリコン薄膜140M(後にチャネル層140a〜140cとなる)との間に緩和層122を設けてもよい。すなわち、実施の形態2に係る緩和層122は、シリコン薄膜140Mを結晶化する際に、シリコン薄膜140Mより下の層に形成されていればよい。

【0107】

(実施の形態3)

次に、図8を参照して、実施の形態3に係る薄膜半導体装置の構成を説明する。図8は、実施の形態3に係る薄膜半導体装置300の断面図である。なお、実施の形態1、2と同一の構成要素には同一の参照番号を付し、詳しい説明は省略する。

【0108】

図8に示される薄膜半導体装置300は、緩和層163が基板110の両端部に設けられている点、及び緩和層163がゲート電極120a〜120cと異なる材料で形成されている点で実施の形態1と相違する。また、図8に示される薄膜半導体装置300は、緩和層163の直下に非晶質シリコン層141が形成されている点で実施の形態1、2と相違する。

【0109】

実施の形態3に係る緩和層163は、基板110上のチャネル層140a〜140cより上の層に、金属材料を所定の形状にパターニングすることによって形成することができる。緩和層163は、表1に示されるような反射率の高い金属を用いることができ、例えば、ソース電極161a〜161c及びドレイン電極162a〜162cと同一の材料で形成してもよい。なお、表1は、緩和層163の材料となり得る金属材料の波長532nmのレーザ光の反射率を示す表である。

【0110】

【表1】

【0111】

次に、図9A〜図9C、図10A、及び図10Bを参照して、実施の形態3に係る薄膜半導体装置の製造方法を説明する。図9A〜図9Cは、本発明の実施の形態3に係る薄膜半導体装置の製造方法であって、実施の形態1の図2Dのシリコン薄膜形成工程および図2Eのチャネル層形成工程に相当する工程の構成を模式的に示した断面図である。図10A及び図10Bは、緩和層163が形成される位置を示す平面図である。なお、その他の工程は実施の形態1とほぼ共通するので、再度の説明は省略する。但し、実施の形態3においては、図2Bに示される工程で緩和層163は形成されない。

【0112】

まず、図9A及び図10Aに示されるように、シリコン薄膜140M上の端部領域及びスクライブ領域に所定形状の緩和層163を形成する。緩和層163となる材料で構成された金属膜を、例えばスパッタによって成膜する。その後、金属膜上に所定形状にパターニングされたレジストを形成し、ウェットエッチングを施すことによって金属膜をパターニングする。

【0113】

次に、図9B及び図10Aに示されるように、一部が緩和層163で覆われたシリコン薄膜140Mの上面全域にレーザ光を照射することにより、シリコン薄膜140Mを結晶化する。その結果、図9Bに示されるように、シリコン薄膜140Mの緩和層163で覆われていない領域は、結晶化されて多結晶シリコン層140となる。

【0114】

一方、表1に示されるレーザ光の反射率の高い金属材料は、表2に示されるように、レーザ光の透過率が極めて低い。その結果、シリコン薄膜140Mの緩和層163で覆われている領域は、緩和層163によってレーザ光が遮光されるので温度がほとんど上昇しないので、この領域におけるシリコン薄膜140Mからマザー基板110Mへの熱伝導量を低下させることができる。また、結果として、シリコン薄膜140Mの緩和層163で覆われている領域は、結晶化されずに非晶質シリコン層141のままとなる。

【0115】

【表2】

【0116】

なお、図10Aでは、シリコン薄膜140Mの全域にレーザ光を照射する例を示したが、必ずしもシリコン薄膜140Mの全域に照射する必要はない。例えば、図10Bに示されるように、マザー基板110Mの2組の対辺のうちの一方側(短辺側)のみに緩和層163を形成した場合、図10Bに示されるように、緩和層163が形成されなかった側(長辺側)の端部(図10Bの非ハッチング領域)をレーザ光の照射範囲から除外してもよい。

【0117】

この場合、レーザ光を、照射範囲から除外する辺と平行な方向(図10Bの例では、左右方向)に走査するのが望ましい。これにより、レーザ光の照射開始位置と照射終了位置とを調整すれば、緩和層163が形成されなかった側の端部を容易に照射範囲から除外することができる。これは、実施の形態1、2についても同様である。

【0118】

次に、図9Cに示されるように、多結晶シリコン層140をパターニングすることにより、ゲート電極120a〜120fそれぞれに重畳する位置にチャネル層140a、140b、140c、140d、140e、140fをパターン形成する。このとき、非晶質シリコン層141は、緩和層163がマスクとして機能するために、除去されずに残る。一方、図9Cのチャネル層形成工程に先立って緩和層163を除去すれば、チャネル層形成工程で非晶質シリコン層141を除去することができる。しかしながら、非晶質シリコン層141及び緩和層163は、薄膜半導体装置300が完成した後に応力緩和層として機能するので、残しておくのが望ましい。

【0119】

次に、上記の各実施の形態1〜3に係る薄膜半導体装置100、200、300を表示装置に適用した例について、図11を用いて説明する。なお、本実施の形態では、有機EL表示装置への適用例について説明する。図11は、本発明の実施の形態に係る有機EL表示装置の一部切り欠き斜視図である。

【0120】

図11に示すように、有機EL表示装置10は、アクティブマトリクス基板(TFTアレイ基板)11と、アクティブマトリクス基板11においてマトリクス状に複数配置された画素12と、画素12に接続され、アクティブマトリクス基板11上にアレイ状に複数配置された画素回路13と、画素12と画素回路13の上に順次積層された陽極14、有機EL層15及び陰極16(透明電極)と、各画素回路13と制御回路(不図示)とを接続する複数本のソース線17及びゲート線18とを備える。有機EL層15は、電子輸送層、発光層、正孔輸送層等の各層が積層されて構成されている。

【0121】

なお、図1の薄膜半導体装置100、200、300に形成された複数の薄膜トランジスタは、図11の画素回路13それぞれに形成されるスイッチングトランジスタ又は駆動トランジスタに相当する。また、図1のEL層180は、図11の陽極、有機EL層15、及び陰極16に相当する。

【0122】

次に、上記有機EL表示装置10における画素12の回路構成について、図12を用いて説明する。図12は、本発明の実施の形態に係る薄膜半導体装置100、200、300を用いた画素の回路構成を示す図である。

【0123】

図12に示すように、画素12は、駆動トランジスタ21と、スイッチングトランジスタ22と、有機EL素子23と、コンデンサ24とを備える。駆動トランジスタ21は、有機EL素子23を駆動するトランジスタであり、また、スイッチングトランジスタ22は、画素12を選択するためのトランジスタである。

【0124】

スイッチングトランジスタ22のソース電極22Sは、ソース線17に接続され、ゲート電極22Gは、ゲート線18に接続され、ドレイン電極22Dは、コンデンサ24及び駆動トランジスタ21のゲート電極21Gに接続されている。また、駆動トランジスタ21のドレイン電極21Dは、電源線25に接続され、ソース電極21Sは有機EL素子23のアノードに接続されている。

【0125】

この構成において、ゲート線18にゲート信号が入力され、スイッチングトランジスタ22をオン状態にすると、ソース線17を介して供給された信号電圧がコンデンサ24に書き込まれる。そして、コンデンサ24に書き込まれた保持電圧は、1フレーム期間を通じて保持される。この保持電圧により、駆動トランジスタ21のコンダクタンスがアナログ的に変化し、発光階調に対応した駆動電流が、有機EL素子23のアノードからカソードへと流れる。これにより、有機EL素子23が発光し、所定の画像を表示することができる。

【0126】

なお、本実施の形態では、有機EL素子を用いた有機EL表示装置について説明したが、液晶表示装置等、アクティブマトリクス基板が用いられる他の表示装置にも適用することができる。また、このように構成される表示装置については、フラットパネルディスプレイとして利用することができ、テレビジョンセット、パーソナルコンピュータ、携帯電話などのあらゆる表示パネルを有する電子機器に適用することができる。

【0127】

以上、図面を参照してこの発明の実施形態を説明したが、この発明は、図示した実施形態のものに限定されない。図示した実施形態に対して、この発明と同一の範囲内において、あるいは均等の範囲内において、種々の修正や変形を加えることが可能である。

【産業上の利用可能性】

【0128】

本発明は、表示装置に画素回路等に用いられる薄膜半導体装置に有利に利用される。

【符号の説明】

【0129】

10 有機EL表示装置

11 アクティブマトリクス基板

12 画素

13 画素回路

14 陽極

15 有機EL層

16 陰極

17 ソース線

18 ゲート線

21 駆動トランジスタ

22 スイッチングトランジスタ

21G,22G,120a,120b,120c,120d,120e,120f ゲート電極

21S,22S,161a,161b,161c,161d,161e,161f ソース電極

21D,22D,162a,162b,162c,162d,162e,162f ドレイン電極

23 有機EL素子

24 コンデンサ

100,100A,100B,200,300 薄膜半導体装置

110,900 基板

121,122,163 緩和層

130,130M ゲート絶縁膜

140 多結晶シリコン層

140a,140b,140c,140d,140e,140f チャネル層

140M シリコン薄膜

141 非晶質シリコン層

150a,150b,150c,150d,150e,150f チャネル保護層

170,170A,170B,170M 層間絶縁膜

180,180A,180B,180M EL層

190,190A,190B,190M 前面ガラス

910 マイクロクラック

920 クラック

【特許請求の範囲】

【請求項1】

基板を準備する基板準備工程と、

前記基板上に第1薄膜を形成する第1薄膜形成工程と、

前記第1薄膜に対して光線を相対走査して照射することにより、前記第1薄膜を結晶化する結晶化工程と、

前記結晶化工程において前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層を、前記結晶化工程の前に、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む、

薄膜形成方法。

【請求項2】

前記緩和層は、

前記基板と前記第1薄膜との間に形成され、

前記緩和層に重畳する位置の前記第1薄膜の前記光線の吸収率を低下させることによって、前記基板への熱伝導量を低下させる、

請求項1に記載の薄膜形成方法。

【請求項3】

前記緩和層は、

前記光線を反射する材料で形成され、

前記第1薄膜に照射される前記光線と、前記緩和層で反射された光線とを光学干渉させることによって、前記第1薄膜の前記光線の吸収率を低下させる、

請求項2に記載の薄膜形成方法。

【請求項4】

前記緩和層は、金属材料で形成される、

請求項2又は3に記載の薄膜形成方法。

【請求項5】

該薄膜形成方法は、さらに、前記基板と前記第1薄膜との間に第2薄膜を形成する第2薄膜形成工程を含み、

前記緩和層は、前記第1及び第2薄膜の平均膜厚が前記基板の中央領域より10%〜20%薄い前記基板の端部領域にのみ形成される、

請求項2〜4のいずれか1項に記載の薄膜形成方法。

【請求項6】

前記緩和層は、

膜厚が500nm〜1000nmであり、

前記基板と前記第1薄膜との間に形成される、

請求項1に記載の薄膜形成方法。

【請求項7】

前記緩和層は、無機材料で形成される、

請求項6に記載の薄膜形成方法。

【請求項8】

前記緩和層は、有機材料と無機材料との混合材料である、

請求項7に記載の薄膜形成方法。

【請求項9】

該薄膜形成方法は、さらに、前記基板上に第3薄膜を形成する第3薄膜形成工程を含み、

前記緩和層は、前記第1及び第3薄膜の間に形成される、

請求項6〜8のいずれか1項に記載の薄膜形成方法。

【請求項10】

前記第3薄膜は、酸化珪素膜であり、

前記緩和層は、SOG(Spin On Glass)膜である、

請求項9に記載の薄膜形成方法。

【請求項11】

前記緩和層は、

前記第1薄膜上に形成され、

前記光線を遮光することによって、前記第1薄膜から前記基板への熱伝導量を低下させる、

請求項1に記載の薄膜形成方法。

【請求項12】

前記緩和層は、金属材料で形成される、

請求項11に記載の薄膜形成方法。

【請求項13】

前記金属材料は、MoW、W、Ta、Cr、Cu、Alのいずれかを含む、

請求項12に記載の薄膜形成方法。

【請求項14】

前記緩和層の前記光線の反射率は、60%以上である、

請求項12又は13に記載の薄膜形成方法。

【請求項15】

前記結晶化工程で結晶化された前記第1薄膜に含まれる結晶粒の平均粒径は、50nm以上、1μm以下である、

請求項1〜14のいずれか1項に記載の薄膜形成方法。

【請求項16】

前記光線は、連続発振のレーザ光線であり、

前記レーザ光線の波長は、532nmである、

請求項1〜15のいずれか1項に記載の薄膜形成方法。

【請求項17】

前記薄膜形成方法は、さらに、前記結晶化工程の後に、前記緩和層に重畳する位置に切断線が位置するように、前記基板を切断する工程を含む、

請求項1〜16のいずれか1項に記載の薄膜形成方法。

【請求項18】

前記基板は、クラック、チッビング、切欠、のいずれかを有する、

請求項1〜17のいずれか1項に記載の薄膜形成方法。

【請求項19】

前記緩和層は、前記基板の端部のうち、前記光線の相対走査方向に交差する側の端部にのみ形成される、

請求項1〜18のいずれか1項に記載の薄膜形成方法。

【請求項20】

前記第1薄膜は、シリコンを含有する材料で構成される、

請求項1〜19のいずれか1項に記載の薄膜形成方法。

【請求項21】

請求項1〜20のいずれか1項に記載の薄膜形成方法を含む、

表示装置の製造方法。

【請求項22】

基板と、

前記基板上に形成され、光線が照射されることによって結晶化された第1薄膜と、

前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に、前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層とを備える、

薄膜形成基板。

【請求項1】

基板を準備する基板準備工程と、

前記基板上に第1薄膜を形成する第1薄膜形成工程と、

前記第1薄膜に対して光線を相対走査して照射することにより、前記第1薄膜を結晶化する結晶化工程と、

前記結晶化工程において前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層を、前記結晶化工程の前に、前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む、

薄膜形成方法。

【請求項2】

前記緩和層は、

前記基板と前記第1薄膜との間に形成され、

前記緩和層に重畳する位置の前記第1薄膜の前記光線の吸収率を低下させることによって、前記基板への熱伝導量を低下させる、

請求項1に記載の薄膜形成方法。

【請求項3】

前記緩和層は、

前記光線を反射する材料で形成され、

前記第1薄膜に照射される前記光線と、前記緩和層で反射された光線とを光学干渉させることによって、前記第1薄膜の前記光線の吸収率を低下させる、

請求項2に記載の薄膜形成方法。

【請求項4】

前記緩和層は、金属材料で形成される、

請求項2又は3に記載の薄膜形成方法。

【請求項5】

該薄膜形成方法は、さらに、前記基板と前記第1薄膜との間に第2薄膜を形成する第2薄膜形成工程を含み、

前記緩和層は、前記第1及び第2薄膜の平均膜厚が前記基板の中央領域より10%〜20%薄い前記基板の端部領域にのみ形成される、

請求項2〜4のいずれか1項に記載の薄膜形成方法。

【請求項6】

前記緩和層は、

膜厚が500nm〜1000nmであり、

前記基板と前記第1薄膜との間に形成される、

請求項1に記載の薄膜形成方法。

【請求項7】

前記緩和層は、無機材料で形成される、

請求項6に記載の薄膜形成方法。

【請求項8】

前記緩和層は、有機材料と無機材料との混合材料である、

請求項7に記載の薄膜形成方法。

【請求項9】

該薄膜形成方法は、さらに、前記基板上に第3薄膜を形成する第3薄膜形成工程を含み、

前記緩和層は、前記第1及び第3薄膜の間に形成される、

請求項6〜8のいずれか1項に記載の薄膜形成方法。

【請求項10】

前記第3薄膜は、酸化珪素膜であり、

前記緩和層は、SOG(Spin On Glass)膜である、

請求項9に記載の薄膜形成方法。

【請求項11】

前記緩和層は、

前記第1薄膜上に形成され、

前記光線を遮光することによって、前記第1薄膜から前記基板への熱伝導量を低下させる、

請求項1に記載の薄膜形成方法。

【請求項12】

前記緩和層は、金属材料で形成される、

請求項11に記載の薄膜形成方法。

【請求項13】

前記金属材料は、MoW、W、Ta、Cr、Cu、Alのいずれかを含む、

請求項12に記載の薄膜形成方法。

【請求項14】

前記緩和層の前記光線の反射率は、60%以上である、

請求項12又は13に記載の薄膜形成方法。

【請求項15】

前記結晶化工程で結晶化された前記第1薄膜に含まれる結晶粒の平均粒径は、50nm以上、1μm以下である、

請求項1〜14のいずれか1項に記載の薄膜形成方法。

【請求項16】

前記光線は、連続発振のレーザ光線であり、

前記レーザ光線の波長は、532nmである、

請求項1〜15のいずれか1項に記載の薄膜形成方法。

【請求項17】

前記薄膜形成方法は、さらに、前記結晶化工程の後に、前記緩和層に重畳する位置に切断線が位置するように、前記基板を切断する工程を含む、

請求項1〜16のいずれか1項に記載の薄膜形成方法。

【請求項18】

前記基板は、クラック、チッビング、切欠、のいずれかを有する、

請求項1〜17のいずれか1項に記載の薄膜形成方法。

【請求項19】

前記緩和層は、前記基板の端部のうち、前記光線の相対走査方向に交差する側の端部にのみ形成される、

請求項1〜18のいずれか1項に記載の薄膜形成方法。

【請求項20】

前記第1薄膜は、シリコンを含有する材料で構成される、

請求項1〜19のいずれか1項に記載の薄膜形成方法。

【請求項21】

請求項1〜20のいずれか1項に記載の薄膜形成方法を含む、

表示装置の製造方法。

【請求項22】

基板と、

前記基板上に形成され、光線が照射されることによって結晶化された第1薄膜と、

前記基板の端部領域及び前記基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に、前記第1薄膜に生じる熱の前記基板への伝導量を低下させる緩和層とを備える、

薄膜形成基板。

【図1】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図2I】

【図2J】

【図2K】

【図3A】

【図3B】

【図3C】

【図4】

【図5】

【図6A】

【図6B】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図10A】

【図10B】

【図11】

【図12】

【図14】

【図13】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図2I】

【図2J】

【図2K】

【図3A】

【図3B】

【図3C】

【図4】

【図5】

【図6A】

【図6B】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図10A】

【図10B】

【図11】

【図12】

【図14】

【図13】

【公開番号】特開2013−102083(P2013−102083A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−245577(P2011−245577)

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]