薄膜抵抗を備えた半導体装置の製造方法

【課題】薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供する。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロムシリコン(CrSi)等で構成された薄膜抵抗を有し、この薄膜抵抗に対して配線部が電気的に接続されてなる薄膜抵抗を備えた半導体装置の製造方法に関するものである。

【背景技術】

【0002】

従来、クロムシリコン等で構成された薄膜抵抗に対して電気的に接続される配線部は、下層にチタン(Ti)膜と窒化チタン(TiN)膜を形成した二層構造などによって構成されている。配線部をチタン膜の単層構造とすることもできるが、チタン膜の単層構造だと、チタン膜を形成した後に、チタン膜の上部に配置される層間絶縁膜にビアホールを形成するときのエッチング選択比が低く、ビアホール加工を制御性良く行なえない。具体的には、フッ素(F)系ガスによって層間絶縁膜に対してビアホールを形成する場合、1/2以下の選択比となる。このため、層間絶縁膜にビアホールを形成する際にチタン膜を突き抜けてしまう可能性がある。また、チタン膜は、パターニング時に用いるレジストとの密着性が悪く、良好なパターニングを行うのが難しい。これらのことから、チタン膜の単層構造ではなく、チタン膜よりも選択比が高く、かつ、チタン膜よりもレジストとの密着性が高い窒化チタン膜をチタン膜の上層に配置した二層構造が採用されている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−60590号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

窒化チタン膜は、スパッタ装置を用いて、チャンバー内に窒素(N2)およびアルゴン(Ar)を同時に導入しつつ、チタンをターゲットとしたスパッタを行うことによって形成される。しかしながら、窒化チタンを形成する際に生成される窒素ラジカルが薄膜抵抗の構成材料(例えばクロムシリコン)と反応して窒化物(例えば窒化クロムシリコン(CrSiN)や窒化シリコン(SiN))が形成され、配線部と薄膜抵抗との接触抵抗を高抵抗化させるという問題がある。

【0005】

本発明は上記点に鑑みて、薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するため、請求項1に記載の発明では、スパッタ装置内にターゲットとなる金属窒化膜を備える工程と、スパッタ装置内に薄膜抵抗(R)を構成する抵抗膜(3)が形成された半導体基板(1)を設置し、スパッタ装置内に窒素を導入することなく、金属窒化膜をターゲットとしたスパッタを行うことで、抵抗膜(3)の表面に金属窒化膜(5)を形成することで、配線部を構成する第1金属層(5)を形成する工程を含んでいることを特徴としている。

【0007】

このように、スパッタ装置内において事前に金属窒化膜を備えておき、その後、窒素を導入することなく金属窒化膜をターゲットとしたスパッタにより、金属窒化膜によって配線部を構成する第1金属層(5)を形成するようにしている。このため、薄膜抵抗(R)と接触する第1金属層(5)を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層(5)の成膜を行うことができるため、薄膜抵抗(R)の露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗(R)と配線部を構成する第1金属層(5)との接触抵抗が高抵抗化することを抑制することが可能となる。

【0008】

例えば、請求項2に記載したように、スパッタ装置内に半導体基板(1)を設置する前に、スパッタ装置内に金属窒化膜の窒化前の材料をターゲットとして設置する工程と、窒化前の材料をターゲットとして設置する工程の後に、スパッタ装置内に窒素を導入して窒素ラジカルを発生させることでターゲットとなる材料を窒化させ、金属窒化膜を形成する工程とを行うことにより、スパッタ装置内に金属窒化膜を備えることができる。

【0009】

請求項3に記載の発明では、第1金属層(5)の表面に絶縁材料にて構成される容量膜(6)を成膜する工程と、容量膜(6)の表面に、第1金属層(5)と対向配置される第2金属層(7)を形成することで、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)を構成する工程と、を含んでいることを特徴としている。

【0010】

このように、第1金属層(5)の表面に容量膜(6)を構成すると共に、容量膜(6)の表面に第2金属層(7)を形成し、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)を構成することもできる。これにより、薄膜抵抗(R)の配線部とメタルキャパシタンス(C)の電極を共通化させることが可能となる。

【0011】

請求項4ないし7に記載の発明では、半導体素子が形成された半導体基板(1)と、半導体基板(1)の上に配置され、抵抗材料からなる抵抗膜(3)にて構成された薄膜抵抗(R)と、薄膜抵抗(R)に接触する金属窒化物で構成された第1金属層(5)と、第1金属層(5)の表面に形成され、絶縁材料にて構成された容量膜(6)と、容量膜(6)の表面に形成され、第1金属層(5)と対向配置された第2金属層(7)とを有し、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)が構成されていると共に、薄膜抵抗(R)に接触させられた第1金属層(5)によって、メタルキャパシタンス(C)の電極が構成されていることを特徴としている。

【0012】

このように、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)が構成されていると共に、薄膜抵抗(R)に接触させられた第1金属層(5)によって、メタルキャパシタンス(C)の電極が構成されるようにすれば、薄膜抵抗(R)の配線部とメタルキャパシタンス(C)の電極を共通化させることが可能となる。

【0013】

例えば、請求項5に記載したように、第1金属層(5)を構成する金属窒化物としては、窒化チタン、窒化タングステン、窒化タンタル、窒化クロム、窒化銅のいずれかを適用することができる。また、請求項6に記載したように、容量膜(6)を構成する絶縁材料としては、シリコン酸化膜、シリコン窒化膜、窒化アルミニウム、ペロブスカイト材料のいずれかを適用することができる。

【0014】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【図面の簡単な説明】

【0015】

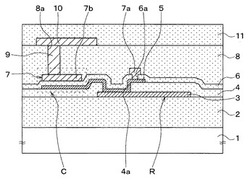

【図1】本発明の第1実施形態にかかる薄膜抵抗Rを備えた半導体装置の断面図である。

【図2】図1に示す薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。

【図3】図2に続く薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。

【図4】図3に続く薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、図中、同一符号を付してある。

【0017】

(第1実施形態)

本発明の第1実施形態について説明する。図1に、本実施形態にかかる薄膜抵抗Rを備えた半導体装置の断面図を示す。以下、この図を参照して、本実施形態にかかる薄膜抵抗Rを備えた半導体装置について説明する。

【0018】

図1に示す半導体装置は、半導体素子(図示せず)が形成された半導体基板1の表面に、層間絶縁膜となる第1絶縁膜2を介して薄膜抵抗RおよびメタルキャパシタンスCを備えることにより構成されている。

【0019】

具体的には、半導体基板1の表面には、TEOS等のシリコン酸化膜によって第1絶縁膜2が形成され、この第1絶縁膜2の表面に薄膜抵抗Rを構成する抵抗膜3が形成されている。抵抗膜3は、クロムシリコン(CrSi)などの抵抗材料によって構成されている。

【0020】

抵抗膜3および第1絶縁膜2の表面には、TEOS等のシリコン酸化膜によって構成された層間絶縁膜となる第2絶縁膜4が形成されている。この第2絶縁膜4には、抵抗膜3の一部を露出させるビアホール4aが形成されている。このビアホール4a内の抵抗膜3の表面および第2絶縁膜4の表面に第1金属層5が形成され、第1金属層5が薄膜抵抗Rに対して電気的に接続されている。

【0021】

第1金属層5は、窒化チタン(TiN)膜によって構成されており、所望のレイアウトにパターニングされている。この第1金属層5は、メタルキャパシタンスCにおける第1電極を構成すると共に、メタルキャパシタンスCと薄膜抵抗Rとを接続する配線層としての機能を果たす。

【0022】

また、第1金属層5の表面には、TEOS等のシリコン酸化膜によって構成された容量膜6が形成されている。この容量膜6の表面には、Al等によって構成された第2金属層7が形成されている。第2金属層7は、第1配線(1st−Al)を構成するもので、容量膜6に形成されたビアホール6aを通じて第1金属層5および薄膜抵抗Rと電気的に接続された部分7aや、容量膜6を挟んで第1金属層5と対向配置される部分7bを有している。例えば、第2金属層7のうち薄膜抵抗Rに電気的に接続された部分7aは、図1とは別断面において外部と電気的に接続される薄膜抵抗Rを制御するために用いられるパッドに繋がっている。また、第1金属層5と対向配置される部分7bは、メタルキャパシタンスCにおける第1電極と対になる第2電極を構成する。これらの部分7a、7bは、電気的に分離されている。

【0023】

このような構成により、図1中の破線にて囲んだ部分、つまり、第1金属層5にて構成される第1電極と容量膜6および第2金属層7によって構成される第2電極によって、メタルキャパシタンスCが形成されている。

【0024】

また、第2金属層7や容量膜6の表面を覆うようにTEOS等のシリコン酸化膜によって構成された層間絶縁膜を構成する第3絶縁膜8が形成されている。この第3絶縁膜8にはビアホール8aが形成されており、ビアホール8a内には、第2金属層7におけるメタルキャパシタンスCの第2電極を構成する部分7bと電気的に接続されたタングステン(W)等で構成された金属プラグ9が埋め込まれている。そして、第3絶縁膜8の表面に、Al等によって構成された第3金属層10がパターニングされている。この第3金属層10は、第2配線(2nd−Al)を構成するもので、金属プラグ9に電気的に接続されることで、メタルキャパシタンスCにおける第2電極となる部分7bと電気的に接続されている。そして、第3金属層10および第3絶縁膜8の表面を覆うようにTEOS等のシリコン酸化膜によって構成された保護膜11が形成されることで、図1に示した薄膜抵抗Rを備えた半導体装置が構成されている。

【0025】

続いて、図1に示す薄膜抵抗Rを備えた半導体装置の製造方法について説明する。図2〜図4は、図1に示す薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。これらの図を参照して説明する。なお、これらの図では、半導体基板1に関しては省略してあり、半導体装置のうち半導体基板1の表面上に形成される部分についてのみ図示してある。

【0026】

〔図2(a)の工程〕

まず、半導体素子を形成した半導体基板1をCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される第1絶縁膜2をデポジションする。

【0027】

〔図2(b)の工程〕

次に、第1絶縁膜2を形成した半導体基板1をスパッタ装置内に設置した後、クロムシリコン等の抵抗材料をターゲットとしたスパッタを行い、例えば膜厚10〜100nmの抵抗膜3を形成する。そして、ホト工程によって薄膜抵抗Rの形成予定領域以外が開口するマスク(図示せず)を配置した後、ウェットエッチングもしくはドライエッチングを行うことで、抵抗膜3をパターニングする。これにより、薄膜抵抗Rが構成される。

【0028】

〔図2(c)の工程〕

図2(b)の工程まで行った半導体基板1を再びCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される第2絶縁膜4をデポジションする。そして、ホト工程によってビアホール形成予定領域が開口するマスク(図示せず)を配置した後、ウェットエッチングもしくはドライエッチングを行うことで、第2絶縁膜4に対してビアホール4aを形成し、抵抗膜3を部分的に露出させる。

【0029】

〔図2(d)の工程〕

図2(c)の工程まで行った半導体基板1を再びスパッタ装置内に設置するが、それに先立って、スパッタ装置に対して以下の処理を行っておく。具体的には、スパッタ装置のチャンバー内にターゲット用のチタン膜を設置しておき、チタン膜の表面を窒化させるための処理を行う。これにより、ターゲット用のチタン膜の少なくとも表面が窒化チタンとなる。例えば、スパッタ装置のチャンバー内に窒素(N2)とアルゴン(Ar)を1:1の比率とした混合ガスを流量7sccmで導入し、スパッタ装置におけるDCパワーを3kWとして窒素ラジカルを発生させることで、チタン膜の表面を窒化チタンとすることができる。

【0030】

その後、ガス導入を停止すると共に、電圧供給を停止する。これにより、窒素ラジカルが完全に無くなってから、半導体基板1をスパッタ装置に設置する。そして、半導体基板1を加熱して基板温度を230℃とし、アルゴンを流量7sccmで導入しつつ、スパッタ装置におけるDCパワーを3kWとしてアルゴンイオンでチタン膜の表面に形成された窒化チタンをターゲットとしたスパッタを行い、窒化チタンにて構成される第1金属層5を例えば0.05〜0.1μmの厚さで成膜する。このとき、窒化ラジカルが残留していない状態でのスパッタを行うことができるため、クロムシリコン等で構成された薄膜抵抗Rの表面、具体的には抵抗膜3のうちビアホール4aから露出した部分が窒化されることで、窒化クロムシリコン(CrSiN)や窒化シリコン(SiN)が形成されることを抑制できる。

【0031】

なお、薄膜抵抗Rとの接触部におけるオーミック性を向上させるために、窒化チタンにて構成される第1金属層5の組成比、つまりチタンの窒素に対する比率は、窒素1に対してチタン1.5以上とすると好ましい。ただし、第1金属層5がすべてこの比率の組成比である必要はなく、薄膜抵抗Rと接触する界面から5nm程度の厚み分がこの比率の組成比となっていれば良い。このような第1金属層5の組成比については、ターゲット用のチタン膜の表面を窒化チタンとするときの窒素とアルゴンの比率や流量、DCパワーの印加時間などによって調整できる。

【0032】

続いて、ホト工程によって第1金属層5の上に当該第1金属層5の不要部分が開口するマスク(図示せず)を配置した後、塩素系(例えばBCl3等)ドライエッチングによって第1金属層5をパターニングする。このとき、第1金属層5の表面がチタン膜ではなく窒化チタン膜によって構成されているため、マスクとなるレジストとの密着性が良く、良好なパターニングを行うことができる。このようにして、薄膜抵抗Rを構成する抵抗膜3に電気的に接続された第1金属層5が構成される。

【0033】

〔図3(a)の工程〕

第1金属層5および第2絶縁膜4の表面全面を覆うようにTEOS膜などで構成された容量膜6を例えば0.05〜0.3μmの厚さで成膜する。例えば、図2(d)の工程まで行われた半導体基板1をCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によって容量膜6をデポジションする。

【0034】

〔図3(b)の工程〕

容量膜6の表面上に、ホト工程によってビアホール形成予定領域が開口するマスク(図示せず)を配置した後、フッ素系のドライエッチングを行うことで、容量膜6に対してビアホール6aを形成し、第1金属層5を部分的に露出させる。このとき、第1金属層5がチタン膜の単層膜ではなく窒化チタン膜によって構成されているため、ビアホール形成時の選択比を高めることが可能となり、第1金属層5を突き抜けてしまうこともない。

【0035】

〔図3(c)の工程〕

ビアホール6a内を含めて容量膜6の表面上に第2金属層7を成膜する。例えば、アルミニウムを主成分とする配線材料を反射防止膜で覆った構造、具体的には、チタン膜、窒化チタン膜、銅を含有したアルミニウム、窒化チタン膜、チタン膜を順にデポジションすることにより、Ti/TiN/Al−Cu/Ti/TiN構造とされた第2金属層7を形成する。そして、第2金属層7の表面に当該第2金属層7の不要部分が開口するマスク(図示せず)を配置した後、フッ素(F)系ドライエッチングによって第2金属層7をパターニングする。

【0036】

〔図3(d)の工程〕

図3(c)の工程まで行った半導体基板1をCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される第3絶縁膜8をデポジションする。

【0037】

〔図4(a)の工程〕

第3絶縁膜8の表面にホト工程によってビアホール形成予定領域が開口するマスク(図示せず)を配置した後、フッ素系ドライエッチングを行うことで、第3絶縁膜8に対してビアホール8aを形成し、第2金属層7を部分的に露出させる。そして、CVD装置などを用いてタングステン等で構成される金属プラグ9の構成材料を成膜することによってビアホール8a内を埋め込み、CMP(Chemical Mechanical Polishing)によって平坦化することで金属プラグ9を形成する。

【0038】

〔図4(b)の工程〕

金属プラグ9および第3絶縁膜8の表面に第3金属層10を形成する。例えば、例えば、アルミニウムを主成分とする配線材料を反射防止膜で覆った構造、具体的には、チタン膜、窒化チタン膜、銅を含有したアルミニウム、窒化チタン膜、チタン膜を順にデポジションすることにより、Ti/TiN/Al−Cu/Ti/TiN構造の第3金属層10を形成する。そして、第3金属層10の表面に当該第3金属層10の不要部分が開口するマスク(図示せず)を配置した後、フッ素(F)系ドライエッチングによって第3金属層10をパターニングする。

【0039】

この後、図4(b)の工程まで行った半導体基板1をCVD装置などの絶縁膜形成用装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される保護膜11をデポジションすることで、図1に示した薄膜抵抗Rを備えた半導体装置が完成する。

【0040】

以上説明したように、本実施形態では、スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成するようにしている。このため、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

【0041】

(他の実施形態)

上記実施形態では、第1金属層5を形成する際に、スパッタ装置内においてターゲット用のチタン膜の表面を窒化チタンにしたのち、スパッタ装置内の窒素ラジカルが完全に無くなるまでガス導入、電圧供給を停止し、その後、窒化チタンをターゲットとしたスパッタを行うようにしている。これに対して、初めから窒化チタン膜を他の装置で焼結などによって製造しておき、それをスパッタ装置内にターゲット用に設置し、スパッタを行うことで第1金属層5を形成するという手法を用いても、上記実施形態と同様の効果を得ることができる。

【0042】

上記実施形態では、第1金属層5を構成する金属窒化膜を窒化チタンにて構成する場合について説明したが、他の金属窒化物にて構成されていても良い。金属窒化物としては、窒化タングステン(WN)、窒化タンタル(TaN)、窒化クロム(CrN)、窒化銅(CuN)がある。特に、窒化銅は、比抵抗が低いことから、第1金属層5として窒化銅を用いれば、配線抵抗の低下の効果を得ることもできる。

【0043】

また、メタルキャパシタンスCを構成するための容量膜6として、上記実施形態では、TEOS等のシリコン酸化膜を用いているが、他の絶縁材料を用いても良い。例えば、シリコン窒化膜、窒化アルミニウム(AlN)、ペロブスカイト材料によって容量膜6を構成することもできる。特に、ペロブスカイトは比誘電率が高いため、容量膜6として用いると高い容量値を得ることができ、キャパシタンス効果が大きい。

【0044】

さらに、上記実施形態では、薄膜抵抗Rを構成する抵抗膜3の抵抗材料としてクロムシリコン(CrSi)を例に挙げて説明したが、その他の材料、例えばニッケルクロム(NiCr)などを使用する場合にも、クロムシリコンを用いる場合と同様の問題が生じるため、本発明を適用することができる。

【符号の説明】

【0045】

1 半導体基板

2 第1絶縁膜

3 抵抗膜

4 第2絶縁膜

4a ビアホール

5 第1金属層

6 容量膜

6a ビアホール

7 第2金属層

8 第3絶縁膜

9 金属プラグ

10 第3金属層

11 保護膜

【技術分野】

【0001】

本発明は、クロムシリコン(CrSi)等で構成された薄膜抵抗を有し、この薄膜抵抗に対して配線部が電気的に接続されてなる薄膜抵抗を備えた半導体装置の製造方法に関するものである。

【背景技術】

【0002】

従来、クロムシリコン等で構成された薄膜抵抗に対して電気的に接続される配線部は、下層にチタン(Ti)膜と窒化チタン(TiN)膜を形成した二層構造などによって構成されている。配線部をチタン膜の単層構造とすることもできるが、チタン膜の単層構造だと、チタン膜を形成した後に、チタン膜の上部に配置される層間絶縁膜にビアホールを形成するときのエッチング選択比が低く、ビアホール加工を制御性良く行なえない。具体的には、フッ素(F)系ガスによって層間絶縁膜に対してビアホールを形成する場合、1/2以下の選択比となる。このため、層間絶縁膜にビアホールを形成する際にチタン膜を突き抜けてしまう可能性がある。また、チタン膜は、パターニング時に用いるレジストとの密着性が悪く、良好なパターニングを行うのが難しい。これらのことから、チタン膜の単層構造ではなく、チタン膜よりも選択比が高く、かつ、チタン膜よりもレジストとの密着性が高い窒化チタン膜をチタン膜の上層に配置した二層構造が採用されている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−60590号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

窒化チタン膜は、スパッタ装置を用いて、チャンバー内に窒素(N2)およびアルゴン(Ar)を同時に導入しつつ、チタンをターゲットとしたスパッタを行うことによって形成される。しかしながら、窒化チタンを形成する際に生成される窒素ラジカルが薄膜抵抗の構成材料(例えばクロムシリコン)と反応して窒化物(例えば窒化クロムシリコン(CrSiN)や窒化シリコン(SiN))が形成され、配線部と薄膜抵抗との接触抵抗を高抵抗化させるという問題がある。

【0005】

本発明は上記点に鑑みて、薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するため、請求項1に記載の発明では、スパッタ装置内にターゲットとなる金属窒化膜を備える工程と、スパッタ装置内に薄膜抵抗(R)を構成する抵抗膜(3)が形成された半導体基板(1)を設置し、スパッタ装置内に窒素を導入することなく、金属窒化膜をターゲットとしたスパッタを行うことで、抵抗膜(3)の表面に金属窒化膜(5)を形成することで、配線部を構成する第1金属層(5)を形成する工程を含んでいることを特徴としている。

【0007】

このように、スパッタ装置内において事前に金属窒化膜を備えておき、その後、窒素を導入することなく金属窒化膜をターゲットとしたスパッタにより、金属窒化膜によって配線部を構成する第1金属層(5)を形成するようにしている。このため、薄膜抵抗(R)と接触する第1金属層(5)を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層(5)の成膜を行うことができるため、薄膜抵抗(R)の露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗(R)と配線部を構成する第1金属層(5)との接触抵抗が高抵抗化することを抑制することが可能となる。

【0008】

例えば、請求項2に記載したように、スパッタ装置内に半導体基板(1)を設置する前に、スパッタ装置内に金属窒化膜の窒化前の材料をターゲットとして設置する工程と、窒化前の材料をターゲットとして設置する工程の後に、スパッタ装置内に窒素を導入して窒素ラジカルを発生させることでターゲットとなる材料を窒化させ、金属窒化膜を形成する工程とを行うことにより、スパッタ装置内に金属窒化膜を備えることができる。

【0009】

請求項3に記載の発明では、第1金属層(5)の表面に絶縁材料にて構成される容量膜(6)を成膜する工程と、容量膜(6)の表面に、第1金属層(5)と対向配置される第2金属層(7)を形成することで、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)を構成する工程と、を含んでいることを特徴としている。

【0010】

このように、第1金属層(5)の表面に容量膜(6)を構成すると共に、容量膜(6)の表面に第2金属層(7)を形成し、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)を構成することもできる。これにより、薄膜抵抗(R)の配線部とメタルキャパシタンス(C)の電極を共通化させることが可能となる。

【0011】

請求項4ないし7に記載の発明では、半導体素子が形成された半導体基板(1)と、半導体基板(1)の上に配置され、抵抗材料からなる抵抗膜(3)にて構成された薄膜抵抗(R)と、薄膜抵抗(R)に接触する金属窒化物で構成された第1金属層(5)と、第1金属層(5)の表面に形成され、絶縁材料にて構成された容量膜(6)と、容量膜(6)の表面に形成され、第1金属層(5)と対向配置された第2金属層(7)とを有し、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)が構成されていると共に、薄膜抵抗(R)に接触させられた第1金属層(5)によって、メタルキャパシタンス(C)の電極が構成されていることを特徴としている。

【0012】

このように、容量膜(6)を挟んだ第1金属層(5)および第2金属層(7)によってメタルキャパシタンス(C)が構成されていると共に、薄膜抵抗(R)に接触させられた第1金属層(5)によって、メタルキャパシタンス(C)の電極が構成されるようにすれば、薄膜抵抗(R)の配線部とメタルキャパシタンス(C)の電極を共通化させることが可能となる。

【0013】

例えば、請求項5に記載したように、第1金属層(5)を構成する金属窒化物としては、窒化チタン、窒化タングステン、窒化タンタル、窒化クロム、窒化銅のいずれかを適用することができる。また、請求項6に記載したように、容量膜(6)を構成する絶縁材料としては、シリコン酸化膜、シリコン窒化膜、窒化アルミニウム、ペロブスカイト材料のいずれかを適用することができる。

【0014】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

【図面の簡単な説明】

【0015】

【図1】本発明の第1実施形態にかかる薄膜抵抗Rを備えた半導体装置の断面図である。

【図2】図1に示す薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。

【図3】図2に続く薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。

【図4】図3に続く薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、図中、同一符号を付してある。

【0017】

(第1実施形態)

本発明の第1実施形態について説明する。図1に、本実施形態にかかる薄膜抵抗Rを備えた半導体装置の断面図を示す。以下、この図を参照して、本実施形態にかかる薄膜抵抗Rを備えた半導体装置について説明する。

【0018】

図1に示す半導体装置は、半導体素子(図示せず)が形成された半導体基板1の表面に、層間絶縁膜となる第1絶縁膜2を介して薄膜抵抗RおよびメタルキャパシタンスCを備えることにより構成されている。

【0019】

具体的には、半導体基板1の表面には、TEOS等のシリコン酸化膜によって第1絶縁膜2が形成され、この第1絶縁膜2の表面に薄膜抵抗Rを構成する抵抗膜3が形成されている。抵抗膜3は、クロムシリコン(CrSi)などの抵抗材料によって構成されている。

【0020】

抵抗膜3および第1絶縁膜2の表面には、TEOS等のシリコン酸化膜によって構成された層間絶縁膜となる第2絶縁膜4が形成されている。この第2絶縁膜4には、抵抗膜3の一部を露出させるビアホール4aが形成されている。このビアホール4a内の抵抗膜3の表面および第2絶縁膜4の表面に第1金属層5が形成され、第1金属層5が薄膜抵抗Rに対して電気的に接続されている。

【0021】

第1金属層5は、窒化チタン(TiN)膜によって構成されており、所望のレイアウトにパターニングされている。この第1金属層5は、メタルキャパシタンスCにおける第1電極を構成すると共に、メタルキャパシタンスCと薄膜抵抗Rとを接続する配線層としての機能を果たす。

【0022】

また、第1金属層5の表面には、TEOS等のシリコン酸化膜によって構成された容量膜6が形成されている。この容量膜6の表面には、Al等によって構成された第2金属層7が形成されている。第2金属層7は、第1配線(1st−Al)を構成するもので、容量膜6に形成されたビアホール6aを通じて第1金属層5および薄膜抵抗Rと電気的に接続された部分7aや、容量膜6を挟んで第1金属層5と対向配置される部分7bを有している。例えば、第2金属層7のうち薄膜抵抗Rに電気的に接続された部分7aは、図1とは別断面において外部と電気的に接続される薄膜抵抗Rを制御するために用いられるパッドに繋がっている。また、第1金属層5と対向配置される部分7bは、メタルキャパシタンスCにおける第1電極と対になる第2電極を構成する。これらの部分7a、7bは、電気的に分離されている。

【0023】

このような構成により、図1中の破線にて囲んだ部分、つまり、第1金属層5にて構成される第1電極と容量膜6および第2金属層7によって構成される第2電極によって、メタルキャパシタンスCが形成されている。

【0024】

また、第2金属層7や容量膜6の表面を覆うようにTEOS等のシリコン酸化膜によって構成された層間絶縁膜を構成する第3絶縁膜8が形成されている。この第3絶縁膜8にはビアホール8aが形成されており、ビアホール8a内には、第2金属層7におけるメタルキャパシタンスCの第2電極を構成する部分7bと電気的に接続されたタングステン(W)等で構成された金属プラグ9が埋め込まれている。そして、第3絶縁膜8の表面に、Al等によって構成された第3金属層10がパターニングされている。この第3金属層10は、第2配線(2nd−Al)を構成するもので、金属プラグ9に電気的に接続されることで、メタルキャパシタンスCにおける第2電極となる部分7bと電気的に接続されている。そして、第3金属層10および第3絶縁膜8の表面を覆うようにTEOS等のシリコン酸化膜によって構成された保護膜11が形成されることで、図1に示した薄膜抵抗Rを備えた半導体装置が構成されている。

【0025】

続いて、図1に示す薄膜抵抗Rを備えた半導体装置の製造方法について説明する。図2〜図4は、図1に示す薄膜抵抗Rを備えた半導体装置の製造工程を示した断面図である。これらの図を参照して説明する。なお、これらの図では、半導体基板1に関しては省略してあり、半導体装置のうち半導体基板1の表面上に形成される部分についてのみ図示してある。

【0026】

〔図2(a)の工程〕

まず、半導体素子を形成した半導体基板1をCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される第1絶縁膜2をデポジションする。

【0027】

〔図2(b)の工程〕

次に、第1絶縁膜2を形成した半導体基板1をスパッタ装置内に設置した後、クロムシリコン等の抵抗材料をターゲットとしたスパッタを行い、例えば膜厚10〜100nmの抵抗膜3を形成する。そして、ホト工程によって薄膜抵抗Rの形成予定領域以外が開口するマスク(図示せず)を配置した後、ウェットエッチングもしくはドライエッチングを行うことで、抵抗膜3をパターニングする。これにより、薄膜抵抗Rが構成される。

【0028】

〔図2(c)の工程〕

図2(b)の工程まで行った半導体基板1を再びCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される第2絶縁膜4をデポジションする。そして、ホト工程によってビアホール形成予定領域が開口するマスク(図示せず)を配置した後、ウェットエッチングもしくはドライエッチングを行うことで、第2絶縁膜4に対してビアホール4aを形成し、抵抗膜3を部分的に露出させる。

【0029】

〔図2(d)の工程〕

図2(c)の工程まで行った半導体基板1を再びスパッタ装置内に設置するが、それに先立って、スパッタ装置に対して以下の処理を行っておく。具体的には、スパッタ装置のチャンバー内にターゲット用のチタン膜を設置しておき、チタン膜の表面を窒化させるための処理を行う。これにより、ターゲット用のチタン膜の少なくとも表面が窒化チタンとなる。例えば、スパッタ装置のチャンバー内に窒素(N2)とアルゴン(Ar)を1:1の比率とした混合ガスを流量7sccmで導入し、スパッタ装置におけるDCパワーを3kWとして窒素ラジカルを発生させることで、チタン膜の表面を窒化チタンとすることができる。

【0030】

その後、ガス導入を停止すると共に、電圧供給を停止する。これにより、窒素ラジカルが完全に無くなってから、半導体基板1をスパッタ装置に設置する。そして、半導体基板1を加熱して基板温度を230℃とし、アルゴンを流量7sccmで導入しつつ、スパッタ装置におけるDCパワーを3kWとしてアルゴンイオンでチタン膜の表面に形成された窒化チタンをターゲットとしたスパッタを行い、窒化チタンにて構成される第1金属層5を例えば0.05〜0.1μmの厚さで成膜する。このとき、窒化ラジカルが残留していない状態でのスパッタを行うことができるため、クロムシリコン等で構成された薄膜抵抗Rの表面、具体的には抵抗膜3のうちビアホール4aから露出した部分が窒化されることで、窒化クロムシリコン(CrSiN)や窒化シリコン(SiN)が形成されることを抑制できる。

【0031】

なお、薄膜抵抗Rとの接触部におけるオーミック性を向上させるために、窒化チタンにて構成される第1金属層5の組成比、つまりチタンの窒素に対する比率は、窒素1に対してチタン1.5以上とすると好ましい。ただし、第1金属層5がすべてこの比率の組成比である必要はなく、薄膜抵抗Rと接触する界面から5nm程度の厚み分がこの比率の組成比となっていれば良い。このような第1金属層5の組成比については、ターゲット用のチタン膜の表面を窒化チタンとするときの窒素とアルゴンの比率や流量、DCパワーの印加時間などによって調整できる。

【0032】

続いて、ホト工程によって第1金属層5の上に当該第1金属層5の不要部分が開口するマスク(図示せず)を配置した後、塩素系(例えばBCl3等)ドライエッチングによって第1金属層5をパターニングする。このとき、第1金属層5の表面がチタン膜ではなく窒化チタン膜によって構成されているため、マスクとなるレジストとの密着性が良く、良好なパターニングを行うことができる。このようにして、薄膜抵抗Rを構成する抵抗膜3に電気的に接続された第1金属層5が構成される。

【0033】

〔図3(a)の工程〕

第1金属層5および第2絶縁膜4の表面全面を覆うようにTEOS膜などで構成された容量膜6を例えば0.05〜0.3μmの厚さで成膜する。例えば、図2(d)の工程まで行われた半導体基板1をCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によって容量膜6をデポジションする。

【0034】

〔図3(b)の工程〕

容量膜6の表面上に、ホト工程によってビアホール形成予定領域が開口するマスク(図示せず)を配置した後、フッ素系のドライエッチングを行うことで、容量膜6に対してビアホール6aを形成し、第1金属層5を部分的に露出させる。このとき、第1金属層5がチタン膜の単層膜ではなく窒化チタン膜によって構成されているため、ビアホール形成時の選択比を高めることが可能となり、第1金属層5を突き抜けてしまうこともない。

【0035】

〔図3(c)の工程〕

ビアホール6a内を含めて容量膜6の表面上に第2金属層7を成膜する。例えば、アルミニウムを主成分とする配線材料を反射防止膜で覆った構造、具体的には、チタン膜、窒化チタン膜、銅を含有したアルミニウム、窒化チタン膜、チタン膜を順にデポジションすることにより、Ti/TiN/Al−Cu/Ti/TiN構造とされた第2金属層7を形成する。そして、第2金属層7の表面に当該第2金属層7の不要部分が開口するマスク(図示せず)を配置した後、フッ素(F)系ドライエッチングによって第2金属層7をパターニングする。

【0036】

〔図3(d)の工程〕

図3(c)の工程まで行った半導体基板1をCVD装置などの絶縁膜形成用の装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される第3絶縁膜8をデポジションする。

【0037】

〔図4(a)の工程〕

第3絶縁膜8の表面にホト工程によってビアホール形成予定領域が開口するマスク(図示せず)を配置した後、フッ素系ドライエッチングを行うことで、第3絶縁膜8に対してビアホール8aを形成し、第2金属層7を部分的に露出させる。そして、CVD装置などを用いてタングステン等で構成される金属プラグ9の構成材料を成膜することによってビアホール8a内を埋め込み、CMP(Chemical Mechanical Polishing)によって平坦化することで金属プラグ9を形成する。

【0038】

〔図4(b)の工程〕

金属プラグ9および第3絶縁膜8の表面に第3金属層10を形成する。例えば、例えば、アルミニウムを主成分とする配線材料を反射防止膜で覆った構造、具体的には、チタン膜、窒化チタン膜、銅を含有したアルミニウム、窒化チタン膜、チタン膜を順にデポジションすることにより、Ti/TiN/Al−Cu/Ti/TiN構造の第3金属層10を形成する。そして、第3金属層10の表面に当該第3金属層10の不要部分が開口するマスク(図示せず)を配置した後、フッ素(F)系ドライエッチングによって第3金属層10をパターニングする。

【0039】

この後、図4(b)の工程まで行った半導体基板1をCVD装置などの絶縁膜形成用装置内に設置した後、基板表面全面に、CVD法等によってTEOS膜などで構成される保護膜11をデポジションすることで、図1に示した薄膜抵抗Rを備えた半導体装置が完成する。

【0040】

以上説明したように、本実施形態では、スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成するようにしている。このため、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

【0041】

(他の実施形態)

上記実施形態では、第1金属層5を形成する際に、スパッタ装置内においてターゲット用のチタン膜の表面を窒化チタンにしたのち、スパッタ装置内の窒素ラジカルが完全に無くなるまでガス導入、電圧供給を停止し、その後、窒化チタンをターゲットとしたスパッタを行うようにしている。これに対して、初めから窒化チタン膜を他の装置で焼結などによって製造しておき、それをスパッタ装置内にターゲット用に設置し、スパッタを行うことで第1金属層5を形成するという手法を用いても、上記実施形態と同様の効果を得ることができる。

【0042】

上記実施形態では、第1金属層5を構成する金属窒化膜を窒化チタンにて構成する場合について説明したが、他の金属窒化物にて構成されていても良い。金属窒化物としては、窒化タングステン(WN)、窒化タンタル(TaN)、窒化クロム(CrN)、窒化銅(CuN)がある。特に、窒化銅は、比抵抗が低いことから、第1金属層5として窒化銅を用いれば、配線抵抗の低下の効果を得ることもできる。

【0043】

また、メタルキャパシタンスCを構成するための容量膜6として、上記実施形態では、TEOS等のシリコン酸化膜を用いているが、他の絶縁材料を用いても良い。例えば、シリコン窒化膜、窒化アルミニウム(AlN)、ペロブスカイト材料によって容量膜6を構成することもできる。特に、ペロブスカイトは比誘電率が高いため、容量膜6として用いると高い容量値を得ることができ、キャパシタンス効果が大きい。

【0044】

さらに、上記実施形態では、薄膜抵抗Rを構成する抵抗膜3の抵抗材料としてクロムシリコン(CrSi)を例に挙げて説明したが、その他の材料、例えばニッケルクロム(NiCr)などを使用する場合にも、クロムシリコンを用いる場合と同様の問題が生じるため、本発明を適用することができる。

【符号の説明】

【0045】

1 半導体基板

2 第1絶縁膜

3 抵抗膜

4 第2絶縁膜

4a ビアホール

5 第1金属層

6 容量膜

6a ビアホール

7 第2金属層

8 第3絶縁膜

9 金属プラグ

10 第3金属層

11 保護膜

【特許請求の範囲】

【請求項1】

半導体素子が形成された半導体基板(1)の上に配置され、抵抗材料からなる抵抗膜(3)にて構成された薄膜抵抗(R)と、

前記薄膜抵抗(R)に接触する金属材料で構成された第1金属層(5)とを有してなる薄膜抵抗を有する半導体装置の製造方法であって。

スパッタ装置内にターゲットとなる金属窒化膜を備える工程と、

前記スパッタ装置内に前記薄膜抵抗(R)を構成する前記抵抗膜(3)が形成された前記半導体基板(1)を設置し、前記スパッタ装置内に窒素を導入することなく、前記金属窒化膜をターゲットとしたスパッタを行うことで、前記抵抗膜(3)の表面に金属窒化膜(5)を形成することで、前記第1金属層(5)を形成する工程を含んでいることを特徴とする薄膜抵抗を備えた半導体装置の製造方法。

【請求項2】

前記スパッタ装置内に前記金属窒化膜を備える工程は、

前記スパッタ装置内に前記半導体基板(1)を設置する前に、前記スパッタ装置内に前記金属窒化膜の窒化前の材料をターゲットとして設置する工程と、

前記窒化前の材料をターゲットとして設置する工程の後に、前記スパッタ装置内に窒素を導入して窒素ラジカルを発生させることでターゲットとなる材料を窒化させ、前記金属窒化膜を形成する工程とを含んでいることを特徴とする請求項1に記載の薄膜抵抗を備えた半導体装置の製造方法。

【請求項3】

前記前記第1金属層(5)の表面に絶縁材料にて構成される容量膜(6)を成膜する工程と、

前記容量膜(6)の表面に、前記第1金属層(5)と対向配置される第2金属層(7)を形成することで、前記容量膜(6)を挟んだ前記第1金属層(5)および前記第2金属層(7)によってメタルキャパシタンス(C)を構成する工程と、を含んでいることを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

半導体素子が形成された半導体基板(1)と、

前記半導体基板(1)の上に配置され、抵抗材料からなる抵抗膜(3)にて構成された薄膜抵抗(R)と、

前記薄膜抵抗(R)に接触する金属窒化物で構成された第1金属層(5)と、

前記第1金属層(5)の表面に形成され、絶縁材料にて構成された容量膜(6)と、

前記容量膜(6)の表面に形成され、前記第1金属層(5)と対向配置された第2金属層(7)とを有し、

前記前記容量膜(6)を挟んだ前記第1金属層(5)および前記第2金属層(7)によってメタルキャパシタンス(C)が構成されていると共に、前記薄膜抵抗(R)に接触させられた前記第1金属層(5)によって、前記メタルキャパシタンス(C)の電極が構成されていることを特徴とする薄膜抵抗を備えた半導体装置。

【請求項5】

前記第1金属層(5)を構成する前記金属窒化物は、窒化チタン、窒化タングステン、窒化タンタル、窒化クロム、窒化銅のいずれかであることを特徴とする請求項4に記載の薄膜抵抗を備えた半導体装置。

【請求項6】

前記容量膜(6)を構成する前記絶縁材料は、シリコン酸化膜、シリコン窒化膜、窒化アルミニウム、ペロブスカイト材料のいずれかであることを特徴とする請求項4または5に記載の薄膜抵抗を備えた半導体装置。

【請求項7】

前記薄膜抵抗(R)を構成する前記抵抗膜(3)の表面には層間絶縁膜(4)が形成され、該層間絶縁膜(4)に形成されたビアホール(4a)を通じて前記抵抗膜(3)の一部が露出させられており、該露出させられた部分に前記第1金属層(5)が接触させられていることを特徴とする請求項4ないし6のいずれか1つに記載の薄膜抵抗を備えた半導体装置。

【請求項1】

半導体素子が形成された半導体基板(1)の上に配置され、抵抗材料からなる抵抗膜(3)にて構成された薄膜抵抗(R)と、

前記薄膜抵抗(R)に接触する金属材料で構成された第1金属層(5)とを有してなる薄膜抵抗を有する半導体装置の製造方法であって。

スパッタ装置内にターゲットとなる金属窒化膜を備える工程と、

前記スパッタ装置内に前記薄膜抵抗(R)を構成する前記抵抗膜(3)が形成された前記半導体基板(1)を設置し、前記スパッタ装置内に窒素を導入することなく、前記金属窒化膜をターゲットとしたスパッタを行うことで、前記抵抗膜(3)の表面に金属窒化膜(5)を形成することで、前記第1金属層(5)を形成する工程を含んでいることを特徴とする薄膜抵抗を備えた半導体装置の製造方法。

【請求項2】

前記スパッタ装置内に前記金属窒化膜を備える工程は、

前記スパッタ装置内に前記半導体基板(1)を設置する前に、前記スパッタ装置内に前記金属窒化膜の窒化前の材料をターゲットとして設置する工程と、

前記窒化前の材料をターゲットとして設置する工程の後に、前記スパッタ装置内に窒素を導入して窒素ラジカルを発生させることでターゲットとなる材料を窒化させ、前記金属窒化膜を形成する工程とを含んでいることを特徴とする請求項1に記載の薄膜抵抗を備えた半導体装置の製造方法。

【請求項3】

前記前記第1金属層(5)の表面に絶縁材料にて構成される容量膜(6)を成膜する工程と、

前記容量膜(6)の表面に、前記第1金属層(5)と対向配置される第2金属層(7)を形成することで、前記容量膜(6)を挟んだ前記第1金属層(5)および前記第2金属層(7)によってメタルキャパシタンス(C)を構成する工程と、を含んでいることを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

半導体素子が形成された半導体基板(1)と、

前記半導体基板(1)の上に配置され、抵抗材料からなる抵抗膜(3)にて構成された薄膜抵抗(R)と、

前記薄膜抵抗(R)に接触する金属窒化物で構成された第1金属層(5)と、

前記第1金属層(5)の表面に形成され、絶縁材料にて構成された容量膜(6)と、

前記容量膜(6)の表面に形成され、前記第1金属層(5)と対向配置された第2金属層(7)とを有し、

前記前記容量膜(6)を挟んだ前記第1金属層(5)および前記第2金属層(7)によってメタルキャパシタンス(C)が構成されていると共に、前記薄膜抵抗(R)に接触させられた前記第1金属層(5)によって、前記メタルキャパシタンス(C)の電極が構成されていることを特徴とする薄膜抵抗を備えた半導体装置。

【請求項5】

前記第1金属層(5)を構成する前記金属窒化物は、窒化チタン、窒化タングステン、窒化タンタル、窒化クロム、窒化銅のいずれかであることを特徴とする請求項4に記載の薄膜抵抗を備えた半導体装置。

【請求項6】

前記容量膜(6)を構成する前記絶縁材料は、シリコン酸化膜、シリコン窒化膜、窒化アルミニウム、ペロブスカイト材料のいずれかであることを特徴とする請求項4または5に記載の薄膜抵抗を備えた半導体装置。

【請求項7】

前記薄膜抵抗(R)を構成する前記抵抗膜(3)の表面には層間絶縁膜(4)が形成され、該層間絶縁膜(4)に形成されたビアホール(4a)を通じて前記抵抗膜(3)の一部が露出させられており、該露出させられた部分に前記第1金属層(5)が接触させられていることを特徴とする請求項4ないし6のいずれか1つに記載の薄膜抵抗を備えた半導体装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−187527(P2011−187527A)

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願番号】特願2010−48717(P2010−48717)

【出願日】平成22年3月5日(2010.3.5)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願日】平成22年3月5日(2010.3.5)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]