表示パネル、表示装置および電子機器

【課題】隣接する画素間のリーク電流を低減することの可能な表示パネル、表示装置および電子機器を提供する。

【解決手段】表示パネルは、表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを備えている。有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有している。複数の層のうち少なくとも正孔注入層は、表示領域内の複数の画素において共通に形成されるとともに、導電性配線層に電気的に接続されている。

【解決手段】表示パネルは、表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを備えている。有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有している。複数の層のうち少なくとも正孔注入層は、表示領域内の複数の画素において共通に形成されるとともに、導電性配線層に電気的に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、有機EL(Electro Luminescence)素子を画素ごとに備えた表示パネルおよびそれを備えた表示装置に関する。また、本技術は、上記の表示装置を備えた電子機器に関する。

【背景技術】

【0002】

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL素子を用いた表示装置が開発され、商品化が進められている。有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置(有機EL表示装置)では、光源(バックライト)が必要ないので、光源を必要とする液晶表示装置と比べて、薄型化、高輝度化することができる。特に、駆動方式としてアクティブマトリクス方式を用いた場合には、各画素をホールド点灯させることができ、低消費電力化することもできる。そのため、有機EL表示装置は、次世代のフラットパネルディスプレイの主流になると期待されている。

【0003】

アクティブマトリックス型の表示装置においては、画素ごとに配した有機EL素子に流れる電流が、有機EL素子ごとに設けた画素回路内に設けた薄膜トランジスタ(TFT; Thin Film Transistor)によって制御される(特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−33193号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

有機EL素子は、アノード電極とカソード電極との間に有機化合物からなる薄膜が設けられている電子素子である。有機EL素子では、アノード電極とカソード電極それぞれからホールと電子が注入され、これらホールと電子との再結合によって発生するエネルギーが光として取り出される。そのため、正孔の注入特性を向上させることで、駆動電圧の低減や、発光効率の向上等がもたらされる。

【0006】

有機EL素子が低分子蒸着型である場合に、有機EL素子をアレイ状に並べるときには、発光層は、蒸着マスクを用いて画素毎に選択的に蒸着することにより形成される。しかし、有機層のうち発光層以外の層は、生産性の向上や、生産コストの削減を考えると、各画素で共通に形成されることが望ましい。とはいえ、正孔注入層(HIL)を各画素で共通化すると、正孔注入層の抵抗率の低さにより、隣接する画素間でリーク電流が生じ、所望の画素以外の画素までもが発光する。その結果、混色が発生し、画質が低下してしまうという問題があった。

【0007】

本技術はかかる問題点に鑑みてなされたものであり、その目的は、隣接する画素間のリーク電流を低減することの可能な表示パネル、表示装置および電子機器を提供することにある。

【課題を解決するための手段】

【0008】

本技術による表示パネルは、表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを備えている。有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有している。複数の層のうち少なくとも正孔注入層は、表示領域内の複数の画素において共通に形成されるとともに、導電性配線層に電気的に接続されている。

【0009】

本技術による表示装置は、上記の表示パネルと、各画素を駆動する駆動回路とを備えている。本技術による電子機器は、上記の表示装置を備えている。

【0010】

本技術による表示パネル、表示装置および電子機器では、上記複数の層のうち少なくとも正孔注入層は、画素間に配置された導電性配線層に電気的に接続されている。これにより、リーク電流が隣接画素に到達する前に、導電性配線層で引き抜かれる。

【発明の効果】

【0011】

本技術による表示パネル、表示装置および電子機器によれば、リーク電流が隣接画素に到達する前に、導電性配線層で引き抜かれるようにしたので、隣接する画素間でリーク電流が生じるのを抑制することができる。その結果、混色や画質低下を抑制することが可能となる。

【図面の簡単な説明】

【0012】

【図1】本技術による一実施の形態に係る表示装置の構成の一例を表す図である。

【図2】画素の構成の一例を表す図である。

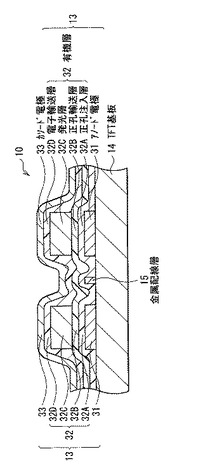

【図3】有機EL素子の断面構成の一例を表す図である。

【図4】図1の表示パネルにおける画素間のリーク電流について説明するための図である。

【図5】比較例に係る表示パネルにおける画素間のリーク電流について説明するための図である。

【図6】上記実施の形態の表示装置を含むモジュールの概略構成を表す平面図である。

【図7】上記実施の形態の発光装置の適用例1の外観を表す斜視図である。

【図8】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図9】適用例3の外観を表す斜視図である。

【図10】適用例4の外観を表す斜視図である。

【図11】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0013】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.実施の形態(表示装置)

画素間に金属配線層が設けられている例

2.適用例(電子機器)

上記実施の形態の表示装置が電子機器に適用される例

【0014】

<1.実施の形態>

[構成]

図1は、本技術による一実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、表示パネル10と、表示パネル10を駆動する駆動回路20とを備えている。駆動回路20は、例えば、タイミング生成回路21、映像信号処理回路22、信号線駆動回路23、走査線駆動回路24、および電源線駆動回路25を有している。

【0015】

(表示パネル10)

表示パネル10は、複数の画素11が表示パネル10の表示領域10A全面に渡って2次元配置されたものである。画素11は、表示パネル110上の画面を構成する最小単位の点に対応するものである。表示パネル10がカラー表示パネルである場合には、画素11は、例えば赤、緑または青などの単色の光を発する副画素に相当し、表示パネル10がモノクロ表示パネルである場合には、画素11は、白色光を発する画素に相当する。

【0016】

表示パネル10は、駆動回路20によって各画素11がアクティブマトリクス駆動されることにより、外部から入力された映像信号20Aに基づく画像を表示するものである。図2は、画素11の回路構成の一例を表したものである。画素11は、例えば、図2に示したように、画素回路12と、有機EL素子13とを有している。

【0017】

画素回路12は、例えば、図2に示したように、駆動トランジスタTr1、書き込みトランジスタTr2および保持容量Csによって構成されたものであり、2Tr1Cの回路構成となっている。書き込みトランジスタTr2は、後述の信号線DTLの電圧をサンプリングするとともに駆動トランジスタTr1のゲートに書き込むものである。駆動トランジスタTr1は、書き込みトランジスタTr2によって書き込まれた電圧の大きさに応じて有機EL素子13に流れる電流を制御するものである。保持容量Csは、駆動トランジスタTr1のゲート−ソース間に所定の電圧を保持するものである。なお、画素回路12は、上述の2Tr1Cの回路構成とは異なる回路構成となっていてもよい。

【0018】

駆動トランジスタTr1および書き込みトランジスタTr2は、例えば、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている。なお、TFTの種類は特に限定されるものではなく、例えば、逆スタガー構造(ボトムゲート型)であってもよいし、スタガー構造(トップゲート型)であってもよい。また、駆動トランジスタTr1または書き込みトランジスタTr2は、pチャネルMOS型のTFTであってもよい。

【0019】

表示パネル10は、図2に示したように、行方向に延在する複数の書込線WSLと、列方向に延在する複数の信号線DTLと、行方向に延在する複数の電源線DSLとを有している。各信号線DTLと各書込線WSLとの交差点近傍には、画素11が設けられている。各信号線DTLは、後述の信号線駆動回路23の出力端(図示せず)と、書き込みトランジスタTr2のソースまたはドレインとに接続されている。各書込線WSLは、後述の書込線駆動回路24の出力端(図示せず)と、書き込みトランジスタTr2のゲートに接続されている。各電源線DSLは、固定の電圧を出力する電源の出力端(図示せず)と、駆動トランジスタTr1のソースまたはドレインに接続されている。

【0020】

書き込みトランジスタTr2のゲートは、書込線WSLに接続されている。書き込みトランジスタTr2のソースまたはドレインが信号線DTLに接続され、書き込みトランジスタTr2のソースおよびドレインのうち信号線DTLに未接続の端子が駆動トランジスタTr1のゲートに接続されている。駆動トランジスタTr1のソースまたはドレインが電源線DSLに接続され、駆動トランジスタTr1のソースおよびドレインのうち電源線DSLに未接続の端子が有機EL素子13のアノードに接続されている。保持容量Csの一端が駆動トランジスタTr1のゲートに接続され、保持容量Csの他端が駆動トランジスタTr1のソース(図2では有機EL素子13側の端子)に接続されている。つまり、保持容量Csは、駆動トランジスタTr1のゲート−ソース間に挿入されている。有機EL素子13のカソードは、グラウンド線GNDに接続されている。グラウンド線GNDは、基準電位(例えばグラウンド電位)となっている外部回路(図示せず)と電気的に接続されるものである。

【0021】

(表示パネル10内の構造)

次に、図3を参照しつつ、表示パネル10内の構造について説明する。図3は、表示パネル10内の有機EL素子13およびその近傍の断面構成の一例を表したものである。表示パネル10は、例えば、図3に示したように、TFT基板14上に、各画素11に対応して設けられた複数の有機EL素子13と、画素11間(具体的には互いに隣接する有機EL素子13間)に設けられた金属配線層15とを有している。

【0022】

TFT基板14は、画素回路12などの形成された基板であって、かつ、少なくとも最上面に、画素回路12と電気的に接続された金属層(図示せず)を有している。有機EL素子13は、その金属層に接して形成されている。金属配線層15は、表示領域10A内において行方向または列方向に延在する帯状の配線層であり、表示領域10A外の金属部材16(図1参照)に電気的に接している。金属部材16は、有機EL素子13の閾値電圧よりも小さな電圧が印加される部材である。ここで、金属部材16に印加される電圧は、グラウンド電圧、または有機EL素子13のカソードの電圧と同一の電圧となっている。金属配線層15は、例えば、後述のアノード電極31と同一の層に形成されており、後述の正孔注入層32Aの下側の面に接している。また、金属配線層15は、例えば、アノード電極31の形成工程と同一の工程で、アノード電極31と一括で形成されている。金属配線層15は、アノード電極31の端部から十分に離れていることが好ましく、例えば、互いに隣接するアノード電極31同士の間の中間の位置に配置されていることが好ましい。なお、金属配線層15は、アノード電極31とは異なる層であって、かつ正孔注入層32Aに接することの可能な層に形成されていてもよい。また、金属配線層15は、正孔注入層32A、後述の正孔輸送層32Bおよび後述の電子輸送層32Cのうち少なくとも正孔注入層32Aと電気的に接続することの可能な構成となっていてもよい。

【0023】

有機EL素子13は、例えば、図3に示したように、TFT基板14側に設けられたアノード電極31と、アノード電極31上に設けられた有機層32と、有機層32上に設けられたカソード電極33とを有している。アノード電極31は、有機層32へ正孔を注入するものである。アノード電極31は、例えば、正孔注入性の良い材料で構成されており、例えばAl系金属で構成されている。Al系金属は、AlやAl合金を含む概念である。有機層32は、有機層32内に流れる電流量に応じた明るさで発光するものである。有機層32は、例えば、アノード電極31側から順に、正孔注入効率を高める正孔注入層32Aと、後述の発光層32Cへの正孔輸送効率を高める正孔輸送層32Bと、電子と正孔との再結合により発光する発光層32Cと、発光層32Cへの電子輸送効率を高める電子輸送層32Dとを積層してなる積層構造を有している。カソード電極33は、有機層32へ電子を注入するためのものである。カソード電極33は、電子注入性の良い材料で構成されており、例えば、MgAgなどの半透過型の金属材料で構成されている。

【0024】

有機層32のうち、発光層32C以外の全ての層は、表示領域10A内の全ての画素11を含む領域全体に渡って形成されている。一方、発光層32Cは、有機EL素子13ごとに選択的に形成されており、例えば、アノード電極31と対向する領域ごとに選択的に形成されている。ここで、正孔輸送層32Bおよび電子輸送層32Dは、全ての画素11で共通化されている。ただし、正孔輸送層32Bおよび電子輸送層32Dでは、抵抗率が正孔注入層32Aの抵抗率よりも大きく、しかも厚さが薄いため、積層面内方向の抵抗が大きくなっている。そのため、正孔輸送層32Bおよび電子輸送層32Dは、全ての画素11で共通化されているといっても、電気的には実質的に画素11ごとに分離されている。

【0025】

一方、正孔注入層32Aでは、正孔輸送層32Bおよび電子輸送層32Dと比べると、抵抗率が若干、小さい。しかし、正孔注入層32Aは、画素11間に設けられた金属配線層15に接している。ここで、金属配線層15は、有機EL素子13の閾値電圧よりも小さな電圧が印加される金属部材16に接してしている。そのため、金属配線層15は、正孔注入層32A内で、隣接する他の画素11に向かって流れてきた電流を正孔注入層32Aから引き抜くことが可能である。

【0026】

図4、図5は、画素間に流れるリーク電流を電流密度の分布で表したものであり、具体的には図中の左側の画素を発光させたときの、その画素の周囲の電流密度の分布を表したものである。図4は、正孔注入層32Aが画素11間で金属配線層15に接しているときの電流密度分布の一例を表したものである。図5は、金属配線層15が設けられていないときの電流密度分布の一例を表したものである。図4、図5において、縦軸の電流密度は、図中の左側の画素を発光させた時に、その画素に流れる電流の密度で規格化されている。

【0027】

図4では、金属配線層15の位置で、電流密度が不連続に変化しており、しかも急激に減少している。そのため、発光画素に隣接する画素(図4の右側の画素)には、発光画素からのリーク電流が到達していない。一方、図5では、電流密度が発光画素から遠ざかるにつれて、なだらかに減少している。そのため、発光画素からのリーク電流が、発光画素に隣接する画素(図4の右側の画素)にまで到達している。以上のことから、正孔注入層32Aの高抵抗構造が、発光画素からのリーク電流を効果的に遮断していることがわかる。

【0028】

(駆動回路20)

次に、駆動回路20について簡単に説明する。駆動回路20は、上述したように、例えば、図1に示したように、タイミング生成回路21、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24および電源線駆動回路25を有している。タイミング生成回路21は、駆動回路20内の各回路が連動して動作するように制御するものである。タイミング生成回路21は、例えば、外部から入力された同期信号20Bに応じて(同期して)、上述した各回路に対して制御信号21Aを出力するようになっている。

【0029】

映像信号処理回路22は、外部から入力されたデジタルの映像信号20Aを補正すると共に、補正した後の映像信号をアナログに変換して信号線駆動回路23に出力するものである。信号線駆動回路23は、映像信号処理回路22から入力されたアナログの映像信号を、制御信号21Aの入力に応じて(同期して)各信号線DTLに出力するものである。書込線駆動回路24は、制御信号21Aの入力に応じて(同期して)、複数の書込線WSLを所定の単位ごとに順次選択するものである。電源線駆動回路25は、例えば、制御信号21Aの入力に応じて(同期して)、複数の電源線DSLを所定の単位ごとに順次選択するものである。なお、コンタクト構造14を介して接続端子15から出力される電流量は、電源線駆動回路25による電源線DSLの選択の態様に応じて変化する。

【0030】

[効果]

次に、本実施の形態の表示装置1の効果について説明する。

【0031】

有機EL素子が低分子蒸着型である場合に、有機EL素子をアレイ状に並べるときには、発光層は、通常、蒸着マスクを用いて画素毎に選択的に蒸着することにより形成される。しかし、有機層のうち発光層以外の層は、生産性の向上や、生産コストの削減を考えると、各画素で共通に形成されることが望ましい。とはいえ、正孔注入層を各画素で共通化すると、正孔注入層の抵抗率の低さにより、隣接する画素間でリーク電流が生じる。例えば、図4に示したように、発光画素からのリーク電流が、発光画素に隣接する画素(図4の右側の画素)に到達する。そのため、所望の画素以外の画素までもが発光するので、混色が発生し、画質が低下してしまう。

【0032】

一方、本実施の形態では、正孔注入層32A、正孔輸送層32Bおよび電子輸送層32Cのうち少なくとも正孔注入層32Aが、画素11間に配置された金属配線層15に電気的に接続されている。これにより、リーク電流が隣接画素に到達する前に、金属配線層15で引き抜かれる。その結果、例えば、図5に示したように、金属配線層15の位置で、電流密度が急激に減少するので、隣接する画素11間でリーク電流が生じるのを抑制することができる。その結果、混色や画質低下を抑制することが可能となる。

【0033】

<2.適用例>

以下、上記各実施の形態およびそれらの変形例で説明した表示装置1の適用例について説明する。上述の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、映像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0034】

(モジュール)

上述の表示装置1は、例えば、図6に示したようなモジュールとして、後述する適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板34の一辺に、封止用基板35から露出した領域210を設け、この露出した領域210に、駆動回路20の配線を延長して外部接続端子(図示せず)を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

【0035】

(適用例1)

図7は、上述の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上述の表示装置1により構成されている。

【0036】

(適用例2)

図8は、上述の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上述の表示装置1により構成されている。

【0037】

(適用例3)

図9は、上述の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および映像を表示する表示部530を有しており、その表示部530は、上述の表示装置1により構成されている。

【0038】

(適用例4)

図10は、上述の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上述の表示装置1により構成されている。

【0039】

(適用例5)

図11は、上述の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上述の表示装置1により構成されている。

【0040】

以上、実施の形態、変形例および適用例を挙げて本技術を説明したが、本技術は上記実施の形態等に限定されるものではなく、種々変形が可能である。

【0041】

例えば、上記実施の形態等では、上述の表示装置1がアクティブマトリクス型である場合について説明したが、アクティブマトリクス駆動のための画素回路12の構成は上記実施の形態等で説明したものに限られず、必要に応じて容量素子やトランジスタを画素回路12に追加してもよい。その場合、画素回路12の変更に応じて、上述した信号線駆動回路23、書込線駆動回路24、電源線駆動回路25のほかに、必要な駆動回路を追加してもよい。

【0042】

また、例えば、上記実施の形態等では、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24、電源線駆動回路25の駆動をタイミング生成回路21が制御していたが、他の回路がこれらの駆動を制御するようにしてもよい。また、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24、電源線駆動回路25の制御は、ハードウェア(回路)で行われていてもよいし、ソフトウェア(プログラム)で行われていてもよい。

【0043】

また、例えば、本技術は以下のような構成を取ることができる。

(1)

表示領域に配置されると共に有機EL素子を含む複数の画素と、

画素間に配置された複数の導電性配線層と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示パネル。

(2)

前記導電性配線層は、前記正孔注入層が共通に形成されている複数の画素の間に配置されている

(1)に記載の表示パネル。

(3)

前記導電性配線層は、前記表示領域外の金属部材に接しており、

前記金属部材は、前記有機EL素子の閾値電圧よりも小さな第1電圧が印加される部材である

(1)または(2)に記載の表示パネル。

(4)

前記第1電圧は、グラウンド電圧、または前記有機EL素子のカソードの電圧と同一の電圧である

(3)に記載の表示パネル。

(5)

前記正孔注入層は、前記表示領域内の全ての画素において共通に形成されている

(1)ないし(4)のいずれか1つに記載の表示パネル。

(6)

前記複数の層は、正孔輸送層と、電子輸送層をさらに含んでいる

(1)ないし(5)のいずれか1つに記載の表示パネル。

(7)

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示装置。

(8)

表示装置を備え、

前記表示装置は、

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を有し、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

電子機器。

【符号の説明】

【0044】

1…表示装置、10…表示パネル、10A…表示領域、11…画素、12…画素回路、13…有機EL素子、14…TFT基板、15…金属配線層、16…金属部材、20…駆動回路、20A…映像信号、20B…同期信号、21…タイミング生成回路、21A…制御信号、22…映像信号処理回路、23…信号線駆動回路、24…書込線駆動回路、25…電源線駆動回路、31…アノード電極、32…有機層、32A…正孔注入層、32B…正孔輸送層、32C…発光層、32D…電子輸送層、33…カソード電極、34…基板、35…封止用基板、210…領域、220…FPC、300…映像表示画面部、310…フロントパネル、320…フィルターガラス、410…発光部、420,530,640…表示部、430…メニュースイッチ、440…シャッターボタン、510…本体、520…キーボード、610…本体部、620…レンズ、630…スタート/ストップスイッチ、710…上側筐体、720…下側筐体、730…連結部、740…ディスプレイ、750…サブディスプレイ、760…ピクチャーライト、770…カメラ、Cs…保持容量、DTL…信号線、GND…グラウンド線、DSL…電源線、Tr1…駆動トランジスタ、Tr2…書き込みトランジスタ、WSL…書込線。

【技術分野】

【0001】

本技術は、有機EL(Electro Luminescence)素子を画素ごとに備えた表示パネルおよびそれを備えた表示装置に関する。また、本技術は、上記の表示装置を備えた電子機器に関する。

【背景技術】

【0002】

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL素子を用いた表示装置が開発され、商品化が進められている。有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置(有機EL表示装置)では、光源(バックライト)が必要ないので、光源を必要とする液晶表示装置と比べて、薄型化、高輝度化することができる。特に、駆動方式としてアクティブマトリクス方式を用いた場合には、各画素をホールド点灯させることができ、低消費電力化することもできる。そのため、有機EL表示装置は、次世代のフラットパネルディスプレイの主流になると期待されている。

【0003】

アクティブマトリックス型の表示装置においては、画素ごとに配した有機EL素子に流れる電流が、有機EL素子ごとに設けた画素回路内に設けた薄膜トランジスタ(TFT; Thin Film Transistor)によって制御される(特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−33193号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

有機EL素子は、アノード電極とカソード電極との間に有機化合物からなる薄膜が設けられている電子素子である。有機EL素子では、アノード電極とカソード電極それぞれからホールと電子が注入され、これらホールと電子との再結合によって発生するエネルギーが光として取り出される。そのため、正孔の注入特性を向上させることで、駆動電圧の低減や、発光効率の向上等がもたらされる。

【0006】

有機EL素子が低分子蒸着型である場合に、有機EL素子をアレイ状に並べるときには、発光層は、蒸着マスクを用いて画素毎に選択的に蒸着することにより形成される。しかし、有機層のうち発光層以外の層は、生産性の向上や、生産コストの削減を考えると、各画素で共通に形成されることが望ましい。とはいえ、正孔注入層(HIL)を各画素で共通化すると、正孔注入層の抵抗率の低さにより、隣接する画素間でリーク電流が生じ、所望の画素以外の画素までもが発光する。その結果、混色が発生し、画質が低下してしまうという問題があった。

【0007】

本技術はかかる問題点に鑑みてなされたものであり、その目的は、隣接する画素間のリーク電流を低減することの可能な表示パネル、表示装置および電子機器を提供することにある。

【課題を解決するための手段】

【0008】

本技術による表示パネルは、表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを備えている。有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有している。複数の層のうち少なくとも正孔注入層は、表示領域内の複数の画素において共通に形成されるとともに、導電性配線層に電気的に接続されている。

【0009】

本技術による表示装置は、上記の表示パネルと、各画素を駆動する駆動回路とを備えている。本技術による電子機器は、上記の表示装置を備えている。

【0010】

本技術による表示パネル、表示装置および電子機器では、上記複数の層のうち少なくとも正孔注入層は、画素間に配置された導電性配線層に電気的に接続されている。これにより、リーク電流が隣接画素に到達する前に、導電性配線層で引き抜かれる。

【発明の効果】

【0011】

本技術による表示パネル、表示装置および電子機器によれば、リーク電流が隣接画素に到達する前に、導電性配線層で引き抜かれるようにしたので、隣接する画素間でリーク電流が生じるのを抑制することができる。その結果、混色や画質低下を抑制することが可能となる。

【図面の簡単な説明】

【0012】

【図1】本技術による一実施の形態に係る表示装置の構成の一例を表す図である。

【図2】画素の構成の一例を表す図である。

【図3】有機EL素子の断面構成の一例を表す図である。

【図4】図1の表示パネルにおける画素間のリーク電流について説明するための図である。

【図5】比較例に係る表示パネルにおける画素間のリーク電流について説明するための図である。

【図6】上記実施の形態の表示装置を含むモジュールの概略構成を表す平面図である。

【図7】上記実施の形態の発光装置の適用例1の外観を表す斜視図である。

【図8】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図9】適用例3の外観を表す斜視図である。

【図10】適用例4の外観を表す斜視図である。

【図11】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0013】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.実施の形態(表示装置)

画素間に金属配線層が設けられている例

2.適用例(電子機器)

上記実施の形態の表示装置が電子機器に適用される例

【0014】

<1.実施の形態>

[構成]

図1は、本技術による一実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、表示パネル10と、表示パネル10を駆動する駆動回路20とを備えている。駆動回路20は、例えば、タイミング生成回路21、映像信号処理回路22、信号線駆動回路23、走査線駆動回路24、および電源線駆動回路25を有している。

【0015】

(表示パネル10)

表示パネル10は、複数の画素11が表示パネル10の表示領域10A全面に渡って2次元配置されたものである。画素11は、表示パネル110上の画面を構成する最小単位の点に対応するものである。表示パネル10がカラー表示パネルである場合には、画素11は、例えば赤、緑または青などの単色の光を発する副画素に相当し、表示パネル10がモノクロ表示パネルである場合には、画素11は、白色光を発する画素に相当する。

【0016】

表示パネル10は、駆動回路20によって各画素11がアクティブマトリクス駆動されることにより、外部から入力された映像信号20Aに基づく画像を表示するものである。図2は、画素11の回路構成の一例を表したものである。画素11は、例えば、図2に示したように、画素回路12と、有機EL素子13とを有している。

【0017】

画素回路12は、例えば、図2に示したように、駆動トランジスタTr1、書き込みトランジスタTr2および保持容量Csによって構成されたものであり、2Tr1Cの回路構成となっている。書き込みトランジスタTr2は、後述の信号線DTLの電圧をサンプリングするとともに駆動トランジスタTr1のゲートに書き込むものである。駆動トランジスタTr1は、書き込みトランジスタTr2によって書き込まれた電圧の大きさに応じて有機EL素子13に流れる電流を制御するものである。保持容量Csは、駆動トランジスタTr1のゲート−ソース間に所定の電圧を保持するものである。なお、画素回路12は、上述の2Tr1Cの回路構成とは異なる回路構成となっていてもよい。

【0018】

駆動トランジスタTr1および書き込みトランジスタTr2は、例えば、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている。なお、TFTの種類は特に限定されるものではなく、例えば、逆スタガー構造(ボトムゲート型)であってもよいし、スタガー構造(トップゲート型)であってもよい。また、駆動トランジスタTr1または書き込みトランジスタTr2は、pチャネルMOS型のTFTであってもよい。

【0019】

表示パネル10は、図2に示したように、行方向に延在する複数の書込線WSLと、列方向に延在する複数の信号線DTLと、行方向に延在する複数の電源線DSLとを有している。各信号線DTLと各書込線WSLとの交差点近傍には、画素11が設けられている。各信号線DTLは、後述の信号線駆動回路23の出力端(図示せず)と、書き込みトランジスタTr2のソースまたはドレインとに接続されている。各書込線WSLは、後述の書込線駆動回路24の出力端(図示せず)と、書き込みトランジスタTr2のゲートに接続されている。各電源線DSLは、固定の電圧を出力する電源の出力端(図示せず)と、駆動トランジスタTr1のソースまたはドレインに接続されている。

【0020】

書き込みトランジスタTr2のゲートは、書込線WSLに接続されている。書き込みトランジスタTr2のソースまたはドレインが信号線DTLに接続され、書き込みトランジスタTr2のソースおよびドレインのうち信号線DTLに未接続の端子が駆動トランジスタTr1のゲートに接続されている。駆動トランジスタTr1のソースまたはドレインが電源線DSLに接続され、駆動トランジスタTr1のソースおよびドレインのうち電源線DSLに未接続の端子が有機EL素子13のアノードに接続されている。保持容量Csの一端が駆動トランジスタTr1のゲートに接続され、保持容量Csの他端が駆動トランジスタTr1のソース(図2では有機EL素子13側の端子)に接続されている。つまり、保持容量Csは、駆動トランジスタTr1のゲート−ソース間に挿入されている。有機EL素子13のカソードは、グラウンド線GNDに接続されている。グラウンド線GNDは、基準電位(例えばグラウンド電位)となっている外部回路(図示せず)と電気的に接続されるものである。

【0021】

(表示パネル10内の構造)

次に、図3を参照しつつ、表示パネル10内の構造について説明する。図3は、表示パネル10内の有機EL素子13およびその近傍の断面構成の一例を表したものである。表示パネル10は、例えば、図3に示したように、TFT基板14上に、各画素11に対応して設けられた複数の有機EL素子13と、画素11間(具体的には互いに隣接する有機EL素子13間)に設けられた金属配線層15とを有している。

【0022】

TFT基板14は、画素回路12などの形成された基板であって、かつ、少なくとも最上面に、画素回路12と電気的に接続された金属層(図示せず)を有している。有機EL素子13は、その金属層に接して形成されている。金属配線層15は、表示領域10A内において行方向または列方向に延在する帯状の配線層であり、表示領域10A外の金属部材16(図1参照)に電気的に接している。金属部材16は、有機EL素子13の閾値電圧よりも小さな電圧が印加される部材である。ここで、金属部材16に印加される電圧は、グラウンド電圧、または有機EL素子13のカソードの電圧と同一の電圧となっている。金属配線層15は、例えば、後述のアノード電極31と同一の層に形成されており、後述の正孔注入層32Aの下側の面に接している。また、金属配線層15は、例えば、アノード電極31の形成工程と同一の工程で、アノード電極31と一括で形成されている。金属配線層15は、アノード電極31の端部から十分に離れていることが好ましく、例えば、互いに隣接するアノード電極31同士の間の中間の位置に配置されていることが好ましい。なお、金属配線層15は、アノード電極31とは異なる層であって、かつ正孔注入層32Aに接することの可能な層に形成されていてもよい。また、金属配線層15は、正孔注入層32A、後述の正孔輸送層32Bおよび後述の電子輸送層32Cのうち少なくとも正孔注入層32Aと電気的に接続することの可能な構成となっていてもよい。

【0023】

有機EL素子13は、例えば、図3に示したように、TFT基板14側に設けられたアノード電極31と、アノード電極31上に設けられた有機層32と、有機層32上に設けられたカソード電極33とを有している。アノード電極31は、有機層32へ正孔を注入するものである。アノード電極31は、例えば、正孔注入性の良い材料で構成されており、例えばAl系金属で構成されている。Al系金属は、AlやAl合金を含む概念である。有機層32は、有機層32内に流れる電流量に応じた明るさで発光するものである。有機層32は、例えば、アノード電極31側から順に、正孔注入効率を高める正孔注入層32Aと、後述の発光層32Cへの正孔輸送効率を高める正孔輸送層32Bと、電子と正孔との再結合により発光する発光層32Cと、発光層32Cへの電子輸送効率を高める電子輸送層32Dとを積層してなる積層構造を有している。カソード電極33は、有機層32へ電子を注入するためのものである。カソード電極33は、電子注入性の良い材料で構成されており、例えば、MgAgなどの半透過型の金属材料で構成されている。

【0024】

有機層32のうち、発光層32C以外の全ての層は、表示領域10A内の全ての画素11を含む領域全体に渡って形成されている。一方、発光層32Cは、有機EL素子13ごとに選択的に形成されており、例えば、アノード電極31と対向する領域ごとに選択的に形成されている。ここで、正孔輸送層32Bおよび電子輸送層32Dは、全ての画素11で共通化されている。ただし、正孔輸送層32Bおよび電子輸送層32Dでは、抵抗率が正孔注入層32Aの抵抗率よりも大きく、しかも厚さが薄いため、積層面内方向の抵抗が大きくなっている。そのため、正孔輸送層32Bおよび電子輸送層32Dは、全ての画素11で共通化されているといっても、電気的には実質的に画素11ごとに分離されている。

【0025】

一方、正孔注入層32Aでは、正孔輸送層32Bおよび電子輸送層32Dと比べると、抵抗率が若干、小さい。しかし、正孔注入層32Aは、画素11間に設けられた金属配線層15に接している。ここで、金属配線層15は、有機EL素子13の閾値電圧よりも小さな電圧が印加される金属部材16に接してしている。そのため、金属配線層15は、正孔注入層32A内で、隣接する他の画素11に向かって流れてきた電流を正孔注入層32Aから引き抜くことが可能である。

【0026】

図4、図5は、画素間に流れるリーク電流を電流密度の分布で表したものであり、具体的には図中の左側の画素を発光させたときの、その画素の周囲の電流密度の分布を表したものである。図4は、正孔注入層32Aが画素11間で金属配線層15に接しているときの電流密度分布の一例を表したものである。図5は、金属配線層15が設けられていないときの電流密度分布の一例を表したものである。図4、図5において、縦軸の電流密度は、図中の左側の画素を発光させた時に、その画素に流れる電流の密度で規格化されている。

【0027】

図4では、金属配線層15の位置で、電流密度が不連続に変化しており、しかも急激に減少している。そのため、発光画素に隣接する画素(図4の右側の画素)には、発光画素からのリーク電流が到達していない。一方、図5では、電流密度が発光画素から遠ざかるにつれて、なだらかに減少している。そのため、発光画素からのリーク電流が、発光画素に隣接する画素(図4の右側の画素)にまで到達している。以上のことから、正孔注入層32Aの高抵抗構造が、発光画素からのリーク電流を効果的に遮断していることがわかる。

【0028】

(駆動回路20)

次に、駆動回路20について簡単に説明する。駆動回路20は、上述したように、例えば、図1に示したように、タイミング生成回路21、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24および電源線駆動回路25を有している。タイミング生成回路21は、駆動回路20内の各回路が連動して動作するように制御するものである。タイミング生成回路21は、例えば、外部から入力された同期信号20Bに応じて(同期して)、上述した各回路に対して制御信号21Aを出力するようになっている。

【0029】

映像信号処理回路22は、外部から入力されたデジタルの映像信号20Aを補正すると共に、補正した後の映像信号をアナログに変換して信号線駆動回路23に出力するものである。信号線駆動回路23は、映像信号処理回路22から入力されたアナログの映像信号を、制御信号21Aの入力に応じて(同期して)各信号線DTLに出力するものである。書込線駆動回路24は、制御信号21Aの入力に応じて(同期して)、複数の書込線WSLを所定の単位ごとに順次選択するものである。電源線駆動回路25は、例えば、制御信号21Aの入力に応じて(同期して)、複数の電源線DSLを所定の単位ごとに順次選択するものである。なお、コンタクト構造14を介して接続端子15から出力される電流量は、電源線駆動回路25による電源線DSLの選択の態様に応じて変化する。

【0030】

[効果]

次に、本実施の形態の表示装置1の効果について説明する。

【0031】

有機EL素子が低分子蒸着型である場合に、有機EL素子をアレイ状に並べるときには、発光層は、通常、蒸着マスクを用いて画素毎に選択的に蒸着することにより形成される。しかし、有機層のうち発光層以外の層は、生産性の向上や、生産コストの削減を考えると、各画素で共通に形成されることが望ましい。とはいえ、正孔注入層を各画素で共通化すると、正孔注入層の抵抗率の低さにより、隣接する画素間でリーク電流が生じる。例えば、図4に示したように、発光画素からのリーク電流が、発光画素に隣接する画素(図4の右側の画素)に到達する。そのため、所望の画素以外の画素までもが発光するので、混色が発生し、画質が低下してしまう。

【0032】

一方、本実施の形態では、正孔注入層32A、正孔輸送層32Bおよび電子輸送層32Cのうち少なくとも正孔注入層32Aが、画素11間に配置された金属配線層15に電気的に接続されている。これにより、リーク電流が隣接画素に到達する前に、金属配線層15で引き抜かれる。その結果、例えば、図5に示したように、金属配線層15の位置で、電流密度が急激に減少するので、隣接する画素11間でリーク電流が生じるのを抑制することができる。その結果、混色や画質低下を抑制することが可能となる。

【0033】

<2.適用例>

以下、上記各実施の形態およびそれらの変形例で説明した表示装置1の適用例について説明する。上述の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、映像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0034】

(モジュール)

上述の表示装置1は、例えば、図6に示したようなモジュールとして、後述する適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板34の一辺に、封止用基板35から露出した領域210を設け、この露出した領域210に、駆動回路20の配線を延長して外部接続端子(図示せず)を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

【0035】

(適用例1)

図7は、上述の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上述の表示装置1により構成されている。

【0036】

(適用例2)

図8は、上述の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上述の表示装置1により構成されている。

【0037】

(適用例3)

図9は、上述の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および映像を表示する表示部530を有しており、その表示部530は、上述の表示装置1により構成されている。

【0038】

(適用例4)

図10は、上述の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上述の表示装置1により構成されている。

【0039】

(適用例5)

図11は、上述の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上述の表示装置1により構成されている。

【0040】

以上、実施の形態、変形例および適用例を挙げて本技術を説明したが、本技術は上記実施の形態等に限定されるものではなく、種々変形が可能である。

【0041】

例えば、上記実施の形態等では、上述の表示装置1がアクティブマトリクス型である場合について説明したが、アクティブマトリクス駆動のための画素回路12の構成は上記実施の形態等で説明したものに限られず、必要に応じて容量素子やトランジスタを画素回路12に追加してもよい。その場合、画素回路12の変更に応じて、上述した信号線駆動回路23、書込線駆動回路24、電源線駆動回路25のほかに、必要な駆動回路を追加してもよい。

【0042】

また、例えば、上記実施の形態等では、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24、電源線駆動回路25の駆動をタイミング生成回路21が制御していたが、他の回路がこれらの駆動を制御するようにしてもよい。また、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24、電源線駆動回路25の制御は、ハードウェア(回路)で行われていてもよいし、ソフトウェア(プログラム)で行われていてもよい。

【0043】

また、例えば、本技術は以下のような構成を取ることができる。

(1)

表示領域に配置されると共に有機EL素子を含む複数の画素と、

画素間に配置された複数の導電性配線層と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示パネル。

(2)

前記導電性配線層は、前記正孔注入層が共通に形成されている複数の画素の間に配置されている

(1)に記載の表示パネル。

(3)

前記導電性配線層は、前記表示領域外の金属部材に接しており、

前記金属部材は、前記有機EL素子の閾値電圧よりも小さな第1電圧が印加される部材である

(1)または(2)に記載の表示パネル。

(4)

前記第1電圧は、グラウンド電圧、または前記有機EL素子のカソードの電圧と同一の電圧である

(3)に記載の表示パネル。

(5)

前記正孔注入層は、前記表示領域内の全ての画素において共通に形成されている

(1)ないし(4)のいずれか1つに記載の表示パネル。

(6)

前記複数の層は、正孔輸送層と、電子輸送層をさらに含んでいる

(1)ないし(5)のいずれか1つに記載の表示パネル。

(7)

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示装置。

(8)

表示装置を備え、

前記表示装置は、

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を有し、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

電子機器。

【符号の説明】

【0044】

1…表示装置、10…表示パネル、10A…表示領域、11…画素、12…画素回路、13…有機EL素子、14…TFT基板、15…金属配線層、16…金属部材、20…駆動回路、20A…映像信号、20B…同期信号、21…タイミング生成回路、21A…制御信号、22…映像信号処理回路、23…信号線駆動回路、24…書込線駆動回路、25…電源線駆動回路、31…アノード電極、32…有機層、32A…正孔注入層、32B…正孔輸送層、32C…発光層、32D…電子輸送層、33…カソード電極、34…基板、35…封止用基板、210…領域、220…FPC、300…映像表示画面部、310…フロントパネル、320…フィルターガラス、410…発光部、420,530,640…表示部、430…メニュースイッチ、440…シャッターボタン、510…本体、520…キーボード、610…本体部、620…レンズ、630…スタート/ストップスイッチ、710…上側筐体、720…下側筐体、730…連結部、740…ディスプレイ、750…サブディスプレイ、760…ピクチャーライト、770…カメラ、Cs…保持容量、DTL…信号線、GND…グラウンド線、DSL…電源線、Tr1…駆動トランジスタ、Tr2…書き込みトランジスタ、WSL…書込線。

【特許請求の範囲】

【請求項1】

表示領域に配置されると共に有機EL素子を含む複数の画素と、

画素間に配置された複数の導電性配線層と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示パネル。

【請求項2】

前記導電性配線層は、前記正孔注入層が共通に形成されている複数の画素の間に配置されている

請求項1に記載の表示パネル。

【請求項3】

前記導電性配線層は、前記表示領域外の金属部材に接しており、

前記金属部材は、前記有機EL素子の閾値電圧よりも小さな第1電圧が印加される部材である

請求項1に記載の表示パネル。

【請求項4】

前記第1電圧は、グラウンド電圧、または前記有機EL素子のカソードの電圧と同一の電圧である

請求項3に記載の表示パネル。

【請求項5】

前記正孔注入層は、前記表示領域内の全ての画素において共通に形成されている

請求項1に記載の表示パネル。

【請求項6】

前記複数の層は、正孔輸送層と、電子輸送層をさらに含んでいる

請求項1に記載の表示パネル。

【請求項7】

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示装置。

【請求項8】

表示装置を備え、

前記表示装置は、

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を有し、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

電子機器。

【請求項1】

表示領域に配置されると共に有機EL素子を含む複数の画素と、

画素間に配置された複数の導電性配線層と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示パネル。

【請求項2】

前記導電性配線層は、前記正孔注入層が共通に形成されている複数の画素の間に配置されている

請求項1に記載の表示パネル。

【請求項3】

前記導電性配線層は、前記表示領域外の金属部材に接しており、

前記金属部材は、前記有機EL素子の閾値電圧よりも小さな第1電圧が印加される部材である

請求項1に記載の表示パネル。

【請求項4】

前記第1電圧は、グラウンド電圧、または前記有機EL素子のカソードの電圧と同一の電圧である

請求項3に記載の表示パネル。

【請求項5】

前記正孔注入層は、前記表示領域内の全ての画素において共通に形成されている

請求項1に記載の表示パネル。

【請求項6】

前記複数の層は、正孔輸送層と、電子輸送層をさらに含んでいる

請求項1に記載の表示パネル。

【請求項7】

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を備え、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

表示装置。

【請求項8】

表示装置を備え、

前記表示装置は、

表示領域に配置されると共に有機EL素子を含む複数の画素と、画素間に配置された複数の導電性配線層とを有する表示パネルと、

各画素を駆動する駆動回路と

を有し、

前記有機EL素子は、少なくとも、正孔注入層と、電子と正孔との再結合により発光する発光層とを含む複数の層を有し、

前記複数の層のうち少なくとも前記正孔注入層は、前記表示領域内の複数の画素において共通に形成されるとともに、前記導電性配線層に電気的に接続されている

電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−89510(P2013−89510A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−230127(P2011−230127)

【出願日】平成23年10月19日(2011.10.19)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月19日(2011.10.19)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]