表示パネルの駆動装置および駆動方法

【課題】 表示素子を駆動させるドライバ回路が、例えば低温状態において誤動作するのを救済することができる表示パネルの駆動装置および駆動方法を提供すること。

【解決手段】 データドライバ2を構成するシフトレジスタ2aの最終段には、異常検知手段6が接続されており、この異常検知手段6はシフトレジスタ2aの初段に入力されるスタート信号が、前記シフトレジスタの最終段に転送されないことを検知した場合に、異常検知信号を出力するように構成されている。制御信号調整手段4aは前記異常検知信号を受けた場合、前記ドライバ回路に供給するクロック信号の周波数を落とし、シフトレジスタが動作し得るように制御する。

【解決手段】 データドライバ2を構成するシフトレジスタ2aの最終段には、異常検知手段6が接続されており、この異常検知手段6はシフトレジスタ2aの初段に入力されるスタート信号が、前記シフトレジスタの最終段に転送されないことを検知した場合に、異常検知信号を出力するように構成されている。制御信号調整手段4aは前記異常検知信号を受けた場合、前記ドライバ回路に供給するクロック信号の周波数を落とし、シフトレジスタが動作し得るように制御する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、例えば発光素子等の画素をマトリクス状に配列して構成した表示パネルの駆動技術に関し、前記発光素子を表示駆動させるドライバ回路が、特に低温状態において誤動作するのを救済することができる表示パネルの駆動装置および駆動方法に関する。

【背景技術】

【0002】

発光素子をマトリクス状に配列して構成される表示パネルを用いたディスプレイの開発が広く進められており、このような表示パネルに用いられる発光素子として、例えば有機材料を発光層に用いた有機EL(エレクトロルミネッセンス)素子が注目されている。これはEL素子の発光層に、良好な発光特性を期待することができる有機化合物を使用することによって、実用に耐えうる高効率化および長寿命化が進んだことも背景にある。

【0003】

かかる有機EL素子を用いた表示パネルとして、EL素子を発光画素としてこれを単にマトリクス状に配列したパッシブマトリクス型表示パネルと、マトリクス状に配列した前記EL素子の各々に、例えばTFT(Thin Film Transistor)からなる駆動素子を加えたアクティブマトリクス型表示パネルが提案されている。

【0004】

前者のパッシブマトリクス型表示パネルにおいては、表示パネルの構成を簡素化させることができるという特質を備えており、また後者のアクティブマトリクス型表示パネルにおいては、前者のパッシブマトリクス型表示パネルに比較して低消費電力化を実現させることが出来、また画素間のクロストークを少なくさせることができる等の特質を備えている。

【0005】

前記したパッシブマトリクス型表示パネルおよびアクティブマトリクス型表示パネルのいずれにおいても、これを発光駆動させる駆動装置においては、基本的には表示パネルに配列された各走査線を選択的に走査電位に設定する走査ドライバと、前記走査に同期して表示パネルに配列されたEL素子を含む各画素に表示信号を供給するためのデータドライバと、前記走査ドライバとデータドライバを制御するためのコントローラが具備される。

【0006】

図1は後者のアクティブマトリクス型表示パネルの駆動装置の例を示したものである。すなわち、符号1は例えばガラス基板上に前記各画素をマトリクス状に配列してなる表示パネルを示している。この表示パネル1にはデータドライバ2および走査ドライバ3が接続されており、さらに前記データドライバ2および走査ドライバ3を制御するコンントローラ4が具備されている。

【0007】

前記データドライバ2はコントローラ4よりデータバス5aを介して1水平走査に対応する各画素ごとの映像データを取り込み、画素を構成するTFTによる走査トランジスタのソースに対して、前記映像データに対応するソース電圧を供給するようになされる。このために、前記データドライバ2には、後で説明するようにシフトレジスタおよびラッチ回路等が具備されている。

【0008】

そして、これらの回路を駆動制御するために、コントローラ4よりデータドライバ2に対し、バスライン5bを介してシフトクロック(Shift Clock)、スタートパルス(Start Pulse)、ラッチパルス(Latch Pulse)等の信号が供給されるように構成されている。

【0009】

一方、前記走査ドライバ3は、アドレス期間において走査される各走査線(以下、これを走査ラインとも言う。)に対して択一的にゲートオン電圧を供給し、各走査ラインにゲートが接続された走査トランジスタを順次オン動作させることで、各画素に対応させて映像データを書き込むように動作する。

【0010】

このために、前記走査ドライバ3には、後で説明するようにシフトレジスタ等が具備されている。そして、これらの回路を駆動制御するために、コントローラ4より走査ドライバ3に対して、バスライン5cを介して走査シフトクロック(Shift Clock)、走査スタートパルス(Start Pulse)が供給されるように構成されている。

【0011】

図2は、図1に示す表示パネル1に配列された各画素の構成例を示したものである。この表示パネル1にはマトリクス状に配列された表示画素のうち、代表して4組の表示画素p11,p12,p21,p22が示されている。そして、表示パネル1には、前記データドライバ2に接続されるデータ線m1,m2,……が縦方向(列方向)に配列され、また、前記走査ドライバ3に接続される走査線n1,n2,……が横方向(行方向)に配列されている。さらに、表示パネル1には、前記各データ線に対応して、電源回路(図示せぬ)に接続される電源供給線q1,q2,……も縦方向に配列されている。

【0012】

図2においては前記各発光表示画素として、最も基本的なコンダクタンスコントロール方式による構成が示されている。すなわち、図2に示す表示パネル1における左上の画素p11を構成する各素子に符号を付けたとおり、nチャンネル型TFTで構成された走査トランジスタTr1のゲートは、走査線n1に接続され、そのソースはデータ線m1に接続されている。また、走査トランジスタTr1のドレインは、pチャンネル型TFTで構成された点灯駆動用トランジスタTr2のゲートに接続されると共に、電荷保持用コンデンサC1の一方の端子に接続されている。

【0013】

そして、点灯駆動用トランジスタTr2のソースは前記コンデンサC1の他方の端子に接続されると共に、電源供給線q1に接続されている。また、点灯駆動用トランジスタTr2のドレインには、発光素子としての有機EL素子E1のアノード端子が接続されると共に、当該EL素子E1のカソード端子は回路の基準電位点(グランド)に接続されている。斯くして、前記した構成の発光表示画素は、前記したとおり表示パネル1上に、縦横方向にマトリクス状に多数配列されている。

【0014】

図2に示した構成において、発光表示画素p11における走査トランジスタTr1のゲートに、走査線n1を介して走査ドライバ3よりオン電圧が供給されると、走査トランジスタTr1はソースに供給されるデータ線m1からのソース電圧に対応した電流を、ソースからドレインに流す。したがって、走査トランジスタTr1のゲートがオン電圧の期間に、前記コンデンサC1には前記ソース電圧に対応した電圧が充電され、その電圧が点灯駆動用トランジスタTr2のゲートに供給される。それ故、点灯駆動用トランジスタTr2は、そのゲート電圧とソース電圧(Vgs)に基づいた電流をEL素子E1に流し、EL素子を発光駆動させる。

【0015】

一方、走査トランジスタTr1のゲートがオフ電圧になると、走査トランジスタTr1はいわゆるカットオフとなり、当該トランジスタのドレインは開放状態となるものの、点灯駆動用トランジスタTr2はコンデンサC1に蓄積された電荷によりゲート電圧が保持される。したがって、次の走査まで駆動用トランジスタTr2の駆動電流が維持され、これによりEL素子E1の発光も維持される。

【0016】

なお、図2に示したように表示画素にEL素子を用いた発光表示パネルの駆動装置として、図1に示したようにデータドライバ2、走査ドライバ3およびコンントローラ4を備えた構成は、きわめて多くの特許文献に開示されており、一例として次に示す特許文献1を挙げることができる。

【特許文献1】特開2002−32057号公報

【発明の開示】

【発明が解決しようとする課題】

【0017】

ところで、前記したような表示パネルの駆動装置においては、特に低温の環境(例えば−20℃以下の環境)においては、前記データドライバ2および走査ドライバ3における特にシフトレジスタの動作特性に遅れが生ずるという問題が発生する。前記シフトレジスタは、後で詳細に説明するように表示パネルに配列された前記データ線および走査線に対応して、それぞれ複数段のレジスタ回路(これをフリップフロップ回路もしくはラッチ回路とも言う)が接続された構成にされている。

【0018】

そして、前記各シフトレジスタは、表示しようとする映像信号のフレーム周波数に同期して入力されるパルス信号(これをスタート信号とも言う。)を、制御信号(これをクロック信号とも言う。)によって、直列接続された各レジスタ回路を順次転送するように動作する。したがって、前記した例えば低温の環境下において、前記シフトレジスタを構成するいずれか一つのレジスタ回路がその機能が果たせなくなった場合には、その後段には前記したスタート信号の転送が不能になる。これにより、映像の垂直もしくは水平の同期がとれなくなり、映像の表示は不可能となる。

【0019】

この発明は前記した問題点に着目してなされたものであり、特に前記したドライバ回路におけるシフトレジスタの誤動作を検知し、これを救済することができる表示パネルの駆動装置および駆動方法を提供することを課題とするものである。

【課題を解決するための手段】

【0020】

前記した課題を解決するためになされたこの発明にかかる発光表示パネルの駆動装置は、請求項1に記載のとおり、複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動装置であって、前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知して異常検知信号を出力する異常検知手段と、前記異常検知手段からの異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号を調整する制御信号調整手段とを具備したことを特徴とする。

【0021】

また、前記した課題を解決するためになされたこの発明にかかる発光表示パネルの駆動方法は、請求項10に記載のとおり、複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動方法であって、前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知した場合に異常検知信号を出力するとともに、前記異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号を調整する動作を実行する点に特徴を有する。

【発明を実施するための最良の形態】

【0022】

以下、この発明にかかる好ましい実施の形態について図面に基づいて説明する。なお、この発明にかかる駆動装置の基本構成は、すでに説明した図1に示すブロック図と同様に表わすことができ、また、表示パネルとしては図2に示した構成のアクティブマトリクス型発光表示パネルを好適に利用することができる。したがって、以下の説明においては、図1および図2の各部に相当する部分を、同一符号で示すことにする。

【0023】

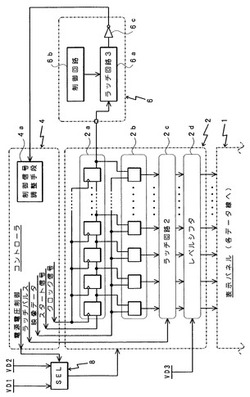

図3は、前記したコントローラ4とデータドライバ2に加えて、異常検知手段6と制御信号調整手段4aとを備えたこの発明にかかる第1の実施の形態を示したものである。すなわち図3に示す実施の形態は、データドライバ2におけるシフトレジスタの動作を監視し、当該シフトレジスタが正常に動作していないことを検知した場合に、これを救済することができるように構成した例を示している。

【0024】

また、図4は前記したコントローラ4と走査ドライバ3に加えて、異常検知手段6と制御信号調整手段4aとを備えたこの発明にかかる第2の実施の形態を示したものである。すなわち図4に示す実施の形態は、走査ドライバ3におけるシフトレジスタの動作を監視し、当該シフトレジスタが正常に動作していないことを検知した場合に、これを救済することができるように構成した例を示している。

【0025】

以下においては、図3に示したデータドライバ2の構成および動作について、また図4に示した走査ドライバ3の構成および動作についてそれぞれ先に説明し、その後においてそれぞれのドライバにおけるシフトレジスタの監視動作等について図3および図4に基づいて順に説明する。

【0026】

まず、図3に示すデータドライバ2には、シフトレジスタ2aが具備されており、このシフトレジスタ2aには、図5に(a)として示す制御信号としてのシフトクロック、および図5に(b)として示すスタート信号としてのスタートパルス(スタートパルス)がコントローラ4より供給されるように構成されている。前記シフトレジスタ2aは、例えばD型フリップフロップ回路からなる複数のレジスタ回路を直列に接続した構成にされており、これは表示パネルに配列された前記データ線m1,m2,……の数に対応して用意されている。

【0027】

前記各レジスタ回路のクロック入力端子には、制御信号としての前記したシフトクロックがそれぞれ供給されるように構成されており、また前記レジスタ回路の出力端は、次のレジスタ回路の入力端に順次接続されている。したがって、初段のレジスタ回路に供給されるスタート信号は、直列接続された各レジスタ回路を、前記クロック信号によって順次転送されるように動作する。そして、各段のレジスタ回路に発生する前記スタートパルスは、第1ラッチ回路2bに対して順にデータ書き込み用信号として供給されるように作用する。

【0028】

前記第1ラッチ回路2bは、図5に(d)として示す各画素に対応する映像データを処理する複数のステージの各ラッチを有しており、前記シフトレジスタ2aより順に供給される前記書き込み用信号によって、データバスを介して供給される映像データを各ラッチに順に書き込み、保持するように作用する。この第1ラッチ回路2bへの1走査ライン分の映像データの書き込みが終了すると、第2ラッチ回路2cに対して図5に(c)として示すラッチパルスがコントローラ4より供給される。

【0029】

これにより、第1ラッチ回路2bに書き込まれた1ライン分の映像データは、一斉に第2ラッチ回路2cに伝送される。そして、第2ラッチ回路2cに対して1ライン分の映像データを送出し終えた第1ラッチ回路2bには、シフトレジスタ2aからの書き込み用信号を受けて、再び次の1ライン分の映像データの書き込みがなされる。

【0030】

前記第2ラッチ回路2cにおいてラッチされた各画素に対応する映像データは、電源電圧VD3によって動作するレベルシフタ2dに供給される。このレベルシフタ2dによって所定のレベルに変換された映像データは、図2に示した表示パネル1の各データ線m1,m2,……を介して走査状態のトランジスタTr1に対し、画素点灯用の信号(ソース電圧)として供給される。

【0031】

一方、図4に示した走査ドライバ3においても、シフトレジスタ3aが具備されており、このシフトレジスタ3aには、図6に(e)として示す制御信号としての走査シフトクロック、および(f)として示すスタート信号としての走査スタートパルスがコントローラ4より供給されるように構成されている。

【0032】

図4に示すシフトレジスタ3aの構成も、すでに説明した図3に示すデータドライバ2におけるシフトレジスタ2aの構成と同様に、複数のレジスタ回路を直列に接続した構成にされており、これは表示パネルに配列された前記走査線n1,n2,……の数に対応して用意されている。

【0033】

前記各レジスタ回路のクロック入力端子には、制御信号としての前記した走査シフトクロックがコントローラ4よりそれぞれ供給されるように構成されており、したがって、初段のレジスタ回路に供給される走査スタート信号は、直列接続された各レジスタ回路を、前記クロック信号によって順次転送されるように動作する。そして、各段のレジスタ回路に発生する前記スタートパルスは、電源電圧VD4によって動作するレベルシフタ3bに対して走査選択信号として順に供給される。

【0034】

このレベルシフタ3bによって所定のレベルに変換された走査選択信号は、図2に示した表示パネル1の各走査線n1,n2,……を介して走査トランジスタTr1のゲートに対して順次ゲートオン電圧、すなわち図6に(g)として示すタイミングでゲート制御信号を供給するように作用する。

【0035】

したがってアドレッシング時において、表示パネル1に配列された各走査線n1,n2,……には、前記したように順次ゲートオン電圧が供給されると共に、これに同期して各データ線m1,m2,……には順に1ラインごとの映像データが供給される。これにより、表示パネル1における各画素には個々に映像データが書き込まれ、表示パネルは前記映像データに応じて発光制御を受ける。これにより前記表示パネル1には前記映像データに基づく映像が再現される。

【0036】

図3に戻り、前記データドライバ2におけるシフトレジスタ2aには、符号6で示す異常検知手段が接続されている。すなわち、この実施の形態においては異常検知手段6にはシフトレジスタ2aにおける最終段の出力が供給されるように構成されており、これは異常検知手段6に具備された第3のラッチ回路6aに供給されるように構成されている。また異常検知手段6には制御回路6bが具備され、この制御回路6bからの制御信号によって、前記第3のラッチ回路6aはシフトレジスタ2aの最終段からの出力をラッチするように構成されている。

【0037】

そして、第3のラッチ回路6aの出力はインバータ6cを介して、制御信号調整手段4aに供給されるように構成されている。なお、制御信号調整手段4aは、この実施の形態においては前記したコントローラ4内に具備されている。

【0038】

図7は、前記した異常検知手段6の動作を説明するタイミングチャートであり、図7(a)は前記データドライバ2におけるシフトレジスタ2aの初段に入力されるスタートパルス、すなわち図5に(b)として示したスタートパルスである。また図7(b)はシフトレジスタ2aの最終段において出力される前記スタートパルスであり、換言すれば前記異常検知手段6における第3のラッチ回路6aに供給されるスタートパルスである。すなわち、前記スタートパルスは図7(a)から(b)に矢印で示したように、シフトレジスタ2aの初段から最終段に転送される時間に対応した遅れが常に発生する。

【0039】

ここで、動作環境(例えば低温時)の影響を受けて、データドライバ2におけるシフトレジスタ2aにおけるいずれかのレジスタ回路がレジスタ動作(ラッチ動作)をしなかった場合においては、予め定められたタイミング、すなわち前記した遅れを持ったタイミングにおいて、異常検知手段6に対して前記スタートパルスが到達しないことになる。なお、図7(b)に示す破線は前記スタートパルスが到達しない状態を示している。

【0040】

前記スタートパルスが通常のタイミングにおいて異常検知手段6に到達したか否かを検証するために、前記制御回路6bからは前記第3のラッチ回路6aに対して前記した遅れを持ったタイミングにおいて、ラッチ動作をさせるための制御信号が出力されるように構成されている。すなわち、前記制御回路6bは前記コントローラ4におけるスタート信号の発生タイミングに同期し、所定の遅延をもって前記第3のラッチ回路6aに対して制御信号を出力するように構成されている。

【0041】

ここで、図7(b)に破線で示すように異常検知手段6に対して前記スタートパルスが到達しない場合には、前記第3のラッチ回路6aはスタートパルスをラッチすることはできず、したがって第3のラッチ回路6aの出力は発生しない(Lレベルになされる)。この状態はインバータ6cによって図7(c)に示すようにレベル反転され、異常検知信号として出力される。そして、前記異常検知信号は前記した制御信号調整手段4aに供給される。

【0042】

図7(c)に示す異常検知信号を受けた制御信号調整手段4aは、コントローラ4からデータドライバ2のシフトレジスタ2aに供給する制御信号としてのクロック信号の形態を、前記した低温時においても確実にシフトレジスタ2aが動作し得るように可変調整する動作を実行する。これには、前記制御信号としてのクロック信号の周波数、またクロック信号の振幅のうちの少なくとも一方を可変調整する手段を採用することができる。

【0043】

図8は前記した異常検知手段6より異常検知信号を受けた場合においてなし得るクロック信号の周波数を低下させる具体例を示すものである。すなわち、前記した制御信号調整手段4aは前記した異常検知信号を受けた場合において、コントローラ4よりシフトレジスタ2aに供給するクロック信号を図8に示す分周手段を介してクロック信号の周波数を変更(低下)させる動作を実行する。

【0044】

図9は、図8に示すクロック信号の分周手段の動作を説明する真理値表を示すものである。これによると、図10(a)として示すクロック信号は図10(b)として示すクロック信号に変換されてデータドライバ2のシフトレジスタ2aに供給される。すなわち、シフトレジスタ2aは通常よりも若干低い周波数のクロック信号によりシフト動作がなされるため、たとえ低温時においてもシフトレジスタ2aの動作の信頼性を上げることができる。

【0045】

なお、図8に示す分周手段の出力を反転させるインバータをさらに付加した場合には、図11に示すように(a)として示すクロック信号を(b)として示すクロック信号に変換することができる。このように、図11(b)に示すクロック信号用いても、低温時におけるシフトレジスタ2aの動作の信頼性を上げることができる。

【0046】

以上説明したように、コントローラ4よりデータドライバ2に供給するクロック信号の周波数を低下させた場合においては、実質的にフレームレートが低下して、いわゆるコマ抜き状態になされるものの、映像信号をリアルタイムに表示させることは可能である。なお、図8に示す回路構成に代えてPLL回路を用い、前記した異常検知手段6より異常検知信号を受けた場合においては、前記PLL回路によってクロック信号の周波数を変更させる動作を実行するようにしてもよい。

【0047】

以上の説明はシフトレジスタ2aの動作の信頼性を上げるために、コントローラ4よりデータドライバ2に供給するクロック信号の周波数を変更する例を示したものであるが、例えばコントローラ4よりデータドライバ2に供給するクロック信号の振幅を上昇させるように制御することでも、低温時においてシフトレジスタ2aが動作不能となるのを救済することができる。

【0048】

この場合においては、コントローラ4に図示せぬレベルシフタを具備し、前記異常検知手段6より異常検知信号を受けた時、データドライバ2に供給される前記クロック信号の振幅を前記レベルシフタにより上昇させるように制御する。この結果、図12(a)に示すように、定常時においてコントローラ4よりデータドライバ2のシフトレジスタ2aに供給されるクロック信号の振幅V1に対して、図12(b)に示すようにさらに大きな振幅V2を有するクロック信号をシフトレジスタ2aに供給することで、前記した低温時においてシフトレジスタ2aが動作不能となるのを救済することができる。

【0049】

また、前記したような対策に加え、前記異常検知手段からの異常検知信号を受けて、前記データドライバ回路に供給する電源電圧値を可変調整する電源電圧調整手段がさらに具備されていることが望ましい。すなわち、図3に示す構成においてはVD1(例えば3V)およびVD2(例えば5V)の電源電圧が用意され、これを選択してデータドライバ2に供給することができる電源電圧調整手段8が備えられている。

【0050】

ここで、前記したデータドライバ2を構成するシフトレジスタ2aにおいても、また第1および第2のラッチ回路2b,2cにおいても、例えばFETによりフリップフロップ回路が構成されている。前記フリップフロップ回路を構成するFETは、例えば低温時においては動作速度が低下しシフトレジスタ2a、第1および第2のラッチ回路2b,2cが誤動作する要因となる。このような問題に対処するには、各フリップフロップ回路の電源電圧を上昇させることが効果的である。

【0051】

そこで、前記異常検知手段6からの異常検知信号を受けた制御信号調整手段4aは、前記電源電圧調整手段8を駆動し、データドライバ2における通常動作時のVD1から、より高い電源電圧のVD2に切り替えるように動作させる。これにより、フリップフロップ回路で構成される前記シフトレジスタ2a、第1および第2のラッチ回路2b,2cの動作の信頼性を向上させることができる。

【0052】

以上の説明は、図3に示すデータドライバ2が、特に低温時において動作不能となる状態を救済する手段を説明するものであるが、これと同様に図4に示す走査ドライバ3においても同様の手段を適用することができる。すなわち、図4に基づいてすでに説明したように走査ドライバ3においてもシフトレジスタ3aが具備されており、これも同様に特に低温時において動作不能となる場合が発生する。

【0053】

この様な状態となるのを阻止するために、図4に示す実施の形態においても異常検知手段6および制御信号調整手段4aが具備されている。この異常検知手段6および制御信号調整手段4aは、図3に基づいて説明した構成と同一であり、したがってその説明は省略する。

【0054】

そして、異常検知手段6より異常検出信号が出力された場合においては、制御信号調整手段4aは、図10または図11に示したように、制御信号としてのクロック信号(走査シフトクロック)の周波数を低下させる手段、さらに図12に示したように、制御信号としてのクロック信号の振幅を増大させる手段を適宜採用するように動作する。

【0055】

さらに、図4に示す実施の形態に示すように、前記異常検知手段6からの異常検知信号を受けて、前記走査ドライバ3に供給する電源電圧値を可変調整する電源電圧調整手段8を備え、電源電圧VD1,VD2が選択できるように構成されていることが望ましい。これを具備することにより、図3に基づいてすでに説明した作用効果と同様の作用効果を享受することができる。

【0056】

図13は、コントローラ4とデータドライバ2に加えて、異常検知手段7と制御信号調整手段4aとを備えたこの発明にかかる第3の実施の形態を示したものである。この図13に示す実施の形態においては、図3に示した異常検知手段6の構成に代えて、カウンタ7aと判定回路7bからなる異常検知手段7が採用されており、他の構成は同一である。したがって、同一部分の説明は割愛する。

【0057】

この図13に示す異常検知手段7においては、データドライバ2におけるシフトレジスタ2aの初段に順次入力されるスタート信号が、前記シフトレジスタの最終段に転送される数を所定の期間にわたって計測する計測手段を構成している。すなわち、カウンタ7aはシフトレジスタ2aの最終段に転送されるスタート信号の数を計測する機能を有し、判定回路7bは前記カウンタ7aにより計測された前記スタート信号の数を予め定められた所定値と比較するように機能する。

【0058】

ここで、前記カウンタ7aと判定回路7bとは、所定の周期をもって計測動作を繰り返すように構成されており、判定回路7bはその所定の周期(期間中)におけるスタート信号の数が前記した予め定められた所定値に達するか否かを判定するように作用する。

【0059】

図15は、その判定動作を説明するものであり、(a)はデータドライバ2におけるシフトレジスタ2aの最終段に到達するスタート信号の様子を示している。このスタート信号は、シフトレジスタ2aが正常状態であれは、一定の周期をもって順次カウンタ7aに到来することになるが、シフトレジスタ2aがその一部で動作不能となっている場合には、図15(a)に破線で示すようにスタート信号は到来せず、したがって、カウンタ7aはこれをカウントすることはできない。

【0060】

そして、前記した所定の周期(期間中)におけるスタート信号の数が、予め定められた所定値に達しない場合には、判定回路7bは図15(b)に示すように異常検知信号を出力する。前記異常検知信号を受けた制御信号調整手段4aは、すでに説明した図3に基づいて説明した例と同様の制御信号調整動作を実行する。

【0061】

また、望ましくはこれに加えて、前記データドライバ回路に供給する電源電圧値を可変調整する電源電圧調整手段8を制御し、データドライバ2に供給する電源電圧を上昇させるように動作させる。したがって、図13に示した実施の形態においても、図3に示した構成と同様の作用効果を得ることができる。

【0062】

図14は、コントローラ4と走査ドライバ3に加えて、異常検知手段7と制御信号調整手段4aとを備えたこの発明にかかる第4の実施の形態を示したものである。この図14に示す実施の形態においても、図4に示した異常検知手段6の構成に代えて、カウンタ7aと判定回路7bからなる異常検知手段7が採用されており、他の構成は同一である。

【0063】

また、カウンタ7aと判定回路7bからなる異常検知手段7の動作は、図13および図15に基づいて説明した異常検知手段7と同様である。したがって、図14に示した実施の形態においても、図4に示した構成と同様の作用効果を得ることができる。

【0064】

なお、以上説明した実施の形態においては、シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの最終段に転送されないことを検知した場合に、異常検知手段より異常検知信号を出力するように構成されている。しかしながら、転送されるパルス信号の抽出点はシフトレジスタの最終段に限られることはなく、前記シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの予め定められた転送段(これは前記最終段も含む)に転送されないことを検知した場合に、前記異常検知信号を出力するように構成されていてもよい。

【0065】

また、以上説明した実施の形態においては、有機EL素子を画素に備えた表示パネルを用いた例を示しているが、これは他の表示画素を配列した表示パネルの駆動装置にも適用することができる。さらに、前記した説明においては、特に低温状態においてシフトレジスタが動作不能になる例を挙げているが、逆に高温状態において同様の不具合が発生する場合においても、効果的にこれを救済することができる。

【図面の簡単な説明】

【0066】

【図1】従来の表示パネルの駆動装置における基本構成を示したブロック図である。

【図2】図1に示す表示パネルに配列された画素部の構成例を示した結線図である。

【図3】この発明にかかる駆動装置の第1の実施の形態を示したブロック図である。

【図4】同じく第2の実施の形態を示したブロック図である。

【図5】データドライバに供給される各信号のタイミング図である。

【図6】走査ドライバに供給される各信号のタイミング図である。

【図7】図3および図4に示す実施の形態において採用された異常検知手段の動作を説明するタイミング図である。

【図8】図3および図4に示す実施の形態において採用された制御信号調整手段の一例を示すブロック図である。

【図9】図8に示すブロック図における動作を説明するための真理値表である。

【図10】制御信号調整手段により調整されるクロック信号の一例を示した波形図である。

【図11】同じくクロック信号の他の例を示した波形図である。

【図12】同じくクロック信号のさらに他の例を示した波形図である。

【図13】この発明にかかる駆動装置の第3の実施の形態を示したブロック図である。

【図14】同じく第4の実施の形態を示したブロック図である。

【図15】図13および図14に示す実施の形態において採用された異常検知手段の動作を説明するタイミング図である。

【符号の説明】

【0067】

1 表示パネル

2 データドライバ

2a シフトレジスタ

2b 第1ラッチ回路

2c 第2ラッチ回路

2d レベルシフタ

3 走査ドライバ

3a シフトレジスタ

3b レベルシフタ

4 コントローラ

4a 制御信号調整手段

6 異常検知手段

6a ラッチ回路

6b 制御回路

6c インバータ

7 異常検知手段

7a カウンタ

7b 判定回路

8 電源電圧調整手段

【技術分野】

【0001】

この発明は、例えば発光素子等の画素をマトリクス状に配列して構成した表示パネルの駆動技術に関し、前記発光素子を表示駆動させるドライバ回路が、特に低温状態において誤動作するのを救済することができる表示パネルの駆動装置および駆動方法に関する。

【背景技術】

【0002】

発光素子をマトリクス状に配列して構成される表示パネルを用いたディスプレイの開発が広く進められており、このような表示パネルに用いられる発光素子として、例えば有機材料を発光層に用いた有機EL(エレクトロルミネッセンス)素子が注目されている。これはEL素子の発光層に、良好な発光特性を期待することができる有機化合物を使用することによって、実用に耐えうる高効率化および長寿命化が進んだことも背景にある。

【0003】

かかる有機EL素子を用いた表示パネルとして、EL素子を発光画素としてこれを単にマトリクス状に配列したパッシブマトリクス型表示パネルと、マトリクス状に配列した前記EL素子の各々に、例えばTFT(Thin Film Transistor)からなる駆動素子を加えたアクティブマトリクス型表示パネルが提案されている。

【0004】

前者のパッシブマトリクス型表示パネルにおいては、表示パネルの構成を簡素化させることができるという特質を備えており、また後者のアクティブマトリクス型表示パネルにおいては、前者のパッシブマトリクス型表示パネルに比較して低消費電力化を実現させることが出来、また画素間のクロストークを少なくさせることができる等の特質を備えている。

【0005】

前記したパッシブマトリクス型表示パネルおよびアクティブマトリクス型表示パネルのいずれにおいても、これを発光駆動させる駆動装置においては、基本的には表示パネルに配列された各走査線を選択的に走査電位に設定する走査ドライバと、前記走査に同期して表示パネルに配列されたEL素子を含む各画素に表示信号を供給するためのデータドライバと、前記走査ドライバとデータドライバを制御するためのコントローラが具備される。

【0006】

図1は後者のアクティブマトリクス型表示パネルの駆動装置の例を示したものである。すなわち、符号1は例えばガラス基板上に前記各画素をマトリクス状に配列してなる表示パネルを示している。この表示パネル1にはデータドライバ2および走査ドライバ3が接続されており、さらに前記データドライバ2および走査ドライバ3を制御するコンントローラ4が具備されている。

【0007】

前記データドライバ2はコントローラ4よりデータバス5aを介して1水平走査に対応する各画素ごとの映像データを取り込み、画素を構成するTFTによる走査トランジスタのソースに対して、前記映像データに対応するソース電圧を供給するようになされる。このために、前記データドライバ2には、後で説明するようにシフトレジスタおよびラッチ回路等が具備されている。

【0008】

そして、これらの回路を駆動制御するために、コントローラ4よりデータドライバ2に対し、バスライン5bを介してシフトクロック(Shift Clock)、スタートパルス(Start Pulse)、ラッチパルス(Latch Pulse)等の信号が供給されるように構成されている。

【0009】

一方、前記走査ドライバ3は、アドレス期間において走査される各走査線(以下、これを走査ラインとも言う。)に対して択一的にゲートオン電圧を供給し、各走査ラインにゲートが接続された走査トランジスタを順次オン動作させることで、各画素に対応させて映像データを書き込むように動作する。

【0010】

このために、前記走査ドライバ3には、後で説明するようにシフトレジスタ等が具備されている。そして、これらの回路を駆動制御するために、コントローラ4より走査ドライバ3に対して、バスライン5cを介して走査シフトクロック(Shift Clock)、走査スタートパルス(Start Pulse)が供給されるように構成されている。

【0011】

図2は、図1に示す表示パネル1に配列された各画素の構成例を示したものである。この表示パネル1にはマトリクス状に配列された表示画素のうち、代表して4組の表示画素p11,p12,p21,p22が示されている。そして、表示パネル1には、前記データドライバ2に接続されるデータ線m1,m2,……が縦方向(列方向)に配列され、また、前記走査ドライバ3に接続される走査線n1,n2,……が横方向(行方向)に配列されている。さらに、表示パネル1には、前記各データ線に対応して、電源回路(図示せぬ)に接続される電源供給線q1,q2,……も縦方向に配列されている。

【0012】

図2においては前記各発光表示画素として、最も基本的なコンダクタンスコントロール方式による構成が示されている。すなわち、図2に示す表示パネル1における左上の画素p11を構成する各素子に符号を付けたとおり、nチャンネル型TFTで構成された走査トランジスタTr1のゲートは、走査線n1に接続され、そのソースはデータ線m1に接続されている。また、走査トランジスタTr1のドレインは、pチャンネル型TFTで構成された点灯駆動用トランジスタTr2のゲートに接続されると共に、電荷保持用コンデンサC1の一方の端子に接続されている。

【0013】

そして、点灯駆動用トランジスタTr2のソースは前記コンデンサC1の他方の端子に接続されると共に、電源供給線q1に接続されている。また、点灯駆動用トランジスタTr2のドレインには、発光素子としての有機EL素子E1のアノード端子が接続されると共に、当該EL素子E1のカソード端子は回路の基準電位点(グランド)に接続されている。斯くして、前記した構成の発光表示画素は、前記したとおり表示パネル1上に、縦横方向にマトリクス状に多数配列されている。

【0014】

図2に示した構成において、発光表示画素p11における走査トランジスタTr1のゲートに、走査線n1を介して走査ドライバ3よりオン電圧が供給されると、走査トランジスタTr1はソースに供給されるデータ線m1からのソース電圧に対応した電流を、ソースからドレインに流す。したがって、走査トランジスタTr1のゲートがオン電圧の期間に、前記コンデンサC1には前記ソース電圧に対応した電圧が充電され、その電圧が点灯駆動用トランジスタTr2のゲートに供給される。それ故、点灯駆動用トランジスタTr2は、そのゲート電圧とソース電圧(Vgs)に基づいた電流をEL素子E1に流し、EL素子を発光駆動させる。

【0015】

一方、走査トランジスタTr1のゲートがオフ電圧になると、走査トランジスタTr1はいわゆるカットオフとなり、当該トランジスタのドレインは開放状態となるものの、点灯駆動用トランジスタTr2はコンデンサC1に蓄積された電荷によりゲート電圧が保持される。したがって、次の走査まで駆動用トランジスタTr2の駆動電流が維持され、これによりEL素子E1の発光も維持される。

【0016】

なお、図2に示したように表示画素にEL素子を用いた発光表示パネルの駆動装置として、図1に示したようにデータドライバ2、走査ドライバ3およびコンントローラ4を備えた構成は、きわめて多くの特許文献に開示されており、一例として次に示す特許文献1を挙げることができる。

【特許文献1】特開2002−32057号公報

【発明の開示】

【発明が解決しようとする課題】

【0017】

ところで、前記したような表示パネルの駆動装置においては、特に低温の環境(例えば−20℃以下の環境)においては、前記データドライバ2および走査ドライバ3における特にシフトレジスタの動作特性に遅れが生ずるという問題が発生する。前記シフトレジスタは、後で詳細に説明するように表示パネルに配列された前記データ線および走査線に対応して、それぞれ複数段のレジスタ回路(これをフリップフロップ回路もしくはラッチ回路とも言う)が接続された構成にされている。

【0018】

そして、前記各シフトレジスタは、表示しようとする映像信号のフレーム周波数に同期して入力されるパルス信号(これをスタート信号とも言う。)を、制御信号(これをクロック信号とも言う。)によって、直列接続された各レジスタ回路を順次転送するように動作する。したがって、前記した例えば低温の環境下において、前記シフトレジスタを構成するいずれか一つのレジスタ回路がその機能が果たせなくなった場合には、その後段には前記したスタート信号の転送が不能になる。これにより、映像の垂直もしくは水平の同期がとれなくなり、映像の表示は不可能となる。

【0019】

この発明は前記した問題点に着目してなされたものであり、特に前記したドライバ回路におけるシフトレジスタの誤動作を検知し、これを救済することができる表示パネルの駆動装置および駆動方法を提供することを課題とするものである。

【課題を解決するための手段】

【0020】

前記した課題を解決するためになされたこの発明にかかる発光表示パネルの駆動装置は、請求項1に記載のとおり、複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動装置であって、前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知して異常検知信号を出力する異常検知手段と、前記異常検知手段からの異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号を調整する制御信号調整手段とを具備したことを特徴とする。

【0021】

また、前記した課題を解決するためになされたこの発明にかかる発光表示パネルの駆動方法は、請求項10に記載のとおり、複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動方法であって、前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知した場合に異常検知信号を出力するとともに、前記異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号を調整する動作を実行する点に特徴を有する。

【発明を実施するための最良の形態】

【0022】

以下、この発明にかかる好ましい実施の形態について図面に基づいて説明する。なお、この発明にかかる駆動装置の基本構成は、すでに説明した図1に示すブロック図と同様に表わすことができ、また、表示パネルとしては図2に示した構成のアクティブマトリクス型発光表示パネルを好適に利用することができる。したがって、以下の説明においては、図1および図2の各部に相当する部分を、同一符号で示すことにする。

【0023】

図3は、前記したコントローラ4とデータドライバ2に加えて、異常検知手段6と制御信号調整手段4aとを備えたこの発明にかかる第1の実施の形態を示したものである。すなわち図3に示す実施の形態は、データドライバ2におけるシフトレジスタの動作を監視し、当該シフトレジスタが正常に動作していないことを検知した場合に、これを救済することができるように構成した例を示している。

【0024】

また、図4は前記したコントローラ4と走査ドライバ3に加えて、異常検知手段6と制御信号調整手段4aとを備えたこの発明にかかる第2の実施の形態を示したものである。すなわち図4に示す実施の形態は、走査ドライバ3におけるシフトレジスタの動作を監視し、当該シフトレジスタが正常に動作していないことを検知した場合に、これを救済することができるように構成した例を示している。

【0025】

以下においては、図3に示したデータドライバ2の構成および動作について、また図4に示した走査ドライバ3の構成および動作についてそれぞれ先に説明し、その後においてそれぞれのドライバにおけるシフトレジスタの監視動作等について図3および図4に基づいて順に説明する。

【0026】

まず、図3に示すデータドライバ2には、シフトレジスタ2aが具備されており、このシフトレジスタ2aには、図5に(a)として示す制御信号としてのシフトクロック、および図5に(b)として示すスタート信号としてのスタートパルス(スタートパルス)がコントローラ4より供給されるように構成されている。前記シフトレジスタ2aは、例えばD型フリップフロップ回路からなる複数のレジスタ回路を直列に接続した構成にされており、これは表示パネルに配列された前記データ線m1,m2,……の数に対応して用意されている。

【0027】

前記各レジスタ回路のクロック入力端子には、制御信号としての前記したシフトクロックがそれぞれ供給されるように構成されており、また前記レジスタ回路の出力端は、次のレジスタ回路の入力端に順次接続されている。したがって、初段のレジスタ回路に供給されるスタート信号は、直列接続された各レジスタ回路を、前記クロック信号によって順次転送されるように動作する。そして、各段のレジスタ回路に発生する前記スタートパルスは、第1ラッチ回路2bに対して順にデータ書き込み用信号として供給されるように作用する。

【0028】

前記第1ラッチ回路2bは、図5に(d)として示す各画素に対応する映像データを処理する複数のステージの各ラッチを有しており、前記シフトレジスタ2aより順に供給される前記書き込み用信号によって、データバスを介して供給される映像データを各ラッチに順に書き込み、保持するように作用する。この第1ラッチ回路2bへの1走査ライン分の映像データの書き込みが終了すると、第2ラッチ回路2cに対して図5に(c)として示すラッチパルスがコントローラ4より供給される。

【0029】

これにより、第1ラッチ回路2bに書き込まれた1ライン分の映像データは、一斉に第2ラッチ回路2cに伝送される。そして、第2ラッチ回路2cに対して1ライン分の映像データを送出し終えた第1ラッチ回路2bには、シフトレジスタ2aからの書き込み用信号を受けて、再び次の1ライン分の映像データの書き込みがなされる。

【0030】

前記第2ラッチ回路2cにおいてラッチされた各画素に対応する映像データは、電源電圧VD3によって動作するレベルシフタ2dに供給される。このレベルシフタ2dによって所定のレベルに変換された映像データは、図2に示した表示パネル1の各データ線m1,m2,……を介して走査状態のトランジスタTr1に対し、画素点灯用の信号(ソース電圧)として供給される。

【0031】

一方、図4に示した走査ドライバ3においても、シフトレジスタ3aが具備されており、このシフトレジスタ3aには、図6に(e)として示す制御信号としての走査シフトクロック、および(f)として示すスタート信号としての走査スタートパルスがコントローラ4より供給されるように構成されている。

【0032】

図4に示すシフトレジスタ3aの構成も、すでに説明した図3に示すデータドライバ2におけるシフトレジスタ2aの構成と同様に、複数のレジスタ回路を直列に接続した構成にされており、これは表示パネルに配列された前記走査線n1,n2,……の数に対応して用意されている。

【0033】

前記各レジスタ回路のクロック入力端子には、制御信号としての前記した走査シフトクロックがコントローラ4よりそれぞれ供給されるように構成されており、したがって、初段のレジスタ回路に供給される走査スタート信号は、直列接続された各レジスタ回路を、前記クロック信号によって順次転送されるように動作する。そして、各段のレジスタ回路に発生する前記スタートパルスは、電源電圧VD4によって動作するレベルシフタ3bに対して走査選択信号として順に供給される。

【0034】

このレベルシフタ3bによって所定のレベルに変換された走査選択信号は、図2に示した表示パネル1の各走査線n1,n2,……を介して走査トランジスタTr1のゲートに対して順次ゲートオン電圧、すなわち図6に(g)として示すタイミングでゲート制御信号を供給するように作用する。

【0035】

したがってアドレッシング時において、表示パネル1に配列された各走査線n1,n2,……には、前記したように順次ゲートオン電圧が供給されると共に、これに同期して各データ線m1,m2,……には順に1ラインごとの映像データが供給される。これにより、表示パネル1における各画素には個々に映像データが書き込まれ、表示パネルは前記映像データに応じて発光制御を受ける。これにより前記表示パネル1には前記映像データに基づく映像が再現される。

【0036】

図3に戻り、前記データドライバ2におけるシフトレジスタ2aには、符号6で示す異常検知手段が接続されている。すなわち、この実施の形態においては異常検知手段6にはシフトレジスタ2aにおける最終段の出力が供給されるように構成されており、これは異常検知手段6に具備された第3のラッチ回路6aに供給されるように構成されている。また異常検知手段6には制御回路6bが具備され、この制御回路6bからの制御信号によって、前記第3のラッチ回路6aはシフトレジスタ2aの最終段からの出力をラッチするように構成されている。

【0037】

そして、第3のラッチ回路6aの出力はインバータ6cを介して、制御信号調整手段4aに供給されるように構成されている。なお、制御信号調整手段4aは、この実施の形態においては前記したコントローラ4内に具備されている。

【0038】

図7は、前記した異常検知手段6の動作を説明するタイミングチャートであり、図7(a)は前記データドライバ2におけるシフトレジスタ2aの初段に入力されるスタートパルス、すなわち図5に(b)として示したスタートパルスである。また図7(b)はシフトレジスタ2aの最終段において出力される前記スタートパルスであり、換言すれば前記異常検知手段6における第3のラッチ回路6aに供給されるスタートパルスである。すなわち、前記スタートパルスは図7(a)から(b)に矢印で示したように、シフトレジスタ2aの初段から最終段に転送される時間に対応した遅れが常に発生する。

【0039】

ここで、動作環境(例えば低温時)の影響を受けて、データドライバ2におけるシフトレジスタ2aにおけるいずれかのレジスタ回路がレジスタ動作(ラッチ動作)をしなかった場合においては、予め定められたタイミング、すなわち前記した遅れを持ったタイミングにおいて、異常検知手段6に対して前記スタートパルスが到達しないことになる。なお、図7(b)に示す破線は前記スタートパルスが到達しない状態を示している。

【0040】

前記スタートパルスが通常のタイミングにおいて異常検知手段6に到達したか否かを検証するために、前記制御回路6bからは前記第3のラッチ回路6aに対して前記した遅れを持ったタイミングにおいて、ラッチ動作をさせるための制御信号が出力されるように構成されている。すなわち、前記制御回路6bは前記コントローラ4におけるスタート信号の発生タイミングに同期し、所定の遅延をもって前記第3のラッチ回路6aに対して制御信号を出力するように構成されている。

【0041】

ここで、図7(b)に破線で示すように異常検知手段6に対して前記スタートパルスが到達しない場合には、前記第3のラッチ回路6aはスタートパルスをラッチすることはできず、したがって第3のラッチ回路6aの出力は発生しない(Lレベルになされる)。この状態はインバータ6cによって図7(c)に示すようにレベル反転され、異常検知信号として出力される。そして、前記異常検知信号は前記した制御信号調整手段4aに供給される。

【0042】

図7(c)に示す異常検知信号を受けた制御信号調整手段4aは、コントローラ4からデータドライバ2のシフトレジスタ2aに供給する制御信号としてのクロック信号の形態を、前記した低温時においても確実にシフトレジスタ2aが動作し得るように可変調整する動作を実行する。これには、前記制御信号としてのクロック信号の周波数、またクロック信号の振幅のうちの少なくとも一方を可変調整する手段を採用することができる。

【0043】

図8は前記した異常検知手段6より異常検知信号を受けた場合においてなし得るクロック信号の周波数を低下させる具体例を示すものである。すなわち、前記した制御信号調整手段4aは前記した異常検知信号を受けた場合において、コントローラ4よりシフトレジスタ2aに供給するクロック信号を図8に示す分周手段を介してクロック信号の周波数を変更(低下)させる動作を実行する。

【0044】

図9は、図8に示すクロック信号の分周手段の動作を説明する真理値表を示すものである。これによると、図10(a)として示すクロック信号は図10(b)として示すクロック信号に変換されてデータドライバ2のシフトレジスタ2aに供給される。すなわち、シフトレジスタ2aは通常よりも若干低い周波数のクロック信号によりシフト動作がなされるため、たとえ低温時においてもシフトレジスタ2aの動作の信頼性を上げることができる。

【0045】

なお、図8に示す分周手段の出力を反転させるインバータをさらに付加した場合には、図11に示すように(a)として示すクロック信号を(b)として示すクロック信号に変換することができる。このように、図11(b)に示すクロック信号用いても、低温時におけるシフトレジスタ2aの動作の信頼性を上げることができる。

【0046】

以上説明したように、コントローラ4よりデータドライバ2に供給するクロック信号の周波数を低下させた場合においては、実質的にフレームレートが低下して、いわゆるコマ抜き状態になされるものの、映像信号をリアルタイムに表示させることは可能である。なお、図8に示す回路構成に代えてPLL回路を用い、前記した異常検知手段6より異常検知信号を受けた場合においては、前記PLL回路によってクロック信号の周波数を変更させる動作を実行するようにしてもよい。

【0047】

以上の説明はシフトレジスタ2aの動作の信頼性を上げるために、コントローラ4よりデータドライバ2に供給するクロック信号の周波数を変更する例を示したものであるが、例えばコントローラ4よりデータドライバ2に供給するクロック信号の振幅を上昇させるように制御することでも、低温時においてシフトレジスタ2aが動作不能となるのを救済することができる。

【0048】

この場合においては、コントローラ4に図示せぬレベルシフタを具備し、前記異常検知手段6より異常検知信号を受けた時、データドライバ2に供給される前記クロック信号の振幅を前記レベルシフタにより上昇させるように制御する。この結果、図12(a)に示すように、定常時においてコントローラ4よりデータドライバ2のシフトレジスタ2aに供給されるクロック信号の振幅V1に対して、図12(b)に示すようにさらに大きな振幅V2を有するクロック信号をシフトレジスタ2aに供給することで、前記した低温時においてシフトレジスタ2aが動作不能となるのを救済することができる。

【0049】

また、前記したような対策に加え、前記異常検知手段からの異常検知信号を受けて、前記データドライバ回路に供給する電源電圧値を可変調整する電源電圧調整手段がさらに具備されていることが望ましい。すなわち、図3に示す構成においてはVD1(例えば3V)およびVD2(例えば5V)の電源電圧が用意され、これを選択してデータドライバ2に供給することができる電源電圧調整手段8が備えられている。

【0050】

ここで、前記したデータドライバ2を構成するシフトレジスタ2aにおいても、また第1および第2のラッチ回路2b,2cにおいても、例えばFETによりフリップフロップ回路が構成されている。前記フリップフロップ回路を構成するFETは、例えば低温時においては動作速度が低下しシフトレジスタ2a、第1および第2のラッチ回路2b,2cが誤動作する要因となる。このような問題に対処するには、各フリップフロップ回路の電源電圧を上昇させることが効果的である。

【0051】

そこで、前記異常検知手段6からの異常検知信号を受けた制御信号調整手段4aは、前記電源電圧調整手段8を駆動し、データドライバ2における通常動作時のVD1から、より高い電源電圧のVD2に切り替えるように動作させる。これにより、フリップフロップ回路で構成される前記シフトレジスタ2a、第1および第2のラッチ回路2b,2cの動作の信頼性を向上させることができる。

【0052】

以上の説明は、図3に示すデータドライバ2が、特に低温時において動作不能となる状態を救済する手段を説明するものであるが、これと同様に図4に示す走査ドライバ3においても同様の手段を適用することができる。すなわち、図4に基づいてすでに説明したように走査ドライバ3においてもシフトレジスタ3aが具備されており、これも同様に特に低温時において動作不能となる場合が発生する。

【0053】

この様な状態となるのを阻止するために、図4に示す実施の形態においても異常検知手段6および制御信号調整手段4aが具備されている。この異常検知手段6および制御信号調整手段4aは、図3に基づいて説明した構成と同一であり、したがってその説明は省略する。

【0054】

そして、異常検知手段6より異常検出信号が出力された場合においては、制御信号調整手段4aは、図10または図11に示したように、制御信号としてのクロック信号(走査シフトクロック)の周波数を低下させる手段、さらに図12に示したように、制御信号としてのクロック信号の振幅を増大させる手段を適宜採用するように動作する。

【0055】

さらに、図4に示す実施の形態に示すように、前記異常検知手段6からの異常検知信号を受けて、前記走査ドライバ3に供給する電源電圧値を可変調整する電源電圧調整手段8を備え、電源電圧VD1,VD2が選択できるように構成されていることが望ましい。これを具備することにより、図3に基づいてすでに説明した作用効果と同様の作用効果を享受することができる。

【0056】

図13は、コントローラ4とデータドライバ2に加えて、異常検知手段7と制御信号調整手段4aとを備えたこの発明にかかる第3の実施の形態を示したものである。この図13に示す実施の形態においては、図3に示した異常検知手段6の構成に代えて、カウンタ7aと判定回路7bからなる異常検知手段7が採用されており、他の構成は同一である。したがって、同一部分の説明は割愛する。

【0057】

この図13に示す異常検知手段7においては、データドライバ2におけるシフトレジスタ2aの初段に順次入力されるスタート信号が、前記シフトレジスタの最終段に転送される数を所定の期間にわたって計測する計測手段を構成している。すなわち、カウンタ7aはシフトレジスタ2aの最終段に転送されるスタート信号の数を計測する機能を有し、判定回路7bは前記カウンタ7aにより計測された前記スタート信号の数を予め定められた所定値と比較するように機能する。

【0058】

ここで、前記カウンタ7aと判定回路7bとは、所定の周期をもって計測動作を繰り返すように構成されており、判定回路7bはその所定の周期(期間中)におけるスタート信号の数が前記した予め定められた所定値に達するか否かを判定するように作用する。

【0059】

図15は、その判定動作を説明するものであり、(a)はデータドライバ2におけるシフトレジスタ2aの最終段に到達するスタート信号の様子を示している。このスタート信号は、シフトレジスタ2aが正常状態であれは、一定の周期をもって順次カウンタ7aに到来することになるが、シフトレジスタ2aがその一部で動作不能となっている場合には、図15(a)に破線で示すようにスタート信号は到来せず、したがって、カウンタ7aはこれをカウントすることはできない。

【0060】

そして、前記した所定の周期(期間中)におけるスタート信号の数が、予め定められた所定値に達しない場合には、判定回路7bは図15(b)に示すように異常検知信号を出力する。前記異常検知信号を受けた制御信号調整手段4aは、すでに説明した図3に基づいて説明した例と同様の制御信号調整動作を実行する。

【0061】

また、望ましくはこれに加えて、前記データドライバ回路に供給する電源電圧値を可変調整する電源電圧調整手段8を制御し、データドライバ2に供給する電源電圧を上昇させるように動作させる。したがって、図13に示した実施の形態においても、図3に示した構成と同様の作用効果を得ることができる。

【0062】

図14は、コントローラ4と走査ドライバ3に加えて、異常検知手段7と制御信号調整手段4aとを備えたこの発明にかかる第4の実施の形態を示したものである。この図14に示す実施の形態においても、図4に示した異常検知手段6の構成に代えて、カウンタ7aと判定回路7bからなる異常検知手段7が採用されており、他の構成は同一である。

【0063】

また、カウンタ7aと判定回路7bからなる異常検知手段7の動作は、図13および図15に基づいて説明した異常検知手段7と同様である。したがって、図14に示した実施の形態においても、図4に示した構成と同様の作用効果を得ることができる。

【0064】

なお、以上説明した実施の形態においては、シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの最終段に転送されないことを検知した場合に、異常検知手段より異常検知信号を出力するように構成されている。しかしながら、転送されるパルス信号の抽出点はシフトレジスタの最終段に限られることはなく、前記シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの予め定められた転送段(これは前記最終段も含む)に転送されないことを検知した場合に、前記異常検知信号を出力するように構成されていてもよい。

【0065】

また、以上説明した実施の形態においては、有機EL素子を画素に備えた表示パネルを用いた例を示しているが、これは他の表示画素を配列した表示パネルの駆動装置にも適用することができる。さらに、前記した説明においては、特に低温状態においてシフトレジスタが動作不能になる例を挙げているが、逆に高温状態において同様の不具合が発生する場合においても、効果的にこれを救済することができる。

【図面の簡単な説明】

【0066】

【図1】従来の表示パネルの駆動装置における基本構成を示したブロック図である。

【図2】図1に示す表示パネルに配列された画素部の構成例を示した結線図である。

【図3】この発明にかかる駆動装置の第1の実施の形態を示したブロック図である。

【図4】同じく第2の実施の形態を示したブロック図である。

【図5】データドライバに供給される各信号のタイミング図である。

【図6】走査ドライバに供給される各信号のタイミング図である。

【図7】図3および図4に示す実施の形態において採用された異常検知手段の動作を説明するタイミング図である。

【図8】図3および図4に示す実施の形態において採用された制御信号調整手段の一例を示すブロック図である。

【図9】図8に示すブロック図における動作を説明するための真理値表である。

【図10】制御信号調整手段により調整されるクロック信号の一例を示した波形図である。

【図11】同じくクロック信号の他の例を示した波形図である。

【図12】同じくクロック信号のさらに他の例を示した波形図である。

【図13】この発明にかかる駆動装置の第3の実施の形態を示したブロック図である。

【図14】同じく第4の実施の形態を示したブロック図である。

【図15】図13および図14に示す実施の形態において採用された異常検知手段の動作を説明するタイミング図である。

【符号の説明】

【0067】

1 表示パネル

2 データドライバ

2a シフトレジスタ

2b 第1ラッチ回路

2c 第2ラッチ回路

2d レベルシフタ

3 走査ドライバ

3a シフトレジスタ

3b レベルシフタ

4 コントローラ

4a 制御信号調整手段

6 異常検知手段

6a ラッチ回路

6b 制御回路

6c インバータ

7 異常検知手段

7a カウンタ

7b 判定回路

8 電源電圧調整手段

【特許請求の範囲】

【請求項1】

複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動装置であって、

前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知して異常検知信号を出力する異常検知手段と、前記異常検知手段からの異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号を調整する制御信号調整手段とを具備したことを特徴とする表示パネルの駆動装置。

【請求項2】

前記制御信号調整手段は、前記異常検知手段からの異常検知信号を受けて前記制御信号の周波数、振幅のうちの少なくとも一方を可変調整するように構成されていることを特徴とする請求項1に記載された表示パネルの駆動装置。

【請求項3】

前記異常検知手段からの異常検知信号を受けて、前記ドライバ回路に供給する電源電圧値を可変調整する電源電圧調整手段がさらに具備されていることを特徴とする請求項2に記載された表示パネルの駆動装置。

【請求項4】

前記ドライバ回路には、前記制御信号を受けてパルス信号を順次転送出力するシフトレジスタが備えられ、前記異常検知手段は、前記シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送されないことを検知した場合に、前記異常検知信号を出力するように構成されていることを特徴とする請求項1ないし請求項3のいずれか1項に記載された表示パネルの駆動装置。

【請求項5】

前記異常検知手段には、前記シフトレジスタの予め定められた転送段に転送される前記パルス信号をラッチするラッチ回路と、前記ラッチ回路を所定のタイミングでラッチ動作させる制御回路とが具備されていることを特徴とする請求項4に記載された表示パネルの駆動装置。

【請求項6】

前記異常検知手段には、前記シフトレジスタの初段に順次入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送される数を所定の期間にわたって計測する計測手段が具備され、前記計測手段の計測結果に応じて前記異常検知信号を出力するように構成されていることを特徴とする請求項4に記載された表示パネルの駆動装置。

【請求項7】

前記異常検知手段は、所定の周期をもって前記計測手段を動作させるように構成されていることを特徴とする請求項6に記載された表示パネルの駆動装置。

【請求項8】

前記異常検知手段には、前記シフトレジスタの予め定められた転送段に転送されるパルス信号の数を計測するカウンタと、当該カウンタにより計測された前記パルス信号数を予め定められた所定値と比較することにより、前記異常検知信号を出力する判定手段とが備えられていることを特徴とする請求項6または請求項7に記載された表示パネルの駆動装置。

【請求項9】

前記制御信号が、前記シフトレジスタの転送動作を実行するクロック信号であることを特徴とする請求項1ないし請求項8のいずれか1項に記載された表示パネルの駆動装置。

【請求項10】

複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動方法であって、

前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知した場合に異常検知信号を出力するとともに、前記異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号の周波数、振幅のうちの少なくとも一方を可変調整する動作を実行することを特徴とする表示パネルの駆動方法。

【請求項11】

前記異常検知信号を受けて、前記ドライバ回路に供給する電源電圧値をさらに可変調整する動作を実行することを特徴とする請求項10に記載された表示パネルの駆動方法。

【請求項12】

前記ドライバ回路には、前記制御信号を受けてパルス信号を順次転送出力するシフトレジスタが備えられ、前記シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送されないことを検知した場合に、前記異常検知信号を出力する動作を実行することを特徴とする請求項10または請求項11に記載された表示パネルの駆動方法。

【請求項13】

前記シフトレジスタの予め定められた転送段に転送される前記パルス信号を、所定のタイミングでラッチする動作を実行することを特徴とする請求項12に記載された表示パネルの駆動方法。

【請求項14】

前記シフトレジスタの初段に順次入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送される数を所定の期間にわたって計測し、計測結果に応じて前記異常検知信号を出力する動作を実行することを特徴とする請求項12に記載された表示パネルの駆動方法。

【請求項15】

前記シフトレジスタの予め定められた転送段に転送される前記パルス信号の数を所定の期間にわたって計測する動作を、所定の周期をもって実行させることを特徴とする請求項14に記載された表示パネルの駆動方法。

【請求項16】

前記シフトレジスタの予め定められた転送段に転送されるパルス信号の数をカウンタにより計測し、当該カウンタにより計測した前記パルス信号の数と、予め定められた所定値との比較により、前記異常検知信号を出力する動作を実行することを特徴とする請求項14または請求項15に記載された表示パネルの駆動方法。

【請求項17】

前記制御信号が、前記シフトレジスタの転送動作を実行するクロック信号であることを特徴とする請求項10ないし請求項16のいずれか1項に記載された表示パネルの駆動方法。

【請求項1】

複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動装置であって、

前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知して異常検知信号を出力する異常検知手段と、前記異常検知手段からの異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号を調整する制御信号調整手段とを具備したことを特徴とする表示パネルの駆動装置。

【請求項2】

前記制御信号調整手段は、前記異常検知手段からの異常検知信号を受けて前記制御信号の周波数、振幅のうちの少なくとも一方を可変調整するように構成されていることを特徴とする請求項1に記載された表示パネルの駆動装置。

【請求項3】

前記異常検知手段からの異常検知信号を受けて、前記ドライバ回路に供給する電源電圧値を可変調整する電源電圧調整手段がさらに具備されていることを特徴とする請求項2に記載された表示パネルの駆動装置。

【請求項4】

前記ドライバ回路には、前記制御信号を受けてパルス信号を順次転送出力するシフトレジスタが備えられ、前記異常検知手段は、前記シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送されないことを検知した場合に、前記異常検知信号を出力するように構成されていることを特徴とする請求項1ないし請求項3のいずれか1項に記載された表示パネルの駆動装置。

【請求項5】

前記異常検知手段には、前記シフトレジスタの予め定められた転送段に転送される前記パルス信号をラッチするラッチ回路と、前記ラッチ回路を所定のタイミングでラッチ動作させる制御回路とが具備されていることを特徴とする請求項4に記載された表示パネルの駆動装置。

【請求項6】

前記異常検知手段には、前記シフトレジスタの初段に順次入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送される数を所定の期間にわたって計測する計測手段が具備され、前記計測手段の計測結果に応じて前記異常検知信号を出力するように構成されていることを特徴とする請求項4に記載された表示パネルの駆動装置。

【請求項7】

前記異常検知手段は、所定の周期をもって前記計測手段を動作させるように構成されていることを特徴とする請求項6に記載された表示パネルの駆動装置。

【請求項8】

前記異常検知手段には、前記シフトレジスタの予め定められた転送段に転送されるパルス信号の数を計測するカウンタと、当該カウンタにより計測された前記パルス信号数を予め定められた所定値と比較することにより、前記異常検知信号を出力する判定手段とが備えられていることを特徴とする請求項6または請求項7に記載された表示パネルの駆動装置。

【請求項9】

前記制御信号が、前記シフトレジスタの転送動作を実行するクロック信号であることを特徴とする請求項1ないし請求項8のいずれか1項に記載された表示パネルの駆動装置。

【請求項10】

複数のデータ線および複数の走査線の各交差位置に、表示画素を配置してなる表示パネルと、前記表示パネルにおける各データ線および各走査線を介して、前記各画素を選択的に表示駆動するドライバ回路とを備えた表示パネルの駆動方法であって、

前記ドライバ回路が正常に動作しているか否かを監視し、正常に動作していないことを検知した場合に異常検知信号を出力するとともに、前記異常検知信号を受けて、前記ドライバ回路の動作を制御する制御信号の周波数、振幅のうちの少なくとも一方を可変調整する動作を実行することを特徴とする表示パネルの駆動方法。

【請求項11】

前記異常検知信号を受けて、前記ドライバ回路に供給する電源電圧値をさらに可変調整する動作を実行することを特徴とする請求項10に記載された表示パネルの駆動方法。

【請求項12】

前記ドライバ回路には、前記制御信号を受けてパルス信号を順次転送出力するシフトレジスタが備えられ、前記シフトレジスタの初段に入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送されないことを検知した場合に、前記異常検知信号を出力する動作を実行することを特徴とする請求項10または請求項11に記載された表示パネルの駆動方法。

【請求項13】

前記シフトレジスタの予め定められた転送段に転送される前記パルス信号を、所定のタイミングでラッチする動作を実行することを特徴とする請求項12に記載された表示パネルの駆動方法。

【請求項14】

前記シフトレジスタの初段に順次入力されるパルス信号が、前記シフトレジスタの予め定められた転送段に転送される数を所定の期間にわたって計測し、計測結果に応じて前記異常検知信号を出力する動作を実行することを特徴とする請求項12に記載された表示パネルの駆動方法。

【請求項15】

前記シフトレジスタの予め定められた転送段に転送される前記パルス信号の数を所定の期間にわたって計測する動作を、所定の周期をもって実行させることを特徴とする請求項14に記載された表示パネルの駆動方法。

【請求項16】

前記シフトレジスタの予め定められた転送段に転送されるパルス信号の数をカウンタにより計測し、当該カウンタにより計測した前記パルス信号の数と、予め定められた所定値との比較により、前記異常検知信号を出力する動作を実行することを特徴とする請求項14または請求項15に記載された表示パネルの駆動方法。

【請求項17】

前記制御信号が、前記シフトレジスタの転送動作を実行するクロック信号であることを特徴とする請求項10ないし請求項16のいずれか1項に記載された表示パネルの駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2007−57637(P2007−57637A)

【公開日】平成19年3月8日(2007.3.8)

【国際特許分類】

【出願番号】特願2005−240674(P2005−240674)

【出願日】平成17年8月23日(2005.8.23)

【出願人】(000221926)東北パイオニア株式会社 (474)

【Fターム(参考)】

【公開日】平成19年3月8日(2007.3.8)

【国際特許分類】

【出願日】平成17年8月23日(2005.8.23)

【出願人】(000221926)東北パイオニア株式会社 (474)

【Fターム(参考)】

[ Back to top ]