表示装置、表示装置の駆動方法、及び、電子機器

【課題】表示階調数の更なる増加を可能にした表示装置、表示装置の駆動方法、及び、当該表示装置を有する電子機器を提供する。

【解決手段】画素の内部に記憶機能を有する表示装置において、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示を行うことで、表示階調数の更なる増加を図る。そして、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心を一致させることで、表示画像の揺らぎをなくすようにする。

【解決手段】画素の内部に記憶機能を有する表示装置において、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示を行うことで、表示階調数の更なる増加を図る。そして、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心を一致させることで、表示画像の揺らぎをなくすようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、表示装置、表示装置の駆動方法、及び、電子機器に関する。

【背景技術】

【0002】

画素の内部に記憶機能を有する表示装置において、解像度の制約により、画素に内蔵する回路規模が限られるため表示階調数が低下する。このため、解像度を犠牲にして見た目の表示階調数を増やすディザリング(ディザ法)と呼ばれる技法が用いられている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−38968号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかし、ディザリングと呼ばれる技法を用いても階調数が不足し、表示画像に粗さがあるため、表示特性の向上にも限界がある。従って、表示特性のより向上を図るために、表示階調数の更なる増加が望まれている。

【0005】

そこで、本開示は、表示階調数の更なる増加を可能にした表示装置、表示装置の駆動方法、及び、当該表示装置を有する電子機器を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するために、本開示は、

画素の内部に記憶機能を有する表示装置において、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示を行い、

階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる

構成を採っている。この表示装置は、各種の電子機器において、その表示部として用いて好適なものである。

【0007】

上記構成の表示装置、または、当該表示装置を有する電子機器において、サブフレーム単位での時分割駆動、即ち、FRC(Frame Rate Control)駆動にて表示を行うことで、フレーム単位での駆動の場合に比べて表示階調数を増加させることができる。ここで、「FRC駆動」とは、異なる複数の階調輝度をサブフレーム単位で高速に切り替えることで人間の目の残像特性(残像効果)を利用し、複数の階調輝度の中間調輝度を表示させる駆動法である。そして、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことで、表示画像に揺らぎが生じない。

【発明の効果】

【0008】

本開示によれば、表示階調数を更に増加させることができるとともに、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる。

【図面の簡単な説明】

【0009】

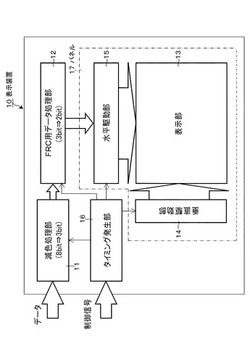

【図1】本開示の実施形態に係る表示装置のシステム構成の概略を示すブロック図である。

【図2】パネルに入力される8ビットのデータ(A)、減色処理部での減色処理後の3ビットのデータ(B)、及び、FRC用データ処理部での変換処理後、MIP方式の画素にサブフレーム単位で書き込まれる2ビットのデータ(C)のタイミング関係を示すタイミングチャートである。

【図3】画素の基本的な画素回路の一例を示す回路図である。

【図4】MIP方式の画素の回路構成の一例を示すブロック図である。

【図5】MIP方式の画素の動作説明に供するタイミングチャートである。

【図6】MIPの画素の具体的な回路構成の一例を示す回路図である。

【図7】面積階調法における画素分割についての説明図である。

【図8】3分割画素構造における3つの副画素電極と2組の駆動回路との対応関係を示す回路図である。

【図9】1フレームの全画面表示周期、部分表示のサブフレーム周期、FRC駆動のサブフレーム数、及び、人の目のちらつきの限界周期との間の関係を模式的に示す図である。

【図10】2ビット面積階調の場合と2ビット面積階調+1ビットFRC駆動の場合についての説明図である。

【図11】実施例1に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図12】実施例2に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図13】実施例3に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図14】実施例4に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図15】実施例2の場合の、1フレームの全画面表示周期、単位サブフレーム内での表示階調数、及び、部分表示のサブフレーム周期と全表示階調数との間の関係を示す図である。

【図16】サブフレーム時間に対する重み付けの具体例を示す図である。

【図17】図16に示した、サブフレーム時間に対する重み付けの具体例(A)〜(F)の各々における表示階調数の一覧を示す図である。

【発明を実施するための形態】

【0010】

以下、本開示の技術を実施するための形態(以下、「実施形態」と記述する)について図面を用いて詳細に説明する。本開示は実施形態に限定されるものではなく、実施形態における種々の数値などは例示である。以下の説明において、同一要素又は同一機能を有する要素には同一符号を用いることとし、重複する説明は省略する。尚、説明は以下の順序で行う。

1.本開示の表示装置及び表示装置の駆動方法、全般に関する説明

2.実施形態に係る表示装置及び表示装置の駆動方法

2−1.システム構成

2−2.画素回路

2−3.MIP方式

2−4.面積階調法

2−5.実施形態の特徴部分

3.電子機器

4.本開示の構成

【0011】

<1.本開示の表示装置及び表示装置の駆動方法、全般に関する説明>

本開示の表示装置は、画素の内部に記憶機能を持つ表示装置である。この種の表示装置としては、例えば、画素内にデータを記憶可能なメモリ部を有する、所謂、MIP(Memory In Pixel)方式の表示装置を例示することができる。

【0012】

表示装置としては、液晶表示装置、エレクトロルミネッセンス表示装置、プラズマ表示装置などといった、周知の表示装置を用いることができる。液晶表示装置の場合には、画素にメモリ性液晶を用いることで、画素に記憶機能を持つ表示装置とすることができる。表示装置は、モノクロ表示対応の表示装置であってもよいし、カラー表示対応の表示装置であってもよい。

【0013】

画素に記憶機能を有する表示装置は、画素にデータを記憶できることで、モード切替えスイッチによってアナログ表示モードによる表示と、メモリ表示モードによる表示とを実現できる。ここで、「アナログ表示モード」とは、画素の階調をアナログ的に表示する表示モードである。また、「メモリ表示モード」とは、画素に記憶されている2値の情報(論理“1”/論理“0”)に基づいて、画素の階調をデジタル的に表示する表示モードである。

【0014】

画素に記憶機能を有する表示装置、例えば、MIP方式の表示装置にあっては、解像度の制約により、画素に内蔵する回路規模が限られるため表示階調数が低下する傾向にある。そのため、MIP方式の表示装置では、解像度を犠牲にして見た目の表示階調数を増やすために、周知の誤差拡散法やディザ法などの技法が減色処理に用いられる。

【0015】

そして、表示階調数の更なる増加を図るために、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示駆動を行う構成とする。前にも述べたように、「FRC駆動」とは、異なる複数の階調輝度をサブフレーム単位で高速に切り替えることで人間の目の残像特性(残像効果)を利用し、複数の階調輝度の中間調輝度を表示させる駆動法である。

【0016】

このサブフレーム単位での時分割駆動、即ち、FRC駆動を行うことで、フレーム単位での駆動の場合に比べて、表示階調数の増加を図ることができる。そして、FRC駆動の表示装置において、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う構成とする。

【0017】

ここで、「一致」とは、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とが厳密に一致する場合の他、実質的に一致する場合も含む。設計上あるいは製造上生ずる種々のばらつきの存在は許容される。また、複数のサブフレーム間で時間的に積分することによって、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とが実質的に一致する場合も含むものとする。

【0018】

このように、FRC駆動の表示装置において、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことで、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる。

【0019】

MIP方式の表示装置は、画素毎に1ビットで2階調しか表現を行うことができない。そのために、画素の駆動に当たっては、階調表現方式として、面積階調法を用いる構成とするのが好ましい。ここで、「面積階調法」とは、面積比を20 ,21 ,22 ,・・・,2N-1 、という具合に重み付けしたN個の副画素電極で2N 個の階調を表現する階調表現方式である。この面積階調法は、例えば、画素回路を構成するTFT(Thin Film Transistor:薄膜トランジスタ)の特性ばらつきによる画質の不均一性を改善する等の目的で採用される。

【0020】

<2.実施形態に係る表示装置及び表示装置の駆動方法>

[2−1.システム構成]

図1は、本開示の実施形態に係る表示装置のシステム構成の概略を示すブロック図である。本実施形態に係る表示装置は、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示を行う構成を採る。また、本実施形態に係る表示装置の画素は、画素毎にメモリ部を有するMIP方式の画素である。

【0021】

図1に示すように、本実施形態に係る表示装置10は、減色処理部11、FRC用データ処理部12、表示部13、垂直駆動部14、水平駆動部15、及び、タイミング発生部16を有する構成となっている。そして、これらの構成要素(11〜16)の内、表示部13、垂直駆動部14、及び、水平駆動部15が、パネル(基板)17上に実装されている。

【0022】

表示装置10には、パネル外部のホスト装置(図示せず)からデータ及び制御信号が入力される。表示装置10に入力されるデータは、表示部13に画像を表示するための例えば8ビットのデータであり、減色処理部11に与えられる。表示装置10に入力される制御信号は、本表示装置10を全体的に制御するための種々の制御情報を含む信号であり、タイミング発生部16に与えられる。

【0023】

タイミング発生部16は、制御信号が入力されると、当該制御信号に基づいて減色処理部11、FRC用データ処理部12、垂直駆動部14、及び、水平駆動部15に対して種々のタイミング信号を与える。すなわち、減色処理部11、FRC用データ処理部12、垂直駆動部14、及び、水平駆動部15は、タイミング発生部16から与えられる、制御信号に基づくタイミング信号による駆動の下に各種の動作を行う。

【0024】

減色処理部11は、タイミング発生部16から与えられるタイミング信号による駆動の下に、外部のホスト装置から入力される8ビットのデータを例えば3ビットのデータに変換する減色処理を行う。この減色処理には、例えば、周知の誤差拡散法が用いられる。但し、減色処理の技法としては、誤差拡散法に限られるものではなく、周知のディザ法などを用いることもできる。

【0025】

減色処理において、原画に対して2ビットの誤差拡散では、画像の粗さが目立つ。これに対して、3ビットの誤差拡散とすることにより、画像の粗さを大幅に改善することができる。減色処理部11で減色処理された3ビットのデータは、FRC用データ処理部12に与えられる。

【0026】

FRC用データ処理部12は、減色処理部11から与えられる3ビットのデータを一時的に格納し、タイミング発生部16から与えられるタイミング信号による駆動の下に、3ビットのデータをFRC変換する。このFRC変換では、FRC駆動を行うに当たって、減色処理された3ビットのデータを当該データよりも少ないビット数のデータ、例えば、2ビットのデータにサブフレーム単位で変換する処理が行われる。

【0027】

上記の構成の本実施形態に係る表示装置10において、FRC用データ処理部12、垂直駆動部14、水平駆動部15、及び、タイミング発生部16は、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を構成している。

【0028】

図2に、パネル17に入力される8ビットのデータ(A)、減色処理部11での減色処理後の3ビットのデータ(B)、及び、FRC用データ処理部12での変換処理後、MIP方式の画素にサブフレーム単位で書き込まれる2ビットのデータ(C)のタイミング関係を示す。図2において、Toは1フレームの全画面表示周期である。

【0029】

図2には、FRC駆動による描画の概念図をも併せて示している。ここでは、理解を容易にするために、「A」という文字を描画する場合を例に挙げている。パネル17には外部のホスト装置から「A」という文字の中間調の8ビットのデータが入力される。この8ビットのデータを3ビットのデータに減色処理する。そして、第1サブフレームでは濃い目の画像を描き、第2サブフレームで淡目の画像を描くことで、1フレームトータルで元の(原画の)中間調の階調を表示することができる。

【0030】

図1に説明を戻す。表示部13は、画素が行列状に2次元配置されて成り、当該画素の行列状配置に対して画素行毎に走査線が配線され、画素列毎に信号線が配線された構成となっている。この表示部13の具体的な構成については後述する。

【0031】

垂直駆動部14は、表示部13の各画素を画素行単位で選択走査する。垂直駆動部14の回路構成は特に限定するものではない。垂直駆動部14は、シフトレジスタや論理回路などによって構成したり、あるいは、アドレスデコーダを用いて構成したりすることができる。

【0032】

水平駆動部15は、垂直駆動部14によって選択された画素行の各画素に対して、FRC用データ処理部12から与えられるデータを信号線を通して供給する。水平駆動部15の回路構成は、特に限定するものではない。水平駆動部15は、垂直駆動部14によって選択された画素行の各画素に対してデータを、1行分同時に供給する構成のものであってもよいし、画素単位で順次供給する構成のものであってよいし、あるいは、複数の画素単位で供給する構成のものであってよい。

【0033】

[2−2.画素回路]

次いで、表示部13を構成する画素の基本的な画素回路について、図3を用いて説明する。ここでは、表示装置10が液晶表示装置から成る場合を例に挙げて説明するものとする。

【0034】

図3に示すように、複数の信号線31(311,312,313,・・・)と、複数の走査線32(321,322,323,・・・)とが交差するように配線され、その交差部に画素20が配されている。信号線31(311,312,313,・・・)の各一端は、水平駆動部15の各列に対応した出力端に接続されている。複数の走査線32(321,322,323,・・・)の各一端は、垂直駆動部14の各行に対応した出力端に接続されている。

【0035】

画素20は、例えば、薄膜トランジスタ(TFT)から成る画素トランジスタ21、液晶容量22、及び、保持容量23を有する構成となっている。画素トランジスタ21は、ゲート電極が走査線32(321,322,323,・・・)に接続され、一方のソース/ドレイン電極が信号線31(311,312,313,・・・)に接続されている。

【0036】

液晶容量22は、画素電極とこれに対向して形成される対向電極との間で発生する液晶材料の容量成分を意味し、画素電極が画素トランジスタ21の他方のソース/ドレイン電極に接続されている。液晶容量22の対向電極には、直流電圧のコモン電位VCOMが全画素共通に印加される。保持容量23は、一方の電極が液晶容量22の画素電極に、他方の電極が液晶容量22の対向電極にそれぞれ接続されている。

【0037】

上記の画素回路から明らかなように、複数の信号線31(311,312,313,・・・)は、画素20を駆動する信号、即ち、水平駆動部15から出力されるデータを画素列毎に画素20に伝送する配線である。また、複数の走査線32(321,322,323,・・・)は、画素20を行単位で選択する信号、即ち、垂直駆動部14から出力される走査信号を画素行毎に伝送する配線である。

【0038】

[2−3.MIP方式]

本実施形態に係る表示装置10にあっては、画素20としてメモリ機能を有する画素、例えば、画素毎にデータを記憶可能なメモリ部を持つMIP方式の画素を用いている。MIP方式の表示装置の場合、画素20に常に一定電圧がかかることになるために、画素トランジスタ21の光リーク等による経時的な電圧変動によるシェーディングの問題を解消することができる。

【0039】

また、MIP方式の画素20は、データを記憶するメモリ部を画素20内に持ち、モード切換えスイッチ(図示せず)により、アナログ表示モードによる表示と、メモリ表示モードによる表示とを実現できる。ここで、「アナログ表示モード」とは、画素20の階調をアナログ的に表示する表示モードである。また、「メモリ表示モード」とは、画素20内のメモリ部に記憶されている2値情報(論理“1”/論理“0”)に基づいて、画素20の階調をデジタル的に表示する表示モードである。

【0040】

メモリ表示モードの場合、メモリ部に保持されている情報を用いるため、階調を反映した信号電位の書き込み動作を単発実行すれば、常時フレーム周期で実行する必要がない。そのため、メモリ表示モードの場合は、階調を反映した信号電位の書き込み動作を常時フレーム周期で実行する必要があるアナログ表示モードの場合に比べて消費電力が少なくて済む、換言すれば、表示装置の低消費電力化を図ることができる。

【0041】

図4は、MIP方式の画素20の回路構成の一例を示すブロック図である。また、図5に、MIP方式の画素20の動作説明に供するタイミングチャートを示す。

【0042】

図4に示すように、画素20は、液晶容量(液晶セル)22に加えて、3つのスイッチ素子24〜26及びラッチ部27を有するSRAM機能付きの画素構成となっている。

【0043】

スイッチ素子24は、信号線31(図3の信号線311〜313に相当)に一端が接続されている。そして、図3の垂直駆動部14から走査線32を介して走査信号φVが与えられることによってオン(閉)状態となり、図3の水平駆動部15から信号線31を介して供給されるデータSIGを取り込む。ラッチ部27は、互いに逆向きに並列接続されたインバータ271,272によって構成されており、スイッチ素子24によって取り込まれたデータSIGに応じた電位を保持(ラッチ)する。

【0044】

スイッチ素子25,26の各一方の端子には、コモン電圧VCOMと同相の電圧FRP及び

逆相の電圧XFRPが与えられる。スイッチ素子25,26の各他方の端子は共通に接続され、本画素回路の出力ノードNoutとなる。スイッチ素子25,26は、ラッチ部27の保持電位の極性に応じていずれか一方がオン状態となる。これにより、対向電極にコモン電位VCOMが印加されている液晶容量22に対して、同相の電圧FRPまたは逆相の電圧XFRPが画素電極に印加される。

【0045】

図5から明らかなように、ノーマリーブラック(無電圧印加時黒表示)の液晶パネルの場合、ラッチ部27の保持電位が負側極性のときは、液晶容量22の画素電位がコモン電位VCOMと同相になるため黒表示となり、ラッチ部27の保持電位が正側極性のときは、液晶容量22の画素電位がコモン電位VCOMと逆相になるため白表示となる。

【0046】

上述したことから明らかなように、MIP方式の画素20にあっては、ラッチ部27の保持電位の極性に応じてスイッチ素子25,26のいずれか一方がオン状態となることにより、液晶容量22の画素電極に対して、同相の電圧FRPまたは逆相の電圧XFRPが印加される。これにより、画素20には常に一定電圧が印加されることになるためにシェーディングが発生する懸念はない。

【0047】

図6は、画素20の具体的な回路構成の一例を示す回路図であり、図中、図4と対応する部分には同一符号を付して示している。

【0048】

図6において、スイッチ素子24は、例えばNchMOSトランジスタQn10から成る。NchMOSトランジスタQn10は、一方のソース/ドレイン電極が信号線31に接続され、ゲート電極が走査線32に接続されている。

【0049】

スイッチ素子25,26は共に、例えば、NchMOSトランジスタ及びPchMOSトランジスタが並列に接続されてなるトランスファスイッチから成る。具体的には、スイッチ素子25は、NchMOSトランジスタQn11及びPchMOSトランジスタQp11が互いに並列に接続された構成となっている。スイッチ素子26は、NchMOSトランジスタQn12及びPchMOSトランジスタQp12が互いに並列に接続された構成となっている。

【0050】

スイッチ素子25,26は、必ずしも、NchMOSトランジスタ及びPchMOSトランジスタを並列接続して成るトランスファスイッチである必要はない。スイッチ素子25,26を、単一導電型のMOSトランジスタ、即ち、NchMOSトランジスタあるいはPchMOSトランジスタを用いて構成することも可能である。スイッチ素子25,26の共通接続ノードが、本画素回路の出力ノードNoutとなる。

【0051】

インバータ271,272は共に、例えばCMOSインバータから成る。具体的には、インバータ271は、NchMOSトランジスタQn13及びPchMOSトランジスタQp13のゲート電極同士及びドレイン電極同士が共通に接続された構成となっている。インバータ272は、NchMOSトランジスタQn14及びPchMOSトランジスタQp14のゲート電極同士及びドレイン電極同士が共通に接続された構成となっている。

【0052】

上記の回路構成を基本とする画素20が、水平方向および垂直方向に展開されて行列状に配置されることになる。この画素20の行列状配列に対して、画素列毎の信号線31及び画素行毎の走査線32に加えて、同相の電圧FRP、逆相の電圧XFRPを伝送する配線33,34、及び、正側電源電圧VDD、負側電源電圧VSSの電源線35,36が画素列毎に配線されている。

【0053】

上述したように、本実施形態に係る表示装置(即ち、アクティブマトリクス型液晶表示装置)10は、表示データに応じた電位を保持するラッチ部27を有するSRAM機能付き画素(MIP)20が行列状に配置された構成となっている。尚、本実施形態では、画素20に内蔵するメモリ部としてSRAMを用いる場合を例に挙げたが、SRAMは一例に過ぎず、他の構成のメモリ部、例えば、DRAMを用いる構成であってもよい。

【0054】

このMIP方式の表示装置10は、画素20毎に記憶機能(メモリ部)を持つことで、前にも述べたように、モード切換えスイッチによりアナログ表示モードによる表示と、メモリ表示モードによる表示とを実現できる。そして、メモリ表示モードの場合、メモリ部に保持されている画素データを用いて表示を行うことから、階調を反映した信号電位の書き込み動作を単発実行するため常時フレーム周期で実行する必要がなく、表示装置10の消費電力の低減を図ることができる、という利点がある。

【0055】

また、表示画面を部分的に、即ち、表示画面の一部だけを書き換えたい、というニーズがある。この場合、部分的に画素データを書き換えれば良いことになる。表示画面を部分的に書き換える、即ち、画素データを部分的に書き換えると、書き換えを行わない画素についてはデータを転送する必要がなくなる。従って、データ転送量を減らすことができるため、表示装置10の更なる省電力化を図ることができる、という利点もある。

【0056】

[2−4.面積階調法]

ところで、画素内部の記憶機能を有する表示装置、例えば、MIP方式の表示装置の場合、画素20毎に1ビットで2階調しか表現を行うことができない。そこで、本実施形態に係る表示装置10にあっては、MIP方式を採用するに当たって、面積階調法を用いるのが好ましい。

【0057】

具体的には、画素20の表示領域となる画素電極を、面積的に重み付けした複数の画素(副画素)電極に分割する面積階調法を用いる。画素電極としては、透過電極であってもよいし、反射電極であってもよい。そして、ラッチ部27の保持電位によって選択された画素電位を面積的に重み付けした画素電極に通電し、重み付けした面積の組み合わせによって階調表示を行うようにする。

【0058】

ここでは、理解を容易にするために、画素電極(副画素電極)の面積(画素面積)に2:1の重みを付けることによって2ビットで4階調を表現する面積階調法を例に挙げて説明するものとする。

【0059】

画素面積に2:1の重みを付ける構造としては、図7(A)に示すように、画素20の画素電極を面積1の副画素電極201と、当該副画素電極201の2倍の面積(面積2)の副画素電極202とに分割する構造が一般的である。しかし、図7(A)の構造の場合には、1画素の中心(重心)に対する各階調(表示画像)の中心(重心)が揃わない(一致しない)ため、階調表現の点で好ましくない。

【0060】

1画素の中心に対する各階調の中心を揃える構造としては、図7(B)に示すように、面積2の副画素電極204の中心部を例えば矩形形状にくり抜き、そのくり抜いた矩形領域の中心部に面積1の副画素電極203を配置する構造が考えられる。しかし、図7(B)の構造の場合には、副画素電極203の両側に位置する、副画素電極204の連結部204A,204Bの幅が狭いため、副画素電極204全体の反射面積が小さくなるとともに、連結部204A,204Bの辺りの液晶配向が難しい。

【0061】

上述したように、面積階調で、無電界時に液晶分子が基板に対してほぼ垂直になるVA(Vertical Aligned:垂直配向)モードにしようとすると、液晶分子に対する電圧のかかり方が、電極形状や電極サイズなどによって変わるため、良好に液晶配向させることが難しい。また、副画素電極の面積比が反射率比になるとは限らないので階調設計が難しい。反射率は、副画素電極の面積や液晶配向などによって決まる。図7(A)の構造の場合、面積比が1:2であっても電極周辺の長さの比が1:2とはならない。従って、副画素電極の面積比が反射率比になるとは限らない。

【0062】

このような観点からすると、面積階調法を採用するに当たっては、階調の表現性と反射面積の有効活用を考える上で、図7(C)に示すように、画素電極を例えば同じ面積(大きさ)の3つの副画素電極205,206A,206Bに分割する、所謂、3分割の電極構成にするのが望ましい。

【0063】

この3分割の電極構成の場合、中央の副画素電極205を挟む上下2つの副画素電極206A,206Bを組とし、当該組となる2つの副画素電極206A,206Bを同時に駆動することで、中央の副画素電極205との間で画素面積に2:1の重みを付けることができる。また、1画素の中心(重心)に対する各階調の中心(重心)を揃えることができる。

【0064】

しかし、3つの副画素電極205,206A,206Bの各々について駆動回路と電気的にコンタクトを取るとすると、図7(A),(B)の構造に比べて金属配線のコンタクト数が増えるため、画素サイズが大きくなり、高精細化の阻害要因となる。特に、画素20毎にメモリ部を有するMIP方式の画素構成の場合には、図6から明らかなように、1つの画素20内にトランジスタ等の多くの回路構成素子やコンタクト部が存在することになり、レイアウト面積的に余裕がないために、コンタクト部1個が画素サイズに大きく影響を及ぼす。

【0065】

コンタクト数を減らすには、1個の副画素電極205を挟むことによって互いの距離が離れた2つの副画素電極206A,206B同士を電気的に結合する(結線する)画素構造とすれば良い。そして、図8に示すように、1つの駆動回路207Aで1個の副画素電極205を駆動し、他の1つの駆動回路207Bで残りの2つの副画素電極206A,206Bを同時に駆動するようにする。ここで、駆動回路207A,207Bは、図6に示した画素回路に相当する。

【0066】

このように、2つの副画素電極206A,206Bを1つの駆動回路207Aによって駆動するようにすることにより、2つの副画素電極206A,206Bを別々の駆動回路によって駆動する構成を採る場合よりも画素20の回路構成を簡略化できる。

【0067】

尚、ここでは、メモリ機能を有する画素として、画素毎にデータを記憶可能なメモリ部を持つMIP方式の画素を用いるとしたが、これは一例に過ぎない。メモリ機能を有する画素としては、MIP方式の画素の他に、例えば、周知のメモリ性液晶を用いる画素を例示することができる。

【0068】

[2−5.実施形態の特徴部分]

以上に説明したように、内部に記憶機能を持つMIP方式の画素20を有する本実施形態に係る表示装置10は、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示を行うことで、フレーム単位での駆動の場合に比べて表示階調数を増加させることができる。本実施形態に係る表示装置10は更に、面積階調法を採用している。

【0069】

そして、FRC駆動の下で面積階調法を採用する、本実施形態に係る表示装置10にあっては、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことを特徴としている。ここで、「階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させる」とは、換言すれば、1画素の中心と複数のサブフレーム間の各階調の中心とを一致させることである。

【0070】

そして、1画素の中心と複数のサブフレーム間の各階調の中心とを一致させるには、複数のサブフレームの各々において、複数の副画素の中で点灯させる副画素の組合せを階調毎に設定するようにすればよい。このように、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことで、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる。

【0071】

ここで、単位画素当たりの最小単位面積数(即ち、副画素電極の数)をg(自然数)、サブフレーム数をf(2以上の自然数)、副画素の点灯個数をn(=0〜g・f)とすると、面積階調における階調の組合せ数、即ち、全表示階調数Ngsは、一般的には、Ngs=gfCnとなる。

【0072】

しかし、サブフレーム内での同時点灯の画素数が結線されなければならないという制約がある。具体的には、先述したように、2つの副画素電極206A,206B同士を結線する画素構造の場合がこれに相当する。また、1つの画素の中心と階調表示の中心とを一致させる必要がある。このような観点から、表示階調数Nは、実際には、Ngs=階調単位面積数+1=g・f+1となる。その具体的な実施例については後述する。

【0073】

ところで、表示画面の中央部付近に部分的に動画を表示する部分動画表示の場合、表示領域が狭いため、フレーム単位(フレーム周期)で表示を行う通常表示では、表示更新が停止している期間が発生している。この時間を逆に利用して、描画速度はそのままで、高速に画像を更新するFRC駆動を行うと、表示ビット数を増やすことができる。FRC駆動は、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部、即ち、FRC用データ処理部12、垂直駆動部14、水平駆動部15、及び、タイミング発生部16によって実現される。

【0074】

前にも述べたように、FRC駆動は目の残像特性を利用している。従って、人の目のちらつきの限界周期(PAL駆動の場合1/50Hz、NTSC駆動の場合1/60Hz)よりも低いフレーム周期でFRC駆動を行うことが重要となる。

【0075】

一般的に、1フレームの全画面表示周期To、部分表示のサブフレーム周期Tsf、FRC駆動のサブフレーム数Nfrc、及び、人の目のちらつきの限界周期の間に、次の関係が成り立つ条件で駆動しなければならない。その関係とは、人の目のちらつきの限界周期よりも1フレームの全画面表示周期Toが小さく、当該全画面表示周期Toよりも部分表示のサブフレーム周期TsfとFRC駆動のサブフレーム数Nfrcとで決まる合計サブフレーム周期(=Tsf×Nfrc)が小さい関係である。

【0076】

一例として、PAL駆動の場合を考えると、1/50Hzの周期よりも短い周期で画面が構成されている。そして、上記の関係が成り立つ条件での駆動とは、その構成されている1画面(1フレーム)の全画面表示周期Toという時間よりも更に短い時間でサブフレームが構成されていることを意味する。

【0077】

図9に、1フレームの全画面表示周期To、部分表示のサブフレーム周期Tsf、FRC駆動のサブフレーム数Nfrc、及び、人の目のちらつきの限界周期(例えば、PAL駆動を考慮した場合1/50Hz)との間の関係を模式的に示す。このような条件の下でFRC駆動を行うことにより、FRC駆動ビット分の表示階調数が増加する。

【0078】

ここで、具体例として、画素20が3分割の電極構成であり、副画素電極205を挟む上下2つの副画素電極206A,206Bを同時に駆動する画素構造において、2ビット表示の部分表示に対して、1ビットのFRC駆動を行った場合について説明する。この場合は、g=3、f=2であり、Ngs=3×2+1=7となるため7階調表示となる。

【0079】

2ビットの面積階調のみ場合は、1画面を1フレーム周期で構成する。図10(A)に示すように、3つの副画素が全て消灯状態となる0、中央の副画素のみが点灯状態となる1、上下の2つの副画素が点灯状態となる2、3つの副画素が全て点灯状態となる3の計4階調表示となる。

【0080】

これに対して、2ビットの面積階調+1ビットのFRC駆動の場合は、1画面を2個のサブフレーム周期で構成する。そして、第1,第2サブフレームで同じ点灯駆動となる上記の4階調に、図10(B)に示す0.5,1.5,2.5の3階調が加わる。階調0.5では、第1サブフレームで3つの副画素が全て消灯状態となり、第2サブフレームで中央の副画素のみが点灯状態となる。

【0081】

階調1.5では、第1サブフレームで中央の副画素のみが点灯状態となり、第2サブフレームで上下の2つの副画素が点灯状態となる、または、第1サブフレームで3つの副画素が全て消灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となる。階調2.5では、第1サブフレームで上下の2つの副画素が点灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となる。

【0082】

上述したことから明らかなように、複数の階調輝度の中間調輝度を表示させる駆動法であるFRC駆動を行うことで、FRC駆動ビット分だけ表示階調数Ngsを増やすことができる。因みに、単純に3ビットの画素構成とした場合、その分の回路を画素(副画素)20内に詰め込むことになるため、配線ルールが高精細化されない限り画素20のサイズが大きくなり、表示装置の高精細化を図る上で不利になる。

【0083】

また、画素20が3分割の電極構成であり、副画素電極205を挟む上下2つの副画素電極206A,206Bを同時駆動する画素構造での面積階調によれば、階調表示の画素の中心と複数のサブフレーム間の表示画像(階調)の中心とを一致させることができる。そして、画素の中心と階調(表示画像)の中心とがサブフレーム間で一致することで、表示画像にサブフレーム周期での揺らぎが生じないため、表示特性の更なる向上を図ることができる。また、表示画像にサブフレーム周期での揺らぎが生じないことで、サブフレーム周期の時間(フレームレート)を遅くすることができるため、FRC駆動の下での消費電力の低減を図ることができる。

【0084】

ここでは、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させるために、副画素電極205を挟む上下2つの副画素電極206A,206B同士を結線するとしたが、これは一例に過ぎない。具体的には、上下2つの副画素電極206A,206B同士を結線しなくても、これら副画素電極206A,206Bを同時に駆動できる構成であればよい。

【0085】

尚、上下2つの副画素電極206A,206B同士を結線するということは、先述したように、これら副画素電極206A,206Bを1つの駆動回路によって駆動することである。これに対して、副画素電極206A,206Bを別々の駆動回路によって駆動する構成とし、これら別々の駆動回路を同じタイミングで動作させることで、副画素電極206A,206Bを同時に駆動することができることになる。

【0086】

続いて、FRC駆動の下での面積階調において、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させるために、複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンについての具体的な実施例について説明する。以下では、点灯状態にある副画素を単に「点灯副画素」と呼ぶ場合がある。

【0087】

以下に説明する実施例1〜4では、画素20が3分割の電極構成であり、副画素電極205を挟む上下2つの副画素電極206A,206Bを1つの駆動回路207A(図8参照)によって同時に駆動することを前提とする。

【0088】

(実施例1)

図11は、実施例1に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。図11において、白の矩形で示した副画素が点灯状態にある副画素を表わし、黒の矩形で示した副画素が消灯状態にある副画素を表わしている。他の実施例においても同様とする。

【0089】

実施例1は、面積比が1:2の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の場合の例である。ここで、時間比とは、第1サブフレーム及び第2サブフレームの各時間の比である。この場合、g=3、f=2であり、表示階調数NgsがNgs=3×2+1=7となるため、0/6〜6/6の7階調での2倍速以上の表示となる。

【0090】

階調0/6では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て消灯状態となる。階調1/6では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。階調2/6では、第1サブフレーム、第2サブフレーム共に、中央の副画素が点灯状態となる。

【0091】

階調3/6では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで上下の2つの副画素が点灯状態となるか、または、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる2通りのパターンとなる2通りのパターンとなる。但し、図の右側のパターンの場合には、第1サブフレームと第2サブフレームとの間の輝度差(階調差)が大きいため、フリッカが発生し易い。従って、階調3/6の場合は、2通りのパターンのうち、図の左側のパターンの方が良好な表示状態となる。

【0092】

階調4/6,5/6,6/6は、階調2/6,1/6,0/6とそれぞれ補完関係にある。すなわち、階調4/6では、第1サブフレーム、第2サブフレーム共に、上下2つの副画素が点灯状態となる。階調5/6では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調6/6では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て点灯状態となる。

【0093】

上述したように、面積比が1:2の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の実施例1の場合は、6つの副画素のうち全てが消灯状態となる階調0/6から、6つの副画素のうち全てが点灯状態となる階調6/6までの7階調での2倍速の表示となる。

【0094】

また、階調3/6の場合のように、サブフレームの点灯状態にある副画素の組合せパターン(以下、「FRCパターン」と記述する場合がある)の設定において、サブフレーム間の輝度差(階調差)の少ないパターンを設定することにより、フリッカの発生を抑えることができる。従って、より良好な表示状態を得ることができる。

【0095】

(実施例2)

図12は、実施例2に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。実施例2は、面積比が1:2の面積階調、サブフレーム数が3で、時間比が1:1:1のFRC駆動の場合の例である。ここで、時間比とは、第1サブフレーム、第2サブフレーム、及び、第3サブフレームの各時間の比である。この場合、g=3、f=3であり、表示階調数NgsがNgs=3×3+1=7となるため、0/9〜9/9の10階調での3倍速以上の表示となる。

【0096】

階調0/9では、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、3つの副画素が全て消灯状態となる。階調1/9では、3通りのパターンとなる。第1パターンでは、第2サブフレームで中央の副画素が点灯状態となり、他の8つの副画素が消灯状態となる。第2パターンでは、第2サブフレームで中央の副画素が点灯状態となり、他の8つの副画素が消灯状態となる。第3パターンでは、第3サブフレームで中央の副画素が点灯状態となり、他の8つの副画素が消灯状態となる。

【0097】

階調2/9でも、3通りのパターンとなる。第1パターンでは、第2,第3サブフレームで中央の副画素が点灯状態となり、他の7つの副画素が消灯状態となる。第2パターンでは、第1,第3サブフレームで中央の副画素が点灯状態となり、他の7つの副画素が消灯状態となる。第3パターンでは、第1,第2サブフレームで中央の副画素が点灯状態となり、他の7つの副画素が消灯状態となる。

【0098】

階調3/9では、4通りのパターンとなる。第1パターンでは、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、中央の副画素が点灯状態となり、他の6つの副画素が消灯状態になる。第2パターンでは、第1サブフレームで3つの副画素が全て消灯状態となり、第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで上下2つの副画素が点灯状態となる。

【0099】

第3パターンでは、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となり、第3サブフレームで中央の副画素が点灯状態となる。第4パターンでは、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで上下の2つの副画素が点灯状態となり、第3サブフレームで3つの副画素が全て消灯状態となる。

【0100】

階調4/9では、6通りのパターンとなる。第1パターンでは、第1サブフレームで3つの副画素が全て消灯状態となり、第2,第3サブフレームで上下2つの副画素が点灯状態となる。第2パターンでは、第1,第3サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる。第3パターンでは、第1,第2サブフレームで上下2つの副画素が点灯状態となり、第3サブフレームで3つの副画素が全て消灯状態となる。

【0101】

第4パターンでは、第1,第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで上下2つの副画素が点灯状態となる。第5パターンでは、第1サブフレームで上下2つの副画素が点灯状態となり、第2,第3サブフレームで中央の副画素が点灯状態となる。第6パターンでは、第1,第3サブフレームで中央の副画素が点灯状態となり、第2サブフレームで上下2つの副画素が点灯状態となる。

【0102】

階調5/9,6/9,7/9,8/9,9/9は、階調4/9,3/9,2/9,1/9,0/9とそれぞれ補完関係にある。すなわち、階調5/9の第1パターンでは、第1サブフレームで3つの副画素が全て点灯状態となり、第2,第3サブフレームで中央の副画素が点灯状態となる。第2パターンでは、第1,第3サブフレームで中央の副画素が点灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となる。第3パターンでは、第1,第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで3つの副画素が全て点灯状態となる。

【0103】

第4パターンでは、第1,第2サブフレームで上下2つの副画素が点灯状態となり、第3サブフレームで中央の副画素が点灯状態となる。第5パターンでは、第1サブフレームで中央の副画素が点灯状態となり、第2,第3サブフレームで上下2つの副画素が点灯状態となる。第6パターンでは、第1,第3サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態となる。

【0104】

階調6/9の第1パターンでは、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、上下2つの副画素が点灯状態となり、中央の副画素が消灯状態になる。第2パターンでは、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで上下2つの副画素が点灯状態となり、第3サブフレームで中央の副画素が点灯状態となる。第3パターンでは、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となり、第3サブフレームで上下の2つの副画素が点灯状態となる。第4パターンでは、第1サブフレームで上下の2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで3つの副画素が全て点灯状態となる。

【0105】

階調7/9の第1パターンでは、第2,第3サブフレームで中央の副画素が消灯状態となり、他の7つの副画素が点灯状態となる。第2パターンでは、第1,第3サブフレームで中央の副画素が消灯状態となり、他の7つの副画素が点灯状態となる。第3パターンでは、第1,第2サブフレームで中央の副画素が消灯状態となり、他の7つの副画素が点灯状態となる。

【0106】

階調8/9の第1パターンでは、第2サブフレームで中央の副画素が消灯状態となり、他の8つの副画素が点灯状態となる。第2パターンでは、第1サブフレームで中央の副画素が消灯状態となり、他の8つの副画素が点灯状態となる。第3パターンでは、第3サブフレームで中央の副画素が消灯状態となり、他の8つの副画素が点灯状態となる。

【0107】

階調9/9では、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、3つの副画素が全て点灯状態となる。

【0108】

上述したように、面積比が1:2の面積階調、サブフレーム数が3で、時間比が1:1:1のFRC駆動の実施例2の場合は、9つの副画素のうち全てが消灯状態となる階調0/9から、9つの副画素のうち全てが点灯状態となる階調9/9までの10階調での3倍速の表示となる。

【0109】

(実施例3)

図13は、実施例3に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。実施例3は、面積比が1:4の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の場合の例である。

【0110】

ここで、面積比が1:4とは、3分割の副画素電極において、中央の副画素電極の面積を1とし、上下2つの副画素電極の面積をそれぞれ2としたときの、中央の副画素電極の面積と上下2つの副画素電極のトータル面積との比である。この場合、g=5、f=2であり、表示階調数NgsがNgs=5×2+1=11となるため、0/10〜10/10の11階調での2倍速以上の表示となるが、実際には、後述する理由により、9階調での2倍速以上の表示となる。

【0111】

階調0/10では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て消灯状態となる。

【0112】

階調1/10では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。階調2/10では、第1サブフレーム、第2サブフレーム共に、中央の副画素が点灯状態となる。

【0113】

階調3/10の場合には、上下2つの副画素の同時駆動が前提となっているため、階調3/10を表現する点灯状態の副画素の組合せは存在しない。従って、階調としては、階調2/10と階調4/10との間で不連続となる。階調7/10の場合にも、階調3/10の場合と同様のことが言える。

【0114】

階調4/10では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで3つの副画素の全てが消灯状態となる。

【0115】

階調5/10では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態になるか、または、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる2通りのパターンとなる。但し、該図の右側のパターンの場合には、第1サブフレームと第2サブフレームとの間の輝度差(階調差)が大きいため、フリッカが発生し易い。従って、階調5/10の場合は、2通りのパターンのうち、図の左側のパターンの方が良好な表示状態となる。

【0116】

階調6/10,8/10,9/10,10/10は、階調4/10,2/10,1/10,0/10とそれぞれ補完関係にある。

【0117】

階調6/10では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで3つの副画素の全てが点灯状態となる。

【0118】

階調8/10では、第1サブフレーム、第2サブフレーム共に、上下2つの副画素が点灯状態となる。

【0119】

階調9/10では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調10/10では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て点灯状態となる。

【0120】

上述したように、面積比が1:4の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の実施例3の場合は、上下2つの副画素の同時駆動が前提となっていることから、階調3/10,7/10が除外されるため、9階調での2倍速以上の表示となる。尚、上下2つの副画素の同時駆動を前提としなければ、即ち、上下2つの副画素を別々の駆動回路で駆動する構成とすれば、階調3/10,7/10を含めた、計11階調の表示は可能となる。

【0121】

また、階調5/10の場合のように、FRCパターン(サブフレームのパターン)の設定において、サブフレーム間の輝度差(階調差)の少ないパターンを設定することで、フリッカの発生を抑えることができるため、より良好な表示状態を得ることができる。

【0122】

(実施例4)

図14は、実施例4に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。実施例4は、面積比が1:3の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の場合の例である。

【0123】

ここで、面積比が1:3とは、3分割の副画素電極において、中央の副画素電極の面積を1とし、上下2つの副画素電極の面積をそれぞれ1.5としたときの、中央の副画素電極の面積と上下2つの副画素電極のトータル面積との比である。この場合、g=4、f=2であり、表示階調数NgsがNgs=4×2+1=9となるため、0/8〜8/8の8階調での2倍速の表示となる。

【0124】

階調0/8では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て消灯状態となる。

【0125】

階調1/8では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。

【0126】

階調2/8では、第1サブフレーム、第2サブフレーム共に、中央の副画素が点灯状態となる。

【0127】

階調3/8では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。

【0128】

階調4/8では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態になるか、または、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる2通りのパターンとなる。但し、該図の右側のパターンの場合には、第1サブフレームと第2サブフレームとの間の輝度差(階調差)が大きいため、フリッカが発生し易い。従って、階調4/8の場合は、2通りのパターンのうち、該図の左側のパターンの方が良好な表示状態となる。

【0129】

階調5/8,6/8,7/8,8/8は、階調3/8,2/8,1/8,0/8とそれぞれ補完関係にある。すなわち、階調5/8では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調6/8では、第1サブフレーム、第2サブフレーム共に、上下2つの副画素が点灯状態となる。階調7/8では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調8/8では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て点灯状態となる。

【0130】

上述したように、面積比が1:3の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の実施例4の場合は、実施例3の場合と同様に、9階調での2倍速以上の表示となる。但し、実施例3の場合と違って、階調としては、階調0/8から階調8/8まで連続となる。従って、階調の連続性、画面の表示性能としては、実施例3の場合よりも優れている。

【0131】

また、階調4/8の場合のように、FRCパターン(サブフレームのパターン)の設定において、サブフレーム間の輝度差(階調差)の少ないパターンを設定することにより、フリッカの発生を抑えることができるため、より良好な表示状態を得ることができる。

【0132】

また、実施例1乃至実施例4に対して共通に言えることであるが、複数のサブフレームの各々における、点灯状態にある副画素の組合せパターン、即ち、FRCパターンを隣接画素間で変更するようにするのが好ましい。FRCパターンを隣接画素間で変更するようにすることで、変更しない場合に比べてフリッカの発生を抑えることができる。FRCパターンを隣接画素間で変更する方法としては、FRCパターンの反転、順次シフト、あるいは、位相シフトなどの方法を例示することができる。

【0133】

尚、実施例1乃至実施例4では、中央の副画素を挟む上下2つの副画素を1つの駆動回路で同時に駆動することを前提としている。このため、前にも述べたように、サブフレーム内での同時点灯の画素数が結線され、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させるためのFRCパターンの数が制限される。

【0134】

これに対し、上下2つの副画素の同時駆動の構成に限らず、3つの副画素を別々の駆動回路によって独立に駆動する構成とすることも可能である。この構成によれば、上下2つの副画素の点灯パターン以外に、中央の副画素と上の副画素との組合せ、または、中央の副画素と下の副画素との組合せの点灯パターンも可能になるため、トータルのFRCパターンを大幅に増やすことができる。

【0135】

この構成を採る場合は、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを厳密に一致させることができないものの、複数のサブフレーム間で時間的に積分することによって、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを実質的に一致させることができる。この場合も、「階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とが一致」の概念に含まれるものとする。

【0136】

以上では、時間比が1:1または1:1:1、即ち、複数のサブフレーム間でサブフレーム時間に重み付け無しのFRC駆動の場合を例に挙げて説明した。このサブフレーム時間に重み付け無しのFRC駆動の部分画面の動画表示において、1フレームの全画面表示周期をTo、単位サブフレーム内での表示階調数を2n 、部分表示のサブフレーム周期をTsfとするとき、全表示階調数Ngsとの間に下記の関係にあることとする。すなわち、全表示階調数をNgsとすると、

Ngs<2n ×(To/Tsf)

の関係にある。

【0137】

図15に、実施例2の場合を例に挙げて、1フレームの全画面表示周期To、単位サブフレーム内での表示階調数2n 、及び、部分表示のサブフレーム周期Tsfと全表示階調数Ngsとの間の関係について示す。実施例2の場合、g=3、f=3であるから、Ngs=3×3+1=10で、全表示階調数Ngsは10階調である。右辺は2n =4、To/Tsf≧3、よって12以上となる。

【0138】

(サブフレーム時間に重み付け有りのFRC駆動)

また、実施例1乃至実施例4では、複数のサブフレーム間でサブフレーム時間に重み付け無しのFRC駆動の場合を例に挙げて説明したが、複数のサブフレーム間でサブフレーム時間に重み付け有りのFRC駆動に対しても同様に適用可能である。一般的なサブフレーム時間重み付け有りFRC駆動の階調表示において、単位サブフレーム内での表示階調数を2n 、サブフレーム周期による階調数(サブフレーム数)を2m とすると、表示階調数Ngsは、Ngs=(2n )m となる。

【0139】

サブフレーム時間に対する重み付けの具体例を図16に示す。図16(A)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:4とし、面積比を1:2とした例である。

【0140】

図16(B)は、1フレームが3つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間:第3サブフレームの時間の比率を1:4:16とし、面積比を1:2とした例である。

【0141】

図16(C)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:8とし、面積比を1:2:4とした例である。図16(D)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:2とし、面積比を1:4とした例である。

【0142】

図16(E)は、1フレームが3つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間:第3サブフレームの時間の比率を1:2:4とし、面積比を1:8とした例である。図16(F)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:2とし、面積比を1:4:16とした例である。

【0143】

上述したように、単位サブフレーム内での表示階調数2n と、サブフレーム数2m との組合せにより、高階調表示が可能となる。図16に示した、サブフレーム時間に対する重み付けの具体例(A)〜(F)の各々における表示階調数2(n+m)は図17に示す通りである。

【0144】

すなわち、図16(A)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:2/(22 )、サブフレーム周期比(時間比)/階調数(2m )が1:4/(22 )、表示階調数2(n+m) が16(=(22 )2 )、サブフレーム周期数が5(=1+4)となる。図16(B)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:2/(22 )、サブフレーム周期比/階調数(2m )が1:4:16/(23 )、表示階調数2(n+m) が64(=(22 )3 )、サブフレーム周期数が21(=1+4+16)となる。

【0145】

図16(C)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:2:4/(23 )、サブフレーム周期比/階調数(2m )が1:8/(22 )、表示階調数2(n+m) が64(=(23 )2 )、サブフレーム周期数が9(=1+8)となる。図16(D)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:4/(22 )、サブフレーム周期比/階調数(2m )が1:2/(22 )、表示階調数2(n+m) が16(=(22 )2 )、サブフレーム周期数が3(=1+2)となる。

【0146】

図16(E)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:8/(22 )、サブフレーム周期比/階調数(2m )が1:2:4/(23 )、表示階調数2(n+m) が64(=(22 )3 )、サブフレーム周期数が7(=1+2+4)となる。図16(F)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:4:16/(23 )、サブフレーム周期比/階調数(2m )が1:2/(22 )、表示階調数2(n+m) が64(=(23 )2 )、サブフレーム周期数が3(=1+2)となる。

【0147】

<3.電子機器>

以上説明した本開示に係る表示装置は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示部(表示装置)として用いることが可能である。

【0148】

先述した実施形態の説明から明らかなように、本開示に係る表示装置は、表示階調数を更に増加させることができるとともに、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる、という特徴を持っている。従って、あらゆる分野の電子機器において、その表示部として本開示に係る表示装置を用いることで、より高画質の画像を表示できる。

【0149】

本開示に係る表示装置を表示部として用いる電子機器としては、例えば、デジタルカメラ、ビデオカメラ、PDA(Personal Digital Assistant)、ゲーム機、ノート型パーソナルコンピュータ、電子書籍等の携帯情報機器、携帯電話機等の携帯通信機器などを例示することができる。

【0150】

<4.本開示の構成>

尚、本開示は以下のような構成を採ることができる。

(1)画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置。

(2)表示画面の中央部付近に部分的に動画を表示する部分動画表示の場合、1フレームの全画面表示周期、部分表示のサブフレーム周期、時分割駆動のサブフレーム数、及び、人の目のちらつきの限界周期の間に、人の目のちらつきの限界周期よりも1フレームの全画面表示周期が小さく、当該全画面表示周期よりも部分表示のサブフレーム周期と時分割駆動のサブフレーム数とで決まる合計サブフレーム周期が小さい関係にある

前記(1)に記載の表示装置。

(3)前記限界周期は、1/50Hzまたは1/60Hzである

前記(2)に記載の表示装置。

(4)入力されるデータに対して減色処理を行って前記駆動部に与える減色処理部を有する

前記(1)から前記(3)のいずれかに記載の表示装置。

(5)前記減色処理部は、誤差拡散法またはディザ法を用いて減色処理を行う

前記(4)に記載の表示装置。

(6)前記駆動部は、前記減色処理部で減色処理されたデータを、当該データよりも少ないビット数のデータにサブフレーム単位で変換する

前記(4)または前記(5)に記載の表示装置。

(7)前記画素は、データを格納するメモリ部を有する

前記(1)から前記(6)のいずれかに記載の表示装置。

(8)前記画素は、メモリ性液晶を用いている

前記(1)から前記(6)のいずれかに記載の表示装置。

(9)前記画素は、複数の副画素から成り、前記複数の副画素の面積の組み合わせによって階調を表示する

前記(1)から前記(8)のいずれかに記載の表示装置。

(10)前記画素の画素電極は、前記複数の副画素毎に複数の電極に分割されており、当該複数の電極の面積の組合せによって階調表示を行う

前記(9)に記載の表示装置。

(11)前記複数の電極は、3つの電極から成り、中央の電極と、当該中央の電極を挟む2つの電極との面積の組合せによって階調表示を行う

前記(10)に記載の表示装置。

(12)前記2つの電極は、面積が同じである

前記(11)に記載の表示装置。

(13)前記2つの電極は、互いに電気的に結線され、1つの駆動回路によって駆動される

前記(11)または前記(12)に記載の表示装置。

(14)前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンの設定において、サブフレーム間の輝度差の少ないパターンを設定する

前記(13)に記載の表示装置。

(15)前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンを隣接画素間で変更する

前記(13)に記載の表示装置。

(16)前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動を行う

前記(1)から前記(15)のいずれかに記載の表示装置。

(17)前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動の部分画面の動画表示において、全表示階調数は、単位サブフレーム内での表示階調数×(1フレームの全画面表示周期/部分表示画面の表示周期)よりも小さい

前記(16)に記載の表示装置。

(18)前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け有りの時分割駆動を行う

前記(1)から前記(17)のいずれかに記載の表示装置。

(19)画素の内部に記憶機能を有する表示装置の駆動に当たって、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示を行い、

階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる

表示装置の駆動方法。

(20)画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置を有する電子機器。

【符号の説明】

【0151】

10・・・表示装置、11・・・減色処理部、12・・・FRC用データ処理部、13・・・表示部、14・・・垂直駆動部、15・・・水平駆動部、16・・・タイミング発生部、20・・・画素、21・・・画素トランジスタ、22・・・液晶容量、23・・・保持容量、31(311,312,313)・・・信号線、32(321,322,323)・・・走査線

【技術分野】

【0001】

本開示は、表示装置、表示装置の駆動方法、及び、電子機器に関する。

【背景技術】

【0002】

画素の内部に記憶機能を有する表示装置において、解像度の制約により、画素に内蔵する回路規模が限られるため表示階調数が低下する。このため、解像度を犠牲にして見た目の表示階調数を増やすディザリング(ディザ法)と呼ばれる技法が用いられている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−38968号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかし、ディザリングと呼ばれる技法を用いても階調数が不足し、表示画像に粗さがあるため、表示特性の向上にも限界がある。従って、表示特性のより向上を図るために、表示階調数の更なる増加が望まれている。

【0005】

そこで、本開示は、表示階調数の更なる増加を可能にした表示装置、表示装置の駆動方法、及び、当該表示装置を有する電子機器を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するために、本開示は、

画素の内部に記憶機能を有する表示装置において、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示を行い、

階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる

構成を採っている。この表示装置は、各種の電子機器において、その表示部として用いて好適なものである。

【0007】

上記構成の表示装置、または、当該表示装置を有する電子機器において、サブフレーム単位での時分割駆動、即ち、FRC(Frame Rate Control)駆動にて表示を行うことで、フレーム単位での駆動の場合に比べて表示階調数を増加させることができる。ここで、「FRC駆動」とは、異なる複数の階調輝度をサブフレーム単位で高速に切り替えることで人間の目の残像特性(残像効果)を利用し、複数の階調輝度の中間調輝度を表示させる駆動法である。そして、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことで、表示画像に揺らぎが生じない。

【発明の効果】

【0008】

本開示によれば、表示階調数を更に増加させることができるとともに、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる。

【図面の簡単な説明】

【0009】

【図1】本開示の実施形態に係る表示装置のシステム構成の概略を示すブロック図である。

【図2】パネルに入力される8ビットのデータ(A)、減色処理部での減色処理後の3ビットのデータ(B)、及び、FRC用データ処理部での変換処理後、MIP方式の画素にサブフレーム単位で書き込まれる2ビットのデータ(C)のタイミング関係を示すタイミングチャートである。

【図3】画素の基本的な画素回路の一例を示す回路図である。

【図4】MIP方式の画素の回路構成の一例を示すブロック図である。

【図5】MIP方式の画素の動作説明に供するタイミングチャートである。

【図6】MIPの画素の具体的な回路構成の一例を示す回路図である。

【図7】面積階調法における画素分割についての説明図である。

【図8】3分割画素構造における3つの副画素電極と2組の駆動回路との対応関係を示す回路図である。

【図9】1フレームの全画面表示周期、部分表示のサブフレーム周期、FRC駆動のサブフレーム数、及び、人の目のちらつきの限界周期との間の関係を模式的に示す図である。

【図10】2ビット面積階調の場合と2ビット面積階調+1ビットFRC駆動の場合についての説明図である。

【図11】実施例1に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図12】実施例2に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図13】実施例3に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図14】実施例4に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。

【図15】実施例2の場合の、1フレームの全画面表示周期、単位サブフレーム内での表示階調数、及び、部分表示のサブフレーム周期と全表示階調数との間の関係を示す図である。

【図16】サブフレーム時間に対する重み付けの具体例を示す図である。

【図17】図16に示した、サブフレーム時間に対する重み付けの具体例(A)〜(F)の各々における表示階調数の一覧を示す図である。

【発明を実施するための形態】

【0010】

以下、本開示の技術を実施するための形態(以下、「実施形態」と記述する)について図面を用いて詳細に説明する。本開示は実施形態に限定されるものではなく、実施形態における種々の数値などは例示である。以下の説明において、同一要素又は同一機能を有する要素には同一符号を用いることとし、重複する説明は省略する。尚、説明は以下の順序で行う。

1.本開示の表示装置及び表示装置の駆動方法、全般に関する説明

2.実施形態に係る表示装置及び表示装置の駆動方法

2−1.システム構成

2−2.画素回路

2−3.MIP方式

2−4.面積階調法

2−5.実施形態の特徴部分

3.電子機器

4.本開示の構成

【0011】

<1.本開示の表示装置及び表示装置の駆動方法、全般に関する説明>

本開示の表示装置は、画素の内部に記憶機能を持つ表示装置である。この種の表示装置としては、例えば、画素内にデータを記憶可能なメモリ部を有する、所謂、MIP(Memory In Pixel)方式の表示装置を例示することができる。

【0012】

表示装置としては、液晶表示装置、エレクトロルミネッセンス表示装置、プラズマ表示装置などといった、周知の表示装置を用いることができる。液晶表示装置の場合には、画素にメモリ性液晶を用いることで、画素に記憶機能を持つ表示装置とすることができる。表示装置は、モノクロ表示対応の表示装置であってもよいし、カラー表示対応の表示装置であってもよい。

【0013】

画素に記憶機能を有する表示装置は、画素にデータを記憶できることで、モード切替えスイッチによってアナログ表示モードによる表示と、メモリ表示モードによる表示とを実現できる。ここで、「アナログ表示モード」とは、画素の階調をアナログ的に表示する表示モードである。また、「メモリ表示モード」とは、画素に記憶されている2値の情報(論理“1”/論理“0”)に基づいて、画素の階調をデジタル的に表示する表示モードである。

【0014】

画素に記憶機能を有する表示装置、例えば、MIP方式の表示装置にあっては、解像度の制約により、画素に内蔵する回路規模が限られるため表示階調数が低下する傾向にある。そのため、MIP方式の表示装置では、解像度を犠牲にして見た目の表示階調数を増やすために、周知の誤差拡散法やディザ法などの技法が減色処理に用いられる。

【0015】

そして、表示階調数の更なる増加を図るために、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示駆動を行う構成とする。前にも述べたように、「FRC駆動」とは、異なる複数の階調輝度をサブフレーム単位で高速に切り替えることで人間の目の残像特性(残像効果)を利用し、複数の階調輝度の中間調輝度を表示させる駆動法である。

【0016】

このサブフレーム単位での時分割駆動、即ち、FRC駆動を行うことで、フレーム単位での駆動の場合に比べて、表示階調数の増加を図ることができる。そして、FRC駆動の表示装置において、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う構成とする。

【0017】

ここで、「一致」とは、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とが厳密に一致する場合の他、実質的に一致する場合も含む。設計上あるいは製造上生ずる種々のばらつきの存在は許容される。また、複数のサブフレーム間で時間的に積分することによって、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とが実質的に一致する場合も含むものとする。

【0018】

このように、FRC駆動の表示装置において、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことで、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる。

【0019】

MIP方式の表示装置は、画素毎に1ビットで2階調しか表現を行うことができない。そのために、画素の駆動に当たっては、階調表現方式として、面積階調法を用いる構成とするのが好ましい。ここで、「面積階調法」とは、面積比を20 ,21 ,22 ,・・・,2N-1 、という具合に重み付けしたN個の副画素電極で2N 個の階調を表現する階調表現方式である。この面積階調法は、例えば、画素回路を構成するTFT(Thin Film Transistor:薄膜トランジスタ)の特性ばらつきによる画質の不均一性を改善する等の目的で採用される。

【0020】

<2.実施形態に係る表示装置及び表示装置の駆動方法>

[2−1.システム構成]

図1は、本開示の実施形態に係る表示装置のシステム構成の概略を示すブロック図である。本実施形態に係る表示装置は、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示を行う構成を採る。また、本実施形態に係る表示装置の画素は、画素毎にメモリ部を有するMIP方式の画素である。

【0021】

図1に示すように、本実施形態に係る表示装置10は、減色処理部11、FRC用データ処理部12、表示部13、垂直駆動部14、水平駆動部15、及び、タイミング発生部16を有する構成となっている。そして、これらの構成要素(11〜16)の内、表示部13、垂直駆動部14、及び、水平駆動部15が、パネル(基板)17上に実装されている。

【0022】

表示装置10には、パネル外部のホスト装置(図示せず)からデータ及び制御信号が入力される。表示装置10に入力されるデータは、表示部13に画像を表示するための例えば8ビットのデータであり、減色処理部11に与えられる。表示装置10に入力される制御信号は、本表示装置10を全体的に制御するための種々の制御情報を含む信号であり、タイミング発生部16に与えられる。

【0023】

タイミング発生部16は、制御信号が入力されると、当該制御信号に基づいて減色処理部11、FRC用データ処理部12、垂直駆動部14、及び、水平駆動部15に対して種々のタイミング信号を与える。すなわち、減色処理部11、FRC用データ処理部12、垂直駆動部14、及び、水平駆動部15は、タイミング発生部16から与えられる、制御信号に基づくタイミング信号による駆動の下に各種の動作を行う。

【0024】

減色処理部11は、タイミング発生部16から与えられるタイミング信号による駆動の下に、外部のホスト装置から入力される8ビットのデータを例えば3ビットのデータに変換する減色処理を行う。この減色処理には、例えば、周知の誤差拡散法が用いられる。但し、減色処理の技法としては、誤差拡散法に限られるものではなく、周知のディザ法などを用いることもできる。

【0025】

減色処理において、原画に対して2ビットの誤差拡散では、画像の粗さが目立つ。これに対して、3ビットの誤差拡散とすることにより、画像の粗さを大幅に改善することができる。減色処理部11で減色処理された3ビットのデータは、FRC用データ処理部12に与えられる。

【0026】

FRC用データ処理部12は、減色処理部11から与えられる3ビットのデータを一時的に格納し、タイミング発生部16から与えられるタイミング信号による駆動の下に、3ビットのデータをFRC変換する。このFRC変換では、FRC駆動を行うに当たって、減色処理された3ビットのデータを当該データよりも少ないビット数のデータ、例えば、2ビットのデータにサブフレーム単位で変換する処理が行われる。

【0027】

上記の構成の本実施形態に係る表示装置10において、FRC用データ処理部12、垂直駆動部14、水平駆動部15、及び、タイミング発生部16は、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を構成している。

【0028】

図2に、パネル17に入力される8ビットのデータ(A)、減色処理部11での減色処理後の3ビットのデータ(B)、及び、FRC用データ処理部12での変換処理後、MIP方式の画素にサブフレーム単位で書き込まれる2ビットのデータ(C)のタイミング関係を示す。図2において、Toは1フレームの全画面表示周期である。

【0029】

図2には、FRC駆動による描画の概念図をも併せて示している。ここでは、理解を容易にするために、「A」という文字を描画する場合を例に挙げている。パネル17には外部のホスト装置から「A」という文字の中間調の8ビットのデータが入力される。この8ビットのデータを3ビットのデータに減色処理する。そして、第1サブフレームでは濃い目の画像を描き、第2サブフレームで淡目の画像を描くことで、1フレームトータルで元の(原画の)中間調の階調を表示することができる。

【0030】

図1に説明を戻す。表示部13は、画素が行列状に2次元配置されて成り、当該画素の行列状配置に対して画素行毎に走査線が配線され、画素列毎に信号線が配線された構成となっている。この表示部13の具体的な構成については後述する。

【0031】

垂直駆動部14は、表示部13の各画素を画素行単位で選択走査する。垂直駆動部14の回路構成は特に限定するものではない。垂直駆動部14は、シフトレジスタや論理回路などによって構成したり、あるいは、アドレスデコーダを用いて構成したりすることができる。

【0032】

水平駆動部15は、垂直駆動部14によって選択された画素行の各画素に対して、FRC用データ処理部12から与えられるデータを信号線を通して供給する。水平駆動部15の回路構成は、特に限定するものではない。水平駆動部15は、垂直駆動部14によって選択された画素行の各画素に対してデータを、1行分同時に供給する構成のものであってもよいし、画素単位で順次供給する構成のものであってよいし、あるいは、複数の画素単位で供給する構成のものであってよい。

【0033】

[2−2.画素回路]

次いで、表示部13を構成する画素の基本的な画素回路について、図3を用いて説明する。ここでは、表示装置10が液晶表示装置から成る場合を例に挙げて説明するものとする。

【0034】

図3に示すように、複数の信号線31(311,312,313,・・・)と、複数の走査線32(321,322,323,・・・)とが交差するように配線され、その交差部に画素20が配されている。信号線31(311,312,313,・・・)の各一端は、水平駆動部15の各列に対応した出力端に接続されている。複数の走査線32(321,322,323,・・・)の各一端は、垂直駆動部14の各行に対応した出力端に接続されている。

【0035】

画素20は、例えば、薄膜トランジスタ(TFT)から成る画素トランジスタ21、液晶容量22、及び、保持容量23を有する構成となっている。画素トランジスタ21は、ゲート電極が走査線32(321,322,323,・・・)に接続され、一方のソース/ドレイン電極が信号線31(311,312,313,・・・)に接続されている。

【0036】

液晶容量22は、画素電極とこれに対向して形成される対向電極との間で発生する液晶材料の容量成分を意味し、画素電極が画素トランジスタ21の他方のソース/ドレイン電極に接続されている。液晶容量22の対向電極には、直流電圧のコモン電位VCOMが全画素共通に印加される。保持容量23は、一方の電極が液晶容量22の画素電極に、他方の電極が液晶容量22の対向電極にそれぞれ接続されている。

【0037】

上記の画素回路から明らかなように、複数の信号線31(311,312,313,・・・)は、画素20を駆動する信号、即ち、水平駆動部15から出力されるデータを画素列毎に画素20に伝送する配線である。また、複数の走査線32(321,322,323,・・・)は、画素20を行単位で選択する信号、即ち、垂直駆動部14から出力される走査信号を画素行毎に伝送する配線である。

【0038】

[2−3.MIP方式]

本実施形態に係る表示装置10にあっては、画素20としてメモリ機能を有する画素、例えば、画素毎にデータを記憶可能なメモリ部を持つMIP方式の画素を用いている。MIP方式の表示装置の場合、画素20に常に一定電圧がかかることになるために、画素トランジスタ21の光リーク等による経時的な電圧変動によるシェーディングの問題を解消することができる。

【0039】

また、MIP方式の画素20は、データを記憶するメモリ部を画素20内に持ち、モード切換えスイッチ(図示せず)により、アナログ表示モードによる表示と、メモリ表示モードによる表示とを実現できる。ここで、「アナログ表示モード」とは、画素20の階調をアナログ的に表示する表示モードである。また、「メモリ表示モード」とは、画素20内のメモリ部に記憶されている2値情報(論理“1”/論理“0”)に基づいて、画素20の階調をデジタル的に表示する表示モードである。

【0040】

メモリ表示モードの場合、メモリ部に保持されている情報を用いるため、階調を反映した信号電位の書き込み動作を単発実行すれば、常時フレーム周期で実行する必要がない。そのため、メモリ表示モードの場合は、階調を反映した信号電位の書き込み動作を常時フレーム周期で実行する必要があるアナログ表示モードの場合に比べて消費電力が少なくて済む、換言すれば、表示装置の低消費電力化を図ることができる。

【0041】

図4は、MIP方式の画素20の回路構成の一例を示すブロック図である。また、図5に、MIP方式の画素20の動作説明に供するタイミングチャートを示す。

【0042】

図4に示すように、画素20は、液晶容量(液晶セル)22に加えて、3つのスイッチ素子24〜26及びラッチ部27を有するSRAM機能付きの画素構成となっている。

【0043】

スイッチ素子24は、信号線31(図3の信号線311〜313に相当)に一端が接続されている。そして、図3の垂直駆動部14から走査線32を介して走査信号φVが与えられることによってオン(閉)状態となり、図3の水平駆動部15から信号線31を介して供給されるデータSIGを取り込む。ラッチ部27は、互いに逆向きに並列接続されたインバータ271,272によって構成されており、スイッチ素子24によって取り込まれたデータSIGに応じた電位を保持(ラッチ)する。

【0044】

スイッチ素子25,26の各一方の端子には、コモン電圧VCOMと同相の電圧FRP及び

逆相の電圧XFRPが与えられる。スイッチ素子25,26の各他方の端子は共通に接続され、本画素回路の出力ノードNoutとなる。スイッチ素子25,26は、ラッチ部27の保持電位の極性に応じていずれか一方がオン状態となる。これにより、対向電極にコモン電位VCOMが印加されている液晶容量22に対して、同相の電圧FRPまたは逆相の電圧XFRPが画素電極に印加される。

【0045】

図5から明らかなように、ノーマリーブラック(無電圧印加時黒表示)の液晶パネルの場合、ラッチ部27の保持電位が負側極性のときは、液晶容量22の画素電位がコモン電位VCOMと同相になるため黒表示となり、ラッチ部27の保持電位が正側極性のときは、液晶容量22の画素電位がコモン電位VCOMと逆相になるため白表示となる。

【0046】

上述したことから明らかなように、MIP方式の画素20にあっては、ラッチ部27の保持電位の極性に応じてスイッチ素子25,26のいずれか一方がオン状態となることにより、液晶容量22の画素電極に対して、同相の電圧FRPまたは逆相の電圧XFRPが印加される。これにより、画素20には常に一定電圧が印加されることになるためにシェーディングが発生する懸念はない。

【0047】

図6は、画素20の具体的な回路構成の一例を示す回路図であり、図中、図4と対応する部分には同一符号を付して示している。

【0048】

図6において、スイッチ素子24は、例えばNchMOSトランジスタQn10から成る。NchMOSトランジスタQn10は、一方のソース/ドレイン電極が信号線31に接続され、ゲート電極が走査線32に接続されている。

【0049】

スイッチ素子25,26は共に、例えば、NchMOSトランジスタ及びPchMOSトランジスタが並列に接続されてなるトランスファスイッチから成る。具体的には、スイッチ素子25は、NchMOSトランジスタQn11及びPchMOSトランジスタQp11が互いに並列に接続された構成となっている。スイッチ素子26は、NchMOSトランジスタQn12及びPchMOSトランジスタQp12が互いに並列に接続された構成となっている。

【0050】

スイッチ素子25,26は、必ずしも、NchMOSトランジスタ及びPchMOSトランジスタを並列接続して成るトランスファスイッチである必要はない。スイッチ素子25,26を、単一導電型のMOSトランジスタ、即ち、NchMOSトランジスタあるいはPchMOSトランジスタを用いて構成することも可能である。スイッチ素子25,26の共通接続ノードが、本画素回路の出力ノードNoutとなる。

【0051】

インバータ271,272は共に、例えばCMOSインバータから成る。具体的には、インバータ271は、NchMOSトランジスタQn13及びPchMOSトランジスタQp13のゲート電極同士及びドレイン電極同士が共通に接続された構成となっている。インバータ272は、NchMOSトランジスタQn14及びPchMOSトランジスタQp14のゲート電極同士及びドレイン電極同士が共通に接続された構成となっている。

【0052】

上記の回路構成を基本とする画素20が、水平方向および垂直方向に展開されて行列状に配置されることになる。この画素20の行列状配列に対して、画素列毎の信号線31及び画素行毎の走査線32に加えて、同相の電圧FRP、逆相の電圧XFRPを伝送する配線33,34、及び、正側電源電圧VDD、負側電源電圧VSSの電源線35,36が画素列毎に配線されている。

【0053】

上述したように、本実施形態に係る表示装置(即ち、アクティブマトリクス型液晶表示装置)10は、表示データに応じた電位を保持するラッチ部27を有するSRAM機能付き画素(MIP)20が行列状に配置された構成となっている。尚、本実施形態では、画素20に内蔵するメモリ部としてSRAMを用いる場合を例に挙げたが、SRAMは一例に過ぎず、他の構成のメモリ部、例えば、DRAMを用いる構成であってもよい。

【0054】

このMIP方式の表示装置10は、画素20毎に記憶機能(メモリ部)を持つことで、前にも述べたように、モード切換えスイッチによりアナログ表示モードによる表示と、メモリ表示モードによる表示とを実現できる。そして、メモリ表示モードの場合、メモリ部に保持されている画素データを用いて表示を行うことから、階調を反映した信号電位の書き込み動作を単発実行するため常時フレーム周期で実行する必要がなく、表示装置10の消費電力の低減を図ることができる、という利点がある。

【0055】

また、表示画面を部分的に、即ち、表示画面の一部だけを書き換えたい、というニーズがある。この場合、部分的に画素データを書き換えれば良いことになる。表示画面を部分的に書き換える、即ち、画素データを部分的に書き換えると、書き換えを行わない画素についてはデータを転送する必要がなくなる。従って、データ転送量を減らすことができるため、表示装置10の更なる省電力化を図ることができる、という利点もある。

【0056】

[2−4.面積階調法]

ところで、画素内部の記憶機能を有する表示装置、例えば、MIP方式の表示装置の場合、画素20毎に1ビットで2階調しか表現を行うことができない。そこで、本実施形態に係る表示装置10にあっては、MIP方式を採用するに当たって、面積階調法を用いるのが好ましい。

【0057】

具体的には、画素20の表示領域となる画素電極を、面積的に重み付けした複数の画素(副画素)電極に分割する面積階調法を用いる。画素電極としては、透過電極であってもよいし、反射電極であってもよい。そして、ラッチ部27の保持電位によって選択された画素電位を面積的に重み付けした画素電極に通電し、重み付けした面積の組み合わせによって階調表示を行うようにする。

【0058】

ここでは、理解を容易にするために、画素電極(副画素電極)の面積(画素面積)に2:1の重みを付けることによって2ビットで4階調を表現する面積階調法を例に挙げて説明するものとする。

【0059】

画素面積に2:1の重みを付ける構造としては、図7(A)に示すように、画素20の画素電極を面積1の副画素電極201と、当該副画素電極201の2倍の面積(面積2)の副画素電極202とに分割する構造が一般的である。しかし、図7(A)の構造の場合には、1画素の中心(重心)に対する各階調(表示画像)の中心(重心)が揃わない(一致しない)ため、階調表現の点で好ましくない。

【0060】

1画素の中心に対する各階調の中心を揃える構造としては、図7(B)に示すように、面積2の副画素電極204の中心部を例えば矩形形状にくり抜き、そのくり抜いた矩形領域の中心部に面積1の副画素電極203を配置する構造が考えられる。しかし、図7(B)の構造の場合には、副画素電極203の両側に位置する、副画素電極204の連結部204A,204Bの幅が狭いため、副画素電極204全体の反射面積が小さくなるとともに、連結部204A,204Bの辺りの液晶配向が難しい。

【0061】

上述したように、面積階調で、無電界時に液晶分子が基板に対してほぼ垂直になるVA(Vertical Aligned:垂直配向)モードにしようとすると、液晶分子に対する電圧のかかり方が、電極形状や電極サイズなどによって変わるため、良好に液晶配向させることが難しい。また、副画素電極の面積比が反射率比になるとは限らないので階調設計が難しい。反射率は、副画素電極の面積や液晶配向などによって決まる。図7(A)の構造の場合、面積比が1:2であっても電極周辺の長さの比が1:2とはならない。従って、副画素電極の面積比が反射率比になるとは限らない。

【0062】

このような観点からすると、面積階調法を採用するに当たっては、階調の表現性と反射面積の有効活用を考える上で、図7(C)に示すように、画素電極を例えば同じ面積(大きさ)の3つの副画素電極205,206A,206Bに分割する、所謂、3分割の電極構成にするのが望ましい。

【0063】

この3分割の電極構成の場合、中央の副画素電極205を挟む上下2つの副画素電極206A,206Bを組とし、当該組となる2つの副画素電極206A,206Bを同時に駆動することで、中央の副画素電極205との間で画素面積に2:1の重みを付けることができる。また、1画素の中心(重心)に対する各階調の中心(重心)を揃えることができる。

【0064】

しかし、3つの副画素電極205,206A,206Bの各々について駆動回路と電気的にコンタクトを取るとすると、図7(A),(B)の構造に比べて金属配線のコンタクト数が増えるため、画素サイズが大きくなり、高精細化の阻害要因となる。特に、画素20毎にメモリ部を有するMIP方式の画素構成の場合には、図6から明らかなように、1つの画素20内にトランジスタ等の多くの回路構成素子やコンタクト部が存在することになり、レイアウト面積的に余裕がないために、コンタクト部1個が画素サイズに大きく影響を及ぼす。

【0065】

コンタクト数を減らすには、1個の副画素電極205を挟むことによって互いの距離が離れた2つの副画素電極206A,206B同士を電気的に結合する(結線する)画素構造とすれば良い。そして、図8に示すように、1つの駆動回路207Aで1個の副画素電極205を駆動し、他の1つの駆動回路207Bで残りの2つの副画素電極206A,206Bを同時に駆動するようにする。ここで、駆動回路207A,207Bは、図6に示した画素回路に相当する。

【0066】

このように、2つの副画素電極206A,206Bを1つの駆動回路207Aによって駆動するようにすることにより、2つの副画素電極206A,206Bを別々の駆動回路によって駆動する構成を採る場合よりも画素20の回路構成を簡略化できる。

【0067】

尚、ここでは、メモリ機能を有する画素として、画素毎にデータを記憶可能なメモリ部を持つMIP方式の画素を用いるとしたが、これは一例に過ぎない。メモリ機能を有する画素としては、MIP方式の画素の他に、例えば、周知のメモリ性液晶を用いる画素を例示することができる。

【0068】

[2−5.実施形態の特徴部分]

以上に説明したように、内部に記憶機能を持つMIP方式の画素20を有する本実施形態に係る表示装置10は、サブフレーム単位での時分割駆動、即ち、FRC駆動にて表示を行うことで、フレーム単位での駆動の場合に比べて表示階調数を増加させることができる。本実施形態に係る表示装置10は更に、面積階調法を採用している。

【0069】

そして、FRC駆動の下で面積階調法を採用する、本実施形態に係る表示装置10にあっては、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことを特徴としている。ここで、「階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させる」とは、換言すれば、1画素の中心と複数のサブフレーム間の各階調の中心とを一致させることである。

【0070】

そして、1画素の中心と複数のサブフレーム間の各階調の中心とを一致させるには、複数のサブフレームの各々において、複数の副画素の中で点灯させる副画素の組合せを階調毎に設定するようにすればよい。このように、階調表示の画素の中心と、複数のサブフレーム間の表示画像の中心とを一致させる駆動を行うことで、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる。

【0071】

ここで、単位画素当たりの最小単位面積数(即ち、副画素電極の数)をg(自然数)、サブフレーム数をf(2以上の自然数)、副画素の点灯個数をn(=0〜g・f)とすると、面積階調における階調の組合せ数、即ち、全表示階調数Ngsは、一般的には、Ngs=gfCnとなる。

【0072】

しかし、サブフレーム内での同時点灯の画素数が結線されなければならないという制約がある。具体的には、先述したように、2つの副画素電極206A,206B同士を結線する画素構造の場合がこれに相当する。また、1つの画素の中心と階調表示の中心とを一致させる必要がある。このような観点から、表示階調数Nは、実際には、Ngs=階調単位面積数+1=g・f+1となる。その具体的な実施例については後述する。

【0073】

ところで、表示画面の中央部付近に部分的に動画を表示する部分動画表示の場合、表示領域が狭いため、フレーム単位(フレーム周期)で表示を行う通常表示では、表示更新が停止している期間が発生している。この時間を逆に利用して、描画速度はそのままで、高速に画像を更新するFRC駆動を行うと、表示ビット数を増やすことができる。FRC駆動は、1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部、即ち、FRC用データ処理部12、垂直駆動部14、水平駆動部15、及び、タイミング発生部16によって実現される。

【0074】

前にも述べたように、FRC駆動は目の残像特性を利用している。従って、人の目のちらつきの限界周期(PAL駆動の場合1/50Hz、NTSC駆動の場合1/60Hz)よりも低いフレーム周期でFRC駆動を行うことが重要となる。

【0075】

一般的に、1フレームの全画面表示周期To、部分表示のサブフレーム周期Tsf、FRC駆動のサブフレーム数Nfrc、及び、人の目のちらつきの限界周期の間に、次の関係が成り立つ条件で駆動しなければならない。その関係とは、人の目のちらつきの限界周期よりも1フレームの全画面表示周期Toが小さく、当該全画面表示周期Toよりも部分表示のサブフレーム周期TsfとFRC駆動のサブフレーム数Nfrcとで決まる合計サブフレーム周期(=Tsf×Nfrc)が小さい関係である。

【0076】

一例として、PAL駆動の場合を考えると、1/50Hzの周期よりも短い周期で画面が構成されている。そして、上記の関係が成り立つ条件での駆動とは、その構成されている1画面(1フレーム)の全画面表示周期Toという時間よりも更に短い時間でサブフレームが構成されていることを意味する。

【0077】

図9に、1フレームの全画面表示周期To、部分表示のサブフレーム周期Tsf、FRC駆動のサブフレーム数Nfrc、及び、人の目のちらつきの限界周期(例えば、PAL駆動を考慮した場合1/50Hz)との間の関係を模式的に示す。このような条件の下でFRC駆動を行うことにより、FRC駆動ビット分の表示階調数が増加する。

【0078】

ここで、具体例として、画素20が3分割の電極構成であり、副画素電極205を挟む上下2つの副画素電極206A,206Bを同時に駆動する画素構造において、2ビット表示の部分表示に対して、1ビットのFRC駆動を行った場合について説明する。この場合は、g=3、f=2であり、Ngs=3×2+1=7となるため7階調表示となる。

【0079】

2ビットの面積階調のみ場合は、1画面を1フレーム周期で構成する。図10(A)に示すように、3つの副画素が全て消灯状態となる0、中央の副画素のみが点灯状態となる1、上下の2つの副画素が点灯状態となる2、3つの副画素が全て点灯状態となる3の計4階調表示となる。

【0080】

これに対して、2ビットの面積階調+1ビットのFRC駆動の場合は、1画面を2個のサブフレーム周期で構成する。そして、第1,第2サブフレームで同じ点灯駆動となる上記の4階調に、図10(B)に示す0.5,1.5,2.5の3階調が加わる。階調0.5では、第1サブフレームで3つの副画素が全て消灯状態となり、第2サブフレームで中央の副画素のみが点灯状態となる。

【0081】

階調1.5では、第1サブフレームで中央の副画素のみが点灯状態となり、第2サブフレームで上下の2つの副画素が点灯状態となる、または、第1サブフレームで3つの副画素が全て消灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となる。階調2.5では、第1サブフレームで上下の2つの副画素が点灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となる。

【0082】

上述したことから明らかなように、複数の階調輝度の中間調輝度を表示させる駆動法であるFRC駆動を行うことで、FRC駆動ビット分だけ表示階調数Ngsを増やすことができる。因みに、単純に3ビットの画素構成とした場合、その分の回路を画素(副画素)20内に詰め込むことになるため、配線ルールが高精細化されない限り画素20のサイズが大きくなり、表示装置の高精細化を図る上で不利になる。

【0083】

また、画素20が3分割の電極構成であり、副画素電極205を挟む上下2つの副画素電極206A,206Bを同時駆動する画素構造での面積階調によれば、階調表示の画素の中心と複数のサブフレーム間の表示画像(階調)の中心とを一致させることができる。そして、画素の中心と階調(表示画像)の中心とがサブフレーム間で一致することで、表示画像にサブフレーム周期での揺らぎが生じないため、表示特性の更なる向上を図ることができる。また、表示画像にサブフレーム周期での揺らぎが生じないことで、サブフレーム周期の時間(フレームレート)を遅くすることができるため、FRC駆動の下での消費電力の低減を図ることができる。

【0084】

ここでは、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させるために、副画素電極205を挟む上下2つの副画素電極206A,206B同士を結線するとしたが、これは一例に過ぎない。具体的には、上下2つの副画素電極206A,206B同士を結線しなくても、これら副画素電極206A,206Bを同時に駆動できる構成であればよい。

【0085】

尚、上下2つの副画素電極206A,206B同士を結線するということは、先述したように、これら副画素電極206A,206Bを1つの駆動回路によって駆動することである。これに対して、副画素電極206A,206Bを別々の駆動回路によって駆動する構成とし、これら別々の駆動回路を同じタイミングで動作させることで、副画素電極206A,206Bを同時に駆動することができることになる。

【0086】

続いて、FRC駆動の下での面積階調において、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させるために、複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンについての具体的な実施例について説明する。以下では、点灯状態にある副画素を単に「点灯副画素」と呼ぶ場合がある。

【0087】

以下に説明する実施例1〜4では、画素20が3分割の電極構成であり、副画素電極205を挟む上下2つの副画素電極206A,206Bを1つの駆動回路207A(図8参照)によって同時に駆動することを前提とする。

【0088】

(実施例1)

図11は、実施例1に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。図11において、白の矩形で示した副画素が点灯状態にある副画素を表わし、黒の矩形で示した副画素が消灯状態にある副画素を表わしている。他の実施例においても同様とする。

【0089】

実施例1は、面積比が1:2の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の場合の例である。ここで、時間比とは、第1サブフレーム及び第2サブフレームの各時間の比である。この場合、g=3、f=2であり、表示階調数NgsがNgs=3×2+1=7となるため、0/6〜6/6の7階調での2倍速以上の表示となる。

【0090】

階調0/6では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て消灯状態となる。階調1/6では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。階調2/6では、第1サブフレーム、第2サブフレーム共に、中央の副画素が点灯状態となる。

【0091】

階調3/6では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで上下の2つの副画素が点灯状態となるか、または、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる2通りのパターンとなる2通りのパターンとなる。但し、図の右側のパターンの場合には、第1サブフレームと第2サブフレームとの間の輝度差(階調差)が大きいため、フリッカが発生し易い。従って、階調3/6の場合は、2通りのパターンのうち、図の左側のパターンの方が良好な表示状態となる。

【0092】

階調4/6,5/6,6/6は、階調2/6,1/6,0/6とそれぞれ補完関係にある。すなわち、階調4/6では、第1サブフレーム、第2サブフレーム共に、上下2つの副画素が点灯状態となる。階調5/6では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調6/6では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て点灯状態となる。

【0093】

上述したように、面積比が1:2の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の実施例1の場合は、6つの副画素のうち全てが消灯状態となる階調0/6から、6つの副画素のうち全てが点灯状態となる階調6/6までの7階調での2倍速の表示となる。

【0094】

また、階調3/6の場合のように、サブフレームの点灯状態にある副画素の組合せパターン(以下、「FRCパターン」と記述する場合がある)の設定において、サブフレーム間の輝度差(階調差)の少ないパターンを設定することにより、フリッカの発生を抑えることができる。従って、より良好な表示状態を得ることができる。

【0095】

(実施例2)

図12は、実施例2に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。実施例2は、面積比が1:2の面積階調、サブフレーム数が3で、時間比が1:1:1のFRC駆動の場合の例である。ここで、時間比とは、第1サブフレーム、第2サブフレーム、及び、第3サブフレームの各時間の比である。この場合、g=3、f=3であり、表示階調数NgsがNgs=3×3+1=7となるため、0/9〜9/9の10階調での3倍速以上の表示となる。

【0096】

階調0/9では、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、3つの副画素が全て消灯状態となる。階調1/9では、3通りのパターンとなる。第1パターンでは、第2サブフレームで中央の副画素が点灯状態となり、他の8つの副画素が消灯状態となる。第2パターンでは、第2サブフレームで中央の副画素が点灯状態となり、他の8つの副画素が消灯状態となる。第3パターンでは、第3サブフレームで中央の副画素が点灯状態となり、他の8つの副画素が消灯状態となる。

【0097】

階調2/9でも、3通りのパターンとなる。第1パターンでは、第2,第3サブフレームで中央の副画素が点灯状態となり、他の7つの副画素が消灯状態となる。第2パターンでは、第1,第3サブフレームで中央の副画素が点灯状態となり、他の7つの副画素が消灯状態となる。第3パターンでは、第1,第2サブフレームで中央の副画素が点灯状態となり、他の7つの副画素が消灯状態となる。

【0098】

階調3/9では、4通りのパターンとなる。第1パターンでは、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、中央の副画素が点灯状態となり、他の6つの副画素が消灯状態になる。第2パターンでは、第1サブフレームで3つの副画素が全て消灯状態となり、第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで上下2つの副画素が点灯状態となる。

【0099】

第3パターンでは、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となり、第3サブフレームで中央の副画素が点灯状態となる。第4パターンでは、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで上下の2つの副画素が点灯状態となり、第3サブフレームで3つの副画素が全て消灯状態となる。

【0100】

階調4/9では、6通りのパターンとなる。第1パターンでは、第1サブフレームで3つの副画素が全て消灯状態となり、第2,第3サブフレームで上下2つの副画素が点灯状態となる。第2パターンでは、第1,第3サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる。第3パターンでは、第1,第2サブフレームで上下2つの副画素が点灯状態となり、第3サブフレームで3つの副画素が全て消灯状態となる。

【0101】

第4パターンでは、第1,第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで上下2つの副画素が点灯状態となる。第5パターンでは、第1サブフレームで上下2つの副画素が点灯状態となり、第2,第3サブフレームで中央の副画素が点灯状態となる。第6パターンでは、第1,第3サブフレームで中央の副画素が点灯状態となり、第2サブフレームで上下2つの副画素が点灯状態となる。

【0102】

階調5/9,6/9,7/9,8/9,9/9は、階調4/9,3/9,2/9,1/9,0/9とそれぞれ補完関係にある。すなわち、階調5/9の第1パターンでは、第1サブフレームで3つの副画素が全て点灯状態となり、第2,第3サブフレームで中央の副画素が点灯状態となる。第2パターンでは、第1,第3サブフレームで中央の副画素が点灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となる。第3パターンでは、第1,第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで3つの副画素が全て点灯状態となる。

【0103】

第4パターンでは、第1,第2サブフレームで上下2つの副画素が点灯状態となり、第3サブフレームで中央の副画素が点灯状態となる。第5パターンでは、第1サブフレームで中央の副画素が点灯状態となり、第2,第3サブフレームで上下2つの副画素が点灯状態となる。第6パターンでは、第1,第3サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態となる。

【0104】

階調6/9の第1パターンでは、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、上下2つの副画素が点灯状態となり、中央の副画素が消灯状態になる。第2パターンでは、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで上下2つの副画素が点灯状態となり、第3サブフレームで中央の副画素が点灯状態となる。第3パターンでは、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで3つの副画素が全て点灯状態となり、第3サブフレームで上下の2つの副画素が点灯状態となる。第4パターンでは、第1サブフレームで上下の2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態となり、第3サブフレームで3つの副画素が全て点灯状態となる。

【0105】

階調7/9の第1パターンでは、第2,第3サブフレームで中央の副画素が消灯状態となり、他の7つの副画素が点灯状態となる。第2パターンでは、第1,第3サブフレームで中央の副画素が消灯状態となり、他の7つの副画素が点灯状態となる。第3パターンでは、第1,第2サブフレームで中央の副画素が消灯状態となり、他の7つの副画素が点灯状態となる。

【0106】

階調8/9の第1パターンでは、第2サブフレームで中央の副画素が消灯状態となり、他の8つの副画素が点灯状態となる。第2パターンでは、第1サブフレームで中央の副画素が消灯状態となり、他の8つの副画素が点灯状態となる。第3パターンでは、第3サブフレームで中央の副画素が消灯状態となり、他の8つの副画素が点灯状態となる。

【0107】

階調9/9では、第1サブフレーム、第2サブフレーム、及び、第3サブフレームのいずれにおいても、3つの副画素が全て点灯状態となる。

【0108】

上述したように、面積比が1:2の面積階調、サブフレーム数が3で、時間比が1:1:1のFRC駆動の実施例2の場合は、9つの副画素のうち全てが消灯状態となる階調0/9から、9つの副画素のうち全てが点灯状態となる階調9/9までの10階調での3倍速の表示となる。

【0109】

(実施例3)

図13は、実施例3に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。実施例3は、面積比が1:4の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の場合の例である。

【0110】

ここで、面積比が1:4とは、3分割の副画素電極において、中央の副画素電極の面積を1とし、上下2つの副画素電極の面積をそれぞれ2としたときの、中央の副画素電極の面積と上下2つの副画素電極のトータル面積との比である。この場合、g=5、f=2であり、表示階調数NgsがNgs=5×2+1=11となるため、0/10〜10/10の11階調での2倍速以上の表示となるが、実際には、後述する理由により、9階調での2倍速以上の表示となる。

【0111】

階調0/10では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て消灯状態となる。

【0112】

階調1/10では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。階調2/10では、第1サブフレーム、第2サブフレーム共に、中央の副画素が点灯状態となる。

【0113】

階調3/10の場合には、上下2つの副画素の同時駆動が前提となっているため、階調3/10を表現する点灯状態の副画素の組合せは存在しない。従って、階調としては、階調2/10と階調4/10との間で不連続となる。階調7/10の場合にも、階調3/10の場合と同様のことが言える。

【0114】

階調4/10では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで3つの副画素の全てが消灯状態となる。

【0115】

階調5/10では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態になるか、または、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる2通りのパターンとなる。但し、該図の右側のパターンの場合には、第1サブフレームと第2サブフレームとの間の輝度差(階調差)が大きいため、フリッカが発生し易い。従って、階調5/10の場合は、2通りのパターンのうち、図の左側のパターンの方が良好な表示状態となる。

【0116】

階調6/10,8/10,9/10,10/10は、階調4/10,2/10,1/10,0/10とそれぞれ補完関係にある。

【0117】

階調6/10では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームで3つの副画素の全てが点灯状態となる。

【0118】

階調8/10では、第1サブフレーム、第2サブフレーム共に、上下2つの副画素が点灯状態となる。

【0119】

階調9/10では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調10/10では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て点灯状態となる。

【0120】

上述したように、面積比が1:4の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の実施例3の場合は、上下2つの副画素の同時駆動が前提となっていることから、階調3/10,7/10が除外されるため、9階調での2倍速以上の表示となる。尚、上下2つの副画素の同時駆動を前提としなければ、即ち、上下2つの副画素を別々の駆動回路で駆動する構成とすれば、階調3/10,7/10を含めた、計11階調の表示は可能となる。

【0121】

また、階調5/10の場合のように、FRCパターン(サブフレームのパターン)の設定において、サブフレーム間の輝度差(階調差)の少ないパターンを設定することで、フリッカの発生を抑えることができるため、より良好な表示状態を得ることができる。

【0122】

(実施例4)

図14は、実施例4に係る点灯状態にある副画素の組合せパターンについての説明に供する図である。実施例4は、面積比が1:3の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の場合の例である。

【0123】

ここで、面積比が1:3とは、3分割の副画素電極において、中央の副画素電極の面積を1とし、上下2つの副画素電極の面積をそれぞれ1.5としたときの、中央の副画素電極の面積と上下2つの副画素電極のトータル面積との比である。この場合、g=4、f=2であり、表示階調数NgsがNgs=4×2+1=9となるため、0/8〜8/8の8階調での2倍速の表示となる。

【0124】

階調0/8では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て消灯状態となる。

【0125】

階調1/8では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。

【0126】

階調2/8では、第1サブフレーム、第2サブフレーム共に、中央の副画素が点灯状態となる。

【0127】

階調3/8では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て消灯状態となる。

【0128】

階調4/8では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームで中央の副画素が点灯状態になるか、または、第1サブフレームで3つの副画素が全て点灯状態となり、第2サブフレームで3つの副画素が全て消灯状態となる2通りのパターンとなる。但し、該図の右側のパターンの場合には、第1サブフレームと第2サブフレームとの間の輝度差(階調差)が大きいため、フリッカが発生し易い。従って、階調4/8の場合は、2通りのパターンのうち、該図の左側のパターンの方が良好な表示状態となる。

【0129】

階調5/8,6/8,7/8,8/8は、階調3/8,2/8,1/8,0/8とそれぞれ補完関係にある。すなわち、階調5/8では、第1サブフレームで中央の副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調6/8では、第1サブフレーム、第2サブフレーム共に、上下2つの副画素が点灯状態となる。階調7/8では、第1サブフレームで上下2つの副画素が点灯状態となり、第2サブフレームでは3つの副画素が全て点灯状態となる。階調8/8では、第1サブフレーム、第2サブフレーム共に、3つの副画素が全て点灯状態となる。

【0130】

上述したように、面積比が1:3の面積階調、サブフレーム数が2で、時間比が1:1のFRC駆動の実施例4の場合は、実施例3の場合と同様に、9階調での2倍速以上の表示となる。但し、実施例3の場合と違って、階調としては、階調0/8から階調8/8まで連続となる。従って、階調の連続性、画面の表示性能としては、実施例3の場合よりも優れている。

【0131】

また、階調4/8の場合のように、FRCパターン(サブフレームのパターン)の設定において、サブフレーム間の輝度差(階調差)の少ないパターンを設定することにより、フリッカの発生を抑えることができるため、より良好な表示状態を得ることができる。

【0132】

また、実施例1乃至実施例4に対して共通に言えることであるが、複数のサブフレームの各々における、点灯状態にある副画素の組合せパターン、即ち、FRCパターンを隣接画素間で変更するようにするのが好ましい。FRCパターンを隣接画素間で変更するようにすることで、変更しない場合に比べてフリッカの発生を抑えることができる。FRCパターンを隣接画素間で変更する方法としては、FRCパターンの反転、順次シフト、あるいは、位相シフトなどの方法を例示することができる。

【0133】

尚、実施例1乃至実施例4では、中央の副画素を挟む上下2つの副画素を1つの駆動回路で同時に駆動することを前提としている。このため、前にも述べたように、サブフレーム内での同時点灯の画素数が結線され、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを一致させるためのFRCパターンの数が制限される。

【0134】

これに対し、上下2つの副画素の同時駆動の構成に限らず、3つの副画素を別々の駆動回路によって独立に駆動する構成とすることも可能である。この構成によれば、上下2つの副画素の点灯パターン以外に、中央の副画素と上の副画素との組合せ、または、中央の副画素と下の副画素との組合せの点灯パターンも可能になるため、トータルのFRCパターンを大幅に増やすことができる。

【0135】

この構成を採る場合は、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを厳密に一致させることができないものの、複数のサブフレーム間で時間的に積分することによって、階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とを実質的に一致させることができる。この場合も、「階調表示の画素の中心と複数のサブフレーム間の表示画像の中心とが一致」の概念に含まれるものとする。

【0136】

以上では、時間比が1:1または1:1:1、即ち、複数のサブフレーム間でサブフレーム時間に重み付け無しのFRC駆動の場合を例に挙げて説明した。このサブフレーム時間に重み付け無しのFRC駆動の部分画面の動画表示において、1フレームの全画面表示周期をTo、単位サブフレーム内での表示階調数を2n 、部分表示のサブフレーム周期をTsfとするとき、全表示階調数Ngsとの間に下記の関係にあることとする。すなわち、全表示階調数をNgsとすると、

Ngs<2n ×(To/Tsf)

の関係にある。

【0137】

図15に、実施例2の場合を例に挙げて、1フレームの全画面表示周期To、単位サブフレーム内での表示階調数2n 、及び、部分表示のサブフレーム周期Tsfと全表示階調数Ngsとの間の関係について示す。実施例2の場合、g=3、f=3であるから、Ngs=3×3+1=10で、全表示階調数Ngsは10階調である。右辺は2n =4、To/Tsf≧3、よって12以上となる。

【0138】

(サブフレーム時間に重み付け有りのFRC駆動)

また、実施例1乃至実施例4では、複数のサブフレーム間でサブフレーム時間に重み付け無しのFRC駆動の場合を例に挙げて説明したが、複数のサブフレーム間でサブフレーム時間に重み付け有りのFRC駆動に対しても同様に適用可能である。一般的なサブフレーム時間重み付け有りFRC駆動の階調表示において、単位サブフレーム内での表示階調数を2n 、サブフレーム周期による階調数(サブフレーム数)を2m とすると、表示階調数Ngsは、Ngs=(2n )m となる。

【0139】

サブフレーム時間に対する重み付けの具体例を図16に示す。図16(A)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:4とし、面積比を1:2とした例である。

【0140】

図16(B)は、1フレームが3つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間:第3サブフレームの時間の比率を1:4:16とし、面積比を1:2とした例である。

【0141】

図16(C)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:8とし、面積比を1:2:4とした例である。図16(D)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:2とし、面積比を1:4とした例である。

【0142】

図16(E)は、1フレームが3つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間:第3サブフレームの時間の比率を1:2:4とし、面積比を1:8とした例である。図16(F)は、1フレームが2つのサブフレームから成るFRC駆動において、第1サブフレームの時間:第2サブフレームの時間の比率を1:2とし、面積比を1:4:16とした例である。

【0143】

上述したように、単位サブフレーム内での表示階調数2n と、サブフレーム数2m との組合せにより、高階調表示が可能となる。図16に示した、サブフレーム時間に対する重み付けの具体例(A)〜(F)の各々における表示階調数2(n+m)は図17に示す通りである。

【0144】

すなわち、図16(A)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:2/(22 )、サブフレーム周期比(時間比)/階調数(2m )が1:4/(22 )、表示階調数2(n+m) が16(=(22 )2 )、サブフレーム周期数が5(=1+4)となる。図16(B)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:2/(22 )、サブフレーム周期比/階調数(2m )が1:4:16/(23 )、表示階調数2(n+m) が64(=(22 )3 )、サブフレーム周期数が21(=1+4+16)となる。

【0145】

図16(C)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:2:4/(23 )、サブフレーム周期比/階調数(2m )が1:8/(22 )、表示階調数2(n+m) が64(=(23 )2 )、サブフレーム周期数が9(=1+8)となる。図16(D)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:4/(22 )、サブフレーム周期比/階調数(2m )が1:2/(22 )、表示階調数2(n+m) が16(=(22 )2 )、サブフレーム周期数が3(=1+2)となる。

【0146】

図16(E)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:8/(22 )、サブフレーム周期比/階調数(2m )が1:2:4/(23 )、表示階調数2(n+m) が64(=(22 )3 )、サブフレーム周期数が7(=1+2+4)となる。図16(F)の具体例の場合は、単位サブフレーム内の面積階調比/階調数(2n )が1:4:16/(23 )、サブフレーム周期比/階調数(2m )が1:2/(22 )、表示階調数2(n+m) が64(=(23 )2 )、サブフレーム周期数が3(=1+2)となる。

【0147】

<3.電子機器>

以上説明した本開示に係る表示装置は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示部(表示装置)として用いることが可能である。

【0148】

先述した実施形態の説明から明らかなように、本開示に係る表示装置は、表示階調数を更に増加させることができるとともに、表示画像に揺らぎが生じないため、表示特性の更なる向上を図ることができる、という特徴を持っている。従って、あらゆる分野の電子機器において、その表示部として本開示に係る表示装置を用いることで、より高画質の画像を表示できる。

【0149】

本開示に係る表示装置を表示部として用いる電子機器としては、例えば、デジタルカメラ、ビデオカメラ、PDA(Personal Digital Assistant)、ゲーム機、ノート型パーソナルコンピュータ、電子書籍等の携帯情報機器、携帯電話機等の携帯通信機器などを例示することができる。

【0150】

<4.本開示の構成>

尚、本開示は以下のような構成を採ることができる。

(1)画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置。

(2)表示画面の中央部付近に部分的に動画を表示する部分動画表示の場合、1フレームの全画面表示周期、部分表示のサブフレーム周期、時分割駆動のサブフレーム数、及び、人の目のちらつきの限界周期の間に、人の目のちらつきの限界周期よりも1フレームの全画面表示周期が小さく、当該全画面表示周期よりも部分表示のサブフレーム周期と時分割駆動のサブフレーム数とで決まる合計サブフレーム周期が小さい関係にある

前記(1)に記載の表示装置。

(3)前記限界周期は、1/50Hzまたは1/60Hzである

前記(2)に記載の表示装置。

(4)入力されるデータに対して減色処理を行って前記駆動部に与える減色処理部を有する

前記(1)から前記(3)のいずれかに記載の表示装置。

(5)前記減色処理部は、誤差拡散法またはディザ法を用いて減色処理を行う

前記(4)に記載の表示装置。

(6)前記駆動部は、前記減色処理部で減色処理されたデータを、当該データよりも少ないビット数のデータにサブフレーム単位で変換する

前記(4)または前記(5)に記載の表示装置。

(7)前記画素は、データを格納するメモリ部を有する

前記(1)から前記(6)のいずれかに記載の表示装置。

(8)前記画素は、メモリ性液晶を用いている

前記(1)から前記(6)のいずれかに記載の表示装置。

(9)前記画素は、複数の副画素から成り、前記複数の副画素の面積の組み合わせによって階調を表示する

前記(1)から前記(8)のいずれかに記載の表示装置。

(10)前記画素の画素電極は、前記複数の副画素毎に複数の電極に分割されており、当該複数の電極の面積の組合せによって階調表示を行う

前記(9)に記載の表示装置。

(11)前記複数の電極は、3つの電極から成り、中央の電極と、当該中央の電極を挟む2つの電極との面積の組合せによって階調表示を行う

前記(10)に記載の表示装置。

(12)前記2つの電極は、面積が同じである

前記(11)に記載の表示装置。

(13)前記2つの電極は、互いに電気的に結線され、1つの駆動回路によって駆動される

前記(11)または前記(12)に記載の表示装置。

(14)前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンの設定において、サブフレーム間の輝度差の少ないパターンを設定する

前記(13)に記載の表示装置。

(15)前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンを隣接画素間で変更する

前記(13)に記載の表示装置。

(16)前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動を行う

前記(1)から前記(15)のいずれかに記載の表示装置。

(17)前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動の部分画面の動画表示において、全表示階調数は、単位サブフレーム内での表示階調数×(1フレームの全画面表示周期/部分表示画面の表示周期)よりも小さい

前記(16)に記載の表示装置。

(18)前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け有りの時分割駆動を行う

前記(1)から前記(17)のいずれかに記載の表示装置。

(19)画素の内部に記憶機能を有する表示装置の駆動に当たって、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示を行い、

階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる

表示装置の駆動方法。

(20)画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置を有する電子機器。

【符号の説明】

【0151】

10・・・表示装置、11・・・減色処理部、12・・・FRC用データ処理部、13・・・表示部、14・・・垂直駆動部、15・・・水平駆動部、16・・・タイミング発生部、20・・・画素、21・・・画素トランジスタ、22・・・液晶容量、23・・・保持容量、31(311,312,313)・・・信号線、32(321,322,323)・・・走査線

【特許請求の範囲】

【請求項1】

画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置。

【請求項2】

表示画面の中央部付近に部分的に動画を表示する部分動画表示の場合、1フレームの全画面表示周期、部分表示のサブフレーム周期、時分割駆動のサブフレーム数、及び、人の目のちらつきの限界周期との間に、人の目のちらつきの限界周期よりも1フレームの全画面表示周期が小さく、当該全画面表示周期よりも部分表示のサブフレーム周期と時分割駆動のサブフレーム数とで決まる合計サブフレーム周期が小さい関係にある

請求項1に記載の表示装置。

【請求項3】

前記限界周期は、1/50Hzまたは1/60Hzである

請求項2に記載の表示装置。

【請求項4】

入力されるデータに対して減色処理を行って前記駆動部に与える減色処理部を有する

請求項1に記載の表示装置。

【請求項5】

前記減色処理部は、誤差拡散法またはディザ法を用いて減色処理を行う

請求項4に記載の表示装置。

【請求項6】

前記駆動部は、前記減色処理部で減色処理されたデータを、当該データよりも少ないビット数のデータにサブフレーム単位で変換する

請求項4に記載の表示装置。

【請求項7】

前記画素は、データを格納するメモリ部を有する

請求項1に記載の表示装置。

【請求項8】

前記画素は、メモリ性液晶を用いている

請求項1に記載の表示装置。

【請求項9】

前記画素は、複数の副画素から成り、前記複数の副画素の面積の組み合わせによって階調を表示する

請求項1に記載の表示装置。

【請求項10】

前記画素の画素電極は、前記複数の副画素毎に複数の電極に分割されており、当該複数の電極の面積の組合せによって階調表示を行う

請求項9に記載の表示装置。

【請求項11】

前記複数の電極は、3つの電極から成り、中央の電極と、当該中央の電極を挟む2つの電極との面積の組合せによって階調表示を行う

請求項10に記載の表示装置。

【請求項12】

前記2つの電極は、面積が同じである

請求項11に記載の表示装置。

【請求項13】

前記2つの電極は、互いに電気的に結線され、1つの駆動回路によって駆動される

請求項11に記載の表示装置。

【請求項14】

前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンの設定において、サブフレーム間の輝度差の少ないパターンを設定する

請求項13に記載の表示装置。

【請求項15】

前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンを隣接画素間で変更する

請求項13に記載の表示装置。

【請求項16】

前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動を行う

請求項1に記載の表示装置。

【請求項17】

前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動の部分画面の動画表示において、全表示階調数は、単位サブフレーム内での表示階調数×(1フレームの全画面表示周期/部分表示画面の表示周期)よりも小さい

請求項16に記載の表示装置。

【請求項18】

前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け有りの時分割駆動を行う

請求項1に記載の表示装置。

【請求項19】

画素の内部に記憶機能を有する表示装置の駆動に当たって、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示を行い、

階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる

表示装置の駆動方法。

【請求項20】

画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置を有する電子機器。

【請求項1】

画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置。

【請求項2】

表示画面の中央部付近に部分的に動画を表示する部分動画表示の場合、1フレームの全画面表示周期、部分表示のサブフレーム周期、時分割駆動のサブフレーム数、及び、人の目のちらつきの限界周期との間に、人の目のちらつきの限界周期よりも1フレームの全画面表示周期が小さく、当該全画面表示周期よりも部分表示のサブフレーム周期と時分割駆動のサブフレーム数とで決まる合計サブフレーム周期が小さい関係にある

請求項1に記載の表示装置。

【請求項3】

前記限界周期は、1/50Hzまたは1/60Hzである

請求項2に記載の表示装置。

【請求項4】

入力されるデータに対して減色処理を行って前記駆動部に与える減色処理部を有する

請求項1に記載の表示装置。

【請求項5】

前記減色処理部は、誤差拡散法またはディザ法を用いて減色処理を行う

請求項4に記載の表示装置。

【請求項6】

前記駆動部は、前記減色処理部で減色処理されたデータを、当該データよりも少ないビット数のデータにサブフレーム単位で変換する

請求項4に記載の表示装置。

【請求項7】

前記画素は、データを格納するメモリ部を有する

請求項1に記載の表示装置。

【請求項8】

前記画素は、メモリ性液晶を用いている

請求項1に記載の表示装置。

【請求項9】

前記画素は、複数の副画素から成り、前記複数の副画素の面積の組み合わせによって階調を表示する

請求項1に記載の表示装置。

【請求項10】

前記画素の画素電極は、前記複数の副画素毎に複数の電極に分割されており、当該複数の電極の面積の組合せによって階調表示を行う

請求項9に記載の表示装置。

【請求項11】

前記複数の電極は、3つの電極から成り、中央の電極と、当該中央の電極を挟む2つの電極との面積の組合せによって階調表示を行う

請求項10に記載の表示装置。

【請求項12】

前記2つの電極は、面積が同じである

請求項11に記載の表示装置。

【請求項13】

前記2つの電極は、互いに電気的に結線され、1つの駆動回路によって駆動される

請求項11に記載の表示装置。

【請求項14】

前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンの設定において、サブフレーム間の輝度差の少ないパターンを設定する

請求項13に記載の表示装置。

【請求項15】

前記複数のサブフレームの各々における、点灯状態にある副画素の組合せパターンを隣接画素間で変更する

請求項13に記載の表示装置。

【請求項16】

前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動を行う

請求項1に記載の表示装置。

【請求項17】

前記複数のサブフレーム間でサブフレーム時間に重み付け無しの時分割駆動の部分画面の動画表示において、全表示階調数は、単位サブフレーム内での表示階調数×(1フレームの全画面表示周期/部分表示画面の表示周期)よりも小さい

請求項16に記載の表示装置。

【請求項18】

前記駆動部は、前記複数のサブフレーム間でサブフレーム時間に重み付け有りの時分割駆動を行う

請求項1に記載の表示装置。

【請求項19】

画素の内部に記憶機能を有する表示装置の駆動に当たって、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示を行い、

階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる

表示装置の駆動方法。

【請求項20】

画素の内部に記憶機能を有し、

1フレームの画像生成を複数のサブフレームに分割して、サブフレーム単位での時分割駆動にて表示駆動を行う駆動部を備え、

前記駆動部は、階調表示の画素の中心と、前記複数のサブフレーム間の表示画像の中心とを一致させる駆動を行う

表示装置を有する電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−57853(P2013−57853A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−196903(P2011−196903)

【出願日】平成23年9月9日(2011.9.9)

【出願人】(598172398)株式会社ジャパンディスプレイウェスト (90)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月9日(2011.9.9)

【出願人】(598172398)株式会社ジャパンディスプレイウェスト (90)

【Fターム(参考)】

[ Back to top ]