表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタを用いたアクティブマトリクス型の表示装置及びその製造方法に関する。

【背景技術】

【0002】

近年、薄膜トランジスタ(TFT:Thin Film Transistor)を画素回路に用いたアクティブマトリクス型表示装置の大型化,画素の高精細化,フレーム周波数の倍増による動画性能向上などが要求されている。最近では、画像を立体的に見せる民生用3D表示装置が発売され、その画質の向上に上述の要求はますます強くなっている。一方、表示装置の価格は予想を上回るペースで下落を続けており、エネルギー資源やレアメタルの高騰など製造コストを押し上げる要因も増大しつつある。従って、更なる製造コスト低減技術を開発することが急務となっている。

【0003】

液晶表示装置の大型化と動画性能や画質の向上、そして製造コスト低減の1つの策として、TFTに適用される配線材料を従来のAl(アルミニウム)またはAl合金からCu(銅)に替える試みがある。Cu配線は従来のAl配線よりも電気抵抗が低いため、配線を伝わる電気信号が遅れる伝播遅延現象を低減でき、さらなる大型化が可能になる。また、フレーム周波数を上げ、動画質向上も可能になる。さらに、Al配線は、ヒロックの発生抑制と透明導電膜との電気的接続を確保するために、Al膜の上下を高価なモリブデン(Mo)で挟んだMo/Al/Moの積層膜構造としているが、Cuは透明導電膜との直接接続が可能であるために省モリブデン化を図ることが可能である。従って、製造コストを低減できる。

【0004】

有機EL表示装置の大型化と画質向上には、従来のAl配線よりも低抵抗な配線材料が求められる。有機EL表示装置の画素回路に設けられる駆動トランジスタは、飽和領域を用いて有機EL層に流れる電流を制御し、その輝度を調整する。表示装置の大型化に伴い配線抵抗による電圧降下が無視できなくなると、想定された電圧が駆動トランジスタに供給されず飽和領域での駆動が不可能になり、結果、輝度むらの原因となる。そこで、表示品位向上のためCu配線の適用が検討されている。

【0005】

しかしながら、Cu配線をTFTに適用する際には以下の問題が存在する。Cuはガラス基板や半導体膜、例えばシリコン(Si)膜や酸化物半導体膜との密着性が悪い。また半導体膜と接する場合、配線形成後の工程で加わる熱により、半導体膜内部にCuが拡散しTFT特性を劣化させ、表示品位を下げる。このような密着性および拡散バリア性問題の対処として、下地膜とCu膜との間にMoやMo合金を形成する方法がある。しかし、前述のようにMoは高価で、また、電気化学的性質の異なる金属の積層構造はエッチングを困難にするため、製造コストが増大する。

【0006】

そこで、熱工程を利用して、自己の添加元素を界面に析出させ、密着性および拡散バリア性に優れた添加元素酸化物を形成させるCu合金を採用する方法がある。ここで熱工程は、CVD(Chemical Vapor Deposition)工程や液晶表示装置での配向膜焼成工程など、配線形成後に薄膜トランジスタ基板が経験する温度を想定している。添加元素酸化物の自己形成には、Cu合金とそれに接する膜の界面に必要十分な酸素原子が予め存在する必要がある。

【0007】

特許文献1ではCuMn合金を推奨し、TFTのゲート電極に適用する方法として、CuMn合金を成膜後に微量の酸化性雰囲気中で加熱処理し、その表面に密着性と拡散バリア性に優れるMn酸化物を形成する方法を提示している。下地のガラス基板は予め必要十分な酸素原子を含有するためMn酸化物の形成は容易である。

【0008】

さらに、特許文献1では、TFTのソース・ドレイン(SD:Source Drain)電極にCu合金を適用する方法として、例えばCu合金成膜前に酸素プラズマ処理を行い、半導体膜上層を改質させ酸化シリコン層SiOxを形成し、添加元素酸化物の形成に必要な酸素を付与する方法を提案している。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2008−282887号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

配線にCuを用いて、Cu配線に酸化性雰囲気中で加熱処理を行うと配線の電気抵抗値が均一にならない。また、配線にCuを用いて、半導体層へプラズマ酸化処理を行うとTFTの電気特性値が均一にならない。

【0011】

本発明は、配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にすることを目的とする。

【課題を解決するための手段】

【0012】

上記課題を解決するための本発明の特徴は以下の通りである。

(1)基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(2)上記(1)において、電極はゲート電極であり、電極近接層はゲート絶縁膜であり、TFTは、半導体層,ソース電極およびドレイン電極を有し、以下の工程を含む表示装置の製造方法(D)基板の上に半導体層,ソース電極およびドレイン電極が形成される工程。

(3)上記(1)において、電極はソース電極およびドレイン電極であり、電極近接層は半導体層であり、TFTはゲート電極およびゲート絶縁膜を有し、以下の工程を含む表示装置の製造方法(E)基板の上にゲート電極およびゲート絶縁膜が形成される工程。

(4)上記(2)または(3)において、ゲート電極の上にソース電極およびドレイン電極が形成される表示装置の製造方法。

(5)上記(2)または(3)において、ソース電極およびドレイン電極の上にゲート電極が形成される表示装置の製造方法。

(6)上記(2)または(3)において、ソース電極およびドレイン電極の上に半導体層が形成される表示装置の製造方法。

(7)上記(2)または(3)において、半導体層の上にソース電極およびドレイン電極が形成される表示装置の製造方法。

(8)上記(2)または(3)において、半導体層は、活性半導体層およびコンタクト膜を含み、活性半導体層およびコンタクト膜は接している表示装置の製造方法。

(9)上記(2)または(3)において、半導体層は、酸化物半導体である表示装置の製造方法。

(10)上記(2)において、以下の工程を含む表示装置の製造方法(F)ソース電極およびドレイン電極がオゾン水で洗浄される工程、(G)(F)の工程後の熱処理により、ソース電極と半導体層との界面およびドレイン電極と半導体層との界面に、酸素を含むソース・ドレイン酸化物膜が形成される工程。

(11)上記(4)において、ゲート電極の上にゲート絶縁膜が形成され、(C)の工程における熱処理は、ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

(12)上記(5)において、TFTは、保護膜を有し、ゲート絶縁膜の上にゲート電極が形成され、ゲート電極の上に保護膜が形成され、(C)の工程における熱処理は、保護膜を形成するための熱処理である表示装置の製造方法。

(13)上記(6)において、(C)の工程における熱処理は、半導体層を形成するための熱処理である表示装置の製造方法。

(14)上記(7)において、TFTは、保護膜を有し、ソース電極およびドレイン電極の上に保護層が形成され、(C)の工程における熱処理は、保護膜を形成するための熱処理である表示装置の製造方法。

(15)上記(3)において、TFTは、保護膜を有し、ソース電極およびドレイン電極の上にゲート絶縁膜が形成され、ゲート絶縁膜の上にゲート電極が形成され、ゲート電極の上に保護膜が形成され、(C)の工程における熱処理は、ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

(16)上記(1)において、酸化物膜中の酸素原子はピークを有し、ピーク値は2at%以上60at%以下であり、基板上でピーク値の3σ/Medianの値は0.5以下である表示装置の製造方法。

(17)上記(2)または(3)において、TFTのチャンネル長Lは、1μm以上100μm以下である表示装置の製造方法。

(18)上記(2)または(3)において、オゾン水の溶存オゾン濃度は、1ppm(mg/L)以上100ppm(mg/L)以下である表示装置の製造方法。

(19)上記(10)において、ゲート電極を洗浄するオゾン水の溶存オゾン濃度は、ソース電極およびドレイン電極を洗浄するオゾン水の溶存オゾン濃度以上である表示装置の製造方法。

【発明の効果】

【0013】

本発明によれば、配線の電気抵抗値とTFTの電気特性値の均一性を損なわずにCu配線適用を実現することが可能になる。

【図面の簡単な説明】

【0014】

【図1】オゾン水酸化処理と熱酸化処理の酸化膜厚と処理時間の関係を示す図である。

【図2(a)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

【図2(b)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

【図2(c)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

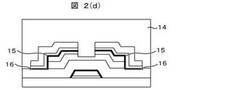

【図2(d)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

【図3(a)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(b)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(c)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(d)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(e)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図4(a)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図4(b)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図4(c)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図4(d)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図5(a)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図5(b)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図5(c)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図5(d)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図6(a)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(b)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(c)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(d)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(e)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図7(a)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図7(b)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図7(c)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図7(d)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図8(a)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図8(b)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図8(c)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図8(d)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図9】液晶表示装置の薄膜トランジスタ基板の画素構成を示す図である。

【図10】液晶表示装置の構成を示す断面図である。

【発明を実施するための形態】

【0015】

以下、本発明にかかるTFTの製造方法と構成およびそれを表示装置に適用する場合の方法について、図面などを用いて説明する。以下の説明は、本願発明の内容の具体例を示すものであり、本願発明がこれらの説明に限定されるものではなく、本明細書に開示される技術的思想の範囲内において当業者による様々な変更および修正が可能である。また、実施例を説明するための全図において、同一の機能を有するものは、同一の符号を付け、その繰り返しの説明は省略する。

【0016】

詳細な実施例の説明に先立ち、電極としてCu配線を採用したTFTの製造にオゾン水酸化処理が適する理由ついて説明する。

【0017】

TFTを用いた電子デバイス、例えばアクティブマトリクス型の表示装置などは薄膜トランジスタ基板全面に渡り配線の電気抵抗値とTFTの電気特性値に高い均一性を要する。ここでTFTの電気特性値とは、移動度,閾値電圧,S値(サブスレショルドスウィング),オフ特性などを指す。この配線の電気抵抗値とTFTの電気特性値の均一性を左右するのが、酸化膜質(酸化膜の厚さと酸素含有量)の均一性である。

【0018】

Cu合金をTFTのゲート電極に適用する手段として、酸化性雰囲気中で200℃〜500℃の加熱処理を行い、添加元素酸化物を形成する方法がある。しかしながら、酸化種の熱拡散を利用した酸化方法は、酸化膜厚の処理時間依存性が大きいことや基板の温度分布に起因して薄膜トランジスタ基板上の一部で配線の電気抵抗値に大きなバラツキが生じる。また、配線の電気抵抗値の低減を図り、Cu合金層の上に純度99.9%以上の純Cu層を形成した「純Cu/Cu合金」または「Cu合金/純Cu/Cu合金」の積層配線があるが、これに酸化性雰囲気中で加熱処理を施すと純Cu層の加工断面から必要以上に酸化が進み、結果、配線の電気抵抗値は上昇し純Cuを導入した効果を失う。

【0019】

Cu合金をTFTのSD電極に適用する手段として、Cu合金の成膜前に酸素プラズマ処理を行い、添加元素酸化物の形成に必要な酸素を付与する方法がある。しかしながら、酸素プラズマ処理はプラズマ密度の分布に起因して、薄膜トランジスタ基板上で酸化膜質にばらつきが生じ、その結果、酸化が不十分な箇所ではCu原子の拡散が抑制できなくなり、TFT特性の低下を招く。また、薄膜トランジスタ基板全面にわたってCu原子の拡散を防ぐ目的で酸素プラズマ処理の酸化度合いを強くすると、今度は一部で必要以上に厚い酸化膜が形成される。この酸化膜が添加元素と化合せずに半導体層側で残存すると、電流経路に寄生抵抗をつくる。実際に電子デバイスや表示装置に用いられるTFTのチャンネル長は1〜100μm程度で、このサイズ領域では寄生抵抗の大きさが移動度の値を大きく左右する。したがって、不要な酸化膜の残存による寄生抵抗の上昇は移動度を急減させ、TFTのオン特性低下を引き起こし、表示品位を劣化させる。

【0020】

その他の酸化手法に、酸素より酸化性の強いオゾンを含む雰囲気下にCu配線や半導体層を暴露する方法があるが、この手法ではCu原子の拡散を抑制できる十分な酸化膜質の形成が難しく、さらにガスが噴射するシャワーヘッドの穴の位置を反映して酸化膜質にバラツキが生じる。必要な酸化膜を得るために200℃〜500℃の加熱処理を施す方法もあるが、上述のゲート電極に適用する手段と同様の理由で適用は困難である。

【0021】

また、オゾンガスに紫外波長域の光を照射し酸化性が極めて強い励起状酸素原子を生成させ、それをCu配線や半導体層に暴露し、極薄酸化膜を形成する光酸化法もある。しかしながら、光酸化法は紫外光を照射するランプの強度分布に依存して酸化膜質に大きなバラツキが生じる。

【0022】

そこで、薄膜トランジスタ基板の全面に渡って酸化膜質の均一性に優れる酸化手法に、オゾン水酸化法がある。オゾン水とCu配線や半導体膜が接触した瞬間、それら界面近傍では互いのコンタクトポテンシャルの差から強い電界が生じる。オゾン水中の酸化種、例えばO- などのアニオンは、その電界によりCu配線や半導体層へ運ばれ酸化膜を形成する。したがって、オゾン水酸化法はこの界面近傍のみに生じる電界と溶存オゾン濃度が酸化膜質を律則する。

【0023】

例として図1に、オゾン水酸化処理(実線)と酸化性雰囲気下で熱酸化処理(点線)を行った際の酸化膜厚と処理時間の関係を示す。各処理はシリコン基板へ行い、酸化膜厚はSiO2に換算して算出する。熱酸化処理は酸化膜厚の処理時間依存性が大きいことが分かる。このような特性は、極薄の酸化膜が要求される場合、例えば5nm以下の酸化膜を作製する際は薄膜トランジスタ基板上で膜厚ばらつきが大きくなることを示唆する。それに対し、オゾン水酸化処理の酸化膜厚は処理開始と同時に急峻に立ち上がった後、素早く飽和する特性を見せ、処理時間依存性が熱酸化法に比べ小さい。この特性を有するため、オゾン水酸化処理は薄膜トランジスタ基板の全面に渡り酸化膜質の均一性を確保する。これは、熱酸化法が拡散律則なのに対し、オゾン水酸化法が界面電界に律則されるためである。なお、基板に200℃〜500℃の加熱処理を加えながらプラズマ酸化法や光酸化法を行う場合も、図1の点線の熱酸化法と同様の特性を示した。

【0024】

なお、オゾン水酸化法を適用したTFTの酸化物膜中の酸素原子濃度はピークを有している。そのピーク値が2at%未満の場合、Cu原子の拡散を抑制するのに十分な酸化膜が形成できない。また、60at%を超えていると、半導体層の奥で酸化膜が残存し電流経路の寄生抵抗となり移動度を急減させる。したがって、酸素原子濃度のピーク値は、2at%以上60at%以下となるように溶存オゾン濃度を調整する必要がある。また、TFT基板上で、ピーク値のばらつきは3σ/Medianの値で0.5以下となるようにする必要がある。これは、3σ/Medianが0.5を超えているとTFT電気特性値が大きくばらつき、表示装置に適用した際に輝度むらが明確に確認できるためである。これらの条件を満足する溶存オゾン濃度は1〜100ppmの範囲にある。

【0025】

以下、具体的なオゾン水酸化処理条件についてTFT製造方法を説明しながら述べる。

【実施例1】

【0026】

以下に、実施例1のTFTの製造法について説明する。本実施例のTFTはボトムゲート型で、半導体層を形成した後にソース電極及びドレイン電極が形成される構造を有する。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。

【0027】

図2(a)〜図2(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、Cu合金2をスパッタリング法により成膜する。膜厚は10nm〜150nmの程度であり、20nm〜50nmが好適である。ここで成膜するCu合金2は、基板1との密着性発現の役割を担う。Cu合金2中のCu以外の添加元素としては、例えば、Mn,Mg,Ca,Ni,Zn,Si,Al,Be,Ga,In,Fe,Ti,V,Co,Zr,Hf、などから1種類以上、Cu合金2中の添加元素の添加量は0.5〜10原子%が好ましい。また、後の熱を伴う製造工程でCu合金2中の添加元素が界面へ拡散し酸化物を形成するために、基板1は必要十分な酸素原子数を予め含有していることが望ましい。例えば、無アルカリガラス基板はこの条件を満たしている。本実施例では、Cu中にMnが4at%添加されたCu−Mn合金を50nmほど成膜した。

【0028】

次に、純Cu3を同様にスパッタリング法にて連続成膜する。膜厚は100〜1000nmの程度で、約200〜500nmが好適である。本実施例ではCu−Mn合金上に純Cuを300nmほど成膜した。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0029】

次いで、オゾン水洗浄を行い、ゲート絶縁膜5を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、1〜50ppmが好適である。濃度が1ppmを下回るとゲート絶縁膜5へのCu原子の拡散が抑制できず、また、100ppmを超えると純Cu3の電気抵抗値が著しく上昇するためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。本実施例では、溶存オゾン濃度20ppmのオゾン水を用いて、1分ほど洗浄した。ここで、図2(a)に示すような、純Cu3およびCu合金2を含むゲート電極4が作製される。ゲート電極4では、電流経路に酸化物膜6が形成されないため、酸化物膜6の膜厚をソース電極12およびドレイン電極13に形成される酸化物膜15の膜厚以上としてもよい。この場合、ゲート電極4に適用するオゾン水の溶存オゾン濃度をソース電極12およびドレイン電極13に適用するオゾン水の溶存オゾン濃度以上にする。ソース電極12とドレイン電極13にCuおよびCu以外の元素が含まれている場合、ゲート電極4はCu合金10および純Cu11でもよいし、Mo/Al合金/Moなどで形成されていてもよい。

【0030】

基板1は無アルカリガラス以外に、フレキシブルなプラスチック基板やステンレス合金などの金属性の基板でも良い。基板からCu層への不純物拡散を気にする場合は、基板上にバリア膜として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を形成しても良い。その際、バリア膜に十分な酸素原子が備わっていない場合、Cu合金2の成膜前に同様のオゾン水洗浄を行い、バリア膜表面に酸化膜を形成する方法が有効である。

【0031】

次に、図2(b)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。膜厚は10nm〜1000nmの程度で、50〜400nmが好適である。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は酸化物膜6を自己形成する。酸化物膜6はゲート絶縁膜5の構成材料、ゲート電極4の構成材料および酸素を含む。酸化物膜15および酸化物膜16が形成されている場合、酸化物膜6は必ずしも形成されている必要はない。オン電流の低下を抑制する観点から、酸化物膜6の膜厚より酸化物膜15の膜厚を小さくすることが望ましい。

【0032】

次いで、プラズマCVD法,スパッタリング法,塗布法により、例えば、活性半導体層7として水素化アモルファスシリコン膜(a−Si:H),コンタクト膜8としてリン(P)をドープした水素化アモルファスシリコン膜(n+a−Si:H)を順次成膜し半導体層9を形成する。活性半導体層7は、不純物が混入されていない半導体であり、ゲート電極4への電圧印加により導電層を形成する層である。活性半導体層7として、微結晶シリコンや多結晶シリコンでもよく、水素化アモルファスシリコン,微結晶シリコン,多結晶シリコンの積層膜でもよい。コンタクト膜8は、活性半導体層7とソース電極12およびドレイン電極13との接触で生じる寄生抵抗を低減させる目的で、活性半導体層7とソース電極12およびドレイン電極13と間に設けられる層である。コンタクト膜8には不純物が混入されている。コンタクト膜8として、微結晶シリコンや多結晶シリコンでもよい。活性半導体層7の膜厚は10〜300nmの程度で30〜200nmが好適で、コンタクト膜8の膜厚は1〜100nmの程度で5〜60nmが好適である。

【0033】

本実施例では、プラズマCVD法を用いて、ゲート絶縁膜5に窒化シリコン膜を350nm程度、活性半導体層7として水素化アモルファスシリコン膜を180nm程度、コンタクト膜8としてリン(P)をドープした水素化アモルファスシリコン膜を25nm程度形成した。

【0034】

次に、図2(b)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法を用いて、活性半導体層7およびコンタクト膜8を含む半導体層9を島パターニングし、レジストを剥離する。半導体層9が電極近接層となる。

【0035】

次に、オゾン水洗浄を行い、半導体層9へのCu原子拡散を抑制する極薄酸化膜(図示せず)を半導体層9の表面に形成する。この時、極薄酸化膜(図示せず)はゲート絶縁膜5の表面でも同時に形成される。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適で、5〜30ppmがさらに好適である。濃度が1ppmを下回ると半導体層9へのCu原子の拡散が抑制できず、また、100ppmを超えると酸化膜は半導体層9側で不必要に厚く形成されCu合金中の添加元素と化合せずに半導体層9側の奥で残存し、電流経路に寄生抵抗をつくり、結果、移動度を急減させる。本実施例では、溶存オゾン濃度20ppmのオゾン水を用いて、1分ほど洗浄を行い、半導体層9上に約1nmほどの極薄シリコン酸化膜を形成した。ソース電極12およびドレイン電極13では、電流経路に酸化物膜15が形成されるため、酸化物膜15の膜厚を酸化物膜6の膜厚以下にしてもよい。この場合、ソース電極12およびドレイン電極13に適用するオゾン水の溶存オゾン濃度をゲート電極4に適用するオゾン水の溶存オゾン濃度以下にする。本実施例では、ソース電極12およびドレイン電極13に適用するオゾン水の溶存オゾン濃度とゲート電極4に適用するオゾン水の溶存オゾン濃度とを20ppmでほぼ同じにしている。これにより、酸化物膜6および酸化物膜15の要求性能を共に満足できる。

【0036】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。Cu合金10の膜厚は10〜150nmの程度で20nm〜50nmが好適で、純Cu11の膜厚は100〜1000nmの程度で、約200〜500nmが好適である。Cu合金10に添加されるCu以外の元素としては、例えば、Mn,Mg,Ca,Ni,Zn,Si,Al,Be,Ga,In,Fe,Ti,V,Co,Zr,Hf、などから1種類以上、添加量は0.5〜10原子%が好ましい。本実施例では、Cu中にMnが4at%混入したCu−Mn合金を50nmほど、Cu−Mn合金上に純Cuを300nmほど成膜した。本実施例では、ゲート電極4とソース電極12およびドレイン電極13とが同じ材料で作製されているが、Cu合金の添加元素を変える等、違う材料としてもよい。ゲート電極4とソース電極12およびドレイン電極13とを同じ材料にすることで、製造コストを削減できる。

【0037】

その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、Cu合金10および純Cu11を含むソース電極12,Cu合金10および純Cu11を含むドレイン電極13を形成する。ゲート電極4にCuおよびCu以外の元素が含まれている場合、ソース電極12とドレイン電極13はCu合金10および純Cu11で形成されていても良いし、Mo/Al合金/Moなどで形成されていてもよい。

【0038】

次いで、図2(c)に示すように、ソース電極12とドレイン電極13形成に使用したフォトレジストをそのまま利用し、ドライエッチング法によりチャンネル上の極薄酸化膜(図示せず)とコンタクト膜8を除去し、レジストを剥離する。極薄酸化膜(図示せず)は数Å〜数nmと非常に薄いためドライエッチングの妨げにはならない。

【0039】

次に、図2(d)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。保護膜14の膜厚は100〜1000nmの程度で、200〜500nmが好適である。このとき、保護膜14の形成温度は200℃以上となるため、ソース電極12及びドレイン電極13下層にあるCu合金10中のCu原子と添加元素が界面に析出される。本実施例のように、保護膜14の形成温度をゲート絶縁膜5の形成温度より小さくすることで、半導体層の劣化を抑制できる。界面に析出したCu原子と添加元素は、コンタクト膜8上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れなお且つ低電気抵抗な酸化物膜15を自己形成する。酸化物膜15は、半導体層9の構成材料,Cu合金10の構成材料および酸素を含む。

【0040】

この際、ゲート絶縁膜5直上の極薄酸化膜(図示せず)でも同様に密着性及び拡散バリア性に優れる酸化物膜16を自己形成するため、ソース電極12及びドレイン電極13の膜剥がれは起きない。酸化物膜16は、ゲート絶縁膜5の構成材料,Cu合金10の構成材料および酸素を含む。本実施例では、保護膜14に窒化シリコン膜を300nmほど形成した。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例1の表示装置向けボトムゲート型TFTを作製することができる。酸化物膜6が形成されている場合、酸化物膜15および酸化物膜16は必ずしも形成されている必要はない。

【0041】

ここで、本実施例と、拡散バリア性と密着性の確保にMoを採用した従来技術のTFTについて、電気特性値を比較評価した結果を述べる。評価したTFTの素子サイズは、チャンネル幅(ゲート幅とも呼ぶ)Wは100μm、チャンネル長(ゲート長とも呼ぶ)Lは10μmで、実際に表示装置に採用される素子サイズに近く、寄生抵抗が移動度の値を大きく左右する領域である。ソース・ドレイン電圧は10Vで、移動度や閾値電圧は飽和領域より算出した。ゲート電極4にMo/Al合金/Mo、ソース電極12及びドレイン電極13にMo/Al合金/Moを採用し、本実施例の工程でオゾン水酸化処理を省略し、同様の工程を経て作製したTFTの電気特性を評価すると、飽和移動度は0.60cm2/Vsほど、飽和閾値電圧は1〜3Vほど、S値は0.9〜1.1V/decほどであった。

【0042】

ゲート電極4に純Cu/Cu−Mn合金,ソース電極12及びドレイン電極13に純Cu/Cu−Mn合金を採用した本実施例のTFTの電気特性は、飽和移動度は0.58cm2/Vsほど、飽和閾値電圧は1.5Vほど、S値は0.98V/decで、Moを採用した従来技術のTFTとほぼ同等の性能であった。また、オフ電流の上昇も少なく、オフ特性は従来技術のTFTと同等であった。これは、ゲート絶縁膜5や半導体層9へCu原子の拡散が抑制されていること、ソース電極12及びドレイン電極13と半導体層9との界面に寄生抵抗としてはたらく酸化膜がないことを示唆する。

【0043】

したがって、本実施例のTFTによれば、熱工程を利用してCu合金中の添加元素を界面に析出させ、密着性および拡散バリア性に優れた添加元素酸化物を自己形成させる技術に必要な酸化処理にはオゾン水酸化処理が有効であることが分かる。

【0044】

本実施例では、ゲート電極4,ソース電極12,ドレイン電極13はCu合金と純Cuの積層から構成されるが、Cu合金の単層でも良い。その場合の添加元素として、低電気抵抗である理由から、例えば、Mg,Znが好ましい。また、Cu合金/純Cu/Cu合金の3層構造であっても良い。TFT電気特性の改善を狙い、チャンネルエッチストッパ構造を採用しても構わない。

【0045】

半導体層9から外に伸びたソース電極12及びドレイン電極13とゲート絶縁膜5との密着性をより強固にしたい場合は、ゲート絶縁膜5を形成した直後にオゾン水酸化処理を行いゲート絶縁膜5上に酸化膜を形成する手法が有効である。また、ソース電極12及びドレイン電極13と保護膜14との界面からCu原子が拡散し保護膜14の密着性が脆弱になる場合は、保護膜14を形成する前にオゾン水酸化処理を行っても良い。

【実施例2】

【0046】

以下に、実施例2のTFTの製造法について説明する。本実施例のTFTはボトムゲート型で、半導体層を形成する前にソース電極及びドレイン電極が形成される構造を有する。なお、正確な膜厚を反映するとTFT構造に煩雑になるため図は模式的に示す。なお、本実施例と実施例1とで重複する説明は端的に述べる。

【0047】

図3(a)〜図3(e)は、各工程時のTFT断面図である。まず、基板1上に、Cu合金2をスパッタリング法により成膜する。ここで成膜するCu合金2は、基板1との密着性発現の役割を担う。

【0048】

次に、純Cu3を同様にスパッタリング法にて連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0049】

次いで、オゾン水洗浄を行い、ゲート絶縁膜5を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。ここで、図3(a)に示すようなゲート電極4が作製される。

【0050】

次に、図3(b)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を成膜する。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)はゲート絶縁膜5とゲート電極4の構成元素で酸化物膜6を自己形成する。

【0051】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。濃度が1ppmを下回るとゲート絶縁膜5へのCu原子の拡散が抑制できず、また、100ppmを超えると厚い酸化膜が形成され、コンタクトホールを形成する際に酸化膜を除去する工程が別途必要になるためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。具体的には、ゲート絶縁膜5に2at%以上の酸素原子が含有されていることが望ましい。

【0052】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図3(c)に示すように、ソース電極12,ドレイン電極13を形成する。ソース電極12,ドレイン電極13のパターニングはリフトオフ法であってもよい。

【0053】

次に、オゾン水洗浄を行い、半導体層へのCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu11とCu合金10の表面に形成する。このとき、ゲート絶縁膜5の表面もオゾン水に暴露され、極薄酸化膜(図示せず)が形成される。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。濃度が1ppmを下回ると半導体層へのCu原子の拡散が抑制できず、また、100ppmを超えると純Cu11の電気抵抗値が著しく上昇するためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。ソース電極12,ドレイン電極13をオゾン水で洗浄をすることにより、半導体層9への酸素原子の拡散を抑え、寄生抵抗を低減でき、オン電流を上昇できる。半導体層9をオゾン水で洗浄する場合に比べて、溶存オゾン濃度を高くできる。

【0054】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、コンタクト膜8としてリン(P)をドープした水素化アモルファスシリコン膜(n+a−Si:H)を成膜する。その後、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いてコンタクト膜8をパターニングし、レジストを剥離する。次いで、プラズマCVD法,スパッタリング法,塗布法により、例えば、活性半導体層7として水素化アモルファスシリコン膜(a−Si:H)を成膜し、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離し、図3(d)に示すように半導体層9を形成する。半導体層9が電極近接層となる。このとき、半導体層9の形成時の温度は200〜400℃の程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、極薄酸化膜(図示せず)と化合し、ゲート絶縁膜5との界面で密着性に優れた酸化物膜16を自己形成する。活性半導体層7を介することなく、ソース電極12,ドレイン電極13とコンタクト膜8とが直に接しているため、活性半導体層7の膜厚抵抗が無く、寄生抵抗が低減し、オン電流を向上できる。

【0055】

その後、半導体層9形成時の熱により極薄酸化膜(図示せず)は酸化物膜15を自己形成する。酸化物膜15は、拡散バリア層として機能し、Cu原子のコンタクト膜8中への拡散を抑制する。なお、電流はソース電極12及びドレイン電極13の下層にあるCu合金10がつくる酸化物膜15とコンタクト膜8の間を横切る。したがって、Cu合金10とコンタクト膜8の界面に形成される酸化物膜15は、低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0056】

次に、図3(e)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例2の表示装置向けボトムゲート型TFTを作製することができる。

【実施例3】

【0057】

以下に、実施例3のTFTの製造法について説明する。本実施例のTFTはトップゲート型で、半導体層を形成する前にソース電極及びドレイン電極が形成される構造を有する。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1及び実施例2とで重複する説明は端的に述べる。

【0058】

図4(a)〜図4(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、基板1との密着性を確保するためCu合金10をスパッタリング法により成膜する。次に、純Cu11を同様にスパッタリング法にて連続成膜する。

【0059】

その次に、例えば、Cu合金10と同じ材料からなるCu合金17をスパッタリング法により連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0060】

次いで、オゾン水洗浄を行い、半導体層を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)をCu合金17と純Cu11とCu合金10の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。ここで、図4(a)に示すようなソース電極12,ドレイン電極13が作製される。

【0061】

次に、プラズマCVD法,スパッタリング法,塗布法により、コンタクト膜8として例えばリン(P)をドープした水素化アモルファスシリコン膜(n+a−Si:H)を成膜する。その後、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いてコンタクト膜8をパターニングし、レジストを剥離する。

【0062】

次いで、プラズマCVD法,スパッタリング法,塗布法により、活性半導体層7として例えば水素化アモルファスシリコン膜(a−Si:H)を成膜し、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離し、図4(b)に示すように半導体層9を形成する。半導体層9が電極近接層となる。このとき、半導体層9の形成時の温度は200〜400℃の程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、基板1の界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、コンタクト膜8とソース電極12及びドレイン電極13の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のコンタクト膜8中への拡散を抑制する。

【0063】

その後、半導体層9形成時の熱により極薄酸化膜(図示せず)はコンタクト膜8とソース電極12及びドレイン電極13の構成元素で酸化物膜15を自己形成する。なお、電流は、ソース電極12及びドレイン電極13の上層にあるCu合金17がつくる酸化物膜15とコンタクト膜8の間を横切る。したがって、Cu合金17とコンタクト膜8の界面に形成される酸化物膜15は低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0064】

次に、図4(c)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。

【0065】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0066】

次に、スパッタ法により、Cu合金2,純Cu3からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、ゲート電極4を形成する。

【0067】

次に、図4(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ゲート電極4下層にあるCu合金2中の添加元素が界面に析出される。界面に析出した添加元素は、ゲート絶縁膜5上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れる酸化物膜18を自己形成する。酸化物膜18は、ゲート絶縁膜5の構成材料,Cu合金10の構成材料および酸素を含む。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例3の表示装置向けトップゲート型TFTを作製することができる。本実施例ではゲート絶縁膜5へオゾン水洗浄を行うため、酸化物膜18中の酸素原子はゲート電極4が存在する側よりゲート絶縁膜5が存在する側で多く、ゲート電極4へオゾン水洗浄を行う場合に比べて電気抵抗値の上昇を抑制できる。

【実施例4】

【0068】

以下に、実施例4のTFTの製造法について説明する。本実施例のTFTは、実施例1と同様にボトムゲート型で、半導体層を形成した後にソース電極及びドレイン電極を形成する構造を有するが、半導体層に酸化物半導体を用いているのが主な特徴である。酸化物半導体はその界面や膜中で酸素の欠損が生じるとTFT特性が大きく劣化する。また、酸化物半導体とゲート絶縁膜の界面、および、酸化物半導体と保護膜やチャンネルエッチストッパ膜の界面に多量の水素が存在してもTFT特性に悪影響を及ぼす。これら問題の解決にもオゾン水酸化法は有効である。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至3とで重複する説明は端的に述べる。

【0069】

図5(a)〜図5(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、Cu合金2をスパッタリング法により成膜する。次に、純Cu3を同様にスパッタリング法にて連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0070】

次いで、オゾン水洗浄を行い、ゲート絶縁膜5を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。ここで、図5(a)に示すようなゲート電極4が作製される。

【0071】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。膜厚は10nm〜1000nmの程度で、50〜400nmが好適である。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は酸化物膜6を自己形成する。

【0072】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。濃度が1ppmを下回るとゲート絶縁膜5へのCu原子の拡散が抑制できず、また、100ppmを超えると厚い酸化膜が形成され、コンタクトホールを形成する際に酸化膜を除去する工程が別途必要になるためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。加えて、ゲート絶縁膜5中に多量の水素が存在する場合、後の熱を伴う工程でゲート絶縁膜5と酸化物半導体の界面へ水素が拡散し、その結果、閾値電圧のシフトが起こりTFT特性の信頼性に悪影響を及ぼすことがある。更に、後の熱を伴う工程で酸化物半導体中の酸素がゲート絶縁膜5へ拡散すると、酸素の欠陥が生じTFT特性が劣化することがある。ゲート絶縁膜5へオゾン水洗浄を行い表面に良質な極薄酸化膜を形成することで、ゲート絶縁膜5からの水素の拡散と酸化物半導体中からの酸素の拡散を抑制し、良好なTFT特性を確保することができる。なお、このオゾン水酸化処理工程は下地となるゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0073】

次いで、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、活性半導体層7として酸化物半導体を成膜する。活性半導体層7が電極近接層となる。金属化合物を酸化して形成される酸化物半導体は、ソース電極12及びドレイン電極13との寄生抵抗が小さく、意図的に不純物がドープされたコンタクト膜を形成しなくても十分なオン電流を確保できる。酸化物半導体は、例えば、酸化亜鉛,酸化インジウム,酸化ガリウム,酸化錫,酸化銅,酸化ジルコニウム,酸化チタン,酸化アルミニウム銅,酸化亜鉛錫,酸化亜鉛インジウム,酸化ガリウムインジウム,酸化亜鉛ガリウム錫,酸化インジウムマグネシウム,酸化亜鉛ガリウムインジウムなどがあり、Zn,In,Ga,Sn,Al,Ti,Mg,Zr,Cuから少なくとも1種以上の元素を含む酸化物より成る。酸化物半導体として、アモルファスでも多結晶でもよく、これらの積層膜でもよい。その中でもTFTの電気特性の均一性に優れるIn−Ga−Zn−O系の酸化物半導体を用いるのが好ましい。活性半導体層7の膜厚は1〜300nmの程度で20〜100nmが好適である。

【0074】

次に、図5(b)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0075】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)を活性半導体層7の表面に形成する。この時、酸化物半導体から成る活性半導体層7へ極薄酸化膜(図示せず)を形成する意味は3つある。第1の意味は、実施例1乃至実施例3で述べたように、活性半導体層7へのCu原子の拡散を抑制することである。第2の意味は、本実施例のようにCu合金中の添加元素が活性半導体層7側から酸素を奪い酸化物膜6を自己形成する場合、酸化物半導体の表面の酸素原子含有量が薄膜トランジスタ基板上でバラつくと、それを反映してTFT電気特性値も大きくバラつくためである。フォトリソグラフィ工程で酸化物半導体の表面はダメージを受け酸素含有量にばらつきが生じるため、オゾン水処理により酸素原子を基板上で均一に付与するのである。第3の意味は、酸化物半導体中の酸素がCu合金側へ拡散するのを防ぎ、TFT特性の劣化を抑制するためである。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。濃度が1ppmを下回ると活性半導体層7へのCu原子の拡散が抑制できず、また、100ppmを超えると酸化膜は活性半導体層7側で不必要に厚く形成されCu合金中の添加元素と化合せずに活性半導体層7側の奥で残存し、電流経路に寄生抵抗をつくり、結果、移動度を急減させる。

【0076】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。Cu合金10の膜厚は10〜150nmの程度で20nm〜50nmが好適で、純Cu11の膜厚は100〜1000nmの程度で、約200〜500nmが好適である。

【0077】

その後、図5(c)に示すように、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、ソース電極12,ドレイン電極13を形成する。このとき、活性半導体層7上に形成した極薄酸化膜(図示せず)はウェットエッチングで用いるエッチャントから活性半導体層7を保護する役割も担う。

【0078】

次に、図5(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。保護膜14の膜厚は100〜1000nmの程度で、200〜500nmが好適である。このとき、保護膜14の形成温度は200℃以上となるため、ソース電極12及びドレイン電極13下層にあるCu合金10中のCu原子と添加元素が界面に析出される。界面に析出したCu原子と添加元素は、活性半導体層7上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れなお且つ低電気抵抗な酸化物膜15を自己形成する。この際、ゲート絶縁膜5直上の極薄酸化膜(図示せず)でも密着性及び拡散バリア性に優れる酸化物膜16を自己形成するため、ソース電極12及びドレイン電極13の膜剥がれは起きない。なお、保護膜14が多量の水素を含む場合、水素が活性半導体層7へ拡散しTFT特性に悪影響を及ぼす。水素の拡散を抑制するため、保護膜14の成膜前にオゾン水酸化処理を行い活性半導体層7の表面に極薄酸化膜を形成しても良い。このオゾン水酸化処理はソース電極12およびドレイン電極13のパターニングで生じた活性半導体層7の酸素欠損を補う効果もある。

【0079】

これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例4の表示装置向け酸化物半導体TFTを作製することができる。

【0080】

また、TFT電気特性を安定かつ均一にするため、酸化物半導体の形成後に熱処理を別途に加えてもよい。熱処理はソース電極12及びドレイン電極13の形成後に行うのが好ましい。ソース電極12及びドレイン電極13中の添加元素の拡散が促進され酸化物膜15,酸化物膜16が得やすくなるためである。

【実施例5】

【0081】

以下に、実施例5のTFTの製造法について説明する。本実施例のTFTは、実施例2と同様にボトムゲート型で、半導体層を形成する前にソース電極及びドレイン電極を形成する構造を有するが、半導体層に酸化物半導体を用いているのが主な特徴である。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至実施例4とで重複する説明は端的に述べる。

【0082】

図6(a)〜図6(e)は、各工程時のTFT断面図である。まず、基板1上に、Cu合金2をスパッタリング法により成膜する。次に、純Cu3を同様にスパッタリング法にて連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。次いで、オゾン水洗浄を行い、ゲート絶縁膜を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。ここで、図6(a)に示すようなゲート電極4が作製される。

【0083】

次に、図6(b)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。膜厚は10〜1000nmの程度で、50〜400nmが好適である。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)はゲート絶縁膜5とゲート電極4の構成元素で酸化物膜6を自己形成する。

【0084】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0085】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図6(c)に示すように、ソース電極12,ドレイン電極13を形成する。

【0086】

次に、オゾン水洗浄を行い、活性半導体層へのCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu11とCu合金10の表面に形成する。このとき、ゲート絶縁膜5の表面もオゾン水に暴露され、極薄酸化膜(図示せず)が形成される。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。

【0087】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、活性半導体層7として実施例4の酸化物半導体を成膜する。活性半導体層7が電極近接層となる。

【0088】

次に、図6(d)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0089】

次に、図6(e)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ソース電極12及びドレイン電極13下層にあるCu合金10中のCu原子と添加元素が活性半導体層7との界面に析出し、密着性及び拡散バリア性に優れなお且つ低電気抵抗な酸化物膜15を自己形成する。この際、ゲート絶縁膜5直上の極薄酸化膜(図示せず)でも密着性及び拡散バリア性に優れる酸化物膜16を自己形成するため、ソース電極12及びドレイン電極13の膜剥がれは起きない。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例5の表示装置向け酸化物半導体TFTを作製することができる。

【実施例6】

【0090】

以下に、実施例6のTFTの製造法について説明する。本実施例のTFTは、実施例3と同様にトップゲート型で、半導体層を形成する前にソース電極及びドレイン電極を形成する構造を有するが、半導体層に酸化物半導体を用いているのが主な特徴である。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至5とで重複する説明は端的に述べる。

【0091】

図7(a)〜図7(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、Cu合金10をスパッタリング法により成膜する。次に、純Cu11を同様にスパッタリング法にて連続成膜する。その次に、例えば、Cu合金10と同じ材料のCu合金17をスパッタリング法により連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。次いで、オゾン水洗浄を行い、活性半導体層7を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)をCu合金17と純Cu11とCu合金10の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。ここで、図7(a)に示すようなソース電極12,ドレイン電極13が作製される。

【0092】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、活性半導体層7として実施例4の酸化物半導体を成膜する。

【0093】

次に、図7(b)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。活性半導体層7が電極近接層となる。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0094】

次に、図7(c)に示すように、プラズマCVD法,スパッタリング法,塗布法により、ゲート絶縁膜5として例えば酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。このとき、ゲート絶縁膜5の形成時の200〜500℃程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、基板1の界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、活性半導体層7とソース電極12及びドレイン電極13の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子の活性半導体層7中への拡散を抑制する。その後ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は活性半導体層7とソース電極12及びドレイン電極13の構成元素で酸化物膜15を自己形成する。なお、電流はソース電極12及びドレイン電極13の上層にあるCu合金17がつくる酸化物膜15と活性半導体層7の間を横切る。したがって、Cu合金17と活性半導体層7の界面に形成される酸化物膜15は低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0095】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0096】

次に、スパッタ法により、Cu合金2,純Cu3からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、ゲート電極4を形成する。

【0097】

次に、図7(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ゲート電極4下層にあるCu合金2中の添加元素が界面に析出される。界面に析出した添加元素は、ゲート絶縁膜5上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れる酸化物膜18を自己形成する。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例6の表示装置向け酸化物半導体TFTを作製することができる。

【実施例7】

【0098】

以下に、実施例7のTFTの製造法について説明する。本実施例のTFTは、構造は実施例6のTFTと同じトップゲート型であるが、半導体層を形成した後にソース電極及びドレイン電極が形成される。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至6とで重複する説明は端的に述べる。

【0099】

図8(a)〜図8(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、プラズマCVD法,スパッタリング法,塗布法などにより、活性半導体層7として実施例4の酸化物半導体を成膜する。

【0100】

次に、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。活性半導体層7が電極近接層となる。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0101】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)を活性半導体層7の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適で、5〜30ppmがさらに好適である。

【0102】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図8(a)に示すように、ソース電極12及びドレイン電極13を形成する。なお、ソース電極12及びドレイン電極13のパターニングはリフトオフ法を用いても良い。その場合は、Cu合金10の成膜前にフォトリソグラフィ工程を施すことになる。

【0103】

次に、オゾン水洗浄を行い、ゲート絶縁膜を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)をCu合金10と純Cu11とCu合金10の表面に形成する。

【0104】

次に、図8(b)に示すように、プラズマCVD法,スパッタリング法,塗布法により、ゲート絶縁膜5として例えば酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。このとき、ゲート絶縁膜5の形成時の200〜500℃の程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、基板1の界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、活性半導体層7とソース電極12及びドレイン電極13の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子の活性半導体層7中への拡散を抑制する。その後ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は活性半導体層7とソース電極12及びドレイン電極13の構成元素で酸化物膜15を自己形成する。なお、電流はソース電極12及びドレイン電極13の下層にあるCu合金10がつくる酸化物膜15と活性半導体層7の間を横切る。したがって、酸化物膜15は低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0105】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0106】

次に、スパッタ法により、Cu合金2,純Cu3からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図8(c)に示すように、ゲート電極4を形成する。

【0107】

次に、図8(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ゲート電極4下層にあるCu合金2中の添加元素が界面に析出される。界面に析出した添加元素は、ゲート絶縁膜5上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れる酸化物膜18を自己形成する。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例7の表示装置向け酸化物半導体TFTを作製することができる。

【実施例8】

【0108】

図9および図10は、実施例8の内容を図示するものであり、液晶表示装置を例にとり、実施例1乃至7のTFTを表示装置へ用いる方法を説明するものである。なお、煩雑さを避けるためTFTの詳細な構造の図示は省略する。

【0109】

図9は、実施例8のアクティブマトリクス型液晶表示装置のTFT基板101の画素構成例を図示したものである。図9に示したように、TFT基板101上に走査線102と、これとは垂直に交差する方向に信号線103が配置されている。走査線102と信号線103の交差するポイントにはTFT104が置かれ、TFT104の配線の一部が画素電極105へ接続される。また、画素電極105及び走査線102の一部を用いてストレージキャパシタ106が設けられている。なお、走査線102を形成する工程で実施例1乃至7のTFTのゲート電極4(図示せず)が、信号線103を形成する工程で実施例1乃至7のTFTのソース電極12(図示せず)及びドレイン電極13(図示せず)が形成される。

【0110】

図10は、実施例8のアクティブマトリクス型液晶表示装置の構成例を示す断面図である。図10に示すように、液晶表示装置は、光源111,偏光板112,TFT基板101,TFT104,絶縁膜113,画素電極105,配向膜114,液晶層115,スペーサ116,共通電極117,カラーフィルタ118,ブラックマトリクス119,カラーフィルタ基板120,偏光フィルム121を有している。

【0111】

ここで、液晶表示装置の表示制御方法について簡単に述べる。光源111から放たれた光は偏光板112により特定の偏光成分のみが通過し、液晶層115へ向かう。液晶層115は画素電極105と共通電極117に供給される電圧に応じて、偏光フィルム121を通過する光透過率を調整することで画素の階調を制御する。

【0112】

次に、液晶層115の制御方法について、図9を用いて簡単に述べる。まず、走査線102からTFT104にゲート信号が印加されるとTFT104はオン状態になり、信号線103に加えられている信号電圧がTFT104を経由し画素電極105とストレージキャパシタ106に印加される。これにより、液晶層115に所望の電圧が印加され、液晶分子が動作し光透過率を制御する。このとき、ストレージキャパシタ106は、電圧信号を保持する役割をもつ。すなわち、TFT104がオフになっても次の信号が印加されるまで、液晶層115に供給されている電圧レベルを一定に調整する。

【0113】

本発明のTFTによれば、配線の電気抵抗値とTFTの電気特性値の均一性を損なわずにCu配線適用を実現することが可能になる。

【0114】

本発明のTFTによれば、配線の電気抵抗値とTFTの電気特性値の均一性を損なわずにCu配線適用を実現することが可能になる。本発明のTFTを実施例8の液晶表示装置に用いることにより、さらなる大型化と画質向上、そして製造コスト低減を図ることができる。

【0115】

なお、本実施例では本発明のTFTを液晶表示装置に適用する例を示したが、本発明のTFTは有機EL表示装置,電子ペーパーにも適用可能である。

【符号の説明】

【0116】

1 基板

2,10,17 Cu合金

3,11 純Cu

4 ゲート電極

5 ゲート絶縁膜

6,15,16,18 酸化物膜

7 活性半導体層

8 コンタクト膜

9 半導体層

12 ソース電極

13 ドレイン電極

14 保護膜

101 TFT基板

102 走査線

103 信号線

104 TFT

105 画素電極

106 ストレージキャパシタ

111 光源

112 偏光板

113 絶縁膜

114 配向膜

115 液晶層

116 スペーサ

117 共通電極

118 カラーフィルタ

119 ブラックマトリクス

120 カラーフィルタ基板

121 偏光フィルム

【技術分野】

【0001】

本発明は、薄膜トランジスタを用いたアクティブマトリクス型の表示装置及びその製造方法に関する。

【背景技術】

【0002】

近年、薄膜トランジスタ(TFT:Thin Film Transistor)を画素回路に用いたアクティブマトリクス型表示装置の大型化,画素の高精細化,フレーム周波数の倍増による動画性能向上などが要求されている。最近では、画像を立体的に見せる民生用3D表示装置が発売され、その画質の向上に上述の要求はますます強くなっている。一方、表示装置の価格は予想を上回るペースで下落を続けており、エネルギー資源やレアメタルの高騰など製造コストを押し上げる要因も増大しつつある。従って、更なる製造コスト低減技術を開発することが急務となっている。

【0003】

液晶表示装置の大型化と動画性能や画質の向上、そして製造コスト低減の1つの策として、TFTに適用される配線材料を従来のAl(アルミニウム)またはAl合金からCu(銅)に替える試みがある。Cu配線は従来のAl配線よりも電気抵抗が低いため、配線を伝わる電気信号が遅れる伝播遅延現象を低減でき、さらなる大型化が可能になる。また、フレーム周波数を上げ、動画質向上も可能になる。さらに、Al配線は、ヒロックの発生抑制と透明導電膜との電気的接続を確保するために、Al膜の上下を高価なモリブデン(Mo)で挟んだMo/Al/Moの積層膜構造としているが、Cuは透明導電膜との直接接続が可能であるために省モリブデン化を図ることが可能である。従って、製造コストを低減できる。

【0004】

有機EL表示装置の大型化と画質向上には、従来のAl配線よりも低抵抗な配線材料が求められる。有機EL表示装置の画素回路に設けられる駆動トランジスタは、飽和領域を用いて有機EL層に流れる電流を制御し、その輝度を調整する。表示装置の大型化に伴い配線抵抗による電圧降下が無視できなくなると、想定された電圧が駆動トランジスタに供給されず飽和領域での駆動が不可能になり、結果、輝度むらの原因となる。そこで、表示品位向上のためCu配線の適用が検討されている。

【0005】

しかしながら、Cu配線をTFTに適用する際には以下の問題が存在する。Cuはガラス基板や半導体膜、例えばシリコン(Si)膜や酸化物半導体膜との密着性が悪い。また半導体膜と接する場合、配線形成後の工程で加わる熱により、半導体膜内部にCuが拡散しTFT特性を劣化させ、表示品位を下げる。このような密着性および拡散バリア性問題の対処として、下地膜とCu膜との間にMoやMo合金を形成する方法がある。しかし、前述のようにMoは高価で、また、電気化学的性質の異なる金属の積層構造はエッチングを困難にするため、製造コストが増大する。

【0006】

そこで、熱工程を利用して、自己の添加元素を界面に析出させ、密着性および拡散バリア性に優れた添加元素酸化物を形成させるCu合金を採用する方法がある。ここで熱工程は、CVD(Chemical Vapor Deposition)工程や液晶表示装置での配向膜焼成工程など、配線形成後に薄膜トランジスタ基板が経験する温度を想定している。添加元素酸化物の自己形成には、Cu合金とそれに接する膜の界面に必要十分な酸素原子が予め存在する必要がある。

【0007】

特許文献1ではCuMn合金を推奨し、TFTのゲート電極に適用する方法として、CuMn合金を成膜後に微量の酸化性雰囲気中で加熱処理し、その表面に密着性と拡散バリア性に優れるMn酸化物を形成する方法を提示している。下地のガラス基板は予め必要十分な酸素原子を含有するためMn酸化物の形成は容易である。

【0008】

さらに、特許文献1では、TFTのソース・ドレイン(SD:Source Drain)電極にCu合金を適用する方法として、例えばCu合金成膜前に酸素プラズマ処理を行い、半導体膜上層を改質させ酸化シリコン層SiOxを形成し、添加元素酸化物の形成に必要な酸素を付与する方法を提案している。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2008−282887号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

配線にCuを用いて、Cu配線に酸化性雰囲気中で加熱処理を行うと配線の電気抵抗値が均一にならない。また、配線にCuを用いて、半導体層へプラズマ酸化処理を行うとTFTの電気特性値が均一にならない。

【0011】

本発明は、配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にすることを目的とする。

【課題を解決するための手段】

【0012】

上記課題を解決するための本発明の特徴は以下の通りである。

(1)基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(2)上記(1)において、電極はゲート電極であり、電極近接層はゲート絶縁膜であり、TFTは、半導体層,ソース電極およびドレイン電極を有し、以下の工程を含む表示装置の製造方法(D)基板の上に半導体層,ソース電極およびドレイン電極が形成される工程。

(3)上記(1)において、電極はソース電極およびドレイン電極であり、電極近接層は半導体層であり、TFTはゲート電極およびゲート絶縁膜を有し、以下の工程を含む表示装置の製造方法(E)基板の上にゲート電極およびゲート絶縁膜が形成される工程。

(4)上記(2)または(3)において、ゲート電極の上にソース電極およびドレイン電極が形成される表示装置の製造方法。

(5)上記(2)または(3)において、ソース電極およびドレイン電極の上にゲート電極が形成される表示装置の製造方法。

(6)上記(2)または(3)において、ソース電極およびドレイン電極の上に半導体層が形成される表示装置の製造方法。

(7)上記(2)または(3)において、半導体層の上にソース電極およびドレイン電極が形成される表示装置の製造方法。

(8)上記(2)または(3)において、半導体層は、活性半導体層およびコンタクト膜を含み、活性半導体層およびコンタクト膜は接している表示装置の製造方法。

(9)上記(2)または(3)において、半導体層は、酸化物半導体である表示装置の製造方法。

(10)上記(2)において、以下の工程を含む表示装置の製造方法(F)ソース電極およびドレイン電極がオゾン水で洗浄される工程、(G)(F)の工程後の熱処理により、ソース電極と半導体層との界面およびドレイン電極と半導体層との界面に、酸素を含むソース・ドレイン酸化物膜が形成される工程。

(11)上記(4)において、ゲート電極の上にゲート絶縁膜が形成され、(C)の工程における熱処理は、ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

(12)上記(5)において、TFTは、保護膜を有し、ゲート絶縁膜の上にゲート電極が形成され、ゲート電極の上に保護膜が形成され、(C)の工程における熱処理は、保護膜を形成するための熱処理である表示装置の製造方法。

(13)上記(6)において、(C)の工程における熱処理は、半導体層を形成するための熱処理である表示装置の製造方法。

(14)上記(7)において、TFTは、保護膜を有し、ソース電極およびドレイン電極の上に保護層が形成され、(C)の工程における熱処理は、保護膜を形成するための熱処理である表示装置の製造方法。

(15)上記(3)において、TFTは、保護膜を有し、ソース電極およびドレイン電極の上にゲート絶縁膜が形成され、ゲート絶縁膜の上にゲート電極が形成され、ゲート電極の上に保護膜が形成され、(C)の工程における熱処理は、ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

(16)上記(1)において、酸化物膜中の酸素原子はピークを有し、ピーク値は2at%以上60at%以下であり、基板上でピーク値の3σ/Medianの値は0.5以下である表示装置の製造方法。

(17)上記(2)または(3)において、TFTのチャンネル長Lは、1μm以上100μm以下である表示装置の製造方法。

(18)上記(2)または(3)において、オゾン水の溶存オゾン濃度は、1ppm(mg/L)以上100ppm(mg/L)以下である表示装置の製造方法。

(19)上記(10)において、ゲート電極を洗浄するオゾン水の溶存オゾン濃度は、ソース電極およびドレイン電極を洗浄するオゾン水の溶存オゾン濃度以上である表示装置の製造方法。

【発明の効果】

【0013】

本発明によれば、配線の電気抵抗値とTFTの電気特性値の均一性を損なわずにCu配線適用を実現することが可能になる。

【図面の簡単な説明】

【0014】

【図1】オゾン水酸化処理と熱酸化処理の酸化膜厚と処理時間の関係を示す図である。

【図2(a)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

【図2(b)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

【図2(c)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

【図2(d)】実施例1の薄膜トランジスタの製造工程を示す断面図である。

【図3(a)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(b)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(c)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(d)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図3(e)】実施例2の薄膜トランジスタの製造工程を示す断面図である。

【図4(a)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図4(b)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図4(c)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図4(d)】実施例3の薄膜トランジスタの製造工程を示す断面図である。

【図5(a)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図5(b)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図5(c)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図5(d)】実施例4の薄膜トランジスタの製造工程を示す断面図である。

【図6(a)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(b)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(c)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(d)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図6(e)】実施例5の薄膜トランジスタの製造工程を示す断面図である。

【図7(a)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図7(b)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図7(c)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図7(d)】実施例6の薄膜トランジスタの製造工程を示す断面図である。

【図8(a)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図8(b)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図8(c)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図8(d)】実施例7の薄膜トランジスタの製造工程を示す断面図である。

【図9】液晶表示装置の薄膜トランジスタ基板の画素構成を示す図である。

【図10】液晶表示装置の構成を示す断面図である。

【発明を実施するための形態】

【0015】

以下、本発明にかかるTFTの製造方法と構成およびそれを表示装置に適用する場合の方法について、図面などを用いて説明する。以下の説明は、本願発明の内容の具体例を示すものであり、本願発明がこれらの説明に限定されるものではなく、本明細書に開示される技術的思想の範囲内において当業者による様々な変更および修正が可能である。また、実施例を説明するための全図において、同一の機能を有するものは、同一の符号を付け、その繰り返しの説明は省略する。

【0016】

詳細な実施例の説明に先立ち、電極としてCu配線を採用したTFTの製造にオゾン水酸化処理が適する理由ついて説明する。

【0017】

TFTを用いた電子デバイス、例えばアクティブマトリクス型の表示装置などは薄膜トランジスタ基板全面に渡り配線の電気抵抗値とTFTの電気特性値に高い均一性を要する。ここでTFTの電気特性値とは、移動度,閾値電圧,S値(サブスレショルドスウィング),オフ特性などを指す。この配線の電気抵抗値とTFTの電気特性値の均一性を左右するのが、酸化膜質(酸化膜の厚さと酸素含有量)の均一性である。

【0018】

Cu合金をTFTのゲート電極に適用する手段として、酸化性雰囲気中で200℃〜500℃の加熱処理を行い、添加元素酸化物を形成する方法がある。しかしながら、酸化種の熱拡散を利用した酸化方法は、酸化膜厚の処理時間依存性が大きいことや基板の温度分布に起因して薄膜トランジスタ基板上の一部で配線の電気抵抗値に大きなバラツキが生じる。また、配線の電気抵抗値の低減を図り、Cu合金層の上に純度99.9%以上の純Cu層を形成した「純Cu/Cu合金」または「Cu合金/純Cu/Cu合金」の積層配線があるが、これに酸化性雰囲気中で加熱処理を施すと純Cu層の加工断面から必要以上に酸化が進み、結果、配線の電気抵抗値は上昇し純Cuを導入した効果を失う。

【0019】

Cu合金をTFTのSD電極に適用する手段として、Cu合金の成膜前に酸素プラズマ処理を行い、添加元素酸化物の形成に必要な酸素を付与する方法がある。しかしながら、酸素プラズマ処理はプラズマ密度の分布に起因して、薄膜トランジスタ基板上で酸化膜質にばらつきが生じ、その結果、酸化が不十分な箇所ではCu原子の拡散が抑制できなくなり、TFT特性の低下を招く。また、薄膜トランジスタ基板全面にわたってCu原子の拡散を防ぐ目的で酸素プラズマ処理の酸化度合いを強くすると、今度は一部で必要以上に厚い酸化膜が形成される。この酸化膜が添加元素と化合せずに半導体層側で残存すると、電流経路に寄生抵抗をつくる。実際に電子デバイスや表示装置に用いられるTFTのチャンネル長は1〜100μm程度で、このサイズ領域では寄生抵抗の大きさが移動度の値を大きく左右する。したがって、不要な酸化膜の残存による寄生抵抗の上昇は移動度を急減させ、TFTのオン特性低下を引き起こし、表示品位を劣化させる。

【0020】

その他の酸化手法に、酸素より酸化性の強いオゾンを含む雰囲気下にCu配線や半導体層を暴露する方法があるが、この手法ではCu原子の拡散を抑制できる十分な酸化膜質の形成が難しく、さらにガスが噴射するシャワーヘッドの穴の位置を反映して酸化膜質にバラツキが生じる。必要な酸化膜を得るために200℃〜500℃の加熱処理を施す方法もあるが、上述のゲート電極に適用する手段と同様の理由で適用は困難である。

【0021】

また、オゾンガスに紫外波長域の光を照射し酸化性が極めて強い励起状酸素原子を生成させ、それをCu配線や半導体層に暴露し、極薄酸化膜を形成する光酸化法もある。しかしながら、光酸化法は紫外光を照射するランプの強度分布に依存して酸化膜質に大きなバラツキが生じる。

【0022】

そこで、薄膜トランジスタ基板の全面に渡って酸化膜質の均一性に優れる酸化手法に、オゾン水酸化法がある。オゾン水とCu配線や半導体膜が接触した瞬間、それら界面近傍では互いのコンタクトポテンシャルの差から強い電界が生じる。オゾン水中の酸化種、例えばO- などのアニオンは、その電界によりCu配線や半導体層へ運ばれ酸化膜を形成する。したがって、オゾン水酸化法はこの界面近傍のみに生じる電界と溶存オゾン濃度が酸化膜質を律則する。

【0023】

例として図1に、オゾン水酸化処理(実線)と酸化性雰囲気下で熱酸化処理(点線)を行った際の酸化膜厚と処理時間の関係を示す。各処理はシリコン基板へ行い、酸化膜厚はSiO2に換算して算出する。熱酸化処理は酸化膜厚の処理時間依存性が大きいことが分かる。このような特性は、極薄の酸化膜が要求される場合、例えば5nm以下の酸化膜を作製する際は薄膜トランジスタ基板上で膜厚ばらつきが大きくなることを示唆する。それに対し、オゾン水酸化処理の酸化膜厚は処理開始と同時に急峻に立ち上がった後、素早く飽和する特性を見せ、処理時間依存性が熱酸化法に比べ小さい。この特性を有するため、オゾン水酸化処理は薄膜トランジスタ基板の全面に渡り酸化膜質の均一性を確保する。これは、熱酸化法が拡散律則なのに対し、オゾン水酸化法が界面電界に律則されるためである。なお、基板に200℃〜500℃の加熱処理を加えながらプラズマ酸化法や光酸化法を行う場合も、図1の点線の熱酸化法と同様の特性を示した。

【0024】

なお、オゾン水酸化法を適用したTFTの酸化物膜中の酸素原子濃度はピークを有している。そのピーク値が2at%未満の場合、Cu原子の拡散を抑制するのに十分な酸化膜が形成できない。また、60at%を超えていると、半導体層の奥で酸化膜が残存し電流経路の寄生抵抗となり移動度を急減させる。したがって、酸素原子濃度のピーク値は、2at%以上60at%以下となるように溶存オゾン濃度を調整する必要がある。また、TFT基板上で、ピーク値のばらつきは3σ/Medianの値で0.5以下となるようにする必要がある。これは、3σ/Medianが0.5を超えているとTFT電気特性値が大きくばらつき、表示装置に適用した際に輝度むらが明確に確認できるためである。これらの条件を満足する溶存オゾン濃度は1〜100ppmの範囲にある。

【0025】

以下、具体的なオゾン水酸化処理条件についてTFT製造方法を説明しながら述べる。

【実施例1】

【0026】

以下に、実施例1のTFTの製造法について説明する。本実施例のTFTはボトムゲート型で、半導体層を形成した後にソース電極及びドレイン電極が形成される構造を有する。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。

【0027】

図2(a)〜図2(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、Cu合金2をスパッタリング法により成膜する。膜厚は10nm〜150nmの程度であり、20nm〜50nmが好適である。ここで成膜するCu合金2は、基板1との密着性発現の役割を担う。Cu合金2中のCu以外の添加元素としては、例えば、Mn,Mg,Ca,Ni,Zn,Si,Al,Be,Ga,In,Fe,Ti,V,Co,Zr,Hf、などから1種類以上、Cu合金2中の添加元素の添加量は0.5〜10原子%が好ましい。また、後の熱を伴う製造工程でCu合金2中の添加元素が界面へ拡散し酸化物を形成するために、基板1は必要十分な酸素原子数を予め含有していることが望ましい。例えば、無アルカリガラス基板はこの条件を満たしている。本実施例では、Cu中にMnが4at%添加されたCu−Mn合金を50nmほど成膜した。

【0028】

次に、純Cu3を同様にスパッタリング法にて連続成膜する。膜厚は100〜1000nmの程度で、約200〜500nmが好適である。本実施例ではCu−Mn合金上に純Cuを300nmほど成膜した。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0029】

次いで、オゾン水洗浄を行い、ゲート絶縁膜5を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、1〜50ppmが好適である。濃度が1ppmを下回るとゲート絶縁膜5へのCu原子の拡散が抑制できず、また、100ppmを超えると純Cu3の電気抵抗値が著しく上昇するためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。本実施例では、溶存オゾン濃度20ppmのオゾン水を用いて、1分ほど洗浄した。ここで、図2(a)に示すような、純Cu3およびCu合金2を含むゲート電極4が作製される。ゲート電極4では、電流経路に酸化物膜6が形成されないため、酸化物膜6の膜厚をソース電極12およびドレイン電極13に形成される酸化物膜15の膜厚以上としてもよい。この場合、ゲート電極4に適用するオゾン水の溶存オゾン濃度をソース電極12およびドレイン電極13に適用するオゾン水の溶存オゾン濃度以上にする。ソース電極12とドレイン電極13にCuおよびCu以外の元素が含まれている場合、ゲート電極4はCu合金10および純Cu11でもよいし、Mo/Al合金/Moなどで形成されていてもよい。

【0030】

基板1は無アルカリガラス以外に、フレキシブルなプラスチック基板やステンレス合金などの金属性の基板でも良い。基板からCu層への不純物拡散を気にする場合は、基板上にバリア膜として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を形成しても良い。その際、バリア膜に十分な酸素原子が備わっていない場合、Cu合金2の成膜前に同様のオゾン水洗浄を行い、バリア膜表面に酸化膜を形成する方法が有効である。

【0031】

次に、図2(b)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。膜厚は10nm〜1000nmの程度で、50〜400nmが好適である。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は酸化物膜6を自己形成する。酸化物膜6はゲート絶縁膜5の構成材料、ゲート電極4の構成材料および酸素を含む。酸化物膜15および酸化物膜16が形成されている場合、酸化物膜6は必ずしも形成されている必要はない。オン電流の低下を抑制する観点から、酸化物膜6の膜厚より酸化物膜15の膜厚を小さくすることが望ましい。

【0032】

次いで、プラズマCVD法,スパッタリング法,塗布法により、例えば、活性半導体層7として水素化アモルファスシリコン膜(a−Si:H),コンタクト膜8としてリン(P)をドープした水素化アモルファスシリコン膜(n+a−Si:H)を順次成膜し半導体層9を形成する。活性半導体層7は、不純物が混入されていない半導体であり、ゲート電極4への電圧印加により導電層を形成する層である。活性半導体層7として、微結晶シリコンや多結晶シリコンでもよく、水素化アモルファスシリコン,微結晶シリコン,多結晶シリコンの積層膜でもよい。コンタクト膜8は、活性半導体層7とソース電極12およびドレイン電極13との接触で生じる寄生抵抗を低減させる目的で、活性半導体層7とソース電極12およびドレイン電極13と間に設けられる層である。コンタクト膜8には不純物が混入されている。コンタクト膜8として、微結晶シリコンや多結晶シリコンでもよい。活性半導体層7の膜厚は10〜300nmの程度で30〜200nmが好適で、コンタクト膜8の膜厚は1〜100nmの程度で5〜60nmが好適である。

【0033】

本実施例では、プラズマCVD法を用いて、ゲート絶縁膜5に窒化シリコン膜を350nm程度、活性半導体層7として水素化アモルファスシリコン膜を180nm程度、コンタクト膜8としてリン(P)をドープした水素化アモルファスシリコン膜を25nm程度形成した。

【0034】

次に、図2(b)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法を用いて、活性半導体層7およびコンタクト膜8を含む半導体層9を島パターニングし、レジストを剥離する。半導体層9が電極近接層となる。

【0035】

次に、オゾン水洗浄を行い、半導体層9へのCu原子拡散を抑制する極薄酸化膜(図示せず)を半導体層9の表面に形成する。この時、極薄酸化膜(図示せず)はゲート絶縁膜5の表面でも同時に形成される。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適で、5〜30ppmがさらに好適である。濃度が1ppmを下回ると半導体層9へのCu原子の拡散が抑制できず、また、100ppmを超えると酸化膜は半導体層9側で不必要に厚く形成されCu合金中の添加元素と化合せずに半導体層9側の奥で残存し、電流経路に寄生抵抗をつくり、結果、移動度を急減させる。本実施例では、溶存オゾン濃度20ppmのオゾン水を用いて、1分ほど洗浄を行い、半導体層9上に約1nmほどの極薄シリコン酸化膜を形成した。ソース電極12およびドレイン電極13では、電流経路に酸化物膜15が形成されるため、酸化物膜15の膜厚を酸化物膜6の膜厚以下にしてもよい。この場合、ソース電極12およびドレイン電極13に適用するオゾン水の溶存オゾン濃度をゲート電極4に適用するオゾン水の溶存オゾン濃度以下にする。本実施例では、ソース電極12およびドレイン電極13に適用するオゾン水の溶存オゾン濃度とゲート電極4に適用するオゾン水の溶存オゾン濃度とを20ppmでほぼ同じにしている。これにより、酸化物膜6および酸化物膜15の要求性能を共に満足できる。

【0036】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。Cu合金10の膜厚は10〜150nmの程度で20nm〜50nmが好適で、純Cu11の膜厚は100〜1000nmの程度で、約200〜500nmが好適である。Cu合金10に添加されるCu以外の元素としては、例えば、Mn,Mg,Ca,Ni,Zn,Si,Al,Be,Ga,In,Fe,Ti,V,Co,Zr,Hf、などから1種類以上、添加量は0.5〜10原子%が好ましい。本実施例では、Cu中にMnが4at%混入したCu−Mn合金を50nmほど、Cu−Mn合金上に純Cuを300nmほど成膜した。本実施例では、ゲート電極4とソース電極12およびドレイン電極13とが同じ材料で作製されているが、Cu合金の添加元素を変える等、違う材料としてもよい。ゲート電極4とソース電極12およびドレイン電極13とを同じ材料にすることで、製造コストを削減できる。

【0037】

その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、Cu合金10および純Cu11を含むソース電極12,Cu合金10および純Cu11を含むドレイン電極13を形成する。ゲート電極4にCuおよびCu以外の元素が含まれている場合、ソース電極12とドレイン電極13はCu合金10および純Cu11で形成されていても良いし、Mo/Al合金/Moなどで形成されていてもよい。

【0038】

次いで、図2(c)に示すように、ソース電極12とドレイン電極13形成に使用したフォトレジストをそのまま利用し、ドライエッチング法によりチャンネル上の極薄酸化膜(図示せず)とコンタクト膜8を除去し、レジストを剥離する。極薄酸化膜(図示せず)は数Å〜数nmと非常に薄いためドライエッチングの妨げにはならない。

【0039】

次に、図2(d)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。保護膜14の膜厚は100〜1000nmの程度で、200〜500nmが好適である。このとき、保護膜14の形成温度は200℃以上となるため、ソース電極12及びドレイン電極13下層にあるCu合金10中のCu原子と添加元素が界面に析出される。本実施例のように、保護膜14の形成温度をゲート絶縁膜5の形成温度より小さくすることで、半導体層の劣化を抑制できる。界面に析出したCu原子と添加元素は、コンタクト膜8上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れなお且つ低電気抵抗な酸化物膜15を自己形成する。酸化物膜15は、半導体層9の構成材料,Cu合金10の構成材料および酸素を含む。

【0040】

この際、ゲート絶縁膜5直上の極薄酸化膜(図示せず)でも同様に密着性及び拡散バリア性に優れる酸化物膜16を自己形成するため、ソース電極12及びドレイン電極13の膜剥がれは起きない。酸化物膜16は、ゲート絶縁膜5の構成材料,Cu合金10の構成材料および酸素を含む。本実施例では、保護膜14に窒化シリコン膜を300nmほど形成した。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例1の表示装置向けボトムゲート型TFTを作製することができる。酸化物膜6が形成されている場合、酸化物膜15および酸化物膜16は必ずしも形成されている必要はない。

【0041】

ここで、本実施例と、拡散バリア性と密着性の確保にMoを採用した従来技術のTFTについて、電気特性値を比較評価した結果を述べる。評価したTFTの素子サイズは、チャンネル幅(ゲート幅とも呼ぶ)Wは100μm、チャンネル長(ゲート長とも呼ぶ)Lは10μmで、実際に表示装置に採用される素子サイズに近く、寄生抵抗が移動度の値を大きく左右する領域である。ソース・ドレイン電圧は10Vで、移動度や閾値電圧は飽和領域より算出した。ゲート電極4にMo/Al合金/Mo、ソース電極12及びドレイン電極13にMo/Al合金/Moを採用し、本実施例の工程でオゾン水酸化処理を省略し、同様の工程を経て作製したTFTの電気特性を評価すると、飽和移動度は0.60cm2/Vsほど、飽和閾値電圧は1〜3Vほど、S値は0.9〜1.1V/decほどであった。

【0042】

ゲート電極4に純Cu/Cu−Mn合金,ソース電極12及びドレイン電極13に純Cu/Cu−Mn合金を採用した本実施例のTFTの電気特性は、飽和移動度は0.58cm2/Vsほど、飽和閾値電圧は1.5Vほど、S値は0.98V/decで、Moを採用した従来技術のTFTとほぼ同等の性能であった。また、オフ電流の上昇も少なく、オフ特性は従来技術のTFTと同等であった。これは、ゲート絶縁膜5や半導体層9へCu原子の拡散が抑制されていること、ソース電極12及びドレイン電極13と半導体層9との界面に寄生抵抗としてはたらく酸化膜がないことを示唆する。

【0043】

したがって、本実施例のTFTによれば、熱工程を利用してCu合金中の添加元素を界面に析出させ、密着性および拡散バリア性に優れた添加元素酸化物を自己形成させる技術に必要な酸化処理にはオゾン水酸化処理が有効であることが分かる。

【0044】

本実施例では、ゲート電極4,ソース電極12,ドレイン電極13はCu合金と純Cuの積層から構成されるが、Cu合金の単層でも良い。その場合の添加元素として、低電気抵抗である理由から、例えば、Mg,Znが好ましい。また、Cu合金/純Cu/Cu合金の3層構造であっても良い。TFT電気特性の改善を狙い、チャンネルエッチストッパ構造を採用しても構わない。

【0045】

半導体層9から外に伸びたソース電極12及びドレイン電極13とゲート絶縁膜5との密着性をより強固にしたい場合は、ゲート絶縁膜5を形成した直後にオゾン水酸化処理を行いゲート絶縁膜5上に酸化膜を形成する手法が有効である。また、ソース電極12及びドレイン電極13と保護膜14との界面からCu原子が拡散し保護膜14の密着性が脆弱になる場合は、保護膜14を形成する前にオゾン水酸化処理を行っても良い。

【実施例2】

【0046】

以下に、実施例2のTFTの製造法について説明する。本実施例のTFTはボトムゲート型で、半導体層を形成する前にソース電極及びドレイン電極が形成される構造を有する。なお、正確な膜厚を反映するとTFT構造に煩雑になるため図は模式的に示す。なお、本実施例と実施例1とで重複する説明は端的に述べる。

【0047】

図3(a)〜図3(e)は、各工程時のTFT断面図である。まず、基板1上に、Cu合金2をスパッタリング法により成膜する。ここで成膜するCu合金2は、基板1との密着性発現の役割を担う。

【0048】

次に、純Cu3を同様にスパッタリング法にて連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0049】

次いで、オゾン水洗浄を行い、ゲート絶縁膜5を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。ここで、図3(a)に示すようなゲート電極4が作製される。

【0050】

次に、図3(b)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を成膜する。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)はゲート絶縁膜5とゲート電極4の構成元素で酸化物膜6を自己形成する。

【0051】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。濃度が1ppmを下回るとゲート絶縁膜5へのCu原子の拡散が抑制できず、また、100ppmを超えると厚い酸化膜が形成され、コンタクトホールを形成する際に酸化膜を除去する工程が別途必要になるためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。具体的には、ゲート絶縁膜5に2at%以上の酸素原子が含有されていることが望ましい。

【0052】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図3(c)に示すように、ソース電極12,ドレイン電極13を形成する。ソース電極12,ドレイン電極13のパターニングはリフトオフ法であってもよい。

【0053】

次に、オゾン水洗浄を行い、半導体層へのCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu11とCu合金10の表面に形成する。このとき、ゲート絶縁膜5の表面もオゾン水に暴露され、極薄酸化膜(図示せず)が形成される。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。濃度が1ppmを下回ると半導体層へのCu原子の拡散が抑制できず、また、100ppmを超えると純Cu11の電気抵抗値が著しく上昇するためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。ソース電極12,ドレイン電極13をオゾン水で洗浄をすることにより、半導体層9への酸素原子の拡散を抑え、寄生抵抗を低減でき、オン電流を上昇できる。半導体層9をオゾン水で洗浄する場合に比べて、溶存オゾン濃度を高くできる。

【0054】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、コンタクト膜8としてリン(P)をドープした水素化アモルファスシリコン膜(n+a−Si:H)を成膜する。その後、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いてコンタクト膜8をパターニングし、レジストを剥離する。次いで、プラズマCVD法,スパッタリング法,塗布法により、例えば、活性半導体層7として水素化アモルファスシリコン膜(a−Si:H)を成膜し、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離し、図3(d)に示すように半導体層9を形成する。半導体層9が電極近接層となる。このとき、半導体層9の形成時の温度は200〜400℃の程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、極薄酸化膜(図示せず)と化合し、ゲート絶縁膜5との界面で密着性に優れた酸化物膜16を自己形成する。活性半導体層7を介することなく、ソース電極12,ドレイン電極13とコンタクト膜8とが直に接しているため、活性半導体層7の膜厚抵抗が無く、寄生抵抗が低減し、オン電流を向上できる。

【0055】

その後、半導体層9形成時の熱により極薄酸化膜(図示せず)は酸化物膜15を自己形成する。酸化物膜15は、拡散バリア層として機能し、Cu原子のコンタクト膜8中への拡散を抑制する。なお、電流はソース電極12及びドレイン電極13の下層にあるCu合金10がつくる酸化物膜15とコンタクト膜8の間を横切る。したがって、Cu合金10とコンタクト膜8の界面に形成される酸化物膜15は、低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0056】

次に、図3(e)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例2の表示装置向けボトムゲート型TFTを作製することができる。

【実施例3】

【0057】

以下に、実施例3のTFTの製造法について説明する。本実施例のTFTはトップゲート型で、半導体層を形成する前にソース電極及びドレイン電極が形成される構造を有する。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1及び実施例2とで重複する説明は端的に述べる。

【0058】

図4(a)〜図4(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、基板1との密着性を確保するためCu合金10をスパッタリング法により成膜する。次に、純Cu11を同様にスパッタリング法にて連続成膜する。

【0059】

その次に、例えば、Cu合金10と同じ材料からなるCu合金17をスパッタリング法により連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0060】

次いで、オゾン水洗浄を行い、半導体層を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)をCu合金17と純Cu11とCu合金10の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。ここで、図4(a)に示すようなソース電極12,ドレイン電極13が作製される。

【0061】

次に、プラズマCVD法,スパッタリング法,塗布法により、コンタクト膜8として例えばリン(P)をドープした水素化アモルファスシリコン膜(n+a−Si:H)を成膜する。その後、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いてコンタクト膜8をパターニングし、レジストを剥離する。

【0062】

次いで、プラズマCVD法,スパッタリング法,塗布法により、活性半導体層7として例えば水素化アモルファスシリコン膜(a−Si:H)を成膜し、これにフォトリソグラフィ工程を施し、ドライエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離し、図4(b)に示すように半導体層9を形成する。半導体層9が電極近接層となる。このとき、半導体層9の形成時の温度は200〜400℃の程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、基板1の界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、コンタクト膜8とソース電極12及びドレイン電極13の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のコンタクト膜8中への拡散を抑制する。

【0063】

その後、半導体層9形成時の熱により極薄酸化膜(図示せず)はコンタクト膜8とソース電極12及びドレイン電極13の構成元素で酸化物膜15を自己形成する。なお、電流は、ソース電極12及びドレイン電極13の上層にあるCu合金17がつくる酸化物膜15とコンタクト膜8の間を横切る。したがって、Cu合金17とコンタクト膜8の界面に形成される酸化物膜15は低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0064】

次に、図4(c)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。

【0065】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0066】

次に、スパッタ法により、Cu合金2,純Cu3からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、ゲート電極4を形成する。

【0067】

次に、図4(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ゲート電極4下層にあるCu合金2中の添加元素が界面に析出される。界面に析出した添加元素は、ゲート絶縁膜5上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れる酸化物膜18を自己形成する。酸化物膜18は、ゲート絶縁膜5の構成材料,Cu合金10の構成材料および酸素を含む。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例3の表示装置向けトップゲート型TFTを作製することができる。本実施例ではゲート絶縁膜5へオゾン水洗浄を行うため、酸化物膜18中の酸素原子はゲート電極4が存在する側よりゲート絶縁膜5が存在する側で多く、ゲート電極4へオゾン水洗浄を行う場合に比べて電気抵抗値の上昇を抑制できる。

【実施例4】

【0068】

以下に、実施例4のTFTの製造法について説明する。本実施例のTFTは、実施例1と同様にボトムゲート型で、半導体層を形成した後にソース電極及びドレイン電極を形成する構造を有するが、半導体層に酸化物半導体を用いているのが主な特徴である。酸化物半導体はその界面や膜中で酸素の欠損が生じるとTFT特性が大きく劣化する。また、酸化物半導体とゲート絶縁膜の界面、および、酸化物半導体と保護膜やチャンネルエッチストッパ膜の界面に多量の水素が存在してもTFT特性に悪影響を及ぼす。これら問題の解決にもオゾン水酸化法は有効である。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至3とで重複する説明は端的に述べる。

【0069】

図5(a)〜図5(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、Cu合金2をスパッタリング法により成膜する。次に、純Cu3を同様にスパッタリング法にて連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。

【0070】

次いで、オゾン水洗浄を行い、ゲート絶縁膜5を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。ここで、図5(a)に示すようなゲート電極4が作製される。

【0071】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。膜厚は10nm〜1000nmの程度で、50〜400nmが好適である。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は酸化物膜6を自己形成する。

【0072】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。濃度が1ppmを下回るとゲート絶縁膜5へのCu原子の拡散が抑制できず、また、100ppmを超えると厚い酸化膜が形成され、コンタクトホールを形成する際に酸化膜を除去する工程が別途必要になるためである。また、処理時間は10秒〜20分の程度で、1〜5分が好適である。加えて、ゲート絶縁膜5中に多量の水素が存在する場合、後の熱を伴う工程でゲート絶縁膜5と酸化物半導体の界面へ水素が拡散し、その結果、閾値電圧のシフトが起こりTFT特性の信頼性に悪影響を及ぼすことがある。更に、後の熱を伴う工程で酸化物半導体中の酸素がゲート絶縁膜5へ拡散すると、酸素の欠陥が生じTFT特性が劣化することがある。ゲート絶縁膜5へオゾン水洗浄を行い表面に良質な極薄酸化膜を形成することで、ゲート絶縁膜5からの水素の拡散と酸化物半導体中からの酸素の拡散を抑制し、良好なTFT特性を確保することができる。なお、このオゾン水酸化処理工程は下地となるゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0073】

次いで、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、活性半導体層7として酸化物半導体を成膜する。活性半導体層7が電極近接層となる。金属化合物を酸化して形成される酸化物半導体は、ソース電極12及びドレイン電極13との寄生抵抗が小さく、意図的に不純物がドープされたコンタクト膜を形成しなくても十分なオン電流を確保できる。酸化物半導体は、例えば、酸化亜鉛,酸化インジウム,酸化ガリウム,酸化錫,酸化銅,酸化ジルコニウム,酸化チタン,酸化アルミニウム銅,酸化亜鉛錫,酸化亜鉛インジウム,酸化ガリウムインジウム,酸化亜鉛ガリウム錫,酸化インジウムマグネシウム,酸化亜鉛ガリウムインジウムなどがあり、Zn,In,Ga,Sn,Al,Ti,Mg,Zr,Cuから少なくとも1種以上の元素を含む酸化物より成る。酸化物半導体として、アモルファスでも多結晶でもよく、これらの積層膜でもよい。その中でもTFTの電気特性の均一性に優れるIn−Ga−Zn−O系の酸化物半導体を用いるのが好ましい。活性半導体層7の膜厚は1〜300nmの程度で20〜100nmが好適である。

【0074】

次に、図5(b)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0075】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)を活性半導体層7の表面に形成する。この時、酸化物半導体から成る活性半導体層7へ極薄酸化膜(図示せず)を形成する意味は3つある。第1の意味は、実施例1乃至実施例3で述べたように、活性半導体層7へのCu原子の拡散を抑制することである。第2の意味は、本実施例のようにCu合金中の添加元素が活性半導体層7側から酸素を奪い酸化物膜6を自己形成する場合、酸化物半導体の表面の酸素原子含有量が薄膜トランジスタ基板上でバラつくと、それを反映してTFT電気特性値も大きくバラつくためである。フォトリソグラフィ工程で酸化物半導体の表面はダメージを受け酸素含有量にばらつきが生じるため、オゾン水処理により酸素原子を基板上で均一に付与するのである。第3の意味は、酸化物半導体中の酸素がCu合金側へ拡散するのを防ぎ、TFT特性の劣化を抑制するためである。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。濃度が1ppmを下回ると活性半導体層7へのCu原子の拡散が抑制できず、また、100ppmを超えると酸化膜は活性半導体層7側で不必要に厚く形成されCu合金中の添加元素と化合せずに活性半導体層7側の奥で残存し、電流経路に寄生抵抗をつくり、結果、移動度を急減させる。

【0076】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。Cu合金10の膜厚は10〜150nmの程度で20nm〜50nmが好適で、純Cu11の膜厚は100〜1000nmの程度で、約200〜500nmが好適である。

【0077】

その後、図5(c)に示すように、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、ソース電極12,ドレイン電極13を形成する。このとき、活性半導体層7上に形成した極薄酸化膜(図示せず)はウェットエッチングで用いるエッチャントから活性半導体層7を保護する役割も担う。

【0078】

次に、図5(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。保護膜14の膜厚は100〜1000nmの程度で、200〜500nmが好適である。このとき、保護膜14の形成温度は200℃以上となるため、ソース電極12及びドレイン電極13下層にあるCu合金10中のCu原子と添加元素が界面に析出される。界面に析出したCu原子と添加元素は、活性半導体層7上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れなお且つ低電気抵抗な酸化物膜15を自己形成する。この際、ゲート絶縁膜5直上の極薄酸化膜(図示せず)でも密着性及び拡散バリア性に優れる酸化物膜16を自己形成するため、ソース電極12及びドレイン電極13の膜剥がれは起きない。なお、保護膜14が多量の水素を含む場合、水素が活性半導体層7へ拡散しTFT特性に悪影響を及ぼす。水素の拡散を抑制するため、保護膜14の成膜前にオゾン水酸化処理を行い活性半導体層7の表面に極薄酸化膜を形成しても良い。このオゾン水酸化処理はソース電極12およびドレイン電極13のパターニングで生じた活性半導体層7の酸素欠損を補う効果もある。

【0079】

これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例4の表示装置向け酸化物半導体TFTを作製することができる。

【0080】

また、TFT電気特性を安定かつ均一にするため、酸化物半導体の形成後に熱処理を別途に加えてもよい。熱処理はソース電極12及びドレイン電極13の形成後に行うのが好ましい。ソース電極12及びドレイン電極13中の添加元素の拡散が促進され酸化物膜15,酸化物膜16が得やすくなるためである。

【実施例5】

【0081】

以下に、実施例5のTFTの製造法について説明する。本実施例のTFTは、実施例2と同様にボトムゲート型で、半導体層を形成する前にソース電極及びドレイン電極を形成する構造を有するが、半導体層に酸化物半導体を用いているのが主な特徴である。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至実施例4とで重複する説明は端的に述べる。

【0082】

図6(a)〜図6(e)は、各工程時のTFT断面図である。まず、基板1上に、Cu合金2をスパッタリング法により成膜する。次に、純Cu3を同様にスパッタリング法にて連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。次いで、オゾン水洗浄を行い、ゲート絶縁膜を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu3とCu合金2の表面に形成する。ここで、図6(a)に示すようなゲート電極4が作製される。

【0083】

次に、図6(b)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、ゲート絶縁膜5として酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。膜厚は10〜1000nmの程度で、50〜400nmが好適である。このとき、形成時の温度は200〜500℃の程度で、ゲート電極4下層のCu合金2中の添加元素は界面に析出し、基板1との界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、ゲート絶縁膜5とゲート電極4の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子のゲート絶縁膜5中への拡散を抑制する。その後、ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)はゲート絶縁膜5とゲート電極4の構成元素で酸化物膜6を自己形成する。

【0084】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0085】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図6(c)に示すように、ソース電極12,ドレイン電極13を形成する。

【0086】

次に、オゾン水洗浄を行い、活性半導体層へのCu原子拡散を抑制する極薄酸化膜(図示せず)を純Cu11とCu合金10の表面に形成する。このとき、ゲート絶縁膜5の表面もオゾン水に暴露され、極薄酸化膜(図示せず)が形成される。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。

【0087】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、活性半導体層7として実施例4の酸化物半導体を成膜する。活性半導体層7が電極近接層となる。

【0088】

次に、図6(d)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0089】

次に、図6(e)に示すように、プラズマCVD法,スパッタリング法,塗布法により、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ソース電極12及びドレイン電極13下層にあるCu合金10中のCu原子と添加元素が活性半導体層7との界面に析出し、密着性及び拡散バリア性に優れなお且つ低電気抵抗な酸化物膜15を自己形成する。この際、ゲート絶縁膜5直上の極薄酸化膜(図示せず)でも密着性及び拡散バリア性に優れる酸化物膜16を自己形成するため、ソース電極12及びドレイン電極13の膜剥がれは起きない。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例5の表示装置向け酸化物半導体TFTを作製することができる。

【実施例6】

【0090】

以下に、実施例6のTFTの製造法について説明する。本実施例のTFTは、実施例3と同様にトップゲート型で、半導体層を形成する前にソース電極及びドレイン電極を形成する構造を有するが、半導体層に酸化物半導体を用いているのが主な特徴である。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至5とで重複する説明は端的に述べる。

【0091】

図7(a)〜図7(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、Cu合金10をスパッタリング法により成膜する。次に、純Cu11を同様にスパッタリング法にて連続成膜する。その次に、例えば、Cu合金10と同じ材料のCu合金17をスパッタリング法により連続成膜する。これにフォトリソグラフィ工程を行った後、ウェットエッチング法を用いてパターニングし、レジストを剥離する。次いで、オゾン水洗浄を行い、活性半導体層7を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)をCu合金17と純Cu11とCu合金10の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適である。ここで、図7(a)に示すようなソース電極12,ドレイン電極13が作製される。

【0092】

次に、プラズマCVD法,スパッタリング法,塗布法などにより、活性半導体層7として実施例4の酸化物半導体を成膜する。

【0093】

次に、図7(b)に示すように、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。活性半導体層7が電極近接層となる。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0094】

次に、図7(c)に示すように、プラズマCVD法,スパッタリング法,塗布法により、ゲート絶縁膜5として例えば酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。このとき、ゲート絶縁膜5の形成時の200〜500℃程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、基板1の界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、活性半導体層7とソース電極12及びドレイン電極13の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子の活性半導体層7中への拡散を抑制する。その後ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は活性半導体層7とソース電極12及びドレイン電極13の構成元素で酸化物膜15を自己形成する。なお、電流はソース電極12及びドレイン電極13の上層にあるCu合金17がつくる酸化物膜15と活性半導体層7の間を横切る。したがって、Cu合金17と活性半導体層7の界面に形成される酸化物膜15は低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0095】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、20〜100ppmが好適である。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0096】

次に、スパッタ法により、Cu合金2,純Cu3からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、ゲート電極4を形成する。

【0097】

次に、図7(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ゲート電極4下層にあるCu合金2中の添加元素が界面に析出される。界面に析出した添加元素は、ゲート絶縁膜5上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れる酸化物膜18を自己形成する。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例6の表示装置向け酸化物半導体TFTを作製することができる。

【実施例7】

【0098】

以下に、実施例7のTFTの製造法について説明する。本実施例のTFTは、構造は実施例6のTFTと同じトップゲート型であるが、半導体層を形成した後にソース電極及びドレイン電極が形成される。なお、正確な膜厚を反映するとTFT構造が煩雑になるため図は模式的に示す。また、本実施例と実施例1乃至6とで重複する説明は端的に述べる。

【0099】

図8(a)〜図8(d)は、各工程時のTFT断面図である。まず、無アルカリガラスなどの絶縁性材料からなる基板1上に、プラズマCVD法,スパッタリング法,塗布法などにより、活性半導体層7として実施例4の酸化物半導体を成膜する。

【0100】

次に、フォトリソグラフィ工程を施し、ドライエッチング法またはウェットエッチング法を用いて活性半導体層7を島パターニングし、レジストを剥離する。活性半導体層7が電極近接層となる。島パターニングはリフトオフ法を用いても良い。その場合は、活性半導体層7の成膜前にフォトリソグラフィ工程を施すことになる。

【0101】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)を活性半導体層7の表面に形成する。オゾン水の溶存オゾン濃度は、1〜100ppmの程度で、3〜50ppmが好適で、5〜30ppmがさらに好適である。

【0102】

次に、スパッタ法により、Cu合金10,純Cu11からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図8(a)に示すように、ソース電極12及びドレイン電極13を形成する。なお、ソース電極12及びドレイン電極13のパターニングはリフトオフ法を用いても良い。その場合は、Cu合金10の成膜前にフォトリソグラフィ工程を施すことになる。

【0103】

次に、オゾン水洗浄を行い、ゲート絶縁膜を形成する際のCu原子拡散を抑制する極薄酸化膜(図示せず)をCu合金10と純Cu11とCu合金10の表面に形成する。

【0104】

次に、図8(b)に示すように、プラズマCVD法,スパッタリング法,塗布法により、ゲート絶縁膜5として例えば酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜,酸化アルミニウム膜,酸化タンタル膜またはこれらの積層膜を成膜する。ゲート絶縁膜5が電極近接層となる。このとき、ゲート絶縁膜5の形成時の200〜500℃の程度で、ソース電極12及びドレイン電極13下層のCu合金10中の添加元素は界面に析出し、基板1の界面で密着性に優れた酸化物膜(図示せず)を自己形成する。また、活性半導体層7とソース電極12及びドレイン電極13の界面ではオゾン水酸化処理により形成した極薄酸化膜(図示せず)が拡散バリア層として機能し、Cu原子の活性半導体層7中への拡散を抑制する。その後ゲート絶縁膜5形成時の熱により極薄酸化膜(図示せず)は活性半導体層7とソース電極12及びドレイン電極13の構成元素で酸化物膜15を自己形成する。なお、電流はソース電極12及びドレイン電極13の下層にあるCu合金10がつくる酸化物膜15と活性半導体層7の間を横切る。したがって、酸化物膜15は低電気抵抗となるようにオゾン水酸化処理の溶存オゾン濃度を調整すると良い。

【0105】

次に、オゾン水洗浄を行い、極薄酸化膜(図示せず)をゲート絶縁膜5の表面に形成する。なお、このオゾン水酸化処理工程は下地のゲート絶縁膜5の表面に十分な酸素原子が含有されている場合は省略しても構わない。

【0106】

次に、スパッタ法により、Cu合金2,純Cu3からなる積層膜を、この順に成膜する。その後、フォトリソグラフィ工程を経て、ウェットエッチング法によりパターニングし、図8(c)に示すように、ゲート電極4を形成する。

【0107】

次に、図8(d)に示すように、プラズマCVD法,スパッタリング法,塗布法などにより、例えば、酸化シリコン膜,窒化シリコン膜,酸窒化シリコン膜、またはこれらの積層膜から成る保護膜14を成膜する。このとき、保護膜14の形成温度は200℃以上となるため、ゲート電極4下層にあるCu合金2中の添加元素が界面に析出される。界面に析出した添加元素は、ゲート絶縁膜5上に事前に形成した極薄酸化膜(図示せず)と化合し、密着性及び拡散バリア性に優れる酸化物膜18を自己形成する。これにフォトリソグラフィ工程を行い、外部装置と電気信号のやり取りを行うためのコンタクトホール(図示せず)を開口し、レジストを剥離する。このようにして、実施例7の表示装置向け酸化物半導体TFTを作製することができる。

【実施例8】

【0108】

図9および図10は、実施例8の内容を図示するものであり、液晶表示装置を例にとり、実施例1乃至7のTFTを表示装置へ用いる方法を説明するものである。なお、煩雑さを避けるためTFTの詳細な構造の図示は省略する。

【0109】

図9は、実施例8のアクティブマトリクス型液晶表示装置のTFT基板101の画素構成例を図示したものである。図9に示したように、TFT基板101上に走査線102と、これとは垂直に交差する方向に信号線103が配置されている。走査線102と信号線103の交差するポイントにはTFT104が置かれ、TFT104の配線の一部が画素電極105へ接続される。また、画素電極105及び走査線102の一部を用いてストレージキャパシタ106が設けられている。なお、走査線102を形成する工程で実施例1乃至7のTFTのゲート電極4(図示せず)が、信号線103を形成する工程で実施例1乃至7のTFTのソース電極12(図示せず)及びドレイン電極13(図示せず)が形成される。

【0110】

図10は、実施例8のアクティブマトリクス型液晶表示装置の構成例を示す断面図である。図10に示すように、液晶表示装置は、光源111,偏光板112,TFT基板101,TFT104,絶縁膜113,画素電極105,配向膜114,液晶層115,スペーサ116,共通電極117,カラーフィルタ118,ブラックマトリクス119,カラーフィルタ基板120,偏光フィルム121を有している。

【0111】

ここで、液晶表示装置の表示制御方法について簡単に述べる。光源111から放たれた光は偏光板112により特定の偏光成分のみが通過し、液晶層115へ向かう。液晶層115は画素電極105と共通電極117に供給される電圧に応じて、偏光フィルム121を通過する光透過率を調整することで画素の階調を制御する。

【0112】

次に、液晶層115の制御方法について、図9を用いて簡単に述べる。まず、走査線102からTFT104にゲート信号が印加されるとTFT104はオン状態になり、信号線103に加えられている信号電圧がTFT104を経由し画素電極105とストレージキャパシタ106に印加される。これにより、液晶層115に所望の電圧が印加され、液晶分子が動作し光透過率を制御する。このとき、ストレージキャパシタ106は、電圧信号を保持する役割をもつ。すなわち、TFT104がオフになっても次の信号が印加されるまで、液晶層115に供給されている電圧レベルを一定に調整する。

【0113】

本発明のTFTによれば、配線の電気抵抗値とTFTの電気特性値の均一性を損なわずにCu配線適用を実現することが可能になる。

【0114】

本発明のTFTによれば、配線の電気抵抗値とTFTの電気特性値の均一性を損なわずにCu配線適用を実現することが可能になる。本発明のTFTを実施例8の液晶表示装置に用いることにより、さらなる大型化と画質向上、そして製造コスト低減を図ることができる。

【0115】

なお、本実施例では本発明のTFTを液晶表示装置に適用する例を示したが、本発明のTFTは有機EL表示装置,電子ペーパーにも適用可能である。

【符号の説明】

【0116】

1 基板

2,10,17 Cu合金

3,11 純Cu

4 ゲート電極

5 ゲート絶縁膜

6,15,16,18 酸化物膜

7 活性半導体層

8 コンタクト膜

9 半導体層

12 ソース電極

13 ドレイン電極

14 保護膜

101 TFT基板

102 走査線

103 信号線

104 TFT

105 画素電極

106 ストレージキャパシタ

111 光源

112 偏光板

113 絶縁膜

114 配向膜

115 液晶層

116 スペーサ

117 共通電極

118 カラーフィルタ

119 ブラックマトリクス

120 カラーフィルタ基板

121 偏光フィルム

【特許請求の範囲】

【請求項1】

基板およびTFTを有する表示装置の製造方法であって、

前記TFTは、電極および電極近接層を有し、前記電極は、銅および銅以外の添加元素を含み、

以下の工程を含む表示装置の製造方法

(A)前記基板の上に前記電極および電極近接層が形成される工程、

(B)前記電極または前記電極近接層がオゾン水で洗浄される工程、

(C)前記(B)の工程後の熱処理により、前記電極と前記電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

【請求項2】

請求項1において、

前記電極はゲート電極であり、

前記電極近接層はゲート絶縁膜であり、

前記TFTは、半導体層,ソース電極およびドレイン電極を有し、

以下の工程を含む表示装置の製造方法

(D)前記基板の上に前記半導体層,前記ソース電極および前記ドレイン電極が形成される工程。

【請求項3】

請求項1において、

前記電極はソース電極およびドレイン電極であり、

前記電極近接層は半導体層であり、

前記TFTはゲート電極およびゲート絶縁膜を有し、

以下の工程を含む表示装置の製造方法

(E)前記基板の上に前記ゲート電極および前記ゲート絶縁膜が形成される工程。

【請求項4】

請求項2または3において、

前記ゲート電極の上に前記ソース電極および前記ドレイン電極が形成される表示装置の製造方法。

【請求項5】

請求項2または3において、

前記ソース電極および前記ドレイン電極の上に前記ゲート電極が形成される表示装置の製造方法。

【請求項6】

請求項2または3において、

前記ソース電極および前記ドレイン電極の上に前記半導体層が形成される表示装置の製造方法。

【請求項7】

請求項2または3において、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成される表示装置の製造方法。

【請求項8】

請求項2または3において、

前記半導体層は、活性半導体層およびコンタクト膜を含み、

前記活性半導体層および前記コンタクト膜は接している表示装置の製造方法。

【請求項9】

請求項2または3において、

前記半導体層は、酸化物半導体である表示装置の製造方法。

【請求項10】

請求項2において、

以下の工程を含む表示装置の製造方法

(F)前記ソース電極および前記ドレイン電極がオゾン水で洗浄される工程、

(G)前記(F)の工程後の熱処理により、前記ソース電極と前記半導体層との界面および前記ドレイン電極と半導体層との界面に、酸素を含むソース・ドレイン酸化物膜が形成される工程。

【請求項11】

請求項4において、

前記ゲート電極の上に前記ゲート絶縁膜が形成され、

前記(C)の工程における熱処理は、前記ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

【請求項12】

請求項5において、

前記TFTは、保護膜を有し、

前記ゲート絶縁膜の上に前記ゲート電極が形成され、

前記ゲート電極の上に前記保護膜が形成され、

前記(C)の工程における熱処理は、前記保護膜を形成するための熱処理である表示装置の製造方法。

【請求項13】

請求項6において、

前記(C)の工程における熱処理は、前記半導体層を形成するための熱処理である表示装置の製造方法。

【請求項14】

請求項7において、

前記TFTは、保護膜を有し、

前記ソース電極および前記ドレイン電極の上に前記保護層が形成され、

前記(C)の工程における熱処理は、前記保護膜を形成するための熱処理である表示装置の製造方法。

【請求項15】

請求項3において、

前記TFTは、保護膜を有し、

前記ソース電極および前記ドレイン電極の上に前記ゲート絶縁膜が形成され、

前記ゲート絶縁膜の上に前記ゲート電極が形成され、

前記ゲート電極の上に前記保護膜が形成され、

前記(C)の工程における熱処理は、前記ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

【請求項16】

請求項1において、

前記酸化物膜中の酸素原子はピークを有し、

前記ピーク値は2at%以上60at%以下であり、

前記基板上で前記ピーク値の3σ/Medianの値は0.5以下である表示装置の製造方法。

【請求項17】

請求項2または3において、

前記TFTのチャンネル長Lは、1μm以上100μm以下である表示装置の製造方法。

【請求項18】

請求項2または3において、

前記オゾン水の溶存オゾン濃度は、1ppm(mg/L)以上100ppm(mg/L)以下である表示装置の製造方法。

【請求項19】

請求項10において、

前記ゲート電極を洗浄するオゾン水の溶存オゾン濃度は、前記ソース電極および前記ドレイン電極を洗浄するオゾン水の溶存オゾン濃度以上である表示装置の製造方法。

【請求項1】

基板およびTFTを有する表示装置の製造方法であって、

前記TFTは、電極および電極近接層を有し、前記電極は、銅および銅以外の添加元素を含み、

以下の工程を含む表示装置の製造方法

(A)前記基板の上に前記電極および電極近接層が形成される工程、

(B)前記電極または前記電極近接層がオゾン水で洗浄される工程、

(C)前記(B)の工程後の熱処理により、前記電極と前記電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

【請求項2】

請求項1において、

前記電極はゲート電極であり、

前記電極近接層はゲート絶縁膜であり、

前記TFTは、半導体層,ソース電極およびドレイン電極を有し、

以下の工程を含む表示装置の製造方法

(D)前記基板の上に前記半導体層,前記ソース電極および前記ドレイン電極が形成される工程。

【請求項3】

請求項1において、

前記電極はソース電極およびドレイン電極であり、

前記電極近接層は半導体層であり、

前記TFTはゲート電極およびゲート絶縁膜を有し、

以下の工程を含む表示装置の製造方法

(E)前記基板の上に前記ゲート電極および前記ゲート絶縁膜が形成される工程。

【請求項4】

請求項2または3において、

前記ゲート電極の上に前記ソース電極および前記ドレイン電極が形成される表示装置の製造方法。

【請求項5】

請求項2または3において、

前記ソース電極および前記ドレイン電極の上に前記ゲート電極が形成される表示装置の製造方法。

【請求項6】

請求項2または3において、

前記ソース電極および前記ドレイン電極の上に前記半導体層が形成される表示装置の製造方法。

【請求項7】

請求項2または3において、

前記半導体層の上に前記ソース電極および前記ドレイン電極が形成される表示装置の製造方法。

【請求項8】

請求項2または3において、

前記半導体層は、活性半導体層およびコンタクト膜を含み、

前記活性半導体層および前記コンタクト膜は接している表示装置の製造方法。

【請求項9】

請求項2または3において、

前記半導体層は、酸化物半導体である表示装置の製造方法。

【請求項10】

請求項2において、

以下の工程を含む表示装置の製造方法

(F)前記ソース電極および前記ドレイン電極がオゾン水で洗浄される工程、

(G)前記(F)の工程後の熱処理により、前記ソース電極と前記半導体層との界面および前記ドレイン電極と半導体層との界面に、酸素を含むソース・ドレイン酸化物膜が形成される工程。

【請求項11】

請求項4において、

前記ゲート電極の上に前記ゲート絶縁膜が形成され、

前記(C)の工程における熱処理は、前記ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

【請求項12】

請求項5において、

前記TFTは、保護膜を有し、

前記ゲート絶縁膜の上に前記ゲート電極が形成され、

前記ゲート電極の上に前記保護膜が形成され、

前記(C)の工程における熱処理は、前記保護膜を形成するための熱処理である表示装置の製造方法。

【請求項13】

請求項6において、

前記(C)の工程における熱処理は、前記半導体層を形成するための熱処理である表示装置の製造方法。

【請求項14】

請求項7において、

前記TFTは、保護膜を有し、

前記ソース電極および前記ドレイン電極の上に前記保護層が形成され、

前記(C)の工程における熱処理は、前記保護膜を形成するための熱処理である表示装置の製造方法。

【請求項15】

請求項3において、

前記TFTは、保護膜を有し、

前記ソース電極および前記ドレイン電極の上に前記ゲート絶縁膜が形成され、

前記ゲート絶縁膜の上に前記ゲート電極が形成され、

前記ゲート電極の上に前記保護膜が形成され、

前記(C)の工程における熱処理は、前記ゲート絶縁膜を形成するための熱処理である表示装置の製造方法。

【請求項16】

請求項1において、

前記酸化物膜中の酸素原子はピークを有し、

前記ピーク値は2at%以上60at%以下であり、

前記基板上で前記ピーク値の3σ/Medianの値は0.5以下である表示装置の製造方法。

【請求項17】

請求項2または3において、

前記TFTのチャンネル長Lは、1μm以上100μm以下である表示装置の製造方法。

【請求項18】

請求項2または3において、

前記オゾン水の溶存オゾン濃度は、1ppm(mg/L)以上100ppm(mg/L)以下である表示装置の製造方法。

【請求項19】

請求項10において、

前記ゲート電極を洗浄するオゾン水の溶存オゾン濃度は、前記ソース電極および前記ドレイン電極を洗浄するオゾン水の溶存オゾン濃度以上である表示装置の製造方法。

【図1】

【図2(a)】

【図2(b)】

【図2(c)】

【図2(d)】

【図3(a)】

【図3(b)】

【図3(c)】

【図3(d)】

【図3(e)】

【図4(a)】

【図4(b)】

【図4(c)】

【図4(d)】

【図5(a)】

【図5(b)】

【図5(c)】

【図5(d)】

【図6(a)】

【図6(b)】

【図6(c)】

【図6(d)】

【図6(e)】

【図7(a)】

【図7(b)】

【図7(c)】

【図7(d)】

【図8(a)】

【図8(b)】

【図8(c)】

【図8(d)】

【図9】

【図10】

【図2(a)】

【図2(b)】

【図2(c)】

【図2(d)】

【図3(a)】

【図3(b)】

【図3(c)】

【図3(d)】

【図3(e)】

【図4(a)】

【図4(b)】

【図4(c)】

【図4(d)】

【図5(a)】

【図5(b)】

【図5(c)】

【図5(d)】

【図6(a)】

【図6(b)】

【図6(c)】

【図6(d)】

【図6(e)】

【図7(a)】

【図7(b)】

【図7(c)】

【図7(d)】

【図8(a)】

【図8(b)】

【図8(c)】

【図8(d)】

【図9】

【図10】

【公開番号】特開2012−222171(P2012−222171A)

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願番号】特願2011−86901(P2011−86901)

【出願日】平成23年4月11日(2011.4.11)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願日】平成23年4月11日(2011.4.11)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]