表示装置およびその駆動方法ならびに電子機器

【課題】閾値補正や書き込みを行う際のタイミングマージンを広くとることができ、かつ消費電力の増大を抑えることができる表示装置およびその駆動方法ならびに電子機器を提供する。

【解決手段】全ての画素においてVth補正が行われた後に、全ての画素において書き込み・μ補正が行われる。Vth補正を一旦休止し、その間に、書き込み・μ補正を行うようなことはしておらず、1フレーム期間内においてVth補正を行っている期間と、1フレーム期間内において書き込み・μ補正を行っている期間とが同時に存在していない。

【解決手段】全ての画素においてVth補正が行われた後に、全ての画素において書き込み・μ補正が行われる。Vth補正を一旦休止し、その間に、書き込み・μ補正を行うようなことはしておらず、1フレーム期間内においてVth補正を行っている期間と、1フレーム期間内において書き込み・μ補正を行っている期間とが同時に存在していない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、時分割方式の表示装置およびその駆動方法に関する。また、本発明は、上記表示装置を備えた電子機器に関する。

【背景技術】

【0002】

近年、平面映像だけでなく立体映像も表示することの可能な表示装置(3Dディスプレイ)が実用化されている。立体映像を表示させる方式としては、現在、偏光眼鏡方式と、時分割方式とが主流となっている。偏光眼鏡方式では、表示装置の左目用画素と右目用画素とで異なる偏光状態の光が射出され、視聴者が偏光眼鏡をかけた上で、左目用画素からの射出光を左目のみで視認し、右目用画素からの射出光を右目のみで視認することにより、立体映像の観察が可能となっている。時分割方式では、表示装置において左目用画像と右目用画像とが経時的に交互に表示され、視聴者がシャッター眼鏡をかけた上で、左目用画像を左目のみで視認し、右目用画像を右目のみで視認することにより、立体映像の観察が可能となっている(特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−031524号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、時分割方式では、クロストークを防止するために、例えば、左目用画像と右目用画像との間に黒画像を表示する。黒画像を左目用画像と右目用画像との間に挿入する場合には、1F期間中に、例えば、黒画像、左目用画像、黒画像、右目用画像を順次表示することが必要となる。そのため、1Fを1/60秒としたときには、240Hzで表示画素を駆動することが必要となる。

【0005】

表示画素が有機EL(electro luminescence)素子からなる場合には、有機EL素子を駆動する画素回路の閾値補正や書き込みを高速で行うことになるが、閾値補正や書き込みを行う際のタイミングマージンが狭くなってしまうという問題があった。また、閾値補正や書き込みの高速化に伴い、消費電力が増大してしまうという問題があった。

【0006】

本発明はかかる問題点に鑑みてなされたもので、その目的は、閾値補正や書き込みを行う際のタイミングマージンを広くとることができ、かつ消費電力の増大を抑えることができる表示装置およびその駆動方法ならびに電子機器を提供することにある。

【課題を解決するための手段】

【0007】

本発明の表示装置は、行列状に配置された複数の発光素子および複数の画素回路と、全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行う駆動回路とを備えたものである。

【0008】

本発明の電子機器は、上記表示装置を備えたものである。

【0009】

本発明の表示装置の駆動方法は、以下の2つのステップを含むものである。

(A)行列状に配置された複数の発光素子および複数の画素回路と、複数の画素回路を駆動する駆動回路とを備えた表示装置を用意するステップ

(B)駆動回路を用いて、全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行うステップ

【0010】

本発明の表示装置およびその駆動方法ならびに電子機器では、全ての画素回路の閾値補正が行われたのち、映像信号に対応する信号電圧の、各画素回路への書き込みが行われる。これにより、閾値補正を一旦休止する期間を設け、その間に他の水平ラインにおける書き込み動作を行うようにした場合と比べて、閾値補正にかける時間を十分長くとることができる。また、画素回路への充放電の回数が減少する。

【発明の効果】

【0011】

本発明の表示装置およびその駆動方法ならびに電子機器によれば、全ての画素回路の閾値補正が行われたのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行うようにした。これにより、閾値補正や書き込みを行う際のタイミングマージンを広くとることができ、かつ消費電力の増大を抑えることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の一実施の形態に係る表示装置の一例を表す構成図である。

【図2】図1の画素回路アレイ部の内部構成の一例を表す構成図である。

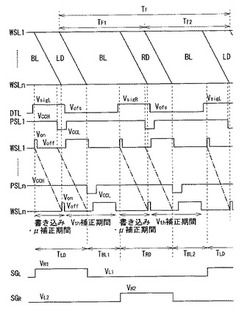

【図3】図1の表示装置の1フレーム期間内の動作の一例について説明するための波形図である。

【図4】図1の表示装置の1H期間内の動作の一例について説明するための波形図である。

【図5】比較例に係る表示装置の1フレーム期間内の動作の一例について説明するための波形図である。

【図6】比較例に係る表示装置の1H期間内の動作の一例について説明するための波形図である。

【図7】図1の表示装置の1フレーム期間内の動作の他の例について説明するための波形図である。

【図8】図1の表示装置の1フレーム期間内の動作のその他の例について説明するための波形図である。

【図9】上記実施の形態の表示装置を含むモジュールの概略構成を表す平面図である。

【図10】上記実施の形態の表示装置の適用例1の外観を表す斜視図である。

【図11】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図12】適用例3の外観を表す斜視図である。

【図13】適用例4の外観を表す斜視図である。

【図14】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0013】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.実施の形態

1.1 表示装置の概略構成

1.2 表示装置の動作

1.3 作用・効果

2.モジュールおよび適用例

【0014】

<1.実施の形態>

(1.1 表示装置の概略構成)

図1は、本発明の一実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、平面映像だけでなく立体映像も表示することの可能な表示装置(3Dディスプレイ)であり、時分割方式により立体映像の観察が可能なものである。

【0015】

表示装置1は、例えば、表示パネル10と、駆動回路20と、シャッター眼鏡(図示せず)とを備えている。表示パネル10は、例えば、複数の有機EL素子11R,11G,11B(発光素子)がマトリクス状に配置された画素回路アレイ部13を有している。本実施の形態では、例えば、互いに隣り合う3つの有機EL素子11R,11G,11Bが1つの画素12を構成している。なお、以下では、有機EL素子11R,11G,11Bの総称として有機EL素子11を適宜、用いるものとする。駆動回路20は、画素回路アレイ部13を駆動するものであり、例えば、映像信号処理回路21、タイミング生成回路22、信号線駆動回路23、走査線駆動回路24および電源線駆動回路25を有している。

【0016】

[画素回路アレイ部]

図2は、画素回路アレイ部13の回路構成の一例を表したものである。画素回路アレイ部13は、表示パネル10の表示領域に形成されている。画素回路アレイ部13は、例えば、図1、図2に示したように、行状に配置された複数の走査線WSLと、列状に配置された複数の信号線DTLと、走査線WSLに沿って行状に配置された複数の電源線PSLとを有している。各走査線WSLと各信号線DTLとの交差部に対応して、複数の有機EL素子11および画素回路14が行列状に配置(2次元配置)されている。画素回路14は、例えば、駆動トランジスタTr1、書き込みトランジスタTr2および保持容量Csによって構成されたものであり、2Tr1Cの回路構成となっている。駆動トランジスタTr1および書き込みトランジスタTr2は、例えば、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている。なお、TFTの種類は特に限定されるものではなく、例えば、逆スタガー構造(いわゆるボトムゲート型)であってもよいし、スタガー構造(トップゲート型)であってもよい。また、駆動トランジスタTr1または書き込みトランジスタTr2は、pチャネルMOS型のTFTであってもよい。

【0017】

画素回路アレイ部13において、各信号線DTLは、信号線駆動回路23の出力端(図示せず)と、書き込みトランジスタTr2のドレイン電極(図示せず)に接続されている。各走査線WSLは、走査線駆動回路24の出力端(図示せず)と、書き込みトランジスタTr2のゲート電極(図示せず)に接続されている。各電源線PSLは、電源線駆動回路25の出力端(図示せず)と、駆動トランジスタTr1のドレイン電極(図示せず)に接続されている。書き込みトランジスタTr2のソース電極(図示せず)は、駆動トランジスタTr1のゲート電極(図示せず)と、保持容量Csの一端に接続されている。駆動トランジスタTr1のソース電極(図示せず)と保持容量Csの他端とが、有機EL素子11のアノード電極(図示せず)に接続されている。有機EL素子11のカソード電極(図示せず)は、例えばグラウンド線GNDに接続されている。なお、カソード電極は、各有機EL素子11の共通電極として用いられており、例えば、表示パネル10の表示領域全体に渡って連続して形成され、平板状となっている。

【0018】

[駆動回路]

次に、画素回路アレイ部13の周辺に設けられた駆動回路20内の各回路について、図1を参照して説明する。映像信号処理回路21は、外部から入力されたデジタルの映像信号20Aに対して所定の補正を行うと共に、補正した後の映像信号を信号線駆動回路23に出力するものである。映像信号20Aの種類としては、例えば、右目用画像用の映像信号、左目用画像用の映像信号、黒画像用の映像信号などが挙げられる。また、所定の補正としては、例えば、ガンマ補正や、オーバードライブ補正などが挙げられる。

【0019】

タイミング生成回路22は、信号線駆動回路23、走査線駆動回路24および電源線駆動回路25が連動して動作するように制御するものである。タイミング生成回路22は、例えば、外部から入力された同期信号20Bに応じて(同期して)、これらの回路に対して制御信号22Aを出力するようになっている。

【0020】

信号線駆動回路23は、制御信号22Aの入力に応じて(同期して)、映像信号処理回路21から入力された映像信号20Aに対応するアナログの映像信号を、各信号線DTLに印加して、アナログの映像信号またはそれに対応する信号を選択対象の画素回路14に書き込むものである。具体的には、信号線駆動回路23は、例えば、図3に示したように、1フレーム期間TFごとに、黒画像用の映像信号20Aに対応する信号電圧Vofsと、右目用画像用の映像信号20Aに対応する信号電圧VsigRと、黒画像用の映像信号20Aに対応する信号電圧Vofsと、左目用画像用の映像信号20Aに対応する信号電圧VsigLとを、この順に各信号線DTLに印加して、選択対象の画素回路14への書き込みを行うものである。なお、図3は、表示装置1を駆動させたときの1フレーム期間内の各種波形の一例を表したものである。

【0021】

ところで、上記の「書き込み」とは、駆動トランジスタTr1のゲート−ソース間に所定の電圧を印加することを指している。また、信号線駆動回路23が1フレーム期間TF中に各信号線DTLに印加する電圧の順番は、上記の順番に限られるものではなく、左目用画像用の映像信号と、右目用画像用の映像信号との間に、黒画像用の映像信号が挿入されていれば、どのような順番であってもよい。

【0022】

信号線駆動回路23は、例えば、有機EL素子11の発光時に駆動トランジスタTr1のゲートに印加する信号電圧VsigR,VsigLと、有機EL素子11の消光時に駆動トランジスタTr1のゲートに印加する電圧Vofsとを出力することが可能となっている。ここで、電圧Vofsは、有機EL素子11の閾値電圧Velよりも低い電圧値(一定値)となっており、かつ信号電圧VsigR,VsigLの最小電圧よりも高い電圧値となっている。

【0023】

走査線駆動回路24は、制御信号22Aの入力に応じて(同期して)、複数の走査線WSLに選択パルスを順次印加して、複数の有機EL素子11および複数の画素回路14を順次選択するものである。走査線駆動回路24は、例えば、書き込みトランジスタTr2をオンさせるときに印加する電圧Vonと、書き込みトランジスタTr2をオフさせるときに印加する電圧Voffとを出力することが可能となっている。ここで、電圧Vonは、書き込みトランジスタTr2のオン電圧以上の値(一定値)となっている。電圧Voffは、書き込みトランジスタTr2のオン電圧よりも低い値(一定値)となっている。

【0024】

電源線駆動回路25は、制御信号22Aの入力に応じて(同期して)、複数の電源線PSLに制御パルスを順次印加して、有機EL素子11の発光および消光を制御するものである。電源線駆動回路25は、例えば、駆動トランジスタTr1に電流を流すときに印加する電圧VccHと、駆動トランジスタTr1に電流を流さないときに印加する電圧VccLとを出力することが可能となっている。ここで、電圧VccLは、有機EL素子11の閾値電圧Velと、有機EL素子11のカソードの電圧Vcaとを足し合わせた電圧(Vel+Vca)よりも低い電圧値(一定値)である。VccHは、電圧(Vel+Vca)以上の電圧値(一定値)である。

【0025】

(シャッター眼鏡)

シャッター眼鏡は、例えば、図示しないが、左目用シャッターと、右目用シャッターと、左目用シャッターの開閉を制御する制御信号を印加する制御線SGLと、右目用シャッターの開閉を制御する制御信号を印加する制御線SGRとを有している。制御線SGLおよび制御線SGRは、駆動回路20に直接接続されていてもよいし、駆動回路20と通信可能な無線装置に接続されていてもよい。

【0026】

(1.2 表示装置の動作)

図4は、表示装置1を駆動させたときの1H期間内の各種波形の一例を表したものである。図4には、例えば、黒画像用の映像信号20Aに対応する信号電圧Vofsと、右目用画像用の映像信号20Aに対応する信号電圧VsigRとが印加される期間TF1の信号波形、または黒画像用の映像信号20Aに対応する信号電圧Vofsと、左目用画像用の映像信号20Aに対応する信号電圧VsigLとが印加される期間TF1の信号波形が表されている。図4(A)〜(C)には、信号線DTLにVofs、VsigL、VsigRが所定のタイミングで印加され、走査線WSLにVon、Voffが所定のタイミングで印加され、電源線PSLにVccL、VccHが所定のタイミングで印加されている様子が示されている。図4(D),(E)には、信号線DTL、走査線WSLおよび電源線PSLへの電圧印加に応じて、駆動トランジスタTr1のゲート電圧Vgおよびソース電圧Vsが時々刻々変化している様子が示されている。

【0027】

[Vth補正準備期間]

まず、Vth補正の準備を行う。具体的には、電源線駆動回路25が電源線PSLの電圧をVccHからVccLに下げる(T1)。すると、ソース電圧VsがVccLとなり、有機EL素子11が消光すると共に、ゲート電圧Vgは発光時のVgsをVgs0とすると(VccL+Vgs0)となる。次に、信号線DTLの電圧がVofsとなっており、かつ電源線PSLの電圧がVccLとなっている間に、走査線駆動回路24が走査線WSLの電圧をVoffからVonに上げる。

【0028】

[Vth補正期間]

次に、Vthの補正を行う。具体的には、信号線DTLの電圧がVofsとなっている間に、電源線駆動回路25が電源線PSLの電圧をVccLからVccHに上げる(T2)。すると、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れ、ソース電圧Vsが上昇する。このとき、ソース電圧Vsが(Vofs−Vth)よりも低い場合(Vth補正がまだ完了していない場合)には、駆動トランジスタTr1がカットオフするまで(電位差VgsがVthになるまで)、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れる。その結果、保持容量CsがVthに充電され、電位差VgsがVthとなる。その後、信号線駆動回路23が信号線DTLの電圧をVofsからVsigLまたはVsigRに切り替える前に、走査線駆動回路24が走査線WSLの電圧をVonからVoffに下げる(T3)。すると、駆動トランジスタTr1のゲートがフローティングとなるので、電位差Vgsを信号線DTLの電圧の大きさに拘わらずVthのままで維持することができる。このように、電位差VgsをVthに設定することにより、駆動トランジスタTr1の閾値電圧Vthが画素回路14ごとにばらついた場合であっても、有機EL素子11の発光輝度がばらつくのをなくすことができる。なお、Vth補正期間において、信号線駆動回路23は信号線DTLの電圧をVofsに維持する。

【0029】

[待機期間]

次に、後述の書き込み・μ補正期間(移動度補正期間)がやってくるまでのしばらくの間、そのままの状態で待機する。このとき、信号線駆動回路23は信号線DTLの電圧をVofsに維持する。その後、書き込み・μ補正期間が開始する少し前に、信号線駆動回路23が信号線DTLの電圧をVofsからVsigLまたはVsigRに切り替える。例えば、1フレーム期間TFの前半では、信号線駆動回路23が信号線DTLの電圧をVofsからVsigRに切り替え、1フレーム期間TFの後半では、信号線駆動回路23が信号線DTLの電圧をVofsからVsigLに切り替える。

【0030】

[書き込み・μ補正期間]

待機期間が終了した後、書き込み・μ補正期間を行う。具体的には、信号線DTLの電圧がVsigLまたはVsigRとなっている間に、走査線駆動回路24が走査線WSLの電圧をVoffからVonに上げ(T4)、駆動トランジスタTr1のゲートを信号線DTLに接続する。すると、駆動トランジスタTr1のゲート電圧がVsigLまたはVsigRとなる。このとき、有機EL素子11のアノード電圧はこの段階ではまだ有機EL素子11の閾値電圧Velよりも小さく、有機EL素子11はカットオフしている。そのため、電流Idは有機EL素子11の素子容量(図示せず)に流れ、素子容量が充電されるので、ソース電圧VsがΔVだけ上昇し、やがて電位差VgsがVsigL+Vth−ΔV(またはVsigR+Vth−ΔV)となる。このようにして、書き込みと同時にμ補正が行われる。ここで、駆動トランジスタTr1の移動度μが大きい程、ΔVも大きくなるので、電位差Vgsを発光前にΔVだけ小さくすることにより、画素回路14ごとの移動度μのばらつきを取り除くことができる。

【0031】

[発光期間]

最後に、走査線駆動回路24が走査線WSLの電圧をVonからVoffに下げる(T5)。すると、駆動トランジスタTr1のゲートがフローティングとなり、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れ、ソース電圧Vsが上昇する。その結果、有機EL素子11が所望の輝度で発光する。このとき、信号線駆動回路23は信号線DTLの電圧をVsigLまたはVsigRに維持する。

【0032】

[繰り返し]

次に、所定の期間が経過したのち、発光期間を終了する。具体的には、電源線駆動回路25が電源線PSLの電圧をVccHからVccLに下げる(T1)。すると、ソース電圧VsがVccLとなり、有機EL素子11が消光する。その後、上述した各期間に対応した駆動を実行する。このように、本実施の形態では、例えば、図4に示したように、Vth補正準備期間、Vth補正期間、待機期間、書き込み・μ補正期間、発光期間がフレーム期間TFごとに繰り返される。

【0033】

ところで、本実施の形態では、走査線駆動回路24および電源線駆動回路25は共に、電源線PSLおよび走査線WSLを行方向にスキャンする。そのため、信号線駆動回路23が、1フレーム期間TFごとに、信号電圧Vofs、VsigR、Vofs、VsigLを、この順に各信号線DTLに印加しているときに、たいていは、表示装置1に表示される画像には、スキャンラインの上方または下方に対応する部分に黒画像の一部が含まれる。なお、表示装置1の画面(画像)全体が右目用画像、左目用画像または黒画像である期間が存在していることが好ましいが、場合によっては存在していなくてもよい。

【0034】

以下では、右目用画像の少なくとも一部が表示装置1に表示されている期間を、右目用画像を表示する期間(右目用画像表示期間TRD)と称するものとする。同様に、左目用画像の少なくとも一部が表示装置1に表示されている期間を、左目用画像を表示する期間(左目用画像表示期間TLD)と称するものとする。また、表示装置1の全体に黒画像が表示されている期間を、黒画像を表示する期間(黒画像表示期間TBL1,TBL2)と称するものとする。なお、黒画像表示期間TBL1は、1フレーム期間TFにおいて右目用画像を表示する前の黒画像表示期間に対応している。黒画像表示期間TBL2は、1フレーム期間TFにおいて左目用画像を表示する前の黒画像表示期間に対応している。

【0035】

本実施の形態では、駆動回路20は、例えば、図3に示したように、黒画像表示期間TBL1、右目用画像表示期間TRD、黒画像表示期間TBL2、左目用画像表示期間TLDをフレーム期間TFごとに繰り返す。このとき、視聴者は、図示しないシャッター眼鏡をかけた上で、左目用画像を左目のみで視認し、右目用画像を右目のみで視認する。例えば、図3に示したように、左目用画像表示期間TLDに、左目用シャッターを開く(左目用眼鏡を透過状態にする)信号電圧VH1が印加され、それ以外の期間に、左目用シャッターを閉じる(左目用眼鏡を非透過状態にする)信号電圧VL1が印加される。また、例えば、図3に示したように、右目用画像表示期間TRDに、右目用シャッターを開く(右目用眼鏡を透過状態にする)信号電圧VH2が印加され、それ以外の期間に、右目用シャッターを閉じる(右目用眼鏡を非透過状態にする)信号電圧VL2が印加される。これにより、左目用画像が左目のみで視認され、右目用画像が右目のみで視認されるので、左目用画像と右目用画像とが観察者の網膜で結像される。その結果、視聴者は立体映像を観察することができる。

【0036】

(1.3 作用・効果)

ところで、従来の有機EL表示装置では、例えば、図5、図6に示したように、Vth補正準備期間、Vth補正期間、Vth補正休止期間、書き込み・μ補正期間、発光期間が1水平ラインごとに順次行われる。このとき、例えば、図5に示したように、1フレーム期間内においてVth補正を行っている期間αと、1フレーム期間内において書き込み・μ補正を行っている期間βとが同時に存在している。ただし、厳密には、1フレーム期間内において、Vth補正と、書き込み・μ補正とを同時に行うことはできないので、従来の有機EL表示装置では、例えば、図6に示したように、Vth補正期間を複数に分けると共に、Vth補正休止期間を複数設け、Vth補正休止期間に他の水平ラインにおける書き込み・μ補正を行うようにしている。ところで、このようにVth補正休止期間を設けた場合に、Vth補正期間として十分な時間を確保するためには、走査線WSLのシフト動作をやや高速化することが必要となる。例えば、1920×1080画素数のパネルでフィールドシーケンシャルの駆動を考えると、走査線WSLのシフト周期は、1/(1080×240Hz)=3.86μsecとなり、この期間内にVth補正、書き込み・μ補正を行う必要がある。

【0037】

一方、本実施の形態では、例えば、図3に示したように、全ての画素12においてVth補正が行われた後に、全ての画素12において書き込み・μ補正が行われている。つまり、Vth補正を一旦休止し、その間に、書き込み・μ補正を行うようなことはしておらず、1フレーム期間内においてVth補正を行っている期間と、1フレーム期間内において書き込み・μ補正を行っている期間とが同時に存在していない。従って、Vth補正にかける時間を十分長くとることができ、走査線WSLのシフト動作を従来ほどに高速化する必要がない。例えば、例えば、1画素12においてVth補正時間が300μsec必要とすると、1/120Hz=8.3msec中の4.3msecがVth補正期間となり、残りの4msecが書き込み・μ補正期間となる。よって、本実施の形態では、走査線WSLのシフト周期は、4msec/1080=3.7μsecとなり、この期間内に書き込み・μ補正だけを行えばよいので、本実施の形態の方が、従来の有機EL表示装置よりも、Vth補正や、書き込み・μ補正を行う際のタイミングマージンが大きい。

【0038】

また、本実施の形態では、全ての画素12においてVth補正が行われた後に、全ての画素12において書き込み・μ補正が行われていることから、従来の有機EL表示装置のような、信号線DTLに1H周期でパルスを印加することを要しない。また、本実施の形態では、走査線WSLについても、従来の有機EL表示装置のような、高速駆動を要しない。従って、画素回路14への充放電の回数、具体的には、信号線DTLおよび走査線WSLの充放電の回数が減少するので、消費電力を低減することができる。

【0039】

<変形例>

上記実施の形態では、Vth補正および書き込み・μ補正は共に、走査線WSLのスキャンにより1水平ラインごとに順次行われていたが、例えば、図7に示したように、Vth補正が全ての画素12において同時に(一括して)行われてもよい。例えば、走査線駆動回路24が、Vth補正に際して、全ての走査線WSLに選択パルスを同時に印加して、全ての有機EL素子11および全ての画素回路14を選択するようにしてもよい。このようにした場合には、Vth補正が走査線WSLのスキャンにより1水平ラインごとに順次行われていた場合と比べて、全ての画素12に対してVth補正を行うのに要する時間を短くすることができる。従って、本変形例の方が、従来の有機EL表示装置や上記の実施の形態の表示装置1よりも、Vth補正や、書き込み・μ補正を行う際のタイミングマージンが大きい。

【0040】

また、本変形例では、Vth補正を行う際にスキャン駆動を行わない。そのため、上記実施の形態の場合と比べて、走査線WSLの充放電が減少するので、消費電力をより低減することができる。

【0041】

また、上記実施の形態では、各画素12において、Vth補正が終了した後、書き込み・μ補正を行うまでの間、電源線PSLにはVccHが印加されていたが、例えば、図8に示したように、その間の少なくとも一部の期間の間、電源線PSLにVccLが印加されていてもよい。このようにした場合には、電源線PSLにVccLが印加されている間、画素回路14への電流供給が停止する。その結果、Vth補正が終了した後、書き込み・μ補正を行うまでの間に、駆動トランジスタTr1のリーク電流に起因して駆動トランジスタTr1のゲート−ソース間の電圧Vgsが変化するのを抑制することができる。

【0042】

<2.モジュールおよび適用例>

以下、上述した実施の形態で説明した表示装置の適用例について説明する。上記実施の形態の表示装置は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、映像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0043】

(モジュール)

上記実施の形態の表示装置1は、例えば、図9に示したようなモジュールとして、後述する適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板31の一辺に、封止用基板32から露出した領域210を設け、この露出した領域210に、駆動回路20の配線を延長して外部接続端子(図示せず)を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

【0044】

(適用例1)

図10は、上記実施の形態の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記各実施の形態に係る表示装置1により構成されている。

【0045】

(適用例2)

図11は、上記実施の形態の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上記実施の形態に係る表示装置1により構成されている。

【0046】

(適用例3)

図12は、上記実施の形態の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および映像を表示する表示部530を有しており、その表示部530は、上記各実施の形態に係る表示装置1により構成されている。

【0047】

(適用例4)

図13は、上記実施の形態の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上記各実施の形態に係る表示装置1により構成されている。

【0048】

(適用例5)

図14は、上記実施の形態の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記各実施の形態に係る表示装置1により構成されている。

【0049】

以上、実施の形態および適用例を挙げて本発明を説明したが、本発明は上記実施の形態等に限定されるものではなく、種々変形が可能である。

【0050】

例えば、上記実施の形態等では、表示装置1がアクティブマトリクス型である場合について説明したが、アクティブマトリクス駆動のための画素回路14の構成は上記実施の形態等で説明したものに限られず、必要に応じて容量素子やトランジスタを画素回路14に追加してもよい。その場合、画素回路14の変更に応じて、上述した信号線駆動回路23、走査線駆動回路24、電源線駆動回路25のほかに、必要な駆動回路を追加してもよい。

【0051】

また、上記実施の形態等では、信号線駆動回路23、走査線駆動回路24、電源線駆動回路25の駆動をタイミング制御回路22が制御していたが、他の回路がこれらの駆動を制御するようにしてもよい。また、信号線駆動回路23、走査線駆動回路24、電源線駆動回路25の制御は、ハードウェア(回路)で行われていてもよいし、ソフトウェア(プログラム)で行われていてもよい。

【0052】

また、上記実施の形態等では、画素回路14が、2Tr1Cの回路構成となっていたが、トランジスタが有機EL素子11に直列に接続された回路構成を含んでいるものであれば、2Tr1Cの回路構成以外の回路構成となっていてもよい。

【0053】

また、上記実施の形態等では、駆動トランジスタTr1,書き込みトランジスタTr2は、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている場合が例示されていたが、pチャネルトランジスタ(例えばpチャネルMOS型のTFT)により形成されていてもよい。ただし、その場合には、トランジスタTr2のソースおよびドレインのうち電源線PSLと未接続の方と保持容量Csの他端とを有機EL素子11のカソードに接続し、有機EL素子11のアノードをGNDなどに接続することが好ましい。

【符号の説明】

【0054】

1…表示装置、10…表示パネル、11,11R,11G,11B…有機EL素子、12…画素、13…画素回路アレイ部、14…画素回路、20…駆動回路、20A…映像信号、20B…同期信号、21…映像信号処理回路、22…タイミング生成回路、22A…制御信号、23…信号線駆動回路、24…走査線駆動回路、25…電源線駆動回路、Cs…保持容量、DTL…信号線、GND…グラウンド線、Id…電流、PSL…電源線、Tr1…駆動トランジスタ、Tr2…書き込みトランジスタ、Vg…ゲート電圧、Vgs…ゲート−ソース間電圧、Vs…ソース電圧、Vth…閾値電圧、WSL…走査線、α…Vth補正期間、β…書き込み・μ補正期間。

【技術分野】

【0001】

本発明は、時分割方式の表示装置およびその駆動方法に関する。また、本発明は、上記表示装置を備えた電子機器に関する。

【背景技術】

【0002】

近年、平面映像だけでなく立体映像も表示することの可能な表示装置(3Dディスプレイ)が実用化されている。立体映像を表示させる方式としては、現在、偏光眼鏡方式と、時分割方式とが主流となっている。偏光眼鏡方式では、表示装置の左目用画素と右目用画素とで異なる偏光状態の光が射出され、視聴者が偏光眼鏡をかけた上で、左目用画素からの射出光を左目のみで視認し、右目用画素からの射出光を右目のみで視認することにより、立体映像の観察が可能となっている。時分割方式では、表示装置において左目用画像と右目用画像とが経時的に交互に表示され、視聴者がシャッター眼鏡をかけた上で、左目用画像を左目のみで視認し、右目用画像を右目のみで視認することにより、立体映像の観察が可能となっている(特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−031524号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、時分割方式では、クロストークを防止するために、例えば、左目用画像と右目用画像との間に黒画像を表示する。黒画像を左目用画像と右目用画像との間に挿入する場合には、1F期間中に、例えば、黒画像、左目用画像、黒画像、右目用画像を順次表示することが必要となる。そのため、1Fを1/60秒としたときには、240Hzで表示画素を駆動することが必要となる。

【0005】

表示画素が有機EL(electro luminescence)素子からなる場合には、有機EL素子を駆動する画素回路の閾値補正や書き込みを高速で行うことになるが、閾値補正や書き込みを行う際のタイミングマージンが狭くなってしまうという問題があった。また、閾値補正や書き込みの高速化に伴い、消費電力が増大してしまうという問題があった。

【0006】

本発明はかかる問題点に鑑みてなされたもので、その目的は、閾値補正や書き込みを行う際のタイミングマージンを広くとることができ、かつ消費電力の増大を抑えることができる表示装置およびその駆動方法ならびに電子機器を提供することにある。

【課題を解決するための手段】

【0007】

本発明の表示装置は、行列状に配置された複数の発光素子および複数の画素回路と、全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行う駆動回路とを備えたものである。

【0008】

本発明の電子機器は、上記表示装置を備えたものである。

【0009】

本発明の表示装置の駆動方法は、以下の2つのステップを含むものである。

(A)行列状に配置された複数の発光素子および複数の画素回路と、複数の画素回路を駆動する駆動回路とを備えた表示装置を用意するステップ

(B)駆動回路を用いて、全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行うステップ

【0010】

本発明の表示装置およびその駆動方法ならびに電子機器では、全ての画素回路の閾値補正が行われたのち、映像信号に対応する信号電圧の、各画素回路への書き込みが行われる。これにより、閾値補正を一旦休止する期間を設け、その間に他の水平ラインにおける書き込み動作を行うようにした場合と比べて、閾値補正にかける時間を十分長くとることができる。また、画素回路への充放電の回数が減少する。

【発明の効果】

【0011】

本発明の表示装置およびその駆動方法ならびに電子機器によれば、全ての画素回路の閾値補正が行われたのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行うようにした。これにより、閾値補正や書き込みを行う際のタイミングマージンを広くとることができ、かつ消費電力の増大を抑えることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の一実施の形態に係る表示装置の一例を表す構成図である。

【図2】図1の画素回路アレイ部の内部構成の一例を表す構成図である。

【図3】図1の表示装置の1フレーム期間内の動作の一例について説明するための波形図である。

【図4】図1の表示装置の1H期間内の動作の一例について説明するための波形図である。

【図5】比較例に係る表示装置の1フレーム期間内の動作の一例について説明するための波形図である。

【図6】比較例に係る表示装置の1H期間内の動作の一例について説明するための波形図である。

【図7】図1の表示装置の1フレーム期間内の動作の他の例について説明するための波形図である。

【図8】図1の表示装置の1フレーム期間内の動作のその他の例について説明するための波形図である。

【図9】上記実施の形態の表示装置を含むモジュールの概略構成を表す平面図である。

【図10】上記実施の形態の表示装置の適用例1の外観を表す斜視図である。

【図11】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図12】適用例3の外観を表す斜視図である。

【図13】適用例4の外観を表す斜視図である。

【図14】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0013】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.実施の形態

1.1 表示装置の概略構成

1.2 表示装置の動作

1.3 作用・効果

2.モジュールおよび適用例

【0014】

<1.実施の形態>

(1.1 表示装置の概略構成)

図1は、本発明の一実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、平面映像だけでなく立体映像も表示することの可能な表示装置(3Dディスプレイ)であり、時分割方式により立体映像の観察が可能なものである。

【0015】

表示装置1は、例えば、表示パネル10と、駆動回路20と、シャッター眼鏡(図示せず)とを備えている。表示パネル10は、例えば、複数の有機EL素子11R,11G,11B(発光素子)がマトリクス状に配置された画素回路アレイ部13を有している。本実施の形態では、例えば、互いに隣り合う3つの有機EL素子11R,11G,11Bが1つの画素12を構成している。なお、以下では、有機EL素子11R,11G,11Bの総称として有機EL素子11を適宜、用いるものとする。駆動回路20は、画素回路アレイ部13を駆動するものであり、例えば、映像信号処理回路21、タイミング生成回路22、信号線駆動回路23、走査線駆動回路24および電源線駆動回路25を有している。

【0016】

[画素回路アレイ部]

図2は、画素回路アレイ部13の回路構成の一例を表したものである。画素回路アレイ部13は、表示パネル10の表示領域に形成されている。画素回路アレイ部13は、例えば、図1、図2に示したように、行状に配置された複数の走査線WSLと、列状に配置された複数の信号線DTLと、走査線WSLに沿って行状に配置された複数の電源線PSLとを有している。各走査線WSLと各信号線DTLとの交差部に対応して、複数の有機EL素子11および画素回路14が行列状に配置(2次元配置)されている。画素回路14は、例えば、駆動トランジスタTr1、書き込みトランジスタTr2および保持容量Csによって構成されたものであり、2Tr1Cの回路構成となっている。駆動トランジスタTr1および書き込みトランジスタTr2は、例えば、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている。なお、TFTの種類は特に限定されるものではなく、例えば、逆スタガー構造(いわゆるボトムゲート型)であってもよいし、スタガー構造(トップゲート型)であってもよい。また、駆動トランジスタTr1または書き込みトランジスタTr2は、pチャネルMOS型のTFTであってもよい。

【0017】

画素回路アレイ部13において、各信号線DTLは、信号線駆動回路23の出力端(図示せず)と、書き込みトランジスタTr2のドレイン電極(図示せず)に接続されている。各走査線WSLは、走査線駆動回路24の出力端(図示せず)と、書き込みトランジスタTr2のゲート電極(図示せず)に接続されている。各電源線PSLは、電源線駆動回路25の出力端(図示せず)と、駆動トランジスタTr1のドレイン電極(図示せず)に接続されている。書き込みトランジスタTr2のソース電極(図示せず)は、駆動トランジスタTr1のゲート電極(図示せず)と、保持容量Csの一端に接続されている。駆動トランジスタTr1のソース電極(図示せず)と保持容量Csの他端とが、有機EL素子11のアノード電極(図示せず)に接続されている。有機EL素子11のカソード電極(図示せず)は、例えばグラウンド線GNDに接続されている。なお、カソード電極は、各有機EL素子11の共通電極として用いられており、例えば、表示パネル10の表示領域全体に渡って連続して形成され、平板状となっている。

【0018】

[駆動回路]

次に、画素回路アレイ部13の周辺に設けられた駆動回路20内の各回路について、図1を参照して説明する。映像信号処理回路21は、外部から入力されたデジタルの映像信号20Aに対して所定の補正を行うと共に、補正した後の映像信号を信号線駆動回路23に出力するものである。映像信号20Aの種類としては、例えば、右目用画像用の映像信号、左目用画像用の映像信号、黒画像用の映像信号などが挙げられる。また、所定の補正としては、例えば、ガンマ補正や、オーバードライブ補正などが挙げられる。

【0019】

タイミング生成回路22は、信号線駆動回路23、走査線駆動回路24および電源線駆動回路25が連動して動作するように制御するものである。タイミング生成回路22は、例えば、外部から入力された同期信号20Bに応じて(同期して)、これらの回路に対して制御信号22Aを出力するようになっている。

【0020】

信号線駆動回路23は、制御信号22Aの入力に応じて(同期して)、映像信号処理回路21から入力された映像信号20Aに対応するアナログの映像信号を、各信号線DTLに印加して、アナログの映像信号またはそれに対応する信号を選択対象の画素回路14に書き込むものである。具体的には、信号線駆動回路23は、例えば、図3に示したように、1フレーム期間TFごとに、黒画像用の映像信号20Aに対応する信号電圧Vofsと、右目用画像用の映像信号20Aに対応する信号電圧VsigRと、黒画像用の映像信号20Aに対応する信号電圧Vofsと、左目用画像用の映像信号20Aに対応する信号電圧VsigLとを、この順に各信号線DTLに印加して、選択対象の画素回路14への書き込みを行うものである。なお、図3は、表示装置1を駆動させたときの1フレーム期間内の各種波形の一例を表したものである。

【0021】

ところで、上記の「書き込み」とは、駆動トランジスタTr1のゲート−ソース間に所定の電圧を印加することを指している。また、信号線駆動回路23が1フレーム期間TF中に各信号線DTLに印加する電圧の順番は、上記の順番に限られるものではなく、左目用画像用の映像信号と、右目用画像用の映像信号との間に、黒画像用の映像信号が挿入されていれば、どのような順番であってもよい。

【0022】

信号線駆動回路23は、例えば、有機EL素子11の発光時に駆動トランジスタTr1のゲートに印加する信号電圧VsigR,VsigLと、有機EL素子11の消光時に駆動トランジスタTr1のゲートに印加する電圧Vofsとを出力することが可能となっている。ここで、電圧Vofsは、有機EL素子11の閾値電圧Velよりも低い電圧値(一定値)となっており、かつ信号電圧VsigR,VsigLの最小電圧よりも高い電圧値となっている。

【0023】

走査線駆動回路24は、制御信号22Aの入力に応じて(同期して)、複数の走査線WSLに選択パルスを順次印加して、複数の有機EL素子11および複数の画素回路14を順次選択するものである。走査線駆動回路24は、例えば、書き込みトランジスタTr2をオンさせるときに印加する電圧Vonと、書き込みトランジスタTr2をオフさせるときに印加する電圧Voffとを出力することが可能となっている。ここで、電圧Vonは、書き込みトランジスタTr2のオン電圧以上の値(一定値)となっている。電圧Voffは、書き込みトランジスタTr2のオン電圧よりも低い値(一定値)となっている。

【0024】

電源線駆動回路25は、制御信号22Aの入力に応じて(同期して)、複数の電源線PSLに制御パルスを順次印加して、有機EL素子11の発光および消光を制御するものである。電源線駆動回路25は、例えば、駆動トランジスタTr1に電流を流すときに印加する電圧VccHと、駆動トランジスタTr1に電流を流さないときに印加する電圧VccLとを出力することが可能となっている。ここで、電圧VccLは、有機EL素子11の閾値電圧Velと、有機EL素子11のカソードの電圧Vcaとを足し合わせた電圧(Vel+Vca)よりも低い電圧値(一定値)である。VccHは、電圧(Vel+Vca)以上の電圧値(一定値)である。

【0025】

(シャッター眼鏡)

シャッター眼鏡は、例えば、図示しないが、左目用シャッターと、右目用シャッターと、左目用シャッターの開閉を制御する制御信号を印加する制御線SGLと、右目用シャッターの開閉を制御する制御信号を印加する制御線SGRとを有している。制御線SGLおよび制御線SGRは、駆動回路20に直接接続されていてもよいし、駆動回路20と通信可能な無線装置に接続されていてもよい。

【0026】

(1.2 表示装置の動作)

図4は、表示装置1を駆動させたときの1H期間内の各種波形の一例を表したものである。図4には、例えば、黒画像用の映像信号20Aに対応する信号電圧Vofsと、右目用画像用の映像信号20Aに対応する信号電圧VsigRとが印加される期間TF1の信号波形、または黒画像用の映像信号20Aに対応する信号電圧Vofsと、左目用画像用の映像信号20Aに対応する信号電圧VsigLとが印加される期間TF1の信号波形が表されている。図4(A)〜(C)には、信号線DTLにVofs、VsigL、VsigRが所定のタイミングで印加され、走査線WSLにVon、Voffが所定のタイミングで印加され、電源線PSLにVccL、VccHが所定のタイミングで印加されている様子が示されている。図4(D),(E)には、信号線DTL、走査線WSLおよび電源線PSLへの電圧印加に応じて、駆動トランジスタTr1のゲート電圧Vgおよびソース電圧Vsが時々刻々変化している様子が示されている。

【0027】

[Vth補正準備期間]

まず、Vth補正の準備を行う。具体的には、電源線駆動回路25が電源線PSLの電圧をVccHからVccLに下げる(T1)。すると、ソース電圧VsがVccLとなり、有機EL素子11が消光すると共に、ゲート電圧Vgは発光時のVgsをVgs0とすると(VccL+Vgs0)となる。次に、信号線DTLの電圧がVofsとなっており、かつ電源線PSLの電圧がVccLとなっている間に、走査線駆動回路24が走査線WSLの電圧をVoffからVonに上げる。

【0028】

[Vth補正期間]

次に、Vthの補正を行う。具体的には、信号線DTLの電圧がVofsとなっている間に、電源線駆動回路25が電源線PSLの電圧をVccLからVccHに上げる(T2)。すると、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れ、ソース電圧Vsが上昇する。このとき、ソース電圧Vsが(Vofs−Vth)よりも低い場合(Vth補正がまだ完了していない場合)には、駆動トランジスタTr1がカットオフするまで(電位差VgsがVthになるまで)、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れる。その結果、保持容量CsがVthに充電され、電位差VgsがVthとなる。その後、信号線駆動回路23が信号線DTLの電圧をVofsからVsigLまたはVsigRに切り替える前に、走査線駆動回路24が走査線WSLの電圧をVonからVoffに下げる(T3)。すると、駆動トランジスタTr1のゲートがフローティングとなるので、電位差Vgsを信号線DTLの電圧の大きさに拘わらずVthのままで維持することができる。このように、電位差VgsをVthに設定することにより、駆動トランジスタTr1の閾値電圧Vthが画素回路14ごとにばらついた場合であっても、有機EL素子11の発光輝度がばらつくのをなくすことができる。なお、Vth補正期間において、信号線駆動回路23は信号線DTLの電圧をVofsに維持する。

【0029】

[待機期間]

次に、後述の書き込み・μ補正期間(移動度補正期間)がやってくるまでのしばらくの間、そのままの状態で待機する。このとき、信号線駆動回路23は信号線DTLの電圧をVofsに維持する。その後、書き込み・μ補正期間が開始する少し前に、信号線駆動回路23が信号線DTLの電圧をVofsからVsigLまたはVsigRに切り替える。例えば、1フレーム期間TFの前半では、信号線駆動回路23が信号線DTLの電圧をVofsからVsigRに切り替え、1フレーム期間TFの後半では、信号線駆動回路23が信号線DTLの電圧をVofsからVsigLに切り替える。

【0030】

[書き込み・μ補正期間]

待機期間が終了した後、書き込み・μ補正期間を行う。具体的には、信号線DTLの電圧がVsigLまたはVsigRとなっている間に、走査線駆動回路24が走査線WSLの電圧をVoffからVonに上げ(T4)、駆動トランジスタTr1のゲートを信号線DTLに接続する。すると、駆動トランジスタTr1のゲート電圧がVsigLまたはVsigRとなる。このとき、有機EL素子11のアノード電圧はこの段階ではまだ有機EL素子11の閾値電圧Velよりも小さく、有機EL素子11はカットオフしている。そのため、電流Idは有機EL素子11の素子容量(図示せず)に流れ、素子容量が充電されるので、ソース電圧VsがΔVだけ上昇し、やがて電位差VgsがVsigL+Vth−ΔV(またはVsigR+Vth−ΔV)となる。このようにして、書き込みと同時にμ補正が行われる。ここで、駆動トランジスタTr1の移動度μが大きい程、ΔVも大きくなるので、電位差Vgsを発光前にΔVだけ小さくすることにより、画素回路14ごとの移動度μのばらつきを取り除くことができる。

【0031】

[発光期間]

最後に、走査線駆動回路24が走査線WSLの電圧をVonからVoffに下げる(T5)。すると、駆動トランジスタTr1のゲートがフローティングとなり、駆動トランジスタTr1のドレイン−ソース間に電流Idが流れ、ソース電圧Vsが上昇する。その結果、有機EL素子11が所望の輝度で発光する。このとき、信号線駆動回路23は信号線DTLの電圧をVsigLまたはVsigRに維持する。

【0032】

[繰り返し]

次に、所定の期間が経過したのち、発光期間を終了する。具体的には、電源線駆動回路25が電源線PSLの電圧をVccHからVccLに下げる(T1)。すると、ソース電圧VsがVccLとなり、有機EL素子11が消光する。その後、上述した各期間に対応した駆動を実行する。このように、本実施の形態では、例えば、図4に示したように、Vth補正準備期間、Vth補正期間、待機期間、書き込み・μ補正期間、発光期間がフレーム期間TFごとに繰り返される。

【0033】

ところで、本実施の形態では、走査線駆動回路24および電源線駆動回路25は共に、電源線PSLおよび走査線WSLを行方向にスキャンする。そのため、信号線駆動回路23が、1フレーム期間TFごとに、信号電圧Vofs、VsigR、Vofs、VsigLを、この順に各信号線DTLに印加しているときに、たいていは、表示装置1に表示される画像には、スキャンラインの上方または下方に対応する部分に黒画像の一部が含まれる。なお、表示装置1の画面(画像)全体が右目用画像、左目用画像または黒画像である期間が存在していることが好ましいが、場合によっては存在していなくてもよい。

【0034】

以下では、右目用画像の少なくとも一部が表示装置1に表示されている期間を、右目用画像を表示する期間(右目用画像表示期間TRD)と称するものとする。同様に、左目用画像の少なくとも一部が表示装置1に表示されている期間を、左目用画像を表示する期間(左目用画像表示期間TLD)と称するものとする。また、表示装置1の全体に黒画像が表示されている期間を、黒画像を表示する期間(黒画像表示期間TBL1,TBL2)と称するものとする。なお、黒画像表示期間TBL1は、1フレーム期間TFにおいて右目用画像を表示する前の黒画像表示期間に対応している。黒画像表示期間TBL2は、1フレーム期間TFにおいて左目用画像を表示する前の黒画像表示期間に対応している。

【0035】

本実施の形態では、駆動回路20は、例えば、図3に示したように、黒画像表示期間TBL1、右目用画像表示期間TRD、黒画像表示期間TBL2、左目用画像表示期間TLDをフレーム期間TFごとに繰り返す。このとき、視聴者は、図示しないシャッター眼鏡をかけた上で、左目用画像を左目のみで視認し、右目用画像を右目のみで視認する。例えば、図3に示したように、左目用画像表示期間TLDに、左目用シャッターを開く(左目用眼鏡を透過状態にする)信号電圧VH1が印加され、それ以外の期間に、左目用シャッターを閉じる(左目用眼鏡を非透過状態にする)信号電圧VL1が印加される。また、例えば、図3に示したように、右目用画像表示期間TRDに、右目用シャッターを開く(右目用眼鏡を透過状態にする)信号電圧VH2が印加され、それ以外の期間に、右目用シャッターを閉じる(右目用眼鏡を非透過状態にする)信号電圧VL2が印加される。これにより、左目用画像が左目のみで視認され、右目用画像が右目のみで視認されるので、左目用画像と右目用画像とが観察者の網膜で結像される。その結果、視聴者は立体映像を観察することができる。

【0036】

(1.3 作用・効果)

ところで、従来の有機EL表示装置では、例えば、図5、図6に示したように、Vth補正準備期間、Vth補正期間、Vth補正休止期間、書き込み・μ補正期間、発光期間が1水平ラインごとに順次行われる。このとき、例えば、図5に示したように、1フレーム期間内においてVth補正を行っている期間αと、1フレーム期間内において書き込み・μ補正を行っている期間βとが同時に存在している。ただし、厳密には、1フレーム期間内において、Vth補正と、書き込み・μ補正とを同時に行うことはできないので、従来の有機EL表示装置では、例えば、図6に示したように、Vth補正期間を複数に分けると共に、Vth補正休止期間を複数設け、Vth補正休止期間に他の水平ラインにおける書き込み・μ補正を行うようにしている。ところで、このようにVth補正休止期間を設けた場合に、Vth補正期間として十分な時間を確保するためには、走査線WSLのシフト動作をやや高速化することが必要となる。例えば、1920×1080画素数のパネルでフィールドシーケンシャルの駆動を考えると、走査線WSLのシフト周期は、1/(1080×240Hz)=3.86μsecとなり、この期間内にVth補正、書き込み・μ補正を行う必要がある。

【0037】

一方、本実施の形態では、例えば、図3に示したように、全ての画素12においてVth補正が行われた後に、全ての画素12において書き込み・μ補正が行われている。つまり、Vth補正を一旦休止し、その間に、書き込み・μ補正を行うようなことはしておらず、1フレーム期間内においてVth補正を行っている期間と、1フレーム期間内において書き込み・μ補正を行っている期間とが同時に存在していない。従って、Vth補正にかける時間を十分長くとることができ、走査線WSLのシフト動作を従来ほどに高速化する必要がない。例えば、例えば、1画素12においてVth補正時間が300μsec必要とすると、1/120Hz=8.3msec中の4.3msecがVth補正期間となり、残りの4msecが書き込み・μ補正期間となる。よって、本実施の形態では、走査線WSLのシフト周期は、4msec/1080=3.7μsecとなり、この期間内に書き込み・μ補正だけを行えばよいので、本実施の形態の方が、従来の有機EL表示装置よりも、Vth補正や、書き込み・μ補正を行う際のタイミングマージンが大きい。

【0038】

また、本実施の形態では、全ての画素12においてVth補正が行われた後に、全ての画素12において書き込み・μ補正が行われていることから、従来の有機EL表示装置のような、信号線DTLに1H周期でパルスを印加することを要しない。また、本実施の形態では、走査線WSLについても、従来の有機EL表示装置のような、高速駆動を要しない。従って、画素回路14への充放電の回数、具体的には、信号線DTLおよび走査線WSLの充放電の回数が減少するので、消費電力を低減することができる。

【0039】

<変形例>

上記実施の形態では、Vth補正および書き込み・μ補正は共に、走査線WSLのスキャンにより1水平ラインごとに順次行われていたが、例えば、図7に示したように、Vth補正が全ての画素12において同時に(一括して)行われてもよい。例えば、走査線駆動回路24が、Vth補正に際して、全ての走査線WSLに選択パルスを同時に印加して、全ての有機EL素子11および全ての画素回路14を選択するようにしてもよい。このようにした場合には、Vth補正が走査線WSLのスキャンにより1水平ラインごとに順次行われていた場合と比べて、全ての画素12に対してVth補正を行うのに要する時間を短くすることができる。従って、本変形例の方が、従来の有機EL表示装置や上記の実施の形態の表示装置1よりも、Vth補正や、書き込み・μ補正を行う際のタイミングマージンが大きい。

【0040】

また、本変形例では、Vth補正を行う際にスキャン駆動を行わない。そのため、上記実施の形態の場合と比べて、走査線WSLの充放電が減少するので、消費電力をより低減することができる。

【0041】

また、上記実施の形態では、各画素12において、Vth補正が終了した後、書き込み・μ補正を行うまでの間、電源線PSLにはVccHが印加されていたが、例えば、図8に示したように、その間の少なくとも一部の期間の間、電源線PSLにVccLが印加されていてもよい。このようにした場合には、電源線PSLにVccLが印加されている間、画素回路14への電流供給が停止する。その結果、Vth補正が終了した後、書き込み・μ補正を行うまでの間に、駆動トランジスタTr1のリーク電流に起因して駆動トランジスタTr1のゲート−ソース間の電圧Vgsが変化するのを抑制することができる。

【0042】

<2.モジュールおよび適用例>

以下、上述した実施の形態で説明した表示装置の適用例について説明する。上記実施の形態の表示装置は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、映像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0043】

(モジュール)

上記実施の形態の表示装置1は、例えば、図9に示したようなモジュールとして、後述する適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板31の一辺に、封止用基板32から露出した領域210を設け、この露出した領域210に、駆動回路20の配線を延長して外部接続端子(図示せず)を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

【0044】

(適用例1)

図10は、上記実施の形態の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記各実施の形態に係る表示装置1により構成されている。

【0045】

(適用例2)

図11は、上記実施の形態の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上記実施の形態に係る表示装置1により構成されている。

【0046】

(適用例3)

図12は、上記実施の形態の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および映像を表示する表示部530を有しており、その表示部530は、上記各実施の形態に係る表示装置1により構成されている。

【0047】

(適用例4)

図13は、上記実施の形態の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上記各実施の形態に係る表示装置1により構成されている。

【0048】

(適用例5)

図14は、上記実施の形態の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記各実施の形態に係る表示装置1により構成されている。

【0049】

以上、実施の形態および適用例を挙げて本発明を説明したが、本発明は上記実施の形態等に限定されるものではなく、種々変形が可能である。

【0050】

例えば、上記実施の形態等では、表示装置1がアクティブマトリクス型である場合について説明したが、アクティブマトリクス駆動のための画素回路14の構成は上記実施の形態等で説明したものに限られず、必要に応じて容量素子やトランジスタを画素回路14に追加してもよい。その場合、画素回路14の変更に応じて、上述した信号線駆動回路23、走査線駆動回路24、電源線駆動回路25のほかに、必要な駆動回路を追加してもよい。

【0051】

また、上記実施の形態等では、信号線駆動回路23、走査線駆動回路24、電源線駆動回路25の駆動をタイミング制御回路22が制御していたが、他の回路がこれらの駆動を制御するようにしてもよい。また、信号線駆動回路23、走査線駆動回路24、電源線駆動回路25の制御は、ハードウェア(回路)で行われていてもよいし、ソフトウェア(プログラム)で行われていてもよい。

【0052】

また、上記実施の形態等では、画素回路14が、2Tr1Cの回路構成となっていたが、トランジスタが有機EL素子11に直列に接続された回路構成を含んでいるものであれば、2Tr1Cの回路構成以外の回路構成となっていてもよい。

【0053】

また、上記実施の形態等では、駆動トランジスタTr1,書き込みトランジスタTr2は、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている場合が例示されていたが、pチャネルトランジスタ(例えばpチャネルMOS型のTFT)により形成されていてもよい。ただし、その場合には、トランジスタTr2のソースおよびドレインのうち電源線PSLと未接続の方と保持容量Csの他端とを有機EL素子11のカソードに接続し、有機EL素子11のアノードをGNDなどに接続することが好ましい。

【符号の説明】

【0054】

1…表示装置、10…表示パネル、11,11R,11G,11B…有機EL素子、12…画素、13…画素回路アレイ部、14…画素回路、20…駆動回路、20A…映像信号、20B…同期信号、21…映像信号処理回路、22…タイミング生成回路、22A…制御信号、23…信号線駆動回路、24…走査線駆動回路、25…電源線駆動回路、Cs…保持容量、DTL…信号線、GND…グラウンド線、Id…電流、PSL…電源線、Tr1…駆動トランジスタ、Tr2…書き込みトランジスタ、Vg…ゲート電圧、Vgs…ゲート−ソース間電圧、Vs…ソース電圧、Vth…閾値電圧、WSL…走査線、α…Vth補正期間、β…書き込み・μ補正期間。

【特許請求の範囲】

【請求項1】

行列状に配置された複数の発光素子および複数の画素回路と、

全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行う駆動回路と

を備えた表示装置。

【請求項2】

前記駆動回路は、全ての画素回路の閾値補正を同時に行う

請求項1に記載の表示装置。

【請求項3】

前記駆動回路は、全ての画素回路の閾値補正を行ったのち、前記書き込みを行うまでの間の少なくとも一部の期間の間、前記画素回路への電流供給を停止する

請求項1に記載の表示装置。

【請求項4】

行列状に配置された複数の発光素子および複数の画素回路と、前記複数の画素回路を駆動する駆動回路とを備えた表示装置を用意するステップと、

前記駆動回路を用いて、全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行うステップと

を含む表示装置の駆動方法。

【請求項5】

表示装置を備え、

前記表示装置は、

行列状に配置された複数の発光素子および複数の画素回路と、

全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行う駆動回路と

を有する

電子機器。

【請求項1】

行列状に配置された複数の発光素子および複数の画素回路と、

全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行う駆動回路と

を備えた表示装置。

【請求項2】

前記駆動回路は、全ての画素回路の閾値補正を同時に行う

請求項1に記載の表示装置。

【請求項3】

前記駆動回路は、全ての画素回路の閾値補正を行ったのち、前記書き込みを行うまでの間の少なくとも一部の期間の間、前記画素回路への電流供給を停止する

請求項1に記載の表示装置。

【請求項4】

行列状に配置された複数の発光素子および複数の画素回路と、前記複数の画素回路を駆動する駆動回路とを備えた表示装置を用意するステップと、

前記駆動回路を用いて、全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行うステップと

を含む表示装置の駆動方法。

【請求項5】

表示装置を備え、

前記表示装置は、

行列状に配置された複数の発光素子および複数の画素回路と、

全ての画素回路の閾値補正を行ったのち、映像信号に対応する信号電圧の、各画素回路への書き込みを行う駆動回路と

を有する

電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2011−22341(P2011−22341A)

【公開日】平成23年2月3日(2011.2.3)

【国際特許分類】

【出願番号】特願2009−167097(P2009−167097)

【出願日】平成21年7月15日(2009.7.15)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成23年2月3日(2011.2.3)

【国際特許分類】

【出願日】平成21年7月15日(2009.7.15)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]