表示装置およびその駆動方法

【課題】可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、画素回路の簡略化による高精細化と高信頼性化を両立させる。

【解決手段】画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、前記第2制御電極には第2制御電圧が入力され、前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有する。

【解決手段】画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、前記第2制御電極には第2制御電圧が入力され、前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置およびその駆動方法に係わり、特に、可動シャッタの位置を電気的に制御して画像表示を行う画像表示装置の画素回路に適用して有効な技術に関する。

【背景技術】

【0002】

機械的シャッタの位置を電気的に制御して画像表示を行う画像表示装置(以下、可動シャッタ方式の画像表示装置)の画素回路としての使用方法がある。

図14は、従来の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

以下、図14を用いて、従来の可動シャッタ方式の画像表示装置に関して説明する。

各画素213には、信号線206が設けられており、信号線206と信号蓄積容量204とは走査スイッチ205で接続されている。

信号蓄積容量204は更にシャッタ負電圧書込み用nMOSトランジスタ203のゲートに接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のドレインは、カスコードnMOSトランジスタ216、カスコードpMOSトランジスタ215を介して、シャッタ正電圧書込み用pMOSトランジスタ202のドレインに接続されている。

各画素は、シャッタ電圧線211に接続された双極性シャッタ(Dual actuator shutter assembly)201を有しているが、二つある双極性シャッタ201の制御電極の内の一方は、カスコードnMOSトランジスタ216を介してシャッタ負電圧書込み用nMOSトランジスタ203のドレインに接続されており、制御電極の他方は制御電極電圧線209に接続されている。

なお、信号蓄積容量204の他端はシャッタ電圧線211に接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のソースはシャッタ負電圧書込み用nMOSソース電圧線212に接続されている。

また、シャッタ正電圧書込み用pMOSトランジスタ202のゲートとドレインは、それぞれシャッタ正電圧書込み用pMOSゲート電圧線207と正電圧線208に接続されている。さらに、カスコードnMOSトランジスタ216及びカスコードpMOSトランジスタ215のゲートはカスコードゲート電圧線217に接続され、走査スイッチ205のゲートは走査線210に接続されている。

なお、双極性シャッタ201は、遮光面上に設けられた開口に対向して設けられており、当該画像表示装置にはこのような画素213がマトリクス状に配列されている。

【0003】

次に、従来の可動シャッタ方式の画像表示装置の動作について説明する。

信号線206に書込まれた画像信号電圧は、走査線210を順次走査することによって走査スイッチ205を介して信号蓄積容量204に記憶される。

次に、全画素の信号蓄積容量204に対する画像信号電圧の書込み走査が終了した後に、各画素において、書込まれた画像信号電圧を元に双極性シャッタ201の制御電極の内の一方に対して画像信号の増幅書込みを行う。即ち、まず全画素において、シャッタ正電圧書込み用pMOSゲート電圧線207を所定の期間だけ低電圧にすることによって、シャッタ正電圧書込み用pMOSトランジスタ202をこの期間のみオン状態にして、双極性シャッタ201の制御電極の内の一方の電極に、正電圧線208に印加されていた所定の正電圧をプリチャージする。

次に、シャッタ負電圧書込み用nMOSソース電圧線212を、所定の期間だけ所定の低電圧にする。このとき、信号蓄積容量204に画像信号電圧として高電圧が書込まれていた画素のみが、この期間、シャッタ負電圧書込み用nMOSトランジスタ203がオン状態となることにより、双極性シャッタ201の制御電極の内の一方の電圧はシャッタ負電圧書込み用nMOSソース電圧線212に印加されている所定の低電圧に書き換えられる。

【0004】

また、信号蓄積容量204に画像信号電圧として低電圧が書込まれていた画素は、この期間もシャッタ負電圧書込み用nMOSトランジスタ203はオフ状態を維持するため、双極性シャッタ201の制御電極の内の一方の電圧は、既にプリチャージされた所定の正電圧を維持する。

このようにして双極性シャッタ201の制御電極の内の一方の電極に画像信号の増幅書込みを行うが、これと並行して制御電極電圧線209への印加電圧を制御することによって、双極性シャッタ201を静電的に開閉操作することができる。このように双極性シャッタ201で遮光面上に設けられた開口を開閉することで光の透過量を制御して、当該画像表示装置は書込まれた画像信号電圧に対応した画像を画素マトリクス上に表示することができる。

なお、前述の動作において、カスコードnMOSトランジスタ216及びカスコードpMOSトランジスタ215は、シャッタ正電圧書込み用pMOSトランジスタ202及びシャッタ負電圧書込み用nMOSトランジスタ203に信頼性寿命を損なうような高いドレイン電圧が印加されることを防止するために設けられたものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】US 2008/0174532号

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の可動シャッタ方式の画像表示装置の画素回路では、シャッタ正電圧書込み用pMOSトランジスタ202及びシャッタ負電圧書込み用nMOSトランジスタ203のドレインに対する高電圧印加に起因する信頼性劣化を回避するために、カスコードnMOSトランジスタ216及びカスコードpMOSトランジスタ215を設ける必要があった。

画像表示装置の高精細化に対応するためには画素回路の簡略化が必要になるが、従来の可動シャッタ方式の画像表示装置の画素回路では高信頼化のためにはカスコードトランジスタが不可欠であり、高精細化と高信頼性化の両立が困難であった。

即ち、低消費電力でありながら高コントラストで色再現性が良いといった、従来の可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、更に画素回路の簡略化による高精細化と高信頼性化の両立を図ることが要望されていた。

本発明は、前述の要望に答えるためになされたものであり、本発明の目的は、可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、画素回路の簡略化による高精細化と高信頼性化を両立させことが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【課題を解決するための手段】

【0007】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

(1)機械的シャッタをそれぞれ有する複数の画素と、前記各画素に画像信号を入力する信号線と、前記各画素に走査電圧を入力する走査線とを備え、前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有し、前記第2制御電極には第2制御電圧が入力され、前記容量制御信号、前記第1制御信号、および、前記第2制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御する。

【0008】

(2)機械的シャッタをそれぞれ有する複数の画素と、前記各画素に第1画像信号を入力する第1信号線と、前記各画素に第2画像信号を入力する第2信号線と、前記各画素に走査電圧を入力する走査線とを備え、前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、前記第1制御電極に前記第1画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、前記第2制御電極に前記第2画像信号に応じた第2制御電圧を入力するための第2制御電圧印加回路とを有し、前記第1制御電圧印加回路は、電流端子の一端が前記第1信号線に接続され、ゲートが前記走査線に接続される第1入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記第1入力トランジスタの電流端子の他端に接続され、前記第1入力トランジスタで取り込んだ電圧を保持する第1保持容量と、ゲートが前記第1保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第1トランジスタとを有し、前記第2制御電極電圧印加回路は、電流端子の一端が前記第2信号線に接続され、ゲートが前記走査線に接続される第2入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記第2入力トランジスタの電流端子の他端に接続され、前記第2入力トランジスタで取り込んだ電圧を保持する第2保持容量と、ゲートが前記第2保持容量の一端に接続され、電流端子の他端が第2制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第2トランジスタとを有し、前記容量制御信号、および、前記制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御する。

【0009】

(3)(1)または(2)において、面状の光源と、透明基板と、前記透明基板上に設けられる遮光膜と、前記遮光膜は、各画素に対応する光学的開口領域を有し、前記面状の光源から射出された光に対して、前記光学的開口領域以外の領域を遮光し、前記機械的シャッタは、前記透明基板上で、光学的開口領域に対応して設けられている。

(4)(1)ないし(3)の何れかにおいて、前記各トランジスタは、半導体層が多結晶シリコン薄膜で構成されるトランジスタ、あるいは、半導体層がアモルファスシリコン薄膜で構成されるトランジスタ、または、半導体層が酸化物薄膜を用いて構成されるトランジスタである。

(5)(1)ないし(3)の何れかにおいて、前記各トランジスタは、n型のトランジスタであり、前記第2電圧レベルは、第1電圧レベルよりも高電位の電圧レベルである。

【発明の効果】

【0010】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明によれば、可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、画素回路の簡略化による高精細化と高信頼性化を両立させことが可能となる。

【図面の簡単な説明】

【0011】

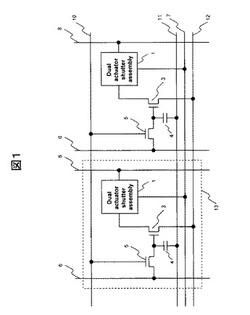

【図1】本発明の実施例1の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図2】本発明の実施例1の可動シャッタ方式の画像表示装置の概略構成を示すブロック図である。

【図3】本発明の実施例1の可動シャッタ方式の画像表示装置の画素部の断面構造を示す断面図である。

【図4】本発明の実施例1の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ:シャッタ=高電圧)である。

【図5】本発明の実施例1の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ反転:シャッタ=低電圧)である。

【図6】本発明の実施例1の可動シャッタ方式の画像表示装置において、画像信号電圧がLowレベルの電圧(例えば、0(V))の時のTFT電極への制御信号電圧の書込みを説明するための図である。

【図7】本発明の実施例1の可動シャッタ方式の画像表示装置において、画像信号電圧がHighレベルの電圧(例えば、5(V))の時のTFT電極への制御信号電圧の書込みを説明するための図である。

【図8】本発明の実施例2の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図9】本発明の実施例3の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図10】本発明の実施例4の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図11】本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ:シャッタ=高電圧)である。

【図12】本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ反転:シャッタ=低電圧)である。

【図13】本発明の実施例5の可動シャッタ方式の画像表示装置を使用するインターネット画像表示装置の概略構成を示すブロック図である。

【図14】従来の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【発明を実施するための形態】

【0012】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

[実施例1]

図1は、本発明の実施例1の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

図2は、本発明の実施例1の可動シャッタ方式の画像表示装置の概略構成を示すブロック図である。

図3は、本発明の実施例1の可動シャッタ方式の画像表示装置の画素部の断面構造を示す断面図である。

以下、図1〜図3を用いて、本実施例の可動シャッタ方式の画像表示装置の画素回路について説明する。

各画素13には信号線6が設けられており、信号線6と信号蓄積容量(本願発明の保持容量)4とは走査スイッチ(本願発明の入力トランジスタ)5で接続されている。信号蓄積容量4は更にTFT電極書込みトランジスタ(本願発明の第1トランジスタ)3のゲートに接続されており、TFT電極書込みトランジスタ3のドレインは双極性シャッタ1の二つある一方の制御電極であるTFT電極に接続されている。双極性シャッタ1の他方の制御電極であるグローバル電極は、グローバル制御線8に接続され、また双極性シャッタ1のシャッタ電極は、シャッタ電極制御線7に接続されている。

なお、信号蓄積容量4の他端は容量制御線11に接続されており、TFT電極書込みトランジスタ3のソースはTFT電極ソース制御線12に、走査スイッチ5のゲートは走査線10に接続されている。

また、前述の双極性シャッタ1は、後に図3を用いて説明するように、遮光面上に設けられた開口に対向して設けられている。

【0013】

次に、本実施例の可動シャッタ方式の画像表示装置の画素周辺回路について説明する。

図2に示すように、マトリクス状に配列された画素13が表示領域を構成しており、画素13には列方向に信号線6と、グローバル制御線8が、行方向に走査線10、容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12が設けられている。

表示領域の周辺で、信号線6の一端は画像信号電圧書込み回路14に接続されており、グローバル制御線8、容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12の一端はそれぞれ制御電極駆動回路16に接続されている。また走査線10の一端は走査回路15に接続されている。

なお、図2は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではないことは明らかである。

【0014】

次に、本実施例の可動シャッタ方式の画像表示装置の画素部断面構造について説明する。

図3に示すように、ガラス基板39上には、多結晶シリコン薄膜31、高濃度n型不純物をドープした多結晶シリコン薄膜(30,32)、ゲート絶縁膜33、高融点金属からなるゲート電極35、ソース電極37、ドレイン電極36とから構成される多結晶シリコン薄膜トランジスタが設けられており、これはTFT電極書込みトランジスタ3に対応するものである。

更にガラス基板39上には、絶縁保護膜34を挟んでソース電極37、ドレイン電極36と同じAl配線層でシャッタ電極制御線7、グローバル制御線8の一部が形成されており、これらはシリコンナイトライドと有機材料の多層膜からなる保護膜38によって覆われている。

保護膜38上には、シャッタ電極26と、TFT電極27、グローバル電極25の2つの制御電極を有する双極性シャッタ1が設けられており、シャッタ電極26はシャッタ電極制御線7に、ドレイン電極36はTFT電極27に、グローバル制御線8はグローバル電極25に、それぞれコンタクトホールを介して接続されている。またこれらシャッタ電極26と、二つの制御電極であるTFT電極27、グローバル電極25は、互いに接触した際の短絡防止のために、表面には絶縁膜が形成されている。

【0015】

ここで、シャッタ電極26は、シャッタ電極26に入力される電圧と、TFT電極27、グローバル電極25に入力される電圧との相対関係による電界でその位置が制御されるため、図3には破線を用いてその可動範囲も開示している。

また、図3には記載されていないが、画素13内に設けられたその他のトランジスタも、同様に多結晶シリコン薄膜トランジスタで構成されている。これらの多結晶シリコン薄膜トランジスタは、公知のエキシマレーザアニーリングプロセス等を用いて形成することができる。

シャッタ電極26に対してガラス基板39と反対側には、R(赤)G(緑)B(青)の3色の独立LED光源からなる光源42を有する導光板22が設けられている。

導光板22の両面には反射膜(21,23)と、更に反射膜23の上には黒色膜24が設けられている。反射膜(21,23)はAgやAlなどの金属膜で、黒色膜24は金属酸化膜や、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させることで形成することができる。

ここで、反射膜23及び黒色膜24には図3に示すように、シャッタ電極26に対応する位置に開口が設けられており、光源42から射出されて導光板22を伝播した光41の一部が、この開口から射出されるように構成されている。また黒色膜24は、外光の反射を防ぐために設けられたものである。

【0016】

次に、図4〜図7を用いて、本実施例の可動シャッタ方式の画像表示装置の動作について説明する。

まず、図1に示す本実施例の画素回路の動作について説明する。

図4、図5は、本発明の実施例の可動シャッタ方式の画像表示装置の画素回路の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。図4ではシャッタ電極制御線7は常に高電圧Vh(例えば、20(V))、図5では常に0(V)であるが、これは双極性シャッタ1の駆動電圧の反転(ポラリティ反転)動作に対応したものである。

本実施例の画像表示装置は、フルカラーの8bit階調をシャッタの開閉で表現するために、1フレームを8×RGB=24以上のサブフレームに分割し、光源42の発光にサブフレーム毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM(Pulse Width Modulation)駆動を行うが、このとき所定のサブフレーム毎にポラリティ反転駆動を行い、双極性シャッタ1の 電極の劣化を回避する。

また、特に最下段に記載した双極性シャッタ1のTFT電極27の電圧値に関しては、画像信号によって約0(V)と約Vh(正確にはVh、またはVh−Vth、VthはTFT電極書込みトランジスタ3のしきい値電圧)の2値を取るため、図面を判り易くするために前者を実線、後者を破線で示している。

【0017】

まずポラリティ(シャッタ=高電圧)における動作を説明する。

図4はポラリティ(シャッタ=高電圧)における動作タイミングチャートである。

(1)時刻(t1)まで

この期間には、画素に対する画像信号電圧の書込みが行われている。グローバル制御線8、容量制御線11は0(V)であり、TFT電極ソース制御線12には中間電圧Vm(例えば5(V))が印加されている。走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は、例えば、5(V)または0(V)であるが、この期間はTFT電極ソース制御線12には、5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

(2)時刻(t1)から時刻(t2)

この期間にはグローバル制御線8の電圧が高電圧Vh(例えば、20(V))に変化する。シャッタ電極26は常時高電圧Vh(例えば20(V))であるから、これによって時刻(t1)まで、シャッタ電極26がグローバル電極25に引き寄せられていた場合は、シャッタ電極26はグローバル電極25から離れる方向に移動する。なお、時刻(t1)までシャッタ電極26がTFT電極27に引き寄せられていた場合は、特に変化は生じない。

【0018】

(3)時刻(t2)から時刻(t3)まで

容量制御線11を高電圧Vh(例えば、20(V))に向けてスイープ開始する。

(4)時刻(t3)から時刻(t4)まで

容量制御線11の電圧が中間電圧Vm(例えば、5(V))に達すると同時に、TFT電極ソース制御線12も高電圧Vh(例えば、20(V))に向けてスイープ開始する。 これにより、容量制御線11とTFT電極ソース制御線12の電圧は、同時に、高電圧Vh(例えば、20(V))に達し、この後停止する。

この操作により、TFT電極27の電圧も上昇し、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は高電圧Vh(例えば、20(V))に達し、0(V)が書込まれていた場合は、Vh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)に収束する。

これによって、時刻(t2)までシャッタ電極26がTFT電極27に引き寄せられていた場合は、シャッタ電極26はTFT電極27から離れる方向に移動する。

(5)時刻(t4)から時刻(t5)まで

容量制御線11及びTFT電極ソース制御線12を同時に0(V)にスイープし、その後停止させる。この操作により、TFT電極27の電圧は、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は0(V)に低下し、0(V)が書込まれていた場合はVh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)で保持される。

【0019】

(6)時刻(t5)から時刻(t6)まで

容量制御線11及びTFT電極ソース制御線12は0(V)で停止するが、この期間に当該画素の信号蓄積容量4に5(V)が書込まれていた場合は、シャッタ電極26はTFT電極27に引き寄せられる。しかし信号蓄積容量4に0(V)が書込まれていた場合には、シャッタ電極26がTFT電極27に引き寄せられることはない。シャッタ電極26を確実にTFT電極27に引き寄せるため、この期間は例えば100μ秒以上、十分に確保しておく必要がある。

(7)時刻(t6)から時刻(t7)まで

TFT電極ソース制御線12に中間電圧Vm(例えば、5(V))が印加されると同時に、画素に対する画像信号電圧の書込みが開始される。走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は、例えば、5(V)または0(V)であるが、この期間には再びTFT電極ソース制御線12には5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

【0020】

(8)時刻(t7)から時刻(t8)まで

この期間にはグローバル制御線8の電圧が高電圧Vh(例えば、20(V))から0(V)に回復する。シャッタ電極26は常時高電圧Vh(例えば、20(V))であるから、時刻(t5)から時刻(t6)までの期間にシャッタ電極26がTFT電極27に引き寄せられていない場合には、シャッタ電極26はグローバル電極25に引き寄せられる。

一方で、時刻(t5)から時刻(t6)までの期間にシャッタ電極26がTFT電極27に既に引き寄せられている場合には、シャッタ電極26はグローバル電極25に引き寄せられることはない。

(9)時刻(t8)以降

シャッタ電極26がグローバル電極25に引き寄せられるために必要な期間、例えば、100μ秒以上を確保した後、この期間にサブフレーム毎に時間重みを持たせて光源42を発光させ、表示領域においてPWM(Pulse Width Modulation)表示を行う。

【0021】

次に、ポラリティ反転(シャッタ=低電圧)における動作を説明する。

図5は、ポラリティ反転(シャッタ=低電圧)における動作タイミングチャートである。

(1)時刻(t1)まで

この期間には、画素に対する画像信号電圧の書込みが行われている。グローバル制御線8は、高電圧Vh(例えば、20(V))、容量制御線11は0(V)であり、TFT電極ソース制御線12には中間電圧Vm(例えば、5(V))が印加されている。

走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は、例えば、5(V)または0(V)であるが、この期間はTFT電極ソース制御線12には5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

(2)時刻(t1)から時刻(t2)まで

この期間にはグローバル制御線8の電圧が低電圧0(V)に変化する。シャッタ電極26は常時低電圧0(V)であるから、これによって、時刻(t1)までシャッタ電極26がグローバル電極25に引き寄せられていた場合は、シャッタ電極26はグローバル電極25から離れる方向に移動する。なお、時刻(t1)までシャッタ電極26がTFT電極27に引き寄せられていた場合は、特に変化は生じない。

【0022】

(3)時刻(t2)から時刻(t3)まで

容量制御線11を高電圧Vh(例えば、20(V))に向けてスイープ開始する。

(4)時刻(t3)から時刻(t4)まで

容量制御線11の電圧が中間電圧Vm(例えば、5(V))に達すると同時に、TFT電極ソース制御線12も高電圧Vh(例えば、20(V))に向けてスイープ開始する。 これにより、容量制御線11とTFT電極ソース制御線12の電圧は、同時に高電圧Vh(例えば、20(V))に達し、この後停止する。

この操作により、TFT電極27の電圧も上昇し、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は、高電圧Vh(例えば、20(V))に達し、0(V)が書込まれていた場合はVh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)に収束する。

これによって、常時低電圧0(V)であるシャッタ電極26を、TFT電極27に引き寄せるため、この期間は例えば100μ秒以上、十分に確保しておく必要がある。

【0023】

(5)時刻(t4)から時刻(t5)まで

容量制御線11及びTFT電極ソース制御線12を、同時に0(V)にスイープし、その後停止させる。この操作により、TFT電極27の電圧は、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は0(V)に低下し、0(V)が書込まれていた場合はVh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)で保持される。

(6)時刻(t5)から時刻(t6)まで

容量制御線11及びTFT電極ソース制御線12は0(V)で停止するが、この期間に当該画素の信号蓄積容量4に5(V)が書込まれていた場合は、シャッタ電極26はTFT電極27から離れる。しかし信号蓄積容量4に0(V)が書込まれていた場合には、シャッタ電極26はTFT電極27に引き寄せられたままである。

(7)時刻(t6)から時刻(t7)まで

TFT電極ソース制御線12に中間電圧Vm(例えば、5(V))が印加されると同時に、画素に対する画像信号電圧の書込みが開始される。走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は例えば5(V)または0(V)であるが、この期間には再びTFT電極ソース制御線12には5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

【0024】

(8)時刻(t7)から時刻(t8)まで

この期間にはグローバル制御線8の電圧が低電圧0(V)から高電圧Vh(例えば、20(V))に回復する。シャッタ電極26は常時低電圧0(V)であるから、時刻(t5)から時刻(t6)までの期間にシャッタ電極26がTFT電極27から離れた場合には、シャッタ電極26はグローバル電極25に引き寄せられる。

一方で、時刻(t5)から時刻(t6)までの期間もシャッタ電極26がTFT電極27に引き寄せられたままの場合には、シャッタ電極26はグローバル電極25に引き寄せられることはない。

(9)時刻(t8)以降

シャッタ電極26がグローバル電極25に引き寄せられるために必要な期間、例えば100μ秒以上を確保した後、この期間にサブフレーム毎に時間重みを持たせて光源42を発光させ、表示領域においてPWM(Pulse Width Modulation)表示を行う。

【0025】

さて上記の説明において、当該画素の信号蓄積容量4に5(V)が書込まれていた場合と0(V)が書込まれていた場合とで、TFT電極27に印加される制御電圧が異なることを述べたが、以下に図6、図7を用いて上記のTFT電極27への信号電圧書込みについて詳細に説明する。

図6は信号蓄積容量4に書込まれていた画像信号電圧がLowレベルの電圧(例えば、0(V))の場合の、TFT電極27への信号電圧の書込みを説明するための図である。

図6(a)はこの期間の最初に信号蓄積容量4に、Lowレベルの0(V)が書込まれている場合の画素等価回路を示しており、ここではTFT電極27に替えて、TFT電極27の等価入力容量45を記載している。

この期間に、容量制御線11とTFT電極ソース制御線12が同時に操作される状態を考えると、これは図6(b)の等価回路に示すように、0(V)が書込まれている信号蓄積容量4は両端が動電圧であるから短絡と等価であり、容量制御線11とTFT電極ソース制御線12をまとめて一本の等価配線46とみなす事ができる。

するとTFT電極書込みトランジスタ3はダイオード接続されたトランジスタであるから、図6(c)の等価回路に示すように、全体はTFT電極27の等価入力容量45がTFT電極書込みトランジスタ3の等価ダイオード47を介して等価配線46と接続された構成とみなすことができる。この図6(c)の等価回路を用いると、容量制御線11とTFT電極ソース制御線12に同時にVh(例えば、20(V))が書込まれた際には、等価ダイオード47がオンしてTFT電極27の等価入力容量45に信号電圧として(Vh−Vth)(VthはTFT電極書込みトランジスタ3のしきい値電圧)が書込まれ、この後に容量制御線11とTFT電極ソース制御線12に同時に0(V)が書込まれてもTFT電極27が(Vh−Vth)を制御信号電圧として保持することが容易に説明できる。

なお、容量制御線11とTFT電極ソース制御線12を同時に操作する代わりに、容量制御線11から少し遅れてTFT電極ソース制御線12を操作するようにしてもよい。

【0026】

次に図7は信号蓄積容量4に書込まれていた画像信号電圧がHighレベルの電圧(例えば、5(V))であった場合の、TFT電極27への信号電圧の書込みを説明するための図である。

図7(a)はこの期間の最初に信号蓄積容量4に、Highレベルの5(V)が書込まれている場合の画素等価回路を示しており、ここでもTFT電極27に替えて、TFT電極27の等価入力容量45を記載してある。

この期間に、容量制御線11とTFT電極ソース制御線12が同時に操作される状態を考えると、これは図7(b)の等価回路に示すように、5(V)が書込まれている信号蓄積容量4は5(V)の直流電源48と等価であり、容量制御線11とTFT電極ソース制御線12はまとめて一本の等価配線46とみなす事ができる。するとゲートに5(V)の直流電源48が接続されたTFT電極書込みトランジスタ3は常時オンであるために等価抵抗49とみなす事ができるから、図7(c)の等価回路に示すように、全体はTFT電極27の等価入力容量45がTFT電極書込みトランジスタ3の等価抵抗49を介して等価配線46と接続された構成とみなすことができる。

この図7(c)の等価回路を用いると、容量制御線11とTFT電極ソース制御線12に同時にVh(例えば、20(V))が書込まれた際には、等価抵抗49を経由してTFT電極27の等価入力容量45には信号電圧として一旦はVhが書込まれ、その後に容量制御線11とTFT電極ソース制御線12に同時に0(V)が書込まれた際には、等価抵抗49を経由してTFT電極27の等価入力容量45には再び0(V)が書込まれることが容易に説明できる。

【0027】

なお、前述したように、容量制御線11とTFT電極ソース制御線12を同時に操作する代わりに、容量制御線11から少し遅れてTFT電極ソース制御線12を操作するようにしてもよい。

ここで信号蓄積容量4に書き込まれるHighレベルの信号電圧は、高い電圧である方が、TFT電極書込みトランジスタ3によるTFT電極27の等価入力容量45への書込み動作がより高速化できるという長所がある。しかしその一方で、画像信号電圧書込み回路14から信号線6にHighレベルの信号電圧を書込む際の消費電力が上昇するという問題が生じる。

また、TFT電極27に0(V)が書込まれた後にはTFT電極27がターンオンしないようにTFT電極ソース制御線12には中間電圧Vmが入力されるが、TFT電極27の電圧は信号蓄積容量4に書き込まれるHighレベルの信号電圧に対して、実際には(H−Vth)の電圧までリークしてしまう。このことからも、Highレベルの信号電圧をあまり大きな電圧に設定するのは好ましくなく、7(V)から5(V)以下が適当である。

【0028】

次に、図2示す画素周辺回路の動作について説明する。

前述の(時刻(t1)まで)に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6には画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施例は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM(Pulse Width Modulation)駆動とサブフレーム毎に発光色を変えるフィールドシーケンシャル駆動を同時に行う。

このため、画像信号電圧書込み回路14から信号線6に書込まれる画像信号電圧は、例えば、0(V)と5(V)の2値の電圧であり、これによって各画素に設けられたTFT電極27に印加される制御信号電圧を制御する。

なお白表示時と黒表示時にそれぞれ5(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的としたシャッタ電極制御線7の印加電圧の値によって制御されることは既に述べたとおりである。またグローバル制御線8、容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12は、制御電極駆動回路16によって前述のように駆動制御される。

【0029】

次に、図3示すシャッタ電極26近傍構造の動作について説明する。

前述のようにシャッタ電極26は、TFT電極27とグローバル電極25のいずれかに静電引力で引き込まれて安定する。

ここでシャッタ電極26がグローバル電極25側に引き込まれた場合には、シャッタ電極26は反射膜23及び黒色膜24の開口上でその位置が安定する。従って光源42から射出されて導光板22を伝播した光41は開口から射出されてもシャッタ電極26で反射されることで再び導光板22に戻されてしまうため、画素は非発光状態として観測される。

またシャッタ電極26がTFT電極27側に引き込まれた場合には、シャッタ電極26は反射膜23及び黒色膜24の遮光上でその位置が安定する。従って光源42から射出されて導光板22を伝播した光41はシャッタ電極26に遮られることなく開口から射出されるため、画素は発光状態として観測される。

本実施例においてはグローバル電極25側にシャッタ電極26が引き寄せられた場合をシャッタ閉として設計したが、TFT電極27側をシャッタ閉とすることもできる。但しシャッタの開閉は、閉じる方が不十分な場合の画質劣化の方が、シャッタ開が不十分な場合の画質劣化よりも厳しいので、常に低インピーダンスで制御されるグローバル電極25側をシャッタ閉とした方が、画質劣化を回避して歩留りを上げられるという効果が有る。

なお本実施例においては、走査スイッチ5及びTFT電極書込みトランジスタ3のオンする期間は、それぞれ当該画素が走査線10によって選択された期間及びTFT電極27への制御信号電圧書込み期間に限定される。これによって、これらの多結晶シリコン薄膜トランジスタのオン期間が長時間継続することに起因するしきい値電圧のシフトを、十分に回避することが可能であるという特長も有する。

【0030】

[実施例2]

図8は、本発明の実施例2の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

以下、図8を用いて、本実施例2の可動シャッタ方式の画像表示装置について説明する。

本実施例2に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は基本的には既に説明した実施例1のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

図8に示す画素50は、図1に示す前述の実施例1の画素と同様である。しかし走査スイッチ5のゲートに接続された走査線10は、行方向に隣接する画素間で共通である。また同様に容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12も、走査線10とは別の組合せで、行方向に隣接する画素間で共通に設けられている。更に信号線(51,52)は2本がペアで設けられており、同一の走査線10に接続された隣接画素間の走査スイッチ5は、それぞれ異なる信号線(51,52)に接続されている。

本実施例2の動作は、隣接する2画素への信号蓄積容量4への信号電圧の書込みを、一回の走査線10の走査で行う点と、画像信号電圧書込み回路14が、2本の信号線(51,52)に同時に信号電圧を書込む点を除けば、前述の実施例1の動作と同様であるため、ここでは動作の説明は省略する。

【0031】

サブフィールド毎に時間重みを持たせて発光を制御するPWM(Pulse Width Modulation)駆動とフィールドシーケンシャル駆動を同時に行う場合には、特に列方向の画素数が大きいディスプレイでは走査線10の走査速度が大きくなるという課題があるが、本実施例2ではこのように隣接画素への信号電圧の書込みを一回の走査線10の走査で行うことができるため、走査回路15による走査線10の走査周波数を1/2に半減することができる。

なお信号蓄積容量4への信号電圧の書込みに際しては、容量制御線11の電圧が安定していることが必要である。しかしながら一本の走査線10による2行分の画素の信号電圧書込みの際に、これら2行分の信号蓄積容量4が同じ容量制御線11に接続していると、容量制御線11の変動量が2倍になってしまう。そこで本実施例では、一本の走査線10による2行分の画素の信号電圧書込みの際に同時に書込まれる信号蓄積容量4は、それぞれ異なる容量制御線11に接続させ、このような問題の回避を図っている。

【0032】

[実施例3]

図9は、本発明の実施例3の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

以下、図9を用いて、本実施例3について説明する。

本実施例3に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は基本的には既に説明した前述の実施例1のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

図9に示す画素60の左半分は、図1に示す実施例1の画素13と同様である。しかし実施例1では双極性シャッタ1の二つある一方の制御電極であるグローバル電極はグローバル制御線8に接続されていたが、本実施例3ではグローバル電極もTFT電極と同様の構造を有している。

即ち、新たに第2信号線62が設けられており、第2信号線62と第2信号蓄積容量64とは第2走査スイッチ65で接続されている。第2信号蓄積容量64は更にグローバル電極書込みトランジスタ63のゲートに接続されており、グローバル電極書込みトランジスタ63のドレインはグローバル電極に接続されている。

図9に示すように、走査スイッチ5と第2走査スイッチ65のゲートは走査線10に、信号蓄積容量4の他端と第2信号蓄積容量64の他端はTFT電極ソース制御線12に、TFT電極書込みトランジスタ3のソースとグローバル電極書込みトランジスタ63のソースはTFT電極ソース制御線12に接続されている。

本実施例3の動作は、第2信号線62には信号線6に対して逆極性の信号電圧が印加されることと、グローバル電極もTFT電極と同一のタイミングで制御されることとを除けば、実施例1の動作と同様であるため、ここでは動作の説明は省略する。

本実施例3においては、グローバル電極もTFT電極と同一のタイミングで制御されるため、図4、図5に記載した時刻(t6)のタイミングで電極への書込み制御を終了することができ、発光に用いることのできる時間をより長くすることができるという長所がある。

これによって、本実施例はより発光時間を長くできるため、高輝度化に有利である。またTFT電極とグローバル電極に入力される制御信号が必ず相補的になるため、シャッタ電極26をノイズ等に対してより安定的に動作させることが可能である。なお、前述の実施例2は、本実施例にも適用可能であることは言うまでもない。

【0033】

[実施例4]

図10は、本発明の実施例4の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

図11は、本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ:シャッタ=高電圧)である。

図12は、本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ反転:シャッタ=低電圧)である。

以下、図10〜図12を用いて、本発明の実施例4について、その構成および動作を順次説明する。

まず、図10を用いて本実施例4の画素回路について説明する。

図10に示すように、各画素70には信号線6が設けられており、信号線6と信号書込み容量71とは走査スイッチ5で接続されている。信号書込み容量71は更に信号蓄積容量4と信号転送スイッチ73で接続されている。信号蓄積容量4はTFT電極書込みトランジスタ3のゲートに接続されており、TFT電極書込みトランジスタ3のドレインは双極性シャッタ1の二つある一方の制御電極であるTFT電極に接続されている。双極性シャッタ1の他方の制御電極であるグローバル電極は、グローバル制御線8に接続され、また双極性シャッタ1のシャッタ電極は、シャッタ電極制御線7に接続されている。

なお、信号蓄積容量4の他端は容量制御線11に接続されており、TFT電極書込みトランジスタ3のソースはTFT電極ソース制御線12に、走査スイッチ5のゲートは走査線10に接続されている。また信号転送スイッチ73のゲートはアップデート線74に、信号書込み容量71の他端は容量接地線72に接続されている。

本実施例4の画素周辺回路は、アップデート線74が制御電極駆動回路16に接続されていること、容量接地線72が接地されていることを除けば、前述の実施例1と同様であるため、その説明は省略する。また画素部断面構造に関しても同様である。

【0034】

次に、図11、図12を用いて、本実施例4の画素回路の動作を説明する。

本実施例4の画素回路の動作は、基本的には、前述の実施例1の動作と同様である。前述の実施例1と比較した際の本実施例4の動作における差異は、時刻(t1)から時刻(t2)までの期間にアップデート線74が一度ターンオンし、信号書込み容量71に書込まれていた信号電圧を信号蓄積容量4に転送する期間が設けられていることと、走査線10の走査が、時刻(t2)から開始されることである。

本実施例においては信号線6からの信号書込みを行う信号書込み容量71と、TFT電極書込みトランジスタ3の駆動を担う信号蓄積容量4が分離しているため、TFT電極書込みトランジスタ3の駆動と走査線10の走査を並行して行うことができる。

本実施例では、これによって、走査回路15による走査線10の走査周波数を低減することができるため、走査回路15の駆動マージンを増加させ、歩留りを向上させることができる。なお、前述の実施例2は、本実施例にも適用可能であることは言うまでもない。

【0035】

前述の実施例1ないし実施例4に開示した技術は、本発明の趣旨を損なわない範囲で、様々な変更が可能である。

前述の実施例1ないし実施例4では、ガラス基板39上の走査スイッチ5とTFT電極書込みトランジスタ3をn型の多結晶シリコン薄膜トランジスタで設けているが、ガラス基板39に変えて耐熱プラスチック基板等を用いることで基板に曲げに対するフレキシビリティを持たせることが可能である。

また、n型の多結晶シリコン薄膜トランジスタに変えて、p型の多結晶シリコン薄膜トランジスタや、結晶化が不要なためより低コストプロセスの適用が可能なアモルファスシリコン薄膜トランジスタを用いることもできる。

なお、p型薄膜トランジスタを用いた際には、これらに印加する電圧関係の正負を逆にする必要があることは言うまでも無い。

或いはまた、n型の多結晶シリコン薄膜トランジスタに変えて、InGaZnOに代表されるアモルファス酸化物薄膜トランジスタを用いることによって、画像信号電圧の振幅を5V以下に下げて低消費電力化を図りながら、かつ多結晶シリコン薄膜トランジスタと比較してプロセス装置コストを低減することができる。

【0036】

[実施例5]

図13は、本発明の実施例5の可動シャッタ方式の画像表示装置を使用するインターネット画像表示装置の概略構成を示すブロック図である。

以下、図13を用いて、本発明の実施例5について説明する。

無線インターフェース(I/F)回路152には、圧縮された画像データ等が外部から無線データとして入力し、無線I/F回路152の出力はI/O(Input/Output)回路153を介してデータバス158に接続される。

データバス158には、この他にマイクロプロセサ(MPU)154、表示パネルコントローラ156、フレームメモリ157等が接続されている。

また、表示パネルコントローラ156の出力は機械的シャッタを用いた表示装置151に入力している。また、インターネット画像表示装置150には、更に、電源159が設けられている。

なおここで機械的シャッタを用いた表示装置151は、先に延べた実施例1と同一の構成および動作を有しているので、その内部の構成及び動作の記載はここでは省略する。

以下、本実施例5の動作について説明する。

始めに、無線I/F回路152は命令に応じて圧縮された画像データを外部から取り込み、この画像データをI/O回路153を介してマイクロプロセサ154及びフレームメモリ157に転送する。

マイクロプロセサ154はユーザからの命令操作を受けて、必要に応じてインターネット画像表示装置150全体を駆動し、圧縮された画像データのデコードや信号処理、情報表示を行う。ここで信号処理された画像データは、フレームメモリ157に一時的に蓄積が可能である。

【0037】

ここでマイクロプロセサ154が表示命令を出した場合には、その指示に従ってフレームメモリ157から表示パネルコントローラ156を介して表示装置151に画像データが入力され、表示装置151は入力された画像データをリアルタイムで表示する。

このとき表示パネルコントローラ156は、同時に画像を表示するために必要な所定のタイミングパルスを出力制御する。

なお、表示装置151がこれらの信号を用いて、入力された画像データをリアルタイムで表示することに関しては、前述の実施例1の説明で述べたとおりである。なおここで電源159には二次電池が含まれており、インターネット画像表示装置150全体を駆動する電力を供給する。

本実施例によれば、高画質表示が可能であり、かつ消費電力の少ないインターネット画像表示装置150を低コストで提供することができる。

なお、本実施例では、画像表示デバイスとして、前述の実施例1で説明した表示装置151を用いたが、これ以外にその他の実施例に記載されたような種々の表示装置を用いることが可能であることは明らかである。

但しこの場合は表示パネルコントローラ156の出力するタイミングパルスには、必要に応じて若干の変更が必要になることは言うまでもない。

【0038】

以上説明したように、本実施例によれば、低消費電力でありながら高コントラストで色再現性が良いといった、機械的シャッタを用いた従来の可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、更にカスコードトランジスタが必要でなく、画素トランジスタの信頼性を確保することができるため、高精細化と高信頼性化の両立が可能となる。

具体的には、TFT電極へ制御電圧の書込みを行うTFT電極書込みトランジスタは、ゲートがターンオンする際には常にソース・ドレイン間に高電圧が印加されることがないため、カスコードトランジスタのような対策をせずとも、信頼性上の問題を回避することができる。

このように、本実施例によれば、特にディスプレイの高画質化と低消費電力化、かつ高精細化と高信頼化の両立を図ることができる。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【符号の説明】

【0039】

1 双極性シャッタ

3 TFT電極書込みトランジスタ

4,204 信号蓄積容量

5,205 走査スイッチ

6,51,52,206 信号線

7 シャッタ電極制御線

8 グローバル制御線

10,210 走査線

11 容量制御線

12 TFT電極ソース制御線

13,50,60,70,213 画素

14 画像信号電圧書込み回路

15 走査回路

16 制御電極駆動回路

21,23 反射膜

22 導光板

24 黒色膜

25 グローバル電極

26 シャッタ電極

27 TFT電極

30,32 高濃度n型不純物をドープした多結晶シリコン薄膜

31 多結晶シリコン薄膜

33 ゲート絶縁膜

34 絶縁保護膜

35 ゲート電極

37 ソース電極

36 ドレイン電極

38 保護膜

39 ガラス基板

41 光

42 光源

45 等価入力容量

46 等価配線

47 等価ダイオード

48 直流電源

49 等価抵抗

62 第2信号線

63 グローバル電極書込みトランジスタ

64 第2信号蓄積容量

65 第2走査スイッチ

71 信号書込み容量

72 容量接地線

73 信号転送スイッチ

74 アップデート線

150 インターネット画像表示装置

151 表示装置

152 無線インターフェース(I/F)回路

153 I/O(Input/Output)回路

154 マイクロプロセサ(MPU)

156 表示パネルコントローラ

157 フレームメモリ

158 データバス

159 電源

201 双極性シャッタ(Dual actuator shutter assembly)

202,215 pMOSトランジスタ

203,216 nMOSトランジスタ

207 pMOSゲート電圧線

208 正電圧線

209 制御電極電圧線

211 シャッタ電圧線

212 nMOSソース電圧線

217 カスコードゲート電圧線

【技術分野】

【0001】

本発明は、表示装置およびその駆動方法に係わり、特に、可動シャッタの位置を電気的に制御して画像表示を行う画像表示装置の画素回路に適用して有効な技術に関する。

【背景技術】

【0002】

機械的シャッタの位置を電気的に制御して画像表示を行う画像表示装置(以下、可動シャッタ方式の画像表示装置)の画素回路としての使用方法がある。

図14は、従来の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

以下、図14を用いて、従来の可動シャッタ方式の画像表示装置に関して説明する。

各画素213には、信号線206が設けられており、信号線206と信号蓄積容量204とは走査スイッチ205で接続されている。

信号蓄積容量204は更にシャッタ負電圧書込み用nMOSトランジスタ203のゲートに接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のドレインは、カスコードnMOSトランジスタ216、カスコードpMOSトランジスタ215を介して、シャッタ正電圧書込み用pMOSトランジスタ202のドレインに接続されている。

各画素は、シャッタ電圧線211に接続された双極性シャッタ(Dual actuator shutter assembly)201を有しているが、二つある双極性シャッタ201の制御電極の内の一方は、カスコードnMOSトランジスタ216を介してシャッタ負電圧書込み用nMOSトランジスタ203のドレインに接続されており、制御電極の他方は制御電極電圧線209に接続されている。

なお、信号蓄積容量204の他端はシャッタ電圧線211に接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のソースはシャッタ負電圧書込み用nMOSソース電圧線212に接続されている。

また、シャッタ正電圧書込み用pMOSトランジスタ202のゲートとドレインは、それぞれシャッタ正電圧書込み用pMOSゲート電圧線207と正電圧線208に接続されている。さらに、カスコードnMOSトランジスタ216及びカスコードpMOSトランジスタ215のゲートはカスコードゲート電圧線217に接続され、走査スイッチ205のゲートは走査線210に接続されている。

なお、双極性シャッタ201は、遮光面上に設けられた開口に対向して設けられており、当該画像表示装置にはこのような画素213がマトリクス状に配列されている。

【0003】

次に、従来の可動シャッタ方式の画像表示装置の動作について説明する。

信号線206に書込まれた画像信号電圧は、走査線210を順次走査することによって走査スイッチ205を介して信号蓄積容量204に記憶される。

次に、全画素の信号蓄積容量204に対する画像信号電圧の書込み走査が終了した後に、各画素において、書込まれた画像信号電圧を元に双極性シャッタ201の制御電極の内の一方に対して画像信号の増幅書込みを行う。即ち、まず全画素において、シャッタ正電圧書込み用pMOSゲート電圧線207を所定の期間だけ低電圧にすることによって、シャッタ正電圧書込み用pMOSトランジスタ202をこの期間のみオン状態にして、双極性シャッタ201の制御電極の内の一方の電極に、正電圧線208に印加されていた所定の正電圧をプリチャージする。

次に、シャッタ負電圧書込み用nMOSソース電圧線212を、所定の期間だけ所定の低電圧にする。このとき、信号蓄積容量204に画像信号電圧として高電圧が書込まれていた画素のみが、この期間、シャッタ負電圧書込み用nMOSトランジスタ203がオン状態となることにより、双極性シャッタ201の制御電極の内の一方の電圧はシャッタ負電圧書込み用nMOSソース電圧線212に印加されている所定の低電圧に書き換えられる。

【0004】

また、信号蓄積容量204に画像信号電圧として低電圧が書込まれていた画素は、この期間もシャッタ負電圧書込み用nMOSトランジスタ203はオフ状態を維持するため、双極性シャッタ201の制御電極の内の一方の電圧は、既にプリチャージされた所定の正電圧を維持する。

このようにして双極性シャッタ201の制御電極の内の一方の電極に画像信号の増幅書込みを行うが、これと並行して制御電極電圧線209への印加電圧を制御することによって、双極性シャッタ201を静電的に開閉操作することができる。このように双極性シャッタ201で遮光面上に設けられた開口を開閉することで光の透過量を制御して、当該画像表示装置は書込まれた画像信号電圧に対応した画像を画素マトリクス上に表示することができる。

なお、前述の動作において、カスコードnMOSトランジスタ216及びカスコードpMOSトランジスタ215は、シャッタ正電圧書込み用pMOSトランジスタ202及びシャッタ負電圧書込み用nMOSトランジスタ203に信頼性寿命を損なうような高いドレイン電圧が印加されることを防止するために設けられたものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】US 2008/0174532号

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の可動シャッタ方式の画像表示装置の画素回路では、シャッタ正電圧書込み用pMOSトランジスタ202及びシャッタ負電圧書込み用nMOSトランジスタ203のドレインに対する高電圧印加に起因する信頼性劣化を回避するために、カスコードnMOSトランジスタ216及びカスコードpMOSトランジスタ215を設ける必要があった。

画像表示装置の高精細化に対応するためには画素回路の簡略化が必要になるが、従来の可動シャッタ方式の画像表示装置の画素回路では高信頼化のためにはカスコードトランジスタが不可欠であり、高精細化と高信頼性化の両立が困難であった。

即ち、低消費電力でありながら高コントラストで色再現性が良いといった、従来の可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、更に画素回路の簡略化による高精細化と高信頼性化の両立を図ることが要望されていた。

本発明は、前述の要望に答えるためになされたものであり、本発明の目的は、可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、画素回路の簡略化による高精細化と高信頼性化を両立させことが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【課題を解決するための手段】

【0007】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

(1)機械的シャッタをそれぞれ有する複数の画素と、前記各画素に画像信号を入力する信号線と、前記各画素に走査電圧を入力する走査線とを備え、前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有し、前記第2制御電極には第2制御電圧が入力され、前記容量制御信号、前記第1制御信号、および、前記第2制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御する。

【0008】

(2)機械的シャッタをそれぞれ有する複数の画素と、前記各画素に第1画像信号を入力する第1信号線と、前記各画素に第2画像信号を入力する第2信号線と、前記各画素に走査電圧を入力する走査線とを備え、前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、前記第1制御電極に前記第1画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、前記第2制御電極に前記第2画像信号に応じた第2制御電圧を入力するための第2制御電圧印加回路とを有し、前記第1制御電圧印加回路は、電流端子の一端が前記第1信号線に接続され、ゲートが前記走査線に接続される第1入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記第1入力トランジスタの電流端子の他端に接続され、前記第1入力トランジスタで取り込んだ電圧を保持する第1保持容量と、ゲートが前記第1保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第1トランジスタとを有し、前記第2制御電極電圧印加回路は、電流端子の一端が前記第2信号線に接続され、ゲートが前記走査線に接続される第2入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記第2入力トランジスタの電流端子の他端に接続され、前記第2入力トランジスタで取り込んだ電圧を保持する第2保持容量と、ゲートが前記第2保持容量の一端に接続され、電流端子の他端が第2制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第2トランジスタとを有し、前記容量制御信号、および、前記制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御する。

【0009】

(3)(1)または(2)において、面状の光源と、透明基板と、前記透明基板上に設けられる遮光膜と、前記遮光膜は、各画素に対応する光学的開口領域を有し、前記面状の光源から射出された光に対して、前記光学的開口領域以外の領域を遮光し、前記機械的シャッタは、前記透明基板上で、光学的開口領域に対応して設けられている。

(4)(1)ないし(3)の何れかにおいて、前記各トランジスタは、半導体層が多結晶シリコン薄膜で構成されるトランジスタ、あるいは、半導体層がアモルファスシリコン薄膜で構成されるトランジスタ、または、半導体層が酸化物薄膜を用いて構成されるトランジスタである。

(5)(1)ないし(3)の何れかにおいて、前記各トランジスタは、n型のトランジスタであり、前記第2電圧レベルは、第1電圧レベルよりも高電位の電圧レベルである。

【発明の効果】

【0010】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明によれば、可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、画素回路の簡略化による高精細化と高信頼性化を両立させことが可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施例1の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図2】本発明の実施例1の可動シャッタ方式の画像表示装置の概略構成を示すブロック図である。

【図3】本発明の実施例1の可動シャッタ方式の画像表示装置の画素部の断面構造を示す断面図である。

【図4】本発明の実施例1の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ:シャッタ=高電圧)である。

【図5】本発明の実施例1の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ反転:シャッタ=低電圧)である。

【図6】本発明の実施例1の可動シャッタ方式の画像表示装置において、画像信号電圧がLowレベルの電圧(例えば、0(V))の時のTFT電極への制御信号電圧の書込みを説明するための図である。

【図7】本発明の実施例1の可動シャッタ方式の画像表示装置において、画像信号電圧がHighレベルの電圧(例えば、5(V))の時のTFT電極への制御信号電圧の書込みを説明するための図である。

【図8】本発明の実施例2の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図9】本発明の実施例3の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図10】本発明の実施例4の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【図11】本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ:シャッタ=高電圧)である。

【図12】本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ反転:シャッタ=低電圧)である。

【図13】本発明の実施例5の可動シャッタ方式の画像表示装置を使用するインターネット画像表示装置の概略構成を示すブロック図である。

【図14】従来の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

【発明を実施するための形態】

【0012】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

[実施例1]

図1は、本発明の実施例1の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

図2は、本発明の実施例1の可動シャッタ方式の画像表示装置の概略構成を示すブロック図である。

図3は、本発明の実施例1の可動シャッタ方式の画像表示装置の画素部の断面構造を示す断面図である。

以下、図1〜図3を用いて、本実施例の可動シャッタ方式の画像表示装置の画素回路について説明する。

各画素13には信号線6が設けられており、信号線6と信号蓄積容量(本願発明の保持容量)4とは走査スイッチ(本願発明の入力トランジスタ)5で接続されている。信号蓄積容量4は更にTFT電極書込みトランジスタ(本願発明の第1トランジスタ)3のゲートに接続されており、TFT電極書込みトランジスタ3のドレインは双極性シャッタ1の二つある一方の制御電極であるTFT電極に接続されている。双極性シャッタ1の他方の制御電極であるグローバル電極は、グローバル制御線8に接続され、また双極性シャッタ1のシャッタ電極は、シャッタ電極制御線7に接続されている。

なお、信号蓄積容量4の他端は容量制御線11に接続されており、TFT電極書込みトランジスタ3のソースはTFT電極ソース制御線12に、走査スイッチ5のゲートは走査線10に接続されている。

また、前述の双極性シャッタ1は、後に図3を用いて説明するように、遮光面上に設けられた開口に対向して設けられている。

【0013】

次に、本実施例の可動シャッタ方式の画像表示装置の画素周辺回路について説明する。

図2に示すように、マトリクス状に配列された画素13が表示領域を構成しており、画素13には列方向に信号線6と、グローバル制御線8が、行方向に走査線10、容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12が設けられている。

表示領域の周辺で、信号線6の一端は画像信号電圧書込み回路14に接続されており、グローバル制御線8、容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12の一端はそれぞれ制御電極駆動回路16に接続されている。また走査線10の一端は走査回路15に接続されている。

なお、図2は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではないことは明らかである。

【0014】

次に、本実施例の可動シャッタ方式の画像表示装置の画素部断面構造について説明する。

図3に示すように、ガラス基板39上には、多結晶シリコン薄膜31、高濃度n型不純物をドープした多結晶シリコン薄膜(30,32)、ゲート絶縁膜33、高融点金属からなるゲート電極35、ソース電極37、ドレイン電極36とから構成される多結晶シリコン薄膜トランジスタが設けられており、これはTFT電極書込みトランジスタ3に対応するものである。

更にガラス基板39上には、絶縁保護膜34を挟んでソース電極37、ドレイン電極36と同じAl配線層でシャッタ電極制御線7、グローバル制御線8の一部が形成されており、これらはシリコンナイトライドと有機材料の多層膜からなる保護膜38によって覆われている。

保護膜38上には、シャッタ電極26と、TFT電極27、グローバル電極25の2つの制御電極を有する双極性シャッタ1が設けられており、シャッタ電極26はシャッタ電極制御線7に、ドレイン電極36はTFT電極27に、グローバル制御線8はグローバル電極25に、それぞれコンタクトホールを介して接続されている。またこれらシャッタ電極26と、二つの制御電極であるTFT電極27、グローバル電極25は、互いに接触した際の短絡防止のために、表面には絶縁膜が形成されている。

【0015】

ここで、シャッタ電極26は、シャッタ電極26に入力される電圧と、TFT電極27、グローバル電極25に入力される電圧との相対関係による電界でその位置が制御されるため、図3には破線を用いてその可動範囲も開示している。

また、図3には記載されていないが、画素13内に設けられたその他のトランジスタも、同様に多結晶シリコン薄膜トランジスタで構成されている。これらの多結晶シリコン薄膜トランジスタは、公知のエキシマレーザアニーリングプロセス等を用いて形成することができる。

シャッタ電極26に対してガラス基板39と反対側には、R(赤)G(緑)B(青)の3色の独立LED光源からなる光源42を有する導光板22が設けられている。

導光板22の両面には反射膜(21,23)と、更に反射膜23の上には黒色膜24が設けられている。反射膜(21,23)はAgやAlなどの金属膜で、黒色膜24は金属酸化膜や、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させることで形成することができる。

ここで、反射膜23及び黒色膜24には図3に示すように、シャッタ電極26に対応する位置に開口が設けられており、光源42から射出されて導光板22を伝播した光41の一部が、この開口から射出されるように構成されている。また黒色膜24は、外光の反射を防ぐために設けられたものである。

【0016】

次に、図4〜図7を用いて、本実施例の可動シャッタ方式の画像表示装置の動作について説明する。

まず、図1に示す本実施例の画素回路の動作について説明する。

図4、図5は、本発明の実施例の可動シャッタ方式の画像表示装置の画素回路の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。図4ではシャッタ電極制御線7は常に高電圧Vh(例えば、20(V))、図5では常に0(V)であるが、これは双極性シャッタ1の駆動電圧の反転(ポラリティ反転)動作に対応したものである。

本実施例の画像表示装置は、フルカラーの8bit階調をシャッタの開閉で表現するために、1フレームを8×RGB=24以上のサブフレームに分割し、光源42の発光にサブフレーム毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM(Pulse Width Modulation)駆動を行うが、このとき所定のサブフレーム毎にポラリティ反転駆動を行い、双極性シャッタ1の 電極の劣化を回避する。

また、特に最下段に記載した双極性シャッタ1のTFT電極27の電圧値に関しては、画像信号によって約0(V)と約Vh(正確にはVh、またはVh−Vth、VthはTFT電極書込みトランジスタ3のしきい値電圧)の2値を取るため、図面を判り易くするために前者を実線、後者を破線で示している。

【0017】

まずポラリティ(シャッタ=高電圧)における動作を説明する。

図4はポラリティ(シャッタ=高電圧)における動作タイミングチャートである。

(1)時刻(t1)まで

この期間には、画素に対する画像信号電圧の書込みが行われている。グローバル制御線8、容量制御線11は0(V)であり、TFT電極ソース制御線12には中間電圧Vm(例えば5(V))が印加されている。走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は、例えば、5(V)または0(V)であるが、この期間はTFT電極ソース制御線12には、5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

(2)時刻(t1)から時刻(t2)

この期間にはグローバル制御線8の電圧が高電圧Vh(例えば、20(V))に変化する。シャッタ電極26は常時高電圧Vh(例えば20(V))であるから、これによって時刻(t1)まで、シャッタ電極26がグローバル電極25に引き寄せられていた場合は、シャッタ電極26はグローバル電極25から離れる方向に移動する。なお、時刻(t1)までシャッタ電極26がTFT電極27に引き寄せられていた場合は、特に変化は生じない。

【0018】

(3)時刻(t2)から時刻(t3)まで

容量制御線11を高電圧Vh(例えば、20(V))に向けてスイープ開始する。

(4)時刻(t3)から時刻(t4)まで

容量制御線11の電圧が中間電圧Vm(例えば、5(V))に達すると同時に、TFT電極ソース制御線12も高電圧Vh(例えば、20(V))に向けてスイープ開始する。 これにより、容量制御線11とTFT電極ソース制御線12の電圧は、同時に、高電圧Vh(例えば、20(V))に達し、この後停止する。

この操作により、TFT電極27の電圧も上昇し、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は高電圧Vh(例えば、20(V))に達し、0(V)が書込まれていた場合は、Vh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)に収束する。

これによって、時刻(t2)までシャッタ電極26がTFT電極27に引き寄せられていた場合は、シャッタ電極26はTFT電極27から離れる方向に移動する。

(5)時刻(t4)から時刻(t5)まで

容量制御線11及びTFT電極ソース制御線12を同時に0(V)にスイープし、その後停止させる。この操作により、TFT電極27の電圧は、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は0(V)に低下し、0(V)が書込まれていた場合はVh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)で保持される。

【0019】

(6)時刻(t5)から時刻(t6)まで

容量制御線11及びTFT電極ソース制御線12は0(V)で停止するが、この期間に当該画素の信号蓄積容量4に5(V)が書込まれていた場合は、シャッタ電極26はTFT電極27に引き寄せられる。しかし信号蓄積容量4に0(V)が書込まれていた場合には、シャッタ電極26がTFT電極27に引き寄せられることはない。シャッタ電極26を確実にTFT電極27に引き寄せるため、この期間は例えば100μ秒以上、十分に確保しておく必要がある。

(7)時刻(t6)から時刻(t7)まで

TFT電極ソース制御線12に中間電圧Vm(例えば、5(V))が印加されると同時に、画素に対する画像信号電圧の書込みが開始される。走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は、例えば、5(V)または0(V)であるが、この期間には再びTFT電極ソース制御線12には5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

【0020】

(8)時刻(t7)から時刻(t8)まで

この期間にはグローバル制御線8の電圧が高電圧Vh(例えば、20(V))から0(V)に回復する。シャッタ電極26は常時高電圧Vh(例えば、20(V))であるから、時刻(t5)から時刻(t6)までの期間にシャッタ電極26がTFT電極27に引き寄せられていない場合には、シャッタ電極26はグローバル電極25に引き寄せられる。

一方で、時刻(t5)から時刻(t6)までの期間にシャッタ電極26がTFT電極27に既に引き寄せられている場合には、シャッタ電極26はグローバル電極25に引き寄せられることはない。

(9)時刻(t8)以降

シャッタ電極26がグローバル電極25に引き寄せられるために必要な期間、例えば、100μ秒以上を確保した後、この期間にサブフレーム毎に時間重みを持たせて光源42を発光させ、表示領域においてPWM(Pulse Width Modulation)表示を行う。

【0021】

次に、ポラリティ反転(シャッタ=低電圧)における動作を説明する。

図5は、ポラリティ反転(シャッタ=低電圧)における動作タイミングチャートである。

(1)時刻(t1)まで

この期間には、画素に対する画像信号電圧の書込みが行われている。グローバル制御線8は、高電圧Vh(例えば、20(V))、容量制御線11は0(V)であり、TFT電極ソース制御線12には中間電圧Vm(例えば、5(V))が印加されている。

走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は、例えば、5(V)または0(V)であるが、この期間はTFT電極ソース制御線12には5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

(2)時刻(t1)から時刻(t2)まで

この期間にはグローバル制御線8の電圧が低電圧0(V)に変化する。シャッタ電極26は常時低電圧0(V)であるから、これによって、時刻(t1)までシャッタ電極26がグローバル電極25に引き寄せられていた場合は、シャッタ電極26はグローバル電極25から離れる方向に移動する。なお、時刻(t1)までシャッタ電極26がTFT電極27に引き寄せられていた場合は、特に変化は生じない。

【0022】

(3)時刻(t2)から時刻(t3)まで

容量制御線11を高電圧Vh(例えば、20(V))に向けてスイープ開始する。

(4)時刻(t3)から時刻(t4)まで

容量制御線11の電圧が中間電圧Vm(例えば、5(V))に達すると同時に、TFT電極ソース制御線12も高電圧Vh(例えば、20(V))に向けてスイープ開始する。 これにより、容量制御線11とTFT電極ソース制御線12の電圧は、同時に高電圧Vh(例えば、20(V))に達し、この後停止する。

この操作により、TFT電極27の電圧も上昇し、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は、高電圧Vh(例えば、20(V))に達し、0(V)が書込まれていた場合はVh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)に収束する。

これによって、常時低電圧0(V)であるシャッタ電極26を、TFT電極27に引き寄せるため、この期間は例えば100μ秒以上、十分に確保しておく必要がある。

【0023】

(5)時刻(t4)から時刻(t5)まで

容量制御線11及びTFT電極ソース制御線12を、同時に0(V)にスイープし、その後停止させる。この操作により、TFT電極27の電圧は、後述のように当該画素の信号蓄積容量4に5(V)が書込まれていた場合は0(V)に低下し、0(V)が書込まれていた場合はVh−Vth(VthはTFT電極書込みトランジスタ3のしきい値電圧)で保持される。

(6)時刻(t5)から時刻(t6)まで

容量制御線11及びTFT電極ソース制御線12は0(V)で停止するが、この期間に当該画素の信号蓄積容量4に5(V)が書込まれていた場合は、シャッタ電極26はTFT電極27から離れる。しかし信号蓄積容量4に0(V)が書込まれていた場合には、シャッタ電極26はTFT電極27に引き寄せられたままである。

(7)時刻(t6)から時刻(t7)まで

TFT電極ソース制御線12に中間電圧Vm(例えば、5(V))が印加されると同時に、画素に対する画像信号電圧の書込みが開始される。走査線10は行毎に順次走査され、選択された走査スイッチ5が一時的にターンオンすることによって、信号電圧が順に信号蓄積容量4に書込まれる。信号電圧は例えば5(V)または0(V)であるが、この期間には再びTFT電極ソース制御線12には5(V)の中間電圧Vmが印加されているため、TFT電極書込みトランジスタ3がターンオンすることはない。

【0024】

(8)時刻(t7)から時刻(t8)まで

この期間にはグローバル制御線8の電圧が低電圧0(V)から高電圧Vh(例えば、20(V))に回復する。シャッタ電極26は常時低電圧0(V)であるから、時刻(t5)から時刻(t6)までの期間にシャッタ電極26がTFT電極27から離れた場合には、シャッタ電極26はグローバル電極25に引き寄せられる。

一方で、時刻(t5)から時刻(t6)までの期間もシャッタ電極26がTFT電極27に引き寄せられたままの場合には、シャッタ電極26はグローバル電極25に引き寄せられることはない。

(9)時刻(t8)以降

シャッタ電極26がグローバル電極25に引き寄せられるために必要な期間、例えば100μ秒以上を確保した後、この期間にサブフレーム毎に時間重みを持たせて光源42を発光させ、表示領域においてPWM(Pulse Width Modulation)表示を行う。

【0025】

さて上記の説明において、当該画素の信号蓄積容量4に5(V)が書込まれていた場合と0(V)が書込まれていた場合とで、TFT電極27に印加される制御電圧が異なることを述べたが、以下に図6、図7を用いて上記のTFT電極27への信号電圧書込みについて詳細に説明する。

図6は信号蓄積容量4に書込まれていた画像信号電圧がLowレベルの電圧(例えば、0(V))の場合の、TFT電極27への信号電圧の書込みを説明するための図である。

図6(a)はこの期間の最初に信号蓄積容量4に、Lowレベルの0(V)が書込まれている場合の画素等価回路を示しており、ここではTFT電極27に替えて、TFT電極27の等価入力容量45を記載している。

この期間に、容量制御線11とTFT電極ソース制御線12が同時に操作される状態を考えると、これは図6(b)の等価回路に示すように、0(V)が書込まれている信号蓄積容量4は両端が動電圧であるから短絡と等価であり、容量制御線11とTFT電極ソース制御線12をまとめて一本の等価配線46とみなす事ができる。

するとTFT電極書込みトランジスタ3はダイオード接続されたトランジスタであるから、図6(c)の等価回路に示すように、全体はTFT電極27の等価入力容量45がTFT電極書込みトランジスタ3の等価ダイオード47を介して等価配線46と接続された構成とみなすことができる。この図6(c)の等価回路を用いると、容量制御線11とTFT電極ソース制御線12に同時にVh(例えば、20(V))が書込まれた際には、等価ダイオード47がオンしてTFT電極27の等価入力容量45に信号電圧として(Vh−Vth)(VthはTFT電極書込みトランジスタ3のしきい値電圧)が書込まれ、この後に容量制御線11とTFT電極ソース制御線12に同時に0(V)が書込まれてもTFT電極27が(Vh−Vth)を制御信号電圧として保持することが容易に説明できる。

なお、容量制御線11とTFT電極ソース制御線12を同時に操作する代わりに、容量制御線11から少し遅れてTFT電極ソース制御線12を操作するようにしてもよい。

【0026】

次に図7は信号蓄積容量4に書込まれていた画像信号電圧がHighレベルの電圧(例えば、5(V))であった場合の、TFT電極27への信号電圧の書込みを説明するための図である。

図7(a)はこの期間の最初に信号蓄積容量4に、Highレベルの5(V)が書込まれている場合の画素等価回路を示しており、ここでもTFT電極27に替えて、TFT電極27の等価入力容量45を記載してある。

この期間に、容量制御線11とTFT電極ソース制御線12が同時に操作される状態を考えると、これは図7(b)の等価回路に示すように、5(V)が書込まれている信号蓄積容量4は5(V)の直流電源48と等価であり、容量制御線11とTFT電極ソース制御線12はまとめて一本の等価配線46とみなす事ができる。するとゲートに5(V)の直流電源48が接続されたTFT電極書込みトランジスタ3は常時オンであるために等価抵抗49とみなす事ができるから、図7(c)の等価回路に示すように、全体はTFT電極27の等価入力容量45がTFT電極書込みトランジスタ3の等価抵抗49を介して等価配線46と接続された構成とみなすことができる。

この図7(c)の等価回路を用いると、容量制御線11とTFT電極ソース制御線12に同時にVh(例えば、20(V))が書込まれた際には、等価抵抗49を経由してTFT電極27の等価入力容量45には信号電圧として一旦はVhが書込まれ、その後に容量制御線11とTFT電極ソース制御線12に同時に0(V)が書込まれた際には、等価抵抗49を経由してTFT電極27の等価入力容量45には再び0(V)が書込まれることが容易に説明できる。

【0027】

なお、前述したように、容量制御線11とTFT電極ソース制御線12を同時に操作する代わりに、容量制御線11から少し遅れてTFT電極ソース制御線12を操作するようにしてもよい。

ここで信号蓄積容量4に書き込まれるHighレベルの信号電圧は、高い電圧である方が、TFT電極書込みトランジスタ3によるTFT電極27の等価入力容量45への書込み動作がより高速化できるという長所がある。しかしその一方で、画像信号電圧書込み回路14から信号線6にHighレベルの信号電圧を書込む際の消費電力が上昇するという問題が生じる。

また、TFT電極27に0(V)が書込まれた後にはTFT電極27がターンオンしないようにTFT電極ソース制御線12には中間電圧Vmが入力されるが、TFT電極27の電圧は信号蓄積容量4に書き込まれるHighレベルの信号電圧に対して、実際には(H−Vth)の電圧までリークしてしまう。このことからも、Highレベルの信号電圧をあまり大きな電圧に設定するのは好ましくなく、7(V)から5(V)以下が適当である。

【0028】

次に、図2示す画素周辺回路の動作について説明する。

前述の(時刻(t1)まで)に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6には画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施例は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM(Pulse Width Modulation)駆動とサブフレーム毎に発光色を変えるフィールドシーケンシャル駆動を同時に行う。

このため、画像信号電圧書込み回路14から信号線6に書込まれる画像信号電圧は、例えば、0(V)と5(V)の2値の電圧であり、これによって各画素に設けられたTFT電極27に印加される制御信号電圧を制御する。

なお白表示時と黒表示時にそれぞれ5(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的としたシャッタ電極制御線7の印加電圧の値によって制御されることは既に述べたとおりである。またグローバル制御線8、容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12は、制御電極駆動回路16によって前述のように駆動制御される。

【0029】

次に、図3示すシャッタ電極26近傍構造の動作について説明する。

前述のようにシャッタ電極26は、TFT電極27とグローバル電極25のいずれかに静電引力で引き込まれて安定する。

ここでシャッタ電極26がグローバル電極25側に引き込まれた場合には、シャッタ電極26は反射膜23及び黒色膜24の開口上でその位置が安定する。従って光源42から射出されて導光板22を伝播した光41は開口から射出されてもシャッタ電極26で反射されることで再び導光板22に戻されてしまうため、画素は非発光状態として観測される。

またシャッタ電極26がTFT電極27側に引き込まれた場合には、シャッタ電極26は反射膜23及び黒色膜24の遮光上でその位置が安定する。従って光源42から射出されて導光板22を伝播した光41はシャッタ電極26に遮られることなく開口から射出されるため、画素は発光状態として観測される。

本実施例においてはグローバル電極25側にシャッタ電極26が引き寄せられた場合をシャッタ閉として設計したが、TFT電極27側をシャッタ閉とすることもできる。但しシャッタの開閉は、閉じる方が不十分な場合の画質劣化の方が、シャッタ開が不十分な場合の画質劣化よりも厳しいので、常に低インピーダンスで制御されるグローバル電極25側をシャッタ閉とした方が、画質劣化を回避して歩留りを上げられるという効果が有る。

なお本実施例においては、走査スイッチ5及びTFT電極書込みトランジスタ3のオンする期間は、それぞれ当該画素が走査線10によって選択された期間及びTFT電極27への制御信号電圧書込み期間に限定される。これによって、これらの多結晶シリコン薄膜トランジスタのオン期間が長時間継続することに起因するしきい値電圧のシフトを、十分に回避することが可能であるという特長も有する。

【0030】

[実施例2]

図8は、本発明の実施例2の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

以下、図8を用いて、本実施例2の可動シャッタ方式の画像表示装置について説明する。

本実施例2に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は基本的には既に説明した実施例1のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

図8に示す画素50は、図1に示す前述の実施例1の画素と同様である。しかし走査スイッチ5のゲートに接続された走査線10は、行方向に隣接する画素間で共通である。また同様に容量制御線11、シャッタ電極制御線7、TFT電極ソース制御線12も、走査線10とは別の組合せで、行方向に隣接する画素間で共通に設けられている。更に信号線(51,52)は2本がペアで設けられており、同一の走査線10に接続された隣接画素間の走査スイッチ5は、それぞれ異なる信号線(51,52)に接続されている。

本実施例2の動作は、隣接する2画素への信号蓄積容量4への信号電圧の書込みを、一回の走査線10の走査で行う点と、画像信号電圧書込み回路14が、2本の信号線(51,52)に同時に信号電圧を書込む点を除けば、前述の実施例1の動作と同様であるため、ここでは動作の説明は省略する。

【0031】

サブフィールド毎に時間重みを持たせて発光を制御するPWM(Pulse Width Modulation)駆動とフィールドシーケンシャル駆動を同時に行う場合には、特に列方向の画素数が大きいディスプレイでは走査線10の走査速度が大きくなるという課題があるが、本実施例2ではこのように隣接画素への信号電圧の書込みを一回の走査線10の走査で行うことができるため、走査回路15による走査線10の走査周波数を1/2に半減することができる。

なお信号蓄積容量4への信号電圧の書込みに際しては、容量制御線11の電圧が安定していることが必要である。しかしながら一本の走査線10による2行分の画素の信号電圧書込みの際に、これら2行分の信号蓄積容量4が同じ容量制御線11に接続していると、容量制御線11の変動量が2倍になってしまう。そこで本実施例では、一本の走査線10による2行分の画素の信号電圧書込みの際に同時に書込まれる信号蓄積容量4は、それぞれ異なる容量制御線11に接続させ、このような問題の回避を図っている。

【0032】

[実施例3]

図9は、本発明の実施例3の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

以下、図9を用いて、本実施例3について説明する。

本実施例3に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は基本的には既に説明した前述の実施例1のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

図9に示す画素60の左半分は、図1に示す実施例1の画素13と同様である。しかし実施例1では双極性シャッタ1の二つある一方の制御電極であるグローバル電極はグローバル制御線8に接続されていたが、本実施例3ではグローバル電極もTFT電極と同様の構造を有している。

即ち、新たに第2信号線62が設けられており、第2信号線62と第2信号蓄積容量64とは第2走査スイッチ65で接続されている。第2信号蓄積容量64は更にグローバル電極書込みトランジスタ63のゲートに接続されており、グローバル電極書込みトランジスタ63のドレインはグローバル電極に接続されている。

図9に示すように、走査スイッチ5と第2走査スイッチ65のゲートは走査線10に、信号蓄積容量4の他端と第2信号蓄積容量64の他端はTFT電極ソース制御線12に、TFT電極書込みトランジスタ3のソースとグローバル電極書込みトランジスタ63のソースはTFT電極ソース制御線12に接続されている。

本実施例3の動作は、第2信号線62には信号線6に対して逆極性の信号電圧が印加されることと、グローバル電極もTFT電極と同一のタイミングで制御されることとを除けば、実施例1の動作と同様であるため、ここでは動作の説明は省略する。

本実施例3においては、グローバル電極もTFT電極と同一のタイミングで制御されるため、図4、図5に記載した時刻(t6)のタイミングで電極への書込み制御を終了することができ、発光に用いることのできる時間をより長くすることができるという長所がある。

これによって、本実施例はより発光時間を長くできるため、高輝度化に有利である。またTFT電極とグローバル電極に入力される制御信号が必ず相補的になるため、シャッタ電極26をノイズ等に対してより安定的に動作させることが可能である。なお、前述の実施例2は、本実施例にも適用可能であることは言うまでもない。

【0033】

[実施例4]

図10は、本発明の実施例4の可動シャッタ方式の画像表示装置の画素回路を示す回路図である。

図11は、本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ:シャッタ=高電圧)である。

図12は、本発明の実施例4の可動シャッタ方式の画像表示装置の動作タイミングチャート(ポラリティ反転:シャッタ=低電圧)である。

以下、図10〜図12を用いて、本発明の実施例4について、その構成および動作を順次説明する。

まず、図10を用いて本実施例4の画素回路について説明する。

図10に示すように、各画素70には信号線6が設けられており、信号線6と信号書込み容量71とは走査スイッチ5で接続されている。信号書込み容量71は更に信号蓄積容量4と信号転送スイッチ73で接続されている。信号蓄積容量4はTFT電極書込みトランジスタ3のゲートに接続されており、TFT電極書込みトランジスタ3のドレインは双極性シャッタ1の二つある一方の制御電極であるTFT電極に接続されている。双極性シャッタ1の他方の制御電極であるグローバル電極は、グローバル制御線8に接続され、また双極性シャッタ1のシャッタ電極は、シャッタ電極制御線7に接続されている。

なお、信号蓄積容量4の他端は容量制御線11に接続されており、TFT電極書込みトランジスタ3のソースはTFT電極ソース制御線12に、走査スイッチ5のゲートは走査線10に接続されている。また信号転送スイッチ73のゲートはアップデート線74に、信号書込み容量71の他端は容量接地線72に接続されている。

本実施例4の画素周辺回路は、アップデート線74が制御電極駆動回路16に接続されていること、容量接地線72が接地されていることを除けば、前述の実施例1と同様であるため、その説明は省略する。また画素部断面構造に関しても同様である。

【0034】

次に、図11、図12を用いて、本実施例4の画素回路の動作を説明する。

本実施例4の画素回路の動作は、基本的には、前述の実施例1の動作と同様である。前述の実施例1と比較した際の本実施例4の動作における差異は、時刻(t1)から時刻(t2)までの期間にアップデート線74が一度ターンオンし、信号書込み容量71に書込まれていた信号電圧を信号蓄積容量4に転送する期間が設けられていることと、走査線10の走査が、時刻(t2)から開始されることである。

本実施例においては信号線6からの信号書込みを行う信号書込み容量71と、TFT電極書込みトランジスタ3の駆動を担う信号蓄積容量4が分離しているため、TFT電極書込みトランジスタ3の駆動と走査線10の走査を並行して行うことができる。

本実施例では、これによって、走査回路15による走査線10の走査周波数を低減することができるため、走査回路15の駆動マージンを増加させ、歩留りを向上させることができる。なお、前述の実施例2は、本実施例にも適用可能であることは言うまでもない。

【0035】

前述の実施例1ないし実施例4に開示した技術は、本発明の趣旨を損なわない範囲で、様々な変更が可能である。

前述の実施例1ないし実施例4では、ガラス基板39上の走査スイッチ5とTFT電極書込みトランジスタ3をn型の多結晶シリコン薄膜トランジスタで設けているが、ガラス基板39に変えて耐熱プラスチック基板等を用いることで基板に曲げに対するフレキシビリティを持たせることが可能である。

また、n型の多結晶シリコン薄膜トランジスタに変えて、p型の多結晶シリコン薄膜トランジスタや、結晶化が不要なためより低コストプロセスの適用が可能なアモルファスシリコン薄膜トランジスタを用いることもできる。

なお、p型薄膜トランジスタを用いた際には、これらに印加する電圧関係の正負を逆にする必要があることは言うまでも無い。

或いはまた、n型の多結晶シリコン薄膜トランジスタに変えて、InGaZnOに代表されるアモルファス酸化物薄膜トランジスタを用いることによって、画像信号電圧の振幅を5V以下に下げて低消費電力化を図りながら、かつ多結晶シリコン薄膜トランジスタと比較してプロセス装置コストを低減することができる。

【0036】

[実施例5]

図13は、本発明の実施例5の可動シャッタ方式の画像表示装置を使用するインターネット画像表示装置の概略構成を示すブロック図である。

以下、図13を用いて、本発明の実施例5について説明する。

無線インターフェース(I/F)回路152には、圧縮された画像データ等が外部から無線データとして入力し、無線I/F回路152の出力はI/O(Input/Output)回路153を介してデータバス158に接続される。

データバス158には、この他にマイクロプロセサ(MPU)154、表示パネルコントローラ156、フレームメモリ157等が接続されている。

また、表示パネルコントローラ156の出力は機械的シャッタを用いた表示装置151に入力している。また、インターネット画像表示装置150には、更に、電源159が設けられている。

なおここで機械的シャッタを用いた表示装置151は、先に延べた実施例1と同一の構成および動作を有しているので、その内部の構成及び動作の記載はここでは省略する。

以下、本実施例5の動作について説明する。

始めに、無線I/F回路152は命令に応じて圧縮された画像データを外部から取り込み、この画像データをI/O回路153を介してマイクロプロセサ154及びフレームメモリ157に転送する。

マイクロプロセサ154はユーザからの命令操作を受けて、必要に応じてインターネット画像表示装置150全体を駆動し、圧縮された画像データのデコードや信号処理、情報表示を行う。ここで信号処理された画像データは、フレームメモリ157に一時的に蓄積が可能である。

【0037】

ここでマイクロプロセサ154が表示命令を出した場合には、その指示に従ってフレームメモリ157から表示パネルコントローラ156を介して表示装置151に画像データが入力され、表示装置151は入力された画像データをリアルタイムで表示する。

このとき表示パネルコントローラ156は、同時に画像を表示するために必要な所定のタイミングパルスを出力制御する。

なお、表示装置151がこれらの信号を用いて、入力された画像データをリアルタイムで表示することに関しては、前述の実施例1の説明で述べたとおりである。なおここで電源159には二次電池が含まれており、インターネット画像表示装置150全体を駆動する電力を供給する。

本実施例によれば、高画質表示が可能であり、かつ消費電力の少ないインターネット画像表示装置150を低コストで提供することができる。

なお、本実施例では、画像表示デバイスとして、前述の実施例1で説明した表示装置151を用いたが、これ以外にその他の実施例に記載されたような種々の表示装置を用いることが可能であることは明らかである。

但しこの場合は表示パネルコントローラ156の出力するタイミングパルスには、必要に応じて若干の変更が必要になることは言うまでもない。

【0038】

以上説明したように、本実施例によれば、低消費電力でありながら高コントラストで色再現性が良いといった、機械的シャッタを用いた従来の可動シャッタ方式の画像表示装置の利点である高画質性能を維持しながら、更にカスコードトランジスタが必要でなく、画素トランジスタの信頼性を確保することができるため、高精細化と高信頼性化の両立が可能となる。

具体的には、TFT電極へ制御電圧の書込みを行うTFT電極書込みトランジスタは、ゲートがターンオンする際には常にソース・ドレイン間に高電圧が印加されることがないため、カスコードトランジスタのような対策をせずとも、信頼性上の問題を回避することができる。

このように、本実施例によれば、特にディスプレイの高画質化と低消費電力化、かつ高精細化と高信頼化の両立を図ることができる。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【符号の説明】

【0039】

1 双極性シャッタ

3 TFT電極書込みトランジスタ

4,204 信号蓄積容量

5,205 走査スイッチ

6,51,52,206 信号線

7 シャッタ電極制御線

8 グローバル制御線

10,210 走査線

11 容量制御線

12 TFT電極ソース制御線

13,50,60,70,213 画素

14 画像信号電圧書込み回路

15 走査回路

16 制御電極駆動回路

21,23 反射膜

22 導光板

24 黒色膜

25 グローバル電極

26 シャッタ電極

27 TFT電極

30,32 高濃度n型不純物をドープした多結晶シリコン薄膜

31 多結晶シリコン薄膜

33 ゲート絶縁膜

34 絶縁保護膜

35 ゲート電極

37 ソース電極

36 ドレイン電極

38 保護膜

39 ガラス基板

41 光

42 光源

45 等価入力容量

46 等価配線

47 等価ダイオード

48 直流電源

49 等価抵抗

62 第2信号線

63 グローバル電極書込みトランジスタ

64 第2信号蓄積容量

65 第2走査スイッチ

71 信号書込み容量

72 容量接地線

73 信号転送スイッチ

74 アップデート線

150 インターネット画像表示装置

151 表示装置

152 無線インターフェース(I/F)回路

153 I/O(Input/Output)回路

154 マイクロプロセサ(MPU)

156 表示パネルコントローラ

157 フレームメモリ

158 データバス

159 電源

201 双極性シャッタ(Dual actuator shutter assembly)

202,215 pMOSトランジスタ

203,216 nMOSトランジスタ

207 pMOSゲート電圧線

208 正電圧線

209 制御電極電圧線

211 シャッタ電圧線

212 nMOSソース電圧線

217 カスコードゲート電圧線

【特許請求の範囲】

【請求項1】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に画像信号を入力する信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、

前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、

ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有し、

前記第2制御電極には第2制御電圧が入力され、

前記容量制御信号、前記第1制御信号、および、前記第2制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御することを特徴とする表示装置。

【請求項2】

前記各画素に前記容量制御信号を入力する容量制御線と、

前記各画素に前記第1制御信号を入力する第1電極線と、

前記各画素に前記第2制御信号を入力する第2電極線と、

前記機械的シャッタに対して所定の電圧を印加するシャッタ電極線と、

前記信号線に前記画像信号を供給する信号回路と、

前記走査線に前記走査電圧を供給する走査回路と、

前記容量制御線、前記第1電極線、前記第2電極線、および、前記シャッタ電極線に、それぞれ前記容量制御信号、前記第1制御信号、前記第2制御信号、および、所定の電圧を供給する制御電極駆動回路とを備えることを特徴とする請求項1に記載の表示装置。

【請求項3】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に第1画像信号を入力する第1信号線と、

前記各画素に第2画像信号を入力する第2信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記第1画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、

前記第2制御電極に前記第2画像信号に応じた第2制御電圧を入力するための第2制御電圧印加回路とを有し、

前記第1制御電圧印加回路は、電流端子の一端が前記第1信号線に接続され、ゲートが前記走査線に接続される第1入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第1入力トランジスタの電流端子の他端に接続され、前記第1入力トランジスタで取り込んだ電圧を保持する第1保持容量と、

ゲートが前記第1保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第1トランジスタとを有し、

前記第2制御電極電圧印加回路は、電流端子の一端が前記第2信号線に接続され、ゲートが前記走査線に接続される第2入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第2入力トランジスタの電流端子の他端に接続され、前記第2入力トランジスタで取り込んだ電圧を保持する第2保持容量と、

ゲートが前記第2保持容量の一端に接続され、電流端子の他端が第2制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第2トランジスタとを有し、

前記容量制御信号、および、前記制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御することを特徴とする表示装置。

【請求項4】

前記各画素に前記容量制御信号を入力する容量制御線と、

前記各画素に前記制御信号を入力する電極線と、

前記機械的シャッタに対して所定の電圧を印加するシャッタ電極線と、

前記信号線に前記第1画像信号と前記第2画像信号を供給する信号回路と、

前記走査線に前記走査電圧を供給する走査回路と、

前記容量制御線、前記電極線、および、前記シャッタ電極線に、それぞれ前記容量制御信号、前記制御信号、および、所定の電圧を供給する制御電極駆動回路とを備えることを特徴とする請求項3に記載の表示装置。

【請求項5】

前記第1トランジスタの電流端子の他端と前記第2トランジスタの電流端子の他端は、それぞれ電極線に接続されていることを特徴とする請求項4に記載の表示装置。

【請求項6】

前記第1保持容量の他端と前記第2保持容量の他端は、それぞれ前記容量制御線に接続されていることを特徴とする請求項3に記載の表示装置。

【請求項7】

面状の光源と、

透明基板と、

前記透明基板上に設けられる遮光膜と、

前記遮光膜は、各画素に対応する光学的開口領域を有し、前記面状の光源から射出された光に対して、前記光学的開口領域以外の領域を遮光し、

前記機械的シャッタは、前記透明基板上で、光学的開口領域に対応して設けられていることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項8】

前記各トランジスタは、半導体層が多結晶シリコン薄膜で構成されるトランジスタであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項9】

前記各トランジスタは、半導体層がアモルファスシリコン薄膜で構成されるトランジスタであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項10】

前記各トランジスタは、半導体層が酸化物薄膜を用いて構成されるトランジスタであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項11】

前記シャッタ電圧印加回路は、所定のタイミングで高電圧印加状態と低電圧印加状態を切替えることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項12】

前記信号線は並行に2本ずつ配置されており、

前記信号線の延長方向に隣接した2個の画素の入力トランジスタのゲートは共通に接続され、かつこれらの2個の画素の入力トランジスタの電流端子の一端は並行に2本ずつに配置されたそれぞれの信号線に接続されていることを特徴とする請求項1に記載の表示装置。

【請求項13】

前記信号線の延長方向に隣接した2個の画素の保持容量の他端は共通に接続され、かつこれらの2個の画素の入力トランジスタのゲートが共通に接続されないことを特徴とする請求項12に記載の表示装置。

【請求項14】

前記第1信号線、および前記第2信号線は並行に2本ずつ配置されており、

前記第1信号線の延長方向に隣接した2個の画素の第1入力トランジスタのゲートは共通に接続され、かつこれらの2個の画素の第1入力トランジスタの電流端子の一端は並行に2本ずつに配置されたそれぞれの第1信号線に接続されており、

前記第2信号線の延長方向に隣接した2個の画素の第2入力トランジスタのゲートは共通に接続され、かつこれらの2個の画素の第2入力トランジスタの電流端子の一端は並行に2本ずつに配置されたそれぞれの第2信号線に接続されていることを特徴とする請求項3に記載の表示装置。

【請求項15】

前記第1信号線の延長方向に隣接した2個の画素の第1保持容量の他端は共通に接続され、かつこれらの2個の画素の第1入力トランジスタのゲートが共通に接続されず、

前記第2信号線の延長方向に隣接した2個の画素の第2保持容量の他端は共通に接続され、かつこれらの2個の画素の第2入力トランジスタのゲートが共通に接続されないことを特徴とする請求項14に記載の表示装置。

【請求項16】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記入力トランジスタの電流端子の他端と前記保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記保持容量の一端に接続される転送トランジスタと、

前記入力トランジスタの電流端子の他端に一端が接続された走査容量を有することを特徴とする請求項1に記載の表示装置。

【請求項17】

前記走査容量の他端が接地されていることを特徴とする請求項16に記載の表示装置。

【請求項18】

前記各画素における前記保持容量の他端に前記容量制御信号と、前記第1トランジスタの電流端子の他端に前記第2制御信号を入力する前に、前記転送トランジスタがオンとなることを特徴とする請求項16に記載の表示装置。

【請求項19】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記第1入力トランジスタの電流端子の他端と前記第1保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第1入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第1保持容量の一端に接続される第1転送トランジスタと、

前記第1入力トランジスタの電流端子の他端に一端が接続された第1走査容量を有し、 前記第2制御電極電圧印加回路は、前記第2入力トランジスタの電流端子の他端と前記第2保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第2入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第2保持容量の一端に接続される第2転送トランジスタと、

前記第2入力トランジスタの電流端子の他端に一端が接続された第2走査容量を有することを特徴とする請求項3に記載の表示装置。

【請求項20】

前記第1走査容量と前記第2走査容量の他端が接地されていることを特徴とする請求項19に記載の表示装置。

【請求項21】

前記各画素における前記第1保持容量と前記第2保持容量の他端に前記容量制御信号と、前記第1トランジスタの電流端子の他端と前記第2トランジスタの電流端子の他端に前記制御信号を入力する前に、前記第1転送トランジスタと前記第2転送トランジスタとがオンとなることを特徴とする請求項19に記載の表示装置。

【請求項22】

前記各トランジスタは、n型のトランジスタであり、

前記第2電圧レベルは、第1電圧レベルよりも高電位の電圧レベルであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項23】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に画像信号を入力する信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路を有し、

前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、

ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有し、

前記第2制御電極には第2制御電圧が入力され、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置の駆動方法であって、

1サブフレーム期間において時刻t1から時刻t6の順に時間が経過するものとするとき、1サブフレーム期間内において、前記機械的シャッタに対して第2電圧レベルの電圧を印加し、

前記全ての画素の保持容量に前記画像信号に対応する電圧が保持した後の時刻t1において、前記第2制御信号を、第1電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t6において、第2電圧レベルの電圧から第1電圧レベルの電圧に変化させることにより、前記第2制御電極の電圧を、時刻t1において第2電圧レベルの電圧に、時刻t6において第1電圧レベルの電圧に変化させ、

前記容量制御信号を、時刻t2において第1電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t4において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させるともに、前記第1制御信号を、時刻t3において中間電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t4において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させ、時刻t5において第1電圧レベルの電圧から中間電圧レベルの電圧に変化させることにより、前記第1制御電極の電圧を、時刻t3において前記第1トランジスタをダイオードとして機能させることにより第2電圧レベルの電圧に変化させ、時刻t4において前記保持容量に保持された電圧に基づき前記第1トランジスタがオンの場合に第1電圧レベルの電圧に変化させ、時刻t4において前記保持容量に保持された電圧に基づき前記第1トランジスタがオフの場合に第2電圧レベルの電圧を維持させることを特徴とする表示装置の駆動方法。

【請求項24】

前記1サブフレーム期間内に、前記機械的シャッタに対して第2電圧レベルの電圧を印加する代わりに、前記機械的シャッタに対して第1電圧レベルの電圧を印加し、

時刻t1において、前記第2制御信号を、第2電圧レベルの電圧から第1電圧レベルの電圧に変化させ、時刻t6において、第1電圧レベルの電圧から第2電圧レベルの電圧に変化させることにより、前記第2制御電極の電圧を、時刻t1において第1電圧レベルの電圧となし、時刻t6において第2電圧レベルの電圧とすることを特徴とする請求項23に記載の表示装置の駆動方法。

【請求項25】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に第1画像信号を入力する第1信号線と、

前記各画素に第2画像信号を入力する第2信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記第1画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、

前記第2制御電極に前記第2画像信号に応じた第2制御電圧を入力するための第2制御電圧印加回路とを有し、

前記第1制御電圧印加回路は、電流端子の一端が前記第1信号線に接続され、ゲートが前記走査線に接続される第1入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第1入力トランジスタの電流端子の他端に接続され、前記第1入力トランジスタで取り込んだ電圧を保持する第1保持容量と、

ゲートが前記第1保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第1トランジスタとを有し、

前記第2制御電極電圧印加回路は、電流端子の一端が前記第2信号線に接続され、ゲートが前記走査線に接続される第2入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第2入力トランジスタの電流端子の他端に接続され、前記第2入力トランジスタで取り込んだ電圧を保持する第2保持容量と、

ゲートが前記第2保持容量の一端に接続され、電流端子の他端が第2制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第2トランジスタとを有し、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置の駆動方法であって、

1サブフレーム期間において時刻t1から時刻t4の順に時間が経過するものとするとき、1サブフレーム期間内において、前記機械的シャッタに対して第2電圧レベルの電圧を印加し、

前記全ての画素の保持容量に前記画像信号に対応する電圧が保持した後の時刻t1において、前記容量制御信号を、第1電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t3において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させるとともに、前記制御信号を時刻t2において中間電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t3において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させ、時刻t4において、第1電圧レベルの電圧から中間電圧レベルの電圧に変化させることにより、前記第1制御電極の電圧を、時刻t2において前記第1トランジスタをダイオードとして機能させることにより第2電圧レベルの電圧に変化させ、時刻t3において前記第1保持容量に保持された電圧に基づき前記第1トランジスタがオンの場合に第1電圧レベルの電圧に変化させ、時刻t3において前記第1保持容量に保持された電圧に基づき前記第1トランジスタがオフの場合に第2電圧レベルの電圧を維持させ、

前記第2制御電極の電圧を、時刻t2において前記第2トランジスタをダイオードとして機能させることにより第2電圧レベルの電圧に変化させ、時刻t3において前記第2保持容量に保持された電圧に基づき前記第2トランジスタがオンの場合に第1電圧レベルの電圧に変化させ、時刻t3において前記第2保持容量に保持された電圧に基づき前記第2トランジスタがオフの場合に第2電圧レベルの電圧を維持させることを特徴とする表示装置の駆動方法。

【請求項26】

前記1サブフレーム期間内に、前記機械的シャッタに対して第2電圧レベルの電圧を印加する代わりに、前記機械的シャッタに対して第1電圧レベルの電圧を印加することを特徴とする請求項25に記載の表示装置の駆動方法。

【請求項27】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記入力トランジスタの電流端子の他端と前記保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が 前記入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記保持容量の一端に接続される転送トランジスタと、

前記入力トランジスタの電流端子の他端に一端が接続された走査容量を有し、

時刻t1以前に前記転送トランジスタをオンとして、前記走査容量に保持された電圧を前記保持容量に一括して転送させることを特徴とする請求項23または請求項24に記載の表示装置の駆動方法。

【請求項28】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記第1入力トランジスタの電流端子の他端と前記第1保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第1入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第1保持容量の一端に接続される第1転送トランジスタと、

前記第1入力トランジスタの電流端子の他端に一端が接続された第1走査容量を有し、 前記第2制御電極電圧印加回路は、前記第2入力トランジスタの電流端子の他端と前記第2保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第2入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第2保持容量の一端に接続される第2転送トランジスタと、

前記第2入力トランジスタの電流端子の他端に一端が接続された第2走査容量を有し、

時刻t1以前に前記第1転送トランジスタをオンとして、前記第1走査容量に保持された電圧を前記第1保持容量に一括して転送させ、

時刻t1以前に前記第2転送トランジスタをオンとして、前記第2走査容量に保持された電圧を前記第2保持容量に一括して転送させることを特徴とする請求項25または請求項26に記載の表示装置の駆動方法。

【請求項1】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に画像信号を入力する信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、

前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、

ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有し、

前記第2制御電極には第2制御電圧が入力され、

前記容量制御信号、前記第1制御信号、および、前記第2制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御することを特徴とする表示装置。

【請求項2】

前記各画素に前記容量制御信号を入力する容量制御線と、

前記各画素に前記第1制御信号を入力する第1電極線と、

前記各画素に前記第2制御信号を入力する第2電極線と、

前記機械的シャッタに対して所定の電圧を印加するシャッタ電極線と、

前記信号線に前記画像信号を供給する信号回路と、

前記走査線に前記走査電圧を供給する走査回路と、

前記容量制御線、前記第1電極線、前記第2電極線、および、前記シャッタ電極線に、それぞれ前記容量制御信号、前記第1制御信号、前記第2制御信号、および、所定の電圧を供給する制御電極駆動回路とを備えることを特徴とする請求項1に記載の表示装置。

【請求項3】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に第1画像信号を入力する第1信号線と、

前記各画素に第2画像信号を入力する第2信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記第1画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、

前記第2制御電極に前記第2画像信号に応じた第2制御電圧を入力するための第2制御電圧印加回路とを有し、

前記第1制御電圧印加回路は、電流端子の一端が前記第1信号線に接続され、ゲートが前記走査線に接続される第1入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第1入力トランジスタの電流端子の他端に接続され、前記第1入力トランジスタで取り込んだ電圧を保持する第1保持容量と、

ゲートが前記第1保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第1トランジスタとを有し、

前記第2制御電極電圧印加回路は、電流端子の一端が前記第2信号線に接続され、ゲートが前記走査線に接続される第2入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第2入力トランジスタの電流端子の他端に接続され、前記第2入力トランジスタで取り込んだ電圧を保持する第2保持容量と、

ゲートが前記第2保持容量の一端に接続され、電流端子の他端が第2制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第2トランジスタとを有し、

前記容量制御信号、および、前記制御信号の電圧レベルを所定のタイミングで変更させて、前記機械的シャッタの位置を制御することを特徴とする表示装置。

【請求項4】

前記各画素に前記容量制御信号を入力する容量制御線と、

前記各画素に前記制御信号を入力する電極線と、

前記機械的シャッタに対して所定の電圧を印加するシャッタ電極線と、

前記信号線に前記第1画像信号と前記第2画像信号を供給する信号回路と、

前記走査線に前記走査電圧を供給する走査回路と、

前記容量制御線、前記電極線、および、前記シャッタ電極線に、それぞれ前記容量制御信号、前記制御信号、および、所定の電圧を供給する制御電極駆動回路とを備えることを特徴とする請求項3に記載の表示装置。

【請求項5】

前記第1トランジスタの電流端子の他端と前記第2トランジスタの電流端子の他端は、それぞれ電極線に接続されていることを特徴とする請求項4に記載の表示装置。

【請求項6】

前記第1保持容量の他端と前記第2保持容量の他端は、それぞれ前記容量制御線に接続されていることを特徴とする請求項3に記載の表示装置。

【請求項7】

面状の光源と、

透明基板と、

前記透明基板上に設けられる遮光膜と、

前記遮光膜は、各画素に対応する光学的開口領域を有し、前記面状の光源から射出された光に対して、前記光学的開口領域以外の領域を遮光し、

前記機械的シャッタは、前記透明基板上で、光学的開口領域に対応して設けられていることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項8】

前記各トランジスタは、半導体層が多結晶シリコン薄膜で構成されるトランジスタであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項9】

前記各トランジスタは、半導体層がアモルファスシリコン薄膜で構成されるトランジスタであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項10】

前記各トランジスタは、半導体層が酸化物薄膜を用いて構成されるトランジスタであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項11】

前記シャッタ電圧印加回路は、所定のタイミングで高電圧印加状態と低電圧印加状態を切替えることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項12】

前記信号線は並行に2本ずつ配置されており、

前記信号線の延長方向に隣接した2個の画素の入力トランジスタのゲートは共通に接続され、かつこれらの2個の画素の入力トランジスタの電流端子の一端は並行に2本ずつに配置されたそれぞれの信号線に接続されていることを特徴とする請求項1に記載の表示装置。

【請求項13】

前記信号線の延長方向に隣接した2個の画素の保持容量の他端は共通に接続され、かつこれらの2個の画素の入力トランジスタのゲートが共通に接続されないことを特徴とする請求項12に記載の表示装置。

【請求項14】

前記第1信号線、および前記第2信号線は並行に2本ずつ配置されており、

前記第1信号線の延長方向に隣接した2個の画素の第1入力トランジスタのゲートは共通に接続され、かつこれらの2個の画素の第1入力トランジスタの電流端子の一端は並行に2本ずつに配置されたそれぞれの第1信号線に接続されており、

前記第2信号線の延長方向に隣接した2個の画素の第2入力トランジスタのゲートは共通に接続され、かつこれらの2個の画素の第2入力トランジスタの電流端子の一端は並行に2本ずつに配置されたそれぞれの第2信号線に接続されていることを特徴とする請求項3に記載の表示装置。

【請求項15】

前記第1信号線の延長方向に隣接した2個の画素の第1保持容量の他端は共通に接続され、かつこれらの2個の画素の第1入力トランジスタのゲートが共通に接続されず、

前記第2信号線の延長方向に隣接した2個の画素の第2保持容量の他端は共通に接続され、かつこれらの2個の画素の第2入力トランジスタのゲートが共通に接続されないことを特徴とする請求項14に記載の表示装置。

【請求項16】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記入力トランジスタの電流端子の他端と前記保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記保持容量の一端に接続される転送トランジスタと、

前記入力トランジスタの電流端子の他端に一端が接続された走査容量を有することを特徴とする請求項1に記載の表示装置。

【請求項17】

前記走査容量の他端が接地されていることを特徴とする請求項16に記載の表示装置。

【請求項18】

前記各画素における前記保持容量の他端に前記容量制御信号と、前記第1トランジスタの電流端子の他端に前記第2制御信号を入力する前に、前記転送トランジスタがオンとなることを特徴とする請求項16に記載の表示装置。

【請求項19】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記第1入力トランジスタの電流端子の他端と前記第1保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第1入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第1保持容量の一端に接続される第1転送トランジスタと、

前記第1入力トランジスタの電流端子の他端に一端が接続された第1走査容量を有し、 前記第2制御電極電圧印加回路は、前記第2入力トランジスタの電流端子の他端と前記第2保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第2入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第2保持容量の一端に接続される第2転送トランジスタと、

前記第2入力トランジスタの電流端子の他端に一端が接続された第2走査容量を有することを特徴とする請求項3に記載の表示装置。

【請求項20】

前記第1走査容量と前記第2走査容量の他端が接地されていることを特徴とする請求項19に記載の表示装置。

【請求項21】

前記各画素における前記第1保持容量と前記第2保持容量の他端に前記容量制御信号と、前記第1トランジスタの電流端子の他端と前記第2トランジスタの電流端子の他端に前記制御信号を入力する前に、前記第1転送トランジスタと前記第2転送トランジスタとがオンとなることを特徴とする請求項19に記載の表示装置。

【請求項22】

前記各トランジスタは、n型のトランジスタであり、

前記第2電圧レベルは、第1電圧レベルよりも高電位の電圧レベルであることを特徴とする請求項1または請求項3に記載の表示装置。

【請求項23】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に画像信号を入力する信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路を有し、

前記第1制御電圧印加回路は、電流端子の一端が前記信号線に接続され、ゲートが前記走査線に接続される入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの電流端子の他端に接続され、前記入力トランジスタで取り込んだ電圧を保持する保持容量と、

ゲートが前記保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に第1制御信号が入力される第1トランジスタとを有し、

前記第2制御電極には第2制御電圧が入力され、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置の駆動方法であって、

1サブフレーム期間において時刻t1から時刻t6の順に時間が経過するものとするとき、1サブフレーム期間内において、前記機械的シャッタに対して第2電圧レベルの電圧を印加し、

前記全ての画素の保持容量に前記画像信号に対応する電圧が保持した後の時刻t1において、前記第2制御信号を、第1電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t6において、第2電圧レベルの電圧から第1電圧レベルの電圧に変化させることにより、前記第2制御電極の電圧を、時刻t1において第2電圧レベルの電圧に、時刻t6において第1電圧レベルの電圧に変化させ、

前記容量制御信号を、時刻t2において第1電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t4において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させるともに、前記第1制御信号を、時刻t3において中間電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t4において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させ、時刻t5において第1電圧レベルの電圧から中間電圧レベルの電圧に変化させることにより、前記第1制御電極の電圧を、時刻t3において前記第1トランジスタをダイオードとして機能させることにより第2電圧レベルの電圧に変化させ、時刻t4において前記保持容量に保持された電圧に基づき前記第1トランジスタがオンの場合に第1電圧レベルの電圧に変化させ、時刻t4において前記保持容量に保持された電圧に基づき前記第1トランジスタがオフの場合に第2電圧レベルの電圧を維持させることを特徴とする表示装置の駆動方法。

【請求項24】

前記1サブフレーム期間内に、前記機械的シャッタに対して第2電圧レベルの電圧を印加する代わりに、前記機械的シャッタに対して第1電圧レベルの電圧を印加し、

時刻t1において、前記第2制御信号を、第2電圧レベルの電圧から第1電圧レベルの電圧に変化させ、時刻t6において、第1電圧レベルの電圧から第2電圧レベルの電圧に変化させることにより、前記第2制御電極の電圧を、時刻t1において第1電圧レベルの電圧となし、時刻t6において第2電圧レベルの電圧とすることを特徴とする請求項23に記載の表示装置の駆動方法。

【請求項25】

機械的シャッタをそれぞれ有する複数の画素と、

前記各画素に第1画像信号を入力する第1信号線と、

前記各画素に第2画像信号を入力する第2信号線と、

前記各画素に走査電圧を入力する走査線とを備え、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置であって、

前記各画素は、前記機械的シャッタの位置を電気的に制御する画素回路を有し、

前記画素回路は、前記可動シャッタに対して対に設けられた第1制御電極と第2制御電極と、

前記第1制御電極に前記第1画像信号に応じた第1制御電圧を入力するための第1制御電圧印加回路とを有し、

前記第2制御電極に前記第2画像信号に応じた第2制御電圧を入力するための第2制御電圧印加回路とを有し、

前記第1制御電圧印加回路は、電流端子の一端が前記第1信号線に接続され、ゲートが前記走査線に接続される第1入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第1入力トランジスタの電流端子の他端に接続され、前記第1入力トランジスタで取り込んだ電圧を保持する第1保持容量と、

ゲートが前記第1保持容量の一端に接続され、電流端子の他端が第1制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第1トランジスタとを有し、

前記第2制御電極電圧印加回路は、電流端子の一端が前記第2信号線に接続され、ゲートが前記走査線に接続される第2入力トランジスタと、

他端に容量制御信号が入力されるとともに、一端が前記第2入力トランジスタの電流端子の他端に接続され、前記第2入力トランジスタで取り込んだ電圧を保持する第2保持容量と、

ゲートが前記第2保持容量の一端に接続され、電流端子の他端が第2制御電極に接続されるとともに、電流端子の一端に制御信号が入力される第2トランジスタとを有し、

前記機械的シャッタの位置を電気的に制御して画像表示を行う表示装置の駆動方法であって、

1サブフレーム期間において時刻t1から時刻t4の順に時間が経過するものとするとき、1サブフレーム期間内において、前記機械的シャッタに対して第2電圧レベルの電圧を印加し、

前記全ての画素の保持容量に前記画像信号に対応する電圧が保持した後の時刻t1において、前記容量制御信号を、第1電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t3において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させるとともに、前記制御信号を時刻t2において中間電圧レベルの電圧から第2電圧レベルの電圧に変化させ、時刻t3において第2電圧レベルの電圧から第1電圧レベルの電圧に変化させ、時刻t4において、第1電圧レベルの電圧から中間電圧レベルの電圧に変化させることにより、前記第1制御電極の電圧を、時刻t2において前記第1トランジスタをダイオードとして機能させることにより第2電圧レベルの電圧に変化させ、時刻t3において前記第1保持容量に保持された電圧に基づき前記第1トランジスタがオンの場合に第1電圧レベルの電圧に変化させ、時刻t3において前記第1保持容量に保持された電圧に基づき前記第1トランジスタがオフの場合に第2電圧レベルの電圧を維持させ、

前記第2制御電極の電圧を、時刻t2において前記第2トランジスタをダイオードとして機能させることにより第2電圧レベルの電圧に変化させ、時刻t3において前記第2保持容量に保持された電圧に基づき前記第2トランジスタがオンの場合に第1電圧レベルの電圧に変化させ、時刻t3において前記第2保持容量に保持された電圧に基づき前記第2トランジスタがオフの場合に第2電圧レベルの電圧を維持させることを特徴とする表示装置の駆動方法。

【請求項26】

前記1サブフレーム期間内に、前記機械的シャッタに対して第2電圧レベルの電圧を印加する代わりに、前記機械的シャッタに対して第1電圧レベルの電圧を印加することを特徴とする請求項25に記載の表示装置の駆動方法。

【請求項27】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記入力トランジスタの電流端子の他端と前記保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が 前記入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記保持容量の一端に接続される転送トランジスタと、

前記入力トランジスタの電流端子の他端に一端が接続された走査容量を有し、

時刻t1以前に前記転送トランジスタをオンとして、前記走査容量に保持された電圧を前記保持容量に一括して転送させることを特徴とする請求項23または請求項24に記載の表示装置の駆動方法。

【請求項28】

アップデート線を有し、

前記第1制御電極電圧印加回路は、前記第1入力トランジスタの電流端子の他端と前記第1保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第1入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第1保持容量の一端に接続される第1転送トランジスタと、

前記第1入力トランジスタの電流端子の他端に一端が接続された第1走査容量を有し、 前記第2制御電極電圧印加回路は、前記第2入力トランジスタの電流端子の他端と前記第2保持容量の一端との間に、ゲートがアップデート線に接続されるとともに、電流端子の一端が前記第2入力トランジスタの電流端子の他端に接続され、電流端子の他端が前記第2保持容量の一端に接続される第2転送トランジスタと、

前記第2入力トランジスタの電流端子の他端に一端が接続された第2走査容量を有し、

時刻t1以前に前記第1転送トランジスタをオンとして、前記第1走査容量に保持された電圧を前記第1保持容量に一括して転送させ、

時刻t1以前に前記第2転送トランジスタをオンとして、前記第2走査容量に保持された電圧を前記第2保持容量に一括して転送させることを特徴とする請求項25または請求項26に記載の表示装置の駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−88510(P2013−88510A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−226844(P2011−226844)

【出願日】平成23年10月14日(2011.10.14)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月14日(2011.10.14)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

[ Back to top ]