表示装置および携帯端末

【課題】画像データを画素に書き込むためのタイミング信号をドライバIC内で容易に生成することのできる表示装置を実現する。

【解決手段】画像データDR、DG、DBがシリアルデータSIに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、シリアルデータSIに、画素に画像データを書き込むか否かを示すフラグD0が付加されており、表示ドライバは、シリアルクロックSCLKのタイミングを用いて、データ信号線ドライバ23の水平期間のタイミング信号SSPを生成する。

【解決手段】画像データDR、DG、DBがシリアルデータSIに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、シリアルデータSIに、画素に画像データを書き込むか否かを示すフラグD0が付加されており、表示ドライバは、シリアルクロックSCLKのタイミングを用いて、データ信号線ドライバ23の水平期間のタイミング信号SSPを生成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置の表示動作に用いるタイミング信号に関するものである。

【背景技術】

【0002】

各画素にメモリ回路(以下、画素メモリと称する)を備え、当該画素メモリに画像データを記憶させることによって、外部から画像データを供給し続けることなく静止画像を低消費電力で表示することができる表示装置が知られている。消費電力の削減には、一度画像データを書き込んだ後は、画素に画像データを供給するためのデータ信号線を画像データで充放電する必要がなくなるので、その充放電に伴う消費電力の削減分と、一度画像データを書き込んだ後は、パネル外部からドライバに画像データを伝送する必要がないので、その伝送に伴う消費電力の削減分とが含まれる。

【0003】

画素メモリとしてはSRAM型のものやDRAM型のものが開発されている。この表示装置では画素電圧がデジタルであるので、クロストークが起こりにくく、表示品位にも優れている。

【0004】

図14に、特許文献1に記載されたこのような画素メモリを備える表示装置の構成を示す。

【0005】

この表示装置は、Xアドレス走査線ドライバ18、デジタルデータドライバ19、およびアナログデータドライバ20を備えており、デジタルデータ画像表示モードとアナログデータ画像表示モードとを使い分けることができる。

【0006】

デジタルデータ画像表示モードについて説明すると、画像データを書き込む画素が接続されているXアドレス信号線4−n(nは自然数)を選択し、対応する第1表示制御線1−nからデジタルデータ信号を、当該画素の第1スイッチ素子8を通して、NAND回路11およびクロックトインバータ素子13によって構成されたデジタルメモリ素子100に書き込む。このとき、表示モード制御線15を通してデジタルメモリ素子100をアクティブにしておく。

【0007】

デジタルメモリ素子100の入力は第2スイッチ素子9に接続されているとともに出力は第3スイッチ素子10に接続されている。従って、デジタルデータ信号のHigh/Lowに応じて第2スイッチ素子9または第3スイッチ素子10のいずれか一方が導通する。第2表示制御線2−nおよび第3表示制御線3の一方には白表示基準電圧、他方には黒表示基準電圧が供給され、第2スイッチ素子9または第3スイッチ素子10のうちの導通したほうのスイッチ素子によって決まる白電圧または黒電圧が、液晶セル6に印加される。再び第1スイッチ素子8が導通して新たなデジタルデータ信号が書き込まれるまで、液晶セル6は、デジタルメモリ素子100が記憶したデジタルデータ信号による表示状態を保持する。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】日本国公開特許公報「特開2003−177717号公報(公開日:2003年6月27日)」

【特許文献2】日本国公開特許公報「特開昭58−23091号公報(公開日:1983年2月10日)」

【特許文献3】日本国公開特許公報「特開2007−286237号公報(公開日:2007年11月1日)」

【発明の概要】

【発明が解決しようとする課題】

【0009】

近年では、液晶表示装置における表示データの伝送のインタフェースは、信号線数の多いパラレル伝送方式のデジタルRGB方式(RGBインタフェース)から、信号線数の少ない高速シリアル伝送方式へと移行しつつある。特に、携帯電話などのモバイル機器では、配線数を減少させて、配線の設置スペースの省略および配線の断線防止を図る目的があるために、シリアル伝送方式は重要な技術となっている。また、差動伝送を行うことで、高速および低消費電力の伝送が達成できる。このようなシリアル伝送では表示データと制御コマンドとは同一バス上を伝送されることとなる。

【0010】

例えば、モバイル機器のアプリケーションプロセッサと周辺装置とのインタフェースである、いわゆるCPUインタフェースに関して共通仕様を定めたMIPI(Mobile Industry Processor Interface)スタンダードなどでは、アプリケーションプロセッサをホスト側として周辺装置の動作を制御する。制御信号を用いる表示駆動装置では、通常表示動作の開始をコマンド制御による指定で行うようになっており、電源起動後にホスト側より表示駆動装置に起動コマンドが送られると、これに沿って画面の表示が開始される。

【0011】

図15に、このような液晶ディスプレイ部にCPUインタフェースを備えた携帯電話における、回路接続構成の概念図を示す。

【0012】

携帯電話101は、液晶表示部102、液晶ドライバ103、アンテナ104、RF回路105、ベースバンドプロセッサ106、および、アプリケーションプロセッサ107を備えている。

【0013】

液晶表示部102は画素がマトリクス状に配置されたものである。各画素にはソースバスラインSL1〜SLnを介してデータ信号が書き込まれる。ソースバスラインSL1〜SLnには液晶ドライバ103からデータ信号を供給される。また、図示しないが、画素にデータ信号を書き込むために、複数の画素からなる各行を選択する走査信号が、液晶ドライバ103からゲートバスラインに順次供給される。

【0014】

液晶ドライバ103は、1チップまたは複数チップからなる、液晶表示部102の表示を駆動する回路であり、タイミングジェネレータや、ソースドライバ、ゲートドライバ、電源回路、メモリといった表示動作に関する各回路部を含んでいる。また、液晶ドライバ103は、ここではアプリケーションプロセッサ107をホストとし、シリアルバスI/F BUSを通して制御されるようになっており、そのインタフェースも内部に含んでいる。

【0015】

アンテナ104は携帯電話101の送受信用のアンテナである。RF回路105は、送受信に伴う高周波信号を処理する。ベースバンドプロセッサ106はRF回路105で復調されたベースバンド信号を処理し、図示しない通話信号処理回路やデータ通信処理回路の動作を制御する。アプリケーションプロセッサ107は、前記液晶ドライバ103や、図示しない動画・音楽・ゲームなどの処理を行う周辺装置を制御する。

【0016】

図16に上記液晶ドライバ103の構成例を示す。

【0017】

液晶ドライバ103内では、シリアルインタフェースバスI/F BUSから制御コマンドおよび表示データをシリアルインタフェース131で受信し、制御コマンドがレジスタ132に書き込まれる。また、その受信タイミングに基づいてタイミングジェネレータ135が、その内部に備えた発振器によりタイミング信号を生成する。当該タイミング信号に基づいて、シリアルインタフェース131からシフトレジスタ133、ソース駆動回路134へと順に表示データが送られ、ソースバスラインSLにデータ信号が供給される。

【0018】

しかしながら、上述したCPUインタフェースを備えた液晶ドライバでは、RGBインタフェースのように垂直同期信号や水平同期信号が外部から供給される代わりに、シリアル伝送された制御コマンドおよび表示データを基に、タイミングジェネレータが自走式による発振器によりタイミング信号を改めて生成し、ドライバ各部や液晶表示部を駆動している。前述した画素メモリを備えた画素では、静止画表示を行うときに表示データをメモリ回路に書き込んだ後は、アプリケーションプロセッサからのデータ供給が停止して消費電力を削減しているため、液晶ドライバ内部で独自にタイミング信号を生成することが重要である。しかし、小型、高速、および、低消費電力という長所を備えたシリアル伝送を採用しているものの、タイミングジェネレータで生成するクロック信号を基に画像データを画素に書き込むためのタイミング信号を生成しなければならない。

【0019】

このように、従来のCPUインタフェース方式では、画像データを書き込むためのタイミング信号をCPUから供給される信号を基にして、ドライバIC内でわざわざ発振器などを用いて生成する必要があり、液晶ドライバの回路規模の縮小化が妨げられるという問題があった。

【0020】

本発明は、上記従来の問題点に鑑みなされたものであり、その目的は、画像データを画素に書き込むためのタイミング信号をドライバIC内で容易に生成することのできる表示装置およびそれを備えた携帯端末を実現することにある。

【課題を解決するための手段】

【0021】

本発明の表示装置は、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、フレーム毎に、上記シリアルデータに、当該フレームにおいて画素に上記画像データを書き込むか否かを示す第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、上記第1フラグが画素に上記画像データを書き込むことを示す場合、当該フレームにおいて第1論理値から第2論理値に変化するモード信号を生成し、上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、上記モード信号が上記第1論理値から上記第2論理値に変化するタイミングおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力することを特徴としている。

【0022】

本発明の表示装置は、上記課題を解決するために、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、上記シリアルデータに、1フレーム期間の開始を指示する第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、上記第1フラグおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、次の水平期間が存在する場合には、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に上記次の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に、上記表示ドライバが備える走査信号線ドライバのシフトレジスタに入力するタイミング信号を生成し、各上記水平期間のタイミング信号と、上記走査信号線ドライバから出力される走査信号とを用いて、上記画像データを画素に書き込むことを特徴としている。

【0023】

上記の発明によれば、表示ドライバは、シリアル伝送されたシリアルデータから、シリアルクロックのタイミングを用いて第1フラグと画像データとを取り出す。そして、第1フラグから1フレーム期間の最初の水平期間のタイミング信号を生成して、データ信号線ドライバのシフトレジスタに入力し、2番目以降の水平期間についてはデータ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に次の水平期間のタイミング信号を順次生成していく。

【0024】

従って、表示ドライバは、シリアル伝送による直接制御によって画像データを画素に書き込むためのタイミング信号を生成することができるので、わざわざ発振器などを用いて生成することなく、容易である。

【0025】

以上により、画像データを画素に書き込むためのタイミング信号をドライバIC内で容易に生成することのできるという効果を奏する。

【0026】

本発明の表示装置は、上記課題を解決するために、上記画素は上記表示ドライバから供給された上記画像データを記憶する画素メモリを備えており、上記画素メモリに上記画像データを記憶させるときには、上記シリアルデータに、上記画素メモリに記憶させる上記画像データを含めるとともに上記第1フラグを付加し、上記画素メモリに記憶させた上記画像データを表示するときには、上記シリアルデータに、上記画素メモリに記憶させる上記画像データの代わりに上記画素に供給しないダミーデータを含めるとともに上記第1フラグを付加することを特徴としている。

【0027】

上記の発明によれば、画素メモリに記憶させた画像データを表示するときに、画素メモリに記憶させる画像データの代わりに画素に供給しないダミーデータに付加した第1フラグによって、画素への画像データ供給による消費電力を発生させることなくコモン反転用のタイミング信号を生成することができるという効果を奏する。

【0028】

本発明の表示装置は、上記課題を解決するために、上記走査信号は、各水平表示期間において、上記画像データの全てがデータ信号線に出力された後に、上記画像データを上記画素メモリに書き込み可能とする信号であることを特徴としている。

【0029】

上記の発明によれば、各水平表示期間において、画像データの全てがデータ信号線に出力された後に画像データが画素メモリに書き込まれるので、画像データがデータ信号線に順次出力されている期間にデータ信号線の電位に乱れが生じても、画素メモリへの記憶に影響が及びにくいという効果を奏する。

【0030】

本発明の表示装置は、上記課題を解決するために、上記シリアルデータに、上記画素メモリに記憶させる上記画像データが含まれているか否かを示す第2フラグが付加されており、上記表示ドライバは、上記シリアルクロックのタイミングを用いて、上記シリアルデータから上記第2フラグを取り出して、上記第2フラグが、上記シリアルデータに、上記画素メモリに記憶させる上記画像データが含まれていることを示すときに、上記シリアルデータから上記画像データを取り出して上記画素メモリに記憶させることを特徴としている。

【0031】

上記の発明によれば、第2フラグによって、シリアルデータに、画素メモリに記憶させる画像データが含まれていることを認識することができるので、画像データが含まれているときにのみ、画素への画像データ供給による消費電力の発生を許容するようにすることができるという効果を奏する。

【0032】

本発明の表示装置は、上記課題を解決するために、上記シリアルデータに、全ての上記画素の表示を初期化するか否かの指示を行う第3フラグが付加されており、上記表示ドライバは、上記シリアルクロックのタイミングを用いて、上記シリアルデータから上記第3フラグを取り出して、上記第3フラグが、全ての上記画素の表示を初期化する指示を行うものであるときに、全ての上記画素の表示を初期化することを特徴としている。

【0033】

上記の発明によれば、第3フラグによって、全ての上記画素の表示を初期化することを認識することができるので、シリアルデータに初期化の画像データを含めなくても初期化することが可能となる。従って、画素へ個別に画像データを供給する必要がなくなり、その分の消費電力を削減することができるという効果を奏する。

【0034】

上記第1フラグは、さらに、コモン電極の電圧の極性を指示するフラグとして上記シリアルデータに付加されていることを特徴とする請求項1または2に記載の表示装置。

【0035】

上記の発明によれば、コモン電極の電圧の極性を1フレームごとに反転させることができるという効果を奏する。

【0036】

本発明の表示装置は、上記課題を解決するために、上記シリアル伝送において、表示を行うか否か、すなわち表示ドライバを動作させるか否かを示すシリアルチップセレクト信号が、上記シリアルデータおよび上記シリアルクロックとは異なる配線によって伝送されることを特徴としている。

【0037】

上記の発明によれば、表示ドライバは、シリアルチップセレクト信号によって動作を行わない期間を認識することによりシリアルデータを取り込まないようにすることができるので、シリアル伝送を停止させることができ、その分の消費電力を削減することができるという効果を奏する。

【0038】

本発明の表示装置は、上記課題を解決するために、上記画素内のアナログスイッチはCMOS回路によって作成されていることを特徴としている。

【0039】

上記の発明によれば、画素内のアナログスイッチがCMOS回路によって作成されていることにより、TFTのようなVth(しきい値)が高いデバイスでも、低電圧で駆動することが可能であるとともに、制御信号とデータ信号とを同一電圧とすることができる。従って、表示の駆動回路に用いる電源振幅を小さくすることができて、消費電力を削減することができるという効果を奏する。

【0040】

本発明の表示装置は、上記課題を解決するために、上記表示ドライバは、表示パネルにモノリシックに作り込まれていることを特徴としている。

【0041】

上記の発明によれば、表示ドライバを、表示パネルにモノリシックにCMOS回路で形成するので、表示装置の小型化およびプロセスの簡略化を図ることができるという効果を奏する。

【0042】

本発明の表示装置は、上記課題を解決するために、上記画素の表示素子に高分子分散型液晶が用いられていることを特徴としている。

【0043】

上記の発明によれば、表示素子に高分子分散型液晶を用いるので、液晶表示装置を偏光板などを省略した高明度の表示装置として、しかも低電圧で駆動することができるという効果を奏する。特に、画素に画素メモリを備える低消費電力の表示装置では、消費電力の削減を飛躍的に向上させることができるという効果を奏する。

【0044】

本発明の表示装置は、上記課題を解決するために、上記画素の表示素子に高分子ネットワーク型液晶が用いられていることを特徴としている。

【0045】

上記の発明によれば、表示素子に高分子ネットワーク型液晶を用いるので、液晶表示装置を偏光板などを省略した高明度の表示装置として、しかも低電圧で駆動することができるという効果を奏する。特に、画素に画素メモリを備える低消費電力の表示装置では、消費電力の削減を飛躍的に向上させることができるという効果を奏する。

【0046】

本発明の表示装置は、上記課題を解決するために、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号をダミーのシフトレジスタにより所定段シフトさせた第1エンドビットと、上記第1エンドビットをさらに上記ダミーのシフトレジスタにより1段だけシフトさせた第2エンドビットとを生成し、上記データ信号線ドライバの上記次の水平期間のタイミング信号を、上記第2エンドビットを用いて生成し、上記走査信号線ドライバのシフトレジスタに入力するタイミング信号を、上記第1エンドビットおよび上記第2エンドビットを用いて生成することを特徴としている。

【0047】

本発明の携帯端末は、上記課題を解決するために、上記表示装置をディスプレイとして備えていることを特徴としている。

【0048】

上記の発明によれば、携帯端末に対して、低消費電力化の要請を容易に満たすことができるという効果を奏する。

【0049】

本発明の他の目的、特徴、および優れた点は、以下に示す記載によって十分分かるであろう。また、本発明の利点は、添付図面を参照した次の説明によって明白になるであろう。

【図面の簡単な説明】

【0050】

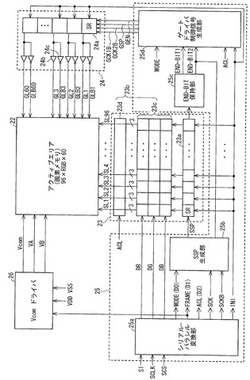

【図1】本発明の実施形態を示すものであり、表示装置の主要部の接続関係を示す回路ブロック図である。

【図2】データ更新モードにおけるシリアル伝送の各信号の波形を示すタイミングチャートである。

【図3】表示モードにおけるシリアル伝送の各信号の波形を示すタイミングチャートである。

【図4】表示装置の全体構成を示すブロック図である。

【図5】画素および画素メモリの構成を示す回路図である。

【図6】Vcomドライバの出力波形を示すタイミングチャートである。

【図7】シリアル−パラレル変換部の構成を示す回路図である。

【図8】END−BIT保持部の構成を示す回路図である。

【図9】ソーススタートパルス生成部の構成を示す回路図である。

【図10】ゲートドライバ制御信号生成部の構成を示す回路図である。

【図11】Vcomドライバの構成を示す回路図である。

【図12】シリアル−パラレル変換部の信号波形を示すタイミングチャートである。

【図13】ゲートドライバ制御信号生成部の信号波形を示すタイミングチャートである。

【図14】従来技術を示すものであり、表示装置の構成を示す回路ブロック図である。

【図15】従来技術を示すものであり、携帯電話の構成を示すブロック図である。

【図16】従来技術を示すものであり、表示ドライバの構成を示すブロック図である。

【発明を実施するための形態】

【0051】

本発明の一実施形態について図1ないし図13に基づいて説明すると以下の通りである。

【0052】

図4に、本実施形態に係る液晶表示装置(表示装置)21の構成を示す。

【0053】

液晶表示装置21は、例えば携帯電話などの携帯端末に搭載されているディスプレイデバイスであり、表示パネル21aおよびフレキシブルプリント基板(FPC)21bを備えている。表示パネル21aは、各種回路がモノリシックに作り込まれたものであり、フレキシブルプリント基板21bは、アプリケーションプロセッサなどのCPUに制御される3線のシリアルインタフェースバスI/F BUSを通したシリアル伝送によって、シリアルデータSI、シリアルチップセレクト信号SCS、および、シリアルクロックSCLKを受け、これらをFPC端子21cを通して表示パネル21aに供給する。シリアル伝送はマイクロコントローラなど他の制御手段によって制御されてもよい。また、フレキシブルプリント基板21bは、外部から供給される5Vの電源VDD、および、0Vの電源VSSを、FPC端子21cを通して表示パネル21aに供給する。

【0054】

表示パネル21aは、アクティブエリア22、バイナリドライバ(データ信号線ドライバ)23、ゲートドライバ(走査信号線ドライバ)24、タイミングジェネレータ25、および、Vcomドライバ26を備えている。バイナリドライバ23、ゲートドライバ24、タイミングジェネレータ25、および、Vcomドライバ26は表示ドライバを構成している。

【0055】

アクティブエリア22はRGBの画素が、例えば96×RGB×60のマトリクス状に配置された領域であり、各画素は画素メモリを備えている。バイナリドライバ23は画像データをソースラインを通してアクティブエリア22に供給する回路であり、シフトレジスタ23aおよびデータラッチ23bを備えている。ゲートドライバ24はアクティブエリア22の画像データを供給すべき画素をゲートラインを通して選択する。タイミングジェネレータ25はフレキシブルプリント基板21bから供給される信号を基に、バイナリドライバ23、ゲートドライバ24、および、Vcomドライバ26に供給する信号を生成する。

【0056】

図5に、アクティブエリア22に配置された各画素PIXの構成を、画素メモリの回路を詳細に表しながら示す。

【0057】

画素PIXは、液晶容量CL、画素メモリ30、アナログスイッチ31、アナログスイッチ33・34を備えている。さらに画素メモリ30は、アナログスイッチ32およびインバータ35・36を備えている。

【0058】

液晶容量CLは、極性出力OUTとコモン電極の電圧であるコモン出力Vcomとの間に、ここでは高分子分散型液晶(PDLC:Polymer Dispersed Liquid Crystal)や、高分子ネットワーク型液晶(PNLC:Polymer Network Liquid Crystal)などの光分散型液晶を用いて構成されている。アナログスイッチ31〜34およびインバータ35・36はCMOS回路で構成されている。

【0059】

アナログスイッチ31は、ソースライン出力SLと画素メモリ30との間に挿入されており、そのPMOSトランジスタ31aのゲートはゲートライン反転出力GLBに接続されているとともに、NMOSトランジスタ31bのゲートはゲートライン出力GLに接続されている。画素メモリ30において、アナログスイッチ32は、インバータ35の入力とインバータ36の出力との間に挿入されており、そのPMOSトランジスタ32aのゲートはゲートライン出力GLに接続されているとともに、NMOSトランジスタ32bのゲートはゲートライン反転出力GLBに接続されている。インバータ35の入力はアナログスイッチ31のソースライン出力SL側とは反対側の接続端子に接続されている。インバータ35の出力はインバータ36の入力に接続されている。インバータ35・36は、電源VDDをHigh側電源に用い、電源VSSをLow側電源に用いている。

【0060】

アナログスイッチ33は、黒極性用出力VAと極性出力OUTとの間に挿入されており、そのPMOSトランジスタ33aのゲートはインバータ35の出力に接続されているとともに、NMOSトランジスタ33bのゲートはインバータ35の入力に接続されている。アナログスイッチ34は、白極性用出力VBと極性出力OUTとの間に挿入されており、そのPMOSトランジスタ34aのゲートはインバータ35の入力に接続されているとともに、NMOSトランジスタ34bのゲートはインバータ35の出力に接続されている。

【0061】

上記のコモン出力Vcom、黒極性用出力VA、および、白極性用出力VBの波形を図6に示す。これらの信号はVcomドライバ26によって生成される。コモン出力Vcomは、1フレームごとに正極性と負極性とが切り替わる5Vp−pのパルス波形をなす。極性の切り替わり周期は、この他にも所定水平期間ごとなど、任意に設定が可能である。黒極性用出力VAは、コモン出力Vcomに対して位相が反転した5Vp−pのパルス波形をなす。白極性用出力VB(ノーマリーホワイトの場合)は、コモン出力Vcomと同相の5Vp−pのパルス波形をなす。

【0062】

図5において、バイナリドライバ23からソースライン出力SLとしてHighレベル(5V)が出力された場合には、Highレベル(5V)のゲートライン出力GLおよびLowレベル(0V)のゲートライン反転出力GLBによって選択される画素PIXのアナログスイッチ31が導通することにより、アナログスイッチ33が導通するとともにアナログスイッチ34が遮断される。従って、極性出力OUTには黒極性用出力VAが出力される。液晶容量CLには黒極性用出力VAとコモン出力Vcomとの差の電圧として5Vが印加され、画素PIXは黒表示状態となる。

【0063】

次いで、ゲートライン出力GLがLowレベル(0V)、ゲートライン反転出力GLBがHighレベル(5V)になると、アナログスイッチ31が遮断されるとともにアナログスイッチ32が導通するので、画素メモリ30にHighレベルが記憶される。この記憶データは、同じ画素PIXが次に選択されてアナログスイッチ31が導通するまで保持される。

【0064】

一方、図5において、バイナリドライバ23からソースライン出力SLとしてLowレベル(0V)が出力された場合には、Highレベル(5V)のゲートライン出力GLおよびLowレベル(0V)のゲートライン反転出力GLBによって選択される画素PIXのアナログスイッチ31が導通することにより、アナログスイッチ33が遮断されるとともにアナログスイッチ34が導通する。従って、極性出力OUTには白極性用出力VBが出力される。液晶容量CLには白極性用出力VBとコモン出力Vcomとの差の電圧として0Vが印加され、画素PIXは白表示状態となる。

【0065】

次いで、ゲートライン出力GLがLowレベル(0V)、ゲートライン反転出力GLBがHighレベル(5V)になると、アナログスイッチ31が遮断されるとともにアナログスイッチ32が導通するので、画素メモリ30にLowレベルが記憶される。この記憶データは、同じ画素PIXが次に選択されてアナログスイッチ31が導通するまで保持される。

【0066】

次に、図1に、タイミングジェネレータ25と、バイナリドライバ23、ゲートドライバ24、および、Vcomドライバ26との間の接続関係を示す。

【0067】

タイミングジェネレータ25は、シリアル−パラレル変換部25a、ソーススタートパルス生成部25b、END−BIT保持部25c、および、ゲートドライバ制御信号生成部25dを備えている。タイミングジェネレータ25は、パネル外部から入力されるシリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSから、モード信号MODE、フレーム信号FRAME、全クリア信号ACL、ソースクロック(データ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号)SCK・SCKB、ソーススタートパルス(水平期間のタイミング信号)SSP、ゲートクロック(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号)GCK1B・GCK2B、ゲートスタートパルスGSP、ゲートイネーブル信号(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号、走査信号)GEN、および、イニシャル信号INIを生成する。タイミングジェネレータ25からバイナリドライバ23へは、ソーススタートパルスSSP、および、イニシャル信号INIが供給され、タイミングジェネレータ25からゲートドライバ24へは、ゲートクロックGCK1B・GCK2B、ゲートスタートパルスGSP、ゲートイネーブル信号GEN、および、イニシャル信号INIが供給され、タイミングジェネレータ25からVcomドライバ26へは、フレーム信号FRAMEが供給される。なお、ソースクロックSCK・SCKBはここではタイミングジェネレータ25の内部で用いられるが、後述するように1水平期間ごとのソーススタートパルスSSPを生成するのに用いられており、バイナリドライバ23のシフトレジスタ23aを動作させるクロック信号である。

【0068】

シリアルパラレル−変換部25aには、フレキシブルプリント基板21bからシリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSが入力される。前述したように、シリアルインタフェースバスI/F BUSは3線式であるので、シリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSは互いに異なる配線によって伝送される。これらの信号を図2および図3に示す。

【0069】

シリアルデータSIは、2値からなるRGBのデジタル画像データがシリアルに配列されたものに、1フレームごとに先頭に設けられたモード選択期間にフラグD0・D1・D2が付加された信号である。

【0070】

画像データは、図2のような、画素メモリ30に画像データを書き込むデータ更新モードにおいては、1水平表示期間分のRGBデータが時系列に配列されたものが、水平表示期間順に配列されている。また、隣接する水平表示期間どうしの水平帰線期間には、ダミーデータdR1・dG1・dB1…が配置されるとともに、先頭の水平表示期間のフラグD0・D1・D2に相当する期間に3つのダミーデータDMY・DMY・DMYが配置されている。これらのダミーデータはHighでもLowでもよい。

【0071】

また、画像データは、図3のような、画素メモリ30に記憶されている画像データを保持する表示モードにおいては、図2のデータ更新モードにおける画像データおよびダミーデータが全てダミーデータDMYで置き換わったものである。

【0072】

フラグ(第2フラグ)D0はモードフラグであり、Highの場合には画素メモリ30に画像データを書き込むデータ更新モードを行うようにタイミングジェネレータ25に指示し、Lowの場合には画素メモリ30に記憶されている画像データを保持する表示モードを行うようにタイミングジェネレータ25に指示する。フラグ(第1フラグ)D1はフレーム反転フラグであり、Highの場合にはコモン出力VcomをHighに設定することをタイミングジェネレータ25に指示し、Lowの場合にはコモン出力VcomをLowに設定することをタイミングジェネレータ25に指示する。すなわち、フラグD1は、1フレームごとに反転するコモン出力Vcomの極性を指示するフラグである。フラグ(第3フラグ)D2は全クリアフラグであり、Highの場合にはそのフレームにおいて全ての画素PIXに白表示データを書き込むことをタイミングジェネレータ25に指示し、Lowの場合にはそのフレームにおいて全ての画素PIXに、供給する画像データを書き込むことを指示する。これによって、フラグD2は、Highの場合に、全ての画素PIXの表示を初期化する指示を行う。フラグD2は通常はLowである。

【0073】

シリアルクロックSCLKは、シリアルデータSIのフラグを含めた各データを取り出すための同期用クロックである。このシリアルクロックSCLKの立ち上がりタイミングおよび立ち下がりタイミングの一例を挙げると、以下の通りである。シリアルクロックSCLKの立ち上がりタイミングは、フラグD0〜D2に対しては各フラグの伝送開始タイミングから時間tsSCLKだけ経過した時点であり、画像データR・G・Bに対しては各画像データの伝送開始タイミングから時間twSCLKLだけ経過した時点である。tsSCLK=twSCLKLであって、シリアルクロックSCLKのLow期間に等しい。また、シリアルクロックSCLKの立ち下がりタイミングは、フラグD0〜D2に対してはシリアルクロックSCLKの立ち上がりタイミングから時間tsSCLKだけ経過した時点であってフラグの伝送終了タイミング(すなわち次のフラグまたはデータへの切り替わりタイミング)であり、画像データR・G・Bに対してはシリアルクロックSCLKの立ち上がりタイミングから時間twSCLKHだけ経過した時点であって各画像データの伝送終了タイミング(すなわち次のフラグまたはデータへの切り替わりタイミング)である。tsSCLK=twSCLKHであって、シリアルクロックSCLKのHigh期間に等しい。ここではシリアルクロックSCLKのデューティは50%である。

【0074】

シリアルチップセレクト信号SCSは、CPUからシリアルインタフェースバスI/F BUSを通してタイミングジェネレータ25にシリアルデータSIおよびシリアルクロックSCLKを伝送するときに期間twSCSHだけHighとなる信号である。シリアルデータSIおよびシリアルクロックSLCKを伝送するフレームについての、シリアルデータSIの伝送開始タイミングよりも時間tsSCSだけ前にHighとなり、シリアルデータSIの伝送終了タイミングよりも時間thSCSだけ後にLowとなる。また、上記High期間の後に期間twSCSLだけLowとなり、期間twSCSHと期間twSCSLとを合わせて垂直帰線期間を含む1フレーム期間tVとなる。

【0075】

図2のデータ更新モードで画素メモリ30に書き込まれた画像データは、図3の表示モードで保持され続ける。データ更新モードでも表示モードでも、シリアルデータSIにはフラグD0・D1・D2が付加されており、フラグD1は1フレームごとにHighとLowとが切り替わっていく。従って、フラグD1は1フレームの開始を指示するフラグでもある。

【0076】

シリアル−パラレル変換部25aは、このようにして入力されるシリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSから、フラグD0・D1・D2のそれぞれと、RのデータDR、GのデータDG、および、BのデータDBとを抽出する。フラグD0はモード信号MODEとして、フラグD1はフレーム信号D1として、フラグD2は全クリア信号ACLとして、それぞれ他の回路での信号生成動作に用いられる。また、データDR・DG・DBはバイナリドライバ23のデータラッチ23bに供給される。

【0077】

また、シリアル−パラレル変換部25aは、シリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSから、ソースクロックSCK・SCKBおよびイニシャル信号INIを生成する。ソースクロックSCK・SCKBはバイナリドライバ23に供給され、イニシャル信号INIは他の回路での信号生成動作に用いられる。

【0078】

次に、ソーススタートパルス生成部25bは、シリアル−パラレル変換部25bから入力されるモード信号MODEおよびソースクロックSCK・SCKBから第1水平表示期間のソーススタートパルスSSPを生成してバイナリドライバ23のシフトレジスタ23aに供給する。この第1水平表示期間のソーススタートパルスSSPは、モード信号MODEのHighへの立ち上がりタイミングを用いて生成することができ、第2水平表示期間以降の水平表示期間については、後述するEND−BIT保持部25cが生成した第2エンドビットEND−BIT2を用いて生成することができる。

【0079】

END−BIT保持部25cは、バイナリドライバ23のシフトレジスタ23aの最終段の出力から、第1エンドビットEND−BIT1および第2エンドビットEND−BIT2を生成して、ゲートドライバ制御信号生成部25dに供給する。第1エンドビットEND−BIT1は、シフトレジスタ23aの最終段の出力をさらにダミーのシフトレジスタにより所定段シフトさせたものであり、第2エンドビットEND−BIT2は、第1エンドビットEND−BIT1をさらに上記ダミーのシフトレジスタにより1段だけシフトさせたものである。

【0080】

ゲートドライバ制御信号生成部25dは、第1エンドビットEND−BIT1、第2エンドビットEND−BIT2、モード信号MODE、全クリア信号ACLから、ゲートクロックGCK1B・GCK2B、ゲートスタートパルスGSP、および、ゲートイネーブル信号GENを生成して、ゲートドライバ24へ供給する。

【0081】

次に、バイナリドライバ23において、シフトレジスタ23aはタイミングジェネレータ25のソーススタートパルス生成部25bから入力されるソーススタートパルスSSPと、タイミングジェネレータ25のシリアルパラレル−変換部25aから入力されるイニシャル信号INIとから、各段SRの出力を生成する。データラッチ23bは1stラッチ回路23cと全クリア回路23dとを備えている。1stラッチ回路23cは、シフトレジスタ23aの各段SRの出力タイミングで、タイミングジェネレータ25のシリアルパラレル−変換部25aから入力されるデータDR・DG・DBを順次ラッチして、対応するソースラインSL(RGBのそれぞれについてSL1〜SL96)に出力する。全クリア回路23dは、シリアルデータSIのフラグD2がHighである場合に、タイミングジェネレータ25のシリアルパラレル−変換部25aからアクティブな全クリア信号ACLが入力されると、全てのソースラインSLに白表示データを出力する。

【0082】

次に、ゲートドライバ24は、シフトレジスタ24aと、複数のバッファ24bおよび反転バッファ24cとを備えている。シフトレジスタ24aは、タイミングジェネレータ25のゲートドライバ制御信号生成部25dから出力された、ゲートクロックGCK1B・GCK2B、ゲートスタートパルスGSP、および、ゲートイネーブル信号GENと、シリアル−パラレル変換部25aから入力されるイニシャル信号INIとから、各段SRの出力を生成する。バッファ24bと反転バッファ24cとは1つずつ対として画素行ごとに設けられている。1対のバッファ24bと反転バッファ24cとの各入力はシフトレジスタ24aの対応する段SRの出力に接続されており、バッファ24bの出力は対応するゲートラインGL(GL1〜GL60)に、反転バッファ24cの出力は対応するゲートラインGLB(GLB1〜GLB60)に、それぞれ接続されている。

【0083】

次に、Vcomドライバ26は、タイミングジェネレータ25のシリアルパラレル−変換部25aから入力されるフレーム信号FRAMEと、電源VDD・VSSとから、コモン出力Vcom、黒極性用出力VA、および、白極性用出力VBを生成してアクティブエリア22に供給する。

【0084】

次に、図7に、シリアル−パラレル変換部25aの詳細な構成例を示す。

【0085】

シリアルデータSIは、縦続に接続されたDフリップフロップ41・42・43を順に通され、3段目のDフリップフロップ43の出力S2がDフリップフロップ44を通されるとモード信号MODEが取り出され、2段目のDフリップフロップ42の出力S1がDフリップフロップ45を通されるとフレーム信号FRAMEが取り出され、初段のDフリップフロップ41の出力S0がDフリップフロップ46を通されると全クリア信号ACLが取り出される。また、画像データがRGBの順に時系列に並んでいるとすると、出力S2がDフリップフロップ47を通されるとデータDRが取り出され、出力S1がDフリップフロップ48を通されるとデータDGが取り出され、出力S0がDフリップフロップ49を通されるとデータDBが取り出される。

【0086】

ここで、Dフリップフロップ41・42・43のHighアクティブのクロック端子CKにはシリアルクロックSCLKが入力され、Dフリップフロップ44・45・46のLowアクティブのクロック端子CKには2入力のNORゲート55の出力DENが入力され、Dフリップフロップ47・48・49のLowアクティブのクロック端子CKにはDフリップフロップ51の出力Aが入力される。

【0087】

NORゲート55の一方の入力はDフリップフロップ53の出力に接続されており、他方の入力は2入力のNANDゲート54の出力Cに接続されている。Dフリップフロップ53の入力は電源VDDに接続されており、Lowアクティブのクロック端子CKはDフリップフロップ52の出力Bに接続されている。NANDゲート54の一方の入力は出力Bに接続されており、他方の入力は出力Aに接続されている。Dフリップフロップ51の入力は出力Cに接続されている。Dフリップフロップ52の入力は出力Aに接続されている。Dフリップフロップ51・52のLowアクティブのクロック端子CKにはシリアルクロックSCLKが入力される。

【0088】

また、ソースクロックSCKBは、Dフリップフロップ56の出力をインバータ57を通して得られ、ソースクロックSCKは、インバータ57の出力をインバータ58を通して得られる。Dフリップフロップ56の入力はインバータ57の出力に接続されており、Highアクティブのクロック端子CKは出力Bに接続されている。

【0089】

上記各Dフリップフロップにおいて、Highアクティブのクロック端子CKではポジティブエッジトリガが行われ、Lowアクティブのクロック端子CKでは、ネガティブエッジトリガが行われる。

【0090】

また、Dフリップフロップ44〜53・56のリセット端子Rには、シリアルチップセレクト信号SCSが入力される。イニシャル信号INIはシリアルチップセレクト信号SCSそのものである。

【0091】

図12のタイミングチャートに、シリアルクロックSCLK、出力A・B・C、および、ソースクロックSCK・SCKB、および、出力DENの波形を示す。

【0092】

次に、図8に、END−BIT保持部25cの詳細な構成例を示す。

【0093】

まず、バイナリドライバ23のシフトレジスタ23aはセットリセットフリップフロップが縦続に接続された構成である。ここでは、最後の2つの(95段目および96段目の)セットリセットフリップフロップB95・B96が図示されており、セットリセットフリップフロップB95のセット入力端子には前段のセットリセットフリップフロップB94の出力Q(B94)が入力されている。END−BIT保持部25cもシフトレジスタ23aの最終段に続いて同じ縦続接続関係により、ダミーのセットリセットフリップフロップDMY1・DMY2・DMY3・DMY4が順に接続された構成である。これらのセットリセットフリップフロップは、次段の出力がリセット信号として入力されるようになっているが、セットリセットフリップフロップDMY4については自段の出力を2つのインバータで遅延させた信号を、それぞれリセット信号としている。

【0094】

セットリセットフリップフロップDMY2の出力が第1エンドビットEND−BIT1、セットリセットフリップフロップDMY3の出力が第2エンドビットEND−BIT2として得られる。

【0095】

次に、図9に、ソーススタートパルス生成部25bの詳細な構成例を示す。

【0096】

2入力のNORゲート61における一方のLowアクティブの入力にモード信号MODEが入力され、他方のHighアクティブな入力に第2エンドビットEND−BIT2が入力される。NORゲート61の出力はDラッチ62に入力され、Dラッチ62の出力はDラッチ63に入力される。Dラッチ62のイネーブル端子ENおよびDラッチ63のイネーブル端子ENBにはシリアル-パラレル変換部25aで生成したソースクロックSCKBが、Dラッチ62のイネーブル端子ENBおよびDラッチ63のイネーブル端子ENにはシリアル-パラレル変換部25aで生成したソースクロックSCKが、それぞれ入力される。Dラッチ62の出力とDラッチ63の出力とは2入力のNORゲート64に入力される。NORゲート64の出力とモード信号MODEとは2入力のNANDゲート65に入力され、NANDゲート65の出力がソーススタートパルスSSPとなる。

【0097】

次に、図10に、ゲートドライバ制御信号生成部25dの詳細な構成例を示す。

【0098】

Dフリップフロップ71のHighアクティブのクロック端子CKとLowアクティブのクロック端子CKBに第1エンドビットEND−BIT1が入力される。Dフリップフロップ71の出力はDフリップフロップ72に入力される。Dフリップフロップ72のLowアクティブのクロック端子CKとHighアクティブのクロック端子CKBとに第2エンドビットEND−BIT2が入力される。Dフリップフロップ72の出力はDフリップフロップ71の入力となる。また、Dフリップフロップ71・72の各出力は、それぞれ2入力のNANDゲート73および2入力のNORゲート76の両入力となる。NANDゲート73の出力および全クリア信号ACLは、2入力のNANDゲート74に入力される。NANDゲート74の出力とイニシャル信号INIとは2入力のNANDゲート75に入力される。NANDゲート75の出力はゲートクロックGCK2Bとなる。

【0099】

また、NORゲート76の出力とモード信号MODEとは2入力のNANDゲート77に入力される。NANDゲート77の出力と全クリア信号ACLとは2入力のNANDゲート78に入力される。NANDゲート78の出力とイニシャル信号INIとは2入力のNANDゲート79に入力される。NANDゲート79の出力はゲートクロックGCK1Bとなる。

【0100】

また、モード信号MODEはDラッチ80に入力される。Dラッチ80のイネーブル端子EN・ENBには第1エンドビットEND−BIT1が入力される。Dラッチ80の出力は2入力のNORゲート81のHighアクティブの入力となり、モード信号MODEはNORゲート81のLowアクティブの入力となる。NORゲート81の出力と全クリア信号ACLとは2入力のNORゲート82に入力される。NORゲート82の出力とイニシャル信号INIとは2入力のNORゲート83に入力される。NORゲート83の出力はゲートスタートパルスGSPとなる。

【0101】

また、第1エンドビットEND−BIT1および第2エンドビットEND−BITは2入力のNORゲート84に入力される。NORゲート84の出力はDフリップフロップ85のLowアクティブのクロック端子CKとHighアクティブのクロック端子CKBとに入力される。Dフリップフロップ85の出力はインバータ86に入力され、Dフリップフロップ85の入力はインバータ86の出力に接続されている。インバータ86の出力と全クリア信号ACLとは2入力のNORゲート87に入力される。NORゲート87の出力と全クリア信号ACLとはNORゲート88に入力される。NORゲート88の出力はゲートイネーブル信号GENとなる。

【0102】

Dフリップフロップ71・72・85およびDラッチ80のイニシャル端子INIにはイニシャル信号INIが入力される。Dフリップフロップ71はポジティブエッジトリガ型であり、Dフリップフロップ72・85はネガティブエッジトリガ型である。

【0103】

図13のタイミングチャートに、ゲートクロックGCK1B・GCK2B、ゲートイネーブル信号GEN、および、ゲートライン出力GL(GL1・GL2)の波形を示す。シフト1は、最初のゲートライン出力GL1に対応するデータDR・DG・DBがソースラインSLに出力されている期間を示し、シフト2は、2番目のゲートライン出力GL2に対応するデータDR・DG・DBがソースラインSLに出力されている期間を示している。水平表示期間の最後にゲートイネーブル信号GENを用いて画素メモリ30に一斉に画像データを書き込むので、データDR・DG・DBがソースラインSLに順次出力されている期間にソースラインSLの電位に乱れが生じても、画素メモリ30への記憶に影響が及びにくい。

【0104】

図11に、Vcomドライバの詳細な構成を示す。

【0105】

フレーム信号FRAMEがバッファを通して、それぞれC接点相当のスイッチSW1・SW2・SW3の制御信号として入力される。スイッチSW1・SW2・SW3は、順にコモン出力Vcom、黒極性用出力VA、白極性用出力VBの電圧を出力するスイッチである。フレーム信号FRAMEがHighとLowとで切り替わる度に、スイッチSW1・SW2・SW3は、順に電源VDD・VSS・VDDの組み合わせと、電源VSS・VDD・VSSの組み合わせとの間で切り替わるように電源を選択する。

【0106】

以上に述べたように、本実施形態の表示装置は、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、上記シリアルデータに、1フレーム期間の開始を指示する第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、上記第1フラグおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、次の水平期間が存在する場合には、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に上記次の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に、上記表示ドライバが備える走査信号線ドライバのシフトレジスタに入力するタイミング信号を生成し、各上記水平期間のタイミング信号と、上記走査信号線ドライバから出力される走査信号とを用いて、上記画像データを画素に書き込む。

【0107】

上記の構成によれば、表示ドライバは、シリアル伝送されたシリアルデータから、シリアルクロックのタイミングを用いて第1フラグと画像データとを取り出す。そして、第1フラグから1フレーム期間の最初の水平期間のタイミング信号を生成して、データ信号線ドライバのシフトレジスタに入力し、2番目以降の水平期間についてはデータ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に次の水平期間のタイミング信号を順次生成していく。

【0108】

従って、表示ドライバは、シリアル伝送による直接制御によって画像データを画素に書き込むためのタイミング信号を生成することができるので、わざわざ発振器などを用いて生成することなく、容易である。

【0109】

以上により、画像データを画素に書き込むためのタイミング信号をドライバIC内で容易に生成することのできるという効果を奏する。

【0110】

また、以上に述べたように、本実施形態の表示装置は、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、上記シリアルデータに、コモン電極の電圧の極性を指示する第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグを取り出して、上記シリアルデータに基づいた表示を行うとともに、取り出した上記第1フラグに従った極性の上記コモン電極の電圧を供給する。

【0111】

上記の構成によれば、表示ドライバは、シリアル伝送されたシリアルデータから、シリアルクロックのタイミングを用いて第1フラグを取り出し、第1フラグに従ってコモン電極の電圧の極性を決定して表示を行う。従って、表示ドライバは、シリアル伝送による直接制御によってコモン反転用のタイミング信号を生成することができるので、発振器や、コモン反転用のタイミング信号生成に関して外部からの制御を行うための特別な制御端子が不要となる。従って、表示ドライバの回路規模を小さくすることができる。

【0112】

以上により、コモン反転用のタイミング信号を小さな回路規模で生成することのできる表示装置を実現することができるという効果を奏する。

【0113】

なお以上の例では、フラグD0・D1・D2を1フレームの先頭に配置したが、これに限らず、タイミングジェネレータ25への指示を行いたい任意のタイミングに各フラグを配置することが可能である。例えば、フラグD1のHighとLowとを、水平期間の整数倍の期間ごとに切り換えたいときには、各水平期間の先頭に配置することなどが可能である。

【0114】

また、以上の例では、各種タイミング信号を生成するのにシリアルチップセレクト信号SCSを用いているが、これは必ずしも必要ではなく、例えばシリアル−パラレル変換部25aが、常にシリアルデータに対する受信のイネーブル状態にあるようにすればよい。

【0115】

また、以上の例ではアクティブエリア22が画素メモリ30を備える構成についての説明であったが、これに限ることはなく、フラグD0によってデータ更新モードと表示モードとを区別しないような構成を備えれば、画素メモリを備えていないアクティブエリアを有する表示装置にも本発明が適用可能である。

【0116】

また、以上の例では、バイナリドライバ23のシフトレジスタ23aが、初段のセット入力にソーススタートパルスSSPが入力されるだけでシフト動作が可能となる構成であったので、シリアル−パラレル変換部25aによって生成されたソースクロックSCK・SCKBは、ソーススタートパルス生成部25bにおいてソーススタートパルスSSPを生成するのに用いられることにより、データ信号線ドライバのシフトレジスタを動作させるクロック信号として機能するものであった。しかし、これに限ることはなく、データ信号線ドライバのシフトレジスタが各段へのクロック信号の入力によってシフト動作を行う構成であって、生成されたソースクロックSCK・SCKBが、ソーススタートパルスSSPを生成するのに用いられるとともに、データ信号線ドライバのシフトレジスタの各段に入力されて当該シフトレジスタの各段の動作に関わることにより、データ信号線ドライバのシフトレジスタを動作させるクロック信号として機能することも可能である。

【0117】

本発明は上述した実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能である。すなわち、請求項に示した範囲で適宜変更した技術的手段を組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。例えばEL表示装置にも適用可能である。

【産業上の利用可能性】

【0118】

本発明は、携帯端末に特に好適に使用することができる。

【符号の説明】

【0119】

21 液晶表示装置(表示装置)

23 バイナリドライバ

23a シフトレジスタ(データ信号線ドライバのシフトレジスタ)

23b データラッチ

24 ゲートドライバ

24a シフトレジスタ(走査信号線ドライバのシフトレジスタ)

25 タイミングジェネレータ

26 Vcomドライバ

30 画素メモリ

D0 フラグ(第2フラグ)

D1 フラグ(第1フラグ)

D2 フラグ(第3フラグ)

GCK1B、GCKB2

ゲートクロック(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号)

GEN ゲートイネーブル信号(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号、走査信号)

SCK、SCKB

ソースクロック(データ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号)

SSP ソーススタートパルス(水平期間のタイミング信号)

I/F BUS シリアルインタフェースバス

SI シリアルデータ

SCLK シリアルクロック

SCS チップセレクト信号

SL ソースライン(データ信号線)

Vcom コモン出力(コモン電極の電圧)

【技術分野】

【0001】

本発明は、表示装置の表示動作に用いるタイミング信号に関するものである。

【背景技術】

【0002】

各画素にメモリ回路(以下、画素メモリと称する)を備え、当該画素メモリに画像データを記憶させることによって、外部から画像データを供給し続けることなく静止画像を低消費電力で表示することができる表示装置が知られている。消費電力の削減には、一度画像データを書き込んだ後は、画素に画像データを供給するためのデータ信号線を画像データで充放電する必要がなくなるので、その充放電に伴う消費電力の削減分と、一度画像データを書き込んだ後は、パネル外部からドライバに画像データを伝送する必要がないので、その伝送に伴う消費電力の削減分とが含まれる。

【0003】

画素メモリとしてはSRAM型のものやDRAM型のものが開発されている。この表示装置では画素電圧がデジタルであるので、クロストークが起こりにくく、表示品位にも優れている。

【0004】

図14に、特許文献1に記載されたこのような画素メモリを備える表示装置の構成を示す。

【0005】

この表示装置は、Xアドレス走査線ドライバ18、デジタルデータドライバ19、およびアナログデータドライバ20を備えており、デジタルデータ画像表示モードとアナログデータ画像表示モードとを使い分けることができる。

【0006】

デジタルデータ画像表示モードについて説明すると、画像データを書き込む画素が接続されているXアドレス信号線4−n(nは自然数)を選択し、対応する第1表示制御線1−nからデジタルデータ信号を、当該画素の第1スイッチ素子8を通して、NAND回路11およびクロックトインバータ素子13によって構成されたデジタルメモリ素子100に書き込む。このとき、表示モード制御線15を通してデジタルメモリ素子100をアクティブにしておく。

【0007】

デジタルメモリ素子100の入力は第2スイッチ素子9に接続されているとともに出力は第3スイッチ素子10に接続されている。従って、デジタルデータ信号のHigh/Lowに応じて第2スイッチ素子9または第3スイッチ素子10のいずれか一方が導通する。第2表示制御線2−nおよび第3表示制御線3の一方には白表示基準電圧、他方には黒表示基準電圧が供給され、第2スイッチ素子9または第3スイッチ素子10のうちの導通したほうのスイッチ素子によって決まる白電圧または黒電圧が、液晶セル6に印加される。再び第1スイッチ素子8が導通して新たなデジタルデータ信号が書き込まれるまで、液晶セル6は、デジタルメモリ素子100が記憶したデジタルデータ信号による表示状態を保持する。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】日本国公開特許公報「特開2003−177717号公報(公開日:2003年6月27日)」

【特許文献2】日本国公開特許公報「特開昭58−23091号公報(公開日:1983年2月10日)」

【特許文献3】日本国公開特許公報「特開2007−286237号公報(公開日:2007年11月1日)」

【発明の概要】

【発明が解決しようとする課題】

【0009】

近年では、液晶表示装置における表示データの伝送のインタフェースは、信号線数の多いパラレル伝送方式のデジタルRGB方式(RGBインタフェース)から、信号線数の少ない高速シリアル伝送方式へと移行しつつある。特に、携帯電話などのモバイル機器では、配線数を減少させて、配線の設置スペースの省略および配線の断線防止を図る目的があるために、シリアル伝送方式は重要な技術となっている。また、差動伝送を行うことで、高速および低消費電力の伝送が達成できる。このようなシリアル伝送では表示データと制御コマンドとは同一バス上を伝送されることとなる。

【0010】

例えば、モバイル機器のアプリケーションプロセッサと周辺装置とのインタフェースである、いわゆるCPUインタフェースに関して共通仕様を定めたMIPI(Mobile Industry Processor Interface)スタンダードなどでは、アプリケーションプロセッサをホスト側として周辺装置の動作を制御する。制御信号を用いる表示駆動装置では、通常表示動作の開始をコマンド制御による指定で行うようになっており、電源起動後にホスト側より表示駆動装置に起動コマンドが送られると、これに沿って画面の表示が開始される。

【0011】

図15に、このような液晶ディスプレイ部にCPUインタフェースを備えた携帯電話における、回路接続構成の概念図を示す。

【0012】

携帯電話101は、液晶表示部102、液晶ドライバ103、アンテナ104、RF回路105、ベースバンドプロセッサ106、および、アプリケーションプロセッサ107を備えている。

【0013】

液晶表示部102は画素がマトリクス状に配置されたものである。各画素にはソースバスラインSL1〜SLnを介してデータ信号が書き込まれる。ソースバスラインSL1〜SLnには液晶ドライバ103からデータ信号を供給される。また、図示しないが、画素にデータ信号を書き込むために、複数の画素からなる各行を選択する走査信号が、液晶ドライバ103からゲートバスラインに順次供給される。

【0014】

液晶ドライバ103は、1チップまたは複数チップからなる、液晶表示部102の表示を駆動する回路であり、タイミングジェネレータや、ソースドライバ、ゲートドライバ、電源回路、メモリといった表示動作に関する各回路部を含んでいる。また、液晶ドライバ103は、ここではアプリケーションプロセッサ107をホストとし、シリアルバスI/F BUSを通して制御されるようになっており、そのインタフェースも内部に含んでいる。

【0015】

アンテナ104は携帯電話101の送受信用のアンテナである。RF回路105は、送受信に伴う高周波信号を処理する。ベースバンドプロセッサ106はRF回路105で復調されたベースバンド信号を処理し、図示しない通話信号処理回路やデータ通信処理回路の動作を制御する。アプリケーションプロセッサ107は、前記液晶ドライバ103や、図示しない動画・音楽・ゲームなどの処理を行う周辺装置を制御する。

【0016】

図16に上記液晶ドライバ103の構成例を示す。

【0017】

液晶ドライバ103内では、シリアルインタフェースバスI/F BUSから制御コマンドおよび表示データをシリアルインタフェース131で受信し、制御コマンドがレジスタ132に書き込まれる。また、その受信タイミングに基づいてタイミングジェネレータ135が、その内部に備えた発振器によりタイミング信号を生成する。当該タイミング信号に基づいて、シリアルインタフェース131からシフトレジスタ133、ソース駆動回路134へと順に表示データが送られ、ソースバスラインSLにデータ信号が供給される。

【0018】

しかしながら、上述したCPUインタフェースを備えた液晶ドライバでは、RGBインタフェースのように垂直同期信号や水平同期信号が外部から供給される代わりに、シリアル伝送された制御コマンドおよび表示データを基に、タイミングジェネレータが自走式による発振器によりタイミング信号を改めて生成し、ドライバ各部や液晶表示部を駆動している。前述した画素メモリを備えた画素では、静止画表示を行うときに表示データをメモリ回路に書き込んだ後は、アプリケーションプロセッサからのデータ供給が停止して消費電力を削減しているため、液晶ドライバ内部で独自にタイミング信号を生成することが重要である。しかし、小型、高速、および、低消費電力という長所を備えたシリアル伝送を採用しているものの、タイミングジェネレータで生成するクロック信号を基に画像データを画素に書き込むためのタイミング信号を生成しなければならない。

【0019】

このように、従来のCPUインタフェース方式では、画像データを書き込むためのタイミング信号をCPUから供給される信号を基にして、ドライバIC内でわざわざ発振器などを用いて生成する必要があり、液晶ドライバの回路規模の縮小化が妨げられるという問題があった。

【0020】

本発明は、上記従来の問題点に鑑みなされたものであり、その目的は、画像データを画素に書き込むためのタイミング信号をドライバIC内で容易に生成することのできる表示装置およびそれを備えた携帯端末を実現することにある。

【課題を解決するための手段】

【0021】

本発明の表示装置は、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、フレーム毎に、上記シリアルデータに、当該フレームにおいて画素に上記画像データを書き込むか否かを示す第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、上記第1フラグが画素に上記画像データを書き込むことを示す場合、当該フレームにおいて第1論理値から第2論理値に変化するモード信号を生成し、上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、上記モード信号が上記第1論理値から上記第2論理値に変化するタイミングおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力することを特徴としている。

【0022】

本発明の表示装置は、上記課題を解決するために、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、上記シリアルデータに、1フレーム期間の開始を指示する第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、上記第1フラグおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、次の水平期間が存在する場合には、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に上記次の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に、上記表示ドライバが備える走査信号線ドライバのシフトレジスタに入力するタイミング信号を生成し、各上記水平期間のタイミング信号と、上記走査信号線ドライバから出力される走査信号とを用いて、上記画像データを画素に書き込むことを特徴としている。

【0023】

上記の発明によれば、表示ドライバは、シリアル伝送されたシリアルデータから、シリアルクロックのタイミングを用いて第1フラグと画像データとを取り出す。そして、第1フラグから1フレーム期間の最初の水平期間のタイミング信号を生成して、データ信号線ドライバのシフトレジスタに入力し、2番目以降の水平期間についてはデータ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に次の水平期間のタイミング信号を順次生成していく。

【0024】

従って、表示ドライバは、シリアル伝送による直接制御によって画像データを画素に書き込むためのタイミング信号を生成することができるので、わざわざ発振器などを用いて生成することなく、容易である。

【0025】

以上により、画像データを画素に書き込むためのタイミング信号をドライバIC内で容易に生成することのできるという効果を奏する。

【0026】

本発明の表示装置は、上記課題を解決するために、上記画素は上記表示ドライバから供給された上記画像データを記憶する画素メモリを備えており、上記画素メモリに上記画像データを記憶させるときには、上記シリアルデータに、上記画素メモリに記憶させる上記画像データを含めるとともに上記第1フラグを付加し、上記画素メモリに記憶させた上記画像データを表示するときには、上記シリアルデータに、上記画素メモリに記憶させる上記画像データの代わりに上記画素に供給しないダミーデータを含めるとともに上記第1フラグを付加することを特徴としている。

【0027】

上記の発明によれば、画素メモリに記憶させた画像データを表示するときに、画素メモリに記憶させる画像データの代わりに画素に供給しないダミーデータに付加した第1フラグによって、画素への画像データ供給による消費電力を発生させることなくコモン反転用のタイミング信号を生成することができるという効果を奏する。

【0028】

本発明の表示装置は、上記課題を解決するために、上記走査信号は、各水平表示期間において、上記画像データの全てがデータ信号線に出力された後に、上記画像データを上記画素メモリに書き込み可能とする信号であることを特徴としている。

【0029】

上記の発明によれば、各水平表示期間において、画像データの全てがデータ信号線に出力された後に画像データが画素メモリに書き込まれるので、画像データがデータ信号線に順次出力されている期間にデータ信号線の電位に乱れが生じても、画素メモリへの記憶に影響が及びにくいという効果を奏する。

【0030】

本発明の表示装置は、上記課題を解決するために、上記シリアルデータに、上記画素メモリに記憶させる上記画像データが含まれているか否かを示す第2フラグが付加されており、上記表示ドライバは、上記シリアルクロックのタイミングを用いて、上記シリアルデータから上記第2フラグを取り出して、上記第2フラグが、上記シリアルデータに、上記画素メモリに記憶させる上記画像データが含まれていることを示すときに、上記シリアルデータから上記画像データを取り出して上記画素メモリに記憶させることを特徴としている。

【0031】

上記の発明によれば、第2フラグによって、シリアルデータに、画素メモリに記憶させる画像データが含まれていることを認識することができるので、画像データが含まれているときにのみ、画素への画像データ供給による消費電力の発生を許容するようにすることができるという効果を奏する。

【0032】

本発明の表示装置は、上記課題を解決するために、上記シリアルデータに、全ての上記画素の表示を初期化するか否かの指示を行う第3フラグが付加されており、上記表示ドライバは、上記シリアルクロックのタイミングを用いて、上記シリアルデータから上記第3フラグを取り出して、上記第3フラグが、全ての上記画素の表示を初期化する指示を行うものであるときに、全ての上記画素の表示を初期化することを特徴としている。

【0033】

上記の発明によれば、第3フラグによって、全ての上記画素の表示を初期化することを認識することができるので、シリアルデータに初期化の画像データを含めなくても初期化することが可能となる。従って、画素へ個別に画像データを供給する必要がなくなり、その分の消費電力を削減することができるという効果を奏する。

【0034】

上記第1フラグは、さらに、コモン電極の電圧の極性を指示するフラグとして上記シリアルデータに付加されていることを特徴とする請求項1または2に記載の表示装置。

【0035】

上記の発明によれば、コモン電極の電圧の極性を1フレームごとに反転させることができるという効果を奏する。

【0036】

本発明の表示装置は、上記課題を解決するために、上記シリアル伝送において、表示を行うか否か、すなわち表示ドライバを動作させるか否かを示すシリアルチップセレクト信号が、上記シリアルデータおよび上記シリアルクロックとは異なる配線によって伝送されることを特徴としている。

【0037】

上記の発明によれば、表示ドライバは、シリアルチップセレクト信号によって動作を行わない期間を認識することによりシリアルデータを取り込まないようにすることができるので、シリアル伝送を停止させることができ、その分の消費電力を削減することができるという効果を奏する。

【0038】

本発明の表示装置は、上記課題を解決するために、上記画素内のアナログスイッチはCMOS回路によって作成されていることを特徴としている。

【0039】

上記の発明によれば、画素内のアナログスイッチがCMOS回路によって作成されていることにより、TFTのようなVth(しきい値)が高いデバイスでも、低電圧で駆動することが可能であるとともに、制御信号とデータ信号とを同一電圧とすることができる。従って、表示の駆動回路に用いる電源振幅を小さくすることができて、消費電力を削減することができるという効果を奏する。

【0040】

本発明の表示装置は、上記課題を解決するために、上記表示ドライバは、表示パネルにモノリシックに作り込まれていることを特徴としている。

【0041】

上記の発明によれば、表示ドライバを、表示パネルにモノリシックにCMOS回路で形成するので、表示装置の小型化およびプロセスの簡略化を図ることができるという効果を奏する。

【0042】

本発明の表示装置は、上記課題を解決するために、上記画素の表示素子に高分子分散型液晶が用いられていることを特徴としている。

【0043】

上記の発明によれば、表示素子に高分子分散型液晶を用いるので、液晶表示装置を偏光板などを省略した高明度の表示装置として、しかも低電圧で駆動することができるという効果を奏する。特に、画素に画素メモリを備える低消費電力の表示装置では、消費電力の削減を飛躍的に向上させることができるという効果を奏する。

【0044】

本発明の表示装置は、上記課題を解決するために、上記画素の表示素子に高分子ネットワーク型液晶が用いられていることを特徴としている。

【0045】

上記の発明によれば、表示素子に高分子ネットワーク型液晶を用いるので、液晶表示装置を偏光板などを省略した高明度の表示装置として、しかも低電圧で駆動することができるという効果を奏する。特に、画素に画素メモリを備える低消費電力の表示装置では、消費電力の削減を飛躍的に向上させることができるという効果を奏する。

【0046】

本発明の表示装置は、上記課題を解決するために、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号をダミーのシフトレジスタにより所定段シフトさせた第1エンドビットと、上記第1エンドビットをさらに上記ダミーのシフトレジスタにより1段だけシフトさせた第2エンドビットとを生成し、上記データ信号線ドライバの上記次の水平期間のタイミング信号を、上記第2エンドビットを用いて生成し、上記走査信号線ドライバのシフトレジスタに入力するタイミング信号を、上記第1エンドビットおよび上記第2エンドビットを用いて生成することを特徴としている。

【0047】

本発明の携帯端末は、上記課題を解決するために、上記表示装置をディスプレイとして備えていることを特徴としている。

【0048】

上記の発明によれば、携帯端末に対して、低消費電力化の要請を容易に満たすことができるという効果を奏する。

【0049】

本発明の他の目的、特徴、および優れた点は、以下に示す記載によって十分分かるであろう。また、本発明の利点は、添付図面を参照した次の説明によって明白になるであろう。

【図面の簡単な説明】

【0050】

【図1】本発明の実施形態を示すものであり、表示装置の主要部の接続関係を示す回路ブロック図である。

【図2】データ更新モードにおけるシリアル伝送の各信号の波形を示すタイミングチャートである。

【図3】表示モードにおけるシリアル伝送の各信号の波形を示すタイミングチャートである。

【図4】表示装置の全体構成を示すブロック図である。

【図5】画素および画素メモリの構成を示す回路図である。

【図6】Vcomドライバの出力波形を示すタイミングチャートである。

【図7】シリアル−パラレル変換部の構成を示す回路図である。

【図8】END−BIT保持部の構成を示す回路図である。

【図9】ソーススタートパルス生成部の構成を示す回路図である。

【図10】ゲートドライバ制御信号生成部の構成を示す回路図である。

【図11】Vcomドライバの構成を示す回路図である。

【図12】シリアル−パラレル変換部の信号波形を示すタイミングチャートである。

【図13】ゲートドライバ制御信号生成部の信号波形を示すタイミングチャートである。

【図14】従来技術を示すものであり、表示装置の構成を示す回路ブロック図である。

【図15】従来技術を示すものであり、携帯電話の構成を示すブロック図である。

【図16】従来技術を示すものであり、表示ドライバの構成を示すブロック図である。

【発明を実施するための形態】

【0051】

本発明の一実施形態について図1ないし図13に基づいて説明すると以下の通りである。

【0052】

図4に、本実施形態に係る液晶表示装置(表示装置)21の構成を示す。

【0053】

液晶表示装置21は、例えば携帯電話などの携帯端末に搭載されているディスプレイデバイスであり、表示パネル21aおよびフレキシブルプリント基板(FPC)21bを備えている。表示パネル21aは、各種回路がモノリシックに作り込まれたものであり、フレキシブルプリント基板21bは、アプリケーションプロセッサなどのCPUに制御される3線のシリアルインタフェースバスI/F BUSを通したシリアル伝送によって、シリアルデータSI、シリアルチップセレクト信号SCS、および、シリアルクロックSCLKを受け、これらをFPC端子21cを通して表示パネル21aに供給する。シリアル伝送はマイクロコントローラなど他の制御手段によって制御されてもよい。また、フレキシブルプリント基板21bは、外部から供給される5Vの電源VDD、および、0Vの電源VSSを、FPC端子21cを通して表示パネル21aに供給する。

【0054】

表示パネル21aは、アクティブエリア22、バイナリドライバ(データ信号線ドライバ)23、ゲートドライバ(走査信号線ドライバ)24、タイミングジェネレータ25、および、Vcomドライバ26を備えている。バイナリドライバ23、ゲートドライバ24、タイミングジェネレータ25、および、Vcomドライバ26は表示ドライバを構成している。

【0055】

アクティブエリア22はRGBの画素が、例えば96×RGB×60のマトリクス状に配置された領域であり、各画素は画素メモリを備えている。バイナリドライバ23は画像データをソースラインを通してアクティブエリア22に供給する回路であり、シフトレジスタ23aおよびデータラッチ23bを備えている。ゲートドライバ24はアクティブエリア22の画像データを供給すべき画素をゲートラインを通して選択する。タイミングジェネレータ25はフレキシブルプリント基板21bから供給される信号を基に、バイナリドライバ23、ゲートドライバ24、および、Vcomドライバ26に供給する信号を生成する。

【0056】

図5に、アクティブエリア22に配置された各画素PIXの構成を、画素メモリの回路を詳細に表しながら示す。

【0057】

画素PIXは、液晶容量CL、画素メモリ30、アナログスイッチ31、アナログスイッチ33・34を備えている。さらに画素メモリ30は、アナログスイッチ32およびインバータ35・36を備えている。

【0058】

液晶容量CLは、極性出力OUTとコモン電極の電圧であるコモン出力Vcomとの間に、ここでは高分子分散型液晶(PDLC:Polymer Dispersed Liquid Crystal)や、高分子ネットワーク型液晶(PNLC:Polymer Network Liquid Crystal)などの光分散型液晶を用いて構成されている。アナログスイッチ31〜34およびインバータ35・36はCMOS回路で構成されている。

【0059】

アナログスイッチ31は、ソースライン出力SLと画素メモリ30との間に挿入されており、そのPMOSトランジスタ31aのゲートはゲートライン反転出力GLBに接続されているとともに、NMOSトランジスタ31bのゲートはゲートライン出力GLに接続されている。画素メモリ30において、アナログスイッチ32は、インバータ35の入力とインバータ36の出力との間に挿入されており、そのPMOSトランジスタ32aのゲートはゲートライン出力GLに接続されているとともに、NMOSトランジスタ32bのゲートはゲートライン反転出力GLBに接続されている。インバータ35の入力はアナログスイッチ31のソースライン出力SL側とは反対側の接続端子に接続されている。インバータ35の出力はインバータ36の入力に接続されている。インバータ35・36は、電源VDDをHigh側電源に用い、電源VSSをLow側電源に用いている。

【0060】

アナログスイッチ33は、黒極性用出力VAと極性出力OUTとの間に挿入されており、そのPMOSトランジスタ33aのゲートはインバータ35の出力に接続されているとともに、NMOSトランジスタ33bのゲートはインバータ35の入力に接続されている。アナログスイッチ34は、白極性用出力VBと極性出力OUTとの間に挿入されており、そのPMOSトランジスタ34aのゲートはインバータ35の入力に接続されているとともに、NMOSトランジスタ34bのゲートはインバータ35の出力に接続されている。

【0061】

上記のコモン出力Vcom、黒極性用出力VA、および、白極性用出力VBの波形を図6に示す。これらの信号はVcomドライバ26によって生成される。コモン出力Vcomは、1フレームごとに正極性と負極性とが切り替わる5Vp−pのパルス波形をなす。極性の切り替わり周期は、この他にも所定水平期間ごとなど、任意に設定が可能である。黒極性用出力VAは、コモン出力Vcomに対して位相が反転した5Vp−pのパルス波形をなす。白極性用出力VB(ノーマリーホワイトの場合)は、コモン出力Vcomと同相の5Vp−pのパルス波形をなす。

【0062】

図5において、バイナリドライバ23からソースライン出力SLとしてHighレベル(5V)が出力された場合には、Highレベル(5V)のゲートライン出力GLおよびLowレベル(0V)のゲートライン反転出力GLBによって選択される画素PIXのアナログスイッチ31が導通することにより、アナログスイッチ33が導通するとともにアナログスイッチ34が遮断される。従って、極性出力OUTには黒極性用出力VAが出力される。液晶容量CLには黒極性用出力VAとコモン出力Vcomとの差の電圧として5Vが印加され、画素PIXは黒表示状態となる。

【0063】

次いで、ゲートライン出力GLがLowレベル(0V)、ゲートライン反転出力GLBがHighレベル(5V)になると、アナログスイッチ31が遮断されるとともにアナログスイッチ32が導通するので、画素メモリ30にHighレベルが記憶される。この記憶データは、同じ画素PIXが次に選択されてアナログスイッチ31が導通するまで保持される。

【0064】

一方、図5において、バイナリドライバ23からソースライン出力SLとしてLowレベル(0V)が出力された場合には、Highレベル(5V)のゲートライン出力GLおよびLowレベル(0V)のゲートライン反転出力GLBによって選択される画素PIXのアナログスイッチ31が導通することにより、アナログスイッチ33が遮断されるとともにアナログスイッチ34が導通する。従って、極性出力OUTには白極性用出力VBが出力される。液晶容量CLには白極性用出力VBとコモン出力Vcomとの差の電圧として0Vが印加され、画素PIXは白表示状態となる。

【0065】

次いで、ゲートライン出力GLがLowレベル(0V)、ゲートライン反転出力GLBがHighレベル(5V)になると、アナログスイッチ31が遮断されるとともにアナログスイッチ32が導通するので、画素メモリ30にLowレベルが記憶される。この記憶データは、同じ画素PIXが次に選択されてアナログスイッチ31が導通するまで保持される。

【0066】

次に、図1に、タイミングジェネレータ25と、バイナリドライバ23、ゲートドライバ24、および、Vcomドライバ26との間の接続関係を示す。

【0067】

タイミングジェネレータ25は、シリアル−パラレル変換部25a、ソーススタートパルス生成部25b、END−BIT保持部25c、および、ゲートドライバ制御信号生成部25dを備えている。タイミングジェネレータ25は、パネル外部から入力されるシリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSから、モード信号MODE、フレーム信号FRAME、全クリア信号ACL、ソースクロック(データ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号)SCK・SCKB、ソーススタートパルス(水平期間のタイミング信号)SSP、ゲートクロック(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号)GCK1B・GCK2B、ゲートスタートパルスGSP、ゲートイネーブル信号(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号、走査信号)GEN、および、イニシャル信号INIを生成する。タイミングジェネレータ25からバイナリドライバ23へは、ソーススタートパルスSSP、および、イニシャル信号INIが供給され、タイミングジェネレータ25からゲートドライバ24へは、ゲートクロックGCK1B・GCK2B、ゲートスタートパルスGSP、ゲートイネーブル信号GEN、および、イニシャル信号INIが供給され、タイミングジェネレータ25からVcomドライバ26へは、フレーム信号FRAMEが供給される。なお、ソースクロックSCK・SCKBはここではタイミングジェネレータ25の内部で用いられるが、後述するように1水平期間ごとのソーススタートパルスSSPを生成するのに用いられており、バイナリドライバ23のシフトレジスタ23aを動作させるクロック信号である。

【0068】

シリアルパラレル−変換部25aには、フレキシブルプリント基板21bからシリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSが入力される。前述したように、シリアルインタフェースバスI/F BUSは3線式であるので、シリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSは互いに異なる配線によって伝送される。これらの信号を図2および図3に示す。

【0069】

シリアルデータSIは、2値からなるRGBのデジタル画像データがシリアルに配列されたものに、1フレームごとに先頭に設けられたモード選択期間にフラグD0・D1・D2が付加された信号である。

【0070】

画像データは、図2のような、画素メモリ30に画像データを書き込むデータ更新モードにおいては、1水平表示期間分のRGBデータが時系列に配列されたものが、水平表示期間順に配列されている。また、隣接する水平表示期間どうしの水平帰線期間には、ダミーデータdR1・dG1・dB1…が配置されるとともに、先頭の水平表示期間のフラグD0・D1・D2に相当する期間に3つのダミーデータDMY・DMY・DMYが配置されている。これらのダミーデータはHighでもLowでもよい。

【0071】

また、画像データは、図3のような、画素メモリ30に記憶されている画像データを保持する表示モードにおいては、図2のデータ更新モードにおける画像データおよびダミーデータが全てダミーデータDMYで置き換わったものである。

【0072】

フラグ(第2フラグ)D0はモードフラグであり、Highの場合には画素メモリ30に画像データを書き込むデータ更新モードを行うようにタイミングジェネレータ25に指示し、Lowの場合には画素メモリ30に記憶されている画像データを保持する表示モードを行うようにタイミングジェネレータ25に指示する。フラグ(第1フラグ)D1はフレーム反転フラグであり、Highの場合にはコモン出力VcomをHighに設定することをタイミングジェネレータ25に指示し、Lowの場合にはコモン出力VcomをLowに設定することをタイミングジェネレータ25に指示する。すなわち、フラグD1は、1フレームごとに反転するコモン出力Vcomの極性を指示するフラグである。フラグ(第3フラグ)D2は全クリアフラグであり、Highの場合にはそのフレームにおいて全ての画素PIXに白表示データを書き込むことをタイミングジェネレータ25に指示し、Lowの場合にはそのフレームにおいて全ての画素PIXに、供給する画像データを書き込むことを指示する。これによって、フラグD2は、Highの場合に、全ての画素PIXの表示を初期化する指示を行う。フラグD2は通常はLowである。

【0073】

シリアルクロックSCLKは、シリアルデータSIのフラグを含めた各データを取り出すための同期用クロックである。このシリアルクロックSCLKの立ち上がりタイミングおよび立ち下がりタイミングの一例を挙げると、以下の通りである。シリアルクロックSCLKの立ち上がりタイミングは、フラグD0〜D2に対しては各フラグの伝送開始タイミングから時間tsSCLKだけ経過した時点であり、画像データR・G・Bに対しては各画像データの伝送開始タイミングから時間twSCLKLだけ経過した時点である。tsSCLK=twSCLKLであって、シリアルクロックSCLKのLow期間に等しい。また、シリアルクロックSCLKの立ち下がりタイミングは、フラグD0〜D2に対してはシリアルクロックSCLKの立ち上がりタイミングから時間tsSCLKだけ経過した時点であってフラグの伝送終了タイミング(すなわち次のフラグまたはデータへの切り替わりタイミング)であり、画像データR・G・Bに対してはシリアルクロックSCLKの立ち上がりタイミングから時間twSCLKHだけ経過した時点であって各画像データの伝送終了タイミング(すなわち次のフラグまたはデータへの切り替わりタイミング)である。tsSCLK=twSCLKHであって、シリアルクロックSCLKのHigh期間に等しい。ここではシリアルクロックSCLKのデューティは50%である。

【0074】

シリアルチップセレクト信号SCSは、CPUからシリアルインタフェースバスI/F BUSを通してタイミングジェネレータ25にシリアルデータSIおよびシリアルクロックSCLKを伝送するときに期間twSCSHだけHighとなる信号である。シリアルデータSIおよびシリアルクロックSLCKを伝送するフレームについての、シリアルデータSIの伝送開始タイミングよりも時間tsSCSだけ前にHighとなり、シリアルデータSIの伝送終了タイミングよりも時間thSCSだけ後にLowとなる。また、上記High期間の後に期間twSCSLだけLowとなり、期間twSCSHと期間twSCSLとを合わせて垂直帰線期間を含む1フレーム期間tVとなる。

【0075】

図2のデータ更新モードで画素メモリ30に書き込まれた画像データは、図3の表示モードで保持され続ける。データ更新モードでも表示モードでも、シリアルデータSIにはフラグD0・D1・D2が付加されており、フラグD1は1フレームごとにHighとLowとが切り替わっていく。従って、フラグD1は1フレームの開始を指示するフラグでもある。

【0076】

シリアル−パラレル変換部25aは、このようにして入力されるシリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSから、フラグD0・D1・D2のそれぞれと、RのデータDR、GのデータDG、および、BのデータDBとを抽出する。フラグD0はモード信号MODEとして、フラグD1はフレーム信号D1として、フラグD2は全クリア信号ACLとして、それぞれ他の回路での信号生成動作に用いられる。また、データDR・DG・DBはバイナリドライバ23のデータラッチ23bに供給される。

【0077】

また、シリアル−パラレル変換部25aは、シリアルデータSI、シリアルクロックSCLK、および、シリアルチップセレクト信号SCSから、ソースクロックSCK・SCKBおよびイニシャル信号INIを生成する。ソースクロックSCK・SCKBはバイナリドライバ23に供給され、イニシャル信号INIは他の回路での信号生成動作に用いられる。

【0078】

次に、ソーススタートパルス生成部25bは、シリアル−パラレル変換部25bから入力されるモード信号MODEおよびソースクロックSCK・SCKBから第1水平表示期間のソーススタートパルスSSPを生成してバイナリドライバ23のシフトレジスタ23aに供給する。この第1水平表示期間のソーススタートパルスSSPは、モード信号MODEのHighへの立ち上がりタイミングを用いて生成することができ、第2水平表示期間以降の水平表示期間については、後述するEND−BIT保持部25cが生成した第2エンドビットEND−BIT2を用いて生成することができる。

【0079】

END−BIT保持部25cは、バイナリドライバ23のシフトレジスタ23aの最終段の出力から、第1エンドビットEND−BIT1および第2エンドビットEND−BIT2を生成して、ゲートドライバ制御信号生成部25dに供給する。第1エンドビットEND−BIT1は、シフトレジスタ23aの最終段の出力をさらにダミーのシフトレジスタにより所定段シフトさせたものであり、第2エンドビットEND−BIT2は、第1エンドビットEND−BIT1をさらに上記ダミーのシフトレジスタにより1段だけシフトさせたものである。

【0080】

ゲートドライバ制御信号生成部25dは、第1エンドビットEND−BIT1、第2エンドビットEND−BIT2、モード信号MODE、全クリア信号ACLから、ゲートクロックGCK1B・GCK2B、ゲートスタートパルスGSP、および、ゲートイネーブル信号GENを生成して、ゲートドライバ24へ供給する。

【0081】

次に、バイナリドライバ23において、シフトレジスタ23aはタイミングジェネレータ25のソーススタートパルス生成部25bから入力されるソーススタートパルスSSPと、タイミングジェネレータ25のシリアルパラレル−変換部25aから入力されるイニシャル信号INIとから、各段SRの出力を生成する。データラッチ23bは1stラッチ回路23cと全クリア回路23dとを備えている。1stラッチ回路23cは、シフトレジスタ23aの各段SRの出力タイミングで、タイミングジェネレータ25のシリアルパラレル−変換部25aから入力されるデータDR・DG・DBを順次ラッチして、対応するソースラインSL(RGBのそれぞれについてSL1〜SL96)に出力する。全クリア回路23dは、シリアルデータSIのフラグD2がHighである場合に、タイミングジェネレータ25のシリアルパラレル−変換部25aからアクティブな全クリア信号ACLが入力されると、全てのソースラインSLに白表示データを出力する。

【0082】

次に、ゲートドライバ24は、シフトレジスタ24aと、複数のバッファ24bおよび反転バッファ24cとを備えている。シフトレジスタ24aは、タイミングジェネレータ25のゲートドライバ制御信号生成部25dから出力された、ゲートクロックGCK1B・GCK2B、ゲートスタートパルスGSP、および、ゲートイネーブル信号GENと、シリアル−パラレル変換部25aから入力されるイニシャル信号INIとから、各段SRの出力を生成する。バッファ24bと反転バッファ24cとは1つずつ対として画素行ごとに設けられている。1対のバッファ24bと反転バッファ24cとの各入力はシフトレジスタ24aの対応する段SRの出力に接続されており、バッファ24bの出力は対応するゲートラインGL(GL1〜GL60)に、反転バッファ24cの出力は対応するゲートラインGLB(GLB1〜GLB60)に、それぞれ接続されている。

【0083】

次に、Vcomドライバ26は、タイミングジェネレータ25のシリアルパラレル−変換部25aから入力されるフレーム信号FRAMEと、電源VDD・VSSとから、コモン出力Vcom、黒極性用出力VA、および、白極性用出力VBを生成してアクティブエリア22に供給する。

【0084】

次に、図7に、シリアル−パラレル変換部25aの詳細な構成例を示す。

【0085】

シリアルデータSIは、縦続に接続されたDフリップフロップ41・42・43を順に通され、3段目のDフリップフロップ43の出力S2がDフリップフロップ44を通されるとモード信号MODEが取り出され、2段目のDフリップフロップ42の出力S1がDフリップフロップ45を通されるとフレーム信号FRAMEが取り出され、初段のDフリップフロップ41の出力S0がDフリップフロップ46を通されると全クリア信号ACLが取り出される。また、画像データがRGBの順に時系列に並んでいるとすると、出力S2がDフリップフロップ47を通されるとデータDRが取り出され、出力S1がDフリップフロップ48を通されるとデータDGが取り出され、出力S0がDフリップフロップ49を通されるとデータDBが取り出される。

【0086】

ここで、Dフリップフロップ41・42・43のHighアクティブのクロック端子CKにはシリアルクロックSCLKが入力され、Dフリップフロップ44・45・46のLowアクティブのクロック端子CKには2入力のNORゲート55の出力DENが入力され、Dフリップフロップ47・48・49のLowアクティブのクロック端子CKにはDフリップフロップ51の出力Aが入力される。

【0087】

NORゲート55の一方の入力はDフリップフロップ53の出力に接続されており、他方の入力は2入力のNANDゲート54の出力Cに接続されている。Dフリップフロップ53の入力は電源VDDに接続されており、Lowアクティブのクロック端子CKはDフリップフロップ52の出力Bに接続されている。NANDゲート54の一方の入力は出力Bに接続されており、他方の入力は出力Aに接続されている。Dフリップフロップ51の入力は出力Cに接続されている。Dフリップフロップ52の入力は出力Aに接続されている。Dフリップフロップ51・52のLowアクティブのクロック端子CKにはシリアルクロックSCLKが入力される。

【0088】

また、ソースクロックSCKBは、Dフリップフロップ56の出力をインバータ57を通して得られ、ソースクロックSCKは、インバータ57の出力をインバータ58を通して得られる。Dフリップフロップ56の入力はインバータ57の出力に接続されており、Highアクティブのクロック端子CKは出力Bに接続されている。

【0089】

上記各Dフリップフロップにおいて、Highアクティブのクロック端子CKではポジティブエッジトリガが行われ、Lowアクティブのクロック端子CKでは、ネガティブエッジトリガが行われる。

【0090】

また、Dフリップフロップ44〜53・56のリセット端子Rには、シリアルチップセレクト信号SCSが入力される。イニシャル信号INIはシリアルチップセレクト信号SCSそのものである。

【0091】

図12のタイミングチャートに、シリアルクロックSCLK、出力A・B・C、および、ソースクロックSCK・SCKB、および、出力DENの波形を示す。

【0092】

次に、図8に、END−BIT保持部25cの詳細な構成例を示す。

【0093】

まず、バイナリドライバ23のシフトレジスタ23aはセットリセットフリップフロップが縦続に接続された構成である。ここでは、最後の2つの(95段目および96段目の)セットリセットフリップフロップB95・B96が図示されており、セットリセットフリップフロップB95のセット入力端子には前段のセットリセットフリップフロップB94の出力Q(B94)が入力されている。END−BIT保持部25cもシフトレジスタ23aの最終段に続いて同じ縦続接続関係により、ダミーのセットリセットフリップフロップDMY1・DMY2・DMY3・DMY4が順に接続された構成である。これらのセットリセットフリップフロップは、次段の出力がリセット信号として入力されるようになっているが、セットリセットフリップフロップDMY4については自段の出力を2つのインバータで遅延させた信号を、それぞれリセット信号としている。

【0094】

セットリセットフリップフロップDMY2の出力が第1エンドビットEND−BIT1、セットリセットフリップフロップDMY3の出力が第2エンドビットEND−BIT2として得られる。

【0095】

次に、図9に、ソーススタートパルス生成部25bの詳細な構成例を示す。

【0096】

2入力のNORゲート61における一方のLowアクティブの入力にモード信号MODEが入力され、他方のHighアクティブな入力に第2エンドビットEND−BIT2が入力される。NORゲート61の出力はDラッチ62に入力され、Dラッチ62の出力はDラッチ63に入力される。Dラッチ62のイネーブル端子ENおよびDラッチ63のイネーブル端子ENBにはシリアル-パラレル変換部25aで生成したソースクロックSCKBが、Dラッチ62のイネーブル端子ENBおよびDラッチ63のイネーブル端子ENにはシリアル-パラレル変換部25aで生成したソースクロックSCKが、それぞれ入力される。Dラッチ62の出力とDラッチ63の出力とは2入力のNORゲート64に入力される。NORゲート64の出力とモード信号MODEとは2入力のNANDゲート65に入力され、NANDゲート65の出力がソーススタートパルスSSPとなる。

【0097】

次に、図10に、ゲートドライバ制御信号生成部25dの詳細な構成例を示す。

【0098】

Dフリップフロップ71のHighアクティブのクロック端子CKとLowアクティブのクロック端子CKBに第1エンドビットEND−BIT1が入力される。Dフリップフロップ71の出力はDフリップフロップ72に入力される。Dフリップフロップ72のLowアクティブのクロック端子CKとHighアクティブのクロック端子CKBとに第2エンドビットEND−BIT2が入力される。Dフリップフロップ72の出力はDフリップフロップ71の入力となる。また、Dフリップフロップ71・72の各出力は、それぞれ2入力のNANDゲート73および2入力のNORゲート76の両入力となる。NANDゲート73の出力および全クリア信号ACLは、2入力のNANDゲート74に入力される。NANDゲート74の出力とイニシャル信号INIとは2入力のNANDゲート75に入力される。NANDゲート75の出力はゲートクロックGCK2Bとなる。

【0099】

また、NORゲート76の出力とモード信号MODEとは2入力のNANDゲート77に入力される。NANDゲート77の出力と全クリア信号ACLとは2入力のNANDゲート78に入力される。NANDゲート78の出力とイニシャル信号INIとは2入力のNANDゲート79に入力される。NANDゲート79の出力はゲートクロックGCK1Bとなる。

【0100】

また、モード信号MODEはDラッチ80に入力される。Dラッチ80のイネーブル端子EN・ENBには第1エンドビットEND−BIT1が入力される。Dラッチ80の出力は2入力のNORゲート81のHighアクティブの入力となり、モード信号MODEはNORゲート81のLowアクティブの入力となる。NORゲート81の出力と全クリア信号ACLとは2入力のNORゲート82に入力される。NORゲート82の出力とイニシャル信号INIとは2入力のNORゲート83に入力される。NORゲート83の出力はゲートスタートパルスGSPとなる。

【0101】

また、第1エンドビットEND−BIT1および第2エンドビットEND−BITは2入力のNORゲート84に入力される。NORゲート84の出力はDフリップフロップ85のLowアクティブのクロック端子CKとHighアクティブのクロック端子CKBとに入力される。Dフリップフロップ85の出力はインバータ86に入力され、Dフリップフロップ85の入力はインバータ86の出力に接続されている。インバータ86の出力と全クリア信号ACLとは2入力のNORゲート87に入力される。NORゲート87の出力と全クリア信号ACLとはNORゲート88に入力される。NORゲート88の出力はゲートイネーブル信号GENとなる。

【0102】

Dフリップフロップ71・72・85およびDラッチ80のイニシャル端子INIにはイニシャル信号INIが入力される。Dフリップフロップ71はポジティブエッジトリガ型であり、Dフリップフロップ72・85はネガティブエッジトリガ型である。

【0103】

図13のタイミングチャートに、ゲートクロックGCK1B・GCK2B、ゲートイネーブル信号GEN、および、ゲートライン出力GL(GL1・GL2)の波形を示す。シフト1は、最初のゲートライン出力GL1に対応するデータDR・DG・DBがソースラインSLに出力されている期間を示し、シフト2は、2番目のゲートライン出力GL2に対応するデータDR・DG・DBがソースラインSLに出力されている期間を示している。水平表示期間の最後にゲートイネーブル信号GENを用いて画素メモリ30に一斉に画像データを書き込むので、データDR・DG・DBがソースラインSLに順次出力されている期間にソースラインSLの電位に乱れが生じても、画素メモリ30への記憶に影響が及びにくい。

【0104】

図11に、Vcomドライバの詳細な構成を示す。

【0105】

フレーム信号FRAMEがバッファを通して、それぞれC接点相当のスイッチSW1・SW2・SW3の制御信号として入力される。スイッチSW1・SW2・SW3は、順にコモン出力Vcom、黒極性用出力VA、白極性用出力VBの電圧を出力するスイッチである。フレーム信号FRAMEがHighとLowとで切り替わる度に、スイッチSW1・SW2・SW3は、順に電源VDD・VSS・VDDの組み合わせと、電源VSS・VDD・VSSの組み合わせとの間で切り替わるように電源を選択する。

【0106】

以上に述べたように、本実施形態の表示装置は、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、上記シリアルデータに、1フレーム期間の開始を指示する第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、上記第1フラグおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、次の水平期間が存在する場合には、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に上記次の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力し、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に、上記表示ドライバが備える走査信号線ドライバのシフトレジスタに入力するタイミング信号を生成し、各上記水平期間のタイミング信号と、上記走査信号線ドライバから出力される走査信号とを用いて、上記画像データを画素に書き込む。

【0107】

上記の構成によれば、表示ドライバは、シリアル伝送されたシリアルデータから、シリアルクロックのタイミングを用いて第1フラグと画像データとを取り出す。そして、第1フラグから1フレーム期間の最初の水平期間のタイミング信号を生成して、データ信号線ドライバのシフトレジスタに入力し、2番目以降の水平期間についてはデータ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に次の水平期間のタイミング信号を順次生成していく。

【0108】

従って、表示ドライバは、シリアル伝送による直接制御によって画像データを画素に書き込むためのタイミング信号を生成することができるので、わざわざ発振器などを用いて生成することなく、容易である。

【0109】

以上により、画像データを画素に書き込むためのタイミング信号をドライバIC内で容易に生成することのできるという効果を奏する。

【0110】

また、以上に述べたように、本実施形態の表示装置は、画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、上記シリアルデータに、コモン電極の電圧の極性を指示する第1フラグが付加されており、上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグを取り出して、上記シリアルデータに基づいた表示を行うとともに、取り出した上記第1フラグに従った極性の上記コモン電極の電圧を供給する。

【0111】

上記の構成によれば、表示ドライバは、シリアル伝送されたシリアルデータから、シリアルクロックのタイミングを用いて第1フラグを取り出し、第1フラグに従ってコモン電極の電圧の極性を決定して表示を行う。従って、表示ドライバは、シリアル伝送による直接制御によってコモン反転用のタイミング信号を生成することができるので、発振器や、コモン反転用のタイミング信号生成に関して外部からの制御を行うための特別な制御端子が不要となる。従って、表示ドライバの回路規模を小さくすることができる。

【0112】

以上により、コモン反転用のタイミング信号を小さな回路規模で生成することのできる表示装置を実現することができるという効果を奏する。

【0113】

なお以上の例では、フラグD0・D1・D2を1フレームの先頭に配置したが、これに限らず、タイミングジェネレータ25への指示を行いたい任意のタイミングに各フラグを配置することが可能である。例えば、フラグD1のHighとLowとを、水平期間の整数倍の期間ごとに切り換えたいときには、各水平期間の先頭に配置することなどが可能である。

【0114】

また、以上の例では、各種タイミング信号を生成するのにシリアルチップセレクト信号SCSを用いているが、これは必ずしも必要ではなく、例えばシリアル−パラレル変換部25aが、常にシリアルデータに対する受信のイネーブル状態にあるようにすればよい。

【0115】

また、以上の例ではアクティブエリア22が画素メモリ30を備える構成についての説明であったが、これに限ることはなく、フラグD0によってデータ更新モードと表示モードとを区別しないような構成を備えれば、画素メモリを備えていないアクティブエリアを有する表示装置にも本発明が適用可能である。

【0116】

また、以上の例では、バイナリドライバ23のシフトレジスタ23aが、初段のセット入力にソーススタートパルスSSPが入力されるだけでシフト動作が可能となる構成であったので、シリアル−パラレル変換部25aによって生成されたソースクロックSCK・SCKBは、ソーススタートパルス生成部25bにおいてソーススタートパルスSSPを生成するのに用いられることにより、データ信号線ドライバのシフトレジスタを動作させるクロック信号として機能するものであった。しかし、これに限ることはなく、データ信号線ドライバのシフトレジスタが各段へのクロック信号の入力によってシフト動作を行う構成であって、生成されたソースクロックSCK・SCKBが、ソーススタートパルスSSPを生成するのに用いられるとともに、データ信号線ドライバのシフトレジスタの各段に入力されて当該シフトレジスタの各段の動作に関わることにより、データ信号線ドライバのシフトレジスタを動作させるクロック信号として機能することも可能である。

【0117】

本発明は上述した実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能である。すなわち、請求項に示した範囲で適宜変更した技術的手段を組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。例えばEL表示装置にも適用可能である。

【産業上の利用可能性】

【0118】

本発明は、携帯端末に特に好適に使用することができる。

【符号の説明】

【0119】

21 液晶表示装置(表示装置)

23 バイナリドライバ

23a シフトレジスタ(データ信号線ドライバのシフトレジスタ)

23b データラッチ

24 ゲートドライバ

24a シフトレジスタ(走査信号線ドライバのシフトレジスタ)

25 タイミングジェネレータ

26 Vcomドライバ

30 画素メモリ

D0 フラグ(第2フラグ)

D1 フラグ(第1フラグ)

D2 フラグ(第3フラグ)

GCK1B、GCKB2

ゲートクロック(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号)

GEN ゲートイネーブル信号(ゲート信号線ドライバのシフトレジスタに入力するタイミング信号、走査信号)

SCK、SCKB

ソースクロック(データ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号)

SSP ソーススタートパルス(水平期間のタイミング信号)

I/F BUS シリアルインタフェースバス

SI シリアルデータ

SCLK シリアルクロック

SCS チップセレクト信号

SL ソースライン(データ信号線)

Vcom コモン出力(コモン電極の電圧)

【特許請求の範囲】

【請求項1】

画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、

フレーム毎に、上記シリアルデータに、当該フレームにおいて画素に上記画像データを書き込むか否かを示す第1フラグが付加されており、

上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、

上記第1フラグが画素に上記画像データを書き込むことを示す場合、当該フレームにおいて第1論理値から第2論理値に変化するモード信号を生成し、

上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、

上記モード信号が上記第1論理値から上記第2論理値に変化するタイミングおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力することを特徴とする表示装置。

【請求項2】

次の水平期間が存在する場合には、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に上記次の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力することを特徴とする請求項1に記載の表示装置。

【請求項3】

上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に、上記表示ドライバが備える走査信号線ドライバに入力するタイミング信号を生成し、

各上記水平期間のタイミング信号と、上記走査信号線ドライバから出力される走査信号とを用いて、上記画像データを画素に書き込むことを特徴とする請求項2に記載の表示装置。

【請求項4】

請求項1から3までのいずれか1項に記載の表示装置をディスプレイとして備えていることを特徴とする携帯端末。

【請求項1】

画像データがシリアルデータに含められてシリアル伝送によって表示ドライバに供給されるアクティブマトリクス型の表示装置であって、

フレーム毎に、上記シリアルデータに、当該フレームにおいて画素に上記画像データを書き込むか否かを示す第1フラグが付加されており、

上記表示ドライバは、上記シリアル伝送に用いられる、上記シリアルデータとは異なる配線によって伝送されるシリアルクロックのタイミングを用いて、上記シリアルデータから上記第1フラグと上記画像データとを取り出し、

上記第1フラグが画素に上記画像データを書き込むことを示す場合、当該フレームにおいて第1論理値から第2論理値に変化するモード信号を生成し、

上記シリアルクロックのタイミングを用いて、上記表示ドライバが備えるデータ信号線ドライバのシフトレジスタを動作させるクロック信号としてのタイミング信号を生成し、

上記モード信号が上記第1論理値から上記第2論理値に変化するタイミングおよび上記シフトレジスタを動作させるクロック信号としてのタイミング信号から、1フレーム期間の最初の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力することを特徴とする表示装置。

【請求項2】

次の水平期間が存在する場合には、上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に上記次の水平期間のタイミング信号を生成して、上記データ信号線ドライバのシフトレジスタに入力することを特徴とする請求項1に記載の表示装置。

【請求項3】

上記データ信号線ドライバのシフトレジスタで1水平表示期間分シフトされた信号を基に、上記表示ドライバが備える走査信号線ドライバに入力するタイミング信号を生成し、

各上記水平期間のタイミング信号と、上記走査信号線ドライバから出力される走査信号とを用いて、上記画像データを画素に書き込むことを特徴とする請求項2に記載の表示装置。

【請求項4】

請求項1から3までのいずれか1項に記載の表示装置をディスプレイとして備えていることを特徴とする携帯端末。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2012−194582(P2012−194582A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2012−149986(P2012−149986)

【出願日】平成24年7月3日(2012.7.3)

【分割の表示】特願2010−508124(P2010−508124)の分割

【原出願日】平成21年1月29日(2009.1.29)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成24年7月3日(2012.7.3)

【分割の表示】特願2010−508124(P2010−508124)の分割

【原出願日】平成21年1月29日(2009.1.29)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]