表示装置における電力レベル制御のための方法及び装置

【課題】表示されるべきピクチャのフレーム周波数を考慮して、電力レベル制御の新たな方法及び装置を開示する。

【解決手段】本発明は、入力画像の画素に対応する複数の発光素子を有する表示装置における電力レベルの制御装置に関する。当該装置は、表示されるべき前記入力画像の特性である平均電力値を決定する平均画像電力回路、決定された平均電力値を第一の保持パルスの数に変換する第一の回路、入力画像のフレーム周波数を測定し、入力画像のフレーム周波数を最多の許容される保持パルスの数に変換する周波数測定回路、第一の保持パルスの数と保持ゲインとを乗算して、第二の保持パルスの数を伝送する第二の回路、保持ゲインは、表示装置の公称のフレーム周波数に対する入力フレームの周波数の割合を表し、第二の保持パルスの数と最多の許容される保持パルスの数との間で最少の保持パルスの数を選択する第三の回路、及び最少の保持パルスの数を、ある電力レベルモードに変換する電力レベル回路を備える。

【解決手段】本発明は、入力画像の画素に対応する複数の発光素子を有する表示装置における電力レベルの制御装置に関する。当該装置は、表示されるべき前記入力画像の特性である平均電力値を決定する平均画像電力回路、決定された平均電力値を第一の保持パルスの数に変換する第一の回路、入力画像のフレーム周波数を測定し、入力画像のフレーム周波数を最多の許容される保持パルスの数に変換する周波数測定回路、第一の保持パルスの数と保持ゲインとを乗算して、第二の保持パルスの数を伝送する第二の回路、保持ゲインは、表示装置の公称のフレーム周波数に対する入力フレームの周波数の割合を表し、第二の保持パルスの数と最多の許容される保持パルスの数との間で最少の保持パルスの数を選択する第三の回路、及び最少の保持パルスの数を、ある電力レベルモードに変換する電力レベル回路を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置の電力レベル制御の方法及び該方法を実行するための装置に関する。

より詳細には、本発明は、プラズマディスプレイパネル(PDP)のような、光放出のデューティサイクル変調(パルス幅変調)の原理に基づく表示装置の入力フレームの周波数動作レンジを改善するものであり、同時に、画像の明るさ及び品質は、公称の入力フレームの周波数値に近似的に同一に保持される。

【背景技術】

【0002】

今日、プラズマ技術は、非常に制限された奥行きをもち、視野角の制限なしに、(CRTの制限から外れて)大型のフラットカラーパネルを達成するのを可能にしている。CRT(Cathode Ray Tube)技術のように、PDPは、それ自身の光を発生する技術である。同様にして、両方の技術は、フルホワイト値よりも高いピークホワイトブライトネスを可能にするパワーマネージメント(又はブライトネス調整)回路を使用している。

【0003】

CRTスクリーンは、いわゆるABL(Average Beam−current Limiter)回路を使用し、この回路は、ビデオコントローラにおけるアナログ手段により実現され、RCステージを通して通常測定される平均ルミナンスの関数としてビデオゲインを減少させる。

【0004】

プラズマディスプレイパネルは、表示されたピクチャの平均電力レベルの関数として多かれ少なかれ保持パルスを発生する、いわゆるAPL(Average Power Level)制御回路を使用する。APL制御は、プラズマディスプレイにおけるより大きなピークホワイトルミナンス値について、多くの保持パルスが必ず必要とされるリフレクションから開始する。他方で、保持パルスは、PDPの高い電力消費量にも対応する。したがって、ソリューションは、平均のピクチャ電力の関数として多かれ少なかれ保持パルスを発生する制御方法であり、すなわち、異なる電力レベルをもつ異なる電力モードの間でスイッチする。かかるAPL制御回路は、国際特許出願WO00/46782で開示されている。比較的低いピクチャパワーを有するピクチャについて、すなわち比較的低いルミナンスの値をもつ多くの画素について、全体の電力消費量が低いルミナンス値をもつ非常に多くの量の画素のために制限されるため、異なるビデオレベルを形成するために多くの保持パルスを使用するモードが使用される。比較的高いピクチャパワーを有するピクチャについて、すなわち比較的高いルミナンス値をもつ多くの画素について、全体の電力消費量が高いルミナンス値をもつ非常に多くの値によって高いため、異なるビデオレベルを形成するために少数の保持パルスを使用するモードが選択される。したがって、電力消費量の良好な管理のために複数の電力レベルモードを定義することができる。

【0005】

APL制御は、以下のように実現される。はじめに、デガンマ後の入力信号の平均ビデオレベルが計算される。この値は、入力ピクチャを再生するために必要とされる全体のルミナンスパワーの良好な推定値である。第二に、ルックアップテーブルにより、許可されたレンジで電力消費量を保持するために入力ピクチャについて生成することができる全体の数の保持パルスが決定され、対応するサブフィールドの編成が同時に選択される。国際特許出願WO00/46782で記載されるように、サブフィールドの編成は、1以上の以下の特性に関して変化させることができる。保持パルスの数、サブフィールドの数、サブフィールドのポジショニング。

【0006】

このソリューションは、所与のフレーム周波数について最適化される。確かに、入力フレーム周波数は、通常は一定であるが、パネルが、トリックモードにおけるビデオカセットレコーダといった標準化されていないビデオソースに接続されている場合に変化する可能性がある。パネルがコンピュータに接続されているときも同じである。同じグラフィックカードについて、周波数は、公称の周波数から著しくはずれる可能性がある。したがって、電源をオーバロードすること、又はパネルピークホワイト及びフルホワイト値を低減するような望まれない作用なしで、フレーム周波数のレンジをトラックすることが困難になる。

【特許文献1】WO00/46782A(DEUTSCHE THOMSON−BRANDTGMBH)

【特許文献2】EP0851400A(NEC CORPORATION)

【特許文献3】EP1437706A(THOMSOM LICENSING S.A)

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は、表示されるべきピクチャのフレーム周波数を考慮して、電力レベル制御のための新たな方法及び装置を開示することにある。

本発明によれば、表示されるべきピクチャの平均電力レベル及びフレーム周波数の関数としてサブフィールドの編成が選択される。

【課題を解決するための手段】

【0008】

本発明によれば、上記目的は、入力ピクチャの画素に対応する複数の発光素子を有する表示装置での電力レベル制御のための方法により解決され、ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変であり、当該方法は、表示されるべきピクチャの電力レベルについて固有な電力値を決定するステップ、入力ピクチャのフレーム周波数を測定するステップ、前記電力値及び前記フレーム周波数に基づいて電力レベルモードを選択するステップを含む。

【0009】

実際に、電力値の関数としてのみ選択される電力レベルモードの保持パルスの数は、入力周波数が公称の周波数よりも高い場合に減少され、入力周波数が通常50Hz又は60Hzである公称の周波数よりも低い場合に増加される。

ピクチャの電力値は、表示されるべきピクチャの平均の電力値であることが好ましい。

【0010】

また、本発明は、入力ピクチャの画素に対応する複数の発光素子を有する表示装置での電力レベル制御のための装置に関し、ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変である。当該装置は、表示されるべきピクチャの電力レベルについて固有な電力値を決定する平均ピクチャ電力回路、入力ピクチャのフレーム周波数を測定する周波数測定回路、前記電力値及び前記フレーム周波数に基づいて電力レベルモードを選択する電力レベル制御回路を含む。

【0011】

好適な実施の形態では、電力レベル制御回路は、平均のピクチャ電力を第一の数の保持パルスに変換する第一の回路、入力ピクチャのフレーム周波数を最大の許容される数の保持パルス及び保持ゲインに変換する第二の回路、前記保持ゲインで第一の数の保持パルスを乗算し、第二の数の保持パルスを伝送する第三の回路、前記第二の数の保持パルスと前記最大の許容される数の保持パルスとの間で最少の数の保持パルスを選択する第四の回路、前記最少の数の保持パルスを電力レベルモードに変換する第五の回路を含む。

【0012】

第一、第二及び第五の回路は、たとえばルックアップテーブルである。

また、本発明は、この装置を含むプラズマディスプレイ装置に関する。

本発明の例示的な実施の形態は、図面で例示され、以下の記載で更に詳細に説明される。

【図面の簡単な説明】

【0013】

【図1】従来技術のプラズマディスプレイパネルの電力レベル制御装置のブロック図である。

【図2】本発明に係るプラズマディスプレイパネルの電力レベル制御装置のブロック図である。

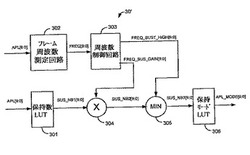

【図3】図2の装置のAPLモードデコーダのブロック図である。

【発明を実施するための形態】

【0014】

図1は、従来技術のプラズマディスプレイパネルの電力レベル制御装置のブロック図を示す。先に記載されたように、この装置により実現される原理は、所与のピクチャの平均電力を計算し、サブフィールドコーディングのための(サブフィールド編成に対応する)適切な電力レベルモードを選択することである。

【0015】

図1を参照して、入力ビデオ信号RED[7:0]、GREEN[7:0]、BLUE[7:0]は、デガンマ(de-gamma)処理20の後に平均電力レベル(APL: Average Power Level)計算回路10に供給される。APL計算回路10は、APL[9:0]と呼ばれる10ビットのAPL信号を出力し、この信号は、入力ピクチャを表示するために必要とされるトータルルミナンスパワーを表す。ピクチャの平均電力値APL[9:0]は、全てのビデオ入力データの画素値を合計し、結果を3で乗算される画素値の数を通して割ることで計算することができる。次いで、信号APL[9:0]は、サブフィールド編成を表す、APL_MODE[9:0]と呼ばれる、電力レベルモードに変換するためのAPLモードデコーダ30により使用される。実際には、APLモードデコーダ30は、シンプルなルックアップテーブルである。異なる電力レベルモードの例がここで与えられる。

【0016】

モード204:204保持パルス(フルホワイト)

モード205:205保持パルス

...

モード700:700保持パルス

モード1000:1000保持パルス

明確さの理由のため、この例で与えられる電力レベルモードの保持パルスの数は、モードナンバーに同一である。保持パルスは、ビデオフレームの異なるサブフィールドの間で分散される。この分散は、電力消費について重要性を有さないので記載されない。

【0017】

入力ビデオ信号RED[7:0]、GREEN[7:0]、BLUE[7:0]は、フレーム遅延回路50及びデガンマ処理60により遅延された後、PDPディスプレイエンジン40に供給される。確かに、入力ビデオ信号は、PDPディスプレイエンジン40がリニアガンマ伝達関数(表示される明るさが発生される保持パルスの数に比例する)を有するため、デガンマ処理される必要がある。また、入力ビデオ信号は、デコーダ30により決定される電力レベルモードAPL_MODE[9:0]がPDPディスプレイエンジン40に供給されるビデオデータに対応するため、フレーム期間から遅延される必要がある。

【0018】

したがって、リニアディスプレイエンジン40は、3つの16ビットのデガンマ処理された入力ビデオ信号RED[15:0]、GREEN[15:0]、BLUE[15:0]、及び発生されるべき保持パルスの数を制御する10ビットのAPLモード値APL_MODE[9:0]を受ける。信号APL_MODE[9:0]により選択されたサブフィールド編成は、ビデオ信号RED[15:0]、GREEN[15:0]、BLUE[15:0]を符号化するため、ディスプレイエンジン40により使用され、ディスプレイエンジン40により出力された信号は、対応する画像を表示するためにPDPドライバ7に供給される。

【0019】

本発明によれば、公称のピークホワイト及びフルホワイト値からの可能性のあるずれをできるだけ小さく有するようなやり方で、入力フレーム周波数の関数として、電力レベルモードを選択し、同時に、パネルの電力供給のオーバロードが防止されることが提案される。より詳細には、ビデオフレームでの保持パルスの数は、入力フレーム周波数の関数として変更される。入力フレーム周波数が測定される。測定されたフレーム周波数が公称のフレーム周波数(50又は60Hz)よりも低い場合、フレーム当たりの高い数の保持パルスによる電力レベルモードが選択される。測定されたフレーム周波数が公称の周波数よりも高い場合、フレーム当たり低い数の保持パルスによる電力レベルモードが選択される。

【0020】

図2は、本発明に係るプラズマディスプレイパネルの電力レベル制御装置のブロック図を示す。同じ参照符号は、同一の回路ブロックについて図1及び図2において使用される。図2において、APLモードデコーダが変更され、ここでは参照符号30’である。信号APL[9:0]に加えて、パネルの垂直同期信号である信号V_PULSEを受信する。

【0021】

図3は、APLモードデコーダ30’のブロック図を示す。提案される回路30’は、APL値APL[9:0]を、考慮されるAPL値に適合される電力レベルモードの保持パルスの数に対応する第一の数の保持パルスSUS_NB1[9:0]に変換するための第一のルックアップテーブル301を有する。この回路は、信号V_PULSEからの入力フレームの周波数を測定するためのフレーム周波数測定回路302を有する。より詳細には、この回路は、入力ビデオ信号の垂直周波数レートを規定する8ビットの符号化デジタル信号FREQUENCY[7:0]における一連のVパルスを変換する。かかる測定回路は、古典的であり、ぞれぞれの垂直パルスV_PULSEでカウンタをリセットし、次いで、(後続する垂直パルスによりカウンタが再びリセットされたとき)端末のカウント値をそれぞれ可能性のある周波数の結果の基準値のセットと比較することを含む。この周波数信号FREQUENCY[7:0]は、次いで、ルックアップテーブルとすることができる周波数制御回路303により2つのサステインナンバー(保持数)制御信号のセットに変換される。

【0022】

信号FREQ_SUST_GAIN[9:0]:ビデオフレームでの全体の数の保持パルスを減少又は増加するためのサステインゲインファクタである。このファクタは、入力フレーム周波数が公称の周波数(50又は60Hz)よりも低いときに1よりも大きく、入力フレーム周波数が公称の周波数よりも高いときに1よりも小さい。

【0023】

信号FREQ_SUST_HIGH[9:0]:所与のフレーム周波数について最も高い許容される数の保持パルスを表す。これは、入力フレーム周波数が増加した場合、ビデオフレームにおいて時間がないために重要であり、したがって、ビデオフレームで発生される最大の数の保持パルスが低減される。

【0024】

保持パルスSUS_NB1[9:0]の数は、乗算回路304により、信号FREQ_SUST_GAIN[9:0]により乗算される。第二の数の保持パルスSUS_NB2[9:0]を伝送する。図3の例では、ゲインファクタFREQ_SUST_GAIN[9:0]は、ゲインファクタが異なる入力フレームの周波数について十分な精度を有するため、比(入力フレーム周波数)×512/(公称のフレーム周波数)に等しい。結果的に、ゲインファクタFREQ_SUST_GAIN[9:0]は、乗算回路304において512で除算される。

【0025】

次いで、第二の数の保持パルスSUS_NB2[9:0]は、回路305により許容される数の保持パルスFREQ_SUST_HIGH[9:0]に比較され、回路305は、これら2つの値の間で最少の値を選択する。この回路により出力される、SUS_NB3[9:0]で参照される保持パルスの数は、次いで、保持モードルックアップテーブル306により電力レベルモードAPL_MODE[9:0]に変換される。2つのルックアップテーブル301,306の内容は、それらが直接接続された場合、それらの機能が図1のAPLモードデコーダ30について使用されるルックアップテーブルに等価である。

【0026】

回路30’の機能の原理は、測定されたフレーム周波数FREQUENCY[7:0]の機能として、適切な電力レベルモードAPL_MODE[9:0]を選択するように、LUT301により出力された全体の数の保持パルスSUS_NB1[9:0]を変えることである。

【0027】

信号FREQUENCY[7:0]、FREQ_SUST_GAIN[9:0]及びFREQ_SUST_HIGH[9:0]の例が以下に与えられる。この表では、ビデオフレームがフルホワイトピクチャについて200の保持パルスを含み、ピークホワイトピクチャについて1000の保持パルスを含むことを想定している。簡単さのため、60Hzの公称周波数の周りの入力フレーム周波数の低減された数が示されている。

【0028】

【表1】

この表は例として示されており、幾つかの他の可能性が許容される。入力フレーム周波数が公称の周波数よりも高い場合、全ての公称の保持パルスを発生するための時間が低減されるため(短いフレーム期間)、最大の許容される数の保持パルスFREQ_SUST_HIGH[9:0]が低減される必要がある。入力フレーム周波数が公称周波数よりも低い場合、1000を超える保持パルスを発生する電力レベルモードAPL_MODE[9:0]が定義されていない事実のため、最大の許容される数の保持パルスFREQ_SUST_HIGH[9:0]を増加することができない。

【0029】

表に示されているように、保持パルスSUS_NB1[9:0]の数に与えられるゲインFREQ_SUST_GAIN[9:0]は、入力フレーム周波数に反比例し、先に説明されたように、比(入力フレーム周波数)×512/(公称のフレーム周波数)に等しい。このように、ピクチャの明るさは、全体の考慮される入力フレーム周波数レンジについて近似的に一定のままである。

【0030】

この表は、そのPDP制御回路及びドライバの物理的な制約を考慮して、PDP製造業者により慎重に生成される。

本実施の形態で提供された本発明は、古典的なパワーマネージメント回路の改善である。本発明は、全体の入力フレーム周波数レンジでパワーマネージメントを改善するためのシンプルかつ容易なやり方を提案する。ユーザの利益は、標準的でない入力ビデオ信号を処理するときでさえ、常に生成された画像が存在することである。

全ての図で示されるブロックは、ハードウェアコンポーネントによるよりはむしろ、適切なコンピュータプログラムで実現することができる。さらに、本発明は、開示される実施の形態に制限されない。

【0031】

様々な変更が可能であり、請求項の範囲に含まれると考えられ、たとえば、他の値の最大の許容される数の保持パルスFREQ_SUST_HIGH[9:0]又はゲインFREQ_SUST_GAIN[9:0]を代わりに使用することができ、他の入力フレームの周波数レンジを使用することができる。

本発明は、グレイレベルバリエーションについて光放出の制御のようなPWMを使用することで制御される全ての種類のディスプレイについて使用することができる。

【符号の説明】

【0032】

10:平均電力レベル計算回路

20,60:デガンマ処理手段

30’:APLモードデコーダ

40:PDPリニアディスプレイエンジン

50:フレームディレイ

70:PDPスクリーン及びドライバ

【技術分野】

【0001】

本発明は、表示装置の電力レベル制御の方法及び該方法を実行するための装置に関する。

より詳細には、本発明は、プラズマディスプレイパネル(PDP)のような、光放出のデューティサイクル変調(パルス幅変調)の原理に基づく表示装置の入力フレームの周波数動作レンジを改善するものであり、同時に、画像の明るさ及び品質は、公称の入力フレームの周波数値に近似的に同一に保持される。

【背景技術】

【0002】

今日、プラズマ技術は、非常に制限された奥行きをもち、視野角の制限なしに、(CRTの制限から外れて)大型のフラットカラーパネルを達成するのを可能にしている。CRT(Cathode Ray Tube)技術のように、PDPは、それ自身の光を発生する技術である。同様にして、両方の技術は、フルホワイト値よりも高いピークホワイトブライトネスを可能にするパワーマネージメント(又はブライトネス調整)回路を使用している。

【0003】

CRTスクリーンは、いわゆるABL(Average Beam−current Limiter)回路を使用し、この回路は、ビデオコントローラにおけるアナログ手段により実現され、RCステージを通して通常測定される平均ルミナンスの関数としてビデオゲインを減少させる。

【0004】

プラズマディスプレイパネルは、表示されたピクチャの平均電力レベルの関数として多かれ少なかれ保持パルスを発生する、いわゆるAPL(Average Power Level)制御回路を使用する。APL制御は、プラズマディスプレイにおけるより大きなピークホワイトルミナンス値について、多くの保持パルスが必ず必要とされるリフレクションから開始する。他方で、保持パルスは、PDPの高い電力消費量にも対応する。したがって、ソリューションは、平均のピクチャ電力の関数として多かれ少なかれ保持パルスを発生する制御方法であり、すなわち、異なる電力レベルをもつ異なる電力モードの間でスイッチする。かかるAPL制御回路は、国際特許出願WO00/46782で開示されている。比較的低いピクチャパワーを有するピクチャについて、すなわち比較的低いルミナンスの値をもつ多くの画素について、全体の電力消費量が低いルミナンス値をもつ非常に多くの量の画素のために制限されるため、異なるビデオレベルを形成するために多くの保持パルスを使用するモードが使用される。比較的高いピクチャパワーを有するピクチャについて、すなわち比較的高いルミナンス値をもつ多くの画素について、全体の電力消費量が高いルミナンス値をもつ非常に多くの値によって高いため、異なるビデオレベルを形成するために少数の保持パルスを使用するモードが選択される。したがって、電力消費量の良好な管理のために複数の電力レベルモードを定義することができる。

【0005】

APL制御は、以下のように実現される。はじめに、デガンマ後の入力信号の平均ビデオレベルが計算される。この値は、入力ピクチャを再生するために必要とされる全体のルミナンスパワーの良好な推定値である。第二に、ルックアップテーブルにより、許可されたレンジで電力消費量を保持するために入力ピクチャについて生成することができる全体の数の保持パルスが決定され、対応するサブフィールドの編成が同時に選択される。国際特許出願WO00/46782で記載されるように、サブフィールドの編成は、1以上の以下の特性に関して変化させることができる。保持パルスの数、サブフィールドの数、サブフィールドのポジショニング。

【0006】

このソリューションは、所与のフレーム周波数について最適化される。確かに、入力フレーム周波数は、通常は一定であるが、パネルが、トリックモードにおけるビデオカセットレコーダといった標準化されていないビデオソースに接続されている場合に変化する可能性がある。パネルがコンピュータに接続されているときも同じである。同じグラフィックカードについて、周波数は、公称の周波数から著しくはずれる可能性がある。したがって、電源をオーバロードすること、又はパネルピークホワイト及びフルホワイト値を低減するような望まれない作用なしで、フレーム周波数のレンジをトラックすることが困難になる。

【特許文献1】WO00/46782A(DEUTSCHE THOMSON−BRANDTGMBH)

【特許文献2】EP0851400A(NEC CORPORATION)

【特許文献3】EP1437706A(THOMSOM LICENSING S.A)

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は、表示されるべきピクチャのフレーム周波数を考慮して、電力レベル制御のための新たな方法及び装置を開示することにある。

本発明によれば、表示されるべきピクチャの平均電力レベル及びフレーム周波数の関数としてサブフィールドの編成が選択される。

【課題を解決するための手段】

【0008】

本発明によれば、上記目的は、入力ピクチャの画素に対応する複数の発光素子を有する表示装置での電力レベル制御のための方法により解決され、ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変であり、当該方法は、表示されるべきピクチャの電力レベルについて固有な電力値を決定するステップ、入力ピクチャのフレーム周波数を測定するステップ、前記電力値及び前記フレーム周波数に基づいて電力レベルモードを選択するステップを含む。

【0009】

実際に、電力値の関数としてのみ選択される電力レベルモードの保持パルスの数は、入力周波数が公称の周波数よりも高い場合に減少され、入力周波数が通常50Hz又は60Hzである公称の周波数よりも低い場合に増加される。

ピクチャの電力値は、表示されるべきピクチャの平均の電力値であることが好ましい。

【0010】

また、本発明は、入力ピクチャの画素に対応する複数の発光素子を有する表示装置での電力レベル制御のための装置に関し、ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変である。当該装置は、表示されるべきピクチャの電力レベルについて固有な電力値を決定する平均ピクチャ電力回路、入力ピクチャのフレーム周波数を測定する周波数測定回路、前記電力値及び前記フレーム周波数に基づいて電力レベルモードを選択する電力レベル制御回路を含む。

【0011】

好適な実施の形態では、電力レベル制御回路は、平均のピクチャ電力を第一の数の保持パルスに変換する第一の回路、入力ピクチャのフレーム周波数を最大の許容される数の保持パルス及び保持ゲインに変換する第二の回路、前記保持ゲインで第一の数の保持パルスを乗算し、第二の数の保持パルスを伝送する第三の回路、前記第二の数の保持パルスと前記最大の許容される数の保持パルスとの間で最少の数の保持パルスを選択する第四の回路、前記最少の数の保持パルスを電力レベルモードに変換する第五の回路を含む。

【0012】

第一、第二及び第五の回路は、たとえばルックアップテーブルである。

また、本発明は、この装置を含むプラズマディスプレイ装置に関する。

本発明の例示的な実施の形態は、図面で例示され、以下の記載で更に詳細に説明される。

【図面の簡単な説明】

【0013】

【図1】従来技術のプラズマディスプレイパネルの電力レベル制御装置のブロック図である。

【図2】本発明に係るプラズマディスプレイパネルの電力レベル制御装置のブロック図である。

【図3】図2の装置のAPLモードデコーダのブロック図である。

【発明を実施するための形態】

【0014】

図1は、従来技術のプラズマディスプレイパネルの電力レベル制御装置のブロック図を示す。先に記載されたように、この装置により実現される原理は、所与のピクチャの平均電力を計算し、サブフィールドコーディングのための(サブフィールド編成に対応する)適切な電力レベルモードを選択することである。

【0015】

図1を参照して、入力ビデオ信号RED[7:0]、GREEN[7:0]、BLUE[7:0]は、デガンマ(de-gamma)処理20の後に平均電力レベル(APL: Average Power Level)計算回路10に供給される。APL計算回路10は、APL[9:0]と呼ばれる10ビットのAPL信号を出力し、この信号は、入力ピクチャを表示するために必要とされるトータルルミナンスパワーを表す。ピクチャの平均電力値APL[9:0]は、全てのビデオ入力データの画素値を合計し、結果を3で乗算される画素値の数を通して割ることで計算することができる。次いで、信号APL[9:0]は、サブフィールド編成を表す、APL_MODE[9:0]と呼ばれる、電力レベルモードに変換するためのAPLモードデコーダ30により使用される。実際には、APLモードデコーダ30は、シンプルなルックアップテーブルである。異なる電力レベルモードの例がここで与えられる。

【0016】

モード204:204保持パルス(フルホワイト)

モード205:205保持パルス

...

モード700:700保持パルス

モード1000:1000保持パルス

明確さの理由のため、この例で与えられる電力レベルモードの保持パルスの数は、モードナンバーに同一である。保持パルスは、ビデオフレームの異なるサブフィールドの間で分散される。この分散は、電力消費について重要性を有さないので記載されない。

【0017】

入力ビデオ信号RED[7:0]、GREEN[7:0]、BLUE[7:0]は、フレーム遅延回路50及びデガンマ処理60により遅延された後、PDPディスプレイエンジン40に供給される。確かに、入力ビデオ信号は、PDPディスプレイエンジン40がリニアガンマ伝達関数(表示される明るさが発生される保持パルスの数に比例する)を有するため、デガンマ処理される必要がある。また、入力ビデオ信号は、デコーダ30により決定される電力レベルモードAPL_MODE[9:0]がPDPディスプレイエンジン40に供給されるビデオデータに対応するため、フレーム期間から遅延される必要がある。

【0018】

したがって、リニアディスプレイエンジン40は、3つの16ビットのデガンマ処理された入力ビデオ信号RED[15:0]、GREEN[15:0]、BLUE[15:0]、及び発生されるべき保持パルスの数を制御する10ビットのAPLモード値APL_MODE[9:0]を受ける。信号APL_MODE[9:0]により選択されたサブフィールド編成は、ビデオ信号RED[15:0]、GREEN[15:0]、BLUE[15:0]を符号化するため、ディスプレイエンジン40により使用され、ディスプレイエンジン40により出力された信号は、対応する画像を表示するためにPDPドライバ7に供給される。

【0019】

本発明によれば、公称のピークホワイト及びフルホワイト値からの可能性のあるずれをできるだけ小さく有するようなやり方で、入力フレーム周波数の関数として、電力レベルモードを選択し、同時に、パネルの電力供給のオーバロードが防止されることが提案される。より詳細には、ビデオフレームでの保持パルスの数は、入力フレーム周波数の関数として変更される。入力フレーム周波数が測定される。測定されたフレーム周波数が公称のフレーム周波数(50又は60Hz)よりも低い場合、フレーム当たりの高い数の保持パルスによる電力レベルモードが選択される。測定されたフレーム周波数が公称の周波数よりも高い場合、フレーム当たり低い数の保持パルスによる電力レベルモードが選択される。

【0020】

図2は、本発明に係るプラズマディスプレイパネルの電力レベル制御装置のブロック図を示す。同じ参照符号は、同一の回路ブロックについて図1及び図2において使用される。図2において、APLモードデコーダが変更され、ここでは参照符号30’である。信号APL[9:0]に加えて、パネルの垂直同期信号である信号V_PULSEを受信する。

【0021】

図3は、APLモードデコーダ30’のブロック図を示す。提案される回路30’は、APL値APL[9:0]を、考慮されるAPL値に適合される電力レベルモードの保持パルスの数に対応する第一の数の保持パルスSUS_NB1[9:0]に変換するための第一のルックアップテーブル301を有する。この回路は、信号V_PULSEからの入力フレームの周波数を測定するためのフレーム周波数測定回路302を有する。より詳細には、この回路は、入力ビデオ信号の垂直周波数レートを規定する8ビットの符号化デジタル信号FREQUENCY[7:0]における一連のVパルスを変換する。かかる測定回路は、古典的であり、ぞれぞれの垂直パルスV_PULSEでカウンタをリセットし、次いで、(後続する垂直パルスによりカウンタが再びリセットされたとき)端末のカウント値をそれぞれ可能性のある周波数の結果の基準値のセットと比較することを含む。この周波数信号FREQUENCY[7:0]は、次いで、ルックアップテーブルとすることができる周波数制御回路303により2つのサステインナンバー(保持数)制御信号のセットに変換される。

【0022】

信号FREQ_SUST_GAIN[9:0]:ビデオフレームでの全体の数の保持パルスを減少又は増加するためのサステインゲインファクタである。このファクタは、入力フレーム周波数が公称の周波数(50又は60Hz)よりも低いときに1よりも大きく、入力フレーム周波数が公称の周波数よりも高いときに1よりも小さい。

【0023】

信号FREQ_SUST_HIGH[9:0]:所与のフレーム周波数について最も高い許容される数の保持パルスを表す。これは、入力フレーム周波数が増加した場合、ビデオフレームにおいて時間がないために重要であり、したがって、ビデオフレームで発生される最大の数の保持パルスが低減される。

【0024】

保持パルスSUS_NB1[9:0]の数は、乗算回路304により、信号FREQ_SUST_GAIN[9:0]により乗算される。第二の数の保持パルスSUS_NB2[9:0]を伝送する。図3の例では、ゲインファクタFREQ_SUST_GAIN[9:0]は、ゲインファクタが異なる入力フレームの周波数について十分な精度を有するため、比(入力フレーム周波数)×512/(公称のフレーム周波数)に等しい。結果的に、ゲインファクタFREQ_SUST_GAIN[9:0]は、乗算回路304において512で除算される。

【0025】

次いで、第二の数の保持パルスSUS_NB2[9:0]は、回路305により許容される数の保持パルスFREQ_SUST_HIGH[9:0]に比較され、回路305は、これら2つの値の間で最少の値を選択する。この回路により出力される、SUS_NB3[9:0]で参照される保持パルスの数は、次いで、保持モードルックアップテーブル306により電力レベルモードAPL_MODE[9:0]に変換される。2つのルックアップテーブル301,306の内容は、それらが直接接続された場合、それらの機能が図1のAPLモードデコーダ30について使用されるルックアップテーブルに等価である。

【0026】

回路30’の機能の原理は、測定されたフレーム周波数FREQUENCY[7:0]の機能として、適切な電力レベルモードAPL_MODE[9:0]を選択するように、LUT301により出力された全体の数の保持パルスSUS_NB1[9:0]を変えることである。

【0027】

信号FREQUENCY[7:0]、FREQ_SUST_GAIN[9:0]及びFREQ_SUST_HIGH[9:0]の例が以下に与えられる。この表では、ビデオフレームがフルホワイトピクチャについて200の保持パルスを含み、ピークホワイトピクチャについて1000の保持パルスを含むことを想定している。簡単さのため、60Hzの公称周波数の周りの入力フレーム周波数の低減された数が示されている。

【0028】

【表1】

この表は例として示されており、幾つかの他の可能性が許容される。入力フレーム周波数が公称の周波数よりも高い場合、全ての公称の保持パルスを発生するための時間が低減されるため(短いフレーム期間)、最大の許容される数の保持パルスFREQ_SUST_HIGH[9:0]が低減される必要がある。入力フレーム周波数が公称周波数よりも低い場合、1000を超える保持パルスを発生する電力レベルモードAPL_MODE[9:0]が定義されていない事実のため、最大の許容される数の保持パルスFREQ_SUST_HIGH[9:0]を増加することができない。

【0029】

表に示されているように、保持パルスSUS_NB1[9:0]の数に与えられるゲインFREQ_SUST_GAIN[9:0]は、入力フレーム周波数に反比例し、先に説明されたように、比(入力フレーム周波数)×512/(公称のフレーム周波数)に等しい。このように、ピクチャの明るさは、全体の考慮される入力フレーム周波数レンジについて近似的に一定のままである。

【0030】

この表は、そのPDP制御回路及びドライバの物理的な制約を考慮して、PDP製造業者により慎重に生成される。

本実施の形態で提供された本発明は、古典的なパワーマネージメント回路の改善である。本発明は、全体の入力フレーム周波数レンジでパワーマネージメントを改善するためのシンプルかつ容易なやり方を提案する。ユーザの利益は、標準的でない入力ビデオ信号を処理するときでさえ、常に生成された画像が存在することである。

全ての図で示されるブロックは、ハードウェアコンポーネントによるよりはむしろ、適切なコンピュータプログラムで実現することができる。さらに、本発明は、開示される実施の形態に制限されない。

【0031】

様々な変更が可能であり、請求項の範囲に含まれると考えられ、たとえば、他の値の最大の許容される数の保持パルスFREQ_SUST_HIGH[9:0]又はゲインFREQ_SUST_GAIN[9:0]を代わりに使用することができ、他の入力フレームの周波数レンジを使用することができる。

本発明は、グレイレベルバリエーションについて光放出の制御のようなPWMを使用することで制御される全ての種類のディスプレイについて使用することができる。

【符号の説明】

【0032】

10:平均電力レベル計算回路

20,60:デガンマ処理手段

30’:APLモードデコーダ

40:PDPリニアディスプレイエンジン

50:フレームディレイ

70:PDPスクリーン及びドライバ

【特許請求の範囲】

【請求項1】

入力画像の画素に対応する複数の発光素子を有する表示装置における電力レベルの制御方法であって、

ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変であり、

当該方法は、

表示されるべき前記入力画像の特性である平均電力値を決定し、決定された平均電力値を第一の保持パルスの数に変換するステップと、

前記入力画像のフレーム周波数を測定し、前記入力画像のフレーム周波数を最多の許容される保持パルスの数に変換し、前記第一の保持パルスの数と保持ゲインとを乗算して第二の保持パルスの数を伝送するステップと、前記保持ゲインは、前記表示装置の公称のフレーム周波数に対する入力フレームの周波数の割合を表し、

前記第二の保持パルスの数と前記最多の許容される保持パルスの数との間で最少の保持パルスの数を選択し、最少の保持パルスの数を、ある電力レベルモードに変換するステップと、

を含むことを特徴とする方法。

【請求項2】

入力画像の画素に対応する複数の発光素子を有する表示装置における電力レベルの制御装置であって、

ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変であり、

当該装置は、

表示されるべき前記入力画像の特性である平均電力値を決定する平均画像電力回路と、

決定された平均電力値を第一の保持パルスの数に変換する第一の回路と、

前記入力画像のフレーム周波数を測定し、前記入力画像のフレーム周波数を最多の許容される保持パルスの数に変換する周波数測定回路と、

前記第一の保持パルスの数と保持ゲインとを乗算して、第二の保持パルスの数を伝送する第二の回路と、前記保持ゲインは、前記表示装置の公称のフレーム周波数に対する入力フレームの周波数の割合を表し、

前記第二の保持パルスの数と前記最多の許容される保持パルスの数との間で最少の保持パルスの数を選択する第三の回路と、

前記最少の保持パルスの数を、ある電力レベルモードに変換する電力レベル回路と、

を備えることを特徴とする装置。

【請求項3】

当該電力レベルの制御装置は、

前記決定された平均電力値を第一の数の保持パルスに変換する第一の回路と、

前記入力画像の前記測定されたフレーム周波数を前記最多の許容される保持パルスの数及び前記保持ゲインに変換する第二の回路と、

前記保持ゲインで第一の保持パルスの数を乗算し、第二の保持パルスの数を出力する第三の回路と、

前記第二の保持パルスの数と前記最多の許容される保持パルスの数との間で最少の保持パルスの数を選択する第四の回路と、

前記少ない方の保持パルスの数を前記電力レベルモードに変換する第五の回路と、

を含む請求項2記載の装置。

【請求項4】

第一、第二及び第五の回路は、ルックアップテーブルである、

請求項3記載の装置。

【請求項1】

入力画像の画素に対応する複数の発光素子を有する表示装置における電力レベルの制御方法であって、

ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変であり、

当該方法は、

表示されるべき前記入力画像の特性である平均電力値を決定し、決定された平均電力値を第一の保持パルスの数に変換するステップと、

前記入力画像のフレーム周波数を測定し、前記入力画像のフレーム周波数を最多の許容される保持パルスの数に変換し、前記第一の保持パルスの数と保持ゲインとを乗算して第二の保持パルスの数を伝送するステップと、前記保持ゲインは、前記表示装置の公称のフレーム周波数に対する入力フレームの周波数の割合を表し、

前記第二の保持パルスの数と前記最多の許容される保持パルスの数との間で最少の保持パルスの数を選択し、最少の保持パルスの数を、ある電力レベルモードに変換するステップと、

を含むことを特徴とする方法。

【請求項2】

入力画像の画素に対応する複数の発光素子を有する表示装置における電力レベルの制御装置であって、

ビデオフレームの期間は複数のサブフィールドに分割され、前記サブフィールドの間、それぞれの発光素子は、対応する画素のビデオレベルを表すサブフィールドコードワードに対応する、以下に保持パルスと呼ばれるスモールパルスで光放出のためにアクチベートすることができ、電力レベルモードのセットは、それぞれの電力レベルモードに対して固有なサブフィールド編成が属する、サブフィールドコーディングについて提供され、前記サブフィールド編成は、フレームの間に保持パルスの数に関して可変であり、

当該装置は、

表示されるべき前記入力画像の特性である平均電力値を決定する平均画像電力回路と、

決定された平均電力値を第一の保持パルスの数に変換する第一の回路と、

前記入力画像のフレーム周波数を測定し、前記入力画像のフレーム周波数を最多の許容される保持パルスの数に変換する周波数測定回路と、

前記第一の保持パルスの数と保持ゲインとを乗算して、第二の保持パルスの数を伝送する第二の回路と、前記保持ゲインは、前記表示装置の公称のフレーム周波数に対する入力フレームの周波数の割合を表し、

前記第二の保持パルスの数と前記最多の許容される保持パルスの数との間で最少の保持パルスの数を選択する第三の回路と、

前記最少の保持パルスの数を、ある電力レベルモードに変換する電力レベル回路と、

を備えることを特徴とする装置。

【請求項3】

当該電力レベルの制御装置は、

前記決定された平均電力値を第一の数の保持パルスに変換する第一の回路と、

前記入力画像の前記測定されたフレーム周波数を前記最多の許容される保持パルスの数及び前記保持ゲインに変換する第二の回路と、

前記保持ゲインで第一の保持パルスの数を乗算し、第二の保持パルスの数を出力する第三の回路と、

前記第二の保持パルスの数と前記最多の許容される保持パルスの数との間で最少の保持パルスの数を選択する第四の回路と、

前記少ない方の保持パルスの数を前記電力レベルモードに変換する第五の回路と、

を含む請求項2記載の装置。

【請求項4】

第一、第二及び第五の回路は、ルックアップテーブルである、

請求項3記載の装置。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−20277(P2013−20277A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2012−239171(P2012−239171)

【出願日】平成24年10月30日(2012.10.30)

【分割の表示】特願2006−304371(P2006−304371)の分割

【原出願日】平成18年11月9日(2006.11.9)

【出願人】(501263810)トムソン ライセンシング (2,848)

【氏名又は名称原語表記】Thomson Licensing

【住所又は居所原語表記】1−5, rue Jeanne d’Arc, 92130 ISSY LES MOULINEAUX, France

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成24年10月30日(2012.10.30)

【分割の表示】特願2006−304371(P2006−304371)の分割

【原出願日】平成18年11月9日(2006.11.9)

【出願人】(501263810)トムソン ライセンシング (2,848)

【氏名又は名称原語表記】Thomson Licensing

【住所又は居所原語表記】1−5, rue Jeanne d’Arc, 92130 ISSY LES MOULINEAUX, France

【Fターム(参考)】

[ Back to top ]