表示装置の作製方法

【課題】少ないマスク数で表示特性が良好な表示装置を作製する。

【解決手段】第1の導電膜と、該第1の導電膜上に絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜をこの順に積層した薄膜積層体と、を形成し、第1のエッチングにより前記第1の導電膜を露出させつつ、少なくとも前記薄膜積層体のパターンを形成し、第2のエッチングにより第1の導電膜のパターンを形成し、第3のエッチングにより第2の導電膜を所望の形状とすることでソース電極及びドレイン電極層を形成することで薄膜トランジスタを作製し、この薄膜トランジスタを覆って保護膜を形成し、該保護膜に開口部を形成し、該保護膜上に画素電極層を選択的に形成することで前記薄膜トランジスタのソース電極及びドレイン電極層と画素電極層を接続させる。そして、前記開口部の形成に際して不要な半導体層等をエッチングして除去する。

【解決手段】第1の導電膜と、該第1の導電膜上に絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜をこの順に積層した薄膜積層体と、を形成し、第1のエッチングにより前記第1の導電膜を露出させつつ、少なくとも前記薄膜積層体のパターンを形成し、第2のエッチングにより第1の導電膜のパターンを形成し、第3のエッチングにより第2の導電膜を所望の形状とすることでソース電極及びドレイン電極層を形成することで薄膜トランジスタを作製し、この薄膜トランジスタを覆って保護膜を形成し、該保護膜に開口部を形成し、該保護膜上に画素電極層を選択的に形成することで前記薄膜トランジスタのソース電極及びドレイン電極層と画素電極層を接続させる。そして、前記開口部の形成に際して不要な半導体層等をエッチングして除去する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置の作製方法に関する。

【背景技術】

【0002】

近年、ガラス基板等の絶縁性表面を有する基板上に形成された、厚さ数nm〜数百nm程度の半導体薄膜により構成される薄膜トランジスタが注目されている。薄膜トランジスタは、IC(Integrated Circuit)及び電気光学装置を始めとした電子デバイスに広く応用されている。薄膜トランジスタは、特に液晶表示装置又はEL(Electro Luminescence)表示装置等に代表される、画像表示装置のスイッチング素子として開発が急がれている。アクティブマトリクス型液晶表示装置では、選択されたスイッチング素子に接続された画素電極と、該画素電極に対応する対向電極の間に電圧が印加されることにより、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。ここで、アクティブマトリクス型液晶表示装置とは、マトリクス状に配置された画素電極をスイッチング素子により駆動することによって、画面上に表示パターンが形成される方式を採用した液晶表示装置をいう。アクティブマトリクス型EL表示装置とは、マトリクス状に配置された画素をスイッチング素子により駆動することによって、画面上に表示パターンが形成される方式を採用したEL表示装置をいう。

【0003】

上記のようなアクティブマトリクス型表示装置の用途は拡大しており、画面サイズの大面積化、高精細化及び高開口率化の要求が高まっている。また、アクティブマトリクス型表示装置には高い信頼性が求められ、その生産方法には高い生産性及び生産コストの低減が求められる。生産性を高め、生産コストを低減する方法の一つに、工程の簡略化が挙げられる。

【0004】

アクティブマトリクス型表示装置では、スイッチング素子として主に薄膜トランジスタが用いられている。薄膜トランジスタの作製において、フォトリソグラフィに用いるフォトマスクの枚数を削減することは、工程の簡略化のために重要である。例えばフォトマスクが1枚増加すると、レジスト塗布、プリベーク、露光、現像、ポストベーク等の工程と、その前後の工程において、被膜の形成及びエッチング工程、更にはレジスト剥離、洗浄及び乾燥工程等が必要になる。そのため、作製工程に使用するフォトマスクが1枚増加するだけで、工程数が大幅に増加する。そのため、作製工程におけるフォトマスクを低減するために、数多くの技術開発がなされている。

【0005】

薄膜トランジスタは、チャネル形成領域がゲート電極より下層に設けられるトップゲート型と、チャネル形成領域がゲート電極より上層に設けられるボトムゲート型に大別される。ボトムゲート型薄膜トランジスタの作製工程において使用されるフォトマスクの枚数は、トップゲート型薄膜トランジスタの作製工程において使用されるフォトマスクの枚数よりも少ないことが知られている。ボトムゲート型薄膜トランジスタは、3枚のフォトマスクにより作製されることが一般的である。

【0006】

フォトマスクの枚数を低減させる従来の技術としては、裏面露光、レジストリフロー又はリフトオフ法といった複雑な技術を用いるものが多く、特殊な装置を必要とするものが多い。このような複雑な技術を用いることで、これに起因する様々な問題が生じ、歩留まりの低下の一因となっている。また、薄膜トランジスタの電気的特性を犠牲にせざるを得ないことも多い。

【0007】

薄膜トランジスタの作製工程における、フォトマスクの枚数を減らすための代表的な手段として、多階調マスク(ハーフトーンマスク又はグレートーンマスクと呼ばれるもの)を用いた技術が広く知られている。多階調マスクを用いて作製工程を低減する技術として、例えば特許文献1が挙げられる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−179069号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明の一態様は、光による影響が小さい薄膜トランジスタ及び表示装置を提供することを課題とする。また、本発明の一態様は、電気的特性が良好な薄膜トランジスタ及び表示特性が良好な表示装置を提供することを課題とする。

【0010】

または、本発明の一態様は、薄膜トランジスタの作製に用いるフォトマスクの枚数を従来よりも少なくし、作製工程を簡略化することを課題とする。本発明の一態様は、薄膜トランジスタを有する表示装置の作製工程を簡略化することを課題とする。

【課題を解決するための手段】

【0011】

本発明の一態様は、薄膜トランジスタを覆って保護膜を形成し、該保護膜に開口部を形成し、該保護膜上に画素電極層を選択的に形成することで前記薄膜トランジスタのソース電極及びドレイン電極層と画素電極層を接続させる表示装置の作製方法であって、前記開口部の形成に際して不要な半導体層等をエッチングして除去する表示装置の作製方法である。

【0012】

好ましい形態として、本発明の一態様は、第1の導電膜と、該第1の導電膜上に絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜をこの順に積層した薄膜積層体と、を形成し、第1のエッチングにより前記第1の導電膜を露出させつつ、少なくとも前記薄膜積層体のパターンを形成し、第2のエッチングにより第1の導電膜のパターンを形成する薄膜トランジスタの作製方法である。ここで、第2のエッチングは、第1の導電膜が選択的にサイドエッチングされる条件により行う。その後、第3のエッチングにより第2の導電膜を所望の形状とすることでソース電極及びドレイン電極層を形成し、薄膜トランジスタを作製する。その後、前記薄膜トランジスタを覆って保護膜を形成し、該保護膜に開口部を形成し、該保護膜上に画素電極層を選択的に形成することで前記薄膜トランジスタのソース電極及びドレイン電極層と画素電極層を接続させる。そして、前記開口部の形成に際して不要な半導体層等をエッチングして除去する。

【発明の効果】

【0013】

光電流による影響が小さく、表示特性が良好な表示装置を作製することができる。

【図面の簡単な説明】

【0014】

【図1】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図2】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図3】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図4】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図5】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図6】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図7】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図8】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図9】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図10】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図11】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図12】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図13】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図14】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図15】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図16】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図17】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図18】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図19】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図20】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図21】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図22】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図23】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図24】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図25】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図26】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図27】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図28】多階調マスクを説明する図。

【図29】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図30】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図31】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図32】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図33】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

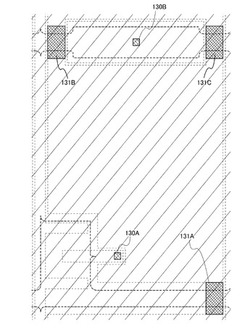

【図34】アクティブマトリクス基板の接続部を説明する図。

【図35】アクティブマトリクス基板の接続部を説明する図。

【図36】アクティブマトリクス基板の接続部を説明する図。

【図37】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図38】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図39】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図40】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図41】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図42】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図43】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図44】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図45】EL表示装置の画素回路の一例を説明する図。

【図46】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図47】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図48】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図49】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図50】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図51】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図52】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図53】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図54】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図55】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図56】電子機器を説明する図。

【図57】電子機器を説明する図。

【図58】電子機器を説明する図。

【発明を実施するための形態】

【0015】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。また、第1の絶縁膜及び第2の絶縁膜は、原則として上面図には表さないものとする。

【0016】

(実施の形態1)

本実施の形態では、薄膜トランジスタの作製方法及び該薄膜トランジスタがマトリクス状に配置された表示装置の作製方法の一例について、図1乃至図36を参照して説明する。

【0017】

なお、図16乃至図23には本実施の形態に係る薄膜トランジスタの上面図を示し、図23は画素電極まで形成した完成図である。図1乃至図3は、図16乃至図23に示すA1−A2における断面図である。図4乃至図6は、図16乃至図23に示すB1−B2における断面図である。図7乃至図9は、図16乃至図23に示すC1−C2における断面図である。図10乃至図12は、図16乃至図23に示すD1−D2における断面図である。図13乃至図15は、図16乃至図23に示すE1−E2における断面図である。

【0018】

本実施の形態にて説明する本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2の導電膜上に第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0019】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第2の導電膜上に第2のレジストマスクを形成し、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0020】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第1のレジストマスクを後退させることで前記第1のレジストマスクの凹部と重畳する前記第2の導電膜を露出させつつ第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0021】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1のレジストマスクを後退させることで前記第1のレジストマスクの凹部と重畳する前記第2の導電膜を露出させつつ第2のレジストマスクを形成し、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0022】

上記構成の表示装置の作製方法において、前記第1のレジストマスクは多階調マスクを用いて形成することが好ましい。多階調マスクを用いることで、簡略な工程で凹部を有するレジストマスクを形成することができる。

【0023】

上記構成の表示装置の作製方法を適用することで、前記第1のエッチングによって素子領域が形成され、前記第2のエッチングによって前記素子領域の側面から概ね等しい距離だけ内側にゲート電極層の側面を形成することができる。

【0024】

上記構成の表示装置の作製方法において、前記第1のエッチングはドライエッチングであり、前記第2のエッチングはウエットエッチングであることが好ましい。

【0025】

上記構成の表示装置の作製方法において、前記第2の絶縁膜は、CVD法又はスパッタリング法により形成した絶縁膜と、スピンコート法により形成した絶縁膜と、を積層して形成することが好ましい。特に好ましくは窒化シリコン膜をCVD法又はスパッタリング法により形成し、有機樹脂膜をスピンコート法により形成する。第2の絶縁膜をこのように形成することで、薄膜トランジスタの電気的特性に影響を及ぼしうる不純物元素等から薄膜トランジスタを保護し、且つ画素電極の被形成面の平坦性を向上させて歩留まりの低下を防止することができる。

【0026】

上記構成の表示装置の作製方法において、前記複数の薄膜トランジスタ間に存在する半導体層を除去するに際して、前記ゲート電極層と重畳していない領域に存在する前記半導体層を除去することが好ましい。ゲート電極層と重畳していない領域に存在する半導体層は光リーク電流の一因となる。そのため、ゲート電極層と重畳していない領域に存在する半導体層を除去することで光リーク電流を低減することができる。

【0027】

以下に、本実施の形態について詳細に説明する。

【0028】

まず、基板100上に、第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110を形成する。これらの膜は、単層で形成してもよいし、複数の膜を積層した積層膜であってもよい。

【0029】

基板100は、絶縁性基板である。表示装置に適用する場合には、基板100としては、ガラス基板又は石英基板を用いることができる。本実施の形態においては、ガラス基板を用いる。

【0030】

基板100としてガラス基板を用いる場合には、基板100上に下地絶縁膜(好ましくは、窒化シリコン膜又は窒化酸化シリコン膜)を設けることが好ましい。下地絶縁膜を設けることで、ガラス基板100中の不純物金属元素が半導体層に侵入することを防ぐことができる。これは、下地絶縁膜が窒素を含む場合に顕著である。更には、下地絶縁膜はハロゲン(フッ素、塩素又は臭素)を含むことが好ましい。ガラス基板100中の不純物金属元素が半導体層に侵入することをより効果的に防ぐことができるためである。絶縁膜にハロゲンを含ませるには、形成に用いるガスに、ハロゲンガス又はハロゲン化合物からなるガスを含ませればよく、CVD法又はスパッタリング法により単層で又は積層して形成することができる。

【0031】

第1の導電膜102は、導電性材料により形成する。第1の導電膜102は、例えばチタン、モリブデン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、ニオブ若しくはスカンジウム等の金属材料又はこれらを主成分とする合金材料等の導電性材料を用いて形成することができる。ただし、後の工程(第1の絶縁膜104の形成等)に耐えうる程度の耐熱性は必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。更には、第2のエッチングによりエッチング可能な材料を用いる。この限りにおいて、第1の導電膜102は特定の材料に限定されない。第1の導電膜102の形成は、例えばスパッタリング法又はCVD法(熱CVD法又はプラズマCVD法等を含む)等により行えばよいが、特定の方法に限定されない。

【0032】

なお、ここで、膜が「耐熱性を有する」とは、後の工程における温度によって当該膜が膜としての形態を保ち、且つ当該膜に求められる機能及び特性を保つことができることをいう。

【0033】

第1の絶縁膜104は、ゲート絶縁層として機能し、絶縁性材料により形成する。第1の絶縁膜104は、例えば、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜又は窒化酸化シリコン膜等を用いて形成することができる。ただし、第1の導電膜102と同様に後の工程(半導体膜106の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。この限りにおいて、第1の絶縁膜104は特定の材料に限定されない。第1の絶縁膜104の形成は、例えばCVD法(熱CVD法又はプラズマCVD法等を含む)又はスパッタリング法等により行えばよいが、特定の方法に限定されない。

【0034】

半導体膜106は、半導体材料により形成する。半導体膜106は、例えば、シランガスにより形成される非晶質シリコン等を用いて形成することができる。ただし、第1の導電膜102等と同様に、後の工程(第2の導電膜110等の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食にくい材料を選択することを要する。この限りにおいて、半導体膜106は特定の材料に限定されるものではない。従って、ゲルマニウム等を用いても良い。なお、半導体膜106の結晶性についても特に限定されない。半導体膜106の形成は、例えばCVD法(熱CVD法又はプラズマCVD法等を含む)又はスパッタリング法等により行えばよいが、特定の方法に限定されない。

【0035】

不純物半導体膜108は、一導電性を付与する不純物元素を含む半導体膜であり、一導電性を付与する不純物元素が添加された半導体材料形成のためのガス等により形成される。例えば、フォスフィン(化学式:PH3)又はジボラン(化学式:B2H6)を含むシランガスにより形成される、リン又はボロンを含むシリコン膜である。ただし、第1の導電膜102等と同様に、後の工程(第2の導電膜110等の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。この限りにおいて、不純物半導体膜108は、特定の材料に限定されない。n型の薄膜トランジスタを作製する場合には、添加する一導電性を付与する不純物元素として、リン又はヒ素等を用いればよい。すなわち、形成に用いるシランガスにはフォスフィン又はアルシン(化学式:AsH3)等を所望の濃度で含ませればよい。または、p型の薄膜トランジスタを作製する場合には、一導電性を付与する不純物元素として、ボロン等を添加すればよい。すなわち、形成に用いるシランガスにはジボラン等を所望の濃度で含ませればよい。なお、不純物半導体膜108の形成は、例えばCVD法(熱CVD法又はプラズマCVD法等を含む)等により行うことができるが、特定の方法に限定されるものではない。なお、不純物半導体膜108の結晶性についても特に限定されない。また、半導体膜106により形成される半導体層の一部に、ドーピング等によりソース電極及びドレイン電極層とオーミック接触可能な領域を設ける場合などには、不純物半導体膜108を設けなくてもよい。

【0036】

第2の導電膜110は、導電性材料(第1の導電膜102として列挙した材料等)であって、第1の導電膜102とは異なる材料により形成する。ここで、「異なる材料」とは、主成分が異なる材料をいう。具体的には、後に説明する第2のエッチングによりエッチングされにくい材料を選択すればよい。また、第1の導電膜102等と同様に、後の工程(第1の保護膜126等の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。従って、この限りにおいて、第2の導電膜110は特定の材料に限定されない。第2の導電膜110の形成は、例えばスパッタリング法又はCVD法(熱CVD法又はプラズマCVD法等を含む)等により行えばよいが、特定の方法に限定されるものではない。

【0037】

なお、上記説明した第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110に対して求められる耐熱性は、第1の導電膜102が最も高く、以下前記した順に続き、第2の導電膜110が最も低い。例えば、半導体膜106が水素を含む非晶質半導体膜である場合には、約300℃以上とすることで半導体膜中の水素が脱離し、電気的特性が変化する。そのため、例えば半導体膜106を形成した後の工程では概ね300℃を超えない温度とすることが好ましい。

【0038】

次に、第2の導電膜110上に第1のレジストマスク112を形成する(図1(A)、図4(A)、図7(A)、図10(A)、図13(A)、図16を参照)。

【0039】

次に、第1のレジストマスク112を用いて第1のエッチングを行う。すなわち、第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110をエッチングによりパターニングし、薄膜積層体114を形成する(図1(B)、図4(B)、図7(B)、図10(B)、図13(B)、図17を参照)。本明細書において、このエッチング工程を第1のエッチングとよぶ。第1のエッチングは、ドライエッチング又はウエットエッチングを用いればよいが、異方性の高いエッチング法(物理的エッチング)により行うことが好ましい。第1のエッチングに異方性の高いエッチング法を用いることで、パターンの加工精度を向上させることができる。なお、第1のエッチングをドライエッチングにより行う場合には一の工程にて行うことが可能であるが、第1のエッチングをウエットエッチングにより行う場合には、複数の工程により第1のエッチングを行うと良い。ウエットエッチングでは、被エッチング膜の種類によってエッチングレートが異なるため、すべての膜を一の工程にてエッチングすることが困難だからである。従って、第1のエッチングには、ドライエッチングを用いることが好ましい。

【0040】

ここで、例えば第1の導電膜102としてモリブデン膜を形成し、第1の絶縁膜104として窒化シリコン膜を形成し、半導体膜106として非晶質シリコン膜を形成し、不純物半導体膜108としてリンを含む非晶質シリコン膜を形成し、第2の導電膜110としてタングステン膜を形成した場合、第1のエッチングは、3段階のドライエッチングにより行えばよい。まず、Cl2ガスとCF4ガスとO2ガスの混合ガスを用いてエッチングを行うことで第2の導電膜110をエッチングする。次に、Cl2ガスを用いてエッチングを行うことで半導体膜106及び不純物半導体膜108をエッチングする。最後に、CHF3ガスを用いてエッチングを行うことで第1の絶縁膜104をエッチングすればよい。また、この後更にCl2ガスとCF4ガスとO2ガスの混合ガスを用いてエッチング行うことで4段階のドライエッチングとしてもよい。

【0041】

次に、第1の導電膜102をサイドエッチングによりパターニングし、ゲート電極層116を形成する(図1(C)、図4(C)、図7(C)、図10(C)、図13(C)、図18を参照)。このエッチング工程を第2のエッチングとよぶ。

【0042】

なお、ゲート電極層116は、薄膜トランジスタのゲート電極、ゲート配線、容量素子の一方の電極及び容量配線を構成している。ゲート電極層116Aと表記する場合には、ゲート配線と薄膜トランジスタのゲート電極を構成するゲート電極層を指す。ゲート電極層116Bと表記する場合には、容量配線と容量素子の一方の電極を構成するゲート電極層を指す。そして、これらを総括してゲート電極層116とよぶ。

【0043】

なお、「ゲート配線」とは、薄膜トランジスタのゲート電極に接続される配線をいう。ゲート配線は、ゲート電極層により形成される。また、ゲート配線は走査線と呼ばれることがある。

【0044】

第2のエッチングは、第1の導電膜102により形成されるゲート電極層116の側面が、薄膜積層体114の側面より内側に形成されるエッチング条件により行う。(図18乃至図21におけるA1−A2断面において、ゲート電極層116の幅が半導体膜106等の幅より小さくなるようにエッチングを行う)。更には、第2の導電膜110に対するエッチングレートが小さく、且つ第1の導電膜102に対するエッチングレートが大きい条件により行う。換言すると、第2の導電膜110に対する第1の導電膜102のエッチング選択比が大きい条件により行う。このような条件により第2のエッチングを行うことで、ゲート電極層116を形成することができる。

【0045】

なお、ゲート電極層116の側面の形状は特に限定されない。例えば、テーパ形状であっても良い。ゲート電極層116の側面の形状は、第2のエッチングにおいて用いる薬液等の条件によって決められるものである。

【0046】

ここで、「第2の導電膜110に対するエッチングレートが小さく、且つ第1の導電膜102に対するエッチングレートが大きい条件」、又は「第2の導電膜110に対する第1の導電膜102のエッチング選択比が大きい条件」とは、以下の第1の要件及び第2の要件を満たすものをいう。

【0047】

第1の要件は、ゲート電極層116が必要な箇所に残存することである。ゲート電極層116の必要な箇所とは、図18におけるレジストマスク内に点線で示される領域をいう。すなわち、第2のエッチング後に、ゲート電極層116がゲート電極、ゲート配線、容量素子の一方の電極及び容量配線を構成するように残存することが必要である。ゲート電極層がゲート配線及び容量配線を構成するためには、これらの配線が断線しないように第2のエッチングを行う必要がある。図1(C)及び図13(C)に示されるように、薄膜積層体114の側面から間隔d1だけ内側にゲート電極層116の側面が形成されることが好ましく、間隔d1は実施者がレイアウトに従って適宜設定すればよい。

【0048】

第2の要件は、ゲート電極層116により構成されるゲート配線及び容量配線の最小幅d3、並びにソース電極及びドレイン電極層120Aにより構成されるソース配線の最小幅d2が適切なものとなることである(図21を参照)。第2のエッチングにより第2の導電膜110がエッチングされるとソース配線の最小幅d2が小さくなり、ソース配線の電流密度が過大となり、電気的特性が低下するためである。そのため、第2のエッチングは、第1の導電膜102のエッチングレートが過大にならず、且つ第2の導電膜110のエッチングレートが可能な限り小さい条件で行う。

【0049】

また、ソース配線の最小幅d2は大きくすることが困難である。ソース配線の最小幅d2はソース配線と重畳する半導体層の最小幅d4により決まり、ソース配線の最小幅d2を大きくするためには半導体層の最小幅d4を大きくせねばならず、隣接するゲート配線と容量配線とを絶縁させることが困難になるためである。従って、半導体層の最小幅d4は、前記した間隔d1の概ね2倍よりも小さくする。換言すると、間隔d1は半導体層の最小幅d4の約半分よりも大きくする。

【0050】

なお、ソース配線と重畳する半導体層の幅を最小幅d4とする部分は、ゲート配線と、該ゲート配線と互いに隣接する容量配線との間に少なくとも一箇所あればよい。好ましくは、図21に示すように、ゲート配線に隣接する領域及び容量配線に隣接する領域の半導体層の幅を最小幅d4とすればよい。

【0051】

なお、ソース電極及びドレイン電極層により形成される、画素電極層と接続される部分の電極の幅はソース配線の最小幅d2とすることが好ましい。

【0052】

第1のレジストマスク112が上記したように所定の形状であり、第2のエッチングが第1の導電膜102のサイドエッチングを伴うことによって、ゲート電極層116により構成される、隣接するゲート配線と容量配線とを絶縁させることができるためである(図18を参照)。ここで、第2のエッチングは、サイドエッチングを伴うエッチングであるため、エッチングは概略等方的に進行する条件により行う。

【0053】

ここで、サイドエッチングとは、被エッチング膜の厚さ方向(基板面に垂直な方向又は下地絶縁膜の面に垂直な方向)のみならず、厚さ方向に対して垂直な方向(基板面に平行な方向又は下地絶縁膜の面に平行な方向)にも被エッチング膜が削られるエッチングをいう。サイドエッチングされた被エッチング膜の端部は、被エッチング膜に対するエッチングガス又はエッチングに用いる薬液のエッチングレートによって様々な形状となるように形成されるが、端部が曲面となるように形成されることが多い。

【0054】

なお、図示していないが、ゲート電極層116と接する空洞部分にゲート電極層116と同一の層により形成される支持部を有していてもよい。支持部を設けることで、薄膜積層体114が自重によって破壊され、又は破損することをも防止でき、歩留まりが向上するため好ましい。

【0055】

次に、第2のエッチングに用いることのできるエッチャント又はエッチングガスと、第1の導電膜102及び第2の導電膜110の組み合わせについて説明する。

【0056】

第2のエッチングをウエットエッチングによって行う場合、例えば、第1の導電膜102はアルミニウムを主成分とする材料若しくはチタンを主成分とする材料又はこれらを積層させて形成し、第2の導電膜110は銅を主成分とする材料により形成し、エッチャントとしては、希硫酸、濃リン酸、濃塩酸、希リン酸又はシュウ酸を用いる。なお、エッチャントとして、希硫酸、希リン酸又はシュウ酸を用いる場合には室温よりも高温(50℃〜100℃、好ましくは60〜75℃)にするとよい。なお、第2の導電膜110は、好ましくはカルシウム及び酸素を含んだ銅を主成分とする材料と、カルシウムを含んだ銅を主成分とする材料と、マグネシウムを含んだ銅を主成分とする材料と、を積層して形成する。または、カルシウム及び酸素を含んだ銅を主成分とする材料と、マグネシウム及び酸素を含んだ銅を主成分とする材料と、マグネシウムを含んだ銅を主成分とする材料と、を積層して形成することが好ましい。またはこれらを混合して用いてもよい。

【0057】

または、例えば、第1の導電膜102はアルミニウムを主成分とする材料若しくはチタンを主成分とする材料又はこれらを積層させて形成し、第2の導電膜110はモリブデンを主成分とする材料により形成してもよく、この場合にはエッチャントとして、フッ酸、希塩酸、濃塩酸、希硫酸、濃硫酸、希リン酸、濃リン酸又はシュウ酸を用いる。なお、エッチャントとして、希塩酸、希硫酸、希リン酸又はシュウ酸を用いる場合には、室温よりも高温(50℃〜100℃、好ましくは60〜75℃)にして用いるとよい。ただし、濃硫酸を用いる場合には、高温では第2の導電膜110の主成分であるモリブデンがエッチングされてしまうため、室温程度で用いる。またはこれらを混合して用いてもよい。

【0058】

ただし、上記列挙したエッチャントのうち、少なくとも、濃硫酸、希リン酸及び濃リン酸は、レジストマスクに対して脱水作用を起こすため、これらのエッチャントを用いる場合にはレジストマスクを除去した状態で用いる。

【0059】

または、好ましい形態として、第1の導電膜102をアルミニウム又はモリブデンにより形成し、第2の導電膜110をチタン又はタングステンにより形成し、エッチャントには、硝酸、酢酸及びリン酸を含む薬液を用いる。または、第1の導電膜102をモリブデンにより形成し、第2の導電膜110をチタン、アルミニウム又はタングステンにより形成し、エッチャントには、過酸化水素水を含む薬液を用いればよい。

【0060】

または、最も好ましい形態として、第1の導電膜102をアルミニウム層上にモリブデン層が積層された積層膜とし、第2の導電膜110をタングステン層とし、エッチャントには、硝酸を2%、酢酸を10%、リン酸を72%含む薬液を用いる。

【0061】

なお、上記した第1の導電膜102を構成する材料として列挙したアルミニウムを主成分とする材料として、好ましくは、ネオジムを添加したアルミニウムを用いる。第1の導電膜102にネオジムを添加したアルミニウムを用いることで、アルミニウムの高抵抗化を抑制しつつ、ヒロックの発生を防止することができる。

【0062】

また、上記した第2の導電膜110を構成する材料として列挙したモリブデンを主成分とする材料として、ニオブを添加したモリブデンを用いてもよい。

【0063】

または、第2のエッチングはドライエッチングによって行ってもよい。例えば、第1の導電膜102はタングステンを主成分とする材料により形成し、第2の導電膜110は、アルミニウムを主成分とする材料若しくはチタンを主成分とする材料又はこれらを積層させて形成し、エッチングガスとして三フッ化塩素(化学式:ClF3)ガスを用いることで第2のエッチングを行うことができる。ただし、半導体膜106にシリコンを用いる場合には三フッ化塩素ガスを用いるとエッチングされてしまうため、第2のエッチングの前に酸化処理を行うとよい。酸化処理は、薄膜積層体114の表面を酸化することができる方法を用いて行えばよく、特定の方法に限定されない。この酸化処理は、酸素プラズマ若しくは水プラズマによるプラズマ処理、オゾン水による処理、または熱処理により行うことができる。

【0064】

なお、図18に示すように、上面から見たゲート電極層116は角(例えば、角151)を有する。これは、ゲート電極層116を形成する第2のエッチングが概略等方的であるために、ゲート電極層116の側面と薄膜積層体114の側面との間隔d1が概略等しくなるようにエッチングされるためである。

【0065】

次に、第2のレジストマスク118を形成する(図2(D)、図5(D)、図8(D)、図11(D)、図14(D)、図19を参照)。なお、ここでは第2のエッチングの後に第2のレジストマスク118を形成するが、これに限定されず、第2のレジストマスク118を形成した後に第2のエッチングを行ってもよい。

【0066】

次に、第2のレジストマスク118を用いて、第2の導電膜110をエッチングし、ソース電極及びドレイン電極層120を形成する。ここでエッチング条件は、第2の導電膜110以外の膜に対する食刻及び腐食が生じにくい条件を選択する。特に、ゲート電極層116の食刻及び腐食が生じにくい条件により行うことが重要である。

【0067】

なお、ソース電極及びドレイン電極層120は、薄膜トランジスタのソース電極、ドレイン電極、ソース配線、薄膜トランジスタと画素電極とを接続する電極、及び容量素子の他方の電極を構成している。「ソース電極及びドレイン電極層120A」又は「ソース電極及びドレイン電極層120C」と表記する場合には、薄膜トランジスタのソース電極及びドレイン電極の一方、及びソース配線を構成する電極層を指す。「ソース電極及びドレイン電極層120B」と表記する場合には、薄膜トランジスタのソース電極及びドレイン電極の他方、及び薄膜トランジスタと画素電極とを接続する電極を構成する電極層を指す。「ソース電極及びドレイン電極層120D」と表記する場合には、容量素子の他方の電極を構成する電極層を指す。そして、これらを総括してソース電極及びドレイン電極層120とよぶ。

【0068】

また、「ソース配線」とは、薄膜トランジスタのソース電極及びドレイン電極の一方に接続される配線をいう。ソース配線は、ソース電極及びドレイン電極層により形成される。また、ソース配線は信号線と呼ばれることがある。

【0069】

なお、第2の導電膜110のエッチングは、ウエットエッチング又はドライエッチングのどちらを用いても良い。

【0070】

続いて、不純物半導体膜108及び半導体膜106の上部(バックチャネル部)をエッチングして、ソース領域及びドレイン領域122と半導体層124を形成する(図2(E)、図5(E)、図8(E)、図11(E)、図14(E)、図20を参照)。ここでエッチング条件は、不純物半導体膜108及び半導体膜106以外の膜に対する食刻及び腐食が生じにくい条件を選択する。特に、ゲート電極層116の食刻及び腐食が生じにくい条件により行うことが重要である。この工程を一括して第3のエッチングとよぶ。第3のエッチングは、上記説明したように、複数の段階に分けて行っても良いし、一括して行っても良い。

【0071】

なお、ソース領域及びドレイン領域122Aは、ソース電極及びドレイン電極層120Aと重畳するものを指し、ソース領域及びドレイン領域122Bは、ソース電極及びドレイン電極層120Bと重畳するものを指し、ソース領域及びドレイン領域122Cは、ソース電極及びドレイン電極層120Cと重畳するものを指し、ソース領域及びドレイン領域122Dは、ソース電極及びドレイン電極層120Dと重畳するものを指す。そして、これらを総括してソース領域及びドレイン領域122とよぶ。

【0072】

なお、不純物半導体膜108及び半導体膜106の上部(バックチャネル部)のエッチングはドライエッチング又はウエットエッチングにより行うことができる。

【0073】

その後、第2のレジストマスク118を除去し、薄膜トランジスタが完成する(図2(F)、図5(F)、図8(F)、図11(F)、図14(F)を参照)。

【0074】

以上のように形成した薄膜トランジスタを覆って第2の絶縁膜を形成する。ここで、第2の絶縁膜は、第1の保護膜126のみで形成しても良いが、好ましくは第1の保護膜126と第2の保護膜128により形成する(図3(G)、図6(G)、図9(G)、図12(G)、図15(G)を参照)。第1の保護膜126は、第1の絶縁膜104と同様に形成すればよい。

【0075】

第2の保護膜128は、表面が概略平坦になる方法により形成する。第2の保護膜128の表面を概略平坦にすることで、第2の保護膜128上に形成される画素電極層132の形成不良などを防止することができるためである。従って、ここで「概略平坦」とは、上記目的を達成しうる程度のものであればよく、高い平坦性が要求されるわけではない。

【0076】

なお、第2の保護膜128は、例えば、感光性ポリイミド、アクリル又はエポキシ樹脂等を用いて、スピンコーティング法等により形成することができる。ただし、これらの材料又は形成方法に限定されるものではない。

【0077】

次に、第2の絶縁膜に第1の開口部130及び第2の開口部131を形成する(図3(H)、図6(H)、図9(H)、図12(H)、図15(H)を参照)。第1の開口部130は、ソース電極及びドレイン電極層120の少なくとも表面に達するように形成する。第2の開口部131は、ゲート電極層116の少なくとも表面に達するように形成する。第1の開口部130及び第2の開口部131の形成方法は、特定の方法に限定されず、第1の開口部130の径等に応じて実施者が適宜選択すればよい。例えば、フォトリソグラフィ法によりドライエッチングを行うことで第1の開口部130及び第2の開口部131を形成することができる。

【0078】

なお、図21に第2の絶縁膜を表して第1の開口部130及び第2の開口部131の位置を明確にしたものを図22に示す。図22に示すように、第1の開口部130A及び第1の開口部130B、並びに第2の開口部131A、第2の開口部131B及び第2の開口部131Cを形成するとよい。

【0079】

ここで、例えば第1の導電膜102としてモリブデン膜を形成し、第1の絶縁膜104として窒化シリコン膜を形成し、半導体膜106として非晶質シリコン膜を形成し、不純物半導体膜108としてリンを含む非晶質シリコン膜を形成し、第2の導電膜110としてタングステン膜を形成した場合には、例えば、CHF3ガスとO2ガスを用いてエッチングを行うことで第1の保護膜126及び第2の保護膜128をエッチングし、Cl2ガスを用いてエッチングを行うことで半導体膜106をエッチングし、CHF3ガスを用いてエッチングを行うことで第1の絶縁膜104をエッチングすればよい。

【0080】

なお、フォトリソグラフィ法によって開口部を形成すると、フォトマスクを1枚使用することになる。

【0081】

次に、第2の絶縁膜上に画素電極層132を形成する(図3(I)、図6(I)、図9(I)、図12(I)、図15(I)、図23を参照)。画素電極層132は、開口部を介してソース電極及びドレイン電極層120に接続されるように形成する。具体的には、画素電極層132は、第1の開口部130を介してソース電極及びドレイン電極層120Bに接続され、第2の開口部131を介してソース電極及びドレイン電極層120Dに接続されるように形成される。画素電極層132は、透光性を有する導電性材料により形成することが好ましい。ここで、透光性を有する導電性材料としては、インジウム錫酸化物(以下、ITOという)、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、又は酸化珪素を添加したインジウム錫酸化物等が挙げられる。透光性を有する導電性材料の膜の形成はスパッタリング法又はCVD法等により行えばよいが、特定の方法に限定されるものではない。また、画素電極層132についても単層で形成しても良いし、複数の膜を積層して形成してもよい。

【0082】

なお、例えば画素電極層132をITOにより形成した場合には、ゲート電極層116とソース電極及びドレイン電極層120の表面にアルミニウムが配されないようにする。ITOとアルミニウムが接触すると電蝕反応が生じるためである。

【0083】

なお、本実施の形態においては、画素電極層132のみに透光性を有する導電性材料を用いたが、これに限定されない。第1の導電膜102及び第2の導電膜110の材料として、透光性を有する導電性材料を用いることもできる。

【0084】

なお、フォトリソグラフィ法によって画素電極層132を形成することで、フォトマスクを1枚使用することになる。

【0085】

以上説明したように、アクティブマトリクス基板の作製(所謂アレイ工程)が完了する(図23を参照)。上記説明したように、サイドエッチングを利用してゲート電極層を形成することで、従来よりもフォトマスクの枚数を1枚低減した薄膜トランジスタの作製が可能となる。

【0086】

上記薄膜トランジスタは、ゲート電極層を有し、前記ゲート電極層上にゲート絶縁層を有し、前記ゲート絶縁層上に半導体層を有し、前記半導体層上にソース領域及びドレイン領域を有する不純物半導体層を有し、前記ソース領域及びドレイン領域上にソース電極及びドレイン電極を有し、前記ゲート電極層の側面に接して空洞を有するものである。また、ゲート絶縁層は、ゲート電極層上にのみ設けられており、ゲート電極の側面はゲート絶縁層により覆われていない構造となる(図3(I)を参照)。このような薄膜トランジスタはゲート電極層の側面に接して空洞を有するため、ゲート電極層端部におけるリーク電流の小さいものとなる。

【0087】

なお、第2の開口部131の位置は、図21及び図22に示す位置に限定されない。第2の開口部131を所定の位置に配することによって、図24乃至図27に示すように、不要な半導体層(点線で示す領域)を除去することができる。

【0088】

なお、上記の説明では多階調マスクを用いない薄膜トランジスタの作製方法及び表示装置の作製方法について説明したが、多階調マスクを用いて薄膜トランジスタ及び表示装置を作製してもよい。多階調マスクを用いることで薄膜トランジスタを1枚のフォトマスクにより作製することが可能となり、フォトマスクの位置合わせの際にずれが発生することを防止することができる。多階調マスクを用いる場合の薄膜トランジスタの作製方法について、図28乃至図33を参照しつつ、以下に説明する。

【0089】

なお、図29は図1及び図2に対応するものである。図30は図10及び図11に対応するものである。図31、図32及び図33は、それぞれ図16、図18及び図19に対応するものである。また、図31乃至図33に示すA1−A2における断面図が図29に相当し、図31乃至図33に示すD1−D2における断面図が図30に相当する。

【0090】

まず、基板100上に、第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110を形成する。これらの膜は、単層で形成してもよいし、複数の膜を積層した積層膜であってもよい。これらの形成に用いることのできる材料及びこれらの形成に適用することのできる方法は上記説明したものと同様である。なお、半導体膜106により形成される半導体層の一部に、ドーピング等によりソース電極及びドレイン電極層とオーミック接触可能な領域を設ける場合などには、不純物半導体膜108を設ける必要がない。

【0091】

この第2の導電膜110上に第1のレジストマスク170を形成する(図29(A)、図30(A)及び図31を参照)。第1のレジストマスク170は凹部及び凸部を有するレジストマスクである。換言すると、厚さの異なる複数の領域(ここでは、二の領域)からなるレジストマスクともいうことができる。第1のレジストマスク170において、厚い領域を第1のレジストマスク170の凸部と呼び、薄い領域を第1のレジストマスク170の凹部とよぶこととする。

【0092】

第1のレジストマスク170において、ソース電極及びドレイン電極層120が形成される領域には凸部が形成され、ソース電極及びドレイン電極層120を有さず半導体層が露出して形成される領域には凹部が形成される。

【0093】

第1のレジストマスク170は、多階調マスクを用いることで形成することができる。ここで、多階調マスクについて図28を参照して以下に説明する。

【0094】

多階調マスクとは、多段階の光量で露光を行うことが可能なマスクであり、代表的には、露光領域、半露光領域及び未露光領域の3段階の光量で露光を行うものをいう。多階調マスクを用いることで、一度の露光及び現像工程によって、複数(代表的には二種類)の厚さを有するレジストマスクを形成することができる。そのため、多階調マスクを用いることで、フォトマスクの枚数を削減することができる。

【0095】

図28(A)及び図28(B)は、代表的な多階調マスクの断面図を示す。図28(A)にはグレートーンマスク140を示し、図28(B)にはハーフトーンマスク145を示す。

【0096】

図28(A)に示すグレートーンマスク140は、透光性を有する基板141上に遮光膜により形成された遮光部142、及び遮光膜のパターンにより設けられた回折格子部143で構成されている。

【0097】

回折格子部143は、露光に用いる光の解像度限界以下の間隔で設けられたスリット、ドット又はメッシュ等を有することで、光の透過量を制御する。なお、回折格子部143に設けられるスリット、ドット又はメッシュは周期的なものであってもよいし、非周期的なものであってもよい。

【0098】

透光性を有する基板141としては、石英等を用いることができる。遮光部142及び回折格子部143を構成する遮光膜は、金属膜を用いて形成すればよく、好ましくはクロム又は酸化クロム等により設けられる。

【0099】

グレートーンマスク140に露光するための光を照射した場合、図28(A)に示すように、遮光部142に重畳する領域における透光率は0%となり、遮光部142又は回折格子部143が設けられていない領域における透光率は100%となる。また、回折格子部143における透光率は、概ね10〜70%の範囲であり、回折格子のスリット、ドット又はメッシュ等の間隔により調整可能である。

【0100】

図28(B)に示すハーフトーンマスク145は、透光性を有する基板146上に半透光膜により形成された半透光部147、及び遮光膜により形成された遮光部148で構成されている。

【0101】

半透光部147は、MoSiN、MoSi、MoSiO、MoSiON、CrSi等の膜を用いて形成することができる。遮光部148は、グレートーンマスクの遮光膜と同様の金属膜を用いて形成すればよく、好ましくはクロム又は酸化クロム等により設けられる。

【0102】

ハーフトーンマスク145に露光するための光を照射した場合、図28(B)に示すように、遮光部148に重畳する領域における透光率は0%となり、遮光部148又は半透光部147が設けられていない領域における透光率は100%となる。また、半透光部147における透光率は、概ね10〜70%の範囲であり、形成する材料の種類又は形成する膜厚等により、調整可能である。

【0103】

多階調マスクを用いて露光して現像を行うことで、膜厚の異なる領域を有する第1のレジストマスク170を形成することができる。

【0104】

次に、第1のレジストマスク170を用いて第1のエッチングを行う。すなわち、第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110をエッチングによりパターニングし、第1の導電膜102上に薄膜積層体114を形成する。その後、第2のエッチングを行うことで、ゲート電極層116を形成する(図29(C)、図30(C)及び図32を参照)。ここで、第2のエッチングの条件は、上記説明した第2のエッチングと同様である。

【0105】

次に、第1のレジストマスク170を後退させることで、薄膜積層体114上に第2のレジストマスク171を形成する。第2のレジストマスク171を用いてソース電極及びドレイン電極層120、ソース領域及びドレイン領域122、半導体層124を形成する(図29(D)、図30(D)及び図33を参照)。第1のレジストマスク170を後退させるには、酸素プラズマによるアッシング等を行えばよい。その後の工程は上記した、多階調マスクを用いない場合と同様である。

【0106】

なお、ここでは第2のエッチングの後に第1のレジストマスク170を形成する場合について説明したが、これに限定されず、第1のレジストマスク170を形成した後に第2のエッチングを行ってもよい。

【0107】

以上説明したように、多階調マスクを用いることで、薄膜トランジスタを作製することができる。多階調マスクを用いることで、使用するフォトマスクの枚数を更に減らすことができ、1枚のフォトマスクにより薄膜トランジスタを作製することができるため、フォトマスクの位置合わせの際にずれが発生することを防止することができる。また、3枚のフォトマスクを用いて画素トランジスタを有するアクティブマトリクス基板を作製することができる。

【0108】

なお、上記説明したように多階調マスクを用いて作製した薄膜トランジスタも、ゲート電極層の側面に接して空洞を有する。ゲート電極層の側面に接して空洞を有するように形成することで、ゲート電極層端部におけるリーク電流の小さい薄膜トランジスタを作製することができる。従って、コントラスト比が高く、表示品質が良好な表示装置を得ることができる。

【0109】

ここで、上記の工程により作製したアクティブマトリクス基板の端子接続部について図34乃至図36を参照して説明する。

【0110】

図34乃至図36は、上記工程により作製した、アクティブマトリクス基板におけるゲート配線側の端子接続部及びソース配線側の端子接続部の上面図と断面図を示す。

【0111】

図34は、ゲート配線側の端子接続部及びソース配線側の端子接続部における、画素部から延伸したゲート配線及びソース配線の上面図を示す。

【0112】

図35は、図34のX1−X2における断面図を示す。すなわち、図35は、ゲート配線側の端子接続部における断面図を示す。図35では、ゲート電極層116が露出されている。このゲート電極層116が露出された領域に、端子部が接続される。

【0113】

図36は、ソース配線側の端子接続部における断面図を示す。図36において、ゲート電極層116と、ソース電極及びドレイン電極層120は画素電極層132を介して接続されている。図36にはゲート電極層116と、ソース電極及びドレイン電極層120の様々な接続形態を示している。端子接続部には、これらのいずれを用いても良いし、図36に示した以外の接続形態を用いても良い。ソース電極及びドレイン電極層120をゲート電極層116に接続させてゲート電極層116に端子を接続する構成とすることで、端子の接続面の高さを概ね等しくすることができる。

【0114】

図36(A)では、第1の保護膜126及び第2の保護膜128の端部がエッチング等により除去され、ゲート電極層116と、ソース電極及びドレイン電極層120とが露出され、この露出された領域に画素電極層132を形成することで電気的な接続を実現している。図36(A)は、図34のY1−Y2における断面図に相当する。

【0115】

なお、ゲート電極層116と、ソース電極及びドレイン電極層120とが露出された領域の形成は、第1の開口部130及び第2の開口部131の形成と同時に行うことができる。

【0116】

図36(B)では、第1の保護膜126及び第2の保護膜128に第3の開口部160Aが設けられており、第1の保護膜126及び第2の保護膜128の端部がエッチング等により除去されることで、ゲート電極層116と、ソース電極及びドレイン電極層120とが露出され、この露出された領域に画素電極層132を形成することで電気的な接続を実現している。

【0117】

なお、第3の開口部160Aの形成、及びゲート電極層116が露出された領域の形成は、第1の開口部130及び第2の開口部131の形成と同時に行うことができる。

【0118】

図36(C)では、第1の保護膜126及び第2の保護膜128に第3の開口部160B及び第4の開口部161が設けられており、ゲート電極層116と、ソース電極及びドレイン電極層120とが露出され、この露出された領域に画素電極層132を形成することで電気的な接続を実現している。ここで、図36(A)及び(B)と同様に、第1の保護膜126及び第2の保護膜128の端部はエッチング等により除去されているが、この領域は端子の接続部として用いられる。

【0119】

なお、第3の開口部160B及び第4の開口部161の形成、並びにゲート電極層116が露出された領域の形成は、第1の開口部130及び第2の開口部131の形成と同時に行うことができる。

【0120】

なお、開口部の数は特に限定されない。一の端子に対して一の開口部を設けるのみならず、一の端子に対して複数の開口部を設けても良い。一の端子に対して複数の開口部を設けることで、開口部を形成するエッチング工程が不十分である等の理由で開口部が良好に形成されなかったとしても、他の開口部により電気的接続を実現することができるため、歩留まりが向上する。更には、全ての開口部が問題なく形成された場合であっても、接触面積を広くすることができるため、コンタクト抵抗を低減することができ、好ましい。

【0121】

次に、上記で説明した工程により作製した、表示装置のアクティブマトリクス基板を用いて液晶表示装置を作製する方法について説明する。すなわち、セル工程及びモジュール工程について説明する。ただし、本発明の一形態である表示装置の作製において、セル工程及びモジュール工程は以下の説明に限定されない。

【0122】

セル工程では、上記した工程により作製したアクティブマトリクス基板と、これに対向する基板(以下、対向基板という)とを貼り合わせて液晶を注入する。まず、対向基板の作製方法について、以下に簡単に説明する。なお、対向基板上に形成する膜は単層でも良いし、複数の膜を積層して形成しても良い。

【0123】

まず、基板上に遮光層を形成し、遮光層上に赤、緑、青のいずれかのカラーフィルター層を形成し、カラーフィルター層上に画素電極層を選択的に形成し、画素電極層上にリブを形成する。

【0124】

遮光層としては、遮光性を有する材料の膜を選択的に形成する。遮光性を有する材料としては、例えば、黒色樹脂(カーボンブラック)を含む有機樹脂を用いることができる。または、クロムを主成分とする材料膜の積層膜を用いても良い。クロムを主成分とする材料膜とは、クロム膜、酸化クロム膜又は窒化クロム膜をいう。遮光層に用いる材料は遮光性を有するものであれば特に限定されない。遮光性を有する材料の膜を選択的に形成するにはフォトリソグラフィ法等を用いる。

【0125】

カラーフィルター層は、バックライトから白色光が照射されると、赤、緑、青のいずれかの光のみを透過させることができる有機樹脂膜により選択的に形成すればよい。カラーフィルター層は、形成時に塗り分けを行うことで、選択的に形成することができる。カラーフィルターの配列は、ストライプ配列、デルタ配列又は正方配列を用いればよい。

【0126】

対向基板の画素電極層は、アクティブマトリクス基板が有する画素電極層132と同様に形成することができる。ただし、対向基板の画素電極層は共通電位とするため選択的に形成する必要がなく、対向基板の全面に形成すればよい。

【0127】

画素電極上に形成するリブは、視野角を拡げることを目的として形成される、パターン形成された有機樹脂膜である。特に必要のない場合には形成しなくてもよい。

【0128】

なお、対向基板の作製方法としては、他にも様々な態様が考えられる。例えば、カラーフィルター層を形成後、画素電極層の形成前にオーバーコート層を形成しても良い。オーバーコート層を形成することで画素電極の被形成面の平坦性を向上させることができるため、歩留まりが向上する。また、カラーフィルター層に含まれる材料の一部が液晶材料中に侵入することを防ぐことができる。オーバーコート層には、アクリル樹脂又はエポキシ樹脂をベースとした熱硬化性材料が用いられる。

【0129】

また、リブの形成前又は形成後にスペーサとしてポストスペーサ(柱状スペーサ)を形成しても良い。ポストスペーサとは、アクティブマトリクス基板と対向基板との間のギャップを一定に保つことを目的として、対向基板上に一定の間隔で形成する構造物をいう。ビーズスペーサ(球状スペーサ)を用いる場合には、ポストスペーサを形成しなくても良い。

【0130】

次に、配向膜をアクティブマトリクス基板及び対向基板に形成する。配向膜の形成は、例えば、ポリイミド樹脂等を有機溶剤に溶かし、これを印刷法又はスピンコーティング法等により塗布し、有機溶媒を溜去した後基板を焼成することにより行う。形成される配向膜の膜厚は、一般に、50nm以上100nm以下程度とする。配向膜には、液晶分子がある一定のプレチルト角を持って配向するようにラビング処理を施す。ラビング処理は、例えば、ベルベット等の毛足の長い布により配向膜を擦ることで行う。

【0131】

次に、アクティブマトリクス基板と、対向基板をシール材料により貼り合わせる。対向基板にポストスペーサが設けられていない場合には、ビーズスペーサを所望の領域に分散させて貼り合わせるとよい。

【0132】

次に、貼り合わせられたアクティブマトリクス基板と対向基板の間に、液晶材料を注入する。液晶材料を注入した後、注入口を紫外線硬化樹脂等で封止する。または、液晶材料をアクティブマトリクス基板と対向基板のいずれかの上に滴下した後に、これらの基板を貼り合わせても良い。

【0133】

次に、アクティブマトリクス基板と対向基板とを貼り合わせた液晶セルの両面に偏光板を貼り付けてセル工程が完了する。

【0134】

次に、モジュール工程として、端子部の入力端子(図36(A)乃至(C)において、ゲート電極層116の露出された領域)にFPC(Flexible Printed Circuit)を接続する。FPCはポリイミド等の有機樹脂フィルム上に導電膜により配線が形成されており、異方性導電性ペースト(Anisotropic Conductive Paste。以下、ACPという)を介して入力端子と接続される。ACPは接着剤として機能するペーストと、金等がメッキされた数十〜数百μm径の導電性表面を有する粒子と、により構成される。ペースト中に混入された粒子が入力端子上の導電層と、FPCに形成された配線に接続された端子上の導電層と、に接触することで、これらの間の電気的な接続を実現することができる。なお、FPCの接続後にアクティブマトリクス基板と対向基板に偏光板を貼り付けてもよい。以上のように、表示装置に用いる液晶パネルを作製することができる。

【0135】

本実施の形態にて説明したように、ゲート電極の形成に新たなフォトマスクを用いることなく、表示装置の画素トランジスタを2枚のフォトマスクにより作製することができ、アクティブマトリクス基板を4枚のフォトマスクにより作製することができる。従って、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。

【0136】

または、多階調マスクを用いることで、表示装置の画素トランジスタを1枚のフォトマスクにより作製することができ、アクティブマトリクス基板を3枚のフォトマスクにより作製することができる。従って、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができるのみならず、フォトマスクの位置合わせの際にずれが発生することを防止することができる。

【0137】

また、裏面露光、レジストリフロー及びリフトオフ法等の複雑な工程を経ることなく、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。従って、歩留まりの低下を抑制しつつ、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。従って、製造コストを大幅に削減することができる。また、薄膜トランジスタの電気的特性の低下を抑制しつつ、製造コストを大幅に削減することができる。

【0138】

また、半導体層を遮光することができるため、光リーク電流が低減され、良好な電気的特性を有する薄膜トランジスタを作製し、表示特性が良好な表示装置を作製することができる。更には、不要な部分の半導体層が開口部を形成する工程と同一の工程により除去されているので、マスク枚数を増加させることなく光リーク電流が低減された、良好な電気的特性を有する薄膜トランジスタ及び良好な表示特性を有する表示装置を作製することができる。

【0139】

更には、ゲート電極層端部に生じるリーク電流が小さい薄膜トランジスタを作製することができるため、コントラスト比が高く、表示品質が良好な表示装置を得ることができる。

【0140】

なお、表示装置は、上記説明した画素構造に限定されず、様々な液晶表示装置に適用することができる。

【0141】

(実施の形態2)

本実施の形態では、実施の形態1とは異なる形態について図37乃至図44を参照して説明する。ここで、実施の形態1において、図2(F)等及び図20を参照して説明したソース領域及びドレイン領域と半導体層を形成して薄膜トランジスタを形成する工程までは実施の形態1と同様である。

【0142】

なお、図42乃至図44には本実施の形態に係る薄膜トランジスタの上面図を示し、図44は画素電極まで形成した完成図である。図37は、図42乃至図44に示すA1−A2における断面図である。図38は、図42乃至図44に示すB1−B2における断面図である。図39は、図42乃至図44に示すC1−C2における断面図である。図40は、図42乃至図44に示すD1−D2における断面図である。図41は、図42乃至図44に示すE1−E2における断面図である。

【0143】

本実施の形態にて説明する本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2の導電膜上に第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記複数の薄膜トランジスタのバックチャネル部を覆う部分の前記第2の絶縁膜のみを残留させるようにエッチングを行い、前記複数の薄膜トランジスタのそれぞれに画素電極を選択的に形成することを特徴とする表示装置の作製方法である。

【0144】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第2の導電膜上に第2のレジストマスクを形成し、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記複数の薄膜トランジスタのバックチャネル部を覆う部分の前記第2の絶縁膜のみを残留させるようにエッチングを行い、前記複数の薄膜トランジスタのそれぞれに画素電極を選択的に形成することを特徴とする表示装置の作製方法である。

【0145】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第1のレジストマスクを後退させることで前記第1のレジストマスクの凹部と重畳する前記第2の導電膜を露出させつつ第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記複数の薄膜トランジスタのバックチャネル部を覆う部分の前記第2の絶縁膜のみを残留させるようにエッチングを行い、前記複数の薄膜トランジスタのそれぞれに画素電極を選択的に形成することを特徴とすることを特徴とする表示装置の作製方法である。

【0146】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1のレジストマスクを後退させることで前記第1のレジストマスクの凹部と重畳する前記第2の導電膜を露出させつつ第2のレジストマスクを形成し、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記複数の薄膜トランジスタのバックチャネル部を覆う部分の前記第2の絶縁膜のみを残留させるようにエッチングを行い、前記複数の薄膜トランジスタのそれぞれに画素電極を選択的に形成することを特徴とすることを特徴とする表示装置の作製方法である。

【0147】

上記構成の表示装置の作製方法において、前記第1のレジストマスクは多階調マスクを用いて形成することが好ましい。多階調マスクを用いることで、簡略な工程で凹部を有するレジストマスクを形成することができる。

【0148】

上記構成の表示装置の作製方法を適用することで、前記第1のエッチングによって素子領域が形成され、前記第2のエッチングによって前記素子領域の側面から概ね等しい距離だけ内側にゲート電極層の側面を形成することができる。

【0149】

上記構成の表示装置の作製方法において、前記第1のエッチングはドライエッチングであり、前記第2のエッチングはウエットエッチングであることが好ましい。

【0150】

上記構成の表示装置の作製方法において、前記第2の絶縁膜は、CVD法又はスパッタリング法により形成した絶縁膜と、スピンコート法により形成した絶縁膜と、を積層して形成することが好ましい。特に好ましくは窒化シリコン膜をCVD法又はスパッタリング法により形成し、有機樹脂膜をスピンコート法により形成する。第2の絶縁膜をこのように形成することで、薄膜トランジスタの電気的特性に影響を及ぼしうる不純物元素等から薄膜トランジスタを保護し、且つ画素電極の被形成面の平坦性を向上させて歩留まりの低下を防止することができる。

【0151】

上記構成の表示装置の作製方法において、前記複数の薄膜トランジスタ間に存在する半導体層を除去するに際して、前記ゲート電極層と重畳していない領域に存在する前記半導体層を除去することが好ましい。ゲート電極層と重畳していない領域に存在する半導体層は光リーク電流の一因となる。そのため、ゲート電極層と重畳していない領域に存在する半導体層を除去することで光リーク電流を低減することができる。

【0152】

以下に、本実施の形態について詳細に説明する。

【0153】

基板200上には、ゲート電極層216が設けられており、ゲート電極層216上には第1の絶縁膜204が設けられており、第1の絶縁膜204上には半導体層224が設けられている。半導体層224上にはソース領域及びドレイン領域222が設けられており、ソース領域及びドレイン領域222上にはソース電極及びドレイン電極層220が設けられている。更には、ソース電極及びドレイン電極層220及び半導体層224等を覆って、第2の絶縁膜(第1の保護膜226と第2の保護膜228)が設けられている。これらの膜は、単層で形成してもよいし、複数の膜を積層した積層膜であってもよい。

【0154】

基板200は実施の形態1における基板100に相当し、ガラス基板又は石英基板を用いることができる。

【0155】

ゲート電極層216は、実施の形態1におけるゲート電極層116に相当する。ゲート電極層216は、薄膜トランジスタのゲート電極、ゲート配線、容量素子の一方の電極及び容量配線を構成している。ゲート電極層216Aと表記する場合には、ゲート配線と薄膜トランジスタのゲート電極を構成するゲート電極層を指す。ゲート電極層216Bと表記する場合には、容量配線と容量素子の一方の電極を構成するゲート電極層を指す。なお、図示していないが、ゲート電極層216と接する空洞部分にゲート電極層216により形成される支持部を有していてもよい。支持部を設けることで、歩留まりが向上する。

【0156】

第1の絶縁膜204は、実施の形態1における第1の絶縁膜104に相当する。

【0157】

半導体膜206は、実施の形態1における半導体膜106に相当する。

【0158】

不純物半導体膜208は、実施の形態1における不純物半導体膜108に相当する。

【0159】

ソース電極及びドレイン電極層220は、実施の形態1におけるソース電極及びドレイン電極層120に相当する。なお、ソース電極及びドレイン電極層220は、薄膜トランジスタのソース電極、ドレイン電極、ソース配線、薄膜トランジスタと画素電極とを接続する電極、及び容量素子の他方の電極を構成している。「ソース電極及びドレイン電極層220A」又は「ソース電極及びドレイン電極層220C」と表記する場合には、薄膜トランジスタのソース電極及びドレイン電極の一方、及びソース配線を構成する電極層を指す。「ソース電極及びドレイン電極層220B」と表記する場合には、薄膜トランジスタのソース電極及びドレイン電極の他方、及び薄膜トランジスタと画素電極とを接続する電極を構成する電極層を指す。「ソース電極及びドレイン電極層120D」と表記する場合には、容量素子の他方の電極を構成する電極層を指す。

【0160】

なお、ソース領域及びドレイン領域222Aは、ソース電極及びドレイン電極層220Aと重畳するものを指し、ソース領域及びドレイン領域222Bは、ソース電極及びドレイン電極層220Bと重畳するものを指し、ソース領域及びドレイン領域222Cは、ソース電極及びドレイン電極層220Cと重畳するものを指し、ソース領域及びドレイン領域222Dは、ソース電極及びドレイン電極層220Dと重畳するものを指す。そして、これらを総括してソース領域及びドレイン領域222とよぶ。

【0161】

まず、実施の形態1と同様に形成した薄膜トランジスタを覆って第2の絶縁膜を形成する。ここで、第2の絶縁膜は、第1の保護膜226のみで形成しても良いが、好ましくは第1の保護膜226と第2の保護膜228により形成する(図37(G)、図38(G)、図39(G)、図40(G)、図41(G)を参照)。

【0162】

第1の保護膜226は、実施の形態1における第1の保護膜126に相当する。

【0163】

第2の保護膜228は、実施の形態1における第2の保護膜128に相当する。

【0164】

次に、第2の保護膜の一部をエッチングにより除去する。ここで、エッチングは実施の形態1における第1の開口部130及び第2の開口部131の形成と同様に行うことが可能である。エッチングにより除去する第2の保護膜は、少なくとも、薄膜トランジスタのバックチャネル部と重畳する部分を除いた領域である。このエッチング工程は、ソース電極及びドレイン電極層220が設けられている領域ではソース電極及びドレイン電極層220の表面に達するように行い、ゲート電極層216が設けられている領域ではゲート電極層216に達するように行う。従って、第1の保護膜226及び第2の保護膜228に対するエッチングレートが高く、ゲート電極層216とソース電極及びドレイン電極層220に対するエッチングレートが低い条件により行うとよい。換言すると、ゲート電極層216とソース電極及びドレイン電極層220に対する第1の保護膜226及び第2の保護膜228のエッチング選択比が高い条件により行うとよい。このようにエッチングを行うことで、残存する保護層229を形成することができる。

【0165】

なお、ここで、エッチングに用いる条件は、ソース領域及びドレイン領域222と半導体層224に対するエッチングレートが低いことが好ましい。

【0166】

なお、図42に第2の絶縁膜を表してエッチングする領域を明確にしたものを図43に示す。図43に二点鎖線で示す領域には第2の保護膜が残存するようにエッチングを行うとよい。

【0167】

なお、ここでエッチングする領域は上記の説明に限定されない。例えば、ソース電極及びドレイン電極層220と重畳する領域の一部にも第2の保護膜が残存するようにエッチングしてもよい。この場合にはソース電極及びドレイン電極層220へのエッチングダメージを低減することができる。

【0168】

上記説明したように第2の保護膜の一部を除去するに際して、半導体層224の一部をも除去してもよい。半導体層224の一部、特にゲート電極層216からはみ出している部分(ゲート電極層216と重畳していない部分)の半導体層224をエッチングにより除去することで、光リーク電流を低減することができる(図37(H)、図38(H)、図39(H)、図40(H)、図41(H)、図43を参照)。

【0169】

次に、第2の絶縁膜上に画素電極層232を形成する(図37(I)、図38(I)、図39(I)、図40(I)、図41(I)、図44を参照)。画素電極層232は、上記エッチング工程によりソース電極及びドレイン電極層220の一部(ここでは、ソース電極及びドレイン電極層220Bと、ソース電極及びドレイン電極層220Dの一部)に接続されるように形成する。画素電極層232は、実施の形態1における画素電極層132に相当する。

【0170】

以上説明したように、アクティブマトリクス基板の作製(所謂アレイ工程)が完了する(図44を参照)。

【0171】

本実施の形態においても、ゲート電極の形成に新たなフォトマスクを用いることなく、表示装置の画素トランジスタを2枚のフォトマスクにより作製することができ、アクティブマトリクス基板を4枚のフォトマスクにより作製することができる。従って、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。

【0172】

なお、上記の説明では多階調マスクを用いない薄膜トランジスタの作製方法及び表示装置の作製方法について説明したが、多階調マスクを用いて薄膜トランジスタ及び表示装置を作製してもよい。多階調マスクを用いることで薄膜トランジスタを1枚のフォトマスクにより作製することが可能となり、フォトマスクの位置合わせの際にずれが発生することを防止することができる。

【0173】

また、裏面露光、レジストリフロー及びリフトオフ法等の複雑な工程を経ることなく、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。従って、歩留まりの低下を抑制しつつ、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。従って、製造コストを大幅に削減することができる。また、薄膜トランジスタの電気的特性の低下を抑制しつつ、製造コストを大幅に削減することができる。

【0174】

また、ゲート電極層と重畳しない(すなわち、上面図においてゲート電極層からはみ出した)半導体層の領域を小さくすることができるため、光リーク電流が低減され、良好な電気的特性を有する薄膜トランジスタを作製し、表示特性が良好な表示装置を作製することができる。更には、不要な部分の半導体層が、ソース電極及びドレイン電極層と画素電極層を接続させる領域の形成と同一の工程により除去されているので、マスク枚数を増加させることなく光リーク電流が低減された、良好な電気的特性を有する薄膜トランジスタ及び良好な表示特性を有する表示装置を作製することができる。

【0175】

更には、ゲート電極層端部に生じるリーク電流が小さい薄膜トランジスタを作製することができるため、コントラスト比が高く、表示品質が良好な表示装置を得ることができる。

【0176】

なお、表示装置は、上記説明した画素構造に限定されず、様々な液晶表示装置に適用することができる。

【0177】

(実施の形態3)

本実施の形態では、薄膜トランジスタ及び該薄膜トランジスタがマトリクス状に配置されたEL表示装置の一例について、図45乃至図55を参照して説明する。

【0178】

薄膜トランジスタをスイッチング素子として用いるEL表示装置(アクティブ型EL表示装置)の画素回路としては、様々なものが検討されている。本実施の形態では、単純な画素回路の一例を、図45に示し、この画素回路を適用した画素構造の作製方法について説明する。ただし、開示するEL表示装置の画素回路は図45に示す構成に限定されるものではない。

【0179】

図45に示すEL表示装置の画素構造において、画素361は、第1のトランジスタ351、第2のトランジスタ352、第3のトランジスタ353、容量素子354及び発光素子355を有する。第1乃至第3のトランジスタはn型トランジスタである。第1のトランジスタ351のゲート電極は、ゲート配線356に接続され、ソース電極及びドレイン電極の一方(第1の電極とする。)は、ソース配線358に接続され、ソース電極及びドレイン電極の他方(第2の電極とする。)は、第2のトランジスタ352のゲート電極、及び容量素子354の一方の電極(第1の電極とする。)に接続されている。容量素子354の他方の電極(第2の電極とする。)は、第2のトランジスタ352のソース電極及びドレイン電極の一方(第1の電極とする。)、第3のトランジスタ353のソース電極及びドレイン電極の一方(第1の電極とする。)、並びに発光素子355の一方の電極(第1の電極とする。)に接続されている。第2のトランジスタ352のソース電極及びドレイン電極の他方(第2の電極とする。)は、第2の電源線359に接続されている。第3のトランジスタ353のソース電極及びドレイン電極の他方(第2の電極とする。)は、第1の電源線357に接続され、ゲート電極はゲート配線356に接続されている。発光素子355の他方の電極(第2の電極とする。)は、共通電極360に接続されている。なお、第1の電源線357と第2の電源線359の電位は異なるものとする。

【0180】

なお、「電源線」とは、電源に接続された、一定の電位に保持された配線をいう。

【0181】

画素361の動作について説明する。ゲート配線356の信号によって第3のトランジスタ353がオンすると、第2のトランジスタ352の第1の電極、発光素子355の第1の電極、及び容量素子354の第2の電極の電位が、第1の電源線357の電位(V357)と等しくなる。ここで、第1の電源線357の電位(V357)は一定とするため、第2のトランジスタ352の第1の電極等の電位は一定(V357)である。

【0182】

ゲート配線356の信号によって第1のトランジスタ351が選択されてオンすると、ソース配線358からの信号の電位(V358)が第1のトランジスタ351を介して第2のトランジスタ352のゲート電極に入力される。このとき、第2の電源線359の電位(V359)が第1の電源線357の電位(V357)よりも高ければVgs=V358−V357となる。そして、Vgsが第2のトランジスタ352のしきい値電圧よりも大きければ、第2のトランジスタ352はオンする。

【0183】

従って、第2のトランジスタ352を線形領域で動作させるときには、ソース配線358の電位(V358)を変化させること(例えば、2値)で、第2のトランジスタ352のオンとオフとを制御することができる。つまり、発光素子355が有するEL層に、電圧を印加するかしないかを制御することができる。

【0184】

また、第2のトランジスタ352を飽和領域で動作させるときには、ソース配線358の電位(V358)を変化させることで、発光素子355に流れる電流量を制御することができる。

【0185】

以上のようにして、第2のトランジスタ352を線形領域で動作させる場合、発光素子355に電圧を印加するかしないかを制御することができ、発光素子355の発光状態と非発光状態とを制御することができる。このような駆動方法は、例えば、デジタル時間階調駆動に用いることができる。デジタル時間階調駆動は、1フレームを複数のサブフレームに分割し、各サブフレームにおいて発光素子355の発光状態と非発光状態とを制御する駆動方法である。また、第2のトランジスタ352を飽和領域で動作させる場合、発光素子355に流れる電流量を制御することができ、発光素子355の輝度を調整することができる。図49は、図55に示すB1−B2における断面図である。

【0186】

次に、図45に示す画素回路を適用した画素構造と、その作製方法について以下に説明する。

【0187】

なお、図50乃至図55には本実施の形態に係る薄膜トランジスタの上面図を示し、図55は第1の画素電極まで形成した図である。図46乃至図48は、図50乃至図55に示すA1−A2における断面図である。図49は、図55に示すB1−B2における断面図である。

【0188】

まず、実施の形態1と同様に、基板300上に第1の導電膜302、第1の絶縁膜304、半導体膜306、不純物半導体膜308及び第2の導電膜310をこの順に積層して形成する。これらの膜は、単層で形成してもよいし、複数の膜を積層して形成した積層膜であってもよい。なお、基板300は実施の形態1における基板100に相当する。第1の導電膜302は第1の導電膜102に相当する。第1の絶縁膜304は第1の絶縁膜104に相当する。半導体膜306は半導体膜106に相当する。不純物半導体膜308は不純物半導体膜108に相当する。第2の導電膜310は第2の導電膜110に相当する。従って、これらの材料及び形成方法は実施の形態1と同様である。

【0189】

なお、実施の形態1と同様に基板300と第1の導電膜302の間には下地絶縁膜が設けられていることが好ましい。

【0190】

半導体膜306は、結晶性半導体膜と、非晶質半導体膜との積層膜を用いることが好ましい。結晶性半導体膜としては、多結晶半導体膜又は微結晶半導体膜等が挙げられる。

【0191】

多結晶半導体膜とは、結晶粒により構成され、該結晶粒間に多くの粒界を含む半導体膜をいう。多結晶半導体膜は、例えば熱結晶化法又はレーザ結晶化法により形成される。ここで、熱結晶化法とは、基板上に非晶質半導体膜を形成し、該基板を加熱することで非晶質半導体を結晶化する結晶化法をいう。また、レーザ結晶化法とは、基板上に非晶質半導体膜を形成し、該非晶質半導体膜に対してレーザを照射して非晶質半導体を結晶化する結晶化法をいう。または、ニッケル等の結晶化促進元素を添加して結晶化する結晶化法を用いても良い。結晶化促進元素を添加して結晶化する場合には、該半導体膜に対してレーザ照射を行うことが好ましい。

【0192】

多結晶半導体は、ガラス基板に歪みを生じない程度の温度と時間で結晶化を行うLTPS(Low Temperature Poly Silicon)と、より高温で結晶化を行うHTPS(High Temperature Poly Silicon)に分類される。

【0193】

微結晶半導体膜とは、粒径が概ね2nm以上100nm以下の結晶粒を含む半導体膜をいい、膜の全面が結晶粒のみによって構成されるもの、または結晶粒間に非晶質半導体が介在するものを含む。微結晶半導体膜の形成方法としては、結晶核を形成して該結晶核を成長させる方法、非晶質半導体膜を形成して該非晶質半導体膜に接して絶縁膜と金属膜とを形成し、該金属膜に対してレーザを照射することで該金属膜に発生した熱により非晶質半導体を結晶化させる方法等を用いればよい。ただし、非晶質半導体膜に対して熱結晶化法又はレーザ結晶化法を用いて形成した結晶性半導体膜は含まないものとする。

【0194】

半導体膜306として、例えば、結晶性半導体膜上に非晶質半導体膜を積層して形成した積層膜を用いると、EL表示装置の画素回路が有するトランジスタを高速に動作させることができる。ここで、結晶性半導体膜としては、多結晶半導体(LTPS及びHTPSを含む)膜を適用しても良いし、微結晶半導体膜を適用しても良い。なお、結晶性半導体膜上に非晶質半導体膜を有することで、微結晶半導体膜の表面が酸化されることを防止することができる。また、耐圧を向上させ、オフ電流を低下させることができる。

【0195】

ただし、EL表示装置の画素回路が正常に動作する限りにおいて、半導体膜306の結晶性については特に限定されない。

【0196】

また、不純物半導体膜308にはリン等の一導電性を付与する不純物元素を含ませて薄膜トランジスタをn型にする。ただし、これに限定されず、薄膜トランジスタをp型にしてもよい。

【0197】

次に、第2の導電膜310上に第1のレジストマスク312を形成する(図46(A)及び図50を参照)。ここで、第1のレジストマスク312は、凹部及び凸部を有するレジストマスクであることが好ましい。このような凹部及び凸部を有するレジストマスクは、多階調マスクにより形成することができる。このとき、ソース電極及びドレイン電極層320が形成される領域には凸部が形成され、ソース電極及びドレイン電極層320を有さず半導体層324が露出して形成される領域には凹部が形成される。

【0198】

次に、第1のレジストマスク312を用いて第1のエッチングを行う。すなわち、第1の導電膜302、第1の絶縁膜304、半導体膜306、不純物半導体膜308及び第2の導電膜310をエッチングによりパターニングし、薄膜積層体314を形成する(図46(B)を参照)。

【0199】

次に、第1のレジストマスク312を用いて第2のエッチングを行う。すなわち、第1の導電膜302をエッチングによりパターニングし、ゲート電極層316を形成する(図46(C)及び図51を参照)。

【0200】

なお、ゲート電極層316は、薄膜トランジスタのゲート電極、ゲート配線、容量素子の一方の電極、及び支持部を構成している。ゲート電極層316Aと表記する場合には、ゲート配線356、第1のトランジスタ351のゲート電極、及び第3のトランジスタ353のゲート電極を構成する電極層を指す。ゲート電極層316Bと表記する場合には、第2のトランジスタ352のゲート電極、及び容量素子354の一方の電極を構成する電極層を指す。ゲート電極層316Cと表記する場合には、支持部を構成する電極層を指す。そして、これらを総括してゲート電極層316とよぶ。

【0201】

第2のエッチングは、第1の導電膜302により形成されるゲート電極層316の側面が、薄膜積層体314の側面より内側に形成されるエッチング条件により行う。換言すると、ゲート電極層316の側面が、薄膜積層体314の底面に接して形成されるようにエッチングを行う(A1−A2断面においてゲート電極層316の幅が半導体膜306等の幅より小さくなるようにエッチングを行う)。更には、第2の導電膜310に対するエッチングレートが小さく、且つ第1の導電膜302に対するエッチングレートが大きい条件により行う。換言すると、第2の導電膜310に対する第1の導電膜302のエッチング選択比が大きい条件により行う。このような条件により第2のエッチングを行うことで、ゲート電極層316を形成することができる。

【0202】

なお、ゲート電極層316の側面の形状は特に限定されない。例えば、テーパ形状であっても良い。ゲート電極層316の側面の形状は、第2のエッチングにおいて用いる薬液等の条件によって決められるものである。

【0203】

ここで、「第2の導電膜310に対するエッチングレートが小さく、且つ第1の導電膜302に対するエッチングレートが大きい条件」、又は「第2の導電膜310に対する第1の導電膜302のエッチング選択比が大きい条件」とは、以下の第1の要件及び第2の要件を満たすものをいう。

【0204】

第1の要件は、ゲート電極層316が必要な箇所に残存することである。ゲート電極層316の必要な箇所とは、図51乃至図55に点線で示される領域をいう。すなわち、第2のエッチング後に、ゲート電極層316がゲート配線、トランジスタが有するゲート電極、及び容量素子が有する一の電極を構成するように残存することが必要である。ゲート電極層がゲート配線及び容量配線を構成するためには、これらの配線が断線しないように第2のエッチングを行う必要がある。図46(C)及び図51に示されるように、薄膜積層体314の側面から間隔d1だけ内側にゲート電極層316の側面が形成されることが好ましく、間隔d1は実施者がレイアウトに従って適宜設定すればよい。

【0205】

第2の要件は、ゲート電極層316により構成されるゲート配線及び容量配線の最小幅d3、並びにソース電極及びドレイン電極層320により構成されるソース配線及び電源線の最小幅d2が適切なものとなることである(図55を参照)。第2のエッチングにより第2の導電膜310がエッチングされるとソース配線及び電源線の最小幅d2が小さくなり、ソース配線及び電源線の電流密度が過大となり、電気的特性が低下するためである。そのため、第2のエッチングは、第1の導電膜302のエッチングレートが過大にならず、且つ第2の導電膜310のエッチングレートが可能な限り小さい条件で行う。

【0206】

また、ソース配線及び電源線の最小幅d2は大きくすることが困難である。ソース配線及び電源線の最小幅d2はソース配線及び電源線と重畳する半導体層の最小幅d4により決まり、ソース配線及び電源線の最小幅d2を大きくするためには半導体層の最小幅d4を大きくせねばならず、隣接するゲート配線と容量配線とを絶縁させることが困難になるためである。半導体層の最小幅d4は、前記した間隔d1の概ね2倍よりも小さくする。換言すると、間隔d1は半導体層の最小幅d4の約半分よりも大きくする。

【0207】

なお、ソース配線及び電源線と重畳する半導体層の幅を最小幅d4とする部分は、ゲート電極層を素子毎に分離するために必要な箇所に適宜設ければよい。第2のエッチングにより、半導体層の幅を最小幅d4とした箇所と重畳する部分にはゲート電極層316が残存しないパターンを形成することができる。

【0208】

なお、ソース電極及びドレイン電極層により形成される、画素電極層と接続される部分の電極の幅はソース配線及び電源線の最小幅d2とすることが好ましい。

【0209】

第1のレジストマスク312が上記したように所定の形状であり、第2のエッチングが第1の導電膜302のサイドエッチングを伴うことによって、ゲート電極層316により構成される、隣接するゲート配線間のみならず、画素回路内の素子の接続を所望のものとするようにパターンの形成を行うことができるためである。第2のエッチングは、サイドエッチングを伴うエッチングであるため、エッチングは概略等方的に進行する条件により行う。

【0210】

なお、図51に示すゲート電極層316Cは、薄膜積層体314を支える支持部として機能する。支持部を有することで、ゲート電極層より上に形成されるゲート絶縁層等の膜剥がれを防止することができる。更には支持部を設けることで、第2のエッチングによりゲート電極層316に接して形成される、空洞の領域が必要以上に広くなることを防止できる。なお、支持部を設けることで、薄膜積層体314が自重によって破壊され、又は破損することをも防止することができ、歩留まりが向上するため好ましい。ただし、これに限定されず、支持部を設けなくとも良い。

【0211】

なお、第2のエッチングに用いることのできるエッチャントと第1の導電膜302と第2の導電膜310との組み合わせは実施の形態1にて説明したとおりである。

【0212】

なお、上面から見たゲート電極層316は角を有する(図51を参照)。これは、ゲート電極層316を形成する第2のエッチングが概略等方的に進行するために、ゲート電極層316の側面と薄膜積層体314の側面との間隔d1が概略等しくなるようにエッチングされるためである。

【0213】

次に、第1のレジストマスク312を後退させて、第2の導電膜310を露出させつつ、第2のレジストマスク318を形成する。第1のレジストマスク312を後退させて、第2のレジストマスク318を形成する手段としては、例えば酸素プラズマを用いたアッシングが挙げられる。しかし、第1のレジストマスク312を後退させて第2のレジストマスク318を形成する手段はこれに限定されるものではない。第2のレジストマスク318が形成される領域は、第1のレジストマスク312の凸部の領域と概略一致する。なお、ここでは第2のエッチングの後に第2のレジストマスク318を形成する場合について説明したが、これに限定されず、第2のレジストマスク318を形成した後に第2のエッチングを行ってもよい。

【0214】

なお、第1のレジストマスク312の形成に多階調マスクを用いない場合には、異なるフォトマスクを用いて第2のレジストマスク318を別途形成すればよい。

【0215】

次に、第2のレジストマスク318を用いて、第2の導電膜310をエッチングし、ソース電極及びドレイン電極層320を形成する(図47(D)及び図52を参照)。ここでエッチング条件は、第2の導電膜310以外の膜に対する食刻及び腐食が生じにくい条件を選択する。特に、ゲート電極層316の食刻及び腐食が生じにくい条件により行うことが重要である。

【0216】

なお、ソース電極及びドレイン電極層320は、薄膜トランジスタのソース電極、ドレイン電極、ソース配線、第1及び第2の電源線、容量素子の他方の電極、及び薄膜トランジスタと発光素子の一の電極とを接続する電極を構成している。ソース電極及びドレイン電極層320Aと表記する場合には、ソース配線358、及び第1のトランジスタ351のソース電極及びドレイン電極の一方を構成する電極層を指す。ソース電極及びドレイン電極層320Bと表記する場合には、第1の電源線357を構成する電極層を指す。ソース電極及びドレイン電極層320Cと表記する場合には、第1のトランジスタ351のソース電極及びドレイン電極の他方、及び第1のトランジスタ351と画素電極とを接続する電極を構成する電極層を指す。ソース電極及びドレイン電極層320Dと表記する場合には、第2の電源線359、及び第2のトランジスタ352のソース電極及びドレイン電極の一方を構成する電極層を指す。ソース電極及びドレイン電極層320Eと表記する場合には、第3のトランジスタ353のソース電極及びドレイン電極の一方を構成する電極層を指す。ソース電極及びドレイン電極層320Fと表記する場合には、容量素子354の他方の電極、第2のトランジスタ352のソース電極及びドレイン電極の他方、第3のトランジスタ353のソース電極及びドレイン電極の他方、並びにこれらから発光素子の一の電極に接続される電極を構成する電極層を指す。

【0217】

なお、第2のレジストマスク318Aは、ソース電極及びドレイン電極層320Aと重畳するものを指し、第2のレジストマスク318Bは、ソース電極及びドレイン電極層320Bと重畳するものを指し、第2のレジストマスク318Cは、ソース電極及びドレイン電極層320Cと重畳するものを指し、第2のレジストマスク318Dは、ソース電極及びドレイン電極層320Dと重畳するものを指し、第2のレジストマスク318Eは、ソース電極及びドレイン電極層320Eと重畳するものを指し、第2のレジストマスク318Fは、ソース電極及びドレイン電極層320Fと重畳するものを指す。そして、これらを総括して第2のレジストマスク318とよぶ。

【0218】

なお、第2の導電膜310のエッチングは、ウエットエッチング又はドライエッチングのどちらを用いても良い。

【0219】

続いて、薄膜積層体314における不純物半導体膜308及び半導体膜306の上部(バックチャネル部)をエッチングして、ソース領域及びドレイン領域322と半導体層324を形成する(図47(E)及び図53を参照)。ここでエッチング条件は、不純物半導体膜308及び半導体膜306以外の膜に対する食刻及び腐食が生じにくい条件を選択する。特に、ゲート電極層316の食刻及び腐食が生じにくい条件により行うことが重要である。

【0220】

なお、ソース領域及びドレイン領域322Aは、ソース電極及びドレイン電極層320Aと重畳するものを指し、以下同様である。そして、これらを総括してソース領域及びドレイン領域322とよぶ。

【0221】

なお、薄膜積層体314における不純物半導体膜308及び半導体膜306の上部(バックチャネル部)のエッチングはドライエッチング又はウエットエッチングにより行うことができる。

【0222】

その後、第2のレジストマスク318を除去し、薄膜トランジスタが完成する(図47(F)を参照)。

【0223】

なお、上記の図47(E)及び図47(F)を参照して説明した工程を一括して第3のエッチングとよぶ。第3のエッチングは、上記説明したように、複数の段階に分けて行っても良いし、一括して行っても良い。

【0224】

以上のようにして形成した薄膜トランジスタを覆って第2の絶縁膜を形成する。ここで、第2の絶縁膜は、第1の保護膜326のみで形成しても良いが、ここでは第1の保護膜326と第2の保護膜328により形成する(図48(G)を参照)。第1の保護膜326は、第1の絶縁膜304と同様に形成すればよいが、好ましくは水素を含有する窒化シリコン又は水素を含有する酸化窒化シリコンにより形成し、半導体層324に金属等の不純物が侵入して拡散し、汚染されることを防止する。

【0225】

第2の保護膜328は、表面が概略平坦になる方法により形成する。第2の保護膜328の表面を概略平坦にすることで、第2の保護膜328上に形成される第1の画素電極層332の形成不良等を防止することができるためである。従って、ここで「概略平坦」とは、上記目的を達成しうる程度のものであればよく、高い平坦性が要求されるわけではない。

【0226】

なお、第2の保護膜328は、例えば、感光性ポリイミド、アクリル又はエポキシ樹脂等により、スピンコーティング法等により形成することができる。ただし、これらの材料又は形成方法に限定されるものではない。

【0227】

なお、第2の保護膜328は、表面が概略平坦になる方法により形成した上記の保護膜と、これを覆って水分の侵入や放出を防止する保護膜を積層して形成したものであることが好ましい。水分の侵入や放出を防止する保護膜は、具体的には、窒化シリコン、酸化窒化シリコン、酸化窒化アルミニウム又は窒化アルミニウム等により形成されていることが好ましい。形成方法としてはスパッタリング法を用いることが好ましい。

【0228】

次に、第2の絶縁膜に第1の開口部330及び第2の開口部331を形成する(図48(H)を参照)。第1の開口部330は、少なくともソース電極及びドレイン電極層320の表面に達するように形成する。第2の開口部331は、少なくともゲート電極層316の表面に達するように形成する。第1の開口部330及び第2の開口部331の形成方法は、特定の方法に限定されず、第1の開口部330の径などに応じて実施者が適宜選択すればよい。例えば、フォトリソグラフィ法によりドライエッチングを行うことで第1の開口部330及び第2の開口部331を形成することができる。

【0229】

第1の開口部330は、ソース電極及びドレイン電極層320に達するように設けられるものであり、図54に示すように必要な箇所に複数個設ける。第1の開口部330Aはソース電極及びドレイン電極層320C上に設け、第1の開口部330Bはソース電極及びドレイン電極層320B上に設け、第1の開口部330Cはソース電極及びドレイン電極層320E上に設ける。

【0230】

第2の開口部331は、ゲート電極層316に達するように設けられるものであり、図54に示すように必要な箇所に複数個設ける。すなわち、第2の開口部331は第2の絶縁膜のみならず、第1の絶縁膜304、半導体層324の所望の箇所も除去して設けられるものである。第2の開口部331Aは、ソース配線358と第2の電源線359の間に設けられている。第2の開口部331Bは、第1の電源線357とソース配線358との間に設けられている。第2の開口部331C及び第2の開口部331Eは、容量素子354の一方の電極として機能するゲート電極層316Bを露出させるために設けられている。

第2の開口部331Dは、第2のトランジスタ352と容量素子354の間に設けられている。第2の開口部331Fは、第1のトランジスタ351と第3のトランジスタ353の間に設けられている。なお、必ずしもこれらのすべてを設けなくてもよい。

【0231】

なお、フォトリソグラフィ法によって開口部を形成することで、フォトマスクを1枚使用することになる。

【0232】

次に、第2の絶縁膜上に第1の画素電極層332を形成する(図49及び図55を参照)。第1の画素電極層332は、第1の開口部330又は第2の開口部331を介してソース電極及びドレイン電極層320又はゲート電極層316に接続されるように形成する。具体的には、第1の画素電極層332Aは、第1の開口部330Dを介してソース電極及びドレイン電極層320Fに接続される。第1の画素電極層332Bは、第1の開口部330Aを介してソース電極及びドレイン電極層320Cに接続され、第2の開口部331を介してゲート電極層316Bに接続されるように形成される。第1の画素電極層332Cは、第1の開口部330Bを介してソース電極及びドレイン電極層320Bに接続され、第1の開口部330Cを介してソース電極及びドレイン電極層320Eに接続される。第1の画素電極層332は単層で形成しても良いし、積層して形成してもよい。

【0233】

なお、フォトリソグラフィ法によって第1の画素電極層332を形成することで、フォトマスクを1枚使用することになる。

【0234】

第1の画素電極層332は、陰極となる材料により形成すればよい。陰極となる材料には、仕事関数が小さい材料、例えば、Ca、Al、MgAg、AlLi等が挙げられる。

【0235】

次に、第1の画素電極層332の側面(端部)及び第2の絶縁膜上に隔壁333を形成する(図48(I)及び図49を参照)。隔壁333は開口部を有し、該開口部において第1の画素電極層332が露出されるように形成する。隔壁333は、有機樹脂膜、無機絶縁膜又は有機ポリシロキサンを用いて形成する。具体的には、ポリイミド、ポリアミド、ポリイミドアミド、アクリル、ベンゾシクロブテンを用いて形成するとよい。特に感光性の材料を用いて、第1の画素電極層332上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0236】

次に、隔壁333の開口部において第1の画素電極層332と接するように、EL層334を形成する(図49を参照)。EL層334は、単数の層で構成されていても、複数の層が積層されて形成された積層膜により構成されていても良い。EL層334は、少なくとも発光層を有する。EL層334は電子注入層を介して第2の画素電極層335と接続されることが好ましい。

【0237】

そして、EL層334を覆うように、陽極となる材料により第2の画素電極層335を形成する(図48(I)及び図49を参照)。第2の画素電極層335は図45における共通電極360に相当する。第2の画素電極層335は、透光性を有する導電性材料により形成することができる。ここで、透光性を有する導電性材料としては、インジウム錫酸化物(以下、ITOという)、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、又は酸化珪素を添加したインジウム錫酸化物等が挙げられる。透光性を有する導電性材料の膜の形成はスパッタリング法又はCVD法等により行えばよいが、特定の方法に限定されるものではない。また、第2の画素電極層335についても単層で形成しても良いし、積層して形成してもよい。

【0238】

ここでは、第2の画素電極層335としてITOを用いる。隔壁333の開口部において、第1の画素電極層332とEL層334と第2の画素電極層335が重なり合うことで、発光素子336が形成される。発光素子336は、図45における発光素子355に相当する。この後、発光素子336に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の画素電極層335及び隔壁333上に第3の保護膜を形成することが好ましい(図示しない)。第3の保護膜は、第1の保護膜326と同様の材料により水分の侵入や放出を防止する機能を有するものを選択するとよい。窒化シリコン、酸化窒化シリコン、酸化窒化アルミニウム又は窒化アルミニウム等により形成されていることが好ましい。更に、第3の保護膜を覆って窒化シリコン膜又はDLC膜等を有することが好ましい。

【0239】

そして、外気に曝されないように、保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)又はカバー材によって、更なるパッケージング(封入)をすることが好ましい。保護フィルム及びカバー材は、ガス透過性が低く、脱ガスの少ない材料により設けることが好ましい。

【0240】

以上説明したように、EL表示装置の発光素子までを形成することができる(図49を参照。図49は、図55のB1−B2における発光素子まで形成した際の断面図に相当する)。

【0241】

なお、第1の画素電極層332を陽極となる材料により形成する場合には、第1の画素電極層332は、例えば、ITOにより形成することができる。第1の画素電極層332をこのような構造にすることで、発光を取り出す効率を向上させることができ、ボトムエミッション型のEL表示装置を作製することができる。そして、EL層334を覆うように、陰極となる材料により第2の画素電極層335を形成するとよい。第2の画素電極層335は図45における共通電極360に相当する。陰極となる材料には、仕事関数が小さい材料、例えば、Ca、Al、MgAg、AlLi等が挙げられる。なお、EL層334及び第2の画素電極層335は、マスクを介した蒸着により形成することが好ましい。従って、第2の画素電極層335は、蒸着により形成することが可能な材料により形成するとよい。なお、EL表示装置の画素を図45に示す回路により構成する場合には、第1の画素電極層332を陽極とし、第2の画素電極層335を陰極とすることが好ましい。

【0242】

本実施の形態のEL表示装置は、上面射出構造(トップエミッション)型EL表示装置、下面射出構造(ボトムエミッション)型EL表示装置、または両面射出構造(デュアルエミッション)型EL表示装置のいずれを選択してもよい。

【0243】

なお、上記で説明した保護膜等は上記した材料又は形成方法に限定されず、EL層の発光を妨げず、劣化等を防止することができる膜であればよい。

【0244】

また、上面射出構造において、画素回路が形成されている領域をも含むように第1の画素電極層332Aを形成してもよい。この場合には、まず、第1の画素電極層332B及び第1の画素電極層332Cに相当する導電層のみを形成し、該導電層上に第1の開口部330Dを有する絶縁膜を形成し、第1の開口部330Dを介してソース電極及びドレイン電極層320Fに接続されるように第1の画素電極層332Aを形成すればよい。画素回路が形成されている領域をも含むように第1の画素電極層332Aを形成することで、発光領域を拡大することができ、より高精細な表示が可能となる。

【0245】

なお、ここでは、発光素子として有機EL素子について述べたが、発光素子として無機EL素子を用いることも可能である。

【0246】

以上のように、EL表示装置を作製することができる。

【0247】

本実施の形態にて説明したように、ゲート電極の形成に新たなフォトマスクを用いることなく、表示装置の画素トランジスタを1枚のフォトマスクにより作製することができ、アクティブマトリクス基板を3枚のフォトマスクにより作製することができる。従って、薄膜トランジスタ及びEL表示装置の作製工程数を大幅に削減することができる。

【0248】

また、裏面露光、レジストリフロー及びリフトオフ法等の複雑な工程を経ることなく、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。そのため、複雑な工程を経ることなく、表示装置の作製工程数を大幅に削減することができる。従って、歩留まりの低下を抑制しつつ、薄膜トランジスタ及び表示装置の作製工程数を大幅に削減することができる。また、薄膜トランジスタの電気的特性の低下を抑制しつつ、製造コストを大幅に削減することができる。

【0249】

また、半導体層を遮光することができるため、光リーク電流が低減され、良好な電気的特性を有する薄膜トランジスタを作製し、表示特性が良好な表示装置を作製することができる。更には、不要な部分の半導体層が開口部を形成する工程と同一の工程により除去されているので、マスク枚数を増加させることなく光リーク電流が低減された、良好な電気的特性を有する薄膜トランジスタ及び良好な表示特性を有するEL表示装置を作製することができる。

【0250】

更には、ゲート電極層端部に生じるリーク電流が小さい薄膜トランジスタを作製することができるため、コントラスト比が高く、表示品質が良好なEL表示装置を得ることができる。

【0251】

なお、表示装置は、上記説明した画素構造に限定されず、様々なEL表示装置に適用することができる。

【0252】

なお、本実施の形態では、実施の形態1と同様に開口部を形成する形態について説明したが、これに限定されず実施の形態2と本実施の形態を組み合わせて実施してもよい。

【0253】

(実施の形態4)

本実施の形態は、実施の形態1乃至実施の形態3にて説明した方法により作製した表示パネル又は表示装置を表示部として組み込んだ電子機器について図56乃至図58を参照して説明する。このような電子機器としては、例えば、ビデオカメラ若しくはデジタルカメラ等のカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)が挙げられる。それらの一例を図56に示す。

【0254】

図56(A)はテレビジョン装置を示す。表示パネルを筐体に組み込むことで、図56(A)に示すテレビジョン装置を完成させることができる。実施の形態1乃至実施の形態3にて説明した作製方法を適用した表示パネルにより主画面403が形成され、その他付属設備としてスピーカ部409、操作スイッチ等が備えられている。

【0255】

図56(A)に示すように、筐体401に実施の形態1乃至実施の形態3にて説明した作製方法を適用した表示用パネル402が組み込まれ、受信機405により一般のテレビ放送の受信をはじめ、モデム404を介して有線又は無線による通信ネットワークに接続することにより片方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又はリモコン操作機406により行うことが可能であり、このリモコン操作機406にも、出力する情報を表示する表示部407が設けられていても良い。

【0256】

また、テレビジョン装置にも、主画面403の他にサブ画面408を第2の表示パネルで形成し、チャンネルや音量などを表示する構成が付加されていても良い。

【0257】

図57は、テレビジョン装置の主要な構成を示すブロック図を示している。表示パネル420には、画素部421が形成されている。信号線駆動回路422と走査線駆動回路423は、表示パネル420にCOG方式により実装されていても良い。

【0258】

その他の外部回路の構成として、映像信号の入力側では、チューナ424で受信した信号のうち、映像信号を増幅する映像信号増幅回路425と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路426と、その映像信号を適切な入力仕様に変換するためのコントロール回路427等を有している。コントロール回路427は、走査線駆動回路423と信号線駆動回路422にそれぞれ信号を出力する。デジタル駆動する場合には、信号線側に信号分割回路428を設け、入力デジタル信号を整数個に分割して供給する構成としても良い。

【0259】

チューナ424で受信した信号のうち、音声信号は、音声信号増幅回路429に送られ、その出力は音声信号処理回路430を経てスピーカ433に供給される。制御回路431は受信局(受信周波数)、音量の制御情報を入力部432から受け、チューナ424及び音声信号処理回路430に信号を送出する。

【0260】

勿論、本発明の一形態である表示装置はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港等における情報表示盤、又は街頭における広告表示盤等の大面積の表示媒体にも適用することができる。そのため、これらの表示媒体の生産性を向上させることができる。

【0261】

主画面403及びサブ画面408の一方又は双方に、実施の形態1乃至実施の形態3で説明した作製方法を適用した表示パネル又は表示装置を用いることで、テレビ装置の生産性を高めることができる。

【0262】

また、図56(B)に示す携帯型のコンピュータは、本体411及び表示部412等を有する。表示部412に、実施の形態1乃至実施の形態3で説明した表示装置の作製方法を適用した表示パネル又は表示装置を用いることで、コンピュータの生産性を高めることができる。

【0263】

図58は、携帯電話の一例を示し、図58(A)が正面図、図58(B)が背面図、図58(C)が2つの筐体をスライドさせたときの正面図である。図58に示す携帯電話は、筐体441及び筐体442二つの筐体で構成されている。図58に示す携帯電話は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能な所謂スマートフォンである。

【0264】

筐体441は、表示部443、スピーカ444、マイクロフォン445、操作キー446、ポインティングデバイス447、表面カメラ用レンズ448、外部接続端子ジャック449及びイヤホン端子450等を備え、筐体442は、キーボード451、外部メモリスロット452、裏面カメラ453、ライト454等により構成されている。また、アンテナは筐体441に内蔵されている。

【0265】

また、図58に示す携帯電話は、上記の構成に加えて、非接触型ICチップ、小型記録装置等を内蔵していてもよい。

【0266】

重なり合った筐体441と筐体442(図58(A)に示す。)は、スライドさせることが可能であり、スライドさせることで図58(C)のように展開する。表示部443には、実施の形態1乃至実施の形態3で説明した表示装置の作製方法を適用した表示パネル又は表示装置を組み込むことが可能である。また、表示部443と表面カメラ用レンズ448を同一の面に備えているため、テレビ電話としての使用が可能である。また、表示部443をファインダーとして用いることで、裏面カメラ453及びライト454で静止画及び動画の撮影が可能である。

【0267】

スピーカ444及びマイクロフォン445を用いることで、図58に示す携帯電話は、音声記録装置(録音装置)又は音声再生装置として使用することができる。また、操作キー446により、電話の発着信操作、電子メール等の簡単な情報入力操作、表示部に表示する画面のスクロール操作、表示部に表示する情報の選択等を行うカーソルの移動操作等が可能である。

【0268】

また、書類の作成、携帯情報端末としての使用等、取り扱う情報が多い場合は、キーボード451を用いると便利である。更に、重なり合った筐体441と筐体442(図58(A)を参照)をスライドさせることで、図58(C)のように展開させることができる。携帯情報端末として使用する場合には、キーボード451及びポインティングデバイス447を用いて、円滑な操作でマウスの操作が可能である。外部接続端子ジャック449はACアダプタ及びUSBケーブル等の各種ケーブルと接続可能であり、充電及びパーソナルコンピュータ等とのデータ通信が可能である。また、外部メモリスロット452に記録媒体を挿入することで、より大量のデータ保存及び移動が可能になる。

【0269】

筐体442の裏面(図58(B)を参照)には、裏面カメラ453及びライト454を備え、表示部443をファインダーとして静止画及び動画の撮影が可能である。

【0270】

また、上記の機能構成に加えて、赤外線通信機能、USBポート、テレビワンセグ受信機能、非接触ICチップ又はイヤホンジャック等を備えたものであってもよい。

【0271】

本実施の形態にて説明した各種電子機器は、実施の形態1乃至実施の形態3にて説明した薄膜トランジスタ及び表示装置の作製方法を適用して作製することができるため、これらの電子機器の生産性を向上させることができる。従って、これらの電子機器の作製コストを大幅に削減することができる。更には、表示部の表示品質の高い電子機器を作製することができる。

【符号の説明】

【0272】

100 基板

102 第1の導電膜

104 第1の絶縁膜

106 半導体膜

108 不純物半導体膜

110 第2の導電膜

112 第1のレジストマスク

114 薄膜積層体

116 ゲート電極層

116A ゲート電極層

116B ゲート電極層

118 第2のレジストマスク

120 ソース電極及びドレイン電極層

120A ソース電極及びドレイン電極層

120B ソース電極及びドレイン電極層

120C ソース電極及びドレイン電極層

120D ソース電極及びドレイン電極層

122 ソース領域及びドレイン領域

122A ソース領域及びドレイン領域

122B ソース領域及びドレイン領域

122C ソース領域及びドレイン領域

122D ソース領域及びドレイン領域

124 半導体層

126 第1の保護膜

128 第2の保護膜

130 第1の開口部

130A 第1の開口部

130B 第1の開口部

131 第2の開口部

131A 第2の開口部

131B 第2の開口部

131C 第2の開口部

132 画素電極層

140 グレートーンマスク

141 基板

142 遮光部

143 回折格子部

145 ハーフトーンマスク

146 基板

147 半透光部

148 遮光部

151 角

160A 第3の開口部

160B 第3の開口部

161 第4の開口部

170 第1のレジストマスク

171 第2のレジストマスク

200 基板

204 第1の絶縁膜

206 半導体膜

208 不純物半導体膜

216 ゲート電極層

216A ゲート電極層

216B ゲート電極層

220 ソース電極及びドレイン電極層

220A ソース電極及びドレイン電極層

220B ソース電極及びドレイン電極層

220C ソース電極及びドレイン電極層

220D ソース電極及びドレイン電極層

222 ソース領域及びドレイン領域

222A ソース領域及びドレイン領域

222B ソース領域及びドレイン領域

222C ソース領域及びドレイン領域

222D ソース領域及びドレイン領域

224 半導体層

226 第1の保護膜

228 第2の保護膜

229 残存する保護層

232 画素電極層

300 基板

302 第1の導電膜

304 第1の絶縁膜

306 半導体膜

308 不純物半導体膜

310 第2の導電膜

312 第1のレジストマスク

314 薄膜積層体

316 ゲート電極層

316A ゲート電極層

316B ゲート電極層

316C ゲート電極層

316D ゲート電極層

318 第2のレジストマスク

318A 第2のレジストマスク

318B 第2のレジストマスク

318C 第2のレジストマスク

318D 第2のレジストマスク

318E 第2のレジストマスク

318F 第2のレジストマスク

320 ソース電極及びドレイン電極層

320A ソース電極及びドレイン電極層

320B ソース電極及びドレイン電極層

320C ソース電極及びドレイン電極層

320D ソース電極及びドレイン電極層

320E ソース電極及びドレイン電極層

320F ソース電極及びドレイン電極層

322 ソース領域及びドレイン領域

322A ソース領域及びドレイン領域

322B ソース領域及びドレイン領域

322C ソース領域及びドレイン領域

322D ソース領域及びドレイン領域

324 半導体層

326 第1の保護膜

328 第2の保護膜

330 第1の開口部

330A 第1の開口部

330B 第1の開口部

330C 第1の開口部

330D 第1の開口部

331 第2の開口部

331A 第2の開口部

331B 第2の開口部

331C 第2の開口部

331D 第2の開口部

331E 第2の開口部

331F 第2の開口部

332 第1の画素電極層

332A 第1の画素電極層

332B 第1の画素電極層

332C 第1の画素電極層

333 隔壁

334 EL層

335 第2の画素電極層

336 発光素子

351 第1のトランジスタ

352 第2のトランジスタ

353 第3のトランジスタ

354 容量素子

355 発光素子

356 ゲート配線

357 第1の電源線

358 ソース配線

359 第2の電源線

360 共通電極

361 画素

401 筐体

402 表示用パネル

403 主画面

404 モデム

405 受信機

406 リモコン操作機

407 表示部

408 サブ画面

409 スピーカ部

411 本体

412 表示部

420 表示パネル

421 画素部

422 信号線駆動回路

423 走査線駆動回路

424 チューナ

425 映像信号増幅回路

426 映像信号処理回路

427 コントロール回路

428 信号分割回路

429 音声信号増幅回路

430 音声信号処理回路

431 制御回路

432 入力部

433 スピーカ

441 筐体

442 筐体

443 表示部

444 スピーカ

445 マイクロフォン

446 操作キー

447 ポインティングデバイス

448 表面カメラ用レンズ

449 外部接続端子ジャック

450 イヤホン端子

451 キーボード

452 外部メモリスロット

453 裏面カメラ

454 ライト

【技術分野】

【0001】

本発明は、表示装置の作製方法に関する。

【背景技術】

【0002】

近年、ガラス基板等の絶縁性表面を有する基板上に形成された、厚さ数nm〜数百nm程度の半導体薄膜により構成される薄膜トランジスタが注目されている。薄膜トランジスタは、IC(Integrated Circuit)及び電気光学装置を始めとした電子デバイスに広く応用されている。薄膜トランジスタは、特に液晶表示装置又はEL(Electro Luminescence)表示装置等に代表される、画像表示装置のスイッチング素子として開発が急がれている。アクティブマトリクス型液晶表示装置では、選択されたスイッチング素子に接続された画素電極と、該画素電極に対応する対向電極の間に電圧が印加されることにより、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。ここで、アクティブマトリクス型液晶表示装置とは、マトリクス状に配置された画素電極をスイッチング素子により駆動することによって、画面上に表示パターンが形成される方式を採用した液晶表示装置をいう。アクティブマトリクス型EL表示装置とは、マトリクス状に配置された画素をスイッチング素子により駆動することによって、画面上に表示パターンが形成される方式を採用したEL表示装置をいう。

【0003】

上記のようなアクティブマトリクス型表示装置の用途は拡大しており、画面サイズの大面積化、高精細化及び高開口率化の要求が高まっている。また、アクティブマトリクス型表示装置には高い信頼性が求められ、その生産方法には高い生産性及び生産コストの低減が求められる。生産性を高め、生産コストを低減する方法の一つに、工程の簡略化が挙げられる。

【0004】

アクティブマトリクス型表示装置では、スイッチング素子として主に薄膜トランジスタが用いられている。薄膜トランジスタの作製において、フォトリソグラフィに用いるフォトマスクの枚数を削減することは、工程の簡略化のために重要である。例えばフォトマスクが1枚増加すると、レジスト塗布、プリベーク、露光、現像、ポストベーク等の工程と、その前後の工程において、被膜の形成及びエッチング工程、更にはレジスト剥離、洗浄及び乾燥工程等が必要になる。そのため、作製工程に使用するフォトマスクが1枚増加するだけで、工程数が大幅に増加する。そのため、作製工程におけるフォトマスクを低減するために、数多くの技術開発がなされている。

【0005】

薄膜トランジスタは、チャネル形成領域がゲート電極より下層に設けられるトップゲート型と、チャネル形成領域がゲート電極より上層に設けられるボトムゲート型に大別される。ボトムゲート型薄膜トランジスタの作製工程において使用されるフォトマスクの枚数は、トップゲート型薄膜トランジスタの作製工程において使用されるフォトマスクの枚数よりも少ないことが知られている。ボトムゲート型薄膜トランジスタは、3枚のフォトマスクにより作製されることが一般的である。

【0006】

フォトマスクの枚数を低減させる従来の技術としては、裏面露光、レジストリフロー又はリフトオフ法といった複雑な技術を用いるものが多く、特殊な装置を必要とするものが多い。このような複雑な技術を用いることで、これに起因する様々な問題が生じ、歩留まりの低下の一因となっている。また、薄膜トランジスタの電気的特性を犠牲にせざるを得ないことも多い。

【0007】

薄膜トランジスタの作製工程における、フォトマスクの枚数を減らすための代表的な手段として、多階調マスク(ハーフトーンマスク又はグレートーンマスクと呼ばれるもの)を用いた技術が広く知られている。多階調マスクを用いて作製工程を低減する技術として、例えば特許文献1が挙げられる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−179069号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明の一態様は、光による影響が小さい薄膜トランジスタ及び表示装置を提供することを課題とする。また、本発明の一態様は、電気的特性が良好な薄膜トランジスタ及び表示特性が良好な表示装置を提供することを課題とする。

【0010】

または、本発明の一態様は、薄膜トランジスタの作製に用いるフォトマスクの枚数を従来よりも少なくし、作製工程を簡略化することを課題とする。本発明の一態様は、薄膜トランジスタを有する表示装置の作製工程を簡略化することを課題とする。

【課題を解決するための手段】

【0011】

本発明の一態様は、薄膜トランジスタを覆って保護膜を形成し、該保護膜に開口部を形成し、該保護膜上に画素電極層を選択的に形成することで前記薄膜トランジスタのソース電極及びドレイン電極層と画素電極層を接続させる表示装置の作製方法であって、前記開口部の形成に際して不要な半導体層等をエッチングして除去する表示装置の作製方法である。

【0012】

好ましい形態として、本発明の一態様は、第1の導電膜と、該第1の導電膜上に絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜をこの順に積層した薄膜積層体と、を形成し、第1のエッチングにより前記第1の導電膜を露出させつつ、少なくとも前記薄膜積層体のパターンを形成し、第2のエッチングにより第1の導電膜のパターンを形成する薄膜トランジスタの作製方法である。ここで、第2のエッチングは、第1の導電膜が選択的にサイドエッチングされる条件により行う。その後、第3のエッチングにより第2の導電膜を所望の形状とすることでソース電極及びドレイン電極層を形成し、薄膜トランジスタを作製する。その後、前記薄膜トランジスタを覆って保護膜を形成し、該保護膜に開口部を形成し、該保護膜上に画素電極層を選択的に形成することで前記薄膜トランジスタのソース電極及びドレイン電極層と画素電極層を接続させる。そして、前記開口部の形成に際して不要な半導体層等をエッチングして除去する。

【発明の効果】

【0013】

光電流による影響が小さく、表示特性が良好な表示装置を作製することができる。

【図面の簡単な説明】

【0014】

【図1】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図2】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図3】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図4】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図5】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図6】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図7】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図8】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図9】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図10】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図11】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図12】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図13】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図14】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図15】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図16】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図17】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図18】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図19】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図20】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図21】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図22】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図23】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図24】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図25】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図26】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図27】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図28】多階調マスクを説明する図。

【図29】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図30】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図31】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図32】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図33】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図34】アクティブマトリクス基板の接続部を説明する図。

【図35】アクティブマトリクス基板の接続部を説明する図。

【図36】アクティブマトリクス基板の接続部を説明する図。

【図37】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図38】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図39】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図40】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図41】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図42】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図43】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図44】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図45】EL表示装置の画素回路の一例を説明する図。

【図46】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図47】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図48】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図49】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図50】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図51】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図52】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図53】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図54】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図55】薄膜トランジスタ及び表示装置の作製方法の一例を説明する図。

【図56】電子機器を説明する図。

【図57】電子機器を説明する図。

【図58】電子機器を説明する図。

【発明を実施するための形態】

【0015】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。また、第1の絶縁膜及び第2の絶縁膜は、原則として上面図には表さないものとする。

【0016】

(実施の形態1)

本実施の形態では、薄膜トランジスタの作製方法及び該薄膜トランジスタがマトリクス状に配置された表示装置の作製方法の一例について、図1乃至図36を参照して説明する。

【0017】

なお、図16乃至図23には本実施の形態に係る薄膜トランジスタの上面図を示し、図23は画素電極まで形成した完成図である。図1乃至図3は、図16乃至図23に示すA1−A2における断面図である。図4乃至図6は、図16乃至図23に示すB1−B2における断面図である。図7乃至図9は、図16乃至図23に示すC1−C2における断面図である。図10乃至図12は、図16乃至図23に示すD1−D2における断面図である。図13乃至図15は、図16乃至図23に示すE1−E2における断面図である。

【0018】

本実施の形態にて説明する本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2の導電膜上に第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0019】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第2の導電膜上に第2のレジストマスクを形成し、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0020】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第1のレジストマスクを後退させることで前記第1のレジストマスクの凹部と重畳する前記第2の導電膜を露出させつつ第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0021】

または、本発明の一態様は、第1の導電膜、第1の絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマスクを形成し、前記第1のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜、前記半導体膜及び前記第1の絶縁膜に第1のエッチングを行い、前記第1のレジストマスクを後退させることで前記第1のレジストマスクの凹部と重畳する前記第2の導電膜を露出させつつ第2のレジストマスクを形成し、前記第1の導電膜の一部にサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、前記第2のレジストマスクを用いて、前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成することで複数の薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記複数の薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に画素電極を選択的に形成し、前記開口部の形成に際して前記複数の薄膜トランジスタ間に存在する半導体層を除去することを特徴とする表示装置の作製方法である。

【0022】

上記構成の表示装置の作製方法において、前記第1のレジストマスクは多階調マスクを用いて形成することが好ましい。多階調マスクを用いることで、簡略な工程で凹部を有するレジストマスクを形成することができる。

【0023】

上記構成の表示装置の作製方法を適用することで、前記第1のエッチングによって素子領域が形成され、前記第2のエッチングによって前記素子領域の側面から概ね等しい距離だけ内側にゲート電極層の側面を形成することができる。

【0024】

上記構成の表示装置の作製方法において、前記第1のエッチングはドライエッチングであり、前記第2のエッチングはウエットエッチングであることが好ましい。

【0025】

上記構成の表示装置の作製方法において、前記第2の絶縁膜は、CVD法又はスパッタリング法により形成した絶縁膜と、スピンコート法により形成した絶縁膜と、を積層して形成することが好ましい。特に好ましくは窒化シリコン膜をCVD法又はスパッタリング法により形成し、有機樹脂膜をスピンコート法により形成する。第2の絶縁膜をこのように形成することで、薄膜トランジスタの電気的特性に影響を及ぼしうる不純物元素等から薄膜トランジスタを保護し、且つ画素電極の被形成面の平坦性を向上させて歩留まりの低下を防止することができる。

【0026】

上記構成の表示装置の作製方法において、前記複数の薄膜トランジスタ間に存在する半導体層を除去するに際して、前記ゲート電極層と重畳していない領域に存在する前記半導体層を除去することが好ましい。ゲート電極層と重畳していない領域に存在する半導体層は光リーク電流の一因となる。そのため、ゲート電極層と重畳していない領域に存在する半導体層を除去することで光リーク電流を低減することができる。

【0027】

以下に、本実施の形態について詳細に説明する。

【0028】

まず、基板100上に、第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110を形成する。これらの膜は、単層で形成してもよいし、複数の膜を積層した積層膜であってもよい。

【0029】

基板100は、絶縁性基板である。表示装置に適用する場合には、基板100としては、ガラス基板又は石英基板を用いることができる。本実施の形態においては、ガラス基板を用いる。

【0030】

基板100としてガラス基板を用いる場合には、基板100上に下地絶縁膜(好ましくは、窒化シリコン膜又は窒化酸化シリコン膜)を設けることが好ましい。下地絶縁膜を設けることで、ガラス基板100中の不純物金属元素が半導体層に侵入することを防ぐことができる。これは、下地絶縁膜が窒素を含む場合に顕著である。更には、下地絶縁膜はハロゲン(フッ素、塩素又は臭素)を含むことが好ましい。ガラス基板100中の不純物金属元素が半導体層に侵入することをより効果的に防ぐことができるためである。絶縁膜にハロゲンを含ませるには、形成に用いるガスに、ハロゲンガス又はハロゲン化合物からなるガスを含ませればよく、CVD法又はスパッタリング法により単層で又は積層して形成することができる。

【0031】

第1の導電膜102は、導電性材料により形成する。第1の導電膜102は、例えばチタン、モリブデン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、ニオブ若しくはスカンジウム等の金属材料又はこれらを主成分とする合金材料等の導電性材料を用いて形成することができる。ただし、後の工程(第1の絶縁膜104の形成等)に耐えうる程度の耐熱性は必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。更には、第2のエッチングによりエッチング可能な材料を用いる。この限りにおいて、第1の導電膜102は特定の材料に限定されない。第1の導電膜102の形成は、例えばスパッタリング法又はCVD法(熱CVD法又はプラズマCVD法等を含む)等により行えばよいが、特定の方法に限定されない。

【0032】

なお、ここで、膜が「耐熱性を有する」とは、後の工程における温度によって当該膜が膜としての形態を保ち、且つ当該膜に求められる機能及び特性を保つことができることをいう。

【0033】

第1の絶縁膜104は、ゲート絶縁層として機能し、絶縁性材料により形成する。第1の絶縁膜104は、例えば、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜又は窒化酸化シリコン膜等を用いて形成することができる。ただし、第1の導電膜102と同様に後の工程(半導体膜106の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。この限りにおいて、第1の絶縁膜104は特定の材料に限定されない。第1の絶縁膜104の形成は、例えばCVD法(熱CVD法又はプラズマCVD法等を含む)又はスパッタリング法等により行えばよいが、特定の方法に限定されない。

【0034】

半導体膜106は、半導体材料により形成する。半導体膜106は、例えば、シランガスにより形成される非晶質シリコン等を用いて形成することができる。ただし、第1の導電膜102等と同様に、後の工程(第2の導電膜110等の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食にくい材料を選択することを要する。この限りにおいて、半導体膜106は特定の材料に限定されるものではない。従って、ゲルマニウム等を用いても良い。なお、半導体膜106の結晶性についても特に限定されない。半導体膜106の形成は、例えばCVD法(熱CVD法又はプラズマCVD法等を含む)又はスパッタリング法等により行えばよいが、特定の方法に限定されない。

【0035】

不純物半導体膜108は、一導電性を付与する不純物元素を含む半導体膜であり、一導電性を付与する不純物元素が添加された半導体材料形成のためのガス等により形成される。例えば、フォスフィン(化学式:PH3)又はジボラン(化学式:B2H6)を含むシランガスにより形成される、リン又はボロンを含むシリコン膜である。ただし、第1の導電膜102等と同様に、後の工程(第2の導電膜110等の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。この限りにおいて、不純物半導体膜108は、特定の材料に限定されない。n型の薄膜トランジスタを作製する場合には、添加する一導電性を付与する不純物元素として、リン又はヒ素等を用いればよい。すなわち、形成に用いるシランガスにはフォスフィン又はアルシン(化学式:AsH3)等を所望の濃度で含ませればよい。または、p型の薄膜トランジスタを作製する場合には、一導電性を付与する不純物元素として、ボロン等を添加すればよい。すなわち、形成に用いるシランガスにはジボラン等を所望の濃度で含ませればよい。なお、不純物半導体膜108の形成は、例えばCVD法(熱CVD法又はプラズマCVD法等を含む)等により行うことができるが、特定の方法に限定されるものではない。なお、不純物半導体膜108の結晶性についても特に限定されない。また、半導体膜106により形成される半導体層の一部に、ドーピング等によりソース電極及びドレイン電極層とオーミック接触可能な領域を設ける場合などには、不純物半導体膜108を設けなくてもよい。

【0036】

第2の導電膜110は、導電性材料(第1の導電膜102として列挙した材料等)であって、第1の導電膜102とは異なる材料により形成する。ここで、「異なる材料」とは、主成分が異なる材料をいう。具体的には、後に説明する第2のエッチングによりエッチングされにくい材料を選択すればよい。また、第1の導電膜102等と同様に、後の工程(第1の保護膜126等の形成等)に耐えうる程度の耐熱性が必要であり、後の工程で食刻又は腐食されにくい材料を選択することを要する。従って、この限りにおいて、第2の導電膜110は特定の材料に限定されない。第2の導電膜110の形成は、例えばスパッタリング法又はCVD法(熱CVD法又はプラズマCVD法等を含む)等により行えばよいが、特定の方法に限定されるものではない。

【0037】

なお、上記説明した第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110に対して求められる耐熱性は、第1の導電膜102が最も高く、以下前記した順に続き、第2の導電膜110が最も低い。例えば、半導体膜106が水素を含む非晶質半導体膜である場合には、約300℃以上とすることで半導体膜中の水素が脱離し、電気的特性が変化する。そのため、例えば半導体膜106を形成した後の工程では概ね300℃を超えない温度とすることが好ましい。

【0038】

次に、第2の導電膜110上に第1のレジストマスク112を形成する(図1(A)、図4(A)、図7(A)、図10(A)、図13(A)、図16を参照)。

【0039】

次に、第1のレジストマスク112を用いて第1のエッチングを行う。すなわち、第1の導電膜102、第1の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110をエッチングによりパターニングし、薄膜積層体114を形成する(図1(B)、図4(B)、図7(B)、図10(B)、図13(B)、図17を参照)。本明細書において、このエッチング工程を第1のエッチングとよぶ。第1のエッチングは、ドライエッチング又はウエットエッチングを用いればよいが、異方性の高いエッチング法(物理的エッチング)により行うことが好ましい。第1のエッチングに異方性の高いエッチング法を用いることで、パターンの加工精度を向上させることができる。なお、第1のエッチングをドライエッチングにより行う場合には一の工程にて行うことが可能であるが、第1のエッチングをウエットエッチングにより行う場合には、複数の工程により第1のエッチングを行うと良い。ウエットエッチングでは、被エッチング膜の種類によってエッチングレートが異なるため、すべての膜を一の工程にてエッチングすることが困難だからである。従って、第1のエッチングには、ドライエッチングを用いることが好ましい。

【0040】

ここで、例えば第1の導電膜102としてモリブデン膜を形成し、第1の絶縁膜104として窒化シリコン膜を形成し、半導体膜106として非晶質シリコン膜を形成し、不純物半導体膜108としてリンを含む非晶質シリコン膜を形成し、第2の導電膜110としてタングステン膜を形成した場合、第1のエッチングは、3段階のドライエッチングにより行えばよい。まず、Cl2ガスとCF4ガスとO2ガスの混合ガスを用いてエッチングを行うことで第2の導電膜110をエッチングする。次に、Cl2ガスを用いてエッチングを行うことで半導体膜106及び不純物半導体膜108をエッチングする。最後に、CHF3ガスを用いてエッチングを行うことで第1の絶縁膜104をエッチングすればよい。また、この後更にCl2ガスとCF4ガスとO2ガスの混合ガスを用いてエッチング行うことで4段階のドライエッチングとしてもよい。

【0041】

次に、第1の導電膜102をサイドエッチングによりパターニングし、ゲート電極層116を形成する(図1(C)、図4(C)、図7(C)、図10(C)、図13(C)、図18を参照)。このエッチング工程を第2のエッチングとよぶ。

【0042】

なお、ゲート電極層116は、薄膜トランジスタのゲート電極、ゲート配線、容量素子の一方の電極及び容量配線を構成している。ゲート電極層116Aと表記する場合には、ゲート配線と薄膜トランジスタのゲート電極を構成するゲート電極層を指す。ゲート電極層116Bと表記する場合には、容量配線と容量素子の一方の電極を構成するゲート電極層を指す。そして、これらを総括してゲート電極層116とよぶ。

【0043】

なお、「ゲート配線」とは、薄膜トランジスタのゲート電極に接続される配線をいう。ゲート配線は、ゲート電極層により形成される。また、ゲート配線は走査線と呼ばれることがある。

【0044】

第2のエッチングは、第1の導電膜102により形成されるゲート電極層116の側面が、薄膜積層体114の側面より内側に形成されるエッチング条件により行う。(図18乃至図21におけるA1−A2断面において、ゲート電極層116の幅が半導体膜106等の幅より小さくなるようにエッチングを行う)。更には、第2の導電膜110に対するエッチングレートが小さく、且つ第1の導電膜102に対するエッチングレートが大きい条件により行う。換言すると、第2の導電膜110に対する第1の導電膜102のエッチング選択比が大きい条件により行う。このような条件により第2のエッチングを行うことで、ゲート電極層116を形成することができる。

【0045】

なお、ゲート電極層116の側面の形状は特に限定されない。例えば、テーパ形状であっても良い。ゲート電極層116の側面の形状は、第2のエッチングにおいて用いる薬液等の条件によって決められるものである。

【0046】

ここで、「第2の導電膜110に対するエッチングレートが小さく、且つ第1の導電膜102に対するエッチングレートが大きい条件」、又は「第2の導電膜110に対する第1の導電膜102のエッチング選択比が大きい条件」とは、以下の第1の要件及び第2の要件を満たすものをいう。

【0047】

第1の要件は、ゲート電極層116が必要な箇所に残存することである。ゲート電極層116の必要な箇所とは、図18におけるレジストマスク内に点線で示される領域をいう。すなわち、第2のエッチング後に、ゲート電極層116がゲート電極、ゲート配線、容量素子の一方の電極及び容量配線を構成するように残存することが必要である。ゲート電極層がゲート配線及び容量配線を構成するためには、これらの配線が断線しないように第2のエッチングを行う必要がある。図1(C)及び図13(C)に示されるように、薄膜積層体114の側面から間隔d1だけ内側にゲート電極層116の側面が形成されることが好ましく、間隔d1は実施者がレイアウトに従って適宜設定すればよい。

【0048】

第2の要件は、ゲート電極層116により構成されるゲート配線及び容量配線の最小幅d3、並びにソース電極及びドレイン電極層120Aにより構成されるソース配線の最小幅d2が適切なものとなることである(図21を参照)。第2のエッチングにより第2の導電膜110がエッチングされるとソース配線の最小幅d2が小さくなり、ソース配線の電流密度が過大となり、電気的特性が低下するためである。そのため、第2のエッチングは、第1の導電膜102のエッチングレートが過大にならず、且つ第2の導電膜110のエッチングレートが可能な限り小さい条件で行う。

【0049】

また、ソース配線の最小幅d2は大きくすることが困難である。ソース配線の最小幅d2はソース配線と重畳する半導体層の最小幅d4により決まり、ソース配線の最小幅d2を大きくするためには半導体層の最小幅d4を大きくせねばならず、隣接するゲート配線と容量配線とを絶縁させることが困難になるためである。従って、半導体層の最小幅d4は、前記した間隔d1の概ね2倍よりも小さくする。換言すると、間隔d1は半導体層の最小幅d4の約半分よりも大きくする。

【0050】

なお、ソース配線と重畳する半導体層の幅を最小幅d4とする部分は、ゲート配線と、該ゲート配線と互いに隣接する容量配線との間に少なくとも一箇所あればよい。好ましくは、図21に示すように、ゲート配線に隣接する領域及び容量配線に隣接する領域の半導体層の幅を最小幅d4とすればよい。

【0051】

なお、ソース電極及びドレイン電極層により形成される、画素電極層と接続される部分の電極の幅はソース配線の最小幅d2とすることが好ましい。

【0052】

第1のレジストマスク112が上記したように所定の形状であり、第2のエッチングが第1の導電膜102のサイドエッチングを伴うことによって、ゲート電極層116により構成される、隣接するゲート配線と容量配線とを絶縁させることができるためである(図18を参照)。ここで、第2のエッチングは、サイドエッチングを伴うエッチングであるため、エッチングは概略等方的に進行する条件により行う。

【0053】

ここで、サイドエッチングとは、被エッチング膜の厚さ方向(基板面に垂直な方向又は下地絶縁膜の面に垂直な方向)のみならず、厚さ方向に対して垂直な方向(基板面に平行な方向又は下地絶縁膜の面に平行な方向)にも被エッチング膜が削られるエッチングをいう。サイドエッチングされた被エッチング膜の端部は、被エッチング膜に対するエッチングガス又はエッチングに用いる薬液のエッチングレートによって様々な形状となるように形成されるが、端部が曲面となるように形成されることが多い。

【0054】

なお、図示していないが、ゲート電極層116と接する空洞部分にゲート電極層116と同一の層により形成される支持部を有していてもよい。支持部を設けることで、薄膜積層体114が自重によって破壊され、又は破損することをも防止でき、歩留まりが向上するため好ましい。

【0055】

次に、第2のエッチングに用いることのできるエッチャント又はエッチングガスと、第1の導電膜102及び第2の導電膜110の組み合わせについて説明する。

【0056】

第2のエッチングをウエットエッチングによって行う場合、例えば、第1の導電膜102はアルミニウムを主成分とする材料若しくはチタンを主成分とする材料又はこれらを積層させて形成し、第2の導電膜110は銅を主成分とする材料により形成し、エッチャントとしては、希硫酸、濃リン酸、濃塩酸、希リン酸又はシュウ酸を用いる。なお、エッチャントとして、希硫酸、希リン酸又はシュウ酸を用いる場合には室温よりも高温(50℃〜100℃、好ましくは60〜75℃)にするとよい。なお、第2の導電膜110は、好ましくはカルシウム及び酸素を含んだ銅を主成分とする材料と、カルシウムを含んだ銅を主成分とする材料と、マグネシウムを含んだ銅を主成分とする材料と、を積層して形成する。または、カルシウム及び酸素を含んだ銅を主成分とする材料と、マグネシウム及び酸素を含んだ銅を主成分とする材料と、マグネシウムを含んだ銅を主成分とする材料と、を積層して形成することが好ましい。またはこれらを混合して用いてもよい。

【0057】

または、例えば、第1の導電膜102はアルミニウムを主成分とする材料若しくはチタンを主成分とする材料又はこれらを積層させて形成し、第2の導電膜110はモリブデンを主成分とする材料により形成してもよく、この場合にはエッチャントとして、フッ酸、希塩酸、濃塩酸、希硫酸、濃硫酸、希リン酸、濃リン酸又はシュウ酸を用いる。なお、エッチャントとして、希塩酸、希硫酸、希リン酸又はシュウ酸を用いる場合には、室温よりも高温(50℃〜100℃、好ましくは60〜75℃)にして用いるとよい。ただし、濃硫酸を用いる場合には、高温では第2の導電膜110の主成分であるモリブデンがエッチングされてしまうため、室温程度で用いる。またはこれらを混合して用いてもよい。

【0058】

ただし、上記列挙したエッチャントのうち、少なくとも、濃硫酸、希リン酸及び濃リン酸は、レジストマスクに対して脱水作用を起こすため、これらのエッチャントを用いる場合にはレジストマスクを除去した状態で用いる。

【0059】

または、好ましい形態として、第1の導電膜102をアルミニウム又はモリブデンにより形成し、第2の導電膜110をチタン又はタングステンにより形成し、エッチャントには、硝酸、酢酸及びリン酸を含む薬液を用いる。または、第1の導電膜102をモリブデンにより形成し、第2の導電膜110をチタン、アルミニウム又はタングステンにより形成し、エッチャントには、過酸化水素水を含む薬液を用いればよい。

【0060】

または、最も好ましい形態として、第1の導電膜102をアルミニウム層上にモリブデン層が積層された積層膜とし、第2の導電膜110をタングステン層とし、エッチャントには、硝酸を2%、酢酸を10%、リン酸を72%含む薬液を用いる。

【0061】

なお、上記した第1の導電膜102を構成する材料として列挙したアルミニウムを主成分とする材料として、好ましくは、ネオジムを添加したアルミニウムを用いる。第1の導電膜102にネオジムを添加したアルミニウムを用いることで、アルミニウムの高抵抗化を抑制しつつ、ヒロックの発生を防止することができる。

【0062】

また、上記した第2の導電膜110を構成する材料として列挙したモリブデンを主成分とする材料として、ニオブを添加したモリブデンを用いてもよい。

【0063】

または、第2のエッチングはドライエッチングによって行ってもよい。例えば、第1の導電膜102はタングステンを主成分とする材料により形成し、第2の導電膜110は、アルミニウムを主成分とする材料若しくはチタンを主成分とする材料又はこれらを積層させて形成し、エッチングガスとして三フッ化塩素(化学式:ClF3)ガスを用いることで第2のエッチングを行うことができる。ただし、半導体膜106にシリコンを用いる場合には三フッ化塩素ガスを用いるとエッチングされてしまうため、第2のエッチングの前に酸化処理を行うとよい。酸化処理は、薄膜積層体114の表面を酸化することができる方法を用いて行えばよく、特定の方法に限定されない。この酸化処理は、酸素プラズマ若しくは水プラズマによるプラズマ処理、オゾン水による処理、または熱処理により行うことができる。

【0064】

なお、図18に示すように、上面から見たゲート電極層116は角(例えば、角151)を有する。これは、ゲート電極層116を形成する第2のエッチングが概略等方的であるために、ゲート電極層116の側面と薄膜積層体114の側面との間隔d1が概略等しくなるようにエッチングされるためである。

【0065】

次に、第2のレジストマスク118を形成する(図2(D)、図5(D)、図8(D)、図11(D)、図14(D)、図19を参照)。なお、ここでは第2のエッチングの後に第2のレジストマスク118を形成するが、これに限定されず、第2のレジストマスク118を形成した後に第2のエッチングを行ってもよい。

【0066】

次に、第2のレジストマスク118を用いて、第2の導電膜110をエッチングし、ソース電極及びドレイン電極層120を形成する。ここでエッチング条件は、第2の導電膜110以外の膜に対する食刻及び腐食が生じにくい条件を選択する。特に、ゲート電極層116の食刻及び腐食が生じにくい条件により行うことが重要である。

【0067】

なお、ソース電極及びドレイン電極層120は、薄膜トランジスタのソース電極、ドレイン電極、ソース配線、薄膜トランジスタと画素電極とを接続する電極、及び容量素子の他方の電極を構成している。「ソース電極及びドレイン電極層120A」又は「ソース電極及びドレイン電極層120C」と表記する場合には、薄膜トランジスタのソース電極及びドレイン電極の一方、及びソース配線を構成する電極層を指す。「ソース電極及びドレイン電極層120B」と表記する場合には、薄膜トランジスタのソース電極及びドレイン電極の他方、及び薄膜トランジスタと画素電極とを接続する電極を構成する電極層を指す。「ソース電極及びドレイン電極層120D」と表記する場合には、容量素子の他方の電極を構成する電極層を指す。そして、これらを総括してソース電極及びドレイン電極層120とよぶ。

【0068】