表示装置の駆動回路、表示装置、および表示装置の駆動方法

【課題】画質を高めることができる表示装置の駆動回路を得る。

【解決手段】交互に設定された第1の期間(反転動作期間PA)および第2の期間(反転動作期間PB)のそれぞれにおいて、フレーム期間ごとに反転する画素信号Vpix2を生成し、表示部に供給する画素信号生成部(RGBデコーダ部13および反転部14)と、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御する書込制御部(反転制御部30)とを備える。

【解決手段】交互に設定された第1の期間(反転動作期間PA)および第2の期間(反転動作期間PB)のそれぞれにおいて、フレーム期間ごとに反転する画素信号Vpix2を生成し、表示部に供給する画素信号生成部(RGBデコーダ部13および反転部14)と、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御する書込制御部(反転制御部30)とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、インターレース映像信号に基づいて表示を行う表示装置を駆動する駆動回路、およびその駆動回路を備えた表示装置、ならびにそのような表示装置の駆動方法に関する。

【背景技術】

【0002】

近年、表示装置においては、CRT(Cathode Ray Tube)表示装置から液晶表示装置への置き換えが進んでいる。液晶表示装置は、CRT表示装置に比べて、薄くできるため省スペースを実現しやすく、また、消費電力が低いためエコロジーの観点からもメリットがある。

【0003】

表示装置の分野では、しばしばインターレース映像信号が用いられる。インターレース映像信号では、各フレーム画像の画像情報は、そのフレーム画像を構成するライン画像を交互に分配して構成した2つのフィールド画像の画像情報に分けられている。CRT表示装置にこのインターレース映像信号が供給された場合には、CRT表示装置は、例えば、これらの2つのフィールド画像を、それぞれ対応する位置に交互に表示する。一方、液晶表示装置にインターレース映像信号が供給された場合には、液晶表示装置は、例えば、いわゆるIP変換によりインターレース映像信号をプログレッシブ映像信号に変換して元のフレーム画像を生成し、その生成されたフレーム画像に基づいて表示を行う。また、液晶表示装置には、インターレース映像信号の各フィールド画像と同じ画素数を有する表示部を備え、IP変換を行わずに各フィールド画像をそのまま時分割的に表示するものもある。このIP変換を行わない表示装置は、IP変換を行う表示装置に比べ、よりシンプルな構成で、インターレース映像信号に基づく表示を行うことができる。

【0004】

ところで、一般に、表示装置では、例えば同じ画像を長時間表示すると、その後に他の画像を表示しても、その長時間表示した画像が少し残って表示されてしまう、いわゆる「焼きつき」と呼ばれる現象が生じる。液晶表示装置においても、このような現象は生じるため、これに対する様々な対策が提案されている。例えば、特許文献1には、IP変換を行わない液晶表示装置において、フレームごとに画素信号を反転して駆動するとともに、所定期間ごとにその反転の方法を変更する液晶表示装置が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平8−191421号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、一般に、表示装置では高い画質が望まれており、IP変換を行わない液晶表示装置でもさらなる画質の改善が望まれている。

【0007】

本開示はかかる問題点に鑑みてなされたもので、その目的は、画質を高めることができる表示装置の駆動回路、表示装置、および表示装置の駆動方法を提供することにある。

【課題を解決するための手段】

【0008】

本開示の表示装置の駆動回路は、画素信号生成部と、書込制御部とを備えている。画素信号生成部は、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成し、表示部に供給するものである。書込制御部は、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御するものである。

【0009】

本開示の表示装置は、画素信号生成部と、表示部と、書込制御部とを備えている。画素信号生成部は、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成するものである。表示部は、画素信号に基づいて表示を行うものである。書込制御部は、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御するものである。

【0010】

本開示の表示装置の駆動方法は、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成して表示部に供給し、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御するものである。

【0011】

本開示の表示装置の駆動回路、表示装置、および表示装置の駆動方法では、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号が、表示部に供給される。その際、第1の期間および第2の期間のそれぞれにおける先頭期間以外の期間において、画素信号が表示部に書き込まれるようになっている。

【発明の効果】

【0012】

本開示の表示装置の駆動回路、表示装置、および表示装置の駆動方法によれば、先頭期間以外の期間において、画素信号が表示部に書き込まれるようにしたので、画質を高めることができる。

【図面の簡単な説明】

【0013】

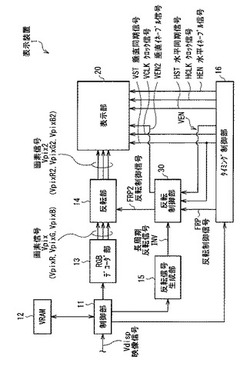

【図1】本開示の第1の実施の形態に係る表示装置の一構成例を表すブロック図である。

【図2】インターレース画像を説明するための説明図である。

【図3】図1に示した反転制御部の一構成例を表す回路図である。

【図4】第1フィールド画像および第2フィールド画像に基づく表示を説明するための説明図である。

【図5】図1に示した表示部の一構成例を表す説明図である。

【図6】図1に示した表示装置の一動作例を表すタイミング波形図である。

【図7】図1に示した表示装置の一動作例を表す他のタイミング波形図である。

【図8】図1に示した反転信号生成部および反転信号制御部の一動作例を表すタイミング波形図である。

【図9】インターレース画像の一例を説明するための説明図である。

【図10】図10に示した画像の表示を説明するための説明図である。

【図11】図1に示した表示装置の一動作例を表す他のタイミング波形図である。

【図12】比較例に係る表示装置の一構成例を表すブロック図である。

【図13】比較例に係る表示装置の一動作例を表すタイミング波形図である。

【図14】第1の実施の形態の変形例に係る表示装置の一構成例を表すブロック図である。

【図15】図14に示した反転制御部の一構成例を表す回路図である。

【図16】第1の実施の形態の他の変形例に係る反転制御部の一構成例を表す回路図である。

【図17】第2の実施の形態に係る表示装置の一構成例を表すブロック図である。

【図18】図17に示した表示装置の一動作例を表す流れ図である。

【図19】第3の実施の形態に係る表示装置の一構成例を表すブロック図である。

【図20】図19に示した表示装置の一動作例を表す流れ図である。

【図21】第3の実施の形態の変形例に係る表示装置の一動作例を表す流れ図である。

【発明を実施するための形態】

【0014】

以下、本開示の実施の形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.第1の実施の形態

2.第2の実施の形態

3.第3の実施の形態

【0015】

<1.第1の実施の形態>

[構成例]

(全体構成例)

図1は、第1の実施の形態に係る表示装置の一構成例を表すものである。表示装置1は、供給されたインターレース映像信号に基づいて、IP変換を行わずに表示を行うものである。なお、本開示の実施の形態に係る表示装置の駆動回路および表示装置の駆動方法は、本実施の形態により具現化されるので、併せて説明する。

【0016】

表示装置1は、制御部11と、タイミング制御部16と、反転信号生成部15と、反転制御部30と、VRAM(Video RAM)12と、RGBデコーダ部13と、反転部14と、表示部20とを備えている。

【0017】

制御部11は、供給された映像信号Vdispに基づいて、VRAM12、RGBデコーダ部13、反転信号生成部15、およびタイミング制御部16に対してそれぞれ制御信号を供給し、これらがお互いに同期して動作するように制御する回路である。

【0018】

映像信号Vdispは、インターレース映像信号であり、複数(ここでは2つ)のフィールド画像の画像情報が交互に表示装置1に供給されるようになっている。

【0019】

図2は、インターレース映像信号の一例を模式的に表すものであり、(A)はフレーム画像Fを示し、(B)は第1フィールド画像Fi1を示し、(C)は第2フィールド画像Fi2を示す。

【0020】

フレーム画像Fは、図2(A)に示したように、複数のライン画像Lから構成されている。フレーム画像Fは、例えば、映像信号VdispがSD(Standard Definition)信号の場合には、水平方向に720画素、垂直方向に480画素の画素情報を有している。また、フレーム画像Fは、例えば映像信号VdispがHD(High Definition)信号の場合には、水平方向に1920画素、垂直方向に1080画素の画素情報を有している。

【0021】

第1フィールド画像Fi1および第2フィールド画像Fi2(図2(B),(C))は、フレーム画像F(図2(A))を構成するライン画像Lを交互に分配して構成したものである。各フィールド画像(第1フィールド画像Fi1および第2フィールド画像Fi2)は、例えば映像信号VdispがSD信号の場合には、水平方向に720画素、垂直方向に240画素の画素情報を有し、例えば映像信号VdispがHD信号の場合には、水平方向に1920画素、垂直方向に540画素の画素情報を有している。

【0022】

制御部11は、映像信号Vdispにより供給された各フィールド画像の画像情報をVRAM12に対して書込むとともに、表示を行う際には、VRAM12から画像データを読み出す。また、制御部11は、RGBデコーダ部13に対して、VRAM12から読み出した画像情報と制御信号を供給し、反転信号生成部15およびタイミング制御部16に対して制御信号を供給する。

【0023】

タイミング制御部16は、制御部11からの制御信号に基づいて、複数の制御信号を生成し、表示部20および反転制御部30に供給するものである。具体的には、タイミング制御部16は、水平同期信号HST、クロック信号HCLK、水平イネーブル信号HEN、垂直同期信号VST、およびクロック信号VCLKを生成し、表示部20に対して供給する。また、タイミング制御部16は、反転制御信号FRPおよび垂直イネーブル信号VENを生成し、垂直同期信号VSTとともに、反転制御部30に対して供給する。

【0024】

ここで、水平同期信号HSTは、後述するように、1水平期間(1H)ごとにパルス波形を有する信号であり、垂直同期信号VSTは、1垂直期間(1V)ごとにパルス波形を有する信号である。また、水平イネーブル信号HENおよび垂直イネーブル信号VENは、後述するように、サブ画素SPixへの画素信号Vpix2の書込みを制御するためのものである。反転制御信号FRPは、1垂直期間ごとに反転する信号である。

【0025】

反転信号生成部15は、制御部11から供給される制御信号に基づいて、所定の複数の垂直期間ごとに、論理が反転する長周期反転信号INVを生成するものである。長周期反転信号INVは、例えば、約1分ごとに論理反転するものである。

【0026】

反転制御部30は、反転信号生成部15から供給される長周期反転信号INVと、タイミング制御部16から供給される反転制御信号FRP、垂直同期信号VST、および垂直イネーブル信号VENに基づいて、反転制御信号FRP2および垂直イネーブル信号VEN2を生成するものである。

【0027】

図3は、反転制御部30の一構成例を表すものである。反転制御部30は、EX−OR回路31と、D型フリップフロップ回路32と、EX−NOR回路33と、論理積回路34とを備えている。EX−OR回路31は、長周期反転信号INVと反転制御信号FRPとの排他的論理和を求め、反転制御信号FRP2として出力するものである。D型フリップフロップ回路32は、そのデータ入力端子に長周期反転信号INVが供給されるとともに、そのクロック入力端子に垂直同期信号VSTが供給され、垂直同期信号VSTに同期して長周期反転信号INVをサンプリングし、その結果を信号VN1として出力するものである。EX−NOR回路33は、長周期反転信号INVと、D型フリップフロップ回路32の出力信号(信号VN1)との排他的論理和の反転を求め、信号VN2として出力するものである。論理積回路34は、EX−NOR回路33の出力信号(信号VN2)と、垂直イネーブル信号VENの論理積を求め、垂直イネーブル信号VEN2として出力するものである。

【0028】

この構成により、反転制御部30は、長周期反転信号INVが低レベルの場合には、反転制御信号FRPと同じ信号を反転制御信号FRP2として出力し、長周期反転信号INVが高レベルの場合には、反転制御信号FRPを反転した信号を反転制御信号FRP2として出力する。また、反転制御部30は、長周期反転信号INVが変化した後の最初の垂直期間において低レベルになり、その他の期間では垂直イネーブル信号VENと同じ信号となる垂直イネーブル信号VEN2を生成するようになっている。

【0029】

VRAM12は、画像情報を記憶する記憶部であり、制御部11から供給されたフィールド画像(第1フィールド画像Fi1および第2フィールド画像Fi2)の画像情報を記憶し、その画像情報を制御部11からの要求に応じて出力するものである。

【0030】

RGBデコーダ部13は、制御部11から供給された画像情報および制御信号に基づいて、赤色(R)、緑色(G)、青色(B)の各成分のアナログ信号である画素信号VpixR,VpixG,VpixBを生成するものである。なお、以下の説明では、説明の便宜上、画素信号VpixR,VpixG,VpixBのうちの任意の一つを示すものとして、画素信号Vpixを適宜用いる。

【0031】

なお、例えば、制御部11と、反転信号生成部15と、RGBデコーダ部13は、例えばマイクロコントローラ(MCU)により構成してもよい。

【0032】

反転部14は、反転制御部30から供給された反転制御信号FRP2に基づいて、RGBデコーダ部13から供給された画素信号VpixR,VpixG,VpixBに対する反転動作を制御し、画素信号VpixR2,VpixG2,VpixB2として出力するものである。具体的には、後述するように、反転部14は、反転制御信号FRP2が高レベルの場合には、画素信号VpixR,VpixG,VpixBをそのまま画素信号VpixR2,VpixG2,VpixB2として出力し、反転制御信号FRP2が低レベルの場合には、画素信号VpixR,VpixG,VpixBを反転して画素信号VpixR2,VpixG2,VpixB2として出力するようになっている。なお、以下の説明では、説明の便宜上、画素信号VpixR2,VpixG2,VpixB2のうちの任意の一つを示すものとして、画素信号Vpix2を適宜用いる。

【0033】

表示部20は、液晶表示部であり、反転部14から供給された画素信号VpixR2,VpixG2,VpixB2、および反転制御部30、タイミング制御部16から供給される様々な制御信号に基づいて表示を行うものである。この例では、表示部20は、ノーマリホワイト型のものである。ただし、表示部20は、これに限定されるものではなく、これに代えて、ノーマリブラック型であってもよい。表示部20は、各フィールド画像の画素数と同じ数の画素を有している。すなわち、表示部20では、フレーム画像Fと比べて、垂直方向の画素数が半分になっている。

【0034】

図4は、表示部20における画像の表示を表すものであり、(A)は第1フィールド画像Fi1を表示した場合を示し、(B)は第2フィールド画像Fi2を表示した場合を示す。この図4は、図2(B),(C)と対応している。すなわち、第1フィールド画像Fi1を表示する際には、図2(B)の画像が図4(A)のように表示され、第2フィールド画像Fi2を表示する際には、図2(C)の画像が図4(B)のように表示される。このように、表示装置1では、IP変換を行うことなく、インターレース映像信号に含まれるフィールド画像が交互に表示されるようになっている。

【0035】

図5は、表示部20の一構成例を表すものである。表示部20は、水平走査部21と、M個の論理積回路22(論理積回路22(1)〜22(M))と、M個のスイッチ23(スイッチ23(1)〜23(M))と、垂直走査部26と、N個の論理積回路27(論理積回路27(1)〜27(N))と、マトリックス状に配置された画素Pixとを備えている。

【0036】

水平走査部21は、水平同期信号HSTおよびクロック信号HCLKに基づいて、マトリックス状に配置された画素Pixを水平方向に走査するものである。この水平走査部21は、例えば、シフトレジスタを用いて構成されており、そのデータ入力端子に水平同期信号HSTが供給され、クロック入力端子にクロック信号HCLKが供給される。この構成により、水平走査部21は、シフトレジスタの各段から、クロック信号HCLKに同期したパルス信号を、走査信号SH1〜SHMとして順次出力するようになっている。

【0037】

論理積回路22(1)〜22(M)のそれぞれは、水平走査部21から供給された走査信号SH1〜SHMのそれぞれと、水平イネーブル信号HENとの論理積を求め、走査信号φH1〜φHMとして出力する回路である。

【0038】

スイッチ23(1)〜23(M)は、それぞれ対応する論理積回路22(1)〜22(M)の出力信号(走査信号φH1〜φHM)に基づいて、オンオフするスイッチである。スイッチ23(1)〜23(M)は、例えば、薄膜トランジスタ(TFT;Thin Film Transistor)を用いたアナログスイッチなどにより形成されるものである。スイッチ23(1)〜23(M)の一端には反転部14から画素信号Vpix2が供給され、他端は画素信号線SGLを介して画素Pixと接続されている。具体的には、スイッチ23(1)には、赤色に係る画素信号VpixR2が供給され、スイッチ23(2)には、青色に係る画素信号VpixG2が供給され、スイッチ23(3)には、緑色に係る画素信号VpixB2が供給される。そして、スイッチがオン状態になると、これらの画素信号VpixR2,VpixG2,VpixB2は、画素信号線SGLを介して、画素Pixを構成する、RGBにそれぞれ対応する各サブ画素SPix(後述)に供給されるようになっている。

【0039】

垂直走査部26は、垂直同期信号VSTおよびクロック信号VCLKに基づいて、マトリックス状に配置された画素Pixの垂直方向に走査するものである。この垂直走査部26は、例えば、シフトレジスタを用いて構成されており、そのデータ入力端子に垂直同期信号VSTが供給され、クロック端子にクロック信号VCLKが供給される。この構成により、垂直走査部26は、シフトレジスタの各段から、クロック信号VCLKに同期したパルス信号を、走査信号SV1〜SVNとして順次出力するようになっている。

【0040】

論理積回路27(1)〜27(N)のそれぞれは、垂直走査部27から供給された走査信号SV1〜SVNのそれぞれと、垂直イネーブル信号VEN2との論理積を求め、走査信号φV1〜φVNとして出力する回路である。この論理積回路27(1)〜27(N)の出力端子は、走査信号線GCLを介して画素Pixと接続されている。

【0041】

画素Pixは、表示画像を構成する表示要素である。画素Pixは、3つのサブ画素SPixにより構成される。サブ画素SPixは、TFT素子Trおよび液晶素子LCを有している。TFT素子Trは、薄膜トランジスタ(TFT)により構成されるものであり、この例では、nチャネルのMOS(Metal Oxide Semiconductor)型のTFTで構成されている。TFT素子Trのソースは画素信号線SGLに接続され、ゲートは走査信号線GCLに接続され、ドレインは液晶素子LCの一端に接続されている。液晶素子LCは、一端がTFT素子Trのドレインに接続され、他端には、共通電圧VCOM(例えば0V)が印加されている。

【0042】

サブ画素SPixは、走査信号線GCLにより、表示部20において同じ行に配置された他のサブ画素SPixと互いに接続されている。また、サブ画素SPixは、画素信号線SGLにより、表示部20において同じ列に配置された他のサブ画素SPixと互いに接続されている。

【0043】

この構成により、表示部20では、垂直走査部26および論理積回路27(1)〜27(N)が走査信号線GCLを時分割的に線順次走査するように駆動することにより、1水平ラインが順次選択される。そして、水平走査部21および論理積回路22(1)〜22(M)が、順次走査により画素信号線SGLを選択し、反転部14が、画素信号Vpix2を、その選択された画素信号線SGLを介して、サブ画素SPixに供給する。各サブ画素SPixでは、TFT素子Trがオン状態のときに、画素信号Vpix2が液晶素子LCの一端に画素電位Vpとして書き込まれ、TFT素子Trがオフ状態になると、その液晶素子LCの一端が画素信号線SGLと電気的に切り離されてハイインピーダンス状態になり、その画素電位Vpが維持されるようになっている。

【0044】

また、水平イネーブル信号HEN、および垂直イネーブル信号VEN2は、サブ画素SPixへの画素信号Vpix2の書込みを制御する。具体的には、水平イネーブル信号HENおよび垂直イネーブル信号VEN2がともに高レベルである場合には、上述したような動作により、サブ画素SPixへの画素信号Vpix2の書込みが行われる。一方、水平イネーブル信号HENが高レベルであり、垂直イネーブル信号VEN2が低レベルである場合には、走査信号φV1〜φVNの全てが低レベルになるため、画素信号Vpix2は、画素信号線SGLに印加されるものの、サブ画素SPixに書き込まれることはない。さらに、水平イネーブル信号HENが低レベルである場合には、走査信号φH1〜φHMの全てが低レベルになるため、スイッチ23(1)〜23(M)の全てがオフ状態になり、画素信号Vpix2は、画素信号線SGLに印加されないようになっている。

【0045】

ここで、RGBデコーダ部13および反転部14は、本開示における「画素信号生成部」の一具体例に対応する。反転制御部30は、本開示における「書込制御部」の一具体例に対応する。長周期反転信号INVは、本開示における「論理信号」の一具体例に対応し、反転信号生成部15は、本開示における「論理信号生成部」の一具体例に対応する。TFT素子Trは、本開示における「画素スイッチ」の一具体例に対応する。スイッチ23(1)〜23(M)は、本開示における「信号線スイッチ」の一具体例に対応する。

【0046】

[動作および作用]

続いて、本実施の形態の表示装置1の動作および作用について説明する。

【0047】

(全体動作概要)

まず、図1を参照して、表示装置1の全体動作概要を説明する。制御部11は、供給された映像信号Vdispに基づいて、VRAM12、RGBデコーダ部13、反転信号生成部15、およびタイミング制御部16に対してそれぞれ制御信号を供給し、これらがお互いに同期して動作するように制御する。タイミング制御部16は、複数の制御信号を生成し、表示部20および反転制御部30に供給する。反転信号生成部15は、長周期反転信号INVを生成し、反転制御部30は、長周期反転信号INVなどに基づいて、反転制御信号FRP2および垂直イネーブル信号VEN2を生成する。RGBデコーダ部13は、画素信号VpixR,VpixG,VpixBを生成する。反転部14は、反転制御信号FRP2に基づいて画素信号VpixR,VpixG,VpixBに対する反転動作を制御し、画素信号VpixR2,VpixG2,VpixB2として出力する。表示部20は、画素信号VpixR2,VpixG2,VpixB2、垂直イネーブル信号VEN2などに基づいて表示を行う。

【0048】

(表示装置1の詳細動作)

次に、図6,7を参照して、表示装置1の詳細動作について説明する。

【0049】

図6は、表示装置1における表示動作のタイミング波形例を表すものであり、(A)は垂直同期信号VSTの波形を示し、(B)はクロック信号VCLKの波形を示し、(C)は垂直イネーブル信号VENの波形を示し、(D)は走査信号φV1〜φVNの波形を示し、(E)は反転制御信号FRP2の波形を示し、(F)は画素信号VpixR,VpixG,VpixBの波形を示し、(G)は画素信号VpixR2,VpixG2,VpixB2の波形を示す。なお、図示していないが、この図6では、長周期反転信号INVは、低レベルもしくは高レベルのいずれかであり、一定レベルである。

【0050】

図7は、1水平期間における表示装置1の表示動作の一例を表すものであり、(A)は水平同期信号HSTの波形を示し、(B)はクロック信号HCLKの波形を示し、(C)は水平イネーブル信号HENの波形を示し、(D)は走査信号φH1〜φHMの波形を示し、(E)は画素信号VpixR2,VpixG2,VpixB2の波形を示す。この例では、スイッチ23(1)〜23(N)は、対応する走査信号φH1〜φHMが高レベルのときにオン状態になるものとする。

【0051】

表示装置1では、第1フィールド画像Fi1および第2フィールド画像Fi2が、垂直期間(1V)ごとに交互に表示される。その際、画素信号VpixR2,VpixG2,VpixB2は、垂直期間ごとに反転する。この垂直期間の長さは、例えば、16.7[msec](=1/60[Hz])である。以下に、この動作を詳細に説明する。

【0052】

まず、タイミングt10付近において、タイミング制御部16は、垂直同期信号VSTとしてパルス信号を生成する(図6(A))。これにより、垂直期間(1V)が開始する。また、このタイミングt10において、タイミング制御部16は、クロック信号VCLKを低レベルから高レベルに変化させる(図6(B))。これにより、垂直走査部26のシフトレジスタでは、垂直同期信号VSTのパルス部分(高レベル部分)がサンプリングされ、走査信号φV1が低レベルから高レベルに変化する(図6(D))。よって、表示部20では、1行目の走査信号線GCLが高レベルになり、表示書込動作の対象となる1水平ラインが選択される。

【0053】

タイミングt10〜t20からの1垂直期間(1V)では、RGBデコーダ部13は、第1フィールド画像Fi1に係る画素信号VpixR,VpixG,VpixBを反転部14に対して供給する。そして、タイミングt10において、反転制御部30は、反転制御信号FRP2を低レベルから高レベルに変化させる(図6(E))。これに伴い、反転部14は、RGBデコーダ部13から供給された第1フィールド画像Fi1に係る画素信号VpixR,VpixG,VpixBを、そのまま、画素信号VpixR2,VpixG2,VpixB2として出力する(図6(F),(G))。

【0054】

そして、このタイミングt10〜t11の期間(1水平期間(1H))において、図7に示したように、画素信号Vpix2が、選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0055】

具体的には、図7において、タイミングt0付近において、タイミング制御部16が、水平同期信号HSTとしてパルス信号を生成する(図7(A))。そして、このタイミングt0において、タイミング制御部16は、クロック信号HCLKを高レベルから低レベルに変化させ(図7(B))、これにより、水平走査部21のシフトレジスタでは、水平同期信号HSTのパルス部分(高レベル部分)がサンプリングされ、走査信号SH1が低レベルから高レベルに変化する(図6(D))。次に、タイミングt1〜t2の期間において、タイミング制御部16は、水平イネーブル信号HENを高レベルにする(図7(C))。これにより、この期間において、スイッチ23(1)がオン状態になり、画素信号VpixR2が、1列目の画素信号線SGLに印加され、選択された1水平ラインに係るサブ画素SPixに供給される。次にタイミングt3において、タイミング制御部16は、クロック信号HCLKを高レベルから低レベルに変化させ(図7(B))、走査信号SH1が高レベルから低レベルに変化するとともに、走査信号SH2が低レベルから高レベルに変化する(図7(D))。次に、タイミングt4〜t5の期間において、タイミング制御部16は、水平イネーブル信号HENを高レベルにする(図7(C))。これにより、この期間において、スイッチ23(2)がオン状態になり、画素信号VpixG2が、2列目の画素信号線SGLに印加され、選択された1水平ラインに係るサブ画素SPixに供給される。このようにして、タイミングt0〜t9までの1水平期間(1H)において、選択された1水平ライン内の全てのサブ画素SPixに対して、画素信号Vpix2が供給され、書込みが行われる。

【0056】

次に、タイミングt11において、タイミング制御部16は、クロック信号VCLKを高レベルから低レベルに変化させる(図6(B))。これにより、垂直走査部26のシフトレジスタでは、データが転送され、走査信号φV1が高レベルから低レベルに変化するとともに、走査信号φV2が低レベルから高レベルに変化する(図6(D))。これにより、表示部20において、2行目の走査信号線GCLが高レベルになることにより、表示書込動作の対象となる1水平ラインが選択され、タイミングt11〜t12の期間において、画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0057】

これ以降、タイミングt20まで、同様の動作が繰り返し行われることにより、表示部20の全面にわたり、表示書込動作の対象となる1水平ラインが順次選択され、第1フィールド画像Fi1に係る画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに順次書き込まれる。これにより、表示部20の全面において、第1フィールド画像Fi1の表示が行われる。

【0058】

次に、タイミングt20付近において、タイミング制御部16は、垂直同期信号VSTとしてパルス信号を生成する(図6(A))。これにより、今までの垂直期間(1V)が終了するとともに、新たな垂直期間が開始する。また、このタイミングt20において、タイミング制御部16は、クロック信号VCLKを低レベルから高レベルに変化させる(図6(B))。これにより、垂直走査部26のシフトレジスタでは、垂直同期信号VSTのパルス部分(高レベル部分)がサンプリングされ、走査信号φV1が低レベルから高レベルに変化する(図6(D))。これにより、表示部20において、1行目の走査信号線GCLが高レベルになり、表示書込動作の対象となる1水平ラインが選択される。

【0059】

タイミングt20からの1垂直期間(1V)では、RGBデコーダ部13は、第2フィールド画像Fi2に係る画素信号VpixR,VpixG,VpixBを反転部14に対して供給する。そして、タイミングt20において、反転制御部30は、反転制御信号FRP2を高レベルから低レベルに変化させる(図6(E))。これに伴い、反転部14は、RGBデコーダ部13から供給された第2フィールド画像Fi2に係る画素信号VpixR,VpixG,VpixBを反転して、画素信号VpixR2,VpixG2,VpixB2として出力する(図6(F),(G))。そして、タイミングt20〜t21の期間において、画素信号Vpix2が、選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0060】

次に、タイミングt21において、タイミング制御部16は、クロック信号VCLKを高レベルから低レベルに変化させる(図6(B))。これにより、表示部20において、2行目の走査信号線GCLが高レベルになることにより、表示書込動作の対象となる1水平ラインが選択され、タイミングt21〜t22の期間において、画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0061】

これ以降、タイミングt20まで、同様の動作が繰り返し行われることにより、表示部20の全面にわたり、表示書込動作の対象となる1水平ラインが順次選択され、第2フィールド画像Fi2に係る画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに順次書き込まれる。これにより、表示部20の全面において、第2フィールド画像Fi2の表示が行われる。

【0062】

(反転信号生成部15および反転制御部30の詳細動作)

次に、反転信号生成部15および反転制御部30の詳細動作を説明する。

【0063】

図8は、反転信号生成部15および反転制御部30の動作の一例を表すものであり、(A)は長周期反転信号INVの波形を示し、(B)は反転制御信号FRPの波形を示し、(C)は反転制御信号FRP2の波形を示し、(D)は垂直同期信号VSTの波形を示し、(E)は信号VN1(D型フリップフロップ回路32の出力信号)の波形を示し、(F)は信号VN2(EX−NOR回路33の出力信号)の波形を示し、(G)は垂直イネーブル信号VENの波形を示し、(H)は垂直イネーブル信号VEN2の波形を示す。

【0064】

表示装置1では、長周期反転信号INVに基づき2つの反転動作期間PA,PB(第1の期間および第2の期間)が設定される。これらの2つの反転動作期間PA,PBでは、反転部14は、互いに異なる方法で画素信号の反転動作を行う。そして、各反転動作期間PA,PBにおいて、表示部20は、その反転部14から出力された画素信号Vpix2に基づいて、第1フィールド画像Fi1と第2フィールド画像Fi2を垂直期間(1V)ごとに交互に表示する。以下に、この動作を詳細に説明する。

【0065】

反転信号生成部15は、タイミングt30〜t40の期間において、長周期反転信号INVを低レベルにする(図8(A))。これにより、反転制御部30のEX−OR回路31は、この期間(反転動作期間PA)において、タイミング制御部16から供給された反転制御信号FRP(図8(B))と同じ信号を反転制御信号FRP2として出力する(図8(C))。また、反転信号生成部15は、タイミングt40〜t50の期間において、長周期反転信号INVを高レベルにする(図8(A))。これにより、反転制御部30のEX−OR回路31は、この期間(反転動作期間PB)において、タイミング制御部16から供給された反転制御信号FRP(図8(B))を反転した信号を反転制御信号FRP2として出力する(図8(C))。結果として、反転動作期間PAと反転動作期間PBとの境界を挟む隣接する垂直期間では、反転制御信号FRP2のレベルは同じものとなる。

【0066】

反転部14は、このようにして生成された反転制御信号FRP2に基づいて、RGBデコーダ13から供給された画素信号VpixR,VpixG,VpixBを反転制御し、画素信号VpixR2,VpixG2,VpixB2として出力する。具体的には、反転部14は、反転制御信号FRP2が高レベルの場合には、画素信号VpixR,VpixG,VpixBをそのまま画素信号VpixR2,VpixG2,VpixB2として出力し、反転制御信号FRP2が低レベルの場合には、画素信号VpixR,VpixG,VpixBを反転して画素信号VpixR2,VpixG2,VpixB2として出力する。すなわち、反転動作期間PAと反転動作期間PBとでは、反転動作の方法が互いに異なっている。

【0067】

また、反転制御部30のD型フリップフロップ回路32は、反転動作期間PA,PBの両方の期間において、垂直同期信号VST(図8(D))の立ち上がりに同期したタイミングで長周期反転信号INV(図8(A))をサンプリングする。このとき、図示していないが、タイミングt30付近において、垂直同期信号VSTが立ち上がった後に、長周期反転信号INVが立ち下がるようになっており、タイミングt40付近において、垂直同期信号VSTが立ち上がった後に、長周期反転信号INVが立ち上がるようになっている。これにより、D型フリップフロップ回路32は、長周期反転信号INVを1垂直期間(1V)分だけ遅延した信号VN1を出力する(図8(A),(E))。すなわち、このD型フリップフロップ回路32は、長周期反転信号INVを1垂直期間(1V)分だけ遅延させる遅延回路として機能している。EX−NOR回路33は、長周期反転信号INV(図8(A))および信号VN1(図8(E))の排他的論理和の反転信号を求め、信号VN2を出力する(図8(F))。この信号VN2は、反転動作期間PA,PBのそれぞれにおいて、最初の垂直期間のみ低レベルとなり、他の期間では高レベルとなる信号である。論理積回路34は、垂直イネーブル信号VEN(図8(G))および信号VN2(図8(F))の論理積を求め、垂直イネーブル信号VEN2として出力する。この垂直イネーブル信号VEN2は、反転動作期間PA,PBのそれぞれにおいて、最初の垂直期間のみ低レベルとなり、他の期間では垂直イネーブル信号VENと同じ信号となる。

【0068】

表示部20では、この垂直イネーブル信号VEN2に基づいて、サブ画素SPixに対する画素信号Vpix2の書込み制御が行われる。具体的には、垂直イネーブル信号VEN2が高レベルである場合には、表示部20において線順次走査が行われ、1水平ラインごとにサブ画素SPixに対する画素信号Vpix2の書込みが行われる。一方、垂直イネーブル信号VEN2が低レベルである場合には、走査信号φV1〜φVNの全てが低レベルになるため、全てのサブ画素SPixに係るTFT素子Trがオフ状態となり、サブ画素SPixに対する画素信号Vpix2の書込みは行われない。

【0069】

すなわち、反転動作期間PA,PBのそれぞれにおける最初の垂直期間では、垂直イネーブル信号VEN2が低レベルになるため、表示画面全面においてサブ画素SPixへの書込みは行われない。よって、この期間において、各サブ画素SPixでは、TFT素子Trがオフ状態になるため、画素電位Vpがほぼ維持される。

【0070】

これにより、表示装置1は、反転動作期間PA,PBのそれぞれにおける最初の垂直期間を除き、第1フィールド画像Fi1(第1フィールド画像表示期間PW1)と第2フィールド画像Fi2(第2フィールド画像表示期間PW2)を、垂直期間(1V)ごとに交互に表示する。

【0071】

次に、この反転信号生成部15および反転制御部30の作用について、具体例を用いて説明する。

【0072】

図9は、インターレース画像の一例を模式的に表すものであり、(A)はフレーム画像Fを示し、(B)は第1フィールド画像Fi1を示し、(C)は第2フィールド画像Fi2を示す。この例では、表示装置1は静止画を表示している。図9において、斜線で示した領域は白色(WH)を表示する領域であり、その他の領域は黒色(BL)を表示する領域である。

【0073】

図10は、表示部20における画像の表示を表すものであり、(A)は、図9(B)に示した第1フィールド画像Fi1を表示した場合を示し、(B)は、図9(C)に示した第2フィールド画像Fi2を表示した場合を示す。表示装置1では、図10(A),(B)に示した各フィールド画像Fi1,Fi2が交互に表示されるが、その際、領域R2では、第1フィールド画像Fi1が表示される際には黒表示が行われ(図10(A))、一方、第2フィールド画像Fi2が表示される際には白表示が行われる(図10(B))。また、領域R3では、第1フィールド画像Fi1が表示される際には白表示が行われ(図10(A))、一方、第2フィールド画像Fi2が表示される際には黒表示が行われる(図10(B))。

【0074】

図11は、図10のような表示が行われる場合における表示装置1の表示動作の一例を表すものであり、(A)は長周期反転信号INVの波形を示し、(B)は反転制御信号FRP2の波形を示し、(C)は垂直イネーブル信号VEN2の波形を示し、(D)〜(F)は画素電位Vpの波形を示す。ここで、図11において、(D)は、常に黒表示が行われる領域R1のサブ画素SPixにおける画素電位Vp(R1)を示し、(E)は領域R2のサブ画素SPixにおける画素電位Vp(R2)を示し、(F)は領域R3のサブ画素SPixにおける画素電位Vp(R3)を示す。なお、図11において、タイミングt30〜t50は、図8におけるタイミングt30〜t50にそれぞれ対応している。

【0075】

常に黒表示が行われる領域R1におけるサブ画素SPixでは、図11(D)に示したように、反転制御信号FRP2(図11(B))に基づいて、各フィールド画像Fi1,Fi2に係る画素信号Vpix2が反転駆動により供給される。その際、このサブ画素SPixは、第1フィールド画像Fi1と第2フィールド画像Fi2とで同じ色の表示を行うため、画素電位Vpは、共通電圧VCOMを中心とした交流波形となる(図11(D))。すなわち、画素電位Vpの時間平均値は、共通電圧VCOMと等しいものである。

【0076】

領域R2,R3におけるサブ画素SPixでも、同様に、反転制御信号FRP2に基づいて反転駆動により書込み動作がおこなわれる。図10に示したように、これらのサブ画素SPixは、領域R1におけるサブ画素SPixとは異なり、第1フィールド画像Fi1と第2フィールド画像Fi2とで異なる色の表示を行うため、画素電位Vpの時間平均値Vavgは、共通電圧VCOMからずれたものになる。具体的には、領域R2におけるサブ画素SPixの画素電位Vpは、第1フィールド表示期間PW1では黒表示に対応する電位となり、第2フィールド表示期間PW2では白表示に対応する電位となるため、その時間平均値Vavgは、図11(E)に示したように、反転動作期間PAでは共通電圧VCOMより高くなり、反転動作期間PBでは共通電圧VCOMより低くなる。また、領域R3におけるサブ画素SPixの画素電位Vpは、第1フィールド表示期間PW1では白表示に対応する電位となり、第2フィールド表示期間PW2では黒表示に対応する電位となるため、その時間平均値Vavgは、図11(F)に示したように、反転動作期間PAでは共通電圧VCOMより低くなり、反転動作期間PBでは共通電圧VCOMより高くなる。

【0077】

しかしながら、反転動作期間PAにおける画素電位Vpの時間平均値Vavgと、反転動作期間PBにおける画素電位Vpの時間平均値Vavgとは、共通電圧VCOMを基準として反転の関係にあるため、反転動作期間PAおよび反転動作期間PBの合計期間では、画素電位Vpの時間平均値は共通電圧VCOMと等しくなる。

【0078】

このように、表示装置1では、互いに異なる方法で反転動作を行う反転動作期間PA,PBを設けたので、図11(D)〜(F)に示したように、反転動作期間PAおよび反転動作期間PBの合計期間における画素電位Vpの時間平均値を、共通電圧VCOMと等しくすることができ、液晶表示装置におけるいわゆる「焼き付き」を低減することができる。

【0079】

また、上述したように、反転動作期間PA,PBのそれぞれおける最初の垂直期間では、垂直イネーブル信号VEN2を低レベルにすることにより、全ての走査信号線GCLの電圧(走査信号φV1〜φVN)を低レベルにしている。これにより、サブ画素SPixでは、TFT素子Trがオフ状態になり、サブ画素SPixへの書込み動作が行われないため、画素電位Vpは、図11(D)〜(F)に示したように、その前の垂直期間における電位を維持する(波形部分W1)。これにより、以下に比較例を参照して説明するように、長周期反転信号INVの反転時における表示画像の乱れを低減することができ、画質を改善することができる。

【0080】

(比較例)

次に、比較例と対比して、本実施の形態の作用を説明する。本比較例は、反転動作期間PA,PBにおける最初の垂直期間でも、サブ画素SPixに対する書込み動作を行うものである。

【0081】

図12は、比較例に係る表示装置1Rの一構成例を表すものである。表示装置1Rは反転制御部30Rを備えている。反転制御部30Rは、本実施の形態に係る反転制御部30(図3)において、D型フリップフロップ回路32、EX−NOR回路33、および論理積回路34を省いたものである。これにより、本比較例では、タイミング制御部16において生成された垂直イネーブル信号VENが、そのまま表示パネル20に入力される。

【0082】

図13は、表示装置1Rの表示動作の一例を表すものであり、(A)は長周期反転信号INVの波形を示し、(B)は反転制御信号FRP2の波形を示し、(C)は垂直イネーブル信号VEN2の波形を示し、(D)は常に所定の中間調の色を表示するサブ画素SPixにおける画素電位Vpの波形を示す。なお、図11において、タイミングt30〜t50は、図8におけるタイミングt30〜t50にそれぞれ対応している。

【0083】

図13に示したように、本比較例に係る表示装置1Rでは、反転動作期間PA,PBにおける最初の垂直期間において、垂直イネーブル信号VENは高レベルであるため、この期間でもサブ画素SPixに対して画素信号Vpix2の書込みが行われる。その際、反転動作期間PAと反転動作期間PBとの境界を挟む隣接する垂直期間では、同じ電圧の画素信号Vpix2が続けて印加される。

【0084】

しかしながら、実際には、この2つの垂直期間における画素電位Vpは等しくならないおそれがある。すなわち、タイミングt29,t39などのように、画素信号Vpix2が反転してサブ画素SPixに供給される場合では、液晶素子LCに充電する電荷量が多いため、反転部14は、そのサブ画素SPixを十分に駆動できず、画素電位Vpは十分に変化しきれないおそれがある(波形部分W2)。一方、タイミングt30,t40などのように、画素信号Vpix2が反転しないで印加される場合では、液晶素子LCに充電する電荷量が少ないため、反転部14は、そのサブ画素SPixを十分に駆動することができ、画素電位Vpを所望の電位により近いレベルにまで変化させることができる(波形部分W3)。よって、例えば、表示装置1Rが、表示画面全体にわたってこの中間調の色を表示した場合、長周期反転信号INV(図13(A))が反転する際、瞬間的に画面全体の輝度が変化してしまう。つまり、約1分ごとに論理反転する長周期反転信号INVを用いた場合には、約1分ごとにこの現象が発生し、画質が低下してしまう。

【0085】

一方、本実施の形態に係る表示装置1では、反転動作期間PA,PBのそれぞれにおける最初の垂直期間において、サブ画素SPixに対する画素信号Vpix2の書込み動作を行わないようにしている。これにより、反転動作期間PAと反転動作期間PBとの境界を挟む隣接する垂直期間では、画素電位Vpが維持されるため、画素電位Vpは互いに等しくなる。よって、例えば、表示装置1が、表示画面全体にわたってこの中間調の色を表示した場合でも、長周期反転信号INVが反転する際に、瞬間的に画面全体の輝度が変化するおそれを低減することができ、画質の低下を抑えることができる。

【0086】

[効果]

以上のように本実施の形態では、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixに対する画素信号の書込み動作を行わないようにしたので、画質の低下を抑えることができる。

【0087】

[変形例1−1]

上記実施の形態では、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixのTFT素子Trをオフ状態にすることにより、画素信号Vpix2の書込み動作を行わないようにしたが、これに限定されるものではなく、これに加えて、さらに、スイッチ23(1)〜23(M)をオフ状態にし、画素信号線SGLに画素信号Vpix2を印加しないようにしてもよい。その具体例を、以下に説明する。

【0088】

図14は、本変形例に係る表示装置1Bの一構成例を表すものである。表示装置1Bは、反転制御部30Bを備えている。反転制御部30Bは、上記実施の形態に係る反転制御部30の機能に加え、水平イネーブル信号HENに基づいて、水平イネーブル信号HEN2を生成する機能も有している。そして、表示パネル20には、この反転制御部30Bが生成した水平イネーブル信号HEN2が入力される。

【0089】

図15は、反転制御部30Bの一構成例を表すものである。反転制御部30Bは、論理積回路35を有している。論理積回路35は、EX−NOR回路33の出力信号(信号VN2)と、水平イネーブル信号HENの論理積を求め、水平イネーブル信号HEN2として出力するものである。

【0090】

この構成により、反転制御部30Bは、長周期反転信号INVが変化した後の最初の垂直期間において低レベルになり、その他の期間では水平イネーブル信号HENと同じ信号となる水平イネーブル信号HEN2を生成する。これにより、長周期反転信号INVが変化した後の最初の垂直期間(反転動作期間PA,PBにおける最初の垂直期間)では、スイッチ23(1)〜23(M)がオフ状態になるため、画素信号Vpix2は画素信号線SGLに印加されることはない。

【0091】

なお、この例では、スイッチ23(1)〜23(M)をオフ状態にしたが、例えば、反転部14に同様のスイッチを設け、長周期反転信号INVが変化した後の最初の垂直期間においてこのスイッチをオフ状態にすることにより、表示部20に画素信号VpixR2,VpixG2,VpixB2を供給しないようにしてもよい。

【0092】

[変形例1−2]

上記実施の形態では、反転制御部30において、長周期反転信号INVを1垂直期間(1V)分だけ遅延させたが、これに限定されるものではなく、これに代えて、複数の垂直期間に対応する時間だけ遅延させてもよい。以下に、長周期反転信号INVを、2つの垂直期間に対応する時間だけ遅延させる場合を例に説明する。

【0093】

図16は、本変形例に係る反転制御部30Cの一構成例を表すものである。反転制御部30Cは、D型フリップフロップ回路32A,32Bを有している。D型フリップフロップ回路32Aは、データ入力端子に長周期反転信号INVが供給されるとともに、クロック入力端子に垂直同期信号VSTが供給される。D型フリップフロップ回路32Bは、データ入力端子にD型フリップフロップ回路32Aの出力端子が接続されるとともに、クロック入力端子に垂直同期信号VSTが供給される。このD型フリップフロップ回路32Bの出力信号は、EX−NOR回路33に入力される。このD型フリップフロップ回路32A,32Bは、長周期反転信号INVを2つの1垂直期間(1V)分だけ遅延させる遅延回路として機能する。これにより、この反転制御部30Cを備えた表示装置では、反転動作期間PA,PBにおける最初の2つの垂直期間において、サブ画素SPixに対する画素信号の書込み動作を行わないようにすることができ、上記実施の形態と同様に、画質の低下を抑えることができる。

【0094】

<2.第2の実施の形態>

次に、第2の実施の形態に係る表示装置2について説明する。本実施の形態は、映像信号Vdispに基づいて、反転動作期間PA,PBの長さを変更することができるものである。なお、上記第1の実施の形態に係る表示装置1と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

【0095】

図17は、本実施の形態における表示装置2の一構成例を表すものである。表示装置2は、反転信号生成部17を備えている。反転信号生成部17は、VRAM12に記憶されたフィールド画像に基づいて、長周期反転信号INVの反転間隔を変更するものである。

【0096】

図18は、表示装置2における動作の流れ図を表すものである。表示装置2では、画像が変化しないときには、長周期反転信号INVの反転間隔を所定の最小時間に設定し、表示する画像が変化するときには、その反転間隔を長く設定する。長周期反転信号INVの反転間隔は、垂直期間の時間を単位とした変数Pで設定される。そして、長周期反転信号INVが反転した後、変数nを垂直期間ごとに0から順にインクリメントしていき、変数nが変数Pと等しくなったときに、長周期反転信号INVを反転する。以下に、その詳細を説明する。

【0097】

まず、制御部11が、供給された映像信号Vdispに含まれるフィールド画像をVRAM12に書き込む(ステップS1)。

【0098】

次に、制御部11は、VRAM12に書き込まれたフィールド画像が第1フィールド画像であるかどうかを確認する(ステップS2)。そのフィールド画像が第1フィールド画像である場合にはステップS3に進み、第1フィールド画像でない場合には、ステップS7に進む。

【0099】

ステップS2において、VRAM12に書き込まれたフィールド画像が第1フィールド画像である場合には、反転信号生成部17は、VRAM12に記憶されている第1フィールド画像に基づいて動き検出を行う(ステップS3)。動き検出は、例えばオプティカルフロー計算により行うことが可能である。オプティカルフローの計算アルゴリズムとしては、例えば、ホーン−シャンク法が適用可能である。このホーンシャンク法については、例えば、“Berthold K.P. Horn and Brian G. Schunck Determining Optical Flow, Artificial Intelligence, Vol. 17, pp.185-203, Aug. 1981”に記載がある。

【0100】

次に、反転信号生成部17は、ステップS3の動き検出の結果に基づいて、フィールド画像が変化しているかどうかを検出する(ステップS4)。ステップS4において、フィールド画像の変化が検出された場合には、反転信号生成部17は、変数Pをインクリメントする(ステップS5)。また、ステップS4において、フィールド画像の変化が検出されなかった場合には、反転信号生成部17は、変数Pを4096に設定する(ステップS6)。

【0101】

次に、反転信号生成部17は、変数nが変数Pよりも小さいかどうかを確認する(ステップS7)。変数nが変数Pよりも小さい場合にはステップS10に進み、変数nが変数P以上である場合にはステップS8に進む。

【0102】

ステップS7において、変数nが変数P以上である場合には、反転信号生成部17は、変数nを0に設定(変数nをリセット)し(ステップS8)、長周期反転信号INVを反転する(ステップS9)。

【0103】

次に、反転信号生成部17は、変数nをインクリメントする(ステップS10)。

【0104】

次に、表示装置2は、VRAM12に記憶されたフィールド画像に基づいて、表示を行う(ステップS11)。

【0105】

そして、またステップS1に戻り、表示装置2は、以上の動作を繰り返す。

【0106】

表示装置2では、フィールド画像に対して動き検出を行い、そのフィールド画像の変化の有無に基づいて、表示部20がそのフィールド画像を表示した際の焼き付きが生じるおそれを判断する。そして、そのフィールド画像の表示により焼き付きが生じるおそれがあると判断した場合には、変数Pを小さく設定することにより焼き付きが生じにくくなるようにし、そのフィールド画像の表示により焼き付きが生じるおそれが低いと判断された場合には、変数Pを大きい値に設定して、画質の低下を抑えるようにしている。

【0107】

具体的には、反転信号生成部17は、フィールド画像の変化が検出されなかった場合に、変数Pを4096に設定する(ステップS6)。すなわち、この場合、反転信号生成部17は、表示部20が、変化しないフィールド画像を表示するため、表示部20において焼き付きが生じるおそれがあると判断し、長周期反転信号INVの反転間隔に対応する変数Pを最小値(この例では4096)に設定する。なお、このときの周期反転信号INVの反転間隔は、例えば、60[Hz]周期でフィールド画像を表示した場合には、68.2[sec](=4096/60[Hz])である。このように、表示装置2は、フィールド画像が変化しないときには、変数Pを最小値に設定することにより、反転動作期間PAと反転動作期間PBとが高い頻度で切り換える。これにより、表示装置2では、表示部20において焼き付きが生じるおそれを低減することができる。

【0108】

また、反転信号生成部17は、フィールド画像の変化が検出された場合には、変数Pをインクリメントする(ステップS5)。すなわち、この場合、反転信号生成部17は、表示部20が、変化するフィールド画像を表示するため、表示部20において焼き付きが生じるおそれは低いと判断し、長周期反転信号INVの反転間隔に対応する変数Pをインクリメントする。このように、表示装置2は、フィールド画像が変化するときには、変数Pを大きい値に設定することにより、反転動作期間PAと反転動作期間PBとの切り替わり頻度を低くする。これにより、表示装置2では、仮に、長周期反転信号INVが反転する際に表示画像が若干乱れる場合でも、その乱れた画像を表示する機会が減少するので、画質の低下を抑えることができる。

【0109】

また、表示装置2は、VRAM12に書き込まれたフィールド画像が第1フィールド画像Fi1である場合においてのみ動き検出を行う(ステップS2〜S3)。これにより、ステップS3,S4において、より高い精度で動き検出を行うことができる。すなわち、例えば、第1フィールド画像Fi1および第2フィールド画像Fi2の両方に基づいて動き検出を行う場合には、ステップS3の動き検出において、第1フィールド画像Fi1と第2フィールド画像Fi2との差に起因する動きも検出されるおそれがある。一方、第1フィールド画像Fi1のみに基づいて動き検出を行う場合には、この誤検出のおそれを低減することができるため、より高い精度でフィールド画像の変化を検出することができる。なお、この例では、VRAM12に書き込まれたフィールド画像が第1フィールド画像Fi1である場合においてのみ動き検出を行うようにしたが、これに限定されるものではなく、VRAM12に書き込まれたフィールド画像が第2フィールド画像Fi2である場合においてのみ動き検出を行うようにしてもよい。

【0110】

以上のように本実施の形態では、フィールド画像の動き検出結果に基づいて反転動作期間PA,PBの長さを変更するようにしたので、焼き付きの低減を実現するとともに、画質の低下を抑えることができる。

【0111】

また、本実施の形態では、フィールド画像の変化が検出されなかった場合に、長周期反転信号の反転間隔を所定の最小値に設定し、反転動作期間PAと反転動作期間PBとが高い頻度で切り換わるようにしたので、表示部における焼き付きの低減を実現することができる。

【0112】

また、本実施の形態では、フィールド画像の変化が検出された場合に、長周期反転信号INVの反転間隔が広くなるように設定し、反転動作期間PAと反転動作期間PBとの切り替わり頻度が低くなるようにしたので、仮に、長周期反転信号が反転する際に表示画像が若干乱れる場合でも、画質の低下を抑えることができる。

【0113】

その他の効果は、上記第1の実施の形態の場合と同様である。

【0114】

[変形例2−1]

上記実施の形態では、フィールド画像の変化の有無に基づいて、焼き付きが生じるおそれを判断するようにしたが、これに限定されるものではなく、例えば、フィールド画像全体における、画像が変化する領域の占める割合がある所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよいし、フィールド画像の各画素における画素情報の変化量が所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよい。

【0115】

[その他の変形例]

上記第2の実施の形態においても、上記第1の実施の形態の変形例1−1に示したように、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixのTFT素子Trに加えて、スイッチ23(1)〜23(M)をオフ状態にしてもよいし、上記第1の実施の形態の変形例1−2に示したように、反転制御部30において、複数の垂直期間に対応する時間だけ遅延させてもよい。

【0116】

<3.第3の実施の形態>

次に、第3の実施の形態に係る表示装置3について説明する。本実施の形態は、表示装置2において、OSD(On Screen Display)画像を表示する場合には、動き検出を行わないようにしたものである。なお、上記第2の実施の形態に係る表示装置2と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

【0117】

図19は、本実施の形態に係る表示装置3を表すものである。表示装置3は、OSD生成部18と、反転信号生成部19とを備えている。

【0118】

OSD生成部18は、OSD画像を生成するものである。このOSD生成部18で生成されたOSD画像は、VRAM12においてフィールド画像に重畳され、このOSD画像が重畳されたフィールド画像が、表示部20に表示されるようになっている。また、OSD生成部18は、OSD画像をフィールド画像に重畳するかどうかを示すOSDフラグ信号Fosdを生成する。

【0119】

反転信号生成部19は、VRAM12に記憶されたフィールド画像、およびOSDフラグ信号Fosdに基づいて、動き検出を行い、長周期反転信号INVの反転間隔を変更するものである。

【0120】

図20は、表示装置3における動作の流れ図を表すものである。なお、上記第2の実施の形態に係る表示装置2の流れ図(図18)と同じステップについては説明を省略する。

【0121】

ステップS2において、VRAM12に書き込まれたフィールド画像が第1フィールド画像である場合には、反転信号生成部19は、OSD生成部18から供給されるOSDフラグ信号Fosdがtrueであるか否かを検出する(ステップS21)。OSDフラグ信号Fosdがtrueである場合にはステップS6に進み、OSDフラグ信号Fosdがtrueでない場合にはステップS3に進む。

【0122】

また、ステップS10の次に、OSD生成部18は、生成したOSD画像をVRAM12に書き込む(ステップS22)。これにより、VRAM12では、記憶されたフィールド画像にOSD画像が重畳される。

【0123】

表示装置3では、OSDフラグ信号Fosdに基づいて、動き検出を行うかどうかを判断している。一般に、OSD画像は静止画であるため、表示部20がそのOSD画像を表示した場合には、表示部20において焼き付きが生じるおそれがある。よって、反転信号生成部19は、OSDフラグ信号Fosdがtrueである場合には、動き検出を行うまでもなく、表示部20において焼き付きが生じるおそれがあると判断し、長周期反転信号INVの反転間隔に対応する変数Pを最小値(この例では4096)に設定する。これにより、上記第2の実施の形態等と同様に、焼き付きが生じるおそれを低減することができる。

【0124】

以上のように本実施の形態では、OSDフラグ信号Fosdがtrueである場合には、動き検出を行わないようにしたので、回路動作の負荷を軽減することができる。その他の効果は、上記第1の実施の形態の場合と同様である。

【0125】

[変形例3−1]

上記実施の形態では、OSDフラグ信号Fosdがtrueであるか否かに基づいて動き検出を行うようにしたが、これに限定されるものではなく、例えば、OSDフラグ信号Fosdの変化に基づいて、動き検出を行うようにしてもよい。以下に、その詳細を説明する。

【0126】

図21は、本変形例に係る表示装置3Bにおける動作の流れ図を表すものである。なお、上記実施の形態に係る表示装置3の流れ図(図20)と同じステップについては説明を省略する。

【0127】

ステップS2において、VRAM12に書き込まれたフィールド画像が第1フィールド画像である場合には、本変形例に係る反転信号生成部19Bは、OSD生成部18から供給されるOSDフラグ信号Fosdが変化したかどうか否かを検出する(ステップS31)。OSDフラグ信号Fosdが変化した場合にはステップS32に進み、OSDフラグ信号Fosdが変化しなかった場合にはステップS3に進む。

【0128】

ステップS31において、OSDフラグ信号Fosdが変化したと検出された場合には、反転信号生成部19Bは、変数nを0に設定(変数nをリセット)し(ステップS32)、長周期反転信号INVを反転する(ステップS33)。そしてフローはステップS6に進む。

【0129】

このように、表示装置3Bでは、OSDフラグ信号Fosdが変化したときに、長周期反転信号INVを反転させ、次の反転動作期間PA,PBを開始するようにしたので、表示部20において焼き付きが生じるおそれを低減することができる。具体的には、例えば、OSDフラグ信号FosdがFalseからTrueに変化した後では、OSD画像(静止画)により表示部20において焼き付きが生じるおそれがあるが、OSDフラグ信号FosdがFalseからTrueに変化するタイミングで長周期反転信号INVを反転させるとともに、変数Pを最小値に設定することにより(ステップS6)、そのOSD画像が表示される期間における焼き付きが生じるおそれを低減することができる。また、例えば、OSDフラグ信号FosdがTrueからFalseに変化する際にも、長周期反転信号INVを反転させるとともに、変数Pを最小値に設定することにより(ステップS6)、OSD画像が表示されていた期間における状態をリセットすることができ、焼き付きが生じるおそれを低減することができる。

【0130】

なお、この例では、OSDフラグ信号Fosdが変化したときに長周期反転信号INVを反転させるようにしたが、これに限定されるものではなく、例えば、OSDフラグ信号FosdがFalseからTrueに変化したときにのみ長周期反転信号INVを反転させるようにしてもよい。

【0131】

[その他の変形例]

上記第3の実施の形態においても、上記第2の実施の形態の変形例2−1に示したように、例えば、フィールド画像全体における、フィールド画像内における画像が変化する領域の占める割合がある所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよいし、フィールド画像の各画素における画素情報の変化量が所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよい。

【0132】

以上、いくつかの実施の形態および変形例を挙げて本技術を説明したが、本技術はこれらの実施の形態等には限定されず、種々の変形が可能である。

【0133】

例えば、第2、第3の実施の形態においても、上記第1の実施の形態の変形例1−1に示したように、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixのTFT素子Trに加えて、スイッチ23(1)〜23(M)をオフ状態にしてもよいし、上記第1の実施の形態の変形例1−2に示したように、反転制御部30において、複数の垂直期間に対応する時間だけ遅延させてもよい。

【0134】

また、例えば、上記実施の形態等では、水平走査部を設け、1H期間において、水平方向に走査することにより、画素Pixに画素信号Vpix2を書き込むようにしたが、これに限定されるものではなく、これに代えて、例えば、この1H期間において、その選択された水平ラインに係る複数の画素Pixに対して同時に画素信号Vpix2を書き込むようにしてもよい。

【0135】

なお、本技術は以下のような構成とすることができる。

【0136】

(1)交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成し、表示部に供給する画素信号生成部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置の駆動回路。

【0137】

(2)前記画素信号生成部は、前記第1の期間および前記第2の期間のそれぞれにおける先頭タイミングでは、画素信号を反転しない

前記(1)に記載の表示装置の駆動回路。

【0138】

(3)前記第1の期間と前記第2の期間とで異なる論理レベルを有する論理信号を生成する論理信号生成部を備え、

前記画素信号生成部は、前記論理信号に基づいて前記画素信号の反転動作を制御する

前記(1)または(2)のいずれかに記載の表示装置の駆動回路。

【0139】

(4)垂直同期信号を生成するタイミング制御部を備え、

前記書込制御部は、前記論理信号と前記垂直同期信号とに基づいて、前記先頭期間を設定する

前記(1)から(3)のいずれかに記載の表示装置の駆動回路。

【0140】

(5)前記書込制御部は、

前記垂直同期信号に同期して前記論理信号をサンプリングするフリップフロップ回路と、

前記フリップフロップ回路の出力信号と前記論理信号との排他的論理和を求める排他的論理和回路と

を有し、

前記排他的論理和回路の出力信号に基づいて前記先頭期間を設定する

前記(4)に記載の表示装置の駆動回路。

【0141】

(6)前記表示部は、複数の画素のそれぞれにおいて、前記画素信号を伝える画素スイッチを有し、

前記書込制御部は、前記先頭期間において、前記画素スイッチをオフ状態にする

前記(1)から(5)のいずれかに記載の表示装置の駆動回路。

【0142】

(7)前記表示部は、

前記複数の画素に画素信号を供給するための画素信号線と、

前記画素信号生成部から供給された画素信号を前記画素信号線に供給するための信号線スイッチと

を有し、

前記書込制御部は、前記先頭期間において、前記信号線スイッチをもオフ状態にする

前記(6)に記載の表示装置の駆動回路。

【0143】

(8)前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記論理信号生成部は、前記画像信号に基づいて画像の変化を検出し、その検出結果に基づいて、前記第1の期間の長さおよび前記第2の期間の長さを設定する

前記(3)に記載の表示装置の駆動回路。

【0144】

(9)前記論理信号生成部は、

画像の変化がない場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定し、

画像の変化がある場合には、前記第1の期間の長さおよび前記第2の期間の長さを前記最小値より長く設定する

前記(8)に記載の表示装置の駆動回路。

【0145】

(10)OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルである場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定する

前記(8)に記載の表示装置の駆動回路。

【0146】

(11)OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルとディセーブルとの間で変化した場合において、前記論理信号の論理レベルを変更する

前記(8)に記載の表示装置の駆動回路。

【0147】

(12)前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記画像信号はインターレース信号であり、

前記表示部は、前記インターレース信号のフィールド画像の画素数と同じ数の画素を有し、各フレーム期間において、第1のフィールド画像および第2のフィールド画像を交互に表示する

前記(1)から(11)のいずれかに記載の表示装置の駆動回路。

【0148】

(13)前記先頭期間は、1つ分のフレーム期間である

前記(1)から(12)のいずれかに記載の表示装置の駆動回路。

【0149】

(14)交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成する画素信号生成部と、

前記画素信号に基づいて表示を行う表示部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置。

【0150】

(15)交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成して表示部に供給し、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する

表示装置の駆動方法。

【符号の説明】

【0151】

1,1B,2,3…表示装置、11…制御部、12…VRAM、13…RGBデコーダ部、14…反転部、15,17,19…反転信号生成部、16…タイミング制御部、18…OSD生成部、20…表示部、21…水平走査部、22,22(1)〜22(M)…論理積回路、23,23(1)〜23(M)…スイッチ、26…垂直走査部、27,27(1)〜27(N)…論理積回路、30,30B…反転制御部、31…EX−OR回路、32,32A,32B…D型フリップフロップ回路、33…EX−NOR回路、34,35…論理積回路、F…フレーム画像、Fi1…第1フィールド画像、Fi2…第2フィールド画像、Fosd…OSDフラグ信号、FRP,FRP2…反転制御信号、HCLK,Pix…画素、SPix…サブ画素、VCLK…クロック信号、HEN,HEN2…水平イネーブル信号、HST…水平同期信号、INV…長周期反転信号、L…ライン画像、LC…液晶素子、PA,PB…反転動作期間、PW1…第1フィールド表示期間、PW2…第2フィールド表示期間、R1〜R3…領域、SH1〜SHM,SV1〜SVN,φH1〜φHM,φV1〜φVN…走査信号、Tr…TFT素子、VCOM…共通電圧、VEN,VEN2…垂直イネーブル信号、Vdisp…映像信号、VN1,VN2…信号、Vp…画素電位、Vpix,VpixR,VpixG,VpixB,Vpix2,VpixR2,VpixG2,VpixB2…画素信号、VST…垂直同期信号。

【技術分野】

【0001】

本開示は、インターレース映像信号に基づいて表示を行う表示装置を駆動する駆動回路、およびその駆動回路を備えた表示装置、ならびにそのような表示装置の駆動方法に関する。

【背景技術】

【0002】

近年、表示装置においては、CRT(Cathode Ray Tube)表示装置から液晶表示装置への置き換えが進んでいる。液晶表示装置は、CRT表示装置に比べて、薄くできるため省スペースを実現しやすく、また、消費電力が低いためエコロジーの観点からもメリットがある。

【0003】

表示装置の分野では、しばしばインターレース映像信号が用いられる。インターレース映像信号では、各フレーム画像の画像情報は、そのフレーム画像を構成するライン画像を交互に分配して構成した2つのフィールド画像の画像情報に分けられている。CRT表示装置にこのインターレース映像信号が供給された場合には、CRT表示装置は、例えば、これらの2つのフィールド画像を、それぞれ対応する位置に交互に表示する。一方、液晶表示装置にインターレース映像信号が供給された場合には、液晶表示装置は、例えば、いわゆるIP変換によりインターレース映像信号をプログレッシブ映像信号に変換して元のフレーム画像を生成し、その生成されたフレーム画像に基づいて表示を行う。また、液晶表示装置には、インターレース映像信号の各フィールド画像と同じ画素数を有する表示部を備え、IP変換を行わずに各フィールド画像をそのまま時分割的に表示するものもある。このIP変換を行わない表示装置は、IP変換を行う表示装置に比べ、よりシンプルな構成で、インターレース映像信号に基づく表示を行うことができる。

【0004】

ところで、一般に、表示装置では、例えば同じ画像を長時間表示すると、その後に他の画像を表示しても、その長時間表示した画像が少し残って表示されてしまう、いわゆる「焼きつき」と呼ばれる現象が生じる。液晶表示装置においても、このような現象は生じるため、これに対する様々な対策が提案されている。例えば、特許文献1には、IP変換を行わない液晶表示装置において、フレームごとに画素信号を反転して駆動するとともに、所定期間ごとにその反転の方法を変更する液晶表示装置が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平8−191421号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、一般に、表示装置では高い画質が望まれており、IP変換を行わない液晶表示装置でもさらなる画質の改善が望まれている。

【0007】

本開示はかかる問題点に鑑みてなされたもので、その目的は、画質を高めることができる表示装置の駆動回路、表示装置、および表示装置の駆動方法を提供することにある。

【課題を解決するための手段】

【0008】

本開示の表示装置の駆動回路は、画素信号生成部と、書込制御部とを備えている。画素信号生成部は、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成し、表示部に供給するものである。書込制御部は、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御するものである。

【0009】

本開示の表示装置は、画素信号生成部と、表示部と、書込制御部とを備えている。画素信号生成部は、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成するものである。表示部は、画素信号に基づいて表示を行うものである。書込制御部は、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御するものである。

【0010】

本開示の表示装置の駆動方法は、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成して表示部に供給し、第1の期間および第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、表示部に対する画素信号の書込みを行うように制御するものである。

【0011】

本開示の表示装置の駆動回路、表示装置、および表示装置の駆動方法では、交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号が、表示部に供給される。その際、第1の期間および第2の期間のそれぞれにおける先頭期間以外の期間において、画素信号が表示部に書き込まれるようになっている。

【発明の効果】

【0012】

本開示の表示装置の駆動回路、表示装置、および表示装置の駆動方法によれば、先頭期間以外の期間において、画素信号が表示部に書き込まれるようにしたので、画質を高めることができる。

【図面の簡単な説明】

【0013】

【図1】本開示の第1の実施の形態に係る表示装置の一構成例を表すブロック図である。

【図2】インターレース画像を説明するための説明図である。

【図3】図1に示した反転制御部の一構成例を表す回路図である。

【図4】第1フィールド画像および第2フィールド画像に基づく表示を説明するための説明図である。

【図5】図1に示した表示部の一構成例を表す説明図である。

【図6】図1に示した表示装置の一動作例を表すタイミング波形図である。

【図7】図1に示した表示装置の一動作例を表す他のタイミング波形図である。

【図8】図1に示した反転信号生成部および反転信号制御部の一動作例を表すタイミング波形図である。

【図9】インターレース画像の一例を説明するための説明図である。

【図10】図10に示した画像の表示を説明するための説明図である。

【図11】図1に示した表示装置の一動作例を表す他のタイミング波形図である。

【図12】比較例に係る表示装置の一構成例を表すブロック図である。

【図13】比較例に係る表示装置の一動作例を表すタイミング波形図である。

【図14】第1の実施の形態の変形例に係る表示装置の一構成例を表すブロック図である。

【図15】図14に示した反転制御部の一構成例を表す回路図である。

【図16】第1の実施の形態の他の変形例に係る反転制御部の一構成例を表す回路図である。

【図17】第2の実施の形態に係る表示装置の一構成例を表すブロック図である。

【図18】図17に示した表示装置の一動作例を表す流れ図である。

【図19】第3の実施の形態に係る表示装置の一構成例を表すブロック図である。

【図20】図19に示した表示装置の一動作例を表す流れ図である。

【図21】第3の実施の形態の変形例に係る表示装置の一動作例を表す流れ図である。

【発明を実施するための形態】

【0014】

以下、本開示の実施の形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.第1の実施の形態

2.第2の実施の形態

3.第3の実施の形態

【0015】

<1.第1の実施の形態>

[構成例]

(全体構成例)

図1は、第1の実施の形態に係る表示装置の一構成例を表すものである。表示装置1は、供給されたインターレース映像信号に基づいて、IP変換を行わずに表示を行うものである。なお、本開示の実施の形態に係る表示装置の駆動回路および表示装置の駆動方法は、本実施の形態により具現化されるので、併せて説明する。

【0016】

表示装置1は、制御部11と、タイミング制御部16と、反転信号生成部15と、反転制御部30と、VRAM(Video RAM)12と、RGBデコーダ部13と、反転部14と、表示部20とを備えている。

【0017】

制御部11は、供給された映像信号Vdispに基づいて、VRAM12、RGBデコーダ部13、反転信号生成部15、およびタイミング制御部16に対してそれぞれ制御信号を供給し、これらがお互いに同期して動作するように制御する回路である。

【0018】

映像信号Vdispは、インターレース映像信号であり、複数(ここでは2つ)のフィールド画像の画像情報が交互に表示装置1に供給されるようになっている。

【0019】

図2は、インターレース映像信号の一例を模式的に表すものであり、(A)はフレーム画像Fを示し、(B)は第1フィールド画像Fi1を示し、(C)は第2フィールド画像Fi2を示す。

【0020】

フレーム画像Fは、図2(A)に示したように、複数のライン画像Lから構成されている。フレーム画像Fは、例えば、映像信号VdispがSD(Standard Definition)信号の場合には、水平方向に720画素、垂直方向に480画素の画素情報を有している。また、フレーム画像Fは、例えば映像信号VdispがHD(High Definition)信号の場合には、水平方向に1920画素、垂直方向に1080画素の画素情報を有している。

【0021】

第1フィールド画像Fi1および第2フィールド画像Fi2(図2(B),(C))は、フレーム画像F(図2(A))を構成するライン画像Lを交互に分配して構成したものである。各フィールド画像(第1フィールド画像Fi1および第2フィールド画像Fi2)は、例えば映像信号VdispがSD信号の場合には、水平方向に720画素、垂直方向に240画素の画素情報を有し、例えば映像信号VdispがHD信号の場合には、水平方向に1920画素、垂直方向に540画素の画素情報を有している。

【0022】

制御部11は、映像信号Vdispにより供給された各フィールド画像の画像情報をVRAM12に対して書込むとともに、表示を行う際には、VRAM12から画像データを読み出す。また、制御部11は、RGBデコーダ部13に対して、VRAM12から読み出した画像情報と制御信号を供給し、反転信号生成部15およびタイミング制御部16に対して制御信号を供給する。

【0023】

タイミング制御部16は、制御部11からの制御信号に基づいて、複数の制御信号を生成し、表示部20および反転制御部30に供給するものである。具体的には、タイミング制御部16は、水平同期信号HST、クロック信号HCLK、水平イネーブル信号HEN、垂直同期信号VST、およびクロック信号VCLKを生成し、表示部20に対して供給する。また、タイミング制御部16は、反転制御信号FRPおよび垂直イネーブル信号VENを生成し、垂直同期信号VSTとともに、反転制御部30に対して供給する。

【0024】

ここで、水平同期信号HSTは、後述するように、1水平期間(1H)ごとにパルス波形を有する信号であり、垂直同期信号VSTは、1垂直期間(1V)ごとにパルス波形を有する信号である。また、水平イネーブル信号HENおよび垂直イネーブル信号VENは、後述するように、サブ画素SPixへの画素信号Vpix2の書込みを制御するためのものである。反転制御信号FRPは、1垂直期間ごとに反転する信号である。

【0025】

反転信号生成部15は、制御部11から供給される制御信号に基づいて、所定の複数の垂直期間ごとに、論理が反転する長周期反転信号INVを生成するものである。長周期反転信号INVは、例えば、約1分ごとに論理反転するものである。

【0026】

反転制御部30は、反転信号生成部15から供給される長周期反転信号INVと、タイミング制御部16から供給される反転制御信号FRP、垂直同期信号VST、および垂直イネーブル信号VENに基づいて、反転制御信号FRP2および垂直イネーブル信号VEN2を生成するものである。

【0027】

図3は、反転制御部30の一構成例を表すものである。反転制御部30は、EX−OR回路31と、D型フリップフロップ回路32と、EX−NOR回路33と、論理積回路34とを備えている。EX−OR回路31は、長周期反転信号INVと反転制御信号FRPとの排他的論理和を求め、反転制御信号FRP2として出力するものである。D型フリップフロップ回路32は、そのデータ入力端子に長周期反転信号INVが供給されるとともに、そのクロック入力端子に垂直同期信号VSTが供給され、垂直同期信号VSTに同期して長周期反転信号INVをサンプリングし、その結果を信号VN1として出力するものである。EX−NOR回路33は、長周期反転信号INVと、D型フリップフロップ回路32の出力信号(信号VN1)との排他的論理和の反転を求め、信号VN2として出力するものである。論理積回路34は、EX−NOR回路33の出力信号(信号VN2)と、垂直イネーブル信号VENの論理積を求め、垂直イネーブル信号VEN2として出力するものである。

【0028】

この構成により、反転制御部30は、長周期反転信号INVが低レベルの場合には、反転制御信号FRPと同じ信号を反転制御信号FRP2として出力し、長周期反転信号INVが高レベルの場合には、反転制御信号FRPを反転した信号を反転制御信号FRP2として出力する。また、反転制御部30は、長周期反転信号INVが変化した後の最初の垂直期間において低レベルになり、その他の期間では垂直イネーブル信号VENと同じ信号となる垂直イネーブル信号VEN2を生成するようになっている。

【0029】

VRAM12は、画像情報を記憶する記憶部であり、制御部11から供給されたフィールド画像(第1フィールド画像Fi1および第2フィールド画像Fi2)の画像情報を記憶し、その画像情報を制御部11からの要求に応じて出力するものである。

【0030】

RGBデコーダ部13は、制御部11から供給された画像情報および制御信号に基づいて、赤色(R)、緑色(G)、青色(B)の各成分のアナログ信号である画素信号VpixR,VpixG,VpixBを生成するものである。なお、以下の説明では、説明の便宜上、画素信号VpixR,VpixG,VpixBのうちの任意の一つを示すものとして、画素信号Vpixを適宜用いる。

【0031】

なお、例えば、制御部11と、反転信号生成部15と、RGBデコーダ部13は、例えばマイクロコントローラ(MCU)により構成してもよい。

【0032】

反転部14は、反転制御部30から供給された反転制御信号FRP2に基づいて、RGBデコーダ部13から供給された画素信号VpixR,VpixG,VpixBに対する反転動作を制御し、画素信号VpixR2,VpixG2,VpixB2として出力するものである。具体的には、後述するように、反転部14は、反転制御信号FRP2が高レベルの場合には、画素信号VpixR,VpixG,VpixBをそのまま画素信号VpixR2,VpixG2,VpixB2として出力し、反転制御信号FRP2が低レベルの場合には、画素信号VpixR,VpixG,VpixBを反転して画素信号VpixR2,VpixG2,VpixB2として出力するようになっている。なお、以下の説明では、説明の便宜上、画素信号VpixR2,VpixG2,VpixB2のうちの任意の一つを示すものとして、画素信号Vpix2を適宜用いる。

【0033】

表示部20は、液晶表示部であり、反転部14から供給された画素信号VpixR2,VpixG2,VpixB2、および反転制御部30、タイミング制御部16から供給される様々な制御信号に基づいて表示を行うものである。この例では、表示部20は、ノーマリホワイト型のものである。ただし、表示部20は、これに限定されるものではなく、これに代えて、ノーマリブラック型であってもよい。表示部20は、各フィールド画像の画素数と同じ数の画素を有している。すなわち、表示部20では、フレーム画像Fと比べて、垂直方向の画素数が半分になっている。

【0034】

図4は、表示部20における画像の表示を表すものであり、(A)は第1フィールド画像Fi1を表示した場合を示し、(B)は第2フィールド画像Fi2を表示した場合を示す。この図4は、図2(B),(C)と対応している。すなわち、第1フィールド画像Fi1を表示する際には、図2(B)の画像が図4(A)のように表示され、第2フィールド画像Fi2を表示する際には、図2(C)の画像が図4(B)のように表示される。このように、表示装置1では、IP変換を行うことなく、インターレース映像信号に含まれるフィールド画像が交互に表示されるようになっている。

【0035】

図5は、表示部20の一構成例を表すものである。表示部20は、水平走査部21と、M個の論理積回路22(論理積回路22(1)〜22(M))と、M個のスイッチ23(スイッチ23(1)〜23(M))と、垂直走査部26と、N個の論理積回路27(論理積回路27(1)〜27(N))と、マトリックス状に配置された画素Pixとを備えている。

【0036】

水平走査部21は、水平同期信号HSTおよびクロック信号HCLKに基づいて、マトリックス状に配置された画素Pixを水平方向に走査するものである。この水平走査部21は、例えば、シフトレジスタを用いて構成されており、そのデータ入力端子に水平同期信号HSTが供給され、クロック入力端子にクロック信号HCLKが供給される。この構成により、水平走査部21は、シフトレジスタの各段から、クロック信号HCLKに同期したパルス信号を、走査信号SH1〜SHMとして順次出力するようになっている。

【0037】

論理積回路22(1)〜22(M)のそれぞれは、水平走査部21から供給された走査信号SH1〜SHMのそれぞれと、水平イネーブル信号HENとの論理積を求め、走査信号φH1〜φHMとして出力する回路である。

【0038】

スイッチ23(1)〜23(M)は、それぞれ対応する論理積回路22(1)〜22(M)の出力信号(走査信号φH1〜φHM)に基づいて、オンオフするスイッチである。スイッチ23(1)〜23(M)は、例えば、薄膜トランジスタ(TFT;Thin Film Transistor)を用いたアナログスイッチなどにより形成されるものである。スイッチ23(1)〜23(M)の一端には反転部14から画素信号Vpix2が供給され、他端は画素信号線SGLを介して画素Pixと接続されている。具体的には、スイッチ23(1)には、赤色に係る画素信号VpixR2が供給され、スイッチ23(2)には、青色に係る画素信号VpixG2が供給され、スイッチ23(3)には、緑色に係る画素信号VpixB2が供給される。そして、スイッチがオン状態になると、これらの画素信号VpixR2,VpixG2,VpixB2は、画素信号線SGLを介して、画素Pixを構成する、RGBにそれぞれ対応する各サブ画素SPix(後述)に供給されるようになっている。

【0039】

垂直走査部26は、垂直同期信号VSTおよびクロック信号VCLKに基づいて、マトリックス状に配置された画素Pixの垂直方向に走査するものである。この垂直走査部26は、例えば、シフトレジスタを用いて構成されており、そのデータ入力端子に垂直同期信号VSTが供給され、クロック端子にクロック信号VCLKが供給される。この構成により、垂直走査部26は、シフトレジスタの各段から、クロック信号VCLKに同期したパルス信号を、走査信号SV1〜SVNとして順次出力するようになっている。

【0040】

論理積回路27(1)〜27(N)のそれぞれは、垂直走査部27から供給された走査信号SV1〜SVNのそれぞれと、垂直イネーブル信号VEN2との論理積を求め、走査信号φV1〜φVNとして出力する回路である。この論理積回路27(1)〜27(N)の出力端子は、走査信号線GCLを介して画素Pixと接続されている。

【0041】

画素Pixは、表示画像を構成する表示要素である。画素Pixは、3つのサブ画素SPixにより構成される。サブ画素SPixは、TFT素子Trおよび液晶素子LCを有している。TFT素子Trは、薄膜トランジスタ(TFT)により構成されるものであり、この例では、nチャネルのMOS(Metal Oxide Semiconductor)型のTFTで構成されている。TFT素子Trのソースは画素信号線SGLに接続され、ゲートは走査信号線GCLに接続され、ドレインは液晶素子LCの一端に接続されている。液晶素子LCは、一端がTFT素子Trのドレインに接続され、他端には、共通電圧VCOM(例えば0V)が印加されている。

【0042】

サブ画素SPixは、走査信号線GCLにより、表示部20において同じ行に配置された他のサブ画素SPixと互いに接続されている。また、サブ画素SPixは、画素信号線SGLにより、表示部20において同じ列に配置された他のサブ画素SPixと互いに接続されている。

【0043】

この構成により、表示部20では、垂直走査部26および論理積回路27(1)〜27(N)が走査信号線GCLを時分割的に線順次走査するように駆動することにより、1水平ラインが順次選択される。そして、水平走査部21および論理積回路22(1)〜22(M)が、順次走査により画素信号線SGLを選択し、反転部14が、画素信号Vpix2を、その選択された画素信号線SGLを介して、サブ画素SPixに供給する。各サブ画素SPixでは、TFT素子Trがオン状態のときに、画素信号Vpix2が液晶素子LCの一端に画素電位Vpとして書き込まれ、TFT素子Trがオフ状態になると、その液晶素子LCの一端が画素信号線SGLと電気的に切り離されてハイインピーダンス状態になり、その画素電位Vpが維持されるようになっている。

【0044】

また、水平イネーブル信号HEN、および垂直イネーブル信号VEN2は、サブ画素SPixへの画素信号Vpix2の書込みを制御する。具体的には、水平イネーブル信号HENおよび垂直イネーブル信号VEN2がともに高レベルである場合には、上述したような動作により、サブ画素SPixへの画素信号Vpix2の書込みが行われる。一方、水平イネーブル信号HENが高レベルであり、垂直イネーブル信号VEN2が低レベルである場合には、走査信号φV1〜φVNの全てが低レベルになるため、画素信号Vpix2は、画素信号線SGLに印加されるものの、サブ画素SPixに書き込まれることはない。さらに、水平イネーブル信号HENが低レベルである場合には、走査信号φH1〜φHMの全てが低レベルになるため、スイッチ23(1)〜23(M)の全てがオフ状態になり、画素信号Vpix2は、画素信号線SGLに印加されないようになっている。

【0045】

ここで、RGBデコーダ部13および反転部14は、本開示における「画素信号生成部」の一具体例に対応する。反転制御部30は、本開示における「書込制御部」の一具体例に対応する。長周期反転信号INVは、本開示における「論理信号」の一具体例に対応し、反転信号生成部15は、本開示における「論理信号生成部」の一具体例に対応する。TFT素子Trは、本開示における「画素スイッチ」の一具体例に対応する。スイッチ23(1)〜23(M)は、本開示における「信号線スイッチ」の一具体例に対応する。

【0046】

[動作および作用]

続いて、本実施の形態の表示装置1の動作および作用について説明する。

【0047】

(全体動作概要)

まず、図1を参照して、表示装置1の全体動作概要を説明する。制御部11は、供給された映像信号Vdispに基づいて、VRAM12、RGBデコーダ部13、反転信号生成部15、およびタイミング制御部16に対してそれぞれ制御信号を供給し、これらがお互いに同期して動作するように制御する。タイミング制御部16は、複数の制御信号を生成し、表示部20および反転制御部30に供給する。反転信号生成部15は、長周期反転信号INVを生成し、反転制御部30は、長周期反転信号INVなどに基づいて、反転制御信号FRP2および垂直イネーブル信号VEN2を生成する。RGBデコーダ部13は、画素信号VpixR,VpixG,VpixBを生成する。反転部14は、反転制御信号FRP2に基づいて画素信号VpixR,VpixG,VpixBに対する反転動作を制御し、画素信号VpixR2,VpixG2,VpixB2として出力する。表示部20は、画素信号VpixR2,VpixG2,VpixB2、垂直イネーブル信号VEN2などに基づいて表示を行う。

【0048】

(表示装置1の詳細動作)

次に、図6,7を参照して、表示装置1の詳細動作について説明する。

【0049】

図6は、表示装置1における表示動作のタイミング波形例を表すものであり、(A)は垂直同期信号VSTの波形を示し、(B)はクロック信号VCLKの波形を示し、(C)は垂直イネーブル信号VENの波形を示し、(D)は走査信号φV1〜φVNの波形を示し、(E)は反転制御信号FRP2の波形を示し、(F)は画素信号VpixR,VpixG,VpixBの波形を示し、(G)は画素信号VpixR2,VpixG2,VpixB2の波形を示す。なお、図示していないが、この図6では、長周期反転信号INVは、低レベルもしくは高レベルのいずれかであり、一定レベルである。

【0050】

図7は、1水平期間における表示装置1の表示動作の一例を表すものであり、(A)は水平同期信号HSTの波形を示し、(B)はクロック信号HCLKの波形を示し、(C)は水平イネーブル信号HENの波形を示し、(D)は走査信号φH1〜φHMの波形を示し、(E)は画素信号VpixR2,VpixG2,VpixB2の波形を示す。この例では、スイッチ23(1)〜23(N)は、対応する走査信号φH1〜φHMが高レベルのときにオン状態になるものとする。

【0051】

表示装置1では、第1フィールド画像Fi1および第2フィールド画像Fi2が、垂直期間(1V)ごとに交互に表示される。その際、画素信号VpixR2,VpixG2,VpixB2は、垂直期間ごとに反転する。この垂直期間の長さは、例えば、16.7[msec](=1/60[Hz])である。以下に、この動作を詳細に説明する。

【0052】

まず、タイミングt10付近において、タイミング制御部16は、垂直同期信号VSTとしてパルス信号を生成する(図6(A))。これにより、垂直期間(1V)が開始する。また、このタイミングt10において、タイミング制御部16は、クロック信号VCLKを低レベルから高レベルに変化させる(図6(B))。これにより、垂直走査部26のシフトレジスタでは、垂直同期信号VSTのパルス部分(高レベル部分)がサンプリングされ、走査信号φV1が低レベルから高レベルに変化する(図6(D))。よって、表示部20では、1行目の走査信号線GCLが高レベルになり、表示書込動作の対象となる1水平ラインが選択される。

【0053】

タイミングt10〜t20からの1垂直期間(1V)では、RGBデコーダ部13は、第1フィールド画像Fi1に係る画素信号VpixR,VpixG,VpixBを反転部14に対して供給する。そして、タイミングt10において、反転制御部30は、反転制御信号FRP2を低レベルから高レベルに変化させる(図6(E))。これに伴い、反転部14は、RGBデコーダ部13から供給された第1フィールド画像Fi1に係る画素信号VpixR,VpixG,VpixBを、そのまま、画素信号VpixR2,VpixG2,VpixB2として出力する(図6(F),(G))。

【0054】

そして、このタイミングt10〜t11の期間(1水平期間(1H))において、図7に示したように、画素信号Vpix2が、選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0055】

具体的には、図7において、タイミングt0付近において、タイミング制御部16が、水平同期信号HSTとしてパルス信号を生成する(図7(A))。そして、このタイミングt0において、タイミング制御部16は、クロック信号HCLKを高レベルから低レベルに変化させ(図7(B))、これにより、水平走査部21のシフトレジスタでは、水平同期信号HSTのパルス部分(高レベル部分)がサンプリングされ、走査信号SH1が低レベルから高レベルに変化する(図6(D))。次に、タイミングt1〜t2の期間において、タイミング制御部16は、水平イネーブル信号HENを高レベルにする(図7(C))。これにより、この期間において、スイッチ23(1)がオン状態になり、画素信号VpixR2が、1列目の画素信号線SGLに印加され、選択された1水平ラインに係るサブ画素SPixに供給される。次にタイミングt3において、タイミング制御部16は、クロック信号HCLKを高レベルから低レベルに変化させ(図7(B))、走査信号SH1が高レベルから低レベルに変化するとともに、走査信号SH2が低レベルから高レベルに変化する(図7(D))。次に、タイミングt4〜t5の期間において、タイミング制御部16は、水平イネーブル信号HENを高レベルにする(図7(C))。これにより、この期間において、スイッチ23(2)がオン状態になり、画素信号VpixG2が、2列目の画素信号線SGLに印加され、選択された1水平ラインに係るサブ画素SPixに供給される。このようにして、タイミングt0〜t9までの1水平期間(1H)において、選択された1水平ライン内の全てのサブ画素SPixに対して、画素信号Vpix2が供給され、書込みが行われる。

【0056】

次に、タイミングt11において、タイミング制御部16は、クロック信号VCLKを高レベルから低レベルに変化させる(図6(B))。これにより、垂直走査部26のシフトレジスタでは、データが転送され、走査信号φV1が高レベルから低レベルに変化するとともに、走査信号φV2が低レベルから高レベルに変化する(図6(D))。これにより、表示部20において、2行目の走査信号線GCLが高レベルになることにより、表示書込動作の対象となる1水平ラインが選択され、タイミングt11〜t12の期間において、画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0057】

これ以降、タイミングt20まで、同様の動作が繰り返し行われることにより、表示部20の全面にわたり、表示書込動作の対象となる1水平ラインが順次選択され、第1フィールド画像Fi1に係る画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに順次書き込まれる。これにより、表示部20の全面において、第1フィールド画像Fi1の表示が行われる。

【0058】

次に、タイミングt20付近において、タイミング制御部16は、垂直同期信号VSTとしてパルス信号を生成する(図6(A))。これにより、今までの垂直期間(1V)が終了するとともに、新たな垂直期間が開始する。また、このタイミングt20において、タイミング制御部16は、クロック信号VCLKを低レベルから高レベルに変化させる(図6(B))。これにより、垂直走査部26のシフトレジスタでは、垂直同期信号VSTのパルス部分(高レベル部分)がサンプリングされ、走査信号φV1が低レベルから高レベルに変化する(図6(D))。これにより、表示部20において、1行目の走査信号線GCLが高レベルになり、表示書込動作の対象となる1水平ラインが選択される。

【0059】

タイミングt20からの1垂直期間(1V)では、RGBデコーダ部13は、第2フィールド画像Fi2に係る画素信号VpixR,VpixG,VpixBを反転部14に対して供給する。そして、タイミングt20において、反転制御部30は、反転制御信号FRP2を高レベルから低レベルに変化させる(図6(E))。これに伴い、反転部14は、RGBデコーダ部13から供給された第2フィールド画像Fi2に係る画素信号VpixR,VpixG,VpixBを反転して、画素信号VpixR2,VpixG2,VpixB2として出力する(図6(F),(G))。そして、タイミングt20〜t21の期間において、画素信号Vpix2が、選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0060】

次に、タイミングt21において、タイミング制御部16は、クロック信号VCLKを高レベルから低レベルに変化させる(図6(B))。これにより、表示部20において、2行目の走査信号線GCLが高レベルになることにより、表示書込動作の対象となる1水平ラインが選択され、タイミングt21〜t22の期間において、画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに書き込まれる。

【0061】

これ以降、タイミングt20まで、同様の動作が繰り返し行われることにより、表示部20の全面にわたり、表示書込動作の対象となる1水平ラインが順次選択され、第2フィールド画像Fi2に係る画素信号Vpix2が、この選択された1水平ラインに係る各サブ画素SPixに順次書き込まれる。これにより、表示部20の全面において、第2フィールド画像Fi2の表示が行われる。

【0062】

(反転信号生成部15および反転制御部30の詳細動作)

次に、反転信号生成部15および反転制御部30の詳細動作を説明する。

【0063】

図8は、反転信号生成部15および反転制御部30の動作の一例を表すものであり、(A)は長周期反転信号INVの波形を示し、(B)は反転制御信号FRPの波形を示し、(C)は反転制御信号FRP2の波形を示し、(D)は垂直同期信号VSTの波形を示し、(E)は信号VN1(D型フリップフロップ回路32の出力信号)の波形を示し、(F)は信号VN2(EX−NOR回路33の出力信号)の波形を示し、(G)は垂直イネーブル信号VENの波形を示し、(H)は垂直イネーブル信号VEN2の波形を示す。

【0064】

表示装置1では、長周期反転信号INVに基づき2つの反転動作期間PA,PB(第1の期間および第2の期間)が設定される。これらの2つの反転動作期間PA,PBでは、反転部14は、互いに異なる方法で画素信号の反転動作を行う。そして、各反転動作期間PA,PBにおいて、表示部20は、その反転部14から出力された画素信号Vpix2に基づいて、第1フィールド画像Fi1と第2フィールド画像Fi2を垂直期間(1V)ごとに交互に表示する。以下に、この動作を詳細に説明する。

【0065】

反転信号生成部15は、タイミングt30〜t40の期間において、長周期反転信号INVを低レベルにする(図8(A))。これにより、反転制御部30のEX−OR回路31は、この期間(反転動作期間PA)において、タイミング制御部16から供給された反転制御信号FRP(図8(B))と同じ信号を反転制御信号FRP2として出力する(図8(C))。また、反転信号生成部15は、タイミングt40〜t50の期間において、長周期反転信号INVを高レベルにする(図8(A))。これにより、反転制御部30のEX−OR回路31は、この期間(反転動作期間PB)において、タイミング制御部16から供給された反転制御信号FRP(図8(B))を反転した信号を反転制御信号FRP2として出力する(図8(C))。結果として、反転動作期間PAと反転動作期間PBとの境界を挟む隣接する垂直期間では、反転制御信号FRP2のレベルは同じものとなる。

【0066】

反転部14は、このようにして生成された反転制御信号FRP2に基づいて、RGBデコーダ13から供給された画素信号VpixR,VpixG,VpixBを反転制御し、画素信号VpixR2,VpixG2,VpixB2として出力する。具体的には、反転部14は、反転制御信号FRP2が高レベルの場合には、画素信号VpixR,VpixG,VpixBをそのまま画素信号VpixR2,VpixG2,VpixB2として出力し、反転制御信号FRP2が低レベルの場合には、画素信号VpixR,VpixG,VpixBを反転して画素信号VpixR2,VpixG2,VpixB2として出力する。すなわち、反転動作期間PAと反転動作期間PBとでは、反転動作の方法が互いに異なっている。

【0067】

また、反転制御部30のD型フリップフロップ回路32は、反転動作期間PA,PBの両方の期間において、垂直同期信号VST(図8(D))の立ち上がりに同期したタイミングで長周期反転信号INV(図8(A))をサンプリングする。このとき、図示していないが、タイミングt30付近において、垂直同期信号VSTが立ち上がった後に、長周期反転信号INVが立ち下がるようになっており、タイミングt40付近において、垂直同期信号VSTが立ち上がった後に、長周期反転信号INVが立ち上がるようになっている。これにより、D型フリップフロップ回路32は、長周期反転信号INVを1垂直期間(1V)分だけ遅延した信号VN1を出力する(図8(A),(E))。すなわち、このD型フリップフロップ回路32は、長周期反転信号INVを1垂直期間(1V)分だけ遅延させる遅延回路として機能している。EX−NOR回路33は、長周期反転信号INV(図8(A))および信号VN1(図8(E))の排他的論理和の反転信号を求め、信号VN2を出力する(図8(F))。この信号VN2は、反転動作期間PA,PBのそれぞれにおいて、最初の垂直期間のみ低レベルとなり、他の期間では高レベルとなる信号である。論理積回路34は、垂直イネーブル信号VEN(図8(G))および信号VN2(図8(F))の論理積を求め、垂直イネーブル信号VEN2として出力する。この垂直イネーブル信号VEN2は、反転動作期間PA,PBのそれぞれにおいて、最初の垂直期間のみ低レベルとなり、他の期間では垂直イネーブル信号VENと同じ信号となる。

【0068】

表示部20では、この垂直イネーブル信号VEN2に基づいて、サブ画素SPixに対する画素信号Vpix2の書込み制御が行われる。具体的には、垂直イネーブル信号VEN2が高レベルである場合には、表示部20において線順次走査が行われ、1水平ラインごとにサブ画素SPixに対する画素信号Vpix2の書込みが行われる。一方、垂直イネーブル信号VEN2が低レベルである場合には、走査信号φV1〜φVNの全てが低レベルになるため、全てのサブ画素SPixに係るTFT素子Trがオフ状態となり、サブ画素SPixに対する画素信号Vpix2の書込みは行われない。

【0069】

すなわち、反転動作期間PA,PBのそれぞれにおける最初の垂直期間では、垂直イネーブル信号VEN2が低レベルになるため、表示画面全面においてサブ画素SPixへの書込みは行われない。よって、この期間において、各サブ画素SPixでは、TFT素子Trがオフ状態になるため、画素電位Vpがほぼ維持される。

【0070】

これにより、表示装置1は、反転動作期間PA,PBのそれぞれにおける最初の垂直期間を除き、第1フィールド画像Fi1(第1フィールド画像表示期間PW1)と第2フィールド画像Fi2(第2フィールド画像表示期間PW2)を、垂直期間(1V)ごとに交互に表示する。

【0071】

次に、この反転信号生成部15および反転制御部30の作用について、具体例を用いて説明する。

【0072】

図9は、インターレース画像の一例を模式的に表すものであり、(A)はフレーム画像Fを示し、(B)は第1フィールド画像Fi1を示し、(C)は第2フィールド画像Fi2を示す。この例では、表示装置1は静止画を表示している。図9において、斜線で示した領域は白色(WH)を表示する領域であり、その他の領域は黒色(BL)を表示する領域である。

【0073】

図10は、表示部20における画像の表示を表すものであり、(A)は、図9(B)に示した第1フィールド画像Fi1を表示した場合を示し、(B)は、図9(C)に示した第2フィールド画像Fi2を表示した場合を示す。表示装置1では、図10(A),(B)に示した各フィールド画像Fi1,Fi2が交互に表示されるが、その際、領域R2では、第1フィールド画像Fi1が表示される際には黒表示が行われ(図10(A))、一方、第2フィールド画像Fi2が表示される際には白表示が行われる(図10(B))。また、領域R3では、第1フィールド画像Fi1が表示される際には白表示が行われ(図10(A))、一方、第2フィールド画像Fi2が表示される際には黒表示が行われる(図10(B))。

【0074】

図11は、図10のような表示が行われる場合における表示装置1の表示動作の一例を表すものであり、(A)は長周期反転信号INVの波形を示し、(B)は反転制御信号FRP2の波形を示し、(C)は垂直イネーブル信号VEN2の波形を示し、(D)〜(F)は画素電位Vpの波形を示す。ここで、図11において、(D)は、常に黒表示が行われる領域R1のサブ画素SPixにおける画素電位Vp(R1)を示し、(E)は領域R2のサブ画素SPixにおける画素電位Vp(R2)を示し、(F)は領域R3のサブ画素SPixにおける画素電位Vp(R3)を示す。なお、図11において、タイミングt30〜t50は、図8におけるタイミングt30〜t50にそれぞれ対応している。

【0075】

常に黒表示が行われる領域R1におけるサブ画素SPixでは、図11(D)に示したように、反転制御信号FRP2(図11(B))に基づいて、各フィールド画像Fi1,Fi2に係る画素信号Vpix2が反転駆動により供給される。その際、このサブ画素SPixは、第1フィールド画像Fi1と第2フィールド画像Fi2とで同じ色の表示を行うため、画素電位Vpは、共通電圧VCOMを中心とした交流波形となる(図11(D))。すなわち、画素電位Vpの時間平均値は、共通電圧VCOMと等しいものである。

【0076】

領域R2,R3におけるサブ画素SPixでも、同様に、反転制御信号FRP2に基づいて反転駆動により書込み動作がおこなわれる。図10に示したように、これらのサブ画素SPixは、領域R1におけるサブ画素SPixとは異なり、第1フィールド画像Fi1と第2フィールド画像Fi2とで異なる色の表示を行うため、画素電位Vpの時間平均値Vavgは、共通電圧VCOMからずれたものになる。具体的には、領域R2におけるサブ画素SPixの画素電位Vpは、第1フィールド表示期間PW1では黒表示に対応する電位となり、第2フィールド表示期間PW2では白表示に対応する電位となるため、その時間平均値Vavgは、図11(E)に示したように、反転動作期間PAでは共通電圧VCOMより高くなり、反転動作期間PBでは共通電圧VCOMより低くなる。また、領域R3におけるサブ画素SPixの画素電位Vpは、第1フィールド表示期間PW1では白表示に対応する電位となり、第2フィールド表示期間PW2では黒表示に対応する電位となるため、その時間平均値Vavgは、図11(F)に示したように、反転動作期間PAでは共通電圧VCOMより低くなり、反転動作期間PBでは共通電圧VCOMより高くなる。

【0077】

しかしながら、反転動作期間PAにおける画素電位Vpの時間平均値Vavgと、反転動作期間PBにおける画素電位Vpの時間平均値Vavgとは、共通電圧VCOMを基準として反転の関係にあるため、反転動作期間PAおよび反転動作期間PBの合計期間では、画素電位Vpの時間平均値は共通電圧VCOMと等しくなる。

【0078】

このように、表示装置1では、互いに異なる方法で反転動作を行う反転動作期間PA,PBを設けたので、図11(D)〜(F)に示したように、反転動作期間PAおよび反転動作期間PBの合計期間における画素電位Vpの時間平均値を、共通電圧VCOMと等しくすることができ、液晶表示装置におけるいわゆる「焼き付き」を低減することができる。

【0079】

また、上述したように、反転動作期間PA,PBのそれぞれおける最初の垂直期間では、垂直イネーブル信号VEN2を低レベルにすることにより、全ての走査信号線GCLの電圧(走査信号φV1〜φVN)を低レベルにしている。これにより、サブ画素SPixでは、TFT素子Trがオフ状態になり、サブ画素SPixへの書込み動作が行われないため、画素電位Vpは、図11(D)〜(F)に示したように、その前の垂直期間における電位を維持する(波形部分W1)。これにより、以下に比較例を参照して説明するように、長周期反転信号INVの反転時における表示画像の乱れを低減することができ、画質を改善することができる。

【0080】

(比較例)

次に、比較例と対比して、本実施の形態の作用を説明する。本比較例は、反転動作期間PA,PBにおける最初の垂直期間でも、サブ画素SPixに対する書込み動作を行うものである。

【0081】

図12は、比較例に係る表示装置1Rの一構成例を表すものである。表示装置1Rは反転制御部30Rを備えている。反転制御部30Rは、本実施の形態に係る反転制御部30(図3)において、D型フリップフロップ回路32、EX−NOR回路33、および論理積回路34を省いたものである。これにより、本比較例では、タイミング制御部16において生成された垂直イネーブル信号VENが、そのまま表示パネル20に入力される。

【0082】

図13は、表示装置1Rの表示動作の一例を表すものであり、(A)は長周期反転信号INVの波形を示し、(B)は反転制御信号FRP2の波形を示し、(C)は垂直イネーブル信号VEN2の波形を示し、(D)は常に所定の中間調の色を表示するサブ画素SPixにおける画素電位Vpの波形を示す。なお、図11において、タイミングt30〜t50は、図8におけるタイミングt30〜t50にそれぞれ対応している。

【0083】

図13に示したように、本比較例に係る表示装置1Rでは、反転動作期間PA,PBにおける最初の垂直期間において、垂直イネーブル信号VENは高レベルであるため、この期間でもサブ画素SPixに対して画素信号Vpix2の書込みが行われる。その際、反転動作期間PAと反転動作期間PBとの境界を挟む隣接する垂直期間では、同じ電圧の画素信号Vpix2が続けて印加される。

【0084】

しかしながら、実際には、この2つの垂直期間における画素電位Vpは等しくならないおそれがある。すなわち、タイミングt29,t39などのように、画素信号Vpix2が反転してサブ画素SPixに供給される場合では、液晶素子LCに充電する電荷量が多いため、反転部14は、そのサブ画素SPixを十分に駆動できず、画素電位Vpは十分に変化しきれないおそれがある(波形部分W2)。一方、タイミングt30,t40などのように、画素信号Vpix2が反転しないで印加される場合では、液晶素子LCに充電する電荷量が少ないため、反転部14は、そのサブ画素SPixを十分に駆動することができ、画素電位Vpを所望の電位により近いレベルにまで変化させることができる(波形部分W3)。よって、例えば、表示装置1Rが、表示画面全体にわたってこの中間調の色を表示した場合、長周期反転信号INV(図13(A))が反転する際、瞬間的に画面全体の輝度が変化してしまう。つまり、約1分ごとに論理反転する長周期反転信号INVを用いた場合には、約1分ごとにこの現象が発生し、画質が低下してしまう。

【0085】

一方、本実施の形態に係る表示装置1では、反転動作期間PA,PBのそれぞれにおける最初の垂直期間において、サブ画素SPixに対する画素信号Vpix2の書込み動作を行わないようにしている。これにより、反転動作期間PAと反転動作期間PBとの境界を挟む隣接する垂直期間では、画素電位Vpが維持されるため、画素電位Vpは互いに等しくなる。よって、例えば、表示装置1が、表示画面全体にわたってこの中間調の色を表示した場合でも、長周期反転信号INVが反転する際に、瞬間的に画面全体の輝度が変化するおそれを低減することができ、画質の低下を抑えることができる。

【0086】

[効果]

以上のように本実施の形態では、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixに対する画素信号の書込み動作を行わないようにしたので、画質の低下を抑えることができる。

【0087】

[変形例1−1]

上記実施の形態では、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixのTFT素子Trをオフ状態にすることにより、画素信号Vpix2の書込み動作を行わないようにしたが、これに限定されるものではなく、これに加えて、さらに、スイッチ23(1)〜23(M)をオフ状態にし、画素信号線SGLに画素信号Vpix2を印加しないようにしてもよい。その具体例を、以下に説明する。

【0088】

図14は、本変形例に係る表示装置1Bの一構成例を表すものである。表示装置1Bは、反転制御部30Bを備えている。反転制御部30Bは、上記実施の形態に係る反転制御部30の機能に加え、水平イネーブル信号HENに基づいて、水平イネーブル信号HEN2を生成する機能も有している。そして、表示パネル20には、この反転制御部30Bが生成した水平イネーブル信号HEN2が入力される。

【0089】

図15は、反転制御部30Bの一構成例を表すものである。反転制御部30Bは、論理積回路35を有している。論理積回路35は、EX−NOR回路33の出力信号(信号VN2)と、水平イネーブル信号HENの論理積を求め、水平イネーブル信号HEN2として出力するものである。

【0090】

この構成により、反転制御部30Bは、長周期反転信号INVが変化した後の最初の垂直期間において低レベルになり、その他の期間では水平イネーブル信号HENと同じ信号となる水平イネーブル信号HEN2を生成する。これにより、長周期反転信号INVが変化した後の最初の垂直期間(反転動作期間PA,PBにおける最初の垂直期間)では、スイッチ23(1)〜23(M)がオフ状態になるため、画素信号Vpix2は画素信号線SGLに印加されることはない。

【0091】

なお、この例では、スイッチ23(1)〜23(M)をオフ状態にしたが、例えば、反転部14に同様のスイッチを設け、長周期反転信号INVが変化した後の最初の垂直期間においてこのスイッチをオフ状態にすることにより、表示部20に画素信号VpixR2,VpixG2,VpixB2を供給しないようにしてもよい。

【0092】

[変形例1−2]

上記実施の形態では、反転制御部30において、長周期反転信号INVを1垂直期間(1V)分だけ遅延させたが、これに限定されるものではなく、これに代えて、複数の垂直期間に対応する時間だけ遅延させてもよい。以下に、長周期反転信号INVを、2つの垂直期間に対応する時間だけ遅延させる場合を例に説明する。

【0093】

図16は、本変形例に係る反転制御部30Cの一構成例を表すものである。反転制御部30Cは、D型フリップフロップ回路32A,32Bを有している。D型フリップフロップ回路32Aは、データ入力端子に長周期反転信号INVが供給されるとともに、クロック入力端子に垂直同期信号VSTが供給される。D型フリップフロップ回路32Bは、データ入力端子にD型フリップフロップ回路32Aの出力端子が接続されるとともに、クロック入力端子に垂直同期信号VSTが供給される。このD型フリップフロップ回路32Bの出力信号は、EX−NOR回路33に入力される。このD型フリップフロップ回路32A,32Bは、長周期反転信号INVを2つの1垂直期間(1V)分だけ遅延させる遅延回路として機能する。これにより、この反転制御部30Cを備えた表示装置では、反転動作期間PA,PBにおける最初の2つの垂直期間において、サブ画素SPixに対する画素信号の書込み動作を行わないようにすることができ、上記実施の形態と同様に、画質の低下を抑えることができる。

【0094】

<2.第2の実施の形態>

次に、第2の実施の形態に係る表示装置2について説明する。本実施の形態は、映像信号Vdispに基づいて、反転動作期間PA,PBの長さを変更することができるものである。なお、上記第1の実施の形態に係る表示装置1と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

【0095】

図17は、本実施の形態における表示装置2の一構成例を表すものである。表示装置2は、反転信号生成部17を備えている。反転信号生成部17は、VRAM12に記憶されたフィールド画像に基づいて、長周期反転信号INVの反転間隔を変更するものである。

【0096】

図18は、表示装置2における動作の流れ図を表すものである。表示装置2では、画像が変化しないときには、長周期反転信号INVの反転間隔を所定の最小時間に設定し、表示する画像が変化するときには、その反転間隔を長く設定する。長周期反転信号INVの反転間隔は、垂直期間の時間を単位とした変数Pで設定される。そして、長周期反転信号INVが反転した後、変数nを垂直期間ごとに0から順にインクリメントしていき、変数nが変数Pと等しくなったときに、長周期反転信号INVを反転する。以下に、その詳細を説明する。

【0097】

まず、制御部11が、供給された映像信号Vdispに含まれるフィールド画像をVRAM12に書き込む(ステップS1)。

【0098】

次に、制御部11は、VRAM12に書き込まれたフィールド画像が第1フィールド画像であるかどうかを確認する(ステップS2)。そのフィールド画像が第1フィールド画像である場合にはステップS3に進み、第1フィールド画像でない場合には、ステップS7に進む。

【0099】

ステップS2において、VRAM12に書き込まれたフィールド画像が第1フィールド画像である場合には、反転信号生成部17は、VRAM12に記憶されている第1フィールド画像に基づいて動き検出を行う(ステップS3)。動き検出は、例えばオプティカルフロー計算により行うことが可能である。オプティカルフローの計算アルゴリズムとしては、例えば、ホーン−シャンク法が適用可能である。このホーンシャンク法については、例えば、“Berthold K.P. Horn and Brian G. Schunck Determining Optical Flow, Artificial Intelligence, Vol. 17, pp.185-203, Aug. 1981”に記載がある。

【0100】

次に、反転信号生成部17は、ステップS3の動き検出の結果に基づいて、フィールド画像が変化しているかどうかを検出する(ステップS4)。ステップS4において、フィールド画像の変化が検出された場合には、反転信号生成部17は、変数Pをインクリメントする(ステップS5)。また、ステップS4において、フィールド画像の変化が検出されなかった場合には、反転信号生成部17は、変数Pを4096に設定する(ステップS6)。

【0101】

次に、反転信号生成部17は、変数nが変数Pよりも小さいかどうかを確認する(ステップS7)。変数nが変数Pよりも小さい場合にはステップS10に進み、変数nが変数P以上である場合にはステップS8に進む。

【0102】

ステップS7において、変数nが変数P以上である場合には、反転信号生成部17は、変数nを0に設定(変数nをリセット)し(ステップS8)、長周期反転信号INVを反転する(ステップS9)。

【0103】

次に、反転信号生成部17は、変数nをインクリメントする(ステップS10)。

【0104】

次に、表示装置2は、VRAM12に記憶されたフィールド画像に基づいて、表示を行う(ステップS11)。

【0105】

そして、またステップS1に戻り、表示装置2は、以上の動作を繰り返す。

【0106】

表示装置2では、フィールド画像に対して動き検出を行い、そのフィールド画像の変化の有無に基づいて、表示部20がそのフィールド画像を表示した際の焼き付きが生じるおそれを判断する。そして、そのフィールド画像の表示により焼き付きが生じるおそれがあると判断した場合には、変数Pを小さく設定することにより焼き付きが生じにくくなるようにし、そのフィールド画像の表示により焼き付きが生じるおそれが低いと判断された場合には、変数Pを大きい値に設定して、画質の低下を抑えるようにしている。

【0107】

具体的には、反転信号生成部17は、フィールド画像の変化が検出されなかった場合に、変数Pを4096に設定する(ステップS6)。すなわち、この場合、反転信号生成部17は、表示部20が、変化しないフィールド画像を表示するため、表示部20において焼き付きが生じるおそれがあると判断し、長周期反転信号INVの反転間隔に対応する変数Pを最小値(この例では4096)に設定する。なお、このときの周期反転信号INVの反転間隔は、例えば、60[Hz]周期でフィールド画像を表示した場合には、68.2[sec](=4096/60[Hz])である。このように、表示装置2は、フィールド画像が変化しないときには、変数Pを最小値に設定することにより、反転動作期間PAと反転動作期間PBとが高い頻度で切り換える。これにより、表示装置2では、表示部20において焼き付きが生じるおそれを低減することができる。

【0108】

また、反転信号生成部17は、フィールド画像の変化が検出された場合には、変数Pをインクリメントする(ステップS5)。すなわち、この場合、反転信号生成部17は、表示部20が、変化するフィールド画像を表示するため、表示部20において焼き付きが生じるおそれは低いと判断し、長周期反転信号INVの反転間隔に対応する変数Pをインクリメントする。このように、表示装置2は、フィールド画像が変化するときには、変数Pを大きい値に設定することにより、反転動作期間PAと反転動作期間PBとの切り替わり頻度を低くする。これにより、表示装置2では、仮に、長周期反転信号INVが反転する際に表示画像が若干乱れる場合でも、その乱れた画像を表示する機会が減少するので、画質の低下を抑えることができる。

【0109】

また、表示装置2は、VRAM12に書き込まれたフィールド画像が第1フィールド画像Fi1である場合においてのみ動き検出を行う(ステップS2〜S3)。これにより、ステップS3,S4において、より高い精度で動き検出を行うことができる。すなわち、例えば、第1フィールド画像Fi1および第2フィールド画像Fi2の両方に基づいて動き検出を行う場合には、ステップS3の動き検出において、第1フィールド画像Fi1と第2フィールド画像Fi2との差に起因する動きも検出されるおそれがある。一方、第1フィールド画像Fi1のみに基づいて動き検出を行う場合には、この誤検出のおそれを低減することができるため、より高い精度でフィールド画像の変化を検出することができる。なお、この例では、VRAM12に書き込まれたフィールド画像が第1フィールド画像Fi1である場合においてのみ動き検出を行うようにしたが、これに限定されるものではなく、VRAM12に書き込まれたフィールド画像が第2フィールド画像Fi2である場合においてのみ動き検出を行うようにしてもよい。

【0110】

以上のように本実施の形態では、フィールド画像の動き検出結果に基づいて反転動作期間PA,PBの長さを変更するようにしたので、焼き付きの低減を実現するとともに、画質の低下を抑えることができる。

【0111】

また、本実施の形態では、フィールド画像の変化が検出されなかった場合に、長周期反転信号の反転間隔を所定の最小値に設定し、反転動作期間PAと反転動作期間PBとが高い頻度で切り換わるようにしたので、表示部における焼き付きの低減を実現することができる。

【0112】

また、本実施の形態では、フィールド画像の変化が検出された場合に、長周期反転信号INVの反転間隔が広くなるように設定し、反転動作期間PAと反転動作期間PBとの切り替わり頻度が低くなるようにしたので、仮に、長周期反転信号が反転する際に表示画像が若干乱れる場合でも、画質の低下を抑えることができる。

【0113】

その他の効果は、上記第1の実施の形態の場合と同様である。

【0114】

[変形例2−1]

上記実施の形態では、フィールド画像の変化の有無に基づいて、焼き付きが生じるおそれを判断するようにしたが、これに限定されるものではなく、例えば、フィールド画像全体における、画像が変化する領域の占める割合がある所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよいし、フィールド画像の各画素における画素情報の変化量が所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよい。

【0115】

[その他の変形例]

上記第2の実施の形態においても、上記第1の実施の形態の変形例1−1に示したように、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixのTFT素子Trに加えて、スイッチ23(1)〜23(M)をオフ状態にしてもよいし、上記第1の実施の形態の変形例1−2に示したように、反転制御部30において、複数の垂直期間に対応する時間だけ遅延させてもよい。

【0116】

<3.第3の実施の形態>

次に、第3の実施の形態に係る表示装置3について説明する。本実施の形態は、表示装置2において、OSD(On Screen Display)画像を表示する場合には、動き検出を行わないようにしたものである。なお、上記第2の実施の形態に係る表示装置2と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。

【0117】

図19は、本実施の形態に係る表示装置3を表すものである。表示装置3は、OSD生成部18と、反転信号生成部19とを備えている。

【0118】

OSD生成部18は、OSD画像を生成するものである。このOSD生成部18で生成されたOSD画像は、VRAM12においてフィールド画像に重畳され、このOSD画像が重畳されたフィールド画像が、表示部20に表示されるようになっている。また、OSD生成部18は、OSD画像をフィールド画像に重畳するかどうかを示すOSDフラグ信号Fosdを生成する。

【0119】

反転信号生成部19は、VRAM12に記憶されたフィールド画像、およびOSDフラグ信号Fosdに基づいて、動き検出を行い、長周期反転信号INVの反転間隔を変更するものである。

【0120】

図20は、表示装置3における動作の流れ図を表すものである。なお、上記第2の実施の形態に係る表示装置2の流れ図(図18)と同じステップについては説明を省略する。

【0121】

ステップS2において、VRAM12に書き込まれたフィールド画像が第1フィールド画像である場合には、反転信号生成部19は、OSD生成部18から供給されるOSDフラグ信号Fosdがtrueであるか否かを検出する(ステップS21)。OSDフラグ信号Fosdがtrueである場合にはステップS6に進み、OSDフラグ信号Fosdがtrueでない場合にはステップS3に進む。

【0122】

また、ステップS10の次に、OSD生成部18は、生成したOSD画像をVRAM12に書き込む(ステップS22)。これにより、VRAM12では、記憶されたフィールド画像にOSD画像が重畳される。

【0123】

表示装置3では、OSDフラグ信号Fosdに基づいて、動き検出を行うかどうかを判断している。一般に、OSD画像は静止画であるため、表示部20がそのOSD画像を表示した場合には、表示部20において焼き付きが生じるおそれがある。よって、反転信号生成部19は、OSDフラグ信号Fosdがtrueである場合には、動き検出を行うまでもなく、表示部20において焼き付きが生じるおそれがあると判断し、長周期反転信号INVの反転間隔に対応する変数Pを最小値(この例では4096)に設定する。これにより、上記第2の実施の形態等と同様に、焼き付きが生じるおそれを低減することができる。

【0124】

以上のように本実施の形態では、OSDフラグ信号Fosdがtrueである場合には、動き検出を行わないようにしたので、回路動作の負荷を軽減することができる。その他の効果は、上記第1の実施の形態の場合と同様である。

【0125】

[変形例3−1]

上記実施の形態では、OSDフラグ信号Fosdがtrueであるか否かに基づいて動き検出を行うようにしたが、これに限定されるものではなく、例えば、OSDフラグ信号Fosdの変化に基づいて、動き検出を行うようにしてもよい。以下に、その詳細を説明する。

【0126】

図21は、本変形例に係る表示装置3Bにおける動作の流れ図を表すものである。なお、上記実施の形態に係る表示装置3の流れ図(図20)と同じステップについては説明を省略する。

【0127】

ステップS2において、VRAM12に書き込まれたフィールド画像が第1フィールド画像である場合には、本変形例に係る反転信号生成部19Bは、OSD生成部18から供給されるOSDフラグ信号Fosdが変化したかどうか否かを検出する(ステップS31)。OSDフラグ信号Fosdが変化した場合にはステップS32に進み、OSDフラグ信号Fosdが変化しなかった場合にはステップS3に進む。

【0128】

ステップS31において、OSDフラグ信号Fosdが変化したと検出された場合には、反転信号生成部19Bは、変数nを0に設定(変数nをリセット)し(ステップS32)、長周期反転信号INVを反転する(ステップS33)。そしてフローはステップS6に進む。

【0129】

このように、表示装置3Bでは、OSDフラグ信号Fosdが変化したときに、長周期反転信号INVを反転させ、次の反転動作期間PA,PBを開始するようにしたので、表示部20において焼き付きが生じるおそれを低減することができる。具体的には、例えば、OSDフラグ信号FosdがFalseからTrueに変化した後では、OSD画像(静止画)により表示部20において焼き付きが生じるおそれがあるが、OSDフラグ信号FosdがFalseからTrueに変化するタイミングで長周期反転信号INVを反転させるとともに、変数Pを最小値に設定することにより(ステップS6)、そのOSD画像が表示される期間における焼き付きが生じるおそれを低減することができる。また、例えば、OSDフラグ信号FosdがTrueからFalseに変化する際にも、長周期反転信号INVを反転させるとともに、変数Pを最小値に設定することにより(ステップS6)、OSD画像が表示されていた期間における状態をリセットすることができ、焼き付きが生じるおそれを低減することができる。

【0130】

なお、この例では、OSDフラグ信号Fosdが変化したときに長周期反転信号INVを反転させるようにしたが、これに限定されるものではなく、例えば、OSDフラグ信号FosdがFalseからTrueに変化したときにのみ長周期反転信号INVを反転させるようにしてもよい。

【0131】

[その他の変形例]

上記第3の実施の形態においても、上記第2の実施の形態の変形例2−1に示したように、例えば、フィールド画像全体における、フィールド画像内における画像が変化する領域の占める割合がある所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよいし、フィールド画像の各画素における画素情報の変化量が所定量以上であるかどうかにより、焼き付きが生じるおそれを判断してもよい。

【0132】

以上、いくつかの実施の形態および変形例を挙げて本技術を説明したが、本技術はこれらの実施の形態等には限定されず、種々の変形が可能である。

【0133】

例えば、第2、第3の実施の形態においても、上記第1の実施の形態の変形例1−1に示したように、反転動作期間PA,PBにおける最初の垂直期間において、サブ画素SPixのTFT素子Trに加えて、スイッチ23(1)〜23(M)をオフ状態にしてもよいし、上記第1の実施の形態の変形例1−2に示したように、反転制御部30において、複数の垂直期間に対応する時間だけ遅延させてもよい。

【0134】

また、例えば、上記実施の形態等では、水平走査部を設け、1H期間において、水平方向に走査することにより、画素Pixに画素信号Vpix2を書き込むようにしたが、これに限定されるものではなく、これに代えて、例えば、この1H期間において、その選択された水平ラインに係る複数の画素Pixに対して同時に画素信号Vpix2を書き込むようにしてもよい。

【0135】

なお、本技術は以下のような構成とすることができる。

【0136】

(1)交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成し、表示部に供給する画素信号生成部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置の駆動回路。

【0137】

(2)前記画素信号生成部は、前記第1の期間および前記第2の期間のそれぞれにおける先頭タイミングでは、画素信号を反転しない

前記(1)に記載の表示装置の駆動回路。

【0138】

(3)前記第1の期間と前記第2の期間とで異なる論理レベルを有する論理信号を生成する論理信号生成部を備え、

前記画素信号生成部は、前記論理信号に基づいて前記画素信号の反転動作を制御する

前記(1)または(2)のいずれかに記載の表示装置の駆動回路。

【0139】

(4)垂直同期信号を生成するタイミング制御部を備え、

前記書込制御部は、前記論理信号と前記垂直同期信号とに基づいて、前記先頭期間を設定する

前記(1)から(3)のいずれかに記載の表示装置の駆動回路。

【0140】

(5)前記書込制御部は、

前記垂直同期信号に同期して前記論理信号をサンプリングするフリップフロップ回路と、

前記フリップフロップ回路の出力信号と前記論理信号との排他的論理和を求める排他的論理和回路と

を有し、

前記排他的論理和回路の出力信号に基づいて前記先頭期間を設定する

前記(4)に記載の表示装置の駆動回路。

【0141】

(6)前記表示部は、複数の画素のそれぞれにおいて、前記画素信号を伝える画素スイッチを有し、

前記書込制御部は、前記先頭期間において、前記画素スイッチをオフ状態にする

前記(1)から(5)のいずれかに記載の表示装置の駆動回路。

【0142】

(7)前記表示部は、

前記複数の画素に画素信号を供給するための画素信号線と、

前記画素信号生成部から供給された画素信号を前記画素信号線に供給するための信号線スイッチと

を有し、

前記書込制御部は、前記先頭期間において、前記信号線スイッチをもオフ状態にする

前記(6)に記載の表示装置の駆動回路。

【0143】

(8)前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記論理信号生成部は、前記画像信号に基づいて画像の変化を検出し、その検出結果に基づいて、前記第1の期間の長さおよび前記第2の期間の長さを設定する

前記(3)に記載の表示装置の駆動回路。

【0144】

(9)前記論理信号生成部は、

画像の変化がない場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定し、

画像の変化がある場合には、前記第1の期間の長さおよび前記第2の期間の長さを前記最小値より長く設定する

前記(8)に記載の表示装置の駆動回路。

【0145】

(10)OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルである場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定する

前記(8)に記載の表示装置の駆動回路。

【0146】

(11)OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルとディセーブルとの間で変化した場合において、前記論理信号の論理レベルを変更する

前記(8)に記載の表示装置の駆動回路。

【0147】

(12)前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記画像信号はインターレース信号であり、

前記表示部は、前記インターレース信号のフィールド画像の画素数と同じ数の画素を有し、各フレーム期間において、第1のフィールド画像および第2のフィールド画像を交互に表示する

前記(1)から(11)のいずれかに記載の表示装置の駆動回路。

【0148】

(13)前記先頭期間は、1つ分のフレーム期間である

前記(1)から(12)のいずれかに記載の表示装置の駆動回路。

【0149】

(14)交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成する画素信号生成部と、

前記画素信号に基づいて表示を行う表示部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置。

【0150】

(15)交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成して表示部に供給し、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する

表示装置の駆動方法。

【符号の説明】

【0151】

1,1B,2,3…表示装置、11…制御部、12…VRAM、13…RGBデコーダ部、14…反転部、15,17,19…反転信号生成部、16…タイミング制御部、18…OSD生成部、20…表示部、21…水平走査部、22,22(1)〜22(M)…論理積回路、23,23(1)〜23(M)…スイッチ、26…垂直走査部、27,27(1)〜27(N)…論理積回路、30,30B…反転制御部、31…EX−OR回路、32,32A,32B…D型フリップフロップ回路、33…EX−NOR回路、34,35…論理積回路、F…フレーム画像、Fi1…第1フィールド画像、Fi2…第2フィールド画像、Fosd…OSDフラグ信号、FRP,FRP2…反転制御信号、HCLK,Pix…画素、SPix…サブ画素、VCLK…クロック信号、HEN,HEN2…水平イネーブル信号、HST…水平同期信号、INV…長周期反転信号、L…ライン画像、LC…液晶素子、PA,PB…反転動作期間、PW1…第1フィールド表示期間、PW2…第2フィールド表示期間、R1〜R3…領域、SH1〜SHM,SV1〜SVN,φH1〜φHM,φV1〜φVN…走査信号、Tr…TFT素子、VCOM…共通電圧、VEN,VEN2…垂直イネーブル信号、Vdisp…映像信号、VN1,VN2…信号、Vp…画素電位、Vpix,VpixR,VpixG,VpixB,Vpix2,VpixR2,VpixG2,VpixB2…画素信号、VST…垂直同期信号。

【特許請求の範囲】

【請求項1】

交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成し、表示部に供給する画素信号生成部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置の駆動回路。

【請求項2】

前記画素信号生成部は、前記第1の期間および前記第2の期間のそれぞれにおける先頭タイミングでは、画素信号を反転しない

請求項1に記載の表示装置の駆動回路。

【請求項3】

前記第1の期間と前記第2の期間とで異なる論理レベルを有する論理信号を生成する論理信号生成部を備え、

前記画素信号生成部は、前記論理信号に基づいて前記画素信号の反転動作を制御する

請求項1に記載の表示装置の駆動回路。

【請求項4】

垂直同期信号を生成するタイミング制御部を備え、

前記書込制御部は、前記論理信号と前記垂直同期信号とに基づいて、前記先頭期間を設定する

請求項3に記載の表示装置の駆動回路。

【請求項5】

前記書込制御部は、

前記垂直同期信号に同期して前記論理信号をサンプリングするフリップフロップ回路と、

前記フリップフロップ回路の出力信号と前記論理信号との排他的論理和を求める排他的論理和回路と

を有し、

前記排他的論理和回路の出力信号に基づいて前記先頭期間を設定する

請求項4に記載の表示装置の駆動回路。

【請求項6】

前記表示部は、複数の画素のそれぞれにおいて、前記画素信号を伝える画素スイッチを有し、

前記書込制御部は、前記先頭期間において、前記画素スイッチをオフ状態にする

請求項1に記載の表示装置の駆動回路。

【請求項7】

前記表示部は、

前記複数の画素に画素信号を供給するための画素信号線と、

前記画素信号生成部から供給された画素信号を前記画素信号線に供給するための信号線スイッチと

を有し、

前記書込制御部は、前記先頭期間において、前記信号線スイッチをもオフ状態にする

請求項6に記載の表示装置の駆動回路。

【請求項8】

前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記論理信号生成部は、前記画像信号に基づいて画像の変化を検出し、その検出結果に基づいて、前記第1の期間の長さおよび前記第2の期間の長さを設定する

請求項3に記載の表示装置の駆動回路。

【請求項9】

前記論理信号生成部は、

画像の変化がない場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定し、

画像の変化がある場合には、前記第1の期間の長さおよび前記第2の期間の長さを前記最小値より長く設定する

請求項8に記載の表示装置の駆動回路。

【請求項10】

OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルである場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定する

請求項8に記載の表示装置の駆動回路。

【請求項11】

OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルとディセーブルとの間で変化した場合において、前記論理信号の論理レベルを変更する

請求項8に記載の表示装置の駆動回路。

【請求項12】

前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記画像信号はインターレース信号であり、

前記表示部は、前記インターレース信号のフィールド画像の画素数と同じ数の画素を有し、各フレーム期間において、第1のフィールド画像および第2のフィールド画像を交互に表示する

請求項1に記載の表示装置の駆動回路。

【請求項13】

前記先頭期間は、1つ分のフレーム期間である

請求項1に記載の表示装置の駆動回路。

【請求項14】

交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成する画素信号生成部と、

前記画素信号に基づいて表示を行う表示部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置。

【請求項15】

交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成して表示部に供給し、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する

表示装置の駆動方法。

【請求項1】

交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成し、表示部に供給する画素信号生成部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置の駆動回路。

【請求項2】

前記画素信号生成部は、前記第1の期間および前記第2の期間のそれぞれにおける先頭タイミングでは、画素信号を反転しない

請求項1に記載の表示装置の駆動回路。

【請求項3】

前記第1の期間と前記第2の期間とで異なる論理レベルを有する論理信号を生成する論理信号生成部を備え、

前記画素信号生成部は、前記論理信号に基づいて前記画素信号の反転動作を制御する

請求項1に記載の表示装置の駆動回路。

【請求項4】

垂直同期信号を生成するタイミング制御部を備え、

前記書込制御部は、前記論理信号と前記垂直同期信号とに基づいて、前記先頭期間を設定する

請求項3に記載の表示装置の駆動回路。

【請求項5】

前記書込制御部は、

前記垂直同期信号に同期して前記論理信号をサンプリングするフリップフロップ回路と、

前記フリップフロップ回路の出力信号と前記論理信号との排他的論理和を求める排他的論理和回路と

を有し、

前記排他的論理和回路の出力信号に基づいて前記先頭期間を設定する

請求項4に記載の表示装置の駆動回路。

【請求項6】

前記表示部は、複数の画素のそれぞれにおいて、前記画素信号を伝える画素スイッチを有し、

前記書込制御部は、前記先頭期間において、前記画素スイッチをオフ状態にする

請求項1に記載の表示装置の駆動回路。

【請求項7】

前記表示部は、

前記複数の画素に画素信号を供給するための画素信号線と、

前記画素信号生成部から供給された画素信号を前記画素信号線に供給するための信号線スイッチと

を有し、

前記書込制御部は、前記先頭期間において、前記信号線スイッチをもオフ状態にする

請求項6に記載の表示装置の駆動回路。

【請求項8】

前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記論理信号生成部は、前記画像信号に基づいて画像の変化を検出し、その検出結果に基づいて、前記第1の期間の長さおよび前記第2の期間の長さを設定する

請求項3に記載の表示装置の駆動回路。

【請求項9】

前記論理信号生成部は、

画像の変化がない場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定し、

画像の変化がある場合には、前記第1の期間の長さおよび前記第2の期間の長さを前記最小値より長く設定する

請求項8に記載の表示装置の駆動回路。

【請求項10】

OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルである場合には、前記第1の期間の長さおよび前記第2の期間の長さを所定の最小値に設定する

請求項8に記載の表示装置の駆動回路。

【請求項11】

OSD画像を生成するとともに、そのOSD画像を前記表示部に表示する際にイネーブルとなるOSDフラグ信号を生成するOSD画像生成部をさらに備え、

前記論理信号生成部は、前記OSDフラグがイネーブルとディセーブルとの間で変化した場合において、前記論理信号の論理レベルを変更する

請求項8に記載の表示装置の駆動回路。

【請求項12】

前記画素信号生成部は、画像信号に基づいて前記画素信号を生成し、

前記画像信号はインターレース信号であり、

前記表示部は、前記インターレース信号のフィールド画像の画素数と同じ数の画素を有し、各フレーム期間において、第1のフィールド画像および第2のフィールド画像を交互に表示する

請求項1に記載の表示装置の駆動回路。

【請求項13】

前記先頭期間は、1つ分のフレーム期間である

請求項1に記載の表示装置の駆動回路。

【請求項14】

交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成する画素信号生成部と、

前記画素信号に基づいて表示を行う表示部と、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する書込制御部と

を備えた表示装置。

【請求項15】

交互に設定された第1の期間および第2の期間のそれぞれにおいて、フレーム期間ごとに反転する画素信号を生成して表示部に供給し、

前記第1の期間および前記第2の期間のそれぞれにおける先頭から所定の長さの先頭期間以外の期間において、前記表示部に対する前記画素信号の書込みを行うように制御する

表示装置の駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−226152(P2012−226152A)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願番号】特願2011−94165(P2011−94165)

【出願日】平成23年4月20日(2011.4.20)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願日】平成23年4月20日(2011.4.20)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]