表示装置の駆動回路、表示装置、及び、電子機器

【課題】サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響を受けることなく、所望の電圧値の直流電圧を信号線に書き込むことが可能な表示装置の駆動回路、当該駆動回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】本開示の表示装置の駆動回路は、画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子とを備える。

【解決手段】本開示の表示装置の駆動回路は、画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、表示装置の駆動回路、表示装置、及び、電子機器に関し、特に、表示装置の信号線を駆動する駆動回路、当該駆動回路を用いた表示装置、及び、当該表示装置を有する電子機器に関する。

【背景技術】

【0002】

有機EL表示装置などの平面型の表示装置では、画素を構成する素子の特性ばらつきなどに起因する画質不良を改善するために、階調電圧の書込みに先立って所定の直流電圧を画素に書込み、当該直流電圧を基準電圧として用いて特性ばらつきについての補正処理が行われる(例えば、特許文献1参照)。

【0003】

所定の直流電圧の書込みは、画素が行列状に配置されて成る画素アレイ部の画素列毎に配線された信号線(データ線)を介して行われる。より具体的には、信号線毎にサンプリングスイッチが設けられており、信号供給源から供給される所定の直流電圧をサンプリングスイッチが画素列単位でサンプリングし、各信号線に書き込むことにより、当該信号線を介して所定の直流電圧が画素に書き込まれる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−310311号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、サンプリングスイッチを介して直流電圧を各画素に書き込む際に、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチの入力ノードの電位が揺れる現象が生じる。そして、サンプリングスイッチの入力ノードの電位の揺れによって直流電圧が変動するため、所望の電圧値の直流電圧を画素に書き込めなくなる。その結果、所望の電圧値の直流電圧を基準電圧とする、特性ばらつきについての補正処理を正常に行えないことになる。

【0006】

そこで、本開示は、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響を受けることなく、所望の電圧値の直流電圧を信号線に書き込むことが可能な表示装置の駆動回路、当該駆動回路を用いた表示装置、及び、当該表示装置を有する電子機器を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本開示の表示装置の駆動回路は、

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える構成となっている。

【0008】

本開示の駆動回路は、画素が行列状に配置されて成る画素アレイ部を有する表示装置において、画素アレイ部の画素列単位で配線された信号線の駆動に用いることができる。また、本開示の駆動回路を用いた表示装置は、表示部を備える各種の電子機器において、その表示部として用いることができる。

【0009】

サンプリングスイッチによるサンプリングによって所定の直流電圧を信号線に書き込む際に、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチの入力ノードの電位が揺らされようとする。このとき、サンプリングスイッチの入力ノードに接続されている容量素子が、チャージインジェクションやクロックフィードスルーの影響を吸収するように作用する。これにより、チャージインジェクションやクロックフィードスルーの影響による、サンプリングスイッチの入力ノードの電位の揺れを抑えることができる。

【発明の効果】

【0010】

本開示によれば、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響による、サンプリングスイッチの入力ノードの電位の揺れを抑えることができるため、当該影響を受けることなく、所望の電圧値の直流電圧を信号線に書き込むことができる。

【図面の簡単な説明】

【0011】

【図1】本開示の実施形態に係るアクティブマトリクス型有機EL表示装置の構成の概略を示すシステム構成図である。

【図2】画素(画素回路)の具体的な回路構成の一例を示す回路図である。

【図3】本開示の実施形態に係るアクティブマトリクス型有機EL表示装置の基本的な回路動作を説明するためのタイミング波形図である。

【図4】駆動トランジスタの閾値電圧Vthのばらつきに起因する課題の説明(A)、及び、駆動トランジスタの移動度μのばらつきに起因する課題の説明(B)に供する特性図である。

【図5】サンプリングスイッチのオフ時のチャージインジェクション及びクロックフィードスルーの影響についての説明図である。

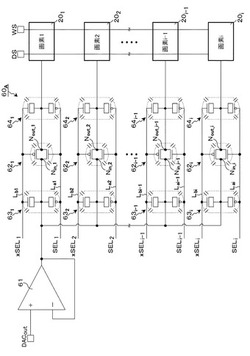

【図6】実施例1に係る信号線駆動回路の回路構成を示す回路図である。

【図7】実施例1に係る信号線駆動回路の回路動作を説明するためのタイミング波形図である。

【図8】実施例1に係る信号線駆動回路の動作説明図である。

【図9】参考例に係る信号線駆動回路の回路構成を示す回路図である。

【図10】参考例に係る信号線駆動回路の回路動作を説明するためのタイミング波形図である。

【図11】参考例に係る信号線駆動回路の動作説明図である。

【図12】実施例2に係る信号線駆動回路の回路構成を示す回路図である。

【発明を実施するための形態】

【0012】

以下、本開示の技術を実施するための形態(以下、「実施形態」と記述する)について図面を用いて詳細に説明する。本開示は実施形態に限定されるものではない。以下の説明において、同一要素又は同一機能を有する要素には同一符号を用いることとし、重複する説明は省略する。尚、説明は以下の順序で行う。

1.本開示の表示装置の駆動回路、表示装置、及び、電子機器、全般に関する説明

2.本開示の実施形態に係るアクティブマトリクス型有機EL表示装置

2−1.システム構成

2−2.画素回路

2−3.基本的な回路動作

2−4.信号線駆動回路

2−4−1.実施例1

2−4−2.参考例

2−4−3.実施例2

3.電子機器

4.本開示の構成

【0013】

<1.本開示の表示装置の駆動回路、表示装置、及び、電子機器、全般に関する説明>

本開示の表示装置の駆動回路は、画素が行列状に配置されて成る画素アレイ部を有する平面型(フラットパネル型)の表示装置において、画素アレイ部の画素列単位で配線された信号線を駆動する、具体的には、信号線に所定の直流電圧を書き込むのに用いることができる。

【0014】

平面型の表示装置としては、画素の発光素子(電気光学素子)として自発光素子を用いる有機EL表示装置やプラズマ表示装置などを例示することができる。これらの表示装置のうち、有機EL表示装置は、有機材料のエレクトロルミネッセンス(Electro Luminescence:EL)を利用し、有機薄膜に電界をかけると発光する現象を用いた有機EL素子を画素の発光素子(電気光学素子)として用いている。

【0015】

有機EL表示装置は次のような特長を持っている。すなわち、有機EL素子は、10V以下の印加電圧で駆動できるために低消費電力である。また、有機EL素子は、自発光素子であるために画像の視認性が高く、しかも、応答速度が数μsec程度と非常に高速であるために動画表示時の残像が発生しない。有機EL素子は、電流駆動型の電気光学素子である。電流駆動型の電気光学素子としては、有機EL素子の他に、無機EL素子、LED素子、半導体レーザー素子などを例示することができる。

【0016】

所定の直流電圧の信号線への書込みに当っては、信号線毎に設けられるサンプリングスイッチが用いられる。サンプリングスイッチは、所定の直流電圧に続いて入力される映像信号の信号電圧(階調電圧、即ち、階調に応じた電圧)についてもサンプリングし、信号線に書き込む。

【0017】

サンプリングスイッチの入力側には、当該サンプリングスイッチに対して所定の直流電圧を入力するアンプが接続された構成とすることができる。また、サンプリングスイッチは、複数の信号線を単位として入力ノードが共通に接続された構成とすることができる。このとき、サンプリングスイッチには、複数の信号線、即ち、複数の画素列に対応した映像信号の信号電圧が、所定の直流電圧に続いて時系列で入力される。この時系列で入力される階調電圧を、サンプリングスイッチは時分割でサンプリングして信号線に書き込むことになる。

【0018】

サンプリングスイッチによるサンプリングによって所定の直流電圧を信号線に書き込む際には、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチの入力ノード/出力ノードの電位が揺らされようとする。

【0019】

ここで、「チャージインジェクション」とは、サンプリングスイッチがMOSトランジスタから成る場合、ゲート電圧の極性が反転するときに、ゲート酸化膜に帯電していた電荷が入力ノード側、出力ノード側に移動することにより、伝達される電圧が変動する現象(過渡的誤差要因)を言う。また、「クロックフィードスルー」とは、サンプリングスイッチのオン/オフ時に、MOSトランジスタのゲート−ドレイン間とゲート−ソース間に存在する寄生容量に起因して、ゲート電圧が入力ノード/出力ノードの電位に影響を与える現象を言う。

【0020】

このチャージインジェクションやクロックフィードスルーの影響を吸収する、即ち、サンプリングスイッチの入力ノードの電位の揺れを吸収するために、本開示の駆動回路は、サンプリングスイッチの入力ノードに容量素子が接続された構成となっている。容量素子は、信号線毎に設ける構成とすることができる。また、サンプリングスイッチの入力ノードを、複数の信号線を単位として共通に接続した構成を採る場合には、容量素子は、共通に接続された入力ノードに1つ接続する、即ち、複数の信号線に対して1つ設ける構成とすることができる。また、容量素子をサンプリングスイッチの出力ノードにも設ける構成とすることができる。

【0021】

サンプリングスイッチは、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されて成るアナログスイッチ(トランスファスイッチ)とすることができる。このとき、容量素子として、MOS容量を用いるのが好ましい。MOS容量は、サンプリングスイッチを構成するPチャネルMOSトランジスタ及びNチャネルMOSトランジスタの各ゲート電極に対して互いに逆相の選択パルスを伝送する伝送線と、サンプリングスイッチの入力ノードとの間に接続されて用いられる。

【0022】

MOS容量は、PチャネルMOSトランジスタとNチャネルMOSトランジスタから成るサンプリングスイッチと逆相に動作することで、当該サンプリングスイッチの入力ノードの電位の揺れを吸収する。MOS容量のサイズとしては、そのゲート電極の面積が、サンプリングスイッチを構成するPチャネルMOSトランジスタ及びNチャネルMOSトランジスタの各ゲート電極の半分を目安とするのが好ましい。ここで、「半分」とは、厳密に半分である場合の他、実質的に半分である場合も含む。設計上あるいは製造上生ずる種々のばらつきの存在は許容される。

【0023】

本開示の駆動回路を用いる表示装置において、画素は、電気光学素子を駆動する駆動トランジスタ、信号線と駆動トランジスタのゲート電極との間に接続された書込みトランジスタ、及び、駆動トランジスタのゲート電極と一方のソース/ドレイン電極との間に接続された保持容量を少なくとも有する。

【0024】

そして、上記構成の画素は、画素を構成する素子の特性ばらつきを補正する機能、具体的には、製造プロセスのばらつきや経時変化などによる駆動トランジスタの閾値電圧の画素毎のばらつきを補正する閾値補正機能を持っている。そして、閾値補正処理の際に、サンプリングスイッチによってサンプリングされ、信号線に書き込まれる所定の直流電圧を当該補正処理の基準電圧として用いることができる。

【0025】

具体的には、サンプリングスイッチによってサンプリングされ、信号線にホールドされる所定の直流電圧は、書込みトランジスタによって画素内に書き込まれ(取り込まれ)、駆動トランジスタのゲート電極に印加される。このとき書き込まれた直流電圧は、駆動トランジスタのゲート電圧の初期化電圧となる。そして、この初期化電圧を基準とし、当該初期化電圧から駆動トランジスタの閾値電圧を減じた電圧に向けて当該駆動トランジスタのソース電圧を変化させる処理が、駆動トランジスタの閾値電圧の画素毎のばらつきを補正する閾値補正処理となる。

【0026】

<2.本開示の実施形態に係るアクティブマトリクス型有機EL表示装置>

[2−1.システム構成]

図1は、本開示の実施形態に係るアクティブマトリクス型有機EL表示装置の構成の概略を示すシステム構成図である。

【0027】

アクティブマトリクス型表示装置は、電気光学素子に流れる電流を、当該電気光学素子と同じ画素内に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタによって制御する表示装置である。絶縁ゲート型電界効果トランジスタとしては、典型的には、TFT(Thin Film Transistor;薄膜トランジスタ)が用いられる。

【0028】

ここでは、一例として、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子である例えば有機EL素子を、画素(画素回路)の発光素子として用いるアクティブマトリクス型有機EL表示装置の場合を例に挙げて説明する。

【0029】

図1に示すように、本実施形態に係る有機EL表示装置10は、有機EL素子を含む複数の画素20が行列状に2次元配置されて成る画素アレイ部30と、当該画素アレイ部30の周辺に配置される駆動回路部とを有する構成となっている。

【0030】

駆動回路部は、書込み走査回路40、電源供給走査回路50、及び、信号線駆動回路60等からなり、画素アレイ部30の各画素20を駆動する。これらの回路部40,50,60には、図示せぬタイミング信号生成部(タイミングジェネレータ)から各種のタイミング信号が供給される。信号線駆動回路60は、本開示の駆動回路である。

【0031】

画素20を構成する能動素子等は、例えば、シリコン基板などの半導体基板70上に形成される。書込み走査回路40、電源供給走査回路50、及び、信号線駆動回路60等については、図1に示すように、画素アレイ部30と同じ半導体基板70上に形成することもできるし、半導体基板70の外部回路として設けることもできる。

【0032】

尚、ここでは、画素20を構成する能動素子等を半導体基板70上に形成する形態を採る場合を例に挙げたが、ガラス基板等の透明絶縁基板上に形成する形態を採るようにすることも可能である。

【0033】

ここで、有機EL表示装置10がカラー表示対応の場合は、カラー画像を形成する単位となる1つの画素(単位画素)は複数の副画素(サブピクセル)から構成され、この副画素の各々が図1の画素20に相当することになる。より具体的には、カラー表示対応の表示装置では、1つの画素は、例えば、赤色(Red;R)光を発光する副画素、緑色(Green;G)光を発光する副画素、青色(Blue;B)光を発光する副画素の3つの副画素から構成される。

【0034】

但し、1つの画素としては、RGBの3原色の副画素の組み合わせに限られるものではなく、3原色の副画素に更に1色あるいは複数色の副画素を加えて1つの画素を構成することも可能である。より具体的には、例えば、輝度向上のために白色(White;W)光を発光する副画素を加えて1つの画素を構成したり、色再現範囲を拡大するために補色光を発光する少なくとも1つの副画素を加えて1つの画素を構成したりすることも可能である。

【0035】

画素アレイ部30には、m行n列の画素20の配列に対して、行方向(画素行の画素の配列方向)に沿って走査線311〜31mと電源供給線321〜32mとが画素行毎に配線されている。更に、m行n列の画素20の配列に対して、列方向(画素列の画素の配列方向)に沿って信号線331〜33nが画素列毎に配線されている。

【0036】

走査線311〜31mは、書込み走査回路40の対応する行の出力端にそれぞれ接続されている。電源供給線321〜32mは、電源供給走査回路50の対応する行の出力端にそれぞれ接続されている。信号線331〜33nは、信号線駆動回路60の対応する列の出力端にそれぞれ接続されている。

【0037】

書込み走査回路40は、クロックパルスckに同期してスタートパルスspを順にシフト(転送)するシフトレジスタ回路等によって構成されている。書込み走査回路40は、画素アレイ部30の各画素20への映像信号の信号電圧の書込みに際し、走査線31(311〜31m)に対して書込み走査信号WS(WS1〜WS m)を順次供給することによって画素アレイ部30の各画素20を行単位で順番に走査(線順次走査)する。

【0038】

電源供給走査回路50は、クロックパルスckに同期してスタートパルスspを順にシフトするシフトレジスタ回路等によって構成されている。電源供給走査回路50は、書込み走査回路40による線順次走査に同期して、第1電源電位Vcc_Hと当該第1電源電位Vcc_Hよりも低い第2電源電位Vcc_Lとで切替え可能な電源電位DS(DS1〜DSm)を電源供給線32(321〜32m)に供給する。後述するように、電源電位DSのVcc_H/Vcc_Lの切替えにより、画素20の発光/非発光(消光)の制御が行なわれる。

【0039】

信号線駆動回路60は、本開示の駆動回路であって、信号供給源(図示せず)から供給される映像信号の信号電圧(以下、単に「信号電圧」と記述する場合もある)Vsigと、所定の直流電圧である基準電圧Vofstとを選択的に信号線331〜33nに書き込む。ここで、信号電圧Vsigは、階調(輝度情報)に応じた電圧(即ち、階調電圧)である。また、基準電圧Vofstは、映像信号の信号電圧Vsigの基準となる電圧(例えば、映像信号の黒レベルに相当する電圧)であり、後述する閾値補正処理の際に用いられる。

【0040】

この信号線駆動回路60の具体的な回路構成が本開示の特徴とするところであり、その詳細については後述する。

【0041】

信号線駆動回路60から出力される映像信号の信号電圧Vsig/基準電圧Vofstは、信号線33(331〜33n)を介して画素アレイ部30の各画素20に対して、書込み走査回路40による走査によって選択された画素行の単位で書き込まれる。すなわち、信号線駆動回路60は、信号電圧Vsigを行(ライン)単位で書き込む線順次書込みの駆動形態を採っている。

【0042】

[2−2.画素回路]

図2は、画素(画素回路)20の具体的な回路構成の一例を示す回路図である。画素20の発光部は、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子である有機EL素子21から成る。

【0043】

図2に示すように、画素20は、有機EL素子21と、有機EL素子21に電流を流すことによって当該有機EL素子21を駆動する駆動回路とによって構成されている。有機EL素子21は、全ての画素20に対して共通に配線された共通電源供給線34にカソード電極が接続されている。

【0044】

有機EL素子21を駆動する駆動回路は、例えば、駆動トランジスタ22、書込みトランジスタ23、及び、保持容量24を有する構成となっている。駆動トランジスタ22及び書込みトランジスタ23としてNチャネル型のTFTを用いることができる。但し、ここで示した、駆動トランジスタ22及び書込みトランジスタ23の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。

【0045】

駆動トランジスタ22は、一方の電極(ソース/ドレイン電極)が有機EL素子21のアノード電極に接続され、他方の電極(ソース/ドレイン電極)が電源供給線32(321〜32m)に接続されている。

【0046】

書込みトランジスタ23は、一方の電極(ソース/ドレイン電極)が信号線33(331〜33n)に接続され、他方の電極(ソース/ドレイン電極)が駆動トランジスタ22のゲート電極に接続されている。また、書込みトランジスタ23のゲート電極は、走査線31(311〜31m)に接続されている。

【0047】

駆動トランジスタ22及び書込みトランジスタ23において、一方の電極とは、一方のソース/ドレイン領域に電気的に接続された金属配線を言い、他方の電極とは、他方のソース/ドレイン領域に電気的に接続された金属配線を言う。また、一方の電極と他方の電極との電位関係によって一方の電極がソース電極ともなればドレイン電極ともなり、他方の電極がドレイン電極ともなればソース電極ともなる。

【0048】

保持容量24は、一方の電極が駆動トランジスタ22のゲート電極に接続され、他方の電極が駆動トランジスタ22の他方の電極、及び、有機EL素子21のアノード電極に接続されている。

【0049】

尚、有機EL素子21の駆動回路としては、駆動トランジスタ22及び書込みトランジスタ23の2つのトランジスタと保持容量24の1つの容量素子とからなる回路構成のものに限られるものではない。一例として、一方の電極が有機EL素子21のアノード電極に、他方の電極が固定電位にそれぞれ接続されることで、有機EL素子21の容量不足分を補う補助容量を必要に応じて設けた回路構成を採ることも可能である。

【0050】

上記構成の画素20において、書込みトランジスタ23は、書込み走査回路40から走査線31を通してゲート電極に印加されるHighアクティブの書込み走査信号WSに応答して導通状態となる。これにより、書込みトランジスタ23は、信号線33を通して信号線駆動回路60から供給される、輝度情報に応じた映像信号の信号電圧Vsigまたは基準電圧Vofstをサンプリングして画素20内に書き込む(取り込む)。書込みトランジスタ23によって書き込まれた信号電圧Vsigまたは基準電圧Vofstは、駆動トランジスタ22のゲート電極に印加されるとともに保持容量24に保持される。

【0051】

駆動トランジスタ22は、電源供給線32(321〜32m)の電源電位DSが第1電源電位Vcc_Hにあるときには、一方の電極がドレイン電極、他方の電極がソース電極となって飽和領域で動作する。これにより、駆動トランジスタ22は、電源供給線32から電流の供給を受けて有機EL素子21を電流駆動にて発光駆動する。より具体的には、駆動トランジスタ22は、飽和領域で動作することにより、保持容量24に保持された信号電圧Vsigの電圧値に応じた電流値の駆動電流を有機EL素子21に供給し、当該有機EL素子21を電流駆動することによって発光させる。

【0052】

駆動トランジスタ22は更に、電源電位DSが第1電源電位Vcc_Hから第2電源電位Vcc_Lに切り替わったときには、一方の電極がソース電極、他方の電極がドレイン電極となってスイッチングトランジスタとして動作する。これにより、駆動トランジスタ22は、有機EL素子21への駆動電流の供給を停止し、有機EL素子21を非発光状態にする。すなわち、駆動トランジスタ22は、有機EL素子21の発光/非発光を制御するトランジスタとしての機能をも併せ持っている。

【0053】

この駆動トランジスタ22のスイッチング動作により、有機EL素子21が非発光状態となる期間(非発光期間)を設け、有機EL素子21の発光期間と非発光期間の割合(デューティ)を制御することができる。このデューティ制御により、1表示フレーム期間に亘って画素が発光することに伴う残像ボケを低減できるために、特に、動画の画品位をより優れたものとすることができる。

【0054】

電源供給走査回路50から電源供給線32を通して選択的に供給される第1,第2電源電位Vcc_H,Vcc_Lのうち、第1電源電位Vcc_Hは有機EL素子21を発光駆動する駆動電流を駆動トランジスタ22に供給するための電源電位である。また、第2電源電位Vcc_Lは、有機EL素子21に対して逆バイアスを掛けるための電源電位である。この第2電源電位Vcc_Lは、基準電圧Vofstよりも低い電位、例えば、駆動トランジスタ22の閾値電圧をVthとするときVofst−Vthよりも低い電位、好ましくは、Vofst−Vthよりも十分に低い電位に設定される。

【0055】

[2−3.基本的な回路動作]

続いて、上記構成の有機EL表示装置10の基本的な回路動作について、図3のタイミング波形図を用いて説明する。図3のタイミング波形図には、書込み走査信号WS、電源電位DS(Vcc_H/Vcc_L)、信号線33の電位(Vsig/Vofst)、駆動トランジスタ22のゲート電位Vg及びソース電位Vsのそれぞれの変化を示している。

【0056】

(前表示フレームの発光期間)

図3のタイミング波形図において、時刻t11以前は、前の表示フレームにおける有機EL素子21の発光期間となる。この前表示フレームの発光期間では、電源供給線32の電位DSが第1電源電位(以下、「高電位」と記述する)Vcc_Hにあり、また、書込みトランジスタ23が非導通状態にある。

【0057】

このとき、駆動トランジスタ22は飽和領域で動作するように設定されている。これにより、駆動トランジスタ22のゲート−ソース間電圧Vgsに応じた駆動電流(ドレイン−ソース間電流)Idsが、電源供給線32から駆動トランジスタ22を通して有機EL素子21に供給される。従って、有機EL素子21が駆動電流Idsの電流値に応じた輝度で発光する。

【0058】

(初期化期間)

時刻t11になると、線順次走査の新しい表示フレーム(現表示フレーム)に入る。そして、電源供給線32の電位DSが高電位Vcc_Hから、信号線33の基準電圧Vofstに対してVofst−Vthよりも十分に低い第2電源電位(以下、「低電位」と記述する)Vcc_Lに切り替わる。

【0059】

ここで、有機EL素子21の閾値電圧をVthel、共通電源供給線34の電位(カソード電位)をVcathとする。このとき、低電位Vcc_LをVcc_L<Vthel+Vcathとすると、駆動トランジスタ22のソース電位Vsが低電位Vcc_Lにほぼ等しくなるために、有機EL素子21は逆バイアス状態となって消光する。

【0060】

次に、時刻t12で走査線31の電位WSが低電位側から高電位側に遷移することで、書込みトランジスタ23が導通状態となる。このとき、信号線駆動回路60から信号線33に対して基準電圧Vofstが供給された状態にあるために、駆動トランジスタ22のゲート電位Vgが基準電圧Vofstになる。また、駆動トランジスタ22のソース電位Vsは、基準電圧Vofstよりも十分に低い電位、即ち、低電位Vcc_Lにある。

【0061】

このとき、駆動トランジスタ22のゲート−ソース間電圧Vgsは(Vofst−Vcc_L)となる。ここで、(Vofst−Vcc_L)が駆動トランジスタ22の閾値電圧Vthよりも大きくないと、後述する閾値補正処理を行うことができないため、Vofst−Vcc_L>Vthなる電位関係に設定する必要がある。

【0062】

このように、駆動トランジスタ22のゲート電位Vgを基準電圧Vofstに固定し、かつ、ソース電位Vsを低電位Vcc_Lに固定する(確定させる)処理が、後述する閾値補正処理(閾値補正動作)を行う前の初期化の処理である。従って、基準電圧Vofst及び低電位Vcc_Lが、駆動トランジスタ22のゲート電位Vg及びソース電位Vsの各初期化電位となる。

【0063】

(閾値補正期間)

次に、時刻t13で、電源供給線32の電位DSが低電位Vcc_Lから高電位Vcc_Hに切り替わると、駆動トランジスタ22のゲート電位Vgが基準電圧Vofstに保たれた状態で閾値補正処理が開始される。すなわち、ゲート電位Vgから駆動トランジスタ22の閾値電圧Vthを減じた電位に向けて駆動トランジスタ22のソース電位Vsが上昇を開始する。

【0064】

ここでは、便宜上、駆動トランジスタ22のゲート電位Vgの初期化電位Vofstを基準とし、当該初期化電位Vofstから駆動トランジスタ22の閾値電圧Vthを減じた電位に向けてソース電位Vsを変化させる処理を閾値補正処理と呼んでいる。この閾値補正処理が進むと、やがて、駆動トランジスタ22のゲート−ソース間電圧Vgsが駆動トランジスタ22の閾値電圧Vthに収束する。この閾値電圧Vthに相当する電圧は保持容量24に保持される。

【0065】

尚、閾値補正処理を行う期間(閾値補正期間)において、電流が専ら保持容量24側に流れ、有機EL素子21側には流れないようにするために、有機EL素子21がカットオフ状態となるように共通電源供給線34の電位Vcathを設定しておくこととする。

【0066】

次に、時刻t14で、書込み走査信号WSが低電位側に遷移することで、書込みトランジスタ23が非導通状態となる。このとき、駆動トランジスタ22のゲート電極が信号線33から電気的に切り離されることによってフローティング状態になる。しかし、ゲート−ソース間電圧Vgsが駆動トランジスタ22の閾値電圧Vthに等しいために、当該駆動トランジスタ22はカットオフ状態にある。従って、駆動トランジスタ22にドレイン−ソース間電流Idsは流れない。

【0067】

(信号書込み&移動度補正期間)

次に、時刻t15で、信号線33の電位が基準電圧Vofstから映像信号の信号電圧Vsigに切り替わる。続いて、時刻t16で、書込み走査信号WSが高電位側に遷移することで、書込みトランジスタ23が導通状態になって映像信号の信号電圧Vsigをサンプリングし、画素20内に書き込む。

【0068】

この書込みトランジスタ23による信号電圧Vsigの書込みにより、駆動トランジスタ22のゲート電位Vgが信号電圧Vsigになる。そして、映像信号の信号電圧Vsigによる駆動トランジスタ22の駆動の際に、当該駆動トランジスタ22の閾値電圧Vthが保持容量24に保持された閾値電圧Vthに相当する電圧と相殺される。この閾値キャンセルの原理の詳細については後述する。

【0069】

このとき、有機EL素子21は、カットオフ状態(ハイインピーダンス状態)にある。従って、映像信号の信号電圧Vsigに応じて電源供給線32から駆動トランジスタ22に流れる電流(ドレイン−ソース間電流Ids)は、有機EL素子21の等価容量に流れ込む。これにより、有機EL素子21の等価容量の充電が開始される。

【0070】

有機EL素子21の等価容量が充電されることにより、駆動トランジスタ22のソース電位Vsが時間の経過とともに上昇していく。このとき既に、駆動トランジスタ22の閾値電圧Vthの画素毎のばらつきがキャンセルされており、駆動トランジスタ22のドレイン−ソース間電流Idsは、当該駆動トランジスタ22の移動度μに依存したものとなる。尚、駆動トランジスタ22の移動度μは、当該駆動トランジスタ22のチャネルを構成する半導体薄膜の移動度である。

【0071】

ここで、映像信号の信号電圧Vsigに対する保持容量24の保持電圧Vgsの比率、即ち、書込みゲインGが1(理想値)であると仮定する。すると、駆動トランジスタ22のソース電位Vsが(Vofst−Vth+ΔV)の電位まで上昇することで、駆動トランジスタ22のゲート‐ソース間電圧Vgsは(Vsig−Vofst+Vth−ΔV)となる。

【0072】

すなわち、駆動トランジスタ22のソース電位Vsの上昇分ΔVは、保持容量24に保持された電圧(Vsig−Vofst+Vth)から差し引かれるように、換言すれば、保持容量24の充電電荷を放電するように作用する。これにより、ソース電位Vsの上昇分ΔVは、保持容量24に対して負帰還がかけられたことになる。従って、ソース電位Vsの上昇分ΔVは負帰還の帰還量となる。

【0073】

このように、駆動トランジスタ22に流れるドレイン−ソース間電流Idsに応じた帰還量ΔVでゲート‐ソース間電圧Vgsに負帰還をかけることで、駆動トランジスタ22のドレイン−ソース間電流Idsの移動度μに対する依存性を打ち消すことができる。この打ち消す処理が、駆動トランジスタ22の移動度μの画素毎のばらつきを補正する移動度補正処理である。

【0074】

より具体的には、駆動トランジスタ22のゲート電極に書き込まれる映像信号の信号振幅Vin(=Vsig−Vofst)が高い程ドレイン−ソース間電流Idsが大きくなるため、負帰還の帰還量ΔVの絶対値も大きくなる。従って、発光輝度レベルに応じた移動度補正処理が行われる。

【0075】

また、映像信号の信号振幅Vinを一定とした場合、駆動トランジスタ22の移動度μが大きいほど負帰還の帰還量ΔVの絶対値も大きくなるため、画素毎の移動度μのばらつきを取り除くことができる。従って、負帰還の帰還量ΔVは、移動度補正処理の補正量とも言える。移動度補正の原理の詳細については後述する。

【0076】

(発光期間)

次に、時刻t17で、書込み走査信号WSが低電位側に遷移することで、書込みトランジスタ23が非導通状態となる。これにより、駆動トランジスタ22のゲート電極は、信号線33から電気的に切り離されるためにフローティング状態になる。

【0077】

ここで、駆動トランジスタ22のゲート電極がフローティング状態にあるときは、駆動トランジスタ22のゲート−ソース間に保持容量24が接続されていることで、駆動トランジスタ22のソース電位Vsの変動に連動してゲート電位Vgも変動する。すなわち、駆動トランジスタ22のソース電位Vs、ゲート電位Vgは、保持容量24に保持されているゲート−ソース間電圧Vgsを保持したまま上昇する。そして、駆動トランジスタ22のソース電位Vsは、トランジスタの飽和電流Idsに応じた有機EL素子21の発光電圧Voledまで上昇する。

【0078】

このように、駆動トランジスタ22のゲート電位Vgがソース電位Vsの変動に連動して変動する動作がブートストラップ動作である。換言すれば、ブートストラップ動作は、保持容量24に保持されたゲート−ソース間電圧Vgs、即ち、保持容量24の両端間電圧を保持したまま、ゲート電位Vg及びソース電位Vsが変動する動作である。

【0079】

駆動トランジスタ22のゲート電極がフローティング状態になり、それと同時に、駆動トランジスタ22のドレイン−ソース間電流Idsが有機EL素子21に流れ始めることにより、当該電流Idsに応じて有機EL素子21のアノード電位が上昇する。そして、有機EL素子21のアノード電位が(Vthel+Vcath)を越えると、有機EL素子21に駆動電流が流れ始めるため有機EL素子21が発光を開始する。

【0080】

有機EL素子21の発光電流は、このときのゲート−ソース間電圧Vgsによって駆動トランジスタ22の飽和電流Idsにより規定される。このため、駆動トランジスタ22は、各信号電圧Vsigにおける定電流源となる。

【0081】

また、有機EL素子21のアノード電位の上昇は、即ち、駆動トランジスタ22のソース電位Vsの上昇に他ならない。そして、駆動トランジスタ22のソース電位Vsが上昇すると、保持容量24のブートストラップ動作により、駆動トランジスタ22のゲート電位Vgも連動して上昇する。

【0082】

このとき、ブートストラップゲインが1(理想値)であると仮定した場合、ゲート電位Vgの上昇量はソース電位Vsの上昇量に等しくなる。故に、発光期間中は、駆動トランジスタ22のゲート‐ソース間電圧Vgsは、(Vsig−Vofst+Vth−ΔV)で一定に保持される。

【0083】

以上説明した一連の回路動作において、閾値補正準備、閾値補正、信号電圧Vsigの書込み(信号書込み)、及び、移動度補正の各処理動作は、1水平期間(1H)において実行される。また、信号書込み及び移動度補正の各処理動作は、時刻t16−t17の期間において並行して実行される。

【0084】

〔分割閾値補正〕

尚、ここでは、閾値補正処理を1回だけ実行する駆動法を採る場合を例に挙げて説明したが、この駆動法は一例に過ぎず、この駆動法に限られるものではない。例えば、閾値補正処理を移動度補正及び信号書込み処理と共に行う1H期間に加えて、当該1H期間に先行する複数の水平期間に亘って分割して閾値補正処理を複数回実行する、所謂、分割閾値補正を行う駆動法を採ることも可能である。

【0085】

この分割閾値補正の駆動法によれば、高精細化に伴う多画素化によって1水平期間として割り当てられる時間が短くなったとしても、閾値補正期間として複数の水平期間に亘って十分な時間を確保することができる。従って、1水平期間として割り当てられる時間が短くなっても、閾値補正期間として十分な時間を確保できるため、閾値補正処理を確実に実行できることになる。

【0086】

〔閾値キャンセルの原理〕

ここで、駆動トランジスタ22の閾値キャンセル(即ち、閾値補正)の原理について説明する。駆動トランジスタ22は、飽和領域で動作するように設計されているために定電流源として動作する。これにより、有機EL素子21には駆動トランジスタ22から、次式(1)で与えられる一定のドレイン−ソース間電流(駆動電流)Idsが供給される。

Ids=(1/2)・μ(W/L)Cox(Vgs−Vth)2 ……(1)

ここで、Wは駆動トランジスタ22のチャネル幅、Lはチャネル長、Coxは単位面積当たりのゲート容量である。

【0087】

図4(A)に、駆動トランジスタ22のドレイン−ソース間電流Ids対ゲート−ソース間電圧Vgsの特性を示す。図4(A)の特性図に示すように、駆動トランジスタ22の閾値電圧Vthの画素毎のばらつきに対するキャンセル処理(補正処理)を行わないと、閾値電圧VthがVth1のときに、ゲート−ソース間電圧Vgsに対応するドレイン−ソース間電流IdsがIds1になる。

【0088】

これに対して、閾値電圧VthがVth2(Vth2>Vth1)のとき、同じゲート−ソース間電圧Vgsに対応するドレイン−ソース間電流IdsがIds2(Ids2<Ids1)になる。すなわち、駆動トランジスタ22の閾値電圧Vthが変動すると、ゲート−ソース間電圧Vgsが一定であってもドレイン−ソース間電流Idsが変動する。

【0089】

一方、上記構成の画素(画素回路)20では、先述したように、発光時の駆動トランジスタ22のゲート−ソース間電圧VgsはVsig−Vofst+Vth−ΔVである。従って、これを式(1)に代入すると、ドレイン−ソース間電流Idsは、次式(2)で表される。

Ids=(1/2)・μ(W/L)Cox(Vsig−Vofst−ΔV)2 ……(2)

【0090】

すなわち、駆動トランジスタ22の閾値電圧Vthの項がキャンセルされており、駆動トランジスタ22から有機EL素子21に供給されるドレイン−ソース間電流Idsは、駆動トランジスタ22の閾値電圧Vthに依存しない。その結果、駆動トランジスタ22の製造プロセスのばらつきや経時変化等により、駆動トランジスタ22の閾値電圧Vthが画素毎に変動したとしても、ドレイン−ソース間電流Idsが変動しないために、有機EL素子21の発光輝度を一定に保つことができる。

【0091】

〔移動度補正の原理〕

次に、駆動トランジスタ22の移動度補正の原理について説明する。図4(B)に、駆動トランジスタ22の移動度μが相対的に大きい画素Aと、駆動トランジスタ22の移動度μが相対的に小さい画素Bとを比較した状態で特性カーブを示す。

【0092】

画素Aと画素Bで移動度μにばらつきがある状態で、駆動トランジスタ22のゲート電極に対して、例えば両画素A,Bに同レベルの信号振幅Vin(=Vsig−Vofst)を書き込んだ場合を考える。この場合、何ら移動度μの補正を行わないと、移動度μの大きい画素Aに流れるドレイン−ソース間電流Ids1′と移動度μの小さい画素Bに流れるドレイン−ソース間電流Ids2′との間には大きな差が生じてしまう。このように、移動度μの画素毎のばらつきに起因してドレイン−ソース間電流Idsに画素間で大きな差が生じると、画面のユニフォーミティ(一様性)が損なわれる。

【0093】

ここで、先述した式(1)のトランジスタ特性式から明らかなように、移動度μが大きいとドレイン−ソース間電流Idsが大きくなる。従って、負帰還における帰還量ΔVは移動度μが大きくなるほど大きくなる。図4(B)に示すように、移動度μの大きな画素Aの帰還量ΔV1は、移動度の小さな画素Bの帰還量ΔV2に比べて大きい。

【0094】

そこで、移動度補正処理によって駆動トランジスタ22のドレイン−ソース間電流Idsに応じた帰還量ΔVでゲート−ソース間電圧Vgsに負帰還をかけることにより、移動度μが大きいほど負帰還が大きくかかることになる。その結果、移動度μの画素毎のばらつきを抑制することができる。

【0095】

具体的には、移動度μの大きな画素Aで帰還量ΔV1の補正をかけると、ドレイン−ソース間電流IdsはIds1′からIds1まで大きく下降する。一方、移動度μの小さな画素Bの帰還量ΔV2は小さいために、ドレイン−ソース間電流IdsはIds2′からIds2までの下降となり、それ程大きく下降しない。結果的に、画素Aのドレイン−ソース間電流Ids1と画素Bのドレイン−ソース間電流Ids2とはほぼ等しくなるために、移動度μの画素毎のばらつきが補正される。

【0096】

以上をまとめると、移動度μの異なる画素Aと画素Bがあった場合、移動度μの大きい画素Aの帰還量ΔV1は移動度μの小さい画素Bの帰還量ΔV2に比べて大きくなる。つまり、移動度μが大きい画素ほど帰還量ΔVが大きく、ドレイン−ソース間電流Idsの減少量が大きくなる。

【0097】

従って、駆動トランジスタ22のドレイン−ソース間電流Idsに応じた帰還量ΔVで、ゲート−ソース間電圧Vgsに負帰還をかけることで、移動度μの異なる画素のドレイン−ソース間電流Idsの電流値が均一化される。その結果、移動度μの画素毎のばらつきを補正することができる。すなわち、駆動トランジスタ22に流れる電流(ドレイン−ソース間電流Ids)に応じた帰還量(補正量)ΔVで、駆動トランジスタ22のゲート−ソース間電圧Vgsに対して、即ち、保持容量24に対して負帰還をかける処理が移動度補正処理となる。

【0098】

[2−4.信号線駆動回路]

本開示の駆動回路である、実施形態に係る信号線駆動回路60は、信号供給源から順に入力される基準電圧Vofst及び信号電圧(階調電圧)Vsigを、サンプリングスイッチによるサンプリングによって信号線33(331〜33n)に書き込む。この書込みの際に、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーが、基準電圧Vofstの書込み動作に悪影響を及ぼす。

【0099】

ここで、理解を容易にするために、サンプリングスイッチSWがNチャネルMOSトランジスタから成る場合を例に挙げて、サンプリングスイッチSWのスイッチング時、特にオフ時のチャージインジェクション及びクロックフィードスルーの影響について、図5を用いて説明する。

【0100】

図5において、サンプリングスイッチSW及び負荷容量Cによってサンプルホールド回路が形成されている。負荷容量Cは、信号線33(331〜33n)の寄生容量などである。このサンプルホールド回路において、サンプリングスイッチSWによってサンプリングされた電圧は、当該サンプリングスイッチSWのオフタイミング(即ち、ホールドタイミング)で信号線33に書き込まれ、ホールドされる。

【0101】

ここで、サンプリングスイッチSWの入力信号の電圧値をVinとし、ゲート電極に与えられる制御パルス(選択パルス)ENの正側の電圧値をVddとし、負側の電圧値を0とする。また、NチャネルMOSトランジスタのチャネル長をL、チャネル幅をW、閾値電圧をVth、ゲート酸化膜容量をCox、オーバーラップ容量をCovとする。オーバーラップ容量Covは、ゲート電極とソース領域やドレイン領域とがオーバーラップする領域に存在する寄生容量である。

【0102】

サンプリングスイッチSWがオフするとき、即ち、制御パルスENがVddから0に遷移するときのチャージインジェクションの影響による電位の変動量ΔVchは、

ΔVch=1/2×W・L・Cox(Vdd−Vin−Vth)/C

となる。また、クロックフィードスルーの影響による電位の変動量ΔVclは、

ΔVcl=Vdd×Cov/(Cov+C)

となる。

【0103】

このサンプリングスイッチSWのオフ時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチSWの入力ノードの電位が変動(変動量ΔVch/ΔVcl)すると、所望の電圧値の基準電圧Vofstを信号線33に書き込めないことになる。先述したように、基準電圧Vofstは閾値補正処理の基準となる電圧であることから、所望の電圧値の基準電圧Vofstを信号線33に書き込めないということは、閾値補正処理を正常に実行できないということになる。

【0104】

本開示の駆動回路は、サンプリングスイッチのスイッチング時、特にオフ時のチャージインジェクションやクロックフィードスルーの影響が、サンプリングスイッチの入力ノード側に及ぶときの不具合を解消すべく為された信号線駆動回路である。以下に、本開示の駆動回路の具体的な実施例について説明する。

【0105】

(2−4−1.実施例1)

図6は、実施例1に係る信号線駆動回路の回路構成を示す回路図である。

【0106】

図6において、実施例1に係る信号線駆動回路60Aは、図1に示す画素アレイ部30におけるn本の信号線331〜33nについて、i本の信号線331〜33iを単位として、アンプ61から入力電圧が与えられる構成となっている。ここでは、図面の簡略化のために、i本の信号線331〜33iに対応する回路構成について図示している。

【0107】

アンプ61から与えられる入力電圧は、所定の直流電圧である基準電圧Vofstと、当該基準電圧Vofstに続いて時系列で入力されるi列分の信号電圧(階調電圧)Vsigである。アンプ61の前段側には、例えば、デジタル信号をアナログ信号に変換するDAコンバータ(図示せず)が配置されており、当該DAコンバータの出力DACoutがアンプ61の非反転(+)入力端子に入力される。

【0108】

DAコンバータは、信号線駆動回路60Aに対して基準電圧Vofst及び信号電圧Vsigを供給する信号供給源を構成している。アンプ61は、反転(−)入力端子と出力端子とが電気的に接続されており、DAコンバータを含む信号供給源の出力段を構成している。

【0109】

一般的には、画素アレイ部30のn本の信号線331〜33nの各々に対して1対1の対応関係をもって信号供給源が設けられる。これに対し、本信号線駆動回路60Aのように、i本の信号線331〜33iを単位として信号供給源を設けることにより、信号供給源、即ち、DAコンバータやアンプ61の数を大幅に削減できるため、システムの回路構成の簡略化を図ることができる利点がある。

【0110】

信号線駆動回路60Aは、i本の信号線331〜33i毎に設けられたサンプリングスイッチ621〜62iを有する。サンプリングスイッチ621〜62iは、信号線331〜33iの寄生容量などと共にサンプルホールド回路を形成し、アンプ61から入力される基準電圧Vofstを一斉にサンプリングし、オフタイミング(ホールドタイミング)で信号線331〜33iにホールドする。サンプリングスイッチ621〜62iは更に、基準電圧Vofstに続いてアンプ61から時系列で入力される信号電圧Vsigを時分割にてサンプリングし、信号線331〜33iに順に書き込む。

【0111】

サンプリングスイッチ621〜62iは、例えば、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されたアナログスイッチ(トランスファスイッチ)によって構成されている。そして、サンプリングスイッチ621〜62iは、互いに逆相の選択パルスSEL,xSEL(SEL1〜SELi,xSEL1〜xSELi)に応じてスイッチング動作(オン/オフ動作)を行うことによって基準電圧Vofst/信号電圧Vsigをサンプルホールドする。

【0112】

正相の選択パルスSEL(SEL1〜SELi)は、サンプリングスイッチ621〜62iを構成するNチャネルMOSトランジスタのゲート電極に対して伝送線La(La1〜Lai)によって伝送される。逆相の選択パルスxSEL(xSEL1〜xSELi)は、サンプリングスイッチ621〜62iを構成するPチャネルMOSトランジスタのゲート電極に対して伝送線Lb(Lb1〜Lbi)によって伝送される。

【0113】

サンプリングスイッチ621〜62iの入力ノードNin(Nin_1〜Nin_i)と、伝送線La(La1〜Lai),Lb(Lb1〜Lbi)との間には、容量素子63(631〜63i)が接続されている。容量素子631〜63iは、例えばMOS容量から成る。具体的には、容量素子631〜63iは、サンプリングスイッチ621〜62iの各入力ノードNinと伝送線Laとの間に接続されたPチャネルMOSトランジスタと、サンプリングスイッチ621〜62iの各入力ノードNinと伝送線Lbとの間に接続されたNチャネルMOSトランジスタとから成る。容量素子631〜63iのトランジスタサイズは、サンプリングスイッチ621〜62iを構成するトランジスタの半分のゲート面積が目安である。

【0114】

サンプリングスイッチ621〜62iの出力ノードNout(Nout_1〜Nout_i)と、伝送線La(La1〜Lai),Lb(Lb1〜Lbi)との間には、容量素子64(641〜64i)が接続されている。容量素子641〜64iも、容量素子631〜63iと同様に、MOS容量から成る。具体的には、容量素子641〜64iは、サンプリングスイッチ621〜62iの各出力ノードNoutと伝送線Laとの間に接続されたPチャネルMOSトランジスタと、サンプリングスイッチ621〜62iの各出力ノードNoutと伝送線Lbとの間に接続されたNチャネルMOSトランジスタとから成る。容量素子641〜64iのトランジスタサイズは、サンプリングスイッチ621〜62iを構成するトランジスタの半分のゲート面積が目安である。

【0115】

続いて、上記構成の実施例1に係る信号線駆動回路60Aの回路動作について、図7のタイミング波形図を用いて、図8の動作説明図を参照しつつ説明する。図7のタイミング波形図において、PIX1〜PIXiは、信号線331〜33iの電位を表わしている。ここでは、基準電圧Vofstをi本の信号線331〜33iに書き込む際の動作について説明し、信号電圧Vsigの書込み動作については省略するものとする。

【0116】

基準電圧Vofstの書込みのために、選択パルスSEL,xSEL(SEL1〜SELi,xSEL1〜xSELi)に応答して、全サンプリングスイッチ621〜62iがオン状態となる。そして、基準電圧Vofstの書込みが完了すると、全サンプリングスイッチ621〜62iがオフ状態となる。

【0117】

サンプリングスイッチ621〜62iがオフ状態となる瞬間、サンプリングスイッチ621〜62iのチャージインジェクションやクロックフィードスルーの影響によって、サンプリングスイッチ621〜62iの各入力ノードNin_1〜Nin_iの電位(即ち、アンプ61の出力電位)が揺らされようとする。特に、サンプリングスイッチ621〜62iの入力ノードNin_1〜Nin_iに対して、図8に破線の矢印で示すように、NチャネルMOSトランジスタ分のチャージインジェクションの影響が及ぶ。

【0118】

このサンプリングスイッチ621〜62iのオフ時には、サンプリングスイッチ621〜62iの各入力ノードNin_1〜Nin_iに接続された容量素子631〜63iが、サンプリングスイッチ621〜62iと逆相に動作する。この逆相の動作による容量素子631〜63iの作用により、サンプリングスイッチ621〜62iのオフ時に生じたチャージインジェクションやクロックフィードスルーの影響、換言すれば、当該影響による入力ノードNin_1〜Nin_iの電位の揺れが抑えられる。

【0119】

すなわち、容量素子631〜63iによって入力ノードNin_1〜Nin_iの電位(即ち、アンプ61の出力電位)の揺れが吸収され、これらの入力ノードNin_1〜Nin_iには、予め規定した所望の電圧値の基準電圧Vofstが与えられる。これにより、図7のタイミング波形図に示すように、選択パルスSEL1〜SELiの相互間にオフ時のタイミング(即ち、ホールドタイミング)に微小なずれが生じていたとしても、所望の電圧値の基準電圧Vofstを信号線331〜33iに書き込むことができる。

【0120】

一方、サンプリングスイッチ621〜62iの出力ノードNout_1〜Nout_iに接続された容量素子641〜64iは、サンプリングスイッチ621〜62iのスイッチング時のチャージインジェクションやクロックフィードスルーの出力ノードNout_1〜Nout_iに対する影響を吸収する作用を為す。

【0121】

本実施例1では、サンプリングスイッチ621〜62iの入力ノード/出力ノードの両側に容量素子631〜63i,641〜64iを設ける構成としたが、これは好ましい実施の形態であって、出力ノード側の容量素子641〜64iは必須の構成要素ではない。すなわち、出力ノード側に容量素子641〜64iが存在しなくても、少なくとも、入力ノード側に容量素子631〜63iが存在することで、サンプリングスイッチ621〜62iのオフ時の入力ノードNin_1〜Nin_iの電位の揺れを抑える、という所期の目的を達成することができる。

【0122】

ここで、サンプリングスイッチ621〜62iの出力ノード側にのみ容量素子641〜64iを設けて成る信号線駆動回路について、参考例に係る信号線駆動回路として以下に説明する。

【0123】

(2−4−2.参考例)

図9は、参考例に係る信号線駆動回路の回路構成を示す回路図である。図9に示すように、参考例に係る信号線駆動回路60Bは、サンプリングスイッチ621〜62iの出力ノード側にのみ、即ち、出力ノードNout_1〜Nout_iと伝送線La1〜Lai,Lb1〜Lbiとの間に容量素子641〜64iが接続された構成となっている。

【0124】

参考例に係る信号線駆動回路60Bのタイミング波形図を図10に、動作説明図を図11にそれぞれ示す。

【0125】

参考例に係る信号線駆動回路60Bの場合、サンプリングスイッチ621〜62iがオフ状態となるタイミング(ホールドタイミング)で、図11に破線の矢印で示すように、Nチャネル分のチャージインジェクションの影響が及ぶ。これにより、図10に破線の○で囲って示すように、入力ノードNin_1〜Nin_iの電位(即ち、アンプ61の出力電位)が揺らされる。

【0126】

一方、サンプリングスイッチ621〜62iは、それぞれ独立したタイミングの選択パルスSEL1〜SELiによって制御される。選択パルスSEL1〜SELiには、これらパルスを生成する回路系や伝送系の定数のばらつき等によって、図10のタイミング波形図に示すように、微小なタイミングのずれが発生する。そして、選択パルスSEL1〜SELiのオフ時のタイミング(ホールドタイミング)の微小なタイミングずれにより、サンプリングスイッチ621〜62iによる入力ノードNin_1〜Nin_iの電位のホールドポイントが信号線331〜33i間でずれる。

【0127】

これにより、図10のタイミング波形図に示すように、基準電圧Vofstが書き込まれたときの信号線331〜33iの電位PIX1〜PINiにばらつき(ΔV1〜ΔVi)が生じる。すなわち、信号線331〜33iにホールドされた基準電圧Vofstの電圧値に信号線331〜33i間でばらつきが生じる。これは、サンプリングスイッチ621〜62iによって所望の電圧値の基準電圧Vofstをサンプルホールドできないこと、即ち、信号線331〜33iには異なる電圧値の基準電圧Vofstがホールドされる(書き込まれる)ことを意味する。

【0128】

基準電圧Vofstは、閾値補正処理の際に、駆動トランジスタ22のゲート電圧の初期化電圧として用いられる。従って、基準電圧Vofstの電圧値に信号線331〜33i間でばらつきが存在することで、1列目〜i列目の各画素列において、異なる電圧値の基準電圧Vofstを用いて閾値補正処理が行われることになる。その結果、基準電圧Vofstの電圧値の信号線331〜33i間でのばらつきが、表示画面上で縦筋(列方向の筋)として視認されるため、画品位(画質)の低下を招くことになる。

【0129】

このように、信号線331〜33iに書き込まれる基準電圧Vofstの電圧値の誤差は、サンプリングスイッチ621〜62iを制御する選択パルスSEL1〜SELiの動作タイミングに依存する。そして、参考例に係る信号線駆動回路60Bの場合は、半導体チップ(半導体基板)の絶対ばらつき、相対ばらつき、温度依存、電源依存などにより、画質が安定しない。

【0130】

尚、サンプリングスイッチ621〜62iのオフ時の入力ノードNin_1〜Nin_iの電位の揺れについては、サンプリングスイッチ621〜62iの前段のアンプ61でカバーすることもできる。しかし、この方策を採る場合には、非常に広帯域のアンプを用いる必要があり、消費電力の著しい増加を招くため好ましい方策とは言えない。

【0131】

これに対して、実施例1に係る信号線駆動回路60Aによれば、サンプリングスイッチ621〜62iの入力ノード側に容量素子631〜63iを配するだけの簡単な構成及び簡単な動作シーケンスにて、参考例に係る信号線駆動回路60Bの問題を解消することができる。すなわち、前段のアンプ61の消費電力を増加させることなく、また、半導体チップ(図1の半導体基板70)のサイズを増大させることなく、所望の電圧値の基準電圧Vofstを信号線331〜33iに書き込むことができる。その結果、各画素列において閾値補正処理をより確実に行うことができるため、輝度ムラのない均一な画質の表示画像を得ることができる。

【0132】

(2−4−3.実施例2)

図12は、実施例2に係る信号線駆動回路の回路構成を示す回路図である。

【0133】

実施例1に係る信号線駆動回路60Aでは、サンプリングスイッチ621〜62iの入力ノードNin_1〜Nin_iに接続する容量素子631〜63iを、i本の信号線331〜33i毎に設ける構成を採っていた。これに対し、実施例2に係る信号線駆動回路60Cでは、i本の信号線331〜33iを単位として当該単位毎に容量素子63を1つ設ける構成を採っている。

【0134】

具体的には、実施例2に係る信号線駆動回路60Cにおいて、サンプリングスイッチ621〜62iの入力ノードNin_1〜Nin_iは、i本の信号線331〜33iを単位として共通に接続されている。そして、この共通に接続された共通入力ノードNin_0と、例えば1列目の伝送線La1,Lb1との間に容量素子63が接続されている。

【0135】

容量素子63は、例えばMOS容量から成る。具体的には、容量素子63は、サンプリングスイッチ621〜62iの共通入力ノードNin_0と伝送線La1との間に接続されたPチャネルMOSトランジスタと、共通入力ノードNin_0と伝送線Lb1との間に接続されたNチャネルMOSトランジスタとから成る。容量素子63のトランジスタサイズは、サンプリングスイッチ621〜62iを構成するトランジスタの半分のゲート面積が目安である。

【0136】

このように、容量素子63をi本の信号線331〜33iを単位として1つ設ける構成を採る実施例2に係る信号線駆動回路60Cによれば、容量素子63を信号線331〜33i毎に設ける構成を採る実施例1に係る信号線駆動回路60Aよりも簡単な回路構成にて、同様の作用、効果を得ることができる。

【0137】

すなわち、サンプリングスイッチ621〜62iがオフする際、共通入力ノードNin_0に接続された容量素子63が、サンプリングスイッチ621と逆相に動作する。この逆相の動作による容量素子63の作用により、サンプリングスイッチ621〜62iのオフ時に生じたチャージインジェクションやクロックフィードスルーの影響、換言すれば、当該影響による共通入力ノードNin_0、ひいては、入力ノードNin_1〜Nin_iの電位の揺れを抑えることができる。

【0138】

これにより、選択パルスSEL1〜SELiの相互間にオフ時のタイミング(即ち、ホールドタイミング)に微小なずれが生じていたとしても、所望の電圧値の基準電圧Vofstを信号線331〜33iに書き込むことができる。但し、本例では、1列目の選択パルスSEL1,xSEL1によって容量素子63を動作させる構成を採っているため、選択パルスSEL1,xSEL1よりも早いタイミングで遷移する選択パルスが存在する場合には、当該選択パルスの画素列についてはタイミングずれを吸収することはできない。

【0139】

このような観点からすれば、単位となるi本の信号線331〜33iに対応する選択パルスSEL1〜SELi,xSEL1〜xSELiのうち、遷移タイミングが一番早い選択パルスを、容量素子63を動作させる選択パルスとし用いるのが好ましい。そうすることで、ホールドタイミングに微小なずれが生じていたとしても、全ての画素列について、タイミングずれを吸収することができる。

【0140】

<3.電子機器>

以上説明した本開示の表示装置の駆動回路は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示する表示部を有するあらゆる分野の電子機器において、その表示部(表示装置)の駆動回路として用いることが可能である。

【0141】

上述した実施形態の説明から明らかなように、本開示の表示装置の駆動回路は、半導体チップのサイズを増大させることなく、低消費電力にて、所望の電圧値の基準電圧Vofstを信号線に書き込むことができる。これにより、当該駆動回路を用いる表示装置にあっては、各画素列において閾値補正処理をより確実に行うことができるため、輝度ムラのない均一な画質の表示画像を得ることができる。従って、あらゆる分野の電子機器において、その表示部として本開示の駆動回路を有する表示装置を用いることで、より優れた画像表示を実現できる。

【0142】

本開示の駆動回路を有する表示装置を表示部として用いる電子機器としては、例えば、ヘッドマウントディスプレイ、デジタルカメラ、ビデオカメラや、PDA(Personal Digital Assistant)、ゲーム機、電子書籍等の携帯情報機器や、携帯電話機等の携帯通信機器などを例示することができる。

【0143】

<4.本開示の構成>

尚、本開示は以下のような構成を採ることができる。

(1)画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える表示装置の駆動回路。

(2)前記サンプリングスイッチは、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されて成るアナログスイッチである

前記(1)に記載の表示装置の駆動回路。

(3)前記容量素子は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極に対して互いに逆相の選択パルスを伝送する伝送線と前記入力ノードとの間に接続されたMOS容量である

前記(2)に記載の表示装置の駆動回路。

(4)前記MOS容量のゲート電極の面積は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極の面積の半分である

前記(3)に記載の表示装置の駆動回路。

(5)前記サンプリングスイッチの入力側には、当該サンプリングスイッチに対して前記所定の直流電圧を入力するアンプが接続されている

前記(1)から前記(4)のいずれかに記載の表示装置の駆動回路。

(6)前記サンプリングスイッチは、複数の信号線を単位として入力ノードが共通に接続されている

前記(1)から前記(5)のいずれかに記載の表示装置の駆動回路。

(7)前記容量素子は、前記複数の信号線を単位として共通に接続された共通入力ノードに1つ接続されている

前記(6)に記載の表示装置の駆動回路。

(8)前記複数の信号線に対応する複数のサンプリングスイッチを独立したタイミングで動作させる複数の選択パルスのうち、遷移タイミングが一番早い選択パルスを前記容量素子の動作に用いる

前記(7)に記載の表示装置の駆動回路。

(9)前記サンプリングスイッチは、前記所定の直流電圧に続いて時系列で入力される映像信号の信号電圧を時分割でサンプリングして前記信号線に書き込む

前記(6)から前記(8)のいずれかに記載の表示装置の駆動回路。

(10)前記サンプリングスイッチの出力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記出力ノードの電位の揺れを吸収する容量素子を有する

前記(1)から前記(9)のいずれかに記載の表示装置の駆動回路。

(11)前記画素は、電気光学素子を駆動する駆動トランジスタ、前記信号線と前記駆動トランジスタのゲート電極との間に接続された書込みトランジスタ、及び、前記駆動トランジスタのゲート電極と一方のソース/ドレイン電極との間に接続された保持容量を有する

前記(1)から前記(10)のいずれかに記載の表示装置の駆動回路。

(12)前記画素は、前記書込みトランジスタによって前記所定の直流電圧が書き込まれたときの前記駆動トランジスタのゲート電圧を初期化電圧とし、当該初期化電圧から前記駆動トランジスタの閾値電圧を減じた電圧に向けて当該駆動トランジスタのソース電圧を変化させる閾値補正処理を行う

前記(11)に記載の表示装置の駆動回路。

(13)画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置。

(14)画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置を有する電子機器。

【符号の説明】

【0144】

10・・・有機EL表示装置、20・・・画素、21・・・有機EL素子、22・・・駆動トランジスタ、23・・・書込みトランジスタ、24・・・保持容量、30・・・画素アレイ部、40・・・書込み走査回路、50・・・電源供給走査回路、60,60A,60B,60C・・・信号線駆動回路、61・・・アンプ、62(621〜62i)・・・サンプリングスイッチ、63(631〜63i),64(641〜64i)・・・容量素子(MOS容量)、70・・・半導体基板

【技術分野】

【0001】

本開示は、表示装置の駆動回路、表示装置、及び、電子機器に関し、特に、表示装置の信号線を駆動する駆動回路、当該駆動回路を用いた表示装置、及び、当該表示装置を有する電子機器に関する。

【背景技術】

【0002】

有機EL表示装置などの平面型の表示装置では、画素を構成する素子の特性ばらつきなどに起因する画質不良を改善するために、階調電圧の書込みに先立って所定の直流電圧を画素に書込み、当該直流電圧を基準電圧として用いて特性ばらつきについての補正処理が行われる(例えば、特許文献1参照)。

【0003】

所定の直流電圧の書込みは、画素が行列状に配置されて成る画素アレイ部の画素列毎に配線された信号線(データ線)を介して行われる。より具体的には、信号線毎にサンプリングスイッチが設けられており、信号供給源から供給される所定の直流電圧をサンプリングスイッチが画素列単位でサンプリングし、各信号線に書き込むことにより、当該信号線を介して所定の直流電圧が画素に書き込まれる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−310311号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、サンプリングスイッチを介して直流電圧を各画素に書き込む際に、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチの入力ノードの電位が揺れる現象が生じる。そして、サンプリングスイッチの入力ノードの電位の揺れによって直流電圧が変動するため、所望の電圧値の直流電圧を画素に書き込めなくなる。その結果、所望の電圧値の直流電圧を基準電圧とする、特性ばらつきについての補正処理を正常に行えないことになる。

【0006】

そこで、本開示は、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響を受けることなく、所望の電圧値の直流電圧を信号線に書き込むことが可能な表示装置の駆動回路、当該駆動回路を用いた表示装置、及び、当該表示装置を有する電子機器を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本開示の表示装置の駆動回路は、

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える構成となっている。

【0008】

本開示の駆動回路は、画素が行列状に配置されて成る画素アレイ部を有する表示装置において、画素アレイ部の画素列単位で配線された信号線の駆動に用いることができる。また、本開示の駆動回路を用いた表示装置は、表示部を備える各種の電子機器において、その表示部として用いることができる。

【0009】

サンプリングスイッチによるサンプリングによって所定の直流電圧を信号線に書き込む際に、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチの入力ノードの電位が揺らされようとする。このとき、サンプリングスイッチの入力ノードに接続されている容量素子が、チャージインジェクションやクロックフィードスルーの影響を吸収するように作用する。これにより、チャージインジェクションやクロックフィードスルーの影響による、サンプリングスイッチの入力ノードの電位の揺れを抑えることができる。

【発明の効果】

【0010】

本開示によれば、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響による、サンプリングスイッチの入力ノードの電位の揺れを抑えることができるため、当該影響を受けることなく、所望の電圧値の直流電圧を信号線に書き込むことができる。

【図面の簡単な説明】

【0011】

【図1】本開示の実施形態に係るアクティブマトリクス型有機EL表示装置の構成の概略を示すシステム構成図である。

【図2】画素(画素回路)の具体的な回路構成の一例を示す回路図である。

【図3】本開示の実施形態に係るアクティブマトリクス型有機EL表示装置の基本的な回路動作を説明するためのタイミング波形図である。

【図4】駆動トランジスタの閾値電圧Vthのばらつきに起因する課題の説明(A)、及び、駆動トランジスタの移動度μのばらつきに起因する課題の説明(B)に供する特性図である。

【図5】サンプリングスイッチのオフ時のチャージインジェクション及びクロックフィードスルーの影響についての説明図である。

【図6】実施例1に係る信号線駆動回路の回路構成を示す回路図である。

【図7】実施例1に係る信号線駆動回路の回路動作を説明するためのタイミング波形図である。

【図8】実施例1に係る信号線駆動回路の動作説明図である。

【図9】参考例に係る信号線駆動回路の回路構成を示す回路図である。

【図10】参考例に係る信号線駆動回路の回路動作を説明するためのタイミング波形図である。

【図11】参考例に係る信号線駆動回路の動作説明図である。

【図12】実施例2に係る信号線駆動回路の回路構成を示す回路図である。

【発明を実施するための形態】

【0012】

以下、本開示の技術を実施するための形態(以下、「実施形態」と記述する)について図面を用いて詳細に説明する。本開示は実施形態に限定されるものではない。以下の説明において、同一要素又は同一機能を有する要素には同一符号を用いることとし、重複する説明は省略する。尚、説明は以下の順序で行う。

1.本開示の表示装置の駆動回路、表示装置、及び、電子機器、全般に関する説明

2.本開示の実施形態に係るアクティブマトリクス型有機EL表示装置

2−1.システム構成

2−2.画素回路

2−3.基本的な回路動作

2−4.信号線駆動回路

2−4−1.実施例1

2−4−2.参考例

2−4−3.実施例2

3.電子機器

4.本開示の構成

【0013】

<1.本開示の表示装置の駆動回路、表示装置、及び、電子機器、全般に関する説明>

本開示の表示装置の駆動回路は、画素が行列状に配置されて成る画素アレイ部を有する平面型(フラットパネル型)の表示装置において、画素アレイ部の画素列単位で配線された信号線を駆動する、具体的には、信号線に所定の直流電圧を書き込むのに用いることができる。

【0014】

平面型の表示装置としては、画素の発光素子(電気光学素子)として自発光素子を用いる有機EL表示装置やプラズマ表示装置などを例示することができる。これらの表示装置のうち、有機EL表示装置は、有機材料のエレクトロルミネッセンス(Electro Luminescence:EL)を利用し、有機薄膜に電界をかけると発光する現象を用いた有機EL素子を画素の発光素子(電気光学素子)として用いている。

【0015】

有機EL表示装置は次のような特長を持っている。すなわち、有機EL素子は、10V以下の印加電圧で駆動できるために低消費電力である。また、有機EL素子は、自発光素子であるために画像の視認性が高く、しかも、応答速度が数μsec程度と非常に高速であるために動画表示時の残像が発生しない。有機EL素子は、電流駆動型の電気光学素子である。電流駆動型の電気光学素子としては、有機EL素子の他に、無機EL素子、LED素子、半導体レーザー素子などを例示することができる。

【0016】

所定の直流電圧の信号線への書込みに当っては、信号線毎に設けられるサンプリングスイッチが用いられる。サンプリングスイッチは、所定の直流電圧に続いて入力される映像信号の信号電圧(階調電圧、即ち、階調に応じた電圧)についてもサンプリングし、信号線に書き込む。

【0017】

サンプリングスイッチの入力側には、当該サンプリングスイッチに対して所定の直流電圧を入力するアンプが接続された構成とすることができる。また、サンプリングスイッチは、複数の信号線を単位として入力ノードが共通に接続された構成とすることができる。このとき、サンプリングスイッチには、複数の信号線、即ち、複数の画素列に対応した映像信号の信号電圧が、所定の直流電圧に続いて時系列で入力される。この時系列で入力される階調電圧を、サンプリングスイッチは時分割でサンプリングして信号線に書き込むことになる。

【0018】

サンプリングスイッチによるサンプリングによって所定の直流電圧を信号線に書き込む際には、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチの入力ノード/出力ノードの電位が揺らされようとする。

【0019】

ここで、「チャージインジェクション」とは、サンプリングスイッチがMOSトランジスタから成る場合、ゲート電圧の極性が反転するときに、ゲート酸化膜に帯電していた電荷が入力ノード側、出力ノード側に移動することにより、伝達される電圧が変動する現象(過渡的誤差要因)を言う。また、「クロックフィードスルー」とは、サンプリングスイッチのオン/オフ時に、MOSトランジスタのゲート−ドレイン間とゲート−ソース間に存在する寄生容量に起因して、ゲート電圧が入力ノード/出力ノードの電位に影響を与える現象を言う。

【0020】

このチャージインジェクションやクロックフィードスルーの影響を吸収する、即ち、サンプリングスイッチの入力ノードの電位の揺れを吸収するために、本開示の駆動回路は、サンプリングスイッチの入力ノードに容量素子が接続された構成となっている。容量素子は、信号線毎に設ける構成とすることができる。また、サンプリングスイッチの入力ノードを、複数の信号線を単位として共通に接続した構成を採る場合には、容量素子は、共通に接続された入力ノードに1つ接続する、即ち、複数の信号線に対して1つ設ける構成とすることができる。また、容量素子をサンプリングスイッチの出力ノードにも設ける構成とすることができる。

【0021】

サンプリングスイッチは、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されて成るアナログスイッチ(トランスファスイッチ)とすることができる。このとき、容量素子として、MOS容量を用いるのが好ましい。MOS容量は、サンプリングスイッチを構成するPチャネルMOSトランジスタ及びNチャネルMOSトランジスタの各ゲート電極に対して互いに逆相の選択パルスを伝送する伝送線と、サンプリングスイッチの入力ノードとの間に接続されて用いられる。

【0022】

MOS容量は、PチャネルMOSトランジスタとNチャネルMOSトランジスタから成るサンプリングスイッチと逆相に動作することで、当該サンプリングスイッチの入力ノードの電位の揺れを吸収する。MOS容量のサイズとしては、そのゲート電極の面積が、サンプリングスイッチを構成するPチャネルMOSトランジスタ及びNチャネルMOSトランジスタの各ゲート電極の半分を目安とするのが好ましい。ここで、「半分」とは、厳密に半分である場合の他、実質的に半分である場合も含む。設計上あるいは製造上生ずる種々のばらつきの存在は許容される。

【0023】

本開示の駆動回路を用いる表示装置において、画素は、電気光学素子を駆動する駆動トランジスタ、信号線と駆動トランジスタのゲート電極との間に接続された書込みトランジスタ、及び、駆動トランジスタのゲート電極と一方のソース/ドレイン電極との間に接続された保持容量を少なくとも有する。

【0024】

そして、上記構成の画素は、画素を構成する素子の特性ばらつきを補正する機能、具体的には、製造プロセスのばらつきや経時変化などによる駆動トランジスタの閾値電圧の画素毎のばらつきを補正する閾値補正機能を持っている。そして、閾値補正処理の際に、サンプリングスイッチによってサンプリングされ、信号線に書き込まれる所定の直流電圧を当該補正処理の基準電圧として用いることができる。

【0025】

具体的には、サンプリングスイッチによってサンプリングされ、信号線にホールドされる所定の直流電圧は、書込みトランジスタによって画素内に書き込まれ(取り込まれ)、駆動トランジスタのゲート電極に印加される。このとき書き込まれた直流電圧は、駆動トランジスタのゲート電圧の初期化電圧となる。そして、この初期化電圧を基準とし、当該初期化電圧から駆動トランジスタの閾値電圧を減じた電圧に向けて当該駆動トランジスタのソース電圧を変化させる処理が、駆動トランジスタの閾値電圧の画素毎のばらつきを補正する閾値補正処理となる。

【0026】

<2.本開示の実施形態に係るアクティブマトリクス型有機EL表示装置>

[2−1.システム構成]

図1は、本開示の実施形態に係るアクティブマトリクス型有機EL表示装置の構成の概略を示すシステム構成図である。

【0027】

アクティブマトリクス型表示装置は、電気光学素子に流れる電流を、当該電気光学素子と同じ画素内に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタによって制御する表示装置である。絶縁ゲート型電界効果トランジスタとしては、典型的には、TFT(Thin Film Transistor;薄膜トランジスタ)が用いられる。

【0028】

ここでは、一例として、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子である例えば有機EL素子を、画素(画素回路)の発光素子として用いるアクティブマトリクス型有機EL表示装置の場合を例に挙げて説明する。

【0029】

図1に示すように、本実施形態に係る有機EL表示装置10は、有機EL素子を含む複数の画素20が行列状に2次元配置されて成る画素アレイ部30と、当該画素アレイ部30の周辺に配置される駆動回路部とを有する構成となっている。

【0030】

駆動回路部は、書込み走査回路40、電源供給走査回路50、及び、信号線駆動回路60等からなり、画素アレイ部30の各画素20を駆動する。これらの回路部40,50,60には、図示せぬタイミング信号生成部(タイミングジェネレータ)から各種のタイミング信号が供給される。信号線駆動回路60は、本開示の駆動回路である。

【0031】

画素20を構成する能動素子等は、例えば、シリコン基板などの半導体基板70上に形成される。書込み走査回路40、電源供給走査回路50、及び、信号線駆動回路60等については、図1に示すように、画素アレイ部30と同じ半導体基板70上に形成することもできるし、半導体基板70の外部回路として設けることもできる。

【0032】

尚、ここでは、画素20を構成する能動素子等を半導体基板70上に形成する形態を採る場合を例に挙げたが、ガラス基板等の透明絶縁基板上に形成する形態を採るようにすることも可能である。

【0033】

ここで、有機EL表示装置10がカラー表示対応の場合は、カラー画像を形成する単位となる1つの画素(単位画素)は複数の副画素(サブピクセル)から構成され、この副画素の各々が図1の画素20に相当することになる。より具体的には、カラー表示対応の表示装置では、1つの画素は、例えば、赤色(Red;R)光を発光する副画素、緑色(Green;G)光を発光する副画素、青色(Blue;B)光を発光する副画素の3つの副画素から構成される。

【0034】

但し、1つの画素としては、RGBの3原色の副画素の組み合わせに限られるものではなく、3原色の副画素に更に1色あるいは複数色の副画素を加えて1つの画素を構成することも可能である。より具体的には、例えば、輝度向上のために白色(White;W)光を発光する副画素を加えて1つの画素を構成したり、色再現範囲を拡大するために補色光を発光する少なくとも1つの副画素を加えて1つの画素を構成したりすることも可能である。

【0035】

画素アレイ部30には、m行n列の画素20の配列に対して、行方向(画素行の画素の配列方向)に沿って走査線311〜31mと電源供給線321〜32mとが画素行毎に配線されている。更に、m行n列の画素20の配列に対して、列方向(画素列の画素の配列方向)に沿って信号線331〜33nが画素列毎に配線されている。

【0036】

走査線311〜31mは、書込み走査回路40の対応する行の出力端にそれぞれ接続されている。電源供給線321〜32mは、電源供給走査回路50の対応する行の出力端にそれぞれ接続されている。信号線331〜33nは、信号線駆動回路60の対応する列の出力端にそれぞれ接続されている。

【0037】

書込み走査回路40は、クロックパルスckに同期してスタートパルスspを順にシフト(転送)するシフトレジスタ回路等によって構成されている。書込み走査回路40は、画素アレイ部30の各画素20への映像信号の信号電圧の書込みに際し、走査線31(311〜31m)に対して書込み走査信号WS(WS1〜WS m)を順次供給することによって画素アレイ部30の各画素20を行単位で順番に走査(線順次走査)する。

【0038】

電源供給走査回路50は、クロックパルスckに同期してスタートパルスspを順にシフトするシフトレジスタ回路等によって構成されている。電源供給走査回路50は、書込み走査回路40による線順次走査に同期して、第1電源電位Vcc_Hと当該第1電源電位Vcc_Hよりも低い第2電源電位Vcc_Lとで切替え可能な電源電位DS(DS1〜DSm)を電源供給線32(321〜32m)に供給する。後述するように、電源電位DSのVcc_H/Vcc_Lの切替えにより、画素20の発光/非発光(消光)の制御が行なわれる。

【0039】

信号線駆動回路60は、本開示の駆動回路であって、信号供給源(図示せず)から供給される映像信号の信号電圧(以下、単に「信号電圧」と記述する場合もある)Vsigと、所定の直流電圧である基準電圧Vofstとを選択的に信号線331〜33nに書き込む。ここで、信号電圧Vsigは、階調(輝度情報)に応じた電圧(即ち、階調電圧)である。また、基準電圧Vofstは、映像信号の信号電圧Vsigの基準となる電圧(例えば、映像信号の黒レベルに相当する電圧)であり、後述する閾値補正処理の際に用いられる。

【0040】

この信号線駆動回路60の具体的な回路構成が本開示の特徴とするところであり、その詳細については後述する。

【0041】

信号線駆動回路60から出力される映像信号の信号電圧Vsig/基準電圧Vofstは、信号線33(331〜33n)を介して画素アレイ部30の各画素20に対して、書込み走査回路40による走査によって選択された画素行の単位で書き込まれる。すなわち、信号線駆動回路60は、信号電圧Vsigを行(ライン)単位で書き込む線順次書込みの駆動形態を採っている。

【0042】

[2−2.画素回路]

図2は、画素(画素回路)20の具体的な回路構成の一例を示す回路図である。画素20の発光部は、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子である有機EL素子21から成る。

【0043】

図2に示すように、画素20は、有機EL素子21と、有機EL素子21に電流を流すことによって当該有機EL素子21を駆動する駆動回路とによって構成されている。有機EL素子21は、全ての画素20に対して共通に配線された共通電源供給線34にカソード電極が接続されている。

【0044】

有機EL素子21を駆動する駆動回路は、例えば、駆動トランジスタ22、書込みトランジスタ23、及び、保持容量24を有する構成となっている。駆動トランジスタ22及び書込みトランジスタ23としてNチャネル型のTFTを用いることができる。但し、ここで示した、駆動トランジスタ22及び書込みトランジスタ23の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。

【0045】

駆動トランジスタ22は、一方の電極(ソース/ドレイン電極)が有機EL素子21のアノード電極に接続され、他方の電極(ソース/ドレイン電極)が電源供給線32(321〜32m)に接続されている。

【0046】

書込みトランジスタ23は、一方の電極(ソース/ドレイン電極)が信号線33(331〜33n)に接続され、他方の電極(ソース/ドレイン電極)が駆動トランジスタ22のゲート電極に接続されている。また、書込みトランジスタ23のゲート電極は、走査線31(311〜31m)に接続されている。

【0047】

駆動トランジスタ22及び書込みトランジスタ23において、一方の電極とは、一方のソース/ドレイン領域に電気的に接続された金属配線を言い、他方の電極とは、他方のソース/ドレイン領域に電気的に接続された金属配線を言う。また、一方の電極と他方の電極との電位関係によって一方の電極がソース電極ともなればドレイン電極ともなり、他方の電極がドレイン電極ともなればソース電極ともなる。

【0048】

保持容量24は、一方の電極が駆動トランジスタ22のゲート電極に接続され、他方の電極が駆動トランジスタ22の他方の電極、及び、有機EL素子21のアノード電極に接続されている。

【0049】

尚、有機EL素子21の駆動回路としては、駆動トランジスタ22及び書込みトランジスタ23の2つのトランジスタと保持容量24の1つの容量素子とからなる回路構成のものに限られるものではない。一例として、一方の電極が有機EL素子21のアノード電極に、他方の電極が固定電位にそれぞれ接続されることで、有機EL素子21の容量不足分を補う補助容量を必要に応じて設けた回路構成を採ることも可能である。

【0050】

上記構成の画素20において、書込みトランジスタ23は、書込み走査回路40から走査線31を通してゲート電極に印加されるHighアクティブの書込み走査信号WSに応答して導通状態となる。これにより、書込みトランジスタ23は、信号線33を通して信号線駆動回路60から供給される、輝度情報に応じた映像信号の信号電圧Vsigまたは基準電圧Vofstをサンプリングして画素20内に書き込む(取り込む)。書込みトランジスタ23によって書き込まれた信号電圧Vsigまたは基準電圧Vofstは、駆動トランジスタ22のゲート電極に印加されるとともに保持容量24に保持される。

【0051】

駆動トランジスタ22は、電源供給線32(321〜32m)の電源電位DSが第1電源電位Vcc_Hにあるときには、一方の電極がドレイン電極、他方の電極がソース電極となって飽和領域で動作する。これにより、駆動トランジスタ22は、電源供給線32から電流の供給を受けて有機EL素子21を電流駆動にて発光駆動する。より具体的には、駆動トランジスタ22は、飽和領域で動作することにより、保持容量24に保持された信号電圧Vsigの電圧値に応じた電流値の駆動電流を有機EL素子21に供給し、当該有機EL素子21を電流駆動することによって発光させる。

【0052】

駆動トランジスタ22は更に、電源電位DSが第1電源電位Vcc_Hから第2電源電位Vcc_Lに切り替わったときには、一方の電極がソース電極、他方の電極がドレイン電極となってスイッチングトランジスタとして動作する。これにより、駆動トランジスタ22は、有機EL素子21への駆動電流の供給を停止し、有機EL素子21を非発光状態にする。すなわち、駆動トランジスタ22は、有機EL素子21の発光/非発光を制御するトランジスタとしての機能をも併せ持っている。

【0053】

この駆動トランジスタ22のスイッチング動作により、有機EL素子21が非発光状態となる期間(非発光期間)を設け、有機EL素子21の発光期間と非発光期間の割合(デューティ)を制御することができる。このデューティ制御により、1表示フレーム期間に亘って画素が発光することに伴う残像ボケを低減できるために、特に、動画の画品位をより優れたものとすることができる。

【0054】

電源供給走査回路50から電源供給線32を通して選択的に供給される第1,第2電源電位Vcc_H,Vcc_Lのうち、第1電源電位Vcc_Hは有機EL素子21を発光駆動する駆動電流を駆動トランジスタ22に供給するための電源電位である。また、第2電源電位Vcc_Lは、有機EL素子21に対して逆バイアスを掛けるための電源電位である。この第2電源電位Vcc_Lは、基準電圧Vofstよりも低い電位、例えば、駆動トランジスタ22の閾値電圧をVthとするときVofst−Vthよりも低い電位、好ましくは、Vofst−Vthよりも十分に低い電位に設定される。

【0055】

[2−3.基本的な回路動作]

続いて、上記構成の有機EL表示装置10の基本的な回路動作について、図3のタイミング波形図を用いて説明する。図3のタイミング波形図には、書込み走査信号WS、電源電位DS(Vcc_H/Vcc_L)、信号線33の電位(Vsig/Vofst)、駆動トランジスタ22のゲート電位Vg及びソース電位Vsのそれぞれの変化を示している。

【0056】

(前表示フレームの発光期間)

図3のタイミング波形図において、時刻t11以前は、前の表示フレームにおける有機EL素子21の発光期間となる。この前表示フレームの発光期間では、電源供給線32の電位DSが第1電源電位(以下、「高電位」と記述する)Vcc_Hにあり、また、書込みトランジスタ23が非導通状態にある。

【0057】

このとき、駆動トランジスタ22は飽和領域で動作するように設定されている。これにより、駆動トランジスタ22のゲート−ソース間電圧Vgsに応じた駆動電流(ドレイン−ソース間電流)Idsが、電源供給線32から駆動トランジスタ22を通して有機EL素子21に供給される。従って、有機EL素子21が駆動電流Idsの電流値に応じた輝度で発光する。

【0058】

(初期化期間)

時刻t11になると、線順次走査の新しい表示フレーム(現表示フレーム)に入る。そして、電源供給線32の電位DSが高電位Vcc_Hから、信号線33の基準電圧Vofstに対してVofst−Vthよりも十分に低い第2電源電位(以下、「低電位」と記述する)Vcc_Lに切り替わる。

【0059】

ここで、有機EL素子21の閾値電圧をVthel、共通電源供給線34の電位(カソード電位)をVcathとする。このとき、低電位Vcc_LをVcc_L<Vthel+Vcathとすると、駆動トランジスタ22のソース電位Vsが低電位Vcc_Lにほぼ等しくなるために、有機EL素子21は逆バイアス状態となって消光する。

【0060】

次に、時刻t12で走査線31の電位WSが低電位側から高電位側に遷移することで、書込みトランジスタ23が導通状態となる。このとき、信号線駆動回路60から信号線33に対して基準電圧Vofstが供給された状態にあるために、駆動トランジスタ22のゲート電位Vgが基準電圧Vofstになる。また、駆動トランジスタ22のソース電位Vsは、基準電圧Vofstよりも十分に低い電位、即ち、低電位Vcc_Lにある。

【0061】

このとき、駆動トランジスタ22のゲート−ソース間電圧Vgsは(Vofst−Vcc_L)となる。ここで、(Vofst−Vcc_L)が駆動トランジスタ22の閾値電圧Vthよりも大きくないと、後述する閾値補正処理を行うことができないため、Vofst−Vcc_L>Vthなる電位関係に設定する必要がある。

【0062】

このように、駆動トランジスタ22のゲート電位Vgを基準電圧Vofstに固定し、かつ、ソース電位Vsを低電位Vcc_Lに固定する(確定させる)処理が、後述する閾値補正処理(閾値補正動作)を行う前の初期化の処理である。従って、基準電圧Vofst及び低電位Vcc_Lが、駆動トランジスタ22のゲート電位Vg及びソース電位Vsの各初期化電位となる。

【0063】

(閾値補正期間)

次に、時刻t13で、電源供給線32の電位DSが低電位Vcc_Lから高電位Vcc_Hに切り替わると、駆動トランジスタ22のゲート電位Vgが基準電圧Vofstに保たれた状態で閾値補正処理が開始される。すなわち、ゲート電位Vgから駆動トランジスタ22の閾値電圧Vthを減じた電位に向けて駆動トランジスタ22のソース電位Vsが上昇を開始する。

【0064】

ここでは、便宜上、駆動トランジスタ22のゲート電位Vgの初期化電位Vofstを基準とし、当該初期化電位Vofstから駆動トランジスタ22の閾値電圧Vthを減じた電位に向けてソース電位Vsを変化させる処理を閾値補正処理と呼んでいる。この閾値補正処理が進むと、やがて、駆動トランジスタ22のゲート−ソース間電圧Vgsが駆動トランジスタ22の閾値電圧Vthに収束する。この閾値電圧Vthに相当する電圧は保持容量24に保持される。

【0065】

尚、閾値補正処理を行う期間(閾値補正期間)において、電流が専ら保持容量24側に流れ、有機EL素子21側には流れないようにするために、有機EL素子21がカットオフ状態となるように共通電源供給線34の電位Vcathを設定しておくこととする。

【0066】

次に、時刻t14で、書込み走査信号WSが低電位側に遷移することで、書込みトランジスタ23が非導通状態となる。このとき、駆動トランジスタ22のゲート電極が信号線33から電気的に切り離されることによってフローティング状態になる。しかし、ゲート−ソース間電圧Vgsが駆動トランジスタ22の閾値電圧Vthに等しいために、当該駆動トランジスタ22はカットオフ状態にある。従って、駆動トランジスタ22にドレイン−ソース間電流Idsは流れない。

【0067】

(信号書込み&移動度補正期間)

次に、時刻t15で、信号線33の電位が基準電圧Vofstから映像信号の信号電圧Vsigに切り替わる。続いて、時刻t16で、書込み走査信号WSが高電位側に遷移することで、書込みトランジスタ23が導通状態になって映像信号の信号電圧Vsigをサンプリングし、画素20内に書き込む。

【0068】

この書込みトランジスタ23による信号電圧Vsigの書込みにより、駆動トランジスタ22のゲート電位Vgが信号電圧Vsigになる。そして、映像信号の信号電圧Vsigによる駆動トランジスタ22の駆動の際に、当該駆動トランジスタ22の閾値電圧Vthが保持容量24に保持された閾値電圧Vthに相当する電圧と相殺される。この閾値キャンセルの原理の詳細については後述する。

【0069】

このとき、有機EL素子21は、カットオフ状態(ハイインピーダンス状態)にある。従って、映像信号の信号電圧Vsigに応じて電源供給線32から駆動トランジスタ22に流れる電流(ドレイン−ソース間電流Ids)は、有機EL素子21の等価容量に流れ込む。これにより、有機EL素子21の等価容量の充電が開始される。

【0070】

有機EL素子21の等価容量が充電されることにより、駆動トランジスタ22のソース電位Vsが時間の経過とともに上昇していく。このとき既に、駆動トランジスタ22の閾値電圧Vthの画素毎のばらつきがキャンセルされており、駆動トランジスタ22のドレイン−ソース間電流Idsは、当該駆動トランジスタ22の移動度μに依存したものとなる。尚、駆動トランジスタ22の移動度μは、当該駆動トランジスタ22のチャネルを構成する半導体薄膜の移動度である。

【0071】

ここで、映像信号の信号電圧Vsigに対する保持容量24の保持電圧Vgsの比率、即ち、書込みゲインGが1(理想値)であると仮定する。すると、駆動トランジスタ22のソース電位Vsが(Vofst−Vth+ΔV)の電位まで上昇することで、駆動トランジスタ22のゲート‐ソース間電圧Vgsは(Vsig−Vofst+Vth−ΔV)となる。

【0072】

すなわち、駆動トランジスタ22のソース電位Vsの上昇分ΔVは、保持容量24に保持された電圧(Vsig−Vofst+Vth)から差し引かれるように、換言すれば、保持容量24の充電電荷を放電するように作用する。これにより、ソース電位Vsの上昇分ΔVは、保持容量24に対して負帰還がかけられたことになる。従って、ソース電位Vsの上昇分ΔVは負帰還の帰還量となる。

【0073】

このように、駆動トランジスタ22に流れるドレイン−ソース間電流Idsに応じた帰還量ΔVでゲート‐ソース間電圧Vgsに負帰還をかけることで、駆動トランジスタ22のドレイン−ソース間電流Idsの移動度μに対する依存性を打ち消すことができる。この打ち消す処理が、駆動トランジスタ22の移動度μの画素毎のばらつきを補正する移動度補正処理である。

【0074】

より具体的には、駆動トランジスタ22のゲート電極に書き込まれる映像信号の信号振幅Vin(=Vsig−Vofst)が高い程ドレイン−ソース間電流Idsが大きくなるため、負帰還の帰還量ΔVの絶対値も大きくなる。従って、発光輝度レベルに応じた移動度補正処理が行われる。

【0075】

また、映像信号の信号振幅Vinを一定とした場合、駆動トランジスタ22の移動度μが大きいほど負帰還の帰還量ΔVの絶対値も大きくなるため、画素毎の移動度μのばらつきを取り除くことができる。従って、負帰還の帰還量ΔVは、移動度補正処理の補正量とも言える。移動度補正の原理の詳細については後述する。

【0076】

(発光期間)

次に、時刻t17で、書込み走査信号WSが低電位側に遷移することで、書込みトランジスタ23が非導通状態となる。これにより、駆動トランジスタ22のゲート電極は、信号線33から電気的に切り離されるためにフローティング状態になる。

【0077】

ここで、駆動トランジスタ22のゲート電極がフローティング状態にあるときは、駆動トランジスタ22のゲート−ソース間に保持容量24が接続されていることで、駆動トランジスタ22のソース電位Vsの変動に連動してゲート電位Vgも変動する。すなわち、駆動トランジスタ22のソース電位Vs、ゲート電位Vgは、保持容量24に保持されているゲート−ソース間電圧Vgsを保持したまま上昇する。そして、駆動トランジスタ22のソース電位Vsは、トランジスタの飽和電流Idsに応じた有機EL素子21の発光電圧Voledまで上昇する。

【0078】

このように、駆動トランジスタ22のゲート電位Vgがソース電位Vsの変動に連動して変動する動作がブートストラップ動作である。換言すれば、ブートストラップ動作は、保持容量24に保持されたゲート−ソース間電圧Vgs、即ち、保持容量24の両端間電圧を保持したまま、ゲート電位Vg及びソース電位Vsが変動する動作である。

【0079】

駆動トランジスタ22のゲート電極がフローティング状態になり、それと同時に、駆動トランジスタ22のドレイン−ソース間電流Idsが有機EL素子21に流れ始めることにより、当該電流Idsに応じて有機EL素子21のアノード電位が上昇する。そして、有機EL素子21のアノード電位が(Vthel+Vcath)を越えると、有機EL素子21に駆動電流が流れ始めるため有機EL素子21が発光を開始する。

【0080】

有機EL素子21の発光電流は、このときのゲート−ソース間電圧Vgsによって駆動トランジスタ22の飽和電流Idsにより規定される。このため、駆動トランジスタ22は、各信号電圧Vsigにおける定電流源となる。

【0081】

また、有機EL素子21のアノード電位の上昇は、即ち、駆動トランジスタ22のソース電位Vsの上昇に他ならない。そして、駆動トランジスタ22のソース電位Vsが上昇すると、保持容量24のブートストラップ動作により、駆動トランジスタ22のゲート電位Vgも連動して上昇する。

【0082】

このとき、ブートストラップゲインが1(理想値)であると仮定した場合、ゲート電位Vgの上昇量はソース電位Vsの上昇量に等しくなる。故に、発光期間中は、駆動トランジスタ22のゲート‐ソース間電圧Vgsは、(Vsig−Vofst+Vth−ΔV)で一定に保持される。

【0083】

以上説明した一連の回路動作において、閾値補正準備、閾値補正、信号電圧Vsigの書込み(信号書込み)、及び、移動度補正の各処理動作は、1水平期間(1H)において実行される。また、信号書込み及び移動度補正の各処理動作は、時刻t16−t17の期間において並行して実行される。

【0084】

〔分割閾値補正〕

尚、ここでは、閾値補正処理を1回だけ実行する駆動法を採る場合を例に挙げて説明したが、この駆動法は一例に過ぎず、この駆動法に限られるものではない。例えば、閾値補正処理を移動度補正及び信号書込み処理と共に行う1H期間に加えて、当該1H期間に先行する複数の水平期間に亘って分割して閾値補正処理を複数回実行する、所謂、分割閾値補正を行う駆動法を採ることも可能である。

【0085】

この分割閾値補正の駆動法によれば、高精細化に伴う多画素化によって1水平期間として割り当てられる時間が短くなったとしても、閾値補正期間として複数の水平期間に亘って十分な時間を確保することができる。従って、1水平期間として割り当てられる時間が短くなっても、閾値補正期間として十分な時間を確保できるため、閾値補正処理を確実に実行できることになる。

【0086】

〔閾値キャンセルの原理〕

ここで、駆動トランジスタ22の閾値キャンセル(即ち、閾値補正)の原理について説明する。駆動トランジスタ22は、飽和領域で動作するように設計されているために定電流源として動作する。これにより、有機EL素子21には駆動トランジスタ22から、次式(1)で与えられる一定のドレイン−ソース間電流(駆動電流)Idsが供給される。

Ids=(1/2)・μ(W/L)Cox(Vgs−Vth)2 ……(1)

ここで、Wは駆動トランジスタ22のチャネル幅、Lはチャネル長、Coxは単位面積当たりのゲート容量である。

【0087】

図4(A)に、駆動トランジスタ22のドレイン−ソース間電流Ids対ゲート−ソース間電圧Vgsの特性を示す。図4(A)の特性図に示すように、駆動トランジスタ22の閾値電圧Vthの画素毎のばらつきに対するキャンセル処理(補正処理)を行わないと、閾値電圧VthがVth1のときに、ゲート−ソース間電圧Vgsに対応するドレイン−ソース間電流IdsがIds1になる。

【0088】

これに対して、閾値電圧VthがVth2(Vth2>Vth1)のとき、同じゲート−ソース間電圧Vgsに対応するドレイン−ソース間電流IdsがIds2(Ids2<Ids1)になる。すなわち、駆動トランジスタ22の閾値電圧Vthが変動すると、ゲート−ソース間電圧Vgsが一定であってもドレイン−ソース間電流Idsが変動する。

【0089】

一方、上記構成の画素(画素回路)20では、先述したように、発光時の駆動トランジスタ22のゲート−ソース間電圧VgsはVsig−Vofst+Vth−ΔVである。従って、これを式(1)に代入すると、ドレイン−ソース間電流Idsは、次式(2)で表される。

Ids=(1/2)・μ(W/L)Cox(Vsig−Vofst−ΔV)2 ……(2)

【0090】

すなわち、駆動トランジスタ22の閾値電圧Vthの項がキャンセルされており、駆動トランジスタ22から有機EL素子21に供給されるドレイン−ソース間電流Idsは、駆動トランジスタ22の閾値電圧Vthに依存しない。その結果、駆動トランジスタ22の製造プロセスのばらつきや経時変化等により、駆動トランジスタ22の閾値電圧Vthが画素毎に変動したとしても、ドレイン−ソース間電流Idsが変動しないために、有機EL素子21の発光輝度を一定に保つことができる。

【0091】

〔移動度補正の原理〕

次に、駆動トランジスタ22の移動度補正の原理について説明する。図4(B)に、駆動トランジスタ22の移動度μが相対的に大きい画素Aと、駆動トランジスタ22の移動度μが相対的に小さい画素Bとを比較した状態で特性カーブを示す。

【0092】

画素Aと画素Bで移動度μにばらつきがある状態で、駆動トランジスタ22のゲート電極に対して、例えば両画素A,Bに同レベルの信号振幅Vin(=Vsig−Vofst)を書き込んだ場合を考える。この場合、何ら移動度μの補正を行わないと、移動度μの大きい画素Aに流れるドレイン−ソース間電流Ids1′と移動度μの小さい画素Bに流れるドレイン−ソース間電流Ids2′との間には大きな差が生じてしまう。このように、移動度μの画素毎のばらつきに起因してドレイン−ソース間電流Idsに画素間で大きな差が生じると、画面のユニフォーミティ(一様性)が損なわれる。

【0093】

ここで、先述した式(1)のトランジスタ特性式から明らかなように、移動度μが大きいとドレイン−ソース間電流Idsが大きくなる。従って、負帰還における帰還量ΔVは移動度μが大きくなるほど大きくなる。図4(B)に示すように、移動度μの大きな画素Aの帰還量ΔV1は、移動度の小さな画素Bの帰還量ΔV2に比べて大きい。

【0094】

そこで、移動度補正処理によって駆動トランジスタ22のドレイン−ソース間電流Idsに応じた帰還量ΔVでゲート−ソース間電圧Vgsに負帰還をかけることにより、移動度μが大きいほど負帰還が大きくかかることになる。その結果、移動度μの画素毎のばらつきを抑制することができる。

【0095】

具体的には、移動度μの大きな画素Aで帰還量ΔV1の補正をかけると、ドレイン−ソース間電流IdsはIds1′からIds1まで大きく下降する。一方、移動度μの小さな画素Bの帰還量ΔV2は小さいために、ドレイン−ソース間電流IdsはIds2′からIds2までの下降となり、それ程大きく下降しない。結果的に、画素Aのドレイン−ソース間電流Ids1と画素Bのドレイン−ソース間電流Ids2とはほぼ等しくなるために、移動度μの画素毎のばらつきが補正される。

【0096】

以上をまとめると、移動度μの異なる画素Aと画素Bがあった場合、移動度μの大きい画素Aの帰還量ΔV1は移動度μの小さい画素Bの帰還量ΔV2に比べて大きくなる。つまり、移動度μが大きい画素ほど帰還量ΔVが大きく、ドレイン−ソース間電流Idsの減少量が大きくなる。

【0097】

従って、駆動トランジスタ22のドレイン−ソース間電流Idsに応じた帰還量ΔVで、ゲート−ソース間電圧Vgsに負帰還をかけることで、移動度μの異なる画素のドレイン−ソース間電流Idsの電流値が均一化される。その結果、移動度μの画素毎のばらつきを補正することができる。すなわち、駆動トランジスタ22に流れる電流(ドレイン−ソース間電流Ids)に応じた帰還量(補正量)ΔVで、駆動トランジスタ22のゲート−ソース間電圧Vgsに対して、即ち、保持容量24に対して負帰還をかける処理が移動度補正処理となる。

【0098】

[2−4.信号線駆動回路]

本開示の駆動回路である、実施形態に係る信号線駆動回路60は、信号供給源から順に入力される基準電圧Vofst及び信号電圧(階調電圧)Vsigを、サンプリングスイッチによるサンプリングによって信号線33(331〜33n)に書き込む。この書込みの際に、サンプリングスイッチのスイッチング時のチャージインジェクションやクロックフィードスルーが、基準電圧Vofstの書込み動作に悪影響を及ぼす。

【0099】

ここで、理解を容易にするために、サンプリングスイッチSWがNチャネルMOSトランジスタから成る場合を例に挙げて、サンプリングスイッチSWのスイッチング時、特にオフ時のチャージインジェクション及びクロックフィードスルーの影響について、図5を用いて説明する。

【0100】

図5において、サンプリングスイッチSW及び負荷容量Cによってサンプルホールド回路が形成されている。負荷容量Cは、信号線33(331〜33n)の寄生容量などである。このサンプルホールド回路において、サンプリングスイッチSWによってサンプリングされた電圧は、当該サンプリングスイッチSWのオフタイミング(即ち、ホールドタイミング)で信号線33に書き込まれ、ホールドされる。

【0101】

ここで、サンプリングスイッチSWの入力信号の電圧値をVinとし、ゲート電極に与えられる制御パルス(選択パルス)ENの正側の電圧値をVddとし、負側の電圧値を0とする。また、NチャネルMOSトランジスタのチャネル長をL、チャネル幅をW、閾値電圧をVth、ゲート酸化膜容量をCox、オーバーラップ容量をCovとする。オーバーラップ容量Covは、ゲート電極とソース領域やドレイン領域とがオーバーラップする領域に存在する寄生容量である。

【0102】

サンプリングスイッチSWがオフするとき、即ち、制御パルスENがVddから0に遷移するときのチャージインジェクションの影響による電位の変動量ΔVchは、

ΔVch=1/2×W・L・Cox(Vdd−Vin−Vth)/C

となる。また、クロックフィードスルーの影響による電位の変動量ΔVclは、

ΔVcl=Vdd×Cov/(Cov+C)

となる。

【0103】

このサンプリングスイッチSWのオフ時のチャージインジェクションやクロックフィードスルーの影響によってサンプリングスイッチSWの入力ノードの電位が変動(変動量ΔVch/ΔVcl)すると、所望の電圧値の基準電圧Vofstを信号線33に書き込めないことになる。先述したように、基準電圧Vofstは閾値補正処理の基準となる電圧であることから、所望の電圧値の基準電圧Vofstを信号線33に書き込めないということは、閾値補正処理を正常に実行できないということになる。

【0104】

本開示の駆動回路は、サンプリングスイッチのスイッチング時、特にオフ時のチャージインジェクションやクロックフィードスルーの影響が、サンプリングスイッチの入力ノード側に及ぶときの不具合を解消すべく為された信号線駆動回路である。以下に、本開示の駆動回路の具体的な実施例について説明する。

【0105】

(2−4−1.実施例1)

図6は、実施例1に係る信号線駆動回路の回路構成を示す回路図である。

【0106】

図6において、実施例1に係る信号線駆動回路60Aは、図1に示す画素アレイ部30におけるn本の信号線331〜33nについて、i本の信号線331〜33iを単位として、アンプ61から入力電圧が与えられる構成となっている。ここでは、図面の簡略化のために、i本の信号線331〜33iに対応する回路構成について図示している。

【0107】

アンプ61から与えられる入力電圧は、所定の直流電圧である基準電圧Vofstと、当該基準電圧Vofstに続いて時系列で入力されるi列分の信号電圧(階調電圧)Vsigである。アンプ61の前段側には、例えば、デジタル信号をアナログ信号に変換するDAコンバータ(図示せず)が配置されており、当該DAコンバータの出力DACoutがアンプ61の非反転(+)入力端子に入力される。

【0108】

DAコンバータは、信号線駆動回路60Aに対して基準電圧Vofst及び信号電圧Vsigを供給する信号供給源を構成している。アンプ61は、反転(−)入力端子と出力端子とが電気的に接続されており、DAコンバータを含む信号供給源の出力段を構成している。

【0109】

一般的には、画素アレイ部30のn本の信号線331〜33nの各々に対して1対1の対応関係をもって信号供給源が設けられる。これに対し、本信号線駆動回路60Aのように、i本の信号線331〜33iを単位として信号供給源を設けることにより、信号供給源、即ち、DAコンバータやアンプ61の数を大幅に削減できるため、システムの回路構成の簡略化を図ることができる利点がある。

【0110】

信号線駆動回路60Aは、i本の信号線331〜33i毎に設けられたサンプリングスイッチ621〜62iを有する。サンプリングスイッチ621〜62iは、信号線331〜33iの寄生容量などと共にサンプルホールド回路を形成し、アンプ61から入力される基準電圧Vofstを一斉にサンプリングし、オフタイミング(ホールドタイミング)で信号線331〜33iにホールドする。サンプリングスイッチ621〜62iは更に、基準電圧Vofstに続いてアンプ61から時系列で入力される信号電圧Vsigを時分割にてサンプリングし、信号線331〜33iに順に書き込む。

【0111】

サンプリングスイッチ621〜62iは、例えば、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されたアナログスイッチ(トランスファスイッチ)によって構成されている。そして、サンプリングスイッチ621〜62iは、互いに逆相の選択パルスSEL,xSEL(SEL1〜SELi,xSEL1〜xSELi)に応じてスイッチング動作(オン/オフ動作)を行うことによって基準電圧Vofst/信号電圧Vsigをサンプルホールドする。

【0112】

正相の選択パルスSEL(SEL1〜SELi)は、サンプリングスイッチ621〜62iを構成するNチャネルMOSトランジスタのゲート電極に対して伝送線La(La1〜Lai)によって伝送される。逆相の選択パルスxSEL(xSEL1〜xSELi)は、サンプリングスイッチ621〜62iを構成するPチャネルMOSトランジスタのゲート電極に対して伝送線Lb(Lb1〜Lbi)によって伝送される。

【0113】

サンプリングスイッチ621〜62iの入力ノードNin(Nin_1〜Nin_i)と、伝送線La(La1〜Lai),Lb(Lb1〜Lbi)との間には、容量素子63(631〜63i)が接続されている。容量素子631〜63iは、例えばMOS容量から成る。具体的には、容量素子631〜63iは、サンプリングスイッチ621〜62iの各入力ノードNinと伝送線Laとの間に接続されたPチャネルMOSトランジスタと、サンプリングスイッチ621〜62iの各入力ノードNinと伝送線Lbとの間に接続されたNチャネルMOSトランジスタとから成る。容量素子631〜63iのトランジスタサイズは、サンプリングスイッチ621〜62iを構成するトランジスタの半分のゲート面積が目安である。

【0114】

サンプリングスイッチ621〜62iの出力ノードNout(Nout_1〜Nout_i)と、伝送線La(La1〜Lai),Lb(Lb1〜Lbi)との間には、容量素子64(641〜64i)が接続されている。容量素子641〜64iも、容量素子631〜63iと同様に、MOS容量から成る。具体的には、容量素子641〜64iは、サンプリングスイッチ621〜62iの各出力ノードNoutと伝送線Laとの間に接続されたPチャネルMOSトランジスタと、サンプリングスイッチ621〜62iの各出力ノードNoutと伝送線Lbとの間に接続されたNチャネルMOSトランジスタとから成る。容量素子641〜64iのトランジスタサイズは、サンプリングスイッチ621〜62iを構成するトランジスタの半分のゲート面積が目安である。

【0115】

続いて、上記構成の実施例1に係る信号線駆動回路60Aの回路動作について、図7のタイミング波形図を用いて、図8の動作説明図を参照しつつ説明する。図7のタイミング波形図において、PIX1〜PIXiは、信号線331〜33iの電位を表わしている。ここでは、基準電圧Vofstをi本の信号線331〜33iに書き込む際の動作について説明し、信号電圧Vsigの書込み動作については省略するものとする。

【0116】

基準電圧Vofstの書込みのために、選択パルスSEL,xSEL(SEL1〜SELi,xSEL1〜xSELi)に応答して、全サンプリングスイッチ621〜62iがオン状態となる。そして、基準電圧Vofstの書込みが完了すると、全サンプリングスイッチ621〜62iがオフ状態となる。

【0117】

サンプリングスイッチ621〜62iがオフ状態となる瞬間、サンプリングスイッチ621〜62iのチャージインジェクションやクロックフィードスルーの影響によって、サンプリングスイッチ621〜62iの各入力ノードNin_1〜Nin_iの電位(即ち、アンプ61の出力電位)が揺らされようとする。特に、サンプリングスイッチ621〜62iの入力ノードNin_1〜Nin_iに対して、図8に破線の矢印で示すように、NチャネルMOSトランジスタ分のチャージインジェクションの影響が及ぶ。

【0118】

このサンプリングスイッチ621〜62iのオフ時には、サンプリングスイッチ621〜62iの各入力ノードNin_1〜Nin_iに接続された容量素子631〜63iが、サンプリングスイッチ621〜62iと逆相に動作する。この逆相の動作による容量素子631〜63iの作用により、サンプリングスイッチ621〜62iのオフ時に生じたチャージインジェクションやクロックフィードスルーの影響、換言すれば、当該影響による入力ノードNin_1〜Nin_iの電位の揺れが抑えられる。

【0119】

すなわち、容量素子631〜63iによって入力ノードNin_1〜Nin_iの電位(即ち、アンプ61の出力電位)の揺れが吸収され、これらの入力ノードNin_1〜Nin_iには、予め規定した所望の電圧値の基準電圧Vofstが与えられる。これにより、図7のタイミング波形図に示すように、選択パルスSEL1〜SELiの相互間にオフ時のタイミング(即ち、ホールドタイミング)に微小なずれが生じていたとしても、所望の電圧値の基準電圧Vofstを信号線331〜33iに書き込むことができる。

【0120】

一方、サンプリングスイッチ621〜62iの出力ノードNout_1〜Nout_iに接続された容量素子641〜64iは、サンプリングスイッチ621〜62iのスイッチング時のチャージインジェクションやクロックフィードスルーの出力ノードNout_1〜Nout_iに対する影響を吸収する作用を為す。

【0121】

本実施例1では、サンプリングスイッチ621〜62iの入力ノード/出力ノードの両側に容量素子631〜63i,641〜64iを設ける構成としたが、これは好ましい実施の形態であって、出力ノード側の容量素子641〜64iは必須の構成要素ではない。すなわち、出力ノード側に容量素子641〜64iが存在しなくても、少なくとも、入力ノード側に容量素子631〜63iが存在することで、サンプリングスイッチ621〜62iのオフ時の入力ノードNin_1〜Nin_iの電位の揺れを抑える、という所期の目的を達成することができる。

【0122】

ここで、サンプリングスイッチ621〜62iの出力ノード側にのみ容量素子641〜64iを設けて成る信号線駆動回路について、参考例に係る信号線駆動回路として以下に説明する。

【0123】

(2−4−2.参考例)

図9は、参考例に係る信号線駆動回路の回路構成を示す回路図である。図9に示すように、参考例に係る信号線駆動回路60Bは、サンプリングスイッチ621〜62iの出力ノード側にのみ、即ち、出力ノードNout_1〜Nout_iと伝送線La1〜Lai,Lb1〜Lbiとの間に容量素子641〜64iが接続された構成となっている。

【0124】

参考例に係る信号線駆動回路60Bのタイミング波形図を図10に、動作説明図を図11にそれぞれ示す。

【0125】

参考例に係る信号線駆動回路60Bの場合、サンプリングスイッチ621〜62iがオフ状態となるタイミング(ホールドタイミング)で、図11に破線の矢印で示すように、Nチャネル分のチャージインジェクションの影響が及ぶ。これにより、図10に破線の○で囲って示すように、入力ノードNin_1〜Nin_iの電位(即ち、アンプ61の出力電位)が揺らされる。

【0126】

一方、サンプリングスイッチ621〜62iは、それぞれ独立したタイミングの選択パルスSEL1〜SELiによって制御される。選択パルスSEL1〜SELiには、これらパルスを生成する回路系や伝送系の定数のばらつき等によって、図10のタイミング波形図に示すように、微小なタイミングのずれが発生する。そして、選択パルスSEL1〜SELiのオフ時のタイミング(ホールドタイミング)の微小なタイミングずれにより、サンプリングスイッチ621〜62iによる入力ノードNin_1〜Nin_iの電位のホールドポイントが信号線331〜33i間でずれる。

【0127】

これにより、図10のタイミング波形図に示すように、基準電圧Vofstが書き込まれたときの信号線331〜33iの電位PIX1〜PINiにばらつき(ΔV1〜ΔVi)が生じる。すなわち、信号線331〜33iにホールドされた基準電圧Vofstの電圧値に信号線331〜33i間でばらつきが生じる。これは、サンプリングスイッチ621〜62iによって所望の電圧値の基準電圧Vofstをサンプルホールドできないこと、即ち、信号線331〜33iには異なる電圧値の基準電圧Vofstがホールドされる(書き込まれる)ことを意味する。

【0128】

基準電圧Vofstは、閾値補正処理の際に、駆動トランジスタ22のゲート電圧の初期化電圧として用いられる。従って、基準電圧Vofstの電圧値に信号線331〜33i間でばらつきが存在することで、1列目〜i列目の各画素列において、異なる電圧値の基準電圧Vofstを用いて閾値補正処理が行われることになる。その結果、基準電圧Vofstの電圧値の信号線331〜33i間でのばらつきが、表示画面上で縦筋(列方向の筋)として視認されるため、画品位(画質)の低下を招くことになる。

【0129】

このように、信号線331〜33iに書き込まれる基準電圧Vofstの電圧値の誤差は、サンプリングスイッチ621〜62iを制御する選択パルスSEL1〜SELiの動作タイミングに依存する。そして、参考例に係る信号線駆動回路60Bの場合は、半導体チップ(半導体基板)の絶対ばらつき、相対ばらつき、温度依存、電源依存などにより、画質が安定しない。

【0130】

尚、サンプリングスイッチ621〜62iのオフ時の入力ノードNin_1〜Nin_iの電位の揺れについては、サンプリングスイッチ621〜62iの前段のアンプ61でカバーすることもできる。しかし、この方策を採る場合には、非常に広帯域のアンプを用いる必要があり、消費電力の著しい増加を招くため好ましい方策とは言えない。

【0131】

これに対して、実施例1に係る信号線駆動回路60Aによれば、サンプリングスイッチ621〜62iの入力ノード側に容量素子631〜63iを配するだけの簡単な構成及び簡単な動作シーケンスにて、参考例に係る信号線駆動回路60Bの問題を解消することができる。すなわち、前段のアンプ61の消費電力を増加させることなく、また、半導体チップ(図1の半導体基板70)のサイズを増大させることなく、所望の電圧値の基準電圧Vofstを信号線331〜33iに書き込むことができる。その結果、各画素列において閾値補正処理をより確実に行うことができるため、輝度ムラのない均一な画質の表示画像を得ることができる。

【0132】

(2−4−3.実施例2)

図12は、実施例2に係る信号線駆動回路の回路構成を示す回路図である。

【0133】

実施例1に係る信号線駆動回路60Aでは、サンプリングスイッチ621〜62iの入力ノードNin_1〜Nin_iに接続する容量素子631〜63iを、i本の信号線331〜33i毎に設ける構成を採っていた。これに対し、実施例2に係る信号線駆動回路60Cでは、i本の信号線331〜33iを単位として当該単位毎に容量素子63を1つ設ける構成を採っている。

【0134】

具体的には、実施例2に係る信号線駆動回路60Cにおいて、サンプリングスイッチ621〜62iの入力ノードNin_1〜Nin_iは、i本の信号線331〜33iを単位として共通に接続されている。そして、この共通に接続された共通入力ノードNin_0と、例えば1列目の伝送線La1,Lb1との間に容量素子63が接続されている。

【0135】

容量素子63は、例えばMOS容量から成る。具体的には、容量素子63は、サンプリングスイッチ621〜62iの共通入力ノードNin_0と伝送線La1との間に接続されたPチャネルMOSトランジスタと、共通入力ノードNin_0と伝送線Lb1との間に接続されたNチャネルMOSトランジスタとから成る。容量素子63のトランジスタサイズは、サンプリングスイッチ621〜62iを構成するトランジスタの半分のゲート面積が目安である。

【0136】

このように、容量素子63をi本の信号線331〜33iを単位として1つ設ける構成を採る実施例2に係る信号線駆動回路60Cによれば、容量素子63を信号線331〜33i毎に設ける構成を採る実施例1に係る信号線駆動回路60Aよりも簡単な回路構成にて、同様の作用、効果を得ることができる。

【0137】

すなわち、サンプリングスイッチ621〜62iがオフする際、共通入力ノードNin_0に接続された容量素子63が、サンプリングスイッチ621と逆相に動作する。この逆相の動作による容量素子63の作用により、サンプリングスイッチ621〜62iのオフ時に生じたチャージインジェクションやクロックフィードスルーの影響、換言すれば、当該影響による共通入力ノードNin_0、ひいては、入力ノードNin_1〜Nin_iの電位の揺れを抑えることができる。

【0138】

これにより、選択パルスSEL1〜SELiの相互間にオフ時のタイミング(即ち、ホールドタイミング)に微小なずれが生じていたとしても、所望の電圧値の基準電圧Vofstを信号線331〜33iに書き込むことができる。但し、本例では、1列目の選択パルスSEL1,xSEL1によって容量素子63を動作させる構成を採っているため、選択パルスSEL1,xSEL1よりも早いタイミングで遷移する選択パルスが存在する場合には、当該選択パルスの画素列についてはタイミングずれを吸収することはできない。

【0139】

このような観点からすれば、単位となるi本の信号線331〜33iに対応する選択パルスSEL1〜SELi,xSEL1〜xSELiのうち、遷移タイミングが一番早い選択パルスを、容量素子63を動作させる選択パルスとし用いるのが好ましい。そうすることで、ホールドタイミングに微小なずれが生じていたとしても、全ての画素列について、タイミングずれを吸収することができる。

【0140】

<3.電子機器>

以上説明した本開示の表示装置の駆動回路は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示する表示部を有するあらゆる分野の電子機器において、その表示部(表示装置)の駆動回路として用いることが可能である。

【0141】

上述した実施形態の説明から明らかなように、本開示の表示装置の駆動回路は、半導体チップのサイズを増大させることなく、低消費電力にて、所望の電圧値の基準電圧Vofstを信号線に書き込むことができる。これにより、当該駆動回路を用いる表示装置にあっては、各画素列において閾値補正処理をより確実に行うことができるため、輝度ムラのない均一な画質の表示画像を得ることができる。従って、あらゆる分野の電子機器において、その表示部として本開示の駆動回路を有する表示装置を用いることで、より優れた画像表示を実現できる。

【0142】

本開示の駆動回路を有する表示装置を表示部として用いる電子機器としては、例えば、ヘッドマウントディスプレイ、デジタルカメラ、ビデオカメラや、PDA(Personal Digital Assistant)、ゲーム機、電子書籍等の携帯情報機器や、携帯電話機等の携帯通信機器などを例示することができる。

【0143】

<4.本開示の構成>

尚、本開示は以下のような構成を採ることができる。

(1)画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える表示装置の駆動回路。

(2)前記サンプリングスイッチは、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されて成るアナログスイッチである

前記(1)に記載の表示装置の駆動回路。

(3)前記容量素子は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極に対して互いに逆相の選択パルスを伝送する伝送線と前記入力ノードとの間に接続されたMOS容量である

前記(2)に記載の表示装置の駆動回路。

(4)前記MOS容量のゲート電極の面積は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極の面積の半分である

前記(3)に記載の表示装置の駆動回路。

(5)前記サンプリングスイッチの入力側には、当該サンプリングスイッチに対して前記所定の直流電圧を入力するアンプが接続されている

前記(1)から前記(4)のいずれかに記載の表示装置の駆動回路。

(6)前記サンプリングスイッチは、複数の信号線を単位として入力ノードが共通に接続されている

前記(1)から前記(5)のいずれかに記載の表示装置の駆動回路。

(7)前記容量素子は、前記複数の信号線を単位として共通に接続された共通入力ノードに1つ接続されている

前記(6)に記載の表示装置の駆動回路。

(8)前記複数の信号線に対応する複数のサンプリングスイッチを独立したタイミングで動作させる複数の選択パルスのうち、遷移タイミングが一番早い選択パルスを前記容量素子の動作に用いる

前記(7)に記載の表示装置の駆動回路。

(9)前記サンプリングスイッチは、前記所定の直流電圧に続いて時系列で入力される映像信号の信号電圧を時分割でサンプリングして前記信号線に書き込む

前記(6)から前記(8)のいずれかに記載の表示装置の駆動回路。

(10)前記サンプリングスイッチの出力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記出力ノードの電位の揺れを吸収する容量素子を有する

前記(1)から前記(9)のいずれかに記載の表示装置の駆動回路。

(11)前記画素は、電気光学素子を駆動する駆動トランジスタ、前記信号線と前記駆動トランジスタのゲート電極との間に接続された書込みトランジスタ、及び、前記駆動トランジスタのゲート電極と一方のソース/ドレイン電極との間に接続された保持容量を有する

前記(1)から前記(10)のいずれかに記載の表示装置の駆動回路。

(12)前記画素は、前記書込みトランジスタによって前記所定の直流電圧が書き込まれたときの前記駆動トランジスタのゲート電圧を初期化電圧とし、当該初期化電圧から前記駆動トランジスタの閾値電圧を減じた電圧に向けて当該駆動トランジスタのソース電圧を変化させる閾値補正処理を行う

前記(11)に記載の表示装置の駆動回路。

(13)画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置。

(14)画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置を有する電子機器。

【符号の説明】

【0144】

10・・・有機EL表示装置、20・・・画素、21・・・有機EL素子、22・・・駆動トランジスタ、23・・・書込みトランジスタ、24・・・保持容量、30・・・画素アレイ部、40・・・書込み走査回路、50・・・電源供給走査回路、60,60A,60B,60C・・・信号線駆動回路、61・・・アンプ、62(621〜62i)・・・サンプリングスイッチ、63(631〜63i),64(641〜64i)・・・容量素子(MOS容量)、70・・・半導体基板

【特許請求の範囲】

【請求項1】

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える表示装置の駆動回路。

【請求項2】

前記サンプリングスイッチは、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されて成るアナログスイッチである

請求項1に記載の表示装置の駆動回路。

【請求項3】

前記容量素子は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極に対して互いに逆相の選択パルスを伝送する伝送線と前記入力ノードとの間に接続されたMOS容量である

請求項2に記載の表示装置の駆動回路。

【請求項4】

前記MOS容量のゲート電極の面積は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極の面積の半分である

請求項3に記載の表示装置の駆動回路。

【請求項5】

前記サンプリングスイッチの入力側には、当該サンプリングスイッチに対して前記所定の直流電圧を入力するアンプが接続されている

請求項1に記載の表示装置の駆動回路。

【請求項6】

前記サンプリングスイッチは、複数の信号線を単位として入力ノードが共通に接続されている

請求項1に記載の表示装置の駆動回路。

【請求項7】

前記容量素子は、前記複数の信号線を単位として共通に接続された共通入力ノードに1つ接続されている

請求項6に記載の表示装置の駆動回路。

【請求項8】

前記複数の信号線に対応する複数のサンプリングスイッチを独立したタイミングで動作させる複数の選択パルスのうち、遷移タイミングが一番早い選択パルスを前記容量素子の動作に用いる

請求項7に記載の表示装置の駆動回路。

【請求項9】

前記サンプリングスイッチは、前記所定の直流電圧に続いて時系列で入力される映像信号の信号電圧を時分割でサンプリングして前記信号線に書き込む

請求項6に記載の表示装置の駆動回路。

【請求項10】

前記サンプリングスイッチの出力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記出力ノードの電位の揺れを吸収する容量素子を有する

請求項1に記載の表示装置の駆動回路。

【請求項11】

前記画素は、電気光学素子を駆動する駆動トランジスタ、前記信号線と前記駆動トランジスタのゲート電極との間に接続された書込みトランジスタ、及び、前記駆動トランジスタのゲート電極と一方のソース/ドレイン電極との間に接続された保持容量を有する

請求項1に記載の表示装置の駆動回路。

【請求項12】

前記画素は、前記書込みトランジスタによって前記所定の直流電圧が書き込まれたときの前記駆動トランジスタのゲート電圧を初期化電圧とし、当該初期化電圧から前記駆動トランジスタの閾値電圧を減じた電圧に向けて当該駆動トランジスタのソース電圧を変化させる閾値補正処理を行う

請求項11に記載の表示装置の駆動回路。

【請求項13】

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置。

【請求項14】

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置を有する電子機器。

【請求項1】

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える表示装置の駆動回路。

【請求項2】

前記サンプリングスイッチは、PチャネルMOSトランジスタとNチャネルMOSトランジスタとが並列に接続されて成るアナログスイッチである

請求項1に記載の表示装置の駆動回路。

【請求項3】

前記容量素子は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極に対して互いに逆相の選択パルスを伝送する伝送線と前記入力ノードとの間に接続されたMOS容量である

請求項2に記載の表示装置の駆動回路。

【請求項4】

前記MOS容量のゲート電極の面積は、前記PチャネルMOSトランジスタ及び前記NチャネルMOSトランジスタの各ゲート電極の面積の半分である

請求項3に記載の表示装置の駆動回路。

【請求項5】

前記サンプリングスイッチの入力側には、当該サンプリングスイッチに対して前記所定の直流電圧を入力するアンプが接続されている

請求項1に記載の表示装置の駆動回路。

【請求項6】

前記サンプリングスイッチは、複数の信号線を単位として入力ノードが共通に接続されている

請求項1に記載の表示装置の駆動回路。

【請求項7】

前記容量素子は、前記複数の信号線を単位として共通に接続された共通入力ノードに1つ接続されている

請求項6に記載の表示装置の駆動回路。

【請求項8】

前記複数の信号線に対応する複数のサンプリングスイッチを独立したタイミングで動作させる複数の選択パルスのうち、遷移タイミングが一番早い選択パルスを前記容量素子の動作に用いる

請求項7に記載の表示装置の駆動回路。

【請求項9】

前記サンプリングスイッチは、前記所定の直流電圧に続いて時系列で入力される映像信号の信号電圧を時分割でサンプリングして前記信号線に書き込む

請求項6に記載の表示装置の駆動回路。

【請求項10】

前記サンプリングスイッチの出力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記出力ノードの電位の揺れを吸収する容量素子を有する

請求項1に記載の表示装置の駆動回路。

【請求項11】

前記画素は、電気光学素子を駆動する駆動トランジスタ、前記信号線と前記駆動トランジスタのゲート電極との間に接続された書込みトランジスタ、及び、前記駆動トランジスタのゲート電極と一方のソース/ドレイン電極との間に接続された保持容量を有する

請求項1に記載の表示装置の駆動回路。

【請求項12】

前記画素は、前記書込みトランジスタによって前記所定の直流電圧が書き込まれたときの前記駆動トランジスタのゲート電圧を初期化電圧とし、当該初期化電圧から前記駆動トランジスタの閾値電圧を減じた電圧に向けて当該駆動トランジスタのソース電圧を変化させる閾値補正処理を行う

請求項11に記載の表示装置の駆動回路。

【請求項13】

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置。

【請求項14】

画素が行列状に配置されて成る画素アレイ部の画素列単位で配線された信号線毎に設けられ、入力される所定の直流電圧をサンプリングして前記信号線に書き込むサンプリングスイッチと、

前記サンプリングスイッチの入力ノードに接続され、当該サンプリングスイッチのスイッチングに起因する前記入力ノードの電位の揺れを吸収する容量素子と

を備える駆動回路を用いた表示装置を有する電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−97100(P2013−97100A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−238604(P2011−238604)

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]