表示装置及びその制御方法

【課題】小規模な外部周辺回路により駆動可能な画素回路を有し、簡略化された製造工程による表示装置及びその制御方法を提供する。

【解決手段】表示装置1が有する発光画素は、有機EL素子14と、ドレインが電源線PSに接続された電流駆動トランジスタ21と、電流駆動トランジスタ21のVgsを保持するコンデンサ22と、コンデンサ22と電源線PSとを導通させるスイッチトランジスタ23と、コンデンサ22と初期化電源線PIとを導通させるスイッチトランジスタ24と、電流駆動トランジスタ21により駆動される電流を有機EL素子14へ流すための電流径路を導通及び遮断する電流スイッチトランジスタ11と、電流スイッチトランジスタ11のVgsを保持するコンデンサ12と、電流スイッチトランジスタ11のゲートとデータ線DTとを導通させる選択トランジスタ13とを備える。

【解決手段】表示装置1が有する発光画素は、有機EL素子14と、ドレインが電源線PSに接続された電流駆動トランジスタ21と、電流駆動トランジスタ21のVgsを保持するコンデンサ22と、コンデンサ22と電源線PSとを導通させるスイッチトランジスタ23と、コンデンサ22と初期化電源線PIとを導通させるスイッチトランジスタ24と、電流駆動トランジスタ21により駆動される電流を有機EL素子14へ流すための電流径路を導通及び遮断する電流スイッチトランジスタ11と、電流スイッチトランジスタ11のVgsを保持するコンデンサ12と、電流スイッチトランジスタ11のゲートとデータ線DTとを導通させる選択トランジスタ13とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及びその制御方法に関し、特に電流駆動型の発光素子を用いた画像表示装置及びその制御方法に関する。

【背景技術】

【0002】

電流駆動型の発光素子を用いた画像表示装置として、有機エレクトロルミネッセンス(EL)素子を用いた画像表示装置が知られている。この自発光する有機EL素子を用いた有機EL表示装置は、液晶表示装置に必要なバックライトが不要で装置の薄型化に最適である。また、視野角にも制限がないため、次世代の表示装置として実用化が期待されている。また、有機EL表示装置に用いられる有機EL素子は、各発光素子の輝度がそこに流れる電流値により制御される点で、液晶セルがそこに印加される電圧により制御されるのとは異なる。

【0003】

有機EL表示装置では、通常、画素を構成する有機EL素子がマトリクス状に配置される。複数の行電極(走査線)と複数の列電極(信号線)との交点に有機EL素子を設け、選択した行電極と複数の列電極との間にデータ信号に相当する電圧を印加するようにして有機EL素子を駆動するものをパッシブマトリクス型の有機ELディスプレイと呼ぶ。

【0004】

一方、複数の走査線と複数の信号線との交点にスイッチング薄膜トランジスタ(TFT:Thin Film Transistor)を設け、このスイッチングTFTに駆動素子のゲートを接続し、選択した走査線を通じてこのスイッチングTFTをオンさせて信号線からデータ信号を駆動素子に入力する。この駆動素子によって有機EL素子を駆動するものをアクティブマトリクス型の有機EL表示装置と呼ぶ。

【0005】

アクティブマトリクス型の有機EL表示装置は、各行電極(走査線)を選択している期間のみ、それに接続された有機EL素子が発光するパッシブマトリクス型の有機EL表示装置とは異なり、次の走査(選択)まで有機EL素子を発光させることが可能であるため、走査線数が増大してもディスプレイの輝度減少を招くようなことはない。従って、アクティブマトリクス型の有機EL表示装置は、低電圧で駆動でき、低消費電力化が可能となる。

【0006】

特許文献1には、アクティブマトリクス型の有機EL表示装置における表示部の回路構成が開示されている。

【0007】

図8は、特許文献1に記載された従来の有機ELディスプレイ装置における表示部の回路構成図である。同図に記載された有機ELディスプレイ装置500は、表示させる画素501を選択する選択線513と、選択された画素501にデータ電圧を与える信号線511と、選択線513と信号線511との交点に対応してマトリクス状に配置される電流駆動型の有機EL素子527と、電源電圧を印加する電源配線512と、電源配線512と有機EL素子527との間に直列に接続されるp型の第1トランジスタ523及び第2トランジスタ521と、第1トランジスタ523のゲート端子とドレイン端子を接続または遮断するn型の第3トランジスタ524と、第1トランジスタ523のゲート端子と可変電位配線515との間に設けられたコンデンサ526と、第2トランジスタ521のゲート端子と信号線511との間に接続されそのゲート端子が選択線513に接続されるn型の第4トランジスタ522とを備えた構成である。

【0008】

以下、上記のように構成される画素501の表示動作について説明する。画素501の表示動作は、時間分割階調方式であり、ソースドライバ及びゲートドライバが実行する。

【0009】

第2トランジスタ521のゲート端子に与えられる電位は、時間分割階調表示データである。時間分割階調表示を行なうには、ゲートドライバにより選択線513がHIGH電位とされた期間に、ソースドライバにより第4トランジスタ522を通して第2トランジスタ521のゲート端子にON電位またはOFF電位が印加される。

【0010】

一方、第1トランジスタ523の出力電流を設定する動作においては、まず、可変電位配線515の電位を所定の電位Vpにし、制御線514をHIGH電位として第3トランジスタ524を導通状態とする。また、選択線513をHIGHレベルとしてソースドライバから第2トランジスタ521を一瞬導通状態とする電圧を印加し、直ぐに非導通状態となる電圧を印加する。このとき、第1トランジスタ523のゲート−ドレイン間は第3トランジスタ524を通して短絡されているので、第1トランジスタ523のゲート端子電位は低下しON電位となる。その後、第2トランジスタ521が上記のように非導通状態となると、第1トランジスタ523のドレイン端子電位が上昇する。その結果、第1トランジスタ523のゲート端子電位が上昇し、第1トランジスタ523が非導通状態に変化する。このときのソース−ゲート間電圧が、第1トランジスタ523の閾値電圧となる。

【0011】

その後、制御線514をLOW電位として第3トランジスタ524を非導通状態とし、コンデンサ526の電位を保持して、さらに、可変電位配線515の電位をVpよりVaだけ低い電位に変化させる。これにより、第1トランジスタ523のゲート端子−ソース端子間電圧Vgsは閾値電位Vth−Vaとなる。

【0012】

なお、第1トランジスタ523のソース−ドレイン間電圧Vdsとソース−ゲート間電圧Vgsとの間に、|Vds|≧|Vgs| の関係があるとき、つまり第1トランジスタ523が飽和領域で動作するとき、第1トランジスタ523の閾値ばらつきを補償して第1トランジスタ523を流れる電流値を設定することができる。そして、第2トランジスタ521が導通状態になると、第1トランジスタ523から第2トランジスタ521を通して有機EL素子527に、閾値電圧に依らない一定の駆動電流Idsを流すことが可能となる。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2006−30946号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

しかしながら、特許文献1に記載された従来の有機ELディスプレイ装置500は、駆動電流Idsを設定するために、基本的な表示動作に必要な信号線511及び選択線513の電位を変化させるドライバ回路に加え、可変電位配線515及び制御線514の電位を変化させるドライバ回路がそれぞれ必要であり、外部周辺回路の構成が複雑である。

【0015】

また、特許文献1に記載された画素501の画素回路では、n型及びp型チャネルのTFTを両方用いており、TFTとして安価で製造容易なアモルファスシリコンTFTに代表されるn型チャネルのTFTのみを用いて画素回路を製造することが困難である。

【0016】

上記課題に鑑み、本発明は、小規模な外部周辺回路により駆動可能な画素回路を有し、簡略化された製造工程による表示装置及びその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0017】

上記課題を解決するために、本発明の一態様に係る表示装置は、マトリクス状に配置された複数の発光画素を有する表示部を備える表示装置であって、電源電圧を前記複数の発光画素に供給するための電源線と、前記複数の発光画素を初期化する初期化電圧を前記複数の発光画素に供給するための初期化電源線と、制御線と、画素行ごとに配置され、映像信号に対応したデータ電圧を書き込む発光画素を選択するための複数の走査線と、画素列ごとに配置され、選択された発光画素に前記データ電圧を書き込むための複数のデータ線とを備え、前記複数の発光画素のそれぞれは、電流駆動型の発光素子と、前記発光素子に定電流を供給するための定電流駆動部と、前記定電流駆動部から前記発光素子へ供給される前記定電流の電流径路を導通及び遮断する定電流スイッチ部とを備え、前記定電流駆動部は、ソース電極及びドレイン電極の一方が前記電源線に接続され、前記電源線からの電流を駆動する電流駆動トランジスタと、前記電流駆動トランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第1コンデンサと、ゲート電極が前記制御線に接続され、前記第1コンデンサの一方の電極と前記電源線との導通及び非導通を切り換える第1スイッチトランジスタと、ゲート電極が前記制御線に接続され、前記第1コンデンサの他方の電極と前記初期化電源線との導通及び非導通を切り換える第2スイッチトランジスタとを備え、前記定電流スイッチ部は、ソース電極及びドレイン電極の一方が前記電流駆動トランジスタのソース電極及びドレイン電極の他方に接続され、ソース電極及びドレイン電極の他方が前記発光素子のアノード電極に接続され、前記電流駆動トランジスタにより駆動される電流を前記発光素子へ流すための前記電流径路を導通及び遮断する電流スイッチトランジスタと、前記電流スイッチトランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第2コンデンサと、ゲート電極が前記複数の走査線のうちの対応する走査線に接続され、前記電流スイッチトランジスタのゲート電極と前記データ線との導通及び非導通を切り換える選択トランジスタとを備えることを特徴とする。

【0018】

上記構成によれば、従来では、基本的な書き込み動作及び発光動作に必要な配線の電位を変化させるドライバ回路に加えて制御線及び可変電位配線を変化させるドライバ回路が必要であったのに対して、制御線の電位を変化させるドライバ回路のみが新たに必要となるだけであり、外部周辺回路の構成を簡略化できる。

【0019】

また、本発明の一態様に係る表示装置は、さらに、前記複数の走査線及び前記制御線に接続され、前記第1スイッチトランジスタ、前記第2スイッチトランジスタ及び前記選択トランジスタの導通及び非導通を制御する走査線制御回路と、前記複数のデータ線に接続され、前記走査線制御回路により前記選択トランジスタが導通状態となった場合、前記電流スイッチトランジスタの前記ゲート電極と前記ドレイン電極または前記ソース電極との間の電圧を決定する前記データ電圧を前記データ線に出力する信号線制御回路とを備えることが好ましい。

【0020】

上記構成によれば、定電流駆動部の第1コンデンサに初期化電圧を設定する場合、電流は電源線と初期化電源線との間を流れ、走査線制御回路及び信号線制御回路へ上記電流が流れ込むことが回避されるので制御回路での損失を低減することが可能となる。

【0021】

また、本発明の一態様に係る表示装置は、前記電流スイッチトランジスタが導通状態となる場合の前記データ電圧の絶対値は、前記電流スイッチトランジスタのドレイン−ソース間電圧の絶対値より大きく、前記電源電圧と前記初期化電圧との電位差の絶対値は、前記電流駆動トランジスタのドレイン−ソース間電圧の絶対値より小さいことが好ましい。

【0022】

これにより、電流駆動トランジスタは飽和領域で動作するので、電源電圧やソース電位の変動などがあっても安定して定電流を供給することができる。また、電流スイッチトランジスタは線形領域で動作するので、オン抵抗が小さく電圧降下が抑制されたスイッチング動作及び電流駆動となり、低消費電力化が実現される。

【0023】

また、本発明の一態様に係る表示装置は、単位表示画像を書き換える時間である1フレーム時間内に、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタの導通状態への切り換えにより前記電源電圧と前記初期化電圧との電位差が前記第1コンデンサに印加される回数は、前記1フレーム時間内に前記信号線制御回路が前記データ電圧を前記データ線に出力する回数よりも少なくてもよい。

【0024】

この構成によれば、電流源としての電流駆動トランジスタの条件設定に必要な時間が短縮されるため、結果的に発光期間を長く確保することが可能となる。よって、高精細な表示パネルを提供でき、また、有機EL素子に流れる電流のピーク値を低くすることができるので、高効率な輝度制御を実行することが可能となる。

【0025】

また、前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全て同一の導電型のチャネルを有する薄膜トランジスタであってもよい。

【0026】

また、前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全てn型のチャネルを有する薄膜トランジスタであることが好ましい。

【0027】

これにより、特に、n型トランジスタのみを用いて画素回路を構成している場合、アモルファスシリコンTFTの製造プロセスを用いて安価かつ簡易的に表示パネルを製造することが可能となる。

【0028】

また、前記電流駆動トランジスタは、飽和領域で動作し、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、線形領域で動作することが好ましい。

【0029】

これにより、電流駆動トランジスタは飽和領域で動作するので、電源電圧やソース電位の変動などがあっても安定して定電流を供給することができる。また、電流スイッチトランジスタ、選択トランジスタ、第1トランジスタ及び第2トランジスタは線形領域で動作するので、オン抵抗の小さいスイッチングとなり低消費電力化が実現される。

【0030】

また、前記発光素子は、有機EL素子であってもよい。

【0031】

また、前記発光素子は、無機EL素子であってもよい。

【0032】

また、本発明は、このような特徴的な手段を備える表示装置として実現することができるだけでなく、表示装置に含まれる特徴的な手段をステップとする表示装置の制御方法として実現することができる。

【発明の効果】

【0033】

本発明の表示装置及びその制御方法によれば、従来に比べドライバ回路が削減された小規模な外部周辺回路により駆動が可能となり、外部周辺回路を簡略化できる。

【図面の簡単な説明】

【0034】

【図1】本発明の実施の形態に係る表示装置の機能ブロック図である。

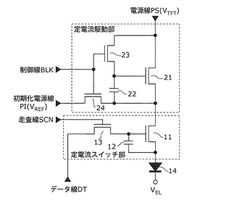

【図2】本発明の実施の形態に係る表示装置が有する表示部の回路構成図である。

【図3】本発明の実施の形態に係る表示装置が有する走査線制御回路の内部回路図である。

【図4】本発明の実施の形態に係る表示装置が有する信号線制御回路の内部回路図である。

【図5】本発明の実施の形態に係る表示装置の駆動タイミングチャートである。

【図6】本発明の実施の形態に係る表示装置の電流源設定動作を説明する状態遷移図である。

【図7】本発明の実施の形態に係る表示装置の書き込み動作を説明する状態遷移図である。

【図8】特許文献1に記載された従来の有機ELディスプレイ装置における表示部の回路構成図である。

【発明を実施するための形態】

【0035】

以下、本発明を実施するための形態について、図面を参照しながら説明する。

【0036】

<表示装置の構成>

図1は、本発明の実施の形態に係る表示装置の機能ブロック図である。同図に記載された表示装置1は、ディジタル階調制御方式で輝度を変動させるアクティブマトリクス型ディスプレイ装置であり、制御回路2と、走査線制御回路4と、信号線制御回路5と、表示部6とを備える。

【0037】

制御回路2は、入力された映像信号に応じて、表示部6の画素ごとに発光させるサブフレームを割り当て、走査線制御回路4及び信号線制御回路5に制御信号を出力する。

【0038】

走査線制御回路4は、表示部6に走査電圧を印加し、信号線制御回路5は表示部にデータ電圧を印加する。以下、上述した表示装置1の構成要素について詳細に説明する。

【0039】

図2は、本発明の実施の形態に係る表示装置が有する表示部の回路構成図である。表示部6は、ディスプレイの解像度(m×n)に応じた、マトリクス状に配置された複数の発光画素が配置された表示部であるが、図2には、表示部6の一部である、1つの発光画素が記載されている。図2に記載された表示部6の発光画素は、電流スイッチトランジスタ11と、スイッチトランジスタ23及び24と、コンデンサ12及び22と、選択トランジスタ13と、有機EL素子14と、電流駆動トランジスタ21と、画素列ごとに配置されたデータ線DTと、画素行ごとに配置された走査線SCNと、制御線BLKと、初期化電源線PIと、電源線PSとを備える。

【0040】

また、表示部6が有する複数の発光画素は、全て同じ回路構成となっている。

【0041】

表示部6が有する発光画素は、有機EL素子14に供給する発光電流である定電流を発生させる定電流駆動部と、当該定電流駆動部から有機EL素子14へ供給される上記定電流の電流径路を導通及び遮断する定電流スイッチ部とに大別される。

【0042】

定電流駆動部は、電流駆動トランジスタ21と、コンデンサ22と、スイッチトランジスタ23及び24とで構成される。定電流駆動部は、電流駆動トランジスタ21を飽和領域で動作させることにより、電流駆動トランジスタ21のソース−ドレイン間電圧Vdsが変動しても定電流を発生し、当該定電流を定電流スイッチ部へ安定供給する。

【0043】

定電流スイッチ部は、電流スイッチトランジスタ11と、コンデンサ12と、選択トランジスタ13とで構成される。データ線DTから供給される2値のデータ電圧(オン電圧及びオフ電圧)が電流スイッチトランジスタ11のゲート端子に印加されることより、電流スイッチトランジスタ11のソース−ドレイン間は、導通状態または非導通状態となる。これにより、定電流駆動部からの定電流を有機EL素子14へ流す、または、流さないという動作がサブフィールド単位で実行され、ディジタル階調制御がなされる。ここで、電流スイッチトランジスタ11のオンオフ制御におけるスイッチング損失を低減させるため、電流スイッチトランジスタ11は、低オン抵抗である線形領域で動作させることが望ましい。一方、薄膜トランジスタを線形領域で動作させた場合、ソース−ドレイン間電圧Vdsの変動により、薄膜トランジスタのドレイン−ソース電流Idsが変動しやすいという課題がある。上記課題を解消するため、上述した定電流駆動部によりVdsが変動してもIdsが変動しない定電流が供給される。

【0044】

つまり、飽和領域で動作する電流駆動トランジスタ21を有する定電流駆動部により、電源電圧やソース電位の変動などがあっても安定して定電流を供給することができ、線形領域で動作する電流スイッチトランジスタ11を有する定電流スイッチ部により、低損失なスイッチングによるディジタル階調表示が可能となる。

【0045】

以下、発光画素の各構成要素及びそれらの接続状態を説明する。

【0046】

電源線PSは、すべての画素行に配置され、電流駆動トランジスタ21のドレインに接続され、正の電源電圧VTFTを当該接続点に印加することにより、電源電圧を複数の発光画素に供給する。

【0047】

なお、本実施の形態では、全ての発光画素に対して、同じ電源電圧VTFTが同じタイミングで印加されるので、電源線PSは、全ての電源線が接続された共通線となっていてもよい。

【0048】

走査線SCNは、画素行ごとに配置され、映像信号に対応したデータ電圧を書き込む発光画素を選択する。

【0049】

制御線BLKは、すべての画素行に配置され、定電流駆動部を初期化するための機能を有する。

【0050】

初期化電源線PIは、すべての画素行に配置され、全ての発光画素を初期化する初期化電圧VREFを全ての発光画素に供給する機能を有する。具体的には、初期化電源線PIは、定電流駆動部を初期化する場合にコンデンサ22の他方の電極に初期化電圧VREFを供給する。なお、本実施の形態では、全ての発光画素に対して、同じ初期化電圧VREFが同じタイミングで印加されるので、各画素行に配置された初期化電源線PIは共通線となっている。よって、駆動回路などの外部周辺回路を簡略化できる。

【0051】

データ線DTは、画素列ごとに配置され、選択された発光画素にデータ電圧を書き込むための機能を有する。

【0052】

有機EL素子14は、電流駆動型の発光素子であり、アノード端子が電流スイッチトランジスタ11のソース端子及びコンデンサ12の一方の電極と接続され、カソード端子が基準端子(基準電圧VEL)に接続されている。

【0053】

電流駆動トランジスタ21は、ドレイン端子が電源線PSに接続され、ゲート端子がコンデンサ22の一方の電極と接続され、ソース端子がコンデンサ22の他方の電極と接続され、電源線PSからの電流を駆動する。電流駆動トランジスタ21は、ドレイン−ソース間電圧Vdsがゲート−ソース間電圧Vgsに比べて十分大きい領域である飽和領域にて動作させることにより、Vgsに応じて、電源電圧から一定の電流を供給する定電流駆動用の薄膜トランジスタである。なお、電流駆動トランジスタ21は、上述したように、Vdsの変動を受けない安定したIdsを有機EL素子14へ供給するが、映像信号に基づく表示階調の傾向により、フレーム単位で、後述する初期化電圧VREFを調整することによりVgsを変化させてIdsの大きさを調整することが可能となる。これにより、全ての階調を高精度に表示することが可能となる。

【0054】

コンデンサ22は、電流駆動トランジスタ21のゲート電極及びソース電極に接続され、電流駆動トランジスタ21のゲート−ソース間電圧を保持する第1コンデンサである。

【0055】

電流スイッチトランジスタ11は、ドレイン端子が電流駆動トランジスタ21のソース端子と接続され、ゲート端子がコンデンサ12の他方の端子と接続され、ソース端子がコンデンサ12の一方の端子及び有機EL素子14のアノード端子と接続され、ゲート−ソース間電圧Vgsがドレイン−ソース間電圧Vdsに比べて十分大きい領域である線形領域にて動作する、定電流スイッチング用の薄膜トランジスタである。電流スイッチトランジスタ11は、電流駆動トランジスタ21により駆動される定電流を有機EL素子14へ流すための電流径路を導通及び遮断する。

【0056】

コンデンサ12は、電流スイッチトランジスタ11のゲート電極とソース電極との間の電圧を保持する第2コンデンサである。

【0057】

選択トランジスタ13は、ドレイン端子が電流スイッチトランジスタ11のゲート端子と接続され、ゲート端子が走査線SCNと接続され、ソース端子がデータ線DTと接続され、有機EL素子14の発光を決定するデータ電圧を書き込むべき発光画素を選択する。つまり、選択トランジスタ13は、電流スイッチトランジスタ11のゲート電極とデータ線DTとの導通及び非導通を切り換える。

【0058】

スイッチトランジスタ23は、ドレイン端子が電源線PSと接続され、ゲート端子が制御線BLKと接続され、ソース端子が電流駆動トランジスタ21のゲート端子及びコンデンサ22の一方の電極と接続された第1スイッチトランジスタであり、スイッチトランジスタ24と同期制御されることにより、コンデンサ22の両端電圧である電流駆動トランジスタ21のVgsを確定させる。

【0059】

スイッチトランジスタ24は、ドレイン端子が電流駆動トランジスタ21のソース端子及びコンデンサ22の他方の電極と接続され、ゲート端子が制御線BLKと接続され、ソース端子が初期化電源線PIと接続された第2スイッチトランジスタであり、スイッチトランジスタ23と同期制御されることにより、コンデンサ22の両端電圧である電流駆動トランジスタ21のVgsを確定させる。

【0060】

電流スイッチトランジスタ11、スイッチトランジスタ23及び24、ならびに選択トランジスタ13は、入力された映像信号に基づいてゲート−ソース間に閾値電圧以上の電圧が印加されることにより、ドレイン−ソース間を導通状態とするスイッチ素子である。

【0061】

電流駆動トランジスタ21、電流スイッチトランジスタ11、スイッチトランジスタ23及び24、ならびに選択トランジスタ13は、同一の導電型のチャネルを有する薄膜トランジスタであることが好ましく、さらには、nチャネルのMOSFETで形成されていることが望ましい。上記トランジスタが、全て、nチャネルのMOSFETで形成されることにより、n型トランジスタのみを用いて画素回路を構成できるので、アモルファスシリコンTFTを用いて安価かつ簡易的に表示パネルを製造することが可能となる。

【0062】

上記回路構成において、データ線DTがHIGHレベル(Vdata)となり走査線SCNがHIGHレベル(VSCN)となることで、選択トランジスタ13のゲート−ソース間に、閾値電圧よりも十分大きい信号電圧が印加される。これにより、選択トランジスタ13は線形領域で動作しドレイン−ソース間はオン抵抗の低い導通状態となる。そして、選択トランジスタ13が導通状態になった後、データ線DTから選択トランジスタ13を経由してコンデンサ12が充電される。これにより、電流スイッチトランジスタ11のゲート−ソース間に、閾値電圧よりも十分大きい電圧が印加され、電流スイッチトランジスタ11は線形領域で動作しドレイン−ソース間はオン抵抗の低い導通状態となる。このとき、電源線PS→電流駆動トランジスタ21→電流スイッチトランジスタ11→有機EL素子14の経路で上述した電流駆動トランジスタ21による定電流が流れ有機EL素子14が発光する。

【0063】

また、本実施の形態では、発光素子として有機EL素子を用いているが、当該発光素子は電流駆動型の発光素子であればよく、例えば、無機EL素子であってもよい。

【0064】

<走査線制御回路>

次に、走査線制御回路4について説明する。走査線制御回路4は、制御回路2からの制御信号により、データ電圧書き込み期間において、発光画素行を選択するための走査信号を、走査線SCNを介して発光画素を有する表示部6に出力する。また、走査線制御回路4は、制御回路2からの制御信号により、初期化期間において、各発光画素の定電流値を定電流駆動部に設定するための初期化信号を、制御線BLKを介して発光画素を有する表示部6に出力する。

【0065】

図3は、本発明の実施の形態に係る表示装置が有する走査線制御回路の内部回路図である。走査線制御回路4は、走査信号の選択電圧であるVSCNまたは非選択電圧VLを選択し、画素行ごとに配置された走査線SCN1〜SCNmに印加する。

【0066】

画素行数がmである場合には、走査線制御回路4は、m本の走査線SCN1〜SCNmを介して表示部6に接続されている。走査線制御回路4は、任意の順序で1ライン毎に走査線SCN1〜SCNmに対して選択電圧VSCNまたは非選択電圧VLを供給することが可能である。もちろん、走査線SCN1、SCN2、・・・SCNmという様に、行順次に走査電圧を印加することも可能であり、あるいは、全ての走査線に対し同時にVSCNまたはVLを供給することも可能である。

【0067】

図3に記載された回路において、例えば、走査線SCN1に選択電圧VSCNを印加し、その他の走査線に非選択電圧VLを印加する場合には、走査線制御回路4は、スイッチSW41A及びスイッチSW42B、SW43B、・・・SW4mBをON状態とし、スイッチSW41B及びスイッチSW42A、SW43A、・・・SW4mAをOFF状態とする。

【0068】

さらに、図示しないが、走査線制御回路4は、初期化信号の選択電圧であるVBLKまたは非選択電圧を選択し、制御線BLKに印加する。制御線BLKに選択電圧VBLKまたは非選択電圧を印加する回路についても、選択電圧VSCNまたは非選択電圧VLを印加する回路と同様の構成である。

【0069】

つまり、走査線制御回路4は、複数の走査線SCN及び制御線BLKに接続され、スイッチトランジスタ23及び24ならびに選択トランジスタ13の導通及び非導通を制御する。

【0070】

なお、選択電圧VSCN及びVBLKを印加するタイミングについては、後述する。

【0071】

また、制御線BLKは、全ての発光画素に共通した制御線であってもよく、また、画素行ごとに配置された制御線BLK1〜BLKmであってもよい。

【0072】

<信号線制御回路>

次に、信号線制御回路5について説明する。信号線制御回路5は、データ電圧書き込み期間において、制御回路2からの制御信号により、走査線制御回路4から出力される走査信号に同期して、映像信号に対応したデータ電圧(オン電圧及びオフ電圧)を、データ線DTを介して電流スイッチトランジスタ11のゲート端子に出力する。

【0073】

図4は、本発明の実施の形態に係る表示装置が有する信号線制御回路の内部回路図である。信号線制御回路5は、スイッチSW51A〜SW5nA及びスイッチSW51B〜SW5nBによる切替えにより、オン電圧Vdataまたはオフ電圧を選択し、画素列ごとに配置されたデータ線DT1〜DTnに印加する。

【0074】

画素列数がnである場合には、信号線制御回路5は、n本のデータ線DT1〜DTnを介して表示部6に接続されている。各データ線には、信号線制御回路5の信号に応じて、1ライン毎にデータ線DT1〜DTnにオン電圧Vdataまたはオフ電圧を供給することが可能である。オン電圧Vdataまたはオフ電圧を印加するタイミングについては、後述する。

【0075】

以上のように、信号線制御回路5は、制御回路2からの制御信号により、データ電圧書き込み期間においてデータ電圧であるオン電圧またはオフ電圧を、データ線DTを介して表示部6に出力する。また、映像信号に応じた駆動信号により、表示部6の解像度に応じた画素列数n本のデータ線を同時に制御可能とするためのメモリ機能を有している。

【0076】

つまり、信号線制御回路5は、複数のデータ線DTに接続され、走査線制御回路4により選択トランジスタ13が導通状態となった場合、電流スイッチトランジスタ11のゲート−ソース間電圧を決定するデータ電圧をデータ線DTに出力する。

【0077】

なお、制御回路2は、発光画素の表示期間の長さを、電流スイッチトランジスタ11のオンオフ制御により変化させることで、有機EL素子14の発光輝度を制御する制御部として機能する。

【0078】

<表示装置の動作>

以下、図5〜7を用いて、表示装置1の動作について述べる。図5は、本発明の実施の形態に係る表示装置の駆動タイミングチャートである。図5の駆動タイミングチャートは、例として、走査線SCN1より行順次に走査した場合の表示装置の動作を表したものであり、上から順に、コンデンサ22の両端電圧V22、コンデンサ12の両端電圧V12、電流駆動トランジスタ21の状態TFT21、電流スイッチトランジスタ11の導通状態TFT11、選択トランジスタ13のゲート電圧V13、スイッチトランジスタ23のゲート電圧V23、スイッチトランジスタ24のゲート電圧V24、制御線BLKの電圧、データ線DTの電圧、走査線SCN1の電圧、・・・、走査線SCN1080の電圧を表している。なお、V22〜V24は、走査線SCN1に接続された画素行に属する発光画素についての動作を表している。また、上記電流駆動トランジスタ21の状態TFT21とは、スイッチトランジスタ23及び24が導通状態でありコンデンサ22が充電状態である場合をハイレベルとし、その他の場合をローレベルとして表している。また、上記電流スイッチトランジスタ11の導通状態TFT11とは、電流スイッチトランジスタ11のドレイン−ソース間が導通状態である場合をハイレベルとし、非導通状態である場合をローレベルとして表している。

【0079】

以下説明する表示装置1の動作は、初期化動作、書き込み動作及び発光動作という一連の単位を1サブフィールドとし、当該サブフィールドを繰り返し実行する。

【0080】

[初期化期間(電流源設定期間)]

定電流駆動部から供給される定電流を設定する初期化期間(電流源設定期間)における動作は、入力された映像信号に基づき、各画素の電流源となる電流駆動トランジスタ21のゲート−ソース間電圧Vgsを設定するステップである。

【0081】

まず、時刻t01〜時刻t02において、電流駆動トランジスタ21のVgsを設定するために、書き込み対象の電流駆動トランジスタ21に直列に接続されている電流スイッチトランジスタ11をオフさせる。オフさせる方法としては、図5のように、行順次に走査線SCNに走査電圧パルスを印加し、データ線DTにオフ電圧を印加して行毎にオフさせてもよいし、全ライン一斉に走査電圧パルスを印加してもよい。また、上記走査電圧パルスの長さは、初期化期間より前の発光期間の長さに応じて変化させてもよい。

【0082】

初期化期間の準備段階として上記動作を行うことにより、電流駆動トランジスタ21のソース電位が電流スイッチトランジスタ11及び有機EL素子14から切り離されてフローティング状態となるため、時刻t02以降での電流駆動トランジスタ21のソース電位を初期化電源線PIから任意に設定でき、これによりVgsを任意に調整することが可能となる。

【0083】

次に、時刻t02において、制御線BLKに正の電圧VBLKを印加し、スイッチトランジスタ23及び24のゲート電圧を閾値電圧以上としドレイン−ソース間の抵抗を下げオンさせる。この動作により、電流駆動トランジスタ21のVgsは、電源線PSと初期化電源線PIとの電位差により設定される。

【0084】

図6は、本発明の実施の形態に係る表示装置の電流源設定動作を説明する状態遷移図である。同図は、行列間で隣接する4つの発光画素6A〜6Dの時刻t02における電気的状態を表している。なお、本実施の形態では、電源線PS、制御線BLK及び初期化電源線PIが全ての発光画素で共通化されているものとしている。これにより、駆動回路などの外部周辺回路を簡略化できる。

【0085】

時刻t02において、走査線制御回路4は、制御線BLKに対してHIGHレベルの選択電圧VBLKを出力する。これにより、スイッチトランジスタ23及び24が導通状態となり、電流駆動トランジスタ21のVgsは、(VTFT−VREF)となる。図6において、矢印(破線)は電圧印加経路を示したものである。

【0086】

ここで、有機EL表示パネルの場合を想定して具体例にて説明する。例えば、電源線PSの電源電圧VTFTは10V、基準電圧VELは−2Vに設定される。また、電流駆動トランジスタ21のドレイン−ソース間電圧Vdsは5V程度、電流スイッチトランジスタ11のVdsは1V程度となる。かかる場合において、前述したように、電流駆動トランジスタ21を、安定した定電流源として動作させるためには、Vds>>VgsとなるようVgsを設定して飽和領域にて動作させる必要がある。つまり、VTFTとVREFとの電位差の絶対値は、電流駆動トランジスタ21のドレイン−ソース間電圧Vdsの絶対値より小さい。本具体例において、電流駆動トランジスタ21のVdsが5V程度であることから、電流駆動トランジスタ21のVgsを1V程度に設定することが望ましい。これより、初期化電圧VREFを9Vと設定すればよい。

【0087】

上述した時刻t02における走査線制御回路4の動作により、定電流駆動部の設定が完了する。

【0088】

その後、時刻t02〜時刻t03の期間において、走査線制御回路4は、制御線BLKをLOWレベルとして、スイッチトランジスタ23及び24のゲート電圧を閾値電圧以下とすることにより、電流駆動トランジスタ21のVgsを保持するコンデンサ22の両電極は、電源線PS及び初期化電源線PIから電気的に切り離される。

【0089】

[書き込み期間(ON/OFF設定期間)]

データ電圧を、選択された発光画素へ書き込む書き込み期間(ON/OFF設定期間)における動作は、各発光画素が有する電流スイッチトランジスタ11の導通状態及び非導通状態を切り換えるステップである。このため、走査線制御回路4は、走査線SCNごとに、選択電圧VSCNまたは非選択電圧VLを印加する。これにより、選択された走査線SCNが接続された画素行に属する発光画素に対して、対応するデータ線DTからのデータ電圧が印加され、電流スイッチトランジスタ11のゲート電圧が制御される。

【0090】

なお、図5では、制御回路2による処理により、サブフィールド期間t03〜t04及び期間t05〜t06では、1行目の発光画素が発光状態であり、サブフィールド期間t04〜t05では、1行目の発光画素が非発光状態であるものと仮定している。

【0091】

まず、時刻t03〜時刻t04のサブフィールド期間において、走査線制御回路4は、走査線SCN1〜SCNmに対して、走査信号パルスを印加する。ここで、走査線SCN1に接続された1行目の発光画素について、より具体的に説明する。

【0092】

図7は、本発明の実施の形態に係る表示装置が有する画素への書き込み動作を説明する状態遷移図である。同図は、行列間で隣接する4つの発光画素6A〜6Dの時刻t03における電気的状態を表している。

【0093】

時刻t03において、走査線制御回路4は、走査線SCN1に対して、選択トランジスタ13の閾値電圧以上となる選択電圧VSCNを出力する。これにより、選択トランジスタ13のドレイン−ソース間の抵抗が下がり、選択トランジスタ13が導通状態となる。また、信号線制御回路5は、データ線DTに対し、オン電圧Vdataを出力する。これにより、電流スイッチトランジスタ11のゲート電圧が閾値電圧以上となり電流スイッチトランジスタ11が導通状態となる。図7において、矢印(破線)は電圧印加経路を示したものであり、矢印(実線)は電流の流れを示したものである。

【0094】

なお、本実施の形態において、例えば、走査線SCN及び制御線BLKのHIGHレベルの電圧VSCN及びVBLKは+20Vであり、LOWレベルの電圧VLは−10Vに設定されている。また、前述したように、電流スイッチトランジスタ11を、スイッチング損失の小さいスイッチ素子として動作させるためには、Vgs>>VdsとなるようVgsを設定して線形領域にて動作させる必要がある。つまり、電流スイッチトランジスタ11が導通状態となる場合のデータ電圧の絶対値は、電流スイッチトランジスタ11のドレイン−ソース間電圧Vdsの絶対値より大きい。本具体例において、電流スイッチトランジスタ11のVdsが1V程度であることから、電流スイッチトランジスタ11のVgsを8V程度に設定することが望ましい。また、有機EL素子14に印加される電圧は、6V程度であることから、有機EL素子14のアノード電位、つまり電流スイッチトランジスタ11のソース電位は4V程度となる。上記電流スイッチトランジスタ11のVgs及びソース電位より、電流スイッチトランジスタ11に印加されるデータ電圧は、オン電圧として12V、オフ電圧として2V程度に設定すればよい。

【0095】

次に、時刻t03〜時刻t04において、走査線SCN1の走査電圧をVSCNからVLに変化させて選択トランジスタ13を非導通状態とし、電流スイッチトランジスタ11のゲート端子とデータ線DTとを電気的に切り離しても、電流スイッチトランジスタ11のゲート−ソース間に接続されたコンデンサ12により、電流スイッチトランジスタ11のVgs電位は保持される。このときのコンデンサ12の容量は、電流スイッチトランジスタ11をオンさせている最大時間幅が経過しても、電流スイッチトランジスタ11の閾値電圧以上の電位を保持できる容量以上とすることが望ましい。

【0096】

上記動作により電流スイッチトランジスタ11が導通状態となると、電源線PS→電流駆動トランジスタ21→電流スイッチトランジスタ11→有機EL素子14→基準端子の経路で電流が流れ、発光画素6A及び6Bの発光期間が開始する。発光期間は電流スイッチトランジスタ11が非導通状態になるまで継続する。

【0097】

その後、走査線SCN2、走査線SCN3、・・・、と順次走査することで、すべての発光画素に対して、所望のタイミングで電流スイッチトランジスタ11をオンさせることが可能となる。

【0098】

以上のように、時刻t03以降において、所望の発光画素に対し走査線ごとに書き込み動作を行うことで、サブフィールドごとに全ての発光画素に対して書き込み及び発光制御を行うことが可能となる。

【0099】

なお、図5に記載された一連の表示動作では、初期化動作を一度しか行っていないが、サブフィールドごとに行ってもよい。ただし、サブフィールド間で、定電流駆動部の電流設定値を変化させる必要が無い場合は初期化動作を行う必要が無く、サブフィールド間での初期化動作を省略することにより駆動時間を大幅に短縮することが可能となる。つまり、単位表示画像を書き換える時間である1フレーム時間内に制御線BLKにVBLKを印加しコンデンサ22に(VTFT−VREF)を設定する回数は、1フレーム時間内に信号線制御回路5がデータ電圧(オン電圧及びオフ電圧)をデータ線DTに出力する回数よりも少ないことが好ましい。これにより、電流源としての電流駆動トランジスタの条件設定に必要な時間が短縮されるため、結果的に発光期間を長く確保することが可能となる。よって、高精細な表示パネルを提供でき、また、有機EL素子に流れる電流のピーク値を低くすることができるので、高効率な輝度制御を実行することが可能となる。

【0100】

また、サブフィールド時分割式で輝度を変調する場合、電流スイッチトランジスタ11のオン/オフ時間比率の最大値または最小値によって最大輝度と最小輝度の制約が生ずるが、電流駆動部における電流設定値を変化させることで、輝度調節範囲を広げることが可能である。具体的には、例えば、電流駆動トランジスタ21のVgsの設定値を調整することにより、輝度調節範囲を広げることが可能である。

【0101】

また、初期化動作に必要な最大時間間隔に応じて、電流駆動トランジスタ21のVgsを保持するコンデンサ22の容量を設定することにより、電流駆動トランジスタ21のVgsを所望の値に保持することが可能となる。

【0102】

以上、本実施の形態によれば、画素回路に定電流源として機能する定電流駆動部が配置されたことにより、定電流スイッチ部を構成する電流スイッチトランジスタ11は、定電流源である必要はなく、画素回路のオンオフ状態を切り換えるスイッチ機能を有していればよい。よって、例えば、電流スイッチトランジスタ11に印加するデータ電圧、つまり、ゲート−ソース間電圧Vgsを、ドレイン−ソース間電圧Vdsに対して十分大きく設定しておくことにより、薄膜トランジスタの線形領域を利用することができるので、ドレイン−ソース電流Idsのオン抵抗を小さくすることが可能となる。よって、電流スイッチトランジスタ11のドレイン−ソース間に発光電流が流れるときの電圧降下を低減でき、表示パネルの電力損失を大幅に低減することができる。

【0103】

また、本実施の形態によれば、基本的な書き込み動作及び発光動作に必要な配線の電位を変化させるドライバ回路に対し、制御線BLKの電位を変化させるドライバ動作のみが新たに必要となるだけであり、外部周辺回路の構成を簡略化できる。

【0104】

さらに、本実施の形態によれば、電流駆動トランジスタ21のVgsを設定するための初期化期間において、電流は電源線PSから初期化電源線PIへと流れる。初期化電源線PIの出力電圧VREFは駆動信号に応じて電圧を変化させる必要は無く一定電圧とできるため、上記電源線PSから電流が流れ込むことによる損失を低減することが可能となる。

【0105】

以上、本発明に係る表示装置及びその制御方法について実施の形態に基づき説明したが、本発明に係る表示装置及びその制御方法は、上述した実施の形態に限定されるものではない。上記実施の形態に対して、本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本発明に係る表示装置を内蔵した各種機器も本発明に含まれる。

【0106】

なお、飽和領域を利用した定電流源である電流駆動トランジスタ21のチャネル幅を、電流スイッチトランジスタ11よりも広くすることが好ましい。これにより、電流駆動トランジスタ21のドレイン−ソース間に発光電流が流れるときの電圧降下を低減でき、表示パネルの電力損失を低減することが可能である。

【0107】

また、上記実施の形態では、各トランジスタのゲート電圧がHIGHレベルの場合にオン状態になるn型トランジスタとして記述しているが、これらをすべてp型トランジスタで形成し、走査線の極性を反転させた表示装置でも、上述した各実施の形態と同様の効果を奏する。あるいは、n型トランジスタ及びp型トランジスタが混在した構成の表示装置であってもよい。

【0108】

また、本発明に係る実施の形態では、各トランジスタは、ゲート、ソース及びドレインを有するFETであることを前提として説明してきたが、これらのトランジスタには、ベース、コレクタ及びエミッタを有するバイポーラトランジスタが適用されてもよい。この場合にも、本発明の目的が達成され同様の効果を奏する。

【産業上の利用可能性】

【0109】

本発明の表示装置及びその制御方法は、特に、ディジタル階調制御方式で輝度を変動させるアクティブ型ディスプレイに有用である。

【符号の説明】

【0110】

1 表示装置

2 制御回路

4 走査線制御回路

5 信号線制御回路

6 表示部

6A、6B、6C、6D 発光画素

11 電流スイッチトランジスタ

12、22 コンデンサ

13 選択トランジスタ

14、527 有機EL素子

21 電流駆動トランジスタ

23、24 スイッチトランジスタ

500 有機ELディスプレイ装置

501 画素

511 信号線

512 電源配線

513 選択線

514 制御線

515 可変電位配線

521 第2トランジスタ

522 第4トランジスタ

523 第1トランジスタ

524 第3トランジスタ

525、526 コンデンサ

【技術分野】

【0001】

本発明は、表示装置及びその制御方法に関し、特に電流駆動型の発光素子を用いた画像表示装置及びその制御方法に関する。

【背景技術】

【0002】

電流駆動型の発光素子を用いた画像表示装置として、有機エレクトロルミネッセンス(EL)素子を用いた画像表示装置が知られている。この自発光する有機EL素子を用いた有機EL表示装置は、液晶表示装置に必要なバックライトが不要で装置の薄型化に最適である。また、視野角にも制限がないため、次世代の表示装置として実用化が期待されている。また、有機EL表示装置に用いられる有機EL素子は、各発光素子の輝度がそこに流れる電流値により制御される点で、液晶セルがそこに印加される電圧により制御されるのとは異なる。

【0003】

有機EL表示装置では、通常、画素を構成する有機EL素子がマトリクス状に配置される。複数の行電極(走査線)と複数の列電極(信号線)との交点に有機EL素子を設け、選択した行電極と複数の列電極との間にデータ信号に相当する電圧を印加するようにして有機EL素子を駆動するものをパッシブマトリクス型の有機ELディスプレイと呼ぶ。

【0004】

一方、複数の走査線と複数の信号線との交点にスイッチング薄膜トランジスタ(TFT:Thin Film Transistor)を設け、このスイッチングTFTに駆動素子のゲートを接続し、選択した走査線を通じてこのスイッチングTFTをオンさせて信号線からデータ信号を駆動素子に入力する。この駆動素子によって有機EL素子を駆動するものをアクティブマトリクス型の有機EL表示装置と呼ぶ。

【0005】

アクティブマトリクス型の有機EL表示装置は、各行電極(走査線)を選択している期間のみ、それに接続された有機EL素子が発光するパッシブマトリクス型の有機EL表示装置とは異なり、次の走査(選択)まで有機EL素子を発光させることが可能であるため、走査線数が増大してもディスプレイの輝度減少を招くようなことはない。従って、アクティブマトリクス型の有機EL表示装置は、低電圧で駆動でき、低消費電力化が可能となる。

【0006】

特許文献1には、アクティブマトリクス型の有機EL表示装置における表示部の回路構成が開示されている。

【0007】

図8は、特許文献1に記載された従来の有機ELディスプレイ装置における表示部の回路構成図である。同図に記載された有機ELディスプレイ装置500は、表示させる画素501を選択する選択線513と、選択された画素501にデータ電圧を与える信号線511と、選択線513と信号線511との交点に対応してマトリクス状に配置される電流駆動型の有機EL素子527と、電源電圧を印加する電源配線512と、電源配線512と有機EL素子527との間に直列に接続されるp型の第1トランジスタ523及び第2トランジスタ521と、第1トランジスタ523のゲート端子とドレイン端子を接続または遮断するn型の第3トランジスタ524と、第1トランジスタ523のゲート端子と可変電位配線515との間に設けられたコンデンサ526と、第2トランジスタ521のゲート端子と信号線511との間に接続されそのゲート端子が選択線513に接続されるn型の第4トランジスタ522とを備えた構成である。

【0008】

以下、上記のように構成される画素501の表示動作について説明する。画素501の表示動作は、時間分割階調方式であり、ソースドライバ及びゲートドライバが実行する。

【0009】

第2トランジスタ521のゲート端子に与えられる電位は、時間分割階調表示データである。時間分割階調表示を行なうには、ゲートドライバにより選択線513がHIGH電位とされた期間に、ソースドライバにより第4トランジスタ522を通して第2トランジスタ521のゲート端子にON電位またはOFF電位が印加される。

【0010】

一方、第1トランジスタ523の出力電流を設定する動作においては、まず、可変電位配線515の電位を所定の電位Vpにし、制御線514をHIGH電位として第3トランジスタ524を導通状態とする。また、選択線513をHIGHレベルとしてソースドライバから第2トランジスタ521を一瞬導通状態とする電圧を印加し、直ぐに非導通状態となる電圧を印加する。このとき、第1トランジスタ523のゲート−ドレイン間は第3トランジスタ524を通して短絡されているので、第1トランジスタ523のゲート端子電位は低下しON電位となる。その後、第2トランジスタ521が上記のように非導通状態となると、第1トランジスタ523のドレイン端子電位が上昇する。その結果、第1トランジスタ523のゲート端子電位が上昇し、第1トランジスタ523が非導通状態に変化する。このときのソース−ゲート間電圧が、第1トランジスタ523の閾値電圧となる。

【0011】

その後、制御線514をLOW電位として第3トランジスタ524を非導通状態とし、コンデンサ526の電位を保持して、さらに、可変電位配線515の電位をVpよりVaだけ低い電位に変化させる。これにより、第1トランジスタ523のゲート端子−ソース端子間電圧Vgsは閾値電位Vth−Vaとなる。

【0012】

なお、第1トランジスタ523のソース−ドレイン間電圧Vdsとソース−ゲート間電圧Vgsとの間に、|Vds|≧|Vgs| の関係があるとき、つまり第1トランジスタ523が飽和領域で動作するとき、第1トランジスタ523の閾値ばらつきを補償して第1トランジスタ523を流れる電流値を設定することができる。そして、第2トランジスタ521が導通状態になると、第1トランジスタ523から第2トランジスタ521を通して有機EL素子527に、閾値電圧に依らない一定の駆動電流Idsを流すことが可能となる。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2006−30946号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

しかしながら、特許文献1に記載された従来の有機ELディスプレイ装置500は、駆動電流Idsを設定するために、基本的な表示動作に必要な信号線511及び選択線513の電位を変化させるドライバ回路に加え、可変電位配線515及び制御線514の電位を変化させるドライバ回路がそれぞれ必要であり、外部周辺回路の構成が複雑である。

【0015】

また、特許文献1に記載された画素501の画素回路では、n型及びp型チャネルのTFTを両方用いており、TFTとして安価で製造容易なアモルファスシリコンTFTに代表されるn型チャネルのTFTのみを用いて画素回路を製造することが困難である。

【0016】

上記課題に鑑み、本発明は、小規模な外部周辺回路により駆動可能な画素回路を有し、簡略化された製造工程による表示装置及びその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0017】

上記課題を解決するために、本発明の一態様に係る表示装置は、マトリクス状に配置された複数の発光画素を有する表示部を備える表示装置であって、電源電圧を前記複数の発光画素に供給するための電源線と、前記複数の発光画素を初期化する初期化電圧を前記複数の発光画素に供給するための初期化電源線と、制御線と、画素行ごとに配置され、映像信号に対応したデータ電圧を書き込む発光画素を選択するための複数の走査線と、画素列ごとに配置され、選択された発光画素に前記データ電圧を書き込むための複数のデータ線とを備え、前記複数の発光画素のそれぞれは、電流駆動型の発光素子と、前記発光素子に定電流を供給するための定電流駆動部と、前記定電流駆動部から前記発光素子へ供給される前記定電流の電流径路を導通及び遮断する定電流スイッチ部とを備え、前記定電流駆動部は、ソース電極及びドレイン電極の一方が前記電源線に接続され、前記電源線からの電流を駆動する電流駆動トランジスタと、前記電流駆動トランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第1コンデンサと、ゲート電極が前記制御線に接続され、前記第1コンデンサの一方の電極と前記電源線との導通及び非導通を切り換える第1スイッチトランジスタと、ゲート電極が前記制御線に接続され、前記第1コンデンサの他方の電極と前記初期化電源線との導通及び非導通を切り換える第2スイッチトランジスタとを備え、前記定電流スイッチ部は、ソース電極及びドレイン電極の一方が前記電流駆動トランジスタのソース電極及びドレイン電極の他方に接続され、ソース電極及びドレイン電極の他方が前記発光素子のアノード電極に接続され、前記電流駆動トランジスタにより駆動される電流を前記発光素子へ流すための前記電流径路を導通及び遮断する電流スイッチトランジスタと、前記電流スイッチトランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第2コンデンサと、ゲート電極が前記複数の走査線のうちの対応する走査線に接続され、前記電流スイッチトランジスタのゲート電極と前記データ線との導通及び非導通を切り換える選択トランジスタとを備えることを特徴とする。

【0018】

上記構成によれば、従来では、基本的な書き込み動作及び発光動作に必要な配線の電位を変化させるドライバ回路に加えて制御線及び可変電位配線を変化させるドライバ回路が必要であったのに対して、制御線の電位を変化させるドライバ回路のみが新たに必要となるだけであり、外部周辺回路の構成を簡略化できる。

【0019】

また、本発明の一態様に係る表示装置は、さらに、前記複数の走査線及び前記制御線に接続され、前記第1スイッチトランジスタ、前記第2スイッチトランジスタ及び前記選択トランジスタの導通及び非導通を制御する走査線制御回路と、前記複数のデータ線に接続され、前記走査線制御回路により前記選択トランジスタが導通状態となった場合、前記電流スイッチトランジスタの前記ゲート電極と前記ドレイン電極または前記ソース電極との間の電圧を決定する前記データ電圧を前記データ線に出力する信号線制御回路とを備えることが好ましい。

【0020】

上記構成によれば、定電流駆動部の第1コンデンサに初期化電圧を設定する場合、電流は電源線と初期化電源線との間を流れ、走査線制御回路及び信号線制御回路へ上記電流が流れ込むことが回避されるので制御回路での損失を低減することが可能となる。

【0021】

また、本発明の一態様に係る表示装置は、前記電流スイッチトランジスタが導通状態となる場合の前記データ電圧の絶対値は、前記電流スイッチトランジスタのドレイン−ソース間電圧の絶対値より大きく、前記電源電圧と前記初期化電圧との電位差の絶対値は、前記電流駆動トランジスタのドレイン−ソース間電圧の絶対値より小さいことが好ましい。

【0022】

これにより、電流駆動トランジスタは飽和領域で動作するので、電源電圧やソース電位の変動などがあっても安定して定電流を供給することができる。また、電流スイッチトランジスタは線形領域で動作するので、オン抵抗が小さく電圧降下が抑制されたスイッチング動作及び電流駆動となり、低消費電力化が実現される。

【0023】

また、本発明の一態様に係る表示装置は、単位表示画像を書き換える時間である1フレーム時間内に、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタの導通状態への切り換えにより前記電源電圧と前記初期化電圧との電位差が前記第1コンデンサに印加される回数は、前記1フレーム時間内に前記信号線制御回路が前記データ電圧を前記データ線に出力する回数よりも少なくてもよい。

【0024】

この構成によれば、電流源としての電流駆動トランジスタの条件設定に必要な時間が短縮されるため、結果的に発光期間を長く確保することが可能となる。よって、高精細な表示パネルを提供でき、また、有機EL素子に流れる電流のピーク値を低くすることができるので、高効率な輝度制御を実行することが可能となる。

【0025】

また、前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全て同一の導電型のチャネルを有する薄膜トランジスタであってもよい。

【0026】

また、前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全てn型のチャネルを有する薄膜トランジスタであることが好ましい。

【0027】

これにより、特に、n型トランジスタのみを用いて画素回路を構成している場合、アモルファスシリコンTFTの製造プロセスを用いて安価かつ簡易的に表示パネルを製造することが可能となる。

【0028】

また、前記電流駆動トランジスタは、飽和領域で動作し、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、線形領域で動作することが好ましい。

【0029】

これにより、電流駆動トランジスタは飽和領域で動作するので、電源電圧やソース電位の変動などがあっても安定して定電流を供給することができる。また、電流スイッチトランジスタ、選択トランジスタ、第1トランジスタ及び第2トランジスタは線形領域で動作するので、オン抵抗の小さいスイッチングとなり低消費電力化が実現される。

【0030】

また、前記発光素子は、有機EL素子であってもよい。

【0031】

また、前記発光素子は、無機EL素子であってもよい。

【0032】

また、本発明は、このような特徴的な手段を備える表示装置として実現することができるだけでなく、表示装置に含まれる特徴的な手段をステップとする表示装置の制御方法として実現することができる。

【発明の効果】

【0033】

本発明の表示装置及びその制御方法によれば、従来に比べドライバ回路が削減された小規模な外部周辺回路により駆動が可能となり、外部周辺回路を簡略化できる。

【図面の簡単な説明】

【0034】

【図1】本発明の実施の形態に係る表示装置の機能ブロック図である。

【図2】本発明の実施の形態に係る表示装置が有する表示部の回路構成図である。

【図3】本発明の実施の形態に係る表示装置が有する走査線制御回路の内部回路図である。

【図4】本発明の実施の形態に係る表示装置が有する信号線制御回路の内部回路図である。

【図5】本発明の実施の形態に係る表示装置の駆動タイミングチャートである。

【図6】本発明の実施の形態に係る表示装置の電流源設定動作を説明する状態遷移図である。

【図7】本発明の実施の形態に係る表示装置の書き込み動作を説明する状態遷移図である。

【図8】特許文献1に記載された従来の有機ELディスプレイ装置における表示部の回路構成図である。

【発明を実施するための形態】

【0035】

以下、本発明を実施するための形態について、図面を参照しながら説明する。

【0036】

<表示装置の構成>

図1は、本発明の実施の形態に係る表示装置の機能ブロック図である。同図に記載された表示装置1は、ディジタル階調制御方式で輝度を変動させるアクティブマトリクス型ディスプレイ装置であり、制御回路2と、走査線制御回路4と、信号線制御回路5と、表示部6とを備える。

【0037】

制御回路2は、入力された映像信号に応じて、表示部6の画素ごとに発光させるサブフレームを割り当て、走査線制御回路4及び信号線制御回路5に制御信号を出力する。

【0038】

走査線制御回路4は、表示部6に走査電圧を印加し、信号線制御回路5は表示部にデータ電圧を印加する。以下、上述した表示装置1の構成要素について詳細に説明する。

【0039】

図2は、本発明の実施の形態に係る表示装置が有する表示部の回路構成図である。表示部6は、ディスプレイの解像度(m×n)に応じた、マトリクス状に配置された複数の発光画素が配置された表示部であるが、図2には、表示部6の一部である、1つの発光画素が記載されている。図2に記載された表示部6の発光画素は、電流スイッチトランジスタ11と、スイッチトランジスタ23及び24と、コンデンサ12及び22と、選択トランジスタ13と、有機EL素子14と、電流駆動トランジスタ21と、画素列ごとに配置されたデータ線DTと、画素行ごとに配置された走査線SCNと、制御線BLKと、初期化電源線PIと、電源線PSとを備える。

【0040】

また、表示部6が有する複数の発光画素は、全て同じ回路構成となっている。

【0041】

表示部6が有する発光画素は、有機EL素子14に供給する発光電流である定電流を発生させる定電流駆動部と、当該定電流駆動部から有機EL素子14へ供給される上記定電流の電流径路を導通及び遮断する定電流スイッチ部とに大別される。

【0042】

定電流駆動部は、電流駆動トランジスタ21と、コンデンサ22と、スイッチトランジスタ23及び24とで構成される。定電流駆動部は、電流駆動トランジスタ21を飽和領域で動作させることにより、電流駆動トランジスタ21のソース−ドレイン間電圧Vdsが変動しても定電流を発生し、当該定電流を定電流スイッチ部へ安定供給する。

【0043】

定電流スイッチ部は、電流スイッチトランジスタ11と、コンデンサ12と、選択トランジスタ13とで構成される。データ線DTから供給される2値のデータ電圧(オン電圧及びオフ電圧)が電流スイッチトランジスタ11のゲート端子に印加されることより、電流スイッチトランジスタ11のソース−ドレイン間は、導通状態または非導通状態となる。これにより、定電流駆動部からの定電流を有機EL素子14へ流す、または、流さないという動作がサブフィールド単位で実行され、ディジタル階調制御がなされる。ここで、電流スイッチトランジスタ11のオンオフ制御におけるスイッチング損失を低減させるため、電流スイッチトランジスタ11は、低オン抵抗である線形領域で動作させることが望ましい。一方、薄膜トランジスタを線形領域で動作させた場合、ソース−ドレイン間電圧Vdsの変動により、薄膜トランジスタのドレイン−ソース電流Idsが変動しやすいという課題がある。上記課題を解消するため、上述した定電流駆動部によりVdsが変動してもIdsが変動しない定電流が供給される。

【0044】

つまり、飽和領域で動作する電流駆動トランジスタ21を有する定電流駆動部により、電源電圧やソース電位の変動などがあっても安定して定電流を供給することができ、線形領域で動作する電流スイッチトランジスタ11を有する定電流スイッチ部により、低損失なスイッチングによるディジタル階調表示が可能となる。

【0045】

以下、発光画素の各構成要素及びそれらの接続状態を説明する。

【0046】

電源線PSは、すべての画素行に配置され、電流駆動トランジスタ21のドレインに接続され、正の電源電圧VTFTを当該接続点に印加することにより、電源電圧を複数の発光画素に供給する。

【0047】

なお、本実施の形態では、全ての発光画素に対して、同じ電源電圧VTFTが同じタイミングで印加されるので、電源線PSは、全ての電源線が接続された共通線となっていてもよい。

【0048】

走査線SCNは、画素行ごとに配置され、映像信号に対応したデータ電圧を書き込む発光画素を選択する。

【0049】

制御線BLKは、すべての画素行に配置され、定電流駆動部を初期化するための機能を有する。

【0050】

初期化電源線PIは、すべての画素行に配置され、全ての発光画素を初期化する初期化電圧VREFを全ての発光画素に供給する機能を有する。具体的には、初期化電源線PIは、定電流駆動部を初期化する場合にコンデンサ22の他方の電極に初期化電圧VREFを供給する。なお、本実施の形態では、全ての発光画素に対して、同じ初期化電圧VREFが同じタイミングで印加されるので、各画素行に配置された初期化電源線PIは共通線となっている。よって、駆動回路などの外部周辺回路を簡略化できる。

【0051】

データ線DTは、画素列ごとに配置され、選択された発光画素にデータ電圧を書き込むための機能を有する。

【0052】

有機EL素子14は、電流駆動型の発光素子であり、アノード端子が電流スイッチトランジスタ11のソース端子及びコンデンサ12の一方の電極と接続され、カソード端子が基準端子(基準電圧VEL)に接続されている。

【0053】

電流駆動トランジスタ21は、ドレイン端子が電源線PSに接続され、ゲート端子がコンデンサ22の一方の電極と接続され、ソース端子がコンデンサ22の他方の電極と接続され、電源線PSからの電流を駆動する。電流駆動トランジスタ21は、ドレイン−ソース間電圧Vdsがゲート−ソース間電圧Vgsに比べて十分大きい領域である飽和領域にて動作させることにより、Vgsに応じて、電源電圧から一定の電流を供給する定電流駆動用の薄膜トランジスタである。なお、電流駆動トランジスタ21は、上述したように、Vdsの変動を受けない安定したIdsを有機EL素子14へ供給するが、映像信号に基づく表示階調の傾向により、フレーム単位で、後述する初期化電圧VREFを調整することによりVgsを変化させてIdsの大きさを調整することが可能となる。これにより、全ての階調を高精度に表示することが可能となる。

【0054】

コンデンサ22は、電流駆動トランジスタ21のゲート電極及びソース電極に接続され、電流駆動トランジスタ21のゲート−ソース間電圧を保持する第1コンデンサである。

【0055】

電流スイッチトランジスタ11は、ドレイン端子が電流駆動トランジスタ21のソース端子と接続され、ゲート端子がコンデンサ12の他方の端子と接続され、ソース端子がコンデンサ12の一方の端子及び有機EL素子14のアノード端子と接続され、ゲート−ソース間電圧Vgsがドレイン−ソース間電圧Vdsに比べて十分大きい領域である線形領域にて動作する、定電流スイッチング用の薄膜トランジスタである。電流スイッチトランジスタ11は、電流駆動トランジスタ21により駆動される定電流を有機EL素子14へ流すための電流径路を導通及び遮断する。

【0056】

コンデンサ12は、電流スイッチトランジスタ11のゲート電極とソース電極との間の電圧を保持する第2コンデンサである。

【0057】

選択トランジスタ13は、ドレイン端子が電流スイッチトランジスタ11のゲート端子と接続され、ゲート端子が走査線SCNと接続され、ソース端子がデータ線DTと接続され、有機EL素子14の発光を決定するデータ電圧を書き込むべき発光画素を選択する。つまり、選択トランジスタ13は、電流スイッチトランジスタ11のゲート電極とデータ線DTとの導通及び非導通を切り換える。

【0058】

スイッチトランジスタ23は、ドレイン端子が電源線PSと接続され、ゲート端子が制御線BLKと接続され、ソース端子が電流駆動トランジスタ21のゲート端子及びコンデンサ22の一方の電極と接続された第1スイッチトランジスタであり、スイッチトランジスタ24と同期制御されることにより、コンデンサ22の両端電圧である電流駆動トランジスタ21のVgsを確定させる。

【0059】

スイッチトランジスタ24は、ドレイン端子が電流駆動トランジスタ21のソース端子及びコンデンサ22の他方の電極と接続され、ゲート端子が制御線BLKと接続され、ソース端子が初期化電源線PIと接続された第2スイッチトランジスタであり、スイッチトランジスタ23と同期制御されることにより、コンデンサ22の両端電圧である電流駆動トランジスタ21のVgsを確定させる。

【0060】

電流スイッチトランジスタ11、スイッチトランジスタ23及び24、ならびに選択トランジスタ13は、入力された映像信号に基づいてゲート−ソース間に閾値電圧以上の電圧が印加されることにより、ドレイン−ソース間を導通状態とするスイッチ素子である。

【0061】

電流駆動トランジスタ21、電流スイッチトランジスタ11、スイッチトランジスタ23及び24、ならびに選択トランジスタ13は、同一の導電型のチャネルを有する薄膜トランジスタであることが好ましく、さらには、nチャネルのMOSFETで形成されていることが望ましい。上記トランジスタが、全て、nチャネルのMOSFETで形成されることにより、n型トランジスタのみを用いて画素回路を構成できるので、アモルファスシリコンTFTを用いて安価かつ簡易的に表示パネルを製造することが可能となる。

【0062】

上記回路構成において、データ線DTがHIGHレベル(Vdata)となり走査線SCNがHIGHレベル(VSCN)となることで、選択トランジスタ13のゲート−ソース間に、閾値電圧よりも十分大きい信号電圧が印加される。これにより、選択トランジスタ13は線形領域で動作しドレイン−ソース間はオン抵抗の低い導通状態となる。そして、選択トランジスタ13が導通状態になった後、データ線DTから選択トランジスタ13を経由してコンデンサ12が充電される。これにより、電流スイッチトランジスタ11のゲート−ソース間に、閾値電圧よりも十分大きい電圧が印加され、電流スイッチトランジスタ11は線形領域で動作しドレイン−ソース間はオン抵抗の低い導通状態となる。このとき、電源線PS→電流駆動トランジスタ21→電流スイッチトランジスタ11→有機EL素子14の経路で上述した電流駆動トランジスタ21による定電流が流れ有機EL素子14が発光する。

【0063】

また、本実施の形態では、発光素子として有機EL素子を用いているが、当該発光素子は電流駆動型の発光素子であればよく、例えば、無機EL素子であってもよい。

【0064】

<走査線制御回路>

次に、走査線制御回路4について説明する。走査線制御回路4は、制御回路2からの制御信号により、データ電圧書き込み期間において、発光画素行を選択するための走査信号を、走査線SCNを介して発光画素を有する表示部6に出力する。また、走査線制御回路4は、制御回路2からの制御信号により、初期化期間において、各発光画素の定電流値を定電流駆動部に設定するための初期化信号を、制御線BLKを介して発光画素を有する表示部6に出力する。

【0065】

図3は、本発明の実施の形態に係る表示装置が有する走査線制御回路の内部回路図である。走査線制御回路4は、走査信号の選択電圧であるVSCNまたは非選択電圧VLを選択し、画素行ごとに配置された走査線SCN1〜SCNmに印加する。

【0066】

画素行数がmである場合には、走査線制御回路4は、m本の走査線SCN1〜SCNmを介して表示部6に接続されている。走査線制御回路4は、任意の順序で1ライン毎に走査線SCN1〜SCNmに対して選択電圧VSCNまたは非選択電圧VLを供給することが可能である。もちろん、走査線SCN1、SCN2、・・・SCNmという様に、行順次に走査電圧を印加することも可能であり、あるいは、全ての走査線に対し同時にVSCNまたはVLを供給することも可能である。

【0067】

図3に記載された回路において、例えば、走査線SCN1に選択電圧VSCNを印加し、その他の走査線に非選択電圧VLを印加する場合には、走査線制御回路4は、スイッチSW41A及びスイッチSW42B、SW43B、・・・SW4mBをON状態とし、スイッチSW41B及びスイッチSW42A、SW43A、・・・SW4mAをOFF状態とする。

【0068】

さらに、図示しないが、走査線制御回路4は、初期化信号の選択電圧であるVBLKまたは非選択電圧を選択し、制御線BLKに印加する。制御線BLKに選択電圧VBLKまたは非選択電圧を印加する回路についても、選択電圧VSCNまたは非選択電圧VLを印加する回路と同様の構成である。

【0069】

つまり、走査線制御回路4は、複数の走査線SCN及び制御線BLKに接続され、スイッチトランジスタ23及び24ならびに選択トランジスタ13の導通及び非導通を制御する。

【0070】

なお、選択電圧VSCN及びVBLKを印加するタイミングについては、後述する。

【0071】

また、制御線BLKは、全ての発光画素に共通した制御線であってもよく、また、画素行ごとに配置された制御線BLK1〜BLKmであってもよい。

【0072】

<信号線制御回路>

次に、信号線制御回路5について説明する。信号線制御回路5は、データ電圧書き込み期間において、制御回路2からの制御信号により、走査線制御回路4から出力される走査信号に同期して、映像信号に対応したデータ電圧(オン電圧及びオフ電圧)を、データ線DTを介して電流スイッチトランジスタ11のゲート端子に出力する。

【0073】

図4は、本発明の実施の形態に係る表示装置が有する信号線制御回路の内部回路図である。信号線制御回路5は、スイッチSW51A〜SW5nA及びスイッチSW51B〜SW5nBによる切替えにより、オン電圧Vdataまたはオフ電圧を選択し、画素列ごとに配置されたデータ線DT1〜DTnに印加する。

【0074】

画素列数がnである場合には、信号線制御回路5は、n本のデータ線DT1〜DTnを介して表示部6に接続されている。各データ線には、信号線制御回路5の信号に応じて、1ライン毎にデータ線DT1〜DTnにオン電圧Vdataまたはオフ電圧を供給することが可能である。オン電圧Vdataまたはオフ電圧を印加するタイミングについては、後述する。

【0075】

以上のように、信号線制御回路5は、制御回路2からの制御信号により、データ電圧書き込み期間においてデータ電圧であるオン電圧またはオフ電圧を、データ線DTを介して表示部6に出力する。また、映像信号に応じた駆動信号により、表示部6の解像度に応じた画素列数n本のデータ線を同時に制御可能とするためのメモリ機能を有している。

【0076】

つまり、信号線制御回路5は、複数のデータ線DTに接続され、走査線制御回路4により選択トランジスタ13が導通状態となった場合、電流スイッチトランジスタ11のゲート−ソース間電圧を決定するデータ電圧をデータ線DTに出力する。

【0077】

なお、制御回路2は、発光画素の表示期間の長さを、電流スイッチトランジスタ11のオンオフ制御により変化させることで、有機EL素子14の発光輝度を制御する制御部として機能する。

【0078】

<表示装置の動作>

以下、図5〜7を用いて、表示装置1の動作について述べる。図5は、本発明の実施の形態に係る表示装置の駆動タイミングチャートである。図5の駆動タイミングチャートは、例として、走査線SCN1より行順次に走査した場合の表示装置の動作を表したものであり、上から順に、コンデンサ22の両端電圧V22、コンデンサ12の両端電圧V12、電流駆動トランジスタ21の状態TFT21、電流スイッチトランジスタ11の導通状態TFT11、選択トランジスタ13のゲート電圧V13、スイッチトランジスタ23のゲート電圧V23、スイッチトランジスタ24のゲート電圧V24、制御線BLKの電圧、データ線DTの電圧、走査線SCN1の電圧、・・・、走査線SCN1080の電圧を表している。なお、V22〜V24は、走査線SCN1に接続された画素行に属する発光画素についての動作を表している。また、上記電流駆動トランジスタ21の状態TFT21とは、スイッチトランジスタ23及び24が導通状態でありコンデンサ22が充電状態である場合をハイレベルとし、その他の場合をローレベルとして表している。また、上記電流スイッチトランジスタ11の導通状態TFT11とは、電流スイッチトランジスタ11のドレイン−ソース間が導通状態である場合をハイレベルとし、非導通状態である場合をローレベルとして表している。

【0079】

以下説明する表示装置1の動作は、初期化動作、書き込み動作及び発光動作という一連の単位を1サブフィールドとし、当該サブフィールドを繰り返し実行する。

【0080】

[初期化期間(電流源設定期間)]

定電流駆動部から供給される定電流を設定する初期化期間(電流源設定期間)における動作は、入力された映像信号に基づき、各画素の電流源となる電流駆動トランジスタ21のゲート−ソース間電圧Vgsを設定するステップである。

【0081】

まず、時刻t01〜時刻t02において、電流駆動トランジスタ21のVgsを設定するために、書き込み対象の電流駆動トランジスタ21に直列に接続されている電流スイッチトランジスタ11をオフさせる。オフさせる方法としては、図5のように、行順次に走査線SCNに走査電圧パルスを印加し、データ線DTにオフ電圧を印加して行毎にオフさせてもよいし、全ライン一斉に走査電圧パルスを印加してもよい。また、上記走査電圧パルスの長さは、初期化期間より前の発光期間の長さに応じて変化させてもよい。

【0082】

初期化期間の準備段階として上記動作を行うことにより、電流駆動トランジスタ21のソース電位が電流スイッチトランジスタ11及び有機EL素子14から切り離されてフローティング状態となるため、時刻t02以降での電流駆動トランジスタ21のソース電位を初期化電源線PIから任意に設定でき、これによりVgsを任意に調整することが可能となる。

【0083】

次に、時刻t02において、制御線BLKに正の電圧VBLKを印加し、スイッチトランジスタ23及び24のゲート電圧を閾値電圧以上としドレイン−ソース間の抵抗を下げオンさせる。この動作により、電流駆動トランジスタ21のVgsは、電源線PSと初期化電源線PIとの電位差により設定される。

【0084】

図6は、本発明の実施の形態に係る表示装置の電流源設定動作を説明する状態遷移図である。同図は、行列間で隣接する4つの発光画素6A〜6Dの時刻t02における電気的状態を表している。なお、本実施の形態では、電源線PS、制御線BLK及び初期化電源線PIが全ての発光画素で共通化されているものとしている。これにより、駆動回路などの外部周辺回路を簡略化できる。

【0085】

時刻t02において、走査線制御回路4は、制御線BLKに対してHIGHレベルの選択電圧VBLKを出力する。これにより、スイッチトランジスタ23及び24が導通状態となり、電流駆動トランジスタ21のVgsは、(VTFT−VREF)となる。図6において、矢印(破線)は電圧印加経路を示したものである。

【0086】

ここで、有機EL表示パネルの場合を想定して具体例にて説明する。例えば、電源線PSの電源電圧VTFTは10V、基準電圧VELは−2Vに設定される。また、電流駆動トランジスタ21のドレイン−ソース間電圧Vdsは5V程度、電流スイッチトランジスタ11のVdsは1V程度となる。かかる場合において、前述したように、電流駆動トランジスタ21を、安定した定電流源として動作させるためには、Vds>>VgsとなるようVgsを設定して飽和領域にて動作させる必要がある。つまり、VTFTとVREFとの電位差の絶対値は、電流駆動トランジスタ21のドレイン−ソース間電圧Vdsの絶対値より小さい。本具体例において、電流駆動トランジスタ21のVdsが5V程度であることから、電流駆動トランジスタ21のVgsを1V程度に設定することが望ましい。これより、初期化電圧VREFを9Vと設定すればよい。

【0087】

上述した時刻t02における走査線制御回路4の動作により、定電流駆動部の設定が完了する。

【0088】

その後、時刻t02〜時刻t03の期間において、走査線制御回路4は、制御線BLKをLOWレベルとして、スイッチトランジスタ23及び24のゲート電圧を閾値電圧以下とすることにより、電流駆動トランジスタ21のVgsを保持するコンデンサ22の両電極は、電源線PS及び初期化電源線PIから電気的に切り離される。

【0089】

[書き込み期間(ON/OFF設定期間)]

データ電圧を、選択された発光画素へ書き込む書き込み期間(ON/OFF設定期間)における動作は、各発光画素が有する電流スイッチトランジスタ11の導通状態及び非導通状態を切り換えるステップである。このため、走査線制御回路4は、走査線SCNごとに、選択電圧VSCNまたは非選択電圧VLを印加する。これにより、選択された走査線SCNが接続された画素行に属する発光画素に対して、対応するデータ線DTからのデータ電圧が印加され、電流スイッチトランジスタ11のゲート電圧が制御される。

【0090】

なお、図5では、制御回路2による処理により、サブフィールド期間t03〜t04及び期間t05〜t06では、1行目の発光画素が発光状態であり、サブフィールド期間t04〜t05では、1行目の発光画素が非発光状態であるものと仮定している。

【0091】

まず、時刻t03〜時刻t04のサブフィールド期間において、走査線制御回路4は、走査線SCN1〜SCNmに対して、走査信号パルスを印加する。ここで、走査線SCN1に接続された1行目の発光画素について、より具体的に説明する。

【0092】

図7は、本発明の実施の形態に係る表示装置が有する画素への書き込み動作を説明する状態遷移図である。同図は、行列間で隣接する4つの発光画素6A〜6Dの時刻t03における電気的状態を表している。

【0093】

時刻t03において、走査線制御回路4は、走査線SCN1に対して、選択トランジスタ13の閾値電圧以上となる選択電圧VSCNを出力する。これにより、選択トランジスタ13のドレイン−ソース間の抵抗が下がり、選択トランジスタ13が導通状態となる。また、信号線制御回路5は、データ線DTに対し、オン電圧Vdataを出力する。これにより、電流スイッチトランジスタ11のゲート電圧が閾値電圧以上となり電流スイッチトランジスタ11が導通状態となる。図7において、矢印(破線)は電圧印加経路を示したものであり、矢印(実線)は電流の流れを示したものである。

【0094】

なお、本実施の形態において、例えば、走査線SCN及び制御線BLKのHIGHレベルの電圧VSCN及びVBLKは+20Vであり、LOWレベルの電圧VLは−10Vに設定されている。また、前述したように、電流スイッチトランジスタ11を、スイッチング損失の小さいスイッチ素子として動作させるためには、Vgs>>VdsとなるようVgsを設定して線形領域にて動作させる必要がある。つまり、電流スイッチトランジスタ11が導通状態となる場合のデータ電圧の絶対値は、電流スイッチトランジスタ11のドレイン−ソース間電圧Vdsの絶対値より大きい。本具体例において、電流スイッチトランジスタ11のVdsが1V程度であることから、電流スイッチトランジスタ11のVgsを8V程度に設定することが望ましい。また、有機EL素子14に印加される電圧は、6V程度であることから、有機EL素子14のアノード電位、つまり電流スイッチトランジスタ11のソース電位は4V程度となる。上記電流スイッチトランジスタ11のVgs及びソース電位より、電流スイッチトランジスタ11に印加されるデータ電圧は、オン電圧として12V、オフ電圧として2V程度に設定すればよい。

【0095】

次に、時刻t03〜時刻t04において、走査線SCN1の走査電圧をVSCNからVLに変化させて選択トランジスタ13を非導通状態とし、電流スイッチトランジスタ11のゲート端子とデータ線DTとを電気的に切り離しても、電流スイッチトランジスタ11のゲート−ソース間に接続されたコンデンサ12により、電流スイッチトランジスタ11のVgs電位は保持される。このときのコンデンサ12の容量は、電流スイッチトランジスタ11をオンさせている最大時間幅が経過しても、電流スイッチトランジスタ11の閾値電圧以上の電位を保持できる容量以上とすることが望ましい。

【0096】

上記動作により電流スイッチトランジスタ11が導通状態となると、電源線PS→電流駆動トランジスタ21→電流スイッチトランジスタ11→有機EL素子14→基準端子の経路で電流が流れ、発光画素6A及び6Bの発光期間が開始する。発光期間は電流スイッチトランジスタ11が非導通状態になるまで継続する。

【0097】

その後、走査線SCN2、走査線SCN3、・・・、と順次走査することで、すべての発光画素に対して、所望のタイミングで電流スイッチトランジスタ11をオンさせることが可能となる。

【0098】

以上のように、時刻t03以降において、所望の発光画素に対し走査線ごとに書き込み動作を行うことで、サブフィールドごとに全ての発光画素に対して書き込み及び発光制御を行うことが可能となる。

【0099】

なお、図5に記載された一連の表示動作では、初期化動作を一度しか行っていないが、サブフィールドごとに行ってもよい。ただし、サブフィールド間で、定電流駆動部の電流設定値を変化させる必要が無い場合は初期化動作を行う必要が無く、サブフィールド間での初期化動作を省略することにより駆動時間を大幅に短縮することが可能となる。つまり、単位表示画像を書き換える時間である1フレーム時間内に制御線BLKにVBLKを印加しコンデンサ22に(VTFT−VREF)を設定する回数は、1フレーム時間内に信号線制御回路5がデータ電圧(オン電圧及びオフ電圧)をデータ線DTに出力する回数よりも少ないことが好ましい。これにより、電流源としての電流駆動トランジスタの条件設定に必要な時間が短縮されるため、結果的に発光期間を長く確保することが可能となる。よって、高精細な表示パネルを提供でき、また、有機EL素子に流れる電流のピーク値を低くすることができるので、高効率な輝度制御を実行することが可能となる。

【0100】

また、サブフィールド時分割式で輝度を変調する場合、電流スイッチトランジスタ11のオン/オフ時間比率の最大値または最小値によって最大輝度と最小輝度の制約が生ずるが、電流駆動部における電流設定値を変化させることで、輝度調節範囲を広げることが可能である。具体的には、例えば、電流駆動トランジスタ21のVgsの設定値を調整することにより、輝度調節範囲を広げることが可能である。

【0101】

また、初期化動作に必要な最大時間間隔に応じて、電流駆動トランジスタ21のVgsを保持するコンデンサ22の容量を設定することにより、電流駆動トランジスタ21のVgsを所望の値に保持することが可能となる。

【0102】

以上、本実施の形態によれば、画素回路に定電流源として機能する定電流駆動部が配置されたことにより、定電流スイッチ部を構成する電流スイッチトランジスタ11は、定電流源である必要はなく、画素回路のオンオフ状態を切り換えるスイッチ機能を有していればよい。よって、例えば、電流スイッチトランジスタ11に印加するデータ電圧、つまり、ゲート−ソース間電圧Vgsを、ドレイン−ソース間電圧Vdsに対して十分大きく設定しておくことにより、薄膜トランジスタの線形領域を利用することができるので、ドレイン−ソース電流Idsのオン抵抗を小さくすることが可能となる。よって、電流スイッチトランジスタ11のドレイン−ソース間に発光電流が流れるときの電圧降下を低減でき、表示パネルの電力損失を大幅に低減することができる。

【0103】

また、本実施の形態によれば、基本的な書き込み動作及び発光動作に必要な配線の電位を変化させるドライバ回路に対し、制御線BLKの電位を変化させるドライバ動作のみが新たに必要となるだけであり、外部周辺回路の構成を簡略化できる。

【0104】

さらに、本実施の形態によれば、電流駆動トランジスタ21のVgsを設定するための初期化期間において、電流は電源線PSから初期化電源線PIへと流れる。初期化電源線PIの出力電圧VREFは駆動信号に応じて電圧を変化させる必要は無く一定電圧とできるため、上記電源線PSから電流が流れ込むことによる損失を低減することが可能となる。

【0105】

以上、本発明に係る表示装置及びその制御方法について実施の形態に基づき説明したが、本発明に係る表示装置及びその制御方法は、上述した実施の形態に限定されるものではない。上記実施の形態に対して、本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本発明に係る表示装置を内蔵した各種機器も本発明に含まれる。

【0106】

なお、飽和領域を利用した定電流源である電流駆動トランジスタ21のチャネル幅を、電流スイッチトランジスタ11よりも広くすることが好ましい。これにより、電流駆動トランジスタ21のドレイン−ソース間に発光電流が流れるときの電圧降下を低減でき、表示パネルの電力損失を低減することが可能である。

【0107】

また、上記実施の形態では、各トランジスタのゲート電圧がHIGHレベルの場合にオン状態になるn型トランジスタとして記述しているが、これらをすべてp型トランジスタで形成し、走査線の極性を反転させた表示装置でも、上述した各実施の形態と同様の効果を奏する。あるいは、n型トランジスタ及びp型トランジスタが混在した構成の表示装置であってもよい。

【0108】

また、本発明に係る実施の形態では、各トランジスタは、ゲート、ソース及びドレインを有するFETであることを前提として説明してきたが、これらのトランジスタには、ベース、コレクタ及びエミッタを有するバイポーラトランジスタが適用されてもよい。この場合にも、本発明の目的が達成され同様の効果を奏する。

【産業上の利用可能性】

【0109】

本発明の表示装置及びその制御方法は、特に、ディジタル階調制御方式で輝度を変動させるアクティブ型ディスプレイに有用である。

【符号の説明】

【0110】

1 表示装置

2 制御回路

4 走査線制御回路

5 信号線制御回路

6 表示部

6A、6B、6C、6D 発光画素

11 電流スイッチトランジスタ

12、22 コンデンサ

13 選択トランジスタ

14、527 有機EL素子

21 電流駆動トランジスタ

23、24 スイッチトランジスタ

500 有機ELディスプレイ装置

501 画素

511 信号線

512 電源配線

513 選択線

514 制御線

515 可変電位配線

521 第2トランジスタ

522 第4トランジスタ

523 第1トランジスタ

524 第3トランジスタ

525、526 コンデンサ

【特許請求の範囲】

【請求項1】

マトリクス状に配置された複数の発光画素を有する表示部を備える表示装置であって、

電源電圧を前記複数の発光画素に供給するための電源線と、

前記複数の発光画素を初期化する初期化電圧を前記複数の発光画素に供給するための初期化電源線と、

制御線と、

画素行ごとに配置され、映像信号に対応したデータ電圧を書き込む発光画素を選択するための複数の走査線と、

画素列ごとに配置され、選択された発光画素に前記データ電圧を書き込むための複数のデータ線とを備え、

前記複数の発光画素のそれぞれは、

電流駆動型の発光素子と、

前記発光素子に定電流を供給するための定電流駆動部と、

前記定電流駆動部から前記発光素子へ供給される前記定電流の電流径路を導通及び遮断する定電流スイッチ部とを備え、

前記定電流駆動部は、

ソース電極及びドレイン電極の一方が前記電源線に接続され、前記電源線からの電流を駆動する電流駆動トランジスタと、

前記電流駆動トランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第1コンデンサと、

ゲート電極が前記制御線に接続され、前記第1コンデンサの一方の電極と前記電源線との導通及び非導通を切り換える第1スイッチトランジスタと、

ゲート電極が前記制御線に接続され、前記第1コンデンサの他方の電極と前記初期化電源線との導通及び非導通を切り換える第2スイッチトランジスタとを備え、

前記定電流スイッチ部は、

ソース電極及びドレイン電極の一方が前記電流駆動トランジスタのソース電極及びドレイン電極の他方に接続され、ソース電極及びドレイン電極の他方が前記発光素子のアノード電極に接続され、前記電流駆動トランジスタにより駆動される電流を前記発光素子へ流すための前記電流径路を導通及び遮断する電流スイッチトランジスタと、

前記電流スイッチトランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第2コンデンサと、

ゲート電極が前記複数の走査線のうちの対応する走査線に接続され、前記電流スイッチトランジスタのゲート電極と前記データ線との導通及び非導通を切り換える選択トランジスタとを備える

表示装置。

【請求項2】

さらに、

前記複数の走査線及び前記制御線に接続され、前記第1スイッチトランジスタ、前記第2スイッチトランジスタ及び前記選択トランジスタの導通及び非導通を制御する走査線制御回路と、

前記複数のデータ線に接続され、前記走査線制御回路により前記選択トランジスタが導通状態となった場合、前記電流スイッチトランジスタの前記ゲート電極と前記ドレイン電極または前記ソース電極との間の電圧を決定する前記データ電圧を前記データ線に出力する信号線制御回路とを備える

請求項1に記載の表示装置。

【請求項3】

前記電流スイッチトランジスタが導通状態となる場合の前記データ電圧の絶対値は、前記電流スイッチトランジスタのドレイン−ソース間電圧の絶対値より大きく、

前記電源電圧と前記初期化電圧との電位差の絶対値は、前記電流駆動トランジスタのドレイン−ソース間電圧の絶対値より小さい

請求項2に記載の表示装置。

【請求項4】

単位表示画像を書き換える時間である1フレーム時間内に、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタの導通状態への切り換えにより前記電源電圧と前記初期化電圧との電位差が前記第1コンデンサに印加される回数は、前記1フレーム時間内に前記信号線制御回路が前記データ電圧を前記データ線に出力する回数よりも少ない

請求項2または3に記載の表示装置。

【請求項5】

前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全て同一の導電型のチャネルを有する薄膜トランジスタである

請求項1〜4のうちいずれか1項に記載の表示装置。

【請求項6】

前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全てn型のチャネルを有する薄膜トランジスタである

請求項5に記載の表示装置。

【請求項7】

前記電流駆動トランジスタは、飽和領域で動作し、

前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、線形領域で動作する

請求項1〜6のうちいずれか1項に記載の表示装置。

【請求項8】

前記発光素子は、有機EL素子である

請求項1〜7のうちいずれか1項に記載の表示装置。

【請求項9】

前記発光素子は、無機EL素子である

請求項1〜7のうちいずれか1項に記載の表示装置。

【請求項10】

マトリクス状に配置された複数の発光画素に電源電圧を供給するための電源線と、

前記複数の発光画素を初期化する初期化電圧を前記複数の発光画素に供給するための初期化電源線と、

画素列ごとに配置され、選択された発光画素にデータ電圧を書き込むための複数のデータ線とを備え、

前記複数の発光画素のそれぞれは、

電流駆動型の発光素子と、

ソース電極及びドレイン電極の一方が前記電源線に接続され、前記電源線からの電流を駆動する電流駆動トランジスタと、

前記電流駆動トランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第1コンデンサと、

前記第1コンデンサの一方の電極と前記電源線との導通及び非導通を切り換える第1スイッチトランジスタと、

前記第1コンデンサの他方の電極と前記初期化電源線との導通及び非導通を切り換える第2スイッチトランジスタと、

前記電流駆動トランジスタにより駆動される電流を前記発光素子へ流すための電流径路を導通及び遮断する電流スイッチトランジスタと、

前記電流スイッチトランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第2コンデンサと、

前記電流スイッチトランジスタのゲート電極と前記データ線との導通及び非導通を切り換える選択トランジスタとを備えた、

表示装置の制御方法であって、

前記第1スイッチトランジスタ及び前記第2スイッチトランジスタを導通状態とし、かつ、前記選択トランジスタを非導通状態とし、前記初期化電圧と前記電源電圧との電位差を前記第1コンデンサに充電する初期化ステップと、

前記初期化ステップの後、前記選択トランジスタを導通状態とし、前記データ電圧を前記データ線に出力し、前記データ電圧と前記電流スイッチトランジスタのドレイン電圧またはソース電圧との電位差を前記第2コンデンサに充電するデータ電圧書き込みステップとを含む

表示装置の制御方法。

【請求項1】

マトリクス状に配置された複数の発光画素を有する表示部を備える表示装置であって、

電源電圧を前記複数の発光画素に供給するための電源線と、

前記複数の発光画素を初期化する初期化電圧を前記複数の発光画素に供給するための初期化電源線と、

制御線と、

画素行ごとに配置され、映像信号に対応したデータ電圧を書き込む発光画素を選択するための複数の走査線と、

画素列ごとに配置され、選択された発光画素に前記データ電圧を書き込むための複数のデータ線とを備え、

前記複数の発光画素のそれぞれは、

電流駆動型の発光素子と、

前記発光素子に定電流を供給するための定電流駆動部と、

前記定電流駆動部から前記発光素子へ供給される前記定電流の電流径路を導通及び遮断する定電流スイッチ部とを備え、

前記定電流駆動部は、

ソース電極及びドレイン電極の一方が前記電源線に接続され、前記電源線からの電流を駆動する電流駆動トランジスタと、

前記電流駆動トランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第1コンデンサと、

ゲート電極が前記制御線に接続され、前記第1コンデンサの一方の電極と前記電源線との導通及び非導通を切り換える第1スイッチトランジスタと、

ゲート電極が前記制御線に接続され、前記第1コンデンサの他方の電極と前記初期化電源線との導通及び非導通を切り換える第2スイッチトランジスタとを備え、

前記定電流スイッチ部は、

ソース電極及びドレイン電極の一方が前記電流駆動トランジスタのソース電極及びドレイン電極の他方に接続され、ソース電極及びドレイン電極の他方が前記発光素子のアノード電極に接続され、前記電流駆動トランジスタにより駆動される電流を前記発光素子へ流すための前記電流径路を導通及び遮断する電流スイッチトランジスタと、

前記電流スイッチトランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第2コンデンサと、

ゲート電極が前記複数の走査線のうちの対応する走査線に接続され、前記電流スイッチトランジスタのゲート電極と前記データ線との導通及び非導通を切り換える選択トランジスタとを備える

表示装置。

【請求項2】

さらに、

前記複数の走査線及び前記制御線に接続され、前記第1スイッチトランジスタ、前記第2スイッチトランジスタ及び前記選択トランジスタの導通及び非導通を制御する走査線制御回路と、

前記複数のデータ線に接続され、前記走査線制御回路により前記選択トランジスタが導通状態となった場合、前記電流スイッチトランジスタの前記ゲート電極と前記ドレイン電極または前記ソース電極との間の電圧を決定する前記データ電圧を前記データ線に出力する信号線制御回路とを備える

請求項1に記載の表示装置。

【請求項3】

前記電流スイッチトランジスタが導通状態となる場合の前記データ電圧の絶対値は、前記電流スイッチトランジスタのドレイン−ソース間電圧の絶対値より大きく、

前記電源電圧と前記初期化電圧との電位差の絶対値は、前記電流駆動トランジスタのドレイン−ソース間電圧の絶対値より小さい

請求項2に記載の表示装置。

【請求項4】

単位表示画像を書き換える時間である1フレーム時間内に、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタの導通状態への切り換えにより前記電源電圧と前記初期化電圧との電位差が前記第1コンデンサに印加される回数は、前記1フレーム時間内に前記信号線制御回路が前記データ電圧を前記データ線に出力する回数よりも少ない

請求項2または3に記載の表示装置。

【請求項5】

前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全て同一の導電型のチャネルを有する薄膜トランジスタである

請求項1〜4のうちいずれか1項に記載の表示装置。

【請求項6】

前記電流駆動トランジスタ、前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、全てn型のチャネルを有する薄膜トランジスタである

請求項5に記載の表示装置。

【請求項7】

前記電流駆動トランジスタは、飽和領域で動作し、

前記電流スイッチトランジスタ、前記選択トランジスタ、前記第1スイッチトランジスタ及び前記第2スイッチトランジスタは、線形領域で動作する

請求項1〜6のうちいずれか1項に記載の表示装置。

【請求項8】

前記発光素子は、有機EL素子である

請求項1〜7のうちいずれか1項に記載の表示装置。

【請求項9】

前記発光素子は、無機EL素子である

請求項1〜7のうちいずれか1項に記載の表示装置。

【請求項10】

マトリクス状に配置された複数の発光画素に電源電圧を供給するための電源線と、

前記複数の発光画素を初期化する初期化電圧を前記複数の発光画素に供給するための初期化電源線と、

画素列ごとに配置され、選択された発光画素にデータ電圧を書き込むための複数のデータ線とを備え、

前記複数の発光画素のそれぞれは、

電流駆動型の発光素子と、

ソース電極及びドレイン電極の一方が前記電源線に接続され、前記電源線からの電流を駆動する電流駆動トランジスタと、

前記電流駆動トランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第1コンデンサと、

前記第1コンデンサの一方の電極と前記電源線との導通及び非導通を切り換える第1スイッチトランジスタと、

前記第1コンデンサの他方の電極と前記初期化電源線との導通及び非導通を切り換える第2スイッチトランジスタと、

前記電流駆動トランジスタにより駆動される電流を前記発光素子へ流すための電流径路を導通及び遮断する電流スイッチトランジスタと、

前記電流スイッチトランジスタのゲート電極とドレイン電極またはソース電極との間の電圧を保持する第2コンデンサと、

前記電流スイッチトランジスタのゲート電極と前記データ線との導通及び非導通を切り換える選択トランジスタとを備えた、

表示装置の制御方法であって、

前記第1スイッチトランジスタ及び前記第2スイッチトランジスタを導通状態とし、かつ、前記選択トランジスタを非導通状態とし、前記初期化電圧と前記電源電圧との電位差を前記第1コンデンサに充電する初期化ステップと、

前記初期化ステップの後、前記選択トランジスタを導通状態とし、前記データ電圧を前記データ線に出力し、前記データ電圧と前記電流スイッチトランジスタのドレイン電圧またはソース電圧との電位差を前記第2コンデンサに充電するデータ電圧書き込みステップとを含む

表示装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−104908(P2013−104908A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−246725(P2011−246725)

【出願日】平成23年11月10日(2011.11.10)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月10日(2011.11.10)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]