表示装置及びその製造方法

【課題】隣接する表示画素間で混色を生じることなく、各表示画素の形成領域の略全域に均一な膜厚を有する担体輸送層が形成された表示パネルを備えた表示装置、及び、当該表示装置の製造方法を提供する。

【解決手段】一面側に突出して配設されたバンク18により、各表示画素PIX(有機EL素子OEL)の形成領域Rpxが画定された絶縁性基板11において、UVオゾン処理等により親液化処理した後、酸系の水溶液に浸漬してソフトエッチングを施してバンク18表面に形成された酸化膜を除去し、その後、トリアジンチオール化合物等の撥液処理溶液に浸漬してバンク18表面にトリアジンチオール化合物の被膜を形成して撥液化することにより、絶縁性基板11上に親液性を示す領域(画素電極15表面)と、撥液性を示す領域(バンク18表面)とを共存させた親疎水パターンを形成する。

【解決手段】一面側に突出して配設されたバンク18により、各表示画素PIX(有機EL素子OEL)の形成領域Rpxが画定された絶縁性基板11において、UVオゾン処理等により親液化処理した後、酸系の水溶液に浸漬してソフトエッチングを施してバンク18表面に形成された酸化膜を除去し、その後、トリアジンチオール化合物等の撥液処理溶液に浸漬してバンク18表面にトリアジンチオール化合物の被膜を形成して撥液化することにより、絶縁性基板11上に親液性を示す領域(画素電極15表面)と、撥液性を示す領域(バンク18表面)とを共存させた親疎水パターンを形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及びその製造方法に関し、特に、担体輸送材料からなる液状材料を塗布することにより担体輸送層が形成される発光素子を有する複数の表示画素を、二次元配列した表示パネルを備えた表示装置及びその製造方法に関する。

【背景技術】

【0002】

近年、携帯電話や携帯音楽プレーヤ等の電子機器の表示デバイスとして、有機エレクトロルミネッセンス素子(以下、「有機EL素子」と略記する)を2次元配列した表示パネル(有機EL表示パネル)を適用したものが知られている。特に、アクティブマトリックス駆動方式を適用した有機EL表示パネルにおいては、広く普及している液晶表示装置に比較して、表示応答速度が速く、視野角依存性もなく、また、高輝度・高コントラスト化、表示画質の高精細化等が可能であるとともに、液晶表示装置のようにバックライト導光板などを必要としないので、一層の薄型軽量化が可能であるという極めて優位な特徴を有している。

【0003】

ここで、有機EL素子は、周知のように、例えば概略、ガラス基板等の一面側に、アノード(陽極)電極と、有機EL層(発光機能層)と、カソード(陰極)電極と、を順次積層した素子構造を有し、有機EL層に発光しきい値を越えるようにアノード電極に正電圧、カソード電極に負電圧を印加することにより、有機EL層内で注入されたホールと電子が再結合する際に生じるエネルギーに基づいて光(励起光)が放射されるものであるが、有機EL層となる正孔輸送層(正孔注入層)や電子輸送性発光層(発光層)を形成する有機材料(正孔輸送材料や電子輸送性発光材料)に応じて、低分子系と高分子系の有機EL素子に大別することができる。

【0004】

低分子系の有機材料を適用した有機EL素子の場合、一般に、製造プロセスにおいて蒸着法を適用する必要があるため、画素形成領域のアノード電極上にのみ当該低分子系の有機膜を選択的に薄膜形成する際に、上記アノード電極以外の領域への低分子材料の蒸着を防止するためのマスクを用いる場合があり、当該マスクの表面にも低分子材料が付着することになるため、製造時の材料ロスが大きいうえ、製造プロセスが非効率的であるという問題を有している。

【0005】

一方、高分子系の有機材料を適用した有機EL素子の場合には、湿式成膜法としてインクジェット法(液滴吐出法)やノズルプリント法(液流吐出法)等を適用することができるので、アノード電極上、又は、アノード電極を含む特定の領域にのみ選択的に上記有機材料の溶液を塗布することができ、材料ロスが少なく効率的な製造プロセスで良好に有機EL層(正孔輸送層や電子輸送性発光層)の薄膜を形成することができるという利点を有している。

【0006】

そして、このような高分子系の有機EL表示パネルにおいては、ガラス基板等の絶縁性基板上に配列される各表示画素の形成領域(画素形成領域)を画定するとともに、高分子系有機材料からなる液状材料(溶液)を塗布する際に、隣接する画素形成領域に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)等が生じる現象を防止するために、各画素形成領域間に絶縁性基板上に連続的に突出して形成された隔壁を設けたパネル構造を有するものが知られている。このような隔壁を備えた有機EL表示パネルについては、例えば、特許文献1等に詳しく説明されている。

【0007】

【特許文献1】特開2001−76881号公報 (第4頁〜第7頁、図1〜図6)

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上述したような高分子系の有機EL素子EL表示パネルにおいては、インクジェット法やノズルプリント法等の湿式成膜法を適用して有機EL層(正孔輸送層及び電子輸送性発光層)を製造する際に、上記有機材料からなる液状材料が塗布される各画素形成領域(アノード電極)や各表示画素(画素形成領域)間に設けられた隔壁の表面の特性(親液性や撥液性)、上記液状材料の溶媒成分に起因する表面張力や凝集力等の様々な要因により、隣接する画素形成領域に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)が生じたり、画素形成領域内(特にアノード電極上)に形成される有機EL層の膜厚が不均一になったりするという問題を有していた。

【0009】

そのため、有機EL素子の発光動作時における発光開始電圧や有機EL層から放射される光の波長(すなわち、画像表示時の色度)が設計値からずれて、所望の表示画質が得られなくなってしまったり、特に有機EL層の膜厚に薄い領域ができると、そこに発光駆動電流が集中して流れることにより、有機EL層(有機EL素子)の劣化が著しくなり、表示パネルの信頼性や寿命が低下するという問題を有していた。

【0010】

そこで、本発明は、上述した問題点に鑑み、隣接する表示画素間で混色を生じることなく、各表示画素の形成領域の略全域に均一な膜厚を有する担体輸送層が形成された表示パネルを備えた表示装置、及び、当該表示装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

請求項1記載の発明は、

担体輸送層を有する発光素子を含む複数の表示画素を備えた表示装置の製造方法において、

基板上にそれぞれ画素電極が設けられた前記複数の表示画素の形成領域間に隔壁を形成する工程と、

前記画素電極表面を親液化する工程と、

前記隔壁の表面をエッチングする工程と、

前記隔壁の表面を撥液化する工程と、

を含むことを特徴とする。

【0012】

請求項2記載の発明は、請求項1記載の表示装置の製造方法において、前記画素電極表面を親液化する工程は、UVオゾン処理又は酸素プラズマ処理により、少なくとも前記画素電極表面を、前記担体輸送層を形成する担体輸送性材料を含む溶液に対して親液化することを特徴とする。

【0013】

請求項3記載の発明は、請求項1記載の表示装置の製造方法において、前記隔壁の表面をエッチングする工程は、前記画素電極表面を親液化する処理の際に少なくとも前記隔壁の表面に形成された酸化膜を除去することを特徴とする。

請求項4記載の発明は、請求項1記載の表示装置の製造方法において、前記隔壁の表面を撥液化する工程は、トリアジンチオール化合物の溶液に前記基板を浸漬し、少なくとも前記隔壁の表面に前記トリアジンチオール化合物を結合させて、前記担体輸送性材料を含む溶液に対して撥液性を有する被膜を形成することを特徴とする。

【0014】

請求項5記載の発明は、請求項1乃至4のいずれかに記載の表示装置の製造方法において、前記画素電極は、表面が導電性の酸化金属層により形成されていることを特徴とする。

請求項6記載の発明は、請求項1乃至5のいずれかに記載の表示装置の製造方法において、前記隔壁は、少なくとも表面が低抵抗の金属材料により形成されていることを特徴とする。

【0015】

請求項7記載の発明は、請求項1乃至6のいずれかに記載の表示装置の製造方法において、前記表示画素の形成領域は、前記隔壁により画定されることを特徴とする。

請求項8記載の発明は、請求項7記載の表示装置の製造方法において、前記担体輸送層は、前記画素形成領域に露出する前記画素電極上に形成されることを特徴とする。

【0016】

請求項9記載の発明は、請求項1乃至8のいずれかに記載の表示装置の製造方法において、前記親液化された前記画素電極上に、前記担体輸送性材料を含む溶液を塗布、乾燥して、前記担体輸送層を形成する工程と、前記担体輸送層を介して前記複数の表示画素の前記画素電極に共通に対向し、かつ、前記撥液化された前記隔壁上に延在して電気的に接続された単一の対向電極を形成する工程と、をさらに含むことを特徴とする。

請求項10記載の発明に係る表示装置は、請求項1乃至9のいずれかに記載の表示装置の製造方法によって製造されたことを特徴とする。

【発明の効果】

【0017】

本発明に係る表示装置及びその製造方法によれば、隣接する表示画素間で混色を生じることなく、各表示画素の形成領域の略全域にわたり、膜厚の均一性が改善された有機EL層等を含む担体輸送層が形成された表示パネルを実現することができる。

【発明を実施するための最良の形態】

【0018】

以下、本発明に係る表示装置及びその製造方法について、実施の形態を示して詳しく説明する。ここで、以下に示す実施形態においては、表示画素を構成する発光素子として、上述した高分子系の有機材料からなる有機EL層を備えた有機EL素子を適用した場合について説明する。

【0019】

(表示パネル)

まず、本発明に係る表示装置に適用される表示パネル(有機ELパネル)及び表示画素について説明する。

図1は、本発明に係る表示装置に適用される表示パネルの画素配列状態の一例を示す概略平面図であり、図2は、本発明に係る表示装置の表示パネルに2次元配列される各表示画素(表示素子及び画素駆動回路)の回路構成例を示す等価回路図である。なお、図1に示す平面図においては、説明の都合上、表示パネル(絶縁性基板)を視野側から見た、各表示画素(色画素)に設けられる画素電極の配置と各配線層の配設構造との関係のみを示し、各表示画素の有機EL素子(表示素子)を発光駆動するために、各表示画素に設けられる図2に示す画素駆動回路内のトランジスタ等の表示を省略した。また、図1においては、画素電極及び各配線層の配置を明瞭にするために、便宜的にハッチングを施して示した。

【0020】

本発明に係る表示装置(表示パネル)は、図1に示すように、ガラス基板等の絶縁性基板11の一面側に、赤(R)、緑(G)、青(B)の3色からなる色画素PXr、PXg、PXbが図面左右方向に繰り返し複数(3の倍数)配列されるとともに、図面上下方向に同一色の色画素PXr、PXg、PXbが複数配列されている。ここでは、隣接するRGB3色の色画素PXr、PXg、PXbを一組として一の表示画素PIXが形成されている。

【0021】

表示パネル10は、絶縁性基板11の一面側から突出し、柵状又は格子状の平面パターンを有して配設されたバンク(隔壁)形状を有する共通電圧ライン(例えばカソードライン)Lcにより、図面上下方向に配列された同一色の複数の色画素PXr、PXg、又はPXbの画素形成領域からなる各色画素領域が画定される。また、各色画素領域に含まれる複数の色画素PXr、PXg、又はPXbが形成される各画素形成領域には、画素電極(例えばアノード電極)15が形成されているとともに、上記共通電圧ラインLcの配設方向に並行して図面上下方向(すなわち列方向)にデータラインLdが配設され、また、当該データラインLdに直交して図面左右方向(すなわち行方向)に選択ラインLs及び供給電圧ライン(例えばアノードライン)Laが配設されている。

【0022】

表示画素PIXの各色画素PXr、PXg、PXbの具体的な回路構成としては、例えば図2に示すように、絶縁性基板11上に1乃至複数のトランジスタ(例えばアモルファスシリコン薄膜トランジスタ等)からなる画素駆動回路(又は画素回路)DCと、当該画素駆動回路DCにより生成される発光駆動電流が、上記画素電極15に供給されることにより発光動作する有機EL素子(表示素子)OELと、を備えている。

【0023】

供給電圧ラインLaは、例えば所定の高電位電源に直接又は間接的に接続され、各表示画素PIX(色画素PXr、PXg、PXb)に設けられる有機EL素子OELの画素電極15(例えばアノード電極)に表示データ(階調電流Idata)に応じた発光駆動電流が流れるための所定の高電圧(供給電圧Vsc)を印加し、共通電圧ラインLcは、例えば所定の低電位電源に直接又は間接的に接続され、有機EL素子OELの対向電極(例えばカソード電極)に所定の低電圧(共通電圧Vcom;例えば接地電位Vgnd)を印加するように設定されている。

【0024】

画素駆動回路DCは、例えば図2に示すように、ゲート端子が表示パネル10(絶縁性基板11)の行方向に配設された選択ラインLsに、ドレイン端子が上記供給電圧ラインLaに、ソース端子が接点N11に各々接続されたトランジスタTr11と、ゲート端子が選択ラインLsに、ソース端子が表示パネル10の列方向に配設されたデータラインLdに、ドレイン端子が接点N12に各々接続されたトランジスタTr12と、ゲート端子が接点N11に、ドレイン端子が供給電圧ラインLaに、ソース端子が接点N12に各々接続されたトランジスタTr13(発光駆動用のスイッチング素子)と、接点N11及び接点N12間(トランジスタTr13のゲート−ソース間)に接続されたキャパシタCsと、を備えている。ここでは、トランジスタTr11〜Tr13はいずれもnチャネル型の薄膜トランジスタが適用されている。薄膜トランジスタは、アモルファスシリコン薄膜トランジスタであっても、ポリシリコン薄膜トランジスタであってもよい。

【0025】

有機EL素子OELは、アノード端子(アノード電極となる画素電極15)が上記画素駆動回路DCの接点N12に接続され、カソード端子(カソード電極となる対向電極)が表示パネル10の列方向に配設された共通電圧ラインLcに接続されている。また、図2において、キャパシタCsはトランジスタTr13のゲート−ソース間に形成される寄生容量、又は、該ゲート−ソース間に付加的に形成される補助容量である。

【0026】

なお、図2に示した画素駆動回路DCにおいて、選択ラインLsは、図示を省略した選択ドライバに接続され、所定のタイミングで表示パネル10の行方向に配列された複数の表示画素PIX(色画素PXr、PXg、PXb)を選択状態に設定するための選択信号Sselが選択ドライバから印加される。また、供給電圧ラインLaは、図示を省略した電源ドライバに接続され、上記選択信号Sselと同期したタイミングで同じ行に配列された表示画素PIXに所定の供給電圧Vscが電源ドライバから印加される。データラインLdは、図示を省略したデータドライバに接続され、上記表示画素PIXの選択状態に同期するタイミングで表示データに応じた階調電流Idataが流れる。

【0027】

そして、このような回路構成を有する画素駆動回路DCを備えた表示画素PIX(表示パネル10)における駆動制御動作は、まず、書込動作期間において、図示を省略した選択ドライバから選択ラインLsに対して、選択レベル(オンレベル;例えばハイレベル)の選択信号Sselを印加するとともに、該選択信号Sselに同期して図示を省略した電源ドライバからローレベルの供給電圧Vscを供給電圧ライン(アノードライン)Laに対して印加する。

【0028】

このタイミングに同期して、図示を省略したデータドライバは、表示データに応じた電流値を有する階調電流IdataがデータラインLdに流れるように制御する。つまり、データドライバは、表示データに応じた階調電流Idataの電流値を制御するドライバであり、本実施形態においては、書込動作期間中において固定されたローレベルの電圧である供給電圧Vscに対してデータドライバがデータラインLdの電位を低くして、表示画素PIX(画素駆動回路DC)側からデータラインLd方向に所望の電流値の階調電流Idataを引き抜くように流すものとする。

【0029】

これにより、画素駆動回路DCのトランジスタTr11及びTr12がオン動作して、ローレベルの供給電圧Vscが接点N11(トランジスタTr13のゲート端子;キャパシタCsの一端側)に印加されるとともに、階調電流Idataの引き込み動作によりトランジスタTr12を介してローレベルの供給電圧Vscよりも低電位の電圧レベルが接点N12(トランジスタTr13のソース端子;キャパシタCsの他端側)に印加され、トランジスタTr13にはデータドライバで設定された階調電流Idataが強制的に流されることになる。

【0030】

このとき、キャパシタCsには、接点N11及びN12間に生じた電位差に対応する電荷が蓄積され、電圧成分として保持される(充電される)。この蓄積された電荷の量は、書込動作時にトランジスタTr13のドレイン−ソース間を流れる階調電流Idataの電流値によって自動的に設定される。また、このとき、ローレベルの供給電圧Vscは、共通電圧ライン(カソードライン)Lcを介してカソード端子に印加される共通電位Vcom(接地電位Vgnd)以下に設定されているので、有機EL素子OELには、順バイアス電圧が印加されないため、書込動作時に有機EL素子OELには発光駆動電流が流れず、発光動作は行われない。

【0031】

次いで、発光動作期間においては、選択ドライバから選択ラインLsに対して、非選択レベル(オフレベル;例えばローレベル)の選択信号Sselを印加するとともに、電源ドライバから供給電圧ラインLaに対して、ハイレベルの供給電圧Vscを印加する。また、このタイミングに同期して、データドライバによる階調電流Idataの引き抜き動作を停止する。

【0032】

これにより、トランジスタTr11及びTr12がオフ動作して、接点N11への供給電圧Vscの印加が遮断されるとともに、接点N12への階調電流Idataの引き込み動作に起因する電圧レベルの印加が遮断されるので、キャパシタCsは、上述した書込動作において蓄積された電荷を保持する。

【0033】

このように、キャパシタCsが書込動作時に蓄積された電荷(充電電圧)を保持することにより、接点N11及びN12間(トランジスタTr13のゲート−ソース間)の電位差が保持されることになり、トランジスタTr13が階調電流Idataの電流値に応じた電流値の電流を流すことができるような状態を維持する。また、供給電圧ラインLaには、共通電圧Vcom(接地電位Vgnd)よりも高い電圧レベルで、且つ、発光動作期間にトランジスタTr13を流れる電流が飽和電流となるようにドレイン−ソース間電位差が十分高くなるような所定の電圧値の供給電圧Vscが印加されると、トランジスタTr13は、書込動作時に蓄積された電荷によるゲート−ソース間電位差によって、書込動作時に流れる階調電流Idataの電流値に応じた発光駆動電流を有機EL素子OELに順バイアス方向に流し、有機EL素子OELは、階調電流Idataひいては表示データにしたがった輝度で発光動作する。

【0034】

そして、このような一連の駆動制御動作を、表示パネル10に2次元配列された全ての表示画素PIX(各色画素PXr、PXg、PXb)について、例えば各行ごとに順次繰り返し実行することにより、所望の画像情報を表示する画像表示動作を実行することができる。

【0035】

(表示画素のデバイス構造)

次いで、上述したような回路構成を有する表示画素(発光駆動回路及び有機EL素子)の具体的なデバイス構造(平面レイアウト及び断面構造)について説明する。

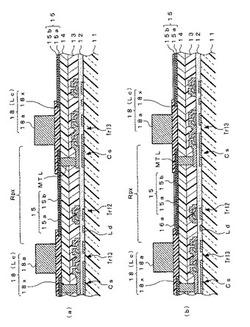

図3は、本実施形態に係る表示装置(表示パネル)に適用可能な表示画素の一例を示す平面レイアウト図であり、図4は、本実施形態に係る表示画素の平面レイアウトの要部詳細図である。ここでは、図1に示した表示画素PIXの赤(R)、緑(G)、青(B)の各色画素PXr、PXg、PXbのうちの、特定の一の色画素の平面レイアウトを示す。なお、図3においては、画素駆動回路DCの各トランジスタ及び配線層等が形成された層を中心に示し、図4においては、図3に示した平面レイアウトのうち、共通電圧ラインLcの下層に形成される各トランジスタ及び配線層等を具体的に示す。また、図4において、括弧数字は、各導電層(配線層を含む)の上下の順を表し、数字が小さいほど下層側(絶縁性基板11側)に形成され、大きいほど上層側(視野側)に形成されていることを示す。また、図5、図6は、各々、図3に示した平面レイアウトを有する表示画素PIXにおけるA−A断面及びB−B断面を示す概略断面図である。

【0036】

図2に示した表示画素PIX(色画素PXr、PXg、PXb)は、具体的には、絶縁性基板11の一面側に設定された画素形成領域(各色画素PXr、PXg、PXbの形成領域)Rpxにおいて、図3に示した平面レイアウトの上方及び下方の縁辺領域に行方向(図面左右方向)に延在するように選択ラインLs及び供給電圧ラインLaが各々配設されるとともに、これらのラインLs、Laに直交するように、上記平面レイアウトの左方及び右方の縁辺領域に列方向(図面上下方向)に延在するようにデータラインLd及び共通電圧ラインLcが各々配設されている。

【0037】

ここで、図3〜図6に示すように、供給電圧ラインLaは、共通電圧ラインLcよりも下層側(絶縁性基板11側)に設けられ、選択ラインLs及び供給電圧ラインLaは、同層に設けられ、データラインLdは、選択ラインLs及び供給電圧ラインLaよりも下層側に設けられている。ここで、選択ラインLsは、トランジスタTr11〜Tr13のソース、ドレインを形成するためのソース、ドレインメタル層をパターニングすることによってソース、ドレインと同じ工程で形成される。また、データラインLdは、トランジスタTr11〜Tr13のゲートを形成するためのゲートメタル層をパターニングすることによってゲートと同じ工程で形成される。

【0038】

すなわち、表示画素PIXは、図5、図6に示すように、絶縁性基板11上に表示画素PIX内に設けられる画素駆動回路DC(図2参照)の複数のトランジスタTr11〜Tr13やキャパシタCs、及び、選択ラインLsやデータラインLdを含む各種配線層が設けられ、当該トランジスタTr11〜Tr13及び配線層を被覆するように順次形成された保護絶縁膜13及び平坦化膜14を介して、その上層に、画素駆動回路DCに接続されて所定の発光駆動電流が供給される画素電極(例えばアノード電極)15、正孔輸送層16a(担体輸送層)と電子輸送性発光層16b(担体輸送層)からなる有機EL層(発光機能層)16、及び、共通電圧Vcomが印加される対向電極(例えばカソード電極)17からなる有機EL素子OELが形成されている。

【0039】

画素駆動回路DCは、より具体的には、図3、図4に示すように、図2に示したトランジスタTr11が行方向に配設された選択ラインLsに沿って延在するように配置され、トランジスタTr12が列方向に配設されたデータラインLdに沿って延在するように配置され、トランジスタTr13が列方向に配設された共通電圧ラインLcに沿って延在するように配置されている。

【0040】

ここで、各トランジスタTr11〜Tr13は、周知の電界効果型トランジスタ構造を有し、各々、絶縁性基板11上に形成されたゲート電極Tr11g〜Tr13gと、ゲート絶縁膜12を介して各ゲート電極Tr11g〜Tr13gに対応する領域に形成された半導体層SMCと、該半導体層SMCの両端部に延在するように形成されたソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13dと、を有している。

【0041】

なお、各トランジスタTr11〜Tr13のソース電極とドレイン電極が対向する半導体層SMC上には当該半導体層SMCへのエッチングダメージを防止するための酸化シリコン又は窒化シリコン等のブロック層BLが形成され、また、ソース電極とドレイン電極が接触する半導体層SMC上には、当該半導体層SMCとソース電極及びドレイン電極とのオーミック接続を実現するための不純物層OHMが形成されている。トランジスタTr11〜Tr13のゲート電極Tr11g〜Tr13gはいずれも同一のゲートメタル層をパターニングすることによって形成されている。トランジスタTr11〜Tr13のソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13dはいずれも同一のソース、ドレインメタル層をパターニングすることによって形成されている。

【0042】

そして、図2に示した画素駆動回路DCの回路構成に対応するように、トランジスタTr11は、図3、図4に示すように、ゲート電極Tr11gがゲート絶縁膜12に設けられたコンタクトホールHLaを介して選択ラインLsに接続され、同ソース電極Tr11sがゲート絶縁膜12に設けられたコンタクトホールHLbを介してキャパシタCsの一端側(接点N11側)の電極Ecaに接続され、同ドレイン電極Tr11dが供給電圧ラインLaと一体的に形成されている。

【0043】

また、トランジスタTr12は、図3〜図5に示すように、ゲート電極Tr12gがゲート絶縁膜12に設けられたコンタクトホールHLaを介して選択ラインLsに接続され、同ソース電極Tr12sがゲート絶縁膜12に設けられたコンタクトホールHLcを介してデータラインLdに接続され、同ドレイン電極Tr12dがキャパシタCsの他端側(接点N12側)の電極Ecbと一体的に形成されている。

【0044】

トランジスタTr13は、図3〜図5に示すように、ゲート電極Tr13gがキャパシタCsの一端側(接点N11側)の電極Ecaと一体的に形成され、同ソース電極Tr13sがキャパシタCsの他端側(接点N12側)の電極Ecbと一体的に形成され、同ドレイン電極Tr13dが供給電圧ラインLaと一体的に形成されている。

【0045】

また、キャパシタCsは、トランジスタTr13のゲート電極Tr13gと一体的に形成された一端側の電極Ecaと、ソース電極Tr13sと一体的に形成された他端側の電極Ecbと、がゲート絶縁膜12を介して対向して延在するように形成されている。

選択ラインLsは、図3、図4、図6に示すように、ゲート絶縁膜12上に延在し、供給電圧ライン(アノードライン)Laと同一層に形成されている。

【0046】

さらに、トランジスタTr13のソース電極Tr13s(キャパシタCsの電極Ecb)上の保護絶縁膜13及び平坦化膜14には、図5に示すように、コンタクトホールHLdが形成され、当該ソース電極Tr13sと有機EL素子OELの画素電極15とが電気的に接続されるように、金属材料(コンタクトメタルMTL)が埋め込まれている。

【0047】

そして、各画素形成領域Rpxの平坦化膜14上には、図5、図6に示すように、例えばアノード電極となる画素電極15、正孔輸送層16a及び電子輸送性発光層16bからなる有機EL層16、及び、例えばカソード電極となる対向電極17を順次積層した有機EL素子が設けられている。ここで、本実施形態においては、有機EL層16において発光した光を、絶縁性基板11と反対側に(後述する封止樹脂層19及び封止基板20を介して)出射するトップエミッション型の発光構造を有している表示パネル(有機ELパネル)について示す。そのため、画素電極15が少なくとも光反射特性を有し、対向電極17が光透過性を有することになる。ここで、画素電極15は、後述する製造方法(図7〜図10参照)において説明するように、下層側の反射金属層15aと上層側の透明な導電性酸化金属層15bからなる積層構造を有している。

【0048】

また、列方向の各画素形成領域Rpx間(各表示画素PIXの有機EL素子OELの形成領域相互の境界領域)には、有機EL素子OELの形成領域(厳密には、有機EL層16の形成領域)を画定するためのバンク(隔壁)18が平坦化膜14の上面から突出するように設けられている。ここで、本実施形態においては、当該バンク18は、例えば図5に示すように、列方向に延在し、各画素形成領域Rpx間の層間絶縁膜としての機能も果たす下層側の下地層18xと、導電性材料からなり、共通電圧ライン(カソードライン)Lcの列方向に延在する部分である上層側のバンクメタル層18aからなる積層構造を有している。

【0049】

バンク18は、より具体的には、行方向に沿って隣接する表示画素PIX間の境界領域付近に露出する平坦化膜14上から、有機EL素子OELの画素電極15の列方向の周縁上に一部が重なるシリコン窒化膜(SiN)等からなる下地層18xが列方向に延在するように設けられ、当該下地層18x上に、導電性材料(例えば、金属材料)からなるバンクメタル層18aが厚さ方向に突出し且つ列方向に延在するように順次積層形成されている。列方向に沿った複数の下地層18x及びバンクメタル層18aの各端は、図1に示すように、複数の表示画素PIXの画素形成領域の外側において行方向に沿って連結されている。

【0050】

すなわち、上記積層構造を有するバンク18を表示パネル10(絶縁性基板11)上に柵状の平面パターンを有するように配設することにより、列方向(図面上下方向)に配列された複数の表示画素PIXをそれぞれ有する複数のストライプ状の画素形成領域が画定されるとともに、バンク18のバンクメタル層18aにより、表示パネル10の全域に配列された表示画素PIX(有機EL素子OEL)の各々に所定の電圧(共通電圧Vcom)を共通に印加することができる配線層(共通電圧ラインLc)として機能させることができる。

【0051】

すなわち、図5、図6に示すように、有機EL素子OELの対向電極(カソード電極)17を、バンクメタル層18aを備えたバンク18上に延在し且つ、バンクメタル層18aに電気的に接続されるように形成することにより、バンク18(バンクメタル層18a)を共通電圧ラインLcとして兼用することができる。

なお、上記画素駆動回路DC、有機EL素子OEL及びバンク18が形成された絶縁性基板11上には、図5、図6に示すように、透明な封止樹脂層19を介して、絶縁性基板11に対向するようにガラス基板等からなる封止基板20が接合されている。

【0052】

そして、このような表示パネル10においては、例えば、表示パネル10の下層(有機EL素子OELの絶縁性基板11側の層)に設けられたトランジスタTr11〜Tr13やキャパシタCs等の機能素子、選択ラインLsやデータラインLd、供給電圧ライン(アノードライン)La等の配線層からなる画素駆動回路DCにおいて、データラインLdを介して供給された表示データに応じた階調電流Idataに基づいて、所定の電流値を有する発光駆動電流がトランジスタTr13のドレイン−ソース間に流れ、当該トランジスタTr13(ソース電極Tr13s)からコンタクトホールHLd(コンタクトメタルMTL)を介して、有機EL素子OELの画素電極15に供給されることにより、各表示画素PIX(各色画素PXr、PXg、PXb)の有機EL素子OELが上記表示データに応じた所望の輝度階調で発光動作する。

【0053】

このとき、本実施形態に示した表示パネル10において、画素電極15が光反射特性を有し、対向電極17が光透過性を有する場合(すなわち、有機EL素子OELがトップエミッション型である場合)、各表示画素PIX(各色画素PXr、PXg、PXb)の有機EL層16において発光した光は、光透過性を有する対向電極17を介して直接、あるいは、光反射特性を有する画素電極15で反射して、絶縁性基板11(表示パネル)を介することなく封止基板20の一面側(図5、図6の図面上方)に出射される。

【0054】

なお、本実施形態においては、トップエミッション型の発光構造を有する表示素子(有機EL素子)について説明したが、本発明はこれに限定されるものではなく、光透過性を有する画素電極15、及び、光反射特性を有する対向電極17を適用して、有機EL層16において発光した光が、光透過性を有する画素電極15を介して直接、あるいは、光反射特性を有する対向電極17で反射して、絶縁性基板11(表示パネル)を介して他面側(図5、図6の図面下方)に出射されるボトムエミッション型の発光構造を有する表示素子を適用するものであってもよい。

【0055】

(表示装置の製造方法)

次に、上述した表示装置(表示パネル)の製造方法について説明する。

図7乃至図10は、本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図である。ここでは、図5に示したA−A断面から見たパネル構造の製造工程について説明する。また、図11は、本実施形態に係る表示装置(表示パネル)に形成されるバンク表面の被膜材料の化学構造式及び被膜材料がバンクメタル層18aに被膜した状態での結合を示す概念図である。

【0056】

上述した表示装置(表示パネル)の製造方法は、まず、図7(a)に示すように、ガラス基板等の絶縁性基板11の一面側(図面上面側)に設定された表示画素PIX(各色画素PXr、PXg、PXb)の形成領域(画素形成領域)Rpxに、上述した画素駆動回路(図2〜図4参照)DCのトランジスタTr11〜Tr13やキャパシタCs、データラインLdや選択ラインLs等の配線層を形成する(図5、図6参照)。

【0057】

具体的には、絶縁性基板11上に、ゲート電極Tr11g〜Tr13g、及び、ゲート電極Tr13gと一体的に形成されるキャパシタCsの一方側の電極Eca、データラインLd(図5参照)を同一のゲートメタル層をパターニングすることによって同時に形成し、その後、絶縁性基板11の全域にゲート絶縁膜12を被覆形成する。

【0058】

次いで、ゲート絶縁膜12上の各ゲート電極Tr11g〜Tr13gに対応する領域に、例えばアモルファスシリコンやポリシリコン等からなる半導体層SMCを形成し、当該半導体層SMC上に設けられたブロック層BLの両側に半導体層SMCとオーミック接続のための不純物層OHMを介してソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13dを形成する。このとき、同一のソース、ドレインメタル層をパターニングすることによってソース電極Tr13s及びドレイン電極Tr12dと接続されたキャパシタCsの他方側の電極Ecb、選択ラインLs、並びに、ドレイン電極Tr11d及びTr13dと接続された供給電圧ラインLa(図6参照)を同時に形成する。

【0059】

なお、上述したトランジスタTr11〜Tr13のソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13d、キャパシタCsの他端側の電極Ecb、選択ラインLs、供給電圧ラインLaは、配線抵抗を低減し、かつ、マイグレーションを低減する目的で、例えばアルミニウム合金層と遷移金属層からなる積層配線構造を有しているものであってもよい。また、トランジスタTr11〜Tr13は、逆スタガ型に限らずコプラナ型等であってもよい。

【0060】

次いで、図7(b)に示すように、上記トランジスタTr11〜Tr13、キャパシタCs、選択ラインLs及び供給電圧ラインLaを含む絶縁性基板11の一面側全域を被覆するように、50nm〜100nm厚の窒化シリコン(SiN)等からなる保護絶縁膜(パッシベーション膜)13及び1μm〜10μm厚の感光性有機樹脂材料等からなる平坦化膜14を順次形成した後、平坦化膜14及び保護絶縁膜13を光の照射及びエッチャントによりパターニングして、トランジスタTr13のソース電極Tr13s(又は、キャパシタCsの他方側の電極Ecb)の上面が露出するコンタクトホールHLdを形成する。

【0061】

次いで、図7(c)に示すように、上記コンタクトホールHLdに金属材料からなるコンタクトメタルMTLを埋め込む。ここで、コンタクトメタルMTLは、例えば無電解めっき法等を用いて、銅(Cu)等の金属材料を堆積して形成される厚膜を適用することができる。その後、図8(a)に示すように、各画素形成領域Rpx(各色画素PXr、PXg、PXbの形成領域)ごとに、当該コンタクトメタルMTLに電気的に接続された画素電極15を形成する。

【0062】

画素電極15は、具体的には、アルミニウム(Al)、クロム(Cr)、銀(Ag)、パラジウム銀(AgPd)系の少なくとも何れかを含む金属または合金等からなる光反射特性を有する反射金属膜をスパッタリング法等を用いて薄膜形成し、所定の形状にパターニングすることによりコンタクトメタルMTLに電気的に接続された下層の反射金属層15aを形成する。その後、当該反射金属層15aを含む絶縁性基板11の一面側全域を被覆するように、錫ドープ酸化インジウム(Indium Thin Oxide;ITO)や亜鉛ドープ酸化インジウム等の透明電極材料からなる(光透過特性を有する)酸化金属膜を薄膜形成し、上記反射金属層15aの上面や端面が露出しないようにパターニングすることにより上層の導電性酸化金属層15bを形成する。

【0063】

このように、上層の酸化金属膜をパターニングする際に、下層側の反射金属層15aが露出しないようにすることにより、酸化金属膜と反射金属層15aとの間でエッチャントによる電池反応を引き起こさないようにすることができるとともに、下層側の反射金属層15aがオーバーエッチングされたり、エッチングダメージを受けたりすることを防止することができる。

【0064】

次いで、反射金属層15a及び導電性酸化金属層15bからなる上記画素電極15を含む絶縁性基板11の一面側全域を被覆するように、化学気相成長法(CVD法)等を用いて、例えばシリコン酸化膜やシリコン窒化膜等の無機の絶縁性材料からなる絶縁層を形成した後パターニングすることにより、図8(b)に示すように、行方向に沿って互いに隣接する表示画素PIXに形成された画素電極15との間の領域(隣接する表示画素PIXとの境界領域)において、列方向に沿うように、後述するバンク18の最下層となる下地層18xを形成する。下地層18xは、図1において、供給電圧ラインLcと略同一形状であり、表示画素PIXの画素形成領域が複数のストライプ形状に開口されるように形成されている。

【0065】

次いで、図9(a)に示すように、下地層18x上に、例えば銅(Cu)や銀(Ag)、アルミニウム(Al)、又は、これらを主成分とした金属単体又は合金等の低抵抗の非酸化金属材料からなるバンクメタル層18a(供給電圧ラインLc)を、表示画素PIXの画素形成領域が複数のストライプ形状に開口されるように形成する。バンクメタル層18aは表面が非酸化金属材料であれば、内部が非酸化金属材料以外の材料を含んでいてもよい。

【0066】

具体的には、上記下地層18xを含む絶縁性基板11の一面側全域を被覆するように、例えばスパッタ法や真空蒸着法等を用いて上記金属材料の薄膜を形成し、フォトリソグラフィー技術を用いて下地層18x上に所定のパターンを有して残留させることによりバンクメタル層18aを形成する。バンクメタル層18aは、列方向に延在している部分において、行方向の両側部から下地層18xが露出するように行方向の幅が下地層18xよりも幅狭に形成されている。下地層18xは、平坦化膜14とバンクメタル層18aとの間の密着性を改善するために介在された層であり、その熱膨張係数は、平坦化膜14の熱膨張係数とバンクメタル層18aの熱膨張係数との間であることが好ましい。

【0067】

これにより、図1に示すように、表示パネル10の列方向に配列された同一色の複数の表示画素PIXの画素形成領域(有機EL素子OELの有機EL層16の形成領域)Rpxがバンクメタル層18a及び下地層18xからなるバンク18により周囲を囲まれて画定され、当該画素形成領域Rpxごとに画素電極15(導電性酸化金属層15b)の上面が露出した状態となる。

【0068】

次いで、絶縁性基板11を純水で洗浄した後、UVオゾン処理や酸素プラズマ処理等を施すことにより、上記バンク18により画定された各画素形成領域Rpxに露出する画素電極15表面(及び、画素電極15の周辺領域に露出する下地層18x表面を含むものであってもよい)の親液化を行う。親液化処理の際にバンクメタル層18aの表面の一部は酸化されてしまい、このままでは、バンクメタル層18aの表面に後述する撥液化処理を行うことができないため、バンクメタル層18aの表面の酸化膜を除去する。次いで、酸化膜が除去されたバンクメタル層18aの表面に選択的に撥液化処理を施す。

【0069】

ここで、画素電極15の親液化処理の一例であるUVオゾン処理においては、酸素ガス雰囲気中で絶縁性基板11に対して紫外光を照射することにより、活性酸素ラジカルを発生させて、画素電極15(ITO等からなる導電性酸化金属層)の表面を、後述する正孔輸送層となる正孔輸送材料を含有する有機化合物含有液や電子輸送性発光層となる電子輸送性発光材料を含有する有機化合物含有液、もしくは、これらの溶液に用いる有機溶媒に対して濡れ性が向上するように親液化(親水化)する。

【0070】

また、酸化膜除去処理は、上述したバンク18が一面側に形成された絶縁性基板11を過硫酸アンモニウム等の酸系の水溶液に浸漬することにより、バンクメタル層18aの表面をソフトエッチングして表面の酸化膜を除去した後、純水で洗浄し、乾燥させる。次いで行われるバンクメタル層18aの撥液化処理は、具体的には、絶縁性基板11をトリアジントリチオール又は官能基にフッ素を含むフッ素系トリアジンジチオール誘導体等のトリアジンチオール化合物の撥液処理溶液の処理槽内に挿入して浸漬する。この処理工程における撥液処理溶液の温度は概ね20〜30℃程度、浸漬時間は概ね数十秒〜10分程度に設定する。その後、絶縁性基板11を撥液処理溶液から取り出し、アルコール等により濯いで絶縁性基板11表面に残留する撥液処理溶液(トリアジンチオール化合物)を洗い流し、絶縁性基板11を純水で2次洗浄した後、窒素ガス(N2)のブローにより乾燥させる。

【0071】

このとき、トリアジンチオール化合物は、酸化膜除去処理で酸化膜が除去されたバンクメタル層18a表面の金属と選択的に結合して被膜が形成されることになるが、画素電極15表面の金属酸化物(導電性酸化金属層15b)や、下地層18xを形成する無機絶縁膜には撥液性を発現する程度には被膜されない。

【0072】

すなわち、トリアジンチオール化合物の一例として適用可能なフッ素系トリアジンジチオール誘導体は、図11(a)に示すように、トリアジン(3個の窒素を含む六員環構造)の窒素(−N)にチオール基(−SH)が結合した分子構造に加え、特定のチオール基(−SH)のS原子にアルキル基(−CH2−CH2−)及びフッ化アルキル基(−CF2−CF2−CF2−CF3)が順次結合した分子構造を有し、他のトリアジンチオール化合物と同様に、図11(b)に示すように、それ自体が撥液性を示すトリアジントリチオールに加えてさらに撥液性を示すフッ素原子を含んでいるので、バンクメタル層18aの表面に形成される被膜は、トリアジントリチオールよりも強い撥液性を示す。なお、上述した処理工程において使用する撥液処理溶液の濃度は、概ね1×10−4〜1×10−2mol/Lの範囲が好ましい。

【0073】

なお、上記フッ素系トリアジンジチオール誘導体は、チオール基のS原子がアルキル基(−CH2−CH2−)と結合した分子構造を有しているが、直接フッ化アルキル基と結合してもよく、またトリアジンチオール化合物がバンクメタル層18aに被覆される際に著しい立体障害にならない限りアルキル基、フッ化アルキル基の炭素数に特別な制限はない。また、上記フッ素系トリアジンジチオール誘導体は、残る二つのチオール基の一つのS原子において、水素基に代わって直接又は間接的にフッ化アルキル基が置換形成されていてもよく、或いはフッ素原子を含む基の炭素間がオレフィン二重結合を有していてもよい。また、その他のトリアジンチオール誘導体として、例えば、6−ジメチルアミノ−1,3,5−トリアジン−2,4−ジチオール−ナトリウム塩或いは6−ジドデシルアミノ−1,3,5−トリアジン−2,4−ジチオール−ナトリウム塩を用い、水に溶解して被膜18cを被膜してもよい。

【0074】

これにより、絶縁性基板11の一面側に形成された各構成のうち、親液化処理によって形成された酸化膜を酸化膜除去処理によって除去された、金属材料からなるバンクメタル層18aの表面では、トリアジンチオール化合物との結合性が著しく向上しているので、撥液性を十分に示す程度にトリアジンチオール化合物の被膜が形成され、一方、酸化金属層(ITO等)15bにより被覆された画素電極15の表面及び下地層18xの表面、画素電極15間から露出した平坦化膜14(或いは保護絶縁膜13)には付着しにくく、被膜がほとんど形成されない。したがって、同一の絶縁性基板11上において、バンクメタル層18aの表面のみが撥液化処理され、当該バンク18により画定された各画素形成領域Rpxに露出する画素電極15表面は撥液化処理されていない状態(親液性が保持された状態)が実現される。

【0075】

なお、本実施形態において使用する「撥液性」とは、後述する正孔輸送層となる正孔輸送材料を含有する有機化合物含有液や、電子輸送性発光層となる電子輸送性発光材料を含有する有機化合物含有液、もしくは、これらの溶液に用いる有機溶媒を、絶縁性基板上等に滴下して、接触角の測定を行った場合に、当該接触角が50°以上になる状態と規定する。また、「撥液性」に対する「親液性」とは、本実施形態においては、上記接触角が40°以下になる状態と規定する。

【0076】

また、表示パネル10の列方向に配列された同一色の各表示画素PIX(有機EL素子OEL)の画素形成領域Rpxが、撥液化処理されたバンク18により、隣接する他の色の表示画素PIX(有機EL素子OEL)の画素形成領域Rpxと隔離されるので、後述する有機EL層16となる発光層(電子輸送性発光層16b)を形成する際に、当該発光材料の溶液又は分散液(液状材料)を塗布する場合であっても、バンク18を越えて隣接する表示画素PIX(色画素PXr、PXg、PXb)に発光材料が混合することがなく、隣接する色画素相互での混色を防止することができる。

【0077】

次いで、図9(b)に示すように、上記バンク18により囲まれた(画定された)各色の画素形成領域(有機EL素子OELの形成領域)Rpxに対して、互いに分離した複数の液滴を所定位置に吐出するインクジェット法、又は、溶液を連続的に流し込むノズルプリント法等を適用して同一工程で、正孔輸送材料の溶液又は分散液を塗布した後、加熱乾燥により残留溶媒を除去し正孔輸送層16aを形成する。続いて、図10(a)に示すように、当該正孔輸送層16a上に電子輸送性発光材料の溶液又は分散液を塗布した後、加熱乾燥により残留溶媒を除去し電子輸送性発光層16bを形成する。これにより、画素電極15上に正孔輸送層16a及び電子輸送性発光層16bからなる有機EL層(発光機能層)16が積層形成される。

【0078】

具体的には、有機高分子系の正孔輸送材料(担体輸送性材料)を含む有機化合物含有液として、例えばポリエチレンジオキシチオフェン/ポリスチレンスルホン酸水溶液(PEDOT/PSS;導電性ポリマーであるポリエチレンジオキシチオフェンPEDOTと、ドーパントであるポリスチレンスルホン酸PSSを水系溶媒に分散させた分散液)を、上記画素電極15(導電性酸化金属層15b)上に塗布した後、塗布された基板11を載置するステージ及び/又はステージ上の雰囲気を100℃以上の温度条件で加熱乾燥処理を行って残留溶媒を除去することにより、当該画素電極15上に有機高分子系の正孔輸送材料を定着させて、担体輸送層である正孔輸送層16aを形成する。

【0079】

ここで、画素電極15及びその周辺の下地層18xの表面は、上記有機化合物含有液(PEDOT/PSS)に対して親液性を有しているので、バンク18により画定された画素形成領域Rpxに塗布された有機化合物含有液は当該領域内(画素電極15上)に充分馴染んで均等に広がる。

【0080】

これにより、後述するように、有機化合物含有液を加熱乾燥処理する際に、当該有機化合物含有液が縁辺領域方向に引っ張られながら乾燥するので、正孔輸送層16aが画素電極15の中央表面上で盛り上がりすぎることがないため、膜厚の均一性が向上する。また、バンクメタル層18aの表面は、上記有機化合物含有液(PEDOT/PSS)に対して撥液性を有しているので、隣接する画素形成領域への有機化合物含有液の漏出や乗り越えを防止することができる。

【0081】

また、有機高分子系の電子輸送性発光材料(担体輸送性材料)を含む有機化合物含有液として、例えばポリパラフェニレンビニレン系やポリフルオレン系等の共役二重結合ポリマーを含む発光材料を、水や或いはテトラリン、テトラメチルベンゼン、メシチレン、キシレン等の有機溶媒に溶解した溶液を、上記正孔輸送層16a上に塗布した後、窒素雰囲気中でステージを加熱或いは1Torr以下の減圧雰囲気下でステージ上の雰囲気を加熱して乾燥処理を行って溶媒を除去することにより、正孔輸送層16a上に有機高分子系の電子輸送性発光材料を定着させて、担体輸送層であり発光層でもある電子輸送性発光層16bを形成する。

【0082】

この場合においても、上述した正孔輸送層16aと同様に、画素電極15上の正孔輸送層16a及びその周辺の下地層18xの表面は、上記有機化合物含有液に対して親液性を有しているので、バンク18により画定された画素形成領域Rpxに塗布された有機化合物含有液は当該領域内(正孔輸送層16a上)に充分馴染んで均等に広がる。

【0083】

これにより、後述するように、有機化合物含有液を加熱乾燥処理する際に、当該有機化合物含有液が縁辺領域方向に引っ張られながら乾燥するので、正孔輸送層16a上に形成される電子輸送性発光層16bの膜厚の均一性が向上する。また、バンクメタル層18aの表面は、上記有機化合物含有液に対して撥液性を有しているので、隣接する画素形成領域への有機化合物含有液の漏出や乗り越えを防止することができる。

【0084】

その後、図10(b)に示すように、少なくとも各画素形成領域Rpxを含む絶縁性基板11上に光透過性を有する導電層(透明電極層)を形成し、上記有機EL層16(正孔輸送層16a及び電子輸送性発光層16b)を介して各画素電極15に対向する共通の対向電極(例えばカソード電極)17を形成する。ここで、対向電極17は、例えば真空蒸着法やスパッタリング法等により電子注入層となるカルシウム(Ca)やバリウム(Ba)、マグネシウム、フッ化リチウム等の金属材料からなる薄膜を形成した後、その上層にスパッタ法等によりITO等の透明電極層を積層形成した、厚さ方向に透明な膜構造を適用することができる。

【0085】

また、対向電極17は、上記画素電極15に対向する領域のみならず、各画素形成領域Rpx(有機EL素子OELの形成領域)を画定するバンク18上にまで延在する単一の導電層として形成されるとともに、バンク18を形成するバンクメタル層18aと電気的に接続されるように接合される。これにより、バンク18を形成するバンクメタル層18aを各表示画素PIXに共通に接続された共通電圧ライン(カソードライン)Lcとして適用することができる。このように、各表示画素PIX(有機EL素子OEL)間に対向電極17と等電位のバンクメタル層18aを網羅することによってカソード全体のシート抵抗を下げ、表示パネル10全体で均一な表示特性にすることができる。

【0086】

次いで、上記対向電極17を形成した後、絶縁性基板11の一面側全域に保護絶縁膜(パッシベーション膜)としてシリコン酸化膜やシリコン窒化膜等からなる封止層19をCVD法等を用いて形成し、さらに、UV硬化又は熱硬化接着剤を用いて、封止蓋や封止基板20を接合する(貼り合わせる)ことにより、図5、図6に示したような断面構造を有する表示パネル10が完成する。

【0087】

なお、上述した実施形態においては、有機EL層16が正孔輸送層16a及び電子輸送性発光層16bからなる場合について説明したが、本発明はこれに限定されるものではなく、例えば正孔輸送兼電子輸送性発光層のみでもよく、正孔輸送性発光層及び電子輸送層でもよく、また、間に適宜担体輸送層が介在してもよく、その他の担体輸送層の組合せであってもよい。

また、上記実施形態では、画素電極15をアノードとしたが、これに限らずカソードとしてもよい。このとき、有機EL層16は、画素電極15に接する担体輸送層が電子輸送性の層であればよい。

【0088】

(比較検証)

次に、上述した本発明に係る表示装置の製造方法に特有の作用効果について、具体的に検証する。

図12は、UVオゾン処理における紫外光の照射時間と純水接触角との関係を示す実験データであり、図13は、親液化処理後のソフトエッチングの処理時間と撥液化処理後の純水接触角との関係を示す実験データである。ここで、図12(a)及び図13(a)は、各実験により得られた数値データの表であり、図12(b)及び図13(b)は、図12(a)及び図13(a)に示した数値データをグラフ化したものである。

【0089】

上述した実施形態においては、一面側に突出して配設されたバンク18により、各表示画素PIX(有機EL素子OEL)の画素形成領域Rpxが画定された絶縁性基板11において、UVオゾン処理等により親液化処理した後、過硫酸アンモニウム等の酸系の水溶液に浸漬してバンク18の表面にソフトエッチングを施し、その後、トリアジンチオール化合物等の撥液処理溶液に浸漬してバンク表面にトリアジンチオール化合物の被膜を形成し、撥液化することにより、絶縁性基板11上に親液性を示す領域(画素電極表面)と、撥液性を示す領域(バンク表面)とを共存させた親疎水パターンを形成する製造方法を示した。

【0090】

ここで、絶縁性基板上に親疎水パターンを形成する方法としては、上述した実施形態に示した製造方法の他に、例えば撥液処理溶液に絶縁性基板を浸漬してバンク表面を撥液化した後、UVオゾン処理や酸素プラズマ処理等により各画素形成領域に露出する画素電極(導電性酸化金属層)表面を親液化する手法(以下、便宜的に「第1の比較例」と記す)が考えられる。

【0091】

このような製造方法においては、先の工程において撥液化したバンク表面に形成された撥液性の被膜(トリアジンチオール化合物の被膜)が、親液化処理の際のUVオゾン処理や酸素プラズマ処理により分解されて、バンク表面の撥液性が低下してしまい、有機化合物含有液を塗布する際に、隣接する画素形成領域(有機EL素子)に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)が生じたりする等の問題を有している。

【0092】

このような問題を回避する手法としては、例えばUVオゾン処理や酸素プラズマ処理等により各画素形成領域の画素電極を親液化した後、バンク表面をソフトエッチングすることなしに撥液処理溶液に絶縁性基板を浸漬してバンク表面に撥液性の被膜を形成させて撥液化する製造方法(以下、便宜的に「第2の比較例」と記す)が考えられる。

【0093】

この場合、バンク(又はバンク表面)を形成する金属材料として、銅や銀、又はこれらを主成分とする低抵抗の合金を適用した場合、UVオゾン処理や酸素プラズマ処理等によりこれらの金属の表面に形成された酸化膜を除去していないので、後続する撥液化処理において撥液性の被膜(トリアジンチオール化合物の被膜)が形成されにくくなったり、有機EL層上に形成される対向電極(例えばカソード電極)とバンクとの接合性が低下して接触抵抗が高くなる等の問題を有している。特に、バンクを形成する金属材料として、低抵抗で比較的安価な銅を適用した場合、銀を適用した場合に比較して酸化されやすく、撥液化処理におけるトリアジンチオール化合物の結合が極端に起こりにくくなり、撥液性の被膜が充分に形成されず撥液性が著しく低下する傾向がある。

【0094】

ここで、上記第1及び第2の比較例において、各々バンクを形成する金属材料として、銅を用い、親液化処理としてUVオゾン処理を適用した場合の純水接触角を測定すると、表1に示すように、銅をトリアジンチオール化合物の撥液処理溶液に浸漬して被膜を形成し撥液化した後、UVオゾン処理を施す第1の比較例においては、純水接触角が73.2°となり、また、銅をUVオゾン処理した後、バンク表面をソフトエッチングすることなしに撥液処理溶液に浸漬して撥液化する第2の比較例においては、純水接触角が54.5°となり、いずれの場合においても純水接触角が比較的低くく、撥液性が低下することが判明した。

【0095】

【表1】

【0096】

一方、上述した実施形態にも示したように、画素電極上に形成される有機EL層(正孔輸送層)の材料として、PEDOT/PSS等の有機化合物含有液を適用した場合、当該溶液の塗布乾燥工程において凝集しやすく、形成される正孔輸送層の膜厚が不均一になりやすいという特性を有している。ここで、PEDOT/PSSを適用した正孔輸送層の膜厚を均一化するためには、画素電極(導電性酸化金属層)の表面の純水接触角を概ね10°以下になるように親液化処理を行う必要がある。

【0097】

このような観点に基づいて、上述した実施形態に示した製造方法における各処理工程ごとの純水接触角を検証すると、まず、絶縁性基板に対してUVオゾン処理を施し、画素電極(導電性酸化金属層)表面を親液化する処理においては、図3に示すように、紫外光の照射時間(UV照射時間)が長くなるほど、画素電極表面の純水接触角が10°以下にまで低くなり、上述したPEDOT/PSSに対する親液性が向上することが判明した。

【0098】

ここで、上記純水接触角の測定は、具体的には、親液化処理として、フィルジェン株式会社製のUVオゾンクリーナー(型式:NL−UV253)を用い、酸素注入条件として流量10L/min、注入時間0.3minに設定し、画素電極表面に形成されるITO膜(導電性酸化金属層)をUVオゾン処理したものを用いた。

【0099】

これにより、絶縁性基板(ITO膜からなる導電性酸化金属層を備えた画素電極)に対する親液化処理として、概ね4分(min)以上紫外光を照射することにより10°以下の純水接触角が得られ、より好ましくは、10分(min)程度照射することにより10°以下の純水接触角が安定的に得られることが判明した。

【0100】

次いで、上記UVオゾン処理の後、1.0wt%の濃度で、室温程度の液温に設定された過硫酸アンモニウム水溶液に絶縁性基板を浸漬してソフトエッチングを施すことにより、上記UVオゾン処理によりバンクを形成する銅の表面に形成された酸化膜を除去する。その後、トリアジンチオール化合物の撥液処理溶液に浸漬してバンクを形成する銅の表面に撥液性の被膜を形成して撥液化処理を行う。この場合のバンク(銅)表面の純水接触角は、図13に示すように、ソフトエッチングの処理時間(過硫酸アンモニウム水溶液への浸漬時間)が長くなるほど上昇し、上述した表1に示したように、ソフトエッチングを行わずに撥液化処理を行った場合の純水接触角(73.2°、54.5°)に比較して、PEDOT/PSSに対して充分な撥液性を示す130°程度に設定されることが判明した。

【0101】

これにより、絶縁性基板上に配設されたバンク(銅)に対する撥液化処理に先立って実行するソフトエッチングとして、概ね10秒以上過硫酸アンモニウム水溶液に浸漬することにより130°程度の純水接触角が安定的に得られることが判明した。

また、この撥液化処理を行った後の画素電極(ITO膜)表面の純粋接触角は、図13に示すように、ソフトエッチングの処理時間に関わらず、略一定(概ね9〜11°程度)となり、PEDOT/PSSに対する充分な親液性を維持していることが判明した。

【0102】

このように、金属材料により形成されたバンクにより各表示画素(有機EL素子)の形成領域が画定された絶縁性基板(パネル基板)において、UVオゾン処理等により画素形成領域(画素電極)の親液化処理を行い、その後、バンク表面のソフトエッチングを施した後、トリアジンチオール化合物の被膜を形成して撥液化する製造方法によれば、画素形成領域に露出する画素電極(ITO膜)表面における純水接触角を概ね10°以下として良好な親液性を実現することができるとともに、当該画素形成領域を画定するバンク表面における純水接触角を概ね130°以上として良好な撥液性を実現することができるので、有機EL層を形成するための有機化合物含有液(PEDOT/PSS等)を絶縁性基盤上に塗布する工程において、有機化合物含有液が画素電極上の全域に充分馴染んで広がり膜厚が均一化された有機EL層(発光機能層)を形成することができるとともに、隣接する画素形成領域(有機EL素子)に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)等が生じる現象を防止することができる。

【0103】

また、UVオゾン処理等による親液化処理によりバンク表面に形成される酸化膜が、撥液化処理前のソフトエッチングにより除去されるので、有機EL層の形成後に各画素形成領域(画素電極)に共通に設けられる対向電極と上記バンクとの接合性が向上して、良好な電気的な接続を実現することができる。

【0104】

したがって、発光動作時における発光開始電圧や、有機EL層から放射される光の波長(色度)の設計値からのずれを抑制して、所望の表示画質を得ることできるとともに、有機EL素子の劣化や接続不良の発生を抑制して、信頼性や寿命に優れた表示パネルを実現することができる。

【0105】

なお、上述した比較検証においては、画素電極の親液化処理としてUVオゾン処理を適用した場合について説明したが、本発明はこれに限定されるものではなく、UVオゾン処理と同様に、プラズマ中で酸素ラジカルを発生させて、画素電極(ITO等からなる導電性酸化金属層)の表面を親液化(親水化)する酸素プラズマ処理により親液化処理を施す場合であっても、上記実験データと略同等の結果が得られ、同等の効果を得ることができる。

【図面の簡単な説明】

【0106】

【図1】本発明に係る表示装置に適用される表示パネルの画素配列状態の一例を示す概略平面図である。

【図2】本発明に係る表示装置の表示パネルに2次元配列される各表示画素(表示素子及び画素駆動回路)の回路構成例を示す等価回路図である。

【図3】本実施形態に係る表示装置(表示パネル)に適用可能な表示画素の一例を示す平面レイアウト図である。

【図4】本実施形態に係る表示画素の平面レイアウトの要部詳細図である。

【図5】本実施形態に係る平面レイアウトを有する表示画素におけるA−A断面を示す概略断面図である。

【図6】本実施形態に係る平面レイアウトを有する表示画素におけるB−B断面を示す概略断面図である。

【図7】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その1)である。

【図8】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その2)である。

【図9】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その3)である。

【図10】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その4)である。

【図11】本実施形態に係る表示装置(表示パネル)に形成されるバンク表面の被膜材料の化学構造式及び被膜材料がバンクメタル層に被膜した状態での結合を示す概念図である。

【図12】UVオゾン処理における紫外光の照射時間と純水接触角との関係を示す実験データである。

【図13】親液化処理後のソフトエッチングの処理時間と撥液化処理後の純水接触角との関係を示す実験データである。

【符号の説明】

【0107】

10 表示パネル

11 絶縁性基板

15 画素電極

15a 反射金属層

15b 導電性酸化金属層

16 有機EL層

16a 正孔輸送層

16b 電子輸送性発光層

17 対向電極

18 バンク

18x 下地層

18a バンクメタル層

PIX 表示画素

Rpx 画素形成領域

【技術分野】

【0001】

本発明は、表示装置及びその製造方法に関し、特に、担体輸送材料からなる液状材料を塗布することにより担体輸送層が形成される発光素子を有する複数の表示画素を、二次元配列した表示パネルを備えた表示装置及びその製造方法に関する。

【背景技術】

【0002】

近年、携帯電話や携帯音楽プレーヤ等の電子機器の表示デバイスとして、有機エレクトロルミネッセンス素子(以下、「有機EL素子」と略記する)を2次元配列した表示パネル(有機EL表示パネル)を適用したものが知られている。特に、アクティブマトリックス駆動方式を適用した有機EL表示パネルにおいては、広く普及している液晶表示装置に比較して、表示応答速度が速く、視野角依存性もなく、また、高輝度・高コントラスト化、表示画質の高精細化等が可能であるとともに、液晶表示装置のようにバックライト導光板などを必要としないので、一層の薄型軽量化が可能であるという極めて優位な特徴を有している。

【0003】

ここで、有機EL素子は、周知のように、例えば概略、ガラス基板等の一面側に、アノード(陽極)電極と、有機EL層(発光機能層)と、カソード(陰極)電極と、を順次積層した素子構造を有し、有機EL層に発光しきい値を越えるようにアノード電極に正電圧、カソード電極に負電圧を印加することにより、有機EL層内で注入されたホールと電子が再結合する際に生じるエネルギーに基づいて光(励起光)が放射されるものであるが、有機EL層となる正孔輸送層(正孔注入層)や電子輸送性発光層(発光層)を形成する有機材料(正孔輸送材料や電子輸送性発光材料)に応じて、低分子系と高分子系の有機EL素子に大別することができる。

【0004】

低分子系の有機材料を適用した有機EL素子の場合、一般に、製造プロセスにおいて蒸着法を適用する必要があるため、画素形成領域のアノード電極上にのみ当該低分子系の有機膜を選択的に薄膜形成する際に、上記アノード電極以外の領域への低分子材料の蒸着を防止するためのマスクを用いる場合があり、当該マスクの表面にも低分子材料が付着することになるため、製造時の材料ロスが大きいうえ、製造プロセスが非効率的であるという問題を有している。

【0005】

一方、高分子系の有機材料を適用した有機EL素子の場合には、湿式成膜法としてインクジェット法(液滴吐出法)やノズルプリント法(液流吐出法)等を適用することができるので、アノード電極上、又は、アノード電極を含む特定の領域にのみ選択的に上記有機材料の溶液を塗布することができ、材料ロスが少なく効率的な製造プロセスで良好に有機EL層(正孔輸送層や電子輸送性発光層)の薄膜を形成することができるという利点を有している。

【0006】

そして、このような高分子系の有機EL表示パネルにおいては、ガラス基板等の絶縁性基板上に配列される各表示画素の形成領域(画素形成領域)を画定するとともに、高分子系有機材料からなる液状材料(溶液)を塗布する際に、隣接する画素形成領域に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)等が生じる現象を防止するために、各画素形成領域間に絶縁性基板上に連続的に突出して形成された隔壁を設けたパネル構造を有するものが知られている。このような隔壁を備えた有機EL表示パネルについては、例えば、特許文献1等に詳しく説明されている。

【0007】

【特許文献1】特開2001−76881号公報 (第4頁〜第7頁、図1〜図6)

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上述したような高分子系の有機EL素子EL表示パネルにおいては、インクジェット法やノズルプリント法等の湿式成膜法を適用して有機EL層(正孔輸送層及び電子輸送性発光層)を製造する際に、上記有機材料からなる液状材料が塗布される各画素形成領域(アノード電極)や各表示画素(画素形成領域)間に設けられた隔壁の表面の特性(親液性や撥液性)、上記液状材料の溶媒成分に起因する表面張力や凝集力等の様々な要因により、隣接する画素形成領域に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)が生じたり、画素形成領域内(特にアノード電極上)に形成される有機EL層の膜厚が不均一になったりするという問題を有していた。

【0009】

そのため、有機EL素子の発光動作時における発光開始電圧や有機EL層から放射される光の波長(すなわち、画像表示時の色度)が設計値からずれて、所望の表示画質が得られなくなってしまったり、特に有機EL層の膜厚に薄い領域ができると、そこに発光駆動電流が集中して流れることにより、有機EL層(有機EL素子)の劣化が著しくなり、表示パネルの信頼性や寿命が低下するという問題を有していた。

【0010】

そこで、本発明は、上述した問題点に鑑み、隣接する表示画素間で混色を生じることなく、各表示画素の形成領域の略全域に均一な膜厚を有する担体輸送層が形成された表示パネルを備えた表示装置、及び、当該表示装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

請求項1記載の発明は、

担体輸送層を有する発光素子を含む複数の表示画素を備えた表示装置の製造方法において、

基板上にそれぞれ画素電極が設けられた前記複数の表示画素の形成領域間に隔壁を形成する工程と、

前記画素電極表面を親液化する工程と、

前記隔壁の表面をエッチングする工程と、

前記隔壁の表面を撥液化する工程と、

を含むことを特徴とする。

【0012】

請求項2記載の発明は、請求項1記載の表示装置の製造方法において、前記画素電極表面を親液化する工程は、UVオゾン処理又は酸素プラズマ処理により、少なくとも前記画素電極表面を、前記担体輸送層を形成する担体輸送性材料を含む溶液に対して親液化することを特徴とする。

【0013】

請求項3記載の発明は、請求項1記載の表示装置の製造方法において、前記隔壁の表面をエッチングする工程は、前記画素電極表面を親液化する処理の際に少なくとも前記隔壁の表面に形成された酸化膜を除去することを特徴とする。

請求項4記載の発明は、請求項1記載の表示装置の製造方法において、前記隔壁の表面を撥液化する工程は、トリアジンチオール化合物の溶液に前記基板を浸漬し、少なくとも前記隔壁の表面に前記トリアジンチオール化合物を結合させて、前記担体輸送性材料を含む溶液に対して撥液性を有する被膜を形成することを特徴とする。

【0014】

請求項5記載の発明は、請求項1乃至4のいずれかに記載の表示装置の製造方法において、前記画素電極は、表面が導電性の酸化金属層により形成されていることを特徴とする。

請求項6記載の発明は、請求項1乃至5のいずれかに記載の表示装置の製造方法において、前記隔壁は、少なくとも表面が低抵抗の金属材料により形成されていることを特徴とする。

【0015】

請求項7記載の発明は、請求項1乃至6のいずれかに記載の表示装置の製造方法において、前記表示画素の形成領域は、前記隔壁により画定されることを特徴とする。

請求項8記載の発明は、請求項7記載の表示装置の製造方法において、前記担体輸送層は、前記画素形成領域に露出する前記画素電極上に形成されることを特徴とする。

【0016】

請求項9記載の発明は、請求項1乃至8のいずれかに記載の表示装置の製造方法において、前記親液化された前記画素電極上に、前記担体輸送性材料を含む溶液を塗布、乾燥して、前記担体輸送層を形成する工程と、前記担体輸送層を介して前記複数の表示画素の前記画素電極に共通に対向し、かつ、前記撥液化された前記隔壁上に延在して電気的に接続された単一の対向電極を形成する工程と、をさらに含むことを特徴とする。

請求項10記載の発明に係る表示装置は、請求項1乃至9のいずれかに記載の表示装置の製造方法によって製造されたことを特徴とする。

【発明の効果】

【0017】

本発明に係る表示装置及びその製造方法によれば、隣接する表示画素間で混色を生じることなく、各表示画素の形成領域の略全域にわたり、膜厚の均一性が改善された有機EL層等を含む担体輸送層が形成された表示パネルを実現することができる。

【発明を実施するための最良の形態】

【0018】

以下、本発明に係る表示装置及びその製造方法について、実施の形態を示して詳しく説明する。ここで、以下に示す実施形態においては、表示画素を構成する発光素子として、上述した高分子系の有機材料からなる有機EL層を備えた有機EL素子を適用した場合について説明する。

【0019】

(表示パネル)

まず、本発明に係る表示装置に適用される表示パネル(有機ELパネル)及び表示画素について説明する。

図1は、本発明に係る表示装置に適用される表示パネルの画素配列状態の一例を示す概略平面図であり、図2は、本発明に係る表示装置の表示パネルに2次元配列される各表示画素(表示素子及び画素駆動回路)の回路構成例を示す等価回路図である。なお、図1に示す平面図においては、説明の都合上、表示パネル(絶縁性基板)を視野側から見た、各表示画素(色画素)に設けられる画素電極の配置と各配線層の配設構造との関係のみを示し、各表示画素の有機EL素子(表示素子)を発光駆動するために、各表示画素に設けられる図2に示す画素駆動回路内のトランジスタ等の表示を省略した。また、図1においては、画素電極及び各配線層の配置を明瞭にするために、便宜的にハッチングを施して示した。

【0020】

本発明に係る表示装置(表示パネル)は、図1に示すように、ガラス基板等の絶縁性基板11の一面側に、赤(R)、緑(G)、青(B)の3色からなる色画素PXr、PXg、PXbが図面左右方向に繰り返し複数(3の倍数)配列されるとともに、図面上下方向に同一色の色画素PXr、PXg、PXbが複数配列されている。ここでは、隣接するRGB3色の色画素PXr、PXg、PXbを一組として一の表示画素PIXが形成されている。

【0021】

表示パネル10は、絶縁性基板11の一面側から突出し、柵状又は格子状の平面パターンを有して配設されたバンク(隔壁)形状を有する共通電圧ライン(例えばカソードライン)Lcにより、図面上下方向に配列された同一色の複数の色画素PXr、PXg、又はPXbの画素形成領域からなる各色画素領域が画定される。また、各色画素領域に含まれる複数の色画素PXr、PXg、又はPXbが形成される各画素形成領域には、画素電極(例えばアノード電極)15が形成されているとともに、上記共通電圧ラインLcの配設方向に並行して図面上下方向(すなわち列方向)にデータラインLdが配設され、また、当該データラインLdに直交して図面左右方向(すなわち行方向)に選択ラインLs及び供給電圧ライン(例えばアノードライン)Laが配設されている。

【0022】

表示画素PIXの各色画素PXr、PXg、PXbの具体的な回路構成としては、例えば図2に示すように、絶縁性基板11上に1乃至複数のトランジスタ(例えばアモルファスシリコン薄膜トランジスタ等)からなる画素駆動回路(又は画素回路)DCと、当該画素駆動回路DCにより生成される発光駆動電流が、上記画素電極15に供給されることにより発光動作する有機EL素子(表示素子)OELと、を備えている。

【0023】

供給電圧ラインLaは、例えば所定の高電位電源に直接又は間接的に接続され、各表示画素PIX(色画素PXr、PXg、PXb)に設けられる有機EL素子OELの画素電極15(例えばアノード電極)に表示データ(階調電流Idata)に応じた発光駆動電流が流れるための所定の高電圧(供給電圧Vsc)を印加し、共通電圧ラインLcは、例えば所定の低電位電源に直接又は間接的に接続され、有機EL素子OELの対向電極(例えばカソード電極)に所定の低電圧(共通電圧Vcom;例えば接地電位Vgnd)を印加するように設定されている。

【0024】

画素駆動回路DCは、例えば図2に示すように、ゲート端子が表示パネル10(絶縁性基板11)の行方向に配設された選択ラインLsに、ドレイン端子が上記供給電圧ラインLaに、ソース端子が接点N11に各々接続されたトランジスタTr11と、ゲート端子が選択ラインLsに、ソース端子が表示パネル10の列方向に配設されたデータラインLdに、ドレイン端子が接点N12に各々接続されたトランジスタTr12と、ゲート端子が接点N11に、ドレイン端子が供給電圧ラインLaに、ソース端子が接点N12に各々接続されたトランジスタTr13(発光駆動用のスイッチング素子)と、接点N11及び接点N12間(トランジスタTr13のゲート−ソース間)に接続されたキャパシタCsと、を備えている。ここでは、トランジスタTr11〜Tr13はいずれもnチャネル型の薄膜トランジスタが適用されている。薄膜トランジスタは、アモルファスシリコン薄膜トランジスタであっても、ポリシリコン薄膜トランジスタであってもよい。

【0025】

有機EL素子OELは、アノード端子(アノード電極となる画素電極15)が上記画素駆動回路DCの接点N12に接続され、カソード端子(カソード電極となる対向電極)が表示パネル10の列方向に配設された共通電圧ラインLcに接続されている。また、図2において、キャパシタCsはトランジスタTr13のゲート−ソース間に形成される寄生容量、又は、該ゲート−ソース間に付加的に形成される補助容量である。

【0026】

なお、図2に示した画素駆動回路DCにおいて、選択ラインLsは、図示を省略した選択ドライバに接続され、所定のタイミングで表示パネル10の行方向に配列された複数の表示画素PIX(色画素PXr、PXg、PXb)を選択状態に設定するための選択信号Sselが選択ドライバから印加される。また、供給電圧ラインLaは、図示を省略した電源ドライバに接続され、上記選択信号Sselと同期したタイミングで同じ行に配列された表示画素PIXに所定の供給電圧Vscが電源ドライバから印加される。データラインLdは、図示を省略したデータドライバに接続され、上記表示画素PIXの選択状態に同期するタイミングで表示データに応じた階調電流Idataが流れる。

【0027】

そして、このような回路構成を有する画素駆動回路DCを備えた表示画素PIX(表示パネル10)における駆動制御動作は、まず、書込動作期間において、図示を省略した選択ドライバから選択ラインLsに対して、選択レベル(オンレベル;例えばハイレベル)の選択信号Sselを印加するとともに、該選択信号Sselに同期して図示を省略した電源ドライバからローレベルの供給電圧Vscを供給電圧ライン(アノードライン)Laに対して印加する。

【0028】

このタイミングに同期して、図示を省略したデータドライバは、表示データに応じた電流値を有する階調電流IdataがデータラインLdに流れるように制御する。つまり、データドライバは、表示データに応じた階調電流Idataの電流値を制御するドライバであり、本実施形態においては、書込動作期間中において固定されたローレベルの電圧である供給電圧Vscに対してデータドライバがデータラインLdの電位を低くして、表示画素PIX(画素駆動回路DC)側からデータラインLd方向に所望の電流値の階調電流Idataを引き抜くように流すものとする。

【0029】

これにより、画素駆動回路DCのトランジスタTr11及びTr12がオン動作して、ローレベルの供給電圧Vscが接点N11(トランジスタTr13のゲート端子;キャパシタCsの一端側)に印加されるとともに、階調電流Idataの引き込み動作によりトランジスタTr12を介してローレベルの供給電圧Vscよりも低電位の電圧レベルが接点N12(トランジスタTr13のソース端子;キャパシタCsの他端側)に印加され、トランジスタTr13にはデータドライバで設定された階調電流Idataが強制的に流されることになる。

【0030】

このとき、キャパシタCsには、接点N11及びN12間に生じた電位差に対応する電荷が蓄積され、電圧成分として保持される(充電される)。この蓄積された電荷の量は、書込動作時にトランジスタTr13のドレイン−ソース間を流れる階調電流Idataの電流値によって自動的に設定される。また、このとき、ローレベルの供給電圧Vscは、共通電圧ライン(カソードライン)Lcを介してカソード端子に印加される共通電位Vcom(接地電位Vgnd)以下に設定されているので、有機EL素子OELには、順バイアス電圧が印加されないため、書込動作時に有機EL素子OELには発光駆動電流が流れず、発光動作は行われない。

【0031】

次いで、発光動作期間においては、選択ドライバから選択ラインLsに対して、非選択レベル(オフレベル;例えばローレベル)の選択信号Sselを印加するとともに、電源ドライバから供給電圧ラインLaに対して、ハイレベルの供給電圧Vscを印加する。また、このタイミングに同期して、データドライバによる階調電流Idataの引き抜き動作を停止する。

【0032】

これにより、トランジスタTr11及びTr12がオフ動作して、接点N11への供給電圧Vscの印加が遮断されるとともに、接点N12への階調電流Idataの引き込み動作に起因する電圧レベルの印加が遮断されるので、キャパシタCsは、上述した書込動作において蓄積された電荷を保持する。

【0033】

このように、キャパシタCsが書込動作時に蓄積された電荷(充電電圧)を保持することにより、接点N11及びN12間(トランジスタTr13のゲート−ソース間)の電位差が保持されることになり、トランジスタTr13が階調電流Idataの電流値に応じた電流値の電流を流すことができるような状態を維持する。また、供給電圧ラインLaには、共通電圧Vcom(接地電位Vgnd)よりも高い電圧レベルで、且つ、発光動作期間にトランジスタTr13を流れる電流が飽和電流となるようにドレイン−ソース間電位差が十分高くなるような所定の電圧値の供給電圧Vscが印加されると、トランジスタTr13は、書込動作時に蓄積された電荷によるゲート−ソース間電位差によって、書込動作時に流れる階調電流Idataの電流値に応じた発光駆動電流を有機EL素子OELに順バイアス方向に流し、有機EL素子OELは、階調電流Idataひいては表示データにしたがった輝度で発光動作する。

【0034】

そして、このような一連の駆動制御動作を、表示パネル10に2次元配列された全ての表示画素PIX(各色画素PXr、PXg、PXb)について、例えば各行ごとに順次繰り返し実行することにより、所望の画像情報を表示する画像表示動作を実行することができる。

【0035】

(表示画素のデバイス構造)

次いで、上述したような回路構成を有する表示画素(発光駆動回路及び有機EL素子)の具体的なデバイス構造(平面レイアウト及び断面構造)について説明する。

図3は、本実施形態に係る表示装置(表示パネル)に適用可能な表示画素の一例を示す平面レイアウト図であり、図4は、本実施形態に係る表示画素の平面レイアウトの要部詳細図である。ここでは、図1に示した表示画素PIXの赤(R)、緑(G)、青(B)の各色画素PXr、PXg、PXbのうちの、特定の一の色画素の平面レイアウトを示す。なお、図3においては、画素駆動回路DCの各トランジスタ及び配線層等が形成された層を中心に示し、図4においては、図3に示した平面レイアウトのうち、共通電圧ラインLcの下層に形成される各トランジスタ及び配線層等を具体的に示す。また、図4において、括弧数字は、各導電層(配線層を含む)の上下の順を表し、数字が小さいほど下層側(絶縁性基板11側)に形成され、大きいほど上層側(視野側)に形成されていることを示す。また、図5、図6は、各々、図3に示した平面レイアウトを有する表示画素PIXにおけるA−A断面及びB−B断面を示す概略断面図である。

【0036】

図2に示した表示画素PIX(色画素PXr、PXg、PXb)は、具体的には、絶縁性基板11の一面側に設定された画素形成領域(各色画素PXr、PXg、PXbの形成領域)Rpxにおいて、図3に示した平面レイアウトの上方及び下方の縁辺領域に行方向(図面左右方向)に延在するように選択ラインLs及び供給電圧ラインLaが各々配設されるとともに、これらのラインLs、Laに直交するように、上記平面レイアウトの左方及び右方の縁辺領域に列方向(図面上下方向)に延在するようにデータラインLd及び共通電圧ラインLcが各々配設されている。

【0037】

ここで、図3〜図6に示すように、供給電圧ラインLaは、共通電圧ラインLcよりも下層側(絶縁性基板11側)に設けられ、選択ラインLs及び供給電圧ラインLaは、同層に設けられ、データラインLdは、選択ラインLs及び供給電圧ラインLaよりも下層側に設けられている。ここで、選択ラインLsは、トランジスタTr11〜Tr13のソース、ドレインを形成するためのソース、ドレインメタル層をパターニングすることによってソース、ドレインと同じ工程で形成される。また、データラインLdは、トランジスタTr11〜Tr13のゲートを形成するためのゲートメタル層をパターニングすることによってゲートと同じ工程で形成される。

【0038】

すなわち、表示画素PIXは、図5、図6に示すように、絶縁性基板11上に表示画素PIX内に設けられる画素駆動回路DC(図2参照)の複数のトランジスタTr11〜Tr13やキャパシタCs、及び、選択ラインLsやデータラインLdを含む各種配線層が設けられ、当該トランジスタTr11〜Tr13及び配線層を被覆するように順次形成された保護絶縁膜13及び平坦化膜14を介して、その上層に、画素駆動回路DCに接続されて所定の発光駆動電流が供給される画素電極(例えばアノード電極)15、正孔輸送層16a(担体輸送層)と電子輸送性発光層16b(担体輸送層)からなる有機EL層(発光機能層)16、及び、共通電圧Vcomが印加される対向電極(例えばカソード電極)17からなる有機EL素子OELが形成されている。

【0039】

画素駆動回路DCは、より具体的には、図3、図4に示すように、図2に示したトランジスタTr11が行方向に配設された選択ラインLsに沿って延在するように配置され、トランジスタTr12が列方向に配設されたデータラインLdに沿って延在するように配置され、トランジスタTr13が列方向に配設された共通電圧ラインLcに沿って延在するように配置されている。

【0040】

ここで、各トランジスタTr11〜Tr13は、周知の電界効果型トランジスタ構造を有し、各々、絶縁性基板11上に形成されたゲート電極Tr11g〜Tr13gと、ゲート絶縁膜12を介して各ゲート電極Tr11g〜Tr13gに対応する領域に形成された半導体層SMCと、該半導体層SMCの両端部に延在するように形成されたソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13dと、を有している。

【0041】

なお、各トランジスタTr11〜Tr13のソース電極とドレイン電極が対向する半導体層SMC上には当該半導体層SMCへのエッチングダメージを防止するための酸化シリコン又は窒化シリコン等のブロック層BLが形成され、また、ソース電極とドレイン電極が接触する半導体層SMC上には、当該半導体層SMCとソース電極及びドレイン電極とのオーミック接続を実現するための不純物層OHMが形成されている。トランジスタTr11〜Tr13のゲート電極Tr11g〜Tr13gはいずれも同一のゲートメタル層をパターニングすることによって形成されている。トランジスタTr11〜Tr13のソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13dはいずれも同一のソース、ドレインメタル層をパターニングすることによって形成されている。

【0042】

そして、図2に示した画素駆動回路DCの回路構成に対応するように、トランジスタTr11は、図3、図4に示すように、ゲート電極Tr11gがゲート絶縁膜12に設けられたコンタクトホールHLaを介して選択ラインLsに接続され、同ソース電極Tr11sがゲート絶縁膜12に設けられたコンタクトホールHLbを介してキャパシタCsの一端側(接点N11側)の電極Ecaに接続され、同ドレイン電極Tr11dが供給電圧ラインLaと一体的に形成されている。

【0043】

また、トランジスタTr12は、図3〜図5に示すように、ゲート電極Tr12gがゲート絶縁膜12に設けられたコンタクトホールHLaを介して選択ラインLsに接続され、同ソース電極Tr12sがゲート絶縁膜12に設けられたコンタクトホールHLcを介してデータラインLdに接続され、同ドレイン電極Tr12dがキャパシタCsの他端側(接点N12側)の電極Ecbと一体的に形成されている。

【0044】

トランジスタTr13は、図3〜図5に示すように、ゲート電極Tr13gがキャパシタCsの一端側(接点N11側)の電極Ecaと一体的に形成され、同ソース電極Tr13sがキャパシタCsの他端側(接点N12側)の電極Ecbと一体的に形成され、同ドレイン電極Tr13dが供給電圧ラインLaと一体的に形成されている。

【0045】

また、キャパシタCsは、トランジスタTr13のゲート電極Tr13gと一体的に形成された一端側の電極Ecaと、ソース電極Tr13sと一体的に形成された他端側の電極Ecbと、がゲート絶縁膜12を介して対向して延在するように形成されている。

選択ラインLsは、図3、図4、図6に示すように、ゲート絶縁膜12上に延在し、供給電圧ライン(アノードライン)Laと同一層に形成されている。

【0046】

さらに、トランジスタTr13のソース電極Tr13s(キャパシタCsの電極Ecb)上の保護絶縁膜13及び平坦化膜14には、図5に示すように、コンタクトホールHLdが形成され、当該ソース電極Tr13sと有機EL素子OELの画素電極15とが電気的に接続されるように、金属材料(コンタクトメタルMTL)が埋め込まれている。

【0047】

そして、各画素形成領域Rpxの平坦化膜14上には、図5、図6に示すように、例えばアノード電極となる画素電極15、正孔輸送層16a及び電子輸送性発光層16bからなる有機EL層16、及び、例えばカソード電極となる対向電極17を順次積層した有機EL素子が設けられている。ここで、本実施形態においては、有機EL層16において発光した光を、絶縁性基板11と反対側に(後述する封止樹脂層19及び封止基板20を介して)出射するトップエミッション型の発光構造を有している表示パネル(有機ELパネル)について示す。そのため、画素電極15が少なくとも光反射特性を有し、対向電極17が光透過性を有することになる。ここで、画素電極15は、後述する製造方法(図7〜図10参照)において説明するように、下層側の反射金属層15aと上層側の透明な導電性酸化金属層15bからなる積層構造を有している。

【0048】

また、列方向の各画素形成領域Rpx間(各表示画素PIXの有機EL素子OELの形成領域相互の境界領域)には、有機EL素子OELの形成領域(厳密には、有機EL層16の形成領域)を画定するためのバンク(隔壁)18が平坦化膜14の上面から突出するように設けられている。ここで、本実施形態においては、当該バンク18は、例えば図5に示すように、列方向に延在し、各画素形成領域Rpx間の層間絶縁膜としての機能も果たす下層側の下地層18xと、導電性材料からなり、共通電圧ライン(カソードライン)Lcの列方向に延在する部分である上層側のバンクメタル層18aからなる積層構造を有している。

【0049】

バンク18は、より具体的には、行方向に沿って隣接する表示画素PIX間の境界領域付近に露出する平坦化膜14上から、有機EL素子OELの画素電極15の列方向の周縁上に一部が重なるシリコン窒化膜(SiN)等からなる下地層18xが列方向に延在するように設けられ、当該下地層18x上に、導電性材料(例えば、金属材料)からなるバンクメタル層18aが厚さ方向に突出し且つ列方向に延在するように順次積層形成されている。列方向に沿った複数の下地層18x及びバンクメタル層18aの各端は、図1に示すように、複数の表示画素PIXの画素形成領域の外側において行方向に沿って連結されている。

【0050】

すなわち、上記積層構造を有するバンク18を表示パネル10(絶縁性基板11)上に柵状の平面パターンを有するように配設することにより、列方向(図面上下方向)に配列された複数の表示画素PIXをそれぞれ有する複数のストライプ状の画素形成領域が画定されるとともに、バンク18のバンクメタル層18aにより、表示パネル10の全域に配列された表示画素PIX(有機EL素子OEL)の各々に所定の電圧(共通電圧Vcom)を共通に印加することができる配線層(共通電圧ラインLc)として機能させることができる。

【0051】

すなわち、図5、図6に示すように、有機EL素子OELの対向電極(カソード電極)17を、バンクメタル層18aを備えたバンク18上に延在し且つ、バンクメタル層18aに電気的に接続されるように形成することにより、バンク18(バンクメタル層18a)を共通電圧ラインLcとして兼用することができる。

なお、上記画素駆動回路DC、有機EL素子OEL及びバンク18が形成された絶縁性基板11上には、図5、図6に示すように、透明な封止樹脂層19を介して、絶縁性基板11に対向するようにガラス基板等からなる封止基板20が接合されている。

【0052】

そして、このような表示パネル10においては、例えば、表示パネル10の下層(有機EL素子OELの絶縁性基板11側の層)に設けられたトランジスタTr11〜Tr13やキャパシタCs等の機能素子、選択ラインLsやデータラインLd、供給電圧ライン(アノードライン)La等の配線層からなる画素駆動回路DCにおいて、データラインLdを介して供給された表示データに応じた階調電流Idataに基づいて、所定の電流値を有する発光駆動電流がトランジスタTr13のドレイン−ソース間に流れ、当該トランジスタTr13(ソース電極Tr13s)からコンタクトホールHLd(コンタクトメタルMTL)を介して、有機EL素子OELの画素電極15に供給されることにより、各表示画素PIX(各色画素PXr、PXg、PXb)の有機EL素子OELが上記表示データに応じた所望の輝度階調で発光動作する。

【0053】

このとき、本実施形態に示した表示パネル10において、画素電極15が光反射特性を有し、対向電極17が光透過性を有する場合(すなわち、有機EL素子OELがトップエミッション型である場合)、各表示画素PIX(各色画素PXr、PXg、PXb)の有機EL層16において発光した光は、光透過性を有する対向電極17を介して直接、あるいは、光反射特性を有する画素電極15で反射して、絶縁性基板11(表示パネル)を介することなく封止基板20の一面側(図5、図6の図面上方)に出射される。

【0054】

なお、本実施形態においては、トップエミッション型の発光構造を有する表示素子(有機EL素子)について説明したが、本発明はこれに限定されるものではなく、光透過性を有する画素電極15、及び、光反射特性を有する対向電極17を適用して、有機EL層16において発光した光が、光透過性を有する画素電極15を介して直接、あるいは、光反射特性を有する対向電極17で反射して、絶縁性基板11(表示パネル)を介して他面側(図5、図6の図面下方)に出射されるボトムエミッション型の発光構造を有する表示素子を適用するものであってもよい。

【0055】

(表示装置の製造方法)

次に、上述した表示装置(表示パネル)の製造方法について説明する。

図7乃至図10は、本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図である。ここでは、図5に示したA−A断面から見たパネル構造の製造工程について説明する。また、図11は、本実施形態に係る表示装置(表示パネル)に形成されるバンク表面の被膜材料の化学構造式及び被膜材料がバンクメタル層18aに被膜した状態での結合を示す概念図である。

【0056】

上述した表示装置(表示パネル)の製造方法は、まず、図7(a)に示すように、ガラス基板等の絶縁性基板11の一面側(図面上面側)に設定された表示画素PIX(各色画素PXr、PXg、PXb)の形成領域(画素形成領域)Rpxに、上述した画素駆動回路(図2〜図4参照)DCのトランジスタTr11〜Tr13やキャパシタCs、データラインLdや選択ラインLs等の配線層を形成する(図5、図6参照)。

【0057】

具体的には、絶縁性基板11上に、ゲート電極Tr11g〜Tr13g、及び、ゲート電極Tr13gと一体的に形成されるキャパシタCsの一方側の電極Eca、データラインLd(図5参照)を同一のゲートメタル層をパターニングすることによって同時に形成し、その後、絶縁性基板11の全域にゲート絶縁膜12を被覆形成する。

【0058】

次いで、ゲート絶縁膜12上の各ゲート電極Tr11g〜Tr13gに対応する領域に、例えばアモルファスシリコンやポリシリコン等からなる半導体層SMCを形成し、当該半導体層SMC上に設けられたブロック層BLの両側に半導体層SMCとオーミック接続のための不純物層OHMを介してソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13dを形成する。このとき、同一のソース、ドレインメタル層をパターニングすることによってソース電極Tr13s及びドレイン電極Tr12dと接続されたキャパシタCsの他方側の電極Ecb、選択ラインLs、並びに、ドレイン電極Tr11d及びTr13dと接続された供給電圧ラインLa(図6参照)を同時に形成する。

【0059】

なお、上述したトランジスタTr11〜Tr13のソース電極Tr11s〜Tr13s及びドレイン電極Tr11d〜Tr13d、キャパシタCsの他端側の電極Ecb、選択ラインLs、供給電圧ラインLaは、配線抵抗を低減し、かつ、マイグレーションを低減する目的で、例えばアルミニウム合金層と遷移金属層からなる積層配線構造を有しているものであってもよい。また、トランジスタTr11〜Tr13は、逆スタガ型に限らずコプラナ型等であってもよい。

【0060】

次いで、図7(b)に示すように、上記トランジスタTr11〜Tr13、キャパシタCs、選択ラインLs及び供給電圧ラインLaを含む絶縁性基板11の一面側全域を被覆するように、50nm〜100nm厚の窒化シリコン(SiN)等からなる保護絶縁膜(パッシベーション膜)13及び1μm〜10μm厚の感光性有機樹脂材料等からなる平坦化膜14を順次形成した後、平坦化膜14及び保護絶縁膜13を光の照射及びエッチャントによりパターニングして、トランジスタTr13のソース電極Tr13s(又は、キャパシタCsの他方側の電極Ecb)の上面が露出するコンタクトホールHLdを形成する。

【0061】

次いで、図7(c)に示すように、上記コンタクトホールHLdに金属材料からなるコンタクトメタルMTLを埋め込む。ここで、コンタクトメタルMTLは、例えば無電解めっき法等を用いて、銅(Cu)等の金属材料を堆積して形成される厚膜を適用することができる。その後、図8(a)に示すように、各画素形成領域Rpx(各色画素PXr、PXg、PXbの形成領域)ごとに、当該コンタクトメタルMTLに電気的に接続された画素電極15を形成する。

【0062】

画素電極15は、具体的には、アルミニウム(Al)、クロム(Cr)、銀(Ag)、パラジウム銀(AgPd)系の少なくとも何れかを含む金属または合金等からなる光反射特性を有する反射金属膜をスパッタリング法等を用いて薄膜形成し、所定の形状にパターニングすることによりコンタクトメタルMTLに電気的に接続された下層の反射金属層15aを形成する。その後、当該反射金属層15aを含む絶縁性基板11の一面側全域を被覆するように、錫ドープ酸化インジウム(Indium Thin Oxide;ITO)や亜鉛ドープ酸化インジウム等の透明電極材料からなる(光透過特性を有する)酸化金属膜を薄膜形成し、上記反射金属層15aの上面や端面が露出しないようにパターニングすることにより上層の導電性酸化金属層15bを形成する。

【0063】

このように、上層の酸化金属膜をパターニングする際に、下層側の反射金属層15aが露出しないようにすることにより、酸化金属膜と反射金属層15aとの間でエッチャントによる電池反応を引き起こさないようにすることができるとともに、下層側の反射金属層15aがオーバーエッチングされたり、エッチングダメージを受けたりすることを防止することができる。

【0064】

次いで、反射金属層15a及び導電性酸化金属層15bからなる上記画素電極15を含む絶縁性基板11の一面側全域を被覆するように、化学気相成長法(CVD法)等を用いて、例えばシリコン酸化膜やシリコン窒化膜等の無機の絶縁性材料からなる絶縁層を形成した後パターニングすることにより、図8(b)に示すように、行方向に沿って互いに隣接する表示画素PIXに形成された画素電極15との間の領域(隣接する表示画素PIXとの境界領域)において、列方向に沿うように、後述するバンク18の最下層となる下地層18xを形成する。下地層18xは、図1において、供給電圧ラインLcと略同一形状であり、表示画素PIXの画素形成領域が複数のストライプ形状に開口されるように形成されている。

【0065】

次いで、図9(a)に示すように、下地層18x上に、例えば銅(Cu)や銀(Ag)、アルミニウム(Al)、又は、これらを主成分とした金属単体又は合金等の低抵抗の非酸化金属材料からなるバンクメタル層18a(供給電圧ラインLc)を、表示画素PIXの画素形成領域が複数のストライプ形状に開口されるように形成する。バンクメタル層18aは表面が非酸化金属材料であれば、内部が非酸化金属材料以外の材料を含んでいてもよい。

【0066】

具体的には、上記下地層18xを含む絶縁性基板11の一面側全域を被覆するように、例えばスパッタ法や真空蒸着法等を用いて上記金属材料の薄膜を形成し、フォトリソグラフィー技術を用いて下地層18x上に所定のパターンを有して残留させることによりバンクメタル層18aを形成する。バンクメタル層18aは、列方向に延在している部分において、行方向の両側部から下地層18xが露出するように行方向の幅が下地層18xよりも幅狭に形成されている。下地層18xは、平坦化膜14とバンクメタル層18aとの間の密着性を改善するために介在された層であり、その熱膨張係数は、平坦化膜14の熱膨張係数とバンクメタル層18aの熱膨張係数との間であることが好ましい。

【0067】

これにより、図1に示すように、表示パネル10の列方向に配列された同一色の複数の表示画素PIXの画素形成領域(有機EL素子OELの有機EL層16の形成領域)Rpxがバンクメタル層18a及び下地層18xからなるバンク18により周囲を囲まれて画定され、当該画素形成領域Rpxごとに画素電極15(導電性酸化金属層15b)の上面が露出した状態となる。

【0068】

次いで、絶縁性基板11を純水で洗浄した後、UVオゾン処理や酸素プラズマ処理等を施すことにより、上記バンク18により画定された各画素形成領域Rpxに露出する画素電極15表面(及び、画素電極15の周辺領域に露出する下地層18x表面を含むものであってもよい)の親液化を行う。親液化処理の際にバンクメタル層18aの表面の一部は酸化されてしまい、このままでは、バンクメタル層18aの表面に後述する撥液化処理を行うことができないため、バンクメタル層18aの表面の酸化膜を除去する。次いで、酸化膜が除去されたバンクメタル層18aの表面に選択的に撥液化処理を施す。

【0069】

ここで、画素電極15の親液化処理の一例であるUVオゾン処理においては、酸素ガス雰囲気中で絶縁性基板11に対して紫外光を照射することにより、活性酸素ラジカルを発生させて、画素電極15(ITO等からなる導電性酸化金属層)の表面を、後述する正孔輸送層となる正孔輸送材料を含有する有機化合物含有液や電子輸送性発光層となる電子輸送性発光材料を含有する有機化合物含有液、もしくは、これらの溶液に用いる有機溶媒に対して濡れ性が向上するように親液化(親水化)する。

【0070】

また、酸化膜除去処理は、上述したバンク18が一面側に形成された絶縁性基板11を過硫酸アンモニウム等の酸系の水溶液に浸漬することにより、バンクメタル層18aの表面をソフトエッチングして表面の酸化膜を除去した後、純水で洗浄し、乾燥させる。次いで行われるバンクメタル層18aの撥液化処理は、具体的には、絶縁性基板11をトリアジントリチオール又は官能基にフッ素を含むフッ素系トリアジンジチオール誘導体等のトリアジンチオール化合物の撥液処理溶液の処理槽内に挿入して浸漬する。この処理工程における撥液処理溶液の温度は概ね20〜30℃程度、浸漬時間は概ね数十秒〜10分程度に設定する。その後、絶縁性基板11を撥液処理溶液から取り出し、アルコール等により濯いで絶縁性基板11表面に残留する撥液処理溶液(トリアジンチオール化合物)を洗い流し、絶縁性基板11を純水で2次洗浄した後、窒素ガス(N2)のブローにより乾燥させる。

【0071】

このとき、トリアジンチオール化合物は、酸化膜除去処理で酸化膜が除去されたバンクメタル層18a表面の金属と選択的に結合して被膜が形成されることになるが、画素電極15表面の金属酸化物(導電性酸化金属層15b)や、下地層18xを形成する無機絶縁膜には撥液性を発現する程度には被膜されない。

【0072】

すなわち、トリアジンチオール化合物の一例として適用可能なフッ素系トリアジンジチオール誘導体は、図11(a)に示すように、トリアジン(3個の窒素を含む六員環構造)の窒素(−N)にチオール基(−SH)が結合した分子構造に加え、特定のチオール基(−SH)のS原子にアルキル基(−CH2−CH2−)及びフッ化アルキル基(−CF2−CF2−CF2−CF3)が順次結合した分子構造を有し、他のトリアジンチオール化合物と同様に、図11(b)に示すように、それ自体が撥液性を示すトリアジントリチオールに加えてさらに撥液性を示すフッ素原子を含んでいるので、バンクメタル層18aの表面に形成される被膜は、トリアジントリチオールよりも強い撥液性を示す。なお、上述した処理工程において使用する撥液処理溶液の濃度は、概ね1×10−4〜1×10−2mol/Lの範囲が好ましい。

【0073】

なお、上記フッ素系トリアジンジチオール誘導体は、チオール基のS原子がアルキル基(−CH2−CH2−)と結合した分子構造を有しているが、直接フッ化アルキル基と結合してもよく、またトリアジンチオール化合物がバンクメタル層18aに被覆される際に著しい立体障害にならない限りアルキル基、フッ化アルキル基の炭素数に特別な制限はない。また、上記フッ素系トリアジンジチオール誘導体は、残る二つのチオール基の一つのS原子において、水素基に代わって直接又は間接的にフッ化アルキル基が置換形成されていてもよく、或いはフッ素原子を含む基の炭素間がオレフィン二重結合を有していてもよい。また、その他のトリアジンチオール誘導体として、例えば、6−ジメチルアミノ−1,3,5−トリアジン−2,4−ジチオール−ナトリウム塩或いは6−ジドデシルアミノ−1,3,5−トリアジン−2,4−ジチオール−ナトリウム塩を用い、水に溶解して被膜18cを被膜してもよい。

【0074】

これにより、絶縁性基板11の一面側に形成された各構成のうち、親液化処理によって形成された酸化膜を酸化膜除去処理によって除去された、金属材料からなるバンクメタル層18aの表面では、トリアジンチオール化合物との結合性が著しく向上しているので、撥液性を十分に示す程度にトリアジンチオール化合物の被膜が形成され、一方、酸化金属層(ITO等)15bにより被覆された画素電極15の表面及び下地層18xの表面、画素電極15間から露出した平坦化膜14(或いは保護絶縁膜13)には付着しにくく、被膜がほとんど形成されない。したがって、同一の絶縁性基板11上において、バンクメタル層18aの表面のみが撥液化処理され、当該バンク18により画定された各画素形成領域Rpxに露出する画素電極15表面は撥液化処理されていない状態(親液性が保持された状態)が実現される。

【0075】

なお、本実施形態において使用する「撥液性」とは、後述する正孔輸送層となる正孔輸送材料を含有する有機化合物含有液や、電子輸送性発光層となる電子輸送性発光材料を含有する有機化合物含有液、もしくは、これらの溶液に用いる有機溶媒を、絶縁性基板上等に滴下して、接触角の測定を行った場合に、当該接触角が50°以上になる状態と規定する。また、「撥液性」に対する「親液性」とは、本実施形態においては、上記接触角が40°以下になる状態と規定する。

【0076】

また、表示パネル10の列方向に配列された同一色の各表示画素PIX(有機EL素子OEL)の画素形成領域Rpxが、撥液化処理されたバンク18により、隣接する他の色の表示画素PIX(有機EL素子OEL)の画素形成領域Rpxと隔離されるので、後述する有機EL層16となる発光層(電子輸送性発光層16b)を形成する際に、当該発光材料の溶液又は分散液(液状材料)を塗布する場合であっても、バンク18を越えて隣接する表示画素PIX(色画素PXr、PXg、PXb)に発光材料が混合することがなく、隣接する色画素相互での混色を防止することができる。

【0077】

次いで、図9(b)に示すように、上記バンク18により囲まれた(画定された)各色の画素形成領域(有機EL素子OELの形成領域)Rpxに対して、互いに分離した複数の液滴を所定位置に吐出するインクジェット法、又は、溶液を連続的に流し込むノズルプリント法等を適用して同一工程で、正孔輸送材料の溶液又は分散液を塗布した後、加熱乾燥により残留溶媒を除去し正孔輸送層16aを形成する。続いて、図10(a)に示すように、当該正孔輸送層16a上に電子輸送性発光材料の溶液又は分散液を塗布した後、加熱乾燥により残留溶媒を除去し電子輸送性発光層16bを形成する。これにより、画素電極15上に正孔輸送層16a及び電子輸送性発光層16bからなる有機EL層(発光機能層)16が積層形成される。

【0078】

具体的には、有機高分子系の正孔輸送材料(担体輸送性材料)を含む有機化合物含有液として、例えばポリエチレンジオキシチオフェン/ポリスチレンスルホン酸水溶液(PEDOT/PSS;導電性ポリマーであるポリエチレンジオキシチオフェンPEDOTと、ドーパントであるポリスチレンスルホン酸PSSを水系溶媒に分散させた分散液)を、上記画素電極15(導電性酸化金属層15b)上に塗布した後、塗布された基板11を載置するステージ及び/又はステージ上の雰囲気を100℃以上の温度条件で加熱乾燥処理を行って残留溶媒を除去することにより、当該画素電極15上に有機高分子系の正孔輸送材料を定着させて、担体輸送層である正孔輸送層16aを形成する。

【0079】

ここで、画素電極15及びその周辺の下地層18xの表面は、上記有機化合物含有液(PEDOT/PSS)に対して親液性を有しているので、バンク18により画定された画素形成領域Rpxに塗布された有機化合物含有液は当該領域内(画素電極15上)に充分馴染んで均等に広がる。

【0080】

これにより、後述するように、有機化合物含有液を加熱乾燥処理する際に、当該有機化合物含有液が縁辺領域方向に引っ張られながら乾燥するので、正孔輸送層16aが画素電極15の中央表面上で盛り上がりすぎることがないため、膜厚の均一性が向上する。また、バンクメタル層18aの表面は、上記有機化合物含有液(PEDOT/PSS)に対して撥液性を有しているので、隣接する画素形成領域への有機化合物含有液の漏出や乗り越えを防止することができる。

【0081】

また、有機高分子系の電子輸送性発光材料(担体輸送性材料)を含む有機化合物含有液として、例えばポリパラフェニレンビニレン系やポリフルオレン系等の共役二重結合ポリマーを含む発光材料を、水や或いはテトラリン、テトラメチルベンゼン、メシチレン、キシレン等の有機溶媒に溶解した溶液を、上記正孔輸送層16a上に塗布した後、窒素雰囲気中でステージを加熱或いは1Torr以下の減圧雰囲気下でステージ上の雰囲気を加熱して乾燥処理を行って溶媒を除去することにより、正孔輸送層16a上に有機高分子系の電子輸送性発光材料を定着させて、担体輸送層であり発光層でもある電子輸送性発光層16bを形成する。

【0082】

この場合においても、上述した正孔輸送層16aと同様に、画素電極15上の正孔輸送層16a及びその周辺の下地層18xの表面は、上記有機化合物含有液に対して親液性を有しているので、バンク18により画定された画素形成領域Rpxに塗布された有機化合物含有液は当該領域内(正孔輸送層16a上)に充分馴染んで均等に広がる。

【0083】

これにより、後述するように、有機化合物含有液を加熱乾燥処理する際に、当該有機化合物含有液が縁辺領域方向に引っ張られながら乾燥するので、正孔輸送層16a上に形成される電子輸送性発光層16bの膜厚の均一性が向上する。また、バンクメタル層18aの表面は、上記有機化合物含有液に対して撥液性を有しているので、隣接する画素形成領域への有機化合物含有液の漏出や乗り越えを防止することができる。

【0084】

その後、図10(b)に示すように、少なくとも各画素形成領域Rpxを含む絶縁性基板11上に光透過性を有する導電層(透明電極層)を形成し、上記有機EL層16(正孔輸送層16a及び電子輸送性発光層16b)を介して各画素電極15に対向する共通の対向電極(例えばカソード電極)17を形成する。ここで、対向電極17は、例えば真空蒸着法やスパッタリング法等により電子注入層となるカルシウム(Ca)やバリウム(Ba)、マグネシウム、フッ化リチウム等の金属材料からなる薄膜を形成した後、その上層にスパッタ法等によりITO等の透明電極層を積層形成した、厚さ方向に透明な膜構造を適用することができる。

【0085】

また、対向電極17は、上記画素電極15に対向する領域のみならず、各画素形成領域Rpx(有機EL素子OELの形成領域)を画定するバンク18上にまで延在する単一の導電層として形成されるとともに、バンク18を形成するバンクメタル層18aと電気的に接続されるように接合される。これにより、バンク18を形成するバンクメタル層18aを各表示画素PIXに共通に接続された共通電圧ライン(カソードライン)Lcとして適用することができる。このように、各表示画素PIX(有機EL素子OEL)間に対向電極17と等電位のバンクメタル層18aを網羅することによってカソード全体のシート抵抗を下げ、表示パネル10全体で均一な表示特性にすることができる。

【0086】

次いで、上記対向電極17を形成した後、絶縁性基板11の一面側全域に保護絶縁膜(パッシベーション膜)としてシリコン酸化膜やシリコン窒化膜等からなる封止層19をCVD法等を用いて形成し、さらに、UV硬化又は熱硬化接着剤を用いて、封止蓋や封止基板20を接合する(貼り合わせる)ことにより、図5、図6に示したような断面構造を有する表示パネル10が完成する。

【0087】

なお、上述した実施形態においては、有機EL層16が正孔輸送層16a及び電子輸送性発光層16bからなる場合について説明したが、本発明はこれに限定されるものではなく、例えば正孔輸送兼電子輸送性発光層のみでもよく、正孔輸送性発光層及び電子輸送層でもよく、また、間に適宜担体輸送層が介在してもよく、その他の担体輸送層の組合せであってもよい。

また、上記実施形態では、画素電極15をアノードとしたが、これに限らずカソードとしてもよい。このとき、有機EL層16は、画素電極15に接する担体輸送層が電子輸送性の層であればよい。

【0088】

(比較検証)

次に、上述した本発明に係る表示装置の製造方法に特有の作用効果について、具体的に検証する。

図12は、UVオゾン処理における紫外光の照射時間と純水接触角との関係を示す実験データであり、図13は、親液化処理後のソフトエッチングの処理時間と撥液化処理後の純水接触角との関係を示す実験データである。ここで、図12(a)及び図13(a)は、各実験により得られた数値データの表であり、図12(b)及び図13(b)は、図12(a)及び図13(a)に示した数値データをグラフ化したものである。

【0089】

上述した実施形態においては、一面側に突出して配設されたバンク18により、各表示画素PIX(有機EL素子OEL)の画素形成領域Rpxが画定された絶縁性基板11において、UVオゾン処理等により親液化処理した後、過硫酸アンモニウム等の酸系の水溶液に浸漬してバンク18の表面にソフトエッチングを施し、その後、トリアジンチオール化合物等の撥液処理溶液に浸漬してバンク表面にトリアジンチオール化合物の被膜を形成し、撥液化することにより、絶縁性基板11上に親液性を示す領域(画素電極表面)と、撥液性を示す領域(バンク表面)とを共存させた親疎水パターンを形成する製造方法を示した。

【0090】

ここで、絶縁性基板上に親疎水パターンを形成する方法としては、上述した実施形態に示した製造方法の他に、例えば撥液処理溶液に絶縁性基板を浸漬してバンク表面を撥液化した後、UVオゾン処理や酸素プラズマ処理等により各画素形成領域に露出する画素電極(導電性酸化金属層)表面を親液化する手法(以下、便宜的に「第1の比較例」と記す)が考えられる。

【0091】

このような製造方法においては、先の工程において撥液化したバンク表面に形成された撥液性の被膜(トリアジンチオール化合物の被膜)が、親液化処理の際のUVオゾン処理や酸素プラズマ処理により分解されて、バンク表面の撥液性が低下してしまい、有機化合物含有液を塗布する際に、隣接する画素形成領域(有機EL素子)に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)が生じたりする等の問題を有している。

【0092】

このような問題を回避する手法としては、例えばUVオゾン処理や酸素プラズマ処理等により各画素形成領域の画素電極を親液化した後、バンク表面をソフトエッチングすることなしに撥液処理溶液に絶縁性基板を浸漬してバンク表面に撥液性の被膜を形成させて撥液化する製造方法(以下、便宜的に「第2の比較例」と記す)が考えられる。

【0093】

この場合、バンク(又はバンク表面)を形成する金属材料として、銅や銀、又はこれらを主成分とする低抵抗の合金を適用した場合、UVオゾン処理や酸素プラズマ処理等によりこれらの金属の表面に形成された酸化膜を除去していないので、後続する撥液化処理において撥液性の被膜(トリアジンチオール化合物の被膜)が形成されにくくなったり、有機EL層上に形成される対向電極(例えばカソード電極)とバンクとの接合性が低下して接触抵抗が高くなる等の問題を有している。特に、バンクを形成する金属材料として、低抵抗で比較的安価な銅を適用した場合、銀を適用した場合に比較して酸化されやすく、撥液化処理におけるトリアジンチオール化合物の結合が極端に起こりにくくなり、撥液性の被膜が充分に形成されず撥液性が著しく低下する傾向がある。

【0094】

ここで、上記第1及び第2の比較例において、各々バンクを形成する金属材料として、銅を用い、親液化処理としてUVオゾン処理を適用した場合の純水接触角を測定すると、表1に示すように、銅をトリアジンチオール化合物の撥液処理溶液に浸漬して被膜を形成し撥液化した後、UVオゾン処理を施す第1の比較例においては、純水接触角が73.2°となり、また、銅をUVオゾン処理した後、バンク表面をソフトエッチングすることなしに撥液処理溶液に浸漬して撥液化する第2の比較例においては、純水接触角が54.5°となり、いずれの場合においても純水接触角が比較的低くく、撥液性が低下することが判明した。

【0095】

【表1】

【0096】

一方、上述した実施形態にも示したように、画素電極上に形成される有機EL層(正孔輸送層)の材料として、PEDOT/PSS等の有機化合物含有液を適用した場合、当該溶液の塗布乾燥工程において凝集しやすく、形成される正孔輸送層の膜厚が不均一になりやすいという特性を有している。ここで、PEDOT/PSSを適用した正孔輸送層の膜厚を均一化するためには、画素電極(導電性酸化金属層)の表面の純水接触角を概ね10°以下になるように親液化処理を行う必要がある。

【0097】

このような観点に基づいて、上述した実施形態に示した製造方法における各処理工程ごとの純水接触角を検証すると、まず、絶縁性基板に対してUVオゾン処理を施し、画素電極(導電性酸化金属層)表面を親液化する処理においては、図3に示すように、紫外光の照射時間(UV照射時間)が長くなるほど、画素電極表面の純水接触角が10°以下にまで低くなり、上述したPEDOT/PSSに対する親液性が向上することが判明した。

【0098】

ここで、上記純水接触角の測定は、具体的には、親液化処理として、フィルジェン株式会社製のUVオゾンクリーナー(型式:NL−UV253)を用い、酸素注入条件として流量10L/min、注入時間0.3minに設定し、画素電極表面に形成されるITO膜(導電性酸化金属層)をUVオゾン処理したものを用いた。

【0099】

これにより、絶縁性基板(ITO膜からなる導電性酸化金属層を備えた画素電極)に対する親液化処理として、概ね4分(min)以上紫外光を照射することにより10°以下の純水接触角が得られ、より好ましくは、10分(min)程度照射することにより10°以下の純水接触角が安定的に得られることが判明した。

【0100】

次いで、上記UVオゾン処理の後、1.0wt%の濃度で、室温程度の液温に設定された過硫酸アンモニウム水溶液に絶縁性基板を浸漬してソフトエッチングを施すことにより、上記UVオゾン処理によりバンクを形成する銅の表面に形成された酸化膜を除去する。その後、トリアジンチオール化合物の撥液処理溶液に浸漬してバンクを形成する銅の表面に撥液性の被膜を形成して撥液化処理を行う。この場合のバンク(銅)表面の純水接触角は、図13に示すように、ソフトエッチングの処理時間(過硫酸アンモニウム水溶液への浸漬時間)が長くなるほど上昇し、上述した表1に示したように、ソフトエッチングを行わずに撥液化処理を行った場合の純水接触角(73.2°、54.5°)に比較して、PEDOT/PSSに対して充分な撥液性を示す130°程度に設定されることが判明した。

【0101】

これにより、絶縁性基板上に配設されたバンク(銅)に対する撥液化処理に先立って実行するソフトエッチングとして、概ね10秒以上過硫酸アンモニウム水溶液に浸漬することにより130°程度の純水接触角が安定的に得られることが判明した。

また、この撥液化処理を行った後の画素電極(ITO膜)表面の純粋接触角は、図13に示すように、ソフトエッチングの処理時間に関わらず、略一定(概ね9〜11°程度)となり、PEDOT/PSSに対する充分な親液性を維持していることが判明した。

【0102】

このように、金属材料により形成されたバンクにより各表示画素(有機EL素子)の形成領域が画定された絶縁性基板(パネル基板)において、UVオゾン処理等により画素形成領域(画素電極)の親液化処理を行い、その後、バンク表面のソフトエッチングを施した後、トリアジンチオール化合物の被膜を形成して撥液化する製造方法によれば、画素形成領域に露出する画素電極(ITO膜)表面における純水接触角を概ね10°以下として良好な親液性を実現することができるとともに、当該画素形成領域を画定するバンク表面における純水接触角を概ね130°以上として良好な撥液性を実現することができるので、有機EL層を形成するための有機化合物含有液(PEDOT/PSS等)を絶縁性基盤上に塗布する工程において、有機化合物含有液が画素電極上の全域に充分馴染んで広がり膜厚が均一化された有機EL層(発光機能層)を形成することができるとともに、隣接する画素形成領域(有機EL素子)に異なる色の発光材料が混入して表示画素間で発光色の混合(混色)等が生じる現象を防止することができる。

【0103】

また、UVオゾン処理等による親液化処理によりバンク表面に形成される酸化膜が、撥液化処理前のソフトエッチングにより除去されるので、有機EL層の形成後に各画素形成領域(画素電極)に共通に設けられる対向電極と上記バンクとの接合性が向上して、良好な電気的な接続を実現することができる。

【0104】

したがって、発光動作時における発光開始電圧や、有機EL層から放射される光の波長(色度)の設計値からのずれを抑制して、所望の表示画質を得ることできるとともに、有機EL素子の劣化や接続不良の発生を抑制して、信頼性や寿命に優れた表示パネルを実現することができる。

【0105】

なお、上述した比較検証においては、画素電極の親液化処理としてUVオゾン処理を適用した場合について説明したが、本発明はこれに限定されるものではなく、UVオゾン処理と同様に、プラズマ中で酸素ラジカルを発生させて、画素電極(ITO等からなる導電性酸化金属層)の表面を親液化(親水化)する酸素プラズマ処理により親液化処理を施す場合であっても、上記実験データと略同等の結果が得られ、同等の効果を得ることができる。

【図面の簡単な説明】

【0106】

【図1】本発明に係る表示装置に適用される表示パネルの画素配列状態の一例を示す概略平面図である。

【図2】本発明に係る表示装置の表示パネルに2次元配列される各表示画素(表示素子及び画素駆動回路)の回路構成例を示す等価回路図である。

【図3】本実施形態に係る表示装置(表示パネル)に適用可能な表示画素の一例を示す平面レイアウト図である。

【図4】本実施形態に係る表示画素の平面レイアウトの要部詳細図である。

【図5】本実施形態に係る平面レイアウトを有する表示画素におけるA−A断面を示す概略断面図である。

【図6】本実施形態に係る平面レイアウトを有する表示画素におけるB−B断面を示す概略断面図である。

【図7】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その1)である。

【図8】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その2)である。

【図9】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その3)である。

【図10】本実施形態に係る表示装置(表示パネル)の製造方法の一例を示す工程断面図(その4)である。

【図11】本実施形態に係る表示装置(表示パネル)に形成されるバンク表面の被膜材料の化学構造式及び被膜材料がバンクメタル層に被膜した状態での結合を示す概念図である。

【図12】UVオゾン処理における紫外光の照射時間と純水接触角との関係を示す実験データである。

【図13】親液化処理後のソフトエッチングの処理時間と撥液化処理後の純水接触角との関係を示す実験データである。

【符号の説明】

【0107】

10 表示パネル

11 絶縁性基板

15 画素電極

15a 反射金属層

15b 導電性酸化金属層

16 有機EL層

16a 正孔輸送層

16b 電子輸送性発光層

17 対向電極

18 バンク

18x 下地層

18a バンクメタル層

PIX 表示画素

Rpx 画素形成領域

【特許請求の範囲】

【請求項1】

担体輸送層を有する発光素子を含む複数の表示画素を備えた表示装置の製造方法において、

基板上にそれぞれ画素電極が設けられた前記複数の表示画素の形成領域間に隔壁を形成する工程と、

前記画素電極表面を親液化する工程と、

前記隔壁の表面をエッチングする工程と、

前記隔壁の表面を撥液化する工程と、

を含むことを特徴とする表示装置の製造方法。

【請求項2】

前記画素電極表面を親液化する工程は、UVオゾン処理又は酸素プラズマ処理により、少なくとも前記画素電極表面を、前記担体輸送層を形成する担体輸送性材料を含む溶液に対して親液化することを特徴とする請求項1記載の表示装置の製造方法。

【請求項3】

前記隔壁の表面をエッチングする工程は、前記画素電極表面を親液化する処理の際に少なくとも前記隔壁の表面に形成された酸化膜を除去することを特徴とする請求項1記載の表示装置の製造方法。

【請求項4】

前記隔壁の表面を撥液化する工程は、トリアジンチオール化合物の溶液に前記基板を浸漬し、少なくとも前記隔壁の表面に前記トリアジンチオール化合物を結合させて、前記担体輸送性材料を含む溶液に対して撥液性を有する被膜を形成することを特徴とする請求項1記載の表示装置の製造方法。

【請求項5】

前記画素電極は、表面が導電性の酸化金属層により形成されていることを特徴とする請求項1乃至4のいずれかに記載の表示装置の製造方法。

【請求項6】

前記隔壁は、少なくとも表面が低抵抗の金属材料により形成されていることを特徴とする請求項1乃至5のいずれかに記載の表示装置の製造方法。

【請求項7】

前記表示画素の形成領域は、前記隔壁により画定されることを特徴とする請求項1乃至6のいずれかに記載の表示装置の製造方法。

【請求項8】

前記担体輸送層は、前記画素形成領域に露出する前記画素電極上に形成されることを特徴とする請求項7記載の表示装置の製造方法。

【請求項9】

前記親液化された前記画素電極上に、前記担体輸送性材料を含む溶液を塗布、乾燥して、前記担体輸送層を形成する工程と、

前記担体輸送層を介して前記複数の表示画素の前記画素電極に共通に対向し、かつ、前記撥液化された前記隔壁上に延在して電気的に接続された単一の対向電極を形成する工程と、

をさらに含むことを特徴とする請求項1乃至8のいずれかに記載の表示装置の製造方法。

【請求項10】

請求項1乃至9のいずれかに記載の表示装置の製造方法によって製造されたことを特徴とする表示装置。

【請求項1】

担体輸送層を有する発光素子を含む複数の表示画素を備えた表示装置の製造方法において、

基板上にそれぞれ画素電極が設けられた前記複数の表示画素の形成領域間に隔壁を形成する工程と、

前記画素電極表面を親液化する工程と、

前記隔壁の表面をエッチングする工程と、

前記隔壁の表面を撥液化する工程と、

を含むことを特徴とする表示装置の製造方法。

【請求項2】

前記画素電極表面を親液化する工程は、UVオゾン処理又は酸素プラズマ処理により、少なくとも前記画素電極表面を、前記担体輸送層を形成する担体輸送性材料を含む溶液に対して親液化することを特徴とする請求項1記載の表示装置の製造方法。

【請求項3】

前記隔壁の表面をエッチングする工程は、前記画素電極表面を親液化する処理の際に少なくとも前記隔壁の表面に形成された酸化膜を除去することを特徴とする請求項1記載の表示装置の製造方法。

【請求項4】

前記隔壁の表面を撥液化する工程は、トリアジンチオール化合物の溶液に前記基板を浸漬し、少なくとも前記隔壁の表面に前記トリアジンチオール化合物を結合させて、前記担体輸送性材料を含む溶液に対して撥液性を有する被膜を形成することを特徴とする請求項1記載の表示装置の製造方法。

【請求項5】

前記画素電極は、表面が導電性の酸化金属層により形成されていることを特徴とする請求項1乃至4のいずれかに記載の表示装置の製造方法。

【請求項6】

前記隔壁は、少なくとも表面が低抵抗の金属材料により形成されていることを特徴とする請求項1乃至5のいずれかに記載の表示装置の製造方法。

【請求項7】

前記表示画素の形成領域は、前記隔壁により画定されることを特徴とする請求項1乃至6のいずれかに記載の表示装置の製造方法。

【請求項8】

前記担体輸送層は、前記画素形成領域に露出する前記画素電極上に形成されることを特徴とする請求項7記載の表示装置の製造方法。

【請求項9】

前記親液化された前記画素電極上に、前記担体輸送性材料を含む溶液を塗布、乾燥して、前記担体輸送層を形成する工程と、

前記担体輸送層を介して前記複数の表示画素の前記画素電極に共通に対向し、かつ、前記撥液化された前記隔壁上に延在して電気的に接続された単一の対向電極を形成する工程と、

をさらに含むことを特徴とする請求項1乃至8のいずれかに記載の表示装置の製造方法。

【請求項10】

請求項1乃至9のいずれかに記載の表示装置の製造方法によって製造されたことを特徴とする表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2007−323963(P2007−323963A)

【公開日】平成19年12月13日(2007.12.13)

【国際特許分類】

【出願番号】特願2006−152964(P2006−152964)

【出願日】平成18年6月1日(2006.6.1)

【出願人】(000001443)カシオ計算機株式会社 (8,748)

【Fターム(参考)】

【公開日】平成19年12月13日(2007.12.13)

【国際特許分類】

【出願日】平成18年6月1日(2006.6.1)

【出願人】(000001443)カシオ計算機株式会社 (8,748)

【Fターム(参考)】

[ Back to top ]