表示装置及び当該表示装置を具備する電子機器

【課題】面積階調方式における外付けICの実装コストの問題、さらに外付けICから信号を入力する場合、スタートパルス信号よりもクロック信号が遅延してしまう問題を、ドライバーの入力部に遅延回路を設けることなく、提供することを課題とする。

【解決手段】副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路及び前記ゲート信号線駆動回路を駆動するための信号を出力する回路を有することを特徴とする構成とした。

【解決手段】副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路及び前記ゲート信号線駆動回路を駆動するための信号を出力する回路を有することを特徴とする構成とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画素がマトリクス状に配置された画素領域を有する表示装置及びに関する。特に副画素を有する画素がマトリクス状に配置された画素領域を有する表示装置に関する。

【背景技術】

【0002】

液晶ディスプレイ(LCD)や、エレクトロルミネッセンス(EL)ディスプレイ等をはじめとする表示装置の階調表示方式の一つである面積階調方式は、画素の発光がオン状態とオフ状態の二値であるので、映像信号処理のためのDAコンバータ回路の実装の必要がない。また時間階調方式でみられる1フレームを複数のサブフレームへと分割する必要がない。そのため、映像信号を順次駆動回路に入力し、画素領域における表示に反映させることが出来る。したがって大規模なフレームメモリを実装する必要がなく、低周波数でディスプレイを動作させることができる。そのため、面積階調方式は、低消費電力化、低コスト化が実現できる表示方式である。

【0003】

しかしながら面積階調方式は副画素(サブ画素ともいう)を含む構成であるため、走査線の数が増加することによる駆動回路と実装コストの増大という問題があった。

【0004】

そこで図18のようにソース線駆動回路(SD)とゲート線駆動回路(GD)とそれぞれのバッファー回路(BUF)と画素マトリクスを同一基板(SUB)上に形成する。そして、ソース線駆動回路とゲート線駆動回路を制御する信号は、基板の外部に実装されたコントロール回路(CTL)から入力されている構成が提案されている(特許文献1参照)。

【特許文献1】特開平10−068931号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

副画素を有する画素がマトリクス状に配置された画素領域を有する構成の面積階調方式では、D/Aコンバータ回路と大規模なフレームメモリを実装しない簡単な構成が可能である。しかしながら、上記特許文献1に記載の方法によるとコントロール回路を外付けすることによりICの実装コストがかかるという問題があった。

【0006】

さらに外付けICから信号を外部接続端子やFPC(Flexible Printed Circuit)を介して入力する場合、駆動回路に信号が入力されるまで外部接続端子とFPCとの接触の状態や外部のノイズの影響等によって、スタートパルス信号よりも、クロック信号が遅延してしまい、駆動回路内のシフトレジスタ回路が誤作動し、正常表示が出来なくなる問題があるため、駆動回路の入力部に遅延回路を設ける必要がある。

【0007】

本発明は前述の課題に鑑み、ごく単純な回路を同一基板上に形成するだけで外部接続端子数を減少させ、外付け部品点数を削減し低コスト化が実現でき、かつクロック信号の遅延を防ぐことのできる表示装置を提供するものである。

【課題を解決するための手段】

【0008】

本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路及び前記ゲート信号線駆動回路を駆動するための信号を出力する回路を有する構成とした。

【0009】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力する構成とした。

【0010】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号は、JKフリップフロップ回路、Dフリップフロップ回路及び複数のインバータ回路を有する回路より出力される構成とした。

【0011】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力される構成とした。

【0012】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力される構成とした。

【0013】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力される構成とした。

【0014】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力される構成とした。

【0015】

また本発明において、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号がJKフリップフロップを介して出力される信号であってもよい

【発明の効果】

【0016】

本発明では、コントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。

【0017】

また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はない。

【発明を実施するための最良の形態】

【0018】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0019】

なお本明細書において、各素子間の接続は、電気的に接続されていることを示す。そのため、接続関係を有する素子間に、半導体素子やスイッチング素子等を介して接続することもありうる。

【0020】

また本明細書において、トランジスタのソース電極及びドレイン電極は、トランジスタの構成上、ゲート電極以外の電極を便宜上区別するために採用されている名称である。本発明において、トランジスタの極性に限定されない構成の場合、その極性を考慮すると、ソース電極及びドレイン電極の名称は変化する。そのため、ソース電極又はドレイン電極を、一方の電極及び他方の電極のいずれかとして記載することがある。

【0021】

(実施の形態1)

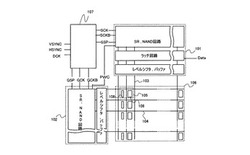

本実施の形態においては、本発明による表示装置の基本構成について説明する。図1は表示装置の模式図を示したものである。

【0022】

図1において、基板上に、ソース線駆動回路101、ゲート線駆動回路102、画素領域106、コントロール回路107が形成されている。画素領域106は、複数の画素105がマトリクス状に配置されており、各画素105は、複数の副画素108から構成されており、副画素108はソース信号線103、ゲート信号線104によって制御される。図1においては2つの副画素で構成しているがこれに限定されず、1つの画素において副画素が3つ以上設けられていればよいことを付記する。

【0023】

なお、本明細書においては、画素とは一つの画像を構成する色要素を具備するものであり、発光素子及び発光素子を駆動する素子(例えば薄膜トランジスタで構成される回路)を有する副画素を複数含むものとする。また本明細書においては、絵素とは、一つの最小の画像を表示するための色要素を構成する画素を具備するものであるとする。よって、R(赤)G(緑)B(青)の色要素からなるフルカラー表示装置の場合には、絵素とはRの色要素、Gの色要素、Bの色要素を含む画素から構成されているものとする。また、各副画素は、その面積の大きさ、形状が異なっていてもよいし、同じでもよい。

【0024】

ソース線駆動回路101は、クロック信号(SCK)、クロック反転信号(SCKB)、スタート信号(SSP)の入力により、シフトレジスタ回路(SRと略記することもある)、NAND回路において順次サンプリングパルスを出力する。その後、レベルシフタ、バッファにおいて、振幅変換あるいは増幅を受け、映像信号(Data)のサンプリグを行い、順次ソース信号線へと出力する。シフトレジスタの最終段以降の出力はゲート線駆動回路のパルス幅制御信号(PWC)として用いても良い。また、ソース線駆動回路101は基板上に設けられた薄膜トランジスタを有するものである。

【0025】

ゲート線駆動回路102は、クロック信号(GCK)、クロック反転信号(GCKB)、スタート信号(GSP)の入力により、SR、NAND回路において順次行選択パルスを出力する。前記行選択パルスはパルス幅を制御された後、レベルシフタ、バッファにおいて、振幅変換あるいは増幅を受け、順次、各行のゲート信号線を選択する。ゲート線駆動回路102は基板上に設けられた薄膜トランジスタを有するものである。

【0026】

コントロール回路107は、映像信号である垂直同期信号VSYNCと水平同期信号HSYNCとドットクロック信号(DCK)の入力により、ソース線駆動回路用スタート信号(SSP)、ソース線駆動回路用クロック信号(SCK)、ソース線駆動回路用クロック反転信号(SCKB)、ゲート線駆動回路用スタートパルス信号(GSP)、ゲート線駆動回路用クロック信号(GCK)、ゲート線駆動回路用クロック反転信号(GCKB)を出力する。コントロール回路107の信号出力部は信号の種類に応じてそれぞれ、ソース信号線駆動回路及びゲート信号線駆動回路の入力端それぞれの近傍に配置し、信号引き回し配線が短くなる構成をとる。

【0027】

図2にコントロール回路の第1の構成を示す。コントロール回路208は、フリップフロップ回路であるDフリップフロップ回路(以下、DFFという)と2つのJフリップフロップ回路(以下、JKFFという)と複数のインバータと複数のバッファと2つのNANDを有する。Jフリップフロップ回路の具体的な構成について、図3に示した回路を採用してもよい。またDフリップフロップ回路の具体的な構成については、図4に示した回路を採用すればよい。

【0028】

図2において、DFF201のCK端子にHSYNC信号線が電気的に接続されている。DFF201のQB端子はDFF201のD端子と電気的に接続されている。DFF201のPRESET端子はVSYNC信号線がインバータ205を介して電気的に接続されている。DFFのQ端子はバッファ204を介してゲート線駆動回路210のGCK信号線と電気的に接続されている。DFF201のQ端子はインバータ205とバッファ204を介してゲート線駆動回路210のGCKB信号線と電気的に接続されている。

【0029】

また、図2において、GCK信号線は第1のJKFF202のCK端子と電気的に接続されている。第1のNAND206の第1の入力端にはVSYNC信号線が電気的に接続されている。第1のNAND206の第2の入力端にはGCK信号線が電気的に接続されている。第1のNAND206の出力端には第1のJKFF202のPRESET端子と電気的に接続されている。

【0030】

また、図2において、第1のJKFF202のJ端子とK端子とQ端子が電気的に接続されている。第1のJKFF202のQ端子はバッファ204を介してゲート線駆動回路のGSP信号線と電気的に接続されている。DCK信号線は、バッファ204を介してソース線駆動回路209のSCK信号線と電気的に接続されている。前記DCK信号線は、インバータ205とバッファ204を介してソース線駆動回路209のSCK信号線と電気的に接続されている。

【0031】

また、図2において、HSYNC信号線は第2のNAND207の第1の入力端と電気的に接続されている。第2のNAND207の第2の入力端はSCK信号線と電気的に接続されている。第2のNAND207の出力端は第2のJKFF203のPRESET端子と電気的に接続されている。SCK信号線は第2のJKFF203のCK端子と電気的に接続されている。第2のJKFF203のJ端子とK端子とQ端子が電気的に接続されている。第2のJKFF203のQ端子はバッファを介してソース線駆動回路209のSSP信号線と電気的に接続されている。上記のバッファの個数は特に限定しない。

【0032】

図2に示すコントロール回路において、外部より入力される垂直同期信号VSYNCはインバータ回路205を介して、Dフリップフロップ回路201のPRESET端子に入力される。また外部より入力される水平同期信号HSYNCはDフリップフロップ回路のCK端子に入力される。そしてDフリップフロップ回路201の出力端子は、ゲート線駆動回路に入力されるゲートクロック信号GCK、及びインバータを介して出力される反転ゲートクロック信号GCKBを出力する。

【0033】

また、図2のコントロール回路において、外部より入力される垂直同期信号VSYNC及び前記ゲートクロック信号GCKが入力されるNAND回路206からの出力がJKフリップフロップ回路202のPRESET端子に入力される。また外部より入力される前記ゲートクロック信号GCKがJKフリップフロップ回路202のCK端子に入力される。そしてJKフリップフロップ回路202の出力端子は、ゲート線駆動回路に入力されるゲートスタートパルス信号GSPを出力する。

【0034】

また、図2のコントロール回路において、外部より入力されるドットクロック信号DCKは、バッファ回路を介してソース信号線駆動回路にソースクロック信号SCKとして出力される。また外部より入力されるドットクロック信号DCKはインバータ回路を介してソース線駆動回路に入力される反転ソースクロック信号SCKBとして出力される。

【0035】

また、図2のコントロール回路において、外部より入力される水平同期信号HSYNC及び外部より入力されるドットクロック信号DCKが入力されるNAND回路205からの出力がJKフリップフロップ回路203のPRESET端子に入力される。また外部より入力されるドットクロック信号DCKがJKフリップフロップ回路203のCK端子に入力される。そしてJKフリップフロップ回路203の出力端子は、ソース線駆動回路に入力されるソーススタートパルス信号GSPを出力する。

【0036】

次に図5にコントロール回路の動作を示す。

【0037】

HSYNCとほぼ同じタイミングでSSPが出力され、DCKとほぼ同じタイミングでSCKが出力され、SCKと反転した論理でSCKBが出力される。この時、入力信号と同じ波形であるが、SCKよりもSSPの方が遅延している。

【0038】

VSYNCのHレベル301の立ち上がりとほぼ同時に、GCKがHレベル305となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、HSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなる。次のHSYNCのHレベル303の立ち上がりとほぼ同時にGCKはHレベル306となる。

【0039】

VSYNCのHレベルのパルス301と同時に立ち上がるHSYNCのHレベルのパルス304を1番目とすると、偶数番目(2m)のHレベルの立ち上がりでGCKはLレベルとなり、奇数番目(2m+1)のHレベルの立ち上げ利でGCKはHレベルとなる。GCKBはGCKと反転した論理で出力される。

【0040】

VSYNCのHレベル301の立ち上がりとほぼ同時に立ち上がるGCKの最初のHレベル305の立ち上がりとほぼ同時に、GSPがHレベル308となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、次に来るHSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなり、次のVSYNCのHレベル307の立ち上がりまでLレベルを保ち続ける。この時GCKの1番目のHレベル305の立ち上がりよりもGSPの1番目のHレベル307の立ち上がりの方が遅延し、GCKの2番目のHレベル306の立ち上がりよりもGSPの1番目のHレベル307の立ち下がりの方が遅延する。

【0041】

図6に、図1におけるソース線駆動回路101の簡単なタイミングチャートを示し、以下にその動作について順次説明する。図6には、入力信号としてクロック信号(SCK、SCKB)、スタートパルス(SSP)、デジタル映像信号(Data)、出力信号として、1段目〜4段目、最終段のサンプリングパルス(SROut1〜4、最終)、ソース信号線出力(SLine1、SLine最終)を示している。

【0042】

まず、第1ライン期間(Period1)について説明する。クロック信号とスタートパルス501に従ってシフトレジスタが動作し、サンプリングパルス503を順次出力する。サンプリングパルス503はそれぞれ、デジタル映像信号のサンプリングを行い、ラッチ回路にデータを保持し順次ソース信号線に出力される。

【0043】

なお、第1ライン期間において、デジタル映像信号504は、全てHレベルを入力している。

【0044】

ここで、ソース信号線出力は、Hレベルとなる(期間507)。

【0045】

次に、第2ライン期間(Period2)に移る。第1ライン期間と同様に、クロック信号とスタートパルス502に従い、サンプリングパルス503が順次出力され、デジタル映像信号のサンプリングが行われる。

【0046】

なお、第2ライン期間において、デジタル映像信号505は、全てLレベルを入力している。

【0047】

このとき、ソース信号線出力は、全段においてLレベルとなる(期間508)。

【0048】

シフトレジスタ最終段以降の出力パルス509はPWC信号としてゲート線駆動回路で用いても良い。

【0049】

図7に、ゲート線駆動回路102とソース線駆動回路101のタイミングチャートを示し、以下にその動作について順次説明する。図7には、ゲート線駆動回路への入力信号としてクロック信号(GCK、GCKB)、スタートパルス(GSP)、出力信号として、1段目〜4段目のゲート線出力信号(GLine1〜4)を示している。

【0050】

クロック信号とスタートパルスに従ってシフトレジスタが動作し、パルス幅をPWCを用いて調整した後、順次ゲート信号線に出力される。

【0051】

上記ゲート信号線出力によりソース信号線出力(SLine1、SLine最終)を副画素に入力する行を選択する。

【0052】

本実施の形態の構成ではゲート線駆動回路のシフトレジスタで用いられているGCK信号線から直接GCKの立ち上がりエッジを用いて、GSPの立ち上がりと立ち下がりエッジを生成しているので、GCKがGSPよりも遅延することはない。

【0053】

本実施の形態ではソース線駆動回路のシフトレジスタで用いられているSCK信号線から直接SCKの立ち上がりエッジを用いて、SSPの立ち上がりと立ち下がりエッジを生成しているので、SCKがSSPよりも遅延することはない。

【0054】

本実施の形態の構成で用いたDFFはD端子とQB端子の接続によりTフリップフロップ(TFF)として動作するのでTFFに置き換えても良い。

【0055】

また、本実施の形態において、外部接続端子数を減少させるため、ソース線駆動回路のシフトレジスタの最終段以降の出力をゲート線駆動回路のパルス幅制御信号(PWC)として用いる構成もある。

【0056】

以上のように本実施の形態は、基板上に形成されたコントロール回路で、ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号を、ドットクロック信号を基にした信号及びドットクロック信号の反転信号を基にした信号として内部生成した信号として出力することができる。またソース信号線駆動回路を駆動するためのスタートパルス信号を、前記水平同期信号を基にした信号として内部生成した信号として出力することができる。またゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号を、垂直同期信号の反転信号及び水平同期信号が入力されるDフリップフロップ回路より出力される信号として内部生成した信号として出力することができる。またゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力される信号として内部生成した信号として出力することができる。前述のコントロール回路におけるソース信号線駆動回路及びゲート信号線駆動回路に出力される各種信号は、デジタル映像信号を入力し、デジタル出力を行う形式のドライバーを用いた表示装置であれば、LCD、ELディスプレイ等、多種の表示装置において、外部接続端子数を削減することが出来る。

【0057】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【0058】

(実施の形態2)

本実施形態においては、実施の形態1と別の構成について説明する。コントロール回路の第1の構成よりも素子数が少なく実装面積の節約できるコントロール回路の構成を図8に示す。

【0059】

フリップフロップ回路であるDFFとJKFFと複数のインバータ603と複数のバッファ604を有し、DFF601のCK端子にHSYNC信号線が電気的に接続されている。DFF601のQB端子はD端子と電気的に接続されている。DFF601のPRESET端子はVSYNC信号線がインバータを介して電気的に接続されている。DFF601のQ端子はバッファ604を介してゲート線駆動回路のGCK信号線と電気的に接続されている。DFF601のQ端子はインバータ603とバッファ604を介してGCKB信号線と電気的に接続されている。GCK信号線はJKFF602のCK端子と電気的に接続されている。JKFF602のPRESET端子はVSYNC信号線が電気的に接続されている。JKFF602のJ端子とK端子とQ端子が電気的に接続されている。JKFF602のQ端子はバッファを介してゲート線駆動回路607のGSP信号線と電気的に接続されている。HSYNC信号線はバッファ604を介してソース線駆動回路606のSCK信号線と電気的に接続されている。HSYNC信号線はインバータ603とバッファ604を介してソース線駆動回路606のSCKB信号線と電気的に接続され、HSYNC信号線はバッファ604を介してソース線駆動回路606のSSP信号線と接続されている。上記のバッファの個数は特に限定しない。

【0060】

図8に示すコントロール回路において、外部より入力される垂直同期信号VSYNCはインバータ回路603を介して、Dフリップフロップ回路601のPRESET端子に入力される。また外部より入力される水平同期信号HSYNCはDフリップフロップ回路のCK端子に入力される。そしてDフリップフロップ回路601の出力端子は、ゲート線駆動回路に入力されるゲートクロック信号GCK、及びインバータを介して出力される反転ゲートクロック信号GCKBを出力する。

【0061】

また、図8のコントロール回路において、外部より入力される垂直同期信号VSYNCはインバータ回路603を介して、JKフリップフロップ回路202のPRESET端子に入力される。また前記ゲートクロック信号GCKがJKフリップフロップ回路602のCK端子に入力される。そしてJKフリップフロップ回路

02の出力端子は、ゲート線駆動回路に入力されるゲートスタートパルス信号GSPを出力する。

【0062】

また、図8のコントロール回路において、外部より入力されるドットクロック信号DCKは、バッファ回路を介してソース信号線駆動回路にソースクロック信号SCKとして出力される。また外部より入力されるドットクロック信号DCKはインバータ回路を介してソース線駆動回路に入力される反転ソースクロック信号SCKBとして出力される。

【0063】

また、図8のコントロール回路において、外部より入力されるドットクロック信号DCKは、バッファ回路を介してソース信号線駆動回路にソーススタートパルス信号SSPとして出力される。

【0064】

実施の形態1と同様に図5を用いてコントロール回路の動作を示す。

【0065】

HSYNCとほぼ同じタイミングでSSPが出力され、DCKとほぼ同じタイミングでSCKが出力され、SCKと反転した論理でSCKBが出力される。この時のSSPとSCKのタイミングの前後関係は不明である。

VSYNCのHレベル301の立ち上がりとほぼ同時に、GCKがHレベル305となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、HSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなる。次のHSYNCのHレベル303の立ち上がりとほぼ同時にGCKはHレベル306となる。

VSYNCのHレベルのパルス301と同時に立ち上がるHSYNCのHレベルのパルス304を1番目とすると、偶数番目(2m)のHレベルの立ち上がりでGCKはLレベルとなり、奇数番目(2m+1)のHレベルの立ち上げ利でGCKはHレベルとなる。GCKBはGCKと反転した論理で出力される。

【0066】

VSYNCのHレベル301の立ち上がりとほぼ同時に、GSPがHレベル308となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、次に来るHSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなり、次のVSYNCのHレベル307の立ち上がりまでLレベルを保ち続ける。この時GCKの2番目のHレベル306の立ち上がりよりもGSPの1番目のHレベル307の立ち下がりのタイミングの方が遅延する。

【0067】

上記第2のコントロール回路構成はGSPの立ち下がりのタイミングのみが、GCKの立ち上がりのタイミングよりも遅延する。

【0068】

本実施の形態の構成ではVSYNCの立ち上がりエッジを用いて、GSPの立ち上がりエッジを生成し、GCKの立ち上がりエッジを用いて、GSPの立ち下がりエッジを生成している。

【0069】

本実施の形態の構成ではGSPの立ち下がりのタイミングがGCKの立ち上がりのタイミングよりも遅延する。

【0070】

本実施の形態の構成で用いたDFFはD端子とQB端子の接続によりTFFとして動作するのでTFFに置き換えても良い。

【0071】

なお、本実施の形態は、コントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【0072】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【実施例1】

【0073】

以下に本発明の表示装置において、絶縁表面を有する基板上に薄膜トランジスタで作製する例について、作製手順を簡略に図9〜11を用いて示す。図9〜11に示す構成のアクティブマトリクス型表示装置は液晶表示装置やEL(Electro Luminescence)素子を用いた表示装置を実現することを可能とするものである。

【0074】

まず、図9(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラス基板401上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成るブロッキング層402を形成する。例えば、プラズマCVD法でSiH4、NH3、N2Oから作製される酸化窒化シリコン膜を10〜200nm(好ましくは50〜100nm)形成し、同様にSiH4、N2Oから作製される酸化窒化水素化シリコン膜を50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。本実施例ではブロッキング層402を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させた構造として形成しても良い。

【0075】

島状に分割された半導体層403〜406は、非晶質構造を有する半導体膜を、レーザーアニール法やファーネスアニール炉を用いた熱処理により結晶構造を有する半導体膜(以下、結晶質半導体膜という)で形成する。この島状の半導体層403〜406の厚さは25〜80nm(好ましくは30〜60nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

【0076】

レーザーアニール法で結晶質半導体膜を作製するには、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO4レーザーを用いる。レーザー発振器から出力されるレーザー光は、光学系で線状に集光し半導体膜に照射する方法を用いる。アニールの条件は実施者が適宣選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数30Hzとし、レーザーエネルギー密度を100〜400mJ/cm2(代表的には200〜300mJ/cm2)とする。また、YAGレーザーを用いる場合には、第2高調波を用いパルス発振周波数1〜10kHzとし、レーザーエネルギー密度を300〜600mJ/cm2(代表的には350〜500mJ/cm2)とすると良い。そして幅100〜1000μm、例えば400μmで線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を80〜98%として行う。

【0077】

次いで、島状の半導体層403〜406を覆うゲート絶縁膜407を形成する。ゲート絶縁膜407はプラズマCVD法またはスパッタ法を用い、厚さを40〜150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、120nmの厚さとして酸化窒化シリコン膜を形成する。勿論、ゲート絶縁膜407はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

【0078】

そして、ゲート絶縁膜407上にゲート電極を形成するための第1の導電膜408aと第2の導電膜408bとを形成する。本実施例では、第1の導電膜408aを窒化タンタルまたはチタンで50〜100nmの厚さに形成し、第2の導電膜408bをタングステンで100〜300nmの厚さに形成する。これらの材料は、窒素雰囲気中における400〜600℃の熱処理でも安定であり、抵抗率が著しく増大することがない。

【0079】

次に図9(B)に示すように、レジストによるマスク409を形成し、ゲート電極を形成するための第1のエッチング処理を行う。エッチング方法に限定はないが、好適にはICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いる。エッチング用ガスにCF4とCl2を混合し、0.5〜2Pa、好ましくは1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した場合にはタングステン膜、窒化タンタル膜及びチタン膜の場合でも、それぞれ同程度の速度でエッチングすることができる。

【0080】

上記エッチング条件では、レジストによるマスクの形状と、基板側に印加するバイアス電圧の効果により端部をテーパー形状とすることができる。テーパー部の角度は25〜45度となるようにする。また、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。タングステンに対する酸化窒化シリコン膜の選択比は2〜4(代表的には3)であるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされる。こうして、第1のエッチング処理により第1の導電膜と第2の導電膜から成る第1の形状の導電層410〜415(第1の導電膜410a〜415aと第2の導電膜410b〜415b)を形成する。416はゲート絶縁膜であり、第1の形状の導電層で覆われない領域は20〜50nm程度エッチングされ薄くなる。

【0081】

そして図9(C)に示すように、第1のドーピング処理を行いn型の不純物(ドナー)をドーピングする。ドーピングの方法はイオンドープ法若しくはイオン注入法で行う。イオンドープ法の条件はドーズ量を1×1013〜5×1014/cm2として行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いる。この場合、加速電圧を制御(例えば、20〜60keV)して、第1の形状の導電層をマスクとして利用する。こうして、第1の不純物領域417〜420を形成する。例えば、第1の不純物領域417〜420おけるn型の不純物の濃度は1×1020〜1×1021/cm3の範囲で形成する。

【0082】

図10(A)で示す第2のエッチング処理は、同様にICPエッチング装置を用い、エッチングガスにCF4とCl2とO2を混合して、1Paの圧力でコイル型の電極に500WのRF電力(13.56MHz)を供給してプラズマを生成する。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、第1のエッチング処理に比べ低い自己バイアス電圧を印加する。このような条件によりタングステン膜を異方性エッチングし、第1の導電層である窒化タンタル膜またはチタン膜を残存させるようにする。こうして、第2の形状の導電層421〜426(第1の導電膜421a〜426aと第2の導電膜421b〜426b)を形成する。ゲート絶縁膜は第2の形状の導電層421〜426で覆われない領域はさらに20〜50nm程度エッチングされて膜厚が薄くなる。

【0083】

次いで、第2のドーピング処理を行う。第1のドーピング処理よりもドーズ量を下げ高加速電圧の条件でn型の不純物(ドナー)をドーピングする。例えば、加速電圧を70〜120keVとし、1×1013/cm2のドーズ量で行い、図9(C)で島状の半導体層に形成された第1の不純物領域の内側に第2の不純物領域427〜430を形成する。このドーピングは、第2の形状の導電層423b〜426bを不純物元素に対するマスクとして用い、第2の形状の導電層423a〜426aの下側の領域に不純物元素が添加されるようにドーピングする。この不純物領域は、第2の形状の導電層423a〜426aがほぼ同じ膜厚で残存していることから、第2の形状の導電層に沿った方向における濃度分布の差は小さく、1×1017〜1×1019/cm3の濃度でn型の不純物(ドナー)が含まれるように形成する。

【0084】

そして、図10(B)に示すように、第3のエッチング処理を行い、ゲート絶縁膜のエッチング処理を行う。その結果、第2の形状の導電層421a〜426aもエッチングされ、端部が後退して小さくなり、第3の形状の導電層431〜436(第1の導電膜431a〜436aと第2の導電膜431b〜436b)が形成される。437は残存するゲート絶縁膜であり、エッチングをさらに進めて半導体層の表面を露出させても良い。

【0085】

pチャネル型TFTに対しては、図10(C)に示すように、レジストマスク438、439を形成し、pチャネル型TFTを形成する島状の半導体層にp型の不純物(アクセプタ)をドーピングする。p型の不純物(アクセプタ)は13族に属する元素から選ばれ、典型的にはボロン(B)を用いる。第3の不純物領域440a〜440cの不純物濃度は2×1020〜2×1021/cm3となるようにする。第3の不純物領域にはリンが添加されているが、それ以上の濃度でボロンを添加して導電型を反転させておく。

【0086】

以上までの工程で半導体層に不純物領域が形成される。図10において、第3の形状の導電層433〜435はゲート電極となり、第3の形状の導電層436は容量配線となる。また、第3の形状の導電層431、432はソース線などの配線を形成する。

【0087】

次に、図11(A)では最初に、窒化シリコン膜(SiN:H)または酸化窒化シリコン膜(SiNxOy:H)から成る第1の絶縁膜441をプラズマCVD法で形成する。そして導電型の制御を目的としてそれぞれの島状の半導体層に添加された不純物元素を活性化する工程を行う。活性化はファーネスアニール炉を用いる熱アニール法で行うことが好ましい。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することもできる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施例では550℃で4時間の熱処理を行う。

【0088】

その後、第1の絶縁膜441上に窒化シリコン膜(SiN:H)または酸化窒化シリコン膜(SiNxOy:H)から成る第2の絶縁膜442を形成する。そして、350〜500℃で熱処理を行う。第2の絶縁膜442から放出される水素により半導体膜の水素化を行う。

【0089】

さらに、図11(B)で示すように有機樹脂からなる第3の絶縁膜443を約1000nmの厚さに形成する。有機樹脂膜としては、ポリイミド、アクリル、ポリイミドアミド等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜を用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成する。

【0090】

次に、第3の絶縁膜443、第2の絶縁膜442、第1の絶縁膜441に、コンタクトホールを形成し、アルミニウム(Al)、チタン(Ti)、タンタル(Ta)などを用いて、接続電極451及びソースまたはドレイン配線444〜447を形成する。また、画素部においては、第1の画素電極450、ゲート配線449、接続電極448を形成する。

【0091】

こうして、同一の基板上にpチャネル型TFT453とnチャネル型TFT454が形成される。図11(B)ではpチャネル型TFT453とnチャネル型TFT454の断面図のみを示しているが、これらのTFTを用いて、本発明の表示装置が具備する薄膜トランジスタを同一基板上に形成することができる。

【0092】

本実施例で説明した薄膜トランジスタの構造はあくまで一実施例であり、図9〜11に示した作製工程及び構造に限定される必要はない。公知の薄膜トランジスタ作製方法によって、本発明の表示装置が具備する薄膜トランジスタを同一基板上に形成することができる。

【0093】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、基板上に薄膜トランジスタで形成された遅延回路を設ける必要はないといった利点を得ることができる。

【実施例2】

【0094】

本実施例では、アクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。図12に示すように、図11(B)の状態の基板上に層間膜461、462を形成し、その上に第2の画素電極463を形成し、その上に配向膜551を形成する。本実施例では配向膜としてポリイミド膜を用いる。また、対向基板552には、透明導電膜553と、配向膜554とを形成する。なお、対向基板には必要に応じてカラーフィルターや遮蔽膜を形成しても良い。

【0095】

次に、配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するように調節する。そして、画素部と、駆動回路が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。

【0096】

その後、両基板の間に液晶555を注入し、封止材(図示せず)によって完全に封止する。液晶には公知の液晶材料を用いれば良い。このようにして図5に示すアクティブマトリクス型液晶表示装置が完成する。

【0097】

次に、このアクティブマトリクス型液晶表示装置の構成を、図13の斜視図を用いて説明する。アクティブマトリクス基板は、ガラス基板701上に形成された、画素部702と、ゲート側駆動回路703と、ソース側駆動回路704で構成される。画素部の画素TFT705はnチャネル型TFTであり、画素電極706及び保持容量707に接続される。

【0098】

また、周辺に設けられる本発明のコントロール回路713はFPCを介してゲート側駆動回路703と、ソース側駆動回路704に接続されている。ゲート側駆動回路703と、ソース側駆動回路704はそれぞれゲート配線708とソース配線709で画素部702に接続されている。また、FPC710が接続された外部入出力端子711にはコントロール回路713まで信号を伝達するための入出力配線(接続配線)712が設けられている。また、614は対向基板である。

【0099】

本実施例で説明したアクティブマトリクス型液晶表示装置の構成はあくまで一実施例であり、図12、図13に示した構造に限定される必要はない。公知のアクティブマトリクス型液晶表示装置の作製方法によって、本発明の表示装置を得ればよい。

【0100】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例3】

【0101】

本実施例では、薄膜トランジスタで構成された副画素を有する画素の等価回路と、その動作について説明する。ここでは画素にEL素子に代表される発光素子を有する構成について説明する。

【0102】

図14には、発光素子2001と、ビデオ信号が入力される信号線2002、ビデオ信号の画素への入力を制御するスイッチング用のトランジスタ2003、発光素子2001の発光または非発光を制御する駆動用のトランジスタ2004、ビデオ信号の電位を保持するための容量素子2005を有する副画素の等価回路を示す。各トランジスタの特性はエンハンスメント型、又はディプリーション型トランジスタを用いることができる。

【0103】

本実施の形態では、スイッチング用のトランジスタ2003をnチャネル型トランジスタ、駆動用トランジスタ2004をpチャネル型トランジスタとする。

【0104】

容量素子2005は、駆動用トランジスタ2004のゲート容量が大きく、各トランジスタからのリーク電流が許容範囲である場合、設ける必要はない。

【0105】

このような画素構成の接続関係を示す。スイッチング用トランジスタ2003のゲート電極は走査線2006に接続され、第1の電極は信号線2002に接続され、第2の電極は駆動用トランジスタ2004のゲート電極に接続されている。駆動用トランジスタ2004の第1の電極は電源線2007に接続され、駆動用トランジスタ2004のゲート・ソース間には容量素子2005が設けられている。容量素子2005はスイッチング用トランジスタ2003が非選択状態(オフ状態)にあるとき、駆動用トランジスタ2004のゲート・ソース間の電位差を保持する、つまりビデオ信号の電位を保持するように接続されている。そのため、容量素子の一方の電極は駆動用トランジスタ2004のゲート電極に接続され、他方の電極は電源線2007に接続されている。

【0106】

このような副画素を多数有し、各発光素子からの発光面積を制御する面積階調表示を行なう。

【0107】

次に副画素における各トランジスタの具体的な動作について、図15に示すタイミングチャートを用いて説明する。なお図21(A)は、縦軸は走査線、横軸は時間のときのタイミングチャートを示し、図15(B)はj行目の走査線Gjのタイミングチャートを示す。

【0108】

表示装置は、そのフレーム周波数を通常60Hz程度とする。つまり、1秒間に60回程度の画面の描画が行われ、画面の描画を1回行なう期間を1フレーム期間(単位フレーム期間)と呼ぶ。副画素は図15(A)に示すように、1フレーム期間に、書き込み期間Ta、発光期間Tsとを行なう。

【0109】

書き込み期間Taにおいて、順次走査線2006が選択されると、走査線2006に接続されているスイッチング用トランジスタ2003がオンとなる。そしてスイッチング用トランジスタ2003がオンとなると、信号線から入力されるビデオ信号によって容量素子2005に電荷が蓄積される。この電荷が駆動用トランジスタ2004のしきい値電圧Vth以上となると、駆動用トランジスタ2004がオンとなり、発光素子2001が発光する。

【0110】

そして発光素子2001は、供給される電流に見合った輝度で発光し、発光期間Tsとなる。

【0111】

発光期間Tsでは、走査線2006の電位を制御することでスイッチング用トランジスタ2003をオフとし、書き込み期間Taにおいて書き込まれたビデオ信号の電位を容量素子2005により保持している。その結果、発光素子2001は発光し続ける。

【0112】

また書き込み期間Taにおいて、信号線から入力されるビデオ信号によって駆動用トランジスタ2004がオフとなる場合、発光期間Tsでは、容量素子2005には電位が保持されていないため、発光素子は非発光となっている。

【0113】

すなわち、書き込み期間Taにおいて駆動用トランジスタ2004をオンとする場合、発光期間Tsではビデオ信号の電位が容量素子2005によって保持されているので、発光し続けている。逆に、書き込み期間Taにおいて駆動用トランジスタ2004をオフとする場合、発光期間Tsではビデオ信号の電位は容量素子2005によって保持されず、非発光となっている。

【0114】

このように、発光素子を発光、又は非発光とすることにより階調表示を行なう。特に、各副画素における発光素子からの発光面積に重みをつけた状態で、発光素子を発光、又は非発光とすることにより面積階調表示を行なう。

【0115】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例4】

【0116】

本実施例では、図14に示す画素回路に対応する上面図について説明する。

【0117】

図14に相当する上面図を示す図16(A)には、信号線2401、電源線2409、走査線2408、スイッチング用のトランジスタ2403、駆動用のトランジスタ2404、第1の副画素の発光素子の第1電極2407a、第1の副画素の発光素子2410a、第2の副画素の発光素子の第1電極2407b、第1の副画素の発光素子2410b、容量素子2406a、2406b、グラウンド線GNDを示す。また、図16(A)に示す条面図に対応する回路図を図16(B)に示す。なお、本実施例では容量素子について容量素子2406a、2406bの複数の構成としたがどちらか一方であってもよいし、設けなくてもよい。

【0118】

図16において、各トランジスタがトップゲート構造の場合は、基板、半導体層、ゲート絶縁膜、走査線、層間絶縁膜、信号線、の順で膜が構成される。ボトムゲート構造の場合は、基板、走査線、ゲート絶縁膜、半導体層、層間絶縁膜、信号線、の順で膜が構成される。

【0119】

図24では、信号線2401と平行して、電源線2409が形成されている。そのため、信号線2408、電源線2409は同一導電膜をパターニングして得る。

【0120】

スイッチング用のトランジスタ2403は半導体膜に対して二つのゲート電極が設けられたダブルゲート型構造を有し、走査線2408の一部がこれらゲート電極として機能している。またスイッチング用のトランジスタ2403の第1の電極は、コンタクトホールを介して信号線2401と接続され、第2の電極は、容量素子2406a、2406bと接続している。さらに容量素子2406bの一方の電極は、駆動用のトランジスタ2404のゲート電極と同一導電膜から構成され、他方の電極に相当する半導体膜は、電源線2409とコンタクトホールを介して接続されている。

【0121】

駆動用のトランジスタ2404のゲート電極は、固定電位を有する電源線2409とコンタクトホールを介して接続され、第2の電極は、信号線と同一導電膜により形成された配線と接続され、当該配線上に発光素子の第1電極2407及び2407bが形成され、接続している。配線と陽極は、コンタクトホールを介して接続されてもよい。

【0122】

なお、スイッチングトランジスタ2403、及び駆動用のトランジスタ2404のチャネル形成領域が、各々2つ形成されるダブルゲート構造について説明したが、チャネル形成領域が一つ形成されるシングルゲート構造または三つ形成されるトリプルゲート構造であってもよい。あるいは、チャネル形成領域の上下にゲート絶縁膜を介して配置された2つのゲート電極を有するデュアルゲート型やその他の構造としてもよい。

【0123】

発光素子の陽極は、ITO(indium tin oxide:インジウム錫酸化物)を代表とする透明導電膜から形成され、その面積比は2407a:2407b=1:2となるように設けられ、陽極上には電界発光層、及び陰極を形成する。そして、信号線2401から入力されるビデオ信号に基づき、電界発光層は発光状態、又は非発光状態となる。その発光面積に1:2と重みをつけて、その選択により面積階調表示を行なう。

【0124】

なお、本発明の表示装置の画素周辺における配線の構成は多岐にわたり、本明細書に列挙した構成に特に限定されないものであることを付記する。

【0125】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例5】

【0126】

本実施の形態では、副画素の断面の拡大図を示す。なお本実施の形態では、トランジスタとして多結晶シリコンを有する薄膜トランジスタ(TFT)を用いる場合で説明する。勿論、本発明の表示装置において、トランジスタは多結晶シリコンで形成されたものに限定されるものではなく、アモルファスシリコン等の半導体特性を有する化合物であればよいことを付記する。

【0127】

図17(A)に示すように、絶縁表面を有する基板2800に設けられたpチャネル型の駆動用のトランジスタ2801は、レーザ照射や加熱による結晶化処理、或いはニッケル、チタンなどの金属元素の触媒作用を用いて結晶化処理が行われた結晶性半導体膜を有する。半導体膜上にはゲート絶縁膜を介してゲート電極及びゲート線が設けられており、ゲート電極下の半導体膜がチャネル形成領域となる。ゲート電極をマスクとして自己整合的にボロン等の不純物元素を半導体膜に添加し、ソース領域及びドレイン領域となる不純物領域が形成される。ゲート電極を覆うように第1の絶縁膜が設けられており、第1の絶縁膜には不純物領域上にコンタクトホールが形成されている。コンタクトホールには配線が形成され、ソース配線及びドレイン配線として機能している。ドレイン電極と電気的に接続するように、発光素子の第1電極2811が設けられる。そして、第1電極2811を覆うように第2の絶縁膜が設けられ、第2の絶縁膜の第1電極上に開口部を形成する。開口部には、電界発光層2812が設けられ、電界発光層や第2の絶縁膜を覆うように発光素子の第2電極2813が設けられる。

【0128】

電界発光層2812は、第1電極2811側から順に、HIL(ホール注入層)、HTL(ホール輸送層)、EML(発光層)、ETL(電子輸送層)、EIL(電子注入層)の順に積層されている。代表的には、HILとしてCuPc、HTLとしてα−NPD、ETLとしてBCP、EILとしてBCP:Liをそれぞれ用いる。

【0129】

また、電界発光層2812として、フルカラー表示とする場合、赤色(R)、緑色(G)、青色(B)の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法、またはインクジェット法などによって選択的に形成すればよい。具体的には、HILとしてCuPcやPEDOT、HTLとしてα−NPD、ETLとしてBCPやAlq3、EILとしてBCP:LiやCaF2をそれぞれ用いる。また例えばEMLは、R、G、Bのそれぞれの発光色に対応したドーパント(Rの場合DCM等、Gの場合DMQD等)をドープしたAlq3を用いればよい。なお、上記電界発光層の積層構造に限定されない。

【0130】

より具体的な電界発光層の積層構造は、赤色の発光を示す電界発光層2812を形成する場合、例えば、CuPcを30nmし、α−NPDを60nmした後、同一のマスクを用いて、赤色の発光層としてDCM2及びルブレンが添加されたAlq3を40nmし、電子輸送層としてBCPを40nmし、電子注入層としてLiが添加されたBCPを1nmする。また、緑色の発光を示す電界発光層2812を形成する場合、例えば、CuPcを30nmし、α―NPDを60nmした後、同一の蒸着マスクを用いて、緑色の発光層としてクマリン545Tが添加されたAlq3を40nm、電子輸送層としてBCPを40nmし、電子注入層としてLiが添加されたBCPを1nmする。また、青色の発光を示す電界発光層2812を形成する場合、例えば、CuPcを30nmし、α−NPDを60nmした後、同一のマスクを用いて発光層としてビス[2−(2−ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛:Zn(PBO)2を10nmし、電子輸送層としてBCPを40nmし、電子注入層としてLiが添加されたBCPを1nmする。

【0131】

以上、各色の電界発光層のうち、共通しているCuPcやα−NPDは、画素部全面に形成することができる。またマスクは、各色で共有することもでき、例えば、赤色の電界発光層を形成後、マスクをずらして、緑色の電界発光層、再度マスクをずらして青色の電界発光層を形成することができる。形成する各色の電界発光層の順序は適宜設定すればよい。

【0132】

また白色の発光を示す電界発光層を形成する場合、カラーフィルター、又はカラーフィルター及び色変換層などを別途設けることによってフルカラー表示を行なうことができる。カラーフィルターや色変換層は、第2の基板に設けた後、張り合わせればよい。

【0133】

また第1電極との仕事関数を考慮して材料を選択する。例えば、第1電極を陽極とし、第2電極を陰極とする場合で説明する。

【0134】

第1電極としては、仕事関数の大きい(仕事関数4.0eV)金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることが好ましい。具体例な材料としては、ITO(indium tin oxide)、酸化インジウムに2〜20%の酸化亜鉛(ZnO)を混合したIZO(indium zinc oxide)の他、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、または金属材料の窒化物(TiN)等を用いることができる。

【0135】

一方、第2電極としては、仕事関数の小さい(仕事関数3.8eV以下)金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることが好ましい。具体的な材料としては、元素周期律の1族または2族に属する元素、すなわちLiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、およびこれらを含む合金(Mg:Ag、Al:Li)や化合物(LiF、CsF、CaF2)の他、希土類金属を含む遷移金属を用いて形成することができる。但し、第2の電極は透光性を有するため、これら金属、又はこれら金属を含む合金を非常に薄く形成し、ITO等の金属(合金を含む)との積層により形成する。

【0136】

これら第1電極、及び第2電極は蒸着法、スパッタリング法等により形成することができる。

【0137】

但し画素構成により、第1電極及び第2電極のいずれも陽極、又は陰極となりうる。例えば、駆動用のトランジスタの極性をnチャネル型とし、第1の電極を陰極、第2の電極と陽極とすることができる。

【0138】

その後、窒素を含むパッシベーション膜2814をスパッタリング法やCVD法により形成し、水分や酸素の侵入を防止する。このとき形成される空間には、窒素を封入し、さらに乾燥剤を配置してもよい。また透光性を有し、吸水性の高い樹脂を充填してもよい。さらに第1電極、第2電極、その他の電極により、表示手段の側面を覆って酸素や水分の侵入を防ぐこともできる。その後、封止基板2815を張り合わせる。

【0139】

またコントラストを高めるため、偏光板又は円偏光板を設けてもよい。例えば、表示面の一面又は両面に偏光板、若しくは円偏光板を設けることができる。

【0140】

このように形成された副画素を有する表示装置は、第1電極2811及び第2電極2813が透光性を有する。そのため、信号線から入力されるビデオ信号に応じた輝度で発光素子から光が両矢印方向に射出する。

【0141】

図17(A)のように、発光素子を有する副画素の発光面積、つまり透明導電膜の面積に重みをつける面積階調表示であって、両方向に光が射出される表示装置は、設計上、透明導電膜の面積を大きくすることができる。その結果、非発光状態での透過率を高くすることができ好ましい。

【0142】

図17(B)は、光の射出方向が封止基板2815側のみである。そのため第1電極2811は非透光性、好ましくは反射性の高い導電膜とし、第2電極2813は透光性を有する導電膜とする。その他の構成は図17(A)と同様であるため説明を省略する。

【0143】

図17(C)は、光の射出方向が基板2800側のみである。そのため第1電極2811は透光性を有する導電膜とし、第2電極2813は非透光性、好ましくは反射性の高い導電膜とする。その他の構成は図17(A)と同様であるため説明を省略する。

【0144】

図17(B)、図17(C)のように、光の射出方向とならない側に設けられた発光素子の電極に、反射性の高い導電膜を用いることにより光を有効利用することができる。

【0145】

本実施例において、透光性を有する導電膜を得るためには、非透光性を有する導電膜を、透光性を有するように薄く形成し、その上に透光性を有する導電膜を積層してもよい。

【0146】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例6】

【0147】

本実施例においては、本発明の表示装置を表示部に有する電子機器の構成例について説明する。

【0148】

発光素子を含む画素領域を備えた表示装置を用いた電子機器として、テレビジョン装置(テレビ、テレビジョン受信機)、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(携帯電話機)、PDA等の携帯情報端末、携帯型ゲーム機、モニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。これらの電子機器の表示部に本発明の表示装置を適用することができる。その電子機器の具体例について、図18を参照して説明する。

【0149】

図18(A)に示す本発明の表示装置を用いた携帯情報端末は、本体9201、表示部9202等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(B)に示す本発明の表示装置を用いたデジタルビデオカメラは、表示部9701、9702等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(C)に示す本発明の表示装置を用いた携帯端末は、本体9101、表示部9102等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(D)に示す本発明の表示装置を用いた携帯型のテレビジョン装置は、本体9301、表示部9302等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(E)に示す本発明の表示装置を用いた携帯型のコンピュータは、本体9401、表示部9402等を含み、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(F)に示す本発明の表示装置を用いたテレビジョン装置は、本体9501、表示部9502等を含み、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。

【0150】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【図面の簡単な説明】

【0151】

【図1】本発明の一実施形態を示す図。

【図2】コントロール回路の第1の構成を示す図。

【図3】JKフリップフロップ回路の回路図。

【図4】Dフリップフロップ回路の回路図。

【図5】コントロール回路のタイミングチャートを示す図。

【図6】ソース線駆動回路のタイミングチャートを示す図。

【図7】ゲート線駆動回路とソース線駆動回路のタイミングチャートを示す図。

【図8】コントロール回路の第2の構成を示す図。

【図9】本発明の表示装置の断面図。

【図10】本発明の表示装置の断面図。

【図11】本発明の表示装置の断面図。

【図12】本発明の表示装置を説明するための図。

【図13】本発明の表示装置における斜視図。

【図14】本発明の表示装置の画素の回路図を示す図。

【図15】本発明の表示装置を説明するための図。

【図16】本発明の表示装置における画素の上面図。

【図17】本発明の表示装置の画素における断面図。

【図18】本発明の実施例5の電子機器の図。

【図19】本発明の従来例を説明する図。

【符号の説明】

【0152】

101 ソース線駆動回路

102 ゲート線駆動回路

103 ソース信号線

104 ゲート信号線

105 画素

106 画素領域

107 タイミングコントロール回路

108 副画素

201 DFF

202 第1のJKFF

203 第2のJKFF

204 バッファ

205 インバータ

206 第1のNAND

209 ソース線駆動回路

210 ゲート線駆動回路

301 Hレベル

302 Hレベル

303 Hレベル

304 パルス

305 Hレベル

306 Hレベル

307 Hレベル

308 Hレベル

401 ガラス基板

402 ブロッキング層

403 半導体層

404 半導体層

405 半導体層

406 半導体層

407 ゲート絶縁膜

408a 第1の導電膜

408b 第2の導電膜

409 マスク

410 導電層

410a 第1の導電膜

410b 第2の導電膜

411 導電層

411a 第1の導電膜

411b 第2の導電膜

412 導電層

412a 第1の導電膜

412b 第2の導電膜

413 導電層

413a 第1の導電膜

413b 第2の導電膜

414 導電層

414a 第1の導電膜

414b 第2の導電膜

415 導電層

415a 第1の導電膜

415b 第2の導電膜

416 ゲート絶縁膜

417 第1の不純物領域

418 第1の不純物領域

419 第1の不純物領域

420 第1の不純物領域

421 導電層

421a 第1の導電膜

421b 第2の導電膜

422 導電層

422a 第1の導電膜

422b 第2の導電膜

423 導電層

423a 第1の導電膜

423b 第2の導電膜

424 導電層

424a 第1の導電膜

424b 第2の導電膜

425 導電層

425a 第1の導電膜

425b 第2の導電膜

426 導電層

426a 第1の導電膜

426b 第2の導電膜

427 第2の不純物領域

428 第2の不純物領域

429 第2の不純物領域

430 第2の不純物領域

431 導電層

431a 第1の導電膜

431b 第2の導電膜

432 導電層

432a 第1の導電膜

432b 第2の導電膜

433 導電層

433a 第1の導電膜

433b 第2の導電膜

434 導電層

434a 第1の導電膜

434b 第2の導電膜

435 導電層

435a 第1の導電膜

435b 第2の導電膜

436 導電層

436a 第1の導電膜

436b 第2の導電膜

437 ゲート絶縁膜

438 レジストマスク

439 レジストマスク

440a 第3の不純物領域

440b 第3の不純物領域

440c 第3の不純物領域

441 第1の絶縁膜

442 第2の絶縁膜

443 第3の絶縁膜

444 ソースまたはドレイン配線

445 ソースまたはドレイン配線

446 ソースまたはドレイン配線

447 ソースまたはドレイン配線

448 接続電極

449 ゲート配線

450 第1の画素電極

451 周辺回路

452 画素部

453 pチャネル型TFT

454 nチャネル型TFT

455 画素TFT

456 保持容量

461 層間膜

462 層間膜

463 画素電極

501 スタートパルス

502 スタートパルス

503 サンプリングパルス

504 デジタル映像信号

505 デジタル映像信号

506 デジタル映像信号505

507 期間

508 期間

509 出力パルス

601 DFF

602 JKFF

603 インバータ

604 バッファ

605 タイミングコントロール回路

606 ソース線駆動回路

607 ゲート線駆動回路

551 配向膜

552 対向基板

553 透明導電膜

554 配向膜

555 液晶

601 ガラス基板

602 画素部

603 ゲート側駆動回路

604 ソース側駆動回路

605 画素TFT

606 画素電極

607 保持容量

608 ゲート配線

609 ソース配線

610 FPC

611 外部入出力端子

612 入出力配線

613 入出力配線

614 対向基板

701 ガラス基板

702 画素部

703 ゲート側駆動回路

704 ソース側駆動回路

705 画素TFT

706 画素電極

707 保持容量

708 ゲート配線

709 ソース配線

710 FPC

711 外部入出力端子

712 入出力配線

713 コントロール回路

714 対向基板

2001 発光素子

2002 信号線

2003 スイッチング用のトランジスタ

2004 駆動用のトランジスタ

2005 容量素子

2006 走査線

2007 電源線

2401 信号線

2403 スイッチング用のトランジスタ

2404 駆動用のトランジスタ

2406a 容量素子

2406b 容量素子

2407a 第1電極

2407b 第1電極

2408 走査線

2409 電源線

2410a 発光素子

2410b 発光素子

2800 基板

2801 トランジスタ

2811 第1電極

2812 電界発光層

2813 第2電極

2814 パッシベーション膜

2815 封止基板

9101 本体

9102 表示部

9201 本体

9202 表示部

9301 本体

9302 表示部

9401 本体

9402 表示部

9501 本体

9502 表示部

9701 表示部

9702 表示部

【技術分野】

【0001】

本発明は、画素がマトリクス状に配置された画素領域を有する表示装置及びに関する。特に副画素を有する画素がマトリクス状に配置された画素領域を有する表示装置に関する。

【背景技術】

【0002】

液晶ディスプレイ(LCD)や、エレクトロルミネッセンス(EL)ディスプレイ等をはじめとする表示装置の階調表示方式の一つである面積階調方式は、画素の発光がオン状態とオフ状態の二値であるので、映像信号処理のためのDAコンバータ回路の実装の必要がない。また時間階調方式でみられる1フレームを複数のサブフレームへと分割する必要がない。そのため、映像信号を順次駆動回路に入力し、画素領域における表示に反映させることが出来る。したがって大規模なフレームメモリを実装する必要がなく、低周波数でディスプレイを動作させることができる。そのため、面積階調方式は、低消費電力化、低コスト化が実現できる表示方式である。

【0003】

しかしながら面積階調方式は副画素(サブ画素ともいう)を含む構成であるため、走査線の数が増加することによる駆動回路と実装コストの増大という問題があった。

【0004】

そこで図18のようにソース線駆動回路(SD)とゲート線駆動回路(GD)とそれぞれのバッファー回路(BUF)と画素マトリクスを同一基板(SUB)上に形成する。そして、ソース線駆動回路とゲート線駆動回路を制御する信号は、基板の外部に実装されたコントロール回路(CTL)から入力されている構成が提案されている(特許文献1参照)。

【特許文献1】特開平10−068931号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

副画素を有する画素がマトリクス状に配置された画素領域を有する構成の面積階調方式では、D/Aコンバータ回路と大規模なフレームメモリを実装しない簡単な構成が可能である。しかしながら、上記特許文献1に記載の方法によるとコントロール回路を外付けすることによりICの実装コストがかかるという問題があった。

【0006】

さらに外付けICから信号を外部接続端子やFPC(Flexible Printed Circuit)を介して入力する場合、駆動回路に信号が入力されるまで外部接続端子とFPCとの接触の状態や外部のノイズの影響等によって、スタートパルス信号よりも、クロック信号が遅延してしまい、駆動回路内のシフトレジスタ回路が誤作動し、正常表示が出来なくなる問題があるため、駆動回路の入力部に遅延回路を設ける必要がある。

【0007】

本発明は前述の課題に鑑み、ごく単純な回路を同一基板上に形成するだけで外部接続端子数を減少させ、外付け部品点数を削減し低コスト化が実現でき、かつクロック信号の遅延を防ぐことのできる表示装置を提供するものである。

【課題を解決するための手段】

【0008】

本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路及び前記ゲート信号線駆動回路を駆動するための信号を出力する回路を有する構成とした。

【0009】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力する構成とした。

【0010】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号は、JKフリップフロップ回路、Dフリップフロップ回路及び複数のインバータ回路を有する回路より出力される構成とした。

【0011】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力される構成とした。

【0012】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力される構成とした。

【0013】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力される構成とした。

【0014】

また別の本発明の表示装置の一は、副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力される構成とした。

【0015】

また本発明において、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号がJKフリップフロップを介して出力される信号であってもよい

【発明の効果】

【0016】

本発明では、コントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。

【0017】

また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はない。

【発明を実施するための最良の形態】

【0018】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0019】

なお本明細書において、各素子間の接続は、電気的に接続されていることを示す。そのため、接続関係を有する素子間に、半導体素子やスイッチング素子等を介して接続することもありうる。

【0020】

また本明細書において、トランジスタのソース電極及びドレイン電極は、トランジスタの構成上、ゲート電極以外の電極を便宜上区別するために採用されている名称である。本発明において、トランジスタの極性に限定されない構成の場合、その極性を考慮すると、ソース電極及びドレイン電極の名称は変化する。そのため、ソース電極又はドレイン電極を、一方の電極及び他方の電極のいずれかとして記載することがある。

【0021】

(実施の形態1)

本実施の形態においては、本発明による表示装置の基本構成について説明する。図1は表示装置の模式図を示したものである。

【0022】

図1において、基板上に、ソース線駆動回路101、ゲート線駆動回路102、画素領域106、コントロール回路107が形成されている。画素領域106は、複数の画素105がマトリクス状に配置されており、各画素105は、複数の副画素108から構成されており、副画素108はソース信号線103、ゲート信号線104によって制御される。図1においては2つの副画素で構成しているがこれに限定されず、1つの画素において副画素が3つ以上設けられていればよいことを付記する。

【0023】

なお、本明細書においては、画素とは一つの画像を構成する色要素を具備するものであり、発光素子及び発光素子を駆動する素子(例えば薄膜トランジスタで構成される回路)を有する副画素を複数含むものとする。また本明細書においては、絵素とは、一つの最小の画像を表示するための色要素を構成する画素を具備するものであるとする。よって、R(赤)G(緑)B(青)の色要素からなるフルカラー表示装置の場合には、絵素とはRの色要素、Gの色要素、Bの色要素を含む画素から構成されているものとする。また、各副画素は、その面積の大きさ、形状が異なっていてもよいし、同じでもよい。

【0024】

ソース線駆動回路101は、クロック信号(SCK)、クロック反転信号(SCKB)、スタート信号(SSP)の入力により、シフトレジスタ回路(SRと略記することもある)、NAND回路において順次サンプリングパルスを出力する。その後、レベルシフタ、バッファにおいて、振幅変換あるいは増幅を受け、映像信号(Data)のサンプリグを行い、順次ソース信号線へと出力する。シフトレジスタの最終段以降の出力はゲート線駆動回路のパルス幅制御信号(PWC)として用いても良い。また、ソース線駆動回路101は基板上に設けられた薄膜トランジスタを有するものである。

【0025】

ゲート線駆動回路102は、クロック信号(GCK)、クロック反転信号(GCKB)、スタート信号(GSP)の入力により、SR、NAND回路において順次行選択パルスを出力する。前記行選択パルスはパルス幅を制御された後、レベルシフタ、バッファにおいて、振幅変換あるいは増幅を受け、順次、各行のゲート信号線を選択する。ゲート線駆動回路102は基板上に設けられた薄膜トランジスタを有するものである。

【0026】

コントロール回路107は、映像信号である垂直同期信号VSYNCと水平同期信号HSYNCとドットクロック信号(DCK)の入力により、ソース線駆動回路用スタート信号(SSP)、ソース線駆動回路用クロック信号(SCK)、ソース線駆動回路用クロック反転信号(SCKB)、ゲート線駆動回路用スタートパルス信号(GSP)、ゲート線駆動回路用クロック信号(GCK)、ゲート線駆動回路用クロック反転信号(GCKB)を出力する。コントロール回路107の信号出力部は信号の種類に応じてそれぞれ、ソース信号線駆動回路及びゲート信号線駆動回路の入力端それぞれの近傍に配置し、信号引き回し配線が短くなる構成をとる。

【0027】

図2にコントロール回路の第1の構成を示す。コントロール回路208は、フリップフロップ回路であるDフリップフロップ回路(以下、DFFという)と2つのJフリップフロップ回路(以下、JKFFという)と複数のインバータと複数のバッファと2つのNANDを有する。Jフリップフロップ回路の具体的な構成について、図3に示した回路を採用してもよい。またDフリップフロップ回路の具体的な構成については、図4に示した回路を採用すればよい。

【0028】

図2において、DFF201のCK端子にHSYNC信号線が電気的に接続されている。DFF201のQB端子はDFF201のD端子と電気的に接続されている。DFF201のPRESET端子はVSYNC信号線がインバータ205を介して電気的に接続されている。DFFのQ端子はバッファ204を介してゲート線駆動回路210のGCK信号線と電気的に接続されている。DFF201のQ端子はインバータ205とバッファ204を介してゲート線駆動回路210のGCKB信号線と電気的に接続されている。

【0029】

また、図2において、GCK信号線は第1のJKFF202のCK端子と電気的に接続されている。第1のNAND206の第1の入力端にはVSYNC信号線が電気的に接続されている。第1のNAND206の第2の入力端にはGCK信号線が電気的に接続されている。第1のNAND206の出力端には第1のJKFF202のPRESET端子と電気的に接続されている。

【0030】

また、図2において、第1のJKFF202のJ端子とK端子とQ端子が電気的に接続されている。第1のJKFF202のQ端子はバッファ204を介してゲート線駆動回路のGSP信号線と電気的に接続されている。DCK信号線は、バッファ204を介してソース線駆動回路209のSCK信号線と電気的に接続されている。前記DCK信号線は、インバータ205とバッファ204を介してソース線駆動回路209のSCK信号線と電気的に接続されている。

【0031】

また、図2において、HSYNC信号線は第2のNAND207の第1の入力端と電気的に接続されている。第2のNAND207の第2の入力端はSCK信号線と電気的に接続されている。第2のNAND207の出力端は第2のJKFF203のPRESET端子と電気的に接続されている。SCK信号線は第2のJKFF203のCK端子と電気的に接続されている。第2のJKFF203のJ端子とK端子とQ端子が電気的に接続されている。第2のJKFF203のQ端子はバッファを介してソース線駆動回路209のSSP信号線と電気的に接続されている。上記のバッファの個数は特に限定しない。

【0032】

図2に示すコントロール回路において、外部より入力される垂直同期信号VSYNCはインバータ回路205を介して、Dフリップフロップ回路201のPRESET端子に入力される。また外部より入力される水平同期信号HSYNCはDフリップフロップ回路のCK端子に入力される。そしてDフリップフロップ回路201の出力端子は、ゲート線駆動回路に入力されるゲートクロック信号GCK、及びインバータを介して出力される反転ゲートクロック信号GCKBを出力する。

【0033】

また、図2のコントロール回路において、外部より入力される垂直同期信号VSYNC及び前記ゲートクロック信号GCKが入力されるNAND回路206からの出力がJKフリップフロップ回路202のPRESET端子に入力される。また外部より入力される前記ゲートクロック信号GCKがJKフリップフロップ回路202のCK端子に入力される。そしてJKフリップフロップ回路202の出力端子は、ゲート線駆動回路に入力されるゲートスタートパルス信号GSPを出力する。

【0034】

また、図2のコントロール回路において、外部より入力されるドットクロック信号DCKは、バッファ回路を介してソース信号線駆動回路にソースクロック信号SCKとして出力される。また外部より入力されるドットクロック信号DCKはインバータ回路を介してソース線駆動回路に入力される反転ソースクロック信号SCKBとして出力される。

【0035】

また、図2のコントロール回路において、外部より入力される水平同期信号HSYNC及び外部より入力されるドットクロック信号DCKが入力されるNAND回路205からの出力がJKフリップフロップ回路203のPRESET端子に入力される。また外部より入力されるドットクロック信号DCKがJKフリップフロップ回路203のCK端子に入力される。そしてJKフリップフロップ回路203の出力端子は、ソース線駆動回路に入力されるソーススタートパルス信号GSPを出力する。

【0036】

次に図5にコントロール回路の動作を示す。

【0037】

HSYNCとほぼ同じタイミングでSSPが出力され、DCKとほぼ同じタイミングでSCKが出力され、SCKと反転した論理でSCKBが出力される。この時、入力信号と同じ波形であるが、SCKよりもSSPの方が遅延している。

【0038】

VSYNCのHレベル301の立ち上がりとほぼ同時に、GCKがHレベル305となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、HSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなる。次のHSYNCのHレベル303の立ち上がりとほぼ同時にGCKはHレベル306となる。

【0039】

VSYNCのHレベルのパルス301と同時に立ち上がるHSYNCのHレベルのパルス304を1番目とすると、偶数番目(2m)のHレベルの立ち上がりでGCKはLレベルとなり、奇数番目(2m+1)のHレベルの立ち上げ利でGCKはHレベルとなる。GCKBはGCKと反転した論理で出力される。

【0040】

VSYNCのHレベル301の立ち上がりとほぼ同時に立ち上がるGCKの最初のHレベル305の立ち上がりとほぼ同時に、GSPがHレベル308となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、次に来るHSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなり、次のVSYNCのHレベル307の立ち上がりまでLレベルを保ち続ける。この時GCKの1番目のHレベル305の立ち上がりよりもGSPの1番目のHレベル307の立ち上がりの方が遅延し、GCKの2番目のHレベル306の立ち上がりよりもGSPの1番目のHレベル307の立ち下がりの方が遅延する。

【0041】

図6に、図1におけるソース線駆動回路101の簡単なタイミングチャートを示し、以下にその動作について順次説明する。図6には、入力信号としてクロック信号(SCK、SCKB)、スタートパルス(SSP)、デジタル映像信号(Data)、出力信号として、1段目〜4段目、最終段のサンプリングパルス(SROut1〜4、最終)、ソース信号線出力(SLine1、SLine最終)を示している。

【0042】

まず、第1ライン期間(Period1)について説明する。クロック信号とスタートパルス501に従ってシフトレジスタが動作し、サンプリングパルス503を順次出力する。サンプリングパルス503はそれぞれ、デジタル映像信号のサンプリングを行い、ラッチ回路にデータを保持し順次ソース信号線に出力される。

【0043】

なお、第1ライン期間において、デジタル映像信号504は、全てHレベルを入力している。

【0044】

ここで、ソース信号線出力は、Hレベルとなる(期間507)。

【0045】

次に、第2ライン期間(Period2)に移る。第1ライン期間と同様に、クロック信号とスタートパルス502に従い、サンプリングパルス503が順次出力され、デジタル映像信号のサンプリングが行われる。

【0046】

なお、第2ライン期間において、デジタル映像信号505は、全てLレベルを入力している。

【0047】

このとき、ソース信号線出力は、全段においてLレベルとなる(期間508)。

【0048】

シフトレジスタ最終段以降の出力パルス509はPWC信号としてゲート線駆動回路で用いても良い。

【0049】

図7に、ゲート線駆動回路102とソース線駆動回路101のタイミングチャートを示し、以下にその動作について順次説明する。図7には、ゲート線駆動回路への入力信号としてクロック信号(GCK、GCKB)、スタートパルス(GSP)、出力信号として、1段目〜4段目のゲート線出力信号(GLine1〜4)を示している。

【0050】

クロック信号とスタートパルスに従ってシフトレジスタが動作し、パルス幅をPWCを用いて調整した後、順次ゲート信号線に出力される。

【0051】

上記ゲート信号線出力によりソース信号線出力(SLine1、SLine最終)を副画素に入力する行を選択する。

【0052】

本実施の形態の構成ではゲート線駆動回路のシフトレジスタで用いられているGCK信号線から直接GCKの立ち上がりエッジを用いて、GSPの立ち上がりと立ち下がりエッジを生成しているので、GCKがGSPよりも遅延することはない。

【0053】

本実施の形態ではソース線駆動回路のシフトレジスタで用いられているSCK信号線から直接SCKの立ち上がりエッジを用いて、SSPの立ち上がりと立ち下がりエッジを生成しているので、SCKがSSPよりも遅延することはない。

【0054】

本実施の形態の構成で用いたDFFはD端子とQB端子の接続によりTフリップフロップ(TFF)として動作するのでTFFに置き換えても良い。

【0055】

また、本実施の形態において、外部接続端子数を減少させるため、ソース線駆動回路のシフトレジスタの最終段以降の出力をゲート線駆動回路のパルス幅制御信号(PWC)として用いる構成もある。

【0056】

以上のように本実施の形態は、基板上に形成されたコントロール回路で、ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号を、ドットクロック信号を基にした信号及びドットクロック信号の反転信号を基にした信号として内部生成した信号として出力することができる。またソース信号線駆動回路を駆動するためのスタートパルス信号を、前記水平同期信号を基にした信号として内部生成した信号として出力することができる。またゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号を、垂直同期信号の反転信号及び水平同期信号が入力されるDフリップフロップ回路より出力される信号として内部生成した信号として出力することができる。またゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力される信号として内部生成した信号として出力することができる。前述のコントロール回路におけるソース信号線駆動回路及びゲート信号線駆動回路に出力される各種信号は、デジタル映像信号を入力し、デジタル出力を行う形式のドライバーを用いた表示装置であれば、LCD、ELディスプレイ等、多種の表示装置において、外部接続端子数を削減することが出来る。

【0057】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【0058】

(実施の形態2)

本実施形態においては、実施の形態1と別の構成について説明する。コントロール回路の第1の構成よりも素子数が少なく実装面積の節約できるコントロール回路の構成を図8に示す。

【0059】

フリップフロップ回路であるDFFとJKFFと複数のインバータ603と複数のバッファ604を有し、DFF601のCK端子にHSYNC信号線が電気的に接続されている。DFF601のQB端子はD端子と電気的に接続されている。DFF601のPRESET端子はVSYNC信号線がインバータを介して電気的に接続されている。DFF601のQ端子はバッファ604を介してゲート線駆動回路のGCK信号線と電気的に接続されている。DFF601のQ端子はインバータ603とバッファ604を介してGCKB信号線と電気的に接続されている。GCK信号線はJKFF602のCK端子と電気的に接続されている。JKFF602のPRESET端子はVSYNC信号線が電気的に接続されている。JKFF602のJ端子とK端子とQ端子が電気的に接続されている。JKFF602のQ端子はバッファを介してゲート線駆動回路607のGSP信号線と電気的に接続されている。HSYNC信号線はバッファ604を介してソース線駆動回路606のSCK信号線と電気的に接続されている。HSYNC信号線はインバータ603とバッファ604を介してソース線駆動回路606のSCKB信号線と電気的に接続され、HSYNC信号線はバッファ604を介してソース線駆動回路606のSSP信号線と接続されている。上記のバッファの個数は特に限定しない。

【0060】

図8に示すコントロール回路において、外部より入力される垂直同期信号VSYNCはインバータ回路603を介して、Dフリップフロップ回路601のPRESET端子に入力される。また外部より入力される水平同期信号HSYNCはDフリップフロップ回路のCK端子に入力される。そしてDフリップフロップ回路601の出力端子は、ゲート線駆動回路に入力されるゲートクロック信号GCK、及びインバータを介して出力される反転ゲートクロック信号GCKBを出力する。

【0061】

また、図8のコントロール回路において、外部より入力される垂直同期信号VSYNCはインバータ回路603を介して、JKフリップフロップ回路202のPRESET端子に入力される。また前記ゲートクロック信号GCKがJKフリップフロップ回路602のCK端子に入力される。そしてJKフリップフロップ回路

02の出力端子は、ゲート線駆動回路に入力されるゲートスタートパルス信号GSPを出力する。

【0062】

また、図8のコントロール回路において、外部より入力されるドットクロック信号DCKは、バッファ回路を介してソース信号線駆動回路にソースクロック信号SCKとして出力される。また外部より入力されるドットクロック信号DCKはインバータ回路を介してソース線駆動回路に入力される反転ソースクロック信号SCKBとして出力される。

【0063】

また、図8のコントロール回路において、外部より入力されるドットクロック信号DCKは、バッファ回路を介してソース信号線駆動回路にソーススタートパルス信号SSPとして出力される。

【0064】

実施の形態1と同様に図5を用いてコントロール回路の動作を示す。

【0065】

HSYNCとほぼ同じタイミングでSSPが出力され、DCKとほぼ同じタイミングでSCKが出力され、SCKと反転した論理でSCKBが出力される。この時のSSPとSCKのタイミングの前後関係は不明である。

VSYNCのHレベル301の立ち上がりとほぼ同時に、GCKがHレベル305となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、HSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなる。次のHSYNCのHレベル303の立ち上がりとほぼ同時にGCKはHレベル306となる。

VSYNCのHレベルのパルス301と同時に立ち上がるHSYNCのHレベルのパルス304を1番目とすると、偶数番目(2m)のHレベルの立ち上がりでGCKはLレベルとなり、奇数番目(2m+1)のHレベルの立ち上げ利でGCKはHレベルとなる。GCKBはGCKと反転した論理で出力される。

【0066】

VSYNCのHレベル301の立ち上がりとほぼ同時に、GSPがHレベル308となり、Hレベルを保ち続ける。VSYNCのHレベル301に対して、次に来るHSYNCのHレベル302の立ち上がりとほぼ同時にGCKはLレベルとなり、次のVSYNCのHレベル307の立ち上がりまでLレベルを保ち続ける。この時GCKの2番目のHレベル306の立ち上がりよりもGSPの1番目のHレベル307の立ち下がりのタイミングの方が遅延する。

【0067】

上記第2のコントロール回路構成はGSPの立ち下がりのタイミングのみが、GCKの立ち上がりのタイミングよりも遅延する。

【0068】

本実施の形態の構成ではVSYNCの立ち上がりエッジを用いて、GSPの立ち上がりエッジを生成し、GCKの立ち上がりエッジを用いて、GSPの立ち下がりエッジを生成している。

【0069】

本実施の形態の構成ではGSPの立ち下がりのタイミングがGCKの立ち上がりのタイミングよりも遅延する。

【0070】

本実施の形態の構成で用いたDFFはD端子とQB端子の接続によりTFFとして動作するのでTFFに置き換えても良い。

【0071】

なお、本実施の形態は、コントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【0072】

なお、本実施の形態は、本明細書中の実施例または実施の形態のいかなる記載とも自由に組み合わせて実施することが可能である。

【実施例1】

【0073】

以下に本発明の表示装置において、絶縁表面を有する基板上に薄膜トランジスタで作製する例について、作製手順を簡略に図9〜11を用いて示す。図9〜11に示す構成のアクティブマトリクス型表示装置は液晶表示装置やEL(Electro Luminescence)素子を用いた表示装置を実現することを可能とするものである。

【0074】

まず、図9(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミノホウケイ酸ガラスなどのガラス基板401上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成るブロッキング層402を形成する。例えば、プラズマCVD法でSiH4、NH3、N2Oから作製される酸化窒化シリコン膜を10〜200nm(好ましくは50〜100nm)形成し、同様にSiH4、N2Oから作製される酸化窒化水素化シリコン膜を50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。本実施例ではブロッキング層402を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させた構造として形成しても良い。

【0075】

島状に分割された半導体層403〜406は、非晶質構造を有する半導体膜を、レーザーアニール法やファーネスアニール炉を用いた熱処理により結晶構造を有する半導体膜(以下、結晶質半導体膜という)で形成する。この島状の半導体層403〜406の厚さは25〜80nm(好ましくは30〜60nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

【0076】

レーザーアニール法で結晶質半導体膜を作製するには、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO4レーザーを用いる。レーザー発振器から出力されるレーザー光は、光学系で線状に集光し半導体膜に照射する方法を用いる。アニールの条件は実施者が適宣選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数30Hzとし、レーザーエネルギー密度を100〜400mJ/cm2(代表的には200〜300mJ/cm2)とする。また、YAGレーザーを用いる場合には、第2高調波を用いパルス発振周波数1〜10kHzとし、レーザーエネルギー密度を300〜600mJ/cm2(代表的には350〜500mJ/cm2)とすると良い。そして幅100〜1000μm、例えば400μmで線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を80〜98%として行う。

【0077】

次いで、島状の半導体層403〜406を覆うゲート絶縁膜407を形成する。ゲート絶縁膜407はプラズマCVD法またはスパッタ法を用い、厚さを40〜150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、120nmの厚さとして酸化窒化シリコン膜を形成する。勿論、ゲート絶縁膜407はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

【0078】

そして、ゲート絶縁膜407上にゲート電極を形成するための第1の導電膜408aと第2の導電膜408bとを形成する。本実施例では、第1の導電膜408aを窒化タンタルまたはチタンで50〜100nmの厚さに形成し、第2の導電膜408bをタングステンで100〜300nmの厚さに形成する。これらの材料は、窒素雰囲気中における400〜600℃の熱処理でも安定であり、抵抗率が著しく増大することがない。

【0079】

次に図9(B)に示すように、レジストによるマスク409を形成し、ゲート電極を形成するための第1のエッチング処理を行う。エッチング方法に限定はないが、好適にはICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いる。エッチング用ガスにCF4とCl2を混合し、0.5〜2Pa、好ましくは1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した場合にはタングステン膜、窒化タンタル膜及びチタン膜の場合でも、それぞれ同程度の速度でエッチングすることができる。

【0080】

上記エッチング条件では、レジストによるマスクの形状と、基板側に印加するバイアス電圧の効果により端部をテーパー形状とすることができる。テーパー部の角度は25〜45度となるようにする。また、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。タングステンに対する酸化窒化シリコン膜の選択比は2〜4(代表的には3)であるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされる。こうして、第1のエッチング処理により第1の導電膜と第2の導電膜から成る第1の形状の導電層410〜415(第1の導電膜410a〜415aと第2の導電膜410b〜415b)を形成する。416はゲート絶縁膜であり、第1の形状の導電層で覆われない領域は20〜50nm程度エッチングされ薄くなる。

【0081】

そして図9(C)に示すように、第1のドーピング処理を行いn型の不純物(ドナー)をドーピングする。ドーピングの方法はイオンドープ法若しくはイオン注入法で行う。イオンドープ法の条件はドーズ量を1×1013〜5×1014/cm2として行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いる。この場合、加速電圧を制御(例えば、20〜60keV)して、第1の形状の導電層をマスクとして利用する。こうして、第1の不純物領域417〜420を形成する。例えば、第1の不純物領域417〜420おけるn型の不純物の濃度は1×1020〜1×1021/cm3の範囲で形成する。

【0082】

図10(A)で示す第2のエッチング処理は、同様にICPエッチング装置を用い、エッチングガスにCF4とCl2とO2を混合して、1Paの圧力でコイル型の電極に500WのRF電力(13.56MHz)を供給してプラズマを生成する。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、第1のエッチング処理に比べ低い自己バイアス電圧を印加する。このような条件によりタングステン膜を異方性エッチングし、第1の導電層である窒化タンタル膜またはチタン膜を残存させるようにする。こうして、第2の形状の導電層421〜426(第1の導電膜421a〜426aと第2の導電膜421b〜426b)を形成する。ゲート絶縁膜は第2の形状の導電層421〜426で覆われない領域はさらに20〜50nm程度エッチングされて膜厚が薄くなる。

【0083】

次いで、第2のドーピング処理を行う。第1のドーピング処理よりもドーズ量を下げ高加速電圧の条件でn型の不純物(ドナー)をドーピングする。例えば、加速電圧を70〜120keVとし、1×1013/cm2のドーズ量で行い、図9(C)で島状の半導体層に形成された第1の不純物領域の内側に第2の不純物領域427〜430を形成する。このドーピングは、第2の形状の導電層423b〜426bを不純物元素に対するマスクとして用い、第2の形状の導電層423a〜426aの下側の領域に不純物元素が添加されるようにドーピングする。この不純物領域は、第2の形状の導電層423a〜426aがほぼ同じ膜厚で残存していることから、第2の形状の導電層に沿った方向における濃度分布の差は小さく、1×1017〜1×1019/cm3の濃度でn型の不純物(ドナー)が含まれるように形成する。

【0084】

そして、図10(B)に示すように、第3のエッチング処理を行い、ゲート絶縁膜のエッチング処理を行う。その結果、第2の形状の導電層421a〜426aもエッチングされ、端部が後退して小さくなり、第3の形状の導電層431〜436(第1の導電膜431a〜436aと第2の導電膜431b〜436b)が形成される。437は残存するゲート絶縁膜であり、エッチングをさらに進めて半導体層の表面を露出させても良い。

【0085】

pチャネル型TFTに対しては、図10(C)に示すように、レジストマスク438、439を形成し、pチャネル型TFTを形成する島状の半導体層にp型の不純物(アクセプタ)をドーピングする。p型の不純物(アクセプタ)は13族に属する元素から選ばれ、典型的にはボロン(B)を用いる。第3の不純物領域440a〜440cの不純物濃度は2×1020〜2×1021/cm3となるようにする。第3の不純物領域にはリンが添加されているが、それ以上の濃度でボロンを添加して導電型を反転させておく。

【0086】

以上までの工程で半導体層に不純物領域が形成される。図10において、第3の形状の導電層433〜435はゲート電極となり、第3の形状の導電層436は容量配線となる。また、第3の形状の導電層431、432はソース線などの配線を形成する。

【0087】

次に、図11(A)では最初に、窒化シリコン膜(SiN:H)または酸化窒化シリコン膜(SiNxOy:H)から成る第1の絶縁膜441をプラズマCVD法で形成する。そして導電型の制御を目的としてそれぞれの島状の半導体層に添加された不純物元素を活性化する工程を行う。活性化はファーネスアニール炉を用いる熱アニール法で行うことが好ましい。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することもできる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施例では550℃で4時間の熱処理を行う。

【0088】

その後、第1の絶縁膜441上に窒化シリコン膜(SiN:H)または酸化窒化シリコン膜(SiNxOy:H)から成る第2の絶縁膜442を形成する。そして、350〜500℃で熱処理を行う。第2の絶縁膜442から放出される水素により半導体膜の水素化を行う。

【0089】

さらに、図11(B)で示すように有機樹脂からなる第3の絶縁膜443を約1000nmの厚さに形成する。有機樹脂膜としては、ポリイミド、アクリル、ポリイミドアミド等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜を用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成する。

【0090】

次に、第3の絶縁膜443、第2の絶縁膜442、第1の絶縁膜441に、コンタクトホールを形成し、アルミニウム(Al)、チタン(Ti)、タンタル(Ta)などを用いて、接続電極451及びソースまたはドレイン配線444〜447を形成する。また、画素部においては、第1の画素電極450、ゲート配線449、接続電極448を形成する。

【0091】

こうして、同一の基板上にpチャネル型TFT453とnチャネル型TFT454が形成される。図11(B)ではpチャネル型TFT453とnチャネル型TFT454の断面図のみを示しているが、これらのTFTを用いて、本発明の表示装置が具備する薄膜トランジスタを同一基板上に形成することができる。

【0092】

本実施例で説明した薄膜トランジスタの構造はあくまで一実施例であり、図9〜11に示した作製工程及び構造に限定される必要はない。公知の薄膜トランジスタ作製方法によって、本発明の表示装置が具備する薄膜トランジスタを同一基板上に形成することができる。

【0093】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、基板上に薄膜トランジスタで形成された遅延回路を設ける必要はないといった利点を得ることができる。

【実施例2】

【0094】

本実施例では、アクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。図12に示すように、図11(B)の状態の基板上に層間膜461、462を形成し、その上に第2の画素電極463を形成し、その上に配向膜551を形成する。本実施例では配向膜としてポリイミド膜を用いる。また、対向基板552には、透明導電膜553と、配向膜554とを形成する。なお、対向基板には必要に応じてカラーフィルターや遮蔽膜を形成しても良い。

【0095】

次に、配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するように調節する。そして、画素部と、駆動回路が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。

【0096】

その後、両基板の間に液晶555を注入し、封止材(図示せず)によって完全に封止する。液晶には公知の液晶材料を用いれば良い。このようにして図5に示すアクティブマトリクス型液晶表示装置が完成する。

【0097】

次に、このアクティブマトリクス型液晶表示装置の構成を、図13の斜視図を用いて説明する。アクティブマトリクス基板は、ガラス基板701上に形成された、画素部702と、ゲート側駆動回路703と、ソース側駆動回路704で構成される。画素部の画素TFT705はnチャネル型TFTであり、画素電極706及び保持容量707に接続される。

【0098】

また、周辺に設けられる本発明のコントロール回路713はFPCを介してゲート側駆動回路703と、ソース側駆動回路704に接続されている。ゲート側駆動回路703と、ソース側駆動回路704はそれぞれゲート配線708とソース配線709で画素部702に接続されている。また、FPC710が接続された外部入出力端子711にはコントロール回路713まで信号を伝達するための入出力配線(接続配線)712が設けられている。また、614は対向基板である。

【0099】

本実施例で説明したアクティブマトリクス型液晶表示装置の構成はあくまで一実施例であり、図12、図13に示した構造に限定される必要はない。公知のアクティブマトリクス型液晶表示装置の作製方法によって、本発明の表示装置を得ればよい。

【0100】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例3】

【0101】

本実施例では、薄膜トランジスタで構成された副画素を有する画素の等価回路と、その動作について説明する。ここでは画素にEL素子に代表される発光素子を有する構成について説明する。

【0102】

図14には、発光素子2001と、ビデオ信号が入力される信号線2002、ビデオ信号の画素への入力を制御するスイッチング用のトランジスタ2003、発光素子2001の発光または非発光を制御する駆動用のトランジスタ2004、ビデオ信号の電位を保持するための容量素子2005を有する副画素の等価回路を示す。各トランジスタの特性はエンハンスメント型、又はディプリーション型トランジスタを用いることができる。

【0103】

本実施の形態では、スイッチング用のトランジスタ2003をnチャネル型トランジスタ、駆動用トランジスタ2004をpチャネル型トランジスタとする。

【0104】

容量素子2005は、駆動用トランジスタ2004のゲート容量が大きく、各トランジスタからのリーク電流が許容範囲である場合、設ける必要はない。

【0105】

このような画素構成の接続関係を示す。スイッチング用トランジスタ2003のゲート電極は走査線2006に接続され、第1の電極は信号線2002に接続され、第2の電極は駆動用トランジスタ2004のゲート電極に接続されている。駆動用トランジスタ2004の第1の電極は電源線2007に接続され、駆動用トランジスタ2004のゲート・ソース間には容量素子2005が設けられている。容量素子2005はスイッチング用トランジスタ2003が非選択状態(オフ状態)にあるとき、駆動用トランジスタ2004のゲート・ソース間の電位差を保持する、つまりビデオ信号の電位を保持するように接続されている。そのため、容量素子の一方の電極は駆動用トランジスタ2004のゲート電極に接続され、他方の電極は電源線2007に接続されている。

【0106】

このような副画素を多数有し、各発光素子からの発光面積を制御する面積階調表示を行なう。

【0107】

次に副画素における各トランジスタの具体的な動作について、図15に示すタイミングチャートを用いて説明する。なお図21(A)は、縦軸は走査線、横軸は時間のときのタイミングチャートを示し、図15(B)はj行目の走査線Gjのタイミングチャートを示す。

【0108】

表示装置は、そのフレーム周波数を通常60Hz程度とする。つまり、1秒間に60回程度の画面の描画が行われ、画面の描画を1回行なう期間を1フレーム期間(単位フレーム期間)と呼ぶ。副画素は図15(A)に示すように、1フレーム期間に、書き込み期間Ta、発光期間Tsとを行なう。

【0109】

書き込み期間Taにおいて、順次走査線2006が選択されると、走査線2006に接続されているスイッチング用トランジスタ2003がオンとなる。そしてスイッチング用トランジスタ2003がオンとなると、信号線から入力されるビデオ信号によって容量素子2005に電荷が蓄積される。この電荷が駆動用トランジスタ2004のしきい値電圧Vth以上となると、駆動用トランジスタ2004がオンとなり、発光素子2001が発光する。

【0110】

そして発光素子2001は、供給される電流に見合った輝度で発光し、発光期間Tsとなる。

【0111】

発光期間Tsでは、走査線2006の電位を制御することでスイッチング用トランジスタ2003をオフとし、書き込み期間Taにおいて書き込まれたビデオ信号の電位を容量素子2005により保持している。その結果、発光素子2001は発光し続ける。

【0112】

また書き込み期間Taにおいて、信号線から入力されるビデオ信号によって駆動用トランジスタ2004がオフとなる場合、発光期間Tsでは、容量素子2005には電位が保持されていないため、発光素子は非発光となっている。

【0113】

すなわち、書き込み期間Taにおいて駆動用トランジスタ2004をオンとする場合、発光期間Tsではビデオ信号の電位が容量素子2005によって保持されているので、発光し続けている。逆に、書き込み期間Taにおいて駆動用トランジスタ2004をオフとする場合、発光期間Tsではビデオ信号の電位は容量素子2005によって保持されず、非発光となっている。

【0114】

このように、発光素子を発光、又は非発光とすることにより階調表示を行なう。特に、各副画素における発光素子からの発光面積に重みをつけた状態で、発光素子を発光、又は非発光とすることにより面積階調表示を行なう。

【0115】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例4】

【0116】

本実施例では、図14に示す画素回路に対応する上面図について説明する。

【0117】

図14に相当する上面図を示す図16(A)には、信号線2401、電源線2409、走査線2408、スイッチング用のトランジスタ2403、駆動用のトランジスタ2404、第1の副画素の発光素子の第1電極2407a、第1の副画素の発光素子2410a、第2の副画素の発光素子の第1電極2407b、第1の副画素の発光素子2410b、容量素子2406a、2406b、グラウンド線GNDを示す。また、図16(A)に示す条面図に対応する回路図を図16(B)に示す。なお、本実施例では容量素子について容量素子2406a、2406bの複数の構成としたがどちらか一方であってもよいし、設けなくてもよい。

【0118】

図16において、各トランジスタがトップゲート構造の場合は、基板、半導体層、ゲート絶縁膜、走査線、層間絶縁膜、信号線、の順で膜が構成される。ボトムゲート構造の場合は、基板、走査線、ゲート絶縁膜、半導体層、層間絶縁膜、信号線、の順で膜が構成される。

【0119】

図24では、信号線2401と平行して、電源線2409が形成されている。そのため、信号線2408、電源線2409は同一導電膜をパターニングして得る。

【0120】

スイッチング用のトランジスタ2403は半導体膜に対して二つのゲート電極が設けられたダブルゲート型構造を有し、走査線2408の一部がこれらゲート電極として機能している。またスイッチング用のトランジスタ2403の第1の電極は、コンタクトホールを介して信号線2401と接続され、第2の電極は、容量素子2406a、2406bと接続している。さらに容量素子2406bの一方の電極は、駆動用のトランジスタ2404のゲート電極と同一導電膜から構成され、他方の電極に相当する半導体膜は、電源線2409とコンタクトホールを介して接続されている。

【0121】

駆動用のトランジスタ2404のゲート電極は、固定電位を有する電源線2409とコンタクトホールを介して接続され、第2の電極は、信号線と同一導電膜により形成された配線と接続され、当該配線上に発光素子の第1電極2407及び2407bが形成され、接続している。配線と陽極は、コンタクトホールを介して接続されてもよい。

【0122】

なお、スイッチングトランジスタ2403、及び駆動用のトランジスタ2404のチャネル形成領域が、各々2つ形成されるダブルゲート構造について説明したが、チャネル形成領域が一つ形成されるシングルゲート構造または三つ形成されるトリプルゲート構造であってもよい。あるいは、チャネル形成領域の上下にゲート絶縁膜を介して配置された2つのゲート電極を有するデュアルゲート型やその他の構造としてもよい。

【0123】

発光素子の陽極は、ITO(indium tin oxide:インジウム錫酸化物)を代表とする透明導電膜から形成され、その面積比は2407a:2407b=1:2となるように設けられ、陽極上には電界発光層、及び陰極を形成する。そして、信号線2401から入力されるビデオ信号に基づき、電界発光層は発光状態、又は非発光状態となる。その発光面積に1:2と重みをつけて、その選択により面積階調表示を行なう。

【0124】

なお、本発明の表示装置の画素周辺における配線の構成は多岐にわたり、本明細書に列挙した構成に特に限定されないものであることを付記する。

【0125】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例5】

【0126】

本実施の形態では、副画素の断面の拡大図を示す。なお本実施の形態では、トランジスタとして多結晶シリコンを有する薄膜トランジスタ(TFT)を用いる場合で説明する。勿論、本発明の表示装置において、トランジスタは多結晶シリコンで形成されたものに限定されるものではなく、アモルファスシリコン等の半導体特性を有する化合物であればよいことを付記する。

【0127】

図17(A)に示すように、絶縁表面を有する基板2800に設けられたpチャネル型の駆動用のトランジスタ2801は、レーザ照射や加熱による結晶化処理、或いはニッケル、チタンなどの金属元素の触媒作用を用いて結晶化処理が行われた結晶性半導体膜を有する。半導体膜上にはゲート絶縁膜を介してゲート電極及びゲート線が設けられており、ゲート電極下の半導体膜がチャネル形成領域となる。ゲート電極をマスクとして自己整合的にボロン等の不純物元素を半導体膜に添加し、ソース領域及びドレイン領域となる不純物領域が形成される。ゲート電極を覆うように第1の絶縁膜が設けられており、第1の絶縁膜には不純物領域上にコンタクトホールが形成されている。コンタクトホールには配線が形成され、ソース配線及びドレイン配線として機能している。ドレイン電極と電気的に接続するように、発光素子の第1電極2811が設けられる。そして、第1電極2811を覆うように第2の絶縁膜が設けられ、第2の絶縁膜の第1電極上に開口部を形成する。開口部には、電界発光層2812が設けられ、電界発光層や第2の絶縁膜を覆うように発光素子の第2電極2813が設けられる。

【0128】

電界発光層2812は、第1電極2811側から順に、HIL(ホール注入層)、HTL(ホール輸送層)、EML(発光層)、ETL(電子輸送層)、EIL(電子注入層)の順に積層されている。代表的には、HILとしてCuPc、HTLとしてα−NPD、ETLとしてBCP、EILとしてBCP:Liをそれぞれ用いる。

【0129】

また、電界発光層2812として、フルカラー表示とする場合、赤色(R)、緑色(G)、青色(B)の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法、またはインクジェット法などによって選択的に形成すればよい。具体的には、HILとしてCuPcやPEDOT、HTLとしてα−NPD、ETLとしてBCPやAlq3、EILとしてBCP:LiやCaF2をそれぞれ用いる。また例えばEMLは、R、G、Bのそれぞれの発光色に対応したドーパント(Rの場合DCM等、Gの場合DMQD等)をドープしたAlq3を用いればよい。なお、上記電界発光層の積層構造に限定されない。

【0130】

より具体的な電界発光層の積層構造は、赤色の発光を示す電界発光層2812を形成する場合、例えば、CuPcを30nmし、α−NPDを60nmした後、同一のマスクを用いて、赤色の発光層としてDCM2及びルブレンが添加されたAlq3を40nmし、電子輸送層としてBCPを40nmし、電子注入層としてLiが添加されたBCPを1nmする。また、緑色の発光を示す電界発光層2812を形成する場合、例えば、CuPcを30nmし、α―NPDを60nmした後、同一の蒸着マスクを用いて、緑色の発光層としてクマリン545Tが添加されたAlq3を40nm、電子輸送層としてBCPを40nmし、電子注入層としてLiが添加されたBCPを1nmする。また、青色の発光を示す電界発光層2812を形成する場合、例えば、CuPcを30nmし、α−NPDを60nmした後、同一のマスクを用いて発光層としてビス[2−(2−ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛:Zn(PBO)2を10nmし、電子輸送層としてBCPを40nmし、電子注入層としてLiが添加されたBCPを1nmする。

【0131】

以上、各色の電界発光層のうち、共通しているCuPcやα−NPDは、画素部全面に形成することができる。またマスクは、各色で共有することもでき、例えば、赤色の電界発光層を形成後、マスクをずらして、緑色の電界発光層、再度マスクをずらして青色の電界発光層を形成することができる。形成する各色の電界発光層の順序は適宜設定すればよい。

【0132】

また白色の発光を示す電界発光層を形成する場合、カラーフィルター、又はカラーフィルター及び色変換層などを別途設けることによってフルカラー表示を行なうことができる。カラーフィルターや色変換層は、第2の基板に設けた後、張り合わせればよい。

【0133】

また第1電極との仕事関数を考慮して材料を選択する。例えば、第1電極を陽極とし、第2電極を陰極とする場合で説明する。

【0134】

第1電極としては、仕事関数の大きい(仕事関数4.0eV)金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることが好ましい。具体例な材料としては、ITO(indium tin oxide)、酸化インジウムに2〜20%の酸化亜鉛(ZnO)を混合したIZO(indium zinc oxide)の他、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、または金属材料の窒化物(TiN)等を用いることができる。

【0135】

一方、第2電極としては、仕事関数の小さい(仕事関数3.8eV以下)金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることが好ましい。具体的な材料としては、元素周期律の1族または2族に属する元素、すなわちLiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、およびこれらを含む合金(Mg:Ag、Al:Li)や化合物(LiF、CsF、CaF2)の他、希土類金属を含む遷移金属を用いて形成することができる。但し、第2の電極は透光性を有するため、これら金属、又はこれら金属を含む合金を非常に薄く形成し、ITO等の金属(合金を含む)との積層により形成する。

【0136】

これら第1電極、及び第2電極は蒸着法、スパッタリング法等により形成することができる。

【0137】

但し画素構成により、第1電極及び第2電極のいずれも陽極、又は陰極となりうる。例えば、駆動用のトランジスタの極性をnチャネル型とし、第1の電極を陰極、第2の電極と陽極とすることができる。

【0138】

その後、窒素を含むパッシベーション膜2814をスパッタリング法やCVD法により形成し、水分や酸素の侵入を防止する。このとき形成される空間には、窒素を封入し、さらに乾燥剤を配置してもよい。また透光性を有し、吸水性の高い樹脂を充填してもよい。さらに第1電極、第2電極、その他の電極により、表示手段の側面を覆って酸素や水分の侵入を防ぐこともできる。その後、封止基板2815を張り合わせる。

【0139】

またコントラストを高めるため、偏光板又は円偏光板を設けてもよい。例えば、表示面の一面又は両面に偏光板、若しくは円偏光板を設けることができる。

【0140】

このように形成された副画素を有する表示装置は、第1電極2811及び第2電極2813が透光性を有する。そのため、信号線から入力されるビデオ信号に応じた輝度で発光素子から光が両矢印方向に射出する。

【0141】

図17(A)のように、発光素子を有する副画素の発光面積、つまり透明導電膜の面積に重みをつける面積階調表示であって、両方向に光が射出される表示装置は、設計上、透明導電膜の面積を大きくすることができる。その結果、非発光状態での透過率を高くすることができ好ましい。

【0142】

図17(B)は、光の射出方向が封止基板2815側のみである。そのため第1電極2811は非透光性、好ましくは反射性の高い導電膜とし、第2電極2813は透光性を有する導電膜とする。その他の構成は図17(A)と同様であるため説明を省略する。

【0143】

図17(C)は、光の射出方向が基板2800側のみである。そのため第1電極2811は透光性を有する導電膜とし、第2電極2813は非透光性、好ましくは反射性の高い導電膜とする。その他の構成は図17(A)と同様であるため説明を省略する。

【0144】

図17(B)、図17(C)のように、光の射出方向とならない側に設けられた発光素子の電極に、反射性の高い導電膜を用いることにより光を有効利用することができる。

【0145】

本実施例において、透光性を有する導電膜を得るためには、非透光性を有する導電膜を、透光性を有するように薄く形成し、その上に透光性を有する導電膜を積層してもよい。

【0146】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【実施例6】

【0147】

本実施例においては、本発明の表示装置を表示部に有する電子機器の構成例について説明する。

【0148】

発光素子を含む画素領域を備えた表示装置を用いた電子機器として、テレビジョン装置(テレビ、テレビジョン受信機)、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(携帯電話機)、PDA等の携帯情報端末、携帯型ゲーム機、モニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。これらの電子機器の表示部に本発明の表示装置を適用することができる。その電子機器の具体例について、図18を参照して説明する。

【0149】

図18(A)に示す本発明の表示装置を用いた携帯情報端末は、本体9201、表示部9202等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(B)に示す本発明の表示装置を用いたデジタルビデオカメラは、表示部9701、9702等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(C)に示す本発明の表示装置を用いた携帯端末は、本体9101、表示部9102等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(D)に示す本発明の表示装置を用いた携帯型のテレビジョン装置は、本体9301、表示部9302等を含み、本発明により外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(E)に示す本発明の表示装置を用いた携帯型のコンピュータは、本体9401、表示部9402等を含み、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。図18(F)に示す本発明の表示装置を用いたテレビジョン装置は、本体9501、表示部9502等を含み、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化をすることができる。

【0150】

なお、本実施例は、本明細書中の他の実施の形態、実施例のいかなる記載とも自由に組み合わせて実施することが可能である。すなわちコントロール回路をソース線駆動回路とゲート線駆動回路と画素マトリクスを含む同一基板上に一体形成することにより、外部接続端子数を減少させ、外付け部品の実装面積を削減し低コスト化できる。また上記第コントロール回路の構成では、スタートパルス信号をクロック信号よりも遅延させるために、TFT基板上に遅延回路を設ける必要はないといった利点を得ることができる。

【図面の簡単な説明】

【0151】

【図1】本発明の一実施形態を示す図。

【図2】コントロール回路の第1の構成を示す図。

【図3】JKフリップフロップ回路の回路図。

【図4】Dフリップフロップ回路の回路図。

【図5】コントロール回路のタイミングチャートを示す図。

【図6】ソース線駆動回路のタイミングチャートを示す図。

【図7】ゲート線駆動回路とソース線駆動回路のタイミングチャートを示す図。

【図8】コントロール回路の第2の構成を示す図。

【図9】本発明の表示装置の断面図。

【図10】本発明の表示装置の断面図。

【図11】本発明の表示装置の断面図。

【図12】本発明の表示装置を説明するための図。

【図13】本発明の表示装置における斜視図。

【図14】本発明の表示装置の画素の回路図を示す図。

【図15】本発明の表示装置を説明するための図。

【図16】本発明の表示装置における画素の上面図。

【図17】本発明の表示装置の画素における断面図。

【図18】本発明の実施例5の電子機器の図。

【図19】本発明の従来例を説明する図。

【符号の説明】

【0152】

101 ソース線駆動回路

102 ゲート線駆動回路

103 ソース信号線

104 ゲート信号線

105 画素

106 画素領域

107 タイミングコントロール回路

108 副画素

201 DFF

202 第1のJKFF

203 第2のJKFF

204 バッファ

205 インバータ

206 第1のNAND

209 ソース線駆動回路

210 ゲート線駆動回路

301 Hレベル

302 Hレベル

303 Hレベル

304 パルス

305 Hレベル

306 Hレベル

307 Hレベル

308 Hレベル

401 ガラス基板

402 ブロッキング層

403 半導体層

404 半導体層

405 半導体層

406 半導体層

407 ゲート絶縁膜

408a 第1の導電膜

408b 第2の導電膜

409 マスク

410 導電層

410a 第1の導電膜

410b 第2の導電膜

411 導電層

411a 第1の導電膜

411b 第2の導電膜

412 導電層

412a 第1の導電膜

412b 第2の導電膜

413 導電層

413a 第1の導電膜

413b 第2の導電膜

414 導電層

414a 第1の導電膜

414b 第2の導電膜

415 導電層

415a 第1の導電膜

415b 第2の導電膜

416 ゲート絶縁膜

417 第1の不純物領域

418 第1の不純物領域

419 第1の不純物領域

420 第1の不純物領域

421 導電層

421a 第1の導電膜

421b 第2の導電膜

422 導電層

422a 第1の導電膜

422b 第2の導電膜

423 導電層

423a 第1の導電膜

423b 第2の導電膜

424 導電層

424a 第1の導電膜

424b 第2の導電膜

425 導電層

425a 第1の導電膜

425b 第2の導電膜

426 導電層

426a 第1の導電膜

426b 第2の導電膜

427 第2の不純物領域

428 第2の不純物領域

429 第2の不純物領域

430 第2の不純物領域

431 導電層

431a 第1の導電膜

431b 第2の導電膜

432 導電層

432a 第1の導電膜

432b 第2の導電膜

433 導電層

433a 第1の導電膜

433b 第2の導電膜

434 導電層

434a 第1の導電膜

434b 第2の導電膜

435 導電層

435a 第1の導電膜

435b 第2の導電膜

436 導電層

436a 第1の導電膜

436b 第2の導電膜

437 ゲート絶縁膜

438 レジストマスク

439 レジストマスク

440a 第3の不純物領域

440b 第3の不純物領域

440c 第3の不純物領域

441 第1の絶縁膜

442 第2の絶縁膜

443 第3の絶縁膜

444 ソースまたはドレイン配線

445 ソースまたはドレイン配線

446 ソースまたはドレイン配線

447 ソースまたはドレイン配線

448 接続電極

449 ゲート配線

450 第1の画素電極

451 周辺回路

452 画素部

453 pチャネル型TFT

454 nチャネル型TFT

455 画素TFT

456 保持容量

461 層間膜

462 層間膜

463 画素電極

501 スタートパルス

502 スタートパルス

503 サンプリングパルス

504 デジタル映像信号

505 デジタル映像信号

506 デジタル映像信号505

507 期間

508 期間

509 出力パルス

601 DFF

602 JKFF

603 インバータ

604 バッファ

605 タイミングコントロール回路

606 ソース線駆動回路

607 ゲート線駆動回路

551 配向膜

552 対向基板

553 透明導電膜

554 配向膜

555 液晶

601 ガラス基板

602 画素部

603 ゲート側駆動回路

604 ソース側駆動回路

605 画素TFT

606 画素電極

607 保持容量

608 ゲート配線

609 ソース配線

610 FPC

611 外部入出力端子

612 入出力配線

613 入出力配線

614 対向基板

701 ガラス基板

702 画素部

703 ゲート側駆動回路

704 ソース側駆動回路

705 画素TFT

706 画素電極

707 保持容量

708 ゲート配線

709 ソース配線

710 FPC

711 外部入出力端子

712 入出力配線

713 コントロール回路

714 対向基板

2001 発光素子

2002 信号線

2003 スイッチング用のトランジスタ

2004 駆動用のトランジスタ

2005 容量素子

2006 走査線

2007 電源線

2401 信号線

2403 スイッチング用のトランジスタ

2404 駆動用のトランジスタ

2406a 容量素子

2406b 容量素子

2407a 第1電極

2407b 第1電極

2408 走査線

2409 電源線

2410a 発光素子

2410b 発光素子

2800 基板

2801 トランジスタ

2811 第1電極

2812 電界発光層

2813 第2電極

2814 パッシベーション膜

2815 封止基板

9101 本体

9102 表示部

9201 本体

9202 表示部

9301 本体

9302 表示部

9401 本体

9402 表示部

9501 本体

9502 表示部

9701 表示部

9702 表示部

【特許請求の範囲】

【請求項1】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路及び前記ゲート信号線駆動回路を駆動するための信号を出力する回路を有することを特徴とする表示装置。

【請求項2】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力することを特徴とする表示装置。

【請求項3】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号は、JKフリップフロップ回路、Dフリップフロップ回路及び複数のインバータ回路を有する回路より出力されることを特徴とする表示装置。

【請求項4】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項5】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項6】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項7】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項8】

請求項6または7において、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号がJKフリップフロップを介して出力される信号であることを特徴とする表示装置。

【請求項9】

請求項1乃至請求項8のいずれか1項に記載の表示装置を具備することを特徴とする電子機器。

【請求項1】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路及び前記ゲート信号線駆動回路を駆動するための信号を出力する回路を有することを特徴とする表示装置。

【請求項2】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力することを特徴とする表示装置。

【請求項3】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号は、JKフリップフロップ回路、Dフリップフロップ回路及び複数のインバータ回路を有する回路より出力されることを特徴とする表示装置。

【請求項4】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項5】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項6】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、JKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項7】

副画素を含む画素がマトリクス状に配置された画素領域、ソース信号線駆動回路、ゲート信号線駆動回路、及びコントロール回路を有し、

前記副画素、前記ソース信号線駆動回路、前記ゲート信号線駆動回路、及び前記コントロール回路は、基板上に形成された薄膜トランジスタを有し、

前記コントロール回路は前記基板の外部より入力された垂直同期信号、水平同期信号、及びドットクロック信号により、前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号、並びに前記ゲート信号線駆動回路を駆動するためのクロック信号、反転クロック信号、及びスタートパルス信号を出力し、

前記ソース信号線駆動回路を駆動するためのクロック信号、反転クロック信号は、前記ドットクロック信号を基にした信号及び前記ドットクロック信号の反転信号を基にした信号であり、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号を基にした信号であり、

前記ゲート信号線駆動回路を駆動するためのクロック信号及び反転クロック信号は、前記垂直同期信号の反転信号及び前記水平同期信号が入力される前記Dフリップフロップ回路より出力される信号及び前記Dフリップフロップ回路より出力される信号の反転信号であり、前記ゲート信号線駆動回路を駆動するためのスタートパルス信号は、前記垂直同期信号及び前記Dフリップフロップ回路より出力される信号が入力されるJKフリップフロップ回路より出力されることを特徴とする表示装置。

【請求項8】

請求項6または7において、前記ソース信号線駆動回路を駆動するためのスタートパルス信号は、前記水平同期信号がJKフリップフロップを介して出力される信号であることを特徴とする表示装置。

【請求項9】

請求項1乃至請求項8のいずれか1項に記載の表示装置を具備することを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2007−114625(P2007−114625A)

【公開日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願番号】特願2005−307897(P2005−307897)

【出願日】平成17年10月21日(2005.10.21)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願日】平成17年10月21日(2005.10.21)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]