表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、可撓性を有する基板上に有機化合物を含む層を有する素子を備えた半導体装

置及びその作製方法に関する。

【背景技術】

【0002】

近年、絶縁表面上に複数の回路が集積され、様々な機能を有する半導体装置の開発が進

められている。また、アンテナを設けることにより、無線によるデータの送受信が可能な

半導体装置の開発が進められている。このような半導体装置は、無線チップ(IDタグ、

ICタグ、ICチップ、RF(Radio Frequency)タグ、無線タグ、電子

タグ、RFID(Radio Frequency Identification)タ

グともよばれる)とよばれ、既に一部の市場で導入されている。

【0003】

現在実用化されているこれらの半導体装置の多くは、Si等の半導体基板を用いた回路

(IC(Integrated Circuit)チップとも呼ばれる)とアンテナとを

有し、当該ICチップは記憶回路(メモリとも呼ぶ)や制御回路等から構成されている。

特に多くのデータを記憶可能な記憶回路を備えることによって、より高機能で付加価値が

高い半導体装置の提供が可能となる。

【0004】

また、これらの半導体装置は低コストで作製することが要求されており、近年、制御回

路や記憶回路等に有機化合物を含む層を用いたトランジスタ、メモリ、太陽電池等の素子

の開発が盛んに行われている(例えば特許文献1)。

【0005】

このような半導体装置を利用したアプリケーションは様々なものが期待されているが、

小型、軽量化を追及し、可撓性を有するプラスチックフィルムを用いることが試みられて

いる。

【0006】

プラスチックフィルムは耐熱性が低いため、プロセスの最高温度を低くせざるを得ず、

結果的にガラス基板上に形成する時ほど良好な電気特性のTFTを形成できないのが現状

である。

【0007】

そこで、ガラス基板上に形成した素子を基板から剥離し、他の基材、例えばプラスチッ

クフィルムなどに貼り付ける技術が提案されている(特許文献2参照)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−47791号公報

【特許文献2】特開2003−174153号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献2に示されるような剥離工程を用いて、有機化合物を含む層を

有する素子を剥離する場合、具体的には図23に示すように基板101上に剥離層102

を形成し、剥離層102上に絶縁層103を形成し、絶縁層103上に薄膜トランジスタ

1111を形成し、薄膜トランジスタ1111に接続する第1の電極層104を形成し、

第1の電極層104の端部を覆う有機絶縁物層1161を形成し、有機絶縁物層1161

上に有機化合物を含む層105を形成し、有機化合物を含む層105上及び有機絶縁物層

1161上に第2の電極層1162を形成することで、有機化合物を含む層を有する素子

151、及び素子151を有する層1163を剥離する場合、有機化合物を含む層105

及び第2の電極層1162の間で剥れるという問題がある。この結果、プラスチック基板

上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製するこ

とが困難である。

【0010】

これは、有機化合物を含む層105及び第2の電極層106の密着力が低いためである

。具体的には、有機絶縁物層を形成するポリイミド、エポキシ樹脂、アクリル樹脂等はイ

ミド基、シアノ基、水酸基などの極性置換基を有するため、無機化合物で形成される層、

ここでは、ゲート絶縁膜や第1の導電層と密着性が高い。しかしながら、有機化合物を含

む層105は半導体として機能するので、キャリア輸送性を有する材料を用いて形成する

。キャリア輸送性を有する材料は、一般的に極性置換基を有さない。この結果、有機化合

物を含む層105及び第2の電極層106の密着性が非常に小さくなってしまい、剥離工

程において有機化合物を含む層105及び第2の電極層106の間で剥れてしまう。

【0011】

上記問題を鑑み、本発明は、可撓性を有する基板上に有機化合物を含む層を有する素子

が設けられた半導体装置を歩留まり高く作製することを課題とする。

【課題を解決するための手段】

【0012】

本発明は、剥離層を有する基板上に、基板を上面からみて密着性が低い領域、及びその

外縁を囲むように密着性が高い領域を形成することを要旨とする。また、密着性が低い領

域の断面においては、例えばイミド基、シアノ基、水酸基などの極性置換基を有さない有

機化合物を含む層と無機化合物層が接しており、密着性が高い領域の断面においては、複

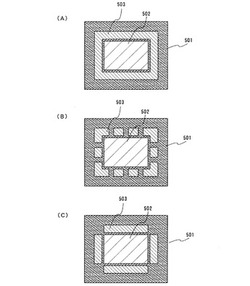

数の無機化合物層が接している。密着性の高い領域503は、図22(A)で一例を示す

ように、密着性の低い領域502の外縁を囲んでも良い。また、図22(B)で一例を示

すように、密着性の低い領域502の外縁を囲むように、密着性の高い領域503が非連

続的に形成されていてもよい。また、図22(C)で一例を示すように、密着性の低い領

域502の各辺に対応するように、矩形状の密着性の高い領域503が形成されていても

よい。なお、密着性の高い領域は、矩形状、円状、楕円状、曲線状等様々な形状とするこ

とが可能である。

【0013】

また、本発明は、剥離層501を有する基板上に、密着性が低い領域502及びその外

縁を囲むように密着性が高い領域503が形成される素子形成層を形成した後、基板及び

素子形成層を剥離層において分離し、可撓性を有する基板に貼りあわせることを要旨とす

る。

【0014】

なお、密着性が低い領域とは代表的には有機化合物を含む層及び第2の電極層が接する

領域であり、密着性が高い領域とは代表的には、第2の電極層及び無機化合物層が接する

領域である。また、密着性が高い領域とは代表的には第2の電極層及び導電層が接する領

域である。

【0015】

また、本発明の一は、基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導

電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する

第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基

板を貼りあわせた後、基板及び素子形成層を剥離層において分離することを特徴とする半

導体装置の作製方法である。

【0016】

また、本発明の一は、可撓性を有する基板と、無機化合物層と、有機化合物を含む層と

、有機化合物を含む層に接すると共に、無機化合物層に接する導電層を有する半導体装置

であることを特徴とする。

【0017】

なお、無機化合物層は、絶縁物層、または導電層である。また無機化合物層の代わりに

金属層を用いても良い。また、無機化合物層は、ゲート絶縁層、層間絶縁層、または接続

層として機能してもよい。

【0018】

有機化合物を含む層、及び有機化合物を含む層に接する導電層は、記憶素子、又は発

光素子の一部を構成する。

【0019】

また、本発明は以下を包含する。

【0020】

本発明の一は、基板上に剥離層を形成し、剥離層上に、無機化合物層、半導体素子、及

び半導体素子に接続する第1の電極層、第1の電極層上に有機化合物を含む層を形成し、

有機化合物を含む層及び無機化合物層に接する第2の電極層を形成して素子形成層を形成

し、第2の電極層上に第1の可撓性を有する基板を貼りあわせた後、基板及び素子形成層

を剥離層において分離することを特徴とする半導体装置の作製方法である。

【0021】

無機化合物層は、半導体素子が薄膜トランジスタの場合、薄膜トランジスタのゲート電

極及び配線を絶縁する絶縁層、薄膜トランジスタのゲート電極及び半導体層を絶縁するゲ

ート絶縁層、薄膜トランジスタのゲート電極と同じ材料で形成されると共に薄膜トランジ

スタのゲート電極と同じ層、薄膜トランジスタの配線と同じ材料で形成されると共に薄膜

トランジスタの配線と同じ層に接する層、または第1の電極層と同じ材料で形成されると

共に第1の電極層が接する層と同じ層に接する層である。

【0022】

本発明の一は、基板上に剥離層を形成した後、剥離層上に薄膜トランジスタを形成し、

薄膜トランジスタに接続する第1の電極層を形成し、第1の電極層の端部を覆う無機絶縁

物層を形成し、無機絶縁物層の一部及び第1の電極層の露出部に有機化合物を含む層を形

成し、有機化合物を含む層及び無機絶縁物層に接する第2の電極層を形成して素子形成層

を形成し、第2の電極層上に第1の可撓性を有する基板を貼りあわせた後、基板及び素子

形成層を剥離層において分離することを特徴とする半導体装置の作製方法である。

【0023】

本発明の一は、基板上に剥離層を形成した後、剥離層上に薄膜トランジスタ及び薄膜ト

ランジスタのゲート電極及び配線を絶縁化する無機絶縁物層を形成し、無機絶縁物層上に

薄膜トランジスタの配線に接続する第1の電極層を形成し、第1の電極層の端部を覆う有

機絶縁物層を形成し、有機絶縁物層の一部及び第1の電極層の露出部に有機化合物を含む

層を形成し、有機化合物を含む層及び無機絶縁物層に接する第2の電極層を形成して素子

形成層を形成し、第2の電極層上に第1の可撓性を有する基板を貼りあわせた後、基板及

び素子形成層を剥離層において分離することを特徴とする半導体装置の作製方法である。

【0024】

本発明の一は、基板上に剥離層を形成した後、剥離層上に半導体層を形成し、半導体層

上に無機絶縁物で形成されるゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成

し、ゲート電極上に第1の有機絶縁物層を形成し、第1の有機絶縁物層の一部を除去して

半導体層の一部及びゲート絶縁層の一部を露出し、第1の有機絶縁物層上に半導体層に接

続する配線を形成し、配線に接続する第1の電極層を形成し、第1の電極層の端部を覆う

第2の有機絶縁物層を形成し、第2の有機絶縁物層の一部及び第1の電極層の露出部に有

機化合物を含む層を形成し、有機化合物を含む層及びゲート絶縁層に接する第2の電極層

を形成して素子形成層を形成し、第2の電極層上に第1の可撓性を有する基板を貼りあわ

せた後、基板と素子形成層を剥離層において分離することを特徴とする半導体装置の作製

方法である。

【0025】

本発明の一は、基板上に剥離層を形成した後、剥離層上に絶縁層を形成し、絶縁層上に

半導体層を形成し、半導体層上に無機絶縁物で形成されるゲート絶縁層を形成し、ゲート

絶縁層上にゲート電極及び第1の導電層を形成し、ゲート電極及び第1の導電層上に有機

絶縁物層を形成し、有機絶縁物層を選択的に除去して半導体層の一部及び第1の導電層の

一部を露出し、有機絶縁物層上に半導体層に接続する配線を形成すると共に第1の導電層

に接続する第2の導電層を形成し、配線に接続する第1の電極層を形成すると共に第2の

導電層に接続する第3の導電層を形成し、第1の電極層及び第3の導電層の端部を覆う有

機絶縁物層を形成し、有機絶縁物層の一部及び第1の電極層の露出部に有機化合物を含む

層を形成し、有機化合物を含む層と第1乃至3の導電層のいずれか一つ以上とに接する第

2の電極層を形成して素子形成層を形成し、第2の電極層上に第1の可撓性を有する基板

を貼りあわせた後、基板及び素子形成層を剥離層において分離することを特徴とする半導

体装置の作製方法である。

【0026】

素子形成層と剥離層とを剥離した後、素子形成層に第2の可撓性を有する基板を貼りあ

わせてもよい。

【0027】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタに接続する第1の電極層と、第1の電極層の

端部を覆う無機絶縁物層と、第1の電極層上に形成される有機化合物を含む層と、有機化

合物を含む層及び無機絶縁物層に接する第2の電極層と、第2の電極層上に形成される第

2の可撓性を有する基板とを有することを特徴とする半導体装置である。

【0028】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタのゲート電極及び配線を絶縁化する無機絶縁

物層と、無機絶縁物層上に形成されると共に、薄膜トランジスタに接続する第1の電極層

と、第1の電極層の端部を覆う有機絶縁物層と、第1の電極層上に形成される有機化合物

を含む層と、有機化合物を含む層、有機絶縁物層、及び無機絶縁物層に接する第2の電極

層と、第2の電極層上に形成される第2の可撓性を有する基板とを有することを特徴とす

る半導体装置である。

【0029】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタのゲート電極及び半導体層を絶縁化する無機

絶縁物で形成されるゲート絶縁層と、ゲート絶縁層の一部に形成されると共に、薄膜トラ

ンジスタのゲート電極及び配線を絶縁化する第1の有機絶縁物層と、第1の有機絶縁物層

上に形成されると共に、薄膜トランジスタに接続する第1の電極層と、第1の電極層の端

部を覆うと共に第1の有機絶縁物層上に形成される第2の有機絶縁物層と、第1の電極層

上に形成される有機化合物を含む層と、有機化合物を含む層、第2の有機絶縁物層、及び

無機絶縁物層に接する第2の電極層と、第2の電極層上に形成される第2の可撓性を有す

る基板とを有することを特徴とする半導体装置である。

【0030】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタのゲート電極と同一の層で形成される第1の

導電層と、薄膜トランジスタのゲート電極を覆う第1の有機絶縁物層と、第1の有機絶縁

物層上に形成される配線と、配線と同一の層で形成されると共に、第1の導電層に接する

第2の導電層と、第1の有機絶縁物層上に形成されると共に、薄膜トランジスタの配線に

接続する第1の電極層と、第1の電極層と同一の層で形成されると共に第2の導電層に接

する第3の導電層と、第1の電極層の端部を覆う第2の有機絶縁物層と、第2の有機絶縁

物層上及び第1の電極層上に形成される有機化合物を含む層と、有機化合物を含む層及び

第3の導電層に接する第2の電極層と、第2の電極層上に形成される第2の可撓性を有す

る基板とを有することを特徴とする半導体装置である。

【0031】

第1の電極層、有機化合物を含む層、及び第2の電極層は、記憶素子、又は発光素子を

構成する一部である。

【発明の効果】

【0032】

本発明において、無機化合物層と導電層との密着性は、有機化合物を含む層と導電層と

の密着性と比較して高いため、剥離工程において無機化合物層と導電層との界面で剥れに

くい。このため、上面からみて密着性が低い領域、及びその外縁を囲むように密着性が高

い領域を形成することにより、導電層と有機化合物を含む層との界面における剥離を防止

することが可能である。また、基板上に形成された記憶素子または発光素子を有する層を

歩留まり高く剥離することが可能である。更には、可撓性を有する基板上に有機化合物を

含む層を有する素子を設けた半導体装置を歩留まり高く作製することが可能である。

【0033】

また、本発明の半導体装置は、無機化合物層及び導電層が有機化合物を含む層や有機絶

縁物層を挟むともに、無機化合物層と導電層が接する領域を多く有する。このため、有機

化合物を含む層や有機絶縁物層が外気に曝される領域が低減し、これらの領域に水分、酸

素等が侵入しにくくなり、半導体装置の劣化を低減することが可能である。

【0034】

また、可撓性を有する基板に有機化合物を含む層を有する素子が設けられた半導体装置を

得ることが可能であるため、軽量で薄型化が可能な半導体装置を得ることが可能である。

【図面の簡単な説明】

【0035】

【図1】本発明の半導体装置の作製工程を説明する断面図である。

【図2】本発明の半導体装置の作製工程を説明する断面図である。

【図3】本発明の半導体装置の作製工程を説明する断面図である。

【図4】本発明の半導体装置の作製工程を説明する断面図である。

【図5】本発明に適用可能な記憶素子の構造を説明する断面図である。

【図6】本発明に適用可能な発光素子の構造を説明する断面図である。

【図7】本発明に適用可能な記憶素子の構造を説明する断面図である。

【図8】本発明の半導体装置を説明する図である。

【図9】本発明の半導体装置を説明する上面図及び断面図である。

【図10】本発明の半導体装置の作製工程を説明する断面図である。

【図11】本発明の半導体装置の構造を説明する断面図である。

【図12】本発明の半導体装置の作製工程を説明する断面図である。

【図13】本発明の半導体装置の作製工程を説明する断面図である。

【図14】本発明の半導体装置を説明する図である。

【図15】本発明の半導体装置の作製工程を説明する断面図である。

【図16】本発明の半導体装置の作製工程を説明する断面図である。

【図17】本発明の半導体装置の等価回路を説明する図である。

【図18】本発明の半導体装置の構造を説明する上面図である。

【図19】本発明の半導体装置の構造を説明する展開図である。

【図20】本発明の半導体装置の使用形態について説明する図である。

【図21】本発明に適用可能な薄膜トランジスタの構造を説明する断面図である。

【図22】本発明の半導体装置を説明する上面図である。

【図23】従来の半導体装置を説明する断面図である。

【発明を実施するための形態】

【0036】

本発明の実施の形態について図面を参照して説明する。但し、本発明は以下の説明に限定

されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更

し得ることは当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形

態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成に

おいて、同じものを指す符号は異なる図面間で共通して用いる。

【0037】

(実施の形態1)

本実施の形態では、有機化合物を含む層を有する素子、及び当該素子を有する素子形成

層を歩留まり高く剥離する方法について図1を用いて説明する。

【0038】

図1(A)に示すように、基板101上に剥離層102を形成し、剥離層102上に絶

縁層103を形成する。次に、絶縁層103上に半導体素子を形成する。ここでは、半導

体素子として薄膜トランジスタ1111を形成する。薄膜トランジスタ1111の配線1

305に接続する第1の電極層104を形成し、第1の電極層104の端部を覆う無機絶

縁物層1115を形成する。第1の電極層104及び無機絶縁物層1115上に蒸着法に

より有機化合物を含む層105を形成する。図1(A)において、領域1116は、露出

された無機絶縁物層である。なお、有機化合物を含む層105は、無機絶縁物層1115

の一部を露出するようにメタルマスクを用いて形成する。又は、第1の電極層及び無機絶

縁物層1115の表面上に有機化合物を含む層105を形成した後、一部をエッチングし

て、無機絶縁物層1115の一部を露出させる。

【0039】

基板101としては、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶

縁層を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用

いる。上記に挙げた基板101には、大きさや形状に制約がないため、例えば、基板10

1として、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向

上させることができる。この利点は、円形のシリコン基板を用いる場合と比較すると、大

きな優位点である。

【0040】

剥離層102は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、タン

グステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(N

b)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ル

テニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリ

ジウム(Ir)、及び珪素(Si)の中から選択された元素、又は元素を主成分とする合

金材料、又は前記元素を主成分とする化合物材料からなる層を、単層又は複数の層を積層

させて形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれでもよい

。なお、ここでは、塗布法は、溶液を被処理物上に吐出させて成膜する方法であり、例え

ばスピンコーティング法や液滴吐出法を含む。また、液滴吐出法とは微粒子を含む組成物

の液滴を微細な孔から吐出して所定の形状のパターンを形成する方法である。

【0041】

剥離層102が単層構造の場合、好ましくは、タングステン、モリブデン、又はタングス

テンとモリブデンの混合物を含む層を形成する。又は、タングステンの酸化物若しくは酸

化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層、又はタングステン

とモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。

【0042】

剥離層102が積層構造の場合、好ましくは、1層目としてタングステン、モリブデン、

又はタングステンとモリブデンの混合物を含む層を形成し、2層目として、タングステン

、モリブデン、又はタングステンとモリブデンの混合物の酸化物、タングステン、モリブ

デン、又はタングステンとモリブデンの混合物の窒化物、タングステン、モリブデン、又

はタングステンとモリブデンの混合物の酸化窒化物、又はタングステン、モリブデン、又

はタングステンとモリブデンの混合物の窒化酸化物を形成する。

【0043】

剥離層102として、タングステンを含む層とタングステンの酸化物を含む層の積層構造

を形成する場合、タングステンを含む層を形成し、その上層に酸化物で形成される絶縁層

を形成することで、タングステンを含む層と絶縁層との界面に、タングステンの酸化物を

含む層が形成されることを活用してもよい。さらには、タングステンを含む層の表面を、

熱酸化処理、酸素プラズマ処理、オゾン水等の酸化力の強い溶液での処理等を行ってタン

グステンの酸化物を含む層を形成してもよい。これは、タングステンの窒化物、酸化窒化

物及び窒化酸化物を含む層を形成する場合も同様であり、タングステンを含む層を形成後

、その上層に窒化珪素層、酸化窒化珪素層、及び/又は窒化酸化珪素層を形成するとよい

。

【0044】

タングステンの酸化物は、WOxで表される。xは2以上3以下の範囲内にあり、xが2

の場合(WO2)、xが2.5の場合(W2O5)、xが2.75の場合(W4O11)

、xが3の場合(WO3)などがある。

【0045】

また、上記の工程によると、基板101に接するように剥離層102を形成しているが、

本発明はこの工程に制約されない。基板101に接するように下地となる絶縁層を形成し

、その絶縁層に接するように剥離層102を設けてもよい。

【0046】

絶縁層103は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、無機

化合物を用いて単層又は多層で形成する。無機化合物の代表例としては、珪素酸化物又は

珪素窒化物が挙げられる。珪素酸化物の代表例としては、酸化珪素、酸化窒化珪素、窒化

酸化珪素等が該当する。珪素窒化物の代表例としては、窒化珪素、酸化窒化珪素、窒化酸

化珪素等が該当する。

【0047】

さらには、絶縁層103を積層構造としても良い。例えば、無機化合物を用いて積層して

もよく、代表的には、酸化珪素、窒化酸化珪素、及び酸化窒化珪素を積層して形成しても

良い。

【0048】

薄膜トランジスタ1111の一態様について、図21を参照して説明する。図21(A)

はトップゲート型の薄膜トランジスタの一例を示している。基板101上に剥離層102

及び絶縁層103が設けられ、絶縁層103上に薄膜トランジスタ1111が設けられて

いる。薄膜トランジスタ1111は、絶縁層103上に半導体層1302、無機絶縁物で

形成されるゲート絶縁層1113が設けられている。ゲート絶縁層1113の上には、半

導体層1302に対応してゲート電極1304が形成され、その上層に保護層として機能

する絶縁層(図示しない)、層間絶縁層として機能する無機絶縁物層1114が設けられ

ている。また、半導体層のソース領域及びドレイン領域1310それぞれに接続する配線

1305が形成される。さらにその上層に、保護層として機能する絶縁層を形成しても良

い。

【0049】

半導体層1302は、結晶構造を有する半導体で形成される層であり、非単結晶半導体

若しくは単結晶半導体を用いることができる。特に、加熱処理により結晶化させた結晶性

半導体、加熱処理とレーザ光の照射を組み合わせて結晶化させた結晶性半導体を適用する

ことが好ましい。加熱処理においては、シリコン半導体の結晶化を助長する作用のあるニ

ッケルなどの金属元素を用いた結晶化法を適用することができる。また、シリコン半導体

の結晶化工程における加熱により、剥離層102及び絶縁層103の界面において、剥離

層の表面を酸化して金属酸化物を形成することが可能である。金属酸化物を形成すること

で、後の剥離工程において、剥離層102及び絶縁層103の間において容易に剥離する

ことが可能である。

【0050】

加熱処理に加えてレーザ光を照射して結晶化する場合には、連続発振レーザ光の照射若

しくは繰り返し周波数が10MHz以上であって、パルス幅が1ナノ秒以下、好ましくは

1乃至100ピコ秒である高繰返周波数超短パルス光を照射することによって、結晶性半

導体が溶融した溶融帯を、当該レーザ光の照射方向に連続的に移動させながら結晶化を行

うことができる。このような結晶化法により、大粒径であって、結晶粒界が一方向に延び

る結晶性半導体を得ることができる。キャリアのドリフト方向を、この結晶粒界が延びる

方向に合わせることで、トランジスタにおける電界効果移動度を高めることができる。例

えば、400cm2/V・sec以上を実現することができる。

【0051】

上記結晶化工程として、ガラス基板の耐熱温度(約600℃)以下の結晶化プロセスを用

いる場合、大面積ガラス基板を用いることが可能である。このため、基板あたり大量の半

導体装置を作製することが可能であり、低コスト化が可能である。

【0052】

また、ガラス基板の耐熱温度以上の加熱により、結晶化工程を行い、半導体層1302を

形成してもよい。代表的には、絶縁表面を有する基板101に石英基板を用い、非晶質若

しくは微結晶質の半導体を700度以上で加熱して半導体層1302を形成する。この結

果、結晶性の高い半導体を形成することが可能である。このため、応答速度や移動度など

の特性が良好で、高速な動作が可能な薄膜トランジスタを提供することができる。

【0053】

ゲート電極1304は金属又は一導電型の不純物を添加した多結晶半導体で形成するこ

とができる。金属を用いる場合は、タングステン(W)、モリブデン(Mo)、チタン(

Ti)、タンタル(Ta)、アルミニウム(Al)などを用いることができる。また、金

属を窒化させた金属窒化物を用いることができる。或いは、当該金属窒化物からなる第1

層と当該金属から成る第2層とを積層させた構造としても良い。積層構造とする場合には

、第1層の端部が第2層の端部より外側に突き出した形状としても良い。このとき第1層

を金属窒化物とすることで、バリアメタルとすることができる。すなわち、第2層の金属

が、ゲート絶縁層1113やその下層の半導体層1302に拡散することを防ぐことがで

きる。

【0054】

半導体層1302、ゲート絶縁層1113、ゲート電極1304などを組み合わせて構

成される薄膜トランジスタは、シングルドレイン構造、LDD(低濃度ドレイン)構造、

ゲートオーバーラップドレイン構造など各種構造を適用することができる。ここでは、シ

ングルドレイン構造の薄膜トランジスタを示す。さらには、等価的には同電位のゲート電

圧が印加されるトランジスタが直列に接続された形となるマルチゲート構造、半導体層の

上下をゲート電極で挟むデュアルゲート構造を適用することができる。

【0055】

本実施の形態においては、無機絶縁物層1114を、酸化シリコン及び酸化窒化シリコ

ンなどの無機絶縁物で形成する。

【0056】

無機絶縁物層1114の上に形成される配線1305は、ゲート電極1304と同じ層

で形成される配線と交差して設けることが可能であり、多層配線構造を形成している。無

機絶縁物層1114と同様な機能を有する絶縁層を複数積層して、その層上に配線を形成

することで多層配線構造を形成することができる。配線1305はチタン(Ti)とアル

ミニウム(Al)の積層構造、モリブデン(Mo)とアルミニウム(Al)との積層構造

など、アルミニウム(Al)のような低抵抗材料と、チタン(Ti)やモリブデン(Mo

)などの高融点金属材料を用いたバリアメタルとの組み合わせで形成することが好ましい

。

【0057】

図21(B)は、ボトムゲート型の薄膜トランジスタの一例を示している。基板101

上に剥離層102及び絶縁層103が形成され、その上に薄膜トランジスタ1111が設

けられている。薄膜トランジスタ1111には、ゲート電極1304、ゲート絶縁層11

13、半導体層1302、層間絶縁層として機能する無機絶縁物層1114が設けられて

いる。さらにその上層には、保護層として機能する絶縁層を形成しても良い。半導体層1

302のソース領域及びドレイン領域に接する配線1305は、無機絶縁物層1114の

上に形成することができる。

【0058】

さらには、薄膜トランジスタ1111の代わりにスイッチング素子として機能し得る半導

体素子であれば、どのような構成で設けてもよい。スイッチング素子の代表例としては、

MIM(Metal−Insulator−Metal)、ダイオード等が挙げられる。

【0059】

図1(A)において、第1の電極層104は、スパッタリング法やプラズマCVD法、塗

布法、印刷法、電解メッキ法、無電解メッキ法等を用い、導電性の高い金属、合金、化合

物等からなる単層または多層構造を用いて形成することができる。代表的には、仕事関数

の大きい(具体的には4.0eV以上)金属、合金、導電性化合物、およびこれらの混合

物や、仕事関数の小さい(具体的には3.8eV以下)金属、合金、導電性化合物、およ

びこれらの混合物などを用いることが可能である。

【0060】

仕事関数の大きい(具体的には4.0eV以上)金属、合金、導電性化合物の代表例とし

ては、インジウム錫酸化物(以下、ITOと示す)、または珪素を含有したインジウム錫

酸化物、2〜20atomic%の酸化亜鉛(ZnO)を含む酸化インジウム等が挙げら

れる。また、チタン(Ti)、金(Au)、白金(Pt)、ニッケル(Ni)、タングス

テン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅

(Cu)、パラジウム(Pd)、または金属材料の窒化物(例えば、窒化チタン:TiN

、窒化タングステン(WN)、窒化モリブデン(MoN))等を用いることも可能である

。

【0061】

仕事関数の小さい(具体的には3.8eV以下)金属、合金、導電性化合物の代表例とし

ては、元素周期表の1族または2族に属する金属、即ちリチウム(Li)やセシウム(C

s)等のアルカリ金属、およびマグネシウム(Mg)、カルシウム(Ca)、ストロンチ

ウム(Sr)等のアルカリ土類金属、アルミニウム(Al)およびこれらのいずれかを含

む合金(MgAg、AlLi)、ユーロピウム(Er)、イッテルビウム(Yb)等の希

土類金属およびこれらを含む合金等が挙げられる。

【0062】

なお、第1の電極層104又は第2の電極層106に、有機化合物を含む層に対して正孔

を注入する電極、すなわち陽極を用いる場合には、仕事関数の大きな材料を用いるのが好

ましい。逆に有機化合物を含む層に対して電子を注入する電極、すなわち陰極を用いる場

合には、仕事関数の小さい材料を用いることが好ましい。

【0063】

無機絶縁物層1115を、酸化珪素、窒化珪素、酸化窒化珪素、窒化アルミニウム等の無

機絶縁物を用い、CVD法、スパッタリング法等の薄膜形成方法を用いて形成する。ここ

では、薄膜形成方法を用いて絶縁膜を形成した後、第1の電極層104の一部が露出する

ように絶縁膜を選択的にエッチングして無機絶縁物層1115を形成する。

【0064】

有機化合物を含む層105は、蒸着法、電子ビーム蒸着法、塗布法等を用いて形成する

ことができる。上記作製方法を用いて有機化合物を含む層を形成する場合、無機絶縁物層

1115の一部を露出する領域1116を形成しながら有機化合物を含む層105を形成

する。また、無機絶縁物層1115及び第1の電極層104表面上に有機化合物を含む層

を形成した後、選択的にエッチングして無機絶縁物層1115が露出する領域1116を

形成してもよい。

【0065】

ここでは、50〜200nmのチタン膜をスパッタリング法により成膜した後、フォトリ

ソグラフィー法により所望の形状にエッチングして第1の電極層104を形成する。次に

、蒸着法によりNPBで形成される有機化合物を含む層を形成する。

【0066】

次に、図1(B)に示すように、無機絶縁物層1115及び有機化合物を含む層105上

に第2の電極層106を形成する。この結果、無機絶縁物層1115に第2の電極層10

6が接する領域1117を形成することができる。また、第1の電極層104、有機化合

物を含む層105、及び第2の電極層106により、有機化合物を含む層を有する素子1

51を形成することができる。第2の電極層106は、蒸着法、スパッタ法、CVD法、

印刷法、塗布法等を用いて形成することができる。第2の電極層106は、第1の電極層

104と同様の材料を用いて形成する。なお、第1の電極層104に仕事関数の大きな材

料を用いる場合、第2の電極層106は仕事関数の小さい材料を用いることが好ましい。

また、第1の電極層104に仕事関数の小さい材料を用いる場合、第2の電極層106は

仕事関数の大きな材料を用いることが好ましい。

【0067】

ここでは、蒸着法によりアルミニウムを蒸着して第2の電極層106を形成する。

【0068】

なお、ここでは、絶縁層103から第2の電極層106までを含む積層物を素子形成層1

118という。

【0069】

ここで、有機化合物を含む層を有する素子151のより具体的な構造について図5を用い

て以下に示す。なお、図5(A)の205は図1の105に対応し、図5(B)の205

と201の積層は図1の105に対応し、図5(C)の205と202の積層は図1の1

05に対応し、図5(D)の205と203の積層は105に対応し、図5(E)の20

5と245と244の積層は図1の105に対応する。

【0070】

図5(A)に示すように、第1の電極層及び第2の電極層に印加された電圧により、結晶

状態や導電性、形状が変化する有機化合物で有機化合物を含む層205を形成することで

、有機化合物を含む層を有する素子151は記憶素子として機能する。なお、有機化合物

を含む層205は、単層で設けてもよいし、異なる有機化合物で形成された層複数を積層

させて設けてもよい。

【0071】

有機化合物を含む層205の厚さは、第1の導電層及び第2の導電層への電圧印加により

記憶素子の電気抵抗が変化する厚さが好ましい。有機化合物を含む層205の代表的な膜

厚は、5nmから100nm、好ましくは10nmから60nm、更に好ましくは5〜3

0nmである。

【0072】

有機化合物を含む層205は、正孔輸送性を有する有機化合物又は電子輸送性を有する有

機化合物を用いて形成することができる。

【0073】

正孔輸送性の有機化合物としては、例えば、フタロシアニン(略称:H2Pc)、銅フタ

ロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)の他、4,

4’,4’’−トリス(N,N−ジフェニルアミノ)トリフェニルアミン(略称:TDA

TA)、4,4’,4’’−トリス[N−(3−メチルフェニル)−N−フェニルアミノ

]トリフェニルアミン(略称:MTDATA)、1,3,5−トリス[N,N−ジ(m−

トリル)アミノ]ベンゼン(略称:m−MTDAB)、N,N’−ジフェニル−N,N’

−ビス(3−メチルフェニル)−1,1’−ビフェニル−4,4’−ジアミン(略称:T

PD)、4,4’−ビス[N−(1−ナフチル)−N−フェニルアミノ]ビフェニル(略

称:NPB)、4,4’−ビス{N−[4−ジ(m−トリル)アミノ]フェニル−N−フ

ェニルアミノ}ビフェニル(略称:DNTPD)、4,4’−ビス[N−(4−ビフェニ

リル)−N−フェニルアミノ]ビフェニル(略称:BBPB)、4,4’,4’’−トリ

(N−カルバゾリル)トリフェニルアミン(略称:TCTA)などが挙げられるが、これ

らに限定されることはない。また、上述した化合物の中でも、TDATA、MTDATA

、m−MTDAB、TPD、DNTPD、BBPB、TCTAなどに代表される芳香族ア

ミン化合物は、正孔を発生しやすく、有機化合物として好適な化合物群である。ここに述

べた物質は、主に10−6cm2/Vs以上の正孔移動度を有する物質である。

【0074】

電子輸送性を有する有機化合物としては、トリス(8−キノリノラト)アルミニウム(

略称:Alq3)、トリス(4−メチル−8−キノリノラト)アルミニウム(略称:Al

mq3)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(略称:Be

Bq2)、ビス(2−メチル−8−キノリノラト)−4−フェニルフェノラト−アルミニ

ウム(略称:BAlq)等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等か

らなる材料を用いることができる。また、この他、ビス[2−(2−ヒドロキシフェニル

)ベンゾオキサゾラト]亜鉛(略称:Zn(BOX)2)、ビス[2−(2−ヒドロキシ

フェニル)ベンゾチアゾラト]亜鉛(略称:Zn(BTZ)2)などのオキサゾール系、

チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯

体以外にも、2−(4−ビフェニリル)−5−(4−tert−ブチルフェニル)−1,

3,4−オキサジアゾール(略称:PBD)、1,3−ビス[5−(p−tert−ブチ

ルフェニル)−1,3,4−オキサジアゾール−2−イル]ベンゼン(略称:OXD−7

)、3−(4−tert−ブチルフェニル)−4−フェニル−5−(4−ビフェニリル)

−1,2,4−トリアゾール(略称:TAZ)、3−(4−tert−ブチルフェニル)

−4−(4−エチルフェニル)−5−(4−ビフェニリル)−1,2,4−トリアゾール

(略称:p−EtTAZ)、バソフェナントロリン(略称:BPhen)、バソキュプロ

イン(略称:BCP)等を用いることができる。ここに述べた物質は、主に10−6cm

2/Vs以上の電子移動度を有する物質である。

【0075】

また、図5(B)に示すように、記憶素子において、第1の電極層104及び有機化合

物を含む層205の間に絶縁層201を形成してもよい。

【0076】

絶縁層201は、トンネル効果により第1の電極層または第2の電極層から有機化合物を

含む層へ、正孔又は電子の電荷を注入する層である。絶縁層201は、所定の電圧におい

て、トンネル効果により有機化合物を含む層205へ電荷を注入することが可能な厚さで

形成する。絶縁層201の代表的な厚さは、1nm以上4nm以下、好ましくは1nm以

上2nm以下の絶縁層である。絶縁層201の膜厚は、1nm以上4nm以下と極めて薄

いため、絶縁層201においてトンネル効果が生じ、有機化合物を含む層205への電荷

注入性が高まる。このため、絶縁層201は、厚さが4nmより厚くなると、絶縁層20

1におけるトンネル効果が生じず、有機化合物を含む層205への電荷注入が困難となり

、記憶素子の書き込み時の印加電圧が上昇する。また、絶縁層201の膜厚は、1nm以

上4nm以下と極めて薄いため、スループットが向上する。

【0077】

絶縁層201は、熱的及び化学的に安定な化合物で形成する。

【0078】

絶縁層201を形成する無機化合物の代表例としては、Li2O、Na2O、K2O、R

b2O、BeO、MgO、CaO、SrO、BaO、Sc2O3、ZrO2、HfO2、

RfO2、TaO2、TcO2、MnO2、Fe2O3、CoO、PdO、Ag2O、A

l2O3、Ga2O3 、Bi2O3等に代表される絶縁性を有する酸化物が挙げられる

。

【0079】

また、絶縁層201を形成する無機化合物の代表例としては、LiF、NaF、KF、C

sF、BeF2、MgF2、CaF2、SrF2、BaF2、AlF3、AgF、MnF

3等に代表される絶縁性を有するフッ化物、LiCl、NaCl、KCl、CsCl、B

eCl2、CaCl2、BaCl2、AlCl3、SnCl4、AgCl、ZnCl2、

TiCl4、TiCl3、ZrCl4、FeCl3、PdCl2、SbCl3、SbCl

2、SrCl2、TlCl3、CuCl、CuCl2、MnCl2、RuCl2等に代表

される絶縁性を有する塩化物、KBr、CsBr、AgBr、BaBr2、LiBr等に

代表される絶縁性を有する臭化物、NaI、KI、BaI2、TlI3、AgI、TiI

4、CaI2、SiI4、CsI等に代表される絶縁性を有するヨウ化物が挙げられる。

【0080】

また、絶縁層201を形成する無機化合物の代表例としては、Li2CO3、K2CO3

、Na2CO3、MgCO3、CaCO3、SrCO3、BaCO3、MnCO3、Fe

CO3、CoCO3 、NiCO3、CuCO3、Ag2CO3、ZnCO3等に代表さ

れる絶縁性を有する炭酸塩、Li2SO4、K2SO4、Na2SO4、MgSO4、C

aSO4、SrSO4、BaSO4、Ti2(SO4)3、Zr(SO4)2、MnSO

4、FeSO4、Fe2(SO4)3、CoSO4、Co2(SO4)3、NiSO4、

CuSO4、Ag2SO4、ZnSO4、Al2(SO4)3、In2(SO4)3、S

nSO4、Sn(SO4)2、Sb2(SO4)3、Bi2(SO4)3等に代表される

絶縁性を有する硫酸塩、LiNO3、KNO3、NaNO3、Mg(NO3)2、Ca(

NO3)2、Sr(NO3)2、Ba(NO3)2、Ti(NO3)4、Zr(NO3)

4、Mn(NO3)2、Fe(NO3)2、Fe(NO3)3、Co(NO3)2、Ni

(NO3)2、Cu(NO3)2、AgNO3、Zn(NO3)2、Al(NO3)3、

In(NO3)3、Sn(NO3)2等に代表される絶縁性を有する硝酸塩、AlN、S

iN等に代表される絶縁性を有する窒化物が挙げられる。なお、これらの無機化合物の組

成は、厳密な整数比である必要はなく、ずれていても良い。

【0081】

なお、絶縁層201を無機化合物で形成する場合、絶縁層の膜厚は、1nm以上2nm以

下が好ましい。絶縁層の膜厚が3nm以上になると、書き込み時の印加電圧が上昇する。

【0082】

絶縁層201を形成する有機化合物の代表例としては、ポリイミド、アクリル、ポリアミ

ド、ベンゾシクロブテン、ポリエステル、ノボラック樹脂、メラミン樹脂、フェノール樹

脂、エポキシ樹脂、珪素樹脂、フラン樹脂、ジアリルフタレート樹脂等に代表される有機

樹脂が挙げられる。

【0083】

絶縁層201の形成方法としては、蒸着法、電子ビーム蒸着法、スパッタリング法、CV

D法等を用いることができる。スピンコート法、ゾル−ゲル法、印刷法または液滴吐出法

等を用いることができる。

【0084】

また、図5(C)に示すように、凹凸を有する連続的な絶縁層202を用いてもよい。

但し、この場合、絶縁層の凸部における厚さは1nm以上4nm以下、好ましくは2nm

以上4nm以下、凹部における厚さは、0.1nm以上2nm未満、好ましくは1nm以

上2nm未満であることが好ましい。

【0085】

また、図5(D)に示すように、第1の電極層104上に分散された非連続な絶縁層2

03であってもよい。非連続な絶縁層203は、島状、縞状、網目状等の形状を有しても

よい。

【0086】

更には、絶縁層201〜203の代わりに、絶縁性粒子を設けてもよい。このときの絶

縁性粒子は、粒径は1nm以上4nm以下であることが好ましい。

【0087】

さらには、有機化合物を含む層205及び第2の電極層106の間に、上記絶縁層20

1〜203または絶縁性粒子を設けてもよい。

【0088】

第1の電極層及び有機化合物を含む層の間、または有機化合物を含む層及び第2の電極

層の間に、厚さが4nm以下、好ましくは2nm以下の絶縁層を設けることにより、当該

絶縁層にトンネル電流が流れるため、記憶素子の書き込み時の印加電圧及び電流値のばら

つきを低減することが可能である。また、第1の電極層及び有機化合物を含む層の間、ま

たは有機化合物を含む層及び第2の電極層の間に、厚さが4nm以下、好ましくは2nm

以下の絶縁層を設けることにより、トンネル効果による電荷注入性が上昇し、有機化合物

を含む層の膜厚を厚くすることが可能であり、初期状態でのショートを防止することが可

能である。この結果、記憶装置及び半導体装置の信頼性を向上させることが可能である。

【0089】

また、上記記憶素子において、第1の電極層104又は第2の電極層106に、整流性

を有する素子を設けてもよい(図5(E))。整流性を有する素子とは、ゲート電極とド

レイン電極を接続したトランジスタ、またはダイオードである。ここでは、第3の電極層

及び半導体層で構成されるダイオード211を、第1の電極層104に接して設ける。さ

らには、整流性を有する素子は、有機化合物を含む層205と第1の電極層104との間

に設けてもよい。また、有機化合物を含む層205と第2の電極層106との間に整流性

を有する素子を設けてもよい。ダイオードの代表例としては、PN接合ダイオード、PI

N接合を有するダイオードやアバランシェダイオード等が挙げられる。また、他の構成の

ダイオードを用いてもよい。このように、整流性がある素子を設けることにより、1つの

方向にしか電流が流れないために、誤差が減少し、読み出しマージンを拡大することがで

きる。

【0090】

次に、有機化合物を含む層105を発光機能を有する層で形成することで、有機化合物を

含む層を有する素子151は発光素子として機能する。この場合、有機化合物を含む層1

05を発光性の有機化合物を用いて形成する。

【0091】

発光性の有機化合物としては、例えば、9,10−ジ(2−ナフチル)アントラセン(

略称:DNA)、2−tert−ブチル−9,10−ジ(2−ナフチル)アントラセン(

略称:t−BuDNA)、4,4’−ビス(2,2−ジフェニルビニル)ビフェニル(略

称:DPVBi)、クマリン30、クマリン6、クマリン545、クマリン545T、ペ

リレン、ルブレン、ペリフランテン、2,5,8,11−テトラ(tert−ブチル)ペ

リレン(略称:TBP)、9,10−ジフェニルアントラセン(略称:DPA)、5,1

2−ジフェニルテトラセン、4−(ジシアノメチレン)−2−メチル−6−[p−(ジメ

チルアミノ)スチリル]−4H−ピラン(略称:DCM1)、4−(ジシアノメチレン)

−2−メチル−6−[2−(ジュロリジン−9−イル)エテニル]−4H−ピラン(略称

:DCM2)、4−(ジシアノメチレン)−2,6−ビス[p−(ジメチルアミノ)スチ

リル]−4H−ピラン(略称:BisDCM)等が挙げられる。また、ビス[2−(4’

,6’−ジフルオロフェニル)ピリジナト−N,C2](ピコリナト)イリジウム(略称

:FIrpic)、ビス{2−[3’,5’−ビス(トリフルオロメチル)フェニル]ピ

リジナト−N,C2}(ピコリナト)イリジウム(略称:Ir(CF3ppy)2(pi

c))、トリス(2−フェニルピリジナト−N,C2)イリジウム(略称:Ir(ppy

)3)、(アセチルアセトナート)ビス(2−フェニルピリジナト−N,C2)イリジウ

ム(略称:Ir(ppy)2(acac))、(アセチルアセトナート)ビス[2−(2

’−チエニル)ピリジナト−N,C3]イリジウム(略称:Ir(thp)2(acac

))、(アセチルアセトナート)ビス(2−フェニルキノリナト−N,C2)イリジウム

(略称:Ir(pq)2(acac))、(アセチルアセトナート)ビス[2−(2’−

ベンゾチエニル)ピリジナト−N,C3]イリジウム(略称:Ir(btp)2(aca

c))などの燐光を放出できる化合物用いることもできる。

【0092】

図6(A)の171〜175は図1の105に対応し、図6(B)の173、176、

177は図1の105に対応する。また、図6(A)に示すように、第1の電極層104

上に正孔注入材料で形成される正孔注入層171、正孔輸送性材料で形成される正孔輸送

層172、発光性の有機化合物で形成される発光層173、電子輸送性材料で形成される

電子輸送層174、電子注入性材料で形成される電子注入層175、及び第2の電極層1

06を積層することにより発光素子として機能する素子151を形成してもよい。

【0093】

ここで、正孔輸送性材料は、図5(A)の有機化合物を含む層205で列挙した正孔輸送

性材料を適宜用いることが出来る。

【0094】

正孔注入性材料は、フタロシアニン系の化合物が有効であり、フタロシアニン(略称:H

2Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VO

Pc)等を用いることができる。また、導電性高分子化合物に化学ドーピングを施した材

料もあり、ポリスチレンスルホン酸(略称:PSS)をドープしたポリエチレンジオキシ

チオフェン(略称:PEDOT)やポリアニリン(略称:PAni)などを用いることも

できる。また、酸化モリブデン(MoOx)、酸化バナジウム(VOx)、酸化ニッケル

(NiOx)などの無機半導体の薄膜や、酸化アルミニウム(Al2O3)などの無機絶

縁体の超薄膜も有効である。また、4,4’,4’’−トリス(N,N−ジフェニル−ア

ミノ)−トリフェニルアミン(略称:TDATA)、4,4’,4’’−トリス[N−(

3−メチルフェニル)−N−フェニル−アミノ]−トリフェニルアミン(略称:MTDA

TA)、N,N’−ビス(3−メチルフェニル)−N,N’−ジフェニル−1,1’−ビ

フェニル−4,4’−ジアミン(略称:TPD)、4,4’−ビス{N−[4−(N,N

−ジ−m−トリルアミノ)フェニル]−N−フェニルアミノ}ビフェニル(略称:DNT

PD)などの芳香族アミン系化合物も用いることができる。さらに、それら芳香族アミン

系化合物に対してアクセプタ性を示す物質を添加してもよく、具体的にはVOPcにアク

セプタである2,3,5,6−テトラフルオロ−7,7,8,8−テトラシアノキノジメ

タン(略称:F4−TCNQ)を添加したものや、NPBにアクセプタであるMoOxを

添加したものを用いてもよい。

【0095】

ここで、電子輸送性材料は、図5(A)の有機化合物を含む層205で列挙した電子輸送

性材料を適宜用いることが出来る。

【0096】

電子注入材料としては、上述した電子輸送性材料の他に、LiF、CsFなどのアルカリ

金属ハロゲン化物や、CaF2のようなアルカリ土類ハロゲン化物、Li2Oなどのアル

カリ金属酸化物のような絶縁体の超薄膜がよく用いられる。また、リチウムアセチルアセ

トネート(略称:Li(acac))や8−キノリノラト−リチウム(略称:Liq)な

どのアルカリ金属錯体も有効である。さらに、上述した電子輸送性材料と、Mg、Li、

Cs等の仕事関数の小さい金属とを共蒸着等により混合した材料を使用することもできる

。

【0097】

また、図6(B)に示すように、第1の電極層104、有機化合物及び有機化合物に対し

て電子受容性を有する無機化合物で形成される正孔輸送層176、発光層173、有機化

合物及び有機化合物に対して電子供与性を有する無機化合物で形成される電子輸送層17

7、並びに第2の電極層106で発光素子として機能する素子151を形成してもよい。

【0098】

有機化合物及び有機化合物に対して電子受容性を有する無機化合物で形成される正孔輸送

層176は、有機化合物としては上記した正孔輸送性の有機化合物を適宜用いて形成する

。また、無機化合物としては、有機化合物から電子を受け取りやすいものであれば何であ

ってもよく、種々の金属酸化物または金属窒化物が可能であるが、周期表第4族乃至第1

2族のいずれかの遷移金属酸化物が電子受容性を示しやすく好適である。具体的には、酸

化チタン、酸化ジルコニウム、酸化バナジウム、酸化モリブデン、酸化タングステン、酸

化レニウム、酸化ルテニウム、酸化亜鉛などが挙げられる。また、上述した金属酸化物の

中でも、周期表第4族乃至第8族のいずれかの遷移金属酸化物は電子受容性の高いものが

多く、好ましい一群である。特に酸化バナジウム、酸化モリブデン、酸化タングステン、

酸化レニウムは真空蒸着が可能で扱いやすいため、好適である。

【0099】

有機化合物及び有機化合物に対して電子供与性を有する無機化合物で形成される電子輸送

層177は、有機化合物としては上記した電子輸送性の有機化合物を適宜用いて形成する

。また、無機化合物としては、有機化合物に電子を与えやすいものであれば何であっても

よく、種々の金属酸化物または金属窒化物が可能であるが、アルカリ金属酸化物、アルカ

リ土類金属酸化物、希土類金属酸化物、アルカリ金属窒化物、アルカリ土類金属窒化物、

希土類金属窒化物が電子供与性を示しやすく好適である。具体的には、酸化リチウム、酸

化ストロンチウム、酸化バリウム、酸化エルビウム、窒化リチウム、窒化マグネシウム、

窒化カルシウム、窒化イットリウム、窒化ランタンなどが挙げられる。特に酸化リチウム

、酸化バリウム、窒化リチウム、窒化マグネシウム、窒化カルシウムは真空蒸着が可能で

扱いやすいため、好適である。

【0100】

有機化合物及び無機化合物で形成される電子輸送層又は正孔輸送層は、電子注入・輸送特

性が優れているため、第1の電極層104、第2の電極層106共に、ほとんど仕事関数

の制限を受けることなく、種々の材料を用いることができる。また駆動電圧を低減するこ

とが可能である。

【0101】

次に、図1(C)に示すように、第2の電極層106上に絶縁層107を形成する。次に

、絶縁層107表面に基板108を貼りあわせる。

【0102】

絶縁層107は、塗布法を用いて組成物を塗布し、乾燥加熱して形成することが好まし

い。このような絶縁層107としては、後の剥離工程での保護層として設けるため、表面

の凹凸の少ない絶縁層であることが好ましい。このような絶縁層は、塗布法により形成す

ることができる。また、CVD法やスパッタリング法等の薄膜形成方法により形成した後

、CMP法により表面を研磨して絶縁層107を形成してもよい。塗布法を用いて形成さ

れた絶縁層107は、アクリル樹脂、ポリイミド樹脂、メラミン樹脂、ポリエステル樹脂

、ポリカーボネート樹脂、フェノール樹脂、エポキシ樹脂、ポリアセタール、ポリエーテ

ル、ポリウレタン、ポリアミド(ナイロン)、フラン樹脂、ジアリルフタレート樹脂等の

有機化合物、シリカガラスに代表されるシロキサンポリマー系材料を出発材料として形成

された珪素、酸素、水素からなる化合物のうちSi−O−Si結合を含む無機シロキサン

ポリマー、又はアルキルシロキサンポリマー、アルキルシルセスキオキサンポリマー、水

素化シルセスキオキサンポリマー、水素化アルキルシルセスキオキサンポリマーに代表さ

れる珪素に結合される水素がメチルやフェニルのような有機基によって置換された有機シ

ロキサンポリマーで形成される。また、上記の薄膜形成方法により絶縁膜を成膜した後、

CMP法により表面を研磨して形成される絶縁層は、酸化珪素、酸化窒化珪素、窒化酸化

珪素、窒化珪素等で形成される。

【0103】

基板108としては、可撓性を有する基板を用いることが好ましく、薄くて軽いものが

好ましい。代表的には、PET(ポリエチレンテレフタレート)、PEN(ポリエチレン

ナフタレート)、PES(ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサ

ルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポ

リフェニレンオキサイド、ポリサルフォン、ポリフタールアミド等からなる基板を用いる

ことができる。また、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミ

ド、無機蒸着フィルム、紙等)と接着性有機樹脂フィルム(アクリル系有機樹脂、エポキ

シ系有機樹脂等)との積層フィルムなどを用いることもできる。上記基板を用いる場合、

図示しないが、絶縁層107と基板108との間に接着層を設けて、絶縁層107及び基

板108を貼りあわせる。

【0104】

又、基板108として、熱圧着により、被処理体とラミネート処理が行われる接着層を

有するフィルム(ラミネートフィルム(ポリプロピレン、ポリエステル、ビニル、ポリフ

ッ化ビニル、塩化ビニルなどからなる))を用いてもよい。ラミネートフィルムは、ベー

スとなるフィルムの表面に設けられた接着層か、又は最外層に設けられた層(接着層では

ない)を加熱処理によって溶かし、加圧により接着することで、被処理体にフィルムを接

着することが可能である。この場合は、絶縁層107及び基板108の間に接着層を別途

設ける必要は無い。

【0105】

ここでは、絶縁層107は、塗布法により組成物を塗布し、乾燥焼成してエポキシ樹脂

を用いて形成する。次に、絶縁層107表面にラミネートフィルムを熱圧着して基板10

8を絶縁層107上に貼りあわせる。

【0106】

次に、図1(D)に示すように、剥離層102から絶縁層103を剥離する。ここでは

、無機絶縁物層1115と第2の電極層106とが接している。無機絶縁物層1115と

第2の電極層106との密着性が高いため、剥離工程において有機化合物を含む層105

及び第2の電極層106の界面では剥離しにくくなり、剥離層102から絶縁層103が

剥離する。

【0107】

なお、本実施の形態においては、基板と素子形成層の間に剥離層及び絶縁層を形成し、剥

離層及び絶縁層の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化して、当

該素子形成層を物理的に剥離する方法を用いたがこれに限られない。(1)基板と素子形

成層の間に水素を含む非晶質珪素膜を設け、レーザ光の照射より非晶質珪素膜の水素ガス

を放出させて基板を剥離する方法、(2)基板と素子形成層の間に剥離層及び絶縁層を形

成し、剥離層及び絶縁層の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化

し、剥離層の一部を溶液やNF3、BrF3、ClF3等のフッ化ハロゲンガスによりエ

ッチングで除去した後、脆弱化された金属酸化膜において物理的に剥離する方法、(3)

素子形成層が形成された基板のみを機械的に削除又は溶液やNF3、BrF3、ClF3

等のフッ化ハロゲンガスによるエッチングで除去する方法、(4)耐熱性の高い基板とト

ランジスタを有する層の間に剥離層として金属層及び金属酸化物層を設け、当該金属酸化

物層を結晶化により脆弱化し、金属層の一部を溶液やNF3、BrF3、ClF3等のフ

ッ化ハロゲンガスによりエッチングで除去した後、脆弱化された金属酸化物層において物

理的に剥離する方法等を適宜用いることが出来る。

【0108】

次に、図1(E)に示すように、絶縁層103表面に基板109を貼り付ける。基板1

09は、基板108と同様のものを適宜用いることが可能である。ここでは、ラミネート

フィルムを熱圧着して基板109を絶縁層103上に貼りあわせる。

【0109】

以上の工程により、剥離工程を用いて歩留まり高く可撓性を有する基板上に有機化合物

を含む層を有する素子を設けることができる。

【0110】

(実施の形態2)

本実施の形態では、実施の形態1と異なる素子形成層を剥離する方法を図2を用いて説

明する。本実施の形態は、実施の形態1と比較して、第1の電極層の端部を覆う無機絶縁

物層の代わりに、有機絶縁物層を形成する点が異なる。

【0111】

図2(A)に示すように、実施の形態1と同様に基板101上に剥離層102を形成し

、剥離層102上に絶縁層103を形成し、絶縁層103上に薄膜トランジスタ1111

を形成する。本実施の形態では、実施の形態1と同様に、薄膜トランジスタ1111のゲ

ート電極と配線を絶縁化する層間絶縁層を無機絶縁物層1114を用いて形成する。次に

無機絶縁物層1114上に第1の電極層104を形成する。

【0112】

次に第1の電極層104の端部を覆う有機絶縁物層1121を形成する。有機絶縁物層

は、断面形状が30度〜75度、好ましくは35〜60度の傾斜角度を有することが好ま

しい。このような傾斜角度を有することにより、後に形成される有機化合物を含む層の断

面被覆率が高まり、段切れを防止すると共に、歩留まりを向上させることが可能である。

【0113】

有機絶縁物層1121は、アクリル樹脂、ポリイミド樹脂、メラミン樹脂、ポリエステル

樹脂、ポリカーボネート樹脂、フェノール樹脂、エポキシ樹脂、ポリアセタール、ポリエ

ーテル、ポリウレタン、ポリアミド(ナイロン)、フラン樹脂、ジアリルフタレート樹脂

等感光性又は非感光性の有機化合物を用い、塗布法、印刷法、液滴吐出法を用いて形成す

る。なお、有機絶縁物層1121を形成する有機化合物は、イミド基、シアノ基、水酸基

などの極性置換基を有する。

【0114】

塗布法を用いて非感光性の有機化合物を塗布して有機絶縁物層1121を形成する場合、

組成物を塗布し、乾燥及び焼成して絶縁膜を形成した後、フォトリソグラフィー工程によ

り形成したレジストマスクを用いて絶縁膜を選択的にエッチングして、第1の電極層10

4の一部、及び無機絶縁物層1114の一部を露出するように有機絶縁物層1121を形

成する。また、感光性の有機化合物を塗布法により塗布して有機絶縁物層1121を形成

する場合、組成物を塗布し、乾燥した後、露光、現像し焼成し、第1の電極層104の一

部、及び無機絶縁物層1114の一部を露出するように有機絶縁物層1121を形成する

。感光性を有する有機化合物を露光し現像して形成した有機絶縁物層1121は、上端部

が曲率を有する絶縁層となる。このため、後に形成される有機化合物を含む層の段切れを

防止することが可能であり、歩留まりを向上させることが可能である。印刷法や液滴吐出

法を用いて有機絶縁物層1121を形成する場合、組成物を第1の電極層104の端部を

覆い、且つ無機絶縁物層1114の一部を露出するように塗布し、乾燥及び焼成を行って

有機絶縁物層1121を形成する。

【0115】

ここでは、塗布法を用いて感光性ポリイミドを含む組成物を塗布し、乾燥、焼成してポ

リイミドで形成される絶縁膜を形成した後、フォトリソグラフィー工程により絶縁膜を露

光、現像して、第1の電極層104の一部、及び無機絶縁物層1114の一部が露出する

ように有機絶縁物層1121を形成する。即ち、無機絶縁物層1114の露出部1122

を形成するように有機絶縁物層1121を形成する。

【0116】

次に、有機絶縁物層1121及び第1の電極層104の露出表面に、実施の形態1と同

様に有機化合物を含む層105を形成する。なお、有機化合物を含む層105は、無機絶

縁物層1114の一部が露出するように形成する。

【0117】

次に、図2(B)に示すように、有機化合物を含む層105及び有機絶縁物層1121

の露出部1122に、実施の形態1と同様に第2の電極層106を形成する。この結果、

無機絶縁物層1114に第2の電極層106が接する領域1123を形成することができ

る。無機絶縁物層1114に第2の電極層106が接する領域1123においては、無機

絶縁物層1114と第2の電極層106との密着性が高いため、剥離工程において有機化

合物を含む層105と第2の電極層106の界面では剥離しにくくなり、剥離層102及

び絶縁層103で剥離することが可能である。

【0118】

なお、ここでは、絶縁層103から第2の電極層106までを含む積層物を素子形成層1

124という。

【0119】

以下、図2(C)に示す絶縁層107の形成、基板108の貼りあわせ、図2(D)に

示す剥離工程、及び図2(E)に示す基板109の貼りあわせは、実施の形態1と同様で

あるためここでは省略する。

【0120】

以上の工程により、剥離工程を用いて歩留まり高く可撓性を有する基板上に有機化合物

を含む層を有する素子を設けることができる。

【0121】

(実施の形態3)

本実施の形態では、実施の形態1及び実施の形態2とは異なる、素子形成層を剥離する

方法を図3を用いて説明する。本実施の形態は、実施の形態2と比較して、薄膜トランジ

スタのゲート電極と配線を絶縁化する無機絶縁物層の代わりに有機絶縁物層を形成する点

が異なる。

【0122】

図3(A)に示すように、実施の形態1と同様に基板101上に剥離層102を形成

し、剥離層102上に絶縁層103を形成し、絶縁層103上に薄膜トランジスタ111

1を形成する。

【0123】

本実施の形態では、実施の形態1及び実施の形態2と異なり、薄膜トランジスタ1111

のゲート電極と配線を絶縁化する層間絶縁層を第1の有機絶縁物層1131を用いて形成

する。また、配線を形成する際、第1の有機絶縁物層の一部をドライエッチングにより除

去してゲート絶縁層1113の一部を露出した後、さらに半導体層を覆うゲート絶縁層1

113の一部をエッチングして半導体層を露出する。この後、半導体層に接続する配線1

305を形成する。

【0124】

有機絶縁物層1131は、実施の形態2に示す有機絶縁物層1121の材料及び形成方法

を適宜選択して形成することが出来る。ここでは、非感光性のアクリル樹脂を用いて有機

絶縁物層1131を形成する。

【0125】

次に、第1の有機絶縁物層1131上に、配線1305に接続する第1の電極層104を

形成する。

【0126】

次に、第1の電極層104の端部を覆う第2の有機絶縁物層1132を形成する。これ

は、実施の形態2の有機絶縁物層1121と同様に形成することができる。

【0127】

ここでは、塗布法を用いて感光性ポリイミドを含む組成物を塗布し、乾燥してポリイミ

ドで形成される絶縁膜を形成した後、フォトリソグラフィー工程により絶縁膜を露光、現

像した後焼成して、第1の電極層104の一部、及びゲート絶縁層1113の一部が露出

するように第2の有機絶縁物層1132を形成する。即ち、ゲート絶縁層1113の露出

部1133を形成する。

【0128】

次に、第2の有機絶縁物層1132及び第1の電極層104の露出表面に、実施の形態

1と同様に有機化合物を含む層105を形成する。なお、有機化合物を含む層105は、

ゲート絶縁層1113の露出部1133を覆わないように形成する。

【0129】

次に、図3(B)に示すように、有機化合物を含む層105及びゲート絶縁層1113

の露出部1133に接するように、実施の形態1と同様に第2の電極層106を形成する

。この結果、ゲート絶縁層1113に第2の電極層106が接する領域1134を形成す

ることができる。ゲート絶縁層1113に第2の電極層106が接する領域1134にお

いては、ゲート絶縁層1113と第2の電極層106との密着性が高いため、剥離工程に

おいて有機化合物を含む層105及び第2の電極層106の界面では剥離しにくくなり、

剥離層102及び絶縁層103で剥離することが可能である。

【0130】

なお、ここでは、絶縁層103から第2の電極層106までを含む積層物を素子形成層1

135という。

【0131】

以下、図3(C)に示す絶縁層107の形成、基板108の貼りあわせ、図3(D)に

示す剥離工程、及び図3(E)に示す基板109の貼りあわせは、実施の形態1と同様で

あるためここでは省略する。

【0132】

以上の工程により、剥離工程を用いて歩留まり高く可撓性を有する基板上に有機化合物

を含む層を有する素子を設けることができる。

【0133】

(実施の形態4)

本実施の形態では、実施の形態1乃至実施の形態3と異なる構成の素子形成層を剥離す

る方法を図4を用いて説明する。本実施の形態は、実施の形態3と比較して、第2の電極

層が、薄膜トランジスタのゲート電極と同様に形成される第1の導電層、薄膜トランジス

タの配線と同様に形成される第2の導電層、及び第1の電極層と同様に形成される第3の

導電層のいずれか一つ以上と接する点が異なる。本実施の形態では、第1の導電層、第2

の導電層、及び第3の導電層が積層されると共に、第3の導電層と第2の電極層とが接す

ることを特徴とする構成について示す。

【0134】

図4(A)に示すように、実施の形態1と同様に基板101上に剥離層102を形成し

、剥離層102上に絶縁層103を形成し、絶縁層103上に薄膜トランジスタ1111

を形成する。本実施の形態では、ゲート絶縁層1113上に導電膜を形成した後、フォト

リソグラフィー工程により形成したレジストマスクを用いて導電膜を選択的にエッチング

してゲート電極1304及び第1の導電層1141を形成する。

【0135】

また、実施の形態3と同様に、薄膜トランジスタ1111のゲート電極と配線を絶縁化す

る層間絶縁層を第1の有機絶縁物層1140を用いて形成する。また、第1の有機絶縁物

層1140の一部は第1の導電層1141の一部を露出する。この後、半導体層に接続す

る配線1305を形成すると共に、第1の導電層1141に接する第2の導電層1142

を形成する。代表的には、第1の有機絶縁物層1140、ゲート電極1304、及び第1

の導電層1141上に導電膜を形成した後、フォトリソグラフィー工程により形成したレ

ジストマスクを用いて導電膜を選択的にエッチングして、配線1305及び第2の導電層

1142を形成する。

【0136】

次に、第1の有機絶縁物層1140上に第1の電極層104を形成すると共に、第2の導

電層1142上に第3の導電層1144を形成する。

【0137】

次に、第1の電極層104の端部を覆う第2の有機絶縁物層1132を形成する。第2

の有機絶縁物層1132は、実施の形態2の有機絶縁物層1121と同様に形成すること

ができる。

【0138】

次に、第2の有機絶縁物層1132及び第1の電極層104の露出表面に、実施の形態

1と同様に有機化合物を含む層105を形成する。なお、有機化合物を含む層105は、

第3の導電層1144の一部が露出するように形成する。なお、第3の導電層1144の

露出部を1143と示す。

【0139】

次に、図4(B)に示すように、有機化合物を含む層105及び第3の導電層1144

の露出部1143に接するように、実施の形態1と同様に第2の電極層106を形成する

。この結果、第3の導電層1144に第2の電極層106が接する領域1145を形成す

ることができる。第3の導電層1144に第2の電極層106が接する領域1145にお

いては、第3の導電層1144と第2の電極層106との密着性が高いため、剥離工程に

おいて有機化合物を含む層105及び第2の電極層106の界面では剥離されにくくなり

、剥離層102及び絶縁層103で剥離することが可能である。

【0140】

なお、図11(A)に示すように、第2の電極層106が、第2の導電層1142及び第

3の導電層1144に接しても良い。

【0141】

また、図11(B)に示すように、第2の電極層106が、第1の導電層1141、第2

の導電層1142、及び第3の導電層1144に接しても良い。

【0142】

また、図11(C)に示すように、第2の電極層106が、第1の導電層1141及び第

3の導電層1144に接しても良い。

【0143】

また、図11(D)に示すように、第2の電極層106が、第3の導電層1144に接し

ても良い。なお、ここでは、第3の導電層1144は第1の導電層1141にも接する。

【0144】

また、図11(E)に示すように、第2の電極層106が、第1の導電層1141、及び

第2の導電層1142に接しても良い。

【0145】

また、図11(F)に示すように、第2の電極層106が、第2の導電層1142に接し

ても良い。なお、ここでは、第2の導電層1142は第1の導電層1141にも接する。

【0146】

また、図11(G)に示すように、第2の電極層106が、第3の導電層1144に接し

ても良い。なお、ここでは、第3の導電層1144はゲート絶縁層1113にも接する。

【0147】

また、図11(H)に示すように、第2の電極層106が、第2の導電層1142に接し

ても良い。なお、ここでは、第2の導電層1142はゲート絶縁層1113にも接する。

【0148】

また、図11(I)に示すように、第2の電極層106が、第1の導電層1141に接し

ても良い。なお、ここでは、第1の導電層1141はゲート絶縁層1113にも接する。

【0149】

なお、図4(B)に示すように、ここでは、絶縁層103から第2の電極層106までの

積層物を素子形成層1146という。

【0150】

以下、図4(C)に示す絶縁層107の形成、基板108の貼りあわせ、図4(D)に

示す剥離工程、及び図4(E)に示す基板109の貼りあわせは、実施の形態1と同様で

あるためここでは省略する。

【0151】

以上の工程により、剥離工程を用いて歩留まり高く可撓性を有する基板上に有機化合物

を含む層を有する素子を設けることができる。

【実施例1】

【0152】

本実施例では、有機化合物を含む層を有する素子として記憶素子を有する半導体装置、代

表的には記憶装置について説明する。

【0153】

図8(A)に示したのは本実施例で示す半導体装置の一構成例であり、メモリセル22

1がマトリクス状に設けられたメモリセルアレイ222、デコーダ223、ワード線駆動

回路224、セレクタ225、読み出し/書き込み回路226を有する。なお、ここで示

す記憶装置216の構成はあくまで一例であり、センスアンプ、出力回路、バッファ等の

他の回路を有していてもよい。

【0154】

ビット線駆動回路、ワード線駆動回路224、書き込み回路、インターフェース等は、記

憶素子と同様に薄膜トランジスタを用いて基板上に形成することができる。また、ICチ

ップとして外付けしても良い。

【0155】

メモリセル221は、ビット線Bx(1≦x≦m)に接続する第1の配線と、ワード線

Wy(1≦y≦n)に接続する第2の配線と、薄膜トランジスタ240と、記憶素子24

1とを有する。記憶素子241は、一対の導電層の間に、有機化合物を含む層が挟まれた

構造を有する。

【0156】

次に、上記構成を有するメモリセルアレイ222の上面図と断面図の一例に関して図9

を用いて説明する。なお、図9(A)はメモリセルアレイ222の上面図の一例を示して

おり、図9(B)は図9(A)におけるA−B間の断面図、及び図9(A)に示していな

いがメモリセルアレイ222の周辺部をC−Dに示している。なお、図9(A)において

は、第1の電極層243上に形成される、有機絶縁物層364、絶縁層331、有機化合

物を含む層265、及び第2の電極層366を省略している。

【0157】

メモリセルアレイ222は、複数のメモリセル221がマトリクス状に設けられている

。又、メモリセル221は、基板334、ここではプラスチック基板上にスイッチング素

子として機能する薄膜トランジスタ240および当該薄膜トランジスタ240に接続され

た記憶素子241が設けられている(図9(A)、図9(B)参照。)。

【0158】

記憶素子241は、有機絶縁物層368上に形成される第1の電極層243と、第1の電

極層243、及び有機絶縁物層364を覆う有機化合物を含む層365と、第2の電極層

366とを有する。また、第1の電極層の一部を覆う有機絶縁物層364が形成される。

【0159】

また、周辺部C−Dにおいては、薄膜トランジスタ240のゲート絶縁層369と第2の

電極層366とが接する領域367が形成される。

【0160】

また、第2の電極層366上には、表面の凹凸を緩和するための絶縁層331が形成され

、絶縁層331上にプラスチック基板335が貼りあわせられている。

【0161】

なお、図9(B)において、有機化合物を含む層365は複数の第1の電極層にまたが

って形成された例を示しているが、各メモリセルのみに有機化合物を含む層365を選択

的に設けてもよい。この場合、メタルマスクを用いた蒸着法を適用することができる。ん

また、液滴吐出法等を用いて有機化合物を吐出し焼成して選択的に有機化合物を含む層を

設けることにより材料の利用効率を向上させることが可能となる。

【0162】

第1の電極層243と第2の電極層366の材料および形成方法は、上記実施の形態1

で示した材料および形成方法のいずれかを用いて同様に行うことができる。

【0163】

また、有機化合物を含む層365は、上記実施の形態1で示した有機化合物を含む層1

05と同様の材料および形成方法を用いて設けることができる。

【0164】

また、基板334、335としては、実施の形態1で示した基板108、109で示し

た可撓性基板、ラミネートフィルム、繊維質な材料からなる紙等を用いることで、半導体

装置の小型、薄型、軽量化を図ることが可能である。

【0165】

次に、アクティブマトリクス型の半導体装置の作製方法について、図10を用いて説明す

る。

【0166】

図10(A)は、アクティブマトリクス型の半導体装置のメモリセルアレイの断面図で

ある。なお、ビット線駆動回路、ワード線駆動回路、インターフェース等の周辺回路は省

略している。

【0167】

図10(A)に示すように、基板301上に厚さ30nmの剥離層302を形成し、剥

離層302上に絶縁層303を形成する。次に、絶縁層303上にTFT240を形成す

る。ここでは、基板301としてガラス基板を用いる。

【0168】

なお、ここでは、TFT240のゲート電極と、ソース電極ドレイン電極とを絶縁する

ための層間絶縁層を有機絶縁物層368で形成している。このため、周辺部C−Dにおい

ては、有機絶縁物層368の一部が除去され、TFTのゲート絶縁層369が露出してい

る。

【0169】

次に、TFT240上に有機絶縁物層364を形成する。次に、有機絶縁物層364と

、TFTのソース電極又はドレイン電極の露出部との上に有機化合物を含む層365を形

成し、有機化合物を含む層365及びゲート絶縁層369上に第2の電極層366を形成

する。

【0170】

ここでは、ゲート絶縁層369と第2の電極層366が接する領域367が形成されるよ

うに第2の電極層366を形成する。ゲート絶縁層369と第2の電極層366が接する

領域では、ゲート絶縁層369と第2の電極層366の密着性が高いため、後の剥離工程

において、歩留まり高く剥離層及び絶縁層を剥離することが可能である。

【0171】

次に、図10(B)に示すように、第2の電極層366上に絶縁層331を形成した後

、絶縁層331上に接着層を有するプラスチックフィルム332を貼り合わせる。次に、

基板301の表面に弱粘着テープ(図示せず)を貼りあわせた後、120〜150度に加

熱してプラスチックフィルム332の接着層を可塑化させて、プラスチックフィルム33

2を絶縁層331に接着させる。

【0172】

次に、基板301を平坦部表面上に配置し、プラスチックフィルム332表面に粘着層

を有するローラー(図示せず)を圧着させ、図10(C)に示すように、剥離層302及

び絶縁層303の界面で剥離する。

【0173】

次に図10(D)に示すように、絶縁層303表面に接着層を有する基板334を貼り

あわせ、120〜150度に加熱して基板334の接着層を可塑化させて、基板334を

絶縁層303表面に接着させる。

【0174】

以上の工程により、プラスチックフィルム上にアクティブマトリクス型の半導体装置を

形成することが出来る。なお、本実施例では実施の形態1乃至4のいずれをも適用するこ

とができる。

【0175】

次に、記憶装置216にデータの書き込みを行うときの動作について説明する(図8、

9)。

【0176】

ここでは、電気的作用、代表的には電圧印加によりデータの書き込みを行うときの動作に

ついて説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メ

モリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気特性を変化

させた状態を「1」とする。

【0177】

n行m列目のメモリセル221にデータを書き込む場合について説明する。メモリセル2

21にデータ「1」を書き込む場合、まず、デコーダ223およびセレクタ225によっ

てメモリセル221を選択する。具体的には、デコーダ223によって、メモリセル22

1に接続されるワード線Wnに所定の電圧V22を印加する。また、デコーダ223とセ

レクタ225によって、メモリセル221に接続されるビット線Bmを読み出し/書き込

み回路226に接続する。そして、読み出し/書き込み回路226からビット線B3へ書

き込み電圧V21を出力する。

【0178】

こうして、メモリセルを構成する薄膜トランジスタ240をオン状態とし、記憶素子24

1に、共通電極及びビット線を電気的に接続し、おおむねVw=VcomーV21の電圧

を印加する。電圧Vwを適切に選ぶことで、当該電極層の間に設けられた有機化合物を含

む層を物理的もしくは電気的変化させ、データ「1」の書き込みを行う。具体的には、読

み出し動作電圧において、データ「1」の状態の第1の電極層と第2の電極層の間の電気

抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよく、単に

短絡(ショート)させてもよい。短絡させた記憶素子は、図7(B)に示すように、短絡

した領域212を有する。なお、電位は、(V21、V22、Vcom)=(5〜15V

、5〜15V、0V)、あるいは(−12〜0V、−12〜0V、3〜5V)の範囲から

適宜選べば良い。電圧Vwは5〜15V、あるいは−15〜−5Vとすればよい。

【0179】

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「

1」が書き込まれないよう制御する。具体的には、非選択のワード線には接続されるメモ

リセルのトランジスタをオフ状態とする電位(例えば0V)を印加し、非選択のビット線

は浮遊状態とするか、Vcomと同程度の電位を印加するとよい。

【0180】

一方、メモリセル221にデータ「0」を書き込む場合は、メモリセル221には電気的

作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコ

ーダ223およびセレクタ225によってメモリセル221を選択するが、読み出し/書

き込み回路226からビット線B3への出力電位をVcomと同程度とするか、ビット線

B3を浮遊状態とする。その結果、記憶素子241には、小さい電圧(例えば−5〜5V

)が印加されるか、電圧が印加されないため、電気特性が変化せず、データ「0」書き込

みが実現される。

【0181】

次に、電気的作用により、データの読み出しを行う際の動作について説明する(図8)。

データの読み出しは、記憶素子241の電気特性が、データ「0」を有するメモリセルと

データ「1」を有するメモリセルとで異なることを利用して行う。例えば、データ「0」

を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR0、データ

「1」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR1と

し、電気抵抗の差を利用して読み出す方法を説明する。なお、R1<R0とする。読み出

し/書き込み回路は、読み出し部分の構成として、例えば、図8(B)に示す抵抗素子2

46と差動増幅器247を用いた回路226を考えることができる。抵抗素子は抵抗値R

rを有し、R1<Rr<R0であるとする。抵抗素子246の代わりに、トランジスタ2

50を用いても良いし、差動増幅器の代わりにクロックトインバータ251を用いること

も可能である(図8(C))。勿論、回路構成は図8に限定されない。

【0182】

n行m列目メモリセル221からデータの読み出しを行う場合、まず、デコーダ223お

よびセレクタ225によってメモリセル221を選択する。具体的には、デコーダ223

によって、メモリセル221に接続されるワード線Wnに所定の電圧V24を印加し、薄

膜トランジスタ240をオン状態にする。また、デコーダ223とセレクタ225によっ

て、メモリセル221に接続されるビット線Bmを読み出し/書き込み回路226の端子

Pに接続する。その結果、端子Pの電位Vpは、VcomとV0が抵抗素子246(抵抗

値Rr)と記憶素子241(抵抗値R0もしくはR1)による抵抗分割によって決定され

る値となる。従って、メモリセル221がデータ「0」を有する場合には、Vp0=Vc

om+(V0−Vcom)×R0/(R0+Rr)となる。また、メモリセル221がデ

ータ「1」を有する場合には、Vp1=Vcom+(V0−Vcom)×R1/(R1+

Rr)となる。その結果、図8(B)では、VrefをVp0とVp1の間となるように

選択することで、図8(C)では、クロックトインバータの変化点をVp0とVp1の間

となるように選択することで、出力電位Voutが、データ「0」/「1」に応じて、L

ow/High(もしくはHigh/Low)が出力され、読み出しを行うことができる

。

【0183】

例えば、差動増幅器をVdd=3Vで動作させ、Vcom=0V、V0=3V、Vref

=1.5Vとする。仮に、R0/Rr=Rr/R1=9とし、薄膜トランジスタ240の

オン抵抗を無視できるとすると、メモリセルのデータが「0」の場合、Vp0=2.7V

となりVoutはHighが出力され、メモリセルのデータが「1」の場合、Vp1=0

.3VとなりVoutはLowが出力される。こうして、メモリセルの読み出しを行うこ

とができる。

【0184】

上記の方法によると、記憶素子241の抵抗値の相違と抵抗分割を利用して、電圧値で読

み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差

を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電

気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場

合には、しきい値電圧の差を利用して読み出しても構わない。

【0185】

なお、本実施例は上記実施の形態と自由に組み合わせて行うことができる。

【0186】

本発明を用いることによって、記憶素子の有機化合物を含む層で剥離せず、剥離層の界面

において剥離を行うことが可能である。このため、耐熱性を有する基板上に形成した記憶

素子を有する層を剥離し、可撓性を有する基板上に設けることが可能である。本発明を用

いることによって、チップ製造時以外にデータの書き込み(追記)が可能であり、また書

き換えができないため、書き換えによる偽造を防止すること可能な半導体装置を得ること

ができる。また、本発明の半導体装置は、一対の導電層間に有機化合物を含む層が挟まれ

た単純な構造の記憶素子を有するため、安価な半導体装置を提供することができる。

【実施例2】

【0187】

本実施例では、非接触でデータの読み出しと書き込みが可能である半導体装置の作製方

法について、図12を用いて説明する。

【0188】

図12(A)は、非接触でデータの読み出しと書き込みが可能である半導体装置のメモ

リセルアレイの断面図である。なお、ビット線駆動回路、ワード線駆動回路、インターフ

ェース等の周辺回路は省略している。

【0189】

図12(A)に示すように、実施例1と同様に基板301上に厚さ30nmの剥離層3

02を形成し、剥離層302上に絶縁層303を形成する。次に、絶縁層303上にTF

T381〜383を形成する。ここでは、TFT381は、アンテナとして機能する導電

層に接続するTFTであり、TFT382、383は、記憶素子に接続するTFTである

。

【0190】

なお、ここでも実施例1と同様に、TFT381〜383のゲート電極と、ソース電極

ドレイン電極とを絶縁するための層間絶縁層を有機絶縁物層388で形成している。この

ため、有機絶縁物層388の一部が除去され、TFTのゲート絶縁層389が露出してい

る。このため、無機絶縁物層のゲート絶縁層389と、金属層で形成される第2の電極層

385とが接する領域387を有する。

【0191】

次に、実施例1と同様にTFT361〜363上に有機絶縁物層364を形成する。次

に、有機絶縁物層364と、TFTのソース電極又はドレイン電極の露出部との上に有機

化合物を含む層384を形成し、有機化合物を含む層384上に第2の電極層385を形

成すると同時にアンテナとして機能する導電層386を形成する。なお、第2の電極層3

85は、有機化合物を含む層384及びゲート絶縁層389に接する。有機絶縁物層36

4、有機化合物を含む層384、及び第2の電極層385はそれぞれ、実施例1で示す有

機絶縁物層310、有機化合物を含む層311、及び第2の電極層312と同様に形成す

ることが出来る。

【0192】

ここでは、ゲート絶縁層389と第2の電極層385が接する領域387が形成されるよ

うに第2の電極層385を形成する。ゲート絶縁層389と第2の電極層385が接する

領域ではゲート絶縁層389と第2の電極層385の密着性が高いため、後の剥離工程に

おいて、有機化合物を含む層384及び第2の電極層385の間で剥離することなく、歩

留まり高く剥離層及び絶縁層を剥離することが可能である。

【0193】

次に、図12(B)に示すように、実施例1と同様に、第2の電極層上に絶縁層331

を形成した後、絶縁層331上に接着層を有するプラスチックフィルム332を貼り合わ

せる。

【0194】

以下、図12(D)に示す剥離工程、及び図12(E)に示す基板109の貼りあわせ

は、実施例1と同様であるためここでは省略する。

【0195】

以上の工程により、プラスチックフィルム上に非接触でデータの読み出しと書き込みが

可能である半導体装置を形成することが出来る。なお、本実施例では実施の形態1乃至4

のいずれをも適用することができる。

【実施例3】

【0196】

本実施例では、実施例2と異なる非接触でデータの読み出しと書き込みが可能である半

導体装置の作製方法について、図13を用いて説明する。

【0197】

図13(A)に示すように、実施例1と同様に基板301上に厚さ30nmの剥離層3

02を形成し、剥離層302上に絶縁層303を形成する。次に、絶縁層303上にTF

T381〜383を形成する。

【0198】

次に、実施例1と同様にTFT381〜383上に有機絶縁物層364を形成する。次

に、有機絶縁物層364と、TFTのソース電極又はドレイン電極の露出部との上に有機

化合物を含む層384を形成し、有機化合物を含む層384上に第2の電極層385を形

成すると同時に接続端子390を形成する。有機絶縁物層364、有機化合物を含む層3

84、及び第2の電極層385はそれぞれ、実施例1で示す有機絶縁物層310、有機化

合物を含む層311、及び第2の電極層312と同様に形成することが出来る。

【0199】

ここでは、ゲート絶縁層389と第2の電極層385が接する領域387が形成されるよ

うに第2の電極層385を形成する。ゲート絶縁層389と第2の電極層385の密着性

が高いため、後の剥離工程において、歩留まり高く剥離層及び絶縁層を剥離することが可

能である。

【0200】

次に、第2の電極層385上に保護層391を形成する。ただし、保護層391は、接

続端子390を露出するように形成する。次に、図13(B)に示すように、保護層39

1上に接着層392を形成し、接着層392に基板393を貼りあわせる。接着層392

は、光可塑性接着剤、熱可塑性接着剤、化学可塑性接着剤等の可塑性接着剤を用いて形成

する。基板393は、基板301と同様のものを用いることが出来る。ここでは、接着層

392として光可塑化樹脂を用い、基板393にガラス基板を用いる。

【0201】

次に、図13(C)に示すように、剥離層302及び絶縁層303の界面で剥離する。

【0202】

次に図17(D)に示すように、絶縁層303表面に接着層を有するプラスチックフィ

ルム394を貼りあわせ、120〜150度に加熱してプラスチックフィルム394の接

着層を可塑化させて、プラスチックフィルム394を絶縁層303表面に接着させる。

【0203】

次に、接着層392を可塑化して基板393及び接着層392を除去する。ここでは、接

着層392にUV光を照射して接着層を可塑化し、基板を除去する。

【0204】

次に、図13(E)に示すように、TFT及び記憶素子を有する基板と、アンテナとし

て機能する導電層398が設けられた基板399を、異方性導電フィルム又は異方性導電

接着剤を用いて貼りあわせる。ここでは、異方性導電接着剤397を用いて接着剤に含ま

れる導電性粒子396により接続端子390とアンテナとして機能する導電層398とを

電気的に接続させる。なお、第2の電極層385は保護層391によって保護されている

ため、第2の電極層385と導電層398とは電気的に接続されることがない。

【0205】

以上の工程により、プラスチックフィルム上に非接触でデータの読み出しと書き込みが

可能である半導体装置を形成することが出来る。

【0206】

なお、本実施例では実施の形態1乃至4のいずれをも適用することができる。

【実施例4】

【0207】

ここで、実施例2、3に示す素子を有する半導体装置の構成について、図14を参照して

説明する。図14(A)に示すように、本発明の半導体装置20は、非接触でデータを交

信する機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、

他の回路を制御する制御回路14、インターフェース回路15、記憶回路16、バス17

、アンテナ18を有する。

【0208】

また、図14(B)に示すように、本発明の半導体装置20は、非接触でデータを交信す

る機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の

回路を制御する制御回路14、インターフェース回路15、記憶回路16、バス17、ア

ンテナ18の他、中央処理ユニット51を有しても良い。

【0209】

また、図14(C)に示すように、本発明の半導体装置20は、非接触でデータを交信す

る機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の

回路を制御する制御回路14、インターフェース回路15、記憶回路16、バス17、ア

ンテナ18、中央処理ユニット51の他、検出素子53、検出制御回路54からなる検出

部52を有しても良い。

【0210】

本実施例の半導体装置は、電源回路11、クロック発生回路12、データ復調/変調回路

13、他の回路を制御する制御回路14、インターフェース回路15、記憶回路16、バ

ス17、アンテナ18、中央処理ユニット51の他、検出素子53、検出制御回路54か

らなる検出部52等を構成することで、小型で多機能を有する半導体装置を形成すること

が可能である。

【0211】

電源回路11は、アンテナ18から入力された交流信号を基に、半導体装置20の内部

の各回路に供給する各種電源を生成する回路である。クロック発生回路12は、アンテナ

18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種クロ

ック信号を生成する回路である。データ復調/変調回路13は、リーダライタ19と交信

するデータを復調/変調する機能を有する。制御回路14は、記憶回路16を制御する機

能を有する。アンテナ18は、電磁波或いは電波の送受信を行う機能を有する。リーダラ

イタ19は、半導体装置との交信、制御及びそのデータに関する処理を制御する。なお、

半導体装置は上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハ

ードウエアといった他の要素を追加した構成であってもよい。

【0212】

記憶回路16は、実施の形態1乃至実施の形態4、及び実施例1並びに実施例2に示す

記憶素子から選択される1つ又は複数を有する。有機化合物を含む層を有する記憶素子は

、小型化、薄膜化および大容量化を同時に実現することができるため、記憶回路16を有

機化合物を含む層を有する記憶素子で設けることにより、半導体装置の小型化、軽量化を

達成することができる。

【0213】

検出部52は、温度、圧力、流量、光、磁気、音波、加速度、湿度、気体成分、液体成分

、その他の特性を物理的又は化学的手段により検出することができる。また、検出部52

は、物理量または化学量を検出する検出素子53と当該検出素子53で検出された物理量

または化学量を電気信号等の適切な信号に変換する検出制御回路54とを有している。検

出素子53としては、抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換

素子、熱起電力素子、トランジスタ、サーミスタ、ダイオード等で形成することができる

。なお、検出部52は複数設けてもよく、この場合、複数の物理量または化学量を同時に

検出することが可能である。

【0214】

また、ここでいう物理量とは、温度、圧力、流量、光、磁気、音波、加速度、湿度等を指

し、化学量とは、ガス等の気体成分やイオン等の液体に含まれる成分等の化学物質等を指

す。化学量としては、他にも、血液、汗、尿等に含まれる特定の生体物質(例えば、血液

中に含まれる血糖値等)等の有機化合物も含まれる。特に、化学量を検出しようとする場

合には、必然的にある特定の物質を選択的に検出することになるため、あらかじめ検出素

子53に検出したい物質と選択的に反応する物質を設けておく。例えば、生体物質の検出

を行う場合には、検出素子53に検出させたい生体物質と選択的に反応する酵素、抗体分

子または微生物細胞等を高分子等に固定化して設けておくことが好ましい。

【0215】

本発明により無線チップとして機能する半導体装置を作製することができる。無線チッ

フ゜の用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類

(運転免許証や住民票等、図20(A)参照)、包装用容器類(包装紙やボトル等、図2

0(C)参照)、記録媒体(DVDソフトやビデオテープ等、図20(B)参照)、乗物

類(自転車等、図20(D)参照)、身の回り品(鞄や眼鏡等)、食品類、植物類、動物

類、人体、衣類、生活用品類、電子機器等の商品や荷物の荷札(図20(E)、図20(

F)参照)等の物品に設けて使用することができる。電子機器とは、液晶表示装置、EL

表示装置、テレビジョン装置(単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ

)及び携帯電話等を指す。

【0216】

本発明の半導体装置20は、プリント基板に実装したり、表面に貼ったり、埋め込んだり

して、物品に固定される。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケー

ジなら当該有機樹脂に埋め込んだりして、各物品に固定される。本発明の半導体装置20

は、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性

を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明

の半導体装置20を設けることにより、認証機能を設けることができ、この認証機能を活

用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、

食品類、衣類、生活用品類、電子機器等に本発明の半導体装置を設けることにより、検品

システム等のシステムの効率化を図ることができる。

【実施例5】

【0217】

本実施例では、発光素子を有する半導体装置の作製工程について説明する。

【0218】

図15(A)に示すように、基板401上に剥離層402を形成する。本実施例では基

板としてAN100を用いる。このガラス基板上にスパッタリング法で剥離層402、こ

こではタングステン層(厚さ10nm〜200nm、好ましくは50nm〜75nm)を

形成し、次に、絶縁層403を形成する。ここでは、CVD法により膜厚140nmの窒

化酸化珪素膜、膜厚100nmの酸化窒化珪素膜を形成する。

【0219】

次に、絶縁層403上に、pチャネル型TFT414、416、nチャネル型TFT41

5を形成する。なお、pチャネル型TFT414及びnチャネル型TFT415により駆

動回路を構成する。また、pチャネル型TFT416は、発光素子を駆動する駆動素子と

して機能する。

【0220】

TFT414〜416のゲート電極及び配線を絶縁化する第1の層間絶縁層417を酸

化窒化珪素、窒化酸化珪素、及びアクリル樹脂を用いて積層して形成する。また、第1の

層間絶縁層417上にTFTの半導体層に接続する配線418〜423、及び接続端子4

24を形成する。ここでは、スパッタリング法により、Ti膜100nm、Al膜700

nm、Ti膜100nmを連続成膜した後、フォトリソグラフィー工程によって形成した

レジストマスクを用いて選択的にエッチングして、配線418〜423、及び接続端子4

24を形成する。その後、レジストマスクを除去する。

【0221】

次いで、層間絶縁層417、配線418〜423、及び接続端子424上に、第2の層間

絶縁層425を形成する。第2の層間絶縁層425としては、酸化珪素膜、窒化珪素膜ま

たは酸化窒化珪素膜などの無機絶縁膜を用いることができ、これらの絶縁膜を単層又は2

以上の複数層で形成すればよい。また、無機絶縁膜を形成する方法としてはスパッタ法、

LPCVD法、またはプラズマCVD法等を用いればよい。

【0222】

本実施例では、プラズマCVD法を用い、無機絶縁膜からなる第2の層間絶縁層425を

100nm〜150nmで形成する。

【0223】

次いで、フォトリソグラフィー工程により形成したレジストマスクを用いて第2の層間

絶縁層425を選択的にエッチングして、駆動用TFTの配線423、及び接続端子42

4に達するコンタクトホールを形成する。その後、レジストマスクを除去する。

【0224】

次いで、駆動用TFTの配線423に接続する第1の電極層426、及び接続端子42

4と接続する導電層430を形成する。第1の電極層426及び導電層430は、スパッ

タリング法により膜厚125nmの酸化珪素を含むITOを成膜した後、フォトリソグラ

フィー工程により形成したレジストマスクを用いて選択的にエッチングして形成する。

【0225】

本実施例のように、第2の層間絶縁層425を形成することで、駆動回路部のTFTや配

線等の露出を防ぎ、汚染物質からTFTを保護することができる。

【0226】

次に、第1の電極層426の端部を覆う有機絶縁物層427を形成する。ここでは、感

光性ポリイミドを塗布し焼成した後、露光及び現像を行って駆動回路、画素領域の第1の

電極層426、及び画素領域の周辺部における第2の層間絶縁層425が露出されるよう

に有機絶縁物層427を形成する。

【0227】

次に、第1の電極層426及び有機絶縁物層427の一部上に蒸着法により発光物質を含

む層428を形成する。発光物質を含む層428は、発光性を有する有機化合物で形成す

る。また、有機化合物を含む層363を赤色の発光性の有機化合物、青色の発光性の有機

化合物、及び緑色の発光性の有機化合物を用いて、それぞれ赤色の発光性の画素、青色の

発光性の画素、及び緑色の発光性の画素を形成する。

【0228】

ここでは、赤色の発光性の有機化合物を含む層として、DNTPDを50nm、NPBを

10nm、ビス[2,3−ビス(4−フルオロフェニル)キノキサリナト]イリジウム(

アセチルアセトナート)(略称:Ir(Fdpq)2(acac))が添加されたNPB

を30nm、Alq3を60nm、及びLiFを1nm積層して形成する。

【0229】

また、緑色の発光性の有機化合物を含む層として、DNTPDを50nm、NPBを10

nm、クマリン545T(C545T)が添加されたAlq3を40nm、Alq3を6

0nm、及びLiFを1nm積層して形成する。

【0230】

また、青色の発光性の有機化合物を含む層として、DNTPDを50nm、NPBを10

nm、2,5,8,11−テトラ(tert−ブチル)ペリレン(略称:TBP)が添加

された、9−[4−(N−カルバゾリル)]フェニル−10−フェニルアントラセン(略

称:CzPA:)を30nm、Alq3を60nm、及びLiFを1nm積層して形成す

る。

【0231】

さらには、白色の発光性の有機化合物を用いて白色の発光性の画素を形成してもよい。白

色の発光性の画素を設けることにより、消費電力を削減することが可能である。

【0232】

次に、図15(B)に示すように、発光物質を含む層428、有機絶縁物層427、及び

第2の層間絶縁層425上に第2の電極層431を形成する。ここでは、膜厚200nm

のAl膜を蒸着法により形成する。このとき、無機化合物で形成される第2の層間絶縁層

425及び第2の電極層431が接する領域432が形成される。無機化合物で形成され

る第2の層間絶縁層425及び第2の電極層431が接する領域432では密着性が高い

ため、後の剥離工程において発光物質を含む層428及び第2の電極層431の間で剥離

することなく、剥離層302及び絶縁層303で剥離することが可能で有る。

【0233】

次に、図15(C)に示すように、第2の電極層431上に保護層441を形成する。

保護層は、発光素子に水分や酸素等が侵入することを防ぐためのものである。保護層44

1は、プラズマCVD法又はスパッタリング法などの薄膜形成法を用い、窒化珪素、酸化

珪素、窒化酸化珪素、酸化窒化珪素、酸化窒化アルミニウム、または酸化アルミニウム、

ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)、その他の絶縁性材料を

用いて形成することが好ましい。

【0234】

次に、保護層441上に絶縁層442を形成する。ここでは、組成物を塗布し焼成して形

成したエポキシ樹脂により絶縁層442を形成する。次に、絶縁層442上にプラスチッ

クフィルム443を貼りあわせる。次に、基板401の表面に弱粘着テープ(図示せず)

を貼りあわせた後、120〜150度に加熱してプラスチックフィルム443の接着層を

可塑化させて、プラスチックフィルム443を絶縁層442に接着させる。

【0235】

次に、基板401を平坦部表面上に配置し、プラスチックフィルム443表面に粘着層

を有するローラー(図示せず)を圧着させ、図16(A)に示すように、剥離層402及

び絶縁層403の界面で剥離する。

【0236】

次に、図16(B)に示すように、絶縁層403表面に粘着層を有するプラスチックフ

ィルム451を貼りあわせ、120〜150度に加熱してプラスチックフィルム451の

接着層を可塑化させて、プラスチックフィルム451を絶縁層403表面に接着させる。

【0237】

次に、異方性導電層453を用いてFPC454を接続端子424に接する導電層430

と貼りつける。

【0238】

以上の工程により、プラスチックフィルム上にアクティブマトリクス型発光素子を有す

る半導体装置を形成することが出来る。

【0239】

ここで本実施例において、フルカラー表示する場合の画素における等価回路図を図17に

示す。図17において、破線で囲まれるTFT639が図16(B)の駆動用のTFT6

03に対応している。

【0240】

赤色を表示する画素は、駆動用のTFT639のドレイン領域に赤色を発光するOLED

703Rが接続され、ソース領域にはアノード側電源線(R)706Rが設けられている

。また、OLED703Rには、カソード側電源線700が設けられている。また、スイ

ッチング用のTFT638はゲート配線705に接続され、駆動用のTFT639のゲー

ト電極は、スイッチング用のTFT638のドレイン領域に接続される。なお、スイッチ

ング用のTFT638のドレイン領域は、アノード側電源線(R)706(R)に接続さ

れた容量素子707と接続している。

【0241】

また、緑色を表示する画素は、駆動用のTFTのドレイン領域に緑色を発光するOLED

703Gが接続され、ソース領域にはアノード側電源線(G)706Gが設けられている

。また、スイッチング用のTFT638はゲート配線705に接続され、駆動用のTFT

639のゲート電極は、スイッチング用のTFT638のドレイン領域に接続される。な

お、スイッチング用のTFT638のドレイン領域は、アノード側電源線(G)706(

G)に接続された容量素子707と接続している。

【0242】

また、青色を表示する画素は、駆動用のTFTのドレイン領域に青色を発光するOLED

703Bが接続され、ソース領域にはアノード側電源線(B)706Bが設けられている

。また、スイッチング用のTFT638はゲート配線705に接続され、駆動用のTFT

639のゲート電極は、スイッチング用のTFT638のドレイン領域に接続される。な

お、スイッチング用のTFT638のドレイン領域は、アノード側電源線(B)706(

B)に接続された容量素子707と接続している。

【0243】

それぞれ色の異なる画素にはEL材料に応じて異なる電圧をそれぞれ印加する。

【0244】

なお、ここでは、ソース配線704とアノード側電源線706R、706G、706Bと

を平行に形成しているが、これに限られず、ゲート配線705とアノード側電源線706

R、706G、706Bとを平行に形成してもよい。更には、駆動用のTFT639をマ

ルチゲート電極構造としてもよい。

【0245】

また、発光装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方

法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法

とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置のソ

ース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であっても

よく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

【0246】

さらに、ビデオ信号がデジタルの発光装置において、画素に入力されるビデオ信号が定電

圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(CV

)には、発光素子に印加される信号の電圧が一定のもの(CVCV)と、発光素子に印加

される信号の電流が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの

(CC)には、発光素子に印加される信号の電圧が一定のもの(CCCV)と、発光素子

に印加される信号の電流が一定のもの(CCCC)とがある。

【0247】

また、発光装置において、静電破壊防止のための保護回路(保護ダイオードなど)を設

けてもよい。

【0248】

以上の工程により、プラスチックフィルム上に設けられたアクティブマトリクス型発光

素子を有する半導体装置を作製することが出来る。

【0249】

なお、本実施例では実施の形態1乃至4のいずれをも適用することができる。

【実施例6】

【0250】

次に、実施例5で示すEL表示パネルにFPCや、駆動用の駆動ICを実装する例につ

いて説明する。ここでは、TFTで形成されるチップ状の駆動用回路を駆動ICという。

【0251】

図18(a)に示す図は、FPC1009を4カ所の端子部1008に貼り付けた発光装

置の上面図の一例を示している。基板1010上には発光素子及びTFTを含む画素部1

002と、TFTを含むゲート側駆動回路1003と、TFTを含む第1の駆動回路10

01とが形成されている。TFTの活性層は結晶構造を有する半導体膜で構成されており

、同一基板上にこれらの回路を形成している。従って、システムオンパネル化を実現した

EL表示パネルを作製することができる。

【0252】

また、画素部を挟むように2カ所に設けられた接続領域1007は、発光素子の第2の電

極(陰極)を下層の配線とコンタクトさせるために設けている。なお、発光素子の第1の

電極(陽極)は画素部に設けられたTFTと電気的に接続している。

【0253】

また、封止基板1004は、画素部および駆動回路を囲むシール材1005、およびシー

ル材1005に囲まれた充填材料によって基板1010と固定されている。また、透明な

乾燥剤を含む充填材料を充填する構成としてもよい。また、画素部と重ならない領域に乾

燥剤を配置してもよい。

【0254】

なお、本実施例では、シール材1005の一部がTFTを含むゲート側駆動回路1003

と重なるように設けているが、表示領域の外周を囲むように設ければよい。すなわち、ゲ

ート側駆動回路1003と重ならないように設けても構わない。

【0255】

また、図18(a)に示した構造は、比較的大きなサイズ(例えば対角4.3インチ)

の発光装置で好適な例を示したが、図18(b)は、狭額縁化させた小型サイズ(例えば

対角1.5インチ)で好適なCOG方式を採用した例である。

【0256】

図18(b)において、基板1010上に駆動IC1011が実装され、駆動ICの先に

配置された端子部1018にFPC1019を実装している。実装される駆動IC101

1は、生産性を向上させる観点から、一辺が300mmから1000mmの矩形状の基板

上に複数作り込むとよい。つまり、基板上に駆動回路部と入出力端子を一つのユニットと

する回路パターンを複数個形成し、最後に分割して駆動ICを個別に取り出せばよい。駆

動ICの長辺の長さは、画素部の一辺の長さや画素ピッチを考慮して、長辺が15〜80

mm、短辺が1〜6mmの矩形状に形成してもよいし、画素領域の一辺、又は画素部の一

辺と各駆動回路の一辺とを足した長さに形成してもよい。

【0257】

駆動ICのICチップに対する外形寸法の優位性は長辺の長さにあり、長辺が15〜80

mmで形成された駆動ICを用いると、ICチップを用いる場合と比較して実装するチッ

プ数を削減することが可能であり、製造上の歩留まりを向上させることができる。また、

ガラス基板上に駆動ICを形成すると、母体として用いる基板の形状に限定されないので

生産性を損なうことが少ない。これは、円形のシリコンウエハからICチップを取り出す

場合と比較すると、大きな優位点である。

【0258】

また、TAB方式を採用してもよく、その場合は、複数のテープを貼り付けて、該テープ

に駆動ICを実装すればよい。COG方式の場合と同様に、単数のテープに単数の駆動I

Cを実装してもよく、この場合には、強度の問題から、駆動ICを固定するための金属片

等を一緒に貼り付けるとよい。

【0259】

また、画素部1102と駆動IC1011の間に設けられた接続領域1017は、発光素

子の第2の電極層を下層の配線とコンタクトさせるために設けている。なお、発光素子の

第1の電極は画素部に設けられたTFTと電気的に接続している。

【0260】

また、封止基板1014は、画素部1012を囲むシール材1015、およびシール材に

囲まれた充填材料によって基板1010に固定されている。

【0261】

なお、駆動ICの代わりに、Siチップで形成されるICチップを用いてもよい。

【0262】

また、画素部のTFTの活性層として非晶質半導体膜を用いる場合には、駆動回路を同一

基板上に形成することは困難であるため、大きなサイズであっても図12(b)の構成と

なる。

【0263】

ここで、接続領域1007を図13を用いて説明する。接続領域1007以外は、実施の

形態4、実施の形態5、又は実施の形態6と同じであるので、説明は省略する。

以上の様に、本発明を実施する、即ち実施例5の発光素子の構成を用いて、様々な電

子機器を完成させることができる。

【実施例7】

【0264】

次に、本発明の半導体装置を実装した電子機器の一態様について図面を参照して説明する

。ここで例示する電子機器は携帯電話機であり、筐体2700、2706、パネル270

1、ハウジング2702、プリント配線基板2703、操作ボタン2704、バッテリ2

705を有する(図19参照)。パネル2701はハウジング2702に脱着自在に組み

込まれ、ハウジング2702はプリント配線基板2703に嵌着される。ハウジング27

02はパネル2701が組み込まれる電子機器に合わせて、形状や寸法が適宜変更される

。プリント配線基板2703には、パッケージングされた複数の半導体装置が実装されて

おり、このうちの1つとして、本発明の半導体装置2710を用いることができる。プリ

ント配線基板2703に実装される複数の半導体装置は、コントローラ、中央処理ユニッ

ト(CPU、Central Processing Unit)、メモリ、電源回路、

音声処理回路、送受信回路等のいずれかの機能を有する。

【0265】

パネル2701は、接続フィルム2708を介して、プリント配線基板2703と接続さ

れる。上記のパネル2701、ハウジング2702、プリント配線基板2703は、操作

ボタン2704やバッテリ2705と共に、筐体2700、2706の内部に収納される

。パネル2701が含む画素領域2709は、筐体2700に設けられた開口窓から視認

できるように配置されている。パネル2701に実施例5及び6で示すような半導体装置

を用いることができる。

【0266】

上記の通り、本発明の半導体装置は、小型、薄型、軽量であることを特徴としており、上

記特徴により、電子機器の筐体2700、2706内部の限られた空間を有効に利用する

ことができる。

【0267】

なお、筐体2700、2706は、携帯電話機の外観形状を一例として示したものであり

、本実施例に係る電子機器は、その機能や用途に応じて様々な態様に変容しうる。

【技術分野】

【0001】

本発明は、可撓性を有する基板上に有機化合物を含む層を有する素子を備えた半導体装

置及びその作製方法に関する。

【背景技術】

【0002】

近年、絶縁表面上に複数の回路が集積され、様々な機能を有する半導体装置の開発が進

められている。また、アンテナを設けることにより、無線によるデータの送受信が可能な

半導体装置の開発が進められている。このような半導体装置は、無線チップ(IDタグ、

ICタグ、ICチップ、RF(Radio Frequency)タグ、無線タグ、電子

タグ、RFID(Radio Frequency Identification)タ

グともよばれる)とよばれ、既に一部の市場で導入されている。

【0003】

現在実用化されているこれらの半導体装置の多くは、Si等の半導体基板を用いた回路

(IC(Integrated Circuit)チップとも呼ばれる)とアンテナとを

有し、当該ICチップは記憶回路(メモリとも呼ぶ)や制御回路等から構成されている。

特に多くのデータを記憶可能な記憶回路を備えることによって、より高機能で付加価値が

高い半導体装置の提供が可能となる。

【0004】

また、これらの半導体装置は低コストで作製することが要求されており、近年、制御回

路や記憶回路等に有機化合物を含む層を用いたトランジスタ、メモリ、太陽電池等の素子

の開発が盛んに行われている(例えば特許文献1)。

【0005】

このような半導体装置を利用したアプリケーションは様々なものが期待されているが、

小型、軽量化を追及し、可撓性を有するプラスチックフィルムを用いることが試みられて

いる。

【0006】

プラスチックフィルムは耐熱性が低いため、プロセスの最高温度を低くせざるを得ず、

結果的にガラス基板上に形成する時ほど良好な電気特性のTFTを形成できないのが現状

である。

【0007】

そこで、ガラス基板上に形成した素子を基板から剥離し、他の基材、例えばプラスチッ

クフィルムなどに貼り付ける技術が提案されている(特許文献2参照)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−47791号公報

【特許文献2】特開2003−174153号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献2に示されるような剥離工程を用いて、有機化合物を含む層を

有する素子を剥離する場合、具体的には図23に示すように基板101上に剥離層102

を形成し、剥離層102上に絶縁層103を形成し、絶縁層103上に薄膜トランジスタ

1111を形成し、薄膜トランジスタ1111に接続する第1の電極層104を形成し、

第1の電極層104の端部を覆う有機絶縁物層1161を形成し、有機絶縁物層1161

上に有機化合物を含む層105を形成し、有機化合物を含む層105上及び有機絶縁物層

1161上に第2の電極層1162を形成することで、有機化合物を含む層を有する素子

151、及び素子151を有する層1163を剥離する場合、有機化合物を含む層105

及び第2の電極層1162の間で剥れるという問題がある。この結果、プラスチック基板

上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製するこ

とが困難である。

【0010】

これは、有機化合物を含む層105及び第2の電極層106の密着力が低いためである

。具体的には、有機絶縁物層を形成するポリイミド、エポキシ樹脂、アクリル樹脂等はイ

ミド基、シアノ基、水酸基などの極性置換基を有するため、無機化合物で形成される層、

ここでは、ゲート絶縁膜や第1の導電層と密着性が高い。しかしながら、有機化合物を含

む層105は半導体として機能するので、キャリア輸送性を有する材料を用いて形成する

。キャリア輸送性を有する材料は、一般的に極性置換基を有さない。この結果、有機化合

物を含む層105及び第2の電極層106の密着性が非常に小さくなってしまい、剥離工

程において有機化合物を含む層105及び第2の電極層106の間で剥れてしまう。

【0011】

上記問題を鑑み、本発明は、可撓性を有する基板上に有機化合物を含む層を有する素子

が設けられた半導体装置を歩留まり高く作製することを課題とする。

【課題を解決するための手段】

【0012】

本発明は、剥離層を有する基板上に、基板を上面からみて密着性が低い領域、及びその

外縁を囲むように密着性が高い領域を形成することを要旨とする。また、密着性が低い領

域の断面においては、例えばイミド基、シアノ基、水酸基などの極性置換基を有さない有

機化合物を含む層と無機化合物層が接しており、密着性が高い領域の断面においては、複

数の無機化合物層が接している。密着性の高い領域503は、図22(A)で一例を示す

ように、密着性の低い領域502の外縁を囲んでも良い。また、図22(B)で一例を示

すように、密着性の低い領域502の外縁を囲むように、密着性の高い領域503が非連

続的に形成されていてもよい。また、図22(C)で一例を示すように、密着性の低い領

域502の各辺に対応するように、矩形状の密着性の高い領域503が形成されていても

よい。なお、密着性の高い領域は、矩形状、円状、楕円状、曲線状等様々な形状とするこ

とが可能である。

【0013】

また、本発明は、剥離層501を有する基板上に、密着性が低い領域502及びその外

縁を囲むように密着性が高い領域503が形成される素子形成層を形成した後、基板及び

素子形成層を剥離層において分離し、可撓性を有する基板に貼りあわせることを要旨とす

る。

【0014】

なお、密着性が低い領域とは代表的には有機化合物を含む層及び第2の電極層が接する

領域であり、密着性が高い領域とは代表的には、第2の電極層及び無機化合物層が接する

領域である。また、密着性が高い領域とは代表的には第2の電極層及び導電層が接する領

域である。

【0015】

また、本発明の一は、基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導

電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する

第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基

板を貼りあわせた後、基板及び素子形成層を剥離層において分離することを特徴とする半

導体装置の作製方法である。

【0016】

また、本発明の一は、可撓性を有する基板と、無機化合物層と、有機化合物を含む層と

、有機化合物を含む層に接すると共に、無機化合物層に接する導電層を有する半導体装置

であることを特徴とする。

【0017】

なお、無機化合物層は、絶縁物層、または導電層である。また無機化合物層の代わりに

金属層を用いても良い。また、無機化合物層は、ゲート絶縁層、層間絶縁層、または接続

層として機能してもよい。

【0018】

有機化合物を含む層、及び有機化合物を含む層に接する導電層は、記憶素子、又は発

光素子の一部を構成する。

【0019】

また、本発明は以下を包含する。

【0020】

本発明の一は、基板上に剥離層を形成し、剥離層上に、無機化合物層、半導体素子、及

び半導体素子に接続する第1の電極層、第1の電極層上に有機化合物を含む層を形成し、

有機化合物を含む層及び無機化合物層に接する第2の電極層を形成して素子形成層を形成

し、第2の電極層上に第1の可撓性を有する基板を貼りあわせた後、基板及び素子形成層

を剥離層において分離することを特徴とする半導体装置の作製方法である。

【0021】

無機化合物層は、半導体素子が薄膜トランジスタの場合、薄膜トランジスタのゲート電

極及び配線を絶縁する絶縁層、薄膜トランジスタのゲート電極及び半導体層を絶縁するゲ

ート絶縁層、薄膜トランジスタのゲート電極と同じ材料で形成されると共に薄膜トランジ

スタのゲート電極と同じ層、薄膜トランジスタの配線と同じ材料で形成されると共に薄膜

トランジスタの配線と同じ層に接する層、または第1の電極層と同じ材料で形成されると

共に第1の電極層が接する層と同じ層に接する層である。

【0022】

本発明の一は、基板上に剥離層を形成した後、剥離層上に薄膜トランジスタを形成し、

薄膜トランジスタに接続する第1の電極層を形成し、第1の電極層の端部を覆う無機絶縁

物層を形成し、無機絶縁物層の一部及び第1の電極層の露出部に有機化合物を含む層を形

成し、有機化合物を含む層及び無機絶縁物層に接する第2の電極層を形成して素子形成層

を形成し、第2の電極層上に第1の可撓性を有する基板を貼りあわせた後、基板及び素子

形成層を剥離層において分離することを特徴とする半導体装置の作製方法である。

【0023】

本発明の一は、基板上に剥離層を形成した後、剥離層上に薄膜トランジスタ及び薄膜ト

ランジスタのゲート電極及び配線を絶縁化する無機絶縁物層を形成し、無機絶縁物層上に

薄膜トランジスタの配線に接続する第1の電極層を形成し、第1の電極層の端部を覆う有

機絶縁物層を形成し、有機絶縁物層の一部及び第1の電極層の露出部に有機化合物を含む

層を形成し、有機化合物を含む層及び無機絶縁物層に接する第2の電極層を形成して素子

形成層を形成し、第2の電極層上に第1の可撓性を有する基板を貼りあわせた後、基板及

び素子形成層を剥離層において分離することを特徴とする半導体装置の作製方法である。

【0024】

本発明の一は、基板上に剥離層を形成した後、剥離層上に半導体層を形成し、半導体層

上に無機絶縁物で形成されるゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成

し、ゲート電極上に第1の有機絶縁物層を形成し、第1の有機絶縁物層の一部を除去して

半導体層の一部及びゲート絶縁層の一部を露出し、第1の有機絶縁物層上に半導体層に接

続する配線を形成し、配線に接続する第1の電極層を形成し、第1の電極層の端部を覆う

第2の有機絶縁物層を形成し、第2の有機絶縁物層の一部及び第1の電極層の露出部に有

機化合物を含む層を形成し、有機化合物を含む層及びゲート絶縁層に接する第2の電極層

を形成して素子形成層を形成し、第2の電極層上に第1の可撓性を有する基板を貼りあわ

せた後、基板と素子形成層を剥離層において分離することを特徴とする半導体装置の作製

方法である。

【0025】

本発明の一は、基板上に剥離層を形成した後、剥離層上に絶縁層を形成し、絶縁層上に

半導体層を形成し、半導体層上に無機絶縁物で形成されるゲート絶縁層を形成し、ゲート

絶縁層上にゲート電極及び第1の導電層を形成し、ゲート電極及び第1の導電層上に有機

絶縁物層を形成し、有機絶縁物層を選択的に除去して半導体層の一部及び第1の導電層の

一部を露出し、有機絶縁物層上に半導体層に接続する配線を形成すると共に第1の導電層

に接続する第2の導電層を形成し、配線に接続する第1の電極層を形成すると共に第2の

導電層に接続する第3の導電層を形成し、第1の電極層及び第3の導電層の端部を覆う有

機絶縁物層を形成し、有機絶縁物層の一部及び第1の電極層の露出部に有機化合物を含む

層を形成し、有機化合物を含む層と第1乃至3の導電層のいずれか一つ以上とに接する第

2の電極層を形成して素子形成層を形成し、第2の電極層上に第1の可撓性を有する基板

を貼りあわせた後、基板及び素子形成層を剥離層において分離することを特徴とする半導

体装置の作製方法である。

【0026】

素子形成層と剥離層とを剥離した後、素子形成層に第2の可撓性を有する基板を貼りあ

わせてもよい。

【0027】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタに接続する第1の電極層と、第1の電極層の

端部を覆う無機絶縁物層と、第1の電極層上に形成される有機化合物を含む層と、有機化

合物を含む層及び無機絶縁物層に接する第2の電極層と、第2の電極層上に形成される第

2の可撓性を有する基板とを有することを特徴とする半導体装置である。

【0028】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタのゲート電極及び配線を絶縁化する無機絶縁

物層と、無機絶縁物層上に形成されると共に、薄膜トランジスタに接続する第1の電極層

と、第1の電極層の端部を覆う有機絶縁物層と、第1の電極層上に形成される有機化合物

を含む層と、有機化合物を含む層、有機絶縁物層、及び無機絶縁物層に接する第2の電極

層と、第2の電極層上に形成される第2の可撓性を有する基板とを有することを特徴とす

る半導体装置である。

【0029】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタのゲート電極及び半導体層を絶縁化する無機

絶縁物で形成されるゲート絶縁層と、ゲート絶縁層の一部に形成されると共に、薄膜トラ

ンジスタのゲート電極及び配線を絶縁化する第1の有機絶縁物層と、第1の有機絶縁物層

上に形成されると共に、薄膜トランジスタに接続する第1の電極層と、第1の電極層の端

部を覆うと共に第1の有機絶縁物層上に形成される第2の有機絶縁物層と、第1の電極層

上に形成される有機化合物を含む層と、有機化合物を含む層、第2の有機絶縁物層、及び

無機絶縁物層に接する第2の電極層と、第2の電極層上に形成される第2の可撓性を有す

る基板とを有することを特徴とする半導体装置である。

【0030】

本発明の一は、第1の可撓性を有する基板上に形成される絶縁層と、絶縁層上に形成さ

れる薄膜トランジスタと、薄膜トランジスタのゲート電極と同一の層で形成される第1の

導電層と、薄膜トランジスタのゲート電極を覆う第1の有機絶縁物層と、第1の有機絶縁

物層上に形成される配線と、配線と同一の層で形成されると共に、第1の導電層に接する

第2の導電層と、第1の有機絶縁物層上に形成されると共に、薄膜トランジスタの配線に

接続する第1の電極層と、第1の電極層と同一の層で形成されると共に第2の導電層に接

する第3の導電層と、第1の電極層の端部を覆う第2の有機絶縁物層と、第2の有機絶縁

物層上及び第1の電極層上に形成される有機化合物を含む層と、有機化合物を含む層及び

第3の導電層に接する第2の電極層と、第2の電極層上に形成される第2の可撓性を有す

る基板とを有することを特徴とする半導体装置である。

【0031】

第1の電極層、有機化合物を含む層、及び第2の電極層は、記憶素子、又は発光素子を

構成する一部である。

【発明の効果】

【0032】

本発明において、無機化合物層と導電層との密着性は、有機化合物を含む層と導電層と

の密着性と比較して高いため、剥離工程において無機化合物層と導電層との界面で剥れに

くい。このため、上面からみて密着性が低い領域、及びその外縁を囲むように密着性が高

い領域を形成することにより、導電層と有機化合物を含む層との界面における剥離を防止

することが可能である。また、基板上に形成された記憶素子または発光素子を有する層を

歩留まり高く剥離することが可能である。更には、可撓性を有する基板上に有機化合物を

含む層を有する素子を設けた半導体装置を歩留まり高く作製することが可能である。

【0033】

また、本発明の半導体装置は、無機化合物層及び導電層が有機化合物を含む層や有機絶

縁物層を挟むともに、無機化合物層と導電層が接する領域を多く有する。このため、有機

化合物を含む層や有機絶縁物層が外気に曝される領域が低減し、これらの領域に水分、酸

素等が侵入しにくくなり、半導体装置の劣化を低減することが可能である。

【0034】

また、可撓性を有する基板に有機化合物を含む層を有する素子が設けられた半導体装置を

得ることが可能であるため、軽量で薄型化が可能な半導体装置を得ることが可能である。

【図面の簡単な説明】

【0035】

【図1】本発明の半導体装置の作製工程を説明する断面図である。

【図2】本発明の半導体装置の作製工程を説明する断面図である。

【図3】本発明の半導体装置の作製工程を説明する断面図である。

【図4】本発明の半導体装置の作製工程を説明する断面図である。

【図5】本発明に適用可能な記憶素子の構造を説明する断面図である。

【図6】本発明に適用可能な発光素子の構造を説明する断面図である。

【図7】本発明に適用可能な記憶素子の構造を説明する断面図である。

【図8】本発明の半導体装置を説明する図である。

【図9】本発明の半導体装置を説明する上面図及び断面図である。

【図10】本発明の半導体装置の作製工程を説明する断面図である。

【図11】本発明の半導体装置の構造を説明する断面図である。

【図12】本発明の半導体装置の作製工程を説明する断面図である。

【図13】本発明の半導体装置の作製工程を説明する断面図である。

【図14】本発明の半導体装置を説明する図である。

【図15】本発明の半導体装置の作製工程を説明する断面図である。

【図16】本発明の半導体装置の作製工程を説明する断面図である。

【図17】本発明の半導体装置の等価回路を説明する図である。

【図18】本発明の半導体装置の構造を説明する上面図である。

【図19】本発明の半導体装置の構造を説明する展開図である。

【図20】本発明の半導体装置の使用形態について説明する図である。

【図21】本発明に適用可能な薄膜トランジスタの構造を説明する断面図である。

【図22】本発明の半導体装置を説明する上面図である。

【図23】従来の半導体装置を説明する断面図である。

【発明を実施するための形態】

【0036】

本発明の実施の形態について図面を参照して説明する。但し、本発明は以下の説明に限定

されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更

し得ることは当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形

態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成に

おいて、同じものを指す符号は異なる図面間で共通して用いる。

【0037】

(実施の形態1)

本実施の形態では、有機化合物を含む層を有する素子、及び当該素子を有する素子形成

層を歩留まり高く剥離する方法について図1を用いて説明する。

【0038】

図1(A)に示すように、基板101上に剥離層102を形成し、剥離層102上に絶

縁層103を形成する。次に、絶縁層103上に半導体素子を形成する。ここでは、半導

体素子として薄膜トランジスタ1111を形成する。薄膜トランジスタ1111の配線1

305に接続する第1の電極層104を形成し、第1の電極層104の端部を覆う無機絶

縁物層1115を形成する。第1の電極層104及び無機絶縁物層1115上に蒸着法に

より有機化合物を含む層105を形成する。図1(A)において、領域1116は、露出

された無機絶縁物層である。なお、有機化合物を含む層105は、無機絶縁物層1115

の一部を露出するようにメタルマスクを用いて形成する。又は、第1の電極層及び無機絶

縁物層1115の表面上に有機化合物を含む層105を形成した後、一部をエッチングし

て、無機絶縁物層1115の一部を露出させる。

【0039】

基板101としては、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶

縁層を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用

いる。上記に挙げた基板101には、大きさや形状に制約がないため、例えば、基板10

1として、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向

上させることができる。この利点は、円形のシリコン基板を用いる場合と比較すると、大

きな優位点である。

【0040】

剥離層102は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、タン

グステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(N

b)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ル

テニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリ

ジウム(Ir)、及び珪素(Si)の中から選択された元素、又は元素を主成分とする合

金材料、又は前記元素を主成分とする化合物材料からなる層を、単層又は複数の層を積層

させて形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれでもよい

。なお、ここでは、塗布法は、溶液を被処理物上に吐出させて成膜する方法であり、例え

ばスピンコーティング法や液滴吐出法を含む。また、液滴吐出法とは微粒子を含む組成物

の液滴を微細な孔から吐出して所定の形状のパターンを形成する方法である。

【0041】

剥離層102が単層構造の場合、好ましくは、タングステン、モリブデン、又はタングス

テンとモリブデンの混合物を含む層を形成する。又は、タングステンの酸化物若しくは酸

化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層、又はタングステン

とモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。

【0042】

剥離層102が積層構造の場合、好ましくは、1層目としてタングステン、モリブデン、

又はタングステンとモリブデンの混合物を含む層を形成し、2層目として、タングステン

、モリブデン、又はタングステンとモリブデンの混合物の酸化物、タングステン、モリブ

デン、又はタングステンとモリブデンの混合物の窒化物、タングステン、モリブデン、又

はタングステンとモリブデンの混合物の酸化窒化物、又はタングステン、モリブデン、又

はタングステンとモリブデンの混合物の窒化酸化物を形成する。

【0043】

剥離層102として、タングステンを含む層とタングステンの酸化物を含む層の積層構造

を形成する場合、タングステンを含む層を形成し、その上層に酸化物で形成される絶縁層

を形成することで、タングステンを含む層と絶縁層との界面に、タングステンの酸化物を

含む層が形成されることを活用してもよい。さらには、タングステンを含む層の表面を、

熱酸化処理、酸素プラズマ処理、オゾン水等の酸化力の強い溶液での処理等を行ってタン

グステンの酸化物を含む層を形成してもよい。これは、タングステンの窒化物、酸化窒化

物及び窒化酸化物を含む層を形成する場合も同様であり、タングステンを含む層を形成後

、その上層に窒化珪素層、酸化窒化珪素層、及び/又は窒化酸化珪素層を形成するとよい

。

【0044】

タングステンの酸化物は、WOxで表される。xは2以上3以下の範囲内にあり、xが2

の場合(WO2)、xが2.5の場合(W2O5)、xが2.75の場合(W4O11)

、xが3の場合(WO3)などがある。

【0045】

また、上記の工程によると、基板101に接するように剥離層102を形成しているが、

本発明はこの工程に制約されない。基板101に接するように下地となる絶縁層を形成し

、その絶縁層に接するように剥離層102を設けてもよい。

【0046】

絶縁層103は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、無機

化合物を用いて単層又は多層で形成する。無機化合物の代表例としては、珪素酸化物又は

珪素窒化物が挙げられる。珪素酸化物の代表例としては、酸化珪素、酸化窒化珪素、窒化

酸化珪素等が該当する。珪素窒化物の代表例としては、窒化珪素、酸化窒化珪素、窒化酸

化珪素等が該当する。

【0047】

さらには、絶縁層103を積層構造としても良い。例えば、無機化合物を用いて積層して

もよく、代表的には、酸化珪素、窒化酸化珪素、及び酸化窒化珪素を積層して形成しても

良い。

【0048】

薄膜トランジスタ1111の一態様について、図21を参照して説明する。図21(A)

はトップゲート型の薄膜トランジスタの一例を示している。基板101上に剥離層102

及び絶縁層103が設けられ、絶縁層103上に薄膜トランジスタ1111が設けられて

いる。薄膜トランジスタ1111は、絶縁層103上に半導体層1302、無機絶縁物で

形成されるゲート絶縁層1113が設けられている。ゲート絶縁層1113の上には、半

導体層1302に対応してゲート電極1304が形成され、その上層に保護層として機能

する絶縁層(図示しない)、層間絶縁層として機能する無機絶縁物層1114が設けられ

ている。また、半導体層のソース領域及びドレイン領域1310それぞれに接続する配線

1305が形成される。さらにその上層に、保護層として機能する絶縁層を形成しても良

い。

【0049】

半導体層1302は、結晶構造を有する半導体で形成される層であり、非単結晶半導体

若しくは単結晶半導体を用いることができる。特に、加熱処理により結晶化させた結晶性

半導体、加熱処理とレーザ光の照射を組み合わせて結晶化させた結晶性半導体を適用する

ことが好ましい。加熱処理においては、シリコン半導体の結晶化を助長する作用のあるニ

ッケルなどの金属元素を用いた結晶化法を適用することができる。また、シリコン半導体

の結晶化工程における加熱により、剥離層102及び絶縁層103の界面において、剥離

層の表面を酸化して金属酸化物を形成することが可能である。金属酸化物を形成すること

で、後の剥離工程において、剥離層102及び絶縁層103の間において容易に剥離する

ことが可能である。

【0050】

加熱処理に加えてレーザ光を照射して結晶化する場合には、連続発振レーザ光の照射若

しくは繰り返し周波数が10MHz以上であって、パルス幅が1ナノ秒以下、好ましくは

1乃至100ピコ秒である高繰返周波数超短パルス光を照射することによって、結晶性半

導体が溶融した溶融帯を、当該レーザ光の照射方向に連続的に移動させながら結晶化を行

うことができる。このような結晶化法により、大粒径であって、結晶粒界が一方向に延び

る結晶性半導体を得ることができる。キャリアのドリフト方向を、この結晶粒界が延びる

方向に合わせることで、トランジスタにおける電界効果移動度を高めることができる。例

えば、400cm2/V・sec以上を実現することができる。

【0051】

上記結晶化工程として、ガラス基板の耐熱温度(約600℃)以下の結晶化プロセスを用

いる場合、大面積ガラス基板を用いることが可能である。このため、基板あたり大量の半

導体装置を作製することが可能であり、低コスト化が可能である。

【0052】

また、ガラス基板の耐熱温度以上の加熱により、結晶化工程を行い、半導体層1302を

形成してもよい。代表的には、絶縁表面を有する基板101に石英基板を用い、非晶質若

しくは微結晶質の半導体を700度以上で加熱して半導体層1302を形成する。この結

果、結晶性の高い半導体を形成することが可能である。このため、応答速度や移動度など

の特性が良好で、高速な動作が可能な薄膜トランジスタを提供することができる。

【0053】

ゲート電極1304は金属又は一導電型の不純物を添加した多結晶半導体で形成するこ

とができる。金属を用いる場合は、タングステン(W)、モリブデン(Mo)、チタン(

Ti)、タンタル(Ta)、アルミニウム(Al)などを用いることができる。また、金

属を窒化させた金属窒化物を用いることができる。或いは、当該金属窒化物からなる第1

層と当該金属から成る第2層とを積層させた構造としても良い。積層構造とする場合には

、第1層の端部が第2層の端部より外側に突き出した形状としても良い。このとき第1層

を金属窒化物とすることで、バリアメタルとすることができる。すなわち、第2層の金属

が、ゲート絶縁層1113やその下層の半導体層1302に拡散することを防ぐことがで

きる。

【0054】

半導体層1302、ゲート絶縁層1113、ゲート電極1304などを組み合わせて構

成される薄膜トランジスタは、シングルドレイン構造、LDD(低濃度ドレイン)構造、

ゲートオーバーラップドレイン構造など各種構造を適用することができる。ここでは、シ

ングルドレイン構造の薄膜トランジスタを示す。さらには、等価的には同電位のゲート電

圧が印加されるトランジスタが直列に接続された形となるマルチゲート構造、半導体層の

上下をゲート電極で挟むデュアルゲート構造を適用することができる。

【0055】

本実施の形態においては、無機絶縁物層1114を、酸化シリコン及び酸化窒化シリコ

ンなどの無機絶縁物で形成する。

【0056】

無機絶縁物層1114の上に形成される配線1305は、ゲート電極1304と同じ層

で形成される配線と交差して設けることが可能であり、多層配線構造を形成している。無

機絶縁物層1114と同様な機能を有する絶縁層を複数積層して、その層上に配線を形成

することで多層配線構造を形成することができる。配線1305はチタン(Ti)とアル

ミニウム(Al)の積層構造、モリブデン(Mo)とアルミニウム(Al)との積層構造

など、アルミニウム(Al)のような低抵抗材料と、チタン(Ti)やモリブデン(Mo

)などの高融点金属材料を用いたバリアメタルとの組み合わせで形成することが好ましい

。

【0057】

図21(B)は、ボトムゲート型の薄膜トランジスタの一例を示している。基板101

上に剥離層102及び絶縁層103が形成され、その上に薄膜トランジスタ1111が設

けられている。薄膜トランジスタ1111には、ゲート電極1304、ゲート絶縁層11

13、半導体層1302、層間絶縁層として機能する無機絶縁物層1114が設けられて

いる。さらにその上層には、保護層として機能する絶縁層を形成しても良い。半導体層1

302のソース領域及びドレイン領域に接する配線1305は、無機絶縁物層1114の

上に形成することができる。

【0058】

さらには、薄膜トランジスタ1111の代わりにスイッチング素子として機能し得る半導

体素子であれば、どのような構成で設けてもよい。スイッチング素子の代表例としては、

MIM(Metal−Insulator−Metal)、ダイオード等が挙げられる。

【0059】

図1(A)において、第1の電極層104は、スパッタリング法やプラズマCVD法、塗

布法、印刷法、電解メッキ法、無電解メッキ法等を用い、導電性の高い金属、合金、化合

物等からなる単層または多層構造を用いて形成することができる。代表的には、仕事関数

の大きい(具体的には4.0eV以上)金属、合金、導電性化合物、およびこれらの混合

物や、仕事関数の小さい(具体的には3.8eV以下)金属、合金、導電性化合物、およ

びこれらの混合物などを用いることが可能である。

【0060】

仕事関数の大きい(具体的には4.0eV以上)金属、合金、導電性化合物の代表例とし

ては、インジウム錫酸化物(以下、ITOと示す)、または珪素を含有したインジウム錫

酸化物、2〜20atomic%の酸化亜鉛(ZnO)を含む酸化インジウム等が挙げら

れる。また、チタン(Ti)、金(Au)、白金(Pt)、ニッケル(Ni)、タングス

テン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅

(Cu)、パラジウム(Pd)、または金属材料の窒化物(例えば、窒化チタン:TiN

、窒化タングステン(WN)、窒化モリブデン(MoN))等を用いることも可能である

。

【0061】

仕事関数の小さい(具体的には3.8eV以下)金属、合金、導電性化合物の代表例とし

ては、元素周期表の1族または2族に属する金属、即ちリチウム(Li)やセシウム(C

s)等のアルカリ金属、およびマグネシウム(Mg)、カルシウム(Ca)、ストロンチ

ウム(Sr)等のアルカリ土類金属、アルミニウム(Al)およびこれらのいずれかを含

む合金(MgAg、AlLi)、ユーロピウム(Er)、イッテルビウム(Yb)等の希

土類金属およびこれらを含む合金等が挙げられる。

【0062】

なお、第1の電極層104又は第2の電極層106に、有機化合物を含む層に対して正孔

を注入する電極、すなわち陽極を用いる場合には、仕事関数の大きな材料を用いるのが好

ましい。逆に有機化合物を含む層に対して電子を注入する電極、すなわち陰極を用いる場

合には、仕事関数の小さい材料を用いることが好ましい。

【0063】

無機絶縁物層1115を、酸化珪素、窒化珪素、酸化窒化珪素、窒化アルミニウム等の無

機絶縁物を用い、CVD法、スパッタリング法等の薄膜形成方法を用いて形成する。ここ

では、薄膜形成方法を用いて絶縁膜を形成した後、第1の電極層104の一部が露出する

ように絶縁膜を選択的にエッチングして無機絶縁物層1115を形成する。

【0064】

有機化合物を含む層105は、蒸着法、電子ビーム蒸着法、塗布法等を用いて形成する

ことができる。上記作製方法を用いて有機化合物を含む層を形成する場合、無機絶縁物層

1115の一部を露出する領域1116を形成しながら有機化合物を含む層105を形成

する。また、無機絶縁物層1115及び第1の電極層104表面上に有機化合物を含む層

を形成した後、選択的にエッチングして無機絶縁物層1115が露出する領域1116を

形成してもよい。

【0065】

ここでは、50〜200nmのチタン膜をスパッタリング法により成膜した後、フォトリ

ソグラフィー法により所望の形状にエッチングして第1の電極層104を形成する。次に

、蒸着法によりNPBで形成される有機化合物を含む層を形成する。

【0066】

次に、図1(B)に示すように、無機絶縁物層1115及び有機化合物を含む層105上

に第2の電極層106を形成する。この結果、無機絶縁物層1115に第2の電極層10

6が接する領域1117を形成することができる。また、第1の電極層104、有機化合

物を含む層105、及び第2の電極層106により、有機化合物を含む層を有する素子1

51を形成することができる。第2の電極層106は、蒸着法、スパッタ法、CVD法、

印刷法、塗布法等を用いて形成することができる。第2の電極層106は、第1の電極層

104と同様の材料を用いて形成する。なお、第1の電極層104に仕事関数の大きな材

料を用いる場合、第2の電極層106は仕事関数の小さい材料を用いることが好ましい。

また、第1の電極層104に仕事関数の小さい材料を用いる場合、第2の電極層106は

仕事関数の大きな材料を用いることが好ましい。

【0067】

ここでは、蒸着法によりアルミニウムを蒸着して第2の電極層106を形成する。

【0068】

なお、ここでは、絶縁層103から第2の電極層106までを含む積層物を素子形成層1

118という。

【0069】

ここで、有機化合物を含む層を有する素子151のより具体的な構造について図5を用い

て以下に示す。なお、図5(A)の205は図1の105に対応し、図5(B)の205

と201の積層は図1の105に対応し、図5(C)の205と202の積層は図1の1

05に対応し、図5(D)の205と203の積層は105に対応し、図5(E)の20

5と245と244の積層は図1の105に対応する。

【0070】

図5(A)に示すように、第1の電極層及び第2の電極層に印加された電圧により、結晶

状態や導電性、形状が変化する有機化合物で有機化合物を含む層205を形成することで

、有機化合物を含む層を有する素子151は記憶素子として機能する。なお、有機化合物

を含む層205は、単層で設けてもよいし、異なる有機化合物で形成された層複数を積層

させて設けてもよい。

【0071】

有機化合物を含む層205の厚さは、第1の導電層及び第2の導電層への電圧印加により

記憶素子の電気抵抗が変化する厚さが好ましい。有機化合物を含む層205の代表的な膜

厚は、5nmから100nm、好ましくは10nmから60nm、更に好ましくは5〜3

0nmである。

【0072】

有機化合物を含む層205は、正孔輸送性を有する有機化合物又は電子輸送性を有する有

機化合物を用いて形成することができる。

【0073】

正孔輸送性の有機化合物としては、例えば、フタロシアニン(略称:H2Pc)、銅フタ

ロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)の他、4,

4’,4’’−トリス(N,N−ジフェニルアミノ)トリフェニルアミン(略称:TDA

TA)、4,4’,4’’−トリス[N−(3−メチルフェニル)−N−フェニルアミノ

]トリフェニルアミン(略称:MTDATA)、1,3,5−トリス[N,N−ジ(m−