表示装置及び電子機器

【課題】駆動回路等を制御するための駆動制御信号の信号線を基板の所定部位に配設することで、基板面の有効利用と、駆動制御信号への外的影響を防止ないし抑制することが可能な表示装置、及びそれを備えた電子機器を提供する。

【解決手段】基板20上に、バンク層221と該バンク層221により区画形成された凹状区画領域223とを所定のマトリクスパターンで配列するとともに、表示部たる画素部110に、表示に寄与する実画素部111と、表示に寄与しないダミー画素部112とを構成する。さらに基板20上には、走査線を導通する走査信号の出力制御を行う走査線駆動回路80と、該走査線駆動回路80を駆動させるための駆動制御信号が導通する駆動制御信号導通部320とが設けられ、基板20を平面視した場合に、駆動制御信号導通部320が、少なくともダミー画素部112のバンク層221と重畳配置する部分を含むように配置されている。

【解決手段】基板20上に、バンク層221と該バンク層221により区画形成された凹状区画領域223とを所定のマトリクスパターンで配列するとともに、表示部たる画素部110に、表示に寄与する実画素部111と、表示に寄与しないダミー画素部112とを構成する。さらに基板20上には、走査線を導通する走査信号の出力制御を行う走査線駆動回路80と、該走査線駆動回路80を駆動させるための駆動制御信号が導通する駆動制御信号導通部320とが設けられ、基板20を平面視した場合に、駆動制御信号導通部320が、少なくともダミー画素部112のバンク層221と重畳配置する部分を含むように配置されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及び電子機器に関するものである。

【背景技術】

【0002】

従来、液晶表示装置、EL表示装置等の光学表示装置においては、基板上に複数の回路素子、電極、液晶又はEL素子等が積層された構成を具備しているものがある。例えばEL表示装置においては、発光物質を含む発光層を陽極及び陰極の電極層で挟んだ構成を具備しており、陽極側から注入された正孔と、陰極側から注入された電子とを発光能を有する発光層内で再結合し、励起状態から失括する際に発光する現象を利用している。

【0003】

このようなEL表示装置の駆動方式としては、行方向に走査線及び列方向にデータ線をマトリクス状に配設するとともに、その交差部分にあるEL素子の画素毎に静電容量素子とトランジスタ等を配置して、書き込み走査時に各画素の静電容量素子に充電した電圧に従って、次に書き換えられるまで発光を持続する、いわゆるアクティブマトリクス駆動方式が知られている(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開第98/3640号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記のようなアクティブマトリクス駆動方式の表示装置において、駆動回路として、各走査線毎に走査選択パルスを印加する走査線用の駆動回路、各データ線毎にデータ信号を供給するデータ線用の駆動回路、及びその制御を行うコントロール回路を有するものがある。このような表示装置においては、駆動回路及び/又はコントロール回路を基板上に配設しなければならず基板が大型化するか、これら回路が配設された領域は表示領域として使用し難く、基板上を表示領域として有効に利用できない等の問題が生じる場合がある。また、所定の電源部から上記駆動回路及び/又はコントロール回路への導電線も基板上に配設しなければならない他、コントロール回路から駆動回路への駆動制御信号線も基板上に配設しなければならないため、さらに表示領域が有効に利用できないものとなる場合がある。

【0006】

一方、上記駆動制御信号は、当該表示装置の作動を司る信号であって、該信号へのノイズ混入、又は信号波形を変化させ得る外的影響は極力回避しなけらばならない。

【0007】

本発明の課題は、駆動回路等を制御するための駆動制御信号の信号線を基板の所定部位に配設することで、基板面を有効に利用するとともに、駆動制御信号への外的影響を防止ないし抑制することが可能な表示装置、及びそれを備えた電子機器を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明の表示装置は、基板上に、表示に寄与する表示領域と、表示に寄与しない非表示領域とを含むとともに、該表示領域及び非表示領域には、隔壁部と該隔壁部により区画形成された凹状区画領域とが所定のマトリクスパターンで配列され、前記表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも第1電極層と、表示若しくは非表示を切り換え可能な物質を含む表示主体層と、第2電極層とを含み、前記非表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも前記表示主体層と、第2電極層とを含み、さらに前記基板上には、前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、そのスイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動制御信号が導通する駆動制御信号導通部とが設けられ、前記駆動制御信号導通部が、少なくとも前記非表示領域に配置された部分を含み、さらに前記基板を平面視した場合に、前記隔壁部と重畳する部分を含むように配置されていることを特徴とする。

【0009】

このような表示装置においては、隔壁部により区画形成された凹状区画領域がマトリクスパターンで配列して画素を形成することとなるが、例えばこのようなマトリクスパターンで画素を配列する場合には、該画素の全てを表示に寄与する表示領域(実画素)とせず、その一部を表示に寄与しない非表示領域(ダミー画素)として形成することがある。これは、製造上の問題で、例えば上記表示本体層を各凹状区画領域に層形成する際、特に基板上の周縁部の凹状区画領域において該表示本体層の層厚を均一に形成することが困難な場合があり、そのような場合においては、上記層厚が不均一となり得る凹状区画領域を含む領域を非表示領域として形成することで、表示本体層の層厚不均一による表示上の不具合を解消している。そのような不具合としては、例えばコントラストの低下、表示むら、画素寿命の低下等が挙げられる。

ところで、上記非表示領域は通常の表示機能を果たしてはいない。

そこで、本発明者は、該非表示領域を積極的に有効利用するために、上記スイッチング手段の作動制御を行う作動制御手段への駆動制御信号の導通部を少なくとも非表示領域に形成した。したがって、非表示領域と同様、実質的に表示機能を担わない駆動制御信号導通部が該非表示領域に配置されるため、基板上における表示機能を担わない部分の面積が相殺されるものとなり、基板上の表示不能な領域の増大を低減させることが可能となる。

さらに駆動制御信号導通部を基板厚さ方向において隔壁部の下側に位置するように、すなわち表示方向において隔壁部と駆動制御信号導通部とが重畳配置する構成とした。この場合、基板を平面視した場合に、駆動制御信号導通部が隔壁部と重畳配置する部分を含むように配置され、非表示領域の第2電極層と駆動制御信号導通部との間の距離が比較的大きなものとなる。すなわち、第2電極層と駆動制御信号導通部との間の距離が、凹状区画領域よりも相対的に大きな隔壁部の下方に駆動制御信号導通部を設けることで、該第2電極層と駆動制御信号導通部との間のキャパシタンスが、凹状区画部の下方に設けるよりも小さくなり、該キャパシタンスによる駆動制御信号への外的影響が低減される。ここで、凹状区画領域は駆動制御信号導通部側(基板側)に凹んだ底部を具備しており、その底部に第2電極層を含んでいるため、隔壁部と比して静電容量が大きくなる傾向にあり、逆に隔壁部は駆動制御信号導通部側(基板側)から突出した凸部を具備しており、その凸部の頂側に第2電極層を含んでいるため凹状区画領域と比して静電容量が小さくなる傾向にある。

したがって、このような本発明の表示装置は、通常の表示を行わない領域を低減し基板を表示領域として有効に利用できるとともに、駆動制御信号への外的影響、例えばパルス波形変化等に基づく当該表示装置の誤作動発生を防止ないし抑制することが可能となる。なお、上記表示装置において、表示本体層には表示物質として例えば有機EL物質を用いることができ、その他にも、表示物質として液晶物質を用いることもできる。

【0010】

また、前記作動制御手段を駆動させるための駆動電圧が印加する駆動電圧導通部が基板上に設けられ、該駆動電圧導通部及び前記駆動制御信号導通部と前記第2電極層との間には絶縁層が形成され、前記駆動制御信号導通部は前記駆動電圧導通部と比して前記第2電極側に遠い絶縁層領域に形成されているものとすることができる。この場合、駆動電圧導通部に対しては上述したキャパシタにより電流値低下が補償されるとともに、駆動制御信号導通部に対しては相対的に上記キャパシタが形成し難くなり、制御信号に対する外的悪影響が生じ難くなる。また、前記非表示領域は、前記基板と前記表示本体層との間に位置する第1電極層を備え、さらに該第1電極層と前記第2電極層との間の導通を遮る絶縁層を備えるものとすることができる。この場合、絶縁層により各電極間の通電が不可能、若しくは表示領域よりも相対的に通電困難となり、非表示領域が形成されるものとされている。なお、製造時において例えば各電極層、表示本体層、絶縁層等をフォトリソグラフィにて形成する場合、該絶縁層を凹状区画領域の全域に形成するか、若しくは絶縁層の一部を開口させて絶縁空乏層を形成するかにより、表示領域、若しくは非表示領域のいずれかを簡便に形成することが可能となる。

【0011】

さらに、該絶縁層の表層面が、前記隔壁部の表層面と比して相対的に前記表示本体層との親和性が高い材質にて構成されているものとすることができる。この場合、表示本体層の層厚が隔壁部近傍で大きくなる等の不具合が生じにくく、該層厚を一層均一にすることが可能となり、ひいては表示むら等の不具合が生じにくくなる。

【0012】

次に、前記基板上には、複数の走査線及び複数のデータ線がマトリクス状に形成されるとともに、前記スイッチング手段が該走査線とデータ線に接続され、前記作動制御手段が前記データ線を導通する信号に関する制御を行うデータ制御手段を含むことができる。一方、前記スイッチング手段が前記走査線とデータ線に接続され、前記作動制御手段が前記走査線を導通する信号に関する制御を行う走査制御手段を含むものとすることも可能で、勿論、作動制御手段がデータ制御手段及び走査制御手段のそれぞれを含むものとすることも可能である。

さらに、前記基板上には、複数の検査線が形成されるとともに、前記スイッチング手段が該検査線に接続され、前記作動制御手段が前記検査線を導通する信号に関する制御を行う検査制御手段を含むものとすることも可能で、勿論、作動制御手段がデータ制御手段及び走査制御手段、検査制御手段のそれぞれを含むものとすることも可能である。この場合、作動制御手段により走査線及び/又はデータ線及び/又は検査線を導通する信号に関する制御を確実に行うことが可能となり、さらにこれら走査線及び/又はデータ線及び/又は検査線、スイッチング手段等を基板上に配設するため、基板面積の有効利用が望まれるが、本発明のような作動制御手段への駆動制御信号導通部の構成を採用することにより該有効利用と、駆動制御信号の安定した送信が可能となり得る。

【0013】

ところで、表示物質として有機EL物質又は液晶物質等を用いる場合、例えば該表示物質を構成する発光物質又は液晶物質等を各画素(凹状区画領域)に対してインクジェット法にて表示本体層を形成することが可能である。該インクジェット法では上述した表示本体層の層厚の不均一化を抑制するために、非表示領域を所定領域、例えば基板面の周縁部において形成する場合がある。したがって、このようなインクジェット法を用いて表示本体を形成した場合、本発明の構成を採用することで、基板面における非表示領域の有効利用が可能となる。

【0014】

なお、本発明の電子機器は、上記表示装置を表示部として備えたことを特徴とする。このような電子機器としては、例えば携帯電話、時計や、ワープロ、パソコン等の情報処理装置等を例示することができる。これら電子機器は小型のものが多いが、本発明の表示装置を採用することで表示領域の有効利用が可能となり、機器全体が小型であるにも拘らず比較的大きな表示領域を確保することが可能となる。

【図面の簡単な説明】

【0015】

【図1】本発明の表示装置の一実施形態たるEL表示装置の平面模式図。

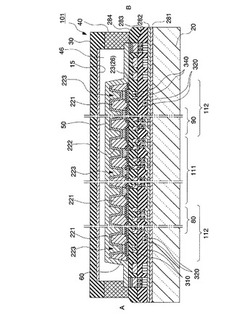

【図2】図1のA−B断面模式図。

【図3】図2の要部を拡大した断面模式図。

【図4】図1のC−D断面模式図。

【図5】図1のEL表示装置の製造プロセスの一例を示す説明図。

【図6】図5に続くEL表示装置の製造プロセスの一例を示す説明図。

【図7】図6に続くEL表示装置の製造プロセスの一例を示す説明図。

【図8】図7に続くEL表示装置の製造プロセスの一例を示す説明図。

【図9】本発明の電子機器の一実施形態を示す模式図。

【発明を実施するための形態】

【0016】

以下、図面を参照して、本発明の実施形態について説明する。かかる実施の形態は、本発明の一態様を示すものであり、この発明を限定するものではなく、本発明の技術的思想の範囲内で任意に変更可能である。なお、以下に示す各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材ごとに縮尺を異ならせてある。

【0017】

まず、表示主体層を構成する電気光学物質の一例としてエレクトロルミネッセンス(以下ELと記す)を用いたEL表示装置に本発明の構成を適用した実施形態について説明する。図1及び図2は、本実施形態に係るEL表示装置の構成を模式的に示す平面図及びA−B断面図である。同図に示すEL表示装置101は、スイッチング素子として薄膜トランジスタ(TFT:Thin Film Transistor)を用いたアクティブマトリクス方式のEL表示装置である。

【0018】

EL表示装置101は、各画素にデータ信号を書き込むか否かを制御するスイッチング手段としてのTFT(図3に示すTFT24であって、画素用TFTとも言う)に加え、走査線駆動回路80及び検査回路90を構成するスイッチング手段の駆動手段たるTFT(駆動回路用TFTとも言う)を基板20上に形成している。また、当該表示装置101の画素部110は、パネル表示に寄与する実画素領域111と、画素部110から実画素領域111を除いた領域に形成され、通常の表示に寄与しないダミー領域112とを備えている。

【0019】

EL表示装置101は、図2に示すように、相互に対向するアクティブマトリクス基板20と、封止基板(対向基板)30とが封止樹脂40を介して貼り合わされるとともに、両基板20,30と封止樹脂40とに囲まれた領域に、乾燥剤45が挿入された構成となっており、さらに両基板20,30間に形成された空間には窒素ガスなどの不活性ガスが充填されたガス充填層46を形成している。また、アクティブマトリクス基板20上には陽極(画素電極)23と、該陽極(画素電極)23から正孔を注入/輸送可能な正孔/注入輸送層70(図3参照)と、電気光学物質の一つである有機EL物質(以下、発光層、または有機EL層ともいう)60とを介して陰極222が例えば蒸着等により形成されている。アクティブマトリクス基板20及び封止基板(対向基板)30は、ガラスや石英、プラスチックといった光透過性を有する絶縁性の板状部材が用いられる。

【0020】

ここで、画素用TFT24(図3参照)を駆動するための走査線駆動回路80は、アクティブマトリクス基板20上に設けられている。一方、データ線駆動回路100はデータドライバICとして外付けで設けられている。もちろん、同一アクティブマトリクス基板20にデータ線駆動回路100を設けることも可能である。

また、検査回路90は、当該表示装置101の作動状況あるいは初期不良等を検査するための回路であって、例えば該検査結果を外部に出力するための検査情報出力手段を備えている。

【0021】

上記走査線駆動回路80及びデータ線駆動回路100は、走査線及びデータ線に導通する信号の出力制御を行う走査制御手段及びデータ制御手段として構成され、これら走査線及びデータ線が上記画素用TFT24(図3参照)に接続されている。すなわち、走査線駆動回路80及びデータ線駆動回路100からの作動指令信号に基づいて画素用TFT24(図3参照)が作動し、該画素用TFT24が画素電極23への通電制御を行っている。

【0022】

走査線駆動回路80及びデータ線駆動回路100の駆動電流または駆動電圧は、所定の電源部から駆動電圧導通部310(図2参照)及び駆動電圧導通部340(図4参照)を介して供給されている。また、これら走査線駆動回路80及びデータ線駆動回路100への駆動制御信号は、当該表示装置101の作動制御を司る所定のメインドライバ等から駆動制御信号導通部320(図2参照)及び駆動制御信号導通部350(図4参照)を介して送信されるようになっている。なお、この場合の駆動制御信号とは、例えば、上記走査線あるいはデータ線への信号出力のタイミングを制御する信号、走査線駆動回路80及びデータ線駆動回路100の制御に関連するクロック信号、イネーブル信号等の種々の制御信号等の指令信号のことを言う。

【0023】

次に、図3は表示領域内において実画素部111に対応して設けられたTFT(画素用TFT)24の近傍の構成を示す断面図である。同図に示すように、アクティブマトリクス基板20の表面には、酸化シリコンを主体とする下地保護層281を下地として、その上層にはシリコン層241が形成されている。このシリコン層241の表面は、酸化シリコン及び/又は窒化シリコンを主体とするゲート絶縁層282によって覆われている。そして、このシリコン層241のうち、ゲート絶縁層282を挟んでゲート電極242と重なる領域がチャネル領域241aとされている。なお、このゲート電極242は走査線の一部である。一方、シリコン層241を覆い、ゲート電極242が形成されたゲート絶縁層282の表面は、酸化シリコンを主体とする第1層間絶縁層283によって覆われている。なお、本明細書において、「主体」とする成分とは最も含有率の高い成分のことを言うものとする。

【0024】

また、シリコン層241のうち、チャネル領域241aのソース側には低濃度ソース領域241b及び高濃度ソース領域241Sが設けられる一方、チャネル領域241aのドレイン側には低濃度ドレイン領域241c及び高濃度ドレイン領域241Dが設けられて、いわゆるLDD(Light Doped Drain)構造となっている。このうち、高濃度ソース領域241Sは、ゲート絶縁層282と第1層間絶縁層283とに亙って開孔するコンタクトホールを介して、ソース電極243に接続されている。このソース電極243は、上述したデータ線(図3における紙面垂直方向に延在する)の一部として構成される。一方、高濃度ドレイン領域241Dは、ゲート絶縁層282と第1層間絶縁層283とに亙って開孔するコンタクトホールを介して、ソース電極243と同一層からなるドレイン電極244に接続されている。

【0025】

ソース電極243及びドレイン電極244が形成された第1層間絶縁層283の上層は、例えばアクリル系の樹脂成分を主体とする第2層間絶縁層284によって覆われている。また、アクリル系の絶縁膜以外にも、窒化シリコン、酸化シリコンからなる絶縁膜を形成することができる。

そして、ITOからなる画素電極23が、この第2層間絶縁層284の面上に形成されるとともに、当該第2層間絶縁層284に設けられたコンタクトホール23aを介してドレイン電極244に接続されている。すなわち、画素電極23は、ドレイン電極244を介して、シリコン層241の高濃度ドレイン電極241Dに接続されている。

【0026】

なお、走査線駆動回路80及び検査回路90に含まれるTFT(駆動回路用TFT)、すなわち、例えばこれらの駆動回路のうち、シフトレジスタに含まれるインバータを構成するNチャネル型又はPチャネル型のTFTは、画素電極23と接続されていない点を除いて上記TFT24と同様の構造となっている。

【0027】

画素電極23が形成された第2層間絶縁層284の表面は、例えば酸化シリコンを主体とする親水性制御層25と、アクリルやポリイミド等からなる有機バンク層221によって覆われている。そして、画素電極23には親水性制御層25に設けられた開口部25a、及び有機バンク221に設けられた開口部221a内側に、正孔注入/輸送層70と、有機EL層60とが画素電極23側からこの順で積層されている。

【0028】

正孔注入/輸送層70と、有機EL層60との上層は、例えばCa222、Alを積層して形成した陰極50によって覆われている。EL表示装置101は、基本的に以上の構成により作成されるが、図2では、封止基板30を用いて乾燥剤45を使用することにより高寿命化を図った構成となっている。

【0029】

図2に戻り、本実施例の表示装置101においては、上記走査線側駆動電圧導通部310がダミー領域112に形成され、特に有機バンク層221により区画形成された凹状区画領域223の下方に形成されている。すなわち、走査線側駆動電圧導通部310が、有機バンク層221を回避して配置され、当該表示装置101若しくは基板20を平面視した場合に、ダミー領域112の凹状区画領域223と重なる位置に少なくとも形成されている。

【0030】

これはダミー領域112が表示に寄与しない非表示領域であって、駆動電圧導通部310とを重ねて配置した構造である。すなわち、図2に示すように、表示可能方向においてこれらを重畳配置したものである。これにより、非表示画素部の有効利用が図られている。凹状区画領域223に上部から順に陰極50、222、親水性制御層25、絶縁層284、電源配線(駆動電圧導通部)310と形成することで、これらを隔壁部に形成するよりも電源配線と陰極との間の距離を小さく出来る。その為、電源配線と陰極との間の静電容量をより多く確保することができることにより、電源配線部における電圧値が低下した場合でも、上記静電容量により電源低下が補償されるものとなり、例えば駆動電圧低下による表示装置の誤作動等の不具合発生を防止ないし抑制することが可能となっている。

【0031】

また、走査線側駆動制御信号導通部(回路用制御信号線)320については、ダミー画素部112に形成され、特に有機バンク層221の下方に形成されている。すなわち、走査線側駆動制御信号導通部320が、有機バンク層221に対応して配置され、当該表示装置101若しくは基板20を平面視した場合に、ダミー画素部112の有機バンク層221と重なる位置に少なくとも形成されている。

【0032】

これはダミー領域112が表示に寄与しない非表示画素部であって、該非表示画素部と、駆動制御信号導通部320とを、表示可能方向において重畳配置したものである。これにより、非表示画素部の有効利用が図られている。また、駆動制御信号導通部320を有機バンク層221の下方に重畳配置して形成することで、上記凹状区画領域223と重畳配置して形成したときと比して、該駆動制御信号導通部320と陰極222との間の距離が相対的に大きくなり、上述のような高い静電容量を具備したキャパシタが形成され難く、駆動制御信号導通部320を導通する信号に対する影響を低減することが可能となる。すなわち、駆動制御信号導通部320を導通するパルス信号は、上記のようなキャパシタの形成によりパルス波形が鈍ってしまう等の不具合が生じる場合があるが、本実施例のように、高い静電容量を具備し難い位置に駆動制御信号導通部50を配置することで、該不具合発生を防止ないし抑制することができる。

【0033】

一方、図4は図1の平面図に示したC−D断面図である。この場合も、検査回路90を駆動させるための検査回路側駆動電圧導通部340が、ダミー領域112内であって、更に有機バンク層221により区画形成された凹状区画領域223の下方に重畳配置して形成されている。また、データ線側駆動制御信号導通部350は、ダミー領域112内であって、更に有機バンク層221の下方に重畳配置して形成されている。これにより、走査線側駆動電圧導通部310及び走査線側駆動制御信号導通部320の場合と同様、実質的に表示機能を具備しないダミー領域112の有効利用が可能となるとともに、検査回路90への安定した駆動電流の供給及びデータ信号の送信が可能となる。なお、データ線駆動回路100を同一基板20上に形成した場合、駆動電圧導通部及び駆動制御信号導通部を、それぞれ上記ダミー領域112の凹状区画領域223及び有機バンク層221の下方に重畳配置させることにより、同様の効果を得ることができる。

【0034】

次に、本実施形態に係る表示装置101の製造プロセスの一例について説明する。

まず、図5ないし図8を参照して、表示装置101の製造プロセス、特にアクティブマトリクス基板20上の各構成要素に関する製造プロセスを説明する。なお、図5ないし図8に示す各断面図は、図1中のA−B線の断面のうち走査線駆動回路80が形成され、ダミー領域112が形成される領域の断面115(図5(a)参照)と、実画素111(TFT24)が形成される領域の断面116(図5(a)参照)とにそれぞれ対応している。なお、以下の説明において、不純物濃度は、いずれも活性化アニール後の不純物として表される。

【0035】

まず、図5(a)に示すように、石英基板やガラス基板などの絶縁性基板であるアクティブマトリクス基板20の表面に、シリコン酸化膜などからなる下地保護層281を形成する。

次に、ICVD法、プラズマCVD法などを用いてアモルファスシリコン層501を形成した後、レーザアニール法又は急速加熱法により結晶粒を成長させてポリシリコン層とする。

さらに、図5(b)に示すように、当該ポリシリコン層をフォトリソグラフィ法によってパターニングし、島状のシリコン層241,251及び261を形成する。このうちシリコン層241は、表示領域内に形成され、画素電極23に接続されるTFT(画素用TFT)24を構成するものであり、シリコン層251,261は、走査線駆動回路80に含まれるPチャネル型及びNチャネル型のTFT(駆動回路用TFT)をそれぞれ構成するものである。

【0036】

次に、図5(b)に示すように、プラズマCVD法、熱酸化法などにより、シリコン層の全表面に厚さが約30nm〜200nmのシリコン酸化膜からなるゲート絶縁層282を形成する。ここで、熱酸化法を利用してゲート絶縁層282を形成する際には、シリコン層241,251及び261の結晶化も行い、これらのシリコン層をポリシリコン層とすることができる。チャネルドープを行う場合には、例えば、このタイミングで約1×1012cm-2のドーズ量でボロンイオンを打ち込む。その結果、シリコン層241,251及び261は、不純物濃度が約1×1017cm-3の低濃度P型のシリコン層となる。

【0037】

次に、Pチャネル型TFT、Nチャネル型TFTのチャネル層の一部にイオン注入選択マスクを形成し、この状態でリンイオンを約1×1015cm-2のドーズ量でイオン注入する。その結果、パターニング用マスクに対してセルフアライン的に高濃度不純物が導入されて、図5(c)に示すように、シリコン層241及び261中に高濃度ソース領域241S及び261S並びに高濃度ドレイン領域241D及び261Dが形成される。

【0038】

次に、図5(c)に示すように、ゲート絶縁層282の表面全体に、ドープドシリコンやシリサイド膜、或いはアルミニウム膜やクロム膜、タンタル膜といった金属膜からなるゲート電極形成用導電層502を形成する。当該導電層502の厚さは概ね500nm程度である。その後、パターニング法により、図5(d)に示すように、Pチャネル型の駆動回路用TFTを形成するゲート電極252、画素用TFTを形成するゲート電極242、Nチャネル型の駆動回路用TFTを形成するゲート電極262を形成する。また、駆動制御信号導通部320(350)、陰極電源配線の第1層121も同時に形成する。なお、この場合、駆動制御信号導通部320(350)はダミー領域112に配設するものとされている。

【0039】

続いて、図5(d)に示すように、ゲート電極242,252及び262をマスクとして用い、シリコン層241,251及び261に対してリンイオンを約4×1013cm-2のドーズ量でイオン注入する。その結果、ゲート電極242,252及び262に対してセルフアライン的に低濃度不純物が導入されて、図5(c)及び(d)に示すように、シリコン層241及び261中に低濃度ソース領域241b及び261b、並びに低濃度ドレイン領域241c及び261cが形成される。また、シリコン層251中に低濃度不純物領域251S及び251Dが形成される。

【0040】

次に、図6(e)に示すように、Pチャネル型の駆動回路用TFT252以外を覆うイオン注入選択マスク503を形成する。このイオン注入選択マスク503を用いて、シリコン層251に対してボロンイオンを約1.5×1015cm-2のドーズ量でイオン注入する。結果として、Pチャネル型駆動回路用TFTを構成するゲート電極252もマスクとして機能するため、シリコン層252中にセルフアライン的に高濃度不純物がドープされる。従って、251S及び251Dはカウンタードープされ、P型チャネル型の駆動回路用TFTのソース領域及びドレイン領域となる。

【0041】

次いで、図6(f)に示すように、アクティブマトリクス基板20の全面に亙って第1層間絶縁層283を形成するとともに、フォトリソグラフィ法を用いて当該第1層間絶縁層283をパターニングすることによって、各TFTのソース電極及びドレイン電極に対応する位置にコンタクトホールCを形成する。

【0042】

次に、図6(g)に示すように、第1層間絶縁層283を覆うように、アルミニウムやクロム、タンタル等の金属からなる導電層504を形成する。この導電層504の厚さは概ね200nmないし800nm程度である。この後、導電層504のうち、各TFTのソース電極及びドレイン電極が形成されるべき領域240a、駆動電圧導通部310(340)が形成されるべき領域310a、陰極電源配線の第2層が形成されるべき領域122aを覆うようにパターニング用マスク505を形成するとともに、当該導電層504をパターニングして、図7(h)に示すソース電極243,253,263、ドレイン電極244,254,264を形成する。

【0043】

次いで、図7(i)に示すように、これらが形成された第1層間絶縁層283を覆う第2層間絶縁層284を、例えばアクリル系などの樹脂材料によって形成する。この第2層間絶縁層284は、約1〜2μm程度の厚さに形成されることが望ましい。なお、窒化シリコンあるいは酸化シリコンにより第2層間絶縁膜を形成することも可能であり、窒化シリコンの膜厚としては200nm、酸化シリコンの膜厚としては800nmに形成することが望ましい。

続いて、図7(j)に示すように、第2層間絶縁層284のうち、画素用TFTのドレイン電極244に対応する部分をエッチングにより除去してコンタクトホール23aを形成する。

【0044】

この後、アクティブマトリクス基板20の全面を覆うようにITO等の透明電極材料からなる薄膜を形成する。そして、当該薄膜をパターニングすることにより、図8(k)に示すように、第2層間絶縁層284のコンタクトホール23aを介してドレイン電極244と導通する画素電極23を形成すると同時に、ダミー領域のダミーパターン26も形成する(図2では、これら画素電極23、ダミーパターン26を総称して画素電極23としている)。ダミーパターン26は、第2層間絶縁層284を介して下層のメタル配線へ接続しない構成とされている。すなわち、ダミーパターン26は、島状に配置され、表示領域に形成されている画素電極23の形状とほぼ同一の形状を有している。もちろん、表示領域に形成されている画素電極23の形状とは異なる構造で有っても良い。なお、この場合、ダミーパターン26は少なくとも上記駆動電圧導通部310(340)の上方に位置するものを含むものとされている。

【0045】

次に、図8(l)に示すように、画素電極23、ダミーパターン26上、及び第2層間絶縁膜上に絶縁層たる親水性制御層25を形成する。なお、画素電極23においては一部が開口する態様にて絶縁層(親水性制御層)25を形成し、該開口部25a(図3も参照)において画素電極23からの正孔移動が可能とされている。逆に、開口部25aを設けないダミーパターン26においては、絶縁層(親水性制御層)25が正孔移動遮蔽層となって正孔移動が生じないものとされている。

【0046】

次に、絶縁層(親水性制御層)25の所定位置を覆うように有機バンク層221を形成する。具体的な有機バンク層の形成方法としては、例えばアクリル樹脂、ポリイミド樹脂等のレジストを溶媒に溶かしたものを、スピンコート、ディップコート等により塗布して有機質層を形成する。なお、有機質層の構成材料は、後述するインクの溶媒に溶解せず、しかもエッチング等によってパターニングしやすいものであればどのようなものでもよい。さらに、有機質層をフォトリソグラフィ技術等により同時にエッチングして、有機質物のバンク開口部221aを形成し、開口部221aに壁面を備えた有機バンク層(隔壁部)221が形成される。なお、この場合、有機バンク層221は少なくとも上記駆動制御信号導通部320(350)の上方に位置するものを含むものとされている。

【0047】

続いて、有機バンク層221の表面に、親インク性を示す領域と、撥インク性を示す領域とを形成する。本実施例においてはプラズマ処理工程により、各領域を形成するものとしている。具体的に該プラズマ処理工程は、予備加熱工程と、バンク部221の上面及び開口部221aの壁面並びに画素電極23の電極面(画素電極の表面)23c、絶縁層(親水性制御層)25の上面を親インク性にする親インク化工程と、有機バンク層の上面及び開口部の壁面を撥インク性にする撥インク化工程と、冷却工程とを具備している。

【0048】

すなわち、基材(バンク等を含む基板20)を所定温度(例えば70〜80℃程度)に加熱し、次いで親インク化工程として大気雰囲気中で酸素を反応ガスとするプラズマ処理(酸素プラズマ処理)を行う。続いて、撥インク化工程として大気雰囲気中で4フッ化メタンを反応ガスとするプラズマ処理(CF4プラズマ処理)を行い、プラズマ処理のために加熱された基材を室温まで冷却することで、親インク性及び撥インク性が所定箇所に付与されることとなる。なお、画素電極23の電極面23c及び絶縁層(親水性制御層)25についても、このCF4プラズマ処理の影響を多少受けるが、画素電極23の材料であるITO(Indium Tin Oxide)及び絶縁層(親水性制御層)25の構成材料である酸化シリコンあるいは酸化チタン等は結果として親インク性を保つ。

【0049】

続いて図8(l)に示す正孔注入/輸送層70(図3も参照)を形成するべく正孔注入/輸送層形成工程が行われる。正孔注入/輸送層形成工程では、インクジェット法により、正孔注入/輸送層材料を含む組成物インクを電極面23c上に吐出した後に、乾燥処理及び熱処理を行い、電極23上に正孔注入/輸送層70を形成する。なお、この正孔注入/輸送層形成工程以降は、正孔注入/輸送層70及び発光層(有機EL層)60の酸化を防止すべく、窒素雰囲気、アルゴン雰囲気等の不活性ガス雰囲気で行うことが好ましい。例えば、インクジェットヘッド(図示略)に正孔注入/輸送層材料を含む組成物インクを充填し、インクジェットヘッドの吐出ノズルを絶縁層(親水性制御層)25に形成された上記開口部25a内に位置する電極面23cに対向させ、インクジェットヘッドと基材(基板20)とを相対移動させながら、吐出ノズルから1滴当たりの液量が制御されたインク滴を電極面23cに吐出する。次に、吐出後のインク滴を乾燥処理して組成物インクに含まれる極性溶媒を蒸発させることにより、正孔注入/輸送層70が形成される(図8(l)及び図3参照)。

【0050】

なお、組成物インクとしては、例えば、ポリエチレンジオキシチオフェン等のポリチオフェン誘導体と、ポリスチレンスルホン酸等の混合物を、イソプロピルアルコール等の極性溶媒に溶解させたものを用いるこいとができる。ここで、吐出されたインク滴は、親インク処理された電極面23c上に広がり、絶縁層(親水性制御層)25の開口部25a内に満たされる。その一方で、撥インク処理された有機バンク層221の上面では、インク滴がはじかれて付着しない。従って、インク滴が所定の吐出位置からはずれて有機バンク層221の上面に吐出されたとしても、該上面がインク滴で濡れることがなく、弾かれたインク滴が絶縁層(親水性制御層)25の開口部25a内に転がり込むものとされている。

【0051】

続いて図8(l)に示す発光層(有機EL層)60(図3も参照)を形成するべく発光層形成工程が行われる。発光層形成工程では、上記と同様なインクジェット法により、発光層用材料を含む組成物インクを正孔注入/輸送層70上に吐出した後に乾燥処理及び熱処理して、有機バンク層221に形成された開口部221a内に発光層60を形成する。

【0052】

発光層形成工程では、正孔注入/輸送層70の再溶解を防止するために、発光層形成の際に用いる組成物インクの溶媒として、正孔注入/輸送層70に対して不溶な無極性溶媒を用いる。しかし、その一方で正孔注入/輸送層70は、無極性溶媒に対する濡れ性が低いため、無極性溶媒を含む組成物インクを正孔注入/輸送層70上に吐出しても、正孔注入/輸送層70により発光層用の組成物インクが弾かれ、正孔注入/輸送層70と発光層60とを密着させることができなくなる場合がある他、発光層60を均一に塗布できない惧れがある。そこで、無極性溶媒に対する正孔注入/輸送層70の表面の濡れ性を高めるために、発光層形成の前に表面改質工程を行うことが好ましい。その表面改質工程は、例えば上記無極性溶媒と同一溶媒又はこれに類する溶媒をインクジェット法、スピンコート法又はディップ法等により正孔注入/輸送層70上に塗布した後に乾燥することにより行うものとすることができる。なお、ここで用いる表面改質用溶媒としては、組成物インクの無極性溶媒と同一なものとして例えば、シクロヘキシルベンゼン、ジハイドロベンゾフラン、トリメチルベンゼン、テトラメチルベンゼン等を例示でき、組成物インクの無極性溶媒に類するものとしては、例えばトルエン、キシレン等を例示することができる。

【0053】

表面改質工程に続く上記インクジェット法による発光層形成工程としては、例えばインクジェットヘッド(図示略)に、青色(B)発光層の材料を含有する組成物インクを充填し、インクジェットヘッドの吐出ノズルを絶縁層(親水性制御層)25の開口部25a内に位置する正孔注入/輸送層70に対向させ、インクジェットヘッドと基材とを相対移動させながら、吐出ノズルから1滴当たりの液量が制御されたインク滴として吐出し、このインク滴を正孔注入/輸送層70上に吐出する。

【0054】

発光層60を構成する発光材料としては、フルオレン系高分子や、(ポリ)パラフェニレンビニレン誘導体、ポリフェニレン誘導体、ポリフルオレン誘導体、ポリビニルカルバゾール、ポリチオフェン誘導体、ペリレン系色素、クマリン系色素、ローダミン系色素、その他ベンゼン誘導体に可溶な低分子有機EL材料、高分子有機EL材料等も用いることができる。例えば、ルブレン、ペリレン、9,10−ジフェニルアントラセン、テトラフェニルブタジエン、ナイルレッド、クマリン6、キナクリドン等を用いることができる。一方、無極性溶媒としては、正孔注入/輸送層70に対して不溶なものが好ましく、例えば、シクロヘキシルベンゼン、ジハイドロベンゾフラン、トリメチルベンゼン、テトラメチルベンゼン等を用いることができる。

【0055】

吐出されたインク滴は、正孔注入/輸送層70上に広がって親水性制御層25の開口部25a内に満たされる。その一方で、撥インク処理された有機バンク層221上面では、インク滴が弾かれて付着しない。これにより、インク滴が所定の吐出位置からはずれて有機バンク層221上面に吐出されたとしても、該上面がインク滴で濡れることがなく、インク滴が上記親水性制御層25の開口部25a内に転がり込み、さらに有機バンク層221の開口部221a内に吐出・充填される。続いて、吐出後のインク滴を乾燥処理することにより組成物インクに含まれる無極性溶媒を蒸発させ、青色発光層(発光層60)が形成される。

【0056】

さらに、青色発光層の場合と同様にして、例えば赤色発光層(発光層60)を形成し、最後に緑色発光層(発光層60)を形成する。なお、各色の発光層60の形成順序は、発光層材料の構成成分数が少ないものから順に行うことが好ましい。成分数の多い色の発光層を先に形成すると、後から形成した別の色の発光層の組成物インクから蒸発した溶媒蒸気によって、先に形成した発光層が再溶解して成分分離を起こす惧れがあるので好ましくない。

なお、正孔注入/輸送層、発光層をそれぞれインクジェットプロセスにより形成するが、この際、インクジェットヘッドは発光ドット間のピッチにより傾き方向を制御している。すなわち、インクジェットヘッドに形成されているノズルのピッチと、発光ドットのピッチとは必ずしも一致しないため、ヘッドの傾けて配置することにより発光ドットのピッチに合うように調整するのである。

【0057】

続いて図8(m)に示す陰極222、50を形成するべく陰極形成工程が行われる。該陰極形成工程においては、発光層60及び有機バンク層221の全面に、陰極222、50となる下部陰極層及び上部陰極層を順次積層する。下部陰極層は仕事関数が上部陰極層よりも相対的に小さいもので構成することが好ましく、例えばフッ化リチウム、カルシウム、アルミニウム等を用いることができる。また、上部陰極層は下部陰極層を保護するもので、下部陰極層よりも仕事関数が相対的に大きいもので構成することが好ましく、製法としては例えば蒸着法、スパッタ法、CVD法等で形成することが好ましく、特に蒸着法で形成することが、発光層60の熱による損傷を防止できる点で好ましい。なお、ここでは図8の222がカルシウム(下部陰極層)、50がアルミニウム(上部陰極層)に対応する。更に、Al以外にもAg膜、Mg/Ag積層膜等を用いることができる。

【0058】

最後に、図8(m)に示す封止基板30を形成するべく封止工程を行う。この封止工程では、封止基板30の内側に乾燥剤45を挿入しつつ、該封止基板30とアクティブマトリクス基板20とを接着剤40にて封止する。なお、この封止工程は、窒素、アルゴン、ヘリウム等の不活性ガス雰囲気で行うことが好ましい。大気中で行うと、反射層50にピンホール等の欠陥が生じていた場合に、この欠陥部分から水や酸素等が陰極222に侵入して陰極222が酸化される惧れがある。

【0059】

以上のような製造プロセスにより、図1〜図3に示すような表示装置101が得られる。

【0060】

以下、本発明の表示装置を備えた電子機器について幾つかの例を示す。

図9(a)は、携帯電話を示す斜視図である。1000は携帯電話本体を示し、そのうちの1001は本発明の表示装置を用いた表示部である。

図9(b)は、腕時計型電子機器を示す図である。1100は時計本体を示す斜視図である。1101は本発明の表示装置を用いた表示部である。

【0061】

図9(c)は、ワープロ、パソコン等の携帯型情報処理装置を示す図である。1200は情報処理装置を示し、1202はキーボード等の入力部、1206は本発明の表示装置を用いた表示部、1204は情報処理装置本体を示す。各々の電子機器は電池により駆動される電子機器であるので、本発明の構成を採用することで、安定した電力供給を実現することが可能となる。また、これら電子機器は小型のものが多いなか、本発明の表示装置を採用することで機器全体が小型であるにも拘らず比較的大きな表示領域を確保することが可能となる。

【0062】

本発明の表示装置によると、基板上において表示を行うことが不可能な領域(駆動制御信号導通部とダミー画素領域)を相殺させ、該基板上の表示不可能な領域の増大を低減可能となり、有効な表示領域を増大することが可能となる。さらに、駆動制御信号導通部を隔壁部と重畳配置したため、陰極層と駆動制御信号導通部との間の距離が凹状区画部と重畳配置した場合に比して相対的に大きくなるため、陰極層と駆動制御信号導通部との間のキャパシタンスが小さくなり、該キャパシタンスによる駆動制御信号への外的影響、具体的にはパルス信号の波形鈍り等の発生が低減される。

【符号の説明】

【0063】

20…アクティブマトリクス基板、23…陽極層、24…画素用TFT(スイッチング手段)、60…有機EL層(発光層、表示本体層)、80…走査線駆動回路(作動制御手段)、90…データ線駆動回路(作動制御手段)、111…実画素部、112…ダミー画素部、221…バンク部、221a…開口部、222…陰極層、320…走査線側駆動制御信号導通部、350…データ線側駆動制御信号導通部。

【技術分野】

【0001】

本発明は、表示装置及び電子機器に関するものである。

【背景技術】

【0002】

従来、液晶表示装置、EL表示装置等の光学表示装置においては、基板上に複数の回路素子、電極、液晶又はEL素子等が積層された構成を具備しているものがある。例えばEL表示装置においては、発光物質を含む発光層を陽極及び陰極の電極層で挟んだ構成を具備しており、陽極側から注入された正孔と、陰極側から注入された電子とを発光能を有する発光層内で再結合し、励起状態から失括する際に発光する現象を利用している。

【0003】

このようなEL表示装置の駆動方式としては、行方向に走査線及び列方向にデータ線をマトリクス状に配設するとともに、その交差部分にあるEL素子の画素毎に静電容量素子とトランジスタ等を配置して、書き込み走査時に各画素の静電容量素子に充電した電圧に従って、次に書き換えられるまで発光を持続する、いわゆるアクティブマトリクス駆動方式が知られている(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開第98/3640号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記のようなアクティブマトリクス駆動方式の表示装置において、駆動回路として、各走査線毎に走査選択パルスを印加する走査線用の駆動回路、各データ線毎にデータ信号を供給するデータ線用の駆動回路、及びその制御を行うコントロール回路を有するものがある。このような表示装置においては、駆動回路及び/又はコントロール回路を基板上に配設しなければならず基板が大型化するか、これら回路が配設された領域は表示領域として使用し難く、基板上を表示領域として有効に利用できない等の問題が生じる場合がある。また、所定の電源部から上記駆動回路及び/又はコントロール回路への導電線も基板上に配設しなければならない他、コントロール回路から駆動回路への駆動制御信号線も基板上に配設しなければならないため、さらに表示領域が有効に利用できないものとなる場合がある。

【0006】

一方、上記駆動制御信号は、当該表示装置の作動を司る信号であって、該信号へのノイズ混入、又は信号波形を変化させ得る外的影響は極力回避しなけらばならない。

【0007】

本発明の課題は、駆動回路等を制御するための駆動制御信号の信号線を基板の所定部位に配設することで、基板面を有効に利用するとともに、駆動制御信号への外的影響を防止ないし抑制することが可能な表示装置、及びそれを備えた電子機器を提供することにある。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明の表示装置は、基板上に、表示に寄与する表示領域と、表示に寄与しない非表示領域とを含むとともに、該表示領域及び非表示領域には、隔壁部と該隔壁部により区画形成された凹状区画領域とが所定のマトリクスパターンで配列され、前記表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも第1電極層と、表示若しくは非表示を切り換え可能な物質を含む表示主体層と、第2電極層とを含み、前記非表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも前記表示主体層と、第2電極層とを含み、さらに前記基板上には、前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、そのスイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動制御信号が導通する駆動制御信号導通部とが設けられ、前記駆動制御信号導通部が、少なくとも前記非表示領域に配置された部分を含み、さらに前記基板を平面視した場合に、前記隔壁部と重畳する部分を含むように配置されていることを特徴とする。

【0009】

このような表示装置においては、隔壁部により区画形成された凹状区画領域がマトリクスパターンで配列して画素を形成することとなるが、例えばこのようなマトリクスパターンで画素を配列する場合には、該画素の全てを表示に寄与する表示領域(実画素)とせず、その一部を表示に寄与しない非表示領域(ダミー画素)として形成することがある。これは、製造上の問題で、例えば上記表示本体層を各凹状区画領域に層形成する際、特に基板上の周縁部の凹状区画領域において該表示本体層の層厚を均一に形成することが困難な場合があり、そのような場合においては、上記層厚が不均一となり得る凹状区画領域を含む領域を非表示領域として形成することで、表示本体層の層厚不均一による表示上の不具合を解消している。そのような不具合としては、例えばコントラストの低下、表示むら、画素寿命の低下等が挙げられる。

ところで、上記非表示領域は通常の表示機能を果たしてはいない。

そこで、本発明者は、該非表示領域を積極的に有効利用するために、上記スイッチング手段の作動制御を行う作動制御手段への駆動制御信号の導通部を少なくとも非表示領域に形成した。したがって、非表示領域と同様、実質的に表示機能を担わない駆動制御信号導通部が該非表示領域に配置されるため、基板上における表示機能を担わない部分の面積が相殺されるものとなり、基板上の表示不能な領域の増大を低減させることが可能となる。

さらに駆動制御信号導通部を基板厚さ方向において隔壁部の下側に位置するように、すなわち表示方向において隔壁部と駆動制御信号導通部とが重畳配置する構成とした。この場合、基板を平面視した場合に、駆動制御信号導通部が隔壁部と重畳配置する部分を含むように配置され、非表示領域の第2電極層と駆動制御信号導通部との間の距離が比較的大きなものとなる。すなわち、第2電極層と駆動制御信号導通部との間の距離が、凹状区画領域よりも相対的に大きな隔壁部の下方に駆動制御信号導通部を設けることで、該第2電極層と駆動制御信号導通部との間のキャパシタンスが、凹状区画部の下方に設けるよりも小さくなり、該キャパシタンスによる駆動制御信号への外的影響が低減される。ここで、凹状区画領域は駆動制御信号導通部側(基板側)に凹んだ底部を具備しており、その底部に第2電極層を含んでいるため、隔壁部と比して静電容量が大きくなる傾向にあり、逆に隔壁部は駆動制御信号導通部側(基板側)から突出した凸部を具備しており、その凸部の頂側に第2電極層を含んでいるため凹状区画領域と比して静電容量が小さくなる傾向にある。

したがって、このような本発明の表示装置は、通常の表示を行わない領域を低減し基板を表示領域として有効に利用できるとともに、駆動制御信号への外的影響、例えばパルス波形変化等に基づく当該表示装置の誤作動発生を防止ないし抑制することが可能となる。なお、上記表示装置において、表示本体層には表示物質として例えば有機EL物質を用いることができ、その他にも、表示物質として液晶物質を用いることもできる。

【0010】

また、前記作動制御手段を駆動させるための駆動電圧が印加する駆動電圧導通部が基板上に設けられ、該駆動電圧導通部及び前記駆動制御信号導通部と前記第2電極層との間には絶縁層が形成され、前記駆動制御信号導通部は前記駆動電圧導通部と比して前記第2電極側に遠い絶縁層領域に形成されているものとすることができる。この場合、駆動電圧導通部に対しては上述したキャパシタにより電流値低下が補償されるとともに、駆動制御信号導通部に対しては相対的に上記キャパシタが形成し難くなり、制御信号に対する外的悪影響が生じ難くなる。また、前記非表示領域は、前記基板と前記表示本体層との間に位置する第1電極層を備え、さらに該第1電極層と前記第2電極層との間の導通を遮る絶縁層を備えるものとすることができる。この場合、絶縁層により各電極間の通電が不可能、若しくは表示領域よりも相対的に通電困難となり、非表示領域が形成されるものとされている。なお、製造時において例えば各電極層、表示本体層、絶縁層等をフォトリソグラフィにて形成する場合、該絶縁層を凹状区画領域の全域に形成するか、若しくは絶縁層の一部を開口させて絶縁空乏層を形成するかにより、表示領域、若しくは非表示領域のいずれかを簡便に形成することが可能となる。

【0011】

さらに、該絶縁層の表層面が、前記隔壁部の表層面と比して相対的に前記表示本体層との親和性が高い材質にて構成されているものとすることができる。この場合、表示本体層の層厚が隔壁部近傍で大きくなる等の不具合が生じにくく、該層厚を一層均一にすることが可能となり、ひいては表示むら等の不具合が生じにくくなる。

【0012】

次に、前記基板上には、複数の走査線及び複数のデータ線がマトリクス状に形成されるとともに、前記スイッチング手段が該走査線とデータ線に接続され、前記作動制御手段が前記データ線を導通する信号に関する制御を行うデータ制御手段を含むことができる。一方、前記スイッチング手段が前記走査線とデータ線に接続され、前記作動制御手段が前記走査線を導通する信号に関する制御を行う走査制御手段を含むものとすることも可能で、勿論、作動制御手段がデータ制御手段及び走査制御手段のそれぞれを含むものとすることも可能である。

さらに、前記基板上には、複数の検査線が形成されるとともに、前記スイッチング手段が該検査線に接続され、前記作動制御手段が前記検査線を導通する信号に関する制御を行う検査制御手段を含むものとすることも可能で、勿論、作動制御手段がデータ制御手段及び走査制御手段、検査制御手段のそれぞれを含むものとすることも可能である。この場合、作動制御手段により走査線及び/又はデータ線及び/又は検査線を導通する信号に関する制御を確実に行うことが可能となり、さらにこれら走査線及び/又はデータ線及び/又は検査線、スイッチング手段等を基板上に配設するため、基板面積の有効利用が望まれるが、本発明のような作動制御手段への駆動制御信号導通部の構成を採用することにより該有効利用と、駆動制御信号の安定した送信が可能となり得る。

【0013】

ところで、表示物質として有機EL物質又は液晶物質等を用いる場合、例えば該表示物質を構成する発光物質又は液晶物質等を各画素(凹状区画領域)に対してインクジェット法にて表示本体層を形成することが可能である。該インクジェット法では上述した表示本体層の層厚の不均一化を抑制するために、非表示領域を所定領域、例えば基板面の周縁部において形成する場合がある。したがって、このようなインクジェット法を用いて表示本体を形成した場合、本発明の構成を採用することで、基板面における非表示領域の有効利用が可能となる。

【0014】

なお、本発明の電子機器は、上記表示装置を表示部として備えたことを特徴とする。このような電子機器としては、例えば携帯電話、時計や、ワープロ、パソコン等の情報処理装置等を例示することができる。これら電子機器は小型のものが多いが、本発明の表示装置を採用することで表示領域の有効利用が可能となり、機器全体が小型であるにも拘らず比較的大きな表示領域を確保することが可能となる。

【図面の簡単な説明】

【0015】

【図1】本発明の表示装置の一実施形態たるEL表示装置の平面模式図。

【図2】図1のA−B断面模式図。

【図3】図2の要部を拡大した断面模式図。

【図4】図1のC−D断面模式図。

【図5】図1のEL表示装置の製造プロセスの一例を示す説明図。

【図6】図5に続くEL表示装置の製造プロセスの一例を示す説明図。

【図7】図6に続くEL表示装置の製造プロセスの一例を示す説明図。

【図8】図7に続くEL表示装置の製造プロセスの一例を示す説明図。

【図9】本発明の電子機器の一実施形態を示す模式図。

【発明を実施するための形態】

【0016】

以下、図面を参照して、本発明の実施形態について説明する。かかる実施の形態は、本発明の一態様を示すものであり、この発明を限定するものではなく、本発明の技術的思想の範囲内で任意に変更可能である。なお、以下に示す各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材ごとに縮尺を異ならせてある。

【0017】

まず、表示主体層を構成する電気光学物質の一例としてエレクトロルミネッセンス(以下ELと記す)を用いたEL表示装置に本発明の構成を適用した実施形態について説明する。図1及び図2は、本実施形態に係るEL表示装置の構成を模式的に示す平面図及びA−B断面図である。同図に示すEL表示装置101は、スイッチング素子として薄膜トランジスタ(TFT:Thin Film Transistor)を用いたアクティブマトリクス方式のEL表示装置である。

【0018】

EL表示装置101は、各画素にデータ信号を書き込むか否かを制御するスイッチング手段としてのTFT(図3に示すTFT24であって、画素用TFTとも言う)に加え、走査線駆動回路80及び検査回路90を構成するスイッチング手段の駆動手段たるTFT(駆動回路用TFTとも言う)を基板20上に形成している。また、当該表示装置101の画素部110は、パネル表示に寄与する実画素領域111と、画素部110から実画素領域111を除いた領域に形成され、通常の表示に寄与しないダミー領域112とを備えている。

【0019】

EL表示装置101は、図2に示すように、相互に対向するアクティブマトリクス基板20と、封止基板(対向基板)30とが封止樹脂40を介して貼り合わされるとともに、両基板20,30と封止樹脂40とに囲まれた領域に、乾燥剤45が挿入された構成となっており、さらに両基板20,30間に形成された空間には窒素ガスなどの不活性ガスが充填されたガス充填層46を形成している。また、アクティブマトリクス基板20上には陽極(画素電極)23と、該陽極(画素電極)23から正孔を注入/輸送可能な正孔/注入輸送層70(図3参照)と、電気光学物質の一つである有機EL物質(以下、発光層、または有機EL層ともいう)60とを介して陰極222が例えば蒸着等により形成されている。アクティブマトリクス基板20及び封止基板(対向基板)30は、ガラスや石英、プラスチックといった光透過性を有する絶縁性の板状部材が用いられる。

【0020】

ここで、画素用TFT24(図3参照)を駆動するための走査線駆動回路80は、アクティブマトリクス基板20上に設けられている。一方、データ線駆動回路100はデータドライバICとして外付けで設けられている。もちろん、同一アクティブマトリクス基板20にデータ線駆動回路100を設けることも可能である。

また、検査回路90は、当該表示装置101の作動状況あるいは初期不良等を検査するための回路であって、例えば該検査結果を外部に出力するための検査情報出力手段を備えている。

【0021】

上記走査線駆動回路80及びデータ線駆動回路100は、走査線及びデータ線に導通する信号の出力制御を行う走査制御手段及びデータ制御手段として構成され、これら走査線及びデータ線が上記画素用TFT24(図3参照)に接続されている。すなわち、走査線駆動回路80及びデータ線駆動回路100からの作動指令信号に基づいて画素用TFT24(図3参照)が作動し、該画素用TFT24が画素電極23への通電制御を行っている。

【0022】

走査線駆動回路80及びデータ線駆動回路100の駆動電流または駆動電圧は、所定の電源部から駆動電圧導通部310(図2参照)及び駆動電圧導通部340(図4参照)を介して供給されている。また、これら走査線駆動回路80及びデータ線駆動回路100への駆動制御信号は、当該表示装置101の作動制御を司る所定のメインドライバ等から駆動制御信号導通部320(図2参照)及び駆動制御信号導通部350(図4参照)を介して送信されるようになっている。なお、この場合の駆動制御信号とは、例えば、上記走査線あるいはデータ線への信号出力のタイミングを制御する信号、走査線駆動回路80及びデータ線駆動回路100の制御に関連するクロック信号、イネーブル信号等の種々の制御信号等の指令信号のことを言う。

【0023】

次に、図3は表示領域内において実画素部111に対応して設けられたTFT(画素用TFT)24の近傍の構成を示す断面図である。同図に示すように、アクティブマトリクス基板20の表面には、酸化シリコンを主体とする下地保護層281を下地として、その上層にはシリコン層241が形成されている。このシリコン層241の表面は、酸化シリコン及び/又は窒化シリコンを主体とするゲート絶縁層282によって覆われている。そして、このシリコン層241のうち、ゲート絶縁層282を挟んでゲート電極242と重なる領域がチャネル領域241aとされている。なお、このゲート電極242は走査線の一部である。一方、シリコン層241を覆い、ゲート電極242が形成されたゲート絶縁層282の表面は、酸化シリコンを主体とする第1層間絶縁層283によって覆われている。なお、本明細書において、「主体」とする成分とは最も含有率の高い成分のことを言うものとする。

【0024】

また、シリコン層241のうち、チャネル領域241aのソース側には低濃度ソース領域241b及び高濃度ソース領域241Sが設けられる一方、チャネル領域241aのドレイン側には低濃度ドレイン領域241c及び高濃度ドレイン領域241Dが設けられて、いわゆるLDD(Light Doped Drain)構造となっている。このうち、高濃度ソース領域241Sは、ゲート絶縁層282と第1層間絶縁層283とに亙って開孔するコンタクトホールを介して、ソース電極243に接続されている。このソース電極243は、上述したデータ線(図3における紙面垂直方向に延在する)の一部として構成される。一方、高濃度ドレイン領域241Dは、ゲート絶縁層282と第1層間絶縁層283とに亙って開孔するコンタクトホールを介して、ソース電極243と同一層からなるドレイン電極244に接続されている。

【0025】

ソース電極243及びドレイン電極244が形成された第1層間絶縁層283の上層は、例えばアクリル系の樹脂成分を主体とする第2層間絶縁層284によって覆われている。また、アクリル系の絶縁膜以外にも、窒化シリコン、酸化シリコンからなる絶縁膜を形成することができる。

そして、ITOからなる画素電極23が、この第2層間絶縁層284の面上に形成されるとともに、当該第2層間絶縁層284に設けられたコンタクトホール23aを介してドレイン電極244に接続されている。すなわち、画素電極23は、ドレイン電極244を介して、シリコン層241の高濃度ドレイン電極241Dに接続されている。

【0026】

なお、走査線駆動回路80及び検査回路90に含まれるTFT(駆動回路用TFT)、すなわち、例えばこれらの駆動回路のうち、シフトレジスタに含まれるインバータを構成するNチャネル型又はPチャネル型のTFTは、画素電極23と接続されていない点を除いて上記TFT24と同様の構造となっている。

【0027】

画素電極23が形成された第2層間絶縁層284の表面は、例えば酸化シリコンを主体とする親水性制御層25と、アクリルやポリイミド等からなる有機バンク層221によって覆われている。そして、画素電極23には親水性制御層25に設けられた開口部25a、及び有機バンク221に設けられた開口部221a内側に、正孔注入/輸送層70と、有機EL層60とが画素電極23側からこの順で積層されている。

【0028】

正孔注入/輸送層70と、有機EL層60との上層は、例えばCa222、Alを積層して形成した陰極50によって覆われている。EL表示装置101は、基本的に以上の構成により作成されるが、図2では、封止基板30を用いて乾燥剤45を使用することにより高寿命化を図った構成となっている。

【0029】

図2に戻り、本実施例の表示装置101においては、上記走査線側駆動電圧導通部310がダミー領域112に形成され、特に有機バンク層221により区画形成された凹状区画領域223の下方に形成されている。すなわち、走査線側駆動電圧導通部310が、有機バンク層221を回避して配置され、当該表示装置101若しくは基板20を平面視した場合に、ダミー領域112の凹状区画領域223と重なる位置に少なくとも形成されている。

【0030】

これはダミー領域112が表示に寄与しない非表示領域であって、駆動電圧導通部310とを重ねて配置した構造である。すなわち、図2に示すように、表示可能方向においてこれらを重畳配置したものである。これにより、非表示画素部の有効利用が図られている。凹状区画領域223に上部から順に陰極50、222、親水性制御層25、絶縁層284、電源配線(駆動電圧導通部)310と形成することで、これらを隔壁部に形成するよりも電源配線と陰極との間の距離を小さく出来る。その為、電源配線と陰極との間の静電容量をより多く確保することができることにより、電源配線部における電圧値が低下した場合でも、上記静電容量により電源低下が補償されるものとなり、例えば駆動電圧低下による表示装置の誤作動等の不具合発生を防止ないし抑制することが可能となっている。

【0031】

また、走査線側駆動制御信号導通部(回路用制御信号線)320については、ダミー画素部112に形成され、特に有機バンク層221の下方に形成されている。すなわち、走査線側駆動制御信号導通部320が、有機バンク層221に対応して配置され、当該表示装置101若しくは基板20を平面視した場合に、ダミー画素部112の有機バンク層221と重なる位置に少なくとも形成されている。

【0032】

これはダミー領域112が表示に寄与しない非表示画素部であって、該非表示画素部と、駆動制御信号導通部320とを、表示可能方向において重畳配置したものである。これにより、非表示画素部の有効利用が図られている。また、駆動制御信号導通部320を有機バンク層221の下方に重畳配置して形成することで、上記凹状区画領域223と重畳配置して形成したときと比して、該駆動制御信号導通部320と陰極222との間の距離が相対的に大きくなり、上述のような高い静電容量を具備したキャパシタが形成され難く、駆動制御信号導通部320を導通する信号に対する影響を低減することが可能となる。すなわち、駆動制御信号導通部320を導通するパルス信号は、上記のようなキャパシタの形成によりパルス波形が鈍ってしまう等の不具合が生じる場合があるが、本実施例のように、高い静電容量を具備し難い位置に駆動制御信号導通部50を配置することで、該不具合発生を防止ないし抑制することができる。

【0033】

一方、図4は図1の平面図に示したC−D断面図である。この場合も、検査回路90を駆動させるための検査回路側駆動電圧導通部340が、ダミー領域112内であって、更に有機バンク層221により区画形成された凹状区画領域223の下方に重畳配置して形成されている。また、データ線側駆動制御信号導通部350は、ダミー領域112内であって、更に有機バンク層221の下方に重畳配置して形成されている。これにより、走査線側駆動電圧導通部310及び走査線側駆動制御信号導通部320の場合と同様、実質的に表示機能を具備しないダミー領域112の有効利用が可能となるとともに、検査回路90への安定した駆動電流の供給及びデータ信号の送信が可能となる。なお、データ線駆動回路100を同一基板20上に形成した場合、駆動電圧導通部及び駆動制御信号導通部を、それぞれ上記ダミー領域112の凹状区画領域223及び有機バンク層221の下方に重畳配置させることにより、同様の効果を得ることができる。

【0034】

次に、本実施形態に係る表示装置101の製造プロセスの一例について説明する。

まず、図5ないし図8を参照して、表示装置101の製造プロセス、特にアクティブマトリクス基板20上の各構成要素に関する製造プロセスを説明する。なお、図5ないし図8に示す各断面図は、図1中のA−B線の断面のうち走査線駆動回路80が形成され、ダミー領域112が形成される領域の断面115(図5(a)参照)と、実画素111(TFT24)が形成される領域の断面116(図5(a)参照)とにそれぞれ対応している。なお、以下の説明において、不純物濃度は、いずれも活性化アニール後の不純物として表される。

【0035】

まず、図5(a)に示すように、石英基板やガラス基板などの絶縁性基板であるアクティブマトリクス基板20の表面に、シリコン酸化膜などからなる下地保護層281を形成する。

次に、ICVD法、プラズマCVD法などを用いてアモルファスシリコン層501を形成した後、レーザアニール法又は急速加熱法により結晶粒を成長させてポリシリコン層とする。

さらに、図5(b)に示すように、当該ポリシリコン層をフォトリソグラフィ法によってパターニングし、島状のシリコン層241,251及び261を形成する。このうちシリコン層241は、表示領域内に形成され、画素電極23に接続されるTFT(画素用TFT)24を構成するものであり、シリコン層251,261は、走査線駆動回路80に含まれるPチャネル型及びNチャネル型のTFT(駆動回路用TFT)をそれぞれ構成するものである。

【0036】

次に、図5(b)に示すように、プラズマCVD法、熱酸化法などにより、シリコン層の全表面に厚さが約30nm〜200nmのシリコン酸化膜からなるゲート絶縁層282を形成する。ここで、熱酸化法を利用してゲート絶縁層282を形成する際には、シリコン層241,251及び261の結晶化も行い、これらのシリコン層をポリシリコン層とすることができる。チャネルドープを行う場合には、例えば、このタイミングで約1×1012cm-2のドーズ量でボロンイオンを打ち込む。その結果、シリコン層241,251及び261は、不純物濃度が約1×1017cm-3の低濃度P型のシリコン層となる。

【0037】

次に、Pチャネル型TFT、Nチャネル型TFTのチャネル層の一部にイオン注入選択マスクを形成し、この状態でリンイオンを約1×1015cm-2のドーズ量でイオン注入する。その結果、パターニング用マスクに対してセルフアライン的に高濃度不純物が導入されて、図5(c)に示すように、シリコン層241及び261中に高濃度ソース領域241S及び261S並びに高濃度ドレイン領域241D及び261Dが形成される。

【0038】

次に、図5(c)に示すように、ゲート絶縁層282の表面全体に、ドープドシリコンやシリサイド膜、或いはアルミニウム膜やクロム膜、タンタル膜といった金属膜からなるゲート電極形成用導電層502を形成する。当該導電層502の厚さは概ね500nm程度である。その後、パターニング法により、図5(d)に示すように、Pチャネル型の駆動回路用TFTを形成するゲート電極252、画素用TFTを形成するゲート電極242、Nチャネル型の駆動回路用TFTを形成するゲート電極262を形成する。また、駆動制御信号導通部320(350)、陰極電源配線の第1層121も同時に形成する。なお、この場合、駆動制御信号導通部320(350)はダミー領域112に配設するものとされている。

【0039】

続いて、図5(d)に示すように、ゲート電極242,252及び262をマスクとして用い、シリコン層241,251及び261に対してリンイオンを約4×1013cm-2のドーズ量でイオン注入する。その結果、ゲート電極242,252及び262に対してセルフアライン的に低濃度不純物が導入されて、図5(c)及び(d)に示すように、シリコン層241及び261中に低濃度ソース領域241b及び261b、並びに低濃度ドレイン領域241c及び261cが形成される。また、シリコン層251中に低濃度不純物領域251S及び251Dが形成される。

【0040】

次に、図6(e)に示すように、Pチャネル型の駆動回路用TFT252以外を覆うイオン注入選択マスク503を形成する。このイオン注入選択マスク503を用いて、シリコン層251に対してボロンイオンを約1.5×1015cm-2のドーズ量でイオン注入する。結果として、Pチャネル型駆動回路用TFTを構成するゲート電極252もマスクとして機能するため、シリコン層252中にセルフアライン的に高濃度不純物がドープされる。従って、251S及び251Dはカウンタードープされ、P型チャネル型の駆動回路用TFTのソース領域及びドレイン領域となる。

【0041】

次いで、図6(f)に示すように、アクティブマトリクス基板20の全面に亙って第1層間絶縁層283を形成するとともに、フォトリソグラフィ法を用いて当該第1層間絶縁層283をパターニングすることによって、各TFTのソース電極及びドレイン電極に対応する位置にコンタクトホールCを形成する。

【0042】

次に、図6(g)に示すように、第1層間絶縁層283を覆うように、アルミニウムやクロム、タンタル等の金属からなる導電層504を形成する。この導電層504の厚さは概ね200nmないし800nm程度である。この後、導電層504のうち、各TFTのソース電極及びドレイン電極が形成されるべき領域240a、駆動電圧導通部310(340)が形成されるべき領域310a、陰極電源配線の第2層が形成されるべき領域122aを覆うようにパターニング用マスク505を形成するとともに、当該導電層504をパターニングして、図7(h)に示すソース電極243,253,263、ドレイン電極244,254,264を形成する。

【0043】

次いで、図7(i)に示すように、これらが形成された第1層間絶縁層283を覆う第2層間絶縁層284を、例えばアクリル系などの樹脂材料によって形成する。この第2層間絶縁層284は、約1〜2μm程度の厚さに形成されることが望ましい。なお、窒化シリコンあるいは酸化シリコンにより第2層間絶縁膜を形成することも可能であり、窒化シリコンの膜厚としては200nm、酸化シリコンの膜厚としては800nmに形成することが望ましい。

続いて、図7(j)に示すように、第2層間絶縁層284のうち、画素用TFTのドレイン電極244に対応する部分をエッチングにより除去してコンタクトホール23aを形成する。

【0044】

この後、アクティブマトリクス基板20の全面を覆うようにITO等の透明電極材料からなる薄膜を形成する。そして、当該薄膜をパターニングすることにより、図8(k)に示すように、第2層間絶縁層284のコンタクトホール23aを介してドレイン電極244と導通する画素電極23を形成すると同時に、ダミー領域のダミーパターン26も形成する(図2では、これら画素電極23、ダミーパターン26を総称して画素電極23としている)。ダミーパターン26は、第2層間絶縁層284を介して下層のメタル配線へ接続しない構成とされている。すなわち、ダミーパターン26は、島状に配置され、表示領域に形成されている画素電極23の形状とほぼ同一の形状を有している。もちろん、表示領域に形成されている画素電極23の形状とは異なる構造で有っても良い。なお、この場合、ダミーパターン26は少なくとも上記駆動電圧導通部310(340)の上方に位置するものを含むものとされている。

【0045】

次に、図8(l)に示すように、画素電極23、ダミーパターン26上、及び第2層間絶縁膜上に絶縁層たる親水性制御層25を形成する。なお、画素電極23においては一部が開口する態様にて絶縁層(親水性制御層)25を形成し、該開口部25a(図3も参照)において画素電極23からの正孔移動が可能とされている。逆に、開口部25aを設けないダミーパターン26においては、絶縁層(親水性制御層)25が正孔移動遮蔽層となって正孔移動が生じないものとされている。

【0046】

次に、絶縁層(親水性制御層)25の所定位置を覆うように有機バンク層221を形成する。具体的な有機バンク層の形成方法としては、例えばアクリル樹脂、ポリイミド樹脂等のレジストを溶媒に溶かしたものを、スピンコート、ディップコート等により塗布して有機質層を形成する。なお、有機質層の構成材料は、後述するインクの溶媒に溶解せず、しかもエッチング等によってパターニングしやすいものであればどのようなものでもよい。さらに、有機質層をフォトリソグラフィ技術等により同時にエッチングして、有機質物のバンク開口部221aを形成し、開口部221aに壁面を備えた有機バンク層(隔壁部)221が形成される。なお、この場合、有機バンク層221は少なくとも上記駆動制御信号導通部320(350)の上方に位置するものを含むものとされている。

【0047】

続いて、有機バンク層221の表面に、親インク性を示す領域と、撥インク性を示す領域とを形成する。本実施例においてはプラズマ処理工程により、各領域を形成するものとしている。具体的に該プラズマ処理工程は、予備加熱工程と、バンク部221の上面及び開口部221aの壁面並びに画素電極23の電極面(画素電極の表面)23c、絶縁層(親水性制御層)25の上面を親インク性にする親インク化工程と、有機バンク層の上面及び開口部の壁面を撥インク性にする撥インク化工程と、冷却工程とを具備している。

【0048】

すなわち、基材(バンク等を含む基板20)を所定温度(例えば70〜80℃程度)に加熱し、次いで親インク化工程として大気雰囲気中で酸素を反応ガスとするプラズマ処理(酸素プラズマ処理)を行う。続いて、撥インク化工程として大気雰囲気中で4フッ化メタンを反応ガスとするプラズマ処理(CF4プラズマ処理)を行い、プラズマ処理のために加熱された基材を室温まで冷却することで、親インク性及び撥インク性が所定箇所に付与されることとなる。なお、画素電極23の電極面23c及び絶縁層(親水性制御層)25についても、このCF4プラズマ処理の影響を多少受けるが、画素電極23の材料であるITO(Indium Tin Oxide)及び絶縁層(親水性制御層)25の構成材料である酸化シリコンあるいは酸化チタン等は結果として親インク性を保つ。

【0049】

続いて図8(l)に示す正孔注入/輸送層70(図3も参照)を形成するべく正孔注入/輸送層形成工程が行われる。正孔注入/輸送層形成工程では、インクジェット法により、正孔注入/輸送層材料を含む組成物インクを電極面23c上に吐出した後に、乾燥処理及び熱処理を行い、電極23上に正孔注入/輸送層70を形成する。なお、この正孔注入/輸送層形成工程以降は、正孔注入/輸送層70及び発光層(有機EL層)60の酸化を防止すべく、窒素雰囲気、アルゴン雰囲気等の不活性ガス雰囲気で行うことが好ましい。例えば、インクジェットヘッド(図示略)に正孔注入/輸送層材料を含む組成物インクを充填し、インクジェットヘッドの吐出ノズルを絶縁層(親水性制御層)25に形成された上記開口部25a内に位置する電極面23cに対向させ、インクジェットヘッドと基材(基板20)とを相対移動させながら、吐出ノズルから1滴当たりの液量が制御されたインク滴を電極面23cに吐出する。次に、吐出後のインク滴を乾燥処理して組成物インクに含まれる極性溶媒を蒸発させることにより、正孔注入/輸送層70が形成される(図8(l)及び図3参照)。

【0050】

なお、組成物インクとしては、例えば、ポリエチレンジオキシチオフェン等のポリチオフェン誘導体と、ポリスチレンスルホン酸等の混合物を、イソプロピルアルコール等の極性溶媒に溶解させたものを用いるこいとができる。ここで、吐出されたインク滴は、親インク処理された電極面23c上に広がり、絶縁層(親水性制御層)25の開口部25a内に満たされる。その一方で、撥インク処理された有機バンク層221の上面では、インク滴がはじかれて付着しない。従って、インク滴が所定の吐出位置からはずれて有機バンク層221の上面に吐出されたとしても、該上面がインク滴で濡れることがなく、弾かれたインク滴が絶縁層(親水性制御層)25の開口部25a内に転がり込むものとされている。

【0051】

続いて図8(l)に示す発光層(有機EL層)60(図3も参照)を形成するべく発光層形成工程が行われる。発光層形成工程では、上記と同様なインクジェット法により、発光層用材料を含む組成物インクを正孔注入/輸送層70上に吐出した後に乾燥処理及び熱処理して、有機バンク層221に形成された開口部221a内に発光層60を形成する。

【0052】

発光層形成工程では、正孔注入/輸送層70の再溶解を防止するために、発光層形成の際に用いる組成物インクの溶媒として、正孔注入/輸送層70に対して不溶な無極性溶媒を用いる。しかし、その一方で正孔注入/輸送層70は、無極性溶媒に対する濡れ性が低いため、無極性溶媒を含む組成物インクを正孔注入/輸送層70上に吐出しても、正孔注入/輸送層70により発光層用の組成物インクが弾かれ、正孔注入/輸送層70と発光層60とを密着させることができなくなる場合がある他、発光層60を均一に塗布できない惧れがある。そこで、無極性溶媒に対する正孔注入/輸送層70の表面の濡れ性を高めるために、発光層形成の前に表面改質工程を行うことが好ましい。その表面改質工程は、例えば上記無極性溶媒と同一溶媒又はこれに類する溶媒をインクジェット法、スピンコート法又はディップ法等により正孔注入/輸送層70上に塗布した後に乾燥することにより行うものとすることができる。なお、ここで用いる表面改質用溶媒としては、組成物インクの無極性溶媒と同一なものとして例えば、シクロヘキシルベンゼン、ジハイドロベンゾフラン、トリメチルベンゼン、テトラメチルベンゼン等を例示でき、組成物インクの無極性溶媒に類するものとしては、例えばトルエン、キシレン等を例示することができる。

【0053】

表面改質工程に続く上記インクジェット法による発光層形成工程としては、例えばインクジェットヘッド(図示略)に、青色(B)発光層の材料を含有する組成物インクを充填し、インクジェットヘッドの吐出ノズルを絶縁層(親水性制御層)25の開口部25a内に位置する正孔注入/輸送層70に対向させ、インクジェットヘッドと基材とを相対移動させながら、吐出ノズルから1滴当たりの液量が制御されたインク滴として吐出し、このインク滴を正孔注入/輸送層70上に吐出する。

【0054】

発光層60を構成する発光材料としては、フルオレン系高分子や、(ポリ)パラフェニレンビニレン誘導体、ポリフェニレン誘導体、ポリフルオレン誘導体、ポリビニルカルバゾール、ポリチオフェン誘導体、ペリレン系色素、クマリン系色素、ローダミン系色素、その他ベンゼン誘導体に可溶な低分子有機EL材料、高分子有機EL材料等も用いることができる。例えば、ルブレン、ペリレン、9,10−ジフェニルアントラセン、テトラフェニルブタジエン、ナイルレッド、クマリン6、キナクリドン等を用いることができる。一方、無極性溶媒としては、正孔注入/輸送層70に対して不溶なものが好ましく、例えば、シクロヘキシルベンゼン、ジハイドロベンゾフラン、トリメチルベンゼン、テトラメチルベンゼン等を用いることができる。

【0055】

吐出されたインク滴は、正孔注入/輸送層70上に広がって親水性制御層25の開口部25a内に満たされる。その一方で、撥インク処理された有機バンク層221上面では、インク滴が弾かれて付着しない。これにより、インク滴が所定の吐出位置からはずれて有機バンク層221上面に吐出されたとしても、該上面がインク滴で濡れることがなく、インク滴が上記親水性制御層25の開口部25a内に転がり込み、さらに有機バンク層221の開口部221a内に吐出・充填される。続いて、吐出後のインク滴を乾燥処理することにより組成物インクに含まれる無極性溶媒を蒸発させ、青色発光層(発光層60)が形成される。

【0056】

さらに、青色発光層の場合と同様にして、例えば赤色発光層(発光層60)を形成し、最後に緑色発光層(発光層60)を形成する。なお、各色の発光層60の形成順序は、発光層材料の構成成分数が少ないものから順に行うことが好ましい。成分数の多い色の発光層を先に形成すると、後から形成した別の色の発光層の組成物インクから蒸発した溶媒蒸気によって、先に形成した発光層が再溶解して成分分離を起こす惧れがあるので好ましくない。

なお、正孔注入/輸送層、発光層をそれぞれインクジェットプロセスにより形成するが、この際、インクジェットヘッドは発光ドット間のピッチにより傾き方向を制御している。すなわち、インクジェットヘッドに形成されているノズルのピッチと、発光ドットのピッチとは必ずしも一致しないため、ヘッドの傾けて配置することにより発光ドットのピッチに合うように調整するのである。

【0057】

続いて図8(m)に示す陰極222、50を形成するべく陰極形成工程が行われる。該陰極形成工程においては、発光層60及び有機バンク層221の全面に、陰極222、50となる下部陰極層及び上部陰極層を順次積層する。下部陰極層は仕事関数が上部陰極層よりも相対的に小さいもので構成することが好ましく、例えばフッ化リチウム、カルシウム、アルミニウム等を用いることができる。また、上部陰極層は下部陰極層を保護するもので、下部陰極層よりも仕事関数が相対的に大きいもので構成することが好ましく、製法としては例えば蒸着法、スパッタ法、CVD法等で形成することが好ましく、特に蒸着法で形成することが、発光層60の熱による損傷を防止できる点で好ましい。なお、ここでは図8の222がカルシウム(下部陰極層)、50がアルミニウム(上部陰極層)に対応する。更に、Al以外にもAg膜、Mg/Ag積層膜等を用いることができる。

【0058】

最後に、図8(m)に示す封止基板30を形成するべく封止工程を行う。この封止工程では、封止基板30の内側に乾燥剤45を挿入しつつ、該封止基板30とアクティブマトリクス基板20とを接着剤40にて封止する。なお、この封止工程は、窒素、アルゴン、ヘリウム等の不活性ガス雰囲気で行うことが好ましい。大気中で行うと、反射層50にピンホール等の欠陥が生じていた場合に、この欠陥部分から水や酸素等が陰極222に侵入して陰極222が酸化される惧れがある。

【0059】

以上のような製造プロセスにより、図1〜図3に示すような表示装置101が得られる。

【0060】

以下、本発明の表示装置を備えた電子機器について幾つかの例を示す。

図9(a)は、携帯電話を示す斜視図である。1000は携帯電話本体を示し、そのうちの1001は本発明の表示装置を用いた表示部である。

図9(b)は、腕時計型電子機器を示す図である。1100は時計本体を示す斜視図である。1101は本発明の表示装置を用いた表示部である。

【0061】

図9(c)は、ワープロ、パソコン等の携帯型情報処理装置を示す図である。1200は情報処理装置を示し、1202はキーボード等の入力部、1206は本発明の表示装置を用いた表示部、1204は情報処理装置本体を示す。各々の電子機器は電池により駆動される電子機器であるので、本発明の構成を採用することで、安定した電力供給を実現することが可能となる。また、これら電子機器は小型のものが多いなか、本発明の表示装置を採用することで機器全体が小型であるにも拘らず比較的大きな表示領域を確保することが可能となる。

【0062】

本発明の表示装置によると、基板上において表示を行うことが不可能な領域(駆動制御信号導通部とダミー画素領域)を相殺させ、該基板上の表示不可能な領域の増大を低減可能となり、有効な表示領域を増大することが可能となる。さらに、駆動制御信号導通部を隔壁部と重畳配置したため、陰極層と駆動制御信号導通部との間の距離が凹状区画部と重畳配置した場合に比して相対的に大きくなるため、陰極層と駆動制御信号導通部との間のキャパシタンスが小さくなり、該キャパシタンスによる駆動制御信号への外的影響、具体的にはパルス信号の波形鈍り等の発生が低減される。

【符号の説明】

【0063】

20…アクティブマトリクス基板、23…陽極層、24…画素用TFT(スイッチング手段)、60…有機EL層(発光層、表示本体層)、80…走査線駆動回路(作動制御手段)、90…データ線駆動回路(作動制御手段)、111…実画素部、112…ダミー画素部、221…バンク部、221a…開口部、222…陰極層、320…走査線側駆動制御信号導通部、350…データ線側駆動制御信号導通部。

【特許請求の範囲】

【請求項1】

基板上に、表示に寄与する表示領域と、表示に寄与しない非表示領域とを含むとともに、該表示領域及び非表示領域には、隔壁部と該隔壁部により区画形成された凹状区画領域とが所定のマトリクスパターンで配列され、前記表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも第1電極層と、表示若しくは非表示を切り換え可能な物質を含む表示主体層と、第2電極層とを含み、

前記非表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも前記表示主体層と、第2電極層とを含み、

前記基板上には、前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、該スイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動制御信号が導通する駆動制御信号導通部とが設けられ、

前記駆動制御信号導通部が、少なくとも前記非表示領域に配置された部分を含み、前記基板を平面視した場合に、前記隔壁部と重畳する部分を含むように配置されていることを特徴とする表示装置。

【請求項2】

前記基板上には、前記作動制御手段を駆動させるための駆動電流を供給する駆動電圧導通部が設けられ、該駆動電圧導通部及び前記駆動制御信号導通部と前記第2電極層との間には絶縁層が形成され、前記駆動制御信号導通部は前記駆動電圧導通部と比して前記第2電極側から遠い絶縁層領域に形成されていることを特徴とする請求項1に記載の表示装置。

【請求項3】

前記非表示領域は、前記基板と前記表示主体層との間に位置する第1電極層を備え、さらに該第1電極層と前記第2電極層との間の導通を遮る遮蔽用絶縁層を備えることを特徴とする請求項1又は2に記載の表示装置。

【請求項4】

前記遮蔽用絶縁層の表層面は、前記隔壁部の表層面と比して相対的に前記表示主体層との親和性が高い材質にて構成されていることを特徴とする請求項3に記載の表示装置。

【請求項5】

前記基板上には、複数の走査線及び複数のデータ線が交差するように形成されてなり、前記スイッチング手段が該走査線とデータ線との交点に対応して形成されてなり、前記作動制御手段が前記データ線を導通する信号に関する制御を行うデータ制御手段を含むことを特徴とする請求項1ないし4のいずれか1項に記載の表示装置。

【請求項6】

前記基板上には、複数の走査線及び複数のデータ線が交差するように形成されてなり、前記スイッチング手段が該走査線とデータ線との交点に対応して形成されてなり、前記作動制御手段が前記走査線を導通する信号に関する制御を行う走査制御手段を含むことを特徴とする請求項1ないし5のいずれか1項に記載の表示装置。

【請求項7】

前記基板上には、複数の検査線が形成されるとともに、前記スイッチング手段が該検査線に接続され、前記作動制御手段が前記検査線を導通する信号に関する制御を行う検査制御手段を含むことを特徴とする請求項1ないし6のいずれか1項に記載の表示装置。

【請求項8】

前記表示主体層は有機EL物質を具備してなることを特徴とする請求項1ないし7のいずれか1項に記載の表示装置。

【請求項9】

隔壁部によって区画形成された複数の凹状領域が形成されてなり、前記複数の凹状領域には、表示領域と前記表示領域に隣接して形成されてなる非表示領域とが形成されてなり、

前記凹状領域には少なくとも発光層が形成されてなり、前記発光層の一方の面側には第1の電極層が形成されてなり、他方の面側には第2の電極層が形成されてなる表示装置であって、

前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、そのスイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動電流を供給する駆動電圧導通部とが設けられ、

前記駆動制御信号導通部が、前記隔壁部と平面的に重なるように配置されてなることを特徴とする表示装置。

【請求項10】

表示領域と、前記表示領域に隣接して形成されてなる非表示領域と、に発光層が形成されてなり、前記発光層の一方の面側には第1の電極層が形成されてなり、他方の面側には第2の電極層が形成なる表示装置であって、

前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、該スイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動電流を供給する駆動電圧導通部とが設けられ、

前記駆動制御信号導通部が、少なくとも前記非表示領域と重なるように配置されてなることを特徴とする表示装置。

【請求項11】

前記表示領域に形成されてなる画素電極と同一材料のパターンが前記非表示領域に形成されてなり、前記駆動制御信号導通部が前記パターンと重ならないように配置されてなることを特徴とする請求項10に記載の表示装置。

【請求項12】

請求項1ないし11のいずれか1項に記載の表示装置を備えたことを特徴とする電子機器。

【請求項1】

基板上に、表示に寄与する表示領域と、表示に寄与しない非表示領域とを含むとともに、該表示領域及び非表示領域には、隔壁部と該隔壁部により区画形成された凹状区画領域とが所定のマトリクスパターンで配列され、前記表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも第1電極層と、表示若しくは非表示を切り換え可能な物質を含む表示主体層と、第2電極層とを含み、

前記非表示領域は、前記凹状区画領域の凹状底部に前記基板側から少なくとも前記表示主体層と、第2電極層とを含み、

前記基板上には、前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、該スイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動制御信号が導通する駆動制御信号導通部とが設けられ、

前記駆動制御信号導通部が、少なくとも前記非表示領域に配置された部分を含み、前記基板を平面視した場合に、前記隔壁部と重畳する部分を含むように配置されていることを特徴とする表示装置。

【請求項2】

前記基板上には、前記作動制御手段を駆動させるための駆動電流を供給する駆動電圧導通部が設けられ、該駆動電圧導通部及び前記駆動制御信号導通部と前記第2電極層との間には絶縁層が形成され、前記駆動制御信号導通部は前記駆動電圧導通部と比して前記第2電極側から遠い絶縁層領域に形成されていることを特徴とする請求項1に記載の表示装置。

【請求項3】

前記非表示領域は、前記基板と前記表示主体層との間に位置する第1電極層を備え、さらに該第1電極層と前記第2電極層との間の導通を遮る遮蔽用絶縁層を備えることを特徴とする請求項1又は2に記載の表示装置。

【請求項4】

前記遮蔽用絶縁層の表層面は、前記隔壁部の表層面と比して相対的に前記表示主体層との親和性が高い材質にて構成されていることを特徴とする請求項3に記載の表示装置。

【請求項5】

前記基板上には、複数の走査線及び複数のデータ線が交差するように形成されてなり、前記スイッチング手段が該走査線とデータ線との交点に対応して形成されてなり、前記作動制御手段が前記データ線を導通する信号に関する制御を行うデータ制御手段を含むことを特徴とする請求項1ないし4のいずれか1項に記載の表示装置。

【請求項6】

前記基板上には、複数の走査線及び複数のデータ線が交差するように形成されてなり、前記スイッチング手段が該走査線とデータ線との交点に対応して形成されてなり、前記作動制御手段が前記走査線を導通する信号に関する制御を行う走査制御手段を含むことを特徴とする請求項1ないし5のいずれか1項に記載の表示装置。

【請求項7】

前記基板上には、複数の検査線が形成されるとともに、前記スイッチング手段が該検査線に接続され、前記作動制御手段が前記検査線を導通する信号に関する制御を行う検査制御手段を含むことを特徴とする請求項1ないし6のいずれか1項に記載の表示装置。

【請求項8】

前記表示主体層は有機EL物質を具備してなることを特徴とする請求項1ないし7のいずれか1項に記載の表示装置。

【請求項9】

隔壁部によって区画形成された複数の凹状領域が形成されてなり、前記複数の凹状領域には、表示領域と前記表示領域に隣接して形成されてなる非表示領域とが形成されてなり、

前記凹状領域には少なくとも発光層が形成されてなり、前記発光層の一方の面側には第1の電極層が形成されてなり、他方の面側には第2の電極層が形成されてなる表示装置であって、

前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、そのスイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動電流を供給する駆動電圧導通部とが設けられ、

前記駆動制御信号導通部が、前記隔壁部と平面的に重なるように配置されてなることを特徴とする表示装置。

【請求項10】

表示領域と、前記表示領域に隣接して形成されてなる非表示領域と、に発光層が形成されてなり、前記発光層の一方の面側には第1の電極層が形成されてなり、他方の面側には第2の電極層が形成なる表示装置であって、

前記第1電極層に接続され、該第1電極層への通電制御を行うスイッチング手段と、該スイッチング手段に接続され、該スイッチング手段の作動を制御する作動制御手段と、該作動制御手段を駆動させるための駆動電流を供給する駆動電圧導通部とが設けられ、

前記駆動制御信号導通部が、少なくとも前記非表示領域と重なるように配置されてなることを特徴とする表示装置。

【請求項11】

前記表示領域に形成されてなる画素電極と同一材料のパターンが前記非表示領域に形成されてなり、前記駆動制御信号導通部が前記パターンと重ならないように配置されてなることを特徴とする請求項10に記載の表示装置。

【請求項12】

請求項1ないし11のいずれか1項に記載の表示装置を備えたことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−3286(P2012−3286A)

【公開日】平成24年1月5日(2012.1.5)

【国際特許分類】

【出願番号】特願2011−204385(P2011−204385)

【出願日】平成23年9月20日(2011.9.20)

【分割の表示】特願2009−75713(P2009−75713)の分割

【原出願日】平成21年3月26日(2009.3.26)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成24年1月5日(2012.1.5)

【国際特許分類】

【出願日】平成23年9月20日(2011.9.20)

【分割の表示】特願2009−75713(P2009−75713)の分割

【原出願日】平成21年3月26日(2009.3.26)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]