表示装置

【課題】2つのコンタクト部を有する1つの導電層の面積を小さくすることができるようにする。

【解決手段】ELパネル100において、アノード電極78と駆動用トランジスタのソース電極75との接続部であるコンタクト部78cと、ソース電極75と多結晶シリコン膜74との接続部であるコンタクト部75cが、平面方向で同一の位置に配置されている。コンタクト部75cを形成しているソース電極75の上側の膜面は平坦面を有し、その平坦面上で、ソース電極75とアノード電極78がコンタクト部78cとして接続されている。また、コンタクト部78cを形成している同一平面上の、ソース電極75側の平坦面の開口幅L1は、アノード電極78の平坦面の開口幅L2よりも大となっている。これにより、レイアウト面積を小さくし、かつ、コンタクト不良を防止することができる。本発明は、例えば、ELパネルを用いた表示装置に適用できる。

【解決手段】ELパネル100において、アノード電極78と駆動用トランジスタのソース電極75との接続部であるコンタクト部78cと、ソース電極75と多結晶シリコン膜74との接続部であるコンタクト部75cが、平面方向で同一の位置に配置されている。コンタクト部75cを形成しているソース電極75の上側の膜面は平坦面を有し、その平坦面上で、ソース電極75とアノード電極78がコンタクト部78cとして接続されている。また、コンタクト部78cを形成している同一平面上の、ソース電極75側の平坦面の開口幅L1は、アノード電極78の平坦面の開口幅L2よりも大となっている。これにより、レイアウト面積を小さくし、かつ、コンタクト不良を防止することができる。本発明は、例えば、ELパネルを用いた表示装置に適用できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置に関し、特に、2つのコンタクト部を有する1つの導電層の面積を小さくすることができるようにする表示装置に関する。

【背景技術】

【0002】

発光素子として有機EL(ELectro Luminescent)デバイスを用いた平面自発光型のパネル(ELパネル)の開発が近年盛んになっている。有機ELデバイスは、ダイオード特性を有し、有機薄膜に電界をかけると発光する現象を利用したデバイスである。有機ELデバイスは、印加電圧が10V以下で駆動するため低消費電力であり、自ら光を発する自発光素子であるため、照明部材を必要とせず軽量化及び薄型化が容易であるという特長を有する。また、有機ELデバイスの応答速度は数μs程度と非常に高速であるので、ELパネルでは動画表示時の残像が発生しないという利点がある。

【0003】

ELパネルの中でも、とりわけ駆動素子として薄膜トランジスタ(TFT)を各画素に集積形成したアクティブマトリクス型のパネルの開発が盛んである。アクティブマトリクス型ELパネルは、例えば、特許文献1乃至5に記載されている。

【0004】

近年のアクティブマトリクス型ELパネルにおいては、液晶パネルと同様に、高精細化が望まれている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−255856号公報

【特許文献2】特開2003−271095号公報

【特許文献3】特開2004−133240号公報

【特許文献4】特開2004−029791号公報

【特許文献5】特開2004−093682号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来、アクティブマトリクス型ELパネルにおいて、1つの導電層で他の2つの導電層とコンタクトをとる必要がある場合、2つのコンタクト部は、コンタクト不良を防止するため、平面方向で離れた位置に配置されていた。そのため、2つのコンタクト部を有する導電層の面積が大きくなり、1画素の領域を有効に利用することができなかった。

【0007】

本発明は、このような状況に鑑みてなされたものであり、2つのコンタクト部を有する1つの導電層の面積を小さくすることができるようにするものである。

【課題を解決するための手段】

【0008】

本発明の一側面の表示装置は、自発光素子により発光する画素が行列状に複数配置されているパネルを有し、前記パネルは、第1乃至第3の導電層が支持基板上に順に積層されており、前記第1の導電層と第2の導電層の第1のコンタクト部と、前記第2の導電層と前記第3の導電層の第2のコンタクト部が、平面方向で同一の位置に配置されている。

【0009】

本発明の一側面においては、自発光素子により発光する画素が行列状に複数配置されているパネルに含まれる第1乃至第3の導電層が支持基板上に順に積層されており、第1の導電層と第2の導電層の第1のコンタクト部と、第2の導電層と第3の導電層の第2のコンタクト部が、平面方向で同一の位置に配置される。

【発明の効果】

【0010】

本発明の一側面によれば、2つのコンタクト部を有する1つの導電層の面積を小さくすることができる。

【図面の簡単な説明】

【0011】

【図1】本発明を適用した表示装置の一実施の形態の構成例を示すブロック図である。

【図2】ELパネルの各画素の色の配列を示す図である。

【図3】画素の等価回路の構成を示したブロック図である。

【図4】画素の動作を説明するタイミングチャートである。

【図5】従来のELパネルの駆動トランジスタ部分の断面図である。

【図6】段切れを説明する図である。

【図7】従来のELパネルを構成する画素の平面図である。

【図8】図1のELパネルの第1の実施の形態の画素の駆動トランジスタ部分の断面図である。

【図9】図1のELパネルの第2の実施の形態の画素の駆動トランジスタ部分の断面図である。

【図10】図9のコンタクト部の上面図である。

【図11】図1のELパネルの平面図である。

【発明を実施するための形態】

【0012】

[表示装置の構成]

図1は、本発明を適用した表示装置の一実施の形態の構成例を示すブロック図である。

【0013】

図1の表示装置1は、例えば、テレビジョン受像機などであり、入力された映像信号に対応する映像をELパネル100に表示する。ELパネル100は、自発光素子としての有機EL(ELectro Luminescent)デバイスを用いたパネルである。ELパネル100は、ソースドライバおよびゲートドライバとからなるドライバIC(Integrated Circuit)を含むパネルモジュールとして表示装置1に組み込まれている。また、表示装置1は、図示せぬ電源回路、画像LSI(Large Scale Integration)なども有している。なお、表示装置1のELパネル100は、携帯電話機、デジタルスチルカメラ、デジタルビデオカメラ、プリンタ等の表示部としても利用することができる。

【0014】

ELパネル100は、複数の画素101を有する画素アレイ部102、水平セレクタ(HSEL)103、ライトスキャナ(WSCN)104、および電源スキャナ(DSCN)105を含むように構成されている。

【0015】

画素アレイ部102には、N×M個(N,Mは相互に独立した1以上の整数値)の画素101−(1,1)乃至101−(N,M)が行列状に配置されて構成されている。なお、図1では、紙面の制約上、画素101−(1,1)乃至101−(N,M)の一部のみが示されている。

【0016】

また、ELパネル100は、M本の走査線WSL10−1乃至10−M、M本の電源線DSL10−1乃至10−M、およびN本の映像信号線DTL10−1乃至10−Nも有する。

【0017】

なお、以下において、走査線WSL10−1乃至10−Mそれぞれを特に区別する必要がない場合、単に、走査線WSL10と称する。また、映像信号線DTL10−1乃至10−Nそれぞれを特に区別する必要がない場合、単に、映像信号線DTL10と称する。画素101−(1,1)乃至101−(N,M)および電源線DSL10−1乃至10−Mについても同様に、画素101および電源線DSL10と称する。

【0018】

水平セレクタ103、ライトスキャナ104、および電源スキャナ105は、画素アレイ部102を駆動する駆動部として動作する。

【0019】

画素101−(1,1)乃至101−(N,M)のうちの第1行目の画素101−(1,1)乃至101−(N,1)は、走査線WSL10−1でライトスキャナ104と、電源線DSL10−1で電源スキャナ105とそれぞれ接続されている。また、画素101−(1,1)乃至101−(N,M)のうちの第M行目の画素101−(1,M)乃至101−(N,M)は、走査線WSL10−Mでライトスキャナ104と、電源線DSL10−Mで電源スキャナ105とそれぞれ接続されている。画素101−(1,1)乃至101−(N,M)の行方向に並ぶその他の画素101についても同様の接続となっている。

【0020】

また、画素101−(1,1)乃至101−(N,M)のうちの第1列目の画素101−(1,1)乃至101−(1,M)は、映像信号線DTL10−1で水平セレクタ103と接続されている。画素101−(1,1)乃至101−(N,M)のうちの第N列目の画素101−(N,1)乃至101−(N,M)は、映像信号線DTL10−Nで水平セレクタ103と接続されている。画素101−(1,1)乃至101−(N,M)の列方向に並ぶその他の画素101についても同様の接続となっている。

【0021】

ライトスキャナ104は、走査線WSL10−1乃至10−Mに水平周期(1H)で順次制御信号を供給して画素101を行単位で線順次走査する。電源スキャナ105は、線順次走査に合わせて電源線DSL10−1乃至10−Mに第1電位Vccまたは第2電位Vss(図4)の電源電圧を供給する。水平セレクタ103は、線順次走査に合わせて各水平期間内(1H)で映像信号に対応する信号電位Vsigと基準電位Vofs(図4)とを切換えて列状の映像信号線DTL10−1乃至10−Mに供給する。

【0022】

[画素101の配列構成]

図2は、ELパネル100の各画素101が発光する色の配列を示している。

【0023】

なお、図2では、走査線WSL10および電源線DSL10が画素101の下側から接続されている点が図1と異なる。走査線WSL10、電源線DSL10、および映像信号線DTL10が画素101とどの側面から接続されるかは、配線レイアウトに応じて適宜変更することができる。水平セレクタ103、ライトスキャナ104、および電源スキャナ105の画素アレイ部102に対する配置についても同様に、適宜変更することができる。

【0024】

画素アレイ部102の各画素101は、赤(R)、緑(G)、または青(B)のいずれかの色を発光する。そして、各色は、例えば、行方向には赤、緑、青の順となり、列方向には同一の色となるように配列されている。従って、各画素101は、いわゆる副画素(サブピクセル)に相当し、行方向(図面左右方向)に並ぶ赤、緑、および青の3つの画素101で表示単位としての1画素が構成される。なお、ELパネル100の色の配列が図2に示した配列に限定されるものではない。

【0025】

[画素101の詳細回路構成]

図3は、ELパネル100に含まれるN×M個の画素101のうちの1つの画素101を拡大することにより、画素101の等価回路(画素回路)の構成を示したブロック図である。

【0026】

なお、図3の画素101が、画素101−(n,m)(n=1,2,・・・,N,m=1,2,・・・,M)であるとすると、走査線WSL10、映像信号線DTL10、および電源線DSL10のそれぞれは、次のようになる。即ち、図3の走査線WSL10、映像信号線DTL10、および電源線DSL10は、画素101−(n,m)に対応する走査線WSL10−n、映像信号線DTL10−n、および電源線DSL10−mとなる。

【0027】

図3の画素101は、サンプリング用トランジスタ31、駆動用トランジスタ32、蓄積容量33、発光素子34、および補助容量35を有する。また、図3では、発光素子34が有する容量成分も、発光素子容量34Bとして示してある。ここで、蓄積容量33、発光素子容量34B、および補助容量35の容量値は、それぞれ、Cs,Coled、およびCsubである。

【0028】

サンプリング用トランジスタ31のゲートは、走査線WSL10と接続され、サンプリング用トランジスタ31のドレインは、映像信号線DTL10と接続される。また、サンプリング用トランジスタ31のソースは、駆動用トランジスタ32のゲートと接続されている。

【0029】

駆動用トランジスタ32のソース及びドレインの一方は、発光素子34のアノードに接続され、他方が、電源線DSL10に接続される。蓄積容量33は、駆動用トランジスタ32のゲートと発光素子34のアノードに接続されている。また、発光素子34のカソードは所定の電位Vcatに設定されている配線36に接続されている。この電位VcatはGNDレベルであり、従って、配線36は接地配線である。

【0030】

補助容量35は、発光素子34の容量成分、即ち発光素子容量34Bを補うために設けられ、発光素子34と並列に接続されている。即ち、補助容量35の一方の電極は、発光素子34のアノード側に接続され、他方の電極は、発光素子34のカソード側と接続される。このように補助容量35を設け、所定の電位を保持させることにより、駆動用トランジスタ32の入力ゲインを向上させることができる。ここで、駆動用トランジスタ32の入力ゲインとは、図4を参照して後述する書き込み+移動度補正期間T5における駆動用トランジスタ32のゲート電位Vgの上昇量に対するソース電位Vsの上昇量の比率である。

【0031】

サンプリング用トランジスタ31および駆動用トランジスタ32は、いずれもNチャネル型トランジスタである。よって、サンプリング用トランジスタ31および駆動用トランジスタ32は、低温ポリシリコンよりも安価に作成できるアモルファスシリコンで作成することができる。これにより、画素回路の製造コストをより安価にすることができる。勿論、サンプリング用トランジスタ31および駆動用トランジスタ32は、低温ポリシリコンや単結晶シリコンで作成しても構わない。

【0032】

発光素子34は、有機EL素子で構成される。有機EL素子はダイオード特性を有する電流発光素子である。よって、発光素子34は、供給される電流値Idsに応じた階調の発光を行う。

【0033】

以上のように構成される画素101において、サンプリング用トランジスタ31が、走査線WSL10からの制御信号に応じてオン(導通)し、映像信号線DTL10を介して階調に応じた信号電位Vsigの映像信号をサンプリングする。蓄積容量33は、映像信号線DTL10を介して水平セレクタ103から供給された電荷を蓄積して保持する。駆動用トランジスタ32は、第1電位Vccにある電源線DSL10から電流の供給を受け、蓄積容量33に保持された信号電位Vsigに応じて駆動電流Idsを発光素子34に流す(供給する)。発光素子34に所定の駆動電流Idsが流れることにより、画素101が発光する。

【0034】

画素101は、閾値補正機能を有する。閾値補正機能とは、駆動用トランジスタ32の閾値電圧Vthに相当する電圧を蓄積容量33に保持させる機能である。閾値補正機能を発揮させることで、ELパネル100の画素毎のばらつきの原因となる駆動用トランジスタ32の閾値電圧Vthの影響をキャンセルすることができる。

【0035】

また、画素101は、上述した閾値補正機能に加え、移動度補正機能も有する。移動度補正機能とは、蓄積容量33に信号電位Vsigを保持する際、駆動用トランジスタ32の移動度μに対する補正を信号電位Vsigに加える機能である。

【0036】

さらに、画素101は、ブートストラップ機能も備えている。ブートストラップ機能とは、駆動用トランジスタ32のソース電位Vsの変動にゲート電位Vgを連動させる機能である。ブートストラップ機能の発揮により、駆動用トランジスタ32のゲートとソース間の電圧Vgsを一定に維持することが出来る。

【0037】

[画素101の動作の説明]

図4は、画素101の動作を説明するタイミングチャートである。

【0038】

図4は、同一の時間軸(図面横方向)に対する走査線WSL10、電源線DSL10、および映像信号線DTL10の電位変化と、それに対応する駆動用トランジスタ32のゲート電位Vg及びソース電位Vsの変化を示している。

【0039】

図4において、時刻t1までの期間は、前の水平期間(1H)の発光がなされている発光期間T1である。

【0040】

発光期間T1が終了した時刻t1から時刻t3までは、駆動用トランジスタ32のゲート電位Vg及びソース電位Vsを初期化することで閾値電圧補正動作の準備を行う閾値補正準備期間T2である。

【0041】

閾値補正準備期間T2では、時刻t1において、電源スキャナ14が、電源線DSLの電位を高電位である第1電位Vccから低電位である第2電位Vssに切換える。ここで、発光素子34の閾値電圧をVthelとする。このとき、第2電位Vssを、Vss<Vthel+Vcatとすると、駆動用トランジスタ32のソース電位Vsが第2電位Vssにほぼ等しくなるために、発光素子34は逆バイアス状態となって消光する。

【0042】

次に、時刻t2において、ライトスキャナ13が、走査線WSLの電位を高電位に切換え、サンプリング用トランジスタ31をオンさせる。これにより、駆動用トランジスタ32のゲート電位Vgが基準電位Vofsにリセットされ、且つ、ソース電位Vsが映像信号線DTLの第2電位Vssにリセットされる。

【0043】

このとき、駆動用トランジスタ32のゲート−ソース間電圧Vgsは、(Vofs−Vss)となる。ここで、(Vofs−Vss)が駆動用トランジスタ32の閾値電圧Vthよりも大きくないと、次の閾値補正処理を行うことができない。そのため、(Vofs−Vss)>Vthの関係を満たすように、基準電位Vofsおよび第2電位Vssが設定されている。

【0044】

時刻t3から時刻t4までは、閾値補正動作を行う閾値補正期間T3である。閾値補正期間T3では、時刻t3において、電源スキャナ14により、電源線DSLの電位が高電位Vccに切換えられ、閾値電圧Vthに相当する電圧が、駆動用トランジスタ32のゲートとソースとの間に接続された蓄積容量33に書き込まれる。即ち、電源線DSLの電位が高電位Vccに切換えられることにより駆動用トランジスタ32のソース電位Vsが上昇し、閾値補正期間T3の時刻t4までに、駆動用トランジスタ32のゲート‐ソース間電圧Vgsが、閾値電圧Vthに等しくなる。

【0045】

なお、閾値補正期間T3では、発光素子34がカットオフ状態となるようにカソード電位Vcatが設定されているため、駆動用トランジスタ32のドレイン−ソース間電流Idsは蓄積容量33側に流れ、発光素子34側には流れない。

【0046】

時刻t4から時刻t6までの書き込み+移動度補正準備期間T4では、走査線WSLの電位が高電位から低電位に一旦切換えられる。このとき、サンプリング用トランジスタ31がオフされるため、駆動用トランジスタ32のゲートがフローティング状態となる。しかし、駆動用トランジスタ32のゲート‐ソース間電圧Vgsが、閾値電圧Vthに等しいため、駆動用トランジスタ32はカットオフ状態にある。従って、駆動用トランジスタ32にドレイン−ソース間電流Idsは流れない。

【0047】

そして、時刻t4から時刻t6の間の時刻t5において、水平セレクタ12が、映像信号線DTLの電位を基準電位Vofsから階調に応じた信号電位Vsigに切換える。

【0048】

その後、時刻t6から時刻t7までの書き込み+移動度補正期間T5において、映像信号の書き込みと移動度補正動作が同時に行われる。即ち、時刻t6から時刻t7までの間、走査線WSLの電位が高電位に設定され、これにより、階調に応じた信号電位Vsigが閾値電圧Vthに足し込まれる形で蓄積容量33に書き込まれる。また、移動度補正用の電圧ΔVが蓄積容量33に保持された電圧から差し引かれる。

【0049】

ここで、書き込み+移動度補正期間T5終了後の時刻t7における駆動用トランジスタ32のゲート‐ソース間電圧Vgsは(Vsig+Vth−ΔV)である。

【0050】

書き込み+移動度補正期間T5終了後の時刻t7において、走査線WSLの電位が低電位に戻される。これにより、駆動用トランジスタ32のゲートは、映像信号線DTLから切り離されるため、フローティング状態となる。駆動用トランジスタ32のゲートがフローティング状態にあるときは、駆動用トランジスタ32のゲート−ソース間に蓄積容量33が接続されていることにより、駆動用トランジスタ32のソース電位Vsの変動に連動してゲート電位Vgも変動する。このように、駆動用トランジスタ32のゲート電位Vgが、ソース電位Vsの変動に連動して変動する動作が、蓄積容量33によるブートストラップ動作である。

【0051】

時刻t7以降、駆動用トランジスタ32のゲートがフローティング状態になり、駆動用トランジスタ32のドレイン−ソース間電流Idsが駆動電流として発光素子34に流れ始めることにより、駆動電流Idsに応じて発光素子34のアノード電位が上昇する。また、ブートストラップ動作により、駆動用トランジスタ32のゲート電位Vgも同様に上昇する。即ち、映像信号線DTLの信号電位Vsigに応じて、駆動用トランジスタ32のゲート‐ソース間電圧Vgs=(Vsig+Vth−ΔV)を一定に維持したまま、駆動用トランジスタ32のゲート電位Vg及びソース電位Vsが上昇する。そして、発光素子34のアノード電位が(Vthel+Vcat)を超えたとき、発光素子34が発光を開始する。

【0052】

書き込み+移動度補正期間T5終了後の時刻t7時点で、閾値電圧Vthと移動度μの補正が終了しているため、発光素子34の発光輝度は駆動用トランジスタ32の閾値電圧Vthや移動度μのばらつきの影響を受けることがない。即ち、発光素子34は、駆動用トランジスタ32の閾値電圧Vthや移動度μのばらつきの影響を受けずに、信号電位Vsigに応じた各画素同一の発光輝度で発光する。

【0053】

そして、時刻t7から所定時間経過後の時刻t8において、映像信号線DTLの電位が、信号電位Vsigから基準電位Vofsに落とされる。

【0054】

以上のようにして、ELパネル100の各画素101では、駆動用トランジスタ32の閾値電圧Vthや移動度μのばらつきの影響を受けることがなく、発光素子34を発光させることができる。従って、ELパネル100を用いた表示装置1では、高品位な画質を得ることができる。

【0055】

次に、ELパネル100の画素101の薄膜トランジスタ(TFT)部分のパターン構造について説明するが、その前に、従来の薄膜トランジスタ部分のパターン構造について説明する。

【0056】

なお、ELパネル100の画素101の薄膜トランジスタ部分のパターン構造を、従来の薄膜トランジスタ部分のパターン構造と比較すると、いくつかの膜の配置場所が異なる。換言すれば、基板上に形成される膜の構成自体に差異はないので、図5および図6に示す従来の薄膜トランジスタ部分のパターン構造においては、ELパネル100の画素101における場合と同様の符号を付して説明する。

【0057】

[従来の画素101の駆動用トランジスタ32部分の断面図]

図5は、従来のELパネル100Xにおける画素101の駆動用トランジスタ32部分の断面図である。

【0058】

ELパネル100Xでは、ガラス等の材料からなる支持基板71上に、駆動用トランジスタ32のゲート電極72が形成される。ゲート電極72の上側には、絶縁膜73を介してチャネル領域となる半導体層としての多結晶シリコン膜74が形成される。

【0059】

さらに多結晶シリコン膜74の上側には、ソース電極75およびドレイン電極76が形成される。ソース電極75は、コンタクト部75aで多結晶シリコン膜74と接続されている。また、ドレイン電極76は、コンタクト部76aで多結晶シリコン膜74と接続されている。コンタクト部75aおよび76a以外のソース電極75と多結晶シリコン膜74との間、およびドレイン電極76と多結晶シリコン膜74との間の層は、絶縁膜73で覆われている。

【0060】

ソース電極75およびドレイン電極76の上には、平坦化膜77が積層され、平坦化膜77の上にアノード電極(反射電極)78が形成される。アノード電極78は、コンタクト部78aでソース電極75と接続されている。

【0061】

アノード電極78の上側には、赤、緑、または青のいずれか所定の色に発光する発光層である有機EL層(図示せず)、有機EL層の上にカソード電極(図示せず)が形成される。

【0062】

[従来の問題]

従来は、図5に示されるように、アノード電極78とソース電極75の接続面であるコンタクト部78aと、ソース電極75と多結晶シリコン膜74との接続面であるコンタクト部75aが、平面方向で離れた位置に配置されていた。これは、導電層間を接続する傾斜部(以下、段差部という)の距離が長いと、段切れ等のコンタクト不良が発生する可能性が高くなるためである。段切れとは、図6に示されるように、段差部に形成される膜が薄くなり、断線することである。

【0063】

アノード電極78の材料には、例えば、アルミニウム(Al)や、銀(Ag)の薄膜の両面をITO膜等の透明導電膜で挟み込むように積層させた積層構造の膜が採用される。銀を用いた積層構造の膜は、アルミニウムよりも反射率が高くなるというメリットがある反面、材料の性質上、銀薄膜の段切れや透明導電膜の段切れが発生しやすくなる。銀薄膜および透明導電膜の段切れまたは成膜不良が発生した場合には、接続抵抗が大きくなったり、銀が腐食して良好なコンタクトを得ることができない。

【0064】

従来、このようなコンタクト不良を防止するため、コンタクト部78aとコンタクト部75aは、図5に示したように、平面方向で離れた位置に配置されていた。

【0065】

しかしながら、コンタクト部78aとコンタクト部75aとを平面方向で離れた位置に配置させることは、レイアウト面積が大きくなり、1画素の面積を小さくしようとした場合の障害となる。即ち、コンタクト部78aとコンタクト部75aとを平面方向で離れた位置に配置させることで、ELパネルの高精細化が困難となるという問題があった。また、1画素の面積を変える必要がない場合には、コンタクト部78aとコンタクト部75aを含むレイアウト面積が大きくなるために、他のレイアウト面積を小さくせざるを得ず、輝度の向上や省電力による駆動などの表示性能の低下を招いていた。

【0066】

[従来の画素101の平面図]

図7は、従来のELパネル100Xを構成する画素101の平面図である。

【0067】

以下、説明の便宜上、支持基板71に最も近く、図5の断面図において最も下の面に位置する、ゲート電極72を形成する金属層を下面金属層という。また、多結晶シリコン膜74を形成する半導体層をシリコン層、ソース電極75およびドレイン電極76を形成する金属層を中間金属層、アノード電極78を形成する金属層を上面金属層とそれぞれ称する。

【0068】

図7において、画素101を横断する走査線WSL10と電源線DSL10は、中間金属層で形成される。また、画素101を縦断する映像信号線DTL10は、走査線WSL10および電源線DSL10と交差しない部分については中間金属層で形成され、走査線WSL10および電源線DSL10と交差する部分については下面金属層で形成される。

【0069】

サンプリング用トランジスタ31に注目すると、サンプリング用トランジスタ31のドレイン電極およびソース電極は中間金属層で形成され、ゲート電極は下面金属層で形成される。そして、サンプリング用トランジスタ31のドレイン電極およびソース電極とゲート電極との間にシリコン層が形成される。シリコン層は、サンプリング用トランジスタ31のドレイン電極およびソース電極としての中間金属層と接続されている。

【0070】

駆動用トランジスタ32に注目すると、駆動用トランジスタ32のドレイン電極およびソース電極は中間金属層で形成され、ゲート電極は下面金属層で形成される。そして、駆動用トランジスタ32のドレイン電極およびソース電極とゲート電極との間にシリコン層が形成される。シリコン層は、駆動用トランジスタ32のドレイン電極およびソース電極としての中間金属層と接続されている。

【0071】

駆動用トランジスタ32のドレイン電極を形成する中間金属層は、コンタクト部76aにより、多結晶シリコン膜74としてのシリコン層と接続されている。駆動用トランジスタ32のソース電極を形成する中間金属層は、コンタクト部75aにより、多結晶シリコン膜74としてのシリコン層と接続されている。さらに、駆動用トランジスタ32のソース電極を形成する中間金属層は、コンタクト部78aにより、アノード電極78と接続されている。

【0072】

蓄積容量33は、下面金属層とシリコン層とを対向させることにより、構成されている。下面金属層で形成されている蓄積容量33の一方の電極は、中間金属層を介して、サンプリング用トランジスタ31のソース電極と接続されている。シリコン層で形成されている蓄積容量33の他方の電極は、コンタクト部75aにより、駆動用トランジスタ32のソース電極を形成する中間金属層と接続されている。駆動用トランジスタ32のソース電極を形成する中間金属層は、上述したようにアノード電極78と接続されているので、結局、シリコン層で形成されている蓄積容量33の他方の電極は、アノード電極78と接続されている。

【0073】

補助容量35も、下面金属層とシリコン層とを対向させることにより、構成されている。補助容量35の一方の電極は、蓄積容量33の他方の電極と共通のシリコン層で形成されているため、アノード電極78と接続されている。補助容量35の他方の電極は、コンタクト部79aにより中間金属層と接続され、中間金属層は、コンタクト部80aにより、アノード電極78と接続されている。ここで、コンタクト部80aを介して接続されるアノード電極78の電位は、電気的には、カソード電位Vcatとなっている。

【0074】

従来のELパネル100Xにおける画素101は、以上のように構成され、コンタクト部75aとコンタクト部78aが離れて位置している。このため、駆動用トランジスタ32のソース電極を形成し、2つのコンタクト部75aと78aを有する中間金属層の面積が大きくなっている。

【0075】

また、コンタクト部79aと80aが離れて位置しているので、コンタクト部79aと80aを有する中間金属層の面積も大きくなっている。

【0076】

従って、従来の配置構成では、ELパネルの高精細化が困難となる、または、輝度の向上や省電力による駆動などの機能低下を招いてしまうという問題があった。

【0077】

そこで、次に、本発明を適用したELパネル100で採用されている、画素101の第1の実施の形態について説明する。

【0078】

<第1の実施の形態>

[ELパネル100における画素101の駆動用トランジスタ32部分の断面図]

図8は、第1の実施の形態における画素101の駆動用トランジスタ32部分の断面図である。

【0079】

図8の画素101では、アノード電極78と駆動用トランジスタ32のソース電極75との接続部であるコンタクト部78bと、ソース電極75と多結晶シリコン膜74との接続部であるコンタクト部75bが、平面方向で同一の位置に配置されている。換言すれば、コンタクト部78bと75bが、上面からみたときの中心位置が同一(同軸)となるように配置されている。

【0080】

これにより、コンタクト部75bと78bを有する中間金属層の面積を小さくすることができ、1画素内の領域を有効に利用することができる。あるいは、1画素の面積を小さくすることができる。

【0081】

しかしながら、図8の配置は、段差部の上にさらに段差部が設けられる構成である。より詳しくは、ソース電極75が多結晶シリコン膜74と接続するための傾斜部に、アノード電極78が接続している。そのため、段切れが発生しやすいとも言える。

【0082】

<第2の実施の形態>

そこで、コンタクト不良の発生をより抑制する、ELパネル100の画素101の第2の実施の形態について説明する。

【0083】

[ELパネル100における画素101の駆動用トランジスタ32部分の断面図]

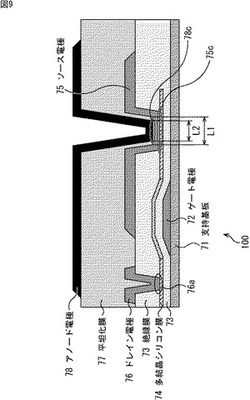

図9は、第2の実施の形態における画素101の駆動用トランジスタ32部分の断面図である。

【0084】

図9の画素101においても、アノード電極78と駆動用トランジスタ32のソース電極75との接続部であるコンタクト部78cと、ソース電極75と多結晶シリコン膜74との接続部であるコンタクト部75cが、平面方向で同一の位置に配置されている。

【0085】

さらに、図9の画素101では、コンタクト部75cを形成しているソース電極75の上側の膜面は平坦面を有し、その平坦面上で、ソース電極75とアノード電極78がコンタクト部78cとして接続されている。即ち、ソース電極75とアノード電極78は、面で接している。

【0086】

また、コンタクト部78cを形成している同一平面上の、ソース電極75側の平坦面の開口幅L1は、アノード電極78の平坦面の開口幅L2よりも大となっている。

【0087】

[コンタクト部78cの上面図]

図10は、コンタクト部78cの上面図である。

【0088】

コンタクト部78cは、図10に示されるように、四角形や円形とすることができる。この場合、ソース電極75側の平坦面も、コンタクト部78cと同一の形状(四角形や円形)とする。

【0089】

また、ソース電極75側の平坦面の開口幅L1は、アノード電極78の平坦面の開口幅L2よりも、例えば、1μmより大きくすることができる。

【0090】

以上のように、ソース電極75の上側の膜面は平坦面を設け、その平坦面上でアノード電極78とソース電極75が接続されるようにすることで、図5に示した従来のコンタクト部78aと同様の接続面が確保される。従って、コンタクト不良を防止することができる。

【0091】

[ELパネル100の平面図]

図11は、第2の実施の形態におけるELパネル100の平面図である。なお、図11は、コンタクト部75cおよび78cの形状を四角形とした例である。

【0092】

図11において、コンタクト部75cおよび78cは、駆動用トランジスタ32の図面下側の位置の1箇所に配置されている。これにより、図11では、図7における場合と比較すると、コンタクト部75cおよび78cを有する中間金属層の面積が小さくなっている。

【0093】

また、図7のコンタクト部79aと80aに対応する、コンタクト部79cと80cについても同様に、平面方向で同一位置に配置された結果、中間金属層の面積が小さくなっている。

【0094】

そして、コンタクト部75cおよび78cを有する中間金属層、および、コンタクト部79cと80cを有する中間金属層の面積がそれぞれ小さくなった結果、図11では、図7と比較して、補助容量35の面積を大きくすることが可能となっている。

【0095】

以上のように、ELパネル100によれば、シリコン層(第1の導電層)と中間金属層(第2の導電層)とのコンタクト部75cと、中間金属層と上面金属層(第3の導電層)のコンタクト部78cが平面方向で同一の位置に配置される。これにより、2つのコンタクト部(コンタクト部75cと78c)を有する中間金属層の面積を小さくすることができ、1画素の面積を小さくすることができる。また、1画素の面積を変える必要がない場合には、表示性能を向上させることができる。

【0096】

また、ELパネル100によれば、シリコン層(第1の導電層)と中間金属層(第2の導電層)とのコンタクト部75cは平坦面を有し、その平坦面上に、中間金属層と上面金属層(第3の導電層)のコンタクト部78cが配置される。これにより、アノード電極78の材料がアルミニウム(Al)の場合は勿論、銀を用いた積層構造の膜を採用した場合であっても、段切れ等のコンタクト不良を防止することができる。

【0097】

本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【0098】

画素101は、図3を参照して説明したように、2個のトランジスタ(サンプリング用トランジスタ31と駆動用トランジスタ32)と2個のキャパシタ(蓄積容量33と補助容量35)で構成されていたが、その他の回路構成を採用することもできる。

【0099】

例えば、補助容量35は、発光素子34の容量成分を補うために設けられているので、省略することができる。従って、画素101は、2個のトランジスタと蓄積容量33としての1個のキャパシタの構成(以下、2Tr/1C画素回路とも称する)とすることができる。

【0100】

さらに、その他の画素101の回路構成として、例えば、次のような回路構成を採用できる。即ち、2Tr/1C画素回路に、第1乃至第3のトランジスタを加えた、5個のトランジスタと1個のキャパシタの構成(以下、5Tr/1C画素回路とも称する)を採用することもできる。5Tr/1C画素回路を採用した画素101では、水平セレクタ103から映像信号線DTL10を介してサンプリング用トランジスタ31に供給される信号電位がVsig固定となる。その結果、サンプリング用トランジスタ31は駆動用トランジスタ32への信号電位Vsigの供給をスイッチングする機能としてのみ動作する。また、電源線DSL10を介して駆動用トランジスタ32に供給される電位が第1電位Vcc固定となる。そして、追加された第1のトランジスタは、駆動用トランジスタ32への第1電位Vccの供給をスイッチングする。第2のトランジスタは、駆動用トランジスタ32への第2電位Vssの供給をスイッチングする。また、第3のトランジスタは、駆動用トランジスタ32への基準電位Vofの供給をスイッチングする。

【0101】

また、その他の画素101の回路構成としては、2Tr/1C画素回路と5Tr/1C画素回路の中間的な回路構成を採用することもできる。即ち、4個のトランジスタと1個のキャパシタからなる構成(4Tr/1C画素回路)や、3個のトランジスタと1個のキャパシタからなる構成(3Tr/1C画素回路)を採用することもできる。4Tr/1C画素回路としては、例えば、5Tr/1C画素回路の第3のトランジスタを省略し、水平セレクタ12からサンプリング用トランジスタ31に供給する信号電位をVsigとVofsでパルス化するなどの構成を取ることができる。

【0102】

3Tr/1C画素回路、4Tr/1C画素回路、および5Tr/1C画素回路には、2Tr/1C画素回路と同様に、補助容量35を追加してもよい。

【符号の説明】

【0103】

1 表示装置, 100 ELパネル, 101 画素, 74 多結晶シリコン膜, 75 ソース電極, 75b,75c コンタクト部, 76 ドレイン電極, 78 アノード電極, 78b,78c コンタクト部, 79c,80c コンタクト部

【技術分野】

【0001】

本発明は、表示装置に関し、特に、2つのコンタクト部を有する1つの導電層の面積を小さくすることができるようにする表示装置に関する。

【背景技術】

【0002】

発光素子として有機EL(ELectro Luminescent)デバイスを用いた平面自発光型のパネル(ELパネル)の開発が近年盛んになっている。有機ELデバイスは、ダイオード特性を有し、有機薄膜に電界をかけると発光する現象を利用したデバイスである。有機ELデバイスは、印加電圧が10V以下で駆動するため低消費電力であり、自ら光を発する自発光素子であるため、照明部材を必要とせず軽量化及び薄型化が容易であるという特長を有する。また、有機ELデバイスの応答速度は数μs程度と非常に高速であるので、ELパネルでは動画表示時の残像が発生しないという利点がある。

【0003】

ELパネルの中でも、とりわけ駆動素子として薄膜トランジスタ(TFT)を各画素に集積形成したアクティブマトリクス型のパネルの開発が盛んである。アクティブマトリクス型ELパネルは、例えば、特許文献1乃至5に記載されている。

【0004】

近年のアクティブマトリクス型ELパネルにおいては、液晶パネルと同様に、高精細化が望まれている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−255856号公報

【特許文献2】特開2003−271095号公報

【特許文献3】特開2004−133240号公報

【特許文献4】特開2004−029791号公報

【特許文献5】特開2004−093682号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来、アクティブマトリクス型ELパネルにおいて、1つの導電層で他の2つの導電層とコンタクトをとる必要がある場合、2つのコンタクト部は、コンタクト不良を防止するため、平面方向で離れた位置に配置されていた。そのため、2つのコンタクト部を有する導電層の面積が大きくなり、1画素の領域を有効に利用することができなかった。

【0007】

本発明は、このような状況に鑑みてなされたものであり、2つのコンタクト部を有する1つの導電層の面積を小さくすることができるようにするものである。

【課題を解決するための手段】

【0008】

本発明の一側面の表示装置は、自発光素子により発光する画素が行列状に複数配置されているパネルを有し、前記パネルは、第1乃至第3の導電層が支持基板上に順に積層されており、前記第1の導電層と第2の導電層の第1のコンタクト部と、前記第2の導電層と前記第3の導電層の第2のコンタクト部が、平面方向で同一の位置に配置されている。

【0009】

本発明の一側面においては、自発光素子により発光する画素が行列状に複数配置されているパネルに含まれる第1乃至第3の導電層が支持基板上に順に積層されており、第1の導電層と第2の導電層の第1のコンタクト部と、第2の導電層と第3の導電層の第2のコンタクト部が、平面方向で同一の位置に配置される。

【発明の効果】

【0010】

本発明の一側面によれば、2つのコンタクト部を有する1つの導電層の面積を小さくすることができる。

【図面の簡単な説明】

【0011】

【図1】本発明を適用した表示装置の一実施の形態の構成例を示すブロック図である。

【図2】ELパネルの各画素の色の配列を示す図である。

【図3】画素の等価回路の構成を示したブロック図である。

【図4】画素の動作を説明するタイミングチャートである。

【図5】従来のELパネルの駆動トランジスタ部分の断面図である。

【図6】段切れを説明する図である。

【図7】従来のELパネルを構成する画素の平面図である。

【図8】図1のELパネルの第1の実施の形態の画素の駆動トランジスタ部分の断面図である。

【図9】図1のELパネルの第2の実施の形態の画素の駆動トランジスタ部分の断面図である。

【図10】図9のコンタクト部の上面図である。

【図11】図1のELパネルの平面図である。

【発明を実施するための形態】

【0012】

[表示装置の構成]

図1は、本発明を適用した表示装置の一実施の形態の構成例を示すブロック図である。

【0013】

図1の表示装置1は、例えば、テレビジョン受像機などであり、入力された映像信号に対応する映像をELパネル100に表示する。ELパネル100は、自発光素子としての有機EL(ELectro Luminescent)デバイスを用いたパネルである。ELパネル100は、ソースドライバおよびゲートドライバとからなるドライバIC(Integrated Circuit)を含むパネルモジュールとして表示装置1に組み込まれている。また、表示装置1は、図示せぬ電源回路、画像LSI(Large Scale Integration)なども有している。なお、表示装置1のELパネル100は、携帯電話機、デジタルスチルカメラ、デジタルビデオカメラ、プリンタ等の表示部としても利用することができる。

【0014】

ELパネル100は、複数の画素101を有する画素アレイ部102、水平セレクタ(HSEL)103、ライトスキャナ(WSCN)104、および電源スキャナ(DSCN)105を含むように構成されている。

【0015】

画素アレイ部102には、N×M個(N,Mは相互に独立した1以上の整数値)の画素101−(1,1)乃至101−(N,M)が行列状に配置されて構成されている。なお、図1では、紙面の制約上、画素101−(1,1)乃至101−(N,M)の一部のみが示されている。

【0016】

また、ELパネル100は、M本の走査線WSL10−1乃至10−M、M本の電源線DSL10−1乃至10−M、およびN本の映像信号線DTL10−1乃至10−Nも有する。

【0017】

なお、以下において、走査線WSL10−1乃至10−Mそれぞれを特に区別する必要がない場合、単に、走査線WSL10と称する。また、映像信号線DTL10−1乃至10−Nそれぞれを特に区別する必要がない場合、単に、映像信号線DTL10と称する。画素101−(1,1)乃至101−(N,M)および電源線DSL10−1乃至10−Mについても同様に、画素101および電源線DSL10と称する。

【0018】

水平セレクタ103、ライトスキャナ104、および電源スキャナ105は、画素アレイ部102を駆動する駆動部として動作する。

【0019】

画素101−(1,1)乃至101−(N,M)のうちの第1行目の画素101−(1,1)乃至101−(N,1)は、走査線WSL10−1でライトスキャナ104と、電源線DSL10−1で電源スキャナ105とそれぞれ接続されている。また、画素101−(1,1)乃至101−(N,M)のうちの第M行目の画素101−(1,M)乃至101−(N,M)は、走査線WSL10−Mでライトスキャナ104と、電源線DSL10−Mで電源スキャナ105とそれぞれ接続されている。画素101−(1,1)乃至101−(N,M)の行方向に並ぶその他の画素101についても同様の接続となっている。

【0020】

また、画素101−(1,1)乃至101−(N,M)のうちの第1列目の画素101−(1,1)乃至101−(1,M)は、映像信号線DTL10−1で水平セレクタ103と接続されている。画素101−(1,1)乃至101−(N,M)のうちの第N列目の画素101−(N,1)乃至101−(N,M)は、映像信号線DTL10−Nで水平セレクタ103と接続されている。画素101−(1,1)乃至101−(N,M)の列方向に並ぶその他の画素101についても同様の接続となっている。

【0021】

ライトスキャナ104は、走査線WSL10−1乃至10−Mに水平周期(1H)で順次制御信号を供給して画素101を行単位で線順次走査する。電源スキャナ105は、線順次走査に合わせて電源線DSL10−1乃至10−Mに第1電位Vccまたは第2電位Vss(図4)の電源電圧を供給する。水平セレクタ103は、線順次走査に合わせて各水平期間内(1H)で映像信号に対応する信号電位Vsigと基準電位Vofs(図4)とを切換えて列状の映像信号線DTL10−1乃至10−Mに供給する。

【0022】

[画素101の配列構成]

図2は、ELパネル100の各画素101が発光する色の配列を示している。

【0023】

なお、図2では、走査線WSL10および電源線DSL10が画素101の下側から接続されている点が図1と異なる。走査線WSL10、電源線DSL10、および映像信号線DTL10が画素101とどの側面から接続されるかは、配線レイアウトに応じて適宜変更することができる。水平セレクタ103、ライトスキャナ104、および電源スキャナ105の画素アレイ部102に対する配置についても同様に、適宜変更することができる。

【0024】

画素アレイ部102の各画素101は、赤(R)、緑(G)、または青(B)のいずれかの色を発光する。そして、各色は、例えば、行方向には赤、緑、青の順となり、列方向には同一の色となるように配列されている。従って、各画素101は、いわゆる副画素(サブピクセル)に相当し、行方向(図面左右方向)に並ぶ赤、緑、および青の3つの画素101で表示単位としての1画素が構成される。なお、ELパネル100の色の配列が図2に示した配列に限定されるものではない。

【0025】

[画素101の詳細回路構成]

図3は、ELパネル100に含まれるN×M個の画素101のうちの1つの画素101を拡大することにより、画素101の等価回路(画素回路)の構成を示したブロック図である。

【0026】

なお、図3の画素101が、画素101−(n,m)(n=1,2,・・・,N,m=1,2,・・・,M)であるとすると、走査線WSL10、映像信号線DTL10、および電源線DSL10のそれぞれは、次のようになる。即ち、図3の走査線WSL10、映像信号線DTL10、および電源線DSL10は、画素101−(n,m)に対応する走査線WSL10−n、映像信号線DTL10−n、および電源線DSL10−mとなる。

【0027】

図3の画素101は、サンプリング用トランジスタ31、駆動用トランジスタ32、蓄積容量33、発光素子34、および補助容量35を有する。また、図3では、発光素子34が有する容量成分も、発光素子容量34Bとして示してある。ここで、蓄積容量33、発光素子容量34B、および補助容量35の容量値は、それぞれ、Cs,Coled、およびCsubである。

【0028】

サンプリング用トランジスタ31のゲートは、走査線WSL10と接続され、サンプリング用トランジスタ31のドレインは、映像信号線DTL10と接続される。また、サンプリング用トランジスタ31のソースは、駆動用トランジスタ32のゲートと接続されている。

【0029】

駆動用トランジスタ32のソース及びドレインの一方は、発光素子34のアノードに接続され、他方が、電源線DSL10に接続される。蓄積容量33は、駆動用トランジスタ32のゲートと発光素子34のアノードに接続されている。また、発光素子34のカソードは所定の電位Vcatに設定されている配線36に接続されている。この電位VcatはGNDレベルであり、従って、配線36は接地配線である。

【0030】

補助容量35は、発光素子34の容量成分、即ち発光素子容量34Bを補うために設けられ、発光素子34と並列に接続されている。即ち、補助容量35の一方の電極は、発光素子34のアノード側に接続され、他方の電極は、発光素子34のカソード側と接続される。このように補助容量35を設け、所定の電位を保持させることにより、駆動用トランジスタ32の入力ゲインを向上させることができる。ここで、駆動用トランジスタ32の入力ゲインとは、図4を参照して後述する書き込み+移動度補正期間T5における駆動用トランジスタ32のゲート電位Vgの上昇量に対するソース電位Vsの上昇量の比率である。

【0031】

サンプリング用トランジスタ31および駆動用トランジスタ32は、いずれもNチャネル型トランジスタである。よって、サンプリング用トランジスタ31および駆動用トランジスタ32は、低温ポリシリコンよりも安価に作成できるアモルファスシリコンで作成することができる。これにより、画素回路の製造コストをより安価にすることができる。勿論、サンプリング用トランジスタ31および駆動用トランジスタ32は、低温ポリシリコンや単結晶シリコンで作成しても構わない。

【0032】

発光素子34は、有機EL素子で構成される。有機EL素子はダイオード特性を有する電流発光素子である。よって、発光素子34は、供給される電流値Idsに応じた階調の発光を行う。

【0033】

以上のように構成される画素101において、サンプリング用トランジスタ31が、走査線WSL10からの制御信号に応じてオン(導通)し、映像信号線DTL10を介して階調に応じた信号電位Vsigの映像信号をサンプリングする。蓄積容量33は、映像信号線DTL10を介して水平セレクタ103から供給された電荷を蓄積して保持する。駆動用トランジスタ32は、第1電位Vccにある電源線DSL10から電流の供給を受け、蓄積容量33に保持された信号電位Vsigに応じて駆動電流Idsを発光素子34に流す(供給する)。発光素子34に所定の駆動電流Idsが流れることにより、画素101が発光する。

【0034】

画素101は、閾値補正機能を有する。閾値補正機能とは、駆動用トランジスタ32の閾値電圧Vthに相当する電圧を蓄積容量33に保持させる機能である。閾値補正機能を発揮させることで、ELパネル100の画素毎のばらつきの原因となる駆動用トランジスタ32の閾値電圧Vthの影響をキャンセルすることができる。

【0035】

また、画素101は、上述した閾値補正機能に加え、移動度補正機能も有する。移動度補正機能とは、蓄積容量33に信号電位Vsigを保持する際、駆動用トランジスタ32の移動度μに対する補正を信号電位Vsigに加える機能である。

【0036】

さらに、画素101は、ブートストラップ機能も備えている。ブートストラップ機能とは、駆動用トランジスタ32のソース電位Vsの変動にゲート電位Vgを連動させる機能である。ブートストラップ機能の発揮により、駆動用トランジスタ32のゲートとソース間の電圧Vgsを一定に維持することが出来る。

【0037】

[画素101の動作の説明]

図4は、画素101の動作を説明するタイミングチャートである。

【0038】

図4は、同一の時間軸(図面横方向)に対する走査線WSL10、電源線DSL10、および映像信号線DTL10の電位変化と、それに対応する駆動用トランジスタ32のゲート電位Vg及びソース電位Vsの変化を示している。

【0039】

図4において、時刻t1までの期間は、前の水平期間(1H)の発光がなされている発光期間T1である。

【0040】

発光期間T1が終了した時刻t1から時刻t3までは、駆動用トランジスタ32のゲート電位Vg及びソース電位Vsを初期化することで閾値電圧補正動作の準備を行う閾値補正準備期間T2である。

【0041】

閾値補正準備期間T2では、時刻t1において、電源スキャナ14が、電源線DSLの電位を高電位である第1電位Vccから低電位である第2電位Vssに切換える。ここで、発光素子34の閾値電圧をVthelとする。このとき、第2電位Vssを、Vss<Vthel+Vcatとすると、駆動用トランジスタ32のソース電位Vsが第2電位Vssにほぼ等しくなるために、発光素子34は逆バイアス状態となって消光する。

【0042】

次に、時刻t2において、ライトスキャナ13が、走査線WSLの電位を高電位に切換え、サンプリング用トランジスタ31をオンさせる。これにより、駆動用トランジスタ32のゲート電位Vgが基準電位Vofsにリセットされ、且つ、ソース電位Vsが映像信号線DTLの第2電位Vssにリセットされる。

【0043】

このとき、駆動用トランジスタ32のゲート−ソース間電圧Vgsは、(Vofs−Vss)となる。ここで、(Vofs−Vss)が駆動用トランジスタ32の閾値電圧Vthよりも大きくないと、次の閾値補正処理を行うことができない。そのため、(Vofs−Vss)>Vthの関係を満たすように、基準電位Vofsおよび第2電位Vssが設定されている。

【0044】

時刻t3から時刻t4までは、閾値補正動作を行う閾値補正期間T3である。閾値補正期間T3では、時刻t3において、電源スキャナ14により、電源線DSLの電位が高電位Vccに切換えられ、閾値電圧Vthに相当する電圧が、駆動用トランジスタ32のゲートとソースとの間に接続された蓄積容量33に書き込まれる。即ち、電源線DSLの電位が高電位Vccに切換えられることにより駆動用トランジスタ32のソース電位Vsが上昇し、閾値補正期間T3の時刻t4までに、駆動用トランジスタ32のゲート‐ソース間電圧Vgsが、閾値電圧Vthに等しくなる。

【0045】

なお、閾値補正期間T3では、発光素子34がカットオフ状態となるようにカソード電位Vcatが設定されているため、駆動用トランジスタ32のドレイン−ソース間電流Idsは蓄積容量33側に流れ、発光素子34側には流れない。

【0046】

時刻t4から時刻t6までの書き込み+移動度補正準備期間T4では、走査線WSLの電位が高電位から低電位に一旦切換えられる。このとき、サンプリング用トランジスタ31がオフされるため、駆動用トランジスタ32のゲートがフローティング状態となる。しかし、駆動用トランジスタ32のゲート‐ソース間電圧Vgsが、閾値電圧Vthに等しいため、駆動用トランジスタ32はカットオフ状態にある。従って、駆動用トランジスタ32にドレイン−ソース間電流Idsは流れない。

【0047】

そして、時刻t4から時刻t6の間の時刻t5において、水平セレクタ12が、映像信号線DTLの電位を基準電位Vofsから階調に応じた信号電位Vsigに切換える。

【0048】

その後、時刻t6から時刻t7までの書き込み+移動度補正期間T5において、映像信号の書き込みと移動度補正動作が同時に行われる。即ち、時刻t6から時刻t7までの間、走査線WSLの電位が高電位に設定され、これにより、階調に応じた信号電位Vsigが閾値電圧Vthに足し込まれる形で蓄積容量33に書き込まれる。また、移動度補正用の電圧ΔVが蓄積容量33に保持された電圧から差し引かれる。

【0049】

ここで、書き込み+移動度補正期間T5終了後の時刻t7における駆動用トランジスタ32のゲート‐ソース間電圧Vgsは(Vsig+Vth−ΔV)である。

【0050】

書き込み+移動度補正期間T5終了後の時刻t7において、走査線WSLの電位が低電位に戻される。これにより、駆動用トランジスタ32のゲートは、映像信号線DTLから切り離されるため、フローティング状態となる。駆動用トランジスタ32のゲートがフローティング状態にあるときは、駆動用トランジスタ32のゲート−ソース間に蓄積容量33が接続されていることにより、駆動用トランジスタ32のソース電位Vsの変動に連動してゲート電位Vgも変動する。このように、駆動用トランジスタ32のゲート電位Vgが、ソース電位Vsの変動に連動して変動する動作が、蓄積容量33によるブートストラップ動作である。

【0051】

時刻t7以降、駆動用トランジスタ32のゲートがフローティング状態になり、駆動用トランジスタ32のドレイン−ソース間電流Idsが駆動電流として発光素子34に流れ始めることにより、駆動電流Idsに応じて発光素子34のアノード電位が上昇する。また、ブートストラップ動作により、駆動用トランジスタ32のゲート電位Vgも同様に上昇する。即ち、映像信号線DTLの信号電位Vsigに応じて、駆動用トランジスタ32のゲート‐ソース間電圧Vgs=(Vsig+Vth−ΔV)を一定に維持したまま、駆動用トランジスタ32のゲート電位Vg及びソース電位Vsが上昇する。そして、発光素子34のアノード電位が(Vthel+Vcat)を超えたとき、発光素子34が発光を開始する。

【0052】

書き込み+移動度補正期間T5終了後の時刻t7時点で、閾値電圧Vthと移動度μの補正が終了しているため、発光素子34の発光輝度は駆動用トランジスタ32の閾値電圧Vthや移動度μのばらつきの影響を受けることがない。即ち、発光素子34は、駆動用トランジスタ32の閾値電圧Vthや移動度μのばらつきの影響を受けずに、信号電位Vsigに応じた各画素同一の発光輝度で発光する。

【0053】

そして、時刻t7から所定時間経過後の時刻t8において、映像信号線DTLの電位が、信号電位Vsigから基準電位Vofsに落とされる。

【0054】

以上のようにして、ELパネル100の各画素101では、駆動用トランジスタ32の閾値電圧Vthや移動度μのばらつきの影響を受けることがなく、発光素子34を発光させることができる。従って、ELパネル100を用いた表示装置1では、高品位な画質を得ることができる。

【0055】

次に、ELパネル100の画素101の薄膜トランジスタ(TFT)部分のパターン構造について説明するが、その前に、従来の薄膜トランジスタ部分のパターン構造について説明する。

【0056】

なお、ELパネル100の画素101の薄膜トランジスタ部分のパターン構造を、従来の薄膜トランジスタ部分のパターン構造と比較すると、いくつかの膜の配置場所が異なる。換言すれば、基板上に形成される膜の構成自体に差異はないので、図5および図6に示す従来の薄膜トランジスタ部分のパターン構造においては、ELパネル100の画素101における場合と同様の符号を付して説明する。

【0057】

[従来の画素101の駆動用トランジスタ32部分の断面図]

図5は、従来のELパネル100Xにおける画素101の駆動用トランジスタ32部分の断面図である。

【0058】

ELパネル100Xでは、ガラス等の材料からなる支持基板71上に、駆動用トランジスタ32のゲート電極72が形成される。ゲート電極72の上側には、絶縁膜73を介してチャネル領域となる半導体層としての多結晶シリコン膜74が形成される。

【0059】

さらに多結晶シリコン膜74の上側には、ソース電極75およびドレイン電極76が形成される。ソース電極75は、コンタクト部75aで多結晶シリコン膜74と接続されている。また、ドレイン電極76は、コンタクト部76aで多結晶シリコン膜74と接続されている。コンタクト部75aおよび76a以外のソース電極75と多結晶シリコン膜74との間、およびドレイン電極76と多結晶シリコン膜74との間の層は、絶縁膜73で覆われている。

【0060】

ソース電極75およびドレイン電極76の上には、平坦化膜77が積層され、平坦化膜77の上にアノード電極(反射電極)78が形成される。アノード電極78は、コンタクト部78aでソース電極75と接続されている。

【0061】

アノード電極78の上側には、赤、緑、または青のいずれか所定の色に発光する発光層である有機EL層(図示せず)、有機EL層の上にカソード電極(図示せず)が形成される。

【0062】

[従来の問題]

従来は、図5に示されるように、アノード電極78とソース電極75の接続面であるコンタクト部78aと、ソース電極75と多結晶シリコン膜74との接続面であるコンタクト部75aが、平面方向で離れた位置に配置されていた。これは、導電層間を接続する傾斜部(以下、段差部という)の距離が長いと、段切れ等のコンタクト不良が発生する可能性が高くなるためである。段切れとは、図6に示されるように、段差部に形成される膜が薄くなり、断線することである。

【0063】

アノード電極78の材料には、例えば、アルミニウム(Al)や、銀(Ag)の薄膜の両面をITO膜等の透明導電膜で挟み込むように積層させた積層構造の膜が採用される。銀を用いた積層構造の膜は、アルミニウムよりも反射率が高くなるというメリットがある反面、材料の性質上、銀薄膜の段切れや透明導電膜の段切れが発生しやすくなる。銀薄膜および透明導電膜の段切れまたは成膜不良が発生した場合には、接続抵抗が大きくなったり、銀が腐食して良好なコンタクトを得ることができない。

【0064】

従来、このようなコンタクト不良を防止するため、コンタクト部78aとコンタクト部75aは、図5に示したように、平面方向で離れた位置に配置されていた。

【0065】

しかしながら、コンタクト部78aとコンタクト部75aとを平面方向で離れた位置に配置させることは、レイアウト面積が大きくなり、1画素の面積を小さくしようとした場合の障害となる。即ち、コンタクト部78aとコンタクト部75aとを平面方向で離れた位置に配置させることで、ELパネルの高精細化が困難となるという問題があった。また、1画素の面積を変える必要がない場合には、コンタクト部78aとコンタクト部75aを含むレイアウト面積が大きくなるために、他のレイアウト面積を小さくせざるを得ず、輝度の向上や省電力による駆動などの表示性能の低下を招いていた。

【0066】

[従来の画素101の平面図]

図7は、従来のELパネル100Xを構成する画素101の平面図である。

【0067】

以下、説明の便宜上、支持基板71に最も近く、図5の断面図において最も下の面に位置する、ゲート電極72を形成する金属層を下面金属層という。また、多結晶シリコン膜74を形成する半導体層をシリコン層、ソース電極75およびドレイン電極76を形成する金属層を中間金属層、アノード電極78を形成する金属層を上面金属層とそれぞれ称する。

【0068】

図7において、画素101を横断する走査線WSL10と電源線DSL10は、中間金属層で形成される。また、画素101を縦断する映像信号線DTL10は、走査線WSL10および電源線DSL10と交差しない部分については中間金属層で形成され、走査線WSL10および電源線DSL10と交差する部分については下面金属層で形成される。

【0069】

サンプリング用トランジスタ31に注目すると、サンプリング用トランジスタ31のドレイン電極およびソース電極は中間金属層で形成され、ゲート電極は下面金属層で形成される。そして、サンプリング用トランジスタ31のドレイン電極およびソース電極とゲート電極との間にシリコン層が形成される。シリコン層は、サンプリング用トランジスタ31のドレイン電極およびソース電極としての中間金属層と接続されている。

【0070】

駆動用トランジスタ32に注目すると、駆動用トランジスタ32のドレイン電極およびソース電極は中間金属層で形成され、ゲート電極は下面金属層で形成される。そして、駆動用トランジスタ32のドレイン電極およびソース電極とゲート電極との間にシリコン層が形成される。シリコン層は、駆動用トランジスタ32のドレイン電極およびソース電極としての中間金属層と接続されている。

【0071】

駆動用トランジスタ32のドレイン電極を形成する中間金属層は、コンタクト部76aにより、多結晶シリコン膜74としてのシリコン層と接続されている。駆動用トランジスタ32のソース電極を形成する中間金属層は、コンタクト部75aにより、多結晶シリコン膜74としてのシリコン層と接続されている。さらに、駆動用トランジスタ32のソース電極を形成する中間金属層は、コンタクト部78aにより、アノード電極78と接続されている。

【0072】

蓄積容量33は、下面金属層とシリコン層とを対向させることにより、構成されている。下面金属層で形成されている蓄積容量33の一方の電極は、中間金属層を介して、サンプリング用トランジスタ31のソース電極と接続されている。シリコン層で形成されている蓄積容量33の他方の電極は、コンタクト部75aにより、駆動用トランジスタ32のソース電極を形成する中間金属層と接続されている。駆動用トランジスタ32のソース電極を形成する中間金属層は、上述したようにアノード電極78と接続されているので、結局、シリコン層で形成されている蓄積容量33の他方の電極は、アノード電極78と接続されている。

【0073】

補助容量35も、下面金属層とシリコン層とを対向させることにより、構成されている。補助容量35の一方の電極は、蓄積容量33の他方の電極と共通のシリコン層で形成されているため、アノード電極78と接続されている。補助容量35の他方の電極は、コンタクト部79aにより中間金属層と接続され、中間金属層は、コンタクト部80aにより、アノード電極78と接続されている。ここで、コンタクト部80aを介して接続されるアノード電極78の電位は、電気的には、カソード電位Vcatとなっている。

【0074】

従来のELパネル100Xにおける画素101は、以上のように構成され、コンタクト部75aとコンタクト部78aが離れて位置している。このため、駆動用トランジスタ32のソース電極を形成し、2つのコンタクト部75aと78aを有する中間金属層の面積が大きくなっている。

【0075】

また、コンタクト部79aと80aが離れて位置しているので、コンタクト部79aと80aを有する中間金属層の面積も大きくなっている。

【0076】

従って、従来の配置構成では、ELパネルの高精細化が困難となる、または、輝度の向上や省電力による駆動などの機能低下を招いてしまうという問題があった。

【0077】

そこで、次に、本発明を適用したELパネル100で採用されている、画素101の第1の実施の形態について説明する。

【0078】

<第1の実施の形態>

[ELパネル100における画素101の駆動用トランジスタ32部分の断面図]

図8は、第1の実施の形態における画素101の駆動用トランジスタ32部分の断面図である。

【0079】

図8の画素101では、アノード電極78と駆動用トランジスタ32のソース電極75との接続部であるコンタクト部78bと、ソース電極75と多結晶シリコン膜74との接続部であるコンタクト部75bが、平面方向で同一の位置に配置されている。換言すれば、コンタクト部78bと75bが、上面からみたときの中心位置が同一(同軸)となるように配置されている。

【0080】

これにより、コンタクト部75bと78bを有する中間金属層の面積を小さくすることができ、1画素内の領域を有効に利用することができる。あるいは、1画素の面積を小さくすることができる。

【0081】

しかしながら、図8の配置は、段差部の上にさらに段差部が設けられる構成である。より詳しくは、ソース電極75が多結晶シリコン膜74と接続するための傾斜部に、アノード電極78が接続している。そのため、段切れが発生しやすいとも言える。

【0082】

<第2の実施の形態>

そこで、コンタクト不良の発生をより抑制する、ELパネル100の画素101の第2の実施の形態について説明する。

【0083】

[ELパネル100における画素101の駆動用トランジスタ32部分の断面図]

図9は、第2の実施の形態における画素101の駆動用トランジスタ32部分の断面図である。

【0084】

図9の画素101においても、アノード電極78と駆動用トランジスタ32のソース電極75との接続部であるコンタクト部78cと、ソース電極75と多結晶シリコン膜74との接続部であるコンタクト部75cが、平面方向で同一の位置に配置されている。

【0085】

さらに、図9の画素101では、コンタクト部75cを形成しているソース電極75の上側の膜面は平坦面を有し、その平坦面上で、ソース電極75とアノード電極78がコンタクト部78cとして接続されている。即ち、ソース電極75とアノード電極78は、面で接している。

【0086】

また、コンタクト部78cを形成している同一平面上の、ソース電極75側の平坦面の開口幅L1は、アノード電極78の平坦面の開口幅L2よりも大となっている。

【0087】

[コンタクト部78cの上面図]

図10は、コンタクト部78cの上面図である。

【0088】

コンタクト部78cは、図10に示されるように、四角形や円形とすることができる。この場合、ソース電極75側の平坦面も、コンタクト部78cと同一の形状(四角形や円形)とする。

【0089】

また、ソース電極75側の平坦面の開口幅L1は、アノード電極78の平坦面の開口幅L2よりも、例えば、1μmより大きくすることができる。

【0090】

以上のように、ソース電極75の上側の膜面は平坦面を設け、その平坦面上でアノード電極78とソース電極75が接続されるようにすることで、図5に示した従来のコンタクト部78aと同様の接続面が確保される。従って、コンタクト不良を防止することができる。

【0091】

[ELパネル100の平面図]

図11は、第2の実施の形態におけるELパネル100の平面図である。なお、図11は、コンタクト部75cおよび78cの形状を四角形とした例である。

【0092】

図11において、コンタクト部75cおよび78cは、駆動用トランジスタ32の図面下側の位置の1箇所に配置されている。これにより、図11では、図7における場合と比較すると、コンタクト部75cおよび78cを有する中間金属層の面積が小さくなっている。

【0093】

また、図7のコンタクト部79aと80aに対応する、コンタクト部79cと80cについても同様に、平面方向で同一位置に配置された結果、中間金属層の面積が小さくなっている。

【0094】

そして、コンタクト部75cおよび78cを有する中間金属層、および、コンタクト部79cと80cを有する中間金属層の面積がそれぞれ小さくなった結果、図11では、図7と比較して、補助容量35の面積を大きくすることが可能となっている。

【0095】

以上のように、ELパネル100によれば、シリコン層(第1の導電層)と中間金属層(第2の導電層)とのコンタクト部75cと、中間金属層と上面金属層(第3の導電層)のコンタクト部78cが平面方向で同一の位置に配置される。これにより、2つのコンタクト部(コンタクト部75cと78c)を有する中間金属層の面積を小さくすることができ、1画素の面積を小さくすることができる。また、1画素の面積を変える必要がない場合には、表示性能を向上させることができる。

【0096】

また、ELパネル100によれば、シリコン層(第1の導電層)と中間金属層(第2の導電層)とのコンタクト部75cは平坦面を有し、その平坦面上に、中間金属層と上面金属層(第3の導電層)のコンタクト部78cが配置される。これにより、アノード電極78の材料がアルミニウム(Al)の場合は勿論、銀を用いた積層構造の膜を採用した場合であっても、段切れ等のコンタクト不良を防止することができる。

【0097】

本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【0098】

画素101は、図3を参照して説明したように、2個のトランジスタ(サンプリング用トランジスタ31と駆動用トランジスタ32)と2個のキャパシタ(蓄積容量33と補助容量35)で構成されていたが、その他の回路構成を採用することもできる。

【0099】

例えば、補助容量35は、発光素子34の容量成分を補うために設けられているので、省略することができる。従って、画素101は、2個のトランジスタと蓄積容量33としての1個のキャパシタの構成(以下、2Tr/1C画素回路とも称する)とすることができる。

【0100】

さらに、その他の画素101の回路構成として、例えば、次のような回路構成を採用できる。即ち、2Tr/1C画素回路に、第1乃至第3のトランジスタを加えた、5個のトランジスタと1個のキャパシタの構成(以下、5Tr/1C画素回路とも称する)を採用することもできる。5Tr/1C画素回路を採用した画素101では、水平セレクタ103から映像信号線DTL10を介してサンプリング用トランジスタ31に供給される信号電位がVsig固定となる。その結果、サンプリング用トランジスタ31は駆動用トランジスタ32への信号電位Vsigの供給をスイッチングする機能としてのみ動作する。また、電源線DSL10を介して駆動用トランジスタ32に供給される電位が第1電位Vcc固定となる。そして、追加された第1のトランジスタは、駆動用トランジスタ32への第1電位Vccの供給をスイッチングする。第2のトランジスタは、駆動用トランジスタ32への第2電位Vssの供給をスイッチングする。また、第3のトランジスタは、駆動用トランジスタ32への基準電位Vofの供給をスイッチングする。

【0101】

また、その他の画素101の回路構成としては、2Tr/1C画素回路と5Tr/1C画素回路の中間的な回路構成を採用することもできる。即ち、4個のトランジスタと1個のキャパシタからなる構成(4Tr/1C画素回路)や、3個のトランジスタと1個のキャパシタからなる構成(3Tr/1C画素回路)を採用することもできる。4Tr/1C画素回路としては、例えば、5Tr/1C画素回路の第3のトランジスタを省略し、水平セレクタ12からサンプリング用トランジスタ31に供給する信号電位をVsigとVofsでパルス化するなどの構成を取ることができる。

【0102】

3Tr/1C画素回路、4Tr/1C画素回路、および5Tr/1C画素回路には、2Tr/1C画素回路と同様に、補助容量35を追加してもよい。

【符号の説明】

【0103】

1 表示装置, 100 ELパネル, 101 画素, 74 多結晶シリコン膜, 75 ソース電極, 75b,75c コンタクト部, 76 ドレイン電極, 78 アノード電極, 78b,78c コンタクト部, 79c,80c コンタクト部

【特許請求の範囲】

【請求項1】

自発光素子により発光する画素が行列状に複数配置されているパネルを有し、

前記パネルは、第1乃至第3の導電層が支持基板上に順に積層されており、

前記第1の導電層と第2の導電層の第1のコンタクト部と、前記第2の導電層と前記第3の導電層の第2のコンタクト部が、平面方向で同一の位置に配置されている

表示装置。

【請求項2】

前記第1のコンタクト部は、平坦面を有し、その平坦面上に、前記第2のコンタクト部が配置される

請求項1に記載の表示装置。

【請求項3】

前記第1のコンタクト部の開口幅は、前記第2のコンタクト部の開口幅よりも大である

請求項2に記載の表示装置。

【請求項4】

前記画素は、

ダイオード特性を有し、駆動電流に応じて発光する発光素子と、

映像信号をサンプリングするサンプリング用トランジスタと、

前記駆動電流を前記発光素子に供給する駆動用トランジスタと、

前記発光素子のアノード側と前記駆動用トランジスタのゲートに接続され、所定の電位を保持する蓄積容量と

を少なくとも有する

請求項3に記載の表示装置。

【請求項5】

前記第1の導電層は、半導体層であり、

前記第2の導電層は、前記駆動用トランジスタのソース電極およびドレイン電極を形成する金属層であり、

前記第3の導電層は、前記発光素子のアノード電極を形成する金属層である

請求項4に記載の表示装置。

【請求項6】

前記第3の導電層の材料には、銀を含む

請求項5に記載の表示装置。

【請求項1】

自発光素子により発光する画素が行列状に複数配置されているパネルを有し、

前記パネルは、第1乃至第3の導電層が支持基板上に順に積層されており、

前記第1の導電層と第2の導電層の第1のコンタクト部と、前記第2の導電層と前記第3の導電層の第2のコンタクト部が、平面方向で同一の位置に配置されている

表示装置。

【請求項2】

前記第1のコンタクト部は、平坦面を有し、その平坦面上に、前記第2のコンタクト部が配置される

請求項1に記載の表示装置。

【請求項3】

前記第1のコンタクト部の開口幅は、前記第2のコンタクト部の開口幅よりも大である

請求項2に記載の表示装置。

【請求項4】

前記画素は、

ダイオード特性を有し、駆動電流に応じて発光する発光素子と、

映像信号をサンプリングするサンプリング用トランジスタと、

前記駆動電流を前記発光素子に供給する駆動用トランジスタと、

前記発光素子のアノード側と前記駆動用トランジスタのゲートに接続され、所定の電位を保持する蓄積容量と

を少なくとも有する

請求項3に記載の表示装置。

【請求項5】

前記第1の導電層は、半導体層であり、

前記第2の導電層は、前記駆動用トランジスタのソース電極およびドレイン電極を形成する金属層であり、

前記第3の導電層は、前記発光素子のアノード電極を形成する金属層である

請求項4に記載の表示装置。

【請求項6】

前記第3の導電層の材料には、銀を含む

請求項5に記載の表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−249935(P2010−249935A)

【公開日】平成22年11月4日(2010.11.4)

【国際特許分類】

【出願番号】特願2009−97083(P2009−97083)

【出願日】平成21年4月13日(2009.4.13)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成22年11月4日(2010.11.4)

【国際特許分類】

【出願日】平成21年4月13日(2009.4.13)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]