表示装置

【課題】正確に焼き付きを防止することの可能な表示装置を提供する。

【解決手段】各ダミー画素16に、互いに異なる大きさの信号電圧が印加され、その信号電圧の大きさに応じた輝度で各ダミー画素16が発光し、各ダミー画素16に流れる電流が電流測定回路26で検知される。各ダミー画素18に、互いに異なる大きさの定電流が流され、その定電流の大きさに応じた輝度で各ダミー画素18が発光し、各ダミー画素18の発光光が受光素子群19で検知される。電流測定回路26から出力された電流信号26Aを用いて電流劣化関数Ii(t),Is(t)が導出され、受光素子群19から出力された受光信号19Aを用い効率劣化関数Fi(t),Fs(t)が導出される。電流劣化関数Ii(t),Is(t)、効率劣化関数Fi(t),Fs(t)および映像信号20Aの履歴から、各表示画素13の電流劣化率および効率劣化率が予測される。

【解決手段】各ダミー画素16に、互いに異なる大きさの信号電圧が印加され、その信号電圧の大きさに応じた輝度で各ダミー画素16が発光し、各ダミー画素16に流れる電流が電流測定回路26で検知される。各ダミー画素18に、互いに異なる大きさの定電流が流され、その定電流の大きさに応じた輝度で各ダミー画素18が発光し、各ダミー画素18の発光光が受光素子群19で検知される。電流測定回路26から出力された電流信号26Aを用いて電流劣化関数Ii(t),Is(t)が導出され、受光素子群19から出力された受光信号19Aを用い効率劣化関数Fi(t),Fs(t)が導出される。電流劣化関数Ii(t),Is(t)、効率劣化関数Fi(t),Fs(t)および映像信号20Aの履歴から、各表示画素13の電流劣化率および効率劣化率が予測される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示パネルに発光素子が設けられた表示装置に関する。

【背景技術】

【0002】

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL(electro luminescence)素子を用いた表示装置が開発され、商品化が進められている。有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置(有機EL表示装置)では、光源(バックライト)が必要ないので、光源を必要とする液晶表示装置と比べて、薄型化、高輝度化することができる。特に、駆動方式としてアクティブマトリクス方式を用いた場合には、各画素をホールド点灯させることができ、低消費電力化することもできる。そのため、有機EL表示装置は、次世代のフラットパネルディスプレイの主流になると期待されている。

【0003】

しかし、有機EL素子では、通電する電流量に応じて素子が劣化し、輝度が低下するという問題がある。そのため、有機EL素子を表示装置の画素として用いた場合には、画素ごとに劣化の状況が異なることがある。例えば、時刻や表示チャンネルなどの情報が長時間、同じ場所に高輝度で表示されていた場合には、その部分の画素だけ劣化が早まる。その結果、劣化の早まった画素を含む部分に高輝度の映像が表示された場合には、劣化の早まった画素の部分だけが暗く表示される焼き付きという現象が生じてしまう。この焼き付きは非可逆性であることから、一旦、焼き付きが生じると、焼き付きが消えることはない。

【0004】

焼き付きを防止する手法は、今までに多数提案されている。例えば、特許文献1では、表示領域外にダミー画素を設け、ダミー画素を発光させたときの端子電圧を検出することによりダミー画素の劣化度合いを見積もり、その見積もりを利用して映像信号を補正する方法が開示されている。また、例えば、特許文献2,3では、各表示画素内に光センサを配置し、光センサから出力される受光信号を利用して映像信号を補正する方法が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−351403号公報

【特許文献2】特開2008−58446号公報

【特許文献3】国際公開番号WO2006/046196

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、特許文献1の手法では、表示領域内の画素の発光情報に基づいて画素の劣化度合いが見積もられておらず、映像信号を正確に補正することが不可能であることから、焼き付きを防止することはできないという問題があった。また、特許文献2,3の手法では、各画素内の光センサの光電変換効率がばらつくので、例えば、同一輝度を表示している2つの画素において、受光信号の大きさが異なってしまうことがある。その結果、正確に焼き付きを防止することができないという問題があった。

【0007】

本発明はかかる問題点に鑑みてなされたものであり、その目的は、正確に焼き付きを防止することの可能な表示装置を提供することにある。

【課題を解決するための手段】

【0008】

本発明による表示装置は、複数の表示画素が2次元配置された表示領域と、複数の第1ダミー画素および複数の第2ダミー画素が配置された非表示領域とを有する表示パネルを備えたものである。この表示装置は、また、各第1ダミー画素に互いに異なる大きさの信号電圧を印加して各第1ダミー画素を発光させる第1駆動部と、各第2ダミー画素に互いに異なる大きさの定電流を流して各第2ダミー画素を発光させる第2駆動部とを備えている。この表示装置は、さらに、各第1ダミー画素に流れる電流を検知して各第1ダミー画素の電流情報を出力する電流測定部と、各第2ダミー画素の発光光を検知して各第2ダミー画素の輝度情報を出力する受光部と、電流情報を用いて電流劣化関数を導出すると共に、輝度情報を用い効率劣化関数を導出する演算部とを備えている。

【0009】

本発明による表示装置では、表示パネルの非表示領域に設けられた各第1ダミー画素に、互いに異なる大きさの信号電圧が印加され、その信号電圧の大きさに応じた輝度で各第1ダミー画素が発光し、各第1ダミー画素に流れる電流が電流測定部で検知され、各第1ダミー画素の電流情報が電流測定部から出力される。また、表示パネルの非表示領域に設けられた各第2ダミー画素に、互いに異なる大きさの定電流が流され、その定電流の大きさに応じた輝度で各第2ダミー画素が発光し、各第2ダミー画素の発光光が受光部で検知され、各第2ダミー画素の輝度情報が受光部から出力される。その後、電流情報を用いて電流劣化関数が導出されると共に、輝度情報を用い効率劣化関数が導出される。これにより、例えば、電流劣化関数、および各表示画素の映像信号の履歴から、各表示画素の電流劣化率を予測することができる。また、効率劣化関数、および各表示画素の映像信号の履歴から、各表示画素の効率劣化率を予測することができる。

【0010】

ここで、本発明による表示装置において、電流劣化関数を導出する周期は、前記効率劣化関数を導出する周期よりも短くなっていることが好ましい。このようにした場合には、電流が補正された状態で、効率劣化を補正することができる。

【図面の簡単な説明】

【0011】

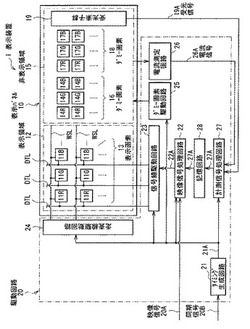

【図1】本発明による一実施の形態に係る表示装置の構成の一例を表す概略図である。

【図2】表示領域の画素回路の構成の一例を表す概略図である。

【図3】非表示領域の画素回路の構成の一例を表す概略図である。

【図4】図1の表示パネルの構成の一例を表す上面図である。

【図5】電流劣化率の経時変化の一例を初期電流ごとに表す特性図である。

【図6】電流劣化率と、初期電流SSのダミー画素の電流劣化率との関係の一例を表す関係図である。

【図7】べき係数n(Si,Ss)と、初期電流の割合Si/Ssとの関係の一例を表す関係図である。

【図8】時刻Tkでの電流劣化率の予測値SS2と、時刻Tkでの電流劣化率の測定値SS1との関係の一例を表す関係図である。

【図9】時刻Tk-1での電流劣化関数Is(t)と、時刻Tkでの電流劣化関数Is(t)との関係の一例を表す関係図である。

【図10】べき係数の算定方法の一例について説明するための概念図である。

【図11】時刻Tk-1でのべき係数n(Si,Ss)と、時刻Tkでのべき係数n(Si,Ss)との関係の一例を表す関係図である。

【図12】電流劣化関数Ii(t)の算定方法の一例について説明するための概念図である。

【図13】基準輝度における累積発光時間Txyの導出方法の一例について説明するための概念図である。

【図14】電流補正量RIの導出方法の一例について説明するための概念図である。

【図15】効率劣化率の経時変化の一例を初期輝度ごとに表す特性図である。

【図16】効率劣化率と、初期輝度YSのダミー画素の効率劣化率との関係の一例を表す関係図である。

【図17】べき係数n(Yi,Ys)と、初期輝度の割合Yi/Ysとの関係の一例を表す関係図である。

【図18】時刻Tkでの効率劣化率の予測値YS2と、時刻Tkでの効率劣化率の測定値YS1との関係の一例を表す関係図である。

【図19】時刻Tk-1での効率劣化関数Fs(t)と、時刻Tkでの効率劣化関数Fs(t)との関係の一例を表す関係図である。

【図20】べき係数の算定方法の一例について説明するための概念図である。

【図21】時刻Tk-1でのべき係数n(Yi,Ys)と、時刻Tkでのべき係数n(Yi,Ys)との関係の一例を表す関係図である。

【図22】効率劣化関数Fi(t)の算定方法の一例について説明するための概念図である。

【図23】基準輝度における累積発光時間Txyの導出方法の一例について説明するための概念図である。

【図24】効率補正量Ryの導出方法の一例について説明するための概念図である。

【図25】上記実施の形態の発光装置の適用例1の外観を表す斜視図である。

【図26】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図27】適用例3の外観を表す斜視図である。

【図28】適用例4の外観を表す斜視図である。

【図29】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0012】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.実施の形態(図1〜図24)

2.変形例(図なし)

・初期電流Siの低い各ダミー画素16を複数のダミー画素で構成した例

・初期輝度Yiの低い各ダミー画素18を複数のダミー画素で構成した例

・基準画素に不具合が生じた場合に別のダミー画素16を新たな基準画素に設定 するようにした例

・基準画素に不具合が生じた場合に別のダミー画素18を新たな基準画素に設定 するようにした例

・サンプリング周期ΔT1を可変にした例

・サンプリング周期ΔT2を可変にした例

・四則演算だけで、べき係数n(Si,Ss)を導出するようにした例

・四則演算だけで、べき係数n(Yi,Ys)を導出するようにした例

3.適用例(図25〜図29)

【0013】

<実施の形態>

(表示装置1の概略構成)

図1は、本発明の第1の実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、表示パネル10と、表示パネル10を駆動する駆動回路20とを備えている。

【0014】

表示パネル10は、複数の有機EL素子11R,11G,11Bが2次元配置された表示領域12を有している。本実施の形態では、互いに隣り合う3つの有機EL素子11R,11G,11Bが1つの画素(表示画素13)を構成している。なお、以下では、有機EL素子11R,11G,11Bの総称として有機EL素子11を適宜、用いるものとする。表示パネル10は、また、複数の有機EL素子14R,14G,14Bが2次元配置された非表示領域15を有している。本実施の形態では、互いに隣り合う3つの有機EL素子14R,14G,14Bが1つの画素(ダミー画素16)を構成している。なお、以下では、有機EL素子14R,14G,14Bの総称として有機EL素子13を適宜、用いるものとする。

【0015】

非表示領域15には、さらに、複数の有機EL素子17R,17G,17Bが2次元配置されている。本実施の形態では、互いに隣り合う3つの有機EL素子17R,17G,17Bが1つの画素(ダミー画素18)を構成している。なお、以下では、有機EL素子17R,17G,17Bの総称として有機EL素子17を適宜、用いるものとする。非表示領域15には、有機EL素子17R,17G,17Bから発せられた光を受光する受光素子群19(受光部)が設けられている。受光素子群19は、例えば、図示しないが、複数の受光素子からなる。複数の受光素子は、例えば、個々の有機EL素子17と対となって2次元配置されており、各受光素子は、各ダミー画素18(各有機EL素子17)から発せられた光(発光光)を検知して、各ダミー画素18の受光信号19A(輝度情報)を出力するようになっている。各受光素子は、例えば、フォトダイオードである。

【0016】

駆動回路20は、タイミング生成回路21、映像信号処理回路22、信号線駆動回路23、走査線駆動回路24、ダミー画素駆動回路25、電流測定回路26、計測信号処理回路27および記憶回路28を有している。

【0017】

(画素回路31)

図2は、表示領域12内の回路構成の一例を表したものである。表示領域12内には、複数の画素回路31が個々の有機EL素子11と対となって2次元配置されている。各画素回路31は、例えば、駆動トランジスタTr1、書き込みトランジスタTr2および保持容量Csによって構成されたものであり、2Tr1Cの回路構成となっている。駆動トランジスタTr1および書き込みトランジスタTr2は、例えば、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている。駆動トランジスタTr1または書き込みトランジスタTr2は、pチャネルMOS型のTFTであってもよい。

【0018】

表示領域12において、列方向には信号線DTLが複数配置され、行方向には走査線WSLおよび電源線Vccがそれぞれ複数配置されている。各信号線DTLと各走査線WSLとの交差点近傍には、有機EL素子11R,11G,11Bのいずれか一つ(サブピクセル)が設けられている。各信号線DTLは、信号線駆動回路23の出力端(図示せず)と、書き込みトランジスタTr2のドレイン電極(図示せず)に接続されている。各走査線WSLは、走査線駆動回路24の出力端(図示せず)と、書き込みトランジスタTr2のゲート電極(図示せず)に接続されている。各電源線Vccは、電源の出力端(図示せず)と、駆動トランジスタTr1のドレイン電極(図示せず)に接続されている。書き込みトランジスタTr2のソース電極(図示せず)は、駆動トランジスタTr1のゲート電極(図示せず)と、保持容量Csの一端に接続されている。駆動トランジスタTr1のソース電極(図示せず)と保持容量Csの他端とが、有機EL素子11のアノード電極(図示せず)に接続されている。有機EL素子11のカソード電極(図示せず)は、例えば、グラウンド線GNDに接続されている。

【0019】

図3は、非表示領域15内の回路構成の一例を表したものである。非表示領域15内には、画素回路31と同一構成の複数の画素回路32が個々の有機EL素子13と対となって2次元配置されている。各画素回路32は、例えば、駆動トランジスタTr1’、書き込みトランジスタTr2’および保持容量Cs’によって構成されたものであり、2Tr1Cの回路構成となっている。駆動トランジスタTr1’および書き込みトランジスタTr2’は、例えば、nチャネルMOS型のTFTにより形成されている。駆動トランジスタTr1’または書き込みトランジスタTr2’は、pチャネルMOS型のTFTであってもよい。

【0020】

非表示領域15においても、列方向には信号線DTL’が複数配置され、行方向には走査線WSL’および電源線Vcc’がそれぞれ複数配置されている。各信号線DTL’と各走査線WSL’との交差点近傍には、有機EL素子14R,14G,14Bのいずれか一つ(サブピクセル)が設けられている。各信号線DTL’は、ダミー画素駆動回路25の出力端(図示せず)と、書き込みトランジスタTr2’のドレイン電極(図示せず)に接続されている。各走査線WSL’は、ダミー画素駆動回路25の出力端(図示せず)と、書き込みトランジスタTr2’のゲート電極(図示せず)に接続されている。各電源線Vcc’は、電源の出力端(図示せず)と、駆動トランジスタTr1’のドレイン電極(図示せず)に接続されている。書き込みトランジスタTr2’のソース電極(図示せず)は、駆動トランジスタTr1’のゲート電極(図示せず)と、保持容量Cs’の一端に接続されている。駆動トランジスタTr1’のソース電極(図示せず)と保持容量Cs’の他端とが、有機EL素子13のアノード電極(図示せず)に接続されている。有機EL素子13のカソード電極(図示せず)は、例えば、グラウンド線GNDに接続されている。

【0021】

(表示パネル10の上面構成)

図4は、表示パネル10の上面構成の一例を表したものである。表示パネル10は、例えば、駆動パネル30と封止パネル40とが封止層(図示せず)を介して貼り合わされた構造となっている。

【0022】

駆動パネル30は、図4に示していないが、表示領域12に、2次元配置された複数の有機EL素子11と、各有機EL素子11に隣接して配置された複数の画素回路31とを有している。駆動パネル30は、また、図4に示していないが、非表示領域15に、2次元配置された複数の有機EL素子13,16と、各有機EL素子17に隣接して配置された複数の受光素子とを有している。

【0023】

駆動パネル30の一辺(長辺)には、例えば、図4に示したように、複数の映像信号供給TAB51と、制御信号供給TCP54と、計測信号出力TCP55とが取り付けられている。駆動パネル30の他の辺(短辺)には、例えば、走査信号供給TAB52が取り付けられている。また、駆動パネル30の一辺(長辺)であって、かつ映像信号供給TAB51とは異なる辺には、例えば、電源供給TCP53が取り付けられている。映像信号供給TAB51は、信号線駆動回路23の集積されたICをフィルム状の配線基板の開口に中空配線したものである。走査信号供給TAB52は、走査線駆動回路24の集積されたICをフィルム状の配線基板の開口に中空配線したものである。電源供給TCP53は、外部の電源と電源線Vcc,Vcc’とを互いに電気的に接続する複数の配線がフィルム上に形成されたものである。制御信号供給TCP54は、外部のダミー画素駆動回路25と、ダミー画素16,17および受光素子群19とを互いに電気的に接続する複数の配線がフィルム上に形成されたものである。計測信号出力TCP55は、外部の計測信号処理回路27と、受光素子群19とを互いに電気的に接続する複数の配線がフィルム上に形成されたものである。なお、信号線駆動回路23および走査線駆動回路24は、TABに形成されていなくてもよく、例えば、駆動パネル30に形成されていてもよい。

【0024】

封止パネル40は、例えば、有機EL素子11,13,16を封止する封止基板(図示せず)と、カラーフィルタ(図示せず)とを有している。カラーフィルタは、例えば、封止基板の表面のうち有機EL素子11の光が通過する領域に設けられている。カラーフィルタは、例えば、有機EL素子11R,11G,11Bのそれぞれに対応して、赤色用のフィルタ、緑色用のフィルタおよび青色用のフィルタ(図示せず)を有している。封止パネル40は、例えば、さらに、光反射部(図示せず)を有している。光反射部は、有機EL素子17から発せられた光を反射して、受光素子群19に入射させるものであり、例えば、封止基板の表面のうち有機EL素子17の光が通過する領域に設けられている。

【0025】

(駆動回路20)

次に、駆動回路20内の各回路について、図1を参照して説明する。タイミング生成回路21は、映像信号処理回路22、信号線駆動回路23、走査線駆動回路24、ダミー画素駆動回路25、電流測定回路26および計測信号処理回路27が連動して動作するように制御するものである。

【0026】

タイミング生成回路21は、例えば、外部から入力された同期信号20Bに応じて(同期して)、上述した各回路に対して制御信号21Aを出力するようになっている。タイミング生成回路21は、例えば、映像信号処理回路22、ダミー画素駆動回路25、電流測定回路26、計測信号処理回路27および記憶回路28などと共に、例えば、表示パネル10とは別体の制御回路基板(図示せず)上に形成されている。

【0027】

映像信号処理回路22は、例えば、制御信号21Aの入力に応じて(同期して)、外部から入力されたデジタルの映像信号20Aを補正すると共に、補正した後の映像信号をアナログに変換して信号線駆動回路23に出力するものである。本実施の形態では、映像信号処理回路22は、記憶回路28から読み出した補正情報27A(後述)を用いて映像信号20Aを補正するようになっている。映像信号処理回路22は、例えば、一水平期間ごとに、記憶回路28から、補正情報27Aとして1ライン分の各表示画素13の補正量(電流補正量RI,効率補正量Ry)(後述)を読み出し、読み出した補正量(電流補正量RI,効率補正量Ry)を用いて映像信号20Aを補正し、補正後の映像信号22Aを信号線駆動回路23に出力するようになっている。

【0028】

信号線駆動回路23は、映像信号処理回路22から入力されたアナログの映像信号22Aを、制御信号21Aの入力に応じて(同期して)各信号線DTLに出力するものである。信号線駆動回路23は、例えば、図4に示したように、駆動パネル30の一辺(長辺)に取り付けられた映像信号供給TAB51に設けられている。走査線駆動回路24は、制御信号21Aの入力に応じて(同期して)、複数の走査線WSLの中から一の走査線WSLを順次選択するものである。走査線駆動回路24は、例えば、図4に示したように、駆動パネル30の他の辺(短辺)に取り付けられた走査信号供給TAB52に設けられている。

【0029】

計測信号処理回路27は、受光素子群19から入力された受光信号19Aに基づいて、補正情報27Aを導出し、導出した補正情報27Aを、制御信号21Aの入力に応じて(同期して)記憶回路28に出力するようになっている。なお、補正情報27Aの導出方法については、後に詳述する。記憶回路28は、計測信号処理回路27から入力された補正情報27Aを格納するものである。記憶回路28は、格納した補正情報27Aを、映像信号処理回路22によって読み出すことができるようになっている。

【0030】

(電流補正について)

ダミー画素駆動回路25は、制御信号21Aの入力に応じて(同期して)、各ダミー画素16に接続された信号線DTL’に互いに異なる大きさの信号電圧Vsigi(一定値)を印加して各ダミー画素16を互いに異なる階調で発光させるものである。ダミー画素駆動回路25は、例えば、ダミー画素16の数がn個である場合に、1番目のダミー画素16には初期階調がS1となるような定電流を流し、2番目のダミー画素16には初期階調がS2(>S1)となるような定電流を流し、i番目のダミー画素16には初期階調がSi(>Si-1)となるような定電流を流し、n番目のダミー画素16には初期階調がSn(>Sn-1)となるような定電流を流すようになっている。ダミー画素駆動回路25は、例えば、各ダミー画素16を発光させた時間を計測するようになっている。

【0031】

なお、各ダミー画素16の輝度は、各ダミー画素16に接続された信号線DTL’に一定の値の信号電圧Vsigiを印加し続けた場合であっても、例えば、図5に示したように、時間の経過に伴って、徐々に低下する。これは、各ダミー画素16に接続された画素回路32に含まれる、駆動トランジスタTr1’などの半導体素子が通電時間(通電積算時間)に応じて劣化していく性質を有しており、その劣化の進行度に応じて電流が流れにくくなるからである。なお、図5中のSsは、各ダミー画素16のうち基準画素(後述)として設定された画素内の有機EL素子13に流れる初期電流である。

【0032】

また、各ダミー画素16内の有機EL素子13に流れる電流の劣化率(電流劣化率)の変移は一様ではない。例えば、図6に示したように、基準画素として設定された画素(ダミー画素16)の電流劣化率を横軸にとると、基準画素の初期電流Ssよりも小さな初期輝度のダミー画素16の電流劣化率の変移は、当初は基準画素の電流劣化よりも緩やかであることがわかる。一方、基準画素の初期電流Ssよりも大きな初期電流のダミー画素16の電流劣化率の変移は、当初は基準画素の電流劣化よりも急峻であることがわかる。図6に例示した各ダミー画素18の電流劣化率の変移を式で表すと以下のようになる。

【数1】

【0033】

数1において、Dsiは、i番目のダミー画素16の電流劣化率である。Dssは、基準画素の電流劣化率である。n(Si,Ss)は、基準画素の電流に対するi番目のダミー画素16の電流のべき係数である。べき係数n(Si,Ss)は、例えば、以下の式に示したように、(Log(Si(Tk))−Log(Si(Tk-1)))を(Log(Ss(Tk))−Log(Ys(Sk-1)))で除算することにより導出される。

【数2】

【0034】

数2において、Log(Ss(Tk))はSs(Tk)の対数であり、Log(Ss(Tk-1))はSs(Tk-1)の対数であり、Log(Si(Tk))はSi(Tk)の対数であり、Log(Si(Tk-1))はSi(Tk-1)の対数である。

【0035】

また、数2において、Ss(Tk)は、時刻Tkにおける基準画素の電流信号26A(輝度情報)であり、基準画素の電流情報のうちで最新の電流情報に相当する。また、Ys(Tk-1)は、時刻Tk-1(<時刻Tk)における基準画素の電流信号26A(電流情報)であり、基準画素の電流情報のうちで最新ではない電流情報に相当する。Si(Tk)は、時刻Tkにおけるi番目のダミー画素16の電流信号26A(電流情報)であり、i番目のダミー画素16(非基準画素)の電流情報のうちで最新の電流情報に相当する。Si(Tk-1)は、時刻Tk-1におけるi番目のダミー画素16の電流信号26A(電流情報)であり、i番目のダミー画素16(非基準画素)の電流情報のうちで最新ではない電流情報に相当する。時刻Tk-1と時刻Tkとの関係は、例えば、以下の式で表される。

【数3】

【0036】

数3において、ΔT1はサンプリング周期である。ここで、サンプリング周期ΔT1とは、例えば、計測信号処理回路27が数2の右辺の分母の値および分子の値を導出する周期を指している。サンプリング周期ΔT1は、後述のサンプリング周期ΔT2よりも短くなっていることが好ましい。計測信号処理回路27は、サンプリング周期ΔT1を常に一定にしている。

【0037】

上記のようにして導出したべき係数n(Si,Ss)は、例えば、図7に示したように、横軸を、基準画素の初期電流Ssに対する各ダミー画素16の初期電流Siの割合(Si/Ss)とすると、時刻Tkにおいて、初期電流Siが大きくなるにつれて大きくなる右肩上がりの曲線を描く。なお、数2からも明らかなように、べき係数n(Si,Ss)は、Ss/Ssにおいて1である。

【0038】

次に、図8〜図14を参照して、映像信号20Aの補正に用いる電流補正量RIの導出方法について説明する。

【0039】

(初期設定)

まず、初期設定について説明する。計測信号処理回路27は、複数のダミー画素16のうちの一の画素を基準画素として設定する。本実施の形態では、この基準画素は、他のダミー画素16(非基準画素)に変更されることはなく、常に、同一のダミー画素16に設定される。

【0040】

次に、計測信号処理回路27は、時刻T1,T2において、電流測定回路26から電流信号26Aを取得する。具体的には、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素16のうちの一の画素である基準画素の電流信号26Aを電流測定回路26から取得する。さらに、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素16のうち基準画素を除く全ての画素である複数の非基準画素の電流信号26Aを電流測定回路26から取得する。続いて、計測信号処理回路27は、基準画素の電流情報から、基準画素の電流劣化情報(Log(Ss(T2))−Log(Ss(T1)))を導出し、各非基準画素の電流情報から、各非基準画素の電流劣化情報(Log(Si(T2))−Log(Si(T1)))を導出する。

【0041】

次に、計測信号処理回路27は、基準画素の電流劣化情報、および各非基準画素の電流劣化情報から、時刻T2の時点における、基準画素の電流情報に対する各非基準画素の電流情報のべき係数n(Si,Ss)を導出する。続いて、計測信号処理回路27は、基準画素の電流情報から、時刻T2の時点における、基準画素の電流の経時変化を表す電流劣化関数Is(t)を導出する。さらに、計測信号処理回路27は、電流劣化関数Is(t)およびべき係数n(Si,Ss)から、時刻T2の時点における、各非基準画素の電流の経時変化を表す電流劣化関数Ii(t)を導出する。このようにして、計測信号処理回路27は、初期の電流情報を用いて、時刻T2の時点における電流劣化関数Is(t),Ii(t)を導出する。

【0042】

(データの更新)

次に、データの更新について説明する。計測信号処理回路27は、時刻Tk-1,Tkにおいて、基準画素の電流信号26Aと、複数の非基準画素の電流信号26Aを電流測定回路26から取得する。このときの基準画素の電流信号26Aの値(測定値)をSs1とする(図8参照)。次に、計測信号処理回路27は、時刻Tk-1の時点における電流劣化関数Is(t)から、時刻Tkにおける基準画素の電流情報を予測する。このときの予測値をSs2とする(図8参照)。続いて、計測信号処理回路27は、測定値Ss1と予測値Ss2とを比較して、測定値Ss1と予測値Ss2とが互いに一致するか否かを判定する。その結果、例えば、測定値Ss1が予測値Ss2と一致する場合には、計測信号処理回路27は、時刻Tk-1の時点における電流劣化関数Is(t)を、時刻Tkの時点における電流劣化関数Is(t)とする。一方、計測信号処理回路27は、測定値Ss1と予測値Ss2とを比較して、例えば、測定値Ss1が予測値Ss2と異なる場合には、計測信号処理回路27は、基準画素の電流情報から、時刻Tkの時点における電流劣化関数Is(t)を導出する。

【0043】

次に、計測信号処理回路27は、基準画素の電流情報から、基準画素の電流劣化情報(Log(Ss(Tk))−Log(Ss(Tk-1)))を導出する。さらに、計測信号処理回路27は、複数の非基準画素の電流情報から、各非基準画素の電流劣化情報(Log(Si(Tk))−Log(Si(Tk-1)))を導出する。次に、計測信号処理回路27は、基準画素の電流劣化情報、および各非基準画素の電流劣化情報から、時刻Tkの時点におけるべき係数n(Si,Ss)を導出する。

【0044】

次に、計測信号処理回路27は、時刻Tk-1の時点における電流劣化関数Is(t)のパラメータ(例えば、p1,p2,……,pm)を、時刻Tkの時点における電流劣化関数Is(t)のパラメータ(例えば、p1’,p2’,……,pm’)に更新する(図9参照)。つまり、計測信号処理回路27は、基準画素の電流情報のうち最新の電流情報(Ss(Tk))と、基準画素の電流情報のうち最新ではない電流情報(Ss(Tk-1))とに合うように、電流劣化関数Is(t)のパラメータを更新する。計測信号処理回路27は、例えば、新たに求めた電流劣化関数Is(t)のパラメータを記憶回路28に格納する。

【0045】

次に、計測信号処理回路27は、時刻Tkの時点における電流劣化関数Is(t)(図10参照)と、べき係数n(Si,Ss)(図11参照)とから、時刻Tkの時点における電流劣化関数Ii(t)を導出する(図12参照)。具体的には、計測信号処理回路27は、以下の式を用いて、時刻Tkの時点における電流劣化関数Ii(t)を導出する。

【数4】

【0046】

次に、計測信号処理回路27は、時刻Tk-1の時点における各非基準画素の電流劣化関数Ii(t)のパラメータを、時刻Tkの時点における各非基準画素の電流劣化関数Ii(t)のパラメータに更新する。計測信号処理回路27は、例えば、新たに求めた電流劣化関数Ii(t)のパラメータを記憶回路28に格納する。

【0047】

(電流劣化率の予測)

次に、計測信号処理回路27は、次のサンプリング期間が到来するまでの間、各表示画素13の電流劣化率を予測する。具体的には、計測信号処理回路27は、電流劣化関数Is(t)、電流劣化関数Ii(t)、および各表示画素13の映像信号20Aの履歴から、各表示画素13の、基準電流における発光積算時間Txyを導出する。計測信号処理回路27は、各表示画素13の、基準電流における発光積算時間Txyを、例えば、以下のようにして求める。

【0048】

図13は、各表示画素13の、基準電流における発光積算時間Txyの導出過程を模式的に表したものである。例えば、図13に示したように、ある表示画素13の輝度が、時刻T=0〜t1の間、初期電流S1(初期輝度Y1)で発光し、時刻T=t1〜t2の間、初期電流S2(初期輝度Y2)で発光し、時刻T=t2〜t3の間、初期電流Sn(初期輝度Yn)で発光したとする。このとき、この表示画素13の輝度は、厳密には、時刻T=0〜t1の間、初期電流S1の劣化曲線に沿って劣化し、時刻T=t1〜t2の間、初期電流S2の劣化曲線に沿って劣化し、時刻T=t2〜t3の間、初期電流Snの劣化曲線に沿って劣化する。その結果、この表示画素13の輝度は、例えば、図13に示したように48%まで劣化したとする。したがって、基準画素の電流劣化曲線(Is(t))において劣化率が48%となるときの時間を求めることにより、この表示画素13の、基準電流における発光積算時間Txyを求めることができる。このように、各階調における電流劣化曲線上を入力信号の大きさ(階調)に応じて追跡することにより、各表示画素13の、基準電流における発光積算時間Txy、および各表示画素13の電流劣化率を求めることができる。

【0049】

(補正量の導出)

次に、計測信号処理回路27は、求めた発光積算時間Txy(または、予測した各表示画素13の電流劣化率)と、表示パネル10ガンマ特性とから映像信号に対する補正量を導出する。計測信号処理回路27は、映像信号に対する補正量を、例えば、以下のようにして求める。

【0050】

図14は、T=0,Txyにおける階調(映像信号20Aの値)と輝度との関係の一例を表したものである。T=0における階調−輝度特性は、いわゆるガンマ特性と呼ばれるものである。T=Txyにおける階調−輝度特性は、ガンマ特性に対して、全階調において、輝度を48%にまで減衰させたものである。ここで、ある表示画素13において、映像信号20Aの値がSxyであったとすると、この表示画素13の輝度は、初期には、図中の白丸に対応する値となっていたことがわかる。つまり、この表示画素13の輝度は、初期から発光積算時間Txyだけ経過したときに、初期の輝度から48%にまで減衰した値となっている、と予測することができる。

【0051】

そこで、計測信号処理回路27は、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、映像信号20Aに掛ける電流補正量RIを導出する。具体的には、計測信号処理回路27は、以下の式を用いて、電流補正量RIを導出する。

【数5】

【0052】

数5において、GIは、電流補正ゲインであり、上の例では1/0.48である。rは、ガンマ特性の指数(ガンマ値)である。

【0053】

最後に、計測信号処理回路27は、電流補正量RIを、補正情報27Aとして記憶回路28に格納する。このようにして、計測信号処理回路27は、画素回路32に含まれる、駆動トランジスタTr1’などの半導体素子の劣化に起因する効率劣化を補正する。

【0054】

(効率補正について)

ダミー画素駆動回路25は、さらに、制御信号21Aの入力に応じて(同期して)、各ダミー画素18に互いに異なる大きさの定電流を流して各ダミー画素18を発光させるものである。ダミー画素駆動回路25は、例えば、ダミー画素18の数がn個である場合に、1番目のダミー画素18には初期輝度がY1となるような定電流を流し、2番目のダミー画素18には初期輝度がY2(>Y1)となるような定電流を流し、i番目のダミー画素18には初期輝度がYi(>Yi-1)となるような定電流を流し、n番目のダミー画素18には初期輝度がYn(>Yn-1)となるような定電流を流すようになっている。ダミー画素駆動回路25は、例えば、各ダミー画素18に電流を流した時間を計測するようになっている。

【0055】

なお、各ダミー画素18の輝度は、各ダミー画素18に定電流を流し続けた場合であっても、例えば、図15に示したように、時間の経過に伴って、徐々に低下する。これは、各ダミー画素18に含まれる有機EL素子17が通電時間(発光積算時間)に応じて劣化していく性質を有しており、その劣化の進行度に応じて発光効率が低下するからである。なお、図15中のYsは、各ダミー画素18のうち基準画素(後述)として設定された画素の初期輝度である。

【0056】

また、各ダミー画素18の効率劣化率の変移は一様ではない。例えば、図16に示したように、基準画素として設定された画素(ダミー画素18)の効率劣化率を横軸にとると、基準画素の初期輝度Ysよりも小さな初期輝度のダミー画素18の効率劣化率の変移は、当初は基準画素の効率劣化よりも緩やかであることがわかる。一方、基準画素の初期輝度Ysよりも大きな初期輝度のダミー画素18の効率劣化率の変移は、当初は基準画素の効率劣化よりも急峻であることがわかる。図16に例示した各ダミー画素18の効率劣化率の変移を式で表すと以下のようになる。

【数6】

【0057】

数6において、Diは、i番目のダミー画素18の効率劣化率である。Dsは、基準画素の効率劣化率である。n(Yi,Ys)は、基準画素の輝度に対するi番目のダミー画素18の輝度のべき係数である。べき係数n(Yi,Ys)は、例えば、以下の式に示したように、(Log(Yi(Tk))−Log(Yi(Tk-1)))を(Log(Ys(Tk))−Log(Ys(Tk-1)))で除算することにより導出される。

【数7】

【0058】

数7において、Log(Ys(Tk))はYs(Tk)の対数であり、Log(Ys(Tk-1))はYs(Tk-1)の対数であり、Log(Yi(Tk))はYi(Tk)の対数であり、Log(Yi(Tk-1))はYi(Tk-1)の対数である。

【0059】

また、数7において、Ys(Tk)は、時刻Tkにおける基準画素の受光信号19A(輝度情報)であり、基準画素の輝度情報のうちで最新の輝度情報に相当する。また、Ys(Tk-1)は、時刻Tk-1(<時刻Tk)における基準画素の受光信号19A(輝度情報)であり、基準画素の輝度情報のうちで最新ではない輝度情報に相当する。Yi(Tk)は、時刻Tkにおけるi番目のダミー画素18の受光信号19A(輝度情報)であり、i番目のダミー画素18(非基準画素)の輝度情報のうちで最新の輝度情報に相当する。Yi(Tk-1)は、時刻Tk-1におけるi番目のダミー画素18の受光信号19A(輝度情報)であり、i番目のダミー画素18(非基準画素)の輝度情報のうちで最新ではない輝度情報に相当する。時刻Tk-1と時刻Tkとの関係は、例えば、以下の式で表される。

【数8】

【0060】

数8において、ΔT2はサンプリング周期である。ここで、サンプリング周期ΔT2とは、例えば、計測信号処理回路27が数8の右辺の分母の値および分子の値を導出する周期を指している。計測信号処理回路27は、サンプリング周期ΔT2を常に一定にしている。

【0061】

上記のようにして導出したべき係数n(Yi,Ys)は、例えば、図17に示したように、横軸を、基準画素の初期輝度Ysに対する各ダミー画素16の初期輝度Yiの割合(Yi/Ys)とすると、時刻Tkにおいて、初期輝度Yiが大きくなるにつれて大きくなる右肩上がりの曲線を描く。なお、数2からも明らかなように、べき係数n(Yi,Ys)は、Ys/Ysにおいて1である。

【0062】

次に、図18〜図24を参照して、映像信号20Aの補正に用いる効率補正量Ryの導出方法について説明する。

【0063】

(初期設定)

まず、初期設定について説明する。計測信号処理回路27は、複数のダミー画素18のうちの一の画素を基準画素として設定する。本実施の形態では、この基準画素は、他のダミー画素18(非基準画素)に変更されることはなく、常に、同一のダミー画素18に設定される。

【0064】

次に、計測信号処理回路27は、時刻T1,T2において、受光素子群19から受光信号19Aを取得する。具体的には、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素18のうちの一の画素である基準画素の受光信号19Aを受光素子群19から取得する。さらに、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素18のうち基準画素を除く全ての画素である複数の非基準画素の受光信号19Aを受光素子群19から取得する。続いて、計測信号処理回路27は、基準画素の輝度情報から、基準画素の効率劣化情報(Log(Ys(T2))−Log(Ys(T1)))を導出し、各非基準画素の輝度情報から、各非基準画素の効率劣化情報(Log(Yi(T2))−Log(Yi(T1)))を導出する。

【0065】

次に、計測信号処理回路27は、基準画素の効率劣化情報、および各非基準画素の効率劣化情報から、時刻T2の時点における、基準画素の輝度情報に対する各非基準画素の輝度情報のべき係数n(Yi,Ys)を導出する。続いて、計測信号処理回路27は、基準画素の輝度情報から、時刻T2の時点における、基準画素の輝度の経時変化を表す効率劣化関数Fs(t)を導出する。さらに、計測信号処理回路27は、効率劣化関数Fs(t)およびべき係数n(Yi,Ys)から、時刻T2の時点における、各非基準画素の輝度の経時変化を表す効率劣化関数Fi(t)を導出する。このようにして、計測信号処理回路27は、初期の輝度情報を用いて、時刻T2の時点における効率劣化関数Fs(t),Fi(t)を導出する。

【0066】

(データの更新)

次に、データの更新について説明する。計測信号処理回路27は、時刻Tk-1,Tkにおいて、基準画素の受光信号19Aと、複数の非基準画素の受光信号19Aを受光素子群19から取得する。このときの基準画素の受光信号19Aの値(測定値)をYs1とする(図18参照)。次に、計測信号処理回路27は、時刻Tk-1の時点における効率劣化関数Fs(t)から、時刻Tkにおける基準画素の輝度情報を予測する。このときの予測値をYs2とする(図18参照)。続いて、計測信号処理回路27は、測定値Ys1と予測値Ys2とを比較して、測定値Ys1と予測値Ys2とが互いに一致するか否かを判定する。その結果、例えば、測定値Ys1が予測値Ys2と一致する場合には、計測信号処理回路27は、時刻Tk-1の時点における効率劣化関数Fs(t)を、時刻Tkの時点における効率劣化関数Fs(t)とする。一方、計測信号処理回路27は、測定値Ys1と予測値Ys2とを比較して、例えば、測定値Ys1が予測値Ys2と異なる場合には、計測信号処理回路27は、基準画素の輝度情報から、時刻Tkの時点における効率劣化関数Fs(t)を導出する。

【0067】

次に、計測信号処理回路27は、基準画素の輝度情報から、基準画素の効率劣化情報(Log(Ys(Tk))−Log(Ys(Tk-1)))を導出する。さらに、計測信号処理回路27は、複数の非基準画素の輝度情報から、各非基準画素の効率劣化情報(Log(Yi(Tk))−Log(Yi(Tk-1)))を導出する。次に、計測信号処理回路27は、基準画素の効率劣化情報、および各非基準画素の効率劣化情報から、時刻Tkの時点におけるべき係数n(Yi,Ys)を導出する。

【0068】

次に、計測信号処理回路27は、時刻Tk-1の時点における効率劣化関数Fs(t)のパラメータ(例えば、p1,p2,……,pm)を、時刻Tkの時点における効率劣化関数Fs(t)のパラメータ(例えば、p1’,p2’,……,pm’)に更新する(図19参照)。つまり、計測信号処理回路27は、基準画素の輝度情報のうち最新の輝度情報(Ys(Tk))と、基準画素の輝度情報のうち最新ではない輝度情報(Ys(Tk-1))とに合うように、効率劣化関数Fs(t)のパラメータを更新する。計測信号処理回路27は、例えば、新たに求めた効率劣化関数Fs(t)のパラメータを記憶回路28に格納する。

【0069】

次に、計測信号処理回路27は、時刻Tkの時点における効率劣化関数Fs(t)(図20参照)と、べき係数n(Yi,Ys)(図21参照)とから、時刻Tkの時点における効率劣化関数Fi(t)を導出する(図22参照)。具体的には、計測信号処理回路27は、以下の式を用いて、時刻Tkの時点における効率劣化関数Fi(t)を導出する。

【数9】

【0070】

次に、計測信号処理回路27は、時刻Tk-1の時点における各非基準画素の効率劣化関数Fi(t)のパラメータを、時刻Tkの時点における各非基準画素の効率劣化関数Fi(t)のパラメータに更新する。計測信号処理回路27は、例えば、新たに求めた効率劣化関数Fi(t)のパラメータを記憶回路28に格納する。

【0071】

(効率劣化率の予測)

次に、計測信号処理回路27は、次のサンプリング期間が到来するまでの間、各表示画素13の効率劣化率を予測する。具体的には、計測信号処理回路27は、効率劣化関数Fs(t)、効率劣化関数Fi(t)、および各表示画素13の映像信号20Aの履歴から、各表示画素13の、基準輝度における発光積算時間Txyを導出する。計測信号処理回路27は、各表示画素13の、基準輝度における発光積算時間Txyを、例えば、以下のようにして求める。

【0072】

図23は、各表示画素13の、基準輝度における発光積算時間Txyの導出過程を模式的に表したものである。例えば、図23に示したように、ある表示画素13の輝度が、時刻T=0〜t1の間、初期輝度Y1で発光し、時刻T=t1〜t2の間、初期輝度Y2で発光し、時刻T=t2〜t3の間、初期輝度Ynで発光したとする。このとき、この表示画素13の輝度は、厳密には、時刻T=0〜t1の間、初期輝度Y1の劣化曲線に沿って劣化し、時刻T=t1〜t2の間、初期輝度Y2の劣化曲線に沿って劣化し、時刻T=t2〜t3の間、初期輝度Ynの劣化曲線に沿って劣化する。その結果、この表示画素13の輝度は、例えば、図23に示したように48%まで劣化したとする。したがって、基準画素の効率劣化曲線(Fs(t))において劣化率が48%となるときの時間を求めることにより、この表示画素13の、基準輝度における発光積算時間Txyを求めることができる。このように、各階調における効率劣化曲線上を入力信号の大きさ(階調)に応じて追跡することにより、各表示画素13の、基準輝度における発光積算時間Txy、および各表示画素13の効率劣化率を求めることができる。

【0073】

(補正量の導出)

次に、計測信号処理回路27は、求めた発光積算時間Txy(または、予測した各表示画素13の効率劣化率)と、表示パネル10ガンマ特性とから映像信号に対する補正量を導出する。計測信号処理回路27は、映像信号に対する補正量を、例えば、以下のようにして求める。

【0074】

図24は、T=0,Txyにおける階調(映像信号20Aの値)と輝度との関係の一例を表したものである。T=0における階調−輝度特性は、いわゆるガンマ特性と呼ばれるものである。T=Txyにおける階調−輝度特性は、ガンマ特性に対して、全階調において、輝度を48%にまで減衰させたものである。ここで、ある表示画素13において、映像信号20Aの値がSxyであったとすると、この表示画素13の輝度は、初期には、図中の白丸に対応する値となっていたことがわかる。つまり、この表示画素13の輝度は、初期から発光積算時間Txyだけ経過したときに、初期の輝度から48%にまで減衰した値となっている、と予測することができる。

【0075】

そこで、計測信号処理回路27は、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、映像信号20Aに掛ける効率補正量Ryを導出する。具体的には、計測信号処理回路27は、以下の式を用いて、効率補正量Ryを導出する。

【数10】

【0076】

数5において、Gyは、輝度補正ゲインであり、上の例では1/0.48である。

【0077】

最後に、計測信号処理回路27は、効率補正量Ryを、補正情報27Aとして記憶回路28に格納する。このようにして、計測信号処理回路27は、各ダミー画素18に含まれる有機EL素子17の劣化に起因する発光効率の劣化を補正する。

【0078】

(動作・効果)

次に、本実施の形態の表示装置1の動作および効果について説明する。表示装置1に対して映像信号20Aおよび同期信号20Bが入力される。すると、信号線駆動回路23および走査線駆動回路24によって各表示画素13が駆動され、各表示画素13の映像信号20Aに応じた映像が表示領域12に表示される。一方で、ダミー画素駆動回路25によって、各ダミー画素16に接続された信号線DTL’に互いに異なる大きさの信号電圧Vsigi(一定値)が印加され、各ダミー画素16が互いに異なる階調で発光する。その結果、電流測定回路26から、各ダミー画素16の有機EL素子13に流れる電流値に対応する電流信号26Aが出力される。さらに、ダミー画素駆動回路25によって、各ダミー画素18が駆動されると同時に受光素子群19も駆動される。これにより、各ダミー画素18に、互いに異なる大きさの定電流が流され、その定電流の大きさに応じた輝度で各ダミー画素18が発光し、各ダミー画素18の発光光が受光素子群19で検知される。その結果、受光素子群19から、各ダミー画素18の発光光に対応する受光信号19Aが出力される。次に、計測信号処理回路27によって、以下の処理が行われる。

【0079】

すなわち、電流信号26Aから、基準画素の電流信号26A(電流情報)に対する非基準画素の電流信号26A(電流情報)のべき係数n(Si,Ss)が導出される。次に、基準画素の電流情報から基準画素の電流劣化関数Is(t)が導出されると共に、電流劣化関数Is(t)およびべき係数n(Si,Ss)から非基準画素の電流劣化関数Ii(t)が導出される。次に、電流劣化関数Is(t)と、電流劣化関数Ii(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の、基準電流における発光積算時間Txyおよび各表示画素13の電流劣化率が予測される。次に、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、各表示画素13の映像信号20Aに対して電流補正量RIが掛けられる。

【0080】

さらに、受光信号19Aから、基準画素の受光信号19A(輝度情報)に対する非基準画素の受光信号19A(輝度情報)のべき係数n(Yi,Ys)が導出される。次に、基準画素の輝度情報から基準画素の効率劣化関数Fs(t)が導出されると共に、効率劣化関数Fs(t)およびべき係数n(Yi,Ys)から非基準画素の効率劣化関数Fi(t)が導出される。次に、効率劣化関数Fs(t)と、効率劣化関数Fi(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の、基準輝度における発光積算時間Txyおよび各表示画素13の効率劣化率が予測される。次に、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、各表示画素13の映像信号20Aに対して効率補正量Ryが掛けられる。

【0081】

このように、本実施の形態では、電流劣化関数Is(t)と、電流劣化関数Is(t)およびべき係数n(Si,Ss)から得られた効率劣化関数Ii(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の電流劣化率が予測される。さらに、効率劣化関数Fs(t)と、効率劣化関数Fs(t)およびべき係数n(Yi,Ys)から得られた効率劣化関数Fi(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の効率劣化率が予測される。これにより、高い精度で各表示画素13の効率劣化を予測することができるので、各表示画素13の輝度が初期の輝度となるように、各表示画素13の映像信号20Aに対して的確な補正量(電流補正量RIおよび効率補正量Ry)を掛けることができる。その結果、正確に焼き付きを防止することができる。

【0082】

また、本実施の形態では、観測時点のデータ(Ss(Tk)、Ss(Tk-1)、Ys(Tk)、Ys(Tk-1))で、各表示画素13の電流劣化率および効率劣化率を予測することができる。これにより、長時間観測をすることなく、高い精度で各表示画素の効率劣化を予測することができる。従って、本実施の形態の予測方法は、極めて現実的である。また、本実施の形態では、観測時点のデータで、各表示画素13の効率劣化率を予測することができることから、更新に必要なメモリ量および計算量を小さく抑えることができる。

【0083】

<変形例>

上記実施の形態では、各表示画素13の映像信号20Aに対して、電流補正量RIおよび効率補正量Ryの双方の補正がなされていたが、電流補正量RIおよび効率補正量Ryのいずれか一方の補正だけが実行されてもよい。

【0084】

また、上記実施の形態では、初期電流S1〜Snの全てのダミー画素16が、有機EL素子14R,14G,14Bを一組とする単一の画素によって構成されていたが、初期電流Siの低い各ダミー画素16(低電流画素)を複数のダミー画素(第2ダミー画素)(図示せず)によって構成してもよい。このようにした場合には、計測信号処理回路27は、複数の第2ダミー画素に接続された有機EL素子13に流れる電流の平均値から、数2の右辺の分母または分子を導出することが可能である。これにより、低輝度のダミー画素16における測定誤差を小さくすることができるので、高い精度で低輝度の表示画素13の効率劣化を予測することができる。その結果、焼き付きをより一層、正確に防止することができる。

【0085】

また、上記実施の形態では、初期輝度Y1〜Ynの全てのダミー画素18が、有機EL素子17R,17G,17Bを一組とする単一の画素によって構成されていたが、初期輝度Yiの低い各ダミー画素18(低輝度画素)を複数のダミー画素(第3ダミー画素)(図示せず)によって構成してもよい。このようにした場合には、計測信号処理回路27は、複数の第3ダミー画素の輝度の平均値から、数7の右辺の分母または分子を導出することが可能である。これにより、低輝度のダミー画素18における測定誤差を小さくすることができるので、高い精度で低輝度の表示画素13の効率劣化を予測することができる。その結果、焼き付きをより一層、正確に防止することができる。

【0086】

また、上記実施の形態では、常に特定のダミー画素16が基準画素となっていたが、必要に応じて、今まで非基準画素であったダミー画素16が基準画素となってもよい。例えば、計測信号処理回路27は、基準画素に接続された有機EL素子13に流れる電流が所定の値以下となったことを検知したときには、今まで基準画素として設定されていたダミー画素16を除外すると共に複数の非基準画素のうちの一の画素を新たな基準画素に設定する。その後は、計測信号処理回路27は、今までと同様にして、数2の右辺の分母および分子を導出する。このようにした場合には、基準画素に不具合が生じた場合でも、継続して、効率劣化を予測することができる。これにより、効率劣化の予測の信頼性を高めることができる。

【0087】

また、上記実施の形態では、常に特定のダミー画素18が基準画素となっていたが、必要に応じて、今まで非基準画素であったダミー画素18が基準画素となってもよい。例えば、計測信号処理回路27は、基準画素の輝度が所定の値以下となったことを検知したときには、今まで基準画素として設定されていたダミー画素18を除外すると共に複数の非基準画素のうちの一の画素を新たな基準画素に設定する。その後は、計測信号処理回路27は、今までと同様にして、数7の右辺の分母および分子を導出する。このようにした場合には、基準画素に不具合が生じた場合でも、継続して、効率劣化を予測することができる。これにより、効率劣化の予測の信頼性を高めることができる。

【0088】

また、上記実施の形態では、サンプリング周期ΔT1が常に一定となっていたが、可変であってもよい。例えば、計測信号処理回路27が、サンプリング周期ΔT1を複数のダミー画素16の発光累積時間に応じて変化させてもよい。そのようにした場合には、例えば、発光累積時間Txyが長時間に達し、効率劣化があまり生じなくなったときに、サンプリング周期ΔT1を長くすることができる。これにより、更新に必要な計算量を小さく抑えることができる。

【0089】

また、上記実施の形態では、サンプリング周期ΔT2が常に一定となっていたが、可変であってもよい。例えば、計測信号処理回路27が、サンプリング周期ΔT2を複数のダミー画素18の発光累積時間に応じて変化させてもよい。そのようにした場合には、例えば、発光累積時間Txyが長時間に達し、効率劣化があまり生じなくなったときに、サンプリング周期ΔT2を長くすることができる。これにより、更新に必要な計算量を小さく抑えることができる。

【0090】

また、上記実施の形態では、数2を用いて、べき係数n(Si,Ss)は導出されていたが、例えば、以下の式を用いて、べき係数n(Si,Ss)が導出されてもよい。

【数11】

【数12】

【0091】

数11において、右辺第2項の分母は、時刻Tkにおける基準画素の劣化速度である。右辺第2項の分子は、時刻Tkにおける非基準画素の劣化速度である。数12において、右辺第2項は、時刻Tkにおける基準画素の劣化速度を、時刻Tkにおける非基準画素の劣化速度で除算することにより得られたものである。

【0092】

数11または数12を用いて、べき係数n(Si,Ss)を導出するようにした場合には、四則演算だけで、べき係数n(Si,Ss)を導出することができ、数2を用いたときのような対数の計算が不要である。従って、本変形例では、数2を用いてべき係数n(Si,Ss)を導出した場合よりも、計算量を小さく抑えることができる。

【0093】

また、上記実施の形態では、数7を用いて、べき係数n(Yi,Ys)は導出されていたが、例えば、以下の式を用いて、べき係数n(Yi,Ys)が導出されてもよい。

【数13】

【数14】

【0094】

数13において、右辺第2項の分母は、時刻Tkにおける基準画素の劣化速度である。右辺第2項の分子は、時刻Tkにおける非基準画素の劣化速度である。数14において、右辺第2項は、時刻Tkにおける基準画素の劣化速度を、時刻Tkにおける非基準画素の劣化速度で除算することにより得られたものである。

【0095】

数13または数14を用いて、べき係数n(Yi,Ys)を導出するようにした場合には、四則演算だけで、べき係数n(Yi,Ys)を導出することができ、数7を用いたときのような対数の計算が不要である。従って、本変形例では、数7を用いてべき係数n(Yi,Ys)を導出した場合よりも、計算量を小さく抑えることができる。

【0096】

<適用例>

以下、上記実施の形態およびその変形例で説明した表示装置1の適用例について説明する。上記実施の形態等の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0097】

(適用例1)

図25は、上記実施の形態等の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記実施の形態等の表示装置1により構成されている。

【0098】

(適用例2)

図26は、上記実施の形態等の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上記実施の形態等の表示装置1により構成されている。

【0099】

(適用例3)

図27は、上記実施の形態等の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、その表示部530は、上記実施の形態等の表示装置1により構成されている。

【0100】

(適用例4)

図28は、上記実施の形態等の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上記実施の形態等の表示装置1により構成されている。

【0101】

(適用例5)

図29は、上記実施の形態等の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記実施の形態等の表示装置1により構成されている。

【符号の説明】

【0102】

1…表示装置、10…表示パネル、11,11R,11G,11B,14,14R,14G,14B,17,17R,17G,17B…有機EL素子、12…表示領域、13…表示画素、15…非表示領域、16,18…ダミー画素、19…受光素子群、19A…受光信号、20…駆動回路、20A,22A…映像信号、20B…同期信号、21…タイミング生成回路、21A…制御信号、22…映像信号処理回路、23…信号線駆動回路、24…走査線駆動回路、25…ダミー画素駆動回路、26…電流測定回路、26A…電流信号、27…計測信号処理回路、27A…補正情報、28…記憶回路、30…駆動パネル、31,32…画素回路、40…封止パネル、51…映像信号供給TAB、52…走査信号供給TAB、53…電源供給TCP、54…制御信号供給TCP、55…計測信号出力TCP、A,B…曲線、Cs…保持容量、D,Ds,Dx,Dsi,Dss…効率劣化率、DTL,DTL’…信号線、Fi(t),Fs(t)…効率劣化関数、GND…グラウンド線、Ii(t),Is(t)…電流劣化関数、n(Yi,Ys),n(Si,Ss)…べき係数、RI…電流補正量、Ry…効率補正量、Sxy…映像信号、T1,T2,Tx,Tk,Tk-1…時刻、Tr1,Tr1’…駆動トランジスタ、Tr2,Tr2’…書き込みトランジスタ、Txy…発光積算時間、Vcc,Vcc’…電源線、Vsigi…信号電圧、WSL,WSL’…走査線、Ss1,Ys1…測定値、Ss2,Ys2…予測値、S1,S2,Si,Ss,Sn…初期電流、Y1,Y2,Yi,Ys,Yn…初期輝度、Si(Tk),Si(Tk-1),Ss(Tk),Ss(Tk-1)…電流情報、Yi(Tk),Yi(Tk-1),Ys(Tk),Ys(Tk-1)…輝度情報、ΔT1,ΔT2…サンプリング周期。

【技術分野】

【0001】

本発明は、表示パネルに発光素子が設けられた表示装置に関する。

【背景技術】

【0002】

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL(electro luminescence)素子を用いた表示装置が開発され、商品化が進められている。有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置(有機EL表示装置)では、光源(バックライト)が必要ないので、光源を必要とする液晶表示装置と比べて、薄型化、高輝度化することができる。特に、駆動方式としてアクティブマトリクス方式を用いた場合には、各画素をホールド点灯させることができ、低消費電力化することもできる。そのため、有機EL表示装置は、次世代のフラットパネルディスプレイの主流になると期待されている。

【0003】

しかし、有機EL素子では、通電する電流量に応じて素子が劣化し、輝度が低下するという問題がある。そのため、有機EL素子を表示装置の画素として用いた場合には、画素ごとに劣化の状況が異なることがある。例えば、時刻や表示チャンネルなどの情報が長時間、同じ場所に高輝度で表示されていた場合には、その部分の画素だけ劣化が早まる。その結果、劣化の早まった画素を含む部分に高輝度の映像が表示された場合には、劣化の早まった画素の部分だけが暗く表示される焼き付きという現象が生じてしまう。この焼き付きは非可逆性であることから、一旦、焼き付きが生じると、焼き付きが消えることはない。

【0004】

焼き付きを防止する手法は、今までに多数提案されている。例えば、特許文献1では、表示領域外にダミー画素を設け、ダミー画素を発光させたときの端子電圧を検出することによりダミー画素の劣化度合いを見積もり、その見積もりを利用して映像信号を補正する方法が開示されている。また、例えば、特許文献2,3では、各表示画素内に光センサを配置し、光センサから出力される受光信号を利用して映像信号を補正する方法が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−351403号公報

【特許文献2】特開2008−58446号公報

【特許文献3】国際公開番号WO2006/046196

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、特許文献1の手法では、表示領域内の画素の発光情報に基づいて画素の劣化度合いが見積もられておらず、映像信号を正確に補正することが不可能であることから、焼き付きを防止することはできないという問題があった。また、特許文献2,3の手法では、各画素内の光センサの光電変換効率がばらつくので、例えば、同一輝度を表示している2つの画素において、受光信号の大きさが異なってしまうことがある。その結果、正確に焼き付きを防止することができないという問題があった。

【0007】

本発明はかかる問題点に鑑みてなされたものであり、その目的は、正確に焼き付きを防止することの可能な表示装置を提供することにある。

【課題を解決するための手段】

【0008】

本発明による表示装置は、複数の表示画素が2次元配置された表示領域と、複数の第1ダミー画素および複数の第2ダミー画素が配置された非表示領域とを有する表示パネルを備えたものである。この表示装置は、また、各第1ダミー画素に互いに異なる大きさの信号電圧を印加して各第1ダミー画素を発光させる第1駆動部と、各第2ダミー画素に互いに異なる大きさの定電流を流して各第2ダミー画素を発光させる第2駆動部とを備えている。この表示装置は、さらに、各第1ダミー画素に流れる電流を検知して各第1ダミー画素の電流情報を出力する電流測定部と、各第2ダミー画素の発光光を検知して各第2ダミー画素の輝度情報を出力する受光部と、電流情報を用いて電流劣化関数を導出すると共に、輝度情報を用い効率劣化関数を導出する演算部とを備えている。

【0009】

本発明による表示装置では、表示パネルの非表示領域に設けられた各第1ダミー画素に、互いに異なる大きさの信号電圧が印加され、その信号電圧の大きさに応じた輝度で各第1ダミー画素が発光し、各第1ダミー画素に流れる電流が電流測定部で検知され、各第1ダミー画素の電流情報が電流測定部から出力される。また、表示パネルの非表示領域に設けられた各第2ダミー画素に、互いに異なる大きさの定電流が流され、その定電流の大きさに応じた輝度で各第2ダミー画素が発光し、各第2ダミー画素の発光光が受光部で検知され、各第2ダミー画素の輝度情報が受光部から出力される。その後、電流情報を用いて電流劣化関数が導出されると共に、輝度情報を用い効率劣化関数が導出される。これにより、例えば、電流劣化関数、および各表示画素の映像信号の履歴から、各表示画素の電流劣化率を予測することができる。また、効率劣化関数、および各表示画素の映像信号の履歴から、各表示画素の効率劣化率を予測することができる。

【0010】

ここで、本発明による表示装置において、電流劣化関数を導出する周期は、前記効率劣化関数を導出する周期よりも短くなっていることが好ましい。このようにした場合には、電流が補正された状態で、効率劣化を補正することができる。

【図面の簡単な説明】

【0011】

【図1】本発明による一実施の形態に係る表示装置の構成の一例を表す概略図である。

【図2】表示領域の画素回路の構成の一例を表す概略図である。

【図3】非表示領域の画素回路の構成の一例を表す概略図である。

【図4】図1の表示パネルの構成の一例を表す上面図である。

【図5】電流劣化率の経時変化の一例を初期電流ごとに表す特性図である。

【図6】電流劣化率と、初期電流SSのダミー画素の電流劣化率との関係の一例を表す関係図である。

【図7】べき係数n(Si,Ss)と、初期電流の割合Si/Ssとの関係の一例を表す関係図である。

【図8】時刻Tkでの電流劣化率の予測値SS2と、時刻Tkでの電流劣化率の測定値SS1との関係の一例を表す関係図である。

【図9】時刻Tk-1での電流劣化関数Is(t)と、時刻Tkでの電流劣化関数Is(t)との関係の一例を表す関係図である。

【図10】べき係数の算定方法の一例について説明するための概念図である。

【図11】時刻Tk-1でのべき係数n(Si,Ss)と、時刻Tkでのべき係数n(Si,Ss)との関係の一例を表す関係図である。

【図12】電流劣化関数Ii(t)の算定方法の一例について説明するための概念図である。

【図13】基準輝度における累積発光時間Txyの導出方法の一例について説明するための概念図である。

【図14】電流補正量RIの導出方法の一例について説明するための概念図である。

【図15】効率劣化率の経時変化の一例を初期輝度ごとに表す特性図である。

【図16】効率劣化率と、初期輝度YSのダミー画素の効率劣化率との関係の一例を表す関係図である。

【図17】べき係数n(Yi,Ys)と、初期輝度の割合Yi/Ysとの関係の一例を表す関係図である。

【図18】時刻Tkでの効率劣化率の予測値YS2と、時刻Tkでの効率劣化率の測定値YS1との関係の一例を表す関係図である。

【図19】時刻Tk-1での効率劣化関数Fs(t)と、時刻Tkでの効率劣化関数Fs(t)との関係の一例を表す関係図である。

【図20】べき係数の算定方法の一例について説明するための概念図である。

【図21】時刻Tk-1でのべき係数n(Yi,Ys)と、時刻Tkでのべき係数n(Yi,Ys)との関係の一例を表す関係図である。

【図22】効率劣化関数Fi(t)の算定方法の一例について説明するための概念図である。

【図23】基準輝度における累積発光時間Txyの導出方法の一例について説明するための概念図である。

【図24】効率補正量Ryの導出方法の一例について説明するための概念図である。

【図25】上記実施の形態の発光装置の適用例1の外観を表す斜視図である。

【図26】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図27】適用例3の外観を表す斜視図である。

【図28】適用例4の外観を表す斜視図である。

【図29】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0012】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

1.実施の形態(図1〜図24)

2.変形例(図なし)

・初期電流Siの低い各ダミー画素16を複数のダミー画素で構成した例

・初期輝度Yiの低い各ダミー画素18を複数のダミー画素で構成した例

・基準画素に不具合が生じた場合に別のダミー画素16を新たな基準画素に設定 するようにした例

・基準画素に不具合が生じた場合に別のダミー画素18を新たな基準画素に設定 するようにした例

・サンプリング周期ΔT1を可変にした例

・サンプリング周期ΔT2を可変にした例

・四則演算だけで、べき係数n(Si,Ss)を導出するようにした例

・四則演算だけで、べき係数n(Yi,Ys)を導出するようにした例

3.適用例(図25〜図29)

【0013】

<実施の形態>

(表示装置1の概略構成)

図1は、本発明の第1の実施の形態に係る表示装置1の概略構成を表したものである。この表示装置1は、表示パネル10と、表示パネル10を駆動する駆動回路20とを備えている。

【0014】

表示パネル10は、複数の有機EL素子11R,11G,11Bが2次元配置された表示領域12を有している。本実施の形態では、互いに隣り合う3つの有機EL素子11R,11G,11Bが1つの画素(表示画素13)を構成している。なお、以下では、有機EL素子11R,11G,11Bの総称として有機EL素子11を適宜、用いるものとする。表示パネル10は、また、複数の有機EL素子14R,14G,14Bが2次元配置された非表示領域15を有している。本実施の形態では、互いに隣り合う3つの有機EL素子14R,14G,14Bが1つの画素(ダミー画素16)を構成している。なお、以下では、有機EL素子14R,14G,14Bの総称として有機EL素子13を適宜、用いるものとする。

【0015】

非表示領域15には、さらに、複数の有機EL素子17R,17G,17Bが2次元配置されている。本実施の形態では、互いに隣り合う3つの有機EL素子17R,17G,17Bが1つの画素(ダミー画素18)を構成している。なお、以下では、有機EL素子17R,17G,17Bの総称として有機EL素子17を適宜、用いるものとする。非表示領域15には、有機EL素子17R,17G,17Bから発せられた光を受光する受光素子群19(受光部)が設けられている。受光素子群19は、例えば、図示しないが、複数の受光素子からなる。複数の受光素子は、例えば、個々の有機EL素子17と対となって2次元配置されており、各受光素子は、各ダミー画素18(各有機EL素子17)から発せられた光(発光光)を検知して、各ダミー画素18の受光信号19A(輝度情報)を出力するようになっている。各受光素子は、例えば、フォトダイオードである。

【0016】

駆動回路20は、タイミング生成回路21、映像信号処理回路22、信号線駆動回路23、走査線駆動回路24、ダミー画素駆動回路25、電流測定回路26、計測信号処理回路27および記憶回路28を有している。

【0017】

(画素回路31)

図2は、表示領域12内の回路構成の一例を表したものである。表示領域12内には、複数の画素回路31が個々の有機EL素子11と対となって2次元配置されている。各画素回路31は、例えば、駆動トランジスタTr1、書き込みトランジスタTr2および保持容量Csによって構成されたものであり、2Tr1Cの回路構成となっている。駆動トランジスタTr1および書き込みトランジスタTr2は、例えば、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor))により形成されている。駆動トランジスタTr1または書き込みトランジスタTr2は、pチャネルMOS型のTFTであってもよい。

【0018】

表示領域12において、列方向には信号線DTLが複数配置され、行方向には走査線WSLおよび電源線Vccがそれぞれ複数配置されている。各信号線DTLと各走査線WSLとの交差点近傍には、有機EL素子11R,11G,11Bのいずれか一つ(サブピクセル)が設けられている。各信号線DTLは、信号線駆動回路23の出力端(図示せず)と、書き込みトランジスタTr2のドレイン電極(図示せず)に接続されている。各走査線WSLは、走査線駆動回路24の出力端(図示せず)と、書き込みトランジスタTr2のゲート電極(図示せず)に接続されている。各電源線Vccは、電源の出力端(図示せず)と、駆動トランジスタTr1のドレイン電極(図示せず)に接続されている。書き込みトランジスタTr2のソース電極(図示せず)は、駆動トランジスタTr1のゲート電極(図示せず)と、保持容量Csの一端に接続されている。駆動トランジスタTr1のソース電極(図示せず)と保持容量Csの他端とが、有機EL素子11のアノード電極(図示せず)に接続されている。有機EL素子11のカソード電極(図示せず)は、例えば、グラウンド線GNDに接続されている。

【0019】

図3は、非表示領域15内の回路構成の一例を表したものである。非表示領域15内には、画素回路31と同一構成の複数の画素回路32が個々の有機EL素子13と対となって2次元配置されている。各画素回路32は、例えば、駆動トランジスタTr1’、書き込みトランジスタTr2’および保持容量Cs’によって構成されたものであり、2Tr1Cの回路構成となっている。駆動トランジスタTr1’および書き込みトランジスタTr2’は、例えば、nチャネルMOS型のTFTにより形成されている。駆動トランジスタTr1’または書き込みトランジスタTr2’は、pチャネルMOS型のTFTであってもよい。

【0020】

非表示領域15においても、列方向には信号線DTL’が複数配置され、行方向には走査線WSL’および電源線Vcc’がそれぞれ複数配置されている。各信号線DTL’と各走査線WSL’との交差点近傍には、有機EL素子14R,14G,14Bのいずれか一つ(サブピクセル)が設けられている。各信号線DTL’は、ダミー画素駆動回路25の出力端(図示せず)と、書き込みトランジスタTr2’のドレイン電極(図示せず)に接続されている。各走査線WSL’は、ダミー画素駆動回路25の出力端(図示せず)と、書き込みトランジスタTr2’のゲート電極(図示せず)に接続されている。各電源線Vcc’は、電源の出力端(図示せず)と、駆動トランジスタTr1’のドレイン電極(図示せず)に接続されている。書き込みトランジスタTr2’のソース電極(図示せず)は、駆動トランジスタTr1’のゲート電極(図示せず)と、保持容量Cs’の一端に接続されている。駆動トランジスタTr1’のソース電極(図示せず)と保持容量Cs’の他端とが、有機EL素子13のアノード電極(図示せず)に接続されている。有機EL素子13のカソード電極(図示せず)は、例えば、グラウンド線GNDに接続されている。

【0021】

(表示パネル10の上面構成)

図4は、表示パネル10の上面構成の一例を表したものである。表示パネル10は、例えば、駆動パネル30と封止パネル40とが封止層(図示せず)を介して貼り合わされた構造となっている。

【0022】

駆動パネル30は、図4に示していないが、表示領域12に、2次元配置された複数の有機EL素子11と、各有機EL素子11に隣接して配置された複数の画素回路31とを有している。駆動パネル30は、また、図4に示していないが、非表示領域15に、2次元配置された複数の有機EL素子13,16と、各有機EL素子17に隣接して配置された複数の受光素子とを有している。

【0023】

駆動パネル30の一辺(長辺)には、例えば、図4に示したように、複数の映像信号供給TAB51と、制御信号供給TCP54と、計測信号出力TCP55とが取り付けられている。駆動パネル30の他の辺(短辺)には、例えば、走査信号供給TAB52が取り付けられている。また、駆動パネル30の一辺(長辺)であって、かつ映像信号供給TAB51とは異なる辺には、例えば、電源供給TCP53が取り付けられている。映像信号供給TAB51は、信号線駆動回路23の集積されたICをフィルム状の配線基板の開口に中空配線したものである。走査信号供給TAB52は、走査線駆動回路24の集積されたICをフィルム状の配線基板の開口に中空配線したものである。電源供給TCP53は、外部の電源と電源線Vcc,Vcc’とを互いに電気的に接続する複数の配線がフィルム上に形成されたものである。制御信号供給TCP54は、外部のダミー画素駆動回路25と、ダミー画素16,17および受光素子群19とを互いに電気的に接続する複数の配線がフィルム上に形成されたものである。計測信号出力TCP55は、外部の計測信号処理回路27と、受光素子群19とを互いに電気的に接続する複数の配線がフィルム上に形成されたものである。なお、信号線駆動回路23および走査線駆動回路24は、TABに形成されていなくてもよく、例えば、駆動パネル30に形成されていてもよい。

【0024】

封止パネル40は、例えば、有機EL素子11,13,16を封止する封止基板(図示せず)と、カラーフィルタ(図示せず)とを有している。カラーフィルタは、例えば、封止基板の表面のうち有機EL素子11の光が通過する領域に設けられている。カラーフィルタは、例えば、有機EL素子11R,11G,11Bのそれぞれに対応して、赤色用のフィルタ、緑色用のフィルタおよび青色用のフィルタ(図示せず)を有している。封止パネル40は、例えば、さらに、光反射部(図示せず)を有している。光反射部は、有機EL素子17から発せられた光を反射して、受光素子群19に入射させるものであり、例えば、封止基板の表面のうち有機EL素子17の光が通過する領域に設けられている。

【0025】

(駆動回路20)

次に、駆動回路20内の各回路について、図1を参照して説明する。タイミング生成回路21は、映像信号処理回路22、信号線駆動回路23、走査線駆動回路24、ダミー画素駆動回路25、電流測定回路26および計測信号処理回路27が連動して動作するように制御するものである。

【0026】

タイミング生成回路21は、例えば、外部から入力された同期信号20Bに応じて(同期して)、上述した各回路に対して制御信号21Aを出力するようになっている。タイミング生成回路21は、例えば、映像信号処理回路22、ダミー画素駆動回路25、電流測定回路26、計測信号処理回路27および記憶回路28などと共に、例えば、表示パネル10とは別体の制御回路基板(図示せず)上に形成されている。

【0027】

映像信号処理回路22は、例えば、制御信号21Aの入力に応じて(同期して)、外部から入力されたデジタルの映像信号20Aを補正すると共に、補正した後の映像信号をアナログに変換して信号線駆動回路23に出力するものである。本実施の形態では、映像信号処理回路22は、記憶回路28から読み出した補正情報27A(後述)を用いて映像信号20Aを補正するようになっている。映像信号処理回路22は、例えば、一水平期間ごとに、記憶回路28から、補正情報27Aとして1ライン分の各表示画素13の補正量(電流補正量RI,効率補正量Ry)(後述)を読み出し、読み出した補正量(電流補正量RI,効率補正量Ry)を用いて映像信号20Aを補正し、補正後の映像信号22Aを信号線駆動回路23に出力するようになっている。

【0028】

信号線駆動回路23は、映像信号処理回路22から入力されたアナログの映像信号22Aを、制御信号21Aの入力に応じて(同期して)各信号線DTLに出力するものである。信号線駆動回路23は、例えば、図4に示したように、駆動パネル30の一辺(長辺)に取り付けられた映像信号供給TAB51に設けられている。走査線駆動回路24は、制御信号21Aの入力に応じて(同期して)、複数の走査線WSLの中から一の走査線WSLを順次選択するものである。走査線駆動回路24は、例えば、図4に示したように、駆動パネル30の他の辺(短辺)に取り付けられた走査信号供給TAB52に設けられている。

【0029】

計測信号処理回路27は、受光素子群19から入力された受光信号19Aに基づいて、補正情報27Aを導出し、導出した補正情報27Aを、制御信号21Aの入力に応じて(同期して)記憶回路28に出力するようになっている。なお、補正情報27Aの導出方法については、後に詳述する。記憶回路28は、計測信号処理回路27から入力された補正情報27Aを格納するものである。記憶回路28は、格納した補正情報27Aを、映像信号処理回路22によって読み出すことができるようになっている。

【0030】

(電流補正について)

ダミー画素駆動回路25は、制御信号21Aの入力に応じて(同期して)、各ダミー画素16に接続された信号線DTL’に互いに異なる大きさの信号電圧Vsigi(一定値)を印加して各ダミー画素16を互いに異なる階調で発光させるものである。ダミー画素駆動回路25は、例えば、ダミー画素16の数がn個である場合に、1番目のダミー画素16には初期階調がS1となるような定電流を流し、2番目のダミー画素16には初期階調がS2(>S1)となるような定電流を流し、i番目のダミー画素16には初期階調がSi(>Si-1)となるような定電流を流し、n番目のダミー画素16には初期階調がSn(>Sn-1)となるような定電流を流すようになっている。ダミー画素駆動回路25は、例えば、各ダミー画素16を発光させた時間を計測するようになっている。

【0031】

なお、各ダミー画素16の輝度は、各ダミー画素16に接続された信号線DTL’に一定の値の信号電圧Vsigiを印加し続けた場合であっても、例えば、図5に示したように、時間の経過に伴って、徐々に低下する。これは、各ダミー画素16に接続された画素回路32に含まれる、駆動トランジスタTr1’などの半導体素子が通電時間(通電積算時間)に応じて劣化していく性質を有しており、その劣化の進行度に応じて電流が流れにくくなるからである。なお、図5中のSsは、各ダミー画素16のうち基準画素(後述)として設定された画素内の有機EL素子13に流れる初期電流である。

【0032】

また、各ダミー画素16内の有機EL素子13に流れる電流の劣化率(電流劣化率)の変移は一様ではない。例えば、図6に示したように、基準画素として設定された画素(ダミー画素16)の電流劣化率を横軸にとると、基準画素の初期電流Ssよりも小さな初期輝度のダミー画素16の電流劣化率の変移は、当初は基準画素の電流劣化よりも緩やかであることがわかる。一方、基準画素の初期電流Ssよりも大きな初期電流のダミー画素16の電流劣化率の変移は、当初は基準画素の電流劣化よりも急峻であることがわかる。図6に例示した各ダミー画素18の電流劣化率の変移を式で表すと以下のようになる。

【数1】

【0033】

数1において、Dsiは、i番目のダミー画素16の電流劣化率である。Dssは、基準画素の電流劣化率である。n(Si,Ss)は、基準画素の電流に対するi番目のダミー画素16の電流のべき係数である。べき係数n(Si,Ss)は、例えば、以下の式に示したように、(Log(Si(Tk))−Log(Si(Tk-1)))を(Log(Ss(Tk))−Log(Ys(Sk-1)))で除算することにより導出される。

【数2】

【0034】

数2において、Log(Ss(Tk))はSs(Tk)の対数であり、Log(Ss(Tk-1))はSs(Tk-1)の対数であり、Log(Si(Tk))はSi(Tk)の対数であり、Log(Si(Tk-1))はSi(Tk-1)の対数である。

【0035】

また、数2において、Ss(Tk)は、時刻Tkにおける基準画素の電流信号26A(輝度情報)であり、基準画素の電流情報のうちで最新の電流情報に相当する。また、Ys(Tk-1)は、時刻Tk-1(<時刻Tk)における基準画素の電流信号26A(電流情報)であり、基準画素の電流情報のうちで最新ではない電流情報に相当する。Si(Tk)は、時刻Tkにおけるi番目のダミー画素16の電流信号26A(電流情報)であり、i番目のダミー画素16(非基準画素)の電流情報のうちで最新の電流情報に相当する。Si(Tk-1)は、時刻Tk-1におけるi番目のダミー画素16の電流信号26A(電流情報)であり、i番目のダミー画素16(非基準画素)の電流情報のうちで最新ではない電流情報に相当する。時刻Tk-1と時刻Tkとの関係は、例えば、以下の式で表される。

【数3】

【0036】

数3において、ΔT1はサンプリング周期である。ここで、サンプリング周期ΔT1とは、例えば、計測信号処理回路27が数2の右辺の分母の値および分子の値を導出する周期を指している。サンプリング周期ΔT1は、後述のサンプリング周期ΔT2よりも短くなっていることが好ましい。計測信号処理回路27は、サンプリング周期ΔT1を常に一定にしている。

【0037】

上記のようにして導出したべき係数n(Si,Ss)は、例えば、図7に示したように、横軸を、基準画素の初期電流Ssに対する各ダミー画素16の初期電流Siの割合(Si/Ss)とすると、時刻Tkにおいて、初期電流Siが大きくなるにつれて大きくなる右肩上がりの曲線を描く。なお、数2からも明らかなように、べき係数n(Si,Ss)は、Ss/Ssにおいて1である。

【0038】

次に、図8〜図14を参照して、映像信号20Aの補正に用いる電流補正量RIの導出方法について説明する。

【0039】

(初期設定)

まず、初期設定について説明する。計測信号処理回路27は、複数のダミー画素16のうちの一の画素を基準画素として設定する。本実施の形態では、この基準画素は、他のダミー画素16(非基準画素)に変更されることはなく、常に、同一のダミー画素16に設定される。

【0040】

次に、計測信号処理回路27は、時刻T1,T2において、電流測定回路26から電流信号26Aを取得する。具体的には、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素16のうちの一の画素である基準画素の電流信号26Aを電流測定回路26から取得する。さらに、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素16のうち基準画素を除く全ての画素である複数の非基準画素の電流信号26Aを電流測定回路26から取得する。続いて、計測信号処理回路27は、基準画素の電流情報から、基準画素の電流劣化情報(Log(Ss(T2))−Log(Ss(T1)))を導出し、各非基準画素の電流情報から、各非基準画素の電流劣化情報(Log(Si(T2))−Log(Si(T1)))を導出する。

【0041】

次に、計測信号処理回路27は、基準画素の電流劣化情報、および各非基準画素の電流劣化情報から、時刻T2の時点における、基準画素の電流情報に対する各非基準画素の電流情報のべき係数n(Si,Ss)を導出する。続いて、計測信号処理回路27は、基準画素の電流情報から、時刻T2の時点における、基準画素の電流の経時変化を表す電流劣化関数Is(t)を導出する。さらに、計測信号処理回路27は、電流劣化関数Is(t)およびべき係数n(Si,Ss)から、時刻T2の時点における、各非基準画素の電流の経時変化を表す電流劣化関数Ii(t)を導出する。このようにして、計測信号処理回路27は、初期の電流情報を用いて、時刻T2の時点における電流劣化関数Is(t),Ii(t)を導出する。

【0042】

(データの更新)

次に、データの更新について説明する。計測信号処理回路27は、時刻Tk-1,Tkにおいて、基準画素の電流信号26Aと、複数の非基準画素の電流信号26Aを電流測定回路26から取得する。このときの基準画素の電流信号26Aの値(測定値)をSs1とする(図8参照)。次に、計測信号処理回路27は、時刻Tk-1の時点における電流劣化関数Is(t)から、時刻Tkにおける基準画素の電流情報を予測する。このときの予測値をSs2とする(図8参照)。続いて、計測信号処理回路27は、測定値Ss1と予測値Ss2とを比較して、測定値Ss1と予測値Ss2とが互いに一致するか否かを判定する。その結果、例えば、測定値Ss1が予測値Ss2と一致する場合には、計測信号処理回路27は、時刻Tk-1の時点における電流劣化関数Is(t)を、時刻Tkの時点における電流劣化関数Is(t)とする。一方、計測信号処理回路27は、測定値Ss1と予測値Ss2とを比較して、例えば、測定値Ss1が予測値Ss2と異なる場合には、計測信号処理回路27は、基準画素の電流情報から、時刻Tkの時点における電流劣化関数Is(t)を導出する。

【0043】

次に、計測信号処理回路27は、基準画素の電流情報から、基準画素の電流劣化情報(Log(Ss(Tk))−Log(Ss(Tk-1)))を導出する。さらに、計測信号処理回路27は、複数の非基準画素の電流情報から、各非基準画素の電流劣化情報(Log(Si(Tk))−Log(Si(Tk-1)))を導出する。次に、計測信号処理回路27は、基準画素の電流劣化情報、および各非基準画素の電流劣化情報から、時刻Tkの時点におけるべき係数n(Si,Ss)を導出する。

【0044】

次に、計測信号処理回路27は、時刻Tk-1の時点における電流劣化関数Is(t)のパラメータ(例えば、p1,p2,……,pm)を、時刻Tkの時点における電流劣化関数Is(t)のパラメータ(例えば、p1’,p2’,……,pm’)に更新する(図9参照)。つまり、計測信号処理回路27は、基準画素の電流情報のうち最新の電流情報(Ss(Tk))と、基準画素の電流情報のうち最新ではない電流情報(Ss(Tk-1))とに合うように、電流劣化関数Is(t)のパラメータを更新する。計測信号処理回路27は、例えば、新たに求めた電流劣化関数Is(t)のパラメータを記憶回路28に格納する。

【0045】

次に、計測信号処理回路27は、時刻Tkの時点における電流劣化関数Is(t)(図10参照)と、べき係数n(Si,Ss)(図11参照)とから、時刻Tkの時点における電流劣化関数Ii(t)を導出する(図12参照)。具体的には、計測信号処理回路27は、以下の式を用いて、時刻Tkの時点における電流劣化関数Ii(t)を導出する。

【数4】

【0046】

次に、計測信号処理回路27は、時刻Tk-1の時点における各非基準画素の電流劣化関数Ii(t)のパラメータを、時刻Tkの時点における各非基準画素の電流劣化関数Ii(t)のパラメータに更新する。計測信号処理回路27は、例えば、新たに求めた電流劣化関数Ii(t)のパラメータを記憶回路28に格納する。

【0047】

(電流劣化率の予測)

次に、計測信号処理回路27は、次のサンプリング期間が到来するまでの間、各表示画素13の電流劣化率を予測する。具体的には、計測信号処理回路27は、電流劣化関数Is(t)、電流劣化関数Ii(t)、および各表示画素13の映像信号20Aの履歴から、各表示画素13の、基準電流における発光積算時間Txyを導出する。計測信号処理回路27は、各表示画素13の、基準電流における発光積算時間Txyを、例えば、以下のようにして求める。

【0048】

図13は、各表示画素13の、基準電流における発光積算時間Txyの導出過程を模式的に表したものである。例えば、図13に示したように、ある表示画素13の輝度が、時刻T=0〜t1の間、初期電流S1(初期輝度Y1)で発光し、時刻T=t1〜t2の間、初期電流S2(初期輝度Y2)で発光し、時刻T=t2〜t3の間、初期電流Sn(初期輝度Yn)で発光したとする。このとき、この表示画素13の輝度は、厳密には、時刻T=0〜t1の間、初期電流S1の劣化曲線に沿って劣化し、時刻T=t1〜t2の間、初期電流S2の劣化曲線に沿って劣化し、時刻T=t2〜t3の間、初期電流Snの劣化曲線に沿って劣化する。その結果、この表示画素13の輝度は、例えば、図13に示したように48%まで劣化したとする。したがって、基準画素の電流劣化曲線(Is(t))において劣化率が48%となるときの時間を求めることにより、この表示画素13の、基準電流における発光積算時間Txyを求めることができる。このように、各階調における電流劣化曲線上を入力信号の大きさ(階調)に応じて追跡することにより、各表示画素13の、基準電流における発光積算時間Txy、および各表示画素13の電流劣化率を求めることができる。

【0049】

(補正量の導出)

次に、計測信号処理回路27は、求めた発光積算時間Txy(または、予測した各表示画素13の電流劣化率)と、表示パネル10ガンマ特性とから映像信号に対する補正量を導出する。計測信号処理回路27は、映像信号に対する補正量を、例えば、以下のようにして求める。

【0050】

図14は、T=0,Txyにおける階調(映像信号20Aの値)と輝度との関係の一例を表したものである。T=0における階調−輝度特性は、いわゆるガンマ特性と呼ばれるものである。T=Txyにおける階調−輝度特性は、ガンマ特性に対して、全階調において、輝度を48%にまで減衰させたものである。ここで、ある表示画素13において、映像信号20Aの値がSxyであったとすると、この表示画素13の輝度は、初期には、図中の白丸に対応する値となっていたことがわかる。つまり、この表示画素13の輝度は、初期から発光積算時間Txyだけ経過したときに、初期の輝度から48%にまで減衰した値となっている、と予測することができる。

【0051】

そこで、計測信号処理回路27は、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、映像信号20Aに掛ける電流補正量RIを導出する。具体的には、計測信号処理回路27は、以下の式を用いて、電流補正量RIを導出する。

【数5】

【0052】

数5において、GIは、電流補正ゲインであり、上の例では1/0.48である。rは、ガンマ特性の指数(ガンマ値)である。

【0053】

最後に、計測信号処理回路27は、電流補正量RIを、補正情報27Aとして記憶回路28に格納する。このようにして、計測信号処理回路27は、画素回路32に含まれる、駆動トランジスタTr1’などの半導体素子の劣化に起因する効率劣化を補正する。

【0054】

(効率補正について)

ダミー画素駆動回路25は、さらに、制御信号21Aの入力に応じて(同期して)、各ダミー画素18に互いに異なる大きさの定電流を流して各ダミー画素18を発光させるものである。ダミー画素駆動回路25は、例えば、ダミー画素18の数がn個である場合に、1番目のダミー画素18には初期輝度がY1となるような定電流を流し、2番目のダミー画素18には初期輝度がY2(>Y1)となるような定電流を流し、i番目のダミー画素18には初期輝度がYi(>Yi-1)となるような定電流を流し、n番目のダミー画素18には初期輝度がYn(>Yn-1)となるような定電流を流すようになっている。ダミー画素駆動回路25は、例えば、各ダミー画素18に電流を流した時間を計測するようになっている。

【0055】

なお、各ダミー画素18の輝度は、各ダミー画素18に定電流を流し続けた場合であっても、例えば、図15に示したように、時間の経過に伴って、徐々に低下する。これは、各ダミー画素18に含まれる有機EL素子17が通電時間(発光積算時間)に応じて劣化していく性質を有しており、その劣化の進行度に応じて発光効率が低下するからである。なお、図15中のYsは、各ダミー画素18のうち基準画素(後述)として設定された画素の初期輝度である。

【0056】

また、各ダミー画素18の効率劣化率の変移は一様ではない。例えば、図16に示したように、基準画素として設定された画素(ダミー画素18)の効率劣化率を横軸にとると、基準画素の初期輝度Ysよりも小さな初期輝度のダミー画素18の効率劣化率の変移は、当初は基準画素の効率劣化よりも緩やかであることがわかる。一方、基準画素の初期輝度Ysよりも大きな初期輝度のダミー画素18の効率劣化率の変移は、当初は基準画素の効率劣化よりも急峻であることがわかる。図16に例示した各ダミー画素18の効率劣化率の変移を式で表すと以下のようになる。

【数6】

【0057】

数6において、Diは、i番目のダミー画素18の効率劣化率である。Dsは、基準画素の効率劣化率である。n(Yi,Ys)は、基準画素の輝度に対するi番目のダミー画素18の輝度のべき係数である。べき係数n(Yi,Ys)は、例えば、以下の式に示したように、(Log(Yi(Tk))−Log(Yi(Tk-1)))を(Log(Ys(Tk))−Log(Ys(Tk-1)))で除算することにより導出される。

【数7】

【0058】

数7において、Log(Ys(Tk))はYs(Tk)の対数であり、Log(Ys(Tk-1))はYs(Tk-1)の対数であり、Log(Yi(Tk))はYi(Tk)の対数であり、Log(Yi(Tk-1))はYi(Tk-1)の対数である。

【0059】

また、数7において、Ys(Tk)は、時刻Tkにおける基準画素の受光信号19A(輝度情報)であり、基準画素の輝度情報のうちで最新の輝度情報に相当する。また、Ys(Tk-1)は、時刻Tk-1(<時刻Tk)における基準画素の受光信号19A(輝度情報)であり、基準画素の輝度情報のうちで最新ではない輝度情報に相当する。Yi(Tk)は、時刻Tkにおけるi番目のダミー画素18の受光信号19A(輝度情報)であり、i番目のダミー画素18(非基準画素)の輝度情報のうちで最新の輝度情報に相当する。Yi(Tk-1)は、時刻Tk-1におけるi番目のダミー画素18の受光信号19A(輝度情報)であり、i番目のダミー画素18(非基準画素)の輝度情報のうちで最新ではない輝度情報に相当する。時刻Tk-1と時刻Tkとの関係は、例えば、以下の式で表される。

【数8】

【0060】

数8において、ΔT2はサンプリング周期である。ここで、サンプリング周期ΔT2とは、例えば、計測信号処理回路27が数8の右辺の分母の値および分子の値を導出する周期を指している。計測信号処理回路27は、サンプリング周期ΔT2を常に一定にしている。

【0061】

上記のようにして導出したべき係数n(Yi,Ys)は、例えば、図17に示したように、横軸を、基準画素の初期輝度Ysに対する各ダミー画素16の初期輝度Yiの割合(Yi/Ys)とすると、時刻Tkにおいて、初期輝度Yiが大きくなるにつれて大きくなる右肩上がりの曲線を描く。なお、数2からも明らかなように、べき係数n(Yi,Ys)は、Ys/Ysにおいて1である。

【0062】

次に、図18〜図24を参照して、映像信号20Aの補正に用いる効率補正量Ryの導出方法について説明する。

【0063】

(初期設定)

まず、初期設定について説明する。計測信号処理回路27は、複数のダミー画素18のうちの一の画素を基準画素として設定する。本実施の形態では、この基準画素は、他のダミー画素18(非基準画素)に変更されることはなく、常に、同一のダミー画素18に設定される。

【0064】

次に、計測信号処理回路27は、時刻T1,T2において、受光素子群19から受光信号19Aを取得する。具体的には、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素18のうちの一の画素である基準画素の受光信号19Aを受光素子群19から取得する。さらに、計測信号処理回路27は、時刻T1,T2において、複数のダミー画素18のうち基準画素を除く全ての画素である複数の非基準画素の受光信号19Aを受光素子群19から取得する。続いて、計測信号処理回路27は、基準画素の輝度情報から、基準画素の効率劣化情報(Log(Ys(T2))−Log(Ys(T1)))を導出し、各非基準画素の輝度情報から、各非基準画素の効率劣化情報(Log(Yi(T2))−Log(Yi(T1)))を導出する。

【0065】

次に、計測信号処理回路27は、基準画素の効率劣化情報、および各非基準画素の効率劣化情報から、時刻T2の時点における、基準画素の輝度情報に対する各非基準画素の輝度情報のべき係数n(Yi,Ys)を導出する。続いて、計測信号処理回路27は、基準画素の輝度情報から、時刻T2の時点における、基準画素の輝度の経時変化を表す効率劣化関数Fs(t)を導出する。さらに、計測信号処理回路27は、効率劣化関数Fs(t)およびべき係数n(Yi,Ys)から、時刻T2の時点における、各非基準画素の輝度の経時変化を表す効率劣化関数Fi(t)を導出する。このようにして、計測信号処理回路27は、初期の輝度情報を用いて、時刻T2の時点における効率劣化関数Fs(t),Fi(t)を導出する。

【0066】

(データの更新)

次に、データの更新について説明する。計測信号処理回路27は、時刻Tk-1,Tkにおいて、基準画素の受光信号19Aと、複数の非基準画素の受光信号19Aを受光素子群19から取得する。このときの基準画素の受光信号19Aの値(測定値)をYs1とする(図18参照)。次に、計測信号処理回路27は、時刻Tk-1の時点における効率劣化関数Fs(t)から、時刻Tkにおける基準画素の輝度情報を予測する。このときの予測値をYs2とする(図18参照)。続いて、計測信号処理回路27は、測定値Ys1と予測値Ys2とを比較して、測定値Ys1と予測値Ys2とが互いに一致するか否かを判定する。その結果、例えば、測定値Ys1が予測値Ys2と一致する場合には、計測信号処理回路27は、時刻Tk-1の時点における効率劣化関数Fs(t)を、時刻Tkの時点における効率劣化関数Fs(t)とする。一方、計測信号処理回路27は、測定値Ys1と予測値Ys2とを比較して、例えば、測定値Ys1が予測値Ys2と異なる場合には、計測信号処理回路27は、基準画素の輝度情報から、時刻Tkの時点における効率劣化関数Fs(t)を導出する。

【0067】

次に、計測信号処理回路27は、基準画素の輝度情報から、基準画素の効率劣化情報(Log(Ys(Tk))−Log(Ys(Tk-1)))を導出する。さらに、計測信号処理回路27は、複数の非基準画素の輝度情報から、各非基準画素の効率劣化情報(Log(Yi(Tk))−Log(Yi(Tk-1)))を導出する。次に、計測信号処理回路27は、基準画素の効率劣化情報、および各非基準画素の効率劣化情報から、時刻Tkの時点におけるべき係数n(Yi,Ys)を導出する。

【0068】

次に、計測信号処理回路27は、時刻Tk-1の時点における効率劣化関数Fs(t)のパラメータ(例えば、p1,p2,……,pm)を、時刻Tkの時点における効率劣化関数Fs(t)のパラメータ(例えば、p1’,p2’,……,pm’)に更新する(図19参照)。つまり、計測信号処理回路27は、基準画素の輝度情報のうち最新の輝度情報(Ys(Tk))と、基準画素の輝度情報のうち最新ではない輝度情報(Ys(Tk-1))とに合うように、効率劣化関数Fs(t)のパラメータを更新する。計測信号処理回路27は、例えば、新たに求めた効率劣化関数Fs(t)のパラメータを記憶回路28に格納する。

【0069】

次に、計測信号処理回路27は、時刻Tkの時点における効率劣化関数Fs(t)(図20参照)と、べき係数n(Yi,Ys)(図21参照)とから、時刻Tkの時点における効率劣化関数Fi(t)を導出する(図22参照)。具体的には、計測信号処理回路27は、以下の式を用いて、時刻Tkの時点における効率劣化関数Fi(t)を導出する。

【数9】

【0070】

次に、計測信号処理回路27は、時刻Tk-1の時点における各非基準画素の効率劣化関数Fi(t)のパラメータを、時刻Tkの時点における各非基準画素の効率劣化関数Fi(t)のパラメータに更新する。計測信号処理回路27は、例えば、新たに求めた効率劣化関数Fi(t)のパラメータを記憶回路28に格納する。

【0071】

(効率劣化率の予測)

次に、計測信号処理回路27は、次のサンプリング期間が到来するまでの間、各表示画素13の効率劣化率を予測する。具体的には、計測信号処理回路27は、効率劣化関数Fs(t)、効率劣化関数Fi(t)、および各表示画素13の映像信号20Aの履歴から、各表示画素13の、基準輝度における発光積算時間Txyを導出する。計測信号処理回路27は、各表示画素13の、基準輝度における発光積算時間Txyを、例えば、以下のようにして求める。

【0072】

図23は、各表示画素13の、基準輝度における発光積算時間Txyの導出過程を模式的に表したものである。例えば、図23に示したように、ある表示画素13の輝度が、時刻T=0〜t1の間、初期輝度Y1で発光し、時刻T=t1〜t2の間、初期輝度Y2で発光し、時刻T=t2〜t3の間、初期輝度Ynで発光したとする。このとき、この表示画素13の輝度は、厳密には、時刻T=0〜t1の間、初期輝度Y1の劣化曲線に沿って劣化し、時刻T=t1〜t2の間、初期輝度Y2の劣化曲線に沿って劣化し、時刻T=t2〜t3の間、初期輝度Ynの劣化曲線に沿って劣化する。その結果、この表示画素13の輝度は、例えば、図23に示したように48%まで劣化したとする。したがって、基準画素の効率劣化曲線(Fs(t))において劣化率が48%となるときの時間を求めることにより、この表示画素13の、基準輝度における発光積算時間Txyを求めることができる。このように、各階調における効率劣化曲線上を入力信号の大きさ(階調)に応じて追跡することにより、各表示画素13の、基準輝度における発光積算時間Txy、および各表示画素13の効率劣化率を求めることができる。

【0073】

(補正量の導出)

次に、計測信号処理回路27は、求めた発光積算時間Txy(または、予測した各表示画素13の効率劣化率)と、表示パネル10ガンマ特性とから映像信号に対する補正量を導出する。計測信号処理回路27は、映像信号に対する補正量を、例えば、以下のようにして求める。

【0074】

図24は、T=0,Txyにおける階調(映像信号20Aの値)と輝度との関係の一例を表したものである。T=0における階調−輝度特性は、いわゆるガンマ特性と呼ばれるものである。T=Txyにおける階調−輝度特性は、ガンマ特性に対して、全階調において、輝度を48%にまで減衰させたものである。ここで、ある表示画素13において、映像信号20Aの値がSxyであったとすると、この表示画素13の輝度は、初期には、図中の白丸に対応する値となっていたことがわかる。つまり、この表示画素13の輝度は、初期から発光積算時間Txyだけ経過したときに、初期の輝度から48%にまで減衰した値となっている、と予測することができる。

【0075】

そこで、計測信号処理回路27は、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、映像信号20Aに掛ける効率補正量Ryを導出する。具体的には、計測信号処理回路27は、以下の式を用いて、効率補正量Ryを導出する。

【数10】

【0076】

数5において、Gyは、輝度補正ゲインであり、上の例では1/0.48である。

【0077】

最後に、計測信号処理回路27は、効率補正量Ryを、補正情報27Aとして記憶回路28に格納する。このようにして、計測信号処理回路27は、各ダミー画素18に含まれる有機EL素子17の劣化に起因する発光効率の劣化を補正する。

【0078】

(動作・効果)

次に、本実施の形態の表示装置1の動作および効果について説明する。表示装置1に対して映像信号20Aおよび同期信号20Bが入力される。すると、信号線駆動回路23および走査線駆動回路24によって各表示画素13が駆動され、各表示画素13の映像信号20Aに応じた映像が表示領域12に表示される。一方で、ダミー画素駆動回路25によって、各ダミー画素16に接続された信号線DTL’に互いに異なる大きさの信号電圧Vsigi(一定値)が印加され、各ダミー画素16が互いに異なる階調で発光する。その結果、電流測定回路26から、各ダミー画素16の有機EL素子13に流れる電流値に対応する電流信号26Aが出力される。さらに、ダミー画素駆動回路25によって、各ダミー画素18が駆動されると同時に受光素子群19も駆動される。これにより、各ダミー画素18に、互いに異なる大きさの定電流が流され、その定電流の大きさに応じた輝度で各ダミー画素18が発光し、各ダミー画素18の発光光が受光素子群19で検知される。その結果、受光素子群19から、各ダミー画素18の発光光に対応する受光信号19Aが出力される。次に、計測信号処理回路27によって、以下の処理が行われる。

【0079】

すなわち、電流信号26Aから、基準画素の電流信号26A(電流情報)に対する非基準画素の電流信号26A(電流情報)のべき係数n(Si,Ss)が導出される。次に、基準画素の電流情報から基準画素の電流劣化関数Is(t)が導出されると共に、電流劣化関数Is(t)およびべき係数n(Si,Ss)から非基準画素の電流劣化関数Ii(t)が導出される。次に、電流劣化関数Is(t)と、電流劣化関数Ii(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の、基準電流における発光積算時間Txyおよび各表示画素13の電流劣化率が予測される。次に、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、各表示画素13の映像信号20Aに対して電流補正量RIが掛けられる。

【0080】

さらに、受光信号19Aから、基準画素の受光信号19A(輝度情報)に対する非基準画素の受光信号19A(輝度情報)のべき係数n(Yi,Ys)が導出される。次に、基準画素の輝度情報から基準画素の効率劣化関数Fs(t)が導出されると共に、効率劣化関数Fs(t)およびべき係数n(Yi,Ys)から非基準画素の効率劣化関数Fi(t)が導出される。次に、効率劣化関数Fs(t)と、効率劣化関数Fi(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の、基準輝度における発光積算時間Txyおよび各表示画素13の効率劣化率が予測される。次に、初期から発光積算時間Txyだけ経過したときの輝度が初期の輝度と等しくなるように、各表示画素13の映像信号20Aに対して効率補正量Ryが掛けられる。

【0081】

このように、本実施の形態では、電流劣化関数Is(t)と、電流劣化関数Is(t)およびべき係数n(Si,Ss)から得られた効率劣化関数Ii(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の電流劣化率が予測される。さらに、効率劣化関数Fs(t)と、効率劣化関数Fs(t)およびべき係数n(Yi,Ys)から得られた効率劣化関数Fi(t)と、各表示画素13の映像信号20Aの履歴とを利用して、各表示画素13の効率劣化率が予測される。これにより、高い精度で各表示画素13の効率劣化を予測することができるので、各表示画素13の輝度が初期の輝度となるように、各表示画素13の映像信号20Aに対して的確な補正量(電流補正量RIおよび効率補正量Ry)を掛けることができる。その結果、正確に焼き付きを防止することができる。

【0082】

また、本実施の形態では、観測時点のデータ(Ss(Tk)、Ss(Tk-1)、Ys(Tk)、Ys(Tk-1))で、各表示画素13の電流劣化率および効率劣化率を予測することができる。これにより、長時間観測をすることなく、高い精度で各表示画素の効率劣化を予測することができる。従って、本実施の形態の予測方法は、極めて現実的である。また、本実施の形態では、観測時点のデータで、各表示画素13の効率劣化率を予測することができることから、更新に必要なメモリ量および計算量を小さく抑えることができる。

【0083】

<変形例>

上記実施の形態では、各表示画素13の映像信号20Aに対して、電流補正量RIおよび効率補正量Ryの双方の補正がなされていたが、電流補正量RIおよび効率補正量Ryのいずれか一方の補正だけが実行されてもよい。

【0084】

また、上記実施の形態では、初期電流S1〜Snの全てのダミー画素16が、有機EL素子14R,14G,14Bを一組とする単一の画素によって構成されていたが、初期電流Siの低い各ダミー画素16(低電流画素)を複数のダミー画素(第2ダミー画素)(図示せず)によって構成してもよい。このようにした場合には、計測信号処理回路27は、複数の第2ダミー画素に接続された有機EL素子13に流れる電流の平均値から、数2の右辺の分母または分子を導出することが可能である。これにより、低輝度のダミー画素16における測定誤差を小さくすることができるので、高い精度で低輝度の表示画素13の効率劣化を予測することができる。その結果、焼き付きをより一層、正確に防止することができる。

【0085】

また、上記実施の形態では、初期輝度Y1〜Ynの全てのダミー画素18が、有機EL素子17R,17G,17Bを一組とする単一の画素によって構成されていたが、初期輝度Yiの低い各ダミー画素18(低輝度画素)を複数のダミー画素(第3ダミー画素)(図示せず)によって構成してもよい。このようにした場合には、計測信号処理回路27は、複数の第3ダミー画素の輝度の平均値から、数7の右辺の分母または分子を導出することが可能である。これにより、低輝度のダミー画素18における測定誤差を小さくすることができるので、高い精度で低輝度の表示画素13の効率劣化を予測することができる。その結果、焼き付きをより一層、正確に防止することができる。

【0086】

また、上記実施の形態では、常に特定のダミー画素16が基準画素となっていたが、必要に応じて、今まで非基準画素であったダミー画素16が基準画素となってもよい。例えば、計測信号処理回路27は、基準画素に接続された有機EL素子13に流れる電流が所定の値以下となったことを検知したときには、今まで基準画素として設定されていたダミー画素16を除外すると共に複数の非基準画素のうちの一の画素を新たな基準画素に設定する。その後は、計測信号処理回路27は、今までと同様にして、数2の右辺の分母および分子を導出する。このようにした場合には、基準画素に不具合が生じた場合でも、継続して、効率劣化を予測することができる。これにより、効率劣化の予測の信頼性を高めることができる。

【0087】

また、上記実施の形態では、常に特定のダミー画素18が基準画素となっていたが、必要に応じて、今まで非基準画素であったダミー画素18が基準画素となってもよい。例えば、計測信号処理回路27は、基準画素の輝度が所定の値以下となったことを検知したときには、今まで基準画素として設定されていたダミー画素18を除外すると共に複数の非基準画素のうちの一の画素を新たな基準画素に設定する。その後は、計測信号処理回路27は、今までと同様にして、数7の右辺の分母および分子を導出する。このようにした場合には、基準画素に不具合が生じた場合でも、継続して、効率劣化を予測することができる。これにより、効率劣化の予測の信頼性を高めることができる。

【0088】

また、上記実施の形態では、サンプリング周期ΔT1が常に一定となっていたが、可変であってもよい。例えば、計測信号処理回路27が、サンプリング周期ΔT1を複数のダミー画素16の発光累積時間に応じて変化させてもよい。そのようにした場合には、例えば、発光累積時間Txyが長時間に達し、効率劣化があまり生じなくなったときに、サンプリング周期ΔT1を長くすることができる。これにより、更新に必要な計算量を小さく抑えることができる。

【0089】

また、上記実施の形態では、サンプリング周期ΔT2が常に一定となっていたが、可変であってもよい。例えば、計測信号処理回路27が、サンプリング周期ΔT2を複数のダミー画素18の発光累積時間に応じて変化させてもよい。そのようにした場合には、例えば、発光累積時間Txyが長時間に達し、効率劣化があまり生じなくなったときに、サンプリング周期ΔT2を長くすることができる。これにより、更新に必要な計算量を小さく抑えることができる。

【0090】

また、上記実施の形態では、数2を用いて、べき係数n(Si,Ss)は導出されていたが、例えば、以下の式を用いて、べき係数n(Si,Ss)が導出されてもよい。

【数11】

【数12】

【0091】

数11において、右辺第2項の分母は、時刻Tkにおける基準画素の劣化速度である。右辺第2項の分子は、時刻Tkにおける非基準画素の劣化速度である。数12において、右辺第2項は、時刻Tkにおける基準画素の劣化速度を、時刻Tkにおける非基準画素の劣化速度で除算することにより得られたものである。

【0092】

数11または数12を用いて、べき係数n(Si,Ss)を導出するようにした場合には、四則演算だけで、べき係数n(Si,Ss)を導出することができ、数2を用いたときのような対数の計算が不要である。従って、本変形例では、数2を用いてべき係数n(Si,Ss)を導出した場合よりも、計算量を小さく抑えることができる。

【0093】

また、上記実施の形態では、数7を用いて、べき係数n(Yi,Ys)は導出されていたが、例えば、以下の式を用いて、べき係数n(Yi,Ys)が導出されてもよい。

【数13】

【数14】

【0094】

数13において、右辺第2項の分母は、時刻Tkにおける基準画素の劣化速度である。右辺第2項の分子は、時刻Tkにおける非基準画素の劣化速度である。数14において、右辺第2項は、時刻Tkにおける基準画素の劣化速度を、時刻Tkにおける非基準画素の劣化速度で除算することにより得られたものである。

【0095】

数13または数14を用いて、べき係数n(Yi,Ys)を導出するようにした場合には、四則演算だけで、べき係数n(Yi,Ys)を導出することができ、数7を用いたときのような対数の計算が不要である。従って、本変形例では、数7を用いてべき係数n(Yi,Ys)を導出した場合よりも、計算量を小さく抑えることができる。

【0096】

<適用例>

以下、上記実施の形態およびその変形例で説明した表示装置1の適用例について説明する。上記実施の形態等の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0097】

(適用例1)

図25は、上記実施の形態等の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記実施の形態等の表示装置1により構成されている。

【0098】

(適用例2)

図26は、上記実施の形態等の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上記実施の形態等の表示装置1により構成されている。

【0099】

(適用例3)

図27は、上記実施の形態等の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、その表示部530は、上記実施の形態等の表示装置1により構成されている。

【0100】

(適用例4)

図28は、上記実施の形態等の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上記実施の形態等の表示装置1により構成されている。

【0101】

(適用例5)

図29は、上記実施の形態等の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記実施の形態等の表示装置1により構成されている。

【符号の説明】

【0102】

1…表示装置、10…表示パネル、11,11R,11G,11B,14,14R,14G,14B,17,17R,17G,17B…有機EL素子、12…表示領域、13…表示画素、15…非表示領域、16,18…ダミー画素、19…受光素子群、19A…受光信号、20…駆動回路、20A,22A…映像信号、20B…同期信号、21…タイミング生成回路、21A…制御信号、22…映像信号処理回路、23…信号線駆動回路、24…走査線駆動回路、25…ダミー画素駆動回路、26…電流測定回路、26A…電流信号、27…計測信号処理回路、27A…補正情報、28…記憶回路、30…駆動パネル、31,32…画素回路、40…封止パネル、51…映像信号供給TAB、52…走査信号供給TAB、53…電源供給TCP、54…制御信号供給TCP、55…計測信号出力TCP、A,B…曲線、Cs…保持容量、D,Ds,Dx,Dsi,Dss…効率劣化率、DTL,DTL’…信号線、Fi(t),Fs(t)…効率劣化関数、GND…グラウンド線、Ii(t),Is(t)…電流劣化関数、n(Yi,Ys),n(Si,Ss)…べき係数、RI…電流補正量、Ry…効率補正量、Sxy…映像信号、T1,T2,Tx,Tk,Tk-1…時刻、Tr1,Tr1’…駆動トランジスタ、Tr2,Tr2’…書き込みトランジスタ、Txy…発光積算時間、Vcc,Vcc’…電源線、Vsigi…信号電圧、WSL,WSL’…走査線、Ss1,Ys1…測定値、Ss2,Ys2…予測値、S1,S2,Si,Ss,Sn…初期電流、Y1,Y2,Yi,Ys,Yn…初期輝度、Si(Tk),Si(Tk-1),Ss(Tk),Ss(Tk-1)…電流情報、Yi(Tk),Yi(Tk-1),Ys(Tk),Ys(Tk-1)…輝度情報、ΔT1,ΔT2…サンプリング周期。

【特許請求の範囲】

【請求項1】

複数の表示画素が2次元配置された表示領域と、複数の第1ダミー画素および複数の第2ダミー画素が配置された非表示領域とを有する表示パネルと、

各第1ダミー画素に互いに異なる大きさの信号電圧を印加して各第1ダミー画素を発光させる第1駆動部と、

各第2ダミー画素に互いに異なる大きさの定電流を流して各第2ダミー画素を発光させる第2駆動部と、

各第1ダミー画素に流れる電流を検知して各第1ダミー画素の電流情報を出力する電流測定部と、

各第2ダミー画素の発光光を検知して各第2ダミー画素の輝度情報を出力する受光部と、

前記電流情報を用いて電流劣化関数を導出すると共に、前記輝度情報を用い効率劣化関数を導出する演算部と

を備えた表示装置。

【請求項2】

前記電流劣化関数を導出する周期は、前記効率劣化関数を導出する周期よりも短くなっている

請求項1に記載の表示装置。

【請求項3】

前記演算部は、前記電流劣化関数、および各表示画素の映像信号の履歴から、各表示画素の電流劣化率を予測し、予測した各表示画素の電流劣化率と、前記表示パネルのガンマ特性とから映像信号に対する第1補正量を導出する

請求項1または請求項2に記載の表示装置。

【請求項4】

前記演算部は、前記効率劣化関数、および各表示画素の映像信号の履歴から、各表示画素の効率劣化率を予測し、予測した各表示画素の効率劣化率と、前記表示パネルのガンマ特性とから映像信号に対する第2補正量を導出する

請求項3に記載の表示装置。

【請求項1】

複数の表示画素が2次元配置された表示領域と、複数の第1ダミー画素および複数の第2ダミー画素が配置された非表示領域とを有する表示パネルと、

各第1ダミー画素に互いに異なる大きさの信号電圧を印加して各第1ダミー画素を発光させる第1駆動部と、

各第2ダミー画素に互いに異なる大きさの定電流を流して各第2ダミー画素を発光させる第2駆動部と、

各第1ダミー画素に流れる電流を検知して各第1ダミー画素の電流情報を出力する電流測定部と、

各第2ダミー画素の発光光を検知して各第2ダミー画素の輝度情報を出力する受光部と、

前記電流情報を用いて電流劣化関数を導出すると共に、前記輝度情報を用い効率劣化関数を導出する演算部と

を備えた表示装置。

【請求項2】

前記電流劣化関数を導出する周期は、前記効率劣化関数を導出する周期よりも短くなっている

請求項1に記載の表示装置。

【請求項3】

前記演算部は、前記電流劣化関数、および各表示画素の映像信号の履歴から、各表示画素の電流劣化率を予測し、予測した各表示画素の電流劣化率と、前記表示パネルのガンマ特性とから映像信号に対する第1補正量を導出する

請求項1または請求項2に記載の表示装置。

【請求項4】

前記演算部は、前記効率劣化関数、および各表示画素の映像信号の履歴から、各表示画素の効率劣化率を予測し、予測した各表示画素の効率劣化率と、前記表示パネルのガンマ特性とから映像信号に対する第2補正量を導出する

請求項3に記載の表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【公開番号】特開2011−65048(P2011−65048A)

【公開日】平成23年3月31日(2011.3.31)

【国際特許分類】

【出願番号】特願2009−217183(P2009−217183)

【出願日】平成21年9月18日(2009.9.18)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成23年3月31日(2011.3.31)

【国際特許分類】

【出願日】平成21年9月18日(2009.9.18)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]