表示装置

【課題】端子設定により、一対の伝送線路の終端方法を切り替える。

【解決手段】各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、前記各駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

【解決手段】各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、前記各駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置に係り、特に、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給される表示装置に適用して有効な技術に関する。

【背景技術】

【0002】

アクティブ素子として薄膜トランジスタを使用するTFT方式の液晶表示装置は高精細な画像を表示できるため、テレビ、パソコン用ディスプレイ等の表示装置として使用されている。特に、小型のTFT方式の液晶表示装置は、携帯電話機の表示部として多用されている。

一般に、液晶表示装置では、隣接する2本の走査線(ゲート線ともいう。)と、隣接する2本の映像線(ソース線またはドレイン線ともいう。)とで囲まれる領域に、走査線からの走査信号によってオンする薄膜トランジスタと、映像線からの映像信号が薄膜トランジスタを介して供給される画素電極とが形成されて、所謂、サブピクセルが構成される。 これら複数のサブピクセルが形成された領域が表示領域であり、当該表示領域を囲んで周辺領域が存在する。周辺領域には、各映像線に映像電圧(階調電圧)を供給するドレインドライバ(ソースドライバともいう。)、及び各走査線に走査電圧を供給するゲートドライバが設けられる。

ドレインドライバおよびゲートドライバには、表示制御回路(タイミングコントローラともいう)から表示制御信号が入力され、ドレインドライバおよびゲートドライバは、表示制御回路により制御・駆動される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平10−258229号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、中小形機器向け液晶表示パネルは、高解像度化か進み、WVGAクラスの高精細の液晶表示パネルが主流を占めているが、高精細・高画質化の要求は留まることなく、タブレット端末等のハイエンドモデルではWXGA化が主流となっている。

このような状況に鑑み、低解像度〜高解像度クラスの幅広い液晶表示パネルに対応する為に、低解像度クラスの液晶表示パネルは、液晶ドライバを1チップ構成、高解像度クラスの液晶表示パネルは、液晶ドライバを複数チップ構成とし、1チップ構成と、複数チップ構成を切り替えられるようにすることが、低コスト化を図るためにも望ましい。

前記要望に答えるために、液晶ドライバに設けた端子により、液晶ドライバを1チップ構成、あるいは、複数チップ構成とすることが想定される。

その様な状況下において、差動シリアル伝送方式で入力信号が供給するための一対の伝送線路を終端する必要があり、さらには、一対の伝送線路を介して信号を読み出す時に、複数の信号が衝突するのを防止することが必要となる。

本発明は、前記要望に答えるためになされたものであり、本発明の目的は、表示装置において、端子設定により、一対の伝送線路の終端方法の切り替えること、あるいは、一対の伝送線路を介する信号の読み出し時に、信号が衝突するのを防止することが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【課題を解決するための手段】

【0005】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

(1)複数の画素と、前記複数の画素を駆動するn(n>2)個の駆動回路を備える表示装置であって、前記各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、前記各駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

(2)(1)において、前記各駆動回路は、SELA端子と、SELB端子を有し、前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第1電圧レベルの時に、前記各駆動回路は、前記マスタの駆動回路として動作し、前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第2電圧レベルの時に、前記各駆動回路は、前記スレーブの駆動回路として動作する。

(3)(1)または(2)において、前記各駆動回路は、SELD1端子ないしSELD(n−2)端子を有し、前記SELD1端子ないしSELD(n−2)端子のそれぞれに入力される電圧レベルに応じて、前記スレーブの駆動回路の各々は、何番目のスレーブの駆動回路かを認識する。

【0006】

(4)複数の画素と、前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各駆動回路は、REVS端子を有し、前記本体側が前記各駆動回路から信号を読み出す時に、前記REVS端子に第2電圧 レベルの電圧が入力される駆動回路のみが、前記一対の伝送線路にデータを送出する。

(5)複数の画素と、前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各駆動回路は、レジスタを有し、前記本体側が前記各駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた駆動回路のみが、前記一対の伝送線路に信号を送出する。

(6)(5)において、本体側から前記読み出し許可のデータを、次に読み出し対象となる駆動回路内のレジスタに書き込む。

(7)(1)ないし(6)の何れかにおいて、前記各駆動回路は、表示制御回路を有する映像線駆動回路である。

【0007】

(8)複数の画素と、前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、表示制御回路を備える表示装置であって、前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各映像線駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、1番目の映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、残りの映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

(9)複数の画素と、前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、表示制御回路を備える表示装置であって、前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各映像線駆動回路は、REVS端子を有し、前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記REVS端子に第2電圧レベルの電圧が入力される映像線駆動回路のみが、前記一対の伝送線路に信号を送出する。

(10)複数の画素と、前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、表示制御回路を備える表示装置であって、前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各駆動回路は、レジスタを有し、前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた映像線駆動回路のみが、前記−対の伝送線路に信号を送出する。

(11)(10)において、前記表示制御回路から前記読み出し許可のデータを、次に読み出し対象となる映像線駆動回路内のレジスタに書き込む。

【発明の効果】

【0008】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明の表示装置によれば、端子設定により、一対の伝送線路の終端方法の切り替えること、あるいは、一対の伝送線路を介する信号の読み出し時に、信号が衝突するのを防止することが可能となる。

【図面の簡単な説明】

【0009】

【図1】本発明の実施例1の液晶表示装置の概略構成を示すブロック図である。

【図2】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

【図3】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

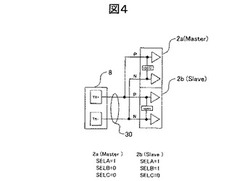

【図4】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

【図5】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

【図6】本発明の実施例1の液晶表示装置の問題点を説明するための図である。

【図7】本発明の実施例2のドレインドライバの端子設定を説明するための図である。

【図8】本発明の実施例2のドレインドライバの端子設定を説明するための図である。

【図9】従来の液晶表示装置の概略構成を示すブロック図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

[実施例1]

図1は、本発明の実施例1の液晶表示装置の概略構成を示すブロック図である。

本実施例の液晶表示装置は、液晶表示パネル1、ドレインドライバ(2a〜2c)、ゲートドライバ3、電源回路5で構成される。

ドレインドライバ(2a〜2c)と、ゲートドライバ3は、液晶表示パネル1の周辺部に設置される。例えば、ドレインドライバ(2a〜2c)と、ゲートドライバ3は、液晶表示パネル1の一対の基板の第1の基板(例えば、ガラス基板)の2辺の周辺部に、それぞれCOG方式で実装される。あるいは、ドレインドライバ(2a〜2c)と、ゲートドライバ3は、液晶表示パネル1の第1の基板の2辺の周辺部に配置されるフレキシブル回路基板に、それぞれCOF方式で実装される。

また、電源回路5は、液晶表示パネル1の周辺部(例えば、液晶表示装置の裏側)に配置される回路基板に実装される。

図1において、40は表示制御回路であり、本実施例の液晶表示装置は、表示制御回路40を、それぞれのドレインドライバに内蔵している。

【0011】

表示制御回路40は、本体コンピュータ8から入力する表示信号を、データの交流化等、液晶表示パネル1の表示に適したタイミング調整を行い、表示形式の入力信号に変換して同期信号(クロック信号)と共にドレインドライバ(2a〜2c)、ゲートドライバ3に入力する。

ゲートドライバ3は、表示制御回路40の制御の基に走査線(ゲート線ともいう;GL)に選択走査電圧を順次供給し、また、ドレインドライバ(2a〜2c)は、映像線(ドレイン線、ソース線ともいう;DL)に映像電圧を供給して映像を表示する。電源回路5は液晶表示装置に要する各種の電圧を生成する。

液晶表示パネル1は、複数のサブピクセルを有し、各サブピクセルは、映像線(DL)と走査線(GL)とで囲まれた領域に設けられる。

各サブピクセルは、薄膜トランジスタ(TFT)を有し、薄膜トランジスタ(TFT)の第1の電極(ドレイン電極またはソース電極)は映像線(DL)に接続され、薄膜トランジスタ(TFT)の第2の電極(ソース電極またはドレイン電極)は画素電極(PX)に接続される。また、薄膜トランジスタ(TFT)のゲート電極は、走査線(GL)に接続される。

なお、図1において、CLは、画素電極(PX)と対向電極(CT)との間に配置される液晶層を等価的に示す液晶容量であり、Caddは、画素電極(PX)と対向電極(CT)との間に形成される保持容量である。

【0012】

図1に示す液晶表示パネル1において、列方向に配置された各サブピクセルの薄膜トランジスタ(TFT)の第1の電極は、それぞれ映像線(DL)に接続され、各映像線(DL)は列方向に配置されたサブピクセルに、表示データに対応する映像電圧を供給するドレインドライバ(2a〜2c)に接続される。

また、行方向に配置された各サブピクセルにおける薄膜トランジスタ(TFT)のゲート電極は、それぞれ走査線(GL)に接続され、各走査線(GL)は、1水平走査時間、薄膜トランジスタ(TFT)のゲートに走査電圧(正または負のバイアス電圧)を供給するゲートドライバ3に接続される。

液晶表示パネル1に画像を表示する際、ゲートドライバ3は、走査線(GL)を、順次、例えば、上から下に向かって選択し、一方、ある走査線の選択期間中に、ドレインドライバ(2a〜2c)は、表示データに対応する映像電圧を、映像線(DL)に供給する。

映像線(DL)に供給された電圧は、薄膜トランジスタ(TFT)を経由して、画素電極(PX)に印加され、最終的に、保持容量(Cadd)と、液晶容量(CL)に電荷がチャージされ、液晶分子をコントロールすることにより画像が表示される。

【0013】

液晶表示パネル1は、画素電極(PX)、薄膜トランジスタ(TFT)等が形成される第1の基板と、カラーフィルタ等が形成される第2の基板とを、所定の間隙を隔てて重ね合わせ、該両基板間の周縁部近傍に枠状に設けたシール材により、両基板を貼り合わせると共に、シール材の一部に設けた液晶封入ロから両基板間のシール材の内側に液晶を封入、封止し、さらに、両基板の外側に偏光板を貼り付けて構成される。

なお、対向電極(CT)は、TN方式やVA方式の液晶表示パネルであれば第2の基板側に設けられる。IPS方式の場合は、第1の基板側に設けられる。

また、本発明は、液晶パネルの内部構造とは関係がないので、液晶パネルの内部構造の詳細な説明は省略する。さらに、本発明は、どのような構造の液晶パネルであっても適用可能である。

【0014】

本実施例の液晶表示装置では、表示制御回路40を、それぞれのドレインドライバに内蔵しているが、ドレインドライバ(2a〜2c)のそれぞれに、表示制御回路40を内蔵すると、それぞれのドレインドライバに内蔵された各表示制御回路40の同期を取る必要が生じる。そこで、本実施例では、複数のドレインドライバの中の1つのドレインドライバをマスタのドレインドライバ(図1では、2aで示すドレインドライバ)として動作させ、それ以外のドレインドライバをスレーブのドレインドライバ(図1では、2b、2cで示すドレインドライバ)として動作させる。

マスタのドレインドライバ(2a)は、自走用クロックを生成し、スレーブのドレインドライバ(2b、2c)には、マスタのドレインドライバ(2a)で生成された自走用クロックが入力される。これにより、マスタのドレインドライバ(2a)も、スレーブのドレインドライバ(2b、2c)も同期して動作することが可能となる。

また、マスタのドレインドライバ(2a)からゲートドライバ制御信号6が先頭のゲートドライバ3に入力され、ゲートドライバデータ転送信号7により、先頭のゲートドライバ3から後段のゲートドライバ3に対して、ゲートドライバ制御信号が転送される。

このように、本実施例の液晶表示装置では、ドレインドライバ(2a〜2c)内に、表示制御回路40を内蔵することにより、部品点数を削減することができるので、コストを低減することが可能となる。

【0015】

本実施例では、外部の本体コンピュータ8から入力される表示信号は、表示データを含み、表示データを含む入力信号は、本体コンピュー夕8から一対の伝送線路を介して、差動シリアル伝送方式で、ドレインドライバ(2a〜2c)に供給される。

図2ないし図4は、本実施例のドレインドライバの端子設定を説明するための図である。なお、図2ないし図4、及び、後述する図5において、本体コンピュータは、信号の送受信部のみを、ドレインドライバは、信号の受信部のみを図示している。また、図2ないし図4、図5において、TX+は、正極性側の送受信部、TX−は、負極性側の送受信部、Pは、一対の伝送線路30の中の正極性側の伝送線路、Nは、一対の伝送線路30の中の負極性側の伝送線路である。

図2ないし図4に示すように、本実施例のドレインドライバでは、SELA端子、SELB端子、SELC端子が設けられる。

SELA端子に入力される電圧がLow(以下、Lレベル)の時に、図2に示すように、1チップ構成となり、SELA端子に入力される電圧がHigh(以下、Hレベル)の時に、図3、図4に示すように、複数チップ構成となる。

そして、図2、図3に示すように、SELA端子に入力される電圧がHigh(以下、Hレベル)、SELB端子に入力される電圧がLレベルの時に、本実施例のドレインドライバは、マスタのドレインドライバ(2a)として動作し、SELA端子に入力される電圧がHレベル、SELB端子に入力される電圧がHレベルの時に、本実施例のドレインドライバは、スレーブのドレインドライバ(2b)として動作する。

【0016】

表示データを含む入力信号は、本体コンピュータ8から一対の伝送線路30を介して、差動シリアル伝送方式で、ドレインドライバに供給されるが、一対の伝送線路30は、終端抵抗で終端する必要がある。 SELC端子は、一対の伝送線路の終端方法を設定するために設けられる。

SELC端子に入力される電圧がLレベルの時に、マスタのドレインドライバ(2a)は、その内部で一対の伝送線路30の間に抵抗値がRa(ここでは、100Ω)の抵抗を接続して、一対の伝送線路30を終端し、スレーブのドレインドライバ(2b)が、その内部で一対の伝送線路30の間に抵抗を接続しないで、一対の伝送線路30を開放する。

一般に、差動シリアル伝送方式では、本体コンピュー夕8から各ドレインドライバ (2a〜2c)までの、一対の伝送線路のライン長が異なる場合は、最遠端のドレインドライバにおいて、一対の伝送線路30を終端する。図4は、このような場合を図示している。

SELC端子に入力される電圧がHレベルの時に、ドレインドライバ(2a、2b)の各々が、一対の伝送線路30の間に抵抗値が(n×Ra)(ここでは、200Ω)の抵抗を接続して、一対の伝送線路30を終端抵抗で終端する。図3は、このような場合を図示している。

以上の端子設定内容を表1に示す。

【0017】

【表1】

【0018】

また、図5に示すように、スレーブのドレインドライバが、2b、2cの2つの場合は、1番目のスレーブのドレインドライバと、2番目のスレーブのドレインドライバを認識する端子、ここではSELD1の端子を設ける。

図5では、スレーブのドレインドライバ(2b)のSELD1端子に入力される電圧がLレベル、スレーブのドレインドライバ(2c)のSELD1端子に入力される電圧がHレベルとなっているので、スレーブのドレインドライバ(2b)が1番目のスレーブのドレインドライバとして、スレーブのドレインドライバ(2c)が2番目のスレーブのドレインドライバとして認識する。

スレーブのドレインドライバがn(n≧3)以上の場合であっても同様に、SELD1端子ないしSELD(n−1)端子の(n−1)個の端子を設け、j(2≦j≦n)番目のスレーブのドレインドライバのSELD(j−1)端子に、Hレベルの電圧を入力し、それ以外のスレーブのドレインドライバのSELD1端子ないしSELD(n−1)端子に、Lレベルの電圧を入力することで、各スレーブのドレインドライバが、何番目のスレーブのドレインドライバかを認識することができる。

以上説明したように、本実施例によれば、端子の設定により、一対の伝送線路の終端方法を切り替えることができる。

また、1チップ構成、複数チップ構成を、端子の設定により、ドレインドライバに認識させることができるため、1種類のドレインドライバで低解像度から高解像度までの液晶表示パネルに対応可能であるばかりか、1系統の本体コンピュータで1チップ構成、または、複数チップ構成を制御できるため、本体コンピュータ側のシステムを容易に組むことが可能である。

さらに、高解像度クラスの液晶表示パネルに適用した場合、複数チップ構成とすることでドレインドライバから液晶表示パネルヘの斜め配線長が短くなり、額縁を狭くすることが可能となる。

【0019】

[実施例2]

図6は、本発明の実施例1の液晶表示装置の問題点を説明するための図である。なお、図6、および後述する図7、図8において、外部の本体コンピュータは、信号の送受信部のみを、ドレインドライバは、信号の送受信部のみを図示している。また、図6、および後述する図7、図8において、TX+は、正極性側の送受信部、TX−は、負極性側の送受信部、Pは、一対の伝送線路30の中の正極性側の伝送線路、Nは、一対の伝送線路30の中の負極性側の伝送線路である。

前述の実施例において、リバース転送時(データリード時)に、即ち、本体コンピュー夕8が、各ドレインドライバ(2a〜2c)から信号を読み出す時に、各ドレインドライバが送出する信号(図6では、A信号とB信号)が衝突する可能性がある。

そこで、本実施例では、リバース転送時に、リバース対象のドレインドライバを認識させるようにしたものである。

図7、図8は、本発明の実施例2の液晶表示装置における、リバース転送を説明するための図である。

図7、図8では、各ドレインドライバ(2a、2b)にREVSという端子を設け、REVS端子に入力される電圧に基づき、選択されたドレインドライバのみが信号を一対の伝送線路30に送出するようにしたものである。

図7では、マスタのドレインドライバ(2a)のREVS端子にHレベルの電圧が入力され、マスタのドレインドライバ(2a)が、一対の伝送線路30に信号を送出し、スレーブのドレインドライバ(2b)のREVS端子にLレベルの電圧が入力され、スレーブのドレインドライバ(2b)が、一対の伝送線路30に接続されているバッファ(トライステートバッファ)36の出力をハイインピーダンス(Hi−Z)とし、一対の伝送線路30に信号を送出しないようにする。

【0020】

図8では、スレーブのドレインドライバ(2b)のREVS端子にHレベルの電圧が入力され、スレーブのドレインドライバ(2b)が、一対の伝送線路30に信号を送出し、マスタのドレインドライバ(2a)のREVS端子にLレベルの電圧が入力され、マスタのドレインドライバ(2a)が、一対の伝送線路30に接続されているバッファ(トライステートバッファ)36の出力をハイインピーダンス(Hi−Z)とし、一対の伝送線路30に信号を送出しないようにする。

この場合、本体コンピュータが、次に、読み出し対象となるドレインドライバのREVS端子にHレベルの電圧を入力し、それ以外のREVS端子にLレベルの電圧を入力する。

また、各ドレインドライバ(2a、2b)にREVS端子を設ける代わりに、レジスタ35を設けることにより、前述と同様の動作を行うことができる。

即ち、読み出し対象のドレインドライバのレジスタ35に、読み出し許可のデータ(例えば、図7では、ドレインドライバ(2a)のレジスタ35の「1」のデータ)を書き込み、読み出し対象のドレインドライバが、一対の伝送線路30に信号を送出し、それ以外のドレインドライバには、レジスタ35に、読み出し不許可のデー夕(例えば、図7では、ドレインドライバ(2b)のレジスタ35の「0」のデータ)を書き込み、読み出し対象以外のドレインドライバが、一対の伝送線路30に接続されているバッファ(トライステートバッファ)36の出力をハイインピーダンス(Hi−Z)として、一対の伝送線路30に信号を送出しないようにすることもできる。

【0021】

[実施例3]

図9は、従来の液晶表示装置の概略構成を示すブロック図である。

図9に示す液晶表示装置は、液晶表示パネル1、ドレインドライバ2、ゲートドライバ3、表示制御回路4、電源回路5で構成される。ここで、表示制御回路4と、電源回路5は、液晶表示パネル1の周辺部(例えば、液晶表示装置の裏側)に配置される回路基板にそれぞれ実装される。

図9に示す従来の液晶表示装置は、表示制御回路4が、ドレインドライバ2の内部に内蔵される代わりに、外部に配置されている点で、前述の実施例と相違する。

図9に示す液晶表示装置において、表示制御回路4が、表示データを、一対の伝送線路を介して、差動シリアル伝送方式で、ドレインドライバ2に供給することが想定される。

このような場合に、前述の実施例1に説明した手法を適用することが可能である。但し、この場合、マスタ/スレーブ構成は必要ないので、各ドレインドライバ2は、SELA端子が必要なく、Lレベルの電圧が入力されるSELB端子を有するドレインドライバ2は、表示制御回路4から最も違い位置にあるドレインドライバとなる。

さらに、図9に示す液晶表示装置において、リバース転送時に、即ち、表示制御回路4が、各ドレインドライバ(2a〜2c)から信号を読み出す時に、前述の実施例2の手法を適用することも可能である。

なお、前述までの説明では、本発明を液晶表示装置に適用した実施例について説明したが、本発明はこれに限定されるものではなく、本発明は、例えば、有機EL表示装置などのサブピクセルを有する表示装置全般に適用可能であることはいうまでもない。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【符号の説明】

【0022】

1 液晶表示パネル

2 ドレインドライバ

2a マスタのドレインドライバ

2b,2c スレーブのドレインドライバ

3 ゲートドライバ

4,40 表示制御回路

5 電源回路

8 本体コンピュー夕

30 一対の伝送線路

35 レジスタ

36 バッファ(トライステートバッファ)

GL 走査線(ゲート線)

DL 映像線(ドレイン線,ソース線)

TFT 薄膜トランジスタ

PX 画素電極

CT 対向電極

CL 液晶容量

Cadd 保持容量

【技術分野】

【0001】

本発明は、表示装置に係り、特に、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給される表示装置に適用して有効な技術に関する。

【背景技術】

【0002】

アクティブ素子として薄膜トランジスタを使用するTFT方式の液晶表示装置は高精細な画像を表示できるため、テレビ、パソコン用ディスプレイ等の表示装置として使用されている。特に、小型のTFT方式の液晶表示装置は、携帯電話機の表示部として多用されている。

一般に、液晶表示装置では、隣接する2本の走査線(ゲート線ともいう。)と、隣接する2本の映像線(ソース線またはドレイン線ともいう。)とで囲まれる領域に、走査線からの走査信号によってオンする薄膜トランジスタと、映像線からの映像信号が薄膜トランジスタを介して供給される画素電極とが形成されて、所謂、サブピクセルが構成される。 これら複数のサブピクセルが形成された領域が表示領域であり、当該表示領域を囲んで周辺領域が存在する。周辺領域には、各映像線に映像電圧(階調電圧)を供給するドレインドライバ(ソースドライバともいう。)、及び各走査線に走査電圧を供給するゲートドライバが設けられる。

ドレインドライバおよびゲートドライバには、表示制御回路(タイミングコントローラともいう)から表示制御信号が入力され、ドレインドライバおよびゲートドライバは、表示制御回路により制御・駆動される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平10−258229号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、中小形機器向け液晶表示パネルは、高解像度化か進み、WVGAクラスの高精細の液晶表示パネルが主流を占めているが、高精細・高画質化の要求は留まることなく、タブレット端末等のハイエンドモデルではWXGA化が主流となっている。

このような状況に鑑み、低解像度〜高解像度クラスの幅広い液晶表示パネルに対応する為に、低解像度クラスの液晶表示パネルは、液晶ドライバを1チップ構成、高解像度クラスの液晶表示パネルは、液晶ドライバを複数チップ構成とし、1チップ構成と、複数チップ構成を切り替えられるようにすることが、低コスト化を図るためにも望ましい。

前記要望に答えるために、液晶ドライバに設けた端子により、液晶ドライバを1チップ構成、あるいは、複数チップ構成とすることが想定される。

その様な状況下において、差動シリアル伝送方式で入力信号が供給するための一対の伝送線路を終端する必要があり、さらには、一対の伝送線路を介して信号を読み出す時に、複数の信号が衝突するのを防止することが必要となる。

本発明は、前記要望に答えるためになされたものであり、本発明の目的は、表示装置において、端子設定により、一対の伝送線路の終端方法の切り替えること、あるいは、一対の伝送線路を介する信号の読み出し時に、信号が衝突するのを防止することが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【課題を解決するための手段】

【0005】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

(1)複数の画素と、前記複数の画素を駆動するn(n>2)個の駆動回路を備える表示装置であって、前記各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、前記各駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

(2)(1)において、前記各駆動回路は、SELA端子と、SELB端子を有し、前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第1電圧レベルの時に、前記各駆動回路は、前記マスタの駆動回路として動作し、前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第2電圧レベルの時に、前記各駆動回路は、前記スレーブの駆動回路として動作する。

(3)(1)または(2)において、前記各駆動回路は、SELD1端子ないしSELD(n−2)端子を有し、前記SELD1端子ないしSELD(n−2)端子のそれぞれに入力される電圧レベルに応じて、前記スレーブの駆動回路の各々は、何番目のスレーブの駆動回路かを認識する。

【0006】

(4)複数の画素と、前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各駆動回路は、REVS端子を有し、前記本体側が前記各駆動回路から信号を読み出す時に、前記REVS端子に第2電圧 レベルの電圧が入力される駆動回路のみが、前記一対の伝送線路にデータを送出する。

(5)複数の画素と、前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各駆動回路は、レジスタを有し、前記本体側が前記各駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた駆動回路のみが、前記一対の伝送線路に信号を送出する。

(6)(5)において、本体側から前記読み出し許可のデータを、次に読み出し対象となる駆動回路内のレジスタに書き込む。

(7)(1)ないし(6)の何れかにおいて、前記各駆動回路は、表示制御回路を有する映像線駆動回路である。

【0007】

(8)複数の画素と、前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、表示制御回路を備える表示装置であって、前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各映像線駆動回路は、SELC端子を有し、前記SELC端子に入力される電圧が第1電圧レベルの時に、1番目の映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、残りの映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端する。

(9)複数の画素と、前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、表示制御回路を備える表示装置であって、前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各映像線駆動回路は、REVS端子を有し、前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記REVS端子に第2電圧レベルの電圧が入力される映像線駆動回路のみが、前記一対の伝送線路に信号を送出する。

(10)複数の画素と、前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、表示制御回路を備える表示装置であって、前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、前記各駆動回路は、レジスタを有し、前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた映像線駆動回路のみが、前記−対の伝送線路に信号を送出する。

(11)(10)において、前記表示制御回路から前記読み出し許可のデータを、次に読み出し対象となる映像線駆動回路内のレジスタに書き込む。

【発明の効果】

【0008】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明の表示装置によれば、端子設定により、一対の伝送線路の終端方法の切り替えること、あるいは、一対の伝送線路を介する信号の読み出し時に、信号が衝突するのを防止することが可能となる。

【図面の簡単な説明】

【0009】

【図1】本発明の実施例1の液晶表示装置の概略構成を示すブロック図である。

【図2】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

【図3】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

【図4】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

【図5】本発明の実施例1のドレインドライバの端子設定を説明するための図である。

【図6】本発明の実施例1の液晶表示装置の問題点を説明するための図である。

【図7】本発明の実施例2のドレインドライバの端子設定を説明するための図である。

【図8】本発明の実施例2のドレインドライバの端子設定を説明するための図である。

【図9】従来の液晶表示装置の概略構成を示すブロック図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

[実施例1]

図1は、本発明の実施例1の液晶表示装置の概略構成を示すブロック図である。

本実施例の液晶表示装置は、液晶表示パネル1、ドレインドライバ(2a〜2c)、ゲートドライバ3、電源回路5で構成される。

ドレインドライバ(2a〜2c)と、ゲートドライバ3は、液晶表示パネル1の周辺部に設置される。例えば、ドレインドライバ(2a〜2c)と、ゲートドライバ3は、液晶表示パネル1の一対の基板の第1の基板(例えば、ガラス基板)の2辺の周辺部に、それぞれCOG方式で実装される。あるいは、ドレインドライバ(2a〜2c)と、ゲートドライバ3は、液晶表示パネル1の第1の基板の2辺の周辺部に配置されるフレキシブル回路基板に、それぞれCOF方式で実装される。

また、電源回路5は、液晶表示パネル1の周辺部(例えば、液晶表示装置の裏側)に配置される回路基板に実装される。

図1において、40は表示制御回路であり、本実施例の液晶表示装置は、表示制御回路40を、それぞれのドレインドライバに内蔵している。

【0011】

表示制御回路40は、本体コンピュータ8から入力する表示信号を、データの交流化等、液晶表示パネル1の表示に適したタイミング調整を行い、表示形式の入力信号に変換して同期信号(クロック信号)と共にドレインドライバ(2a〜2c)、ゲートドライバ3に入力する。

ゲートドライバ3は、表示制御回路40の制御の基に走査線(ゲート線ともいう;GL)に選択走査電圧を順次供給し、また、ドレインドライバ(2a〜2c)は、映像線(ドレイン線、ソース線ともいう;DL)に映像電圧を供給して映像を表示する。電源回路5は液晶表示装置に要する各種の電圧を生成する。

液晶表示パネル1は、複数のサブピクセルを有し、各サブピクセルは、映像線(DL)と走査線(GL)とで囲まれた領域に設けられる。

各サブピクセルは、薄膜トランジスタ(TFT)を有し、薄膜トランジスタ(TFT)の第1の電極(ドレイン電極またはソース電極)は映像線(DL)に接続され、薄膜トランジスタ(TFT)の第2の電極(ソース電極またはドレイン電極)は画素電極(PX)に接続される。また、薄膜トランジスタ(TFT)のゲート電極は、走査線(GL)に接続される。

なお、図1において、CLは、画素電極(PX)と対向電極(CT)との間に配置される液晶層を等価的に示す液晶容量であり、Caddは、画素電極(PX)と対向電極(CT)との間に形成される保持容量である。

【0012】

図1に示す液晶表示パネル1において、列方向に配置された各サブピクセルの薄膜トランジスタ(TFT)の第1の電極は、それぞれ映像線(DL)に接続され、各映像線(DL)は列方向に配置されたサブピクセルに、表示データに対応する映像電圧を供給するドレインドライバ(2a〜2c)に接続される。

また、行方向に配置された各サブピクセルにおける薄膜トランジスタ(TFT)のゲート電極は、それぞれ走査線(GL)に接続され、各走査線(GL)は、1水平走査時間、薄膜トランジスタ(TFT)のゲートに走査電圧(正または負のバイアス電圧)を供給するゲートドライバ3に接続される。

液晶表示パネル1に画像を表示する際、ゲートドライバ3は、走査線(GL)を、順次、例えば、上から下に向かって選択し、一方、ある走査線の選択期間中に、ドレインドライバ(2a〜2c)は、表示データに対応する映像電圧を、映像線(DL)に供給する。

映像線(DL)に供給された電圧は、薄膜トランジスタ(TFT)を経由して、画素電極(PX)に印加され、最終的に、保持容量(Cadd)と、液晶容量(CL)に電荷がチャージされ、液晶分子をコントロールすることにより画像が表示される。

【0013】

液晶表示パネル1は、画素電極(PX)、薄膜トランジスタ(TFT)等が形成される第1の基板と、カラーフィルタ等が形成される第2の基板とを、所定の間隙を隔てて重ね合わせ、該両基板間の周縁部近傍に枠状に設けたシール材により、両基板を貼り合わせると共に、シール材の一部に設けた液晶封入ロから両基板間のシール材の内側に液晶を封入、封止し、さらに、両基板の外側に偏光板を貼り付けて構成される。

なお、対向電極(CT)は、TN方式やVA方式の液晶表示パネルであれば第2の基板側に設けられる。IPS方式の場合は、第1の基板側に設けられる。

また、本発明は、液晶パネルの内部構造とは関係がないので、液晶パネルの内部構造の詳細な説明は省略する。さらに、本発明は、どのような構造の液晶パネルであっても適用可能である。

【0014】

本実施例の液晶表示装置では、表示制御回路40を、それぞれのドレインドライバに内蔵しているが、ドレインドライバ(2a〜2c)のそれぞれに、表示制御回路40を内蔵すると、それぞれのドレインドライバに内蔵された各表示制御回路40の同期を取る必要が生じる。そこで、本実施例では、複数のドレインドライバの中の1つのドレインドライバをマスタのドレインドライバ(図1では、2aで示すドレインドライバ)として動作させ、それ以外のドレインドライバをスレーブのドレインドライバ(図1では、2b、2cで示すドレインドライバ)として動作させる。

マスタのドレインドライバ(2a)は、自走用クロックを生成し、スレーブのドレインドライバ(2b、2c)には、マスタのドレインドライバ(2a)で生成された自走用クロックが入力される。これにより、マスタのドレインドライバ(2a)も、スレーブのドレインドライバ(2b、2c)も同期して動作することが可能となる。

また、マスタのドレインドライバ(2a)からゲートドライバ制御信号6が先頭のゲートドライバ3に入力され、ゲートドライバデータ転送信号7により、先頭のゲートドライバ3から後段のゲートドライバ3に対して、ゲートドライバ制御信号が転送される。

このように、本実施例の液晶表示装置では、ドレインドライバ(2a〜2c)内に、表示制御回路40を内蔵することにより、部品点数を削減することができるので、コストを低減することが可能となる。

【0015】

本実施例では、外部の本体コンピュータ8から入力される表示信号は、表示データを含み、表示データを含む入力信号は、本体コンピュー夕8から一対の伝送線路を介して、差動シリアル伝送方式で、ドレインドライバ(2a〜2c)に供給される。

図2ないし図4は、本実施例のドレインドライバの端子設定を説明するための図である。なお、図2ないし図4、及び、後述する図5において、本体コンピュータは、信号の送受信部のみを、ドレインドライバは、信号の受信部のみを図示している。また、図2ないし図4、図5において、TX+は、正極性側の送受信部、TX−は、負極性側の送受信部、Pは、一対の伝送線路30の中の正極性側の伝送線路、Nは、一対の伝送線路30の中の負極性側の伝送線路である。

図2ないし図4に示すように、本実施例のドレインドライバでは、SELA端子、SELB端子、SELC端子が設けられる。

SELA端子に入力される電圧がLow(以下、Lレベル)の時に、図2に示すように、1チップ構成となり、SELA端子に入力される電圧がHigh(以下、Hレベル)の時に、図3、図4に示すように、複数チップ構成となる。

そして、図2、図3に示すように、SELA端子に入力される電圧がHigh(以下、Hレベル)、SELB端子に入力される電圧がLレベルの時に、本実施例のドレインドライバは、マスタのドレインドライバ(2a)として動作し、SELA端子に入力される電圧がHレベル、SELB端子に入力される電圧がHレベルの時に、本実施例のドレインドライバは、スレーブのドレインドライバ(2b)として動作する。

【0016】

表示データを含む入力信号は、本体コンピュータ8から一対の伝送線路30を介して、差動シリアル伝送方式で、ドレインドライバに供給されるが、一対の伝送線路30は、終端抵抗で終端する必要がある。 SELC端子は、一対の伝送線路の終端方法を設定するために設けられる。

SELC端子に入力される電圧がLレベルの時に、マスタのドレインドライバ(2a)は、その内部で一対の伝送線路30の間に抵抗値がRa(ここでは、100Ω)の抵抗を接続して、一対の伝送線路30を終端し、スレーブのドレインドライバ(2b)が、その内部で一対の伝送線路30の間に抵抗を接続しないで、一対の伝送線路30を開放する。

一般に、差動シリアル伝送方式では、本体コンピュー夕8から各ドレインドライバ (2a〜2c)までの、一対の伝送線路のライン長が異なる場合は、最遠端のドレインドライバにおいて、一対の伝送線路30を終端する。図4は、このような場合を図示している。

SELC端子に入力される電圧がHレベルの時に、ドレインドライバ(2a、2b)の各々が、一対の伝送線路30の間に抵抗値が(n×Ra)(ここでは、200Ω)の抵抗を接続して、一対の伝送線路30を終端抵抗で終端する。図3は、このような場合を図示している。

以上の端子設定内容を表1に示す。

【0017】

【表1】

【0018】

また、図5に示すように、スレーブのドレインドライバが、2b、2cの2つの場合は、1番目のスレーブのドレインドライバと、2番目のスレーブのドレインドライバを認識する端子、ここではSELD1の端子を設ける。

図5では、スレーブのドレインドライバ(2b)のSELD1端子に入力される電圧がLレベル、スレーブのドレインドライバ(2c)のSELD1端子に入力される電圧がHレベルとなっているので、スレーブのドレインドライバ(2b)が1番目のスレーブのドレインドライバとして、スレーブのドレインドライバ(2c)が2番目のスレーブのドレインドライバとして認識する。

スレーブのドレインドライバがn(n≧3)以上の場合であっても同様に、SELD1端子ないしSELD(n−1)端子の(n−1)個の端子を設け、j(2≦j≦n)番目のスレーブのドレインドライバのSELD(j−1)端子に、Hレベルの電圧を入力し、それ以外のスレーブのドレインドライバのSELD1端子ないしSELD(n−1)端子に、Lレベルの電圧を入力することで、各スレーブのドレインドライバが、何番目のスレーブのドレインドライバかを認識することができる。

以上説明したように、本実施例によれば、端子の設定により、一対の伝送線路の終端方法を切り替えることができる。

また、1チップ構成、複数チップ構成を、端子の設定により、ドレインドライバに認識させることができるため、1種類のドレインドライバで低解像度から高解像度までの液晶表示パネルに対応可能であるばかりか、1系統の本体コンピュータで1チップ構成、または、複数チップ構成を制御できるため、本体コンピュータ側のシステムを容易に組むことが可能である。

さらに、高解像度クラスの液晶表示パネルに適用した場合、複数チップ構成とすることでドレインドライバから液晶表示パネルヘの斜め配線長が短くなり、額縁を狭くすることが可能となる。

【0019】

[実施例2]

図6は、本発明の実施例1の液晶表示装置の問題点を説明するための図である。なお、図6、および後述する図7、図8において、外部の本体コンピュータは、信号の送受信部のみを、ドレインドライバは、信号の送受信部のみを図示している。また、図6、および後述する図7、図8において、TX+は、正極性側の送受信部、TX−は、負極性側の送受信部、Pは、一対の伝送線路30の中の正極性側の伝送線路、Nは、一対の伝送線路30の中の負極性側の伝送線路である。

前述の実施例において、リバース転送時(データリード時)に、即ち、本体コンピュー夕8が、各ドレインドライバ(2a〜2c)から信号を読み出す時に、各ドレインドライバが送出する信号(図6では、A信号とB信号)が衝突する可能性がある。

そこで、本実施例では、リバース転送時に、リバース対象のドレインドライバを認識させるようにしたものである。

図7、図8は、本発明の実施例2の液晶表示装置における、リバース転送を説明するための図である。

図7、図8では、各ドレインドライバ(2a、2b)にREVSという端子を設け、REVS端子に入力される電圧に基づき、選択されたドレインドライバのみが信号を一対の伝送線路30に送出するようにしたものである。

図7では、マスタのドレインドライバ(2a)のREVS端子にHレベルの電圧が入力され、マスタのドレインドライバ(2a)が、一対の伝送線路30に信号を送出し、スレーブのドレインドライバ(2b)のREVS端子にLレベルの電圧が入力され、スレーブのドレインドライバ(2b)が、一対の伝送線路30に接続されているバッファ(トライステートバッファ)36の出力をハイインピーダンス(Hi−Z)とし、一対の伝送線路30に信号を送出しないようにする。

【0020】

図8では、スレーブのドレインドライバ(2b)のREVS端子にHレベルの電圧が入力され、スレーブのドレインドライバ(2b)が、一対の伝送線路30に信号を送出し、マスタのドレインドライバ(2a)のREVS端子にLレベルの電圧が入力され、マスタのドレインドライバ(2a)が、一対の伝送線路30に接続されているバッファ(トライステートバッファ)36の出力をハイインピーダンス(Hi−Z)とし、一対の伝送線路30に信号を送出しないようにする。

この場合、本体コンピュータが、次に、読み出し対象となるドレインドライバのREVS端子にHレベルの電圧を入力し、それ以外のREVS端子にLレベルの電圧を入力する。

また、各ドレインドライバ(2a、2b)にREVS端子を設ける代わりに、レジスタ35を設けることにより、前述と同様の動作を行うことができる。

即ち、読み出し対象のドレインドライバのレジスタ35に、読み出し許可のデータ(例えば、図7では、ドレインドライバ(2a)のレジスタ35の「1」のデータ)を書き込み、読み出し対象のドレインドライバが、一対の伝送線路30に信号を送出し、それ以外のドレインドライバには、レジスタ35に、読み出し不許可のデー夕(例えば、図7では、ドレインドライバ(2b)のレジスタ35の「0」のデータ)を書き込み、読み出し対象以外のドレインドライバが、一対の伝送線路30に接続されているバッファ(トライステートバッファ)36の出力をハイインピーダンス(Hi−Z)として、一対の伝送線路30に信号を送出しないようにすることもできる。

【0021】

[実施例3]

図9は、従来の液晶表示装置の概略構成を示すブロック図である。

図9に示す液晶表示装置は、液晶表示パネル1、ドレインドライバ2、ゲートドライバ3、表示制御回路4、電源回路5で構成される。ここで、表示制御回路4と、電源回路5は、液晶表示パネル1の周辺部(例えば、液晶表示装置の裏側)に配置される回路基板にそれぞれ実装される。

図9に示す従来の液晶表示装置は、表示制御回路4が、ドレインドライバ2の内部に内蔵される代わりに、外部に配置されている点で、前述の実施例と相違する。

図9に示す液晶表示装置において、表示制御回路4が、表示データを、一対の伝送線路を介して、差動シリアル伝送方式で、ドレインドライバ2に供給することが想定される。

このような場合に、前述の実施例1に説明した手法を適用することが可能である。但し、この場合、マスタ/スレーブ構成は必要ないので、各ドレインドライバ2は、SELA端子が必要なく、Lレベルの電圧が入力されるSELB端子を有するドレインドライバ2は、表示制御回路4から最も違い位置にあるドレインドライバとなる。

さらに、図9に示す液晶表示装置において、リバース転送時に、即ち、表示制御回路4が、各ドレインドライバ(2a〜2c)から信号を読み出す時に、前述の実施例2の手法を適用することも可能である。

なお、前述までの説明では、本発明を液晶表示装置に適用した実施例について説明したが、本発明はこれに限定されるものではなく、本発明は、例えば、有機EL表示装置などのサブピクセルを有する表示装置全般に適用可能であることはいうまでもない。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【符号の説明】

【0022】

1 液晶表示パネル

2 ドレインドライバ

2a マスタのドレインドライバ

2b,2c スレーブのドレインドライバ

3 ゲートドライバ

4,40 表示制御回路

5 電源回路

8 本体コンピュー夕

30 一対の伝送線路

35 レジスタ

36 バッファ(トライステートバッファ)

GL 走査線(ゲート線)

DL 映像線(ドレイン線,ソース線)

TFT 薄膜トランジスタ

PX 画素電極

CT 対向電極

CL 液晶容量

Cadd 保持容量

【特許請求の範囲】

【請求項1】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の駆動回路を備える表示装置であって、

前記各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、

前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、

前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、

前記各駆動回路は、SELC端子を有し、

前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、

前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端することを特徴とする表示装置。

【請求項2】

前記各駆動回路は、SELA端子と、SELB端子を有し、

前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第1電圧レベルの時に、前記各駆動回路は、前記マスタの駆動回路として動作し、

前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第2電圧レベルの時に、前記各駆動回路は、前記スレーブの駆動回路として動作することを特徴とする請求項1に記載の表示装置。

【請求項3】

前記各駆動回路は、SELD1端子ないしSELD(n−2)端子を有し、

前記SELD1端子ないしSELD(n−2)端子のそれぞれに入力される電圧レベルに応じて、前記スレーブの駆動回路の各々は、何番目のスレーブの駆動回路かを認識することを特徴とする請求項1または請求項2に記載の表示装置。

【請求項4】

複数の画素と、

前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、

前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各駆動回路は、REVS端子を有し、

前記本体側が前記各駆動回路から信号を読み出す時に、前記REVS端子に第2電圧 レベルの電圧が入力される駆動回路のみが、前記一対の伝送線路にデータを送出することを特徴とする表示装置。

【請求項5】

複数の画素と、

前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、

前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各駆動回路は、レジスタを有し、

前記本体側が前記各駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた駆動回路のみが、前記一対の伝送線路に信号を送出することを特徴とする表示装置。

【請求項6】

本体側から前記読み出し許可のデータを、次に読み出し対象となる駆動回路内のレジスタに書き込むことを特徴とする請求項5に記載の表示装置。

【請求項7】

前記各駆動回路は、表示制御回路を有する映像線駆動回路であることを特徴とする請求項1ないし請求項6のいずれか1項に記載の表示装置。

【請求項8】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、

表示制御回路を備える表示装置であって、

前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各映像線駆動回路は、SELC端子を有し、

前記SELC端子に入力される電圧が第1電圧レベルの時に、1番目の映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、残りの映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、

前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端することを特徴とする表示装置。

【請求項9】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、

表示制御回路を備える表示装置であって、

前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信 号が差動シリアル伝送方式で供給され、

前記各映像線駆動回路は、REVS端子を有し、

前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記REVS端子に第2電圧レベルの電圧が入力される映像線駆動回路のみが、前記一対の伝送線路に信号を送出することを特徴とする表示装置。

【請求項10】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、

表示制御回路を備える表示装置であって、

前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各駆動回路は、レジスタを有し、

前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた映像線駆動回路のみが、前記−対の伝送線路に信号を送出することを特徴とする表示装置。

【請求項11】

前記表示制御回路から前記読み出し許可のデータを、次に読み出し対象となる映像線駆動回路内のレジスタに書き込むことを特徴とする請求項10に記載の表示装置。

【請求項1】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の駆動回路を備える表示装置であって、

前記各駆動回路には、本体側より、一対の伝送線路を介して、表示データが差動シリアル伝送方式で供給され、

前記n個の駆動回路の中の1つの駆動回路は、マスタの駆動回路として動作し、

前記n個の駆動回路の中の前記マスタの駆動回路以外の駆動回路はスレーブの駆動回路として動作し、

前記各駆動回路は、SELC端子を有し、

前記SELC端子に入力される電圧が第1電圧レベルの時に、前記マスタの駆動回路は、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、前記スレーブの駆動回路は、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、

前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端することを特徴とする表示装置。

【請求項2】

前記各駆動回路は、SELA端子と、SELB端子を有し、

前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第1電圧レベルの時に、前記各駆動回路は、前記マスタの駆動回路として動作し、

前記SELA端子に入力される電圧が第2電圧レベル、前記SELB端子に入力される電圧が第2電圧レベルの時に、前記各駆動回路は、前記スレーブの駆動回路として動作することを特徴とする請求項1に記載の表示装置。

【請求項3】

前記各駆動回路は、SELD1端子ないしSELD(n−2)端子を有し、

前記SELD1端子ないしSELD(n−2)端子のそれぞれに入力される電圧レベルに応じて、前記スレーブの駆動回路の各々は、何番目のスレーブの駆動回路かを認識することを特徴とする請求項1または請求項2に記載の表示装置。

【請求項4】

複数の画素と、

前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、

前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各駆動回路は、REVS端子を有し、

前記本体側が前記各駆動回路から信号を読み出す時に、前記REVS端子に第2電圧 レベルの電圧が入力される駆動回路のみが、前記一対の伝送線路にデータを送出することを特徴とする表示装置。

【請求項5】

複数の画素と、

前記複数の画素を駆動する複数の駆動回路を備える表示装置であって、

前記各駆動回路には、本体側より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各駆動回路は、レジスタを有し、

前記本体側が前記各駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた駆動回路のみが、前記一対の伝送線路に信号を送出することを特徴とする表示装置。

【請求項6】

本体側から前記読み出し許可のデータを、次に読み出し対象となる駆動回路内のレジスタに書き込むことを特徴とする請求項5に記載の表示装置。

【請求項7】

前記各駆動回路は、表示制御回路を有する映像線駆動回路であることを特徴とする請求項1ないし請求項6のいずれか1項に記載の表示装置。

【請求項8】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、

表示制御回路を備える表示装置であって、

前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各映像線駆動回路は、SELC端子を有し、

前記SELC端子に入力される電圧が第1電圧レベルの時に、1番目の映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗値がRaの抵抗を接続して前記一対の伝送線路を終端し、残りの映像線駆動回路が、その内部で前記一対の伝送線路の間に抵抗を接続しないで前記一対の伝送線路を開放し、

前記SELC端子に入力される電圧が前記第1電圧レベルとは異なる第2電圧レベルの時に、前記n個の駆動回路の各々が、その内部で前記一対の伝送線路の間に抵抗値が(n×Ra)の抵抗を接続して前記一対の伝送線路を終端することを特徴とする表示装置。

【請求項9】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、

表示制御回路を備える表示装置であって、

前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信 号が差動シリアル伝送方式で供給され、

前記各映像線駆動回路は、REVS端子を有し、

前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記REVS端子に第2電圧レベルの電圧が入力される映像線駆動回路のみが、前記一対の伝送線路に信号を送出することを特徴とする表示装置。

【請求項10】

複数の画素と、

前記複数の画素を駆動するn(n>2)個の映像線駆動回路と、

表示制御回路を備える表示装置であって、

前記各映像線駆動回路には、前記表示制御回路より、一対の伝送線路を介して、入力信号が差動シリアル伝送方式で供給され、

前記各駆動回路は、レジスタを有し、

前記表示制御回路が前記各映像線駆動回路から信号を読み出す時に、前記レジスタ内に読み出し許可のデータが書き込まれた映像線駆動回路のみが、前記−対の伝送線路に信号を送出することを特徴とする表示装置。

【請求項11】

前記表示制御回路から前記読み出し許可のデータを、次に読み出し対象となる映像線駆動回路内のレジスタに書き込むことを特徴とする請求項10に記載の表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−76814(P2013−76814A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−216150(P2011−216150)

【出願日】平成23年9月30日(2011.9.30)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月30日(2011.9.30)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

[ Back to top ]