表示装置

【課題】高開口率を有し、容量の大きな保持容量を有する表示装置を提供する。

【解決手段】第1導電膜によるゲート電極と、第1導電膜上の第1絶縁層によるゲート絶縁膜と、第1絶縁層上にゲート電極と重なる第1半導体層と、第1半導体層上かつゲート電極に重なる第2絶縁層によるチャネル保護膜と、第1半導体層と重なりソース領域及びドレイン領域に分離された導電性の第2半導体層と、第2半導体層上の第2導電膜によるソース電極及びドレイン電極とを含む薄膜トランジスタと、第2導電膜上に形成された第3絶縁層と、第3絶縁層上の第3導電膜により形成され、ソース電極またはドレイン電極の一方と接続する画素電極と、第1絶縁層上の容量配線と、容量配線上の第3絶縁層を挟んで、画素電極の重畳領域に形成される保持容量とを有する表示装置及びその作製方法。

【解決手段】第1導電膜によるゲート電極と、第1導電膜上の第1絶縁層によるゲート絶縁膜と、第1絶縁層上にゲート電極と重なる第1半導体層と、第1半導体層上かつゲート電極に重なる第2絶縁層によるチャネル保護膜と、第1半導体層と重なりソース領域及びドレイン領域に分離された導電性の第2半導体層と、第2半導体層上の第2導電膜によるソース電極及びドレイン電極とを含む薄膜トランジスタと、第2導電膜上に形成された第3絶縁層と、第3絶縁層上の第3導電膜により形成され、ソース電極またはドレイン電極の一方と接続する画素電極と、第1絶縁層上の容量配線と、容量配線上の第3絶縁層を挟んで、画素電極の重畳領域に形成される保持容量とを有する表示装置及びその作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及びその作製方法に関する。

【背景技術】

【0002】

ノート型のパーソナルコンピュータやデスクトップ型のパーソナルコンピュータ用のモ

ニタ、携帯電話、音楽再生装置、テレビ、携帯端末、デジタルスチルカメラ、ビデオカメ

ラ、画像・動画閲覧専用のビューワ等の電子機器に、画像や文字情報を表示するためのア

クティブマトリクス型表示装置は幅広く用いられている。

【0003】

アクティブマトリクス型表示装置は、表示領域となる画素部において能動素子(例えば

薄膜トランジスタ(Thin Film Transistor:TFT))を個々の画

素に対応してマトリクス状に配置して構成している。TFTはスイッチング素子として画

素に印加される電圧を制御し所望の画像表示を行っている。

【0004】

スイッチング素子として用いられるTFTのうち、チャネルストッパ型(チャネル保護

型、エッチストッパ型ともいう)の逆スタガ型TFTを有する素子基板は、5枚のフォト

マスクを用いて画素電極までを作製していた(特許文献1参照)。

【0005】

従来のチャネルストッパ型の逆スタガ型TFT及びそれを含む画素部の例を図6、図7

、図8(A)〜図8(C)、図9(A)〜図9(B)に示す。図6は一画素及びその周辺

の上面図であり、図7は図6のB−B’における断面図である。図8(A)〜図8(C)

、図9(A)〜図9(B)は、図7に至る作製工程を示す断面図である。

【0006】

一画素には、TFT領域1141、容量領域1142、配線領域1143が基板110

1上に設けられている。TFT領域1141には、ゲート配線1102、ゲート絶縁膜1

104、チャネル形成領域を有するi型半導体層1113、絶縁膜からなるチャネル保護

膜1108、一導電性を付与する不純物元素を有する半導体層からなるソース領域111

8及びドレイン領域1117、ソース配線1122、ドレイン電極1121、保護膜11

27、画素電極1131が設けられている。

【0007】

容量領域1142には、容量配線1151、ゲート絶縁膜1104、保護膜1127、

画素電極1131が設けられている。また配線領域1143には、ソース配線1122が

設けられている。

【0008】

容量領域1142は、ゲート配線1102と同じ材料及び同じ工程で形成された容量配

線1151、並びに、画素電極1131を上下の電極とし、電極間に挟まれたゲート絶縁

膜1104と保護膜1127とを誘電体とした構成であった。

【0009】

従来のチャネルストッパ型の逆スタガ型TFT及び画素部を作製するには、まず基板1

101上に第1の導電膜1161を形成し、さらに第1の導電膜1161上にレジストマ

スク1162を形成する(図8(A)参照)。

【0010】

ここでレジストマスクは、レジスト材料を塗布し、フォトマスクを用いて露光し、さら

に現像という工程を経ることにより形成される。塗布されたレジスト材料を上方から露光

する場合には、レジストマスクを形成するには、フォトマスクが1枚必要になる。すなわ

ち、レジストマスク1162を形成するには、第1のフォトマスクが必要である。

【0011】

レジストマスク1162をマスクとして、第1の導電膜1161をエッチングし、ゲー

ト配線1102及び容量配線1151を形成する。次いでレジストマスク1162を除去

後、ゲート絶縁膜1104、半導体層1105、絶縁膜1106を成膜する。次いでチャ

ネル保護膜1108を形成する領域に、レジストマスク1109を形成する(図8(B)

参照)。すなわちレジストマスク1109を形成するために、第2のフォトマスクを用い

る必要がある。

【0012】

次いでレジストマスク1109をマスクとして、絶縁膜1106をエッチングして、チ

ャネル保護膜1108を形成する。レジストマスク1109を除去後、半導体層1105

及びチャネル保護膜1108上に、一導電性を付与する不純物元素を含む半導体層111

1、第2の導電膜1112を成膜する。第2の導電膜1112上に、レジストマスク11

25を形成する(図8(C)参照)。すなわち第3のフォトマスクが用いられる。

【0013】

レジストマスク1125をマスクとして、第2の導電膜1112及び半導体層1111

をエッチングする。このとき、チャネル保護膜1108及びゲート絶縁膜1104がエッ

チングストッパとして機能する。これにより第2の導電膜1112は分断されて、ソース

配線1122及びドレイン電極1121が形成される。また一導電性を付与する不純物元

素を含む半導体層1111も分断され、ソース領域1118及びドレイン領域1117に

分断される。さらに半導体層1105もエッチングされ、その端部は、ドレイン領域11

17及びドレイン電極1121の端部と一致する。次いでレジストマスク1125を除去

後、保護膜1127を全面に成膜し、さらにレジストマスク1128を形成する(図9(

A)参照)。すなわち第4のフォトマスクが用いられる。

【0014】

レジストマスク1128を用いて、保護膜1127をエッチングしてコンタクトホール

1173を形成する。レジストマスク1128を除去後、第3の導電膜1129を成膜し

、第3の導電膜1129上の、画素電極1131が形成される領域に、レジストマスク1

134を形成する(図9(B)参照)。すなわち第5のフォトマスクが用いられる。

【0015】

レジストマスク1134をマスクとして、第3の導電膜1129がエッチングされ、画

素電極1131が形成される。次いでレジストマスク1134を除去すると、図7に示す

画素部が完成する。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2002−148658号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

従来の画素部の作製には、フォトマスクが5枚必要であった。フォトマスクが1枚増え

ると、レジスト材料を塗布、フォトマスクを用いて露光、現像という工程の他に、露光前

のプリベーク、露光後のポストベーク、レジスト剥離、レジスト剥離後の洗浄、洗浄後の

乾燥等、様々な工程が増え、作製時間や作製コストが増大する。

【0018】

また剥離できなかったレジスト材料が、素子の中に入り込み、不良の原因となる恐れも

ある。このため素子や装置の信頼性が低くなってしまう可能性もある。

【0019】

また、図6及び図7に示す構成において、保持容量の誘電体膜は、ゲート絶縁膜110

4と保護膜1127という二層の絶縁膜で構成される。そのため、誘電体膜が絶縁膜一層

である場合と比べて、誘電体が絶縁膜二層であると保持容量は小さくなってしまう。

【0020】

容量は誘電体膜の膜厚に反比例し、面積に比例する。従って、目的とする保持容量の値

を確保するためには、容量領域1142の面積を大きく取る必要があった。

【0021】

しかしながら容量領域1142の面積を大きくしてしまうと、画素部の開口率が低下し

てしまう。

【0022】

そこで本発明は、フォトマスクの数を増やさず、かつ、画素部の開口率を低下させずに

、誘電体膜の厚さを薄くして容量を増加させることを目的とする。

【課題を解決するための手段】

【0023】

本発明は、チャネルストッパ型の逆スタガ型TFTにおいて、高開口率を得るため、保

持容量を、画素電極、並びに、ソース電極及びドレイン電極と同様の材料及び同様の工程

により形成される導電膜(以下、第2の導電膜という)を用いて形成する。画素電極と第

2の導電膜の間の誘電体膜は保護膜一層のみとする。これにより、高開口率な画素部と容

量の大きな保持容量を同時に得ることができる。

【0024】

ソース配線もゲート配線と同様の材料及び同様の工程により形成される導電膜(以下、

第1の導電膜という)で形成する。また、ソース配線とゲート配線の交差部については、

いずれか一方の配線を交差する部分で分断し、第2の導電膜により中継する。

【0025】

特に、第1の導電膜と第2の導電膜との中継において、画素電極の材料である透光性導

電膜を使用する。第1の導電膜と第2の導電膜とを接続させる場合、従来ではゲート絶縁

膜のコンタクトホール形成工程が必要となる。

【0026】

しかし本発明においては、後述する構造とすることで、ゲート絶縁膜のコンタクトホー

ル形成工程を行わなくてもよい。すなわち、第1の導電膜上のゲート絶縁膜、半導体層、

第2の導電膜にコンタクトホールを形成し(第1のコンタクトホール)、さらに第1のコ

ンタクトホールよりも広いコンタクトホールを保護膜に形成する(第2のコンタクトホー

ル)。第2のコンタクトホールに接する透光性導電膜を、第2のコンタクトホール内に部

分的に露出した第2の導電膜と、第1のコンタクトホール内に露出した第1の導電膜に接

続させる。

【0027】

第1のコンタクトホールを作製する際、TFTにはチャネル保護膜があるため、i型半

導体層のエッチングが阻害され、第1のコンタクトホールにおける半導体層だけを選択的

にエッチングすることができる。

【0028】

本発明は、第1の導電膜により形成されるゲート電極と、前記第1の導電膜上の第1の

絶縁層で形成されるゲート絶縁膜と、前記第1の絶縁層上に、前記ゲート電極と重なる第

1の半導体層と、前記第1の半導体層上に配置され、かつ、前記ゲート電極に重なる第2

の絶縁層で形成されるチャネル保護膜と、前記第1の半導体層と重なり、一端がチャネル

保護膜上に延び、ソース領域及びドレイン領域に分離された、一導電性を付与する不純物

元素を有する第2の半導体層と、前記第2の半導体層上の第2の導電膜により形成され、

前記ソース領域及びドレイン領域に対応して形成されたソース電極及びドレイン電極と、

を含む薄膜トランジスタと、前記第2の導電膜上に形成された第3の絶縁層と、前記第3

の絶縁層上の第3の導電膜により形成され、前記第3の絶縁層に形成されたコンタクトホ

ールを介して前記ソース電極またはドレイン電極の一方と電気的に接続する画素電極と、

前記第1の絶縁層上の、前記第1の半導体層、前記第2の半導体層及び前記第2の導電膜

の積層体で形成される容量配線と、前記容量配線上の前記第3の絶縁層と、前記画素電極

の重畳領域に形成される保持容量とを有する表示装置に関する。

【0029】

また本発明は、第1の導電膜により形成されるゲート電極と、前記第1の導電膜上の第

1の絶縁層で形成されるゲート絶縁膜と、前記第1の絶縁層上に、前記ゲート電極と重な

る第1の半導体層と、前記第1の半導体層上に配置され、かつ、前記ゲート電極に重なる

第2の絶縁層で形成されるチャネル保護膜と、前記第1の半導体層と重なり、一端がチャ

ネル保護膜上に延び、ソース領域及びドレイン領域に分離された、一導電性を付与する不

純物元素を有する第2の半導体層と、前記第2の半導体層上の第2の導電膜により形成さ

れ、前記ソース領域及びドレイン領域に対応して形成されたソース電極及びドレイン電極

と、を含む薄膜トランジスタと、前記第2の導電膜上に形成された第3の絶縁層と、前記

第3の絶縁層上の第3の導電膜により形成され、前記第3の絶縁層に形成されたコンタク

トホールを介して前記ソース電極またはドレイン電極の一方と電気的に接続する画素電極

と、前記第1の絶縁層上の、前記第1の半導体層、前記第2の半導体層及び前記第2の導

電膜の積層体で形成される容量配線と、前記容量配線上の前記第3の絶縁層と、前記画素

電極の重畳領域に形成される保持容量と、前記第1の導電膜により形成される配線と、前

記配線上の前記第3の導電膜により形成され、前記ソース電極またはドレイン電極の他方

の上面と側面に接する電極とを有する接続領域を有する表示装置に関する。

【0030】

本発明において、前記第3の導電膜は、透光性導電膜である。

【0031】

また本発明は、基板上に第1の導電膜を成膜し、前記第1の導電膜上に、第1のレジス

トマスクを形成し、前記第1のレジストマスクを用いて、前記第1の導電膜をエッチング

して、ゲート配線及びソース配線を形成し、前記ゲート配線及びソース配線上に、ゲート

絶縁膜となる第1の絶縁膜、i型半導体層、第2の絶縁膜を成膜し、前記第2の絶縁膜上

、第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の絶縁

膜をエッチングして、チャネル保護膜を形成し、前記i型半導体層及びチャネル保護膜上

に、一導電性を付与する不純物元素を含む導電型半導体層、第2の導電膜を成膜し、前記

第2の導電膜上に、第3のレジストマスクを形成し、前記第2の導電膜、前記導電型半導

体層、前記i型半導体層をエッチングして、前記チャネル保護膜を露出させ、前記第3の

レジストマスクを用いた前記第2の導電膜のエッチングにより、ソース電極及びドレイン

電極、並びに、容量配線の配線が形成され、前記第3のレジストマスクを用いた前記導電

型半導体層のエッチングにより、ソース領域及びドレイン領域、並びに、前記容量配線の

導電型半導体層が形成され、前記第3のレジストマスクを用いた前記i型半導体層のエッ

チングにより、チャネル形成領域を含むi型半導体層、並びに、容量配線のi型半導体層

が形成され、前記第3のレジストマスクを用いた、前記第2の導電膜、前記導電型半導体

層、前記i型半導体層のエッチングにより、前記ソース配線及び前記ゲート絶縁膜上に、

第1のコンタクトホールを形成し、前記ソース電極及びドレイン電極、前記チャネル保護

膜、前記容量配線の配線を覆って、保護膜を形成し、前記保護膜上に第4のレジストマス

クを形成し、前記第4のレジストマスクを用いて、前記保護膜及び前記ゲート絶縁膜をエ

ッチングし、前記第4のレジストマスクを用いた前記保護膜のエッチングにより、前記第

1のコンタクトホールより径の大きい第2のコンタクトホールを形成し、かつ、前記ゲー

ト絶縁膜のエッチングにより、前記第1のコンタクトホール中のゲート絶縁膜が除去され

、前記ソース配線が露出し、前記ゲート絶縁膜が除去された第1のコンタクトホール及び

第2のコンタクトホールにより、前記保護膜、前記ソース電極、前記ソース領域、前記i

型半導体層、前記ゲート絶縁膜中に、階段状コンタクトホールが形成され、前記第4のレ

ジストマスクを用いた前記保護膜のエッチングにより、前記保護膜中に、前記ドレイン電

極に達する第3のコンタクトホールが形成され、前記保護膜、前記階段状コンタクトホー

ル、前記第3のコンタクトホールを覆って、第3の導電膜を成膜し、前記第3の導電膜上

に、第5のレジストマスクを形成し、前記第5のレジストマスクを用いて、前記第3の導

電膜をエッチングし、前記第3のコンタクトホールを介して前記ドレイン電極に電気的に

接続され、前記容量配線上に延びる画素電極を形成し、前記第5のレジストマスクを用い

た前記第3の導電膜のエッチングにより、前記階段状コンタクトホール中に、前記ソース

配線及び前記ソース電極を電気的に接続する電極を形成することを特徴とする表示装置の

作製方法に関するものである。

【0032】

本発明において、前記第3の導電膜は、透光性導電膜である。

【0033】

なお、半導体装置とは、半導体特性を利用することで機能する薄膜トランジスタ等の素

子、及びそのような素子を有する装置全般を指し、例えば、薄膜トランジスタを用いた液

晶表示装置や、薄膜トランジスタを用いた電子機器をその範疇に含む。

【発明の効果】

【0034】

本発明により、フォトマスクの数を増やすことなく、保持容量の容量が大きく、また開

口率の高い画素部を得ることが可能となる。このため、作製コスト及び作製時間が少なく

、信頼性の高い表示装置及びそのような表示装置を有する電子機器を得ることが可能とな

る。

【図面の簡単な説明】

【0035】

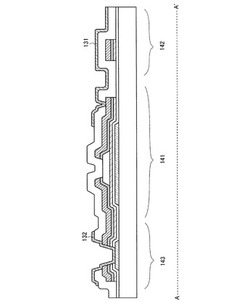

【図1】本発明の画素部の作製工程を説明する断面図。

【図2】本発明の画素部の作製工程を説明する断面図。

【図3】本発明の画素部の作製工程を説明する断面図。

【図4】本発明の画素部の作製工程を説明する断面図。

【図5】本発明の画素部の上面図。

【図6】従来の画素部の上面図。

【図7】従来の画素部の作製工程を説明する断面図。

【図8】従来の画素部の作製工程を説明する断面図。

【図9】従来の画素部の作製工程を説明する断面図。

【図10】本発明の液晶表示装置の作製工程を説明する断面図。

【図11】本発明の液晶表示装置の作製工程を説明する上面図。

【図12】本発明の液晶表示装置の作製工程を説明する上面図。

【図13】本発明が適用される電子機器の例を示す図。

【図14】本発明が適用される電子機器の例を示す図。

【図15】本発明が適用される電子機器の例を示す図。

【図16】本発明が適用される電子機器の例を示す図。

【図17】本発明が適用される電子機器の例を示す図。

【図18】本発明が適用される電子機器の例を示す図。

【図19】本発明が適用される電子機器の例を示す図。

【図20】本発明の画素部の作製工程を説明する断面図。

【図21】本発明の画素部の作製工程を説明する上面図。

【図22】本発明の画素部の作製工程を説明する上面図。

【図23】本発明の画素部の作製工程を説明する上面図。

【発明を実施するための形態】

【0036】

以下、本発明の実施の形態について図面を参照して説明する。ただし本発明は多くの異

なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなく

その形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、

本実施の形態の記載内容に限定して解釈されるものではない。

【0037】

なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部

分には同一の符号を付し、その繰り返しの説明は省略する。

【0038】

[実施の形態1]

本実施の形態では、本発明のチャネルストッパ型の逆スタガ型TFT及びそれを有する

画素部の作製方法について、図1(A)〜図1(D)、図2(A)〜図2(C)、図3(

A)〜図3(C)、図4、図5、図20、図21、図22、図23を用いてを説明する。

【0039】

本実施の形態により作製される画素部の上面図が図5であり、図5に示すA−A’の断

面図が図4である。図4及び図5において、TFT領域141、容量領域142、中継領

域143が基板101上に形成される。図4に至るまでの作製工程を図1(A)〜図1(

D)、図2(A)〜図2(C)、図3(A)〜図3(C)、図20、図21、図22、図

23を用いて以下に説明する。

【0040】

まず基板101上に、第1の導電膜161を形成し、さらにゲート配線102及びソー

ス配線103を形成するためのレジストマスク162を形成する(図1(A)参照)。

【0041】

上述のように、レジストマスク162を形成するためには、フォトマスクが1枚必要と

なる。レジストマスク162を形成するためのフォトマスクを第1のフォトマスクとする

。

【0042】

基板101は透光性を有する絶縁性基板を用い、例えば基板101として、コーニング

社の♯7059や♯1737、EAGLE2000などに代表されるバリウムホウケイ酸

ガラス、アルミノホウケイ酸ガラス、アルミノシリケートガラスなどの透光性のガラス基

板を用いることができる。その他に透光性を有する石英基板などを使用しても良い。

【0043】

第1の導電膜161は、アルミニウム(Al)、などの低抵抗導電性材料で形成するこ

とが望ましいが、アルミニウム単体では耐熱性が劣り、また腐食しやすい等の問題がある

ことから耐熱性導電性材料と組み合わせて積層膜を形成することが望ましい。

【0044】

耐熱性導電性材料としては、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)

、タングステン(W)、クロム(Cr)から選ばれた元素、または前記元素を成分とする

合金膜、または前記元素を成分とする窒化物で形成する。或いは、このような耐熱性導電

性材料をのみを組み合わせて用いても良い。

【0045】

またアルミニウムは純アルミニウムの他に、0.01〜5atomic%のスカンジウ

ム(Sc)、チタン(Ti)、シリコン(Si)、銅(Cu)、クロム(Cr)、ネオジ

ム(Nd)、モリブデン(Mo)等を含有するアルミニウムを使用してもよい。アルミニ

ウムよりも質量の重い原子を添加することで、熱処理時のアルミニウム原子の移動を制限

しヒロックを発生するのを防ぐ効果がある。

【0046】

上記のアルミニウムと耐熱性導電性材料との組合せの例として、クロム(Cr)及びア

ルミニウム(Al)の積層膜、クロム(Cr)及びネオジムを含有するアルミニウム(A

l−Nd)との積層膜、チタン(Ti)、アルミニウム(Al)及びチタン(Ti)の積

層膜、チタン(Ti)、ネオジムを含有するアルミニウム(Al−Nd)及びチタン(T

i)の積層膜、モリブデン(Mo)、アルミニウム(Al)及びモリブデン(Mo)の積

層膜、モリブデン(Mo)、ネオジムを含有するアルミニウム(Al−Nd)及びモリブ

デン(Mo)の積層膜、モリブデン(Mo)及びアルミニウム(Al)の積層膜、モリブ

デン(Mo)及びネオジムを含有するアルミニウム(Al−Nd)の積層膜などを用いる

ことができる。

【0047】

次いでレジストマスク162をマスクとして、第1の導電膜161をエッチングし、ゲ

ート配線102及びソース配線103を形成し、レジストマスク162を除去する(図1

(B)参照)。

【0048】

図1(B)は、上面図である図21のA−A’の断面を示している。

【0049】

次いで、基板101、ゲート配線102、ソース配線103上に、第1の絶縁膜である

ゲート絶縁膜104、i型半導体層105、第2の絶縁膜106を、大気に触れないよう

に真空状態を保ったまま、連続してCVD法にて成膜する。

【0050】

ここで、i型半導体層とは、真性半導体層ともいい、半導体層に含まれる一導電性を付

与する不純物元素、すなわちp型もしくはn型を付与する不純物元素が1×1020cm

−3以下の濃度であり、酸素及び窒素が9×1019cm−3以下の濃度であり、暗伝導

度に対して光伝導度が100倍以上である半導体を指す。この真性半導体には、周期表第

13族若しくは第15族の不純物元素が含まれるものを含む。すなわち、微結晶半導体層

は、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いn型の電気伝導

性を示すので、i型微結晶半導体層においては、p型を付与する不純物元素を成膜と同時

に、或いは成膜後に、意図的若しくは非意図的に添加することがあるためである。

【0051】

本実施の形態では、i型半導体層105として、ノンドープアモルファスシリコン(ノ

ンドープ非晶質珪素)膜を用いるが、半導体層としてシリコン(珪素)膜に限定されるも

のではなく、ゲルマニウム膜、シリコンゲルマニウム膜等を用いてもよい。

【0052】

またゲート絶縁膜104及び第2の絶縁膜106は、酸化珪素膜、窒化珪素膜、酸素を

含む窒化珪素膜、窒素を含む酸化膜のいずれか1つあるいは2つ以上の積層膜を成膜すれ

ばよい。本実施の形態では、ゲート絶縁膜104及び第2の絶縁膜106として窒化珪素

膜を成膜する。

【0053】

次いで第2の絶縁膜106上にレジストマスク109を形成し(図1(C)参照)、レ

ジストマスク109をマスクとしてエッチングし、チャネル保護膜108を形成する(図

1(D)参照)。またこのエッチング工程において、ハーフトーンマスクやリフローを用

いて、i型半導体層105をエッチングして島状半導体層を形成してもよい。

【0054】

図1(D)は、上面図である図22のA−A’の断面を示している。

【0055】

レジストマスク109を形成する際には、第2のフォトマスクが用いられる。

【0056】

また、エッチング方法によっては、チャネル保護膜108やレジストマスク109をマ

スクとして、i型半導体層105をエッチングし、第2の絶縁膜106から形成されるチ

ャネル保護膜108よりも緩やかなテーパー形状を持つ、島状半導体層形成することもで

きる。

【0057】

ただしi型半導体層105から島状半導体層を形成する場合には、島状半導体層上に成

膜される、一導電性を付与する不純物元素を有する半導体層(以下「導電型半導体層」と

いう)と接続が可能な上面を有する必要がある。

【0058】

i型半導体層105、チャネル保護膜108を覆って、導電型半導体層111、第2の

導電膜112を成膜する。導電型半導体層111に含まれる、一導電性を付与する不純物

元素は、n型を付与する不純物元素であればリン(P)またはヒ素(As)を用いればよ

く、p型であればホウ素(B)を用いればよい。本実施の形態では、n型のチャネルスト

ッパ型逆スタガ型TFTを形成するため、リンを含む非晶質珪素膜を導電型半導体層11

1として成膜する。また第2の導電膜112は、第1の導電膜161と同様の材料を用い

て成膜すればよい。

【0059】

次いで、第2の導電膜112上にレジストマスク125を形成し、レジストマスク12

5をマスクとして、i型半導体層105、導電型半導体層111、第2の導電膜112を

エッチングする(図2(A)参照)。i型半導体層105及び導電型半導体層111のエ

ッチングはドライエッチングにより行うが、第2の導電膜112はウエットエッチングで

もドライエッチングでもよい。エッチング終了後、レジストマスク125を除去する(図

2(B)参照)。

【0060】

レジストマスク125が形成されるためには、第3のフォトマスクが必要である。

【0061】

TFT領域141において、i型半導体層105中のチャネル形成領域となる領域にお

いては、チャネル保護膜108がエッチングストッパとして働き、導電型半導体層111

及び第2の導電膜112のみがエッチングされ、i型半導体層105はエッチングされな

い。エッチングされた導電型半導体層111及び第2の導電膜112はそれぞれ、ソース

領域118とドレイン領域117、並びに、ソース電極122とドレイン電極121に分

断される。

【0062】

なお本実施の形態では、ソース領域118とドレイン領域117、ソース電極122と

ドレイン電極121、さらにソース配線103と、ソースとドレインを説明をわかりやす

くするために区別しているが、電流の向きによってはソースとドレインが反転することも

ある。

【0063】

中継領域143ではチャネル保護膜がないため、i型半導体層105及び導電型半導体

層111がエッチングされ、i型半導体層105及び導電型半導体層111中に、第1の

コンタクトホール171が形成される。

【0064】

また、容量領域142には、本エッチング工程により、第2の導電膜からなる配線12

3、導電型半導体層116、i型半導体層114の積層体からなる容量配線が形成される

。

【0065】

図2(B)は、上面図である図23のA−A’の断面を示している。

【0066】

次いで第3の絶縁膜による保護膜127を全面に成膜する(図2(C)参照)。保護膜

127は、ゲート絶縁膜104や第2の絶縁膜106と同様の材料で形成すればよく、本

実施の形態では窒化珪素膜を用いる。

【0067】

保護膜127を形成後、レジストマスク128を形成し、レジストマスク128をマス

クとして保護膜127をエッチングする。本実施の形態では、保護膜127のエッチング

はドライエッチングにより行う(図3(A)参照)。

【0068】

レジストマスク128を形成する際には、第4のフォトマスクが用いられる。

【0069】

TFT領域141においては、後の工程で形成する画素電極131と、TFTのドレイ

ン電極121とを接続するための第3のコンタクトホール173を形成する。第3のコン

タクトホール173形成のための保護膜127のエッチングの際には、第2の導電膜によ

り形成されたドレイン電極121がエッチングストッパとして働く。

【0070】

一方、中継領域143には、保護膜127とゲート絶縁膜104がエッチングされ、ソ

ース配線103が露出する。また、このエッチングにより、i型半導体層105及び導電

型半導体層111がエッチングされて形成された第1のコンタクトホール171よりも広

く、第1のコンタクトホール171を完全に覆う第2のコンタクトホール172を形成す

る。

【0071】

第1のコンタクトホール171と第2のコンタクトホール172が重ならない領域では

、第2の導電膜により形成されたソース電極122が存在するため、ドライエッチングは

ソース電極122、特にソース電極122の上面で止まる。すなわちソース電極122が

エッチングストッパとして機能する。

【0072】

また、第1のコンタクトホール171と第2のコンタクトホール172が重なる領域は

、保護膜127の下のゲート絶縁膜104もエッチングされ、第1の導電膜で形成された

ソース配線103が露出する。

【0073】

このエッチング工程によって、中継領域143に階段状のコンタクトホールが形成され

る。上述のように第1のコンタクトホール171と第2のコンタクトホール172が重な

らない領域ではソース電極122の上面と側面が露出する。ソース電極122が露出した

領域が、後の工程で形成される透光性導電膜からなる接続電極132との接続領域となる

ため、接触抵抗を考慮した幅となるように設計する必要がある。即ち、露出面積が大きけ

れば接触抵抗は下がる。一方、露出面積が小さければ、接触抵抗も増加する。このため、

適宜設計する必要がある。

【0074】

容量領域142においては、保護膜127が容量を形成する誘電体膜となるため、エッ

チングを行わずにそのまま残存させる。

【0075】

次いでレジストマスク128を除去し、透光性導電膜129を成膜する(図3(B)参

照)。透光性導電膜129として、インジウム錫酸化物(Indium Tin Oxi

de:略称ITO)、酸化珪素を含むインジウム錫酸化物、酸化インジウム酸化亜鉛(I

ndium Zinc Oxide:略称IZO)、酸化亜鉛等の等の金属酸化物や半導

体酸化物が用いられる。本実施の形態では、インジウム錫酸化物を透光性導電膜129と

して用いる。

【0076】

透光性導電膜129上にレジストマスク134を形成し、レジストマスク134をマス

クとして、透光性導電膜129をエッチングし、画素電極131及び接続電極132を形

成する(図3(C)参照)。

【0077】

レジストマスク134を形成するには、第5のフォトマスクが必要である。

【0078】

TFT領域141では、保護膜127に形成されたコンタクトホールを介して、ドレイ

ン電極121と画素電極131が電気的に接続される。

【0079】

画素電極131は容量領域142まで延び、画素電極131が保護膜127を挟んで配

線123と重なる領域に保持容量が形成される。

【0080】

一方中継領域143においては、前述した階段状のコンタクトホール上に、第2のコン

タクトホール172を完全に覆う広さを持ち、透光性導電膜129により形成された接続

電極132が形成されるので、接続電極132、ソース配線103、ソース電極122は

電気的に接続される。接続電極132とソース電極122は、露出していた表面および側

面とで接続するため、確実な接触を行うことができる。

【0081】

次いでレジストマスク134を除去し、本実施の形態の画素部が完成する(図4参照)

。

【0082】

5枚のフォトマスクを使用して、チャネルストッパ型の逆スタガ型TFTを含むTFT

領域141、容量領域142、中継領域143完成させることができる。そして、これら

を個々の画素に対応してマトリクス状に配置して画像表示部を構成する。これにより能動

素子であるTFTを用いたアクティブマトリクス型の表示装置を作製するための一方の基

板とすることができる。本明細書では便宜上、このような基板をTFT基板と呼ぶ。

【0083】

また図20に示すように、i型半導体層113を、微結晶半導体層(「セミアモルファ

ス半導体層」ともいう)113aと非晶質半導体層113bの積層膜としてもよい。

【0084】

なおセミアモルファス半導体(本明細書では「Semi−amorphous Smi

conductor(SAS)」ともいう)層とは、非晶質半導体と結晶構造を有する半

導体(単結晶、多結晶を含む)層の中間的な構造の半導体を含む層である。このセミアモ

ルファス半導体層は、自由エネルギー的に安定な第3の状態を有する半導体層であって、

短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5〜20nmと

して非単結晶半導体膜中に分散させて存在せしめることが可能である。なお微結晶半導体

層(マイクロクリスタル半導体膜)もセミアモルファス半導体層に含まれる。

【0085】

セミアモルファス半導体層の1つの例として、セミアモルファス珪素層が挙げられる。

セミアモルファス珪素層は、そのラマンスペクトルが520cm−1よりも低波数側にシ

フトしており、またX線回折ではSi結晶格子に由来するとされる(111)、(220

)の回折ピークが観測される。また、未結合手(ダングリングボンド)を終端化させるた

めに水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。本明細書で

は便宜上、このような珪素層をセミアモルファス珪素層と呼ぶ。さらに、ヘリウム、アル

ゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させること

で安定性が増し良好なセミアモルファス半導体層が得られる。

【0086】

またセミアモルファス珪素層は珪素(シリコン)を含む気体をグロー放電分解すること

により得ることができる。代表的な珪素(シリコン)を含む気体としては、SiH4であ

り、その他にもSi2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4など

を用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンか

ら選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素(シリコン)を含む

気体を希釈して用いることで、セミアモルファス珪素層の形成を容易なものとすることが

できる。希釈率は2倍〜1000倍の範囲で珪素(シリコン)を含む気体を希釈すること

が好ましい。またさらに、珪素(シリコン)を含む気体中に、CH4、C2H6などの炭

化物気体、GeH4、GeF4などのゲルマニウム化気体、F2などを混入させて、エネ

ルギーバンド幅を1.5〜2.4eV、若しくは0.9〜1.1eVに調節しても良い。

【0087】

チャネル形成領域が微結晶半導体層113aと非晶質半導体層113bの積層で形成さ

れていると、オン状態の際に、キャリアが微結晶半導体層113aを流れるので、オン電

流が高くなり、TFTの移動度が高くなるという利点がある。

【0088】

一方オフ状態の際には、リーク電流が微結晶半導体層を流れてしまうと、リーク電流が

高くなってしまう恐れがある。しかしながら、チャネル形成領域が微結晶半導体層113

aと非晶質半導体層113bの積層では、リーク電流は非晶質半導体層113bを通るの

で、リーク電流を抑制することができる。

【0089】

本実施の形態で形成された画素部と従来の画素部の比較を、それぞれ図4及び図5、並

びに、図7及び図6を用いて以下に説明する。

【0090】

保持容量は、面積に比例し、誘電体膜の膜厚に反比例する。そこで例えば、ゲート絶縁

膜104及びゲート絶縁膜1104、並びに、保護膜127及び保護膜1127が、全て

膜厚300nmの窒化珪素膜で形成されているとする。本発明の保持容量の誘電体膜の膜

厚は、保護膜127の膜厚300nmであるのに対して、従来の保持容量の誘電体膜の膜

厚は、ゲート絶縁膜1104及び保護膜1127の膜厚を合計した厚さである600nm

となる。

【0091】

従って、本発明の保持容量は、従来の保持容量の2倍の容量を持つことができるという

ことになる。

【0092】

さらに、本発明の保持容量と従来の保持容量の容量が同じ場合には、本発明の保持容量

では、従来の保持容量よりも面積が半分ですむということとなる。すると、遮光材料で形

成される配線123の面積は、容量配線1151の半分の面積でよいことになり、従来の

画素部よりも開口率を高くすることができる。

【0093】

以上から、本発明のチャネルストッパ型の逆スタガ型TFT及びそれを有する画素部は

、フォトマスクの数を増やすことなく、保持容量の容量が大きく、かつ、開口率の高い画

素部を作製することができる。

【0094】

また本発明では、i型半導体層105の膜厚を薄くすることができるので、CVD法に

よる成膜時間の短縮化や、光照射時のリーク電流の発生の低減が可能となる。

【0095】

本発明の逆スタガ型TFTはチャネルストッパ型であるので、チャネル保護膜108に

より、i型半導体層113中のチャネル形成領域は、大気に露出することがない。

【0096】

また中継領域143において、階段状のコンタクトホールを介して、ソース配線103

、ソース電極122、接続電極132が電気的に接続されている。一方、一般的に2つの

異なる層からなる配線を他の配線で接続する場合、橋渡しのためにコンタクトホールは2

つ必要となる。本発明の階段状のコンタクトホールは、橋渡しのために形成される2つの

コンタクトホールの1つと比べ、若干サイズが大きくなる可能性はあるが、コンタクトホ

ールを2つを併せた面積に比べれば十分小さい。このため開口率向上に有利である。さら

にコンタクトホール数が減ることは、不良発生率の低下を意味する。

【0097】

[実施の形態2]

本実施の形態では、実施の形態1で作製したTFT基板を用いて、液晶表示装置を完成

させるまでの作製工程を、図10、図11(A)〜図11(D)、図12、を用いて以下

に説明する。

【0098】

TFT基板上の保護膜127及び画素電極131を覆うように、配向膜208を形成す

る。なお、配向膜208は、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いれ

ばよい。その後、配向膜208の表面にラビング処理を行う。

【0099】

そして、対向基板211には、着色層212、遮光層(ブラックマトリクス)213、

及びオーバーコート層214からなるカラーフィルタを設け、さらに透光性導電膜を用い

て形成された対向電極215と、その上に配向膜216を形成する(図10参照)。対向

電極215が透光性導電膜を用いて形成されることにより、本実施の形態の液晶表示装置

は透過型液晶表示装置となる。なお対向電極215を反射電極で形成すると、本実施の形

態の液晶表示装置は反射型液晶表示装置となる。

【0100】

そして、シール材221をディスペンサにより画素部231と重なる領域を囲むように

描画する。ここでは液晶218を滴下するため、シール材221を画素部231を囲むよ

うに描画する例を示すが、シール材で画素部231を囲みかつ開口部を有するように設け

、TFT基板を貼りあわせた後に毛細管現象を用いて液晶を注入するディップ式(汲み上

げ式)を用いてもよい(図11(A)参照)。

【0101】

次いで、気泡が入らないように減圧下で液晶218の滴下を行い(図11(B)参照)

、基板101及び対向基板211を貼り合わせる(図11(C)参照)。シール材221

に囲まれた領域内に液晶218を1回若しくは複数回滴下する。

【0102】

液晶218の配向モードとしては、液晶分子の配列が光の入射から射出に向かって90

°ツイスト配向したTNモードを用いる場合が多い。TNモードの液晶表示装置を作製す

る場合には、基板のラビング方向が直交するように貼り合わせる。

【0103】

なお、一対の基板間隔は、球状のスペーサを散布することや、樹脂からなる柱状のスペ

ーサを形成することや、シール材221にフィラーを含ませることによって維持すればよ

い。上記柱状のスペーサは、アクリル、ポリイミド、ポリイミドアミド、エポキシの少な

くとも1つを主成分とする有機樹脂材料、もしくは酸化珪素、窒化珪素、窒素を含む酸化

珪素のいずれか一種の材料、或いはこれらの積層膜からなる無機材料であることを特徴と

している。

【0104】

次いで、基板の分断を行う。多面取りの場合、それぞれのパネルを分断する。また、1

面取りの場合、予めカットされている対向基板を貼り合わせることによって、分断工程を

省略することもできる(図11(D)参照)。

【0105】

そして、異方性導電体層を介し、公知の技術を用いてFPC(Flexible Pr

inted Circuit)222を貼りつける(図12参照)。以上の工程で液晶表

示装置が完成する。また、必要があれば光学フィルムを貼り付ける。透過型液晶表示装置

とする場合、偏光板は、TFT基板と対向基板の両方に貼り付ける。以上により本実施の

形態の液晶表示装置が作製される。

【0106】

[実施の形態3]

本発明が適用される電子機器として、テレビ、ビデオカメラ、デジタルカメラ、ゴーグ

ル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオコンポ等)

、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型

ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigita

l Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示し

うるディスプレイを備えた装置)などが挙げられる。

【0107】

それらの電子機器の具体例を、図13、図14、図15(A)〜図15(B)、図16

(A)〜図16(B)、図17、図18(A)〜図18(E)、図19(A)〜図19(

B)に示す。

【0108】

図13は液晶表示パネル2001と、回路基板2011を組み合わせた液晶モジュール

を示している。回路基板2011には、コントロール回路2012や信号分割回路201

3などが形成されており、接続配線2014によって本発明を用いて形成された液晶表示

パネル2001と電気的に接続されている。

【0109】

この液晶表示パネル2001には、複数の画素が設けられた画素部2002と、走査線

駆動回路2003、選択された画素にビデオ信号を供給する信号線駆動回路2004を備

えている。画素部2002は、実施の形態2に基づいて作製すればよく、走査線駆動回路

2003及び信号線駆動回路2004は、チップで形成し、FPC等を用いて、画素部2

002、並びに、走査線駆動回路2003及び信号線駆動回路2004を接続すればよい

。

【0110】

図13に示す液晶モジュールにより液晶テレビ受像器を完成させることができる。図1

4は、液晶テレビ受像機の主要な構成を示すブロック図である。チューナ2101は映像

信号と音声信号を受信する。映像信号は、映像信号増幅回路2102と、そこから出力さ

れる信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路2103と、

その映像信号をドライバICの入力仕様に変換するためのコントロール回路2012によ

り処理される。コントロール回路2012は、走査線側と信号線側にそれぞれ信号が出力

する。デジタル駆動する場合には、信号線側に信号分割回路2013を設け、入力デジタ

ル信号をm個に分割して供給する構成としても良い。

【0111】

チューナ2101で受信した信号のうち、音声信号は音声信号増幅回路2105に送ら

れ、その出力は音声信号処理回路2106を経てスピーカ2107に供給される。制御回

路2108は受信局(受信周波数)や音量の制御情報を入力部2109から受け、チュー

ナ2101や音声信号処理回路2106に信号を送出する。

【0112】

図15(A)に示すように、液晶モジュールを筐体2201に組みこんで、テレビ受像

機を完成させることができる。液晶モジュールにより、表示画面2202が形成される。

また、スピーカ2203、操作スイッチ2204などが適宜備えられている。

【0113】

また図15(B)に、ワイヤレスでディスプレイのみを持ち運び可能なテレビ受像器を

示す。筐体2212にはバッテリ及び信号受信器が内蔵されており、そのバッテリーで表

示部2213やスピーカ部2217を駆動させる。バッテリは充電器2210で繰り返し

充電が可能となっている。また、充電器2210は映像信号を送受信することが可能で、

その映像信号をディスプレイの信号受信器に送信することでができる。筐体2212は操

作キー2216によって制御する。また、図15(B)に示す装置は、操作キー2216

を操作することによって、筐体2212から充電器2210に信号を送ることも可能であ

るため映像音声双方向通信装置とも言える。また、操作キー2216を操作することによ

って、筐体2212から充電器2210に信号を送り、さらに充電器2210が送信でき

る信号を他の電子機器に受信させることによって、他の電子機器の通信制御も可能であり

、汎用遠隔制御装置とも言える。本発明は表示部2213に適用することができる。

【0114】

本発明を図13、図14、図15(A)〜図15(B)に示すテレビ受像器使用するこ

とにより、品質のよい表示装置を備えたテレビ受像器を得ることが可能となる。

【0115】

勿論、本発明はテレビ受像機に限定されず、パーソナルコンピュータのモニタをはじめ

、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など特に大面積の

表示媒体として様々な用途に適用することができる。

【0116】

図16(A)は本発明を用いて形成された液晶表示パネル2301とプリント配線基板

2302を組み合わせたモジュールを示している。液晶表示パネル2301は、複数の画

素が設けられた画素部2303と、第1の走査線駆動回路2304、第2の走査線駆動回

路2305と、選択された画素にビデオ信号を供給する信号線駆動回路2306を備えて

いる。

【0117】

プリント配線基板2302には、コントローラ2307、中央処理装置(CPU)23

08、メモリ2309、電源回路2310、音声処理回路2311及び送受信回路231

2などが備えられている。プリント配線基板2302と液晶表示パネル2301は、フレ

キシブル・プリント・サーキット(FPC)2313により接続されている。プリント配

線基板2302には、容量素子、バッファ回路などを設け、電源電圧や信号にノイズがの

ったり、信号の立ち上がりが鈍ったりすることを防ぐ構成としても良い。また、コントロ

ーラ2307、音声処理回路2311、メモリ2309、CPU2308、電源回路23

10などは、COG(Chip On Glass)方式を用いて液晶表示パネル230

1に実装することもできる。COG方式により、プリント配線基板2302の規模を縮小

することができる。

【0118】

プリント配線基板2302に備えられたインターフェース2314を介して、各種制御

信号の入出力が行われる。また、アンテナとの間の信号の送受信を行なうためのアンテナ

用ポート2315が、プリント配線基板2302に設けられている。

【0119】

図16(B)は、図16(A)に示したモジュールのブロック図を示す。このモジュー

ルは、メモリ2309としてVRAM2316、DRAM2317、フラッシュメモリ2

318などが含まれている。VRAM2316にはパネルに表示する画像のデータが、D

RAM2317には画像データまたは音声データが、フラッシュメモリには各種プログラ

ムが記憶されている。

【0120】

電源回路2310は、液晶表示パネル2301、コントローラ2307、CPU230

8、音声処理回路2311、メモリ2309、送受信回路2312を動作させる電力を供

給する。またパネルの仕様によっては、電源回路2310に電流源が備えられている場合

もある。

【0121】

CPU2308は、制御信号生成回路2320、デコーダ2321、レジスタ2322

、演算回路2323、RAM2324、CPU2308用のインターフェース2319な

どを有している。インターフェース2319を介してCPU2308に入力された各種信

号は、一旦レジスタ2322に保持された後、演算回路2323、デコーダ2321など

に入力される。演算回路2323では、入力された信号に基づき演算を行ない、各種命令

を送る場所を指定する。一方デコーダ2321に入力された信号はデコードされ、制御信

号生成回路2320に入力される。制御信号生成回路2320は入力された信号に基づき

、各種命令を含む信号を生成し、演算回路2323において指定された場所、具体的には

メモリ2309、送受信回路2312、音声処理回路2311、コントローラ2307な

どに送る。

【0122】

メモリ2309、送受信回路2312、音声処理回路2311、コントローラ2307

は、それぞれ受けた命令に従って動作する。以下その動作について簡単に説明する。

【0123】

入力手段2325から入力された信号は、インターフェース2314を介してプリント

配線基板2302に実装されたCPU2308に送られる。制御信号生成回路2320は

、ポインティングデバイスやキーボードなどの入力手段2325から送られてきた信号に

従い、VRAM2316に格納してある画像データを所定のフォーマットに変換し、コン

トローラ2307に送付する。

【0124】

コントローラ2307は、パネルの仕様に合わせてCPU2308から送られてきた画

像データを含む信号にデータ処理を施し、液晶表示パネル2301に供給する。またコン

トローラ2307は、電源回路2310から入力された電源電圧やCPU2308から入

力された各種信号をもとに、Hsync信号、Vsync信号、クロック信号CLK、交

流電圧(AC Cont)、切り替え信号L/Rを生成し、液晶表示パネル2301に供

給する。

【0125】

送受信回路2312では、アンテナ2328において電波として送受信される信号が処

理されており、具体的にはアイソレータ、バンドパスフィルタ、VCO(Voltage

Controlled Oscillator)、LPF(Low Pass Fil

ter)、カプラ、バランなどの高周波回路を含んでいる。送受信回路2312において

送受信される信号のうち音声情報を含む信号が、CPU2308からの命令に従って、音

声処理回路2311に送られる。

【0126】

CPU2308の命令に従って送られてきた音声情報を含む信号は、音声処理回路23

11において音声信号に復調され、スピーカ2327に送られる。またマイク2326か

ら送られてきた音声信号は、音声処理回路2311において変調され、CPU2308か

らの命令に従って、送受信回路2312に送られる。

【0127】

コントローラ2307、CPU2308、電源回路2310、音声処理回路2311、

メモリ2309を、本実施の形態のパッケージとして実装することができる。本実施の形

態は、アイソレータ、バンドパスフィルタ、VCO(Voltage Controll

ed Oscillator)、LPF(Low Pass Filter)、カプラ、

バランなどの高周波回路以外であれば、どのような回路にも応用することができる。

【0128】

図17は、図16(A)〜図16(B)に示すモジュールを含む携帯電話機の一態様を

示している。液晶表示パネル2301はハウジング2330に脱着自在に組み込まれる。

ハウジング2330は液晶表示パネル2301のサイズに合わせて、形状や寸法を適宜変

更することができる。液晶表示パネル2301を固定したハウジング2330はプリント

基板2331に嵌着されモジュールとして組み立てられる。

【0129】

液晶表示パネル2301はFPC2313を介してプリント基板2331に接続される

。プリント基板2331には、スピーカ2332、マイクロフォン2333、送受信回路

2334、CPU及びコントローラなどを含む信号処理回路2335が形成されている。

このようなモジュールと、入力手段2336、バッテリ2337、アンテナ2340を組

み合わせ、筐体2339に収納する。液晶表示パネル2301の画素部は筐体2339に

形成された開口窓から視認できように配置する。

【0130】

本実施の形態に係る携帯電話機は、その機能や用途に応じてさまざまな態様に変容し得

る。例えば、表示パネルを複数備えたり、筐体を適宜複数に分割して蝶番により開閉式と

した構成としても、上記した作用効果を奏することができる。

【0131】

本発明を図16(A)〜図16(B)、図17に示す携帯電話に使用することにより、

品質のよい表示装置を備えた携帯電話を得ることが可能となる。

【0132】

図18(A)は液晶ディスプレイであり、筐体2401、支持台2402、表示部24

03などによって構成されている。本発明は表示部2403に適用が可能である。

【0133】

本発明を使用することにより、品質のよい表示装置を備えた液晶ディスプレイを得るこ

とが可能となる。

【0134】

図18(B)はコンピュータであり、本体2501、筐体2502、表示部2503、

キーボード2504、外部接続ポート2505、ポインティングデバイス2506等を含

む。本発明は表示部2503に適用することができる。

【0135】

本発明を使用することにより、品質のよい表示装置を備えたコンピュータを得ることが

可能となる。

【0136】

図18(C)は携帯可能なコンピュータであり、本体2601、表示部2602、スイ

ッチ2603、操作キー2604、赤外線ポート2605等を含む。本発明は表示部26

02に適用することができる。

【0137】

本発明を使用することにより、品質のよい表示装置を備えたコンピュータを得ることが

可能となる。

【0138】

図18(D)は携帯型のゲーム機であり、筐体2701、表示部2702、スピーカ部

2703、操作キー2704、記録媒体挿入部2705等を含む。本発明は表示部270

2に適用することができる。

【0139】

本発明を使用することにより、品質のよい表示装置を備えたゲーム機を得ることが可能

となる。

【0140】

図18(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)

であり、本体2801、筐体2802、表示部A2803、表示部B2804、記録媒体

読込部2805、操作キー2806、スピーカ部2807等を含む。表示部A2803は

主として画像情報を表示し、表示部B2804は主として文字情報を表示する。本発明は

表示部A2803、表示部B2804及び制御用回路部等に適用することができる。なお

、記憶媒体とは、DVD等であり、記録媒体を備えた画像再生装置には家庭用ゲーム機器

なども含まれる。

【0141】

本発明を使用することにより、品質のよい表示装置を備えた画像再生装置を得ることが

可能となる。

【0142】

図19(A)及び図19(B)は、本発明の液晶表示装置をカメラ、例えばデジタルカ

メラに組み込んだ例を示す図である。図19(A)は、デジタルカメラの前面方向から見

た斜視図、図19(B)は、後面方向から見た斜視図である。図19(A)において、デ

ジタルカメラには、リリースボタン2901、メインスイッチ2902、ファインダ窓2

903、フラッシュ2904、レンズ2905、鏡胴2906、筺体2907が備えられ

ている。

【0143】

また、図19(B)において、ファインダ接眼窓2911、モニタ2912、操作ボタ

ン2913が備えられている。

【0144】

リリースボタン2901は、半分の位置まで押下されると、焦点調整機構および露出調

整機構が作動し、最下部まで押下されるとシャッターが開く。

【0145】

メインスイッチ2902は、押下又は回転によりデジタルカメラの電源のON/OFF

を切り替える。

【0146】

ファインダ窓2903は、デジタルカメラの前面のレンズ2905の上部に配置されて

おり、図19(B)に示すファインダ接眼窓2911から撮影する範囲やピントの位置を

確認するための装置である。

【0147】

フラッシュ2904は、デジタルカメラの前面上部に配置され、被写体輝度が低いとき

に、リリースボタン2901が押下されてシャッターが開くと同時に補助光を照射する。

【0148】

レンズ2905は、デジタルカメラの正面に配置されている。レンズは、フォーカシン

グレンズ、ズームレンズ等により構成され、図示しないシャッター及び絞りと共に撮影光

学系を構成する。また、レンズの後方には、CCD(Charge Coupled D

evice)等の撮像素子が設けられている。

【0149】

鏡胴2906は、フォーカシングレンズ、ズームレンズ等のピントを合わせるためにレ

ンズの位置を移動するものであり、撮影時には、鏡胴を繰り出すことにより、レンズ29

05を手前に移動させる。また、携帯時は、レンズ2905を沈銅させてコンパクトにす

る。なお、本実施の形態においては、鏡胴を繰り出すことにより被写体をズーム撮影する

ことができる構造としているが、この構造に限定されるものではなく、筺体2907内で

の撮影光学系の構成により鏡胴を繰り出さずともズーム撮影が可能なデジタルカメラでも

よい。

【0150】

ファインダ接眼窓2911は、デジタルカメラの後面上部に設けられており、撮影する

範囲やピントの位置を確認する際に接眼するために設けられた窓である。

【0151】

操作ボタン2913は、デジタルカメラの後面に設けられた各種機能ボタンであり、セ

ットアップボタン、メニューボタン、ディスプレイボタン、機能ボタン、選択ボタン等に

より構成されている。

【0152】

本発明の液晶表示装置は、図19(A)及び図19(B)に示すカメラのモニタ291

2に組み込むことができる。これにより品質のよい表示装置を備えたデジタルカメラを得

ることが可能となる。

【0153】

なお、本実施の形態に示した例はごく一例であり、これらの用途に限定するものではな

いことを付記する。

【符号の説明】

【0154】

101 基板

102 ゲート配線

103 ソース配線

104 ゲート絶縁膜

105 i型半導体層

106 絶縁膜

108 チャネル保護膜

109 レジストマスク

111 導電型半導体層

112 導電膜

113 i型半導体層

113a 微結晶半導体層

113b 非晶質半導体層

114 i型半導体層

116 導電型半導体層

117 ドレイン領域

118 ソース領域

121 ドレイン電極

122 ソース電極

123 配線

125 レジストマスク

127 保護膜

128 レジストマスク

129 透光性導電膜

131 画素電極

132 接続電極

134 レジストマスク

141 TFT領域

142 容量領域

143 中継領域

161 導電膜

162 レジストマスク

171 コンタクトホール

172 コンタクトホール

173 コンタクトホール

208 配向膜

211 対向基板

212 着色層

213 遮光層(ブラックマトリクス)

214 オーバーコート層

215 対向電極

216 配向膜

218 液晶

221 シール材

222 FPC

231 画素部

1101 基板

1102 ゲート配線

1104 ゲート絶縁膜

1105 半導体層

1106 絶縁膜

1108 チャネル保護膜

1109 レジストマスク

1111 半導体層

1112 導電膜

1113 i型半導体層

1117 ドレイン領域

1118 ソース領域

1121 ドレイン電極

1122 ソース配線

1125 レジストマスク

1127 保護膜

1128 レジストマスク

1129 導電膜

1131 画素電極

1134 レジストマスク

1141 TFT領域

1142 容量領域

1143 配線領域

1151 容量配線

1161 導電膜

1162 レジストマスク

1173 コンタクトホール

2001 液晶表示パネル

2002 画素部

2003 走査線駆動回路

2004 信号線駆動回路

2011 回路基板

2012 コントロール回路

2013 信号分割回路

2014 接続配線

2101 チューナ

2102 映像信号増幅回路

2103 映像信号処理回路

2105 音声信号増幅回路

2106 音声信号処理回路

2107 スピーカ

2108 制御回路

2109 入力部

2201 筐体

2202 表示画面

2203 スピーカ

2204 操作スイッチ

2210 充電器

2212 筐体

2213 表示部

2216 操作キー

2217 スピーカ部

2301 液晶表示パネル

2302 プリント配線基板

2303 画素部

2304 走査線駆動回路

2305 走査線駆動回路

2306 信号線駆動回路

2307 コントローラ

2308 CPU

2309 メモリ

2310 電源回路

2311 音声処理回路

2312 送受信回路

2313 FPC

2314 インターフェース

2315 アンテナ用ポート

2316 VRAM

2317 DRAM

2318 フラッシュメモリ

2319 インターフェース

2320 制御信号生成回路

2321 デコーダ

2322 レジスタ

2323 演算回路

2324 RAM

2325 入力手段

2326 マイク

2327 スピーカ

2328 アンテナ

2330 ハウジング

2331 プリント基板

2332 スピーカ

2333 マイクロフォン

2334 送受信回路

2335 信号処理回路

2336 入力手段

2337 バッテリ

2339 筐体

2340 アンテナ

2401 筐体

2402 支持台

2403 表示部

2501 本体

2502 筐体

2503 表示部

2504 キーボード

2505 外部接続ポート

2506 ポインティングデバイス

2601 本体

2602 表示部

2603 スイッチ

2604 操作キー

2605 赤外線ポート

2701 筐体

2702 表示部

2703 スピーカ部

2704 操作キー

2705 記録媒体挿入部

2801 本体

2802 筐体

2803 表示部A

2804 表示部B

2805 記録媒体読込部

2806 操作キー

2807 スピーカ部

2901 リリースボタン

2902 メインスイッチ

2903 ファインダ窓

2904 フラッシュ

2905 レンズ

2906 鏡胴

2907 筺体

2911 ファインダ接眼窓

2912 モニタ

2913 操作ボタン

【技術分野】

【0001】

本発明は、表示装置及びその作製方法に関する。

【背景技術】

【0002】

ノート型のパーソナルコンピュータやデスクトップ型のパーソナルコンピュータ用のモ

ニタ、携帯電話、音楽再生装置、テレビ、携帯端末、デジタルスチルカメラ、ビデオカメ

ラ、画像・動画閲覧専用のビューワ等の電子機器に、画像や文字情報を表示するためのア

クティブマトリクス型表示装置は幅広く用いられている。

【0003】

アクティブマトリクス型表示装置は、表示領域となる画素部において能動素子(例えば

薄膜トランジスタ(Thin Film Transistor:TFT))を個々の画

素に対応してマトリクス状に配置して構成している。TFTはスイッチング素子として画

素に印加される電圧を制御し所望の画像表示を行っている。

【0004】

スイッチング素子として用いられるTFTのうち、チャネルストッパ型(チャネル保護

型、エッチストッパ型ともいう)の逆スタガ型TFTを有する素子基板は、5枚のフォト

マスクを用いて画素電極までを作製していた(特許文献1参照)。

【0005】

従来のチャネルストッパ型の逆スタガ型TFT及びそれを含む画素部の例を図6、図7

、図8(A)〜図8(C)、図9(A)〜図9(B)に示す。図6は一画素及びその周辺

の上面図であり、図7は図6のB−B’における断面図である。図8(A)〜図8(C)

、図9(A)〜図9(B)は、図7に至る作製工程を示す断面図である。

【0006】

一画素には、TFT領域1141、容量領域1142、配線領域1143が基板110

1上に設けられている。TFT領域1141には、ゲート配線1102、ゲート絶縁膜1

104、チャネル形成領域を有するi型半導体層1113、絶縁膜からなるチャネル保護

膜1108、一導電性を付与する不純物元素を有する半導体層からなるソース領域111

8及びドレイン領域1117、ソース配線1122、ドレイン電極1121、保護膜11

27、画素電極1131が設けられている。

【0007】

容量領域1142には、容量配線1151、ゲート絶縁膜1104、保護膜1127、

画素電極1131が設けられている。また配線領域1143には、ソース配線1122が

設けられている。

【0008】

容量領域1142は、ゲート配線1102と同じ材料及び同じ工程で形成された容量配

線1151、並びに、画素電極1131を上下の電極とし、電極間に挟まれたゲート絶縁

膜1104と保護膜1127とを誘電体とした構成であった。

【0009】

従来のチャネルストッパ型の逆スタガ型TFT及び画素部を作製するには、まず基板1

101上に第1の導電膜1161を形成し、さらに第1の導電膜1161上にレジストマ

スク1162を形成する(図8(A)参照)。

【0010】

ここでレジストマスクは、レジスト材料を塗布し、フォトマスクを用いて露光し、さら

に現像という工程を経ることにより形成される。塗布されたレジスト材料を上方から露光

する場合には、レジストマスクを形成するには、フォトマスクが1枚必要になる。すなわ

ち、レジストマスク1162を形成するには、第1のフォトマスクが必要である。

【0011】

レジストマスク1162をマスクとして、第1の導電膜1161をエッチングし、ゲー

ト配線1102及び容量配線1151を形成する。次いでレジストマスク1162を除去

後、ゲート絶縁膜1104、半導体層1105、絶縁膜1106を成膜する。次いでチャ

ネル保護膜1108を形成する領域に、レジストマスク1109を形成する(図8(B)

参照)。すなわちレジストマスク1109を形成するために、第2のフォトマスクを用い

る必要がある。

【0012】

次いでレジストマスク1109をマスクとして、絶縁膜1106をエッチングして、チ

ャネル保護膜1108を形成する。レジストマスク1109を除去後、半導体層1105

及びチャネル保護膜1108上に、一導電性を付与する不純物元素を含む半導体層111

1、第2の導電膜1112を成膜する。第2の導電膜1112上に、レジストマスク11

25を形成する(図8(C)参照)。すなわち第3のフォトマスクが用いられる。

【0013】

レジストマスク1125をマスクとして、第2の導電膜1112及び半導体層1111

をエッチングする。このとき、チャネル保護膜1108及びゲート絶縁膜1104がエッ

チングストッパとして機能する。これにより第2の導電膜1112は分断されて、ソース

配線1122及びドレイン電極1121が形成される。また一導電性を付与する不純物元

素を含む半導体層1111も分断され、ソース領域1118及びドレイン領域1117に

分断される。さらに半導体層1105もエッチングされ、その端部は、ドレイン領域11

17及びドレイン電極1121の端部と一致する。次いでレジストマスク1125を除去

後、保護膜1127を全面に成膜し、さらにレジストマスク1128を形成する(図9(

A)参照)。すなわち第4のフォトマスクが用いられる。

【0014】

レジストマスク1128を用いて、保護膜1127をエッチングしてコンタクトホール

1173を形成する。レジストマスク1128を除去後、第3の導電膜1129を成膜し

、第3の導電膜1129上の、画素電極1131が形成される領域に、レジストマスク1

134を形成する(図9(B)参照)。すなわち第5のフォトマスクが用いられる。

【0015】

レジストマスク1134をマスクとして、第3の導電膜1129がエッチングされ、画

素電極1131が形成される。次いでレジストマスク1134を除去すると、図7に示す

画素部が完成する。

【先行技術文献】

【特許文献】

【0016】

【特許文献1】特開2002−148658号公報

【発明の概要】

【発明が解決しようとする課題】

【0017】

従来の画素部の作製には、フォトマスクが5枚必要であった。フォトマスクが1枚増え

ると、レジスト材料を塗布、フォトマスクを用いて露光、現像という工程の他に、露光前

のプリベーク、露光後のポストベーク、レジスト剥離、レジスト剥離後の洗浄、洗浄後の

乾燥等、様々な工程が増え、作製時間や作製コストが増大する。

【0018】

また剥離できなかったレジスト材料が、素子の中に入り込み、不良の原因となる恐れも

ある。このため素子や装置の信頼性が低くなってしまう可能性もある。

【0019】

また、図6及び図7に示す構成において、保持容量の誘電体膜は、ゲート絶縁膜110

4と保護膜1127という二層の絶縁膜で構成される。そのため、誘電体膜が絶縁膜一層

である場合と比べて、誘電体が絶縁膜二層であると保持容量は小さくなってしまう。

【0020】

容量は誘電体膜の膜厚に反比例し、面積に比例する。従って、目的とする保持容量の値

を確保するためには、容量領域1142の面積を大きく取る必要があった。

【0021】

しかしながら容量領域1142の面積を大きくしてしまうと、画素部の開口率が低下し

てしまう。

【0022】

そこで本発明は、フォトマスクの数を増やさず、かつ、画素部の開口率を低下させずに

、誘電体膜の厚さを薄くして容量を増加させることを目的とする。

【課題を解決するための手段】

【0023】

本発明は、チャネルストッパ型の逆スタガ型TFTにおいて、高開口率を得るため、保

持容量を、画素電極、並びに、ソース電極及びドレイン電極と同様の材料及び同様の工程

により形成される導電膜(以下、第2の導電膜という)を用いて形成する。画素電極と第

2の導電膜の間の誘電体膜は保護膜一層のみとする。これにより、高開口率な画素部と容

量の大きな保持容量を同時に得ることができる。

【0024】

ソース配線もゲート配線と同様の材料及び同様の工程により形成される導電膜(以下、

第1の導電膜という)で形成する。また、ソース配線とゲート配線の交差部については、

いずれか一方の配線を交差する部分で分断し、第2の導電膜により中継する。

【0025】

特に、第1の導電膜と第2の導電膜との中継において、画素電極の材料である透光性導

電膜を使用する。第1の導電膜と第2の導電膜とを接続させる場合、従来ではゲート絶縁

膜のコンタクトホール形成工程が必要となる。

【0026】

しかし本発明においては、後述する構造とすることで、ゲート絶縁膜のコンタクトホー

ル形成工程を行わなくてもよい。すなわち、第1の導電膜上のゲート絶縁膜、半導体層、

第2の導電膜にコンタクトホールを形成し(第1のコンタクトホール)、さらに第1のコ

ンタクトホールよりも広いコンタクトホールを保護膜に形成する(第2のコンタクトホー

ル)。第2のコンタクトホールに接する透光性導電膜を、第2のコンタクトホール内に部

分的に露出した第2の導電膜と、第1のコンタクトホール内に露出した第1の導電膜に接

続させる。

【0027】

第1のコンタクトホールを作製する際、TFTにはチャネル保護膜があるため、i型半

導体層のエッチングが阻害され、第1のコンタクトホールにおける半導体層だけを選択的

にエッチングすることができる。

【0028】

本発明は、第1の導電膜により形成されるゲート電極と、前記第1の導電膜上の第1の

絶縁層で形成されるゲート絶縁膜と、前記第1の絶縁層上に、前記ゲート電極と重なる第

1の半導体層と、前記第1の半導体層上に配置され、かつ、前記ゲート電極に重なる第2

の絶縁層で形成されるチャネル保護膜と、前記第1の半導体層と重なり、一端がチャネル

保護膜上に延び、ソース領域及びドレイン領域に分離された、一導電性を付与する不純物

元素を有する第2の半導体層と、前記第2の半導体層上の第2の導電膜により形成され、

前記ソース領域及びドレイン領域に対応して形成されたソース電極及びドレイン電極と、

を含む薄膜トランジスタと、前記第2の導電膜上に形成された第3の絶縁層と、前記第3

の絶縁層上の第3の導電膜により形成され、前記第3の絶縁層に形成されたコンタクトホ

ールを介して前記ソース電極またはドレイン電極の一方と電気的に接続する画素電極と、

前記第1の絶縁層上の、前記第1の半導体層、前記第2の半導体層及び前記第2の導電膜

の積層体で形成される容量配線と、前記容量配線上の前記第3の絶縁層と、前記画素電極

の重畳領域に形成される保持容量とを有する表示装置に関する。

【0029】

また本発明は、第1の導電膜により形成されるゲート電極と、前記第1の導電膜上の第

1の絶縁層で形成されるゲート絶縁膜と、前記第1の絶縁層上に、前記ゲート電極と重な

る第1の半導体層と、前記第1の半導体層上に配置され、かつ、前記ゲート電極に重なる

第2の絶縁層で形成されるチャネル保護膜と、前記第1の半導体層と重なり、一端がチャ

ネル保護膜上に延び、ソース領域及びドレイン領域に分離された、一導電性を付与する不

純物元素を有する第2の半導体層と、前記第2の半導体層上の第2の導電膜により形成さ

れ、前記ソース領域及びドレイン領域に対応して形成されたソース電極及びドレイン電極

と、を含む薄膜トランジスタと、前記第2の導電膜上に形成された第3の絶縁層と、前記

第3の絶縁層上の第3の導電膜により形成され、前記第3の絶縁層に形成されたコンタク

トホールを介して前記ソース電極またはドレイン電極の一方と電気的に接続する画素電極

と、前記第1の絶縁層上の、前記第1の半導体層、前記第2の半導体層及び前記第2の導

電膜の積層体で形成される容量配線と、前記容量配線上の前記第3の絶縁層と、前記画素

電極の重畳領域に形成される保持容量と、前記第1の導電膜により形成される配線と、前

記配線上の前記第3の導電膜により形成され、前記ソース電極またはドレイン電極の他方

の上面と側面に接する電極とを有する接続領域を有する表示装置に関する。

【0030】

本発明において、前記第3の導電膜は、透光性導電膜である。

【0031】

また本発明は、基板上に第1の導電膜を成膜し、前記第1の導電膜上に、第1のレジス

トマスクを形成し、前記第1のレジストマスクを用いて、前記第1の導電膜をエッチング

して、ゲート配線及びソース配線を形成し、前記ゲート配線及びソース配線上に、ゲート

絶縁膜となる第1の絶縁膜、i型半導体層、第2の絶縁膜を成膜し、前記第2の絶縁膜上

、第2のレジストマスクを形成し、前記第2のレジストマスクを用いて、前記第2の絶縁

膜をエッチングして、チャネル保護膜を形成し、前記i型半導体層及びチャネル保護膜上

に、一導電性を付与する不純物元素を含む導電型半導体層、第2の導電膜を成膜し、前記

第2の導電膜上に、第3のレジストマスクを形成し、前記第2の導電膜、前記導電型半導

体層、前記i型半導体層をエッチングして、前記チャネル保護膜を露出させ、前記第3の

レジストマスクを用いた前記第2の導電膜のエッチングにより、ソース電極及びドレイン

電極、並びに、容量配線の配線が形成され、前記第3のレジストマスクを用いた前記導電

型半導体層のエッチングにより、ソース領域及びドレイン領域、並びに、前記容量配線の

導電型半導体層が形成され、前記第3のレジストマスクを用いた前記i型半導体層のエッ

チングにより、チャネル形成領域を含むi型半導体層、並びに、容量配線のi型半導体層

が形成され、前記第3のレジストマスクを用いた、前記第2の導電膜、前記導電型半導体

層、前記i型半導体層のエッチングにより、前記ソース配線及び前記ゲート絶縁膜上に、

第1のコンタクトホールを形成し、前記ソース電極及びドレイン電極、前記チャネル保護

膜、前記容量配線の配線を覆って、保護膜を形成し、前記保護膜上に第4のレジストマス

クを形成し、前記第4のレジストマスクを用いて、前記保護膜及び前記ゲート絶縁膜をエ

ッチングし、前記第4のレジストマスクを用いた前記保護膜のエッチングにより、前記第

1のコンタクトホールより径の大きい第2のコンタクトホールを形成し、かつ、前記ゲー

ト絶縁膜のエッチングにより、前記第1のコンタクトホール中のゲート絶縁膜が除去され

、前記ソース配線が露出し、前記ゲート絶縁膜が除去された第1のコンタクトホール及び

第2のコンタクトホールにより、前記保護膜、前記ソース電極、前記ソース領域、前記i

型半導体層、前記ゲート絶縁膜中に、階段状コンタクトホールが形成され、前記第4のレ

ジストマスクを用いた前記保護膜のエッチングにより、前記保護膜中に、前記ドレイン電

極に達する第3のコンタクトホールが形成され、前記保護膜、前記階段状コンタクトホー

ル、前記第3のコンタクトホールを覆って、第3の導電膜を成膜し、前記第3の導電膜上

に、第5のレジストマスクを形成し、前記第5のレジストマスクを用いて、前記第3の導

電膜をエッチングし、前記第3のコンタクトホールを介して前記ドレイン電極に電気的に

接続され、前記容量配線上に延びる画素電極を形成し、前記第5のレジストマスクを用い

た前記第3の導電膜のエッチングにより、前記階段状コンタクトホール中に、前記ソース

配線及び前記ソース電極を電気的に接続する電極を形成することを特徴とする表示装置の

作製方法に関するものである。

【0032】

本発明において、前記第3の導電膜は、透光性導電膜である。

【0033】

なお、半導体装置とは、半導体特性を利用することで機能する薄膜トランジスタ等の素

子、及びそのような素子を有する装置全般を指し、例えば、薄膜トランジスタを用いた液

晶表示装置や、薄膜トランジスタを用いた電子機器をその範疇に含む。

【発明の効果】

【0034】

本発明により、フォトマスクの数を増やすことなく、保持容量の容量が大きく、また開

口率の高い画素部を得ることが可能となる。このため、作製コスト及び作製時間が少なく

、信頼性の高い表示装置及びそのような表示装置を有する電子機器を得ることが可能とな

る。

【図面の簡単な説明】

【0035】

【図1】本発明の画素部の作製工程を説明する断面図。

【図2】本発明の画素部の作製工程を説明する断面図。

【図3】本発明の画素部の作製工程を説明する断面図。

【図4】本発明の画素部の作製工程を説明する断面図。

【図5】本発明の画素部の上面図。

【図6】従来の画素部の上面図。

【図7】従来の画素部の作製工程を説明する断面図。

【図8】従来の画素部の作製工程を説明する断面図。

【図9】従来の画素部の作製工程を説明する断面図。

【図10】本発明の液晶表示装置の作製工程を説明する断面図。

【図11】本発明の液晶表示装置の作製工程を説明する上面図。

【図12】本発明の液晶表示装置の作製工程を説明する上面図。

【図13】本発明が適用される電子機器の例を示す図。

【図14】本発明が適用される電子機器の例を示す図。

【図15】本発明が適用される電子機器の例を示す図。

【図16】本発明が適用される電子機器の例を示す図。

【図17】本発明が適用される電子機器の例を示す図。

【図18】本発明が適用される電子機器の例を示す図。

【図19】本発明が適用される電子機器の例を示す図。

【図20】本発明の画素部の作製工程を説明する断面図。

【図21】本発明の画素部の作製工程を説明する上面図。

【図22】本発明の画素部の作製工程を説明する上面図。

【図23】本発明の画素部の作製工程を説明する上面図。

【発明を実施するための形態】

【0036】

以下、本発明の実施の形態について図面を参照して説明する。ただし本発明は多くの異

なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなく

その形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、

本実施の形態の記載内容に限定して解釈されるものではない。

【0037】

なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部

分には同一の符号を付し、その繰り返しの説明は省略する。

【0038】

[実施の形態1]

本実施の形態では、本発明のチャネルストッパ型の逆スタガ型TFT及びそれを有する

画素部の作製方法について、図1(A)〜図1(D)、図2(A)〜図2(C)、図3(

A)〜図3(C)、図4、図5、図20、図21、図22、図23を用いてを説明する。

【0039】

本実施の形態により作製される画素部の上面図が図5であり、図5に示すA−A’の断

面図が図4である。図4及び図5において、TFT領域141、容量領域142、中継領

域143が基板101上に形成される。図4に至るまでの作製工程を図1(A)〜図1(

D)、図2(A)〜図2(C)、図3(A)〜図3(C)、図20、図21、図22、図

23を用いて以下に説明する。

【0040】

まず基板101上に、第1の導電膜161を形成し、さらにゲート配線102及びソー

ス配線103を形成するためのレジストマスク162を形成する(図1(A)参照)。

【0041】

上述のように、レジストマスク162を形成するためには、フォトマスクが1枚必要と

なる。レジストマスク162を形成するためのフォトマスクを第1のフォトマスクとする

。

【0042】

基板101は透光性を有する絶縁性基板を用い、例えば基板101として、コーニング

社の♯7059や♯1737、EAGLE2000などに代表されるバリウムホウケイ酸

ガラス、アルミノホウケイ酸ガラス、アルミノシリケートガラスなどの透光性のガラス基

板を用いることができる。その他に透光性を有する石英基板などを使用しても良い。

【0043】

第1の導電膜161は、アルミニウム(Al)、などの低抵抗導電性材料で形成するこ

とが望ましいが、アルミニウム単体では耐熱性が劣り、また腐食しやすい等の問題がある

ことから耐熱性導電性材料と組み合わせて積層膜を形成することが望ましい。

【0044】

耐熱性導電性材料としては、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)

、タングステン(W)、クロム(Cr)から選ばれた元素、または前記元素を成分とする

合金膜、または前記元素を成分とする窒化物で形成する。或いは、このような耐熱性導電

性材料をのみを組み合わせて用いても良い。

【0045】

またアルミニウムは純アルミニウムの他に、0.01〜5atomic%のスカンジウ

ム(Sc)、チタン(Ti)、シリコン(Si)、銅(Cu)、クロム(Cr)、ネオジ

ム(Nd)、モリブデン(Mo)等を含有するアルミニウムを使用してもよい。アルミニ

ウムよりも質量の重い原子を添加することで、熱処理時のアルミニウム原子の移動を制限

しヒロックを発生するのを防ぐ効果がある。

【0046】

上記のアルミニウムと耐熱性導電性材料との組合せの例として、クロム(Cr)及びア

ルミニウム(Al)の積層膜、クロム(Cr)及びネオジムを含有するアルミニウム(A

l−Nd)との積層膜、チタン(Ti)、アルミニウム(Al)及びチタン(Ti)の積

層膜、チタン(Ti)、ネオジムを含有するアルミニウム(Al−Nd)及びチタン(T

i)の積層膜、モリブデン(Mo)、アルミニウム(Al)及びモリブデン(Mo)の積

層膜、モリブデン(Mo)、ネオジムを含有するアルミニウム(Al−Nd)及びモリブ

デン(Mo)の積層膜、モリブデン(Mo)及びアルミニウム(Al)の積層膜、モリブ

デン(Mo)及びネオジムを含有するアルミニウム(Al−Nd)の積層膜などを用いる

ことができる。

【0047】

次いでレジストマスク162をマスクとして、第1の導電膜161をエッチングし、ゲ

ート配線102及びソース配線103を形成し、レジストマスク162を除去する(図1

(B)参照)。

【0048】

図1(B)は、上面図である図21のA−A’の断面を示している。

【0049】

次いで、基板101、ゲート配線102、ソース配線103上に、第1の絶縁膜である

ゲート絶縁膜104、i型半導体層105、第2の絶縁膜106を、大気に触れないよう

に真空状態を保ったまま、連続してCVD法にて成膜する。

【0050】

ここで、i型半導体層とは、真性半導体層ともいい、半導体層に含まれる一導電性を付

与する不純物元素、すなわちp型もしくはn型を付与する不純物元素が1×1020cm

−3以下の濃度であり、酸素及び窒素が9×1019cm−3以下の濃度であり、暗伝導

度に対して光伝導度が100倍以上である半導体を指す。この真性半導体には、周期表第

13族若しくは第15族の不純物元素が含まれるものを含む。すなわち、微結晶半導体層

は、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いn型の電気伝導

性を示すので、i型微結晶半導体層においては、p型を付与する不純物元素を成膜と同時

に、或いは成膜後に、意図的若しくは非意図的に添加することがあるためである。

【0051】

本実施の形態では、i型半導体層105として、ノンドープアモルファスシリコン(ノ

ンドープ非晶質珪素)膜を用いるが、半導体層としてシリコン(珪素)膜に限定されるも

のではなく、ゲルマニウム膜、シリコンゲルマニウム膜等を用いてもよい。

【0052】

またゲート絶縁膜104及び第2の絶縁膜106は、酸化珪素膜、窒化珪素膜、酸素を

含む窒化珪素膜、窒素を含む酸化膜のいずれか1つあるいは2つ以上の積層膜を成膜すれ

ばよい。本実施の形態では、ゲート絶縁膜104及び第2の絶縁膜106として窒化珪素

膜を成膜する。

【0053】

次いで第2の絶縁膜106上にレジストマスク109を形成し(図1(C)参照)、レ

ジストマスク109をマスクとしてエッチングし、チャネル保護膜108を形成する(図

1(D)参照)。またこのエッチング工程において、ハーフトーンマスクやリフローを用

いて、i型半導体層105をエッチングして島状半導体層を形成してもよい。

【0054】

図1(D)は、上面図である図22のA−A’の断面を示している。

【0055】

レジストマスク109を形成する際には、第2のフォトマスクが用いられる。

【0056】

また、エッチング方法によっては、チャネル保護膜108やレジストマスク109をマ

スクとして、i型半導体層105をエッチングし、第2の絶縁膜106から形成されるチ

ャネル保護膜108よりも緩やかなテーパー形状を持つ、島状半導体層形成することもで

きる。

【0057】

ただしi型半導体層105から島状半導体層を形成する場合には、島状半導体層上に成

膜される、一導電性を付与する不純物元素を有する半導体層(以下「導電型半導体層」と

いう)と接続が可能な上面を有する必要がある。

【0058】

i型半導体層105、チャネル保護膜108を覆って、導電型半導体層111、第2の

導電膜112を成膜する。導電型半導体層111に含まれる、一導電性を付与する不純物

元素は、n型を付与する不純物元素であればリン(P)またはヒ素(As)を用いればよ

く、p型であればホウ素(B)を用いればよい。本実施の形態では、n型のチャネルスト

ッパ型逆スタガ型TFTを形成するため、リンを含む非晶質珪素膜を導電型半導体層11

1として成膜する。また第2の導電膜112は、第1の導電膜161と同様の材料を用い

て成膜すればよい。

【0059】

次いで、第2の導電膜112上にレジストマスク125を形成し、レジストマスク12

5をマスクとして、i型半導体層105、導電型半導体層111、第2の導電膜112を

エッチングする(図2(A)参照)。i型半導体層105及び導電型半導体層111のエ

ッチングはドライエッチングにより行うが、第2の導電膜112はウエットエッチングで

もドライエッチングでもよい。エッチング終了後、レジストマスク125を除去する(図

2(B)参照)。

【0060】

レジストマスク125が形成されるためには、第3のフォトマスクが必要である。

【0061】

TFT領域141において、i型半導体層105中のチャネル形成領域となる領域にお

いては、チャネル保護膜108がエッチングストッパとして働き、導電型半導体層111

及び第2の導電膜112のみがエッチングされ、i型半導体層105はエッチングされな

い。エッチングされた導電型半導体層111及び第2の導電膜112はそれぞれ、ソース

領域118とドレイン領域117、並びに、ソース電極122とドレイン電極121に分

断される。

【0062】

なお本実施の形態では、ソース領域118とドレイン領域117、ソース電極122と

ドレイン電極121、さらにソース配線103と、ソースとドレインを説明をわかりやす

くするために区別しているが、電流の向きによってはソースとドレインが反転することも

ある。

【0063】

中継領域143ではチャネル保護膜がないため、i型半導体層105及び導電型半導体

層111がエッチングされ、i型半導体層105及び導電型半導体層111中に、第1の

コンタクトホール171が形成される。

【0064】

また、容量領域142には、本エッチング工程により、第2の導電膜からなる配線12

3、導電型半導体層116、i型半導体層114の積層体からなる容量配線が形成される

。

【0065】

図2(B)は、上面図である図23のA−A’の断面を示している。

【0066】

次いで第3の絶縁膜による保護膜127を全面に成膜する(図2(C)参照)。保護膜

127は、ゲート絶縁膜104や第2の絶縁膜106と同様の材料で形成すればよく、本

実施の形態では窒化珪素膜を用いる。

【0067】

保護膜127を形成後、レジストマスク128を形成し、レジストマスク128をマス

クとして保護膜127をエッチングする。本実施の形態では、保護膜127のエッチング

はドライエッチングにより行う(図3(A)参照)。

【0068】

レジストマスク128を形成する際には、第4のフォトマスクが用いられる。

【0069】

TFT領域141においては、後の工程で形成する画素電極131と、TFTのドレイ

ン電極121とを接続するための第3のコンタクトホール173を形成する。第3のコン

タクトホール173形成のための保護膜127のエッチングの際には、第2の導電膜によ

り形成されたドレイン電極121がエッチングストッパとして働く。

【0070】

一方、中継領域143には、保護膜127とゲート絶縁膜104がエッチングされ、ソ

ース配線103が露出する。また、このエッチングにより、i型半導体層105及び導電

型半導体層111がエッチングされて形成された第1のコンタクトホール171よりも広

く、第1のコンタクトホール171を完全に覆う第2のコンタクトホール172を形成す

る。

【0071】

第1のコンタクトホール171と第2のコンタクトホール172が重ならない領域では

、第2の導電膜により形成されたソース電極122が存在するため、ドライエッチングは

ソース電極122、特にソース電極122の上面で止まる。すなわちソース電極122が

エッチングストッパとして機能する。

【0072】

また、第1のコンタクトホール171と第2のコンタクトホール172が重なる領域は

、保護膜127の下のゲート絶縁膜104もエッチングされ、第1の導電膜で形成された

ソース配線103が露出する。

【0073】

このエッチング工程によって、中継領域143に階段状のコンタクトホールが形成され

る。上述のように第1のコンタクトホール171と第2のコンタクトホール172が重な

らない領域ではソース電極122の上面と側面が露出する。ソース電極122が露出した

領域が、後の工程で形成される透光性導電膜からなる接続電極132との接続領域となる

ため、接触抵抗を考慮した幅となるように設計する必要がある。即ち、露出面積が大きけ

れば接触抵抗は下がる。一方、露出面積が小さければ、接触抵抗も増加する。このため、

適宜設計する必要がある。

【0074】

容量領域142においては、保護膜127が容量を形成する誘電体膜となるため、エッ

チングを行わずにそのまま残存させる。

【0075】

次いでレジストマスク128を除去し、透光性導電膜129を成膜する(図3(B)参

照)。透光性導電膜129として、インジウム錫酸化物(Indium Tin Oxi

de:略称ITO)、酸化珪素を含むインジウム錫酸化物、酸化インジウム酸化亜鉛(I

ndium Zinc Oxide:略称IZO)、酸化亜鉛等の等の金属酸化物や半導

体酸化物が用いられる。本実施の形態では、インジウム錫酸化物を透光性導電膜129と

して用いる。

【0076】

透光性導電膜129上にレジストマスク134を形成し、レジストマスク134をマス

クとして、透光性導電膜129をエッチングし、画素電極131及び接続電極132を形

成する(図3(C)参照)。

【0077】

レジストマスク134を形成するには、第5のフォトマスクが必要である。

【0078】

TFT領域141では、保護膜127に形成されたコンタクトホールを介して、ドレイ

ン電極121と画素電極131が電気的に接続される。

【0079】

画素電極131は容量領域142まで延び、画素電極131が保護膜127を挟んで配

線123と重なる領域に保持容量が形成される。

【0080】

一方中継領域143においては、前述した階段状のコンタクトホール上に、第2のコン

タクトホール172を完全に覆う広さを持ち、透光性導電膜129により形成された接続

電極132が形成されるので、接続電極132、ソース配線103、ソース電極122は

電気的に接続される。接続電極132とソース電極122は、露出していた表面および側

面とで接続するため、確実な接触を行うことができる。

【0081】

次いでレジストマスク134を除去し、本実施の形態の画素部が完成する(図4参照)

。

【0082】

5枚のフォトマスクを使用して、チャネルストッパ型の逆スタガ型TFTを含むTFT

領域141、容量領域142、中継領域143完成させることができる。そして、これら

を個々の画素に対応してマトリクス状に配置して画像表示部を構成する。これにより能動

素子であるTFTを用いたアクティブマトリクス型の表示装置を作製するための一方の基

板とすることができる。本明細書では便宜上、このような基板をTFT基板と呼ぶ。

【0083】

また図20に示すように、i型半導体層113を、微結晶半導体層(「セミアモルファ

ス半導体層」ともいう)113aと非晶質半導体層113bの積層膜としてもよい。

【0084】

なおセミアモルファス半導体(本明細書では「Semi−amorphous Smi

conductor(SAS)」ともいう)層とは、非晶質半導体と結晶構造を有する半

導体(単結晶、多結晶を含む)層の中間的な構造の半導体を含む層である。このセミアモ

ルファス半導体層は、自由エネルギー的に安定な第3の状態を有する半導体層であって、

短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5〜20nmと

して非単結晶半導体膜中に分散させて存在せしめることが可能である。なお微結晶半導体

層(マイクロクリスタル半導体膜)もセミアモルファス半導体層に含まれる。

【0085】

セミアモルファス半導体層の1つの例として、セミアモルファス珪素層が挙げられる。

セミアモルファス珪素層は、そのラマンスペクトルが520cm−1よりも低波数側にシ

フトしており、またX線回折ではSi結晶格子に由来するとされる(111)、(220

)の回折ピークが観測される。また、未結合手(ダングリングボンド)を終端化させるた

めに水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。本明細書で

は便宜上、このような珪素層をセミアモルファス珪素層と呼ぶ。さらに、ヘリウム、アル

ゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させること

で安定性が増し良好なセミアモルファス半導体層が得られる。

【0086】

またセミアモルファス珪素層は珪素(シリコン)を含む気体をグロー放電分解すること

により得ることができる。代表的な珪素(シリコン)を含む気体としては、SiH4であ

り、その他にもSi2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4など

を用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンか

ら選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素(シリコン)を含む

気体を希釈して用いることで、セミアモルファス珪素層の形成を容易なものとすることが

できる。希釈率は2倍〜1000倍の範囲で珪素(シリコン)を含む気体を希釈すること

が好ましい。またさらに、珪素(シリコン)を含む気体中に、CH4、C2H6などの炭

化物気体、GeH4、GeF4などのゲルマニウム化気体、F2などを混入させて、エネ

ルギーバンド幅を1.5〜2.4eV、若しくは0.9〜1.1eVに調節しても良い。

【0087】

チャネル形成領域が微結晶半導体層113aと非晶質半導体層113bの積層で形成さ

れていると、オン状態の際に、キャリアが微結晶半導体層113aを流れるので、オン電

流が高くなり、TFTの移動度が高くなるという利点がある。

【0088】

一方オフ状態の際には、リーク電流が微結晶半導体層を流れてしまうと、リーク電流が

高くなってしまう恐れがある。しかしながら、チャネル形成領域が微結晶半導体層113

aと非晶質半導体層113bの積層では、リーク電流は非晶質半導体層113bを通るの

で、リーク電流を抑制することができる。

【0089】

本実施の形態で形成された画素部と従来の画素部の比較を、それぞれ図4及び図5、並

びに、図7及び図6を用いて以下に説明する。

【0090】

保持容量は、面積に比例し、誘電体膜の膜厚に反比例する。そこで例えば、ゲート絶縁

膜104及びゲート絶縁膜1104、並びに、保護膜127及び保護膜1127が、全て

膜厚300nmの窒化珪素膜で形成されているとする。本発明の保持容量の誘電体膜の膜

厚は、保護膜127の膜厚300nmであるのに対して、従来の保持容量の誘電体膜の膜

厚は、ゲート絶縁膜1104及び保護膜1127の膜厚を合計した厚さである600nm

となる。

【0091】

従って、本発明の保持容量は、従来の保持容量の2倍の容量を持つことができるという

ことになる。

【0092】

さらに、本発明の保持容量と従来の保持容量の容量が同じ場合には、本発明の保持容量

では、従来の保持容量よりも面積が半分ですむということとなる。すると、遮光材料で形

成される配線123の面積は、容量配線1151の半分の面積でよいことになり、従来の

画素部よりも開口率を高くすることができる。

【0093】

以上から、本発明のチャネルストッパ型の逆スタガ型TFT及びそれを有する画素部は

、フォトマスクの数を増やすことなく、保持容量の容量が大きく、かつ、開口率の高い画

素部を作製することができる。

【0094】

また本発明では、i型半導体層105の膜厚を薄くすることができるので、CVD法に

よる成膜時間の短縮化や、光照射時のリーク電流の発生の低減が可能となる。

【0095】

本発明の逆スタガ型TFTはチャネルストッパ型であるので、チャネル保護膜108に

より、i型半導体層113中のチャネル形成領域は、大気に露出することがない。

【0096】

また中継領域143において、階段状のコンタクトホールを介して、ソース配線103

、ソース電極122、接続電極132が電気的に接続されている。一方、一般的に2つの

異なる層からなる配線を他の配線で接続する場合、橋渡しのためにコンタクトホールは2

つ必要となる。本発明の階段状のコンタクトホールは、橋渡しのために形成される2つの

コンタクトホールの1つと比べ、若干サイズが大きくなる可能性はあるが、コンタクトホ

ールを2つを併せた面積に比べれば十分小さい。このため開口率向上に有利である。さら

にコンタクトホール数が減ることは、不良発生率の低下を意味する。

【0097】

[実施の形態2]

本実施の形態では、実施の形態1で作製したTFT基板を用いて、液晶表示装置を完成

させるまでの作製工程を、図10、図11(A)〜図11(D)、図12、を用いて以下

に説明する。

【0098】

TFT基板上の保護膜127及び画素電極131を覆うように、配向膜208を形成す

る。なお、配向膜208は、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いれ

ばよい。その後、配向膜208の表面にラビング処理を行う。

【0099】

そして、対向基板211には、着色層212、遮光層(ブラックマトリクス)213、

及びオーバーコート層214からなるカラーフィルタを設け、さらに透光性導電膜を用い

て形成された対向電極215と、その上に配向膜216を形成する(図10参照)。対向

電極215が透光性導電膜を用いて形成されることにより、本実施の形態の液晶表示装置

は透過型液晶表示装置となる。なお対向電極215を反射電極で形成すると、本実施の形

態の液晶表示装置は反射型液晶表示装置となる。

【0100】

そして、シール材221をディスペンサにより画素部231と重なる領域を囲むように

描画する。ここでは液晶218を滴下するため、シール材221を画素部231を囲むよ

うに描画する例を示すが、シール材で画素部231を囲みかつ開口部を有するように設け

、TFT基板を貼りあわせた後に毛細管現象を用いて液晶を注入するディップ式(汲み上

げ式)を用いてもよい(図11(A)参照)。

【0101】

次いで、気泡が入らないように減圧下で液晶218の滴下を行い(図11(B)参照)

、基板101及び対向基板211を貼り合わせる(図11(C)参照)。シール材221

に囲まれた領域内に液晶218を1回若しくは複数回滴下する。

【0102】

液晶218の配向モードとしては、液晶分子の配列が光の入射から射出に向かって90

°ツイスト配向したTNモードを用いる場合が多い。TNモードの液晶表示装置を作製す

る場合には、基板のラビング方向が直交するように貼り合わせる。

【0103】

なお、一対の基板間隔は、球状のスペーサを散布することや、樹脂からなる柱状のスペ

ーサを形成することや、シール材221にフィラーを含ませることによって維持すればよ

い。上記柱状のスペーサは、アクリル、ポリイミド、ポリイミドアミド、エポキシの少な

くとも1つを主成分とする有機樹脂材料、もしくは酸化珪素、窒化珪素、窒素を含む酸化

珪素のいずれか一種の材料、或いはこれらの積層膜からなる無機材料であることを特徴と

している。

【0104】

次いで、基板の分断を行う。多面取りの場合、それぞれのパネルを分断する。また、1

面取りの場合、予めカットされている対向基板を貼り合わせることによって、分断工程を

省略することもできる(図11(D)参照)。

【0105】

そして、異方性導電体層を介し、公知の技術を用いてFPC(Flexible Pr

inted Circuit)222を貼りつける(図12参照)。以上の工程で液晶表

示装置が完成する。また、必要があれば光学フィルムを貼り付ける。透過型液晶表示装置

とする場合、偏光板は、TFT基板と対向基板の両方に貼り付ける。以上により本実施の

形態の液晶表示装置が作製される。

【0106】

[実施の形態3]

本発明が適用される電子機器として、テレビ、ビデオカメラ、デジタルカメラ、ゴーグ

ル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオコンポ等)

、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型

ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigita

l Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示し

うるディスプレイを備えた装置)などが挙げられる。

【0107】

それらの電子機器の具体例を、図13、図14、図15(A)〜図15(B)、図16

(A)〜図16(B)、図17、図18(A)〜図18(E)、図19(A)〜図19(

B)に示す。

【0108】

図13は液晶表示パネル2001と、回路基板2011を組み合わせた液晶モジュール

を示している。回路基板2011には、コントロール回路2012や信号分割回路201

3などが形成されており、接続配線2014によって本発明を用いて形成された液晶表示

パネル2001と電気的に接続されている。

【0109】

この液晶表示パネル2001には、複数の画素が設けられた画素部2002と、走査線

駆動回路2003、選択された画素にビデオ信号を供給する信号線駆動回路2004を備

えている。画素部2002は、実施の形態2に基づいて作製すればよく、走査線駆動回路

2003及び信号線駆動回路2004は、チップで形成し、FPC等を用いて、画素部2

002、並びに、走査線駆動回路2003及び信号線駆動回路2004を接続すればよい

。

【0110】

図13に示す液晶モジュールにより液晶テレビ受像器を完成させることができる。図1

4は、液晶テレビ受像機の主要な構成を示すブロック図である。チューナ2101は映像

信号と音声信号を受信する。映像信号は、映像信号増幅回路2102と、そこから出力さ

れる信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路2103と、

その映像信号をドライバICの入力仕様に変換するためのコントロール回路2012によ

り処理される。コントロール回路2012は、走査線側と信号線側にそれぞれ信号が出力

する。デジタル駆動する場合には、信号線側に信号分割回路2013を設け、入力デジタ

ル信号をm個に分割して供給する構成としても良い。

【0111】

チューナ2101で受信した信号のうち、音声信号は音声信号増幅回路2105に送ら

れ、その出力は音声信号処理回路2106を経てスピーカ2107に供給される。制御回

路2108は受信局(受信周波数)や音量の制御情報を入力部2109から受け、チュー

ナ2101や音声信号処理回路2106に信号を送出する。

【0112】

図15(A)に示すように、液晶モジュールを筐体2201に組みこんで、テレビ受像

機を完成させることができる。液晶モジュールにより、表示画面2202が形成される。

また、スピーカ2203、操作スイッチ2204などが適宜備えられている。

【0113】

また図15(B)に、ワイヤレスでディスプレイのみを持ち運び可能なテレビ受像器を

示す。筐体2212にはバッテリ及び信号受信器が内蔵されており、そのバッテリーで表

示部2213やスピーカ部2217を駆動させる。バッテリは充電器2210で繰り返し

充電が可能となっている。また、充電器2210は映像信号を送受信することが可能で、

その映像信号をディスプレイの信号受信器に送信することでができる。筐体2212は操

作キー2216によって制御する。また、図15(B)に示す装置は、操作キー2216

を操作することによって、筐体2212から充電器2210に信号を送ることも可能であ

るため映像音声双方向通信装置とも言える。また、操作キー2216を操作することによ

って、筐体2212から充電器2210に信号を送り、さらに充電器2210が送信でき

る信号を他の電子機器に受信させることによって、他の電子機器の通信制御も可能であり

、汎用遠隔制御装置とも言える。本発明は表示部2213に適用することができる。

【0114】

本発明を図13、図14、図15(A)〜図15(B)に示すテレビ受像器使用するこ

とにより、品質のよい表示装置を備えたテレビ受像器を得ることが可能となる。

【0115】

勿論、本発明はテレビ受像機に限定されず、パーソナルコンピュータのモニタをはじめ

、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など特に大面積の

表示媒体として様々な用途に適用することができる。

【0116】

図16(A)は本発明を用いて形成された液晶表示パネル2301とプリント配線基板

2302を組み合わせたモジュールを示している。液晶表示パネル2301は、複数の画

素が設けられた画素部2303と、第1の走査線駆動回路2304、第2の走査線駆動回

路2305と、選択された画素にビデオ信号を供給する信号線駆動回路2306を備えて

いる。

【0117】

プリント配線基板2302には、コントローラ2307、中央処理装置(CPU)23

08、メモリ2309、電源回路2310、音声処理回路2311及び送受信回路231

2などが備えられている。プリント配線基板2302と液晶表示パネル2301は、フレ

キシブル・プリント・サーキット(FPC)2313により接続されている。プリント配

線基板2302には、容量素子、バッファ回路などを設け、電源電圧や信号にノイズがの

ったり、信号の立ち上がりが鈍ったりすることを防ぐ構成としても良い。また、コントロ

ーラ2307、音声処理回路2311、メモリ2309、CPU2308、電源回路23

10などは、COG(Chip On Glass)方式を用いて液晶表示パネル230

1に実装することもできる。COG方式により、プリント配線基板2302の規模を縮小

することができる。

【0118】

プリント配線基板2302に備えられたインターフェース2314を介して、各種制御

信号の入出力が行われる。また、アンテナとの間の信号の送受信を行なうためのアンテナ

用ポート2315が、プリント配線基板2302に設けられている。

【0119】

図16(B)は、図16(A)に示したモジュールのブロック図を示す。このモジュー

ルは、メモリ2309としてVRAM2316、DRAM2317、フラッシュメモリ2

318などが含まれている。VRAM2316にはパネルに表示する画像のデータが、D

RAM2317には画像データまたは音声データが、フラッシュメモリには各種プログラ

ムが記憶されている。

【0120】

電源回路2310は、液晶表示パネル2301、コントローラ2307、CPU230

8、音声処理回路2311、メモリ2309、送受信回路2312を動作させる電力を供

給する。またパネルの仕様によっては、電源回路2310に電流源が備えられている場合

もある。

【0121】

CPU2308は、制御信号生成回路2320、デコーダ2321、レジスタ2322

、演算回路2323、RAM2324、CPU2308用のインターフェース2319な

どを有している。インターフェース2319を介してCPU2308に入力された各種信

号は、一旦レジスタ2322に保持された後、演算回路2323、デコーダ2321など

に入力される。演算回路2323では、入力された信号に基づき演算を行ない、各種命令

を送る場所を指定する。一方デコーダ2321に入力された信号はデコードされ、制御信

号生成回路2320に入力される。制御信号生成回路2320は入力された信号に基づき

、各種命令を含む信号を生成し、演算回路2323において指定された場所、具体的には

メモリ2309、送受信回路2312、音声処理回路2311、コントローラ2307な

どに送る。

【0122】

メモリ2309、送受信回路2312、音声処理回路2311、コントローラ2307

は、それぞれ受けた命令に従って動作する。以下その動作について簡単に説明する。

【0123】

入力手段2325から入力された信号は、インターフェース2314を介してプリント

配線基板2302に実装されたCPU2308に送られる。制御信号生成回路2320は

、ポインティングデバイスやキーボードなどの入力手段2325から送られてきた信号に

従い、VRAM2316に格納してある画像データを所定のフォーマットに変換し、コン

トローラ2307に送付する。

【0124】

コントローラ2307は、パネルの仕様に合わせてCPU2308から送られてきた画

像データを含む信号にデータ処理を施し、液晶表示パネル2301に供給する。またコン

トローラ2307は、電源回路2310から入力された電源電圧やCPU2308から入

力された各種信号をもとに、Hsync信号、Vsync信号、クロック信号CLK、交

流電圧(AC Cont)、切り替え信号L/Rを生成し、液晶表示パネル2301に供

給する。

【0125】

送受信回路2312では、アンテナ2328において電波として送受信される信号が処

理されており、具体的にはアイソレータ、バンドパスフィルタ、VCO(Voltage

Controlled Oscillator)、LPF(Low Pass Fil

ter)、カプラ、バランなどの高周波回路を含んでいる。送受信回路2312において

送受信される信号のうち音声情報を含む信号が、CPU2308からの命令に従って、音

声処理回路2311に送られる。

【0126】

CPU2308の命令に従って送られてきた音声情報を含む信号は、音声処理回路23

11において音声信号に復調され、スピーカ2327に送られる。またマイク2326か

ら送られてきた音声信号は、音声処理回路2311において変調され、CPU2308か

らの命令に従って、送受信回路2312に送られる。

【0127】

コントローラ2307、CPU2308、電源回路2310、音声処理回路2311、

メモリ2309を、本実施の形態のパッケージとして実装することができる。本実施の形

態は、アイソレータ、バンドパスフィルタ、VCO(Voltage Controll

ed Oscillator)、LPF(Low Pass Filter)、カプラ、

バランなどの高周波回路以外であれば、どのような回路にも応用することができる。

【0128】

図17は、図16(A)〜図16(B)に示すモジュールを含む携帯電話機の一態様を

示している。液晶表示パネル2301はハウジング2330に脱着自在に組み込まれる。

ハウジング2330は液晶表示パネル2301のサイズに合わせて、形状や寸法を適宜変

更することができる。液晶表示パネル2301を固定したハウジング2330はプリント

基板2331に嵌着されモジュールとして組み立てられる。

【0129】

液晶表示パネル2301はFPC2313を介してプリント基板2331に接続される

。プリント基板2331には、スピーカ2332、マイクロフォン2333、送受信回路

2334、CPU及びコントローラなどを含む信号処理回路2335が形成されている。

このようなモジュールと、入力手段2336、バッテリ2337、アンテナ2340を組

み合わせ、筐体2339に収納する。液晶表示パネル2301の画素部は筐体2339に

形成された開口窓から視認できように配置する。

【0130】

本実施の形態に係る携帯電話機は、その機能や用途に応じてさまざまな態様に変容し得

る。例えば、表示パネルを複数備えたり、筐体を適宜複数に分割して蝶番により開閉式と

した構成としても、上記した作用効果を奏することができる。

【0131】

本発明を図16(A)〜図16(B)、図17に示す携帯電話に使用することにより、

品質のよい表示装置を備えた携帯電話を得ることが可能となる。

【0132】

図18(A)は液晶ディスプレイであり、筐体2401、支持台2402、表示部24

03などによって構成されている。本発明は表示部2403に適用が可能である。

【0133】

本発明を使用することにより、品質のよい表示装置を備えた液晶ディスプレイを得るこ

とが可能となる。

【0134】

図18(B)はコンピュータであり、本体2501、筐体2502、表示部2503、

キーボード2504、外部接続ポート2505、ポインティングデバイス2506等を含

む。本発明は表示部2503に適用することができる。

【0135】

本発明を使用することにより、品質のよい表示装置を備えたコンピュータを得ることが

可能となる。

【0136】

図18(C)は携帯可能なコンピュータであり、本体2601、表示部2602、スイ

ッチ2603、操作キー2604、赤外線ポート2605等を含む。本発明は表示部26

02に適用することができる。

【0137】

本発明を使用することにより、品質のよい表示装置を備えたコンピュータを得ることが

可能となる。

【0138】

図18(D)は携帯型のゲーム機であり、筐体2701、表示部2702、スピーカ部

2703、操作キー2704、記録媒体挿入部2705等を含む。本発明は表示部270

2に適用することができる。

【0139】

本発明を使用することにより、品質のよい表示装置を備えたゲーム機を得ることが可能

となる。

【0140】

図18(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)

であり、本体2801、筐体2802、表示部A2803、表示部B2804、記録媒体

読込部2805、操作キー2806、スピーカ部2807等を含む。表示部A2803は

主として画像情報を表示し、表示部B2804は主として文字情報を表示する。本発明は

表示部A2803、表示部B2804及び制御用回路部等に適用することができる。なお

、記憶媒体とは、DVD等であり、記録媒体を備えた画像再生装置には家庭用ゲーム機器

なども含まれる。

【0141】

本発明を使用することにより、品質のよい表示装置を備えた画像再生装置を得ることが

可能となる。

【0142】

図19(A)及び図19(B)は、本発明の液晶表示装置をカメラ、例えばデジタルカ

メラに組み込んだ例を示す図である。図19(A)は、デジタルカメラの前面方向から見

た斜視図、図19(B)は、後面方向から見た斜視図である。図19(A)において、デ

ジタルカメラには、リリースボタン2901、メインスイッチ2902、ファインダ窓2

903、フラッシュ2904、レンズ2905、鏡胴2906、筺体2907が備えられ

ている。

【0143】

また、図19(B)において、ファインダ接眼窓2911、モニタ2912、操作ボタ

ン2913が備えられている。

【0144】

リリースボタン2901は、半分の位置まで押下されると、焦点調整機構および露出調

整機構が作動し、最下部まで押下されるとシャッターが開く。

【0145】

メインスイッチ2902は、押下又は回転によりデジタルカメラの電源のON/OFF

を切り替える。

【0146】

ファインダ窓2903は、デジタルカメラの前面のレンズ2905の上部に配置されて

おり、図19(B)に示すファインダ接眼窓2911から撮影する範囲やピントの位置を

確認するための装置である。

【0147】

フラッシュ2904は、デジタルカメラの前面上部に配置され、被写体輝度が低いとき

に、リリースボタン2901が押下されてシャッターが開くと同時に補助光を照射する。

【0148】

レンズ2905は、デジタルカメラの正面に配置されている。レンズは、フォーカシン

グレンズ、ズームレンズ等により構成され、図示しないシャッター及び絞りと共に撮影光

学系を構成する。また、レンズの後方には、CCD(Charge Coupled D

evice)等の撮像素子が設けられている。

【0149】

鏡胴2906は、フォーカシングレンズ、ズームレンズ等のピントを合わせるためにレ

ンズの位置を移動するものであり、撮影時には、鏡胴を繰り出すことにより、レンズ29

05を手前に移動させる。また、携帯時は、レンズ2905を沈銅させてコンパクトにす

る。なお、本実施の形態においては、鏡胴を繰り出すことにより被写体をズーム撮影する

ことができる構造としているが、この構造に限定されるものではなく、筺体2907内で

の撮影光学系の構成により鏡胴を繰り出さずともズーム撮影が可能なデジタルカメラでも

よい。

【0150】

ファインダ接眼窓2911は、デジタルカメラの後面上部に設けられており、撮影する

範囲やピントの位置を確認する際に接眼するために設けられた窓である。

【0151】

操作ボタン2913は、デジタルカメラの後面に設けられた各種機能ボタンであり、セ

ットアップボタン、メニューボタン、ディスプレイボタン、機能ボタン、選択ボタン等に

より構成されている。

【0152】

本発明の液晶表示装置は、図19(A)及び図19(B)に示すカメラのモニタ291

2に組み込むことができる。これにより品質のよい表示装置を備えたデジタルカメラを得

ることが可能となる。

【0153】

なお、本実施の形態に示した例はごく一例であり、これらの用途に限定するものではな

いことを付記する。

【符号の説明】

【0154】

101 基板

102 ゲート配線

103 ソース配線

104 ゲート絶縁膜

105 i型半導体層

106 絶縁膜

108 チャネル保護膜

109 レジストマスク

111 導電型半導体層

112 導電膜

113 i型半導体層

113a 微結晶半導体層

113b 非晶質半導体層

114 i型半導体層

116 導電型半導体層

117 ドレイン領域

118 ソース領域

121 ドレイン電極

122 ソース電極

123 配線

125 レジストマスク

127 保護膜

128 レジストマスク

129 透光性導電膜

131 画素電極

132 接続電極

134 レジストマスク

141 TFT領域

142 容量領域

143 中継領域

161 導電膜

162 レジストマスク

171 コンタクトホール

172 コンタクトホール

173 コンタクトホール

208 配向膜

211 対向基板

212 着色層

213 遮光層(ブラックマトリクス)

214 オーバーコート層

215 対向電極

216 配向膜

218 液晶

221 シール材

222 FPC

231 画素部

1101 基板

1102 ゲート配線

1104 ゲート絶縁膜

1105 半導体層

1106 絶縁膜

1108 チャネル保護膜

1109 レジストマスク

1111 半導体層

1112 導電膜

1113 i型半導体層

1117 ドレイン領域

1118 ソース領域

1121 ドレイン電極

1122 ソース配線

1125 レジストマスク

1127 保護膜

1128 レジストマスク

1129 導電膜

1131 画素電極

1134 レジストマスク

1141 TFT領域

1142 容量領域

1143 配線領域

1151 容量配線

1161 導電膜

1162 レジストマスク

1173 コンタクトホール

2001 液晶表示パネル

2002 画素部

2003 走査線駆動回路

2004 信号線駆動回路

2011 回路基板

2012 コントロール回路

2013 信号分割回路

2014 接続配線

2101 チューナ

2102 映像信号増幅回路

2103 映像信号処理回路

2105 音声信号増幅回路

2106 音声信号処理回路

2107 スピーカ

2108 制御回路

2109 入力部

2201 筐体

2202 表示画面

2203 スピーカ

2204 操作スイッチ

2210 充電器

2212 筐体

2213 表示部

2216 操作キー

2217 スピーカ部

2301 液晶表示パネル

2302 プリント配線基板

2303 画素部

2304 走査線駆動回路

2305 走査線駆動回路

2306 信号線駆動回路

2307 コントローラ

2308 CPU

2309 メモリ

2310 電源回路

2311 音声処理回路

2312 送受信回路

2313 FPC

2314 インターフェース

2315 アンテナ用ポート

2316 VRAM

2317 DRAM

2318 フラッシュメモリ

2319 インターフェース

2320 制御信号生成回路

2321 デコーダ

2322 レジスタ

2323 演算回路

2324 RAM

2325 入力手段

2326 マイク

2327 スピーカ

2328 アンテナ

2330 ハウジング

2331 プリント基板

2332 スピーカ

2333 マイクロフォン

2334 送受信回路

2335 信号処理回路

2336 入力手段

2337 バッテリ

2339 筐体

2340 アンテナ

2401 筐体

2402 支持台

2403 表示部

2501 本体

2502 筐体

2503 表示部

2504 キーボード

2505 外部接続ポート

2506 ポインティングデバイス

2601 本体

2602 表示部

2603 スイッチ

2604 操作キー

2605 赤外線ポート

2701 筐体

2702 表示部

2703 スピーカ部

2704 操作キー

2705 記録媒体挿入部

2801 本体

2802 筐体

2803 表示部A

2804 表示部B

2805 記録媒体読込部

2806 操作キー

2807 スピーカ部

2901 リリースボタン

2902 メインスイッチ

2903 ファインダ窓

2904 フラッシュ

2905 レンズ

2906 鏡胴

2907 筺体

2911 ファインダ接眼窓

2912 モニタ

2913 操作ボタン

【特許請求の範囲】

【請求項1】

第1の導電層及び第2の導電層と、

前記第1の導電層及び前記第2の導電層上に設けられた第1の絶縁層と、

前記第1の絶縁層上に設けられた第1の半導体層と、

前記第1の半導体層上に設けられた第2の絶縁層と、

前記第2の絶縁層上に設けられた第3の導電層、

前記第2の絶縁層上に設けられた第4の導電層と、

前記第1の絶縁層上に設けられた第5の導電層と、

前記第3の導電層、前記第4の導電層、及び前記第5の導電層上に設けられた第3の絶縁層と、

前記第3の絶縁層上に設けられた第6の導電層と、

前記第3の絶縁層上に設けられた第7の導電層と、

を有し、

前記第1の導電層は、トランジスタのゲート電極となる機能を有し、

前記第1の絶縁層は、前記トランジスタのゲート絶縁層となる機能を有し、

前記第1の半導体層は、前記第1の絶縁層を介して前記第1の導電層と重なる領域を有し、

前記第1の半導体層は、前記トランジスタのチャネル形成領域を有し、

前記第2の絶縁層は、前記チャネル形成領域と重なる領域を有し、

前記第3の導電層と、前記第4の導電層と、は、前記第2の絶縁層上において間隔をあけて設けられ、

前記第3の導電層は、前記トランジスタのソース電極又はドレイン電極の一方となる機能を有し、

前記第4の導電層は、前記トランジスタのソース電極又はドレイン電極の他方となる機能を有し、

前記第6の導電層は、表示素子に電圧を印加する一対の電極の一方となる機能を有し、

前記第6の導電層は、前記第3の絶縁層に設けられたコンタクトホールを介して、前記第3の導電層と電気的に接続され、

前記第5の導電層は、容量素子の一対の電極のうちの一方となる機能を有し、

前記第3の絶縁層は、前記容量素子の誘電体層となる機能を有し、

前記第6の導電層は、前記容量素子の一対の電極のうちの他方となる機能を有し、

前記第2の導電層は、第7の導電層によって、前記第4の導電層と電気的に接続され、

前記第7の導電層は、前記第4の導電層の上面と接する領域と、前記第4の導電層の側面と接する領域と、前記第2の導電層と接する領域と、を有することを特徴とする表示装置。

【請求項1】

第1の導電層及び第2の導電層と、

前記第1の導電層及び前記第2の導電層上に設けられた第1の絶縁層と、

前記第1の絶縁層上に設けられた第1の半導体層と、

前記第1の半導体層上に設けられた第2の絶縁層と、

前記第2の絶縁層上に設けられた第3の導電層、

前記第2の絶縁層上に設けられた第4の導電層と、

前記第1の絶縁層上に設けられた第5の導電層と、

前記第3の導電層、前記第4の導電層、及び前記第5の導電層上に設けられた第3の絶縁層と、

前記第3の絶縁層上に設けられた第6の導電層と、

前記第3の絶縁層上に設けられた第7の導電層と、

を有し、

前記第1の導電層は、トランジスタのゲート電極となる機能を有し、

前記第1の絶縁層は、前記トランジスタのゲート絶縁層となる機能を有し、

前記第1の半導体層は、前記第1の絶縁層を介して前記第1の導電層と重なる領域を有し、

前記第1の半導体層は、前記トランジスタのチャネル形成領域を有し、

前記第2の絶縁層は、前記チャネル形成領域と重なる領域を有し、

前記第3の導電層と、前記第4の導電層と、は、前記第2の絶縁層上において間隔をあけて設けられ、

前記第3の導電層は、前記トランジスタのソース電極又はドレイン電極の一方となる機能を有し、

前記第4の導電層は、前記トランジスタのソース電極又はドレイン電極の他方となる機能を有し、

前記第6の導電層は、表示素子に電圧を印加する一対の電極の一方となる機能を有し、

前記第6の導電層は、前記第3の絶縁層に設けられたコンタクトホールを介して、前記第3の導電層と電気的に接続され、

前記第5の導電層は、容量素子の一対の電極のうちの一方となる機能を有し、

前記第3の絶縁層は、前記容量素子の誘電体層となる機能を有し、

前記第6の導電層は、前記容量素子の一対の電極のうちの他方となる機能を有し、

前記第2の導電層は、第7の導電層によって、前記第4の導電層と電気的に接続され、

前記第7の導電層は、前記第4の導電層の上面と接する領域と、前記第4の導電層の側面と接する領域と、前記第2の導電層と接する領域と、を有することを特徴とする表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2013−80228(P2013−80228A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2012−237398(P2012−237398)

【出願日】平成24年10月29日(2012.10.29)

【分割の表示】特願2008−296460(P2008−296460)の分割

【原出願日】平成20年11月20日(2008.11.20)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成24年10月29日(2012.10.29)

【分割の表示】特願2008−296460(P2008−296460)の分割

【原出願日】平成20年11月20日(2008.11.20)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]