表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光表示装置に関する。また当該発光表示装置を具備する電子機器に関する。

【背景技術】

【0002】

液晶表示装置に代表されるように、ガラス基板等の平板に形成される薄膜トランジスタは

、アモルファスシリコン、多結晶シリコンによって作製されている。アモルファスシリコ

ンを用いた薄膜トランジスタは、電界効果移動度が低いもののガラス基板の大面積化に対

応することができ、一方、結晶シリコンを用いた薄膜トランジスタは電界効果移動度が高

いものの、レーザアニール等の結晶化工程が必要であり、ガラス基板の大面積化には必ず

しも適応しないといった特性を有している。

【0003】

これに対し、酸化物半導体を用いて薄膜トランジスタを作製し、電子デバイスや光デバイ

スに応用する技術が注目されている。例えば、酸化物半導体膜として酸化亜鉛、In−G

a−Zn−O系酸化物半導体を用いて薄膜トランジスタを作製し、発光表示装置のスイッ

チング素子などに用いる技術が特許文献1で開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−31750号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

酸化物半導体をチャネル領域に用いた薄膜トランジスタは、アモルファスシリコンをチャ

ネル領域に用いた薄膜トランジスタよりも高い電界効果移動度が得られている。このよう

な酸化物半導体を用いて形成した薄膜トランジスタを具備する画素は、ELディスプレイ

等の発光表示装置への応用が期待される。また、3Dディスプレイ、4k2kディスプレ

イ等、さらなる付加価値のついた発光表示装置では、画素一つあたりの面積が小さくなる

ことが予想される一方で、開口率の向上した画素を有する発光表示装置が望まれる。

【0006】

そこで、本発明は、酸化物半導体を用いた薄膜トランジスタを具備する画素において、開

口率の向上を図ることのできる発光表示装置を提供することを課題の一とする。

【課題を解決するための手段】

【0007】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第

1の配線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は

、第1の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層

とが重畳して設けられる発光表示装置である。

【0008】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線と、信号線として機能する第2の配線に電気的に接続

されており、薄膜トランジスタは、第1の配線上にゲート絶縁膜を介して設けられた酸化

物半導体層を有し、酸化物半導体層は、第1の配線が設けられた領域をはみ出て設けられ

ており、第2の配線は、第1の配線上のゲート絶縁膜上を延在して酸化物半導体層上に接

しており、発光素子と、酸化物半導体層とが重畳して設けられる発光表示装置である。

【0009】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線と、信号線として機能する第2の配線に電気的に接続

されており、薄膜トランジスタは、第1の配線上にゲート絶縁膜を介して設けられた酸化

物半導体層を有し、酸化物半導体層は、第1の配線が設けられた領域をはみ出て設けられ

ており、第2の配線は、第1の配線上のゲート絶縁膜及びゲート絶縁膜上の層間絶縁層上

を延在して酸化物半導体層上に接しており、発光素子と、酸化物半導体層とが重畳して設

けられる発光表示装置である。

【0010】

本発明の一態様は、第1の薄膜トランジスタ、第2の薄膜トランジスタ、及び発光素子を

有する複数の画素を有し、画素は、走査線として機能する第1の配線と、信号線として機

能する第2の配線に電気的に接続されており、第1の薄膜トランジスタは、第1の配線上

にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1の配

線が設けられた領域をはみ出て設けられており、第2の配線は、第1の配線上のゲート絶

縁膜上を延在して酸化物半導体層上に接し、酸化物半導体層に接し、且つ第1の薄膜トラ

ンジスタと第2の薄膜トランジスタとの電気的な接続をとるための第3の配線は、第1の

配線上のゲート絶縁膜上を延在して設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる発光表示装置である。

【0011】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線と、信号線として機能する第2の配線に電気的に接続

されており、薄膜トランジスタは、第1の配線上にゲート絶縁膜を介して設けられた酸化

物半導体層を有し、酸化物半導体層は、第1の配線が設けられた領域をはみ出て設けられ

ており、第2の配線は、第1の配線上のゲート絶縁膜及びゲート絶縁膜上の層間絶縁層上

を延在して酸化物半導体層上に接し、酸化物半導体層に接し、且つ第1の薄膜トランジス

タと第2の薄膜トランジスタとの電気的な接続をとるための第3の配線は、第1の配線上

のゲート絶縁膜及びゲート絶縁膜上の層間絶縁層上を延在して設けられており、発光素子

と、酸化物半導体層とが重畳して設けられる発光表示装置である。

【発明の効果】

【0012】

酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を

図ることができる。従って、高精細な表示部を有する発光表示装置とすることができる。

【図面の簡単な説明】

【0013】

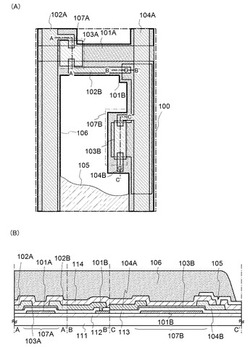

【図1】発光表示装置について説明する上面図及び断面図。

【図2】発光表示装置について説明する断面図。

【図3】発光表示装置について説明する上面図。

【図4】発光表示装置について説明する上面図及び断面図。

【図5】発光表示装置について説明する上面図。

【図6】発光表示装置について説明する上面図及び断面図。

【図7】発光表示装置について説明する回路図。

【図8】発光表示装置について説明する回路図。

【図9】発光表示装置について説明する断面図。

【図10】電子機器について説明する図。

【図11】電子機器について説明する図。

【図12】発光表示装置について説明する上面図及び断面図。

【発明を実施するための形態】

【0014】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通

して用い、その繰り返しの説明は省略する。

【0015】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、又は領域は、明瞭

化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0016】

なお、本明細書にて用いる第1、第2、第3、等の用語は、構成要素の混同を避けるため

に付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「

第2の」又は「第3の」などと適宜置き換えて説明することができる。

【0017】

(実施の形態1)

本実施の形態では、一例として、薄膜トランジスタ(以下、TFTともいう)及び当該T

FTに接続された発光素子を有する画素について示し、発光表示装置の説明をする。なお

画素とは、表示装置の各画素に設けられた各素子、例えば薄膜トランジスタ、発光素子、

及び配線等の電気的な信号により表示を制御するための素子で構成される素子群、のこと

をいう。なお画素は、カラーフィルター等を含むものであっても良く、一画素によって、

明るさを制御できる色要素一つ分としてもよい。よって、一例として、RGBの色要素か

らなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素と

の三画素から構成されるものとなり、複数の画素によって画像を得ることができるものと

なる。

【0018】

なお発光素子は一対の電極(陽極及び陰極)の間に発光層を具備する構成であり、電極上

に発光層を構成する素子を積層して形成される。本明細書中で発光素子の一方の電極を図

中で示す際には、発光素子ということもある。

【0019】

なお、AとBとが接続されている、と記載する場合は、AとBとが電気的に接続されて

いる場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは

、電気的作用を有する対象物であるとする。具体的には、トランジスタをはじめとするス

イッチング素子を介してAとBとが接続され、該スイッチング素子の導通によって、Aと

Bとが概略同電位となる場合や、抵抗素子を介してAとBとが接続され、該抵抗素子の両

端に発生する電位差が、AとBとを含む回路の動作に影響しない程度となっている場合な

ど、回路動作を考えた場合、AとBとの間の部分を同じノードとして捉えて差し支えない

状態である場合を表す。

【0020】

図1(A)には、画素の上面図を示す。なお図1(A)に示すTFTの構造は、ボトムゲ

ート型構造であり、ゲートとなる配線から見てチャネル領域となる酸化物半導体層の反対

側に、TFTのソース電極及びドレイン電極となる配線層を有する、いわゆる逆スタガ型

の構成について示している。

【0021】

図1(A)に示す画素100は、走査線として機能する第1の配線101A、信号線とし

て機能する第2の配線102A、第1の酸化物半導体層103A、第2の酸化物半導体層

103B、電源線104A、容量電極101B、発光素子105を有する。また図1(A

)に示す画素100は、第1の酸化物半導体層103Aと容量電極101Bとを電気的に

接続するための第3の配線102Bを有し、第1の薄膜トランジスタ107Aが構成され

る。また図1(A)に示す画素100は、第2の酸化物半導体層103Bと発光素子10

5とを電気的に接続するための第4の配線104Bを有し、第2の薄膜トランジスタ10

7Bが構成される。

【0022】

第1の配線101A、第2の配線102A、第3の配線102B、第4の配線104B、

第1の酸化物半導体層103A、第2の酸化物半導体層103B、電源線104A、及び

容量電極101B上には、発光素子を画素毎に分離するための隔壁106が設けられる。

なお隔壁106の内側に第4の配線104Bに接続される発光素子105が設けられるこ

ととなる。

【0023】

第1の配線101Aは第1の薄膜トランジスタ107Aのゲートとして機能する配線でも

ある。容量電極101Bは第2の薄膜トランジスタ107Bのゲート、及び容量素子の一

方の電極として機能する配線でもある。第2の配線102Aは、第1の薄膜トランジスタ

107Aのソース電極またはドレイン電極の一方として機能する配線でもある。第3の配

線102Bは、第1の薄膜トランジスタ107Aのソース電極またはドレイン電極の他方

として機能する配線でもある。電源線104Aは、第2の薄膜トランジスタ107Bのソ

ース電極またはドレイン電極の一方、及び容量素子の他方の電極として機能する配線でも

ある。第4の配線104Bは、第2の薄膜トランジスタ107Bのソース電極またはドレ

イン電極の他方として機能する配線でもある。

【0024】

なお第1の配線101Aと、容量電極101Bとが同層から設けられ、第2の配線102

A、第3の配線102B、電源線104A、及び第4の配線104Bが同層から設けられ

る。また電源線104Aと容量電極101Bとは、一部重畳して設けられており、第2の

薄膜トランジスタ107Bの保持容量を形成している。

【0025】

なお、第1の薄膜トランジスタ107Aが有する第1の酸化物半導体層103Aは、第1

の配線101A上にゲート絶縁膜(図示せず)を介して設けられている。第1の酸化物半

導体層103Aは第1の配線101Aが設けられた領域及び隔壁106をはみ出て設けら

れている。

【0026】

なおAがBよりはみ出ているとは、積層されたA、Bに着目して上面図をみた場合に、A

、Bの端部が一致せず、AがBの端部より外側に延在していることをいう。

【0027】

なお第1の薄膜トランジスタ107A、第2の薄膜トランジスタ107Bの他に、複数の

薄膜トランジスタを具備する構成としてもよい。なお第1の薄膜トランジスタ107Aは

、当該第1の薄膜トランジスタ107Aを具備する画素を選択するための機能を有し、選

択トランジスタともいう。また第2の薄膜トランジスタ107Bは、当該第2の薄膜トラ

ンジスタ107Bを有する画素の発光素子105に流す電流を制御するための機能を有し

、駆動トランジスタともいう。

【0028】

また図1(B)には、図1(A)における一点鎖線A−A’、B−B’、C−C’間の断

面構造について示している。図1(B)に示す断面構造で、基板111上には、下地膜1

12を介して、ゲートである第1の配線101A、容量電極101Bが設けられている。

第1の配線101A、及び容量電極101Bを覆うように、ゲート絶縁膜113が設けら

れている。ゲート絶縁膜113上には、第1の酸化物半導体層103A、第2の酸化物半

導体層103Bが設けられている。第1の酸化物半導体層103A上には、第2の配線1

02A、第3の配線102B、第2の酸化物半導体層103B上には、電源線104A、

第4の配線104Bが設けられている。また、第1の酸化物半導体層103A、第2の酸

化物半導体層103B、第2の配線102A、第3の配線102B、電源線104A、及

び第4の配線104B上には、パッシベーション膜として機能する酸化物絶縁層114が

設けられている。第1の配線101A、第2の配線102A、第3の配線102B、第4

の配線104B、第1の酸化物半導体層103A、第2の酸化物半導体層103B、電源

線104A、及び容量電極101B上の酸化物絶縁層114上には、隔壁106が設けら

れている。また第4の配線104B上の酸化物絶縁層114には開口部が形成されており

、開口部において発光素子105の電極と第4の配線104Bとの接続がなされる。また

一点鎖線B−B’において、第3の配線102Bと容量電極101Bとが、ゲート絶縁膜

113に形成される開口部を介して接続されている。

【0029】

なお、図1(A)、(B)に示す画素は、図7に示す基板700上の複数の画素701の

ように、マトリクス状に配置されるものである。図7では、基板700上には、画素部7

02、走査線駆動回路703、及び信号線駆動回路704を有する構成について示してい

る。画素701は、走査線駆動回路703に接続された第1の配線101Aによって供給

される走査信号により、各行ごとに選択状態か、非選択状態かが決定される。また走査信

号によって選択されている画素701は、信号線駆動回路704に接続された第2の配線

102Aによって、ビデオ電圧(画像信号、ビデオ信号、ビデオデータともいう)が供給

される。また、画素701には基板700の外部に設けられた電源回路705より延在し

て設けられる電源線104Aに接続される。

【0030】

図7では、走査線駆動回路703、信号線駆動回路704が基板700上に設けられる構

成について示したが、走査線駆動回路703または信号線駆動回路704のいずれか一が

基板700上に設けられる構成としてもよい。また画素部702のみを基板700上に設

ける構成としても良い。また図7では、電源回路705が基板700の外部に設けられる

構成について示したが基板700上に設けられる構成でもよい。

【0031】

図7で画素部702には、複数の画素701がマトリクス状に配置(ストライプ配置)す

る例について示している。なお、画素701は必ずしもマトリクス状に配置されている必

要はなく、例えば、画素701をデルタ配置、またはベイヤー配置としてもよい。また画

素部702における表示方式はプログレッシブ方式、インターレース方式のいずれかを用

いることができる。なお、カラー表示する際に画素で制御する色要素としては、RGB(

Rは赤、Gは緑、Bは青)の三色に限定されず、それ以上でもよく、例えば、RGBW(

Wは白)、又はRGBに、イエロー、シアン、マゼンタなどを一色以上追加したものなど

がある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。

【0032】

図7において、第1の配線101A、第2の配線102A、及び電源線104Aは画素の

行方向及び列方向の数に応じて示している。なお、第1の配線101A、第2の配線10

2A、及び電源線104Aは、画素を構成するサブ画素(副画素、サブピクセルともいう

)の数、または画素内のトランジスタの数に応じて、本数を増やす構成としてもよい。ま

た画素間で第1の配線101A、第2の配線102A、及び電源線104Aを共有して画

素701を駆動する構成としても良い。

【0033】

なお、図1(A)ではTFTの形状を、第2の配線102Aが矩形状であるものとして示

しているが、第3の配線102Bを囲む形状(具体的には、U字型またはC字型)とし、

キャリアが移動する領域の面積を増加させ、流れる電流量を増やす構成としてもよい。

【0034】

なお、第1の薄膜トランジスタ107Aとなる領域以外の第1の配線101Aの幅は、部

分的に細くなるよう小さくとってもよい。第1の配線の幅を小さくすることにより、画素

の開口率の向上を図ることができる。

【0035】

なお開口率とは、単位面積に対し、光が透過する領域の面積を表したものである。従って

、光を透過しない部材が占める領域が広くなると、開口率が低下し、光を透過する部材が

占める領域が広くなると開口率が向上することとなる。発光表示装置では、隔壁の内側に

設けられる発光素子が占める領域に光を透過しない配線等が重畳しないようにすること、

薄膜トランジスタのサイズを小さくすることで開口率が向上することとなる。

【0036】

なお、薄膜トランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの

端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、

ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、

ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれが

ソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレイ

ンとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一

例としては、それぞれを第1端子、第2端子と表記する場合がある。あるいは、それぞれ

を第1電極、第2電極と表記する場合がある。あるいは、第1領域、第2領域と表記する

場合がある。

【0037】

次に図1(A)、(B)に示した上面図及び断面図をもとに、画素の作製方法について図

2を用いて説明する。

【0038】

まず、透光性を有する基板111にはガラス基板を用いることができる。なお基板111

上に基板111からの不純物の拡散の防止、または基板111上に設ける各素子との密着

性を向上するための下地膜112を設ける構成を示している。なお下地膜112は、必ず

しも設ける必要はない。

【0039】

次いで、導電層を基板111全面に成膜した後、第1のフォトリソグラフィー工程を行い

、レジストマスクを形成し、エッチングにより不要な部分を除去して第1の配線101A

、容量電極101Bを形成する。このとき少なくとも第1の配線101A及び容量電極1

01Bの端部がテーパー形状となるようにエッチングする。

【0040】

第1の配線101A及び容量電極101Bは、アルミニウム(Al)や銅(Cu)などの

低抵抗導電性材料で形成することが望ましいが、Al単体では耐熱性が劣り、また腐蝕し

やすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。耐熱性導電性材

料としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(M

o)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、ま

たは上述した元素を成分とする合金か、上述した元素を組み合わせた合金、または上述し

た元素を成分とする窒化物で形成する。

【0041】

なお、インクジェットや印刷法を用いてTFTを構成する配線等を形成することができる

。これらにより、室温で製造、低真空度で製造、又は大型基板上に製造することができる

。フォトマスクを用いなくても製造することができるため、トランジスタのレイアウトを

容易に変更することが出来る。さらに、レジストを用いる必要がないので、材料費が安く

なり、工程数を削減できる。またインクジェットや印刷法を用いてレジストマスク等を形

成することもできる。インクジェットや印刷法を用いてレジストを必要な部分にのみ形成

し、露光及び現像によりレジストマスクとすることで、全面にレジストを形成するよりも

、低コスト化が図れる。

【0042】

また、多階調マスクにより複数(代表的には二種類)の厚さの領域を有するレジストマス

クを形成し、配線等の形成を行っても良い。

【0043】

次いで、第1の配線101A及び容量電極101B上に絶縁膜(以下、ゲート絶縁膜11

3という)を全面に成膜する。ゲート絶縁膜113はスパッタ法などを用いる。

【0044】

例えば、ゲート絶縁膜113としてスパッタ法により酸化シリコン膜を用いて形成する。

勿論、ゲート絶縁膜113はこのような酸化シリコン膜に限定されるものでなく、酸化窒

化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化タンタル膜などの他の絶縁膜

を用い、これらの材料から成る単層または積層構造として形成しても良い。

【0045】

なお、酸化物半導体を成膜する前に、アルゴンガスを導入してプラズマを発生させる逆ス

パッタを行い、ゲート絶縁膜113の表面に付着しているゴミを除去することが好ましい

。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰

囲気に酸素、N2Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気にCl2

、CF4などを加えた雰囲気で行ってもよい。

【0046】

次に、ゲート絶縁膜113上に、酸化物半導体を、ゲート絶縁膜113表面のプラズマ処

理後、大気に曝すことなく成膜する。酸化物半導体をトランジスタの半導体層として用い

ることにより、アモルファスシリコン等のシリコン系半導体材料と比較して電界効果移動

度を高めることが出来る。なお酸化物半導体としては、例えば、酸化亜鉛(ZnO)、酸

化スズ(SnO2)なども用いることができる。また、ZnOにInやGaなどを添加す

ることもできる。

【0047】

酸化物半導体としてInMO3(ZnO)x(x>0)で表記される薄膜を用いることが

できる。なお、Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(M

n)及びコバルト(Co)から選ばれた一の金属元素又は複数の金属元素を示す。例えば

Mとして、Gaの場合があることの他、GaとNi又はGaとFeなど、Ga以外の上記

金属元素が含まれる場合がある。また、上記酸化物半導体において、Mとして含まれる金

属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、又は該遷移金属の酸

化物が含まれているものがある。例えば、酸化物半導体層としてIn−Ga−Zn−O系

膜を用いることができる。

【0048】

酸化物半導体(InMO3(ZnO)x(x>0)膜)としてIn−Ga−Zn−O系膜

のかわりに、Mを他の金属元素とするInMO3(ZnO)x(x>0)膜を用いてもよ

い。また、酸化物半導体として上記の他にも、In−Sn−Zn−O系、In−Al−Z

n−O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn−O系

、In−Zn−O系、Sn−Zn−O系、Al−Zn−O系、In−O系、Sn−O系、

Zn−O系の酸化物半導体を適用することができる。

【0049】

なお酸化物半導体として、In−Ga−Zn−O系を用いる。ここでは、In2O3:G

a2O3:ZnO=1:1:1としたターゲットを用いる。基板とターゲットとの間の距

離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率1

00%)雰囲気下で成膜する。なお、パルス直流(DC)電源を用いると、成膜時に発生

する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も均一となるために

好ましい。

【0050】

なお酸化物半導体の成膜は、先に逆スパッタを行ったチャンバーと同一チャンバーを用い

てもよいし、先に逆スパッタを行ったチャンバーと異なるチャンバーで成膜してもよい。

【0051】

スパッタ法にはスパッタ用電源に高周波電源を用いるRFスパッタ法、直流電源を用いる

DCスパッタ法、さらにパルス的にバイアスを与えるパルスDCスパッタ法がある。RF

スパッタ法は主に絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に金属膜を成膜

する場合に用いられる。

【0052】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ

装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種

類の材料を同時に放電させて成膜することもできる。

【0053】

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタ法を用いるスパッタ装置

や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ

法を用いるスパッタ装置がある。

【0054】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分

とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に

基板にも電圧をかけるバイアススパッタ法もある。

【0055】

次いで、酸化物半導体層の脱水化または脱水素化を行う。脱水化または脱水素化を行う第

1の加熱処理の温度は、400℃以上であって750℃未満、好ましくは425℃以上と

する。なお、425℃以上であれば熱処理時間は1時間以下でよいが、425℃未満であ

れば加熱処理時間は、1時間よりも長時間行うこととする。ここでは、加熱処理装置の一

つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理

を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化

物半導体層を得る。本実施の形態では、酸化物半導体層の脱水化または脱水素化を行う加

熱温度Tから、再び水が入らないような十分な温度まで同じ炉を用い、具体的には加熱温

度Tよりも100℃以上下がるまで窒素雰囲気下で徐冷する。また、窒素雰囲気に限定さ

れず、希ガス(ヘリウム、ネオン、アルゴン等)雰囲気下において脱水化または脱水素化

を行う。

【0056】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱

輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas

Rapid Thermal Anneal)装置、LRTA(Lamp Rapid

Thermal Anneal)装置等のRTA(Rapid Thermal An

neal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライ

ドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧

水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置

である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、ア

ルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と殆ど反応しない

不活性気体が用いられる。

【0057】

酸化物半導体層を400℃以上750℃未満の温度で熱処理することで、酸化物半導体層

の脱水化、脱水素化が図られ、その後の水(H2O)の再含浸を防ぐことができる。

【0058】

また、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガス

に、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、

またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上

、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ま

しくは0.1ppm以下)とすることが好ましい。

【0059】

なお、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層

が結晶化し、微結晶膜または多結晶膜となる場合もある。例えば、結晶化率が90%以上

、または80%以上の微結晶の酸化物半導体膜となる場合もある。また、第1の加熱処理

の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半

導体膜となる場合もある。

【0060】

酸化物半導体層は、脱水化または脱水素化のための第1の加熱処理後に酸素欠乏型となり

、低抵抗化する。第1の加熱処理後の酸化物半導体層は、成膜直後の酸化物半導体膜より

もキャリア濃度が高まり、好ましくは1×1018/cm3以上のキャリア濃度を有する

酸化物半導体層となる。

【0061】

次いで、第2のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチング

により不要な部分を除去して酸化物半導体でなる第1の酸化物半導体層103A、第2の

酸化物半導体層103Bを形成する。なお第1の酸化物半導体層103A、第2の酸化物

半導体層103Bへの第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半

導体膜に行うこともできる。この際のエッチング方法としてウェットエッチングまたはド

ライエッチングを用いる。この段階での断面図を図2(A)に示す。

【0062】

なおゲート絶縁膜113の成膜後に、図2(A)に示すような、ゲート絶縁膜113に容

量電極101Bに達する開口部121を形成し、後に形成する配線と容量電極との接続を

するようにしてもよい。

【0063】

次に、酸化物半導体層上に金属材料からなる導電膜をスパッタ法や真空蒸着法で形成する

。導電膜の材料としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または

上述した元素を成分とする合金か、上述した元素を組み合わせた合金等が挙げられる。ま

た、200℃〜600℃の熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に

持たせることが好ましい。Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があ

るので耐熱性導電性材料と組み合わせて形成する。Alと組み合わせる耐熱性導電性材料

としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo

)、クロム(Cr)、ネオジム(Nd)、Sc(スカンジウム)から選ばれた元素、また

は上述した元素を成分とする合金か、上述した元素を組み合わせた合金、または上述した

元素を成分とする窒化物で形成する。

【0064】

ここでは、導電膜としてチタン膜の単層構造とする。また、導電膜は、2層構造としても

よく、アルミニウム膜上にチタン膜を積層してもよい。また、導電膜としてTi膜と、そ

のTi膜上に重ねてNdを含むアルミニウム(Al−Nd)膜を積層し、さらにその上に

Ti膜を成膜する3層構造としてもよい。導電膜は、シリコンを含むアルミニウム膜の単

層構造としてもよい。

【0065】

次に、第3のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングに

より不要な部分を除去して導電膜でなる第2の配線102A、第3の配線102B、電源

線104A、及び第4の配線104Bを形成する。この際のエッチング方法としてウェッ

トエッチングまたはドライエッチングを用いる。例えば、アンモニア過水(31重量%過

酸化水素水:28重量%アンモニア水:水=5:2:2)を用いたウェットエッチングに

より、Ti膜の導電膜をエッチングして第2の配線102A、第3の配線102B、電源

線104A、及び第4の配線104Bを選択的にエッチングして第1の酸化物半導体層1

03A、第2の酸化物半導体層103Bを残存させることができる。

【0066】

また、エッチング条件にもよるが第3のフォトリソグラフィー工程において酸化物半導体

層の露出領域がエッチングされる場合がある。その場合、第2の配線102A及び第3の

配線102Bに挟まれる領域の第1の酸化物半導体層103Aは、第1の配線101A上

で第2の配線102A及び第3の配線102Bと重なる領域の酸化物半導体層に比べ、膜

厚が薄くなる。また、電源線104A及び第4の配線104Bに挟まれる領域の第2の酸

化物半導体層103Bは、容量電極101B上で電源線104A及び第4の配線104B

と重なる領域の酸化物半導体層に比べ、膜厚が薄くなる。

【0067】

次いで、ゲート絶縁膜113、第1の酸化物半導体層103A、第2の酸化物半導体層1

03B、第2の配線102A、第3の配線102B、電源線104A、第4の配線104

B上に酸化物絶縁層114を形成する。この段階で、第1の酸化物半導体層103A、及

び第2の酸化物半導体層103Bの一部は、酸化物絶縁層114と接する。なお、ゲート

絶縁膜113を挟んで第1の配線101Aと重なる第1の酸化物半導体層103Aの領域

、及び容量電極101Bと重なる第2の酸化物半導体層103Bの領域がチャネル形成領

域となる。

【0068】

酸化物絶縁層114は、少なくとも1nm以上の膜厚とし、スパッタリング法など、酸化

物絶縁層に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。

本実施の形態では、スパッタリング法を用いて酸化物絶縁層として酸化珪素膜を成膜する

。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃

とする。酸化珪素膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰

囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素混合雰囲気下にお

いて行うことができる。また、ターゲットとして酸化珪素ターゲットまたは珪素ターゲッ

トを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び希ガス雰囲気下

でスパッタリング法により酸化珪素膜を形成することができる。低抵抗化した酸化物半導

体層に接して形成する酸化物絶縁層は、水分や、水素イオンや、OH−などの不純物を含

まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化

珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用

いる。なお、スパッタ法で成膜した酸化物絶縁層は特に緻密であり、接する層へ不純物が

拡散する現象を抑制する保護膜として単層であっても利用することができる。また、リン

(P)や硼素(B)をドープしたターゲットを用い、酸化物絶縁層にリン(P)や硼素(

B)を添加することもできる。

【0069】

本実施の形態では、純度が6Nであり、柱状多結晶Bドープの珪素ターゲット(抵抗値0

.01Ωcm)を用い、基板とターゲットとの間の距離(T−S間距離)を89mm、圧

力0.4Pa、直流(DC)電源6kW、酸素(酸素流量比率100%)雰囲気下でパル

スDCスパッタ法により成膜する。膜厚は300nmとする。

【0070】

なお、酸化物絶縁層114は酸化物半導体層のチャネル形成領域となる領域上に接して設

けられ、チャネル保護層としての機能も有する。

【0071】

次いで、第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上3

50℃以下)を不活性ガス雰囲気下、または窒素ガス雰囲気下で行ってもよい。例えば、

窒素雰囲気下で250℃、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、第

1の酸化物半導体層103A、及び第2の酸化物半導体層103Bの一部が酸化物絶縁層

114と接した状態で加熱される。

【0072】

第1の加熱処理で低抵抗化された第1の酸化物半導体層103A、及び第2の酸化物半導

体層103Bが酸化物絶縁層114と接した状態で第2の加熱処理が施されると、酸化物

絶縁層114が接した領域が酸素過剰な状態となる。その結果、第1の酸化物半導体層1

03A、及び第2の酸化物半導体層103Bの酸化物絶縁層114が接する領域から、第

1の酸化物半導体層103A、及び第2の酸化物半導体層103Bの深さ方向に向けて、

I型化(高抵抗化)する。

【0073】

次いで、酸化物絶縁層114に第4のフォトリソグラフィー工程により、開口部122を

形成する。この段階での断面図を図2(B)に示す。

【0074】

次いで、第4の配線104Bと接続するための透光性を有する導電膜を成膜する。透光性

を有する導電膜の材料としては、酸化インジウム(In2O3)や酸化インジウム酸化ス

ズ合金(In2O3―SnO2、ITOと略記する)などをスパッタ法や真空蒸着法など

を用いて成膜する。透光性を有する導電膜の他の材料として、窒素を含ませたAl−Zn

−O系膜、即ちAl−Zn−O−N系膜や、窒素を含ませたZn−O系膜や、窒素を含ま

せたSn−Zn−O系膜を用いてもよい。なお、Al−Zn−O−N系膜の亜鉛の組成比

(原子%)は、47原子%以下とし、膜中のアルミニウムの組成比(原子%)より大きく

、膜中のアルミニウムの組成比(原子%)は、膜中の窒素の組成比(原子%)より大きい

。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特にITOのエ

ッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム

酸化亜鉛合金(In2O3―ZnO)を用いても良い。

【0075】

なお、透光性を有する導電膜の組成比の単位は原子%とし、電子線マイクロアナライザー

(EPMA:Electron Probe X−ray MicroAnalyzer

)を用いた分析により評価するものとする。

【0076】

次に、第5のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングに

より不要な部分を除去して発光素子の一方の電極を形成する。発光素子は一対の電極(陽

極及び陰極)の間に発光層を具備する構成であり、電極上に発光層を構成する素子を積層

して形成する。そこで、発光素子の一方の電極を発光素子105という。

【0077】

次いで、第1の配線101A、第2の配線102A、第3の配線102B、第4の配線1

04B、第1の酸化物半導体層103A、第2の酸化物半導体層103B、電源線104

A、及び容量電極101B上には、発光素子を画素毎に分離するための隔壁106が設け

られる。なお隔壁106の内側に第4の配線104Bに接続される発光素子105が設け

られることとなる。この段階での断面図を図2(C)に示す。

【0078】

こうして、第1の薄膜トランジスタ107A及び第2の薄膜トランジスタ107Bを有す

る画素を作製することができる。そして、これらを個々の画素に対応してマトリクス状に

配置して画素部を構成することによりアクティブマトリクス型の発光表示装置を作製する

ことができる。

【0079】

図1、図2で説明した本実施の形態の構成による利点について図3(A)、(B)を用い

て詳細に説明を行う。

【0080】

図3(A)、(B)は、図1(A)の上面図における酸化物半導体層近傍の拡大図である

。また、図3(A)における第1の酸化物半導体層103Aの幅(図3(A)中、W1)

を大きくとった図が、図3(B)の第1の酸化物半導体層103Aの幅(図3(B)中、

W2)とした図に対応する。

【0081】

本実施の形態における図1(A)での画素の上面図では、図3(A)、(B)で示すよう

に、第1の配線101Aより配線を分岐させることなく、第1の配線101A上に第1の

酸化物半導体層103Aを設けている。酸化物半導体層での第2の配線102Aと第3の

配線102Bとの間に形成されるチャネル領域が第1の配線101A上の重畳する領域に

形成されることとなる。第1の酸化物半導体層103Aはチャネル領域に光が照射される

ことでTFT特性にばらつきが生じることもあるため、第1の配線101Aより分岐した

配線により確実に遮光を行う必要があり、画素の開口率を下げる要因ともなっていた。本

実施の形態の構成である第1の配線101A上に重畳するように酸化物半導体層を設け、

第1の配線101Aより分岐した配線を形成しないことで、開口率の向上を図ることがで

きる。

【0082】

また、薄膜トランジスタの半導体層として、透光性を有する酸化物半導体層を用いること

により、酸化物半導体層が第1の配線101Aと重畳する領域から、設計の位置よりもず

れた領域に形成され、発光素子105と重畳することとなっても、開口率を低減すること

なく、表示を行うことができる。

【0083】

所定のサイズより大きなパターンで酸化物半導体層を形成することで、設計の位置から多

少ずれた箇所に酸化物半導体層が形成されたとしても、動作不良及び開口率の低下といっ

たことなく良好な表示を行うことができる。そのため、発光表示装置のアクティブマトリ

クス基板が作りやすくなり、歩留まりの向上を図ることができるといえる。

【0084】

次いで、酸化物半導体層を用いた薄膜トランジスタを用いることにより、保持容量を削減

する際の具体的な上面図の一例について示す。

【0085】

酸化物半導体を有する薄膜トランジスタでは、ゲートにトランジスタを非導通状態とする

電圧を印加した際にトランジスタに流れる電流(以下、リーク電流という)が0.1pA

以下であるのに対し、アモルファスシリコンを有する薄膜トランジスタでは数100nA

程度となる。そのため、酸化物半導体を有する薄膜トランジスタでは、保持容量の縮小を

図ることができる。すなわち酸化物半導体を有する薄膜トランジスタが設けられる画素で

は、アモルファスシリコンを有する薄膜トランジスタが設けられる画素に比べ各素子のレ

イアウトの自由度を高めることが出来る。

【0086】

酸化物半導体層を有する薄膜トランジスタは、リーク電流が非常に小さいため、保持容量

を省略することも可能である。具体的に保持容量を省略した場合の上面図、及びその断面

図について図12(A)、(B)に示す。図12(A)に示す画素の上面図は、上記説明

した図1(A)での上面図において、容量線を省略した図に相当する。図12(A)に示

す上面図、図12(B)に示す断面図からもわかるように、酸化物半導体層を有する薄膜

トランジスタを用いることで、第2の薄膜トランジスタの配置によって、第3の配線10

2B等の引き回しを短くし、開口率を向上することができる。

【0087】

以上説明したように本実施の形態で示す構成とすることにより、酸化物半導体を用いた薄

膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。従っ

て、高精細な表示部を有する発光表示装置とすることができる。

【0088】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【0089】

(実施の形態2)

上記実施の形態とは別のTFTの構成の表示装置の画素を構成する例を以下に説明する。

【0090】

実施の形態1の構成とは異なる、画素の上面図について図4(A)に示す。なお図4(A

)に示すTFTの構造は、ボトムゲート型構造であり、ゲートとなる配線から見てチャネ

ル領域となる酸化物半導体層の反対側に、TFTのソース電極及びドレイン電極となる配

線層を有する、いわゆる逆スタガ型の構成について示している。

【0091】

図4(A)に示す画素400は、走査線として機能する第1の配線401A、信号線とし

て機能する第2の配線402A、第1の酸化物半導体層403A、第2の酸化物半導体層

403B、電源線404A、容量電極401B、発光素子405を有する。また、第1の

酸化物半導体層403Aと容量電極401Bとを電気的に接続するための第3の配線40

2Bを有し、第1の薄膜トランジスタ407Aが構成される。また、第2の酸化物半導体

層403Bと発光素子405とを電気的に接続するための第4の配線404Bを有し、第

2の薄膜トランジスタ407Bが構成される。また第1の配線401A、第2の配線40

2A、第3の配線402B、第4の配線404B、第1の酸化物半導体層403A、第2

の酸化物半導体層403B、電源線404A、及び容量電極401B上には、発光素子を

画素毎に分離するための隔壁406が設けられる。なお隔壁406の内側に第4の配線4

04Bに接続される発光素子405が設けられることとなる。

【0092】

第1の配線401Aは第1の薄膜トランジスタ407Aのゲートとして機能する配線でも

ある。容量電極401Bは、第2の薄膜トランジスタ407Bのゲート及び保持容量の一

方の電極としてとして機能する配線でもある。第2の配線402Aは、第1の薄膜トラン

ジスタ407Aのソース電極またはドレイン電極の一方として機能する配線でもある。第

3の配線402Bは、第1の薄膜トランジスタ407Aのソース電極またはドレイン電極

の他方として機能する配線でもある。電源線404Aは、第2の薄膜トランジスタ407

Bのソース電極またはドレイン電極の一方、及び保持容量の他方の電極として機能する配

線でもある。第4の配線404Bは、第2の薄膜トランジスタ407Bのソース電極また

はドレイン電極の他方として機能する配線でもある。

【0093】

なお第1の配線401Aと、容量電極401Bとが同層から設けられ、第2の配線402

A、第3の配線402B、電源線404A、及び第4の配線404Bが同層から設けられ

る。また電源線404Aと容量電極401Bとは、一部重畳して設けられており、第2の

薄膜トランジスタ407Bの保持容量を形成している。なお、第1の薄膜トランジスタ4

07Aが有する第1の酸化物半導体層403Aは、第1の配線401A上にゲート絶縁膜

(図示せず)を介して設けられており、第1の酸化物半導体層403Aは第1の配線40

1A及び隔壁406が設けられた領域をはみ出て設けられている。

【0094】

また図4(B)には、図4(A)における一点鎖線A−A’、B−B’、C−C’間の断

面構造について示している。図4(B)に示す断面構造で、基板411上には、下地膜4

12を介して、ゲートである第1の配線401A、容量電極401Bが設けられている。

第1の配線401A、及び容量電極401Bを覆うように、ゲート絶縁膜413が設けら

れている。ゲート絶縁膜413上には、第1の酸化物半導体層403A、第2の酸化物半

導体層403Bが設けられている。第1の酸化物半導体層403A上には、第2の配線4

02A、第3の配線402B、第2の酸化物半導体層403B上には、電源線404A、

第4の配線404Bが設けられている。また、第1の酸化物半導体層403A、第2の酸

化物半導体層403B、第2の配線402A、第3の配線402B、電源線404A、及

び第4の配線404B上には、パッシベーション膜として機能する酸化物絶縁層414が

設けられている。第1の配線401A、第2の配線402A、第3の配線402B、第4

の配線404B、第1の酸化物半導体層403A、第2の酸化物半導体層403B、電源

線404A、及び容量電極401B上の酸化物絶縁層414上には、隔壁406が設けら

れている。また第4の配線404B上の酸化物絶縁層414には開口部が形成されており

、開口部において発光素子405の電極と第4の配線404Bとの接続がなされる。また

一点鎖線B−B’において、第3の配線402Bと容量電極401Bとが、ゲート絶縁膜

413に形成される開口部を介して接続されている。

【0095】

なお、図4(A)、(B)に示す画素は、実施の形態1の図1(A)、(B)での説明と

同様に、図7での基板700上にマトリクス状の複数の画素701として配置されるもの

である。図7に関する説明は実施の形態1と同様である。

【0096】

また、図4(B)に示す断面図は、図1(B)に示した断面図と同様であり、画素の作製

方法については実施の形態1における図2での説明と同様である。

【0097】

図4(A)、(B)で説明した本実施の形態の構成による利点について図5(A)、(B

)を用いて詳細に説明を行う。

【0098】

図5(A)、(B)は、図4(A)の上面図における酸化物半導体層近傍の拡大図である

。また、図5(A)における第1の酸化物半導体層403Aの幅(図5(A)中、W1)

を大きくとった図が、図5(B)の第1の酸化物半導体層403Aの幅(図5(B)中、

W2)とした図に対応する。

【0099】

本実施の形態における図4(A)での画素の上面図では、図5(A)、(B)で示すよう

に、第1の配線401Aより配線を分岐させることなく、第1の配線401A上に第1の

酸化物半導体層403Aを設けている。酸化物半導体層での第2の配線402Aと第3の

配線402Bとの間に形成されるチャネル領域が第1の配線401A上の重畳する領域に

形成されることとなる。加えて本実施の形態で第1の酸化物半導体層403Aは、第1の

配線401A上のゲート絶縁膜上を延在して第2の配線402A及び第3の配線402B

に接することとなる。

【0100】

第1の酸化物半導体層403Aはチャネル領域に光が照射されることでTFT特性にばら

つきが生じることもあるため、第1の配線401Aより分岐した配線により確実に遮光を

行う必要があり、画素の開口率を下げる要因ともなっていた。本実施の形態の構成である

第1の配線401A上に重畳するように酸化物半導体層を設け、第1の配線401Aより

分岐した配線を形成しない構成、及び第1の配線401A上のゲート絶縁膜上を延在して

第2の配線402A及び第3の配線402Bを第1の酸化物半導体層403Aに接する構

成で、開口率の向上を図ることができる。

【0101】

また、薄膜トランジスタの半導体層として、透光性を有する酸化物半導体層を用いること

により、酸化物半導体層が第1の配線401Aと重畳する領域から、設計の位置よりもず

れた領域に形成され、発光素子405と重畳することとなっても、開口率を低減すること

なく、表示を行うことができる。

【0102】

なお図4(A)で示す第1の配線401A上を延在する第2の配線402A及び第3の配

線402Bは、第1の配線401A上に重畳して設けられていればよい。また第2の配線

402A及び第3の配線402Bは、蛇行して(メアンダ状に)引き回されていてもよい

し、直線状に配線を設ける構成としてもよい。

【0103】

所定のサイズより大きなパターンで酸化物半導体層を形成することで、多少設計の位置よ

りもずれた箇所に酸化物半導体層が形成されたとしても、動作不良及び開口率の低下とい

ったことなく良好な表示を行うことができる。そのため、発光表示装置のアクティブマト

リクス基板が作りやすくなり、歩留まりの向上を図ることができるといえる。

【0104】

以上説明したように本実施の形態で示す構成とすることにより、酸化物半導体を用いた薄

膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。従っ

て、高精細な表示部を有する発光表示装置とすることができる。

【0105】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【0106】

(実施の形態3)

上記実施の形態とは別のTFTの構成の表示装置の画素を構成する例を以下に説明する。

【0107】

実施の形態2の構成とは異なる、画素の上面図及び断面図について図6(A)、(B)に

示す。なお図6(A)に示す上面図の構造は、図4(A)と同様であり、ここでは説明を

省略する。また図6(B)に示す断面図の構造が、図4(B)に示す断面図の構造と異な

る点は、第1の配線401Aと第2の配線402Aとの間に層間絶縁層601Aを設ける

構成とする点、及び第1の配線401Aと第3の配線402Bとの間に層間絶縁層601

Bを設ける構成とする点にある。

【0108】

第1の配線401A上に第2の配線402A及び第3の配線402Bを延在させて設ける

場合、ゲート絶縁膜413の膜厚によっては、第1の配線401Aと第2の配線402A

、第1の配線401Aと第3の配線402Bとの間、及び第1の配線401Aと電源線4

04Aの間に寄生容量が生じることとなる。そのため、図6(B)に示すように、層間絶

縁層601A、層間絶縁層601Bを設けることで寄生容量を低減し、誤動作等の不良を

低減することができる。

【0109】

以上説明したように本実施の形態で示す構成とすることにより、酸化物半導体を用いた薄

膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。また

本実施の形態では、上記実施の形態2の構成に加えて、寄生容量の低減を図ることができ

る。従って、高精細な表示部を有し、且つ誤動作を低減することのできる発光表示装置と

することができる。

【0110】

(実施の形態4)

本実施の形態では、表示素子である発光素子の構成について説明する。

【0111】

図9は、薄膜トランジスタに接続された発光素子の断面構造の一形態について示したも

のである。発光素子は、第1電極911、発光層を有するEL層913、第2電極914

が順に積層して設けられている。第1電極911または第2電極914の一方は陽極とし

て機能し、他方は陰極として機能する。発光素子は、陽極から注入される正孔及び陰極か

ら注入される電子がEL層に含まれる発光層で再結合して、発光する。発光素子の第1電

極911は、基板111上に形成された薄膜トランジスタ107Bに接続する。また、薄

膜トランジスタ107Bのソース又はドレインとなる一方の電極及び第1電極911を覆

うように隔壁106が設けられる。また、第1電極911上の隔壁106の開口部に、E

L層913が設けられ、EL層913や隔壁106を覆うように第2電極914が設けら

れる。なお、本実施の形態では、実施の形態1に示す薄膜トランジスタを用いて示したが

、他の実施の形態に示す薄膜トランジスタを用いることができる。

【0112】

第1電極911または第2電極914は、金属、合金、または電気伝導性化合物を用い

て形成する。

【0113】

例えば、第1電極911または第2電極914は、仕事関数の大きい(仕事関数が4.

0eV以上)金属、合金、電気伝導性化合物などを用いることできる。代表的には、酸化

インジウム−酸化スズ(ITO:Indium Tin Oxide)、珪素若しくは酸

化珪素を含有した酸化インジウム−酸化スズ、酸化インジウム−酸化亜鉛(IZO:In

dium Zinc Oxide)、酸化タングステン及び酸化亜鉛を含有した酸化イン

ジウム(IWZO)等の透光性を有する導電性金属酸化物層がある。

【0114】

また、第1電極911または第2電極914は、仕事関数の小さい(代表的には、仕事

関数が3.8eV以下)金属、合金、電気伝導性化合物などを用いることができる。代表

的には、元素周期表の第1族または第2族に属する元素、すなわちリチウムやセシウム等

のアルカリ金属、およびマグネシウム、カルシウム、ストロンチウム等のアルカリ土類金

属、およびこれらを含む合金(アルミニウム、マグネシウムと銀との合金、アルミニウム

とリチウムの合金)、ユーロピウム、イッテルビウム等の希土類金属およびこれらを含む

合金等がある。

【0115】

アルカリ金属、アルカリ土類金属、及びこれらを含む合金は、真空蒸着法、スパッタリ

ング法などを用いて形成する。また、銀ペーストなどをインクジェット法により吐出し焼

成して形成することも可能である。また、第1電極911および第2電極914は、単層

に限らず、積層して形成することもできる。

【0116】

なお、EL層で発光する光を外部に取り出すため、第1電極911または第2電極91

4のいずれか一方或いは両方を、EL層からの発光を透過するように形成する。第1電極

911のみが透光性を有する電極である場合、光は、矢印方向900に示すように第1電

極911を通って、信号線から入力されるビデオ信号に応じた輝度で基板111側から取

り出される。また、第2電極914のみが透光性を有する電極である場合、光は第2電極

914を通って信号線から入力されるビデオ信号に応じた輝度で封止基板916側から取

り出される。第1電極911および第2電極914がいずれも透光性を有する電極である

場合、光は第1電極911および第2電極914を通って、信号線から入力されるビデオ

信号に応じた輝度で基板111側及び封止基板916側の両方から取り出される。

【0117】

透光性を有する電極は、例えば、透光性を有する導電性金属酸化物を用いて形成するか

、或いは、銀、アルミニウム等を数nm乃至数十nmの厚さとなるように形成する。また

、膜厚を薄くした銀、アルミニウムなどの金属層と、透光性を有する導電性金属酸化物層

との積層構造とすることもできる。

【0118】

陽極として機能する第1電極911または第2電極914の一方は、仕事関数の大きい

(仕事関数4.0eV以上)金属、合金、電気伝導性化合物などを用いることが好ましい

。また、陰極として機能する第1電極911または第2電極914の他方は、仕事関数の

小さい(仕事関数3.8eV以下)金属、合金、電気伝導性化合物などを用いることが好

ましい。代表的には、アルカリ金属、アルカリ土類金属、及びこれらを含む合金や化合物

、並びに希土類金属を含む遷移金属を用いて形成することができる。

【0119】

EL層913は、発光層を有する。また、EL層913は、発光層のほかに、正孔注入

層、正孔輸送層、電子輸送層及び電子注入層を有してもよい。正孔輸送層は、陽極と発光

層の間に設けられる。また、正孔注入層は陽極と発光層との間、或いは陽極と正孔輸送層

との間に設けられる。一方、電子輸送層は、陰極と発光層との間に設けられる。電子注入

層は陰極と発光層との間、或いは陰極と電子輸送層との間に設けられる。なお、正孔注入

層、正孔輸送層、電子輸送層及び電子注入層は全ての層を設ける必要はなく、適宜求める

機能等に応じて選択して設ければよい。

【0120】

発光層は発光性の物質を含む。発光性の物質としては、例えば、蛍光を発光する蛍光性

化合物や燐光を発光する燐光性化合物を用いることができる。

【0121】

また、発光層は、発光性の物質をホスト材料に分散して形成できる。発光性の物質をホ

スト材料に分散して発光層を形成すると、発光物質同士が消光反応を引き起こす濃度消光

現象や、結晶化現象を抑制できる。

【0122】

発光性の物質が蛍光性化合物の場合には、ホスト材料に蛍光性化合物よりも一重項励起

エネルギー(基底状態と一重項励起状態とのエネルギー差)が大きい物質を用いることが

好ましい。また、燐光性化合物の場合には、ホスト材料に燐光性化合物よりも三重項励起

エネルギー(基底状態と三重項励起状態とのエネルギー差)が大きい物質を用いることが

好ましい。

【0123】

また、ホスト材料に分散する発光性の物質としては、上述した燐光性化合物や蛍光性化

合物を用いることができる。

【0124】

なお、発光層として、2種類以上のホスト材料と発光性の物質を用いてもよいし、2種

類以上の発光性の物質とホスト材料を用いてもよい。また、2種類以上のホスト材料及び

2種類以上の発光性の物質を用いてもよい。

【0125】

また、正孔注入層として、正孔輸送性の高い物質と電子受容性を示す物質を含む層を用

いることができる。正孔輸送性の高い物質と電子受容性を示す物質とを含む層は、キャリ

ア密度が高く、正孔注入性に優れている。また、正孔輸送性の高い物質と電子受容性を示

す物質とを含む層を、陽極として機能する電極に接する正孔注入層として用いることによ

り、陽極として機能する電極材料の仕事関数の大小に関わらず、様々な金属、合金、電気

伝導性化合物、およびこれらの混合物などを用いることができる。

【0126】

発光層、正孔注入層、正孔輸送層、電子輸送層及び電子注入層は、蒸着法、塗布法等に

より形成することができる。

【0127】

また、第2電極914及び隔壁106上にパッシベーション層915をスパッタリング

法やCVD法により形成してもよい。パッシベーション層915を設けることで、外部か

ら発光素子への水分や酸素の侵入による発光素子の劣化を低減することができる。さらに

は、パッシベーション層915及び封止基板916の空間に窒素を封入し、さらに乾燥剤

を配置してもよい。または、パッシベーション層915及び封止基板916の間を、透光

性を有し、且つ吸水性の高い有機樹脂で充填してもよい。

【0128】

発光素子が白色の発光を示す場合、カラーフィルター、又は色変換層などを、基板11

1または封止基板916に設けることによってフルカラー表示を行なうことができる。

【0129】

またコントラストを高めるため、基板111または封止基板916に偏光板又は円偏光

板を設けてもよい。

【0130】

本実施の形態の画素においても、上記実施の形態の構成を組み合わせることによって、

酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を

図ることができる。

【0131】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可

能である。

【0132】

(実施の形態5)

本実施の形態においては、発光表示装置に適用できる画素の回路構成について説明する。

【0133】

図8は、発光表示装置に適用できる画素構成の一例を示す図である。画素800は、第1

の薄膜トランジスタ801、第2の薄膜トランジスタ802、容量素子803、発光素子

804を有している。第1の薄膜トランジスタ801のゲートは第1の配線805と電気

的に接続される。第1の薄膜トランジスタ801の第1端子は第2の配線806と電気的

に接続される。第1の薄膜トランジスタ801の第2端子は容量素子803の第1電極及

び第2の薄膜トランジスタ802のゲートに電気的に接続される。容量素子803の第2

電極は、電源線807と電気的に接続される。第2の薄膜トランジスタ802の第1端子

は、電源線807と電気的に接続される。第2の薄膜トランジスタ802の第2端子は、

発光素子804の一方の電極と電気的に接続される。

【0134】

第1の配線805に関しては、上記実施の形態1で説明した第1の配線101Aの機能と

同様である。第2の配線806に関しては、上記実施の形態1で説明した第2の配線10

2Aの機能と同様である。電源線807に関しては、上記実施の形態1で説明した電源線

104Aの機能と同等である。発光素子804の構成に関しては、上記実施の形態4で説

明した発光素子の構成と同等である。

【0135】

本実施の形態の画素においても、上記実施の形態の構成を組み合わせることによって、酸

化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を図

ることができる。

【0136】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【0137】

(実施の形態6)

本実施の形態においては、上記実施の形態で説明した発光表示装置を具備する電子機器の

例について説明する。

【0138】

図10(A)は携帯型遊技機であり、筐体9630、表示部9631、スピーカ9633

、操作キー9635、接続端子9636、記録媒体読込部9672、等を有することがで

きる。図10(A)に示す携帯型遊技機は、記録媒体に記録されているプログラム又はデ

ータを読み出して表示部に表示する機能、他の携帯型遊技機と無線通信を行って情報を共

有する機能、等を有することができる。なお、図10(A)に示す携帯型遊技機が有する

機能はこれに限定されず、様々な機能を有することができる。

【0139】

図10(B)はデジタルカメラであり、筐体9630、表示部9631、スピーカ963

3、操作キー9635、接続端子9636、シャッターボタン9676、受像部9677

、等を有することができる。図10(B)に示すテレビ受像機能付きデジタルカメラは、

静止画を撮影する機能、動画を撮影する機能、撮影した画像を自動または手動で補正する

機能、アンテナから様々な情報を取得する機能、撮影した画像、又はアンテナから取得し

た情報を保存する機能、撮影した画像、又はアンテナから取得した情報を表示部に表示す

る機能、等を有することができる。なお、図10(B)に示すテレビ受像機能付きデジタ

ルカメラが有する機能はこれに限定されず、様々な機能を有することができる。

【0140】

図10(C)はテレビ受像器であり、筐体9630、表示部9631、スピーカ9633

、操作キー9635、接続端子9636、等を有することができる。図10(C)に示す

テレビ受像機は、テレビ用電波を処理して画像信号に変換する機能、画像信号を処理して

表示に適した信号に変換する機能、画像信号のフレーム周波数を変換する機能、等を有す

ることができる。なお、図10(C)に示すテレビ受像機が有する機能はこれに限定され

ず、様々な機能を有することができる。

【0141】

図11(A)はコンピュータであり、筐体9630、表示部9631、スピーカ9633

、操作キー9635、接続端子9636、外部接続ポート9680、ポインティングデバ

イス9681等を有することができる。図11(A)に示すコンピュータは、様々な情報

(静止画、動画、テキスト画像など)を表示部に表示する機能、様々なソフトウェア(プ

ログラム)によって処理を制御する機能、無線通信又は有線通信などの通信機能、通信機

能を用いて様々なコンピュータネットワークに接続する機能、通信機能を用いて様々なデ

ータの送信又は受信を行う機能、等を有することができる。なお、図11(A)に示すコ

ンピュータが有する機能はこれに限定されず、様々な機能を有することができる。

【0142】

次に、図11(B)は携帯電話であり、筐体9630、表示部9631、スピーカ963

3、操作キー9635、マイクロフォン9638等を有することができる。図11(B)

に示した携帯電話は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、

カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又

は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を

有することができる。なお、図11(B)に示した携帯電話が有する機能はこれに限定さ

れず、様々な機能を有することができる。

【0143】

次に、図11(C)は電子ペーパー(E−bookともいう)であり、筐体9630、表

示部9631、操作キー9635等を有することができる。図11(C)に示した電子ペ

ーパーは、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー

、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する

機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有すること

ができる。なお、図11(C)に示した電子ペーパーが有する機能はこれに限定されず、

様々な機能を有することができる。

【0144】

本実施の形態において述べた電子機器は、表示部を構成する複数の画素において、開口率

の向上を図ることができる。

【0145】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【符号の説明】

【0146】

100 画素

103 酸化物半導体層

105 発光素子

106 隔壁

111 基板

112 下地膜

113 ゲート絶縁膜

114 酸化物絶縁層

121 開口部

122 開口部

400 画素

405 発光素子

406 隔壁

411 基板

412 下地膜

413 ゲート絶縁膜

414 酸化物絶縁層

700 基板

701 画素

702 画素部

703 走査線駆動回路

704 信号線駆動回路

705 電源回路

800 画素

801 薄膜トランジスタ

802 薄膜トランジスタ

803 容量素子

804 発光素子

805 配線

806 配線

807 電源線

900 矢印方向

911 電極

912 隔壁

913 EL層

914 電極

915 パッシベーション層

916 封止基板

101A 配線

101B 容量電極

102A 配線

102B 配線

103A 酸化物半導体層

103B 酸化物半導体層

104A 電源線

104B 配線

107A 薄膜トランジスタ

107B 薄膜トランジスタ

401A 配線

401B 容量電極

402A 配線

402B 配線

403A 酸化物半導体層

403B 酸化物半導体層

404A 電源線

404B 配線

407A 薄膜トランジスタ

407B 薄膜トランジスタ

601A 層間絶縁層

601B 層間絶縁層

9630 筐体

9631 表示部

9633 スピーカ

9635 操作キー

9636 接続端子

9638 マイクロフォン

9672 記録媒体読込部

9676 シャッターボタン

9677 受像部

9680 外部接続ポート

9681 ポインティングデバイス

【技術分野】

【0001】

本発明は、発光表示装置に関する。また当該発光表示装置を具備する電子機器に関する。

【背景技術】

【0002】

液晶表示装置に代表されるように、ガラス基板等の平板に形成される薄膜トランジスタは

、アモルファスシリコン、多結晶シリコンによって作製されている。アモルファスシリコ

ンを用いた薄膜トランジスタは、電界効果移動度が低いもののガラス基板の大面積化に対

応することができ、一方、結晶シリコンを用いた薄膜トランジスタは電界効果移動度が高

いものの、レーザアニール等の結晶化工程が必要であり、ガラス基板の大面積化には必ず

しも適応しないといった特性を有している。

【0003】

これに対し、酸化物半導体を用いて薄膜トランジスタを作製し、電子デバイスや光デバイ

スに応用する技術が注目されている。例えば、酸化物半導体膜として酸化亜鉛、In−G

a−Zn−O系酸化物半導体を用いて薄膜トランジスタを作製し、発光表示装置のスイッ

チング素子などに用いる技術が特許文献1で開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−31750号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

酸化物半導体をチャネル領域に用いた薄膜トランジスタは、アモルファスシリコンをチャ

ネル領域に用いた薄膜トランジスタよりも高い電界効果移動度が得られている。このよう

な酸化物半導体を用いて形成した薄膜トランジスタを具備する画素は、ELディスプレイ

等の発光表示装置への応用が期待される。また、3Dディスプレイ、4k2kディスプレ

イ等、さらなる付加価値のついた発光表示装置では、画素一つあたりの面積が小さくなる

ことが予想される一方で、開口率の向上した画素を有する発光表示装置が望まれる。

【0006】

そこで、本発明は、酸化物半導体を用いた薄膜トランジスタを具備する画素において、開

口率の向上を図ることのできる発光表示装置を提供することを課題の一とする。

【課題を解決するための手段】

【0007】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第

1の配線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は

、第1の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層

とが重畳して設けられる発光表示装置である。

【0008】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線と、信号線として機能する第2の配線に電気的に接続

されており、薄膜トランジスタは、第1の配線上にゲート絶縁膜を介して設けられた酸化

物半導体層を有し、酸化物半導体層は、第1の配線が設けられた領域をはみ出て設けられ

ており、第2の配線は、第1の配線上のゲート絶縁膜上を延在して酸化物半導体層上に接

しており、発光素子と、酸化物半導体層とが重畳して設けられる発光表示装置である。

【0009】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線と、信号線として機能する第2の配線に電気的に接続

されており、薄膜トランジスタは、第1の配線上にゲート絶縁膜を介して設けられた酸化

物半導体層を有し、酸化物半導体層は、第1の配線が設けられた領域をはみ出て設けられ

ており、第2の配線は、第1の配線上のゲート絶縁膜及びゲート絶縁膜上の層間絶縁層上

を延在して酸化物半導体層上に接しており、発光素子と、酸化物半導体層とが重畳して設

けられる発光表示装置である。

【0010】

本発明の一態様は、第1の薄膜トランジスタ、第2の薄膜トランジスタ、及び発光素子を

有する複数の画素を有し、画素は、走査線として機能する第1の配線と、信号線として機

能する第2の配線に電気的に接続されており、第1の薄膜トランジスタは、第1の配線上

にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1の配

線が設けられた領域をはみ出て設けられており、第2の配線は、第1の配線上のゲート絶

縁膜上を延在して酸化物半導体層上に接し、酸化物半導体層に接し、且つ第1の薄膜トラ

ンジスタと第2の薄膜トランジスタとの電気的な接続をとるための第3の配線は、第1の

配線上のゲート絶縁膜上を延在して設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる発光表示装置である。

【0011】

本発明の一態様は、薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は

、走査線として機能する第1の配線と、信号線として機能する第2の配線に電気的に接続

されており、薄膜トランジスタは、第1の配線上にゲート絶縁膜を介して設けられた酸化

物半導体層を有し、酸化物半導体層は、第1の配線が設けられた領域をはみ出て設けられ

ており、第2の配線は、第1の配線上のゲート絶縁膜及びゲート絶縁膜上の層間絶縁層上

を延在して酸化物半導体層上に接し、酸化物半導体層に接し、且つ第1の薄膜トランジス

タと第2の薄膜トランジスタとの電気的な接続をとるための第3の配線は、第1の配線上

のゲート絶縁膜及びゲート絶縁膜上の層間絶縁層上を延在して設けられており、発光素子

と、酸化物半導体層とが重畳して設けられる発光表示装置である。

【発明の効果】

【0012】

酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を

図ることができる。従って、高精細な表示部を有する発光表示装置とすることができる。

【図面の簡単な説明】

【0013】

【図1】発光表示装置について説明する上面図及び断面図。

【図2】発光表示装置について説明する断面図。

【図3】発光表示装置について説明する上面図。

【図4】発光表示装置について説明する上面図及び断面図。

【図5】発光表示装置について説明する上面図。

【図6】発光表示装置について説明する上面図及び断面図。

【図7】発光表示装置について説明する回路図。

【図8】発光表示装置について説明する回路図。

【図9】発光表示装置について説明する断面図。

【図10】電子機器について説明する図。

【図11】電子機器について説明する図。

【図12】発光表示装置について説明する上面図及び断面図。

【発明を実施するための形態】

【0014】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通

して用い、その繰り返しの説明は省略する。

【0015】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、又は領域は、明瞭

化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0016】

なお、本明細書にて用いる第1、第2、第3、等の用語は、構成要素の混同を避けるため

に付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「

第2の」又は「第3の」などと適宜置き換えて説明することができる。

【0017】

(実施の形態1)

本実施の形態では、一例として、薄膜トランジスタ(以下、TFTともいう)及び当該T

FTに接続された発光素子を有する画素について示し、発光表示装置の説明をする。なお

画素とは、表示装置の各画素に設けられた各素子、例えば薄膜トランジスタ、発光素子、

及び配線等の電気的な信号により表示を制御するための素子で構成される素子群、のこと

をいう。なお画素は、カラーフィルター等を含むものであっても良く、一画素によって、

明るさを制御できる色要素一つ分としてもよい。よって、一例として、RGBの色要素か

らなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素と

の三画素から構成されるものとなり、複数の画素によって画像を得ることができるものと

なる。

【0018】

なお発光素子は一対の電極(陽極及び陰極)の間に発光層を具備する構成であり、電極上

に発光層を構成する素子を積層して形成される。本明細書中で発光素子の一方の電極を図

中で示す際には、発光素子ということもある。

【0019】

なお、AとBとが接続されている、と記載する場合は、AとBとが電気的に接続されて

いる場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは

、電気的作用を有する対象物であるとする。具体的には、トランジスタをはじめとするス

イッチング素子を介してAとBとが接続され、該スイッチング素子の導通によって、Aと

Bとが概略同電位となる場合や、抵抗素子を介してAとBとが接続され、該抵抗素子の両

端に発生する電位差が、AとBとを含む回路の動作に影響しない程度となっている場合な

ど、回路動作を考えた場合、AとBとの間の部分を同じノードとして捉えて差し支えない

状態である場合を表す。

【0020】

図1(A)には、画素の上面図を示す。なお図1(A)に示すTFTの構造は、ボトムゲ

ート型構造であり、ゲートとなる配線から見てチャネル領域となる酸化物半導体層の反対

側に、TFTのソース電極及びドレイン電極となる配線層を有する、いわゆる逆スタガ型

の構成について示している。

【0021】

図1(A)に示す画素100は、走査線として機能する第1の配線101A、信号線とし

て機能する第2の配線102A、第1の酸化物半導体層103A、第2の酸化物半導体層

103B、電源線104A、容量電極101B、発光素子105を有する。また図1(A

)に示す画素100は、第1の酸化物半導体層103Aと容量電極101Bとを電気的に

接続するための第3の配線102Bを有し、第1の薄膜トランジスタ107Aが構成され

る。また図1(A)に示す画素100は、第2の酸化物半導体層103Bと発光素子10

5とを電気的に接続するための第4の配線104Bを有し、第2の薄膜トランジスタ10

7Bが構成される。

【0022】

第1の配線101A、第2の配線102A、第3の配線102B、第4の配線104B、

第1の酸化物半導体層103A、第2の酸化物半導体層103B、電源線104A、及び

容量電極101B上には、発光素子を画素毎に分離するための隔壁106が設けられる。

なお隔壁106の内側に第4の配線104Bに接続される発光素子105が設けられるこ

ととなる。

【0023】

第1の配線101Aは第1の薄膜トランジスタ107Aのゲートとして機能する配線でも

ある。容量電極101Bは第2の薄膜トランジスタ107Bのゲート、及び容量素子の一

方の電極として機能する配線でもある。第2の配線102Aは、第1の薄膜トランジスタ

107Aのソース電極またはドレイン電極の一方として機能する配線でもある。第3の配

線102Bは、第1の薄膜トランジスタ107Aのソース電極またはドレイン電極の他方

として機能する配線でもある。電源線104Aは、第2の薄膜トランジスタ107Bのソ

ース電極またはドレイン電極の一方、及び容量素子の他方の電極として機能する配線でも

ある。第4の配線104Bは、第2の薄膜トランジスタ107Bのソース電極またはドレ

イン電極の他方として機能する配線でもある。

【0024】

なお第1の配線101Aと、容量電極101Bとが同層から設けられ、第2の配線102

A、第3の配線102B、電源線104A、及び第4の配線104Bが同層から設けられ

る。また電源線104Aと容量電極101Bとは、一部重畳して設けられており、第2の

薄膜トランジスタ107Bの保持容量を形成している。

【0025】

なお、第1の薄膜トランジスタ107Aが有する第1の酸化物半導体層103Aは、第1

の配線101A上にゲート絶縁膜(図示せず)を介して設けられている。第1の酸化物半

導体層103Aは第1の配線101Aが設けられた領域及び隔壁106をはみ出て設けら

れている。

【0026】

なおAがBよりはみ出ているとは、積層されたA、Bに着目して上面図をみた場合に、A

、Bの端部が一致せず、AがBの端部より外側に延在していることをいう。

【0027】

なお第1の薄膜トランジスタ107A、第2の薄膜トランジスタ107Bの他に、複数の

薄膜トランジスタを具備する構成としてもよい。なお第1の薄膜トランジスタ107Aは

、当該第1の薄膜トランジスタ107Aを具備する画素を選択するための機能を有し、選

択トランジスタともいう。また第2の薄膜トランジスタ107Bは、当該第2の薄膜トラ

ンジスタ107Bを有する画素の発光素子105に流す電流を制御するための機能を有し

、駆動トランジスタともいう。

【0028】

また図1(B)には、図1(A)における一点鎖線A−A’、B−B’、C−C’間の断

面構造について示している。図1(B)に示す断面構造で、基板111上には、下地膜1

12を介して、ゲートである第1の配線101A、容量電極101Bが設けられている。

第1の配線101A、及び容量電極101Bを覆うように、ゲート絶縁膜113が設けら

れている。ゲート絶縁膜113上には、第1の酸化物半導体層103A、第2の酸化物半

導体層103Bが設けられている。第1の酸化物半導体層103A上には、第2の配線1

02A、第3の配線102B、第2の酸化物半導体層103B上には、電源線104A、

第4の配線104Bが設けられている。また、第1の酸化物半導体層103A、第2の酸

化物半導体層103B、第2の配線102A、第3の配線102B、電源線104A、及

び第4の配線104B上には、パッシベーション膜として機能する酸化物絶縁層114が

設けられている。第1の配線101A、第2の配線102A、第3の配線102B、第4

の配線104B、第1の酸化物半導体層103A、第2の酸化物半導体層103B、電源

線104A、及び容量電極101B上の酸化物絶縁層114上には、隔壁106が設けら

れている。また第4の配線104B上の酸化物絶縁層114には開口部が形成されており

、開口部において発光素子105の電極と第4の配線104Bとの接続がなされる。また

一点鎖線B−B’において、第3の配線102Bと容量電極101Bとが、ゲート絶縁膜

113に形成される開口部を介して接続されている。

【0029】

なお、図1(A)、(B)に示す画素は、図7に示す基板700上の複数の画素701の

ように、マトリクス状に配置されるものである。図7では、基板700上には、画素部7

02、走査線駆動回路703、及び信号線駆動回路704を有する構成について示してい

る。画素701は、走査線駆動回路703に接続された第1の配線101Aによって供給

される走査信号により、各行ごとに選択状態か、非選択状態かが決定される。また走査信

号によって選択されている画素701は、信号線駆動回路704に接続された第2の配線

102Aによって、ビデオ電圧(画像信号、ビデオ信号、ビデオデータともいう)が供給

される。また、画素701には基板700の外部に設けられた電源回路705より延在し

て設けられる電源線104Aに接続される。

【0030】

図7では、走査線駆動回路703、信号線駆動回路704が基板700上に設けられる構

成について示したが、走査線駆動回路703または信号線駆動回路704のいずれか一が

基板700上に設けられる構成としてもよい。また画素部702のみを基板700上に設

ける構成としても良い。また図7では、電源回路705が基板700の外部に設けられる

構成について示したが基板700上に設けられる構成でもよい。

【0031】

図7で画素部702には、複数の画素701がマトリクス状に配置(ストライプ配置)す

る例について示している。なお、画素701は必ずしもマトリクス状に配置されている必

要はなく、例えば、画素701をデルタ配置、またはベイヤー配置としてもよい。また画

素部702における表示方式はプログレッシブ方式、インターレース方式のいずれかを用

いることができる。なお、カラー表示する際に画素で制御する色要素としては、RGB(

Rは赤、Gは緑、Bは青)の三色に限定されず、それ以上でもよく、例えば、RGBW(

Wは白)、又はRGBに、イエロー、シアン、マゼンタなどを一色以上追加したものなど

がある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。

【0032】

図7において、第1の配線101A、第2の配線102A、及び電源線104Aは画素の

行方向及び列方向の数に応じて示している。なお、第1の配線101A、第2の配線10

2A、及び電源線104Aは、画素を構成するサブ画素(副画素、サブピクセルともいう

)の数、または画素内のトランジスタの数に応じて、本数を増やす構成としてもよい。ま

た画素間で第1の配線101A、第2の配線102A、及び電源線104Aを共有して画

素701を駆動する構成としても良い。

【0033】

なお、図1(A)ではTFTの形状を、第2の配線102Aが矩形状であるものとして示

しているが、第3の配線102Bを囲む形状(具体的には、U字型またはC字型)とし、

キャリアが移動する領域の面積を増加させ、流れる電流量を増やす構成としてもよい。

【0034】

なお、第1の薄膜トランジスタ107Aとなる領域以外の第1の配線101Aの幅は、部

分的に細くなるよう小さくとってもよい。第1の配線の幅を小さくすることにより、画素

の開口率の向上を図ることができる。

【0035】

なお開口率とは、単位面積に対し、光が透過する領域の面積を表したものである。従って

、光を透過しない部材が占める領域が広くなると、開口率が低下し、光を透過する部材が

占める領域が広くなると開口率が向上することとなる。発光表示装置では、隔壁の内側に

設けられる発光素子が占める領域に光を透過しない配線等が重畳しないようにすること、

薄膜トランジスタのサイズを小さくすることで開口率が向上することとなる。

【0036】

なお、薄膜トランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの

端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、

ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、

ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれが

ソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレイ

ンとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一

例としては、それぞれを第1端子、第2端子と表記する場合がある。あるいは、それぞれ

を第1電極、第2電極と表記する場合がある。あるいは、第1領域、第2領域と表記する

場合がある。

【0037】

次に図1(A)、(B)に示した上面図及び断面図をもとに、画素の作製方法について図

2を用いて説明する。

【0038】

まず、透光性を有する基板111にはガラス基板を用いることができる。なお基板111

上に基板111からの不純物の拡散の防止、または基板111上に設ける各素子との密着

性を向上するための下地膜112を設ける構成を示している。なお下地膜112は、必ず

しも設ける必要はない。

【0039】

次いで、導電層を基板111全面に成膜した後、第1のフォトリソグラフィー工程を行い

、レジストマスクを形成し、エッチングにより不要な部分を除去して第1の配線101A

、容量電極101Bを形成する。このとき少なくとも第1の配線101A及び容量電極1

01Bの端部がテーパー形状となるようにエッチングする。

【0040】

第1の配線101A及び容量電極101Bは、アルミニウム(Al)や銅(Cu)などの

低抵抗導電性材料で形成することが望ましいが、Al単体では耐熱性が劣り、また腐蝕し

やすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。耐熱性導電性材

料としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(M

o)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、ま

たは上述した元素を成分とする合金か、上述した元素を組み合わせた合金、または上述し

た元素を成分とする窒化物で形成する。

【0041】

なお、インクジェットや印刷法を用いてTFTを構成する配線等を形成することができる

。これらにより、室温で製造、低真空度で製造、又は大型基板上に製造することができる

。フォトマスクを用いなくても製造することができるため、トランジスタのレイアウトを

容易に変更することが出来る。さらに、レジストを用いる必要がないので、材料費が安く

なり、工程数を削減できる。またインクジェットや印刷法を用いてレジストマスク等を形

成することもできる。インクジェットや印刷法を用いてレジストを必要な部分にのみ形成

し、露光及び現像によりレジストマスクとすることで、全面にレジストを形成するよりも

、低コスト化が図れる。

【0042】

また、多階調マスクにより複数(代表的には二種類)の厚さの領域を有するレジストマス

クを形成し、配線等の形成を行っても良い。

【0043】

次いで、第1の配線101A及び容量電極101B上に絶縁膜(以下、ゲート絶縁膜11

3という)を全面に成膜する。ゲート絶縁膜113はスパッタ法などを用いる。

【0044】

例えば、ゲート絶縁膜113としてスパッタ法により酸化シリコン膜を用いて形成する。

勿論、ゲート絶縁膜113はこのような酸化シリコン膜に限定されるものでなく、酸化窒

化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化タンタル膜などの他の絶縁膜

を用い、これらの材料から成る単層または積層構造として形成しても良い。

【0045】

なお、酸化物半導体を成膜する前に、アルゴンガスを導入してプラズマを発生させる逆ス

パッタを行い、ゲート絶縁膜113の表面に付着しているゴミを除去することが好ましい

。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰

囲気に酸素、N2Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気にCl2

、CF4などを加えた雰囲気で行ってもよい。

【0046】

次に、ゲート絶縁膜113上に、酸化物半導体を、ゲート絶縁膜113表面のプラズマ処

理後、大気に曝すことなく成膜する。酸化物半導体をトランジスタの半導体層として用い

ることにより、アモルファスシリコン等のシリコン系半導体材料と比較して電界効果移動

度を高めることが出来る。なお酸化物半導体としては、例えば、酸化亜鉛(ZnO)、酸

化スズ(SnO2)なども用いることができる。また、ZnOにInやGaなどを添加す

ることもできる。

【0047】

酸化物半導体としてInMO3(ZnO)x(x>0)で表記される薄膜を用いることが

できる。なお、Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(M

n)及びコバルト(Co)から選ばれた一の金属元素又は複数の金属元素を示す。例えば

Mとして、Gaの場合があることの他、GaとNi又はGaとFeなど、Ga以外の上記

金属元素が含まれる場合がある。また、上記酸化物半導体において、Mとして含まれる金

属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、又は該遷移金属の酸

化物が含まれているものがある。例えば、酸化物半導体層としてIn−Ga−Zn−O系

膜を用いることができる。

【0048】

酸化物半導体(InMO3(ZnO)x(x>0)膜)としてIn−Ga−Zn−O系膜

のかわりに、Mを他の金属元素とするInMO3(ZnO)x(x>0)膜を用いてもよ

い。また、酸化物半導体として上記の他にも、In−Sn−Zn−O系、In−Al−Z

n−O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn−O系

、In−Zn−O系、Sn−Zn−O系、Al−Zn−O系、In−O系、Sn−O系、

Zn−O系の酸化物半導体を適用することができる。

【0049】

なお酸化物半導体として、In−Ga−Zn−O系を用いる。ここでは、In2O3:G

a2O3:ZnO=1:1:1としたターゲットを用いる。基板とターゲットとの間の距

離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率1

00%)雰囲気下で成膜する。なお、パルス直流(DC)電源を用いると、成膜時に発生

する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も均一となるために

好ましい。

【0050】

なお酸化物半導体の成膜は、先に逆スパッタを行ったチャンバーと同一チャンバーを用い

てもよいし、先に逆スパッタを行ったチャンバーと異なるチャンバーで成膜してもよい。

【0051】

スパッタ法にはスパッタ用電源に高周波電源を用いるRFスパッタ法、直流電源を用いる

DCスパッタ法、さらにパルス的にバイアスを与えるパルスDCスパッタ法がある。RF

スパッタ法は主に絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に金属膜を成膜

する場合に用いられる。

【0052】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ

装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種

類の材料を同時に放電させて成膜することもできる。

【0053】

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタ法を用いるスパッタ装置

や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ

法を用いるスパッタ装置がある。

【0054】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分

とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に

基板にも電圧をかけるバイアススパッタ法もある。

【0055】

次いで、酸化物半導体層の脱水化または脱水素化を行う。脱水化または脱水素化を行う第

1の加熱処理の温度は、400℃以上であって750℃未満、好ましくは425℃以上と

する。なお、425℃以上であれば熱処理時間は1時間以下でよいが、425℃未満であ

れば加熱処理時間は、1時間よりも長時間行うこととする。ここでは、加熱処理装置の一

つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理

を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化

物半導体層を得る。本実施の形態では、酸化物半導体層の脱水化または脱水素化を行う加

熱温度Tから、再び水が入らないような十分な温度まで同じ炉を用い、具体的には加熱温

度Tよりも100℃以上下がるまで窒素雰囲気下で徐冷する。また、窒素雰囲気に限定さ

れず、希ガス(ヘリウム、ネオン、アルゴン等)雰囲気下において脱水化または脱水素化

を行う。

【0056】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱

輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas

Rapid Thermal Anneal)装置、LRTA(Lamp Rapid

Thermal Anneal)装置等のRTA(Rapid Thermal An

neal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライ

ドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧

水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置

である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、ア

ルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と殆ど反応しない

不活性気体が用いられる。

【0057】

酸化物半導体層を400℃以上750℃未満の温度で熱処理することで、酸化物半導体層

の脱水化、脱水素化が図られ、その後の水(H2O)の再含浸を防ぐことができる。

【0058】

また、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガス

に、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、

またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上

、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ま

しくは0.1ppm以下)とすることが好ましい。

【0059】

なお、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層

が結晶化し、微結晶膜または多結晶膜となる場合もある。例えば、結晶化率が90%以上

、または80%以上の微結晶の酸化物半導体膜となる場合もある。また、第1の加熱処理

の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半

導体膜となる場合もある。

【0060】

酸化物半導体層は、脱水化または脱水素化のための第1の加熱処理後に酸素欠乏型となり

、低抵抗化する。第1の加熱処理後の酸化物半導体層は、成膜直後の酸化物半導体膜より

もキャリア濃度が高まり、好ましくは1×1018/cm3以上のキャリア濃度を有する

酸化物半導体層となる。

【0061】

次いで、第2のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチング

により不要な部分を除去して酸化物半導体でなる第1の酸化物半導体層103A、第2の

酸化物半導体層103Bを形成する。なお第1の酸化物半導体層103A、第2の酸化物

半導体層103Bへの第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半

導体膜に行うこともできる。この際のエッチング方法としてウェットエッチングまたはド

ライエッチングを用いる。この段階での断面図を図2(A)に示す。

【0062】

なおゲート絶縁膜113の成膜後に、図2(A)に示すような、ゲート絶縁膜113に容

量電極101Bに達する開口部121を形成し、後に形成する配線と容量電極との接続を

するようにしてもよい。

【0063】

次に、酸化物半導体層上に金属材料からなる導電膜をスパッタ法や真空蒸着法で形成する

。導電膜の材料としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または

上述した元素を成分とする合金か、上述した元素を組み合わせた合金等が挙げられる。ま

た、200℃〜600℃の熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に

持たせることが好ましい。Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があ

るので耐熱性導電性材料と組み合わせて形成する。Alと組み合わせる耐熱性導電性材料

としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo

)、クロム(Cr)、ネオジム(Nd)、Sc(スカンジウム)から選ばれた元素、また

は上述した元素を成分とする合金か、上述した元素を組み合わせた合金、または上述した

元素を成分とする窒化物で形成する。

【0064】

ここでは、導電膜としてチタン膜の単層構造とする。また、導電膜は、2層構造としても

よく、アルミニウム膜上にチタン膜を積層してもよい。また、導電膜としてTi膜と、そ

のTi膜上に重ねてNdを含むアルミニウム(Al−Nd)膜を積層し、さらにその上に

Ti膜を成膜する3層構造としてもよい。導電膜は、シリコンを含むアルミニウム膜の単

層構造としてもよい。

【0065】

次に、第3のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングに

より不要な部分を除去して導電膜でなる第2の配線102A、第3の配線102B、電源

線104A、及び第4の配線104Bを形成する。この際のエッチング方法としてウェッ

トエッチングまたはドライエッチングを用いる。例えば、アンモニア過水(31重量%過

酸化水素水:28重量%アンモニア水:水=5:2:2)を用いたウェットエッチングに

より、Ti膜の導電膜をエッチングして第2の配線102A、第3の配線102B、電源

線104A、及び第4の配線104Bを選択的にエッチングして第1の酸化物半導体層1

03A、第2の酸化物半導体層103Bを残存させることができる。

【0066】

また、エッチング条件にもよるが第3のフォトリソグラフィー工程において酸化物半導体

層の露出領域がエッチングされる場合がある。その場合、第2の配線102A及び第3の

配線102Bに挟まれる領域の第1の酸化物半導体層103Aは、第1の配線101A上

で第2の配線102A及び第3の配線102Bと重なる領域の酸化物半導体層に比べ、膜

厚が薄くなる。また、電源線104A及び第4の配線104Bに挟まれる領域の第2の酸

化物半導体層103Bは、容量電極101B上で電源線104A及び第4の配線104B

と重なる領域の酸化物半導体層に比べ、膜厚が薄くなる。

【0067】

次いで、ゲート絶縁膜113、第1の酸化物半導体層103A、第2の酸化物半導体層1

03B、第2の配線102A、第3の配線102B、電源線104A、第4の配線104

B上に酸化物絶縁層114を形成する。この段階で、第1の酸化物半導体層103A、及

び第2の酸化物半導体層103Bの一部は、酸化物絶縁層114と接する。なお、ゲート

絶縁膜113を挟んで第1の配線101Aと重なる第1の酸化物半導体層103Aの領域

、及び容量電極101Bと重なる第2の酸化物半導体層103Bの領域がチャネル形成領

域となる。

【0068】

酸化物絶縁層114は、少なくとも1nm以上の膜厚とし、スパッタリング法など、酸化

物絶縁層に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。

本実施の形態では、スパッタリング法を用いて酸化物絶縁層として酸化珪素膜を成膜する

。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃

とする。酸化珪素膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰

囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素混合雰囲気下にお

いて行うことができる。また、ターゲットとして酸化珪素ターゲットまたは珪素ターゲッ

トを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び希ガス雰囲気下

でスパッタリング法により酸化珪素膜を形成することができる。低抵抗化した酸化物半導

体層に接して形成する酸化物絶縁層は、水分や、水素イオンや、OH−などの不純物を含

まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化

珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用

いる。なお、スパッタ法で成膜した酸化物絶縁層は特に緻密であり、接する層へ不純物が

拡散する現象を抑制する保護膜として単層であっても利用することができる。また、リン

(P)や硼素(B)をドープしたターゲットを用い、酸化物絶縁層にリン(P)や硼素(

B)を添加することもできる。

【0069】

本実施の形態では、純度が6Nであり、柱状多結晶Bドープの珪素ターゲット(抵抗値0

.01Ωcm)を用い、基板とターゲットとの間の距離(T−S間距離)を89mm、圧

力0.4Pa、直流(DC)電源6kW、酸素(酸素流量比率100%)雰囲気下でパル

スDCスパッタ法により成膜する。膜厚は300nmとする。

【0070】

なお、酸化物絶縁層114は酸化物半導体層のチャネル形成領域となる領域上に接して設

けられ、チャネル保護層としての機能も有する。

【0071】

次いで、第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上3

50℃以下)を不活性ガス雰囲気下、または窒素ガス雰囲気下で行ってもよい。例えば、

窒素雰囲気下で250℃、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、第

1の酸化物半導体層103A、及び第2の酸化物半導体層103Bの一部が酸化物絶縁層

114と接した状態で加熱される。

【0072】

第1の加熱処理で低抵抗化された第1の酸化物半導体層103A、及び第2の酸化物半導

体層103Bが酸化物絶縁層114と接した状態で第2の加熱処理が施されると、酸化物

絶縁層114が接した領域が酸素過剰な状態となる。その結果、第1の酸化物半導体層1

03A、及び第2の酸化物半導体層103Bの酸化物絶縁層114が接する領域から、第

1の酸化物半導体層103A、及び第2の酸化物半導体層103Bの深さ方向に向けて、

I型化(高抵抗化)する。

【0073】

次いで、酸化物絶縁層114に第4のフォトリソグラフィー工程により、開口部122を

形成する。この段階での断面図を図2(B)に示す。

【0074】

次いで、第4の配線104Bと接続するための透光性を有する導電膜を成膜する。透光性

を有する導電膜の材料としては、酸化インジウム(In2O3)や酸化インジウム酸化ス

ズ合金(In2O3―SnO2、ITOと略記する)などをスパッタ法や真空蒸着法など

を用いて成膜する。透光性を有する導電膜の他の材料として、窒素を含ませたAl−Zn

−O系膜、即ちAl−Zn−O−N系膜や、窒素を含ませたZn−O系膜や、窒素を含ま

せたSn−Zn−O系膜を用いてもよい。なお、Al−Zn−O−N系膜の亜鉛の組成比

(原子%)は、47原子%以下とし、膜中のアルミニウムの組成比(原子%)より大きく

、膜中のアルミニウムの組成比(原子%)は、膜中の窒素の組成比(原子%)より大きい

。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特にITOのエ

ッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム

酸化亜鉛合金(In2O3―ZnO)を用いても良い。

【0075】

なお、透光性を有する導電膜の組成比の単位は原子%とし、電子線マイクロアナライザー

(EPMA:Electron Probe X−ray MicroAnalyzer

)を用いた分析により評価するものとする。

【0076】

次に、第5のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングに

より不要な部分を除去して発光素子の一方の電極を形成する。発光素子は一対の電極(陽

極及び陰極)の間に発光層を具備する構成であり、電極上に発光層を構成する素子を積層

して形成する。そこで、発光素子の一方の電極を発光素子105という。

【0077】

次いで、第1の配線101A、第2の配線102A、第3の配線102B、第4の配線1

04B、第1の酸化物半導体層103A、第2の酸化物半導体層103B、電源線104

A、及び容量電極101B上には、発光素子を画素毎に分離するための隔壁106が設け

られる。なお隔壁106の内側に第4の配線104Bに接続される発光素子105が設け

られることとなる。この段階での断面図を図2(C)に示す。

【0078】

こうして、第1の薄膜トランジスタ107A及び第2の薄膜トランジスタ107Bを有す

る画素を作製することができる。そして、これらを個々の画素に対応してマトリクス状に

配置して画素部を構成することによりアクティブマトリクス型の発光表示装置を作製する

ことができる。

【0079】

図1、図2で説明した本実施の形態の構成による利点について図3(A)、(B)を用い

て詳細に説明を行う。

【0080】

図3(A)、(B)は、図1(A)の上面図における酸化物半導体層近傍の拡大図である

。また、図3(A)における第1の酸化物半導体層103Aの幅(図3(A)中、W1)

を大きくとった図が、図3(B)の第1の酸化物半導体層103Aの幅(図3(B)中、

W2)とした図に対応する。

【0081】

本実施の形態における図1(A)での画素の上面図では、図3(A)、(B)で示すよう

に、第1の配線101Aより配線を分岐させることなく、第1の配線101A上に第1の

酸化物半導体層103Aを設けている。酸化物半導体層での第2の配線102Aと第3の

配線102Bとの間に形成されるチャネル領域が第1の配線101A上の重畳する領域に

形成されることとなる。第1の酸化物半導体層103Aはチャネル領域に光が照射される

ことでTFT特性にばらつきが生じることもあるため、第1の配線101Aより分岐した

配線により確実に遮光を行う必要があり、画素の開口率を下げる要因ともなっていた。本

実施の形態の構成である第1の配線101A上に重畳するように酸化物半導体層を設け、

第1の配線101Aより分岐した配線を形成しないことで、開口率の向上を図ることがで

きる。

【0082】

また、薄膜トランジスタの半導体層として、透光性を有する酸化物半導体層を用いること

により、酸化物半導体層が第1の配線101Aと重畳する領域から、設計の位置よりもず

れた領域に形成され、発光素子105と重畳することとなっても、開口率を低減すること

なく、表示を行うことができる。

【0083】

所定のサイズより大きなパターンで酸化物半導体層を形成することで、設計の位置から多

少ずれた箇所に酸化物半導体層が形成されたとしても、動作不良及び開口率の低下といっ

たことなく良好な表示を行うことができる。そのため、発光表示装置のアクティブマトリ

クス基板が作りやすくなり、歩留まりの向上を図ることができるといえる。

【0084】

次いで、酸化物半導体層を用いた薄膜トランジスタを用いることにより、保持容量を削減

する際の具体的な上面図の一例について示す。

【0085】

酸化物半導体を有する薄膜トランジスタでは、ゲートにトランジスタを非導通状態とする

電圧を印加した際にトランジスタに流れる電流(以下、リーク電流という)が0.1pA

以下であるのに対し、アモルファスシリコンを有する薄膜トランジスタでは数100nA

程度となる。そのため、酸化物半導体を有する薄膜トランジスタでは、保持容量の縮小を

図ることができる。すなわち酸化物半導体を有する薄膜トランジスタが設けられる画素で

は、アモルファスシリコンを有する薄膜トランジスタが設けられる画素に比べ各素子のレ

イアウトの自由度を高めることが出来る。

【0086】

酸化物半導体層を有する薄膜トランジスタは、リーク電流が非常に小さいため、保持容量

を省略することも可能である。具体的に保持容量を省略した場合の上面図、及びその断面

図について図12(A)、(B)に示す。図12(A)に示す画素の上面図は、上記説明

した図1(A)での上面図において、容量線を省略した図に相当する。図12(A)に示

す上面図、図12(B)に示す断面図からもわかるように、酸化物半導体層を有する薄膜

トランジスタを用いることで、第2の薄膜トランジスタの配置によって、第3の配線10

2B等の引き回しを短くし、開口率を向上することができる。

【0087】

以上説明したように本実施の形態で示す構成とすることにより、酸化物半導体を用いた薄

膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。従っ

て、高精細な表示部を有する発光表示装置とすることができる。

【0088】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【0089】

(実施の形態2)

上記実施の形態とは別のTFTの構成の表示装置の画素を構成する例を以下に説明する。

【0090】

実施の形態1の構成とは異なる、画素の上面図について図4(A)に示す。なお図4(A

)に示すTFTの構造は、ボトムゲート型構造であり、ゲートとなる配線から見てチャネ

ル領域となる酸化物半導体層の反対側に、TFTのソース電極及びドレイン電極となる配

線層を有する、いわゆる逆スタガ型の構成について示している。

【0091】

図4(A)に示す画素400は、走査線として機能する第1の配線401A、信号線とし

て機能する第2の配線402A、第1の酸化物半導体層403A、第2の酸化物半導体層

403B、電源線404A、容量電極401B、発光素子405を有する。また、第1の

酸化物半導体層403Aと容量電極401Bとを電気的に接続するための第3の配線40

2Bを有し、第1の薄膜トランジスタ407Aが構成される。また、第2の酸化物半導体

層403Bと発光素子405とを電気的に接続するための第4の配線404Bを有し、第

2の薄膜トランジスタ407Bが構成される。また第1の配線401A、第2の配線40

2A、第3の配線402B、第4の配線404B、第1の酸化物半導体層403A、第2

の酸化物半導体層403B、電源線404A、及び容量電極401B上には、発光素子を

画素毎に分離するための隔壁406が設けられる。なお隔壁406の内側に第4の配線4

04Bに接続される発光素子405が設けられることとなる。

【0092】

第1の配線401Aは第1の薄膜トランジスタ407Aのゲートとして機能する配線でも

ある。容量電極401Bは、第2の薄膜トランジスタ407Bのゲート及び保持容量の一

方の電極としてとして機能する配線でもある。第2の配線402Aは、第1の薄膜トラン

ジスタ407Aのソース電極またはドレイン電極の一方として機能する配線でもある。第

3の配線402Bは、第1の薄膜トランジスタ407Aのソース電極またはドレイン電極

の他方として機能する配線でもある。電源線404Aは、第2の薄膜トランジスタ407

Bのソース電極またはドレイン電極の一方、及び保持容量の他方の電極として機能する配

線でもある。第4の配線404Bは、第2の薄膜トランジスタ407Bのソース電極また

はドレイン電極の他方として機能する配線でもある。

【0093】

なお第1の配線401Aと、容量電極401Bとが同層から設けられ、第2の配線402

A、第3の配線402B、電源線404A、及び第4の配線404Bが同層から設けられ

る。また電源線404Aと容量電極401Bとは、一部重畳して設けられており、第2の

薄膜トランジスタ407Bの保持容量を形成している。なお、第1の薄膜トランジスタ4

07Aが有する第1の酸化物半導体層403Aは、第1の配線401A上にゲート絶縁膜

(図示せず)を介して設けられており、第1の酸化物半導体層403Aは第1の配線40

1A及び隔壁406が設けられた領域をはみ出て設けられている。

【0094】

また図4(B)には、図4(A)における一点鎖線A−A’、B−B’、C−C’間の断

面構造について示している。図4(B)に示す断面構造で、基板411上には、下地膜4

12を介して、ゲートである第1の配線401A、容量電極401Bが設けられている。

第1の配線401A、及び容量電極401Bを覆うように、ゲート絶縁膜413が設けら

れている。ゲート絶縁膜413上には、第1の酸化物半導体層403A、第2の酸化物半

導体層403Bが設けられている。第1の酸化物半導体層403A上には、第2の配線4

02A、第3の配線402B、第2の酸化物半導体層403B上には、電源線404A、

第4の配線404Bが設けられている。また、第1の酸化物半導体層403A、第2の酸

化物半導体層403B、第2の配線402A、第3の配線402B、電源線404A、及

び第4の配線404B上には、パッシベーション膜として機能する酸化物絶縁層414が

設けられている。第1の配線401A、第2の配線402A、第3の配線402B、第4

の配線404B、第1の酸化物半導体層403A、第2の酸化物半導体層403B、電源

線404A、及び容量電極401B上の酸化物絶縁層414上には、隔壁406が設けら

れている。また第4の配線404B上の酸化物絶縁層414には開口部が形成されており

、開口部において発光素子405の電極と第4の配線404Bとの接続がなされる。また

一点鎖線B−B’において、第3の配線402Bと容量電極401Bとが、ゲート絶縁膜

413に形成される開口部を介して接続されている。

【0095】

なお、図4(A)、(B)に示す画素は、実施の形態1の図1(A)、(B)での説明と

同様に、図7での基板700上にマトリクス状の複数の画素701として配置されるもの

である。図7に関する説明は実施の形態1と同様である。

【0096】

また、図4(B)に示す断面図は、図1(B)に示した断面図と同様であり、画素の作製

方法については実施の形態1における図2での説明と同様である。

【0097】

図4(A)、(B)で説明した本実施の形態の構成による利点について図5(A)、(B

)を用いて詳細に説明を行う。

【0098】

図5(A)、(B)は、図4(A)の上面図における酸化物半導体層近傍の拡大図である

。また、図5(A)における第1の酸化物半導体層403Aの幅(図5(A)中、W1)

を大きくとった図が、図5(B)の第1の酸化物半導体層403Aの幅(図5(B)中、

W2)とした図に対応する。

【0099】

本実施の形態における図4(A)での画素の上面図では、図5(A)、(B)で示すよう

に、第1の配線401Aより配線を分岐させることなく、第1の配線401A上に第1の

酸化物半導体層403Aを設けている。酸化物半導体層での第2の配線402Aと第3の

配線402Bとの間に形成されるチャネル領域が第1の配線401A上の重畳する領域に

形成されることとなる。加えて本実施の形態で第1の酸化物半導体層403Aは、第1の

配線401A上のゲート絶縁膜上を延在して第2の配線402A及び第3の配線402B

に接することとなる。

【0100】

第1の酸化物半導体層403Aはチャネル領域に光が照射されることでTFT特性にばら

つきが生じることもあるため、第1の配線401Aより分岐した配線により確実に遮光を

行う必要があり、画素の開口率を下げる要因ともなっていた。本実施の形態の構成である

第1の配線401A上に重畳するように酸化物半導体層を設け、第1の配線401Aより

分岐した配線を形成しない構成、及び第1の配線401A上のゲート絶縁膜上を延在して

第2の配線402A及び第3の配線402Bを第1の酸化物半導体層403Aに接する構

成で、開口率の向上を図ることができる。

【0101】

また、薄膜トランジスタの半導体層として、透光性を有する酸化物半導体層を用いること

により、酸化物半導体層が第1の配線401Aと重畳する領域から、設計の位置よりもず

れた領域に形成され、発光素子405と重畳することとなっても、開口率を低減すること

なく、表示を行うことができる。

【0102】

なお図4(A)で示す第1の配線401A上を延在する第2の配線402A及び第3の配

線402Bは、第1の配線401A上に重畳して設けられていればよい。また第2の配線

402A及び第3の配線402Bは、蛇行して(メアンダ状に)引き回されていてもよい

し、直線状に配線を設ける構成としてもよい。

【0103】

所定のサイズより大きなパターンで酸化物半導体層を形成することで、多少設計の位置よ

りもずれた箇所に酸化物半導体層が形成されたとしても、動作不良及び開口率の低下とい

ったことなく良好な表示を行うことができる。そのため、発光表示装置のアクティブマト

リクス基板が作りやすくなり、歩留まりの向上を図ることができるといえる。

【0104】

以上説明したように本実施の形態で示す構成とすることにより、酸化物半導体を用いた薄

膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。従っ

て、高精細な表示部を有する発光表示装置とすることができる。

【0105】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【0106】

(実施の形態3)

上記実施の形態とは別のTFTの構成の表示装置の画素を構成する例を以下に説明する。

【0107】

実施の形態2の構成とは異なる、画素の上面図及び断面図について図6(A)、(B)に

示す。なお図6(A)に示す上面図の構造は、図4(A)と同様であり、ここでは説明を

省略する。また図6(B)に示す断面図の構造が、図4(B)に示す断面図の構造と異な

る点は、第1の配線401Aと第2の配線402Aとの間に層間絶縁層601Aを設ける

構成とする点、及び第1の配線401Aと第3の配線402Bとの間に層間絶縁層601

Bを設ける構成とする点にある。

【0108】

第1の配線401A上に第2の配線402A及び第3の配線402Bを延在させて設ける

場合、ゲート絶縁膜413の膜厚によっては、第1の配線401Aと第2の配線402A

、第1の配線401Aと第3の配線402Bとの間、及び第1の配線401Aと電源線4

04Aの間に寄生容量が生じることとなる。そのため、図6(B)に示すように、層間絶

縁層601A、層間絶縁層601Bを設けることで寄生容量を低減し、誤動作等の不良を

低減することができる。

【0109】

以上説明したように本実施の形態で示す構成とすることにより、酸化物半導体を用いた薄

膜トランジスタを具備する画素を作製する際に、開口率の向上を図ることができる。また

本実施の形態では、上記実施の形態2の構成に加えて、寄生容量の低減を図ることができ

る。従って、高精細な表示部を有し、且つ誤動作を低減することのできる発光表示装置と

することができる。

【0110】

(実施の形態4)

本実施の形態では、表示素子である発光素子の構成について説明する。

【0111】

図9は、薄膜トランジスタに接続された発光素子の断面構造の一形態について示したも

のである。発光素子は、第1電極911、発光層を有するEL層913、第2電極914

が順に積層して設けられている。第1電極911または第2電極914の一方は陽極とし

て機能し、他方は陰極として機能する。発光素子は、陽極から注入される正孔及び陰極か

ら注入される電子がEL層に含まれる発光層で再結合して、発光する。発光素子の第1電

極911は、基板111上に形成された薄膜トランジスタ107Bに接続する。また、薄

膜トランジスタ107Bのソース又はドレインとなる一方の電極及び第1電極911を覆

うように隔壁106が設けられる。また、第1電極911上の隔壁106の開口部に、E

L層913が設けられ、EL層913や隔壁106を覆うように第2電極914が設けら

れる。なお、本実施の形態では、実施の形態1に示す薄膜トランジスタを用いて示したが

、他の実施の形態に示す薄膜トランジスタを用いることができる。

【0112】

第1電極911または第2電極914は、金属、合金、または電気伝導性化合物を用い

て形成する。

【0113】

例えば、第1電極911または第2電極914は、仕事関数の大きい(仕事関数が4.

0eV以上)金属、合金、電気伝導性化合物などを用いることできる。代表的には、酸化

インジウム−酸化スズ(ITO:Indium Tin Oxide)、珪素若しくは酸

化珪素を含有した酸化インジウム−酸化スズ、酸化インジウム−酸化亜鉛(IZO:In

dium Zinc Oxide)、酸化タングステン及び酸化亜鉛を含有した酸化イン

ジウム(IWZO)等の透光性を有する導電性金属酸化物層がある。

【0114】

また、第1電極911または第2電極914は、仕事関数の小さい(代表的には、仕事

関数が3.8eV以下)金属、合金、電気伝導性化合物などを用いることができる。代表

的には、元素周期表の第1族または第2族に属する元素、すなわちリチウムやセシウム等

のアルカリ金属、およびマグネシウム、カルシウム、ストロンチウム等のアルカリ土類金

属、およびこれらを含む合金(アルミニウム、マグネシウムと銀との合金、アルミニウム

とリチウムの合金)、ユーロピウム、イッテルビウム等の希土類金属およびこれらを含む

合金等がある。

【0115】

アルカリ金属、アルカリ土類金属、及びこれらを含む合金は、真空蒸着法、スパッタリ

ング法などを用いて形成する。また、銀ペーストなどをインクジェット法により吐出し焼

成して形成することも可能である。また、第1電極911および第2電極914は、単層

に限らず、積層して形成することもできる。

【0116】

なお、EL層で発光する光を外部に取り出すため、第1電極911または第2電極91

4のいずれか一方或いは両方を、EL層からの発光を透過するように形成する。第1電極

911のみが透光性を有する電極である場合、光は、矢印方向900に示すように第1電

極911を通って、信号線から入力されるビデオ信号に応じた輝度で基板111側から取

り出される。また、第2電極914のみが透光性を有する電極である場合、光は第2電極

914を通って信号線から入力されるビデオ信号に応じた輝度で封止基板916側から取

り出される。第1電極911および第2電極914がいずれも透光性を有する電極である

場合、光は第1電極911および第2電極914を通って、信号線から入力されるビデオ

信号に応じた輝度で基板111側及び封止基板916側の両方から取り出される。

【0117】

透光性を有する電極は、例えば、透光性を有する導電性金属酸化物を用いて形成するか

、或いは、銀、アルミニウム等を数nm乃至数十nmの厚さとなるように形成する。また

、膜厚を薄くした銀、アルミニウムなどの金属層と、透光性を有する導電性金属酸化物層

との積層構造とすることもできる。

【0118】

陽極として機能する第1電極911または第2電極914の一方は、仕事関数の大きい

(仕事関数4.0eV以上)金属、合金、電気伝導性化合物などを用いることが好ましい

。また、陰極として機能する第1電極911または第2電極914の他方は、仕事関数の

小さい(仕事関数3.8eV以下)金属、合金、電気伝導性化合物などを用いることが好

ましい。代表的には、アルカリ金属、アルカリ土類金属、及びこれらを含む合金や化合物

、並びに希土類金属を含む遷移金属を用いて形成することができる。

【0119】

EL層913は、発光層を有する。また、EL層913は、発光層のほかに、正孔注入

層、正孔輸送層、電子輸送層及び電子注入層を有してもよい。正孔輸送層は、陽極と発光

層の間に設けられる。また、正孔注入層は陽極と発光層との間、或いは陽極と正孔輸送層

との間に設けられる。一方、電子輸送層は、陰極と発光層との間に設けられる。電子注入

層は陰極と発光層との間、或いは陰極と電子輸送層との間に設けられる。なお、正孔注入

層、正孔輸送層、電子輸送層及び電子注入層は全ての層を設ける必要はなく、適宜求める

機能等に応じて選択して設ければよい。

【0120】

発光層は発光性の物質を含む。発光性の物質としては、例えば、蛍光を発光する蛍光性

化合物や燐光を発光する燐光性化合物を用いることができる。

【0121】

また、発光層は、発光性の物質をホスト材料に分散して形成できる。発光性の物質をホ

スト材料に分散して発光層を形成すると、発光物質同士が消光反応を引き起こす濃度消光

現象や、結晶化現象を抑制できる。

【0122】

発光性の物質が蛍光性化合物の場合には、ホスト材料に蛍光性化合物よりも一重項励起

エネルギー(基底状態と一重項励起状態とのエネルギー差)が大きい物質を用いることが

好ましい。また、燐光性化合物の場合には、ホスト材料に燐光性化合物よりも三重項励起

エネルギー(基底状態と三重項励起状態とのエネルギー差)が大きい物質を用いることが

好ましい。

【0123】

また、ホスト材料に分散する発光性の物質としては、上述した燐光性化合物や蛍光性化

合物を用いることができる。

【0124】

なお、発光層として、2種類以上のホスト材料と発光性の物質を用いてもよいし、2種

類以上の発光性の物質とホスト材料を用いてもよい。また、2種類以上のホスト材料及び

2種類以上の発光性の物質を用いてもよい。

【0125】

また、正孔注入層として、正孔輸送性の高い物質と電子受容性を示す物質を含む層を用

いることができる。正孔輸送性の高い物質と電子受容性を示す物質とを含む層は、キャリ

ア密度が高く、正孔注入性に優れている。また、正孔輸送性の高い物質と電子受容性を示

す物質とを含む層を、陽極として機能する電極に接する正孔注入層として用いることによ

り、陽極として機能する電極材料の仕事関数の大小に関わらず、様々な金属、合金、電気

伝導性化合物、およびこれらの混合物などを用いることができる。

【0126】

発光層、正孔注入層、正孔輸送層、電子輸送層及び電子注入層は、蒸着法、塗布法等に

より形成することができる。

【0127】

また、第2電極914及び隔壁106上にパッシベーション層915をスパッタリング

法やCVD法により形成してもよい。パッシベーション層915を設けることで、外部か

ら発光素子への水分や酸素の侵入による発光素子の劣化を低減することができる。さらに

は、パッシベーション層915及び封止基板916の空間に窒素を封入し、さらに乾燥剤

を配置してもよい。または、パッシベーション層915及び封止基板916の間を、透光

性を有し、且つ吸水性の高い有機樹脂で充填してもよい。

【0128】

発光素子が白色の発光を示す場合、カラーフィルター、又は色変換層などを、基板11

1または封止基板916に設けることによってフルカラー表示を行なうことができる。

【0129】

またコントラストを高めるため、基板111または封止基板916に偏光板又は円偏光

板を設けてもよい。

【0130】

本実施の形態の画素においても、上記実施の形態の構成を組み合わせることによって、

酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を

図ることができる。

【0131】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可

能である。

【0132】

(実施の形態5)

本実施の形態においては、発光表示装置に適用できる画素の回路構成について説明する。

【0133】

図8は、発光表示装置に適用できる画素構成の一例を示す図である。画素800は、第1

の薄膜トランジスタ801、第2の薄膜トランジスタ802、容量素子803、発光素子

804を有している。第1の薄膜トランジスタ801のゲートは第1の配線805と電気

的に接続される。第1の薄膜トランジスタ801の第1端子は第2の配線806と電気的

に接続される。第1の薄膜トランジスタ801の第2端子は容量素子803の第1電極及

び第2の薄膜トランジスタ802のゲートに電気的に接続される。容量素子803の第2

電極は、電源線807と電気的に接続される。第2の薄膜トランジスタ802の第1端子

は、電源線807と電気的に接続される。第2の薄膜トランジスタ802の第2端子は、

発光素子804の一方の電極と電気的に接続される。

【0134】

第1の配線805に関しては、上記実施の形態1で説明した第1の配線101Aの機能と

同様である。第2の配線806に関しては、上記実施の形態1で説明した第2の配線10

2Aの機能と同様である。電源線807に関しては、上記実施の形態1で説明した電源線

104Aの機能と同等である。発光素子804の構成に関しては、上記実施の形態4で説

明した発光素子の構成と同等である。

【0135】

本実施の形態の画素においても、上記実施の形態の構成を組み合わせることによって、酸

化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、開口率の向上を図

ることができる。

【0136】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【0137】

(実施の形態6)

本実施の形態においては、上記実施の形態で説明した発光表示装置を具備する電子機器の

例について説明する。

【0138】

図10(A)は携帯型遊技機であり、筐体9630、表示部9631、スピーカ9633

、操作キー9635、接続端子9636、記録媒体読込部9672、等を有することがで

きる。図10(A)に示す携帯型遊技機は、記録媒体に記録されているプログラム又はデ

ータを読み出して表示部に表示する機能、他の携帯型遊技機と無線通信を行って情報を共

有する機能、等を有することができる。なお、図10(A)に示す携帯型遊技機が有する

機能はこれに限定されず、様々な機能を有することができる。

【0139】

図10(B)はデジタルカメラであり、筐体9630、表示部9631、スピーカ963

3、操作キー9635、接続端子9636、シャッターボタン9676、受像部9677

、等を有することができる。図10(B)に示すテレビ受像機能付きデジタルカメラは、

静止画を撮影する機能、動画を撮影する機能、撮影した画像を自動または手動で補正する

機能、アンテナから様々な情報を取得する機能、撮影した画像、又はアンテナから取得し

た情報を保存する機能、撮影した画像、又はアンテナから取得した情報を表示部に表示す

る機能、等を有することができる。なお、図10(B)に示すテレビ受像機能付きデジタ

ルカメラが有する機能はこれに限定されず、様々な機能を有することができる。

【0140】

図10(C)はテレビ受像器であり、筐体9630、表示部9631、スピーカ9633

、操作キー9635、接続端子9636、等を有することができる。図10(C)に示す

テレビ受像機は、テレビ用電波を処理して画像信号に変換する機能、画像信号を処理して

表示に適した信号に変換する機能、画像信号のフレーム周波数を変換する機能、等を有す

ることができる。なお、図10(C)に示すテレビ受像機が有する機能はこれに限定され

ず、様々な機能を有することができる。

【0141】

図11(A)はコンピュータであり、筐体9630、表示部9631、スピーカ9633

、操作キー9635、接続端子9636、外部接続ポート9680、ポインティングデバ

イス9681等を有することができる。図11(A)に示すコンピュータは、様々な情報

(静止画、動画、テキスト画像など)を表示部に表示する機能、様々なソフトウェア(プ

ログラム)によって処理を制御する機能、無線通信又は有線通信などの通信機能、通信機

能を用いて様々なコンピュータネットワークに接続する機能、通信機能を用いて様々なデ

ータの送信又は受信を行う機能、等を有することができる。なお、図11(A)に示すコ

ンピュータが有する機能はこれに限定されず、様々な機能を有することができる。

【0142】

次に、図11(B)は携帯電話であり、筐体9630、表示部9631、スピーカ963

3、操作キー9635、マイクロフォン9638等を有することができる。図11(B)

に示した携帯電話は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、

カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又

は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を

有することができる。なお、図11(B)に示した携帯電話が有する機能はこれに限定さ

れず、様々な機能を有することができる。

【0143】

次に、図11(C)は電子ペーパー(E−bookともいう)であり、筐体9630、表

示部9631、操作キー9635等を有することができる。図11(C)に示した電子ペ

ーパーは、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー

、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する

機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有すること

ができる。なお、図11(C)に示した電子ペーパーが有する機能はこれに限定されず、

様々な機能を有することができる。

【0144】

本実施の形態において述べた電子機器は、表示部を構成する複数の画素において、開口率

の向上を図ることができる。

【0145】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能

である。

【符号の説明】

【0146】

100 画素

103 酸化物半導体層

105 発光素子

106 隔壁

111 基板

112 下地膜

113 ゲート絶縁膜

114 酸化物絶縁層

121 開口部

122 開口部

400 画素

405 発光素子

406 隔壁

411 基板

412 下地膜

413 ゲート絶縁膜

414 酸化物絶縁層

700 基板

701 画素

702 画素部

703 走査線駆動回路

704 信号線駆動回路

705 電源回路

800 画素

801 薄膜トランジスタ

802 薄膜トランジスタ

803 容量素子

804 発光素子

805 配線

806 配線

807 電源線

900 矢印方向

911 電極

912 隔壁

913 EL層

914 電極

915 パッシベーション層

916 封止基板

101A 配線

101B 容量電極

102A 配線

102B 配線

103A 酸化物半導体層

103B 酸化物半導体層

104A 電源線

104B 配線

107A 薄膜トランジスタ

107B 薄膜トランジスタ

401A 配線

401B 容量電極

402A 配線

402B 配線

403A 酸化物半導体層

403B 酸化物半導体層

404A 電源線

404B 配線

407A 薄膜トランジスタ

407B 薄膜トランジスタ

601A 層間絶縁層

601B 層間絶縁層

9630 筐体

9631 表示部

9633 スピーカ

9635 操作キー

9636 接続端子

9638 マイクロフォン

9672 記録媒体読込部

9676 シャッターボタン

9677 受像部

9680 外部接続ポート

9681 ポインティングデバイス

【特許請求の範囲】

【請求項1】

第1の配線と、第2の配線と、第1の画素と、第2の画素と、を有し、

前記第1の画素は、第1のトランジスタと、透光性を有する第1の導電層と、を有し、

前記第2の画素は、第2のトランジスタと、透光性を有する第2の導電層と、を有し、

前記第1のトランジスタのゲートは、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第1のトランジスタは、第1の酸化物半導体層を有し、

前記第2のトランジスタは、第2の酸化物半導体層を有し、

前記第1の酸化物半導体層は、インジウムと、ガリウムと、亜鉛と、酸素と、を有し、

前記第2の酸化物半導体層は、インジウムと、ガリウムと、亜鉛と、酸素と、を有し、

前記第1の酸化物半導体層は、ゲート絶縁層を介して前記第1の配線と重なる領域を有し、

前記第1の酸化物半導体層は、前記第1の配線の幅よりも幅の広い領域を有し、

前記第2の配線は、前記第1の配線の上方に設けられた領域を有し、

前記第2の配線は、前記第1の配線に沿うような方向に延びた領域を有し、

前記第2の導電層は、前記第1の酸化物半導体層と重なる領域を有することを特徴とする表示装置。

【請求項1】

第1の配線と、第2の配線と、第1の画素と、第2の画素と、を有し、

前記第1の画素は、第1のトランジスタと、透光性を有する第1の導電層と、を有し、

前記第2の画素は、第2のトランジスタと、透光性を有する第2の導電層と、を有し、

前記第1のトランジスタのゲートは、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第1のトランジスタは、第1の酸化物半導体層を有し、

前記第2のトランジスタは、第2の酸化物半導体層を有し、

前記第1の酸化物半導体層は、インジウムと、ガリウムと、亜鉛と、酸素と、を有し、

前記第2の酸化物半導体層は、インジウムと、ガリウムと、亜鉛と、酸素と、を有し、

前記第1の酸化物半導体層は、ゲート絶縁層を介して前記第1の配線と重なる領域を有し、

前記第1の酸化物半導体層は、前記第1の配線の幅よりも幅の広い領域を有し、

前記第2の配線は、前記第1の配線の上方に設けられた領域を有し、

前記第2の配線は、前記第1の配線に沿うような方向に延びた領域を有し、

前記第2の導電層は、前記第1の酸化物半導体層と重なる領域を有することを特徴とする表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−80257(P2013−80257A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2013−956(P2013−956)

【出願日】平成25年1月8日(2013.1.8)

【分割の表示】特願2010−225633(P2010−225633)の分割

【原出願日】平成22年10月5日(2010.10.5)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成25年1月8日(2013.1.8)

【分割の表示】特願2010−225633(P2010−225633)の分割

【原出願日】平成22年10月5日(2010.10.5)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]