表示装置

【課題】クロック信号を停止させることなく双方向走査可能とすることにより、回路規模を縮小した双方向走査可能な表示装置を提供する。

【解決手段】表示装置は、並行する複数の出力信号線のうち一番端の出力信号線である初段出力信号線に出力するための回路である初段出力回路を有し、初段出力回路は、複数の出力信号線に対して順次導通電位を印加させるための開始の信号が印加されるスタート信号線と、クロック信号である第1クロック信号が印加される第1クロック信号線と、第1クロック信号とは異なるクロック信号である第2クロック信号が印加される第2クロック信号線と、初段出力信号線がソースに接続され、第1クロック信号線がドレインに接続された第1トランジスタと、スタート信号線がゲートに接続され、スタート信号線が導通電位となることにより、第2クロック信号線と第1トランジスタのゲートとを導通させる第2トランジスタと、を備える。

【解決手段】表示装置は、並行する複数の出力信号線のうち一番端の出力信号線である初段出力信号線に出力するための回路である初段出力回路を有し、初段出力回路は、複数の出力信号線に対して順次導通電位を印加させるための開始の信号が印加されるスタート信号線と、クロック信号である第1クロック信号が印加される第1クロック信号線と、第1クロック信号とは異なるクロック信号である第2クロック信号が印加される第2クロック信号線と、初段出力信号線がソースに接続され、第1クロック信号線がドレインに接続された第1トランジスタと、スタート信号線がゲートに接続され、スタート信号線が導通電位となることにより、第2クロック信号線と第1トランジスタのゲートとを導通させる第2トランジスタと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置に関する。

【背景技術】

【0002】

コンピュータ等の情報通信端末やテレビ受像機の表示デバイスとして、液晶表示装置が広く用いられている。また、有機EL表示装置(OLED)、電界放出ディスプレイ装置(FED)なども、薄型の表示装置として知られている。液晶表示装置は、2つの基板の間に封じ込められた液晶組成物の配向を電界の変化により変え、2つの基板と液晶組成物を通過する光の透過度合いを制御することにより画像を表示させる装置である。

【0003】

このような液晶表示装置を含め、所定の階調値に対応する電圧を画面の各画素に印加する表示装置では、各画素に階調値に対応する電圧を印加するための画素トランジスタが配置されている。一般に、画面の1ライン分の画素トランジスタのゲートは一つの信号線(以下「走査信号線」という。)に接続され、この走査信号線は、駆動回路により、各ライン毎に順にこの画素トランジスタを導通させる導通電圧を出力するように制御されている。また、画面の上下を反転させても表示できるように、導通電圧を出力する順を順方向と逆方向との両方で行うことができる双方向走査(双方向スキャン)機能を有するものもある。特許文献1には、双方向走査を実現するための回路が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−73301号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図13は、双方向走査回路の一例を概略的に示す図である。この図に示されるように、双方向走査回路は、表示領域802の上部から順に走査する順走査と、表示領域802の下部から走査する逆走査があり、表示領域802の左右に配置された複数の出力回路から交互に出力して走査することにより、順走査及び逆走査を実現している。

【0006】

複数の出力回路は、スタート信号VSTをトリガーとして動作し、出力を行なう初段出力回路815と、表示領域を挟んで対向する出力回路からの出力をトリガーとして動作し、出力を行なう繰返し出力回路816と、対向する出力回路からの出力を入力しても最終段出力を出力する最終段出力回路817と、を有している。図14には、図13の右上及び左下に示される初段出力回路815の回路図が示されている。回路規模を縮小するために、順走査及び逆走査において同じスタート信号VSTが入力されることとしている。

【0007】

図15は、図13の右上に示される初段出力回路815(図14参照)において、順走査時に入力される信号とノードN1及びN2及び出力VOUT0信号の変化について示すタイミングチャートである。このタイミングチャートに示されるように、スタート信号VSTの入力により、ノードN1がHigh電位となり、その後クロック信号CK3のHigh電位により、出力VOUT0信号が出力されるようになっている。

【0008】

図16には、同じく図13の右上に示される初段出力回路815において、逆走査時の信号が入力された場合のタイミングチャートが示されている。この図に示されるように、逆走査時には、右上の初段出力回路815は、スタート信号VSTによりノードN1はHigh電位となるが、出力用のクロック信号CK3がHigh電位となる前に、クロック信号CK1によりノードN1電位が下げられるために出力されることはない。

【0009】

これらの図15及び図16のタイミングチャートに見られるように、クロック信号CK2及びCK3は、スタート信号VSTの出力の際に停止させている。しかしながら、このようにスタート信号VSTのタイミング等により停止を必要とするクロック信号発生回路の構成は回路規模が大きくなると共に、またコスト的にも無駄が多いため、図17に示されるような、連続したクロック信号のまま初段出力回路815を動作させることが考えられる。この場合にも、図17のタイミングチャートに示されるように、順走査の場合には、問題なく動作させることが可能である。しかしながら、逆走査を行なった場合には、図18のタイミングチャートに示されるように、右上の初段出力回路から出力が発生してしまう場合がある。

【0010】

本発明は、上述の事情を鑑みてされたものであり、クロック信号を停止させることなく双方向走査可能とすることにより、回路規模を縮小した双方向走査可能な表示装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の表示装置は、並行する複数の出力信号線に対して、順に画素トランジスタを導通させる電位である導通電位を印加する駆動回路を備え、前記駆動回路は、前記複数の出力信号線のうち一番端の出力信号線である初段出力信号線に出力するための回路である初段出力回路を有し、前記初段出力回路は、前記複数の出力信号線に対して順次導通電位を印加させるための開始の信号が印加されるスタート信号線と、クロック信号である第1クロック信号が印加される第1クロック信号線と、前記第1クロック信号とは導通電位となる時間が重ならないクロック信号である第2クロック信号が印加される第2クロック信号線と、前記初段出力信号線が、直接又は間接的にソース及びドレインのいずれか一方に接続され、前記第1クロック信号線が、直接又は間接的に前記ソース及びドレインのいずれか他方に接続されたトランジスタである第1トランジスタと、前記第1トランジスタのゲートと直接又は間接的に接続されたノードと、前記スタート信号線がゲートに接続され、前記スタート信号線が導通電位となることにより、前記第2クロック信号線と前記ノードとを導通させる第2トランジスタと、を備えることを特徴とする表示装置である。

【0012】

ここで、出力信号線は、表示領域内の走査信号線のほか、表示領域外のダミー回路等への出力信号線も含むこととし、表示領域内を含めて順次導通信号が印加されるすべての信号線含む意味である。

【0013】

また、本発明の表示装置において、前記スタート信号線の信号が導通電位になるタイミングは、前記第2クロック信号線の信号が導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前としてもよい。

【0014】

また、本発明の表示装置において、前記スタート信号線の信号がトランジスタを導通させない非導通電位になるタイミングは、前記第2クロック信号線が非導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前としてもよい。

【0015】

また、本発明の表示装置において、前記第1クロック信号及び前記第2クロック信号とは、前記導通電位となる時間が重ならないクロック信号である第3クロック信号が印加される第3クロック信号線と、トランジスタを導通させない非導通電位を保持する非導通電位保持線と、前記第3クロック信号線がゲートに接続され、前記第3クロック信号線が導通電位となることにより前記ノードと前記非導通電位保持線とを接続する第3トランジスタと、を更に備えることとしてもよい。

【0016】

また、本発明の表示装置において、前記複数の出力信号線であり、前記初段出力信号線の隣に配置された次段出力信号線と、前記次段出力信号線は、前記次段出力信号線が導通電位となることにより、整流装置を介して前記ノードと導通することとしてもよい。

【0017】

また、本発明の表示装置において、前記次段出力信号線は、画像が表示される表示領域を挟んで、前記初段出力信号線に前記導通電位が印加される側とは反対側で導通電位が印加される、こととしてもよい。

【0018】

また、本発明の表示装置において、前記駆動回路は、前記並行する複数の出力信号線のうち、一方の端の前記出力信号線に出力する前記初段出力回路である第1初段出力回路と、前記並行する複数の出力信号線のうち、他方の端の前記出力信号線に出力する前記初段出力回路である第2初段出力回路と、を有し、前記一方の端から順に前記画素トランジスタを導通させる順走査と、前記他方の端から順に前記画素トランジスタを導通させる逆走査とを切替えて行ない、前記スタート信号線は、前記順走査及び前記逆走査において共通である、こととしてもよい。

【図面の簡単な説明】

【0019】

【図1】本発明の一実施形態に係る表示装置を概略的に示す図である。

【図2】図1の表示パネルの構成を示す図である。

【図3】図2の駆動回路の構成について概略的に示す図である。

【図4】図3の右側駆動回路の繰返し出力回路の回路構成を具体的に示す図である。

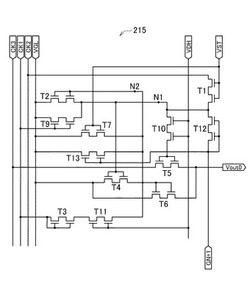

【図5】図3の右側駆動回路の初段出力回路の回路構成を示す図である。

【図6】図3の右側駆動回路の最終段出力回路の回路構成を示す図である。

【図7】図5の右側駆動回路の初段出力回路の順走査時の動作のタイミングチャートである。

【図8】順走査時のスタート信号線VSTとクロック信号CK2とタイミング差について示す図である。

【図9】図5の右側駆動回路の初段出力回路の逆走査時の動作のタイミングチャートである。

【図10】図4の繰返し出力回路の変形例である出力回路を示す図である。

【図11】トランジスタT8を配置しない構成とした場合のタイミングチャートである。

【図12】図4の繰返し出力回路の変形例である出力回路を示す図である。

【図13】双方向走査回路の一例を概略的に示す図である。

【図14】図13の右上に示される初段出力回路の回路図である。

【図15】初段出力回路の順走査時の信号の変化を示すタイミングチャートである。

【図16】初段出力回路の逆走査時の信号の変化を示すタイミングチャートである。

【図17】連続したクロック信号により駆動した場合の初段出力回路の順走査時の信号の変化を示すタイミングチャートである。

【図18】連続したクロック信号により駆動した場合の初段出力回路の逆走査時の信号の変化を示すタイミングチャートである。

【発明を実施するための形態】

【0020】

以下、本発明の実施形態について、図面を参照しつつ説明する。なお、図面において、同一又は同等の要素には同一の符号を付し、重複する説明を省略する。なお、各信号に付された符号は、当該信号が印加される各信号線を示すものとする。

【0021】

図1には、本発明の一実施形態に係る表示装置100が概略的に示されている。この図に示されるように、表示装置100は、上フレーム110及び下フレーム120に挟まれるように固定された表示パネル200等から構成されている。なお、表示パネル200は液晶表示パネル、有機EL表示パネル等の薄膜トランジスタ基板を利用した表示パネルであればいずれの表示パネルでもよいが、本実施形態においては、表示パネル200は液晶表示パネルであるものとする。

【0022】

図2には、図1の表示パネル200の構成が示されている。表示パネル200は、TFT(Thin Film Transistor:薄膜トランジスタ)基板220とカラーフィルタ基板230の2枚の基板を有し、これらの基板の間には液晶組成物が封止されている。TFT基板220は、走査信号線G1〜Gnに対して、順に所定の電圧を印加する駆動回路210と、画素領域202において走査信号線G1〜Gnに垂直に交差するように延びる不図示の複数のデータ信号線に対して画素の階調値に対応する電圧を印加すると共に、駆動回路210を制御する駆動IC(Integrated Circuit)260とを有している。なお、駆動回路210は、図面に向って画素領域202の右側にある右側駆動回路212と、画素領域202の左側にある左側駆動回路214とを有している。

【0023】

図3は、駆動回路210の回路の構成について概略的に示す図である。この図に示されるように、右側駆動回路212は、奇数番目の走査信号線G2i−1(iは自然数)に対して各画素に配置されたTFTのゲートにTFTのソース・ドレイン間を導通させるためのHigh電位(導通電圧)を印加するための駆動回路であり、左側駆動回路214は、偶数番目の走査信号線G2iに対して各画素に配置されたTFTのゲートにTFTのソース・ドレイン間を導通させるためのHigh電位を印加するための駆動回路である。右側駆動回路212及び左側駆動回路214は、それぞれ、初段出力回路215と、最終段出力回路217と、初段出力回路215及び最終段出力回路217の間に配置される繰返し出力回路216と、を有している。右側駆動回路212の繰返し出力回路216は、左側駆動回路214の出力をトリガーとして出力を行い、左側駆動回路214の繰返し出力回路216は、右側駆動回路212の出力をトリガーとして出力を行う。初段出力回路215はスタート信号VSTをトリガーとして出力を行なう。なお、右側駆動回路212のスタート信号VSTと左側駆動回路214のスタート信号はVSTとは、同一の信号であり、同時に両方の初段出力回路215に入力される。初段出力回路215を除く右側駆動回路212は、クロック信号CK1及びCK3により駆動し、右側駆動回路212の初段出力回路215は、クロック信号CK1及びCK3に加えてクロック信号CK2を利用している。また、初段出力回路215を除く左側駆動回路214はクロック信号CK2及びCK4により駆動し、左側駆動回路214の初段出力回路215は、クロック信号CK2及びCK4に加えてクロックCK3を利用している。また、クロック信号CK1〜CK4は、順走査時には、CK1、CK2、CK3、CK4の順にHigh電位となる4相クロックであり、逆走査時には、CK4、CK3、CK2、CK1の順にHigh電位となる4相クロックである。

【0024】

順走査は、スタート信号VSTをトリガーとして、右側駆動回路212の初段出力回路215の出力Vout0に対するHigh電位の出力から開始し、右側駆動回路212の最終段出力回路217で終了する。逆走査は、スタート信号VSTをトリガーとして、左側駆動回路214の初段出力回路215の出力Vout0に対する出力で開始し、左側駆動回路214の最終段出力回路217で終了する。

【0025】

図4には、右側駆動回路212の繰返し出力回路216の回路構成が具体的に示されている。ここで、図4に示された端子の名称は、後述する図7のタイミングチャートにおける説明のために、図3の繰返し出力回路216の端子の名称ではなく、図3の駆動回路210の外部端子の名称に変更している。図4に示されるように、繰返し出力回路216は、2つのクロックCK1及びCK3により動作する回路であり、2つの走査信号線G2i−1及びG2i+1へ出力する部分が示されている。なお、符号Tはトランジスタを示し、符号Nはノードを示す。なお、各トランジスタはLTPS(Low Temperature Poly Silicon)により形成されている。

【0026】

この図に示されるように、走査信号線G2i−1へ出力するための回路は、順走査時に回路入力となるダイオードトランジスタT1と、後述するトランジスタT5のゲート電極をトランジスタの非導通電圧であるLow電位(VGL)に固定するトランジスタT2と、保持ノードN2を充電するトランジスタT3と、保持ノードリセット用トランジスタT4と、走査信号線G2i−1へHigh電位を出力するためのトランジスタT5と、保持ノードN2により走査信号線G2i−1を電圧VGLに固定するトランジスタT6と、順走査時に入力信号により保持ノードN2をリセットするトランジスタT7と、初期リセット用トランジスタT8と、トランジスタT5のゲート電極リセット用トランジスタT9と、トランジスタT5のゲートの昇圧を中間電圧VDHで制限する電圧緩和用トランジスタT10と、トランジスタT3で充電した電圧を中間電圧VDHで降圧するトランジスタT11と、逆走査時に回路入力となるダイオードトランジスタT12と、逆走査時に入力信号により保持ノードN2を電圧VGLにリセットするトランジスタT13とから構成されている。なお、中間電圧VDHは、走査信号線G2i−1のHigh電位であるVGHより低い電圧であって、トランジスタを導通させる電位を有している。ここでは、中間電圧VDHもHigh電位として表している。

【0027】

図5には、回路の初段となる初段出力回路215の回路構成が示されている。初段出力回路215の構成は、基本的に繰返し出力回路216の構成と同様であるが、スタート信号VSTは、トランジスタT7のゲートに接続されると共に、トランジスタT1のゲートに接続され、トランジスタT1のドレイン側はクロック信号CK2に接続されている。また、初期リセット用トランジスタT8が配置されない構成となっている。この初段出力回路の動作については、後述する。

【0028】

図6には、回路の最終段となる最終段出力回路217の回路構成が示されている。最終段出力回路217は、繰返し出力回路216と比較して、検査用端子に接続されるトランジスタT14及びT15を追加した構成となっている。

【0029】

図7には、図5の右側駆動回路212の初段出力回路215の順走査時の動作のタイミングチャートが示されている。以下、図7のタイミングチャートを用いて、初段出力回路215の動作について説明する。まず、初段出力回路215は、時刻t1のクロック信号CK2のタイミングより微少時間ts1だけ前に(図8参照)、スタート信号線VSTにHigh電位を入力することにより、トランジスタT7を導通させ、ノードN2をLow電位(VGL)と接続させLow電位とする。次にクロック信号CK2がHigh電位となることによりトランジスタT1を導通させ、保持ノードN1の電位をHighに設定し、トランジスタT5を導通させる。このように、クロック信号CK2がHigh電位になる少し前にスタート信号をHigh電位にすることにより、ノードN2をノードN1がHigh電位になる前にLow電位に落とすことができるため、貫通電流を防止することができ、信頼性の向上および消費電力を抑えることが出来る。また、スタート信号VSTの立ち下がりのタイミングは、クロック信号CK2の立ち下がりのタイミングより微少時間ts2だけ前になっている(図8参照)。これにより、トランジスタT1を先に遮断して、ノードN1をHighに維持することができる。ここで微少時間は、クロック信号の周期より十分に小さい時間であることを意味する。

【0030】

引き続き、t2のタイミングにおいて、クロック信号CK3がHigh電位になると、トランジスタT5のゲートの電圧は、所謂ブートストラップ効果により更に昇圧され、出力Vout0には、High信号が出力され、引き続き、クロックCK3の動作に追従して、Low信号が出力される。

【0031】

次に、t3のタイミングにおいて、CK1がHighになることにより、T3が導通し、ノードN2をHigh電位に上げると共に、トランジスタT9が導通するため、ノードN1はLow電位に下げられる。ノードN1はトランジスタT10を介してトランジスタT5のソース・ドレイン間を遮断すると共に、ノードN2のHigh電位によりトランジスタT6が導通することにより、出力Vout0は、Low電位(VGL)と接続される。

【0032】

ここで、トランジスタT10は、クロック信号CK3がHighになることにより、昇圧された電圧に耐えられるようにトランジスタを2つ重ねて配置するダブルゲート構成として高耐圧化している。出力された出力Vout0にHigh信号は、左側駆動回路214の繰返し出力回路216への入力信号となり、上述の動作と同様の動作により、走査信号線G1にHigh信号を出力する。

【0033】

図9には、図5の右側駆動回路212の初段出力回路215の逆走査時の動作のタイミングチャートが示されている。図7と比較して、CK1〜CK4の位相が異なり、逆順序でHigh電位となっている。まず、t4のタイミングにおいて、左側駆動回路214の初段出力回路215をスタートさせるために、クロック信号CK3に合わせてスタート信号VSTがHigh電位となる。これにより、左側駆動回路214の初段出力回路215においては、ノードN1がHigh電位となり、ノードN2がLow電位となるが、右側駆動回路212においては、トランジスタT1が導通してCK2のLow電位より、動作を開始しない。これにより、逆走査の際にスタート信号VSTをHigh電位になったとしても、右側駆動回路212の初段出力回路215は走査を開始しない。

【0034】

以上説明したように、上述の実施形態においては、クロック信号を停止させることなく双方向走査可能となるため、回路規模を縮小して双方向走査可能な表示装置とすることができる。

【0035】

また、上述の実施形態においては、順方向に走査する回路と逆方向に走査する回路は、同じ回路を利用するため、逆方向の走査のための回路を配置する必要がなく、回路規模を縮小でき、表示装置の額縁領域を小さくすることができる。

【0036】

また、トランジスタを重ねて配置するダブルゲート構成としているため、LTPSトランジスタであっても高耐圧の回路とすることができる。

【0037】

図10には、上述した図4の繰返し出力回路216の変形例である出力回路301が示されている。繰返し出力回路216との違いは、トランジスタT8が配置されていない点であり、上述の実施形態においては、トランジスタT8は、スタート信号VSTにより保持ノードN2を充電するために配置されている。しかしながら、全クロック信号CK1〜CK4をHigh電位とすることでも保持ノードN2を充電することが可能であることから、図11に示されるように、スタート信号VSTの前にクロック信号CK1〜CK4を同時にHigh電位とする駆動方法を用いることにより、トランジスタT8を配置しない構成とし、より回路規模を縮小させることが可能である。

【0038】

図12には、上述した図4の繰返し出力回路216の変形例である出力回路302が示されている。繰返し出力回路216との違いは、トランジスタT8及びT11が配置されていない点である。トランジスタT11は、トランジスタT2及びT6のゲートにクロック信号CK1〜CK4の高電圧が直接かからないように配置されていたが、製造ラインのNa汚染等が抑えられる場合には、トランジスタT11を配置しない構成とし、より回路規模を縮小させることが可能である。

【0039】

なお、上述の実施形態においては、High電位を導通電位として、High電位がゲートに入力されることで、ソース・ドレイン間が導通するNMOS型のトランジスタとしたが、Low電位を導通電位として、Low電位がゲートに入力することによりソース・ドレイン間が導通するPMOS型のトランジスタとしてもよい。

【0040】

また、上述の実施形態においては、クロック信号を4相クロックを用いることとしたが、これ以外のクロック信号を用いて実現してもよい。

【0041】

また、上述の各実施形態の液晶表示装置は、IPS(In-Plane Switching)方式、VA(Vertically Aligned)方式及びTN(Twisted Nematic)方式のいずれの方式の液晶表示装置であっても適用することができる。また、液晶表示装置に限らず、有機EL表示装置、電界放出ディスプレイ装置(FED)及び駆動回路を用いるその他の表示装置に用いることができる。

【符号の説明】

【0042】

100 表示装置、110 上フレーム、120 下フレーム、200 表示パネル、202 画素領域、210 駆動回路、212 右側駆動回路、214 左側駆動回路、215 初段出力回路、216 繰返し出力回路、217 最終段出力回路、220 TFT基板、230 カラーフィルタ基板、260 駆動IC、301 出力回路、302 出力回路、802 表示領域、815 初段出力回路、816 繰返し出力回路、817 最終段出力回路。

【技術分野】

【0001】

本発明は、表示装置に関する。

【背景技術】

【0002】

コンピュータ等の情報通信端末やテレビ受像機の表示デバイスとして、液晶表示装置が広く用いられている。また、有機EL表示装置(OLED)、電界放出ディスプレイ装置(FED)なども、薄型の表示装置として知られている。液晶表示装置は、2つの基板の間に封じ込められた液晶組成物の配向を電界の変化により変え、2つの基板と液晶組成物を通過する光の透過度合いを制御することにより画像を表示させる装置である。

【0003】

このような液晶表示装置を含め、所定の階調値に対応する電圧を画面の各画素に印加する表示装置では、各画素に階調値に対応する電圧を印加するための画素トランジスタが配置されている。一般に、画面の1ライン分の画素トランジスタのゲートは一つの信号線(以下「走査信号線」という。)に接続され、この走査信号線は、駆動回路により、各ライン毎に順にこの画素トランジスタを導通させる導通電圧を出力するように制御されている。また、画面の上下を反転させても表示できるように、導通電圧を出力する順を順方向と逆方向との両方で行うことができる双方向走査(双方向スキャン)機能を有するものもある。特許文献1には、双方向走査を実現するための回路が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−73301号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図13は、双方向走査回路の一例を概略的に示す図である。この図に示されるように、双方向走査回路は、表示領域802の上部から順に走査する順走査と、表示領域802の下部から走査する逆走査があり、表示領域802の左右に配置された複数の出力回路から交互に出力して走査することにより、順走査及び逆走査を実現している。

【0006】

複数の出力回路は、スタート信号VSTをトリガーとして動作し、出力を行なう初段出力回路815と、表示領域を挟んで対向する出力回路からの出力をトリガーとして動作し、出力を行なう繰返し出力回路816と、対向する出力回路からの出力を入力しても最終段出力を出力する最終段出力回路817と、を有している。図14には、図13の右上及び左下に示される初段出力回路815の回路図が示されている。回路規模を縮小するために、順走査及び逆走査において同じスタート信号VSTが入力されることとしている。

【0007】

図15は、図13の右上に示される初段出力回路815(図14参照)において、順走査時に入力される信号とノードN1及びN2及び出力VOUT0信号の変化について示すタイミングチャートである。このタイミングチャートに示されるように、スタート信号VSTの入力により、ノードN1がHigh電位となり、その後クロック信号CK3のHigh電位により、出力VOUT0信号が出力されるようになっている。

【0008】

図16には、同じく図13の右上に示される初段出力回路815において、逆走査時の信号が入力された場合のタイミングチャートが示されている。この図に示されるように、逆走査時には、右上の初段出力回路815は、スタート信号VSTによりノードN1はHigh電位となるが、出力用のクロック信号CK3がHigh電位となる前に、クロック信号CK1によりノードN1電位が下げられるために出力されることはない。

【0009】

これらの図15及び図16のタイミングチャートに見られるように、クロック信号CK2及びCK3は、スタート信号VSTの出力の際に停止させている。しかしながら、このようにスタート信号VSTのタイミング等により停止を必要とするクロック信号発生回路の構成は回路規模が大きくなると共に、またコスト的にも無駄が多いため、図17に示されるような、連続したクロック信号のまま初段出力回路815を動作させることが考えられる。この場合にも、図17のタイミングチャートに示されるように、順走査の場合には、問題なく動作させることが可能である。しかしながら、逆走査を行なった場合には、図18のタイミングチャートに示されるように、右上の初段出力回路から出力が発生してしまう場合がある。

【0010】

本発明は、上述の事情を鑑みてされたものであり、クロック信号を停止させることなく双方向走査可能とすることにより、回路規模を縮小した双方向走査可能な表示装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の表示装置は、並行する複数の出力信号線に対して、順に画素トランジスタを導通させる電位である導通電位を印加する駆動回路を備え、前記駆動回路は、前記複数の出力信号線のうち一番端の出力信号線である初段出力信号線に出力するための回路である初段出力回路を有し、前記初段出力回路は、前記複数の出力信号線に対して順次導通電位を印加させるための開始の信号が印加されるスタート信号線と、クロック信号である第1クロック信号が印加される第1クロック信号線と、前記第1クロック信号とは導通電位となる時間が重ならないクロック信号である第2クロック信号が印加される第2クロック信号線と、前記初段出力信号線が、直接又は間接的にソース及びドレインのいずれか一方に接続され、前記第1クロック信号線が、直接又は間接的に前記ソース及びドレインのいずれか他方に接続されたトランジスタである第1トランジスタと、前記第1トランジスタのゲートと直接又は間接的に接続されたノードと、前記スタート信号線がゲートに接続され、前記スタート信号線が導通電位となることにより、前記第2クロック信号線と前記ノードとを導通させる第2トランジスタと、を備えることを特徴とする表示装置である。

【0012】

ここで、出力信号線は、表示領域内の走査信号線のほか、表示領域外のダミー回路等への出力信号線も含むこととし、表示領域内を含めて順次導通信号が印加されるすべての信号線含む意味である。

【0013】

また、本発明の表示装置において、前記スタート信号線の信号が導通電位になるタイミングは、前記第2クロック信号線の信号が導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前としてもよい。

【0014】

また、本発明の表示装置において、前記スタート信号線の信号がトランジスタを導通させない非導通電位になるタイミングは、前記第2クロック信号線が非導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前としてもよい。

【0015】

また、本発明の表示装置において、前記第1クロック信号及び前記第2クロック信号とは、前記導通電位となる時間が重ならないクロック信号である第3クロック信号が印加される第3クロック信号線と、トランジスタを導通させない非導通電位を保持する非導通電位保持線と、前記第3クロック信号線がゲートに接続され、前記第3クロック信号線が導通電位となることにより前記ノードと前記非導通電位保持線とを接続する第3トランジスタと、を更に備えることとしてもよい。

【0016】

また、本発明の表示装置において、前記複数の出力信号線であり、前記初段出力信号線の隣に配置された次段出力信号線と、前記次段出力信号線は、前記次段出力信号線が導通電位となることにより、整流装置を介して前記ノードと導通することとしてもよい。

【0017】

また、本発明の表示装置において、前記次段出力信号線は、画像が表示される表示領域を挟んで、前記初段出力信号線に前記導通電位が印加される側とは反対側で導通電位が印加される、こととしてもよい。

【0018】

また、本発明の表示装置において、前記駆動回路は、前記並行する複数の出力信号線のうち、一方の端の前記出力信号線に出力する前記初段出力回路である第1初段出力回路と、前記並行する複数の出力信号線のうち、他方の端の前記出力信号線に出力する前記初段出力回路である第2初段出力回路と、を有し、前記一方の端から順に前記画素トランジスタを導通させる順走査と、前記他方の端から順に前記画素トランジスタを導通させる逆走査とを切替えて行ない、前記スタート信号線は、前記順走査及び前記逆走査において共通である、こととしてもよい。

【図面の簡単な説明】

【0019】

【図1】本発明の一実施形態に係る表示装置を概略的に示す図である。

【図2】図1の表示パネルの構成を示す図である。

【図3】図2の駆動回路の構成について概略的に示す図である。

【図4】図3の右側駆動回路の繰返し出力回路の回路構成を具体的に示す図である。

【図5】図3の右側駆動回路の初段出力回路の回路構成を示す図である。

【図6】図3の右側駆動回路の最終段出力回路の回路構成を示す図である。

【図7】図5の右側駆動回路の初段出力回路の順走査時の動作のタイミングチャートである。

【図8】順走査時のスタート信号線VSTとクロック信号CK2とタイミング差について示す図である。

【図9】図5の右側駆動回路の初段出力回路の逆走査時の動作のタイミングチャートである。

【図10】図4の繰返し出力回路の変形例である出力回路を示す図である。

【図11】トランジスタT8を配置しない構成とした場合のタイミングチャートである。

【図12】図4の繰返し出力回路の変形例である出力回路を示す図である。

【図13】双方向走査回路の一例を概略的に示す図である。

【図14】図13の右上に示される初段出力回路の回路図である。

【図15】初段出力回路の順走査時の信号の変化を示すタイミングチャートである。

【図16】初段出力回路の逆走査時の信号の変化を示すタイミングチャートである。

【図17】連続したクロック信号により駆動した場合の初段出力回路の順走査時の信号の変化を示すタイミングチャートである。

【図18】連続したクロック信号により駆動した場合の初段出力回路の逆走査時の信号の変化を示すタイミングチャートである。

【発明を実施するための形態】

【0020】

以下、本発明の実施形態について、図面を参照しつつ説明する。なお、図面において、同一又は同等の要素には同一の符号を付し、重複する説明を省略する。なお、各信号に付された符号は、当該信号が印加される各信号線を示すものとする。

【0021】

図1には、本発明の一実施形態に係る表示装置100が概略的に示されている。この図に示されるように、表示装置100は、上フレーム110及び下フレーム120に挟まれるように固定された表示パネル200等から構成されている。なお、表示パネル200は液晶表示パネル、有機EL表示パネル等の薄膜トランジスタ基板を利用した表示パネルであればいずれの表示パネルでもよいが、本実施形態においては、表示パネル200は液晶表示パネルであるものとする。

【0022】

図2には、図1の表示パネル200の構成が示されている。表示パネル200は、TFT(Thin Film Transistor:薄膜トランジスタ)基板220とカラーフィルタ基板230の2枚の基板を有し、これらの基板の間には液晶組成物が封止されている。TFT基板220は、走査信号線G1〜Gnに対して、順に所定の電圧を印加する駆動回路210と、画素領域202において走査信号線G1〜Gnに垂直に交差するように延びる不図示の複数のデータ信号線に対して画素の階調値に対応する電圧を印加すると共に、駆動回路210を制御する駆動IC(Integrated Circuit)260とを有している。なお、駆動回路210は、図面に向って画素領域202の右側にある右側駆動回路212と、画素領域202の左側にある左側駆動回路214とを有している。

【0023】

図3は、駆動回路210の回路の構成について概略的に示す図である。この図に示されるように、右側駆動回路212は、奇数番目の走査信号線G2i−1(iは自然数)に対して各画素に配置されたTFTのゲートにTFTのソース・ドレイン間を導通させるためのHigh電位(導通電圧)を印加するための駆動回路であり、左側駆動回路214は、偶数番目の走査信号線G2iに対して各画素に配置されたTFTのゲートにTFTのソース・ドレイン間を導通させるためのHigh電位を印加するための駆動回路である。右側駆動回路212及び左側駆動回路214は、それぞれ、初段出力回路215と、最終段出力回路217と、初段出力回路215及び最終段出力回路217の間に配置される繰返し出力回路216と、を有している。右側駆動回路212の繰返し出力回路216は、左側駆動回路214の出力をトリガーとして出力を行い、左側駆動回路214の繰返し出力回路216は、右側駆動回路212の出力をトリガーとして出力を行う。初段出力回路215はスタート信号VSTをトリガーとして出力を行なう。なお、右側駆動回路212のスタート信号VSTと左側駆動回路214のスタート信号はVSTとは、同一の信号であり、同時に両方の初段出力回路215に入力される。初段出力回路215を除く右側駆動回路212は、クロック信号CK1及びCK3により駆動し、右側駆動回路212の初段出力回路215は、クロック信号CK1及びCK3に加えてクロック信号CK2を利用している。また、初段出力回路215を除く左側駆動回路214はクロック信号CK2及びCK4により駆動し、左側駆動回路214の初段出力回路215は、クロック信号CK2及びCK4に加えてクロックCK3を利用している。また、クロック信号CK1〜CK4は、順走査時には、CK1、CK2、CK3、CK4の順にHigh電位となる4相クロックであり、逆走査時には、CK4、CK3、CK2、CK1の順にHigh電位となる4相クロックである。

【0024】

順走査は、スタート信号VSTをトリガーとして、右側駆動回路212の初段出力回路215の出力Vout0に対するHigh電位の出力から開始し、右側駆動回路212の最終段出力回路217で終了する。逆走査は、スタート信号VSTをトリガーとして、左側駆動回路214の初段出力回路215の出力Vout0に対する出力で開始し、左側駆動回路214の最終段出力回路217で終了する。

【0025】

図4には、右側駆動回路212の繰返し出力回路216の回路構成が具体的に示されている。ここで、図4に示された端子の名称は、後述する図7のタイミングチャートにおける説明のために、図3の繰返し出力回路216の端子の名称ではなく、図3の駆動回路210の外部端子の名称に変更している。図4に示されるように、繰返し出力回路216は、2つのクロックCK1及びCK3により動作する回路であり、2つの走査信号線G2i−1及びG2i+1へ出力する部分が示されている。なお、符号Tはトランジスタを示し、符号Nはノードを示す。なお、各トランジスタはLTPS(Low Temperature Poly Silicon)により形成されている。

【0026】

この図に示されるように、走査信号線G2i−1へ出力するための回路は、順走査時に回路入力となるダイオードトランジスタT1と、後述するトランジスタT5のゲート電極をトランジスタの非導通電圧であるLow電位(VGL)に固定するトランジスタT2と、保持ノードN2を充電するトランジスタT3と、保持ノードリセット用トランジスタT4と、走査信号線G2i−1へHigh電位を出力するためのトランジスタT5と、保持ノードN2により走査信号線G2i−1を電圧VGLに固定するトランジスタT6と、順走査時に入力信号により保持ノードN2をリセットするトランジスタT7と、初期リセット用トランジスタT8と、トランジスタT5のゲート電極リセット用トランジスタT9と、トランジスタT5のゲートの昇圧を中間電圧VDHで制限する電圧緩和用トランジスタT10と、トランジスタT3で充電した電圧を中間電圧VDHで降圧するトランジスタT11と、逆走査時に回路入力となるダイオードトランジスタT12と、逆走査時に入力信号により保持ノードN2を電圧VGLにリセットするトランジスタT13とから構成されている。なお、中間電圧VDHは、走査信号線G2i−1のHigh電位であるVGHより低い電圧であって、トランジスタを導通させる電位を有している。ここでは、中間電圧VDHもHigh電位として表している。

【0027】

図5には、回路の初段となる初段出力回路215の回路構成が示されている。初段出力回路215の構成は、基本的に繰返し出力回路216の構成と同様であるが、スタート信号VSTは、トランジスタT7のゲートに接続されると共に、トランジスタT1のゲートに接続され、トランジスタT1のドレイン側はクロック信号CK2に接続されている。また、初期リセット用トランジスタT8が配置されない構成となっている。この初段出力回路の動作については、後述する。

【0028】

図6には、回路の最終段となる最終段出力回路217の回路構成が示されている。最終段出力回路217は、繰返し出力回路216と比較して、検査用端子に接続されるトランジスタT14及びT15を追加した構成となっている。

【0029】

図7には、図5の右側駆動回路212の初段出力回路215の順走査時の動作のタイミングチャートが示されている。以下、図7のタイミングチャートを用いて、初段出力回路215の動作について説明する。まず、初段出力回路215は、時刻t1のクロック信号CK2のタイミングより微少時間ts1だけ前に(図8参照)、スタート信号線VSTにHigh電位を入力することにより、トランジスタT7を導通させ、ノードN2をLow電位(VGL)と接続させLow電位とする。次にクロック信号CK2がHigh電位となることによりトランジスタT1を導通させ、保持ノードN1の電位をHighに設定し、トランジスタT5を導通させる。このように、クロック信号CK2がHigh電位になる少し前にスタート信号をHigh電位にすることにより、ノードN2をノードN1がHigh電位になる前にLow電位に落とすことができるため、貫通電流を防止することができ、信頼性の向上および消費電力を抑えることが出来る。また、スタート信号VSTの立ち下がりのタイミングは、クロック信号CK2の立ち下がりのタイミングより微少時間ts2だけ前になっている(図8参照)。これにより、トランジスタT1を先に遮断して、ノードN1をHighに維持することができる。ここで微少時間は、クロック信号の周期より十分に小さい時間であることを意味する。

【0030】

引き続き、t2のタイミングにおいて、クロック信号CK3がHigh電位になると、トランジスタT5のゲートの電圧は、所謂ブートストラップ効果により更に昇圧され、出力Vout0には、High信号が出力され、引き続き、クロックCK3の動作に追従して、Low信号が出力される。

【0031】

次に、t3のタイミングにおいて、CK1がHighになることにより、T3が導通し、ノードN2をHigh電位に上げると共に、トランジスタT9が導通するため、ノードN1はLow電位に下げられる。ノードN1はトランジスタT10を介してトランジスタT5のソース・ドレイン間を遮断すると共に、ノードN2のHigh電位によりトランジスタT6が導通することにより、出力Vout0は、Low電位(VGL)と接続される。

【0032】

ここで、トランジスタT10は、クロック信号CK3がHighになることにより、昇圧された電圧に耐えられるようにトランジスタを2つ重ねて配置するダブルゲート構成として高耐圧化している。出力された出力Vout0にHigh信号は、左側駆動回路214の繰返し出力回路216への入力信号となり、上述の動作と同様の動作により、走査信号線G1にHigh信号を出力する。

【0033】

図9には、図5の右側駆動回路212の初段出力回路215の逆走査時の動作のタイミングチャートが示されている。図7と比較して、CK1〜CK4の位相が異なり、逆順序でHigh電位となっている。まず、t4のタイミングにおいて、左側駆動回路214の初段出力回路215をスタートさせるために、クロック信号CK3に合わせてスタート信号VSTがHigh電位となる。これにより、左側駆動回路214の初段出力回路215においては、ノードN1がHigh電位となり、ノードN2がLow電位となるが、右側駆動回路212においては、トランジスタT1が導通してCK2のLow電位より、動作を開始しない。これにより、逆走査の際にスタート信号VSTをHigh電位になったとしても、右側駆動回路212の初段出力回路215は走査を開始しない。

【0034】

以上説明したように、上述の実施形態においては、クロック信号を停止させることなく双方向走査可能となるため、回路規模を縮小して双方向走査可能な表示装置とすることができる。

【0035】

また、上述の実施形態においては、順方向に走査する回路と逆方向に走査する回路は、同じ回路を利用するため、逆方向の走査のための回路を配置する必要がなく、回路規模を縮小でき、表示装置の額縁領域を小さくすることができる。

【0036】

また、トランジスタを重ねて配置するダブルゲート構成としているため、LTPSトランジスタであっても高耐圧の回路とすることができる。

【0037】

図10には、上述した図4の繰返し出力回路216の変形例である出力回路301が示されている。繰返し出力回路216との違いは、トランジスタT8が配置されていない点であり、上述の実施形態においては、トランジスタT8は、スタート信号VSTにより保持ノードN2を充電するために配置されている。しかしながら、全クロック信号CK1〜CK4をHigh電位とすることでも保持ノードN2を充電することが可能であることから、図11に示されるように、スタート信号VSTの前にクロック信号CK1〜CK4を同時にHigh電位とする駆動方法を用いることにより、トランジスタT8を配置しない構成とし、より回路規模を縮小させることが可能である。

【0038】

図12には、上述した図4の繰返し出力回路216の変形例である出力回路302が示されている。繰返し出力回路216との違いは、トランジスタT8及びT11が配置されていない点である。トランジスタT11は、トランジスタT2及びT6のゲートにクロック信号CK1〜CK4の高電圧が直接かからないように配置されていたが、製造ラインのNa汚染等が抑えられる場合には、トランジスタT11を配置しない構成とし、より回路規模を縮小させることが可能である。

【0039】

なお、上述の実施形態においては、High電位を導通電位として、High電位がゲートに入力されることで、ソース・ドレイン間が導通するNMOS型のトランジスタとしたが、Low電位を導通電位として、Low電位がゲートに入力することによりソース・ドレイン間が導通するPMOS型のトランジスタとしてもよい。

【0040】

また、上述の実施形態においては、クロック信号を4相クロックを用いることとしたが、これ以外のクロック信号を用いて実現してもよい。

【0041】

また、上述の各実施形態の液晶表示装置は、IPS(In-Plane Switching)方式、VA(Vertically Aligned)方式及びTN(Twisted Nematic)方式のいずれの方式の液晶表示装置であっても適用することができる。また、液晶表示装置に限らず、有機EL表示装置、電界放出ディスプレイ装置(FED)及び駆動回路を用いるその他の表示装置に用いることができる。

【符号の説明】

【0042】

100 表示装置、110 上フレーム、120 下フレーム、200 表示パネル、202 画素領域、210 駆動回路、212 右側駆動回路、214 左側駆動回路、215 初段出力回路、216 繰返し出力回路、217 最終段出力回路、220 TFT基板、230 カラーフィルタ基板、260 駆動IC、301 出力回路、302 出力回路、802 表示領域、815 初段出力回路、816 繰返し出力回路、817 最終段出力回路。

【特許請求の範囲】

【請求項1】

並行する複数の出力信号線に対して、順に画素トランジスタを導通させる電位である導通電位を印加する駆動回路を備え、

前記駆動回路は、前記複数の出力信号線のうち一番端の出力信号線である初段出力信号線に出力するための回路である初段出力回路を有し、

前記初段出力回路は、

前記複数の出力信号線に対して順次導通電位を印加させるための開始の信号が印加されるスタート信号線と、

クロック信号である第1クロック信号が印加される第1クロック信号線と、

前記第1クロック信号とは導通電位となる時間が重ならないクロック信号である第2クロック信号が印加される第2クロック信号線と、

前記初段出力信号線が、直接又は間接的にソース及びドレインのいずれか一方に接続され、前記第1クロック信号線が、直接又は間接的に前記ソース及びドレインのいずれか他方に接続されたトランジスタである第1トランジスタと、

前記第1トランジスタのゲートと直接又は間接的に接続されたノードと、

前記スタート信号線がゲートに接続され、前記スタート信号線が導通電位となることにより、前記第2クロック信号線と前記ノードとを導通させる第2トランジスタと、を備えることを特徴とする表示装置。

【請求項2】

前記スタート信号線の信号が導通電位になるタイミングは、前記第2クロック信号線の信号が導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前である、ことを特徴とする請求項1に記載の表示装置。

【請求項3】

前記スタート信号線の信号がトランジスタを導通させない非導通電位になるタイミングは、前記第2クロック信号線が非導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前である、ことを特徴とする請求項1又は2に記載の表示装置。

【請求項4】

前記第1クロック信号及び前記第2クロック信号とは、前記導通電位となる時間が重ならないクロック信号である第3クロック信号が印加される第3クロック信号線と、

トランジスタを導通させない非導通電位を保持する非導通電位保持線と、

前記第3クロック信号線がゲートに接続され、前記第3クロック信号線が導通電位となることにより前記ノードと前記非導通電位保持線とを接続する第3トランジスタと、を更に備えることを特徴とする請求項1乃至3のいずれか一項に記載の表示装置。

【請求項5】

前記複数の出力信号線であり、前記初段出力信号線の隣に配置された次段出力信号線と、

前記次段出力信号線は、前記次段出力信号線が導通電位となることにより、整流装置を介して前記ノードと導通する、ことを特徴とする請求項1乃至4のいずれか一項に記載の表示装置。

【請求項6】

前記次段出力信号線は、画像が表示される表示領域を挟んで、前記初段出力信号線に前記導通電位が印加される側とは反対側で導通電位が印加される、ことを特徴とする請求項5に記載の表示装置。

【請求項7】

前記駆動回路は、

前記並行する複数の出力信号線のうち、一方の端の前記出力信号線に出力する前記初段出力回路である第1初段出力回路と、

前記並行する複数の出力信号線のうち、他方の端の前記出力信号線に出力する前記初段出力回路である第2初段出力回路と、を有し、

前記一方の端から順に前記画素トランジスタを導通させる順走査と、前記他方の端から順に前記画素トランジスタを導通させる逆走査とを切替えて行ない、

前記スタート信号線は、前記順走査及び前記逆走査において共通である、ことを特徴とする請求項1乃至6のいずれか一項に記載の表示装置。

【請求項1】

並行する複数の出力信号線に対して、順に画素トランジスタを導通させる電位である導通電位を印加する駆動回路を備え、

前記駆動回路は、前記複数の出力信号線のうち一番端の出力信号線である初段出力信号線に出力するための回路である初段出力回路を有し、

前記初段出力回路は、

前記複数の出力信号線に対して順次導通電位を印加させるための開始の信号が印加されるスタート信号線と、

クロック信号である第1クロック信号が印加される第1クロック信号線と、

前記第1クロック信号とは導通電位となる時間が重ならないクロック信号である第2クロック信号が印加される第2クロック信号線と、

前記初段出力信号線が、直接又は間接的にソース及びドレインのいずれか一方に接続され、前記第1クロック信号線が、直接又は間接的に前記ソース及びドレインのいずれか他方に接続されたトランジスタである第1トランジスタと、

前記第1トランジスタのゲートと直接又は間接的に接続されたノードと、

前記スタート信号線がゲートに接続され、前記スタート信号線が導通電位となることにより、前記第2クロック信号線と前記ノードとを導通させる第2トランジスタと、を備えることを特徴とする表示装置。

【請求項2】

前記スタート信号線の信号が導通電位になるタイミングは、前記第2クロック信号線の信号が導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前である、ことを特徴とする請求項1に記載の表示装置。

【請求項3】

前記スタート信号線の信号がトランジスタを導通させない非導通電位になるタイミングは、前記第2クロック信号線が非導通電位になるタイミングより、クロック信号の周期より十分小さい微少時間だけ前である、ことを特徴とする請求項1又は2に記載の表示装置。

【請求項4】

前記第1クロック信号及び前記第2クロック信号とは、前記導通電位となる時間が重ならないクロック信号である第3クロック信号が印加される第3クロック信号線と、

トランジスタを導通させない非導通電位を保持する非導通電位保持線と、

前記第3クロック信号線がゲートに接続され、前記第3クロック信号線が導通電位となることにより前記ノードと前記非導通電位保持線とを接続する第3トランジスタと、を更に備えることを特徴とする請求項1乃至3のいずれか一項に記載の表示装置。

【請求項5】

前記複数の出力信号線であり、前記初段出力信号線の隣に配置された次段出力信号線と、

前記次段出力信号線は、前記次段出力信号線が導通電位となることにより、整流装置を介して前記ノードと導通する、ことを特徴とする請求項1乃至4のいずれか一項に記載の表示装置。

【請求項6】

前記次段出力信号線は、画像が表示される表示領域を挟んで、前記初段出力信号線に前記導通電位が印加される側とは反対側で導通電位が印加される、ことを特徴とする請求項5に記載の表示装置。

【請求項7】

前記駆動回路は、

前記並行する複数の出力信号線のうち、一方の端の前記出力信号線に出力する前記初段出力回路である第1初段出力回路と、

前記並行する複数の出力信号線のうち、他方の端の前記出力信号線に出力する前記初段出力回路である第2初段出力回路と、を有し、

前記一方の端から順に前記画素トランジスタを導通させる順走査と、前記他方の端から順に前記画素トランジスタを導通させる逆走査とを切替えて行ない、

前記スタート信号線は、前記順走査及び前記逆走査において共通である、ことを特徴とする請求項1乃至6のいずれか一項に記載の表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−83678(P2013−83678A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−221543(P2011−221543)

【出願日】平成23年10月6日(2011.10.6)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月6日(2011.10.6)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【Fターム(参考)】

[ Back to top ]