表面実装可能な集積回路のパッケージ化機構

【課題】表面実装可能な集積回路のパッケージ化機構を提供する。

【解決手段】集積回路(IC)パッケージが開示される。ICパッケージは、上部層、中間層、及び底部層を有する基板と、基板の上部層に埋め込まれたミリメートル波アンテナのアレイと、基板の底部層に実装されたモノリシック・マイクロ波集積回路(MMIC)とを含む。1つの実施形態において、プリント回路基板(PCB)への表面実装のための第2のレベルの相互接続が基板の底部層に設けられる。

【解決手段】集積回路(IC)パッケージが開示される。ICパッケージは、上部層、中間層、及び底部層を有する基板と、基板の上部層に埋め込まれたミリメートル波アンテナのアレイと、基板の底部層に実装されたモノリシック・マイクロ波集積回路(MMIC)とを含む。1つの実施形態において、プリント回路基板(PCB)への表面実装のための第2のレベルの相互接続が基板の底部層に設けられる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は集積回路パッケージに関し、より具体的には、ミリメートル波集積回路パッケージに関する。

【背景技術】

【0002】

ビーム形成及びステアリングを行うミリメートル波システムは、典型的には、多数のアンテナ素子、集積回路、及び相互接続を含む。このようなシステムは、高いデータ転送速度の短距離無線接続を顧客アプリケーションに提供するための実現可能な機構の基礎である。性能及びコストの目的を達成するために、一般的な課題は、大量製造及び組立て工程と両立できる集積化プラットフォーム・パッケージを開発することである。

このような集積パッケージは、集積レベルが増加するのに伴って、様々な機能を収容すると予想される。これらの機能には、中でも、低損失無共振のmm波信号経路の提供、多層アンテナ素子とそれらのフィード・ネットワークの埋め込み、局部発振器(LO)、中間周波数(IF)分配及び受動回路の統合、並びに制御層とバイアス層の組み込みが含まれる。

【発明の概要】

【発明が解決しようとする課題】

【0003】

ミリメートル波アンテナが集積回路(IC)と統合される典型的なシナリオにおいては、アンテナとICの両方が、許容できる性能を保証するために一つの基板の上部層の上に配置される。この手法は、1つ又はそれ以上のICの上に配置された別個のRFポートによって個々に駆動される必要がある多数のアンテナ素子が存在するとき、問題に遭遇する。第1に、ルーティング輻輳が素子の数を制限することになる。

さらに、IC及びアンテナを十分な間隔で同じ表面上に配置する必要があるので、パッケージが大きくなる。パッケージの大きさが増大するのに伴って、コストが増加し、場合によっては、基板が製造するのに大きくなりすぎる可能性さえある。最後に、ICからの熱除去が難しくなる。

【課題を解決するための手段】

【0004】

一実施形態により、集積回路(IC)パッケージが開示される。ICパッケージは、上部層、中間層、及び底部層を有する基板と、基板の1つの層(例えば、上部層)に埋め込まれたミリメートル波アンテナのアレイと、基板の別の異なる層(例えば、底部層)の上に実装されたモノリシック・マイクロ波集積回路(MMIC)とを含む。

別の実施形態により、システムが開示される。このシステムは、上部層、中間層、及び底部層を有する基板と、基板の1つの層(例えば、上部層)に埋め込まれたミリメートル波アンテナのアレイと、基板の別の層(例えば、底部層)の上に実装されたモノリシック・マイクロ波集積回路(MMIC)とを含む集積回路(IC)パッケージを含む。プリント回路基板(PCB)は、基板のこの第2の層の上に実装される。

【図面の簡単な説明】

【0005】

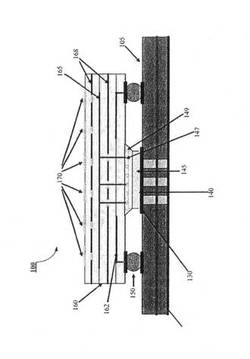

【図1】両面型表面実装集積ミリメートル波パッケージの1つの実施形態を示す。

【図2】基板の1つの実施形態を示す。

【図3】両面型表面実装集積ミリメートル波パッケージの別の実施形態を示す。

【図4】両面型表面実装集積ミリメートル波パッケージのさらに別の実施形態を示す。

【図5】両面型表面実装集積ミリメートル波パッケージのさらに別の実施形態を示す。

【発明を実施するための形態】

【0006】

本発明は、以下の説明、並びに本発明の実施形態を例示するために用いられる添付の図面を参照することによって、最も良く理解することができる。

ミリメートル波モジュールの放射素子と集積回路素子を統合するための表面実装可能なパッケージング・スキームを説明する。1つの実施形態によれば、アンテナは、基板の上部層内に組み込まれる。モノリシック・マイクロ波集積回路(MMIC)及びボール・グリッド・アレイ(BGA)は、基板の底面に取り付けられる。

【0007】

上述の問題の大部分を解決するか又は軽減するための手法は、アンテナが上部に配置され、ICがパッケージ基板の低部に配置された両面型パッケージを使用することである。

従って、十分な性能を有するミリメートル波機能の高レベルの統合を可能にする両面型パッケージングを実施する機構を説明する。

以下の説明において、多数の詳細が示される。しかしながら、当業者であれば、これらの特定の詳細なしに本発明の実施形態を実施できることは明らかであろう。他の場合には、説明の理解を不明瞭にすることを避けるために、周知の構造体、デバイス及び技術は、詳細には示されていない。従って、この説明は、限定するのではなく例証するものと考えられたい。

【0008】

本明細書における「1つの実施形態」又は「一実施形態」への言及は、特定の特徴、構造体、又は実施形態に関連して説明される特性が、本発明の少なくとも1つの実施形態に含まれることを意味する。本明細書内の各所における「1つの実施形態において」という語句の出現は、必ずしも全てが同じ実施形態を指すわけではない。

【0009】

図1は、両面型表面実装ミリメートル波集積システム100の1つの実施形態を示す。

システム100は、プリント回路基板(PCB)105の上に実装された多層基板160を含む。基板160は、誘電体層と、2つの誘電体層の界面に配置された金属層とを含む。本明細書において説明されるように、単独での「層」という用語への如何なる言及も「金属層」を示す。1つの実施形態において、基板160は、High Temperature Co−Fired Ceramics(HTCC)又はLow Temperature Co−Fired Ceramics(LTCC)アルミナによる大量生産に適しているが、例えば、積層ベース又はビルドアップ有機物のような他の基板型を用いることもできる。さらに、1つの実施形態において、基板160は、キャビティ、又は、側壁メタライゼーション等のような特定の構造部を含まない。

【0010】

1つの実施形態において、アンテナ・アレイ170は、基板の上部に埋め込まれる。1つの実施形態において、アンテナ・アレイ170は、多層上の金属パターンを有する。1つの実施形態において、上部の2つの層は、アンテナ・アレイ170用に用いられる。アンテナ・アレイ170はフィードされ、それらの分配は、基板160の幾つかの内部層を用いて実現される。基板160の底部においては、1つ又はそれ以上のMMIC145が基板160にフリップチップ実装される。代替的な実施形態において、例えば、チップと基板の間の相互接続としてのワイヤ・ボンドによる上向き(チップの底面が基板に接合される)実装のような、他の実装及び構成が用いられ、このような場合には、チップは、ミリメートル波動作に重要なワイヤ・ボンド長を短くするために、キャビティ内で上向きに配置される。パッケージ基板内のキャビティが望ましくない場合には、チップは薄く重ね合わせることができる。しかしながら、チップが薄すぎると、取り扱い及び組立ての問題が生じ得る。

【0011】

伝送ライン165及び接地平面168は、基板160の内部に含まれる。伝送ライン165は、アンテナ・アレイ170内のアンテナと1つ又はそれ以上のMMIC145との間でミリメートル波信号を伝送する。

1つの実施形態によれば、アンテナ・アレイ170の素子の各々は、MMIC145のうちの1つの上に、対応するミリメートル波ポートを有する。フリップチップ・バンプ147は、アンダーフィル149によって、対応するアンテナ・アレイ170の素子をMMIC145に結合する。その結果、MMIC145から発したミリメートル波信号は、基板160の中間層に伝わり、そこで、これらの信号は、それぞれのアンテナ・フィード・ポイント165に分配され、結局アンテナ・アレイ170内のアンテナに結合される。

【0012】

他のアナログ信号(例えば、LO及びIF信号、バイアス及び制御信号)は、アナログ信号ルーティング162を介して基板160の底部層の一部を用いて伝送される。ボール・グリッド・アレイBGAボール150は、パッケージをPCB105上に表面実装することを可能にするように、基板160の底部に取り付けられる。1つの実施形態において、BGAボール150の大きさは、フリップチップ実装されるMMICダイ145の結合した高さがBGAボール150の高さよりも確実に低くなるように選択される。

【0013】

さらに別の実施形態において、表面実装操作中、BGAボール150がリフローするとき、ダイ145はハード・ストップとして機能し、BGAボール150が完全に潰れるのを防止する。1つの実施形態において、熱対応パッドがダイの下に配置されて、PCB105への低い熱抵抗接触を確実にする。さらに別の実施形態においては、はんだ付け可能パッド130が、ダイ145の直下のPCB105上に配置され、ダイ145の裏面は、金属成分140によってメタライズされる。従って、ダイ145の裏面は表面実装中にはんだ付けして、PCB105に対するダイ145の良好な熱的接続を確実にすることができる。

【0014】

1つの実施形態によれば、システム100は、上面のアンテナ・アレイ170と底面のMMIC145との統合のための多層基板160の構成と、表面実装組立体のための基板160底面の構成と、パッケージをPCB105に実装するための構成とを含む。

【0015】

多層基板構成

図2は、基板160の1つの実施形態の断面図を示す。埋め込んだ主要機能に基づいて、それらの層は、接地平面168によって分離される、上部210、中間部220及び底部230の3つのグループに分けられる。1つの実施形態において、上部層210は、平面アンテナ素子に割り当てられる。多くの場合、パッチ積層化のような技術を実施してアンテナの性能を高めるために多層が必要とされる。代替的な実施形態において、単一層を平面アンテナ素子用に用いることができることに留意されたい。誘電体層の厚さは、アンテナ設計の考慮事項から決定することができる。上部接地平面168は、アンテナ層210をパッケージの残り部分から絶縁し、これにより電磁干渉からの耐性を与える。

【0016】

中間層220は、アンテナへのミリメートル波信号の分配に用いられる。1つの実施形態において、アンテナ素子は、フィード・ラインを共有せず、ミリメートル波のフィード・ラインの数は、アンテナ・アレイ内の素子の数と同じになる。1つの実施形態において、簡潔な方法で多数のフィード・ラインを効率的に分配するために、1つ又はそれ以上の層が用いられる。接地平面168は他の層の回路からの遮蔽を与える。1つの実施形態によれば、信号ライン以外のメタライゼーションは、均一な電磁環境のためにこれらの層においては最小に保たれる。1つの実施形態において、信号トレースからの遮断領域は、トレース幅及び基板層の厚さ等のような因子に依存する設計パラメータである。他の実施形態においては、他の因子がこの設計パラメータに影響を与える可能性がある。単一のTEMモードの伝搬を向上させるために、フェンシングよって接地を有するストリップ・ラインを信号ライン用に用いることができるが、ここで、フェンシングは、信号トレースが経路設定される際にその信号トレースの両側の特定の距離のところにビアを配置することを言う。トレースから接地ビアまでの距離及びビアの間の間隔は、設計パラメータである。

【0017】

底部層230は、DC信号、制御信号及び低周波アナログ信号用に用いられる。1つの実施形態において、高集積MMIC145は、LO及びIF信号ラインに加えて多数のDC及び制御ラインを必要とする。これに適合させるため、並びに、ダイ145及びBGA150が密集する底部層230を補うために、2つ又はそれ以上の層を用いることができる。1つの実施形態において、パッケージは、表面実装用途を意図したものであり、従ってこれらの層は、パッケージ直下のPCBの事前には未知の電気特性を認識する。このように、明確な電磁界面がないので、ミリメートル波信号ルーティングは、底部層において最小にする必要がある。

【0018】

上述のように、ミリメートル波信号の分配は、接地平面168によって遮蔽された中間層220の内部に留められる。さらに、多層を上部及び底部に付加して他の機能を収容する。これにより、基板160はミリメートル波の波長スケールにおいて相対的に厚くなる。従って、ミリメートル波信号は、一つの層から他の層に進む際に、垂直方向にかなりの距離を横断しなければならない。1つの実施形態において、単純なビア遷移部、又は、従来の準同軸のビア遷移部でさえも、長い垂直的な相互接続内に存在することになる共振、高次モード及び反射を抑制するのに十分ではない。

従って、1つの実施形態において、この垂直相互接続の問題の解決法として、補償用垂直相互接続機構が実施される。この垂直相互接続機構において、ミリメートル波信号は、基板の内側金属層である補償用垂直相互接続215の上をフリップチップ・パッド208に至るまで伝送される。

【0019】

さらに別の実施形態において、補償構造体は層遷移構造体に組み込まれる。このような実施形態においては、補償構造体の配置、大きさ及び形状は、モデリング処理によって決定される。さらに別の実施形態において、モデリング処理には、3次元(3D)電磁ツール(例えば、Ansoft CorporationからのHigh Frequency Structure Simulator(HFSS))及び回路シミュレータ(例えば、Agilent Technologies,Inc.からの高度設計システム(ADS))を利用する最適化法が含まれる。

1つの実施形態によれば、補償用垂直相互接続は、底部のMMICの全てのミリメートル波ポートの位置に又はその極めて近くに配置される。他の実施形態においては、同様の垂直相互接続が、ミリメートル波信号を中間層から上部層に伝送する必要があるフィード・スキームにおけるアンテナ・フィード・ネットワーク内で用いられる。

【0020】

基板底面構成

1つの実施形態によれば、基板160の底面は、MMIC145及びパッケージの第2のレベルの相互接続面の両方として構成される。1つ又はそれ以上のMMIC145は、標準的なフリップチップ組立て技術を用いて基板160にフリップチップ実装される。上述のように、他の実装技術を用いることができる。それらの低い電気的寄生振動により、フリップチップ相互接続は、mm波周波数において十分な性能をもたらすことができる。

さらに別の実施形態において、ダイ145は、高周波動作のための短いワイヤ・ボンド長を達成するためにキャビティ実装される。この構成におけるフリップチップ実装の別の利点は、ダイ145の裏面が露出するので効率的な熱除去のために使用できることである。

【0021】

第2のレベルの相互接続として、ボール150が1つ又はそれ以上の列内で基板160の外周付近に配置されるBGA型接続部が用いられる。1つの実施形態において、周波数変換、周波数逓倍及び位相シフトのような、全てのミリメートル波処理がMMIC145内で実施され、アンテナを介した放射を除いてミリメートル信号が完全にパッケージ内に包含されるようになる。この場合、低周波数IF、LO及び基準信号のみが、パッケージ外部の電源から供給される。

このようなシナリオにおいては、第2のレベルの相互接続は低周波数において十分な性能を有し、従ってその仕様を緩和する。結果として、他の型の相互接続を実施することが可能になる。図3は、BGAボール150ではなくリード300が基板160をPCB105に結合させるシステム100の実施形態を示す。

【0022】

パッケージ実装構成

1つの実施形態において、フリップチップ実装されたダイ145及びBGAボール150は、パッケージの表面実装面にあり、このパッケージはPCB105に取り付ける準備ができた状態にある。パッケージをPCB105に取り付けることができる幾つかの方法がある。図1に示されるように、ダイ145のメタライズされた裏面140が、表面実装操作中にPCB105上のはんだ付け可能な実装用パッド130と結合する。ダイと実装用パッドの間のギャップの大きさは考慮する必要がある。BGAにおける良好なはんだ接続のために、はんだボール150はリフロー中に十分に潰れる必要がある。ダイ145はPCB105に対するハード・ストップとして機能するので、小さすぎるギャップは、はんだボール150が良好な接続を形成するのを妨げる。

【0023】

別の実施形態において、パッケージはPCB105に取り付けられるが、一方ダイ145は表面実装中にはPCB105と結合しない。図4は、システム100のこのような実施形態を示す。図4に示されるように、ダイ145がPCB105に接触できるレベルまでBGAはんだボール150が潰れるのを防止することが重要である。1つの実施形態において、これは、堅固な芯のBGAボール、又は、ダイとPCBの間にギャップが存在するような大きさにする必要がある数個のより小さな非リフロー型ボールを用いて達成される。

第3の取付け方法において、PCB105は、ダイ145の大きさよりも大きな貫通切欠き部を含む。図5は、システム100のこのような実施形態を示す。図5に示されるように、切欠き部505はダイの真下に配置されることになる。表面実装中、BGAボール150が潰れつつあるとき、ダイ145は切欠き部に滑り込む。ダイ145とPCB105の間にギャップが必要ないので、この構成は、より小さなBGAボール150の使用を可能にすることになる。ダイ145の裏面は、切欠き部505を通して露出することになるので、例えば、ヒートシンクを用いて、熱接続を確立することができる。

【0024】

別の実施形態において、ダイ145の裏面は、熱接続のためにメタライズされない。このような実施形態においては、熱接着剤を用いて薄い金属パドル510を裏面に接着することができ、次いで金属パドル510をPCB105に取り付けて、低抵抗接続部を確立することができる。

上述のシステムは、アンテナが基板の上部層に組み込まれ、MMIC及び表面実装用BGAが底部に取り付けられた厚い多層基板をベースとする高集積ミリメートル波パッケージを形成する機構を説明する。この機構は、このような従来にないパッケージ化体を製造する困難を克服し、大量製造プロセスを用いて実施することができる。

【0025】

本発明の例示的な実施形態の前述の説明においては、1つ又はそれ以上の種々の本発明の態様を理解するのに役立つ開示を能率的にする目的で、本発明の種々の特徴が場合によりその単一の実施形態、図面、又は説明にまとめられていることを認識されたい。しかしながら、この開示方法は、請求された本発明が各々の請求項において明白に詳述されたものよりも多くの特徴を要求する意図を示すものと解釈されるべきではない。むしろ、添付の請求項が示すように、本発明の態様は、単一の前述の開示された実施形態の全ての特徴よりも少ない特徴にある。従って、詳細な説明に添付された請求項は、その結果、この詳細な説明に明確に組み込まれ、各々の請求項は、それ自体で本発明の別個の実施形態として主張するものである。

【0026】

前述の説明は、特定の実施形態に向けられた。当業者であれば、説明された実施形態に修正を加え、利点の全て又は一部を達成することができることは明らかであろう。従って、添付の特許請求の範囲の目的は、そのような変形及び修正の全てを本発明の精神及び範囲内に入るものとして包含することである。

【符号の説明】

【0027】

100:システム

105:プリント回路基板(PCB)

130:はんだ可能パッド

140:金属成分

145:モノリシック・マイクロ波集積回路(MMIC)

147:フリップチップ・バンプ

149:アンダーフィル

150:ボール・グリッド・アレイ(BGA)

160:基板

162:信号ルーティング

165:伝送ライン(アンテナ・フィード・ポイント)

168:接地面

170:アンテナ・アレイ

210:上部層(アンテナ層)

220:中間層

230:底部層

300:リード

505:切欠き部

510:金属パドル

【技術分野】

【0001】

本発明の実施形態は集積回路パッケージに関し、より具体的には、ミリメートル波集積回路パッケージに関する。

【背景技術】

【0002】

ビーム形成及びステアリングを行うミリメートル波システムは、典型的には、多数のアンテナ素子、集積回路、及び相互接続を含む。このようなシステムは、高いデータ転送速度の短距離無線接続を顧客アプリケーションに提供するための実現可能な機構の基礎である。性能及びコストの目的を達成するために、一般的な課題は、大量製造及び組立て工程と両立できる集積化プラットフォーム・パッケージを開発することである。

このような集積パッケージは、集積レベルが増加するのに伴って、様々な機能を収容すると予想される。これらの機能には、中でも、低損失無共振のmm波信号経路の提供、多層アンテナ素子とそれらのフィード・ネットワークの埋め込み、局部発振器(LO)、中間周波数(IF)分配及び受動回路の統合、並びに制御層とバイアス層の組み込みが含まれる。

【発明の概要】

【発明が解決しようとする課題】

【0003】

ミリメートル波アンテナが集積回路(IC)と統合される典型的なシナリオにおいては、アンテナとICの両方が、許容できる性能を保証するために一つの基板の上部層の上に配置される。この手法は、1つ又はそれ以上のICの上に配置された別個のRFポートによって個々に駆動される必要がある多数のアンテナ素子が存在するとき、問題に遭遇する。第1に、ルーティング輻輳が素子の数を制限することになる。

さらに、IC及びアンテナを十分な間隔で同じ表面上に配置する必要があるので、パッケージが大きくなる。パッケージの大きさが増大するのに伴って、コストが増加し、場合によっては、基板が製造するのに大きくなりすぎる可能性さえある。最後に、ICからの熱除去が難しくなる。

【課題を解決するための手段】

【0004】

一実施形態により、集積回路(IC)パッケージが開示される。ICパッケージは、上部層、中間層、及び底部層を有する基板と、基板の1つの層(例えば、上部層)に埋め込まれたミリメートル波アンテナのアレイと、基板の別の異なる層(例えば、底部層)の上に実装されたモノリシック・マイクロ波集積回路(MMIC)とを含む。

別の実施形態により、システムが開示される。このシステムは、上部層、中間層、及び底部層を有する基板と、基板の1つの層(例えば、上部層)に埋め込まれたミリメートル波アンテナのアレイと、基板の別の層(例えば、底部層)の上に実装されたモノリシック・マイクロ波集積回路(MMIC)とを含む集積回路(IC)パッケージを含む。プリント回路基板(PCB)は、基板のこの第2の層の上に実装される。

【図面の簡単な説明】

【0005】

【図1】両面型表面実装集積ミリメートル波パッケージの1つの実施形態を示す。

【図2】基板の1つの実施形態を示す。

【図3】両面型表面実装集積ミリメートル波パッケージの別の実施形態を示す。

【図4】両面型表面実装集積ミリメートル波パッケージのさらに別の実施形態を示す。

【図5】両面型表面実装集積ミリメートル波パッケージのさらに別の実施形態を示す。

【発明を実施するための形態】

【0006】

本発明は、以下の説明、並びに本発明の実施形態を例示するために用いられる添付の図面を参照することによって、最も良く理解することができる。

ミリメートル波モジュールの放射素子と集積回路素子を統合するための表面実装可能なパッケージング・スキームを説明する。1つの実施形態によれば、アンテナは、基板の上部層内に組み込まれる。モノリシック・マイクロ波集積回路(MMIC)及びボール・グリッド・アレイ(BGA)は、基板の底面に取り付けられる。

【0007】

上述の問題の大部分を解決するか又は軽減するための手法は、アンテナが上部に配置され、ICがパッケージ基板の低部に配置された両面型パッケージを使用することである。

従って、十分な性能を有するミリメートル波機能の高レベルの統合を可能にする両面型パッケージングを実施する機構を説明する。

以下の説明において、多数の詳細が示される。しかしながら、当業者であれば、これらの特定の詳細なしに本発明の実施形態を実施できることは明らかであろう。他の場合には、説明の理解を不明瞭にすることを避けるために、周知の構造体、デバイス及び技術は、詳細には示されていない。従って、この説明は、限定するのではなく例証するものと考えられたい。

【0008】

本明細書における「1つの実施形態」又は「一実施形態」への言及は、特定の特徴、構造体、又は実施形態に関連して説明される特性が、本発明の少なくとも1つの実施形態に含まれることを意味する。本明細書内の各所における「1つの実施形態において」という語句の出現は、必ずしも全てが同じ実施形態を指すわけではない。

【0009】

図1は、両面型表面実装ミリメートル波集積システム100の1つの実施形態を示す。

システム100は、プリント回路基板(PCB)105の上に実装された多層基板160を含む。基板160は、誘電体層と、2つの誘電体層の界面に配置された金属層とを含む。本明細書において説明されるように、単独での「層」という用語への如何なる言及も「金属層」を示す。1つの実施形態において、基板160は、High Temperature Co−Fired Ceramics(HTCC)又はLow Temperature Co−Fired Ceramics(LTCC)アルミナによる大量生産に適しているが、例えば、積層ベース又はビルドアップ有機物のような他の基板型を用いることもできる。さらに、1つの実施形態において、基板160は、キャビティ、又は、側壁メタライゼーション等のような特定の構造部を含まない。

【0010】

1つの実施形態において、アンテナ・アレイ170は、基板の上部に埋め込まれる。1つの実施形態において、アンテナ・アレイ170は、多層上の金属パターンを有する。1つの実施形態において、上部の2つの層は、アンテナ・アレイ170用に用いられる。アンテナ・アレイ170はフィードされ、それらの分配は、基板160の幾つかの内部層を用いて実現される。基板160の底部においては、1つ又はそれ以上のMMIC145が基板160にフリップチップ実装される。代替的な実施形態において、例えば、チップと基板の間の相互接続としてのワイヤ・ボンドによる上向き(チップの底面が基板に接合される)実装のような、他の実装及び構成が用いられ、このような場合には、チップは、ミリメートル波動作に重要なワイヤ・ボンド長を短くするために、キャビティ内で上向きに配置される。パッケージ基板内のキャビティが望ましくない場合には、チップは薄く重ね合わせることができる。しかしながら、チップが薄すぎると、取り扱い及び組立ての問題が生じ得る。

【0011】

伝送ライン165及び接地平面168は、基板160の内部に含まれる。伝送ライン165は、アンテナ・アレイ170内のアンテナと1つ又はそれ以上のMMIC145との間でミリメートル波信号を伝送する。

1つの実施形態によれば、アンテナ・アレイ170の素子の各々は、MMIC145のうちの1つの上に、対応するミリメートル波ポートを有する。フリップチップ・バンプ147は、アンダーフィル149によって、対応するアンテナ・アレイ170の素子をMMIC145に結合する。その結果、MMIC145から発したミリメートル波信号は、基板160の中間層に伝わり、そこで、これらの信号は、それぞれのアンテナ・フィード・ポイント165に分配され、結局アンテナ・アレイ170内のアンテナに結合される。

【0012】

他のアナログ信号(例えば、LO及びIF信号、バイアス及び制御信号)は、アナログ信号ルーティング162を介して基板160の底部層の一部を用いて伝送される。ボール・グリッド・アレイBGAボール150は、パッケージをPCB105上に表面実装することを可能にするように、基板160の底部に取り付けられる。1つの実施形態において、BGAボール150の大きさは、フリップチップ実装されるMMICダイ145の結合した高さがBGAボール150の高さよりも確実に低くなるように選択される。

【0013】

さらに別の実施形態において、表面実装操作中、BGAボール150がリフローするとき、ダイ145はハード・ストップとして機能し、BGAボール150が完全に潰れるのを防止する。1つの実施形態において、熱対応パッドがダイの下に配置されて、PCB105への低い熱抵抗接触を確実にする。さらに別の実施形態においては、はんだ付け可能パッド130が、ダイ145の直下のPCB105上に配置され、ダイ145の裏面は、金属成分140によってメタライズされる。従って、ダイ145の裏面は表面実装中にはんだ付けして、PCB105に対するダイ145の良好な熱的接続を確実にすることができる。

【0014】

1つの実施形態によれば、システム100は、上面のアンテナ・アレイ170と底面のMMIC145との統合のための多層基板160の構成と、表面実装組立体のための基板160底面の構成と、パッケージをPCB105に実装するための構成とを含む。

【0015】

多層基板構成

図2は、基板160の1つの実施形態の断面図を示す。埋め込んだ主要機能に基づいて、それらの層は、接地平面168によって分離される、上部210、中間部220及び底部230の3つのグループに分けられる。1つの実施形態において、上部層210は、平面アンテナ素子に割り当てられる。多くの場合、パッチ積層化のような技術を実施してアンテナの性能を高めるために多層が必要とされる。代替的な実施形態において、単一層を平面アンテナ素子用に用いることができることに留意されたい。誘電体層の厚さは、アンテナ設計の考慮事項から決定することができる。上部接地平面168は、アンテナ層210をパッケージの残り部分から絶縁し、これにより電磁干渉からの耐性を与える。

【0016】

中間層220は、アンテナへのミリメートル波信号の分配に用いられる。1つの実施形態において、アンテナ素子は、フィード・ラインを共有せず、ミリメートル波のフィード・ラインの数は、アンテナ・アレイ内の素子の数と同じになる。1つの実施形態において、簡潔な方法で多数のフィード・ラインを効率的に分配するために、1つ又はそれ以上の層が用いられる。接地平面168は他の層の回路からの遮蔽を与える。1つの実施形態によれば、信号ライン以外のメタライゼーションは、均一な電磁環境のためにこれらの層においては最小に保たれる。1つの実施形態において、信号トレースからの遮断領域は、トレース幅及び基板層の厚さ等のような因子に依存する設計パラメータである。他の実施形態においては、他の因子がこの設計パラメータに影響を与える可能性がある。単一のTEMモードの伝搬を向上させるために、フェンシングよって接地を有するストリップ・ラインを信号ライン用に用いることができるが、ここで、フェンシングは、信号トレースが経路設定される際にその信号トレースの両側の特定の距離のところにビアを配置することを言う。トレースから接地ビアまでの距離及びビアの間の間隔は、設計パラメータである。

【0017】

底部層230は、DC信号、制御信号及び低周波アナログ信号用に用いられる。1つの実施形態において、高集積MMIC145は、LO及びIF信号ラインに加えて多数のDC及び制御ラインを必要とする。これに適合させるため、並びに、ダイ145及びBGA150が密集する底部層230を補うために、2つ又はそれ以上の層を用いることができる。1つの実施形態において、パッケージは、表面実装用途を意図したものであり、従ってこれらの層は、パッケージ直下のPCBの事前には未知の電気特性を認識する。このように、明確な電磁界面がないので、ミリメートル波信号ルーティングは、底部層において最小にする必要がある。

【0018】

上述のように、ミリメートル波信号の分配は、接地平面168によって遮蔽された中間層220の内部に留められる。さらに、多層を上部及び底部に付加して他の機能を収容する。これにより、基板160はミリメートル波の波長スケールにおいて相対的に厚くなる。従って、ミリメートル波信号は、一つの層から他の層に進む際に、垂直方向にかなりの距離を横断しなければならない。1つの実施形態において、単純なビア遷移部、又は、従来の準同軸のビア遷移部でさえも、長い垂直的な相互接続内に存在することになる共振、高次モード及び反射を抑制するのに十分ではない。

従って、1つの実施形態において、この垂直相互接続の問題の解決法として、補償用垂直相互接続機構が実施される。この垂直相互接続機構において、ミリメートル波信号は、基板の内側金属層である補償用垂直相互接続215の上をフリップチップ・パッド208に至るまで伝送される。

【0019】

さらに別の実施形態において、補償構造体は層遷移構造体に組み込まれる。このような実施形態においては、補償構造体の配置、大きさ及び形状は、モデリング処理によって決定される。さらに別の実施形態において、モデリング処理には、3次元(3D)電磁ツール(例えば、Ansoft CorporationからのHigh Frequency Structure Simulator(HFSS))及び回路シミュレータ(例えば、Agilent Technologies,Inc.からの高度設計システム(ADS))を利用する最適化法が含まれる。

1つの実施形態によれば、補償用垂直相互接続は、底部のMMICの全てのミリメートル波ポートの位置に又はその極めて近くに配置される。他の実施形態においては、同様の垂直相互接続が、ミリメートル波信号を中間層から上部層に伝送する必要があるフィード・スキームにおけるアンテナ・フィード・ネットワーク内で用いられる。

【0020】

基板底面構成

1つの実施形態によれば、基板160の底面は、MMIC145及びパッケージの第2のレベルの相互接続面の両方として構成される。1つ又はそれ以上のMMIC145は、標準的なフリップチップ組立て技術を用いて基板160にフリップチップ実装される。上述のように、他の実装技術を用いることができる。それらの低い電気的寄生振動により、フリップチップ相互接続は、mm波周波数において十分な性能をもたらすことができる。

さらに別の実施形態において、ダイ145は、高周波動作のための短いワイヤ・ボンド長を達成するためにキャビティ実装される。この構成におけるフリップチップ実装の別の利点は、ダイ145の裏面が露出するので効率的な熱除去のために使用できることである。

【0021】

第2のレベルの相互接続として、ボール150が1つ又はそれ以上の列内で基板160の外周付近に配置されるBGA型接続部が用いられる。1つの実施形態において、周波数変換、周波数逓倍及び位相シフトのような、全てのミリメートル波処理がMMIC145内で実施され、アンテナを介した放射を除いてミリメートル信号が完全にパッケージ内に包含されるようになる。この場合、低周波数IF、LO及び基準信号のみが、パッケージ外部の電源から供給される。

このようなシナリオにおいては、第2のレベルの相互接続は低周波数において十分な性能を有し、従ってその仕様を緩和する。結果として、他の型の相互接続を実施することが可能になる。図3は、BGAボール150ではなくリード300が基板160をPCB105に結合させるシステム100の実施形態を示す。

【0022】

パッケージ実装構成

1つの実施形態において、フリップチップ実装されたダイ145及びBGAボール150は、パッケージの表面実装面にあり、このパッケージはPCB105に取り付ける準備ができた状態にある。パッケージをPCB105に取り付けることができる幾つかの方法がある。図1に示されるように、ダイ145のメタライズされた裏面140が、表面実装操作中にPCB105上のはんだ付け可能な実装用パッド130と結合する。ダイと実装用パッドの間のギャップの大きさは考慮する必要がある。BGAにおける良好なはんだ接続のために、はんだボール150はリフロー中に十分に潰れる必要がある。ダイ145はPCB105に対するハード・ストップとして機能するので、小さすぎるギャップは、はんだボール150が良好な接続を形成するのを妨げる。

【0023】

別の実施形態において、パッケージはPCB105に取り付けられるが、一方ダイ145は表面実装中にはPCB105と結合しない。図4は、システム100のこのような実施形態を示す。図4に示されるように、ダイ145がPCB105に接触できるレベルまでBGAはんだボール150が潰れるのを防止することが重要である。1つの実施形態において、これは、堅固な芯のBGAボール、又は、ダイとPCBの間にギャップが存在するような大きさにする必要がある数個のより小さな非リフロー型ボールを用いて達成される。

第3の取付け方法において、PCB105は、ダイ145の大きさよりも大きな貫通切欠き部を含む。図5は、システム100のこのような実施形態を示す。図5に示されるように、切欠き部505はダイの真下に配置されることになる。表面実装中、BGAボール150が潰れつつあるとき、ダイ145は切欠き部に滑り込む。ダイ145とPCB105の間にギャップが必要ないので、この構成は、より小さなBGAボール150の使用を可能にすることになる。ダイ145の裏面は、切欠き部505を通して露出することになるので、例えば、ヒートシンクを用いて、熱接続を確立することができる。

【0024】

別の実施形態において、ダイ145の裏面は、熱接続のためにメタライズされない。このような実施形態においては、熱接着剤を用いて薄い金属パドル510を裏面に接着することができ、次いで金属パドル510をPCB105に取り付けて、低抵抗接続部を確立することができる。

上述のシステムは、アンテナが基板の上部層に組み込まれ、MMIC及び表面実装用BGAが底部に取り付けられた厚い多層基板をベースとする高集積ミリメートル波パッケージを形成する機構を説明する。この機構は、このような従来にないパッケージ化体を製造する困難を克服し、大量製造プロセスを用いて実施することができる。

【0025】

本発明の例示的な実施形態の前述の説明においては、1つ又はそれ以上の種々の本発明の態様を理解するのに役立つ開示を能率的にする目的で、本発明の種々の特徴が場合によりその単一の実施形態、図面、又は説明にまとめられていることを認識されたい。しかしながら、この開示方法は、請求された本発明が各々の請求項において明白に詳述されたものよりも多くの特徴を要求する意図を示すものと解釈されるべきではない。むしろ、添付の請求項が示すように、本発明の態様は、単一の前述の開示された実施形態の全ての特徴よりも少ない特徴にある。従って、詳細な説明に添付された請求項は、その結果、この詳細な説明に明確に組み込まれ、各々の請求項は、それ自体で本発明の別個の実施形態として主張するものである。

【0026】

前述の説明は、特定の実施形態に向けられた。当業者であれば、説明された実施形態に修正を加え、利点の全て又は一部を達成することができることは明らかであろう。従って、添付の特許請求の範囲の目的は、そのような変形及び修正の全てを本発明の精神及び範囲内に入るものとして包含することである。

【符号の説明】

【0027】

100:システム

105:プリント回路基板(PCB)

130:はんだ可能パッド

140:金属成分

145:モノリシック・マイクロ波集積回路(MMIC)

147:フリップチップ・バンプ

149:アンダーフィル

150:ボール・グリッド・アレイ(BGA)

160:基板

162:信号ルーティング

165:伝送ライン(アンテナ・フィード・ポイント)

168:接地面

170:アンテナ・アレイ

210:上部層(アンテナ層)

220:中間層

230:底部層

300:リード

505:切欠き部

510:金属パドル

【特許請求の範囲】

【請求項1】

第1、第2及び第3の組の1つ又はそれ以上の層を有し、前記第2の組の1つ又はそれ以上の層は前記第1及び第3の組の1つ又はそれ以上の層の間にある、基板と、

前記基板の前記第1の組の層に埋め込まれたミリメートル波アンテナのアレイと、

前記基板の前記第3の組の層のうちの1つの上に実装されたモノリシック・マイクロ波集積回路(MMIC)と、

前記基板の前記第2の組の層のうちの1つ又はそれ以上の中に埋め込まれたアンテナ・フィード・ポイントと、

前記MMICから前記フィード・ポイントに信号を伝送するための相互接続と、

前記基板をプリント回路基板(PCB)に実装するための、前記第3の組の層上に取り付けられたリードと、

を備えることを特徴とする集積回路(IC)パッケージ。

【請求項2】

前記MMICは、前記アレイ内のアンテナに対応する1つ又はそれ以上のポートを備えることを特徴とする、請求項1に記載のパッケージ。

【請求項3】

前記相互接続は、前記第3の組の層の内の層から前記第2の組の層に至る遷移部の寄生効果を減少させるための補償構造体を含むことを特徴とする、請求項1に記載のパッケージ。

【請求項4】

前記第3の組の層に埋め込まれたアナログ信号ラインをさらに備えることを特徴とする、請求項1に記載のパッケージ。

【請求項5】

前記基板をプリント回路基板(PCB)に実装するための、前記第3の組の層上に取り付けられたボール・グリッド・アレイ(BGA)ボールをさらに備えることを特徴とする、請求項4に記載のパッケージ。

【請求項6】

第1、第2及び第3の組の1つ又はそれ以上の層を有し、前記第2の組の1つ又はそれ以上の層は、前記第1及び第3の組の1つ又はそれ以上の層の間にある、基板と、

前記基板の前記第1の組の層に埋め込まれたミリメートル波アンテナのアレイと、

前記基板の前記第3の組の層のうちの1つの上に実装されたモノリシック・マイクロ波集積回路(MMIC)と、

前記基板の前記第2の組の層のうちの1つ又はそれ以上の中に埋め込まれたアンテナ・フィード・ポイントと、

前記MMICから前記フィード・ポイントに信号を伝送するための相互接続と、

プリント回路基板(PCB)に実装するための、前記MMICダイの直下に取り付けられたパッドと、

を備えることを特徴とする集積回路(IC)パッケージ。

【請求項7】

前記MMICダイの裏面はメタライズされることを特徴とする、請求項6に記載のパッケージ。

【請求項8】

前記MMICは、前記アレイ内のアンテナに対応する1つ又はそれ以上のポートを備えることを特徴とする、請求項6に記載のパッケージ。

【請求項9】

第1、第2及び第3の組の1つ又はそれ以上の層を有し、前記第2の組の1つ又はそれ以上の層は、前記第1及び第3の組の1つ又はそれ以上の層の間にある、基板と、

前記基板の前記第1の組の層に埋め込まれたミリメートル波アンテナのアレイと、

前記基板の前記第3の組の層のうちの1つの上に実装されたモノリシック・マイクロ波集積回路(MMIC)と、

を含む集積回路(IC)パッケージと、

前記基板の前記第3の組の層の上に、前記基板をプリント回路基板に実装するための前記第3の組みの層のうちの少なくとも1つに取り付けられたリードを用いて、実装されたプリント回路基板(PCB)と、

を備えることを特徴とするシステム。

【請求項10】

前記MMICは、前記アレイ内のアンテナに対応する1つ又はそれ以上のポートを備えることを特徴とする、請求項9に記載のシステム。

【請求項11】

前記パッケージは、前記基板の前記第2の組の層のうちの1つ又はそれ以上の中に埋め込まれたアンテナ・フィード・ポイントをさらに備えることを特徴とする、請求項10に記載のシステム。

【請求項12】

前記MMICから前記フィード・ポイントまで信号を伝送するための相互接続をさらに備えることを特徴とする、請求項11に記載のシステム。

【請求項1】

第1、第2及び第3の組の1つ又はそれ以上の層を有し、前記第2の組の1つ又はそれ以上の層は前記第1及び第3の組の1つ又はそれ以上の層の間にある、基板と、

前記基板の前記第1の組の層に埋め込まれたミリメートル波アンテナのアレイと、

前記基板の前記第3の組の層のうちの1つの上に実装されたモノリシック・マイクロ波集積回路(MMIC)と、

前記基板の前記第2の組の層のうちの1つ又はそれ以上の中に埋め込まれたアンテナ・フィード・ポイントと、

前記MMICから前記フィード・ポイントに信号を伝送するための相互接続と、

前記基板をプリント回路基板(PCB)に実装するための、前記第3の組の層上に取り付けられたリードと、

を備えることを特徴とする集積回路(IC)パッケージ。

【請求項2】

前記MMICは、前記アレイ内のアンテナに対応する1つ又はそれ以上のポートを備えることを特徴とする、請求項1に記載のパッケージ。

【請求項3】

前記相互接続は、前記第3の組の層の内の層から前記第2の組の層に至る遷移部の寄生効果を減少させるための補償構造体を含むことを特徴とする、請求項1に記載のパッケージ。

【請求項4】

前記第3の組の層に埋め込まれたアナログ信号ラインをさらに備えることを特徴とする、請求項1に記載のパッケージ。

【請求項5】

前記基板をプリント回路基板(PCB)に実装するための、前記第3の組の層上に取り付けられたボール・グリッド・アレイ(BGA)ボールをさらに備えることを特徴とする、請求項4に記載のパッケージ。

【請求項6】

第1、第2及び第3の組の1つ又はそれ以上の層を有し、前記第2の組の1つ又はそれ以上の層は、前記第1及び第3の組の1つ又はそれ以上の層の間にある、基板と、

前記基板の前記第1の組の層に埋め込まれたミリメートル波アンテナのアレイと、

前記基板の前記第3の組の層のうちの1つの上に実装されたモノリシック・マイクロ波集積回路(MMIC)と、

前記基板の前記第2の組の層のうちの1つ又はそれ以上の中に埋め込まれたアンテナ・フィード・ポイントと、

前記MMICから前記フィード・ポイントに信号を伝送するための相互接続と、

プリント回路基板(PCB)に実装するための、前記MMICダイの直下に取り付けられたパッドと、

を備えることを特徴とする集積回路(IC)パッケージ。

【請求項7】

前記MMICダイの裏面はメタライズされることを特徴とする、請求項6に記載のパッケージ。

【請求項8】

前記MMICは、前記アレイ内のアンテナに対応する1つ又はそれ以上のポートを備えることを特徴とする、請求項6に記載のパッケージ。

【請求項9】

第1、第2及び第3の組の1つ又はそれ以上の層を有し、前記第2の組の1つ又はそれ以上の層は、前記第1及び第3の組の1つ又はそれ以上の層の間にある、基板と、

前記基板の前記第1の組の層に埋め込まれたミリメートル波アンテナのアレイと、

前記基板の前記第3の組の層のうちの1つの上に実装されたモノリシック・マイクロ波集積回路(MMIC)と、

を含む集積回路(IC)パッケージと、

前記基板の前記第3の組の層の上に、前記基板をプリント回路基板に実装するための前記第3の組みの層のうちの少なくとも1つに取り付けられたリードを用いて、実装されたプリント回路基板(PCB)と、

を備えることを特徴とするシステム。

【請求項10】

前記MMICは、前記アレイ内のアンテナに対応する1つ又はそれ以上のポートを備えることを特徴とする、請求項9に記載のシステム。

【請求項11】

前記パッケージは、前記基板の前記第2の組の層のうちの1つ又はそれ以上の中に埋め込まれたアンテナ・フィード・ポイントをさらに備えることを特徴とする、請求項10に記載のシステム。

【請求項12】

前記MMICから前記フィード・ポイントまで信号を伝送するための相互接続をさらに備えることを特徴とする、請求項11に記載のシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−110434(P2013−110434A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2013−20236(P2013−20236)

【出願日】平成25年2月5日(2013.2.5)

【分割の表示】特願2008−292779(P2008−292779)の分割

【原出願日】平成20年10月20日(2008.10.20)

【出願人】(508339312)サイビーム インコーポレイテッド (2)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成25年2月5日(2013.2.5)

【分割の表示】特願2008−292779(P2008−292779)の分割

【原出願日】平成20年10月20日(2008.10.20)

【出願人】(508339312)サイビーム インコーポレイテッド (2)

[ Back to top ]