複合圧電基板の製造方法

【課題】圧電体材料を効率良く利用して、均質な厚みの極薄圧電膜を形成することができる、複合圧電基板の製造方法を提供する。

【解決手段】圧電体基板2の表面2aからイオンを注入して、圧電体基板2内において表面2aから所定深さの領域に欠陥層4を形成する。圧電体基板2の表面2aに支持基板10を接合して基板接合体40を形成する。基板接合体40を、圧電体基板2内に形成された欠陥層4で分離して、圧電体基板2の表面2aと欠陥層4との間の剥離層3が圧電体基板2から剥離されて支持基板10に接合された複合圧電基板30を形成し、複合圧電基板30の剥離層3の表面3aを平滑化する。イオン注入後に、複合圧電基板30の剥離層3の分極処理を行う。

【解決手段】圧電体基板2の表面2aからイオンを注入して、圧電体基板2内において表面2aから所定深さの領域に欠陥層4を形成する。圧電体基板2の表面2aに支持基板10を接合して基板接合体40を形成する。基板接合体40を、圧電体基板2内に形成された欠陥層4で分離して、圧電体基板2の表面2aと欠陥層4との間の剥離層3が圧電体基板2から剥離されて支持基板10に接合された複合圧電基板30を形成し、複合圧電基板30の剥離層3の表面3aを平滑化する。イオン注入後に、複合圧電基板30の剥離層3の分極処理を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複合圧電基板の製造方法に関し、詳しくは、圧電膜を有する複合圧電基板の製造方法に関する。

【背景技術】

【0002】

近年、極めて薄い圧電体(極薄圧電膜)を利用したフィルタ等の開発が活発に行われている。これらのフィルタ等の極薄圧電膜には、一般には、スパッタ法やCVD法などの堆積法で形成されたAlN薄膜やZnO薄膜が用いられているが、いずれもC軸が基板の上下に整列したC軸配向膜である。

【0003】

一方、圧電体の単結晶基板を支持基板に張り合わせた後に、研磨により圧電体の単結晶基板を薄化することにより、圧電膜を有する複合圧電基板を製造することも提案されている。

【0004】

例えば図6の断面図に示す弾性表面波装置100では、励振電極105が形成されている単結晶からなる圧電基板101は、予めガラス層108を介して保護基板103に接合された状態で研磨され薄板化されたものである(例えば、特許文献1、非特許文献1参照)。

【0005】

また、圧電基板に水素イオンを注入し、圧電基板と支持基板を湿潤雰囲気下に置いて、それぞれの基板表面に親水基を形成した後に、圧電基板と支持基板を張り合わせ、その後、高速加熱して、イオン注入した深さで圧電基板を割って圧電薄膜を得る手法が提案されている(例えば、特許文献2参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−16468号公報

【特許文献2】特表2002−534885号公報

【0007】

【非特許文献1】Y. 0sugi et a1、「Single crysta1 FBAR with LiNbO3 and LiTaO3」、2007 IEEE MTT-S International Microwave Symposium、pp.873-876

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、堆積法で形成した圧電膜は、配向膜を得るための成膜温度や成膜条件などから材料制約が厳しく、主としてAlNが利用される。また、結晶軸の配向方向を制御することもできず、C軸配向膜が主として採用されるため、圧電軸を傾斜させることによる振動モードの工夫が難しい。

【0009】

一方、圧電体の単結晶基板を研磨して形成した圧電膜は、大半の圧電単結晶を研磨クズとして廃棄するため、材料の利用効率が悪い。さらに、圧電膜の厚みは、研磨速度のばらつき、研磨前の基板のうねりにより左右されるため、均質な厚みを得るための制御は難しく生産性が悪い。

【0010】

特許文献2では、親水基による接合が用いられる。この接合方法では、圧電基板表面と支持基板表面に親水基を形成し、その親水基を介して接合される。この親水基による接合は極めて弱いため、強固な接合を得るために、親水基を分解できる温度(例えば400℃)で加熱して、親水基(OH)から水素(H)を脱離させ、圧電基板表面と支持基板表面のボンドを強固にする工程を経る必要がある。

【0011】

しかしながら、接合後に水素ガスを脱離するため、接合界面にガスが溜まり、マイクロキャビティを形成したり、水素ガスが十分に除去できずに圧電結晶中に残留し、結晶構造を破損し、圧電性を劣化させるなどの問題点があった。マイクロキャビティや結晶破壊による接合界面の不均一は、表面波フィルタやバルク波フィルタに応用するときに、弾性散乱や吸音による発熱を引き起こし、フィルタの挿入損失の劣化や発熱による耐電力性能の劣化を引き起こす要因となっていた。

【0012】

特に、Li系圧電材料であるLiTaO3やLiNbO3を用いる場合、水素が残留すると、LiイオンサイトのLiと水素が置換し、圧電性の劣化を生じやすい。

【0013】

例えば、圧電基板としてタンタル酸リチウムやニオブ酸リチウム基板、支持基板としてもタンタル酸リチウムやニオブ酸リチウム基板を用い、圧電基板と支持基板の表面をCMP(化学機械研磨)により平滑化し、その後、湿潤雰囲気下に圧電基板と支持基板を晒して親水基を形成し、基板表面同士を接して張り合わせて親水基による弱い接合をし、500℃で1時間加熱して親水基を分解して強固な接合を行った。このような方法で接合した複合圧電基板は、親水基による弱い接合をした後、500℃で加熱する前は、外力を加えることにより接合界面で容易に剥離することができた。一方、500℃で加熱した後は、接合が強化されたが、接合界面には、目視できる程度のキャビティが随所に形成されていた。また、接合界面の結晶配列をTEM(透過型電子戦顕微鏡)で観察すると、数十nmのキャビティや結晶配列の乱れが観察された。

【0014】

さらに、非線形誘電率顕微鏡を用いて、Hイオンを注入し、400℃で加熱してLiTaO3の分極状態を調査したところ、当初整列していた分極極性がドメイン単位で局所的に反転し、圧電性が劣化していることが分かった。より高温の500℃で加熱すると更に圧電性劣化が顕著となる。

【0015】

本発明は、かかる実情に鑑み、圧電体材料を効率良く利用して、均質な厚みの極薄圧電膜を形成することができる、複合圧電基板の製造方法を提供しようとするものである。

【課題を解決するための手段】

【0016】

本発明は、以下のように構成した複合圧電基板の製造方法を提供する。

【0017】

複合圧電基板の製造方法は、(a)圧電体基板と、支持基板とを準備する、第1の工程と、(b)前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、(c)前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、(d)前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、(e)前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程とを含む。複合圧電基板の製造方法は、(f)前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含む。前記分極処理工程は、前記剥離層に電界を断続的に印加する工程である。

【0018】

上記方法によれば、イオン注入によりに分極が反転しても、修復することができる。

【0019】

また、本発明は、以下のように構成した複合圧電基板の製造方法を提供する。

【0020】

複合圧電基板の製造方法は、(a)圧電体基板と、支持基板とを準備する、第1の工程と、(b)前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、(c)前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、(d)前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、(e)前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程とを含む。複合圧電基板の製造方法は、(f)前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含む。前記分極処理工程は、前記圧電体基板のキュリー温度より100度以上低い温度で行われる工程である。

【0021】

上記方法によれば、イオン注入によりに分極が反転しても、修復することができる。

【0022】

好ましくは、前記分極処理工程は、200度以上で行われる工程である。

【0023】

また、本発明は、以下のように構成した複合圧電基板の製造方法を提供する。

【0024】

複合圧電基板の製造方法は、(a)圧電体基板と、支持基板とを準備する、第1の工程と、(b)前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、(c)前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、(d)前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、(e)前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程とを含む。前記第2の工程において、イオン注入をするときに、自発分極している前記圧電体基板の構成原子がシフトしている方向と同一方向にイオンを注入する。

【0025】

上記方法により圧電体基板の剥離層が接合された複合圧電基板を製造すると、複合圧電基板の表面に極めて薄い圧電体(極薄圧電膜)を形成することができる。例えば単結晶の圧電体基板を用いて、圧電体の極薄単結晶膜を有する複合圧電基板を製造することができる。

【0026】

上記方法によれば、剥離層が剥離された後の圧電体基板は、複合圧電基板の製造に再び利用することができる。1枚の圧電体基板から多量の複合圧電基板を製造することができ、圧電基板を研磨して圧電膜を形成する場合に比べ、圧電体材料を廃棄する量が減るので、高価な圧電体の使用量を減らすことができる。

【0027】

また、剥離層の厚みは、イオン注入するときのエネルギーで決まり、研磨のように基板のうねりに圧電体の厚みが左右されることがないため、極薄でも均一にすることができる。したがって、表面に均一な厚みの極薄圧電膜を有する複合圧電基板が得られる。

【0028】

イオン注入をするときに、自発分極している前記圧電体基板の構成原子がシフトしている方向と同一方向にイオンを注入する。

【0029】

この場合、圧電体基板について、イオン注入による圧電性の劣化を抑制できる。

【0030】

また、親水化処理によるOH基を用いた接合でなく、清浄活性化工程によるOH基を用いない接合であるので、接合界面に残留する水素の脱離が必要ない。このため、親水基を分解するための高温長時間の加熱が不要であり、また、接合界面のガス発生やマイクロキャビティ形成がなく、圧電結晶中への水素ガス残留がない。このため、結晶構造の破損や圧電性の劣化が抑制される。特に、Li系圧電材料であるLiTaO3やLiNbO3を用いる場合、水素残留によるLiイオンサイトのLiと水素の交換を生じないので、圧電性が維持される。

【0031】

好ましくは、前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、より好ましくは前記第5の工程の後に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含む。

【0032】

この場合、分極処理工程における圧電体基板の表面に励起される焦電荷によるイオン注入加工(ドーズ量、注入深さ)のばらつき、基板の破損が避けられる。

【0033】

好ましくは、(f)前記欠陥層が形成された前記圧電体基板の表面と前記支持基板の表面との少なくとも一方について、当該表面に付着した不純物を除去して当該表面を構成する原子を直接露出させ、活性化させる、清浄活性化工程をさらに含む。

【0034】

好ましくは、接合界面に金属元素を配する。

【0035】

好ましくは、前記圧電体基板にリチウム系圧電材料を用いる。

【0036】

上記方法で製造された複合圧電基板に形成された圧電体基板の剥離層の極めて薄い圧電体を利用して、弾性表面波素子、弾性境界波素子、バルク波素子、板波素子などの弾性波素子を形成することができる。これらの弾性波素子を有する電子部品の製造に、上記方法で製造された複合圧電基板を用いると、高価な圧電体基板の使用量を削減できる。

【発明の効果】

【0037】

本発明の複合圧電基板の製造方法によれば、圧電体材料を効率良く利用して、均質な厚みの極薄圧電膜を形成することができる。

【図面の簡単な説明】

【0038】

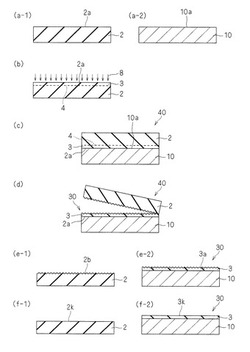

【図1】複合圧電基板の製造工程を示す断面図である。(実施例1)

【図2】BAWデバイスの製造工程を示す断面図である。(実施例2)

【図3】BAWデバイスの製造工程を示す断面図である。(実施例3)

【図4】BAWデバイスの断面図である。(実施例3)

【図5】SAWデバイスの製造工程を示す断面図である。(実施例1)

【図6】弾性表面波装置の断面図である。(従来例)

【発明を実施するための形態】

【0039】

以下、本発明の実施の形態について、図1〜図5を参照しながら説明する。

【0040】

<実施例1> 実施例1のSAW(surface acoustic wave;弾性表面波)デバイスの製造方法について、図1、図5を参照しながら説明する。

【0041】

まず、SAWデバイスに用いる複合圧電基板30の製造工程について、図1を参照しながら説明する。図1は、複合圧電基板30の製造工程を示す断面図である。

【0042】

(工程1) 図1(a−1)及び(a−2)に示すように、圧電体基板2と支持基板10を準備する。例えば、圧電体基板2として42°YカットLiTaO3基板、支持基板10としてSi基板を準備する。それぞれの基板2、10の表面2a,10aは、予め鏡面研磨しておく。

【0043】

(工程2) 次いで、図1(b)に示すように、圧電体基板2の表面2aに、矢印8で示すように、イオンを注入して、圧電体基板2内において表面2aから所定深さの領域に、破線で模式的に示す欠陥層4を形成する。例えば、LiTaO3圧電体基板2にH+イオンを注入する。注入エネルギーは150KeV、ドーズ量は9×1016cm−1である。このとき、H+イオンが圧電体基板2の表面2aから1μm程度の深さに分布する欠陥層4が形成される。

【0044】

(洗浄活性化工程) 圧電体基板2と支持基板20を減圧チャンバに入れ、それぞれの表面2a,10aにArイオンをビーム照射し、表面2a,10aに付着した親水基、水素、酸化被膜などの不純物を除去する。不純物が除去された表面2a,10aは、基板2,10を構成する原子が直接露出し、活性化される。このように、清浄活性化した表面2a,10a同士を真空中で接触させると、元素同士が直接ボンドを結び、強固な接合が得られる。接合界面に不純物が存在しないため、接合後に不純物を除去する必要がなく、接合界面付近の結晶の破損も抑制される。

【0045】

(工程3) 次いで、図1(c)に示すように、圧電体基板2の表面2aと、支持基板10の表面10aとを接合して、基板接合体40を形成する。

【0046】

LiTaO3圧電体基板2とSi支持基板10の場合には、線熱膨張係数が異なるので、常温において、基板表面2a,10aをプラズマにより活性化し、真空中で接合する常温直接接合を行うことが望ましい。

【0047】

LiTaO3圧電体基板2とSi支持基板10とを接合した後、500℃で加熱する。これにより、H+イオンを注入したLiTaO3圧電体基板2の表面2aから1μmの深さの欠陥層4には、表面2aに沿ってマイクロキャビティが発生し、加熱によりこのキャビティが成長する。

【0048】

なお、接合界面に、元素同士のボンドを強化するために微量(数nm)のFeなどの金属元素を配してもよい。金属元素は大気中での酸化反応などにより汚染されやすい。そこで、金属イオンの堆積は、接合を行う真空に減圧したチャンバ内で、接合の直前に行うことが望ましい。

【0049】

(工程4) 次いで、図1(d)に示すように、基板接合体40の圧電体基板2と支持基板10とを、圧電体基板2内に形成された欠陥層4で分離して、圧電体基板2の表面2aと欠陥層4との間の剥離層3が圧電体基板2から剥離されて支持基板10に接合された複合圧電基板30を形成する。

【0050】

例えば、LiTaO3圧電体基板2の表面2aから1μmの深さの欠陥層4に形成されたマイクロキャビティに沿って分離するため、1μmの厚さのLiTaO3薄膜の剥離層3が支持基板10の表面10aに接合された複合圧電基板30と、表面2a側からLiTaO3薄膜の剥離層3が剥離されたLiTaO3圧電体基板2とに分離する。

【0051】

(工程5) 次いで、図1(e−1)及び(e−2)に模式的に示すように凹凸が形成された破断面である圧電体基板2と複合圧電基板30の表面2a,3aを研磨し、図1(f−1)及び(f−2)に示すように圧電体基板2と複合圧電基板30の表面2k,3kを平滑化する。

【0052】

例えば、LiTaO3薄膜の剥離層3の破断面が現れる複合圧電基板30の表面3aと、LiTaO3薄膜の剥離層3が剥離されたLiTaO3圧電体基板2の表面2aは、RMS(root mean square)で1nm程度の荒れた面になっているため、CMP(chemical-mechanical polishing;化学機械研磨)により表面2a,3aから厚さ100nm程度研磨して除去して平滑化する。

【0053】

(工程6) 表面3kが平滑化された複合圧電基板30について、剥離層3の圧電体の分極反転を修正するため、分極処理を行う。例えば、表面3aを平滑化したLiTaO3薄膜の剥離層3について、400℃で5ms、22kVのパルス電圧を印加する分極処理を行う。

【0054】

圧電体結晶を構成する原子の一部は、正又は負に荷電しイオン化している。このイオン化した原子に、例えば電界を印加すると正に荷電したイオンは陰極側に、負に荷電したイオンは陽極側に結晶内をわずかにシフトし、電気双板子を生ずる。この現象は電気分極と呼ばれている。電界の印加を止めても分極の状態を維持することができる結晶も存在し、この状態は前述した自発分極と呼ばれる。自発分極する圧電体結晶に高エネルギーで多量のイオンを注入すると、このイオンのシフトした状態が変化し、分極の極性が反転したりする。部分的な分極の反転は圧電性の劣化を引き起こすため、好ましくない。

【0055】

そこで、イオン注入した後に分極処理を行うことで分極の反転を修復できる。例えば、LiNbO3の場合、700℃の加熱雰囲気で22kV/mmの電界を印加する。分極処理は剥離工程後に行うことが望ましく、温度は支持基板や電極の融点や熱膨張係数差を考慮して、200〜1200℃で行う。高温であるほど抗電界が下がるので、印加する電界を低く抑えることができる。また、電界は1μs〜1分の範囲で断続的に印加すると直流電界による結晶へのダメージを抑制できるので、望ましい。また、200℃以上での加熱は、イオン注入により受けた結晶のひずみを緩和するため望ましい。結晶ひずみをとるための加熱温度は、分極の解消を避けるためにキューリー温度より100℃以上低くする。

【0056】

なお、分極反転などの圧電性の劣化は工程6の分極処理により回復できるが、結晶に負担がかかるため、工程6に至る前の分極反転などの圧電性劣化は極力抑制しておくことが望ましい。また、結晶材料や結晶方位によっては分極処理が難しい圧電体も存在するため、工程6に至る前の圧電性劣化の抑制策は重要である。

【0057】

分極はイオン化した圧電結晶の構成元素がわずかにシフトすることで生じる。一般に、わずかにシフトさせるためのエネルギー量は、構成元素が結晶単位からはずれるエネルギー量に比べて小さい。そこで、自発分極を示すイオンのシフトしている方向と同一方向からイオンを注入することで、自発分極の極性反転が生じるのを抑制できる。

【0058】

例えば、LiTaO3やLiNbOの場合、LiイオンやTaイオン、Nbイオンは+C軸方向にわずかにシフトしているので、−C軸側から+C軸側に向かってイオンを注入することが望ましい。なお、イオンの注入方向に対してC軸のなす角度θが−90°<θ<+90°の範囲とすれば効果が得られる。

【0059】

また、工程4において、剥離は圧電体のキューリー温度以下で行うことが望ましい。キューリー温度を超えると、分極が一旦開放されるため、圧電性が劣化する。

【0060】

本願発明者の知見によれば、工程4において、欠陥層で剥離するために必要な加熱温度は500〜600℃である。一般に電子部品用に供給されているLiTaO3ウェハは、キューリー温度が600℃前後と低く、剥離に必要な加熱温度とキューリー温度が近接している。このため、圧電性が劣化しやすい。LiTaO3やLiNbO3において、LiのTaやNbに対する組成比xが48.0%≦x<49.5%の場合、コングルエント組成と呼ばれ、前述の電子部品用圧電基板として大量に供給されているウェハに用いられている。一方、組成比が49.5%≦x≦50.5%はストイキオ組成と呼ばれている。LiTaO3の場合、コングルエント組成の場合はキューリー温度が590〜650℃と低く、ストイキオ組成の場合は660〜700℃となる。そこで、LiTaO3を用いる場合、LiのTaに対する組成比を49.5%≦x≦50.5%としたストイキオ組成とすることが工程4における加熱時の圧電性劣化を抑制できるので望ましい。

【0061】

なお、LiNbO3の場合、コングルエント組成の場合は1100〜1180℃、ストイキオ組成の場合は1180〜1200℃となる。

【0062】

また、工程4において、圧電体がLiTaO3やLiNbO3のように焦電性をもつ場合、昇温や降温により基板表面に電荷が蓄積される。表面に蓄積された電荷による電界が分極方向と逆方向から圧電体の抗電界を超えて加わると分極が反転し圧電性が劣化する。工程4では昇温と降温のいずれかにおいて、分極と逆方向から電界が加わるため、圧電性の劣化を生じやすい。

【0063】

本願発明者は圧電体の導電率を高め、かつ、温度変化のペースを焦電荷による電界が圧電体の抗電界以下となるようにすることにより、圧電性の劣化を抑制できることを見出した。

【0064】

実施例1において、LiTaO3の導電率を高めて4×1010S/cmとなるように処理したウェハを用い、工程4において表面の電位が200V以下となるように昇温及び降温のペースを低下させることにより圧電性の劣化を抑制できた。LiTaO3やLiNbO3の導電率を高める処理は、特開2004−328712のように低酸素雰囲気中で高温アニールしたり、特開2005−119906や特開2005−179117のように金属粉末中で加熱する手段が知られている。

【0065】

以上に説明した製造工程により製造された複合圧電基板の作製例について、観察した。すなわち、圧電体基板としてLiTaO3基板、支持基板としてもLiTaO3基板を用い、圧電体基板と支持基板の表面をCMPにより平滑化し、真空中で圧電体基板と支持基板の表面にArイオンビームを照射して、基板表面を清浄活性化し、基板表面同士を接して張り合わせて、基板の元素同士が直接ボンドする強固な接合を行った後の複合圧電基板の外形写真を撮影した。撮影した写真には、接合界面に目視できるようなキャビティはなかった。また、接合界面の結晶配列をTEM(透過型電子戦顕微鏡)で観察すると、整列した結晶配列が観察された。

【0066】

以上に説明した製造工程により製造された複合圧電基板30は、表面に圧電体の剥離層3を有しているので、弾性波素子を作製するために用いることができる。残った圧電体基板2は、次の複合圧電基板30を作製するための素材として再び利用する。

【0067】

次に、SAWデバイスの製造工程について、図5の断面図を参照しながら説明する。

【0068】

図5(a)に示すように、前述の工程1〜6で製造された複合圧電基板30を準備し、図5(b)に示すように、複合圧電基板30の表面3kに、IDT電極15等を形成する。

【0069】

例えば、支持基板10の表面10aにLiTaO3薄膜の剥離層3が接合された複合圧電基板30の表面3kに露出するLiTaO3薄膜の剥離層3の平滑化された表面に、フォトリソグラフィ技術を用いてアルミニウム膜をパターンニングし、IDT電極15、パッド電極(不図示)、IDT電極15とパッド電極との間を接続する配線(不図示)などの導体パターンを形成して、SAWフィルタなどのSAWデバイスを作製する。

【0070】

以上に説明した工程でSAWデバイスを作製すると、次のような効果を得ることができる。

【0071】

(1) SAWデバイスを製造する上で、圧電体の材料、結晶方位は、電気機械結合係数や周波数温度特性、音速に影響するため、SAWデバイスの周波数や帯域幅、挿入損失などに重要な影響を与える。圧電体の材料や結晶方位の選択自由度が高い方が、優れたSAWデバイスを構成しやすい。

【0072】

すなわち、スパッタやCVDなどの成膜法で圧電体薄膜を形成すると、薄膜の材料、結晶方位が制約される。薄膜材料はAlNやZnOなど、成膜法で形成できる膜の種類は少なく、圧電体を単結晶化することは難しく、通常はC軸配向膜が得られるに過ぎない。このため、圧電軸が上下にしか向かないのでSH型のSAWを励振することが困難だった。

【0073】

一方、圧電体単結晶から薄膜を剥離する本発明の手法であれば、圧電体の結晶方位の自由度が高く、優れたSH型SAWが励振する36°〜46゜Yカットの圧電基板を得ることができる。

【0074】

(2) 単結晶の育成速度が遅く、割れやすいためスライスしづらく、LiやTaなどの原料が希少で高価なために、基板が高価なLiTaO3基板やLiNbO3基板、水晶基板などの圧電体基板に比べ、Si基板は安価である。

【0075】

すなわち、従来は、1枚のSAWデバイス用ウェハには、1枚の高価な圧電体基板が用いられていた。これに対し、本発明の複合圧電基板は、1枚のSAWデバイス用ウェハを製造するために、1枚の安価なSi基板と圧電体薄膜のみを材料とし、この圧電薄膜は1枚の圧電体基板から数十枚〜数百枚得ることができるので、材料の使用量としては無視できる程度の量に抑えることができる。このため、希少で高価なLiやTaなどの使用量を抑制でき、環境負荷が小さく、安価な圧電基板を得ることができる。

【0076】

(3) 携帯電話用のRFフィルタには、1〜2Wの大きな電力印加に耐えることが望まれる。SAWフィルタの耐電力性能は、電気信号を加えたときのIDT領域の温度により大きな影響を受ける。電力印加によりIDT領域が250℃などの高温になると、SAWフィルタが破壊するまでの時間が著しく短くなる。IDT領域の温度上昇は、電気的なオーミック損に起因するジュール熱や弾性的な吸音による発熱が、圧電体基板の熱伝導率の低さにより十分に放熱されないことが要因である。LiTaO3やLiNbO3などの圧電体のみで構成された圧電基板は、熱伝導率がSiに比べて小さく、放熱性がよくない。本発明の複合圧電基板は、Siと同等の熱伝導率を得ることができるため、放熱性がよい。このため、大きな電力印加に耐えることができる。

【0077】

(4) 極薄圧電体の厚みはイオン注入するときのエネルギーで決まる。したがって、研磨のように基板うねりに厚みが左右されることはなく、極薄圧電体でも安定した厚みが得られる。圧電体薄膜の厚みは、SAWの音速(周波数=音速/波長なので周波数が決まる)を決定するので重要である。本発明の複合圧電基板は、一定厚みの圧電薄膜を形成できるので、SAWデバイスの特性が安定する。

【0078】

(5) 42°YカットのLiTaO3基板は、−Z軸が42°傾斜して表面側となる。LiTaO3を構成するLi原子とTa原子は、わずかに裏面側(+Z軸側)にシフトして自発分極している。本発明では、−Z軸側からイオンを注入することで、分極反転を抑制している。

【0079】

(6) 工程1〜6で作製した複合圧電基板は、SAWフィルタに限らず、境界波やラム波などの板波を用いたフィルタなどにも用いることができる。境界波の場合は、次の実施例2のように複合圧電基板に素子部を構成すればよい。板波を用いる場合は、次の実施例3のように、支持基板を裏面からエッチングして圧電体の剥離層を裏面から露出させればよい。

【0080】

(7) SiはLiTaO3に比べて線膨張係数が小さいため、Si支持基板にLiTaO3剥離膜が接合された複合圧電基板は、周波数温度係数を抑制できる。

【0081】

<実施例2> 実施例2のBAW(bulk acoustic wave;バルク弾性波)デバイスについて、図2を参照しながら説明する。図2は、BAWデバイスの製造工程を示す断面図である。

【0082】

実施例2のBAWデバイスは、次の工程で製造する。

【0083】

まず、図2(a)に示すように、複合圧電基板30を準備する。例えば、20°YカットLiTaO3圧電体基板とSi支持基板10とを用い、実施例1の工程1〜5と同じ工程で、Si支持基板10の表面10aに20°YカットのLiTaO3剥離層3が接合された複合圧電基板30を作製する。

【0084】

次いで、図2(b)に示すように、複合圧電基板30の表面3kに上部電極16を形成する。例えば、LiTaO3剥離層3の表面3kに、電子ビーム蒸着法とフォトリソグラフィ法により、アルミニウムで上部電極16を形成する。

【0085】

次いで、図2(c)に示すように、支持基板10に穴13を形成し、剥離層3の裏面3sを露出させる。例えば、Si支持基板10の剥離層3とは反対側の裏面10bから、フォトリソグラフィ法とリアクティブイオンエッチング法により、Si支持基板10をエッチングして穴13を形成し、圧電体の剥離層3の裏面3sを露出させる。

【0086】

次いで、図2(d)に示すように、剥離層3の裏面3sに下部電極14を形成する。例えば、LiTaO3剥離層3の裏面3sに、アルミニウムで下部電極14を電子ビーム蒸着法とフォトリソグラフィ法により形成する。

【0087】

次いで、図2(e)に示すように、剥離層3に下部電極14が露出する孔20を形成する。例えば、LiTaO3剥離層3の表面3k側から、フォトリソグラフィ法とリアクティブイオンエッチング法で孔20を形成する。

【0088】

次いで、図2(f)に示すように、孔20を介して下部電極14に電気的に接続された配線18を形成する。例えば、フォトリソグラフィ法と蒸着法でアルミニウムにより配線18を形成し、LiTaO3剥離層3の孔20を介して、配線18と下部電極14を接続する。図示していないが、さらに、配線18の電気抵抗を下げるために、バルク波素子の振動領域(下部電極14と上部電極16とが剥離層3を挟んで対向する領域)以外の領域にアルミニウムを厚付けし、配線18を外部端子に接続してパッケージングする。

【0089】

以上の工程でBAWデバイスを作製すると、次のような効果を得ることができる。

【0090】

(1) BAWデバイスを製造する上で、圧電体の材料、結晶方位は、電気機械結合係数や周波数温度特性、音速に影響するため、BAWデバイスの周波数や帯域幅、挿入損失などに重要な影響を与える。圧電体の材料や結晶方位の選択自由度が高い方が、優れたBAWデバイスを構成しやすい。スパッタやCVDなどの成膜法で圧電体薄膜を形成すると、薄膜の材料、結晶方位が制約される。薄膜材料はAlNやZnOなど成膜法で形成できる膜の種類は少なく、圧電体を単結晶化することは難しく、通常はC軸配向膜が得られるに過ぎない。このため、圧電軸が上下にしか向かないので厚みすべり型のBAWを励振することが困難だった。

【0091】

一方、圧電体単結晶から薄膜を剥離する本発明の手法であれば、圧電体の結晶方位の自由度が高く、優れた厚みすべり型BAWが励振する基板を得ることができる。

【0092】

また、BAWデバイスのエネルギー閉じ込め状態やスプリアス応用は、励振されるバルク波の分散関係により決定されるが、材料や結晶方位を調整することで、エネルギー閉じ込めとスプリアス抑制を両立した高Qなバルク波素子が作成できる。

【0093】

(2) 単結晶の育成速度が遅く、割れやすいためスライスしづらく、LiやTaなどの原料が希少で高価なために、LiTaO3基板やLiNbO3基板、水晶基板などの圧電体基板は高価である。単結晶薄膜を形成した複合圧電基板を得る手段として、Si基板と圧電基板を張り合わせた後にCMP(chemical-mechanical polishing;化学機械研磨)で圧電体を研磨しで薄化する手段も考えられるが、この場合、1枚の複合圧電基板を得るために、1枚のSi基板と1枚の圧電体基板が必要であるため、高価な圧電体の材料効率が悪い。

【0094】

本発明の複合圧電基板は、1枚のBAWデバイス用ウェハを製造するために、1枚の安価なSi基板と圧電体薄膜のみを材料とし、この圧電薄膜は1枚の圧電体基板から数十枚〜数百枚得ることができるので、材料の使用量としては無視できる程度に抑えることができる。このため、希少で高価なLiやTaなどの使用量を抑制でき、環境負荷が小さく、安価な圧電基板を得ることができる。

【0095】

(3) 極薄圧電体の厚みはイオン注入するときのエネルギーで決まる。したがって、研磨のように基板うねりに厚みが左右されることはなく、極薄圧電体でも安定した厚みが得られる。圧電体薄膜の厚みは、BAWの波長(周波数=音速/波長なので周波数が決まる)を決定するので、重要である。

【0096】

<実施例3> 実施例3のBAWデバイスについて、図3及び図4を参照しながら説明する。図3は、BAWデバイスの製造工程を示す断面図である。図4はBAWデバイスの平面図である。

【0097】

実施例3のBAWデバイスは、次の工程で製造する。

【0098】

まず、実施例1の工程1〜5と略同様の工程で、複合圧電基板を準備する。

【0099】

すなわち、工程1で、20°YカットLiTaO3圧電体基板と、図3(a)に示す支持基板10xを準備する。支持基板10xは、実施例1と異なり、Si支持基板11にリアクティブイオンエッチングで窪み13aを形成し、窪み13aに犠牲層13xを形成し、Si支持基板11の表面11aをCMPで平滑化し、スパッタ法により、W(タングステン)で下部電極14aを形成したものである。工程2において、実施例2と同じく、圧電体基板にイオン注入する。工程3において、圧電体基板を支持基板10xの下部電極14aに金属接合に接合して基板接合体を形成し、実施例1と同様に、工程4において基板接合体を圧電体基板の欠陥層で剥離し、工程5において圧電体基板及び支持基板の表面を平滑化し、図3(b)に示すように、20°YカットLiTaO3の剥離層3aを有する複合圧電基板30aを準備する。

【0100】

次いで、図3(c)に示すように、LiTaO3の剥離層3aの表面3kに、アルミニウムで上部電極16aを電子ビーム蒸着法とフォトリソグラフィ法により形成する。

【0101】

次いで、図3(d)に示すように、剥離層3aと下部電極14aに、フォトリソグラフィ法とリアクティブイオンエッチング法で、犠牲層13xに達する孔22と、下部電極14aに達する孔24とを形成する。

【0102】

次いで、図3(e)に示すように、犠牲層13xに達する孔22を通してドライエッチングにより犠牲層13xを除去する。

【0103】

次いで、図3(f)及び図4に示すように、フォトリソグラフィ法と蒸着法でアルミニウムにより配線18aを形成し、下部電極14aに達する孔24を介して下部電極14aと接続される配線18aを形成する。図示していないが、さらに、配線18aの電気抵抗を下げるために、バルク波素子の振動領域(下部電極14aと上部電極16aとが剥離層3aを挟んで対向する領域)以外の領域にアルミニウムを厚付けし、配線18aを外部端子に接続してパッケージングする。

【0104】

実施例2のように支持基板10の裏面10bに穴13が開いていると、裏面10b側に別途基板を張り合わせるなどしてフタをする必要があるが、実施例3の構造は支持基板11に穴が開いていないため、裏面側の密閉は不要となる。その他の効果は、実施例2と同じである。

【0105】

<まとめ> 以上に説明した方法で複合圧電基板を製造すると、圧電体材料を効率良く利用して、均質な厚みの極薄圧電膜を形成することができる。

【0106】

なお、本発明は、上記した実施の形態に限定されるものではなく、種々変更を加えて実施することが可能である。

【0107】

例えば、本発明の方法で製造された複合圧電基板は、SAW素子、BAW素子、センサー素子、屈曲振動子、その他の種々の素子に用いることができる。

【符号の説明】

【0108】

2 圧電体基板

3 剥離層

4 欠陥層

10,10x 支持基板

30,30a 複合圧電基板

【技術分野】

【0001】

本発明は、複合圧電基板の製造方法に関し、詳しくは、圧電膜を有する複合圧電基板の製造方法に関する。

【背景技術】

【0002】

近年、極めて薄い圧電体(極薄圧電膜)を利用したフィルタ等の開発が活発に行われている。これらのフィルタ等の極薄圧電膜には、一般には、スパッタ法やCVD法などの堆積法で形成されたAlN薄膜やZnO薄膜が用いられているが、いずれもC軸が基板の上下に整列したC軸配向膜である。

【0003】

一方、圧電体の単結晶基板を支持基板に張り合わせた後に、研磨により圧電体の単結晶基板を薄化することにより、圧電膜を有する複合圧電基板を製造することも提案されている。

【0004】

例えば図6の断面図に示す弾性表面波装置100では、励振電極105が形成されている単結晶からなる圧電基板101は、予めガラス層108を介して保護基板103に接合された状態で研磨され薄板化されたものである(例えば、特許文献1、非特許文献1参照)。

【0005】

また、圧電基板に水素イオンを注入し、圧電基板と支持基板を湿潤雰囲気下に置いて、それぞれの基板表面に親水基を形成した後に、圧電基板と支持基板を張り合わせ、その後、高速加熱して、イオン注入した深さで圧電基板を割って圧電薄膜を得る手法が提案されている(例えば、特許文献2参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−16468号公報

【特許文献2】特表2002−534885号公報

【0007】

【非特許文献1】Y. 0sugi et a1、「Single crysta1 FBAR with LiNbO3 and LiTaO3」、2007 IEEE MTT-S International Microwave Symposium、pp.873-876

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、堆積法で形成した圧電膜は、配向膜を得るための成膜温度や成膜条件などから材料制約が厳しく、主としてAlNが利用される。また、結晶軸の配向方向を制御することもできず、C軸配向膜が主として採用されるため、圧電軸を傾斜させることによる振動モードの工夫が難しい。

【0009】

一方、圧電体の単結晶基板を研磨して形成した圧電膜は、大半の圧電単結晶を研磨クズとして廃棄するため、材料の利用効率が悪い。さらに、圧電膜の厚みは、研磨速度のばらつき、研磨前の基板のうねりにより左右されるため、均質な厚みを得るための制御は難しく生産性が悪い。

【0010】

特許文献2では、親水基による接合が用いられる。この接合方法では、圧電基板表面と支持基板表面に親水基を形成し、その親水基を介して接合される。この親水基による接合は極めて弱いため、強固な接合を得るために、親水基を分解できる温度(例えば400℃)で加熱して、親水基(OH)から水素(H)を脱離させ、圧電基板表面と支持基板表面のボンドを強固にする工程を経る必要がある。

【0011】

しかしながら、接合後に水素ガスを脱離するため、接合界面にガスが溜まり、マイクロキャビティを形成したり、水素ガスが十分に除去できずに圧電結晶中に残留し、結晶構造を破損し、圧電性を劣化させるなどの問題点があった。マイクロキャビティや結晶破壊による接合界面の不均一は、表面波フィルタやバルク波フィルタに応用するときに、弾性散乱や吸音による発熱を引き起こし、フィルタの挿入損失の劣化や発熱による耐電力性能の劣化を引き起こす要因となっていた。

【0012】

特に、Li系圧電材料であるLiTaO3やLiNbO3を用いる場合、水素が残留すると、LiイオンサイトのLiと水素が置換し、圧電性の劣化を生じやすい。

【0013】

例えば、圧電基板としてタンタル酸リチウムやニオブ酸リチウム基板、支持基板としてもタンタル酸リチウムやニオブ酸リチウム基板を用い、圧電基板と支持基板の表面をCMP(化学機械研磨)により平滑化し、その後、湿潤雰囲気下に圧電基板と支持基板を晒して親水基を形成し、基板表面同士を接して張り合わせて親水基による弱い接合をし、500℃で1時間加熱して親水基を分解して強固な接合を行った。このような方法で接合した複合圧電基板は、親水基による弱い接合をした後、500℃で加熱する前は、外力を加えることにより接合界面で容易に剥離することができた。一方、500℃で加熱した後は、接合が強化されたが、接合界面には、目視できる程度のキャビティが随所に形成されていた。また、接合界面の結晶配列をTEM(透過型電子戦顕微鏡)で観察すると、数十nmのキャビティや結晶配列の乱れが観察された。

【0014】

さらに、非線形誘電率顕微鏡を用いて、Hイオンを注入し、400℃で加熱してLiTaO3の分極状態を調査したところ、当初整列していた分極極性がドメイン単位で局所的に反転し、圧電性が劣化していることが分かった。より高温の500℃で加熱すると更に圧電性劣化が顕著となる。

【0015】

本発明は、かかる実情に鑑み、圧電体材料を効率良く利用して、均質な厚みの極薄圧電膜を形成することができる、複合圧電基板の製造方法を提供しようとするものである。

【課題を解決するための手段】

【0016】

本発明は、以下のように構成した複合圧電基板の製造方法を提供する。

【0017】

複合圧電基板の製造方法は、(a)圧電体基板と、支持基板とを準備する、第1の工程と、(b)前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、(c)前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、(d)前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、(e)前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程とを含む。複合圧電基板の製造方法は、(f)前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含む。前記分極処理工程は、前記剥離層に電界を断続的に印加する工程である。

【0018】

上記方法によれば、イオン注入によりに分極が反転しても、修復することができる。

【0019】

また、本発明は、以下のように構成した複合圧電基板の製造方法を提供する。

【0020】

複合圧電基板の製造方法は、(a)圧電体基板と、支持基板とを準備する、第1の工程と、(b)前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、(c)前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、(d)前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、(e)前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程とを含む。複合圧電基板の製造方法は、(f)前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含む。前記分極処理工程は、前記圧電体基板のキュリー温度より100度以上低い温度で行われる工程である。

【0021】

上記方法によれば、イオン注入によりに分極が反転しても、修復することができる。

【0022】

好ましくは、前記分極処理工程は、200度以上で行われる工程である。

【0023】

また、本発明は、以下のように構成した複合圧電基板の製造方法を提供する。

【0024】

複合圧電基板の製造方法は、(a)圧電体基板と、支持基板とを準備する、第1の工程と、(b)前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、(c)前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、(d)前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、(e)前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程とを含む。前記第2の工程において、イオン注入をするときに、自発分極している前記圧電体基板の構成原子がシフトしている方向と同一方向にイオンを注入する。

【0025】

上記方法により圧電体基板の剥離層が接合された複合圧電基板を製造すると、複合圧電基板の表面に極めて薄い圧電体(極薄圧電膜)を形成することができる。例えば単結晶の圧電体基板を用いて、圧電体の極薄単結晶膜を有する複合圧電基板を製造することができる。

【0026】

上記方法によれば、剥離層が剥離された後の圧電体基板は、複合圧電基板の製造に再び利用することができる。1枚の圧電体基板から多量の複合圧電基板を製造することができ、圧電基板を研磨して圧電膜を形成する場合に比べ、圧電体材料を廃棄する量が減るので、高価な圧電体の使用量を減らすことができる。

【0027】

また、剥離層の厚みは、イオン注入するときのエネルギーで決まり、研磨のように基板のうねりに圧電体の厚みが左右されることがないため、極薄でも均一にすることができる。したがって、表面に均一な厚みの極薄圧電膜を有する複合圧電基板が得られる。

【0028】

イオン注入をするときに、自発分極している前記圧電体基板の構成原子がシフトしている方向と同一方向にイオンを注入する。

【0029】

この場合、圧電体基板について、イオン注入による圧電性の劣化を抑制できる。

【0030】

また、親水化処理によるOH基を用いた接合でなく、清浄活性化工程によるOH基を用いない接合であるので、接合界面に残留する水素の脱離が必要ない。このため、親水基を分解するための高温長時間の加熱が不要であり、また、接合界面のガス発生やマイクロキャビティ形成がなく、圧電結晶中への水素ガス残留がない。このため、結晶構造の破損や圧電性の劣化が抑制される。特に、Li系圧電材料であるLiTaO3やLiNbO3を用いる場合、水素残留によるLiイオンサイトのLiと水素の交換を生じないので、圧電性が維持される。

【0031】

好ましくは、前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、より好ましくは前記第5の工程の後に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含む。

【0032】

この場合、分極処理工程における圧電体基板の表面に励起される焦電荷によるイオン注入加工(ドーズ量、注入深さ)のばらつき、基板の破損が避けられる。

【0033】

好ましくは、(f)前記欠陥層が形成された前記圧電体基板の表面と前記支持基板の表面との少なくとも一方について、当該表面に付着した不純物を除去して当該表面を構成する原子を直接露出させ、活性化させる、清浄活性化工程をさらに含む。

【0034】

好ましくは、接合界面に金属元素を配する。

【0035】

好ましくは、前記圧電体基板にリチウム系圧電材料を用いる。

【0036】

上記方法で製造された複合圧電基板に形成された圧電体基板の剥離層の極めて薄い圧電体を利用して、弾性表面波素子、弾性境界波素子、バルク波素子、板波素子などの弾性波素子を形成することができる。これらの弾性波素子を有する電子部品の製造に、上記方法で製造された複合圧電基板を用いると、高価な圧電体基板の使用量を削減できる。

【発明の効果】

【0037】

本発明の複合圧電基板の製造方法によれば、圧電体材料を効率良く利用して、均質な厚みの極薄圧電膜を形成することができる。

【図面の簡単な説明】

【0038】

【図1】複合圧電基板の製造工程を示す断面図である。(実施例1)

【図2】BAWデバイスの製造工程を示す断面図である。(実施例2)

【図3】BAWデバイスの製造工程を示す断面図である。(実施例3)

【図4】BAWデバイスの断面図である。(実施例3)

【図5】SAWデバイスの製造工程を示す断面図である。(実施例1)

【図6】弾性表面波装置の断面図である。(従来例)

【発明を実施するための形態】

【0039】

以下、本発明の実施の形態について、図1〜図5を参照しながら説明する。

【0040】

<実施例1> 実施例1のSAW(surface acoustic wave;弾性表面波)デバイスの製造方法について、図1、図5を参照しながら説明する。

【0041】

まず、SAWデバイスに用いる複合圧電基板30の製造工程について、図1を参照しながら説明する。図1は、複合圧電基板30の製造工程を示す断面図である。

【0042】

(工程1) 図1(a−1)及び(a−2)に示すように、圧電体基板2と支持基板10を準備する。例えば、圧電体基板2として42°YカットLiTaO3基板、支持基板10としてSi基板を準備する。それぞれの基板2、10の表面2a,10aは、予め鏡面研磨しておく。

【0043】

(工程2) 次いで、図1(b)に示すように、圧電体基板2の表面2aに、矢印8で示すように、イオンを注入して、圧電体基板2内において表面2aから所定深さの領域に、破線で模式的に示す欠陥層4を形成する。例えば、LiTaO3圧電体基板2にH+イオンを注入する。注入エネルギーは150KeV、ドーズ量は9×1016cm−1である。このとき、H+イオンが圧電体基板2の表面2aから1μm程度の深さに分布する欠陥層4が形成される。

【0044】

(洗浄活性化工程) 圧電体基板2と支持基板20を減圧チャンバに入れ、それぞれの表面2a,10aにArイオンをビーム照射し、表面2a,10aに付着した親水基、水素、酸化被膜などの不純物を除去する。不純物が除去された表面2a,10aは、基板2,10を構成する原子が直接露出し、活性化される。このように、清浄活性化した表面2a,10a同士を真空中で接触させると、元素同士が直接ボンドを結び、強固な接合が得られる。接合界面に不純物が存在しないため、接合後に不純物を除去する必要がなく、接合界面付近の結晶の破損も抑制される。

【0045】

(工程3) 次いで、図1(c)に示すように、圧電体基板2の表面2aと、支持基板10の表面10aとを接合して、基板接合体40を形成する。

【0046】

LiTaO3圧電体基板2とSi支持基板10の場合には、線熱膨張係数が異なるので、常温において、基板表面2a,10aをプラズマにより活性化し、真空中で接合する常温直接接合を行うことが望ましい。

【0047】

LiTaO3圧電体基板2とSi支持基板10とを接合した後、500℃で加熱する。これにより、H+イオンを注入したLiTaO3圧電体基板2の表面2aから1μmの深さの欠陥層4には、表面2aに沿ってマイクロキャビティが発生し、加熱によりこのキャビティが成長する。

【0048】

なお、接合界面に、元素同士のボンドを強化するために微量(数nm)のFeなどの金属元素を配してもよい。金属元素は大気中での酸化反応などにより汚染されやすい。そこで、金属イオンの堆積は、接合を行う真空に減圧したチャンバ内で、接合の直前に行うことが望ましい。

【0049】

(工程4) 次いで、図1(d)に示すように、基板接合体40の圧電体基板2と支持基板10とを、圧電体基板2内に形成された欠陥層4で分離して、圧電体基板2の表面2aと欠陥層4との間の剥離層3が圧電体基板2から剥離されて支持基板10に接合された複合圧電基板30を形成する。

【0050】

例えば、LiTaO3圧電体基板2の表面2aから1μmの深さの欠陥層4に形成されたマイクロキャビティに沿って分離するため、1μmの厚さのLiTaO3薄膜の剥離層3が支持基板10の表面10aに接合された複合圧電基板30と、表面2a側からLiTaO3薄膜の剥離層3が剥離されたLiTaO3圧電体基板2とに分離する。

【0051】

(工程5) 次いで、図1(e−1)及び(e−2)に模式的に示すように凹凸が形成された破断面である圧電体基板2と複合圧電基板30の表面2a,3aを研磨し、図1(f−1)及び(f−2)に示すように圧電体基板2と複合圧電基板30の表面2k,3kを平滑化する。

【0052】

例えば、LiTaO3薄膜の剥離層3の破断面が現れる複合圧電基板30の表面3aと、LiTaO3薄膜の剥離層3が剥離されたLiTaO3圧電体基板2の表面2aは、RMS(root mean square)で1nm程度の荒れた面になっているため、CMP(chemical-mechanical polishing;化学機械研磨)により表面2a,3aから厚さ100nm程度研磨して除去して平滑化する。

【0053】

(工程6) 表面3kが平滑化された複合圧電基板30について、剥離層3の圧電体の分極反転を修正するため、分極処理を行う。例えば、表面3aを平滑化したLiTaO3薄膜の剥離層3について、400℃で5ms、22kVのパルス電圧を印加する分極処理を行う。

【0054】

圧電体結晶を構成する原子の一部は、正又は負に荷電しイオン化している。このイオン化した原子に、例えば電界を印加すると正に荷電したイオンは陰極側に、負に荷電したイオンは陽極側に結晶内をわずかにシフトし、電気双板子を生ずる。この現象は電気分極と呼ばれている。電界の印加を止めても分極の状態を維持することができる結晶も存在し、この状態は前述した自発分極と呼ばれる。自発分極する圧電体結晶に高エネルギーで多量のイオンを注入すると、このイオンのシフトした状態が変化し、分極の極性が反転したりする。部分的な分極の反転は圧電性の劣化を引き起こすため、好ましくない。

【0055】

そこで、イオン注入した後に分極処理を行うことで分極の反転を修復できる。例えば、LiNbO3の場合、700℃の加熱雰囲気で22kV/mmの電界を印加する。分極処理は剥離工程後に行うことが望ましく、温度は支持基板や電極の融点や熱膨張係数差を考慮して、200〜1200℃で行う。高温であるほど抗電界が下がるので、印加する電界を低く抑えることができる。また、電界は1μs〜1分の範囲で断続的に印加すると直流電界による結晶へのダメージを抑制できるので、望ましい。また、200℃以上での加熱は、イオン注入により受けた結晶のひずみを緩和するため望ましい。結晶ひずみをとるための加熱温度は、分極の解消を避けるためにキューリー温度より100℃以上低くする。

【0056】

なお、分極反転などの圧電性の劣化は工程6の分極処理により回復できるが、結晶に負担がかかるため、工程6に至る前の分極反転などの圧電性劣化は極力抑制しておくことが望ましい。また、結晶材料や結晶方位によっては分極処理が難しい圧電体も存在するため、工程6に至る前の圧電性劣化の抑制策は重要である。

【0057】

分極はイオン化した圧電結晶の構成元素がわずかにシフトすることで生じる。一般に、わずかにシフトさせるためのエネルギー量は、構成元素が結晶単位からはずれるエネルギー量に比べて小さい。そこで、自発分極を示すイオンのシフトしている方向と同一方向からイオンを注入することで、自発分極の極性反転が生じるのを抑制できる。

【0058】

例えば、LiTaO3やLiNbOの場合、LiイオンやTaイオン、Nbイオンは+C軸方向にわずかにシフトしているので、−C軸側から+C軸側に向かってイオンを注入することが望ましい。なお、イオンの注入方向に対してC軸のなす角度θが−90°<θ<+90°の範囲とすれば効果が得られる。

【0059】

また、工程4において、剥離は圧電体のキューリー温度以下で行うことが望ましい。キューリー温度を超えると、分極が一旦開放されるため、圧電性が劣化する。

【0060】

本願発明者の知見によれば、工程4において、欠陥層で剥離するために必要な加熱温度は500〜600℃である。一般に電子部品用に供給されているLiTaO3ウェハは、キューリー温度が600℃前後と低く、剥離に必要な加熱温度とキューリー温度が近接している。このため、圧電性が劣化しやすい。LiTaO3やLiNbO3において、LiのTaやNbに対する組成比xが48.0%≦x<49.5%の場合、コングルエント組成と呼ばれ、前述の電子部品用圧電基板として大量に供給されているウェハに用いられている。一方、組成比が49.5%≦x≦50.5%はストイキオ組成と呼ばれている。LiTaO3の場合、コングルエント組成の場合はキューリー温度が590〜650℃と低く、ストイキオ組成の場合は660〜700℃となる。そこで、LiTaO3を用いる場合、LiのTaに対する組成比を49.5%≦x≦50.5%としたストイキオ組成とすることが工程4における加熱時の圧電性劣化を抑制できるので望ましい。

【0061】

なお、LiNbO3の場合、コングルエント組成の場合は1100〜1180℃、ストイキオ組成の場合は1180〜1200℃となる。

【0062】

また、工程4において、圧電体がLiTaO3やLiNbO3のように焦電性をもつ場合、昇温や降温により基板表面に電荷が蓄積される。表面に蓄積された電荷による電界が分極方向と逆方向から圧電体の抗電界を超えて加わると分極が反転し圧電性が劣化する。工程4では昇温と降温のいずれかにおいて、分極と逆方向から電界が加わるため、圧電性の劣化を生じやすい。

【0063】

本願発明者は圧電体の導電率を高め、かつ、温度変化のペースを焦電荷による電界が圧電体の抗電界以下となるようにすることにより、圧電性の劣化を抑制できることを見出した。

【0064】

実施例1において、LiTaO3の導電率を高めて4×1010S/cmとなるように処理したウェハを用い、工程4において表面の電位が200V以下となるように昇温及び降温のペースを低下させることにより圧電性の劣化を抑制できた。LiTaO3やLiNbO3の導電率を高める処理は、特開2004−328712のように低酸素雰囲気中で高温アニールしたり、特開2005−119906や特開2005−179117のように金属粉末中で加熱する手段が知られている。

【0065】

以上に説明した製造工程により製造された複合圧電基板の作製例について、観察した。すなわち、圧電体基板としてLiTaO3基板、支持基板としてもLiTaO3基板を用い、圧電体基板と支持基板の表面をCMPにより平滑化し、真空中で圧電体基板と支持基板の表面にArイオンビームを照射して、基板表面を清浄活性化し、基板表面同士を接して張り合わせて、基板の元素同士が直接ボンドする強固な接合を行った後の複合圧電基板の外形写真を撮影した。撮影した写真には、接合界面に目視できるようなキャビティはなかった。また、接合界面の結晶配列をTEM(透過型電子戦顕微鏡)で観察すると、整列した結晶配列が観察された。

【0066】

以上に説明した製造工程により製造された複合圧電基板30は、表面に圧電体の剥離層3を有しているので、弾性波素子を作製するために用いることができる。残った圧電体基板2は、次の複合圧電基板30を作製するための素材として再び利用する。

【0067】

次に、SAWデバイスの製造工程について、図5の断面図を参照しながら説明する。

【0068】

図5(a)に示すように、前述の工程1〜6で製造された複合圧電基板30を準備し、図5(b)に示すように、複合圧電基板30の表面3kに、IDT電極15等を形成する。

【0069】

例えば、支持基板10の表面10aにLiTaO3薄膜の剥離層3が接合された複合圧電基板30の表面3kに露出するLiTaO3薄膜の剥離層3の平滑化された表面に、フォトリソグラフィ技術を用いてアルミニウム膜をパターンニングし、IDT電極15、パッド電極(不図示)、IDT電極15とパッド電極との間を接続する配線(不図示)などの導体パターンを形成して、SAWフィルタなどのSAWデバイスを作製する。

【0070】

以上に説明した工程でSAWデバイスを作製すると、次のような効果を得ることができる。

【0071】

(1) SAWデバイスを製造する上で、圧電体の材料、結晶方位は、電気機械結合係数や周波数温度特性、音速に影響するため、SAWデバイスの周波数や帯域幅、挿入損失などに重要な影響を与える。圧電体の材料や結晶方位の選択自由度が高い方が、優れたSAWデバイスを構成しやすい。

【0072】

すなわち、スパッタやCVDなどの成膜法で圧電体薄膜を形成すると、薄膜の材料、結晶方位が制約される。薄膜材料はAlNやZnOなど、成膜法で形成できる膜の種類は少なく、圧電体を単結晶化することは難しく、通常はC軸配向膜が得られるに過ぎない。このため、圧電軸が上下にしか向かないのでSH型のSAWを励振することが困難だった。

【0073】

一方、圧電体単結晶から薄膜を剥離する本発明の手法であれば、圧電体の結晶方位の自由度が高く、優れたSH型SAWが励振する36°〜46゜Yカットの圧電基板を得ることができる。

【0074】

(2) 単結晶の育成速度が遅く、割れやすいためスライスしづらく、LiやTaなどの原料が希少で高価なために、基板が高価なLiTaO3基板やLiNbO3基板、水晶基板などの圧電体基板に比べ、Si基板は安価である。

【0075】

すなわち、従来は、1枚のSAWデバイス用ウェハには、1枚の高価な圧電体基板が用いられていた。これに対し、本発明の複合圧電基板は、1枚のSAWデバイス用ウェハを製造するために、1枚の安価なSi基板と圧電体薄膜のみを材料とし、この圧電薄膜は1枚の圧電体基板から数十枚〜数百枚得ることができるので、材料の使用量としては無視できる程度の量に抑えることができる。このため、希少で高価なLiやTaなどの使用量を抑制でき、環境負荷が小さく、安価な圧電基板を得ることができる。

【0076】

(3) 携帯電話用のRFフィルタには、1〜2Wの大きな電力印加に耐えることが望まれる。SAWフィルタの耐電力性能は、電気信号を加えたときのIDT領域の温度により大きな影響を受ける。電力印加によりIDT領域が250℃などの高温になると、SAWフィルタが破壊するまでの時間が著しく短くなる。IDT領域の温度上昇は、電気的なオーミック損に起因するジュール熱や弾性的な吸音による発熱が、圧電体基板の熱伝導率の低さにより十分に放熱されないことが要因である。LiTaO3やLiNbO3などの圧電体のみで構成された圧電基板は、熱伝導率がSiに比べて小さく、放熱性がよくない。本発明の複合圧電基板は、Siと同等の熱伝導率を得ることができるため、放熱性がよい。このため、大きな電力印加に耐えることができる。

【0077】

(4) 極薄圧電体の厚みはイオン注入するときのエネルギーで決まる。したがって、研磨のように基板うねりに厚みが左右されることはなく、極薄圧電体でも安定した厚みが得られる。圧電体薄膜の厚みは、SAWの音速(周波数=音速/波長なので周波数が決まる)を決定するので重要である。本発明の複合圧電基板は、一定厚みの圧電薄膜を形成できるので、SAWデバイスの特性が安定する。

【0078】

(5) 42°YカットのLiTaO3基板は、−Z軸が42°傾斜して表面側となる。LiTaO3を構成するLi原子とTa原子は、わずかに裏面側(+Z軸側)にシフトして自発分極している。本発明では、−Z軸側からイオンを注入することで、分極反転を抑制している。

【0079】

(6) 工程1〜6で作製した複合圧電基板は、SAWフィルタに限らず、境界波やラム波などの板波を用いたフィルタなどにも用いることができる。境界波の場合は、次の実施例2のように複合圧電基板に素子部を構成すればよい。板波を用いる場合は、次の実施例3のように、支持基板を裏面からエッチングして圧電体の剥離層を裏面から露出させればよい。

【0080】

(7) SiはLiTaO3に比べて線膨張係数が小さいため、Si支持基板にLiTaO3剥離膜が接合された複合圧電基板は、周波数温度係数を抑制できる。

【0081】

<実施例2> 実施例2のBAW(bulk acoustic wave;バルク弾性波)デバイスについて、図2を参照しながら説明する。図2は、BAWデバイスの製造工程を示す断面図である。

【0082】

実施例2のBAWデバイスは、次の工程で製造する。

【0083】

まず、図2(a)に示すように、複合圧電基板30を準備する。例えば、20°YカットLiTaO3圧電体基板とSi支持基板10とを用い、実施例1の工程1〜5と同じ工程で、Si支持基板10の表面10aに20°YカットのLiTaO3剥離層3が接合された複合圧電基板30を作製する。

【0084】

次いで、図2(b)に示すように、複合圧電基板30の表面3kに上部電極16を形成する。例えば、LiTaO3剥離層3の表面3kに、電子ビーム蒸着法とフォトリソグラフィ法により、アルミニウムで上部電極16を形成する。

【0085】

次いで、図2(c)に示すように、支持基板10に穴13を形成し、剥離層3の裏面3sを露出させる。例えば、Si支持基板10の剥離層3とは反対側の裏面10bから、フォトリソグラフィ法とリアクティブイオンエッチング法により、Si支持基板10をエッチングして穴13を形成し、圧電体の剥離層3の裏面3sを露出させる。

【0086】

次いで、図2(d)に示すように、剥離層3の裏面3sに下部電極14を形成する。例えば、LiTaO3剥離層3の裏面3sに、アルミニウムで下部電極14を電子ビーム蒸着法とフォトリソグラフィ法により形成する。

【0087】

次いで、図2(e)に示すように、剥離層3に下部電極14が露出する孔20を形成する。例えば、LiTaO3剥離層3の表面3k側から、フォトリソグラフィ法とリアクティブイオンエッチング法で孔20を形成する。

【0088】

次いで、図2(f)に示すように、孔20を介して下部電極14に電気的に接続された配線18を形成する。例えば、フォトリソグラフィ法と蒸着法でアルミニウムにより配線18を形成し、LiTaO3剥離層3の孔20を介して、配線18と下部電極14を接続する。図示していないが、さらに、配線18の電気抵抗を下げるために、バルク波素子の振動領域(下部電極14と上部電極16とが剥離層3を挟んで対向する領域)以外の領域にアルミニウムを厚付けし、配線18を外部端子に接続してパッケージングする。

【0089】

以上の工程でBAWデバイスを作製すると、次のような効果を得ることができる。

【0090】

(1) BAWデバイスを製造する上で、圧電体の材料、結晶方位は、電気機械結合係数や周波数温度特性、音速に影響するため、BAWデバイスの周波数や帯域幅、挿入損失などに重要な影響を与える。圧電体の材料や結晶方位の選択自由度が高い方が、優れたBAWデバイスを構成しやすい。スパッタやCVDなどの成膜法で圧電体薄膜を形成すると、薄膜の材料、結晶方位が制約される。薄膜材料はAlNやZnOなど成膜法で形成できる膜の種類は少なく、圧電体を単結晶化することは難しく、通常はC軸配向膜が得られるに過ぎない。このため、圧電軸が上下にしか向かないので厚みすべり型のBAWを励振することが困難だった。

【0091】

一方、圧電体単結晶から薄膜を剥離する本発明の手法であれば、圧電体の結晶方位の自由度が高く、優れた厚みすべり型BAWが励振する基板を得ることができる。

【0092】

また、BAWデバイスのエネルギー閉じ込め状態やスプリアス応用は、励振されるバルク波の分散関係により決定されるが、材料や結晶方位を調整することで、エネルギー閉じ込めとスプリアス抑制を両立した高Qなバルク波素子が作成できる。

【0093】

(2) 単結晶の育成速度が遅く、割れやすいためスライスしづらく、LiやTaなどの原料が希少で高価なために、LiTaO3基板やLiNbO3基板、水晶基板などの圧電体基板は高価である。単結晶薄膜を形成した複合圧電基板を得る手段として、Si基板と圧電基板を張り合わせた後にCMP(chemical-mechanical polishing;化学機械研磨)で圧電体を研磨しで薄化する手段も考えられるが、この場合、1枚の複合圧電基板を得るために、1枚のSi基板と1枚の圧電体基板が必要であるため、高価な圧電体の材料効率が悪い。

【0094】

本発明の複合圧電基板は、1枚のBAWデバイス用ウェハを製造するために、1枚の安価なSi基板と圧電体薄膜のみを材料とし、この圧電薄膜は1枚の圧電体基板から数十枚〜数百枚得ることができるので、材料の使用量としては無視できる程度に抑えることができる。このため、希少で高価なLiやTaなどの使用量を抑制でき、環境負荷が小さく、安価な圧電基板を得ることができる。

【0095】

(3) 極薄圧電体の厚みはイオン注入するときのエネルギーで決まる。したがって、研磨のように基板うねりに厚みが左右されることはなく、極薄圧電体でも安定した厚みが得られる。圧電体薄膜の厚みは、BAWの波長(周波数=音速/波長なので周波数が決まる)を決定するので、重要である。

【0096】

<実施例3> 実施例3のBAWデバイスについて、図3及び図4を参照しながら説明する。図3は、BAWデバイスの製造工程を示す断面図である。図4はBAWデバイスの平面図である。

【0097】

実施例3のBAWデバイスは、次の工程で製造する。

【0098】

まず、実施例1の工程1〜5と略同様の工程で、複合圧電基板を準備する。

【0099】

すなわち、工程1で、20°YカットLiTaO3圧電体基板と、図3(a)に示す支持基板10xを準備する。支持基板10xは、実施例1と異なり、Si支持基板11にリアクティブイオンエッチングで窪み13aを形成し、窪み13aに犠牲層13xを形成し、Si支持基板11の表面11aをCMPで平滑化し、スパッタ法により、W(タングステン)で下部電極14aを形成したものである。工程2において、実施例2と同じく、圧電体基板にイオン注入する。工程3において、圧電体基板を支持基板10xの下部電極14aに金属接合に接合して基板接合体を形成し、実施例1と同様に、工程4において基板接合体を圧電体基板の欠陥層で剥離し、工程5において圧電体基板及び支持基板の表面を平滑化し、図3(b)に示すように、20°YカットLiTaO3の剥離層3aを有する複合圧電基板30aを準備する。

【0100】

次いで、図3(c)に示すように、LiTaO3の剥離層3aの表面3kに、アルミニウムで上部電極16aを電子ビーム蒸着法とフォトリソグラフィ法により形成する。

【0101】

次いで、図3(d)に示すように、剥離層3aと下部電極14aに、フォトリソグラフィ法とリアクティブイオンエッチング法で、犠牲層13xに達する孔22と、下部電極14aに達する孔24とを形成する。

【0102】

次いで、図3(e)に示すように、犠牲層13xに達する孔22を通してドライエッチングにより犠牲層13xを除去する。

【0103】

次いで、図3(f)及び図4に示すように、フォトリソグラフィ法と蒸着法でアルミニウムにより配線18aを形成し、下部電極14aに達する孔24を介して下部電極14aと接続される配線18aを形成する。図示していないが、さらに、配線18aの電気抵抗を下げるために、バルク波素子の振動領域(下部電極14aと上部電極16aとが剥離層3aを挟んで対向する領域)以外の領域にアルミニウムを厚付けし、配線18aを外部端子に接続してパッケージングする。

【0104】

実施例2のように支持基板10の裏面10bに穴13が開いていると、裏面10b側に別途基板を張り合わせるなどしてフタをする必要があるが、実施例3の構造は支持基板11に穴が開いていないため、裏面側の密閉は不要となる。その他の効果は、実施例2と同じである。

【0105】

<まとめ> 以上に説明した方法で複合圧電基板を製造すると、圧電体材料を効率良く利用して、均質な厚みの極薄圧電膜を形成することができる。

【0106】

なお、本発明は、上記した実施の形態に限定されるものではなく、種々変更を加えて実施することが可能である。

【0107】

例えば、本発明の方法で製造された複合圧電基板は、SAW素子、BAW素子、センサー素子、屈曲振動子、その他の種々の素子に用いることができる。

【符号の説明】

【0108】

2 圧電体基板

3 剥離層

4 欠陥層

10,10x 支持基板

30,30a 複合圧電基板

【特許請求の範囲】

【請求項1】

圧電体基板と、支持基板とを準備する、第1の工程と、

前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、

前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、

前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、

前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程と、

を含み、

前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含み、

前記分極処理工程は、前記剥離層に電界を断続的に印加する工程であることを特徴とする、複合圧電基板の製造方法。

【請求項2】

圧電体基板と、支持基板とを準備する、第1の工程と、

前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、

前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、

前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、

前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程と、

を含み、

前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含み、

前記分極処理工程は、前記圧電体基板のキュリー温度より100度以上低い温度で行われる工程であることを特徴とする、複合圧電基板の製造方法。

【請求項3】

前記分極処理工程は、200度以上で行われる工程であることを特徴とする、請求項2に記載の複合圧電基板の製造方法。

【請求項4】

圧電体基板と、支持基板とを準備する、第1の工程と、

前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、

前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、

前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、

前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程と、

を含み、

前記第2の工程において、イオン注入をするときに、自発分極している前記圧電体基板の構成原子がシフトしている方向と同一方向にイオンを注入することを特徴とする、複合圧電基板の製造方法。

【請求項5】

前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含むことを特徴とする、請求項4に記載の複合圧電基板の製造方法。

【請求項6】

前記欠陥層が形成された前記圧電体基板の表面と前記支持基板の表面との少なくとも一方について、当該表面に付着した不純物を除去して当該表面を構成する原子を直接露出させ、活性化させる、清浄活性化工程をさらに含むことを特徴とする、請求項1から5のいずれか1つに記載の複合圧電基板の製造方法。

【請求項7】

接合界面に金属元素を配したことを特徴とする、請求項1乃至6のいずれか一つに記載の複合圧電基板の製造方法。

【請求項8】

前記圧電体基板にリチウム系圧電材料を用いたことを特徴とする、請求項1乃至7のいずれか一つに記載の複合圧電基板の製造方法。

【請求項1】

圧電体基板と、支持基板とを準備する、第1の工程と、

前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、

前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、

前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、

前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程と、

を含み、

前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含み、

前記分極処理工程は、前記剥離層に電界を断続的に印加する工程であることを特徴とする、複合圧電基板の製造方法。

【請求項2】

圧電体基板と、支持基板とを準備する、第1の工程と、

前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、

前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、

前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、

前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程と、

を含み、

前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含み、

前記分極処理工程は、前記圧電体基板のキュリー温度より100度以上低い温度で行われる工程であることを特徴とする、複合圧電基板の製造方法。

【請求項3】

前記分極処理工程は、200度以上で行われる工程であることを特徴とする、請求項2に記載の複合圧電基板の製造方法。

【請求項4】

圧電体基板と、支持基板とを準備する、第1の工程と、

前記圧電体基板の表面からイオンを注入して、前記圧電体基板内において前記表面から所定深さの領域に欠陥層を形成する、第2の工程と、

前記欠陥層が形成された前記圧電体基板の前記表面に前記支持基板を接合して基板接合体を形成する、第3の工程と、

前記基板接合体を、前記圧電体基板内に形成された前記欠陥層で分離して、前記圧電体基板の前記表面と前記欠陥層との間の剥離層が前記圧電体基板から剥離されて前記支持基板に接合された複合圧電基板を形成する、第4の工程と、

前記複合圧電基板の前記剥離層の表面を平滑化する、第5の工程と、

を含み、

前記第2の工程において、イオン注入をするときに、自発分極している前記圧電体基板の構成原子がシフトしている方向と同一方向にイオンを注入することを特徴とする、複合圧電基板の製造方法。

【請求項5】

前記第2の工程の後かつ前記第3の工程の前又はそれ以降に、前記複合圧電基板の前記剥離層の分極処理を行う分極処理工程をさらに含むことを特徴とする、請求項4に記載の複合圧電基板の製造方法。

【請求項6】

前記欠陥層が形成された前記圧電体基板の表面と前記支持基板の表面との少なくとも一方について、当該表面に付着した不純物を除去して当該表面を構成する原子を直接露出させ、活性化させる、清浄活性化工程をさらに含むことを特徴とする、請求項1から5のいずれか1つに記載の複合圧電基板の製造方法。

【請求項7】

接合界面に金属元素を配したことを特徴とする、請求項1乃至6のいずれか一つに記載の複合圧電基板の製造方法。

【請求項8】

前記圧電体基板にリチウム系圧電材料を用いたことを特徴とする、請求項1乃至7のいずれか一つに記載の複合圧電基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−213244(P2012−213244A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2012−177723(P2012−177723)

【出願日】平成24年8月10日(2012.8.10)

【分割の表示】特願2009−546984(P2009−546984)の分割

【原出願日】平成20年10月23日(2008.10.23)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成24年8月10日(2012.8.10)

【分割の表示】特願2009−546984(P2009−546984)の分割

【原出願日】平成20年10月23日(2008.10.23)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]