複合基板の製造方法および半導体デバイスの製造方法

【課題】中間層の一部および支持基板の一部の少なくともいずれかが露出している複合基板であっても、半導体デバイスを歩留まりよく製造することができる複合基板の製造方法を提供する。

【解決手段】本複合基板の製造方法は、支持基板10と、その主面の少なくとも一部上に配置された中間層20と、その主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1を準備する工程と、第1の複合基板1の中間層20の露出部分を選択的にエッチングにより除去することにより第2の複合基板2を得る工程と、第2の複合基板2の支持基板10の主面の露出部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板3を得る工程と、を含む。

【解決手段】本複合基板の製造方法は、支持基板10と、その主面の少なくとも一部上に配置された中間層20と、その主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1を準備する工程と、第1の複合基板1の中間層20の露出部分を選択的にエッチングにより除去することにより第2の複合基板2を得る工程と、第2の複合基板2の支持基板10の主面の露出部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板3を得る工程と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、支持基板に中間層を介在させてIII族窒化物層を積層させた複合基板の製造方法およびこれにより得られた複合基板を用いた半導体デバイスの製造方法に関する。

【背景技術】

【0002】

III族窒化物半導体を用いた半導体デバイスは種々の方法で形成されている。一つの方法は、III族窒化物半導体基板上に、少なくとも1層のIII族窒化物半導体層をエピタキシャル成長させる方法である。しかし、かかる方法は、III族窒化物半導体基板が非常に高価であるため、得られる半導体デバイスも非常に高価となる。

【0003】

このため、III族窒化物半導体とは化学組成が異なる支持基板上にIII族窒化物半導体層を積層させた複合基板のIII族窒化物半導体層上にIII族窒化物半導体層をエピタキシャル成長させる方法が好適に用いられている。

【0004】

たとえば、特開2006−210660号公報(特許文献1)は、積層された半導体基板の製造方法として、第1の窒化物半導体基板の表面近傍にイオンを注入する工程と、その第1の窒化物半導体基板の表面側を第2の基板に重ね合わせる工程と、重ね合わせた上記2枚の基板を熱処理する工程と、イオン注入された層を境として上記第1の窒化物半導体基板の大部分を上記第2の窒化物半導体基板から引き剥がす工程と含む製造方法を開示する。

【0005】

また、特開2008−300562号公報(特許文献2)は、III族窒化物半導体層貼り合わせ基板として、III族窒化物半導体基板と下地基板とが貼り合わされている基板であって、III族窒化物半導体層の熱膨張係数と下地基板の熱膨張係数との差が4.5×10-6K-1以下と小さく、下地基板の熱伝導率が50W・m-1・K-1以上と高い貼り合わせ基板を開示する。また、かかるIII族窒化物半導体層貼り合わせ基板上に形成されている少なくとも1層のIII族窒化物半導体エピタキシャル層を含む半導体デバイスを開示する。

【0006】

また、特開2010−165927号公報(特許文献3)は、発光素子用基板として、波長が400nm以上600nm以下の光に対して透明な透明基板と、透明基板の一方の主面上に接合により形成された窒化物系化合物半導体薄膜とを備え、透明基板の主表面に垂直な方向における透明基板の熱膨張係数をα1、窒化物系化合物半導体薄膜の熱膨張係数をα2とすれば、(α1−α2)/α2が−0.5以上1.0以下と小さい基板が開示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2006−210660号公報

【特許文献2】特開2008−300562号公報

【特許文献3】特開2010−165927号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記の特開2006−210660号公報(特許文献1)、特開2008−300562号公報(特許文献2)および特開2010−165927号公報(特許文献3)に開示された複合基板は、いずれも支持基板としての下地基板とIII族窒化物層とを直接貼り合わせたものであり、支持基板(下地基板)の種類によってはIII族窒化物層との接合強度が必ずしも十分でない場合があった。

【0009】

このため、支持基板とIII族窒化物半導体層との接合強度を高めるため、支持基板とIII族窒化物層とをそれらの間に中間層を介在させて貼り合わせた複合基板が検討されつつある。

【0010】

しかしながら、現在の実際の製造において得られる支持基板とIII族窒化物層との間に中間層を介在させて積層された複合基板上にIII族窒化物半導体層をエピタキシャル成長させると、複合基板の主面の一部上にエピタキシャル成長とは異なり異常な成長、具体的には、膜厚や組成、結晶方位、成長モードなどが不均一な成長が発生するため、半導体デバイスの歩留まりが低下するという問題点がある。これにより、複合基板の主面上に数百nm〜数十μmの凹凸が形成される。この凹凸は、たとえば、半導体デバイス作製時の樹脂(レジスト)成膜時に樹脂厚みの不均一の原因となったり、別の保持基板へ貼り替える際に面内一様な密着を阻害する原因となったりすることで、半導体デバイスの歩留まりが低下するという問題を引き起こす。

【0011】

本発明者らは、上記問題点の原因について鋭意調査研究した結果、複合基板上のIII族窒化物層の一部が欠落して中間層および支持基板の主面の少なくとも一部が露出しており、複合基板のIII族窒化物層上にIII族窒化物半導体層をエピタキシャル成長させる際に、この露出部上にIII族窒化物が不均一成長などの異常成長を引き起こすことをつきとめた。本発明は、上記の知見に基づき、中間層の一部および支持基板の一部の少なくともいずれかが露出している複合基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まり良く製造することができる複合基板の製造方法および半導体デバイスの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、支持基板と、支持基板の主面の少なくとも一部上に配置された中間層と、中間層の主面の少なくとも一部上に配置されたIII族窒化物層とを含み、III族窒化物層の主面と、中間層の主面の一部および支持基板の主面の一部の少なくともいずれかと、が露出している第1の複合基板を準備する工程と、第1の複合基板の中間層の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板を得る工程と、第2の複合基板の支持基板の主面が露出している部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板を得る工程と、を含む複合基板の製造方法である。

【0013】

本発明にかかる複合基板の製造方法において、中間層は、その上におけるIII族窒化物半導体の成長が不均一であるものとすることができる。さらに、中間層は、ケイ素酸化物、ケイ素窒化物、金属酸化物、金属窒化物およびこれらの複合物からなる群から選ばれる少なくとも一つを含むことができる。また、支持基板は、その上におけるIII族窒化物半導体の成長が不均一であるものとすることができる。さらに、支持基板は、ケイ素酸化物、金属酸化物、多結晶GaN、多結晶SiC、Cu、WおよびMoからなる群から選ばれる少なくとも一つを含むことができる。

【0014】

また、本発明は、上記の複合基板の製造方法により得られた第3の複合基板のIII族窒化物層の主面上に少なくとも1層のIII族窒化物半導体層をエピタキシャル成長させる工程を含む半導体デバイスの製造方法である。

【0015】

本発明にかかる半導体デバイスの製造方法において、III族窒化物層の厚さと、中間層のエッチングにより除去された部分の厚さと、支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さとの和を、エピタキシャル成長させるIII族窒化物半導体層の厚さより大きくすることができる。また、III族窒化物層の厚さと、中間層のエッチングにより除去された部分の厚さと、支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さと、エピタキシャル成長させたIII族窒化物半導体層の厚さとの和を、III族窒化物半導体層のエピタキシャル成長の際に支持基板のエッチング窪み上に不均一に成長したIII族窒化物半導体の最大高さよりも大きくすることができる。

【発明の効果】

【0016】

本発明によれば、中間層の一部および支持基板の一部の少なくともいずれかが露出している複合基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まり良く製造することができる複合基板の製造方法および半導体デバイスの製造方法を提供できる。

【図面の簡単な説明】

【0017】

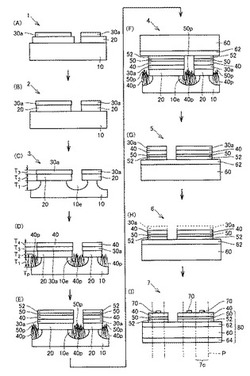

【図1】本発明にかかる複合基板の製造方法および半導体デバイスの製造方法の一例を示す概略断面図である。

【図2】本発明に用いられる第1の複合基板の一例を示す概略図である。ここで、(A)は概略平面図であり、(B)は(A)のIIB−IIBにおける概略断面図である。

【図3】本発明に用いられる第1の複合基板を準備する方法を示す概略断面図である。

【発明を実施するための形態】

【0018】

[実施形態1]

図1を参照して、本発明の一実施形態である複合基板の製造方法は、支持基板10と、支持基板10の主面の少なくとも一部上に配置された中間層20と、中間層20の主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1を準備する工程(図1(A))と、第1の複合基板1の中間層20の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板2を得る工程(図1(B))と、第2の複合基板2の支持基板10の主面が露出している部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板3を得る工程(図1(C))と、を含む。

【0019】

本実施形態の複合基板の製造方法により得られる第3の複合基板3は、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に、支持基板10のエッチングにより除去された部分により形成されるエッチング窪み10e上にIII族窒化物半導体40pが不均一に成長するが、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくすることが可能となり、このため、品質の高い半導体デバイスを歩留まり良く製造することができる。

【0020】

{第1複合基板の準備工程}

図1(A)、図2および図3を参照して、本実施形態の複合基板の製造方法は、まず、支持基板10と、支持基板10の主面の少なくとも一部上に配置された中間層20と、中間層20の主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1を準備する工程を含む。

【0021】

ここで、図3を参照して、第1の複合基板を準備する工程は、特に制限はなく、たとえば、支持基板10に中間層20aを形成するサブ工程(図3(A))、III族窒化物基板に中間層およびイオン注入領域を形成するサブ工程(図3(B))、支持基板とIII族窒化物基板とを貼り合わせるサブ工程(図3(C))およびIII族窒化物基板をイオン注入領域で分離することにより第1の複合基板を形成するサブ工程(図3(D)〜(E))を含む。

【0022】

(支持基板に中間層を形成するサブ工程)

図3(A)を参照して、支持基板10の主面10m上に中間層20aを形成する。支持基板10は、それに接合されるIII族窒化物層30aを支持できる基板であれば特に制限はないが、III族窒化物の熱膨張係数と同一または近似の熱膨張係数を有することが好ましく、さらに、本発明が特に有効なのはその上におけるIII族窒化物半導体の成長が不均一である支持基板10が用いられる場合である観点から、ケイ素酸化物、金属酸化物、多結晶GaN、多結晶SiC、Cu、WおよびMoからなる群から選ばれる少なくとも一つを含むことが好ましく、ケイ素酸化物含有基板、金属酸化物含有基板、ケイ素酸化物および金属酸化物のうち複数の種類の酸化物である複合酸化物を含有する基板、多結晶GaN含有基板、多結晶SiC含有基板およびMo含有基板などが好ましく挙げられる。ここで、ケイ素酸化物としては、SiO2などが挙げられる。金属酸化物としては、Al2O3、TiO2、ZrO2、Ga2O3、MgO、Y2O3などが挙げられる。複合酸化物としてはムライト(3Al2O3・2SiO2〜2Al2O3・SiO2)、ジルコン(ZrO2・SiO2)、スピネル(MgO・Al2O3)などが挙げられる。

【0023】

中間層20aは、特に制限はないが、支持基板10とIII族窒化物基板30との接合強度を高め、さらに、本発明が特に有効なのはその上におけるIII族窒化物半導体の成長が不均一である中間層20,20a,20bが用いられる場合である観点から、ケイ素酸化物、ケイ素窒化物、金属酸化物、金属窒化物およびこれらの複合物からなる群から選ばれる少なくとも一つを含むことが好ましく、ケイ素酸化物層、ケイ素窒化物層、金属酸化物層、金属窒化物層およびこれらの複合物層からなる群から選ばれる少なくとも一つであることがより好ましい。ケイ素酸化物としては、SiO2などが挙げられる。ケイ素窒化物としては、Si3N4などが挙げられる。金属酸化物としてはTiO2、ZnO、In2O3、SnO2、Al2O3,ZrO2、Ga2O3,NiO、Sb2O3、Y2O3、NbO、WO3、MoO2などが挙げられる。金属窒化物としては、TiN、AlNなどが挙げられる。

【0024】

中間層20aを形成する方法は、その中間層20aの形成に適している限り特に制限はないが、品質のよい中間層20aを効率的に形成する観点から、スパッタ法、CVD(化学気相堆積)法、PLD(パルスレーザ堆積)法、MBE(分子線成長)法、電子線蒸着法などが好ましい。

【0025】

さらに、中間層20aは、支持基板10とIII族窒化物基板との接合強度を高める観点から、その主面を鏡面(たとえば、JIS B 0601:2001に規定される算術平均粗さRaが10nm以下の鏡面)に研磨することが好ましい。中間層20aの主面を研磨する方法は、特に制限はなく、たとえばCMP(化学機械的研磨)などが用いられる。

【0026】

(III族窒化物基板に中間層およびイオン注入領域を形成するサブ工程)

図3(B)を参照して、III族窒化物基板30の主面30n上に中間層20bを形成し、III族窒化物基板30の主面30nから所定の深さの位置にイオン注入領域30iを形成する。

【0027】

III族窒化物基板30は、後工程における分離によりIII族窒化物層30aを形成させるものであり、III族窒化物層30aと同様に、少なくともc軸方向に配向しているIII族窒化物結晶(好ましくはIII族窒化物単結晶)で形成されている。かかるIII族窒化物基板30を準備する方法は、特に制限はないが、結晶性のよいIII族窒化物基板30を得る観点から、HVPE(ハイドライド気相成長)法、MOVPE(有機金属気相成長)法、MBE法、昇華法などの気相法、フラックス法、高窒素圧溶液法などの液相法などが好適である。

【0028】

中間層20bおよび中間層20bを形成する方法は、上記の中間層20aおよび中間層20aを形成する方法とそれぞれ同様であるため、ここでは繰り返さない。

【0029】

III族窒化物基板30の主面30nから所定の深さの位置にイオン注入領域30iを形成することは、III族窒化物基板30の主面30n上に形成された中間層20b側からイオンIを注入することにより行なう。注入するイオンIは、イオン注入されるIII族窒化物層30aの結晶性の低下を抑制する観点から、質量の小さいイオンが好ましく、たとえば水素イオン、ヘリウムイオンなどが好ましい。また、イオンIが注入される所定の深さは、10nm以上1000nm以下が好ましい。

【0030】

さらに、III族窒化物基板30にイオン注入領域30iを形成した後、中間層20bは、支持基板10とIII族窒化物基板との接合強度を高める観点から、その主面を鏡面(たとえば、JIS B 0601:2001に規定される算術平均粗さRaが10nm以下の鏡面)に研磨することが好ましい。中間層20bの主面を研磨する方法は、特に制限はなく、たとえばCMP(化学機械的研磨)などが用いられる。

【0031】

なお、図3(A)に示す支持基板10に中間層20aを形成するサブ工程と、図3(B)に示すIII族窒化物基板30に中間層20bおよびイオン注入領域30iを形成するサブ工程とは、いずれのサブ工程を先に行なってもよく、併行して行なってもよく、また、同時に行なってもよい。

【0032】

(支持基板とIII族窒化物基板とを貼り合わせるサブ工程)

図3(C)を参照して、次いで、支持基板10に形成された中間層20aとIII族窒化物基板30に形成された中間層20bとを貼り合わせる。その貼り合わせ方法は、特に制限はなく、貼り合わせ面を洗浄しそのまま貼り合わせた後600℃〜1200℃程度に昇温して接合する直接接合法、貼り合わせ面を洗浄しプラズマやイオンなどで活性させた後に室温(たとえば25℃)〜400℃程度の低温で接合する表面活性化法などが好適である。かかる貼り合わせにより、中間層20aと中間層20bとが接合により一体化して中間層20が形成され、支持基板10とIII族窒化物基板30とが中間層20を介在させて接合される。

【0033】

本実施形態においては、支持基板10およびIII族窒化物基板30のそれぞれに中間層20a,20bを形成した後貼り合わせる方法を示したが、支持基板10およびIII族窒化物基板30のいずれかのみに中間層を形成した後貼り合わせてもよい。

【0034】

(第1のIII族窒化物複合基板を形成する工程)

図3(D)を参照して、次いで、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合されたIII族窒化物複合基板を形成する。

【0035】

III族窒化物基板30をイオン注入領域30iにおいて分離する方法は、III族窒化物基板30のイオン注入領域30iに何らかのエネルギーを与える方法であれば特に制限はなく、イオン注入領域30iに、応力を加える方法、熱を加える方法、光を照射する方法、および超音波を印加する方法の少なくともいずれかの方法が可能である。

【0036】

かかるイオン注入領域30iは、注入されたイオンにより脆化しているため、上記エネルギーを受けることにより、III族窒化物基板30は、支持基板10上の中間層20上に貼りあわされたIII族窒化物層30aと、残りのIII族窒化物基板30bと、に容易に分離される。

【0037】

上記のようにして、支持基板10上の中間層20上にIII族窒化物層30aを形成することにより、支持基板10と、支持基板10上に配置されている中間層20と、中間層20上に配置されているIII族窒化物層30aと、を含む第1の複合基板1が得られる。

【0038】

上記のようにして得られる第1の複合基板1は、支持基板10の反り、中間層20,20a,20bの不均一、III族窒化物基板30へのイオン注入の不均一、支持基板10、中間層20,20a,20bおよび/またはIII族窒化物基板30の結晶欠陥、残存した研磨傷および研磨残渣の除去不十分、貼り合わせの際における荷重の不均一、支持基板10およびIII族窒化物基板30などのハンドリングの際におけるゴミの付着などにより、図1(A)、図2および図3(E)に示すように、主面の一部において、支持基板10と中間層20との間および中間層20とIII族窒化物層30aとの間の少なくともいずれかの接合が不十分となるため、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1が得られる。

【0039】

すなわち、上記ようにして、支持基板10と、支持基板10の主面の少なくとも一部上に配置された中間層20と、中間層20の主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1が準備される。

【0040】

{第1の複合基板の中間層の露出部分をエッチング除去することにより第2の複合基板を得る工程}

図1(B)を参照して、本実施形態の複合基板の製造方法は、次に、第1の複合基板1の中間層20の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板2を得る工程を含む。かかる工程により、中間層20の主面が露出している部分が除去され、中間層20の主面の露出がなくIII族窒化物層30aの主面と支持基板10の主面の一部とが露出している第2の複合基板が得られる。このため、第2の複合基板においては、中間層20の主面上に不均一なIII族窒化物半導体が成長するのが防止される。

【0041】

中間層20の主面が露出している部分をエッチングにより除去する方法は、その部分を選択的にエッチングできる方法であれば特に制限はなく、ドライエッチングであってもウェットエッチングであってもよく、中間層20の材質に適した方法が適用される。より好ましくは、III族窒化物層30aをエッチングしない方法が適用される。たとえば、中間層20がケイ素酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングが好適に用いられ、中間層20がケイ素窒化物を含む場合はCF4ガスを用いたドライエッチング(たとえば、RIE(反応性イオンエッチング。以下同じ。)が好適に用いられ、中間層20が金属酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングが好適に用いられ、中間層20が金属窒化物を含む場合はCF4ガスを用いたドライエッチングが好適に用いられる。

【0042】

{第2の複合基板の支持基板の露出部分を所定の深さまでエッチング除去することにより第3の複合基板を得る工程}

図1(C)を参照して、本実施形態の複合基板の製造方法は、次に、第2の複合基板2の支持基板10の主面が露出している部分を所定の深さT4まで選択的にエッチングにより除去することにより第3の複合基板3を得る工程を含む。かかる工程により、中間層20の主面の露出がなくIII族窒化物層30aの主面と支持基板10の主面の一部が露出しており支持基板10の主面が露出している部分にエッチング窪み10eが形成された第3の複合基板が得られる。このため、第3の複合基板3においては、中間層20の主面上に不均一なIII族窒化物半導体が成長するのが防止されるとともに、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に支持基板10のエッチング窪み10e上に不均一に成長するIII族窒化物半導体を形成することにより、品質の高い半導体デバイスを歩留まり良く製造することができる。

【0043】

支持基板10の主面が露出している部分をエッチングにより除去する方法は、その部分を選択的にエッチングできる方法であれば特に制限はなく、ドライエッチングであってもウェットエッチングであってもよく、支持基板10の材質に適した方法が適用される。たとえば、支持基板10がMoを含む場合は硝酸溶液を用いたウェットエッチングが好適に用いられ、支持基板10がケイ素酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングが好適に用いられ、支持基板10が金属酸化物を含む場合はフッ化水素酸を用いたウェットエッチングが好適に用いられ、支持基板10が多結晶GaNを含む場合は塩素(Cl2)ガスを用いたドライエッチングが好適に用いられ、支持基板10が多結晶SiCを含む場合はSF6ガスを用いたドライエッチングが好適に用いられる。

【0044】

支持基板10のエッチング窪みの深さTPは、品質の高い半導体デバイスを歩留まり良く製造する観点から、以下の条件を満たすことが好ましい。すなわち、第3の複合基板3は、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に、支持基板10のエッチングにより除去された部分により形成されるエッチング窪み10e上にIII族窒化物半導体40pが不均一に成長するが、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくすること(TP<T(=T1+T2+T3+T4))が好ましい。

【0045】

また、上記のように、不均一に成長したIII族窒化物半導体40pの最高高さTPより不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくするために、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2およびIII族窒化物層30aの厚さT3の和T1+T2+T3を、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍より大きくすることが好ましい。不均一に成長したIII族窒化物半導体40pの最高高さTPは、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍を超えることがほとんどないからである。

【0046】

[実施形態2]

図1を参照して、本発明の別の実施形態である半導体デバイスの製造方法は、実施形態1の複合基板の製造方法(図1(A)〜(C))により得られた第3の複合基板3のIII族窒化物層30aの主面上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる工程(図1(D))を含む。本実施形態の半導体デバイスの製造方法によれば、品質の高い半導体デバイスを歩留まり良く製造することができる。

【0047】

{III族窒化物半導体層のエピタキシャル成長工程}

図1(D)を参照して、本実施形態の半導体デバイスの製造方法は、実施形態1の第3の複合基板3のIII族窒化物層30aの主面上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる工程を含む。

【0048】

ここで、少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる方法は、特に制限はないが、結晶性のよいIII族窒化物半導体層をエピタキシャル成長させる観点から、MOVPE法、MBE法、HVPE法、昇華法などの気相法、フラックス法、高窒素圧溶液法などの液相法などが好適である。

【0049】

本実施形態において、第3の複合基板3のIII族窒化物層30aの主面上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させると、支持基板10のエッチング窪み10e上にもIII族窒化物半導体40pが成長する。このようなIII族窒化物半導体40pは、その成長が不均一であるため、III族窒化物半導体40pの最大高さTPが、III族窒化物半導体層40の厚さT4より大きくなる場合が多い。このような場合に、本実施形態の第3の複合基板3は、支持基板10の主面が露出している部分にエッチング窪み10eが形成されているため、支持基板10のかかるエッチング窪み10e上に不均一に成長するIII族窒化物半導体40pを形成することにより、III族窒化物半導体層40の最表面よりも低い位置にIII族窒化物半導体40pを押さえることができ、品質の高い半導体デバイスを歩留まり良く製造するのに適したIII族窒化物半導体層40を形成できるようになる。

【0050】

ここで、少なくとも1層のIII族窒化物半導体層40の厚さT4は、特に制限はないが、品質の高い半導体デバイスを歩留まり良く製造する観点から、以下の条件を満たすことが好ましい。すなわち、第3の複合基板3は、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に、支持基板10のエッチングにより除去された部分により形成されるエッチング窪み10e上にIII族窒化物半導体40pが不均一に成長するが、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくすること(TP<T(=T1+T2+T3+T4))が好ましい。

【0051】

また、上記のように、不均一に成長したIII族窒化物半導体40pの最高高さTPより不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくするために、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2およびIII族窒化物層30aの厚さT3の和T1+T2+T3を、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍より大きくすることが好ましい。不均一に成長したIII族窒化物半導体40pの最高高さTPは、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍を超えることがほとんどないからである。

【0052】

ここで、少なくとも1層のIII族窒化物半導体層40は、形成する半導体デバイスの種類に適したものであれば特に制限はなく、たとえば、LED(発光デバイス)の場合、n型GaN層、n型In0.08Ga0.92N層、3周期のIn0.14Ga0.86N井戸層およびGaN障壁層で構成される多重量子井戸構造の活性層、p型Al0.08Ga0.92N層ならびにp+型GaN層がこの順に形成される。

【0053】

{その他の工程}

図1(E)〜(H)を参照して、本実施形態の半導体デバイスの製造方法は、以下の工程をさらに含むことができる。

【0054】

(第1の導電側オーミック電極の形成工程)

図1(E)を参照して、第3の複合基板3のIII族窒化物層30a上にエピタキシャル成長させた少なくとも1層のIII族窒化物半導体層40の最上層上にたとえばNi層/Au層をこの順に形成し、さらにアニールにより最上層とオーミック接合させて第1の導電側オーミック電極50とする。さらに、第1の導電側オーミック電極50上に、たとえばTi層/Au層をこの順に形成してパッド層52とする。このとき、支持基板10のエッチング窪み10e上に形成されたIII族窒化物半導体40p上に堆積物50pが形成される。この堆積物50pの厚さは第1の導電側オーミック電極50の厚さとパッド層52の厚さの和にほぼ等しいため、パッド層52の主面は堆積物50pの最高高さより高い位置にある。

【0055】

(デバイス用支持基板の貼り合わせ工程)

図1(F)を参照して、デバイス用支持基板60としてたとえばp型Si基板を準備し、その主面上にたとえばTi層/Au層/AuSn層をこの順に形成してパッド層62とする。第3の複合基板3のIII族窒化物層30a上に形成されたIII族窒化物半導体層40上に形成された第1の導電側オーミック電極50上に形成されたパッド層52とデバイス用支持基板60上に形成されたパッド層62とを貼り合わせることにより、第3の複合基板3とIII族窒化物半導体層40とデバイス用支持基板60とが貼り合わされた積層基板4が得られる。

【0056】

(支持基板の除去工程)

図1(F)および(G)を参照して、積層基板4から第3の複合基板3の支持基板10をエッチングにより除去する。支持基板10は、たとえばMo基板の場合、硝酸溶液を用いたウェットエッチングにより除去できる。さらに第3の複合基板3の中間層20をエッチングにより除去する。中間層20は、たとえばケイ素酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングにより除去でき、ケイ酸窒化物を含む場合はドライエッチングの一種であるCF4ガスを用いたRIE(反応性イオンエッチング)により除去できる。このようにして、デバイス用支持基板60上にパッド層62,52および第1の導電側オーミック電極50を介在させて少なくとも1層のIII族窒化物半導体層40およびIII族窒化物層30aが形成された半導体ウエハ5が得られる。

【0057】

図1(G)および(H)を参照して、半導体ウエハ5からIII族窒化物層30aをエッチングにより除去する。III族窒化物層30aは、たとえばドライエッチングの一種であるCl2ガスを用いたRIEにより除去できる。このようにして、デバイス用支持基板60上にパッド層62,52および第1の導電側オーミック電極50を介在させて少なくとも1層のIII族窒化物半導体層40が形成された半導体ウエハ6が得られる。

【0058】

(電極の形成工程)

図1(H)および(I)を参照して、半導体ウエハ6のIII族窒化物半導体層40上にたとえばTi層/Al層/Ti層/Au層をこの順に形成して第2の導電側電極70とする。また、半導体ウエハ6のデバイス用支持基板60を分割が容易な厚さまで研磨した後、デバイス用支持基板60のパッド層62が形成されていない側の主面上にたとえばTi層/Au層をこの順に形成してパッド電極64とする。第1の導電側オーミック電極50、パッド層52,62、デバイス用支持基板60およびパッド電極64により第1の導電側電極80が構成される。こうして、デバイス用支持基板60を含む第1の導電側電極80と、少なくとも1層のIII族窒化物半導体層40と、III族窒化物層30aと、第2の導電側電極70とを含む半導体デバイス7が歩留まり良く得られる。

【0059】

(チップ化工程)

図1(I)を参照して、半導体デバイス7を所定の大きさのチップに分割することにより、半導体デバイスチップ7cが得られる。半導体デバイス7をチップ化する方法は、特に制限はなく、たとえば半導体デバイス7のデバイス用支持基板60側にスクライブラインを形成し、そのスクライブラインに沿った劈開面Pで劈開することができる。

【実施例】

【0060】

(実施例1)

1.第1の複合基板の準備

図3(A)を参照して、支持基板10として直径2インチ(50.8mm)で厚さ400μmのMo基板を準備した。Mo基板(支持基板10)は、純度が99.99質量%以上で、充填率が99%以上(すなわち空隙率が1%以下)であり、その少なくとも一方の主面10mがCMP(化学機械的研磨)されて算術平均粗さRaが5nm以下の鏡面であった。Mo基板(支持基板10)の鏡面化された主面10m上にプラズマCVD法により中間層20aとして厚さ300nmのSiO2層を形成した。次いで、SiO2層(中間層20a)をCMPしてその厚さを150nmとし、その主面を算術平均粗さRaが1nm以下の鏡面とした。

【0061】

また、図3(B)を参照して、III族窒化物基板30として直径2インチ(50.8mm)で厚さ300μmのGaN基板を準備した。GaN基板(III族窒化物基板30)は、その窒素原子面側の主面30nがCMPされて算術平均粗さRaが5nm以下の鏡面であった。GaN基板(III族窒化物基板30)の鏡面化された主面30n上にプラズマCVD法により中間層20bとして厚さ300nmのSiO2層を形成した。次いで、GaN基板(III族窒化物基板30)の主面30nに形成されたSiO2層(中間層20b)側からイオン注入装置により水素イオン(プロトン)を注入することにより、主面30nから300nmの深さの位置のGaN基板(III族窒化物基板30)内にイオン注入領域30iを形成した。次いで、SiO2層(中間層20b)をCMPして、その厚さを150nmとし、その主面を算術平均粗さRaが1nm以下の鏡面とした。

【0062】

次に、図3(C)〜(E)を参照して、Mo基板(支持基板10)上に形成されたSiO2層(中間層20a)と、GaN基板(III族窒化物基板30)上に形成されたSiO2層(中間層20b)と、を重ね合わせて、7MPaの荷重を加えることにより機械的に貼り合わせて接合させた。2つのSiO2層(中間層20a,20b)は一体化して1つのSiO2層(中間層20)が形成された。これによりMo基板(支持基板10)とGaN基板(III族窒化物基板30)とがSiO2層(中間層20)を介在させて貼り合わされた接合基板が得られた。

【0063】

次に、図3(D)および図1(A)を参照して、支持基板(支持基板10)およびGaN基板(III族窒化物基板30)の上記接合基板を500℃に加熱して熱応力をかけることにより、GaN基板(III族窒化物基板30)をそのイオン注入領域30iでGaN層(III族窒化物層30a)と残りのGaN基板(残りのIII族窒化物基板30b)とに分離することにより、厚さ400μmのMo基板(支持基板10)と、Mo基板(支持基板10)の主面の少なくとも一部上に配置された厚さ300nmのSiO2層(中間層20)と、SiO2層(中間層20)の主面の少なくとも一部上に配置された厚さ300nmのGaN層(III族窒化物層30a)とを含む主面の直径が2インチ(50.8mm)の第1の複合基板1が得られた。

【0064】

図1(A)を参照して、このようにして得られた第1の複合基板1は、SiO2層(中間層20,20a,20b)の不均一、GaN基板(III族窒化物基板30)へのイオン注入の不均一、Mo基板(支持基板10)、SiO2層(中間層20,20a,20b)および/またはGaN基板(III族窒化物基板30)の結晶欠陥、残存した研磨傷および研磨残渣の除去不十分、貼り合わせの際における荷重の不均一、Mo基板(支持基板10)およびGaN基板(III族窒化物基板30)などのハンドリングの際におけるゴミの付着などにより、GaN基板(III族窒化物基板30)に由来するGaN層(III族窒化物層30a)とMo基板(支持基板10)との間の接合が部分的に不十分となり、第1の複合基板1の主面の一部に、GaN層(III族窒化物層30a)の一部が欠落しSiO2層(中間層20)の主面の一部が露出した部分および/またはGaN層(III族窒化物層30a)およびSiO2層(中間層20)の一部が欠落しMo基板(支持基板10)の主面の一部が露出した部分が存在した。第1の複合基板1の主面全体(直径2インチ(50.8mm))の面積に対してGaN層(III族窒化物層30a)が存在している主面の面積は、光学顕微鏡の画像解析により算出したところ、80%であった。

【0065】

2.第1の複合基板の中間層の露出部分のエッチングによる第2の複合基板の形成

図1(B)を参照して、第1の複合基板1を、そのMo基板(支持基板10)側の主面および側面を、アルコールワックス(たとえば日化精工(株)製アルコワックス5022)で覆った(図示せず)後、50質量%フッ化水素酸水溶液と40質量%フッ化アンモニウム水溶液を1:5の体積比で混合したバッファードフッ酸(BHF)水溶液に7分間浸漬した。これにより、第1の複合基板1においてGaN層(III族窒化物層30a)が欠落しSiO2層(中間層20)の主面が露出している部分がエッチングされて、Mo基板(支持基板10)が露出した第2の複合基板2が得られた。一方、GaN層(III族窒化物層30a)直下のSiO2層(中間層20)は、GaN層(III族窒化物層30a)がBHFによりエッチングされないため、エッチングは生じなかった。得られた第2の複合基板2を、純水でリンスしてBHFを除去した後、乾燥させた。

【0066】

3.第2の複合基板の支持基板の支持基板の露出部分を所定の深さまでのエッチングによる第3の複合基板の形成

図1(C)を参照して、第2の複合基板2を、40質量%の硝酸水溶液に2分間浸漬した。これにより、第2の複合基板2のGaN層(III族窒化物層30a)およびSiO2層(中間層20)が欠落し、Mo基板(支持基板10)の主面の一部が露出している部分では、Moが等方的にエッチングされて、エッチング窪み10eが形成されて、第3の複合基板3が得られた。エッチング窪み10eの深さは、Mo基板(支持基板10)が露出している部分の形状および/またはサイズに依存し、20μm〜30μmであった。一方、GaN層(III族窒化物層30a)およびSiO2層(中間層20)直下のMo基板(支持基板10)はGaN層およびSiO2層が硝酸によりエッチングされないため、エッチングは生じなかった。また、第2の複合基板2のMo基板(支持基板10)側の主面および側面がワックスで保護してあったため、Mo基板(支持基板10)はエッチングされなかった。第3の複合基板3を、十分に水洗して硝酸水溶液を除去した後、アセトンでワックスを除去した。さらに、剥離液(東京応化工業社製剥離液502)およびIPA(イソプロピルアルコール)による洗浄で、ワックス残渣を完全に除去した。

【0067】

4.III族窒化物半導体層の成長

図1(D)を参照して、第3の複合基板3のGaN層(III族窒化物層30a)の主面上に、MOVPE法により、III族窒化物半導体層40として以下に示す青色LED構造を構成する複数のGaN系半導体層を成長させた。すなわち、III族窒化物半導体層40として、第3の複合基板3のGaN層(III族窒化物層30a)の主面側から順に、厚さ5μmのn型GaN層、厚さ50nmのn型In0.08Ga0.92N層、3周期の厚さ3nmのIn0.14Ga0.86N井戸層および厚さ15nmのGaN障壁層で構成される多重量子井戸構造の活性層、厚さ20nmのp型Al0.08Ga0.92N層ならびに厚さ50nmのp+型GaN層を成長させた。

【0068】

このとき、第3の複合基板3のMo基板(支持基板10)の露出しているエッチング窪み10e上に、多結晶のGaN半導体(III族窒化物半導体40p)が形成された。このGaN半導体(III族窒化物半導体40p)は2μm〜10μm程度であった。

【0069】

このため、GaN半導体(III族窒化物半導体40p)の最大高さは、GaN系半導体層(III族窒化物半導体層40)の最上層の主面よりも低い位置にあった。すなわち、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)が大きくなった(TP<T(=T1+T2+T3+T4))。

【0070】

成長させたGaN系層(III族窒化物半導体層40)の各層は、その元素組成をSIMS(2次イオン質量分析)法により測定したところ、Moおよびその他の不純物は、検出されず、それらの濃度が分析感度未満であるため、LEDの性能に悪い影響を与えないものであった。

【0071】

さらに、図1(E)を参照して、GaN系層(III族窒化物半導体層40)の最上層の主面の全面に、電子ビーム蒸着法により、Ni層(厚さ5nm)/Au層(厚さ11nm)をこの順に形成し、窒素と酸素の混合ガス雰囲気中500℃でアニールすることにより、p側オーミック電極(第1の導電側オーミック電極50)とした。さらに、p側オーミック電極(第1の導電側オーミック電極50)上に、電子ビーム蒸着法により、Ti層(厚さ20nm)/Au層(厚さ300nm)をこの順に形成して、パッド層52とした。このとき、支持基板10のエッチング窪み10e上に形成されたIII族窒化物半導体40p上に堆積物50pが形成された。この堆積物50pの厚さは第1の導電側オーミック電極50の厚さとパッド層52の厚さの和にほぼ等しかったため、パッド層52の主面は堆積物50pの最高高さより高い位置にあった。

【0072】

5.デバイス用支持基板の貼り合わせ

図1(F)を参照して、デバイス用支持基板60として、直径が2インチ(50.8mm)で厚さが300μmで主面の面方位が(001)で比抵抗が0.05Ωcm以下で一方の主面がCMPされて算術平均粗さRaが5nm以下の鏡面であるSi基板を準備した。このSi基板(デバイス用支持基板60)の鏡面化された主面上に、真空加熱蒸着法により、Ti層(厚さ20nm)/Au層(厚さ300nm)/AuSn層(厚さ1.5μmでAu:Snの質量比が8:2)をこの順で形成し、パッド層62とした。

【0073】

次いで、Si基板(デバイス用支持基板60)上に形成したパッド層62と、Mo基板(第3の複合基板3)上に順次形成したGaN層(III族窒化物層30a)、GaN系半導体層(III族窒化物半導体層40)、p側オーミック電極(第1の導電側オーミック電極50)およびパッド層52と、を重ね合わせ、Si基板(デバイス用支持基板60)の(100)面の結晶方位と、GaN層(III族窒化物層30a)およびGaN系半導体層(III族窒化物半導体層40)の(0001)面の結晶方位とが±0.3°以内になる様に調整した後、真空(0.1Pa未満)中で100kgfの荷重を印加しつつ300℃まで加熱し、パッド層62のAuSnとパッド層52のAuとの拡散接合により、Si基板(デバイス用支持基板60)と第3の複合基板3とが接合された積層基板4が得られた。超音波顕微鏡で積層基板4の接合界面の状態を観察したところ、第3の複合基板3を作製したときにGaN層(III族窒化物層30a)が欠落していた部分とその欠落部の外周から数百μmの領域では空隙(未接合状態)が観察されたが、GaN層が存在した部分では、空隙のない均一な接合が得られた。

【0074】

6.支持基板の除去

図1(F)および(G)を参照して、上記の積層基板4を30質量%硝酸水溶液に45分間浸漬した。これにより、Mo基板(支持基板10)は完全に除去された。積層基板4を水洗し硝酸水溶液を除去した後、上記のBHF水溶液に10分間浸漬し、SiO2層(中間層20)を完全に溶解除去した。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)およびGaN層(III族窒化物層30a)がこの順に接合された半導体ウエハ5が得られた。

【0075】

こうして得られた半導体ウエハ5について、その最上層であるGaN層(III族窒化物層30a)には、クラックなどはみられなかった。また、半導体ウエハ5の主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率は、75%であった。

【0076】

なお、本発明を適用せずに、第1の複合基板1を用いて作製した半導体ウエハは、その主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率が10%〜20%であり、GaN層(III族窒化物層30a)の欠落部分を起点にして数百μm〜数mmにわたりGaN層(III族窒化物層30a)にクラックが生じている場合があった。

【0077】

図1(G)および(H)を参照して、上記の半導体ウエハ5のGaN層(III族窒化物層30a)を、Cl2ガスを用いたRIEにより、除去して、GaN系半導体層(III族窒化物半導体層40)を露出させた。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)が接合された半導体ウエハ6が得られた。

【0078】

7.電極の形成

図1(H)および(I)を参照して、半導体ウエハ6のGaN層(III族窒化物層30a)上にフォトリソグラフィー法で形成したレジストパターン上に、電子ビーム蒸着法により、Ti層(厚さ20nm)/Al層(厚さ200nm)/Ti層(厚さ20nm)/Pt層(厚さ20nm)/Au層(厚さ300nm)をこの順に形成し、リフトオフ法により後述の半導体デバイスのチップ化された1領域(1チップ領域)である400μm角あたり1つ存在するように形成して、n側電極(第2の導電側電極70)とした。また、Si基板(デバイス用支持基板60)を、後述のチップ化を容易にするために、厚さが150μmになるまで機械的研磨およびCMPした後に、パッド層62が形成されていない側の主面の全面に、電子ビーム蒸着法により、Ti層(厚さ20nm)/Au層(厚さ300nm)をこの順に形成し、パッド電極64とした。このようにして半導体デバイス7が得られた。半導体デバイス7において、p側オーミック電極(第1の導電側オーミック電極50)、パッド層52,62、デバイス用支持基板60およびパッド電極64によりp側電極(第1の導電側電極80)が構成された。

【0079】

8.チップ化

図1(I)を参照して、半導体デバイス7において、それに形成されたn側電極(第2の導電側電極70)の配置パターンに対応するように、Si基板(デバイス用支持基板60)のパッド電極64側にダイヤペンで400μm角のスクライブラインを形成し、ブレーカを用いて半導体デバイス7をスクライブラインに沿って劈開することにより、大きさが400μm角の半導体デバイスチップ7cが得られた。

【0080】

9.実装

半導体デバイス(発光デバイス)用のステム(または表面実装用パッケージ)(図示せず)の第1の導電側部位に、銀ペーストを用いて半導体デバイスチップ7cのp側電極(第1の導電側電極80)を構成するSi基板(デバイス用支持基板60)のパッド電極64を電気的に接続した。また、半導体デバイスチップ7cのn側電極(第2の導電側電極70)を、金ワイヤを用いて、ステムの第2の導電側部位に電気的に接続した。このように、第3の複合基板3を用いて半導体デバイスチップ7cを作製し実装することにより、実装サンプル中の良品の歩留まり率(5Vの逆バイアス電圧を印加したときのリーク電流が100μA未満の半導体デバイスチップを良品とする)は、90%以上となった。

【0081】

(実施例2)

1.第1の複合基板の準備

図1(A)および図3を参照して、中間層20,20a,20bとしてSi3N4層を用いたこと以外は、実施例1と同様にして、厚さ400μmのMo基板(支持基板10)と、Mo基板(支持基板10)の主面の少なくとも一部上に配置された厚さ300nmのSi3N4層(中間層20)と、Si3N4層(中間層20)の主面の少なくとも一部上に配置された厚さ300nmのGaN層(III族窒化物層30a)とを含む主面の直径が2インチ(50.8mm)の第1の複合基板1が得られた。

【0082】

本実施例の第1の複合基板1は、実施例1の第1の複合基板1と同様に、第1の複合基板1の主面の一部に、GaN層(III族窒化物層30a)の一部が欠落しSi3N4層(中間層20)の主面の一部が露出した部分および/またはGaN層(III族窒化物層30a)およびSi3N4層(中間層20)の一部が欠落しMo基板(支持基板10)の主面の一部が露出した部分が存在した。第1の複合基板1の主面全体(直径2インチ(50.8mm))の面積に対してGaN層(III族窒化物層30a)が存在している主面の面積は、80%であった。

【0083】

2.第1の複合基板の中間層の露出部分のエッチングによる第2の複合基板の形成

図1(B)を参照して、第1の複合基板1を、CF4ガスを用いたRIEで処理した。これにより、第1の複合基板1においてGaN層(III族窒化物層30a)が欠落しSi3N4層(中間層20)の主面が露出している部分がエッチングされて、Mo基板(支持基板10)が露出した第2の複合基板2が得られた。一方、GaN層(III族窒化物層30a)直下のSi3N4層(中間層20)は、GaN層(III族窒化物層30a)がCF4ガスを用いたRIEによりエッチングされないため、エッチングは生じなかった。

【0084】

3.第2の複合基板の支持基板の支持基板の露出部分を所定の深さまでのエッチングによる第3の複合基板の形成

図1(C)を参照して、得られた第2の複合基板2を、そのMo基板(支持基板10)側の主面および側面を、アルコールワックス(たとえば日化精工(株)製アルコワックス5022)で覆った(図示せず)後、30質量%の硝酸水溶液に2分間浸漬した。これにより、第2の複合基板2のGaN層(III族窒化物層30a)およびSi3N4層(中間層20)が欠落し、Mo基板(支持基板10)の主面の一部が露出している部分では、Moが等方的にエッチングされて、エッチング窪み10eが形成されて、第3の複合基板3が得られた。エッチング窪み10eの深さは、Mo基板(支持基板10)が露出している部分の形状および/またはサイズに依存し、10μm〜30μmであった。一方、GaN層(III族窒化物層30a)およびSi3N4層(中間層20)直下のMo基板(支持基板10)はGaN層およびSi3N4層が硝酸によりエッチングされないため、エッチングは生じなかった。また、第2の複合基板2のMo基板(支持基板10)側の主面および側面がワックスで保護してあったため、Mo基板(支持基板10)はエッチングされなかった。第3の複合基板3を、十分に水洗して硝酸水溶液を除去した後、アセトンでワックスを除去した。さらに、剥離液(東京応化工業社製剥離液502)およびIPA(イソプロピルアルコール)による洗浄で、CF4ガスを用いたRIEで生じた副生成物およびワックス残渣を完全に除去した。

【0085】

4.III族窒化物半導体層の成長

図1(D)を参照して、実施例1と同様にして、第3の複合基板3のGaN層(III族窒化物層30a)の主面上に、III族窒化物半導体層40として、第3の複合基板3のGaN層(III族窒化物層30a)の主面側から順に、厚さ5μmのn型GaN層、厚さ50nmのn型In0.08Ga0.92N層、3周期の厚さ3nmのIn0.14Ga0.86N井戸層および厚さ15nmのGaN障壁層で構成される多重量子井戸構造の活性層、厚さ20nmのp型Al0.08Ga0.92N層ならびに厚さ50nmのp+型GaN層を成長させた。

【0086】

このとき、第3の複合基板3のMo基板(支持基板10)の露出しているエッチング窪み10e上に、多結晶のGaN半導体(III族窒化物半導体40p)が形成された。このGaN半導体(III族窒化物半導体40p)は2μm〜10μm程度であった。

【0087】

このため、GaN半導体(III族窒化物半導体40p)の最大高さは、GaN系半導体層(III族窒化物半導体層40)の最上層の主面よりも低い位置にあった。すなわち、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)が大きくなった(TP<T(=T1+T2+T3+T4))。

【0088】

成長させたGaN系層(III族窒化物半導体層40)の各層は、その元素組成をSIMS(2次イオン質量分析)法により測定したところ、Moおよびその他の不純物は、検出されず、それらの濃度が分析感度未満であるため、LEDの性能に悪い影響を与えないものであった。

【0089】

さらに、図1(E)を参照して、実施例1と同様にして、GaN系層(III族窒化物半導体層40)の最上層の主面の全面上にp側オーミック電極(第1の導電側オーミック電極50)を形成し、p側オーミック電極(第1の導電側オーミック電極50)上にパッド層52を形成した。

【0090】

5.デバイス用支持基板の貼り合わせ

図1(F)を参照して、実施例1と同様にして、Si基板(デバイス用支持基板60)を準備し、その鏡面化された主面上にパッド層62を形成した。次いで、実施例1同様にして、Si基板(デバイス用支持基板60)上に形成されたパッド層62と、Mo基板(第3の複合基板3)上に順次形成したGaN層(III族窒化物層30a)、GaN系半導体層(III族窒化物半導体層40)、p側オーミック電極(第1の導電側オーミック電極50)を介在させて形成されたパッド層52と、を重ね合わせることにより、Si基板(デバイス用支持基板60)と第3の複合基板3とが接合された積層基板4が得られた。超音波顕微鏡で積層基板4の接合界面の状態を観察したところ、第3の複合基板3を作製したときにGaN層(III族窒化物層30a)が欠落していた部分とその欠落部の外周から数百μmの領域では空隙(未接合状態)が観察されたが、GaN層が存在した部分では、空隙のない均一な接合が得られた。

【0091】

6.支持基板の除去

図1(F)および(G)を参照して、実施例1と同様にして、上記の積層基板4を30質量%硝酸水溶液に45分間浸漬することにより、Mo基板(支持基板10)を完全に除去した。その後、積層基板4を水洗し硝酸水溶液を水洗した。次いで、CF4ガスを用いたRIEにより、Si3N4層(中間層20)を完全に除去した。さらに、CF4ガスを用いたRIEにより生成した副生成物を、O2を用いたRIEにより除去した。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)およびGaN層(III族窒化物層30a)がこの順に接合された半導体ウエハ5が得られた。

【0092】

こうして得られた半導体ウエハ5について、その最上層であるGaN層(III族窒化物層30a)には、クラックなどはみられなかった。また、半導体ウエハ5の主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率は、75%であった。

【0093】

なお、本発明を適用せずに、第1の複合基板1を用いて作製した半導体ウエハは、その主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率が10%〜20%であり、GaN層(III族窒化物層30a)の欠落部分を起点にして数百μm〜数mmにわたりGaN層(III族窒化物層30a)にクラックが生じている場合があった。

【0094】

図1(G)および(H)を参照して、上記の半導体ウエハ5のGaN層(III族窒化物層30a)を、Cl2ガスを用いたRIEにより、除去して、GaN系半導体層(III族窒化物半導体層40)を露出させた。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)が接合された半導体ウエハ6が得られた。

【0095】

7.電極の形成

図1(H)および(I)を参照して、実施例1と同様にして、半導体ウエハ6のGaN層(III族窒化物層30a)上に、後述の半導体デバイスのチップ化された1領域(1チップ領域)である400μm角あたり1つ存在するように、n側電極(第2の導電側電極70)を形成した。次いで、実施例1と同様にして、Si基板(デバイス用支持基板60)を、厚さが150μmになるまで機械的研磨およびCMPした後に、パッド層62が形成されていない側の主面の全面に、パッド電極64を形成した。このようにして半導体デバイス7が得られた。半導体デバイス7において、p側オーミック電極(第1の導電側オーミック電極50)、パッド層52,62、デバイス用支持基板60およびパッド電極64によりp側電極(第1の導電側電極80)が構成された。

【0096】

8.チップ化

図1(I)を参照して、実施例1と同様にして、半導体デバイス7を劈開することにより、大きさが400μm角の半導体デバイスチップ7cが得られた。

【0097】

9.実装

実施例1と同様にして、半導体デバイス(発光デバイス)用のステムに半導体デバイスチップ7cを実装した。実装サンプル中の良品の歩留まり率(5Vの逆バイアス電圧を印加したときのリーク電流が100μA未満の半導体デバイスチップを良品とする)は、90%以上となった。

【0098】

実施例1および実施例2を参照して、本発明にかかる複合基板の製造方法により得られる第3の複合基板を用いて半導体デバイスを製造することにより、高い歩留まり率で半導体デバイスを製造することができた。

【0099】

今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0100】

1 第1の複合基板、2 第2の複合基板、3 第3の複合基板、4 積層基板、5,6 半導体ウエハ、7 半導体デバイス、7c 半導体デバイスチップ、10 支持基板、10e エッチング窪み、10m,30n 主面、20,20a,20b 中間層、30 III族窒化物基板、30a III族窒化物層GaN層、30b 残りのIII族窒化物基板、40 III族窒化物半導体層、40p III族窒化物半導体、50 第1の導電側オーミック電極、50p 堆積物、52,62 パッド層、60 デバイス用支持基板、64 パッド電極、70 第2の導電側電極、80 第1の導電側電極。

【技術分野】

【0001】

本発明は、支持基板に中間層を介在させてIII族窒化物層を積層させた複合基板の製造方法およびこれにより得られた複合基板を用いた半導体デバイスの製造方法に関する。

【背景技術】

【0002】

III族窒化物半導体を用いた半導体デバイスは種々の方法で形成されている。一つの方法は、III族窒化物半導体基板上に、少なくとも1層のIII族窒化物半導体層をエピタキシャル成長させる方法である。しかし、かかる方法は、III族窒化物半導体基板が非常に高価であるため、得られる半導体デバイスも非常に高価となる。

【0003】

このため、III族窒化物半導体とは化学組成が異なる支持基板上にIII族窒化物半導体層を積層させた複合基板のIII族窒化物半導体層上にIII族窒化物半導体層をエピタキシャル成長させる方法が好適に用いられている。

【0004】

たとえば、特開2006−210660号公報(特許文献1)は、積層された半導体基板の製造方法として、第1の窒化物半導体基板の表面近傍にイオンを注入する工程と、その第1の窒化物半導体基板の表面側を第2の基板に重ね合わせる工程と、重ね合わせた上記2枚の基板を熱処理する工程と、イオン注入された層を境として上記第1の窒化物半導体基板の大部分を上記第2の窒化物半導体基板から引き剥がす工程と含む製造方法を開示する。

【0005】

また、特開2008−300562号公報(特許文献2)は、III族窒化物半導体層貼り合わせ基板として、III族窒化物半導体基板と下地基板とが貼り合わされている基板であって、III族窒化物半導体層の熱膨張係数と下地基板の熱膨張係数との差が4.5×10-6K-1以下と小さく、下地基板の熱伝導率が50W・m-1・K-1以上と高い貼り合わせ基板を開示する。また、かかるIII族窒化物半導体層貼り合わせ基板上に形成されている少なくとも1層のIII族窒化物半導体エピタキシャル層を含む半導体デバイスを開示する。

【0006】

また、特開2010−165927号公報(特許文献3)は、発光素子用基板として、波長が400nm以上600nm以下の光に対して透明な透明基板と、透明基板の一方の主面上に接合により形成された窒化物系化合物半導体薄膜とを備え、透明基板の主表面に垂直な方向における透明基板の熱膨張係数をα1、窒化物系化合物半導体薄膜の熱膨張係数をα2とすれば、(α1−α2)/α2が−0.5以上1.0以下と小さい基板が開示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2006−210660号公報

【特許文献2】特開2008−300562号公報

【特許文献3】特開2010−165927号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上記の特開2006−210660号公報(特許文献1)、特開2008−300562号公報(特許文献2)および特開2010−165927号公報(特許文献3)に開示された複合基板は、いずれも支持基板としての下地基板とIII族窒化物層とを直接貼り合わせたものであり、支持基板(下地基板)の種類によってはIII族窒化物層との接合強度が必ずしも十分でない場合があった。

【0009】

このため、支持基板とIII族窒化物半導体層との接合強度を高めるため、支持基板とIII族窒化物層とをそれらの間に中間層を介在させて貼り合わせた複合基板が検討されつつある。

【0010】

しかしながら、現在の実際の製造において得られる支持基板とIII族窒化物層との間に中間層を介在させて積層された複合基板上にIII族窒化物半導体層をエピタキシャル成長させると、複合基板の主面の一部上にエピタキシャル成長とは異なり異常な成長、具体的には、膜厚や組成、結晶方位、成長モードなどが不均一な成長が発生するため、半導体デバイスの歩留まりが低下するという問題点がある。これにより、複合基板の主面上に数百nm〜数十μmの凹凸が形成される。この凹凸は、たとえば、半導体デバイス作製時の樹脂(レジスト)成膜時に樹脂厚みの不均一の原因となったり、別の保持基板へ貼り替える際に面内一様な密着を阻害する原因となったりすることで、半導体デバイスの歩留まりが低下するという問題を引き起こす。

【0011】

本発明者らは、上記問題点の原因について鋭意調査研究した結果、複合基板上のIII族窒化物層の一部が欠落して中間層および支持基板の主面の少なくとも一部が露出しており、複合基板のIII族窒化物層上にIII族窒化物半導体層をエピタキシャル成長させる際に、この露出部上にIII族窒化物が不均一成長などの異常成長を引き起こすことをつきとめた。本発明は、上記の知見に基づき、中間層の一部および支持基板の一部の少なくともいずれかが露出している複合基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まり良く製造することができる複合基板の製造方法および半導体デバイスの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、支持基板と、支持基板の主面の少なくとも一部上に配置された中間層と、中間層の主面の少なくとも一部上に配置されたIII族窒化物層とを含み、III族窒化物層の主面と、中間層の主面の一部および支持基板の主面の一部の少なくともいずれかと、が露出している第1の複合基板を準備する工程と、第1の複合基板の中間層の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板を得る工程と、第2の複合基板の支持基板の主面が露出している部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板を得る工程と、を含む複合基板の製造方法である。

【0013】

本発明にかかる複合基板の製造方法において、中間層は、その上におけるIII族窒化物半導体の成長が不均一であるものとすることができる。さらに、中間層は、ケイ素酸化物、ケイ素窒化物、金属酸化物、金属窒化物およびこれらの複合物からなる群から選ばれる少なくとも一つを含むことができる。また、支持基板は、その上におけるIII族窒化物半導体の成長が不均一であるものとすることができる。さらに、支持基板は、ケイ素酸化物、金属酸化物、多結晶GaN、多結晶SiC、Cu、WおよびMoからなる群から選ばれる少なくとも一つを含むことができる。

【0014】

また、本発明は、上記の複合基板の製造方法により得られた第3の複合基板のIII族窒化物層の主面上に少なくとも1層のIII族窒化物半導体層をエピタキシャル成長させる工程を含む半導体デバイスの製造方法である。

【0015】

本発明にかかる半導体デバイスの製造方法において、III族窒化物層の厚さと、中間層のエッチングにより除去された部分の厚さと、支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さとの和を、エピタキシャル成長させるIII族窒化物半導体層の厚さより大きくすることができる。また、III族窒化物層の厚さと、中間層のエッチングにより除去された部分の厚さと、支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さと、エピタキシャル成長させたIII族窒化物半導体層の厚さとの和を、III族窒化物半導体層のエピタキシャル成長の際に支持基板のエッチング窪み上に不均一に成長したIII族窒化物半導体の最大高さよりも大きくすることができる。

【発明の効果】

【0016】

本発明によれば、中間層の一部および支持基板の一部の少なくともいずれかが露出している複合基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まり良く製造することができる複合基板の製造方法および半導体デバイスの製造方法を提供できる。

【図面の簡単な説明】

【0017】

【図1】本発明にかかる複合基板の製造方法および半導体デバイスの製造方法の一例を示す概略断面図である。

【図2】本発明に用いられる第1の複合基板の一例を示す概略図である。ここで、(A)は概略平面図であり、(B)は(A)のIIB−IIBにおける概略断面図である。

【図3】本発明に用いられる第1の複合基板を準備する方法を示す概略断面図である。

【発明を実施するための形態】

【0018】

[実施形態1]

図1を参照して、本発明の一実施形態である複合基板の製造方法は、支持基板10と、支持基板10の主面の少なくとも一部上に配置された中間層20と、中間層20の主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1を準備する工程(図1(A))と、第1の複合基板1の中間層20の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板2を得る工程(図1(B))と、第2の複合基板2の支持基板10の主面が露出している部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板3を得る工程(図1(C))と、を含む。

【0019】

本実施形態の複合基板の製造方法により得られる第3の複合基板3は、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に、支持基板10のエッチングにより除去された部分により形成されるエッチング窪み10e上にIII族窒化物半導体40pが不均一に成長するが、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくすることが可能となり、このため、品質の高い半導体デバイスを歩留まり良く製造することができる。

【0020】

{第1複合基板の準備工程}

図1(A)、図2および図3を参照して、本実施形態の複合基板の製造方法は、まず、支持基板10と、支持基板10の主面の少なくとも一部上に配置された中間層20と、中間層20の主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1を準備する工程を含む。

【0021】

ここで、図3を参照して、第1の複合基板を準備する工程は、特に制限はなく、たとえば、支持基板10に中間層20aを形成するサブ工程(図3(A))、III族窒化物基板に中間層およびイオン注入領域を形成するサブ工程(図3(B))、支持基板とIII族窒化物基板とを貼り合わせるサブ工程(図3(C))およびIII族窒化物基板をイオン注入領域で分離することにより第1の複合基板を形成するサブ工程(図3(D)〜(E))を含む。

【0022】

(支持基板に中間層を形成するサブ工程)

図3(A)を参照して、支持基板10の主面10m上に中間層20aを形成する。支持基板10は、それに接合されるIII族窒化物層30aを支持できる基板であれば特に制限はないが、III族窒化物の熱膨張係数と同一または近似の熱膨張係数を有することが好ましく、さらに、本発明が特に有効なのはその上におけるIII族窒化物半導体の成長が不均一である支持基板10が用いられる場合である観点から、ケイ素酸化物、金属酸化物、多結晶GaN、多結晶SiC、Cu、WおよびMoからなる群から選ばれる少なくとも一つを含むことが好ましく、ケイ素酸化物含有基板、金属酸化物含有基板、ケイ素酸化物および金属酸化物のうち複数の種類の酸化物である複合酸化物を含有する基板、多結晶GaN含有基板、多結晶SiC含有基板およびMo含有基板などが好ましく挙げられる。ここで、ケイ素酸化物としては、SiO2などが挙げられる。金属酸化物としては、Al2O3、TiO2、ZrO2、Ga2O3、MgO、Y2O3などが挙げられる。複合酸化物としてはムライト(3Al2O3・2SiO2〜2Al2O3・SiO2)、ジルコン(ZrO2・SiO2)、スピネル(MgO・Al2O3)などが挙げられる。

【0023】

中間層20aは、特に制限はないが、支持基板10とIII族窒化物基板30との接合強度を高め、さらに、本発明が特に有効なのはその上におけるIII族窒化物半導体の成長が不均一である中間層20,20a,20bが用いられる場合である観点から、ケイ素酸化物、ケイ素窒化物、金属酸化物、金属窒化物およびこれらの複合物からなる群から選ばれる少なくとも一つを含むことが好ましく、ケイ素酸化物層、ケイ素窒化物層、金属酸化物層、金属窒化物層およびこれらの複合物層からなる群から選ばれる少なくとも一つであることがより好ましい。ケイ素酸化物としては、SiO2などが挙げられる。ケイ素窒化物としては、Si3N4などが挙げられる。金属酸化物としてはTiO2、ZnO、In2O3、SnO2、Al2O3,ZrO2、Ga2O3,NiO、Sb2O3、Y2O3、NbO、WO3、MoO2などが挙げられる。金属窒化物としては、TiN、AlNなどが挙げられる。

【0024】

中間層20aを形成する方法は、その中間層20aの形成に適している限り特に制限はないが、品質のよい中間層20aを効率的に形成する観点から、スパッタ法、CVD(化学気相堆積)法、PLD(パルスレーザ堆積)法、MBE(分子線成長)法、電子線蒸着法などが好ましい。

【0025】

さらに、中間層20aは、支持基板10とIII族窒化物基板との接合強度を高める観点から、その主面を鏡面(たとえば、JIS B 0601:2001に規定される算術平均粗さRaが10nm以下の鏡面)に研磨することが好ましい。中間層20aの主面を研磨する方法は、特に制限はなく、たとえばCMP(化学機械的研磨)などが用いられる。

【0026】

(III族窒化物基板に中間層およびイオン注入領域を形成するサブ工程)

図3(B)を参照して、III族窒化物基板30の主面30n上に中間層20bを形成し、III族窒化物基板30の主面30nから所定の深さの位置にイオン注入領域30iを形成する。

【0027】

III族窒化物基板30は、後工程における分離によりIII族窒化物層30aを形成させるものであり、III族窒化物層30aと同様に、少なくともc軸方向に配向しているIII族窒化物結晶(好ましくはIII族窒化物単結晶)で形成されている。かかるIII族窒化物基板30を準備する方法は、特に制限はないが、結晶性のよいIII族窒化物基板30を得る観点から、HVPE(ハイドライド気相成長)法、MOVPE(有機金属気相成長)法、MBE法、昇華法などの気相法、フラックス法、高窒素圧溶液法などの液相法などが好適である。

【0028】

中間層20bおよび中間層20bを形成する方法は、上記の中間層20aおよび中間層20aを形成する方法とそれぞれ同様であるため、ここでは繰り返さない。

【0029】

III族窒化物基板30の主面30nから所定の深さの位置にイオン注入領域30iを形成することは、III族窒化物基板30の主面30n上に形成された中間層20b側からイオンIを注入することにより行なう。注入するイオンIは、イオン注入されるIII族窒化物層30aの結晶性の低下を抑制する観点から、質量の小さいイオンが好ましく、たとえば水素イオン、ヘリウムイオンなどが好ましい。また、イオンIが注入される所定の深さは、10nm以上1000nm以下が好ましい。

【0030】

さらに、III族窒化物基板30にイオン注入領域30iを形成した後、中間層20bは、支持基板10とIII族窒化物基板との接合強度を高める観点から、その主面を鏡面(たとえば、JIS B 0601:2001に規定される算術平均粗さRaが10nm以下の鏡面)に研磨することが好ましい。中間層20bの主面を研磨する方法は、特に制限はなく、たとえばCMP(化学機械的研磨)などが用いられる。

【0031】

なお、図3(A)に示す支持基板10に中間層20aを形成するサブ工程と、図3(B)に示すIII族窒化物基板30に中間層20bおよびイオン注入領域30iを形成するサブ工程とは、いずれのサブ工程を先に行なってもよく、併行して行なってもよく、また、同時に行なってもよい。

【0032】

(支持基板とIII族窒化物基板とを貼り合わせるサブ工程)

図3(C)を参照して、次いで、支持基板10に形成された中間層20aとIII族窒化物基板30に形成された中間層20bとを貼り合わせる。その貼り合わせ方法は、特に制限はなく、貼り合わせ面を洗浄しそのまま貼り合わせた後600℃〜1200℃程度に昇温して接合する直接接合法、貼り合わせ面を洗浄しプラズマやイオンなどで活性させた後に室温(たとえば25℃)〜400℃程度の低温で接合する表面活性化法などが好適である。かかる貼り合わせにより、中間層20aと中間層20bとが接合により一体化して中間層20が形成され、支持基板10とIII族窒化物基板30とが中間層20を介在させて接合される。

【0033】

本実施形態においては、支持基板10およびIII族窒化物基板30のそれぞれに中間層20a,20bを形成した後貼り合わせる方法を示したが、支持基板10およびIII族窒化物基板30のいずれかのみに中間層を形成した後貼り合わせてもよい。

【0034】

(第1のIII族窒化物複合基板を形成する工程)

図3(D)を参照して、次いで、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合されたIII族窒化物複合基板を形成する。

【0035】

III族窒化物基板30をイオン注入領域30iにおいて分離する方法は、III族窒化物基板30のイオン注入領域30iに何らかのエネルギーを与える方法であれば特に制限はなく、イオン注入領域30iに、応力を加える方法、熱を加える方法、光を照射する方法、および超音波を印加する方法の少なくともいずれかの方法が可能である。

【0036】

かかるイオン注入領域30iは、注入されたイオンにより脆化しているため、上記エネルギーを受けることにより、III族窒化物基板30は、支持基板10上の中間層20上に貼りあわされたIII族窒化物層30aと、残りのIII族窒化物基板30bと、に容易に分離される。

【0037】

上記のようにして、支持基板10上の中間層20上にIII族窒化物層30aを形成することにより、支持基板10と、支持基板10上に配置されている中間層20と、中間層20上に配置されているIII族窒化物層30aと、を含む第1の複合基板1が得られる。

【0038】

上記のようにして得られる第1の複合基板1は、支持基板10の反り、中間層20,20a,20bの不均一、III族窒化物基板30へのイオン注入の不均一、支持基板10、中間層20,20a,20bおよび/またはIII族窒化物基板30の結晶欠陥、残存した研磨傷および研磨残渣の除去不十分、貼り合わせの際における荷重の不均一、支持基板10およびIII族窒化物基板30などのハンドリングの際におけるゴミの付着などにより、図1(A)、図2および図3(E)に示すように、主面の一部において、支持基板10と中間層20との間および中間層20とIII族窒化物層30aとの間の少なくともいずれかの接合が不十分となるため、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1が得られる。

【0039】

すなわち、上記ようにして、支持基板10と、支持基板10の主面の少なくとも一部上に配置された中間層20と、中間層20の主面の少なくとも一部上に配置されたIII族窒化物層30aとを含み、III族窒化物層30aの主面と、中間層20の主面の一部および支持基板10の主面の一部の少なくともいずれかと、が露出している第1の複合基板1が準備される。

【0040】

{第1の複合基板の中間層の露出部分をエッチング除去することにより第2の複合基板を得る工程}

図1(B)を参照して、本実施形態の複合基板の製造方法は、次に、第1の複合基板1の中間層20の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板2を得る工程を含む。かかる工程により、中間層20の主面が露出している部分が除去され、中間層20の主面の露出がなくIII族窒化物層30aの主面と支持基板10の主面の一部とが露出している第2の複合基板が得られる。このため、第2の複合基板においては、中間層20の主面上に不均一なIII族窒化物半導体が成長するのが防止される。

【0041】

中間層20の主面が露出している部分をエッチングにより除去する方法は、その部分を選択的にエッチングできる方法であれば特に制限はなく、ドライエッチングであってもウェットエッチングであってもよく、中間層20の材質に適した方法が適用される。より好ましくは、III族窒化物層30aをエッチングしない方法が適用される。たとえば、中間層20がケイ素酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングが好適に用いられ、中間層20がケイ素窒化物を含む場合はCF4ガスを用いたドライエッチング(たとえば、RIE(反応性イオンエッチング。以下同じ。)が好適に用いられ、中間層20が金属酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングが好適に用いられ、中間層20が金属窒化物を含む場合はCF4ガスを用いたドライエッチングが好適に用いられる。

【0042】

{第2の複合基板の支持基板の露出部分を所定の深さまでエッチング除去することにより第3の複合基板を得る工程}

図1(C)を参照して、本実施形態の複合基板の製造方法は、次に、第2の複合基板2の支持基板10の主面が露出している部分を所定の深さT4まで選択的にエッチングにより除去することにより第3の複合基板3を得る工程を含む。かかる工程により、中間層20の主面の露出がなくIII族窒化物層30aの主面と支持基板10の主面の一部が露出しており支持基板10の主面が露出している部分にエッチング窪み10eが形成された第3の複合基板が得られる。このため、第3の複合基板3においては、中間層20の主面上に不均一なIII族窒化物半導体が成長するのが防止されるとともに、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に支持基板10のエッチング窪み10e上に不均一に成長するIII族窒化物半導体を形成することにより、品質の高い半導体デバイスを歩留まり良く製造することができる。

【0043】

支持基板10の主面が露出している部分をエッチングにより除去する方法は、その部分を選択的にエッチングできる方法であれば特に制限はなく、ドライエッチングであってもウェットエッチングであってもよく、支持基板10の材質に適した方法が適用される。たとえば、支持基板10がMoを含む場合は硝酸溶液を用いたウェットエッチングが好適に用いられ、支持基板10がケイ素酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングが好適に用いられ、支持基板10が金属酸化物を含む場合はフッ化水素酸を用いたウェットエッチングが好適に用いられ、支持基板10が多結晶GaNを含む場合は塩素(Cl2)ガスを用いたドライエッチングが好適に用いられ、支持基板10が多結晶SiCを含む場合はSF6ガスを用いたドライエッチングが好適に用いられる。

【0044】

支持基板10のエッチング窪みの深さTPは、品質の高い半導体デバイスを歩留まり良く製造する観点から、以下の条件を満たすことが好ましい。すなわち、第3の複合基板3は、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に、支持基板10のエッチングにより除去された部分により形成されるエッチング窪み10e上にIII族窒化物半導体40pが不均一に成長するが、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくすること(TP<T(=T1+T2+T3+T4))が好ましい。

【0045】

また、上記のように、不均一に成長したIII族窒化物半導体40pの最高高さTPより不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくするために、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2およびIII族窒化物層30aの厚さT3の和T1+T2+T3を、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍より大きくすることが好ましい。不均一に成長したIII族窒化物半導体40pの最高高さTPは、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍を超えることがほとんどないからである。

【0046】

[実施形態2]

図1を参照して、本発明の別の実施形態である半導体デバイスの製造方法は、実施形態1の複合基板の製造方法(図1(A)〜(C))により得られた第3の複合基板3のIII族窒化物層30aの主面上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる工程(図1(D))を含む。本実施形態の半導体デバイスの製造方法によれば、品質の高い半導体デバイスを歩留まり良く製造することができる。

【0047】

{III族窒化物半導体層のエピタキシャル成長工程}

図1(D)を参照して、本実施形態の半導体デバイスの製造方法は、実施形態1の第3の複合基板3のIII族窒化物層30aの主面上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる工程を含む。

【0048】

ここで、少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる方法は、特に制限はないが、結晶性のよいIII族窒化物半導体層をエピタキシャル成長させる観点から、MOVPE法、MBE法、HVPE法、昇華法などの気相法、フラックス法、高窒素圧溶液法などの液相法などが好適である。

【0049】

本実施形態において、第3の複合基板3のIII族窒化物層30aの主面上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させると、支持基板10のエッチング窪み10e上にもIII族窒化物半導体40pが成長する。このようなIII族窒化物半導体40pは、その成長が不均一であるため、III族窒化物半導体40pの最大高さTPが、III族窒化物半導体層40の厚さT4より大きくなる場合が多い。このような場合に、本実施形態の第3の複合基板3は、支持基板10の主面が露出している部分にエッチング窪み10eが形成されているため、支持基板10のかかるエッチング窪み10e上に不均一に成長するIII族窒化物半導体40pを形成することにより、III族窒化物半導体層40の最表面よりも低い位置にIII族窒化物半導体40pを押さえることができ、品質の高い半導体デバイスを歩留まり良く製造するのに適したIII族窒化物半導体層40を形成できるようになる。

【0050】

ここで、少なくとも1層のIII族窒化物半導体層40の厚さT4は、特に制限はないが、品質の高い半導体デバイスを歩留まり良く製造する観点から、以下の条件を満たすことが好ましい。すなわち、第3の複合基板3は、そのIII族窒化物層30a上に少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させる際に、支持基板10のエッチングにより除去された部分により形成されるエッチング窪み10e上にIII族窒化物半導体40pが不均一に成長するが、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくすること(TP<T(=T1+T2+T3+T4))が好ましい。

【0051】

また、上記のように、不均一に成長したIII族窒化物半導体40pの最高高さTPより不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)を大きくするために、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2およびIII族窒化物層30aの厚さT3の和T1+T2+T3を、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍より大きくすることが好ましい。不均一に成長したIII族窒化物半導体40pの最高高さTPは、III族窒化物層30aの主面上にエピタキシャル成長させるIII族窒化物半導体層40の厚さT4の10倍を超えることがほとんどないからである。

【0052】

ここで、少なくとも1層のIII族窒化物半導体層40は、形成する半導体デバイスの種類に適したものであれば特に制限はなく、たとえば、LED(発光デバイス)の場合、n型GaN層、n型In0.08Ga0.92N層、3周期のIn0.14Ga0.86N井戸層およびGaN障壁層で構成される多重量子井戸構造の活性層、p型Al0.08Ga0.92N層ならびにp+型GaN層がこの順に形成される。

【0053】

{その他の工程}

図1(E)〜(H)を参照して、本実施形態の半導体デバイスの製造方法は、以下の工程をさらに含むことができる。

【0054】

(第1の導電側オーミック電極の形成工程)

図1(E)を参照して、第3の複合基板3のIII族窒化物層30a上にエピタキシャル成長させた少なくとも1層のIII族窒化物半導体層40の最上層上にたとえばNi層/Au層をこの順に形成し、さらにアニールにより最上層とオーミック接合させて第1の導電側オーミック電極50とする。さらに、第1の導電側オーミック電極50上に、たとえばTi層/Au層をこの順に形成してパッド層52とする。このとき、支持基板10のエッチング窪み10e上に形成されたIII族窒化物半導体40p上に堆積物50pが形成される。この堆積物50pの厚さは第1の導電側オーミック電極50の厚さとパッド層52の厚さの和にほぼ等しいため、パッド層52の主面は堆積物50pの最高高さより高い位置にある。

【0055】

(デバイス用支持基板の貼り合わせ工程)

図1(F)を参照して、デバイス用支持基板60としてたとえばp型Si基板を準備し、その主面上にたとえばTi層/Au層/AuSn層をこの順に形成してパッド層62とする。第3の複合基板3のIII族窒化物層30a上に形成されたIII族窒化物半導体層40上に形成された第1の導電側オーミック電極50上に形成されたパッド層52とデバイス用支持基板60上に形成されたパッド層62とを貼り合わせることにより、第3の複合基板3とIII族窒化物半導体層40とデバイス用支持基板60とが貼り合わされた積層基板4が得られる。

【0056】

(支持基板の除去工程)

図1(F)および(G)を参照して、積層基板4から第3の複合基板3の支持基板10をエッチングにより除去する。支持基板10は、たとえばMo基板の場合、硝酸溶液を用いたウェットエッチングにより除去できる。さらに第3の複合基板3の中間層20をエッチングにより除去する。中間層20は、たとえばケイ素酸化物を含む場合はフッ化水素酸溶液を用いたウェットエッチングにより除去でき、ケイ酸窒化物を含む場合はドライエッチングの一種であるCF4ガスを用いたRIE(反応性イオンエッチング)により除去できる。このようにして、デバイス用支持基板60上にパッド層62,52および第1の導電側オーミック電極50を介在させて少なくとも1層のIII族窒化物半導体層40およびIII族窒化物層30aが形成された半導体ウエハ5が得られる。

【0057】

図1(G)および(H)を参照して、半導体ウエハ5からIII族窒化物層30aをエッチングにより除去する。III族窒化物層30aは、たとえばドライエッチングの一種であるCl2ガスを用いたRIEにより除去できる。このようにして、デバイス用支持基板60上にパッド層62,52および第1の導電側オーミック電極50を介在させて少なくとも1層のIII族窒化物半導体層40が形成された半導体ウエハ6が得られる。

【0058】

(電極の形成工程)

図1(H)および(I)を参照して、半導体ウエハ6のIII族窒化物半導体層40上にたとえばTi層/Al層/Ti層/Au層をこの順に形成して第2の導電側電極70とする。また、半導体ウエハ6のデバイス用支持基板60を分割が容易な厚さまで研磨した後、デバイス用支持基板60のパッド層62が形成されていない側の主面上にたとえばTi層/Au層をこの順に形成してパッド電極64とする。第1の導電側オーミック電極50、パッド層52,62、デバイス用支持基板60およびパッド電極64により第1の導電側電極80が構成される。こうして、デバイス用支持基板60を含む第1の導電側電極80と、少なくとも1層のIII族窒化物半導体層40と、III族窒化物層30aと、第2の導電側電極70とを含む半導体デバイス7が歩留まり良く得られる。

【0059】

(チップ化工程)

図1(I)を参照して、半導体デバイス7を所定の大きさのチップに分割することにより、半導体デバイスチップ7cが得られる。半導体デバイス7をチップ化する方法は、特に制限はなく、たとえば半導体デバイス7のデバイス用支持基板60側にスクライブラインを形成し、そのスクライブラインに沿った劈開面Pで劈開することができる。

【実施例】

【0060】

(実施例1)

1.第1の複合基板の準備

図3(A)を参照して、支持基板10として直径2インチ(50.8mm)で厚さ400μmのMo基板を準備した。Mo基板(支持基板10)は、純度が99.99質量%以上で、充填率が99%以上(すなわち空隙率が1%以下)であり、その少なくとも一方の主面10mがCMP(化学機械的研磨)されて算術平均粗さRaが5nm以下の鏡面であった。Mo基板(支持基板10)の鏡面化された主面10m上にプラズマCVD法により中間層20aとして厚さ300nmのSiO2層を形成した。次いで、SiO2層(中間層20a)をCMPしてその厚さを150nmとし、その主面を算術平均粗さRaが1nm以下の鏡面とした。

【0061】

また、図3(B)を参照して、III族窒化物基板30として直径2インチ(50.8mm)で厚さ300μmのGaN基板を準備した。GaN基板(III族窒化物基板30)は、その窒素原子面側の主面30nがCMPされて算術平均粗さRaが5nm以下の鏡面であった。GaN基板(III族窒化物基板30)の鏡面化された主面30n上にプラズマCVD法により中間層20bとして厚さ300nmのSiO2層を形成した。次いで、GaN基板(III族窒化物基板30)の主面30nに形成されたSiO2層(中間層20b)側からイオン注入装置により水素イオン(プロトン)を注入することにより、主面30nから300nmの深さの位置のGaN基板(III族窒化物基板30)内にイオン注入領域30iを形成した。次いで、SiO2層(中間層20b)をCMPして、その厚さを150nmとし、その主面を算術平均粗さRaが1nm以下の鏡面とした。

【0062】

次に、図3(C)〜(E)を参照して、Mo基板(支持基板10)上に形成されたSiO2層(中間層20a)と、GaN基板(III族窒化物基板30)上に形成されたSiO2層(中間層20b)と、を重ね合わせて、7MPaの荷重を加えることにより機械的に貼り合わせて接合させた。2つのSiO2層(中間層20a,20b)は一体化して1つのSiO2層(中間層20)が形成された。これによりMo基板(支持基板10)とGaN基板(III族窒化物基板30)とがSiO2層(中間層20)を介在させて貼り合わされた接合基板が得られた。

【0063】

次に、図3(D)および図1(A)を参照して、支持基板(支持基板10)およびGaN基板(III族窒化物基板30)の上記接合基板を500℃に加熱して熱応力をかけることにより、GaN基板(III族窒化物基板30)をそのイオン注入領域30iでGaN層(III族窒化物層30a)と残りのGaN基板(残りのIII族窒化物基板30b)とに分離することにより、厚さ400μmのMo基板(支持基板10)と、Mo基板(支持基板10)の主面の少なくとも一部上に配置された厚さ300nmのSiO2層(中間層20)と、SiO2層(中間層20)の主面の少なくとも一部上に配置された厚さ300nmのGaN層(III族窒化物層30a)とを含む主面の直径が2インチ(50.8mm)の第1の複合基板1が得られた。

【0064】

図1(A)を参照して、このようにして得られた第1の複合基板1は、SiO2層(中間層20,20a,20b)の不均一、GaN基板(III族窒化物基板30)へのイオン注入の不均一、Mo基板(支持基板10)、SiO2層(中間層20,20a,20b)および/またはGaN基板(III族窒化物基板30)の結晶欠陥、残存した研磨傷および研磨残渣の除去不十分、貼り合わせの際における荷重の不均一、Mo基板(支持基板10)およびGaN基板(III族窒化物基板30)などのハンドリングの際におけるゴミの付着などにより、GaN基板(III族窒化物基板30)に由来するGaN層(III族窒化物層30a)とMo基板(支持基板10)との間の接合が部分的に不十分となり、第1の複合基板1の主面の一部に、GaN層(III族窒化物層30a)の一部が欠落しSiO2層(中間層20)の主面の一部が露出した部分および/またはGaN層(III族窒化物層30a)およびSiO2層(中間層20)の一部が欠落しMo基板(支持基板10)の主面の一部が露出した部分が存在した。第1の複合基板1の主面全体(直径2インチ(50.8mm))の面積に対してGaN層(III族窒化物層30a)が存在している主面の面積は、光学顕微鏡の画像解析により算出したところ、80%であった。

【0065】

2.第1の複合基板の中間層の露出部分のエッチングによる第2の複合基板の形成

図1(B)を参照して、第1の複合基板1を、そのMo基板(支持基板10)側の主面および側面を、アルコールワックス(たとえば日化精工(株)製アルコワックス5022)で覆った(図示せず)後、50質量%フッ化水素酸水溶液と40質量%フッ化アンモニウム水溶液を1:5の体積比で混合したバッファードフッ酸(BHF)水溶液に7分間浸漬した。これにより、第1の複合基板1においてGaN層(III族窒化物層30a)が欠落しSiO2層(中間層20)の主面が露出している部分がエッチングされて、Mo基板(支持基板10)が露出した第2の複合基板2が得られた。一方、GaN層(III族窒化物層30a)直下のSiO2層(中間層20)は、GaN層(III族窒化物層30a)がBHFによりエッチングされないため、エッチングは生じなかった。得られた第2の複合基板2を、純水でリンスしてBHFを除去した後、乾燥させた。

【0066】

3.第2の複合基板の支持基板の支持基板の露出部分を所定の深さまでのエッチングによる第3の複合基板の形成

図1(C)を参照して、第2の複合基板2を、40質量%の硝酸水溶液に2分間浸漬した。これにより、第2の複合基板2のGaN層(III族窒化物層30a)およびSiO2層(中間層20)が欠落し、Mo基板(支持基板10)の主面の一部が露出している部分では、Moが等方的にエッチングされて、エッチング窪み10eが形成されて、第3の複合基板3が得られた。エッチング窪み10eの深さは、Mo基板(支持基板10)が露出している部分の形状および/またはサイズに依存し、20μm〜30μmであった。一方、GaN層(III族窒化物層30a)およびSiO2層(中間層20)直下のMo基板(支持基板10)はGaN層およびSiO2層が硝酸によりエッチングされないため、エッチングは生じなかった。また、第2の複合基板2のMo基板(支持基板10)側の主面および側面がワックスで保護してあったため、Mo基板(支持基板10)はエッチングされなかった。第3の複合基板3を、十分に水洗して硝酸水溶液を除去した後、アセトンでワックスを除去した。さらに、剥離液(東京応化工業社製剥離液502)およびIPA(イソプロピルアルコール)による洗浄で、ワックス残渣を完全に除去した。

【0067】

4.III族窒化物半導体層の成長

図1(D)を参照して、第3の複合基板3のGaN層(III族窒化物層30a)の主面上に、MOVPE法により、III族窒化物半導体層40として以下に示す青色LED構造を構成する複数のGaN系半導体層を成長させた。すなわち、III族窒化物半導体層40として、第3の複合基板3のGaN層(III族窒化物層30a)の主面側から順に、厚さ5μmのn型GaN層、厚さ50nmのn型In0.08Ga0.92N層、3周期の厚さ3nmのIn0.14Ga0.86N井戸層および厚さ15nmのGaN障壁層で構成される多重量子井戸構造の活性層、厚さ20nmのp型Al0.08Ga0.92N層ならびに厚さ50nmのp+型GaN層を成長させた。

【0068】

このとき、第3の複合基板3のMo基板(支持基板10)の露出しているエッチング窪み10e上に、多結晶のGaN半導体(III族窒化物半導体40p)が形成された。このGaN半導体(III族窒化物半導体40p)は2μm〜10μm程度であった。

【0069】

このため、GaN半導体(III族窒化物半導体40p)の最大高さは、GaN系半導体層(III族窒化物半導体層40)の最上層の主面よりも低い位置にあった。すなわち、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)が大きくなった(TP<T(=T1+T2+T3+T4))。

【0070】

成長させたGaN系層(III族窒化物半導体層40)の各層は、その元素組成をSIMS(2次イオン質量分析)法により測定したところ、Moおよびその他の不純物は、検出されず、それらの濃度が分析感度未満であるため、LEDの性能に悪い影響を与えないものであった。

【0071】

さらに、図1(E)を参照して、GaN系層(III族窒化物半導体層40)の最上層の主面の全面に、電子ビーム蒸着法により、Ni層(厚さ5nm)/Au層(厚さ11nm)をこの順に形成し、窒素と酸素の混合ガス雰囲気中500℃でアニールすることにより、p側オーミック電極(第1の導電側オーミック電極50)とした。さらに、p側オーミック電極(第1の導電側オーミック電極50)上に、電子ビーム蒸着法により、Ti層(厚さ20nm)/Au層(厚さ300nm)をこの順に形成して、パッド層52とした。このとき、支持基板10のエッチング窪み10e上に形成されたIII族窒化物半導体40p上に堆積物50pが形成された。この堆積物50pの厚さは第1の導電側オーミック電極50の厚さとパッド層52の厚さの和にほぼ等しかったため、パッド層52の主面は堆積物50pの最高高さより高い位置にあった。

【0072】

5.デバイス用支持基板の貼り合わせ

図1(F)を参照して、デバイス用支持基板60として、直径が2インチ(50.8mm)で厚さが300μmで主面の面方位が(001)で比抵抗が0.05Ωcm以下で一方の主面がCMPされて算術平均粗さRaが5nm以下の鏡面であるSi基板を準備した。このSi基板(デバイス用支持基板60)の鏡面化された主面上に、真空加熱蒸着法により、Ti層(厚さ20nm)/Au層(厚さ300nm)/AuSn層(厚さ1.5μmでAu:Snの質量比が8:2)をこの順で形成し、パッド層62とした。

【0073】

次いで、Si基板(デバイス用支持基板60)上に形成したパッド層62と、Mo基板(第3の複合基板3)上に順次形成したGaN層(III族窒化物層30a)、GaN系半導体層(III族窒化物半導体層40)、p側オーミック電極(第1の導電側オーミック電極50)およびパッド層52と、を重ね合わせ、Si基板(デバイス用支持基板60)の(100)面の結晶方位と、GaN層(III族窒化物層30a)およびGaN系半導体層(III族窒化物半導体層40)の(0001)面の結晶方位とが±0.3°以内になる様に調整した後、真空(0.1Pa未満)中で100kgfの荷重を印加しつつ300℃まで加熱し、パッド層62のAuSnとパッド層52のAuとの拡散接合により、Si基板(デバイス用支持基板60)と第3の複合基板3とが接合された積層基板4が得られた。超音波顕微鏡で積層基板4の接合界面の状態を観察したところ、第3の複合基板3を作製したときにGaN層(III族窒化物層30a)が欠落していた部分とその欠落部の外周から数百μmの領域では空隙(未接合状態)が観察されたが、GaN層が存在した部分では、空隙のない均一な接合が得られた。

【0074】

6.支持基板の除去

図1(F)および(G)を参照して、上記の積層基板4を30質量%硝酸水溶液に45分間浸漬した。これにより、Mo基板(支持基板10)は完全に除去された。積層基板4を水洗し硝酸水溶液を除去した後、上記のBHF水溶液に10分間浸漬し、SiO2層(中間層20)を完全に溶解除去した。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)およびGaN層(III族窒化物層30a)がこの順に接合された半導体ウエハ5が得られた。

【0075】

こうして得られた半導体ウエハ5について、その最上層であるGaN層(III族窒化物層30a)には、クラックなどはみられなかった。また、半導体ウエハ5の主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率は、75%であった。

【0076】

なお、本発明を適用せずに、第1の複合基板1を用いて作製した半導体ウエハは、その主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率が10%〜20%であり、GaN層(III族窒化物層30a)の欠落部分を起点にして数百μm〜数mmにわたりGaN層(III族窒化物層30a)にクラックが生じている場合があった。

【0077】

図1(G)および(H)を参照して、上記の半導体ウエハ5のGaN層(III族窒化物層30a)を、Cl2ガスを用いたRIEにより、除去して、GaN系半導体層(III族窒化物半導体層40)を露出させた。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)が接合された半導体ウエハ6が得られた。

【0078】

7.電極の形成

図1(H)および(I)を参照して、半導体ウエハ6のGaN層(III族窒化物層30a)上にフォトリソグラフィー法で形成したレジストパターン上に、電子ビーム蒸着法により、Ti層(厚さ20nm)/Al層(厚さ200nm)/Ti層(厚さ20nm)/Pt層(厚さ20nm)/Au層(厚さ300nm)をこの順に形成し、リフトオフ法により後述の半導体デバイスのチップ化された1領域(1チップ領域)である400μm角あたり1つ存在するように形成して、n側電極(第2の導電側電極70)とした。また、Si基板(デバイス用支持基板60)を、後述のチップ化を容易にするために、厚さが150μmになるまで機械的研磨およびCMPした後に、パッド層62が形成されていない側の主面の全面に、電子ビーム蒸着法により、Ti層(厚さ20nm)/Au層(厚さ300nm)をこの順に形成し、パッド電極64とした。このようにして半導体デバイス7が得られた。半導体デバイス7において、p側オーミック電極(第1の導電側オーミック電極50)、パッド層52,62、デバイス用支持基板60およびパッド電極64によりp側電極(第1の導電側電極80)が構成された。

【0079】

8.チップ化

図1(I)を参照して、半導体デバイス7において、それに形成されたn側電極(第2の導電側電極70)の配置パターンに対応するように、Si基板(デバイス用支持基板60)のパッド電極64側にダイヤペンで400μm角のスクライブラインを形成し、ブレーカを用いて半導体デバイス7をスクライブラインに沿って劈開することにより、大きさが400μm角の半導体デバイスチップ7cが得られた。

【0080】

9.実装

半導体デバイス(発光デバイス)用のステム(または表面実装用パッケージ)(図示せず)の第1の導電側部位に、銀ペーストを用いて半導体デバイスチップ7cのp側電極(第1の導電側電極80)を構成するSi基板(デバイス用支持基板60)のパッド電極64を電気的に接続した。また、半導体デバイスチップ7cのn側電極(第2の導電側電極70)を、金ワイヤを用いて、ステムの第2の導電側部位に電気的に接続した。このように、第3の複合基板3を用いて半導体デバイスチップ7cを作製し実装することにより、実装サンプル中の良品の歩留まり率(5Vの逆バイアス電圧を印加したときのリーク電流が100μA未満の半導体デバイスチップを良品とする)は、90%以上となった。

【0081】

(実施例2)

1.第1の複合基板の準備

図1(A)および図3を参照して、中間層20,20a,20bとしてSi3N4層を用いたこと以外は、実施例1と同様にして、厚さ400μmのMo基板(支持基板10)と、Mo基板(支持基板10)の主面の少なくとも一部上に配置された厚さ300nmのSi3N4層(中間層20)と、Si3N4層(中間層20)の主面の少なくとも一部上に配置された厚さ300nmのGaN層(III族窒化物層30a)とを含む主面の直径が2インチ(50.8mm)の第1の複合基板1が得られた。

【0082】

本実施例の第1の複合基板1は、実施例1の第1の複合基板1と同様に、第1の複合基板1の主面の一部に、GaN層(III族窒化物層30a)の一部が欠落しSi3N4層(中間層20)の主面の一部が露出した部分および/またはGaN層(III族窒化物層30a)およびSi3N4層(中間層20)の一部が欠落しMo基板(支持基板10)の主面の一部が露出した部分が存在した。第1の複合基板1の主面全体(直径2インチ(50.8mm))の面積に対してGaN層(III族窒化物層30a)が存在している主面の面積は、80%であった。

【0083】

2.第1の複合基板の中間層の露出部分のエッチングによる第2の複合基板の形成

図1(B)を参照して、第1の複合基板1を、CF4ガスを用いたRIEで処理した。これにより、第1の複合基板1においてGaN層(III族窒化物層30a)が欠落しSi3N4層(中間層20)の主面が露出している部分がエッチングされて、Mo基板(支持基板10)が露出した第2の複合基板2が得られた。一方、GaN層(III族窒化物層30a)直下のSi3N4層(中間層20)は、GaN層(III族窒化物層30a)がCF4ガスを用いたRIEによりエッチングされないため、エッチングは生じなかった。

【0084】

3.第2の複合基板の支持基板の支持基板の露出部分を所定の深さまでのエッチングによる第3の複合基板の形成

図1(C)を参照して、得られた第2の複合基板2を、そのMo基板(支持基板10)側の主面および側面を、アルコールワックス(たとえば日化精工(株)製アルコワックス5022)で覆った(図示せず)後、30質量%の硝酸水溶液に2分間浸漬した。これにより、第2の複合基板2のGaN層(III族窒化物層30a)およびSi3N4層(中間層20)が欠落し、Mo基板(支持基板10)の主面の一部が露出している部分では、Moが等方的にエッチングされて、エッチング窪み10eが形成されて、第3の複合基板3が得られた。エッチング窪み10eの深さは、Mo基板(支持基板10)が露出している部分の形状および/またはサイズに依存し、10μm〜30μmであった。一方、GaN層(III族窒化物層30a)およびSi3N4層(中間層20)直下のMo基板(支持基板10)はGaN層およびSi3N4層が硝酸によりエッチングされないため、エッチングは生じなかった。また、第2の複合基板2のMo基板(支持基板10)側の主面および側面がワックスで保護してあったため、Mo基板(支持基板10)はエッチングされなかった。第3の複合基板3を、十分に水洗して硝酸水溶液を除去した後、アセトンでワックスを除去した。さらに、剥離液(東京応化工業社製剥離液502)およびIPA(イソプロピルアルコール)による洗浄で、CF4ガスを用いたRIEで生じた副生成物およびワックス残渣を完全に除去した。

【0085】

4.III族窒化物半導体層の成長

図1(D)を参照して、実施例1と同様にして、第3の複合基板3のGaN層(III族窒化物層30a)の主面上に、III族窒化物半導体層40として、第3の複合基板3のGaN層(III族窒化物層30a)の主面側から順に、厚さ5μmのn型GaN層、厚さ50nmのn型In0.08Ga0.92N層、3周期の厚さ3nmのIn0.14Ga0.86N井戸層および厚さ15nmのGaN障壁層で構成される多重量子井戸構造の活性層、厚さ20nmのp型Al0.08Ga0.92N層ならびに厚さ50nmのp+型GaN層を成長させた。

【0086】

このとき、第3の複合基板3のMo基板(支持基板10)の露出しているエッチング窪み10e上に、多結晶のGaN半導体(III族窒化物半導体40p)が形成された。このGaN半導体(III族窒化物半導体40p)は2μm〜10μm程度であった。

【0087】

このため、GaN半導体(III族窒化物半導体40p)の最大高さは、GaN系半導体層(III族窒化物半導体層40)の最上層の主面よりも低い位置にあった。すなわち、不均一に成長したIII族窒化物半導体40pの最高高さTPよりも、支持基板10のエッチング窪み10eの深さT1、中間層20のエッチングにより除去された厚さT2、III族窒化物層30aの厚さT3およびIII族窒化物半導体層40の厚さT4の和T(T=T1+T2+T3+T4)が大きくなった(TP<T(=T1+T2+T3+T4))。

【0088】

成長させたGaN系層(III族窒化物半導体層40)の各層は、その元素組成をSIMS(2次イオン質量分析)法により測定したところ、Moおよびその他の不純物は、検出されず、それらの濃度が分析感度未満であるため、LEDの性能に悪い影響を与えないものであった。

【0089】

さらに、図1(E)を参照して、実施例1と同様にして、GaN系層(III族窒化物半導体層40)の最上層の主面の全面上にp側オーミック電極(第1の導電側オーミック電極50)を形成し、p側オーミック電極(第1の導電側オーミック電極50)上にパッド層52を形成した。

【0090】

5.デバイス用支持基板の貼り合わせ

図1(F)を参照して、実施例1と同様にして、Si基板(デバイス用支持基板60)を準備し、その鏡面化された主面上にパッド層62を形成した。次いで、実施例1同様にして、Si基板(デバイス用支持基板60)上に形成されたパッド層62と、Mo基板(第3の複合基板3)上に順次形成したGaN層(III族窒化物層30a)、GaN系半導体層(III族窒化物半導体層40)、p側オーミック電極(第1の導電側オーミック電極50)を介在させて形成されたパッド層52と、を重ね合わせることにより、Si基板(デバイス用支持基板60)と第3の複合基板3とが接合された積層基板4が得られた。超音波顕微鏡で積層基板4の接合界面の状態を観察したところ、第3の複合基板3を作製したときにGaN層(III族窒化物層30a)が欠落していた部分とその欠落部の外周から数百μmの領域では空隙(未接合状態)が観察されたが、GaN層が存在した部分では、空隙のない均一な接合が得られた。

【0091】

6.支持基板の除去

図1(F)および(G)を参照して、実施例1と同様にして、上記の積層基板4を30質量%硝酸水溶液に45分間浸漬することにより、Mo基板(支持基板10)を完全に除去した。その後、積層基板4を水洗し硝酸水溶液を水洗した。次いで、CF4ガスを用いたRIEにより、Si3N4層(中間層20)を完全に除去した。さらに、CF4ガスを用いたRIEにより生成した副生成物を、O2を用いたRIEにより除去した。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)およびGaN層(III族窒化物層30a)がこの順に接合された半導体ウエハ5が得られた。

【0092】

こうして得られた半導体ウエハ5について、その最上層であるGaN層(III族窒化物層30a)には、クラックなどはみられなかった。また、半導体ウエハ5の主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率は、75%であった。

【0093】

なお、本発明を適用せずに、第1の複合基板1を用いて作製した半導体ウエハは、その主面全体の面積に対するGaN層(III族窒化物層30a)が存在している面積の比率が10%〜20%であり、GaN層(III族窒化物層30a)の欠落部分を起点にして数百μm〜数mmにわたりGaN層(III族窒化物層30a)にクラックが生じている場合があった。

【0094】

図1(G)および(H)を参照して、上記の半導体ウエハ5のGaN層(III族窒化物層30a)を、Cl2ガスを用いたRIEにより、除去して、GaN系半導体層(III族窒化物半導体層40)を露出させた。これにより、Si基板(デバイス用支持基板60)にパッド層62,52を介在してGaN系半導体層(III族窒化物半導体層40)が接合された半導体ウエハ6が得られた。

【0095】

7.電極の形成

図1(H)および(I)を参照して、実施例1と同様にして、半導体ウエハ6のGaN層(III族窒化物層30a)上に、後述の半導体デバイスのチップ化された1領域(1チップ領域)である400μm角あたり1つ存在するように、n側電極(第2の導電側電極70)を形成した。次いで、実施例1と同様にして、Si基板(デバイス用支持基板60)を、厚さが150μmになるまで機械的研磨およびCMPした後に、パッド層62が形成されていない側の主面の全面に、パッド電極64を形成した。このようにして半導体デバイス7が得られた。半導体デバイス7において、p側オーミック電極(第1の導電側オーミック電極50)、パッド層52,62、デバイス用支持基板60およびパッド電極64によりp側電極(第1の導電側電極80)が構成された。

【0096】

8.チップ化

図1(I)を参照して、実施例1と同様にして、半導体デバイス7を劈開することにより、大きさが400μm角の半導体デバイスチップ7cが得られた。

【0097】

9.実装

実施例1と同様にして、半導体デバイス(発光デバイス)用のステムに半導体デバイスチップ7cを実装した。実装サンプル中の良品の歩留まり率(5Vの逆バイアス電圧を印加したときのリーク電流が100μA未満の半導体デバイスチップを良品とする)は、90%以上となった。

【0098】

実施例1および実施例2を参照して、本発明にかかる複合基板の製造方法により得られる第3の複合基板を用いて半導体デバイスを製造することにより、高い歩留まり率で半導体デバイスを製造することができた。

【0099】

今回開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0100】

1 第1の複合基板、2 第2の複合基板、3 第3の複合基板、4 積層基板、5,6 半導体ウエハ、7 半導体デバイス、7c 半導体デバイスチップ、10 支持基板、10e エッチング窪み、10m,30n 主面、20,20a,20b 中間層、30 III族窒化物基板、30a III族窒化物層GaN層、30b 残りのIII族窒化物基板、40 III族窒化物半導体層、40p III族窒化物半導体、50 第1の導電側オーミック電極、50p 堆積物、52,62 パッド層、60 デバイス用支持基板、64 パッド電極、70 第2の導電側電極、80 第1の導電側電極。

【特許請求の範囲】

【請求項1】

支持基板と、前記支持基板の主面の少なくとも一部上に配置された中間層と、前記中間層の主面の少なくとも一部上に配置されたIII族窒化物層と、を含み、前記III族窒化物層の主面と、前記中間層の主面の一部および前記支持基板の主面の一部の少なくともいずれかと、が露出している第1の複合基板を準備する工程と、

前記第1の複合基板の前記中間層の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板を得る工程と、

前記第2の複合基板の前記支持基板の主面が露出している部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板を得る工程と、を含む複合基板の製造方法。

【請求項2】

前記中間層は、その上におけるIII族窒化物半導体の成長が不均一である(請求項1に記載の複合基板の製造方法。

【請求項3】

前記中間層は、ケイ素酸化物、ケイ素窒化物、金属酸化物、金属窒化物およびこれらの複合物からなる群から選ばれる少なくとも一つを含む請求項2に記載の複合基板の製造方法。

【請求項4】

前記支持基板は、その上におけるIII族窒化物半導体の成長が不均一である請求項1に記載の複合基板の製造方法。

【請求項5】

前記支持基板は、ケイ素酸化物、金属酸化物、多結晶GaN、多結晶SiC、Cu、WおよびMoからなる群から選ばれる少なくとも一つを含む請求項4に記載の複合基板の製造方法。

【請求項6】

請求項1に記載の複合基板の製造方法により得られた前記第3の複合基板の前記III族窒化物層の主面上に少なくとも1層のIII族窒化物半導体層をエピタキシャル成長させる工程を含む半導体デバイスの製造方法。

【請求項7】

前記III族窒化物層の厚さと、前記中間層のエッチングにより除去された部分の厚さと、前記支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さとの和が、エピタキシャル成長させる前記III族窒化物半導体層の厚さより大きい請求項6に記載の半導体デバイスの製造方法。

【請求項8】

前記III族窒化物層の厚さと、前記中間層のエッチングにより除去された部分の厚さと、前記支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さと、エピタキシャル成長させた前記III族窒化物半導体層の厚さとの和が、前記III族窒化物半導体層のエピタキシャル成長の際に前記支持基板の前記エッチング窪み上に不均一に成長したIII族窒化物半導体の最大高さよりも大きい請求項6に記載の半導体デバイスの製造方法。

【請求項1】

支持基板と、前記支持基板の主面の少なくとも一部上に配置された中間層と、前記中間層の主面の少なくとも一部上に配置されたIII族窒化物層と、を含み、前記III族窒化物層の主面と、前記中間層の主面の一部および前記支持基板の主面の一部の少なくともいずれかと、が露出している第1の複合基板を準備する工程と、

前記第1の複合基板の前記中間層の主面が露出している部分を選択的にエッチングにより除去することにより第2の複合基板を得る工程と、

前記第2の複合基板の前記支持基板の主面が露出している部分を所定の深さまで選択的にエッチングにより除去することにより第3の複合基板を得る工程と、を含む複合基板の製造方法。

【請求項2】

前記中間層は、その上におけるIII族窒化物半導体の成長が不均一である(請求項1に記載の複合基板の製造方法。

【請求項3】

前記中間層は、ケイ素酸化物、ケイ素窒化物、金属酸化物、金属窒化物およびこれらの複合物からなる群から選ばれる少なくとも一つを含む請求項2に記載の複合基板の製造方法。

【請求項4】

前記支持基板は、その上におけるIII族窒化物半導体の成長が不均一である請求項1に記載の複合基板の製造方法。

【請求項5】

前記支持基板は、ケイ素酸化物、金属酸化物、多結晶GaN、多結晶SiC、Cu、WおよびMoからなる群から選ばれる少なくとも一つを含む請求項4に記載の複合基板の製造方法。

【請求項6】

請求項1に記載の複合基板の製造方法により得られた前記第3の複合基板の前記III族窒化物層の主面上に少なくとも1層のIII族窒化物半導体層をエピタキシャル成長させる工程を含む半導体デバイスの製造方法。

【請求項7】

前記III族窒化物層の厚さと、前記中間層のエッチングにより除去された部分の厚さと、前記支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さとの和が、エピタキシャル成長させる前記III族窒化物半導体層の厚さより大きい請求項6に記載の半導体デバイスの製造方法。

【請求項8】

前記III族窒化物層の厚さと、前記中間層のエッチングにより除去された部分の厚さと、前記支持基板のエッチングにより除去された部分により形成されたエッチング窪みの深さと、エピタキシャル成長させた前記III族窒化物半導体層の厚さとの和が、前記III族窒化物半導体層のエピタキシャル成長の際に前記支持基板の前記エッチング窪み上に不均一に成長したIII族窒化物半導体の最大高さよりも大きい請求項6に記載の半導体デバイスの製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−115112(P2013−115112A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257611(P2011−257611)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

[ Back to top ]